Page 1

5

Vinafix.com

Table of Contents

4

3

2

1

Page

D D

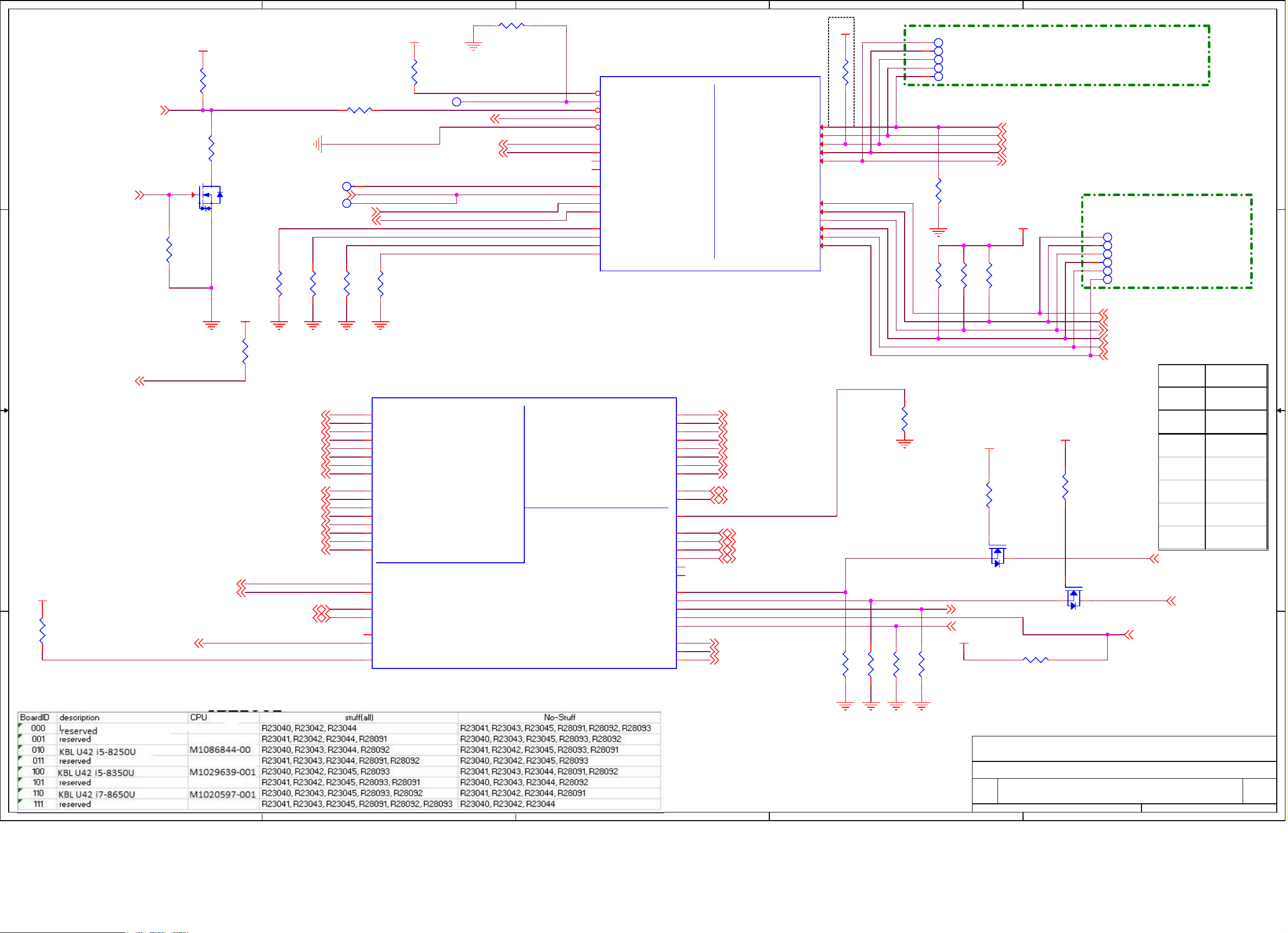

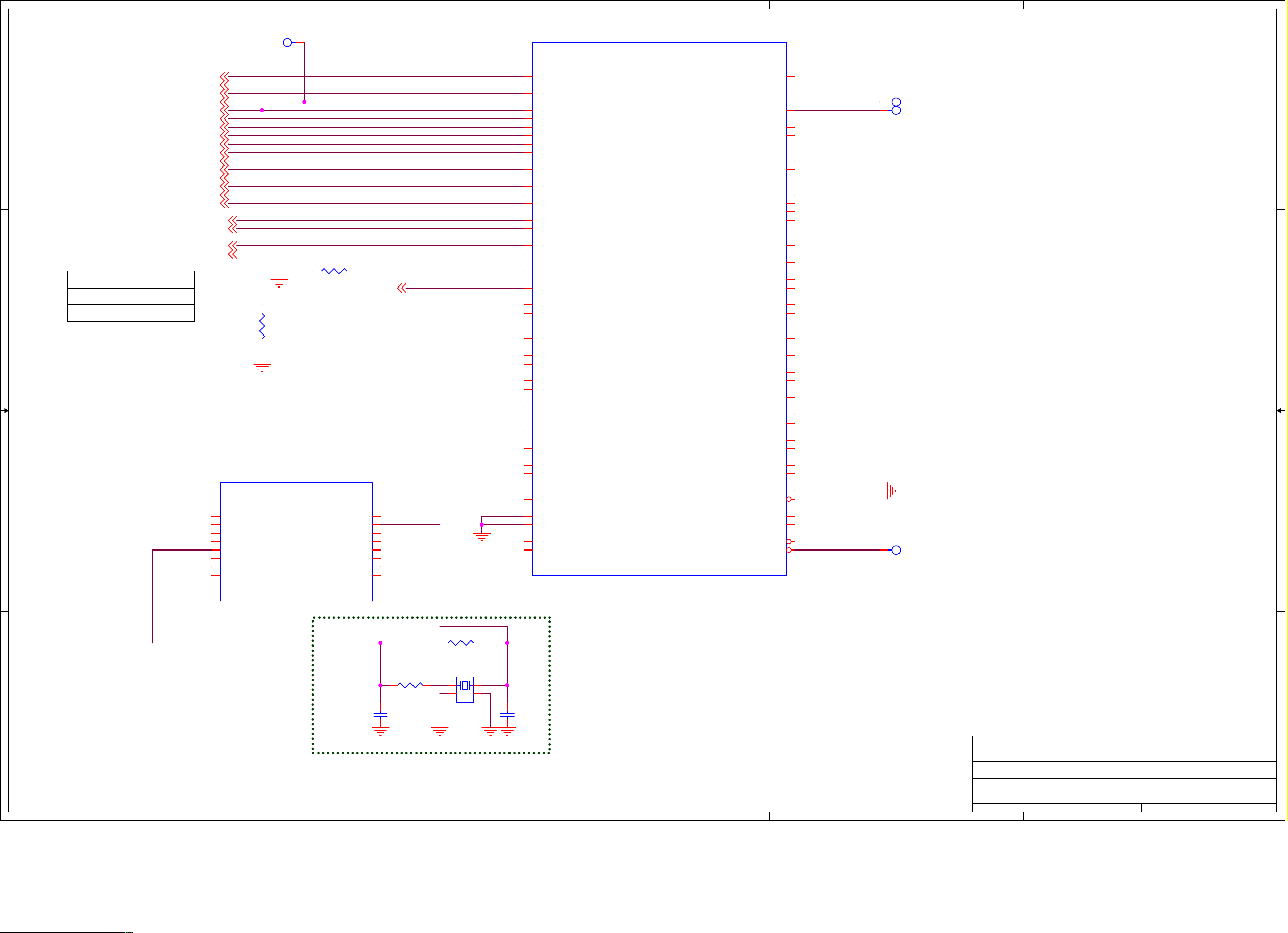

01 Table of Contents

02 CHANGE HISTORY

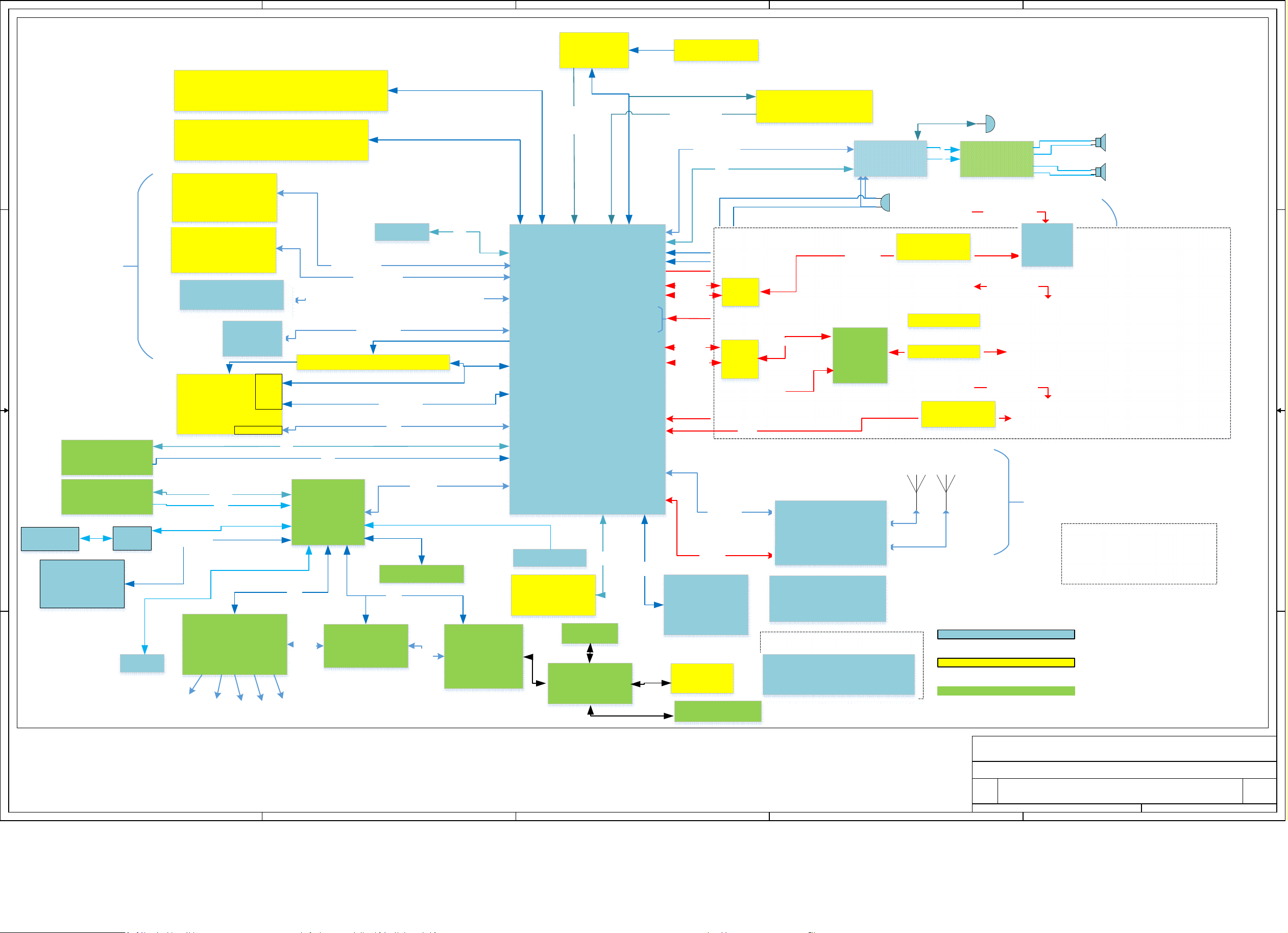

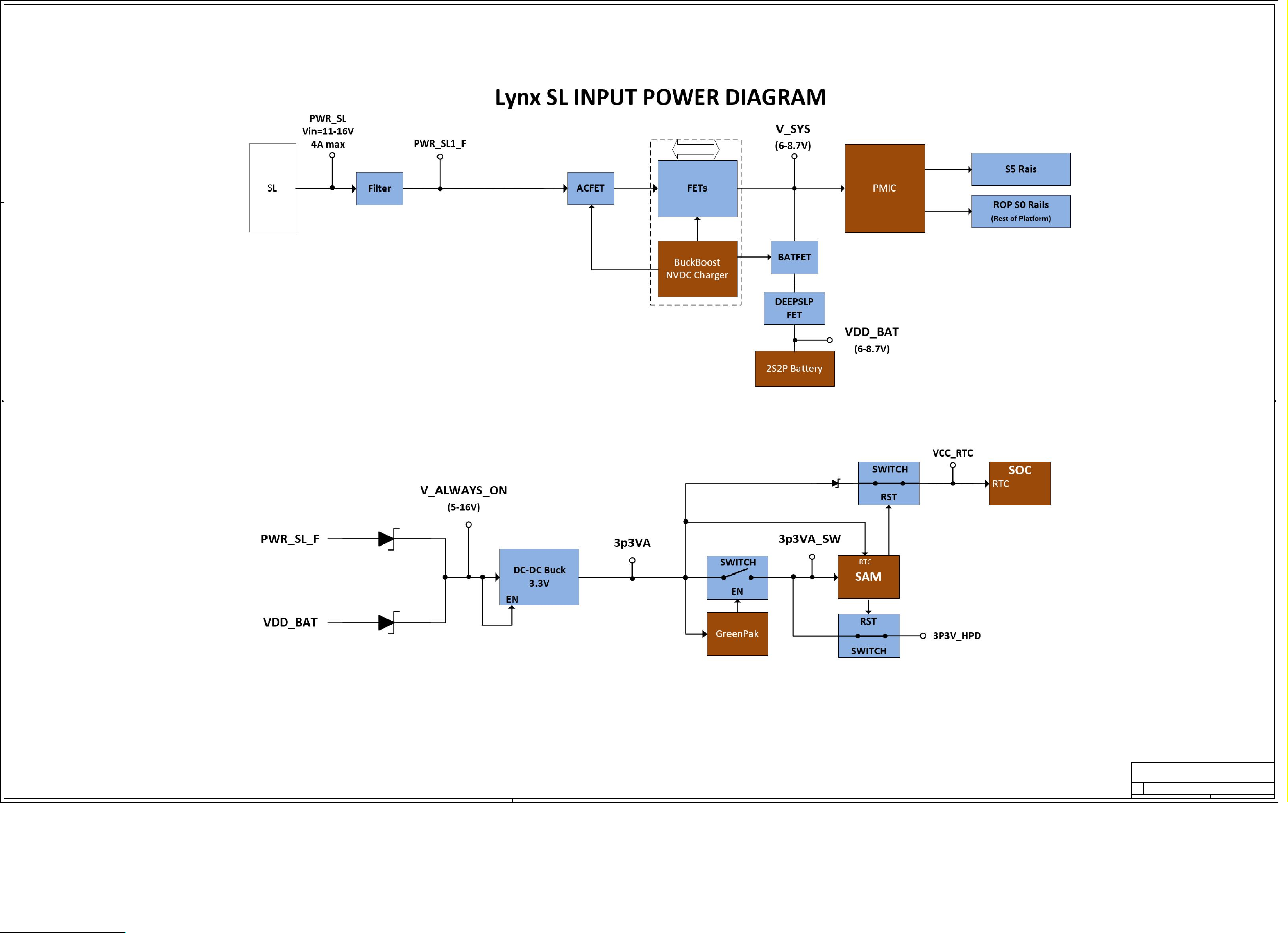

03 BLOCK DIAGRAM

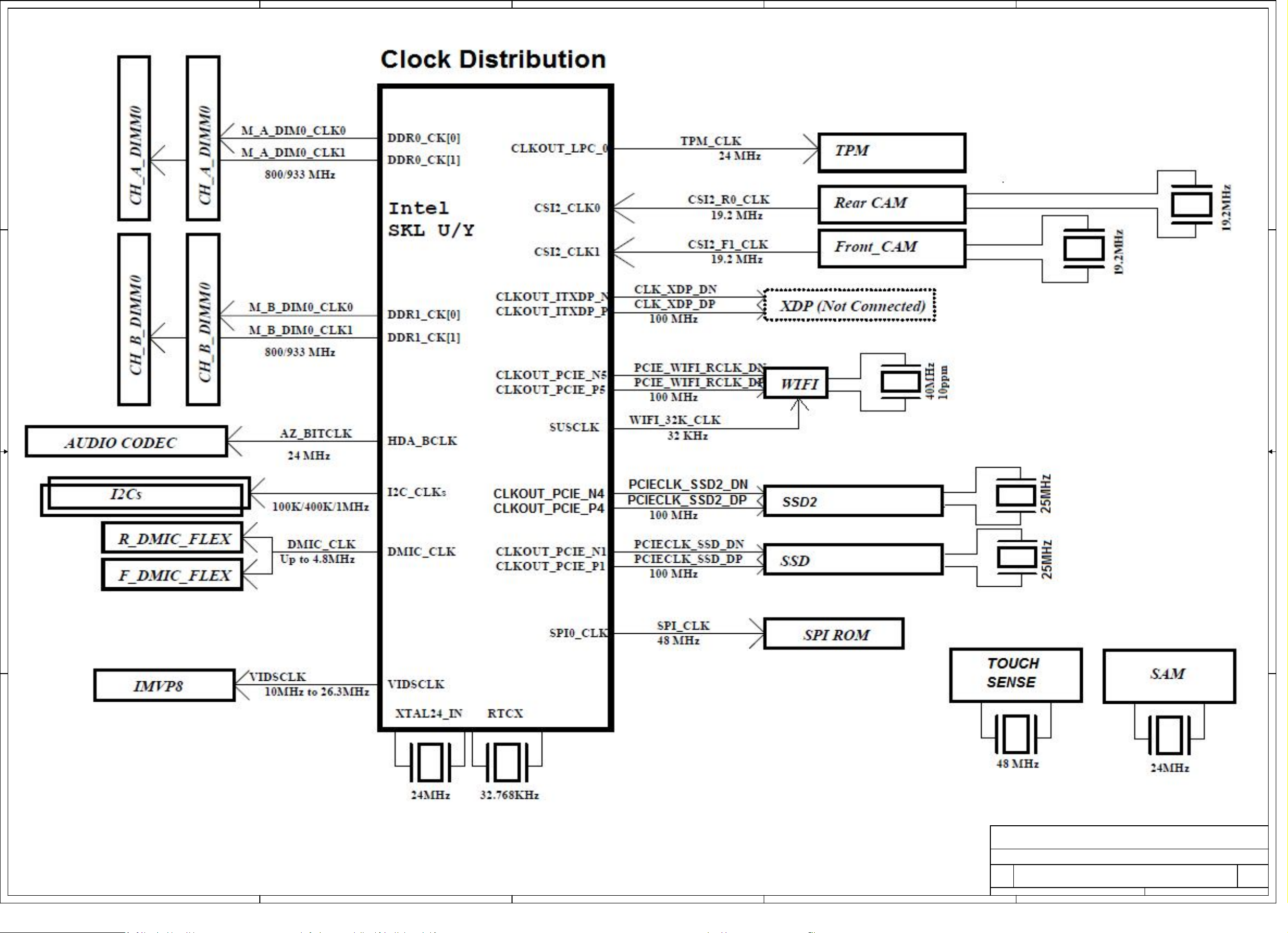

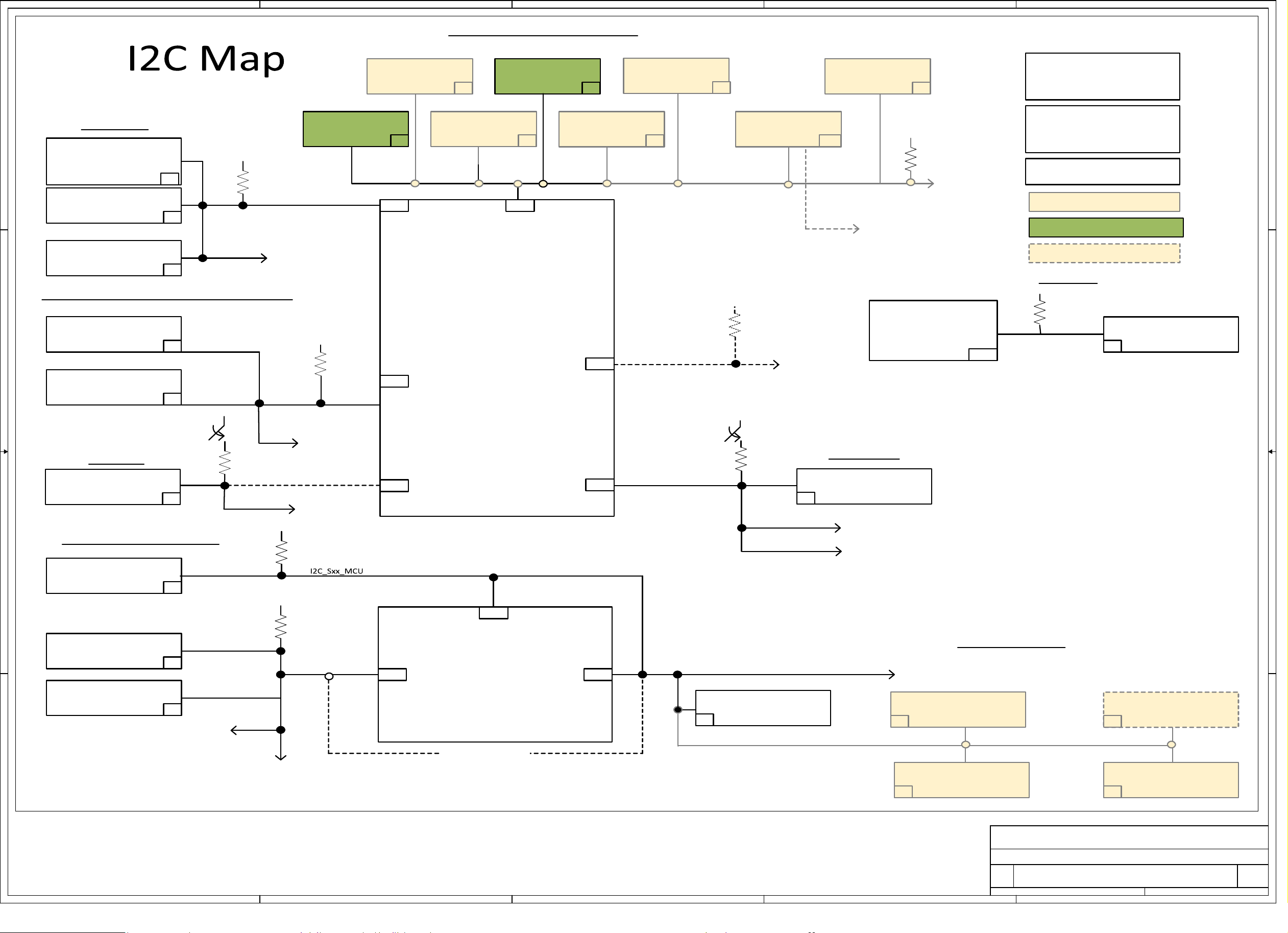

04 CLOCK DISTRIBUTION

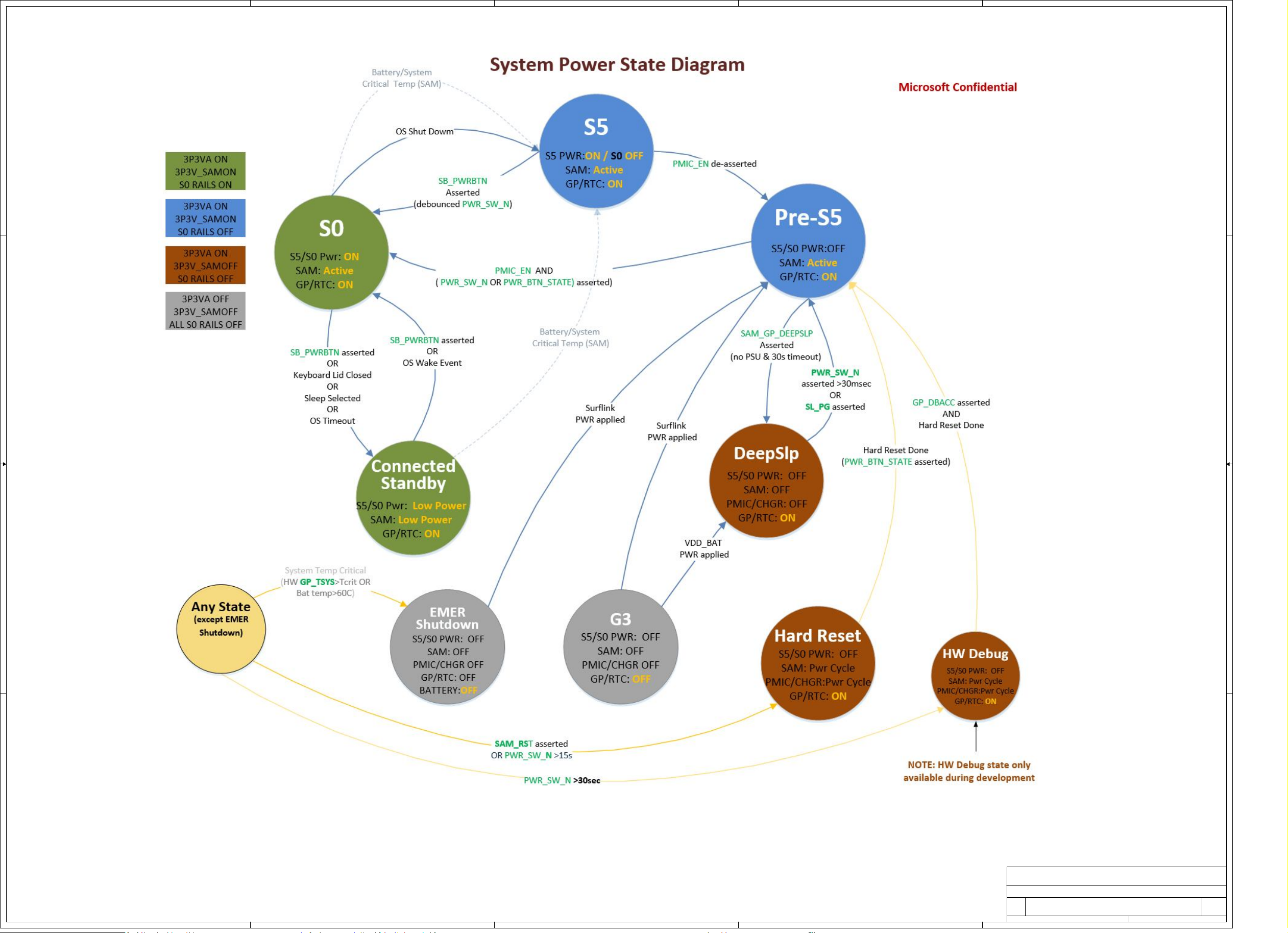

05 SYSTEM POWER STATE DIAGRAM

06 POWER DISTRIBUTION

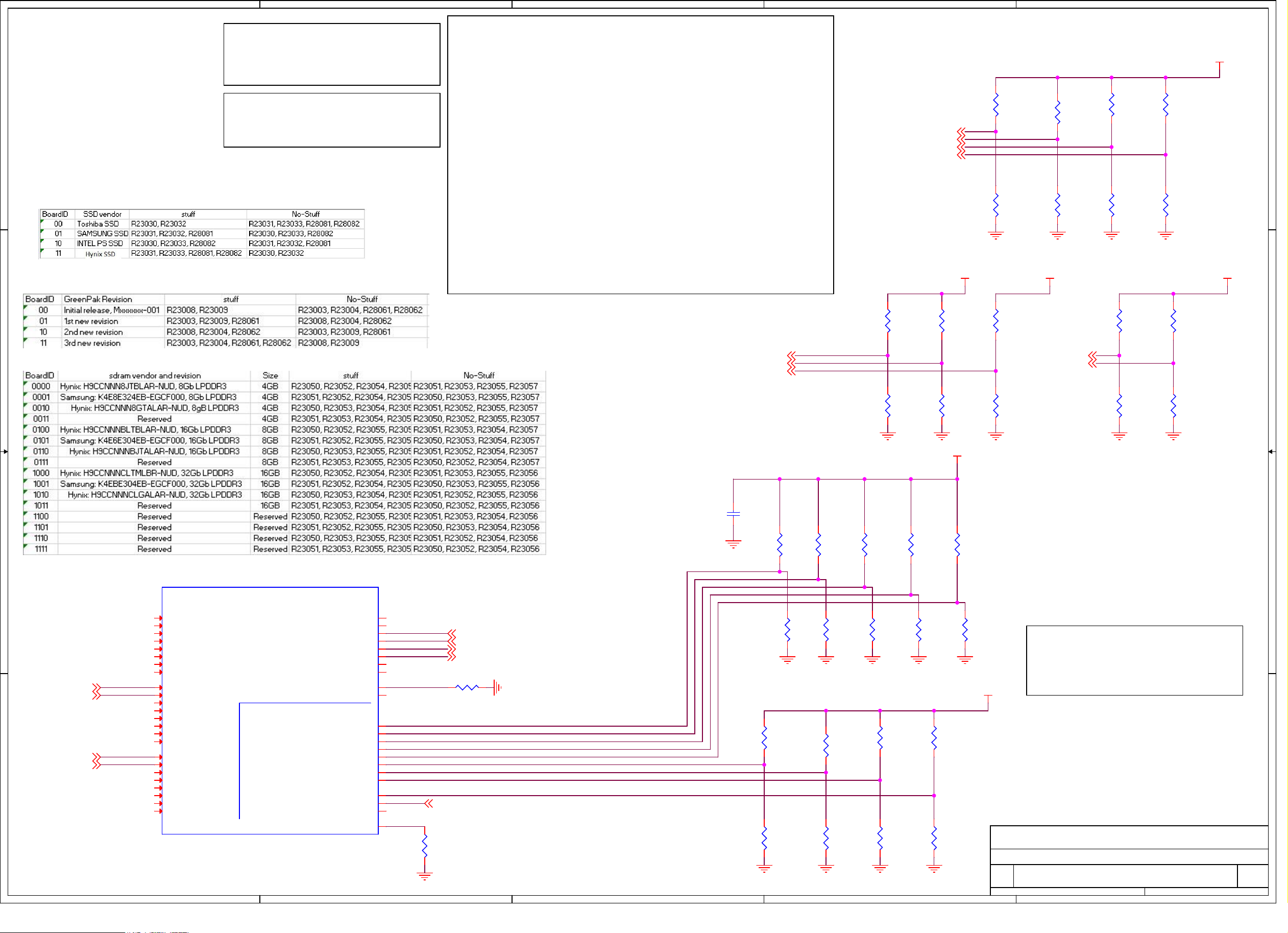

07 INPUT POWER DIAGRAM

08 POWER SYSTEM/CONTROL DIAG

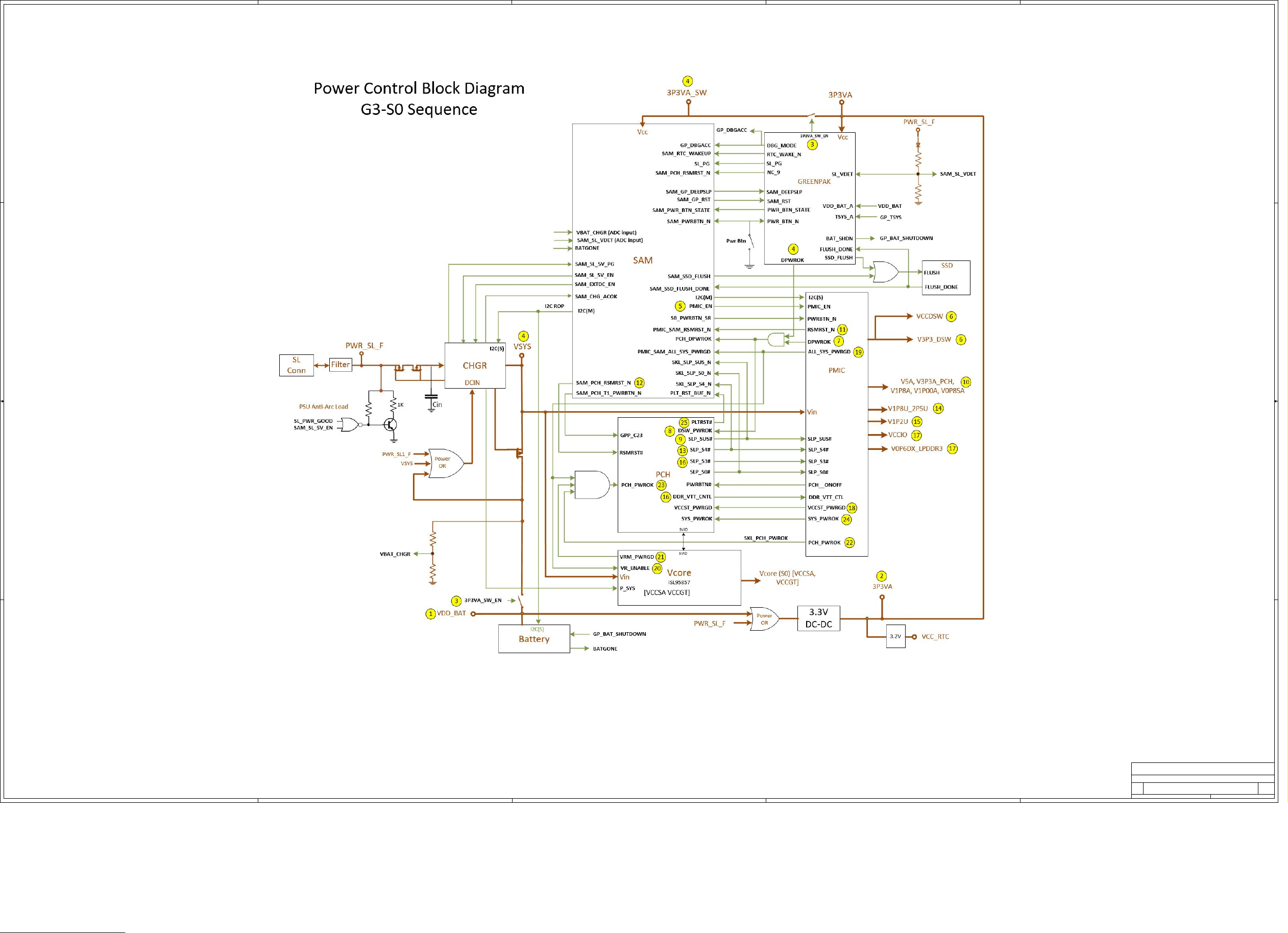

09 I2C MAP

10 CPU(1)_MISC,JTAG,DDI.EDP

C C

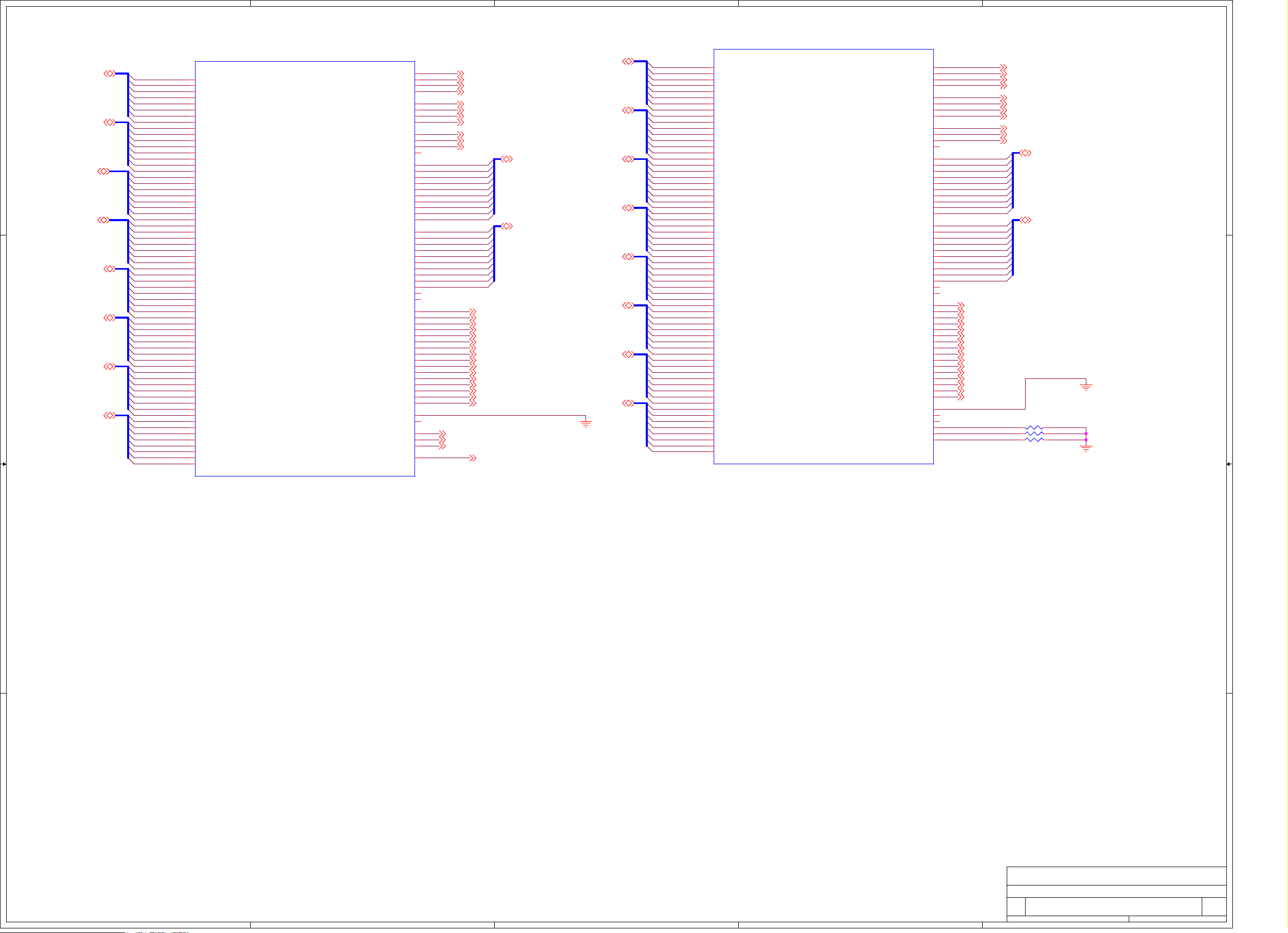

11 CPU(2)_LPDDR3

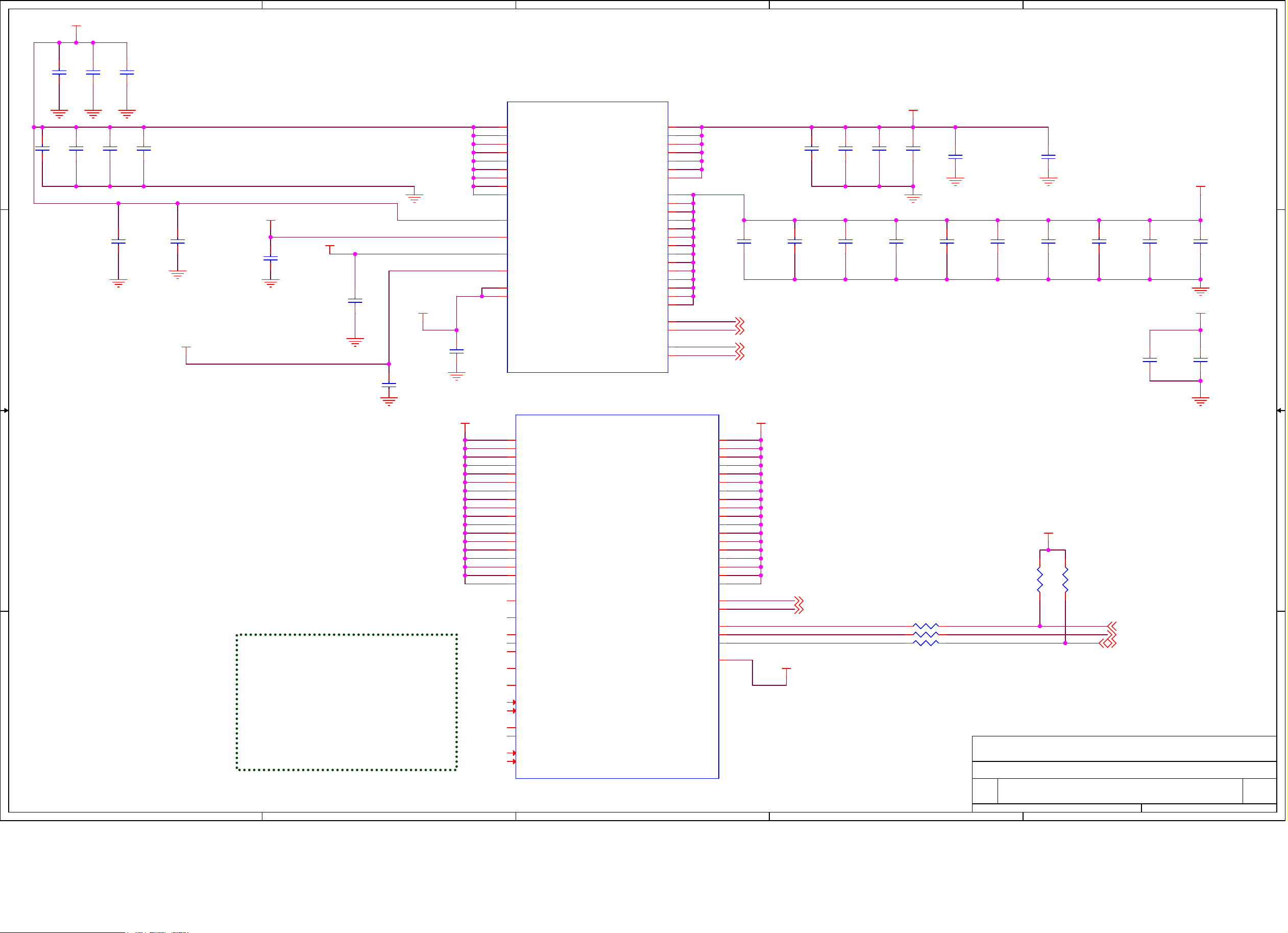

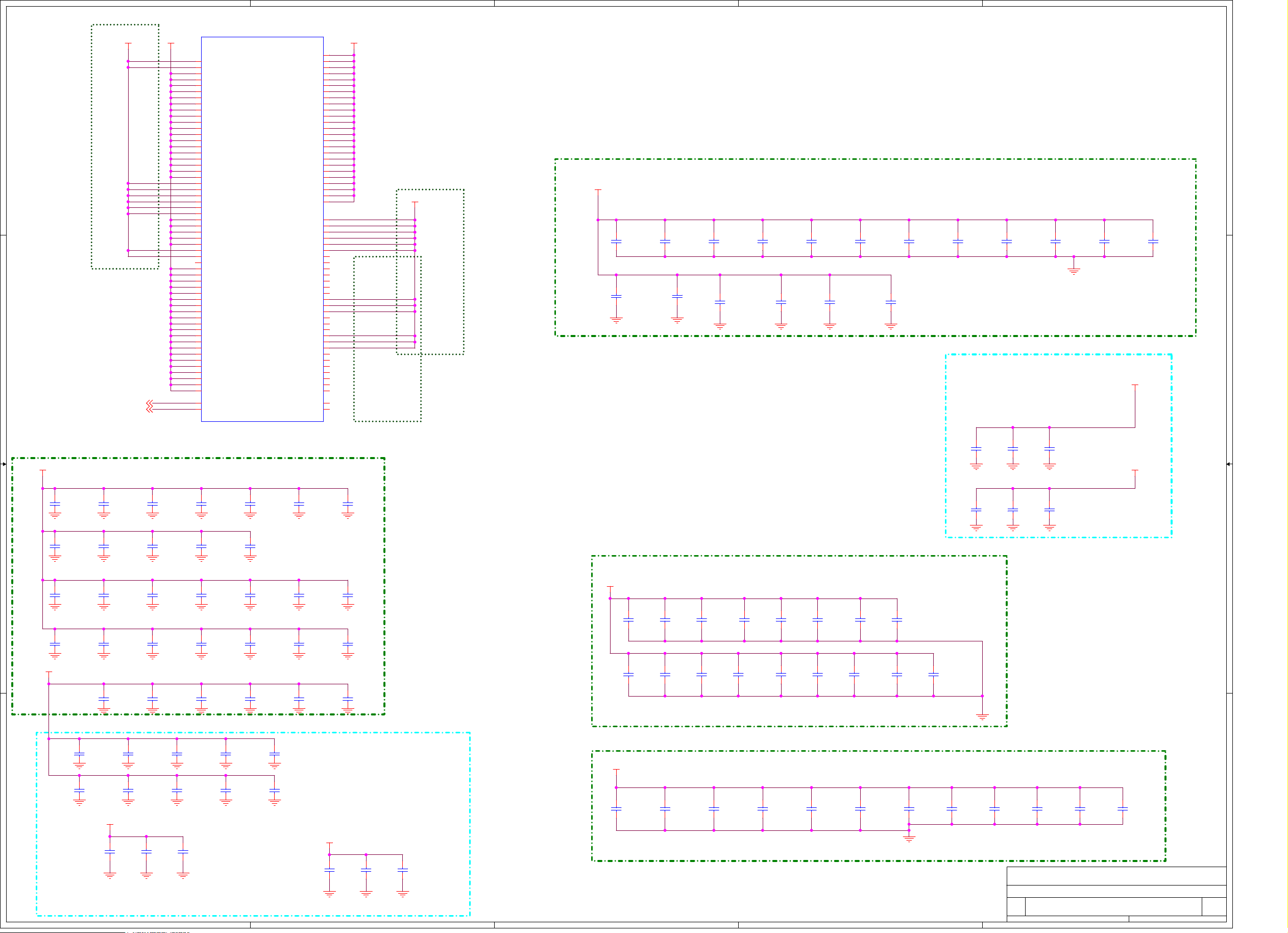

12 CPU(3)_SKL POWER1

Title

Page

Title

31 Debug mux

32 Debug buttons

33 SW Debug Conn

34 EE Debug Connector

35 SM BUS, DIAGNOSTIC CONN

36 Power Monitor

37 SPI ROM UEFI

38 TPM

39 Temp Sensor/System Fan

40 REALTEK ALC3269 CODEC

41 Audio Jack/Spkr

42 Audio Amplifier

Page

Title

61 Discrete Load Switches

62 1.8VSB & Load SW

63 CHARGER

64 5V Load SW

65 3P3V Load SW

66 VCPU Controller

67 VCORE VCCSA

68 VCVGT

69 SL Power

70 BATT CONN, power input

71 Empty

72 LCD backlight/TB

13 CPU(4)_SKL_POWER2

14 CPU(5)_GND

15 CPU(6)_CFG_RESERVED

16 LPDDR3(1)_MEMORY DOWN

17 LPDDR3(2)_MEMORY DOWN

18 XDP

19 LPDDR3(3)_CA/DQ Voltage

20 PCH(1)_SD,HDA,RTC, CLK

B B

21 PCH(2)_CLK,SMB,LPC, SPI

22 PCH(3)_SYS PWR CONTR

23 PCH(4)_CCI, HWID

24 PCH(5)_PCIE,USB

25 PCH(6)_CPU,GPIO,MISC

26 PCH(7)_POWER

43 SSD page 1

44 SSD Page 2

45 USB3.0, TYPE A

46 SL HDMI MUX/3P3V_HPD

47 SurfLink Connector

48 BLADE

49 G5 touch circuitry

50 Wi-Fi_BT

51 Empty

52 Empty

53 mDP

54 Camera/Sensor Conn.

55 eDP connector

56 3P3VA & Reset

73 Empty

74 Empty

75 Empty

76 TP's and Mech

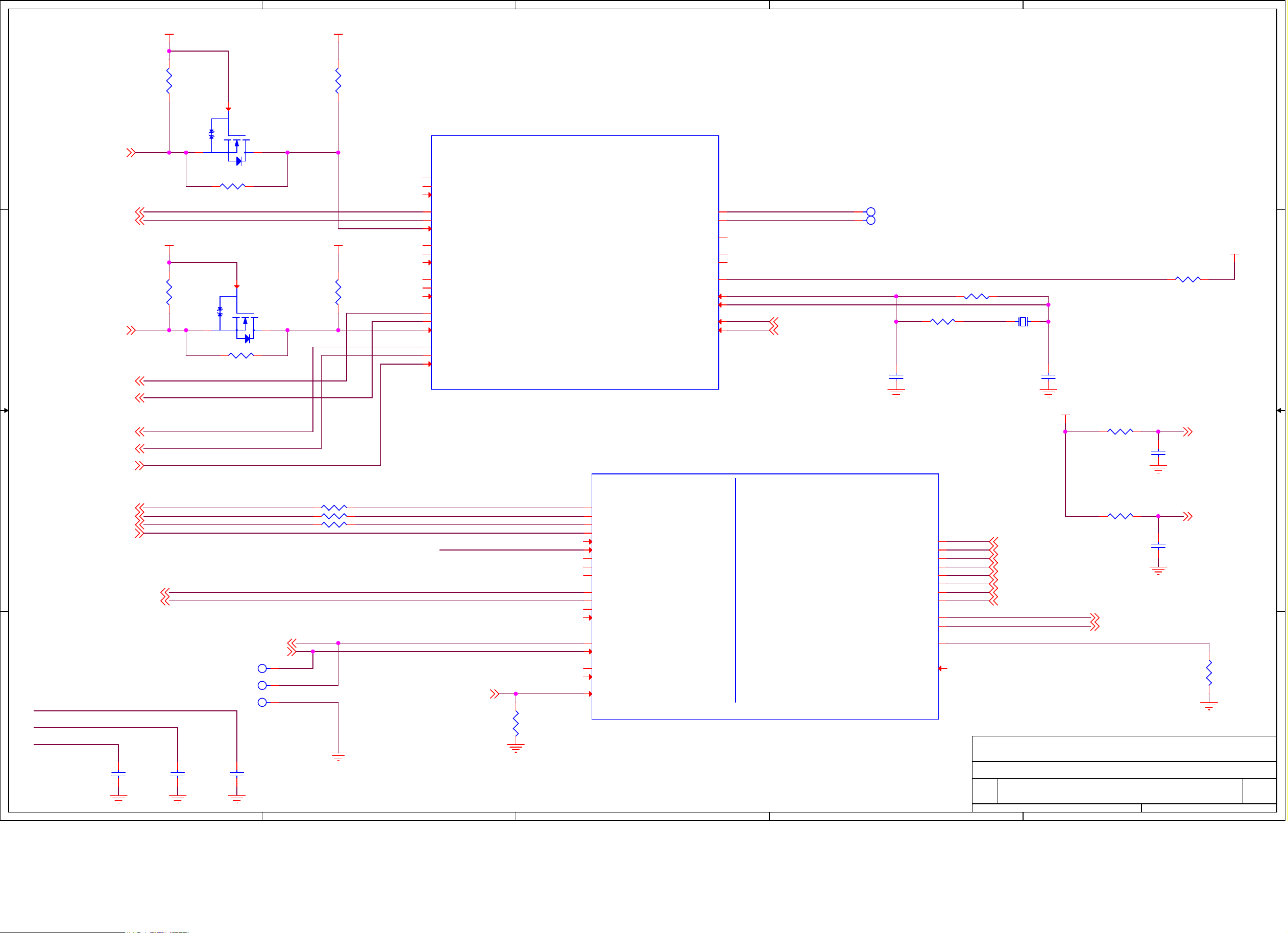

27 SAM_1, K22

28 SAM_2, K22

29 SAM_3, K22

30 INSTANT_ON

A A

57 VCCEDRAM & VCCEOPIO

58 PMIC 1

59 PMIC 2

60 PMIC 3

CAD Note:

Default component footprint is SMD 0201, X5R, 1% resistors.

01. Table of Contents

01. Table of Contents

Property: BUILD-OPT

DNP = Do Not Place

5

Title:

Title:

S or DB = Replace after Debug

4

3

2

Microsoft Confidential

Microsoft Confidential

Microsoft Confidential

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

A

A

A

Title:

Engineer:

Engineer:

Engineer:

01. Table of Contents

Surface

Surface

Surface

1 79Thursday, April 26, 2018

1 79Thursday, April 26, 2018

1

1 79Thursday, April 26, 2018

1.0.0.1

1.0.0.1

1.0.0.1

Page 2

5

Vinafix.com

4

3

2

1

Schematics Change History

Schematics Change is maintained in spreadsheet, and would not fit on this page.

D D

C C

B B

A A

CAD Note:

Default component footprint is SMD 0201, X5R, 1% resistors

Property: BUILD-OPT

DNP = Not Installed Part.

5

4

S = Short after design fixed

3

02. CHANGE HISTORY

02. CHANGE HISTORY

Title:

Title:

Title:

Microsoft Confidential

Microsoft Confidential

Microsoft Confidential

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

A

A

A

Engineer:

Engineer:

Engineer:

02. CHANGE HISTORY

Surface

Surface

Surface

2 79Thursday, April 26, 2018

2 79Thursday, April 26, 2018

1

2 79Thursday, April 26, 2018

1.0.0.1

1.0.0.1

1.0.0.1

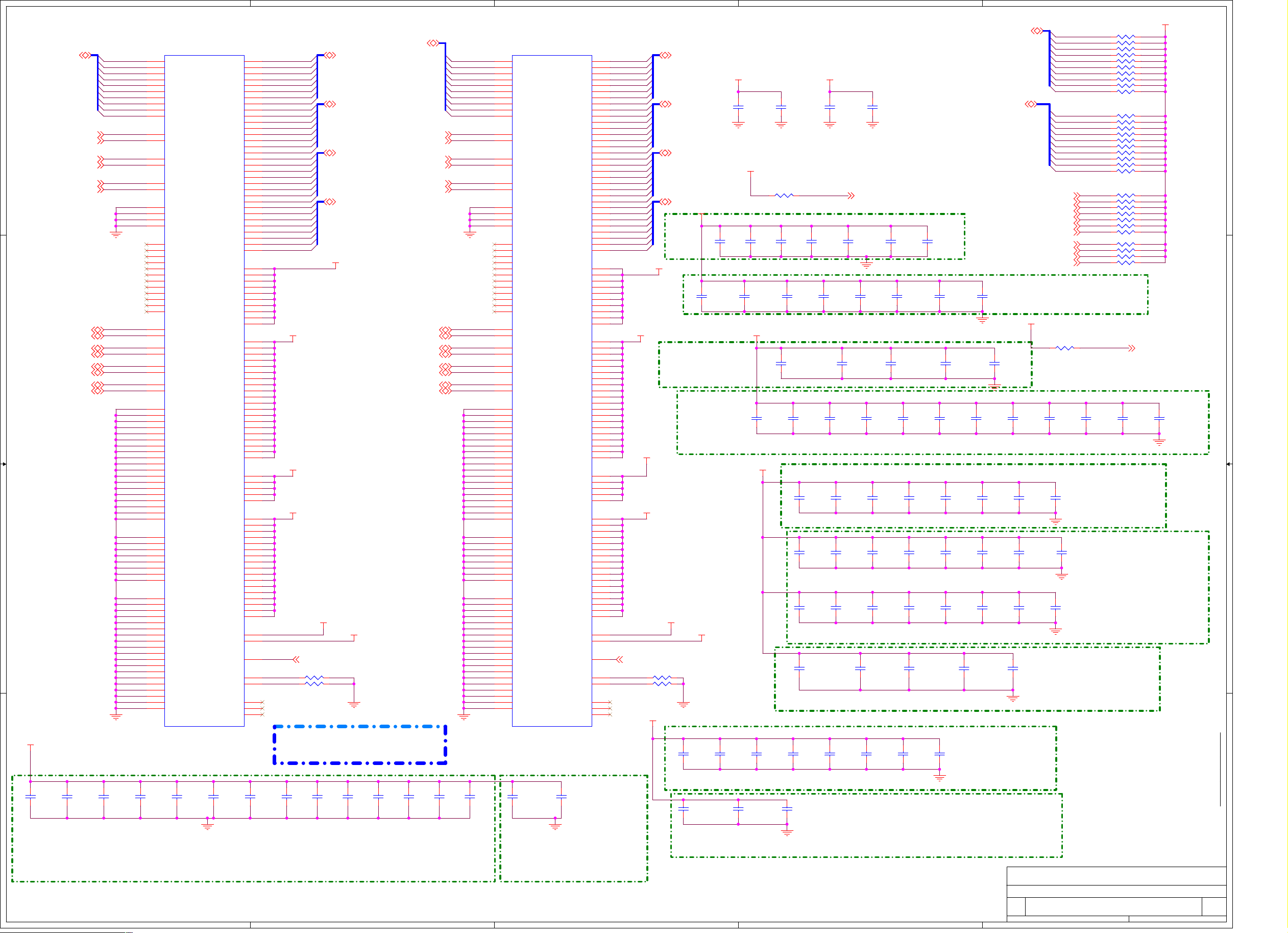

Page 3

5

Vinafix.com

4

3

2

1

Front IR

(OV7251)

Debug UART, external connector

D D

Power Monitor Components

(DEBUG)

MIPI CSIx1

(1Gbps)

I2C

Illuminator

MIPI CSIx1

HD Audio

I2C

Front RGB

(720p – OV9734)

Codec

SSD2 BGA chip

Architectural Diagram I-Core

Analog audio combo jack (3.5mm)

Audio

R

L

AMP

Right

ALC1304

Left

Rev 2.5

128GB, 256GB

512GB, 1TB

UART2

CSI2x2

Memory/

SSD BGA chip

128GB, 256GB

512GB, 1TB

2/4 x PCIe

2/4 x PCIe

ALS

I2C

I2C1

I2C3

PCIe 11/12

PCIe 7/8

LPDDR3 x32

Storage

C C

LPDDR3 x32

LPDDR3 x32

LPDDR3 x32

16,8,4 GB (4x)

16MB

128-bit (32b x 4) – 2 Chl -64 bit each

Quad SPI

SPI ROM

Backlight Controller

LCD

13.5"

TrackPad

KeyBoard

B B

UART

INT

TCON

NTRIG G5

eDP 1.4a

SPI

I2C

INT

UART

SC

Freescale

DDR0x64, DD1x64

SPI0

GPIOs

I2C5

eDP

SPI1

I2C0

UART1

SKL-U

15W

2+2/2+3E

O

I

P

G

K22

SL UART

MUX

PWM/Tach

Hall Effect

Fan/Fan

Connection

Temp

Power/PMIC

BD9992GW

(sep Block Dia)

I2C

7.4V

Battery

45WH

w/Fuel G

SC Debug

I2C

7.4V

Battery

Charger

ISL9237

Debug XDP

SC,K22

Greenpak

CSI2x2

XDP

P

D

X

I2C2

HDA

I2C4

DMIC

DDI1

DDI1_AUX

DDPB_CTRL

USB3p2

USB2p2

DDI2

DDI2_AUX

DDPC_CTRL

USB3p1

USB2p1

PCIe9

USB2p5

LPC

LPC

DDI2_A UX

DDPC_CTRL

DDI2_A UX

DDPC_CTRL

1XPCIe

USB2

TPM

Infineon

Nuvaton

NationZ

Surflink

DP1.2

MUX

USB2/USB3.0/DP1.2x4

AUX/DDPC

MUX

Debug

Signals

USB3.0

USB2

Wifi abgn+ac

Marvell 88W8897

BT

IMVP8 PMIC

ISL95857

W/2+3E support

POR CHANGES

2xTPS62134

VCCEDRAM/VCCEOPIO

2 Mic

AUX/DDPC

Debug

MUX

CMC + ESD

CMC + ESD

CMC + ESD

CMC + ESD

3.3V@0.8A OUT

POWER IN/OUT

SurfLink

5V@1.78A OUT

Antennas

mDP

USB3.0

Type-A

LEGEND

External

Connectors

POR CHANGES

Power path updates

Separate Block Diagram

POR CHANGES

Mostly same as P

Changed Feature/Implementation

New Feature/Implementation

A A

5

4

3

SD FLUSH

03. BLOCK DIAGRAM

03. BLOCK DIAGRAM

Title:

Title:

Title:

Microsoft Confidential

Microsoft Confidential

Microsoft Confidential

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

B

B

B

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

A

A

A

Engineer:

Engineer:

Engineer:

03. BLOCK DIAGRAM

Surface

Surface

Surface

3 79Thursday, April 26, 2018

3 79Thursday, April 26, 2018

1

3 79Thursday, April 26, 2018

1.0.0.1

1.0.0.1

1.0.0.1

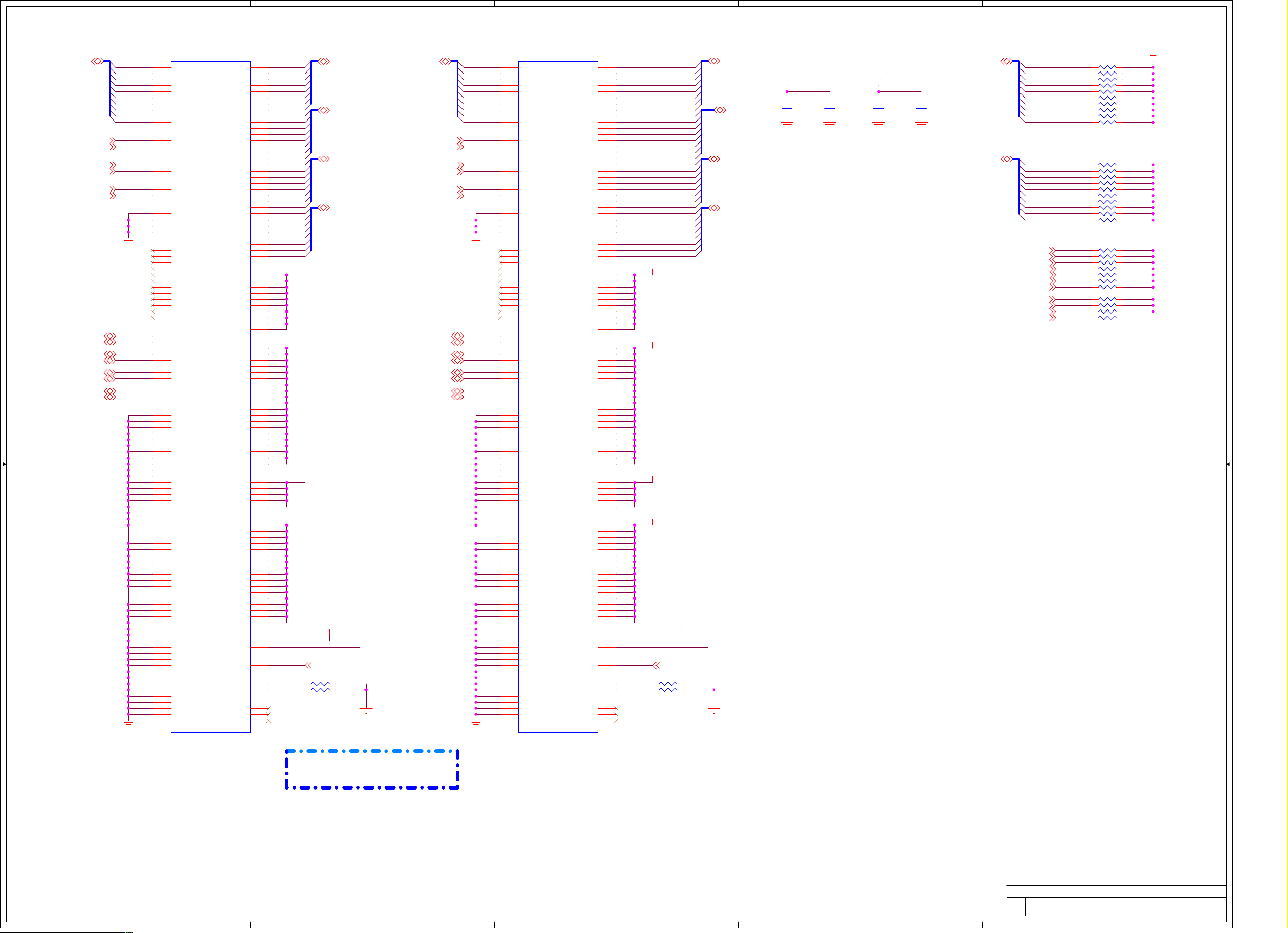

Page 4

5

Vinafix.com

D D

4

3

2

1

C C

B B

A A

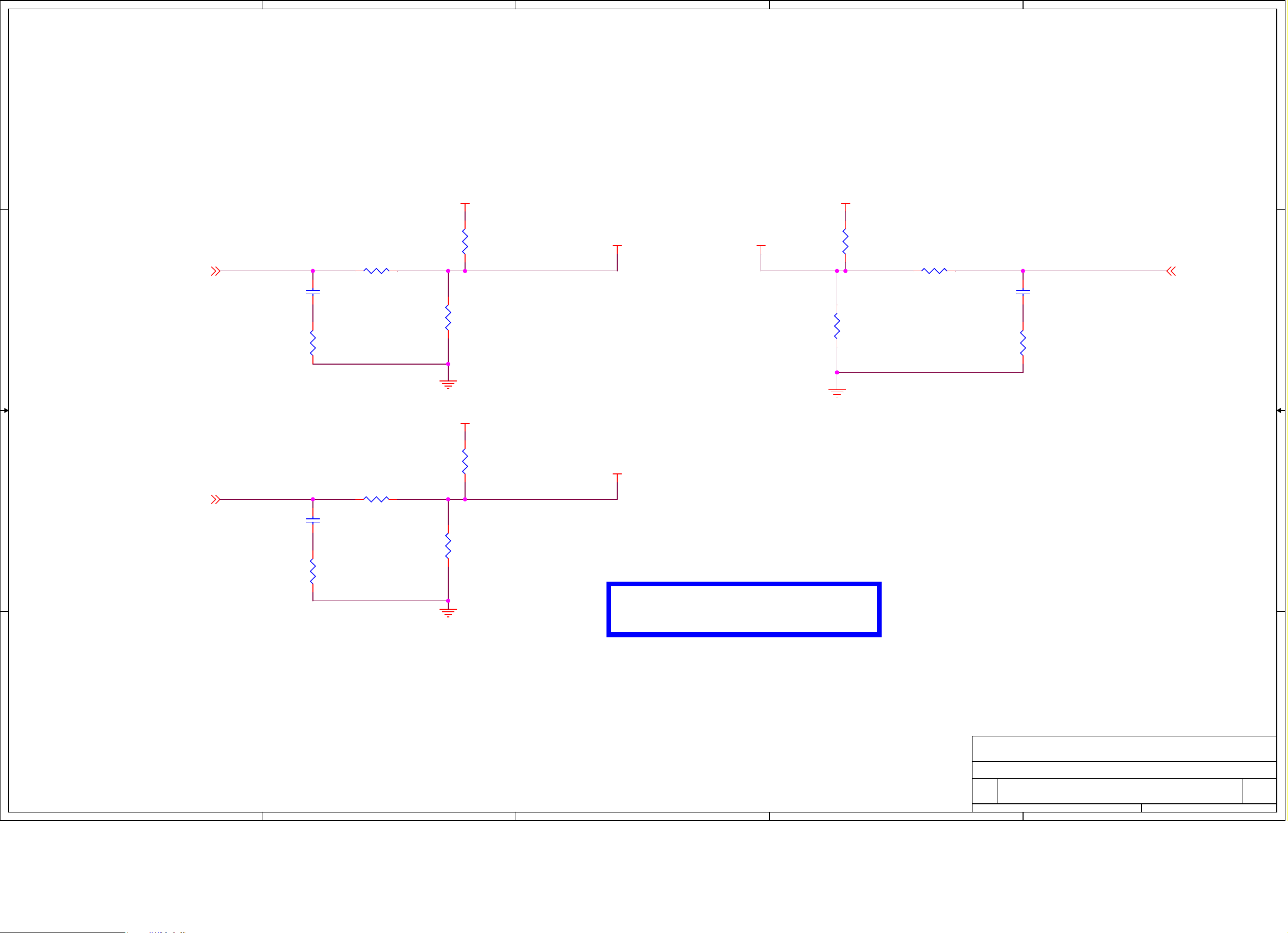

04. CLOCK DISTRIBUTION

04. CLOCK DISTRIBUTION

Title:

Title:

Title:

Microsoft Confidential

Microsoft Confidential

Microsoft Confidential

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

A

A

A

Engineer:

Engineer:

Engineer:

04. CLOCK DISTRIBUTION

Surface

Surface

Surface

4 79Thursday, April 26, 2018

4 79Thursday, April 26, 2018

1

4 79Thursday, April 26, 2018

1.0.0.1

1.0.0.1

1.0.0.1

Page 5

5

Vinafix.com

D D

4

3

2

1

C C

B B

A A

05. SIGNAL & RESET MAP

05. SIGNAL & RESET MAP

05. SIGNAL & RESET MAP

Surface

Surface

Surface

5 79Thursday, April 26, 2018

5 79Thursday, April 26, 2018

1

5 79Thursday, April 26, 2018

1.0.0.1

1.0.0.1

1.0.0.1

Title:

Title:

Title:

Microsoft Conf idential

Microsoft Conf idential

Microsoft Conf idential

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

Engineer:

Engineer:

A

A

A

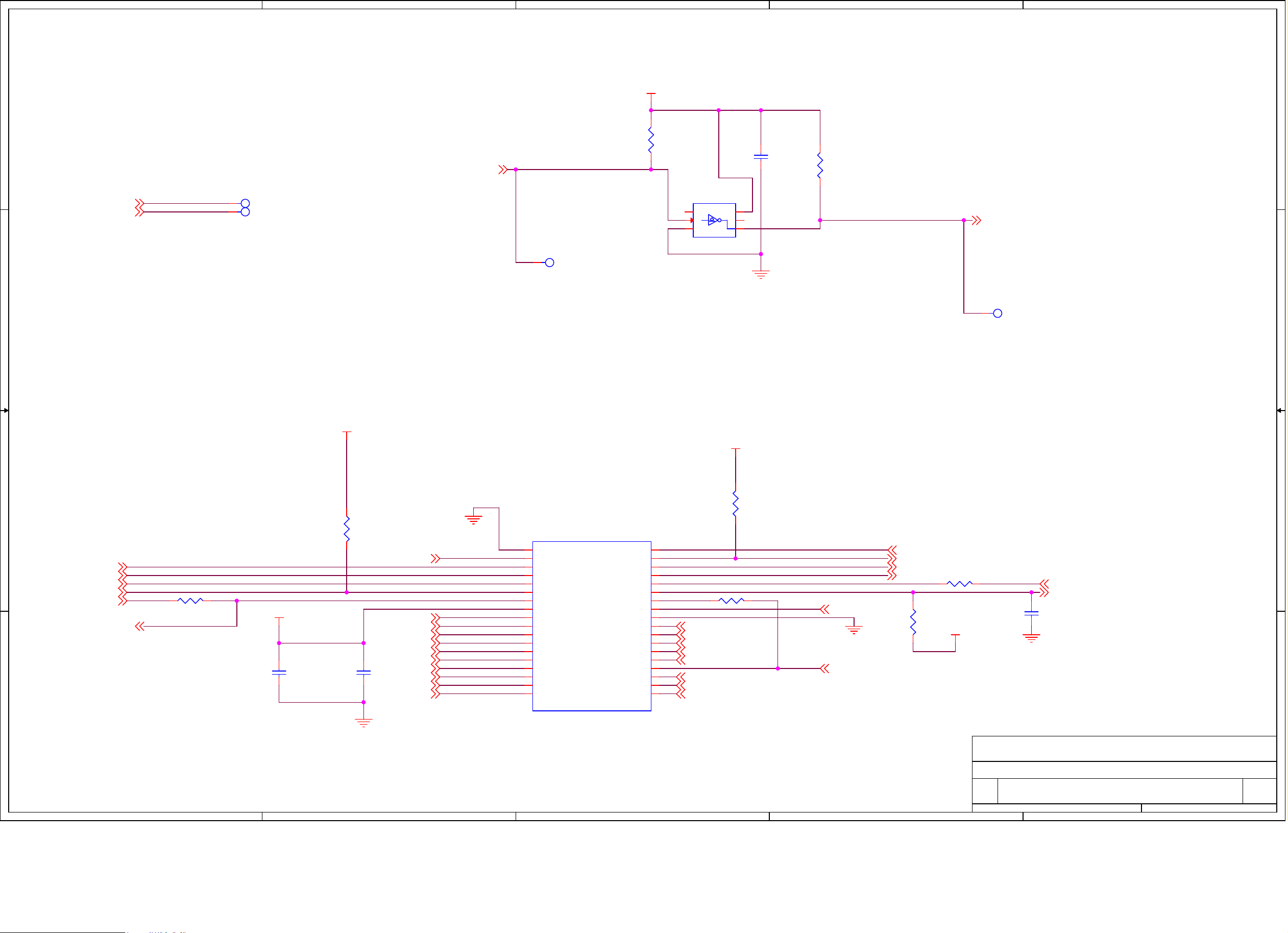

Page 6

5

Vinafix.com

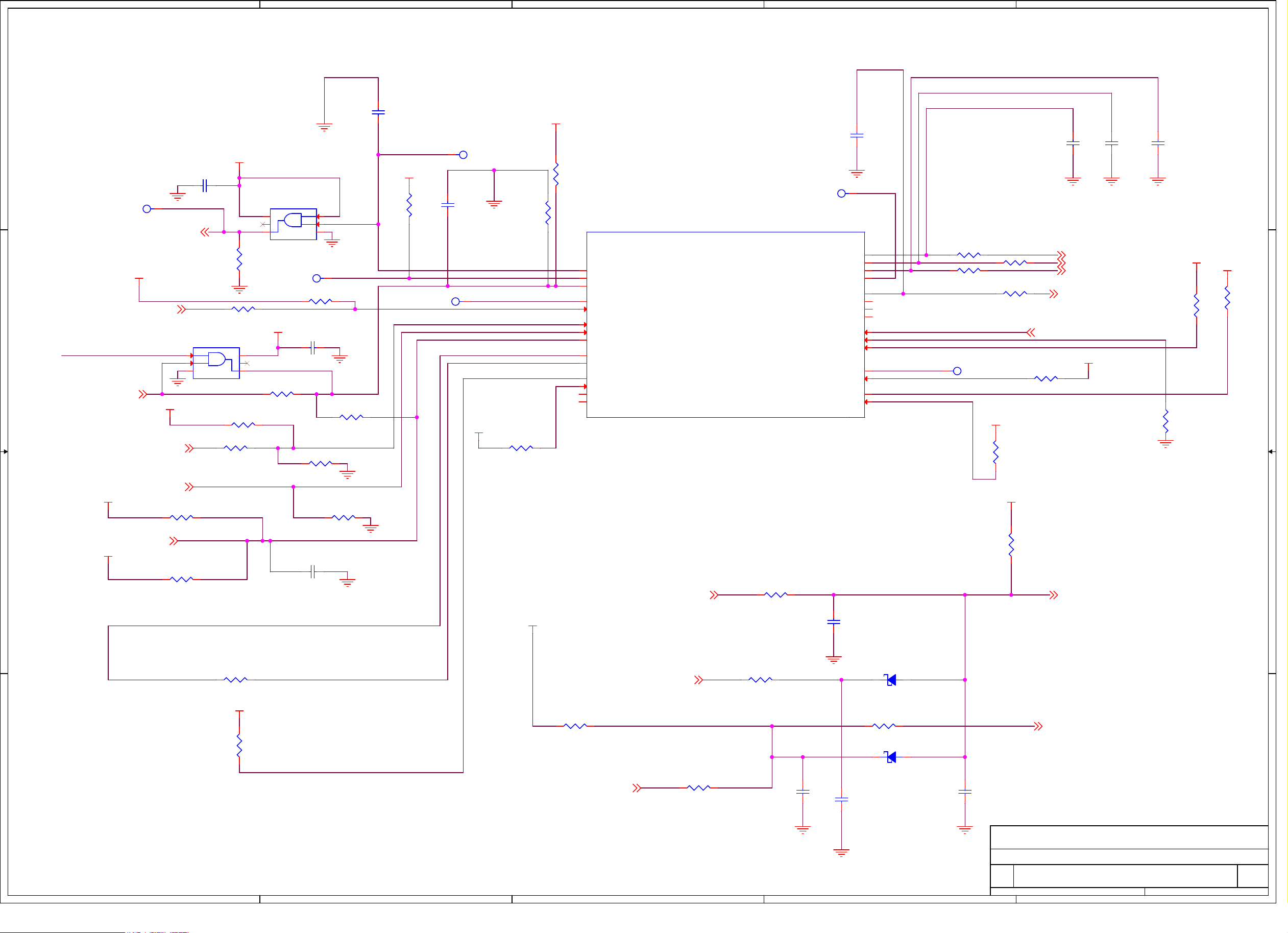

J47001

SurfLink Connector

PWR_SL1

D D

PWR_SL1_F

VDD_BAT

C C

B B

U56002

TPS62177

3P3VA

Always On

PWR_SL1

3P3VA

Imax = .5A

R56007

100mєÀ

Q63008/Q63009

Back to Back FETS

U56005

NX3P1108

3P3VA_SW_EN

DeepSleep Rail

S4/S5 Rail

Power Monitor Input

S0 Rail

Load switch

Control Signal

DC-DC

Regulator

A A

Linear

Regulator

5

External

Regulator /Load

Switch

U63001

ISL9237

Buck/Boost Charger

R36023

100mєA

R28001

100mєA

R31023

0mє À

VCC_RTC

Imax=100uA

R99999

20mєA

4

PWR_SL1_R

R63001

20mєA

VSYS_R

R63009

10mєA

VDD_BAT

J70001/J70002/J70003

Battery Connector

2S

Battery

7.6V typ

R56031

100mєA

R39016

100mєA

3P3V_PMI_DBG

3P3VA_SAM

3P3V_DEBUG

4

3P3VA_SW

Imax = .3A

3P3VA_TEMP

R63042

10mє À

Vsys

R67007

20mє À

R68001

20mє À

R67008

50mє À

R58034

10mє À

R58019

5mєA

R58012

20mє À

R58002

10mє À

R59023

25m㤿

R59003

25mє À

R58023

10mє À

R58032

25mєA

R58004

25mєA

R72001

20mє À

3

VCCGT/GTx

Platform PMIC

V3P3A_PCH

V1P8U_2P5U

L_BKLTEN

3

IMVP8

VCORE

VCCSA

U58001

V3P3_DSW

V6

V5A

V5

V1P8A

V8

V7

V0P85A

V12

V1P00A

V11

V9

V1P2U

V10

V0P6DX_LPDDR3

VCCIO

V4

U72001

RT8555

3P3V_SWPWR

V13

VCORE

VCCGT

VCCSA

V3P3_DSW

R58039

20mєA

V5A

R58024

10mєA

V1P8A

R58016

20mєA

V3P3A_PCH

R58008

50mєA

V0P85A

R59027

10mєA

V1P00A

R59007

10mєA

V1P8U_2P5U

R58026

50mєA

V1P2U

R58037

5mєA

R59032

10mєA

R59035

20mєA

VCCIO

R58009

10mєA

2

R64006

50mєA

2

R26004

10mєA

U65003

TPS22920

3P3V_SSD_EN

U65001

TPS22920

EDP_VDD_EN

R53007

0єÀ

R54005

100mєA

R45003

5mє À

R48022

100mєÀ

R64016

20mє À

R64020

20mєA

U62001

SLG59 M1448V

PCH_AUD_1V8_EN

U62003

NX3 P1108

PCH_TPANEL_PWR_EN

TPS22920

WWAN_ PWREN

U61002

SLG5NT1477

VCCSTG_EN

U61003

SLG5NT1477

SKL_SLP_S4_N +

XDP_PR ESENT _LOGIC

U61001

SLG5NT1477

SOiX_EN

SKL

VCORE

Imax = 20A

VCCGT/GTx

Imax = 20A

VCCSA

Imax = 7A

3VSUS_ORG

R38001

100mєÀ

U43005

TPS62085

1P8V_SSD

U43006

TPS62085

1P2V_SSD

R65002

50mєA

ML_V3P3_PWRU53005

3P3V_SSD

R65010 10mє A

R43017

25mєA

R43016

25mєA

NCP380

mDP_PWR_EN

3P3V_CAM

U45004

5V_USBPWR_A

AP2553

SKL_SLP_S4_N

SLG59M1448V

PCH_TPANEL_ PWR_EN

U64002

SLG59M1448V

PCH_TPANEL_PWR_EN

SLG59M1448V

PCH_AUD_5V_EN

SLG59M1448V

SAM_FAN_PWR_EN

U65004

U48002

U64004

U64006

R64019

10mєA

R26003

10mєA

R62002

20mєA

R40005

20mє À

R62007

20mєA

R65012

40mєA

5V0_OFFBOARD

5V_SWPWR

5V_TS

5V_AUDIO

5V_FAN (i-core only)

1P8VSUS_ORG

1P8V_AUDIO

1P8V_AUDIO_DVDD

1P8V_TS

3P3V_WWAN

V0P85A

V1P00A

1V_MODPHY

R61007

20mє À

VCCSTG

R61003

10 mєÀ

VCCST_CPU

R61006

10 mєÀ

V1P00A_XDP

R18001

0 mєA

V1P8U_2P5U

V1P2U

VCCPLL_OC

R61001

10mєA

V0P6DX_LPDDR3

VCCIO

VCC_EDP_BKLT_OUT

DVi7U7660s16s512x2Retail

DVi7U7660s16s512x2Retail

DVi7U7660s16s512x2Retail

Title:

Title:

Microsoft Confidential

Microsoft Confidential

Microsoft Confidential

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Title:

Engineer:

Engineer:

Engineer:

A

A

A

1

3P3V_TPM

1P8V_SSD

1P2V_SSD

3P3V_PANEL

J53001

mDP

Connector

J45001

USB 3.0 A

Connector

(keyboard)

06. POWER DISTRIBUTION

06. POWER DISTRIBUTION

06. POWER DISTRIBUTION

Surface

Surface

Surface

6 79Thursday, April 26, 2018

6 79Thursday, April 26, 2018

6 79Thursday, April 26, 2018

1

1.0.0.1

1.0.0.1

1.0.0.1

Page 7

5

Vinafix.com

D D

4

3

2

1

C C

B B

A A

DVi7U7660s16s512x2Retail

DVi7U7660s16s512x2Retail

DVi7U7660s16s512x2Retail

07. POW ER SEQUENCE 1

07. POW ER SEQUENCE 1

07. POW ER SEQUENCE 1

Title:

Title:

Microsoft Confidential

Microsoft Confidential

Microsoft Confidential

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

D

D

D

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Title:

Engineer:

Engineer:

Engineer:

A

A

A

Surface

Surface

Surface

7 79Thursday, April 26, 2018

7 79Thursday, April 26, 2018

7 79Thursday, April 26, 2018

1.0.0.1

1.0.0.1

1.0.0.1

Page 8

5

Vinafix.com

D D

4

3

2

1

C C

B B

A A

DVi7U7660s16s512x2Retail

DVi7U7660s16s512x2Retail

DVi7U7660s16s512x2Retail

08. POWER SEQUENCE

08. POWER SEQUENCE

08. POWER SEQUENCE

Title:

Title:

Microsoft Confidential

Microsoft Confidential

Microsoft Confidential

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

D

D

D

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Title:

Engineer:

Engineer:

Engineer:

A

A

A

Surface

Surface

Surface

8 79Thursday, April 26, 2018

8 79Thursday, April 26, 2018

8 79Thursday, April 26, 2018

1.0.0.1

1.0.0.1

1.0.0.1

Page 9

5

Vinafix.com

4

3

2

1

D EB U G : P ow e r M on ito rs

U 36 00 2

PM I1 M A X3 44 07

7 -b it s la v e add re ss e s

Sep te m b e r 2 8 , 201 6

D D

1

0

0

4

5

J

1

0

0

4

5

J

1

0

0

4

5

J

Cam e ra s

EE PRO M G T2 4C 0 8S

0x50 , 0 x 5 1,

0x52, 0 x 5 3

Fro n t R G B O V9 73 4

0x36

IR C am O V0 72 5 1

0x60

1P 8V SU S_ OR G

5

/

S

4

1

0

5

2

R

2k?

I2 C_ S xx_ C AM

S

To E E P ow er D ebu g

Co n ne cto r

S

U 36 00 1

PM I0 M A X3 44 07

0x1E

S

M

0x12

I2C 2

S S

U 36 0 03

PM I2 M AX 34 40 7

0x10

U3 60 04

PM I3 M AX 34 4 0 7

0x18

U 36 00 5 U3 60 07

PM I4 M A X3 44 07

S S S

M

I2 C1

0x1A

Light S e nsor a nd B KLT C o n tro lle r

ALS ISL2 9 033

1

0

C C

B B

0

4

5

J

1

B a cklig h t D rv r R T8 55 5

0

0

2

7

U

0x44

0x31

D isp la y

1

TC O N M LT S15 20 00

0

0

5

5

J

0x28

Pow e r M an a g e m e n t

1

0

PM IC B D 999 9 2G W

0

8

5

U

1

0

Ch arge r BQ 24 7 70

0

8

5

U

1

3

Fu el G a uge B Q 40x 5 0

0

0

0

0

0

0

7

7

J

J

0x30

0x09

0x0B

S

I2 C_ Sxx _ A LS

I2 C_ Sx x_ B KLT

S

D ispl ay _V DD 18

3P 3V _P AN EL

d

r

a

o

b

f

f

O

S

S

CH G _S xx

S

BA T T_I2C _x xx

S

To De bu g M ux e s

2

/

1

1

7

R

4.7 k?

I2 C_ DISP LA Y _ Sxx ( DN P)

3P 3V A_ SW

2

/

1

0

0

9

5

R

3P 3V A_ SW

7

/

6

3

0

7

2

R

1P 8V SU S_ OR G

5

/

4

7

0

5

2

R

To De bu g

Co nn ecto r

To De bu g

Co nn ecto r

2k ?

2.2 k?

I2 C_ RO P_ Sx x

2k?

M

I2C 3

I2C 4

M

K22 P 121M 120SF5

M M

I2 C1

SO C/PC H

U 1 0001

0x4D

M

I2 C2

SA M

U 2 7001

0x28

I2C 5

I2C 0

I2 C0

M

M

U 36 00 6

PM I5 M AX 34 40 7

0x1C

PM I_ I2C _S xx

I2 C_ Sxx _ A LS (D NP )

5V A ->

TP _P W R_ EN

I2 C _S xx_ T P

I2 C_ Sx x_ M CU

S

S

PM IB A T T IN A 23 1

0x40

1P 8V SU S_ OR G

4

/

3

6

2k ?

0

5

2

R

O pti on to Co nn ec t to

A LS Sen s o r a t J5 40 01

P3 V 3_T P

d

r

2

/

a

1

o

2.2 k?

1

b

f

6

f

R

O

Crit ical T e m p S N1 51 10 04

0x48

U 36 0 08

PM I6 IN A23 1

0x41

3P 3V _P M I_D BG

2

/

1

2

0

6

3

R

O p tio n to con nec t

to I2 C_ RO P_ Sx x

W ifi 88W 88 97

U 50001

Tra c kp a d

Tra ck p ad IC S 910 1 B

S

0x20

To De bu g

M ux es

To D eb ug

Co n ne cto r

3

0

0

9

3

U

To E E P ow er D eb ug

Te m p S en so r S TT S7 51

S

S

2.2 k?

To E E P ow er De b ug

Co n ne cto r

1

0

0

8

4

J

Tem p S ensors

Co n ne cto r

0x3B

M

D e b ug C o nn e ctor

EE Po w er D e b ug

Con n ecto r

D e b ug M uxe s

Rem ov e d in R e tail

D EB U G _O SG in Reta il

D N P in N o n-R eta il/R eta il

W ifi/B T

1P 8V _W IF I_ INT _O UT

+

1

l

a

3

0

n

r

e

t

n

I

10k ?

0

5

R

SER _S x x

EE P RO M AT2 4 C16 D

S

1

0

0

9

3

U

S

1

0

0

3

3

J

1

0

0

4

3

J

,

,

1

2

0

0

0

0

1

1

3

3

U

U

0x50 -0x57

IR T em p T M P0 07

0x40

,

5

3

0

0

0

0

1

1

3

3

U

U

3

0

0

0

5

U

6

0

0

9

3

U

O p tio n to Co nn ect I2 C s

To E E P ow er De b ug

A A

5

Co n ne cto r

4

3

Te m p S en sor S TTS 75 1

S S

2

0x3A

DVi7U7660s16s512x2Retail

DVi7U7660s16s512x2Retail

DVi7U7660s16s512x2Retail

Microsoft Confidential

Microsoft Confidential

Microsoft Confidential

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

2

0

0

9

3

U

A

A

A

Te m p S en sor S TT S7 5 1

0x4A

09. I2C MAP

09. I2C MAP

Title:

Title:

Title:

Engineer:

Engineer:

Engineer:

09. I2C MAP

1

Surface

Surface

Surface

9 79Thursday, April 26, 2018

9 79Thursday, April 26, 2018

9 79Thursday, April 26, 2018

4

0

0

9

3

U

1.0.0.1

1.0.0.1

1.0.0.1

Page 10

5

Vinafix.com

VCCSTG

R10001

1K

0201

D D

C C

PROCHOT_N[34,60,63,66]

R10004

100

0402

D

SAM_PROCHOT[29]

G

RUM002N02GT2L

0201

R10029 100K

Q10001

S

VCCST_CPU

R10019

1K

0201

XDP_TP10001

TS_IRQ_3V3_N[49]

XDP_TP10002

TRACKPAD_INT_N[27,48]

mDP_PWR_EN[53]

0201

R10011 49.9

R10012 49.9

0201

R10003 499

EE SQ 13.8mil

EE SQ 13.8mil

0201

0201

R10013 49.9

4

VCCST_CPU

SMD RND 22.8mil

0201

R10014 49.9

DNP

R10002

49.9

0201

GTP10006

PM_THERMTRIP_N[10,56]

XDP_BPM0[18]

XDP_BPM1[18]

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

R10035 330 0201

TP_CATERR_R_N

H_PROCHOT_R_N

GPP_E3

U10001D

D63

CATERR#

A54

PECI

C65

PROCHOT#

C63

THERMTRIP#

A65

SKTOCC#

C55

BPM#[0]

D55

BPM#[1]

B54

BPM#[2]

C56

BPM#[3]

A6

GPP_E3/CPU_GP0

A7

GPP_E7/CPU_GP1

BA5

GPP_B3/CPU_GP2

AY5

GPP_B4/CPU_GP3

AT16

PROC_POPIRCOMP

AU16

PCH_OPIRCOMP

H66

OPCE_RCOMP

H65

OPC_RCOMP

KBL-R U42

<$LOCATION>

<MATERIAL>

4 OF 20

REV = 1

3

CPU MISC

KBL_R_U42

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

JTAGX

VCCSTG

R10032 100

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

0201

2

MTP10001 SMD RND 22.8mil

MTP10002 SMD RND 22.8mil

MTP10003 SMD RND 22.8mil

MTP10004 SMD RND 22.8mil

MTP10005 SMD RND 22.8mil

PROC_TCK [10,18]

PROC_TDI [10,18]

PROC_TDO [10,18]

PROC_TMS [10,18]

PROC_TRST_N [10,18]

0201

PLACE TP's on BOTTOM,

1

PLACE TP's on BOTTOM,

R10008 51

0201

0201

R10015 51

R10016 100

0201

R10017 51

VCCSTG

MTP10007 SMD RND 22.8mil

MTP10008 SMD RND 22.8mil

MTP10009 SMD RND 22.8mil

MTP10010 SMD RND 22.8mil

MTP10011 SMD RND 22.8mil

MTP10012 SMD RND 22.8mil

PCH_JTAG_TCK [18]

PROC_TDI [10,18]

PROC_TDO [10,18]

PROC_TMS [10,18]

PROC_TRST_N [10,18]

PROC_TCK [10,18]

TBL1002

PM_THERMTRIP_N[10,56]

U10001A

MDP_DDI1_ML0_DN[53]

MDP_DDI1_ML0_DP[53]

MDP_DDI1_ML1_DN[53]

MDP_DDI1_ML1_DP[53]

MDP_DDI1_ML2_DN[53]

MDP_DDI1_ML2_DP[53]

MDP_DDI1_ML3_DN[53]

MDP_DDI1_ML3_DP[53]

SL_DDI2_ML0_DN[47]

SL_DDI2_ML0_DP[47]

B B

DDPB_CTRL_CLK[53]

VCCIO

R10025

24.9

0201

SAM_PCH_HALL_INT[27]

DDPB_CTRL_DATA[53]

SL_DDI2_ML1_DN[47]

SL_DDI2_ML1_DP[47]

SL_DDI2_ML2_DN[47]

SL_DDI2_ML2_DP[47]

SL_DDI2_ML3_DN[47]

SL_DDI2_ML3_DP[47]

DDPC_CTRL_CLK[46]

DDPC_CTRL_DATA[46]

EDP_COMP

INT. PD

INT. PD

TBL1001

A A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

KBL-R U42

1 OF 20

REV = 1

KBL_R_U42

DDI

DISPLAY SIDEBANDS

EDP

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

RSVD_G46

RSVD_F46

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

EDP_TX0_DN [55]

EDP_TX0_DP [55]

EDP_TX1_DN [55]

EDP_TX1_DP [55]

EDP_TX2_DN [55]

EDP_TX2_DP [55]

EDP_TX3_DN [55]

EDP_TX3_DP [55]

EDP_AUX_DN [55]

EDP_AUX_DP [55]

eDP x 4

MDP_DDI1_AUX_DN [53]

MDP_DDI1_AUX_DP [53]

SL_DDI2_AUX_DN [46]

SL_DDI2_AUX_DP [46]

SOC_BKLTEN [30]

SOC_BKLT_CTRL_IN [30]

SOC_DISPLAY_VDD_EN [30]

EDP_DISP_UTIL

0201DNP

0201DNP

R10026 100K

R10027 100K

0201

R10028 100K

DNP

R10022

0

0201

0201

R10037 49.9K

V5A

R10033

10K

0201

5

34

Q10002B

NX3008NBKS

SOT-363

BL_INST_ON_HNDSHK [29,30]

EDP_HPD [55]

3VSUS_ORG

R10039 49.9K

0201

V5A

2

R10034

10K

0201

61

Q10002A

NX3008NBKS

SOT-363

GPP_A 3.3V

GPP_B 3.3V

GPP_C 3.3V

GPP_D 1.8V

GPP_E 3.3V

GPP_F 1.8V

GPP_G 3.3V

GDP 3.3V

MDP_SNK1_HPD [53]

SL_SNK0_HPD [47]

SAM_PCH_RSV1 [27]

10. CPU(1)_MISC,JTAG,DDI.EDP

10. CPU(1)_MISC,JTAG,DDI.EDP

Title:

Title:

Title:

Microsoft Confidential

Microsoft Confidential

Microsoft Confidential

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

B

B

U SPECIFIC

5

4

3

2

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

A

A

A

Engineer:

Engineer:

Engineer:

10. CPU(1)_MISC,JTAG,DDI.EDP

Surface

Surface

Surface

10 79Friday, April 27, 2018

10 79Friday, April 27, 2018

1

10 79Friday, April 27, 2018

1.0.0.1

1.0.0.1

1.0.0.1

Page 11

5

Vinafix.com

4

3

2

1

U10001C

U10001B

M_A_D[7:0][16]

D D

C C

M_A_D[15:8][16]

M_A_D[39:32][16]

M_A_D[47:40][16]

M_B_D[7:0][17]

M_B_D[15:8][17]

M_B_D[39:32][17]

M_B_D[47:40][17]

M_A_D0

M_A_D1

M_A_D2

M_A_D3

M_A_D4

M_A_D5

M_A_D6

M_A_D7

M_A_D8

M_A_D9

M_A_D10

M_A_D11

M_A_D12

M_A_D13

M_A_D14

M_A_D15

M_A_D32

M_A_D33

M_A_D34

M_A_D35

M_A_D36

M_A_D37

M_A_D38

M_A_D39

M_A_D40

M_A_D41

M_A_D42

M_A_D43

M_A_D44

M_A_D45

M_A_D46

M_A_D47

M_B_D0

M_B_D1

M_B_D2

M_B_D3

M_B_D4

M_B_D5

M_B_D6

M_B_D7

M_B_D8

M_B_D9

M_B_D10

M_B_D11

M_B_D12

M_B_D13

M_B_D14

M_B_D15

M_B_D32

M_B_D33

M_B_D34

M_B_D35

M_B_D36

M_B_D37

M_B_D38

M_B_D39

M_B_D40

M_B_D41

M_B_D42

M_B_D43

M_B_D44

M_B_D45

M_B_D46

M_B_D47

DDR4(IL)/LP3-DDR4(NIL)

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

KBL-R U42

<$LOCATION>

<MATERIAL>

2 OF 20

REV = 1

KBL_R_U42

DDR CH - A

LP3/DDR4

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

LP3/DDR4

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]/NC

DDR0_CKE[3]/NC

LP3/DDR4

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

NC/DDR0_ODT[1]

LP3/DDR4

DDR0_CAA[0]/DDR0_MA[5]

DDR0_CAA[1]/DDR0_MA[9]

DDR0_CAA[2]/DDR0_MA[6]

DDR0_CAA[3]/DDR0_MA[8]

DDR0_CAA[4]/DDR0_MA[7]

DDR0_CAA[5]/DDR0_BG[0]

DDR0_CAA[6]/DDR0_MA[12]

DDR0_CAA[7]/DDR0_MA[11]

DDR0_CAA[8]/DDR0_ACT#

DDR0_CAA[9]/DDR0_BG[1]

DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAB[1]/DDR0_MA[15]

DDR0_CAB[2]/DDR0_MA[14]

DDR0_CAB[3]/DDR0_MA[16]

DDR0_CAB[7]/DDR0_MA[10]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

LP3/DDR4

DDR0_CAB[4]/DDR0_BA[0]

DDR0_CAB[5]/DDR0_MA[2]

DDR0_CAB[6]/DDR0_BA[1]

DDR0_CAB[8]/DDR0_MA[1]

DDR0_CAB[9]/DDR0_MA[0]

NC/DDR0_MA[3]

NC/DDR0_MA[4]

DDR4(IL)/LP3-DDR4(NIL)

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

LP3/DDR4

NC/DDR0_ALERT#

NC/DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

M_A_CAA0

BA51

M_A_CAA1

BB54

M_A_CAA2

BA52

M_A_CAA3

AY52

M_A_CAA4

AW52

M_A_CAA5

AY55

M_A_CAA6

AW54

M_A_CAA7

BA54

M_A_CAA8

BA55

M_A_CAA9

AY54

M_A_CAB0

AU46

M_A_CAB1

AU48

M_A_CAB2

AT46

M_A_CAB3

AU50

M_A_CAB4

AU52

M_A_CAB5

AY51

M_A_CAB6

AT48

M_A_CAB7

AT50

M_A_CAB8

BB50

M_A_CAB9

AY50

BA50

BB52

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW50

AT52

AY67

DIMM_VREF_C A [19]

AY68

DIMM0_VREF_D Q [19]

BA67

DIMM1_VREF_D Q [19]

AW67

M_A_DIM0_CLKN 0 [16]

M_A_DIM0_CLKP0 [16]

M_A_DIM0_CLKN 1 [16]

M_A_DIM0_CLKP1 [16]

M_A_DIM0_CKE0 [16]

M_A_DIM0_CKE1 [16]

M_A_DIM0_CKE2 [16]

M_A_DIM0_CKE3 [16]

M_A_DIM0_CS0_N [16]

M_A_DIM0_CS1_N [16]

M_A_DIM0_ODT0 [16]

M_A_CAA[9:0] [16]

M_A_CAB[9:0] [16]

M_A_DQSN0 [16]

M_A_DQSP0 [16]

M_A_DQSN1 [16]

M_A_DQSP1 [16]

M_A_DQSN4 [16]

M_A_DQSP4 [16]

M_A_DQSN5 [16]

M_A_DQSP5 [16]

M_B_DQSN0 [17]

M_B_DQSN1 [17]

M_B_DQSP1 [17]

M_B_DQSN4 [17]

M_B_DQSP4 [17]

M_B_DQSN5 [17]

M_B_DQSP5 [17]

DDR_VTT_CTL [34,59]

M_A_D[23:16][16]

M_A_D[31:24][16]

M_A_D[55:48][16]

M_A_D[63:56][16]

M_B_D[23:16][17]

M_B_D[31:24][17]

M_B_D[55:48][17]

M_B_D[63:56][17]

M_A_D16

M_A_D17

M_A_D18

M_A_D19

M_A_D20

M_A_D21

M_A_D22

M_A_D23

M_A_D24

M_A_D25

M_A_D26

M_A_D27

M_A_D28

M_A_D29

M_A_D30

M_A_D31

M_A_D48

M_A_D49

M_A_D50

M_A_D51

M_A_D52

M_A_D53

M_A_D54

M_A_D55

M_A_D56

M_A_D57

M_A_D58

M_A_D59

M_A_D60

M_A_D61

M_A_D62

M_A_D63

M_B_D16

M_B_D17

M_B_D18

M_B_D19

M_B_D20

M_B_D21

M_B_D22

M_B_D23

M_B_D24

M_B_D25

M_B_D26

M_B_D27

M_B_D28

M_B_D29

M_B_D30

M_B_D31

M_B_D48

M_B_D49

M_B_D50

M_B_D51

M_B_D52

M_B_D53

M_B_D54

M_B_D55

M_B_D56

M_B_D57

M_B_D58

M_B_D59

M_B_D60

M_B_D61

M_B_D62

M_B_D63

DDR4(IL)/LP3-DDR4(NIL) LP3/DDR4

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

KBL-R U42

<$LOCATION>

<MATERIAL>

3 OF 20

REV = 1

KBL_R_U42

DDR CH - B

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

LP3/DDR4

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]/NC

DDR1_CKE[3]/NC

LP3/DDR4

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

NC/DDR1_ODT[1]

DDR1_CAA[0]/DDR1_MA[5]

DDR1_CAA[1]/DDR1_MA[9]

DDR1_CAA[2]/DDR1_MA[6]

DDR1_CAA[3]/DDR1_MA[8]

DDR1_CAA[4]/DDR1_MA[7]

DDR1_CAA[5]/DDR1_BG[0]

DDR1_CAA[6]/DDR1_MA[12]

DDR1_CAA[7]/DDR1_MA[11]

DDR1_CAA[8]/DDR1_ACT#

DDR1_CAA[9]/DDR1_BG[1]

DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAB[1]/DDR1_MA[15]

DDR1_CAB[2]/DDR1_MA[14]

DDR1_CAB[3]/DDR1_MA[16]

DDR1_CAB[4]/DDR1_BA[0]

DDR1_CAB[5]/DDR1_MA[2]

DDR1_CAB[6]/DDR1_BA[1]

DDR1_CAB[7]/DDR1_MA[10]

DDR1_CAB[8]/DDR1_MA[1]

DDR1_CAB[9]/DDR1_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

LP3/DDR4

LP3/DDR4

NC/DDR1_MA[3]

NC/DDR1_MA[4]

DDR4(IL)/LP3-DDR4(NIL)

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

LP3/DDR4

NC/DDR1_ALERT#

NC/DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

M_B_CAA0

M_B_CAA1

M_B_CAA2

M_B_CAA3

M_B_CAA4

M_B_CAA5

M_B_CAA6

M_B_CAA7

M_B_CAA8

M_B_CAA9

M_B_CAB0

M_B_CAB1

M_B_CAB2

M_B_CAB3

M_B_CAB4

M_B_CAB5

M_B_CAB6

M_B_CAB7

M_B_CAB8

M_B_CAB9

M_A_DQSN2 [16]

M_A_DQSP2 [16]

M_A_DQSN3 [16]

M_A_DQSP3 [16]

M_A_DQSN6 [16]

M_A_DQSP6 [16]

M_A_DQSN7 [16]

M_A_DQSP7 [16]

M_B_DQSN2 [17]

M_B_DQSP2 [17]

M_B_DQSN3 [17]M_B_DQSP0 [17]

M_B_DQSP3 [17]

M_B_DQSN6 [17]

M_B_DQSP6 [17]

M_B_DQSN7 [17]

M_B_DQSP7 [17]

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

M_B_DIM0_CLKN 0 [17]

M_B_DIM0_CLKN 1 [17]

M_B_DIM0_CLKP0 [17]

M_B_DIM0_CLKP1 [17]

M_B_DIM0_CKE0 [17]

M_B_DIM0_CKE1 [17]

M_B_DIM0_CKE2 [17]

M_B_DIM0_CKE3 [17]

M_B_DIM0_CS0_N [17]

M_B_DIM0_CS1_N [17]

M_B_DIM0_ODT0 [17]

M_B_CAA[9:0] [17]

M_B_CAB[9:0] [17]

R110042001%

R1100580.6

R110061621%

0201

0201

0402

B B

A A

11. CPU(2)_LPDDR3

11. CPU(2)_LPDDR3

11. CPU(2)_LPDDR3

Title:

Title:

Microsoft Conf idential

Microsoft Conf idential

Microsoft Conf idential

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

C

C

5

4

3

2

U SPECIFIC

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Title:

Surface

Surface

Surface

Engineer:

Engineer:

Engineer:

1.0.0.1

1.0.0.1

A

A

A

1

11 79Friday, April 27, 2018

11 79Friday, April 27, 2018

11 79Friday, April 27, 2018

1.0.0.1

Page 12

V1P2U

Vinafix.com

5

4

3

2

1

0402

C12004 10u

4V

0603

C12002 22u

4V

0402

C12005 10u

4V

0402

C12024 10u

0603

C12003 22u

4V

4V

5

6.3V

0402

C12011 10u

4V

DNP

C12025 10u

0402

VCCPLL_OC

VCCST_CPU

from 1VSB, control SLP_S4 (S3 rail)

C12040

6.3V

1u

0402

VCCSTG

0402

C12041 10u

4V

VCCST_CPU

C12049

1u

0402

REMOVED +VCCEDRAM & +VCCEOPIO RAILS

4

6.3V

C12042

1u

0402

VCORE

AU23

AU28

AU35

AU42

BB23

BB32

BB41

BB47

BB51

AM40

A18

A22

AL23

K20

K21

6.3V

A30

A34

A39

A44

AK33

AK35

AK37

AK38

AK40

AL33

AL37

AL40

AM32

AM33

AM35

AM37

AM38

G30

K32

AK32

AB62

P62

V62

H63

G61

AC63

AE63

AE62

AG62

AL63

AJ62

U10001N

VDDQ_AU23

VDDQ_AU28

VDDQ_AU35

VDDQ_AU42

VDDQ_BB23

VDDQ_BB32

VDDQ_BB41

VDDQ_BB47

VDDQ_BB51

VDDQC

VCCST

VCCSTG_A22

VCCPLL_OC

VCCPLL_K20

VCCPLL_K21

KBL-R U42

<$LOCATION>

<MATERIAL>

14 OF 20

REV = 1

KBL_R_U42

CPU POWER 3 OF 4

U10001L

VCCCORE_A30

VCCCORE_A34

VCCCORE_A39

VCCCORE_A44

VCCCORE_AK33

VCCCORE_AK35

VCCCORE_AK37

VCCCORE_AK38

VCCCORE_AK40

VCCCORE_AL33

VCCCORE_AL37

VCCCORE_AL40

VCCCORE_AM32

VCCCORE_AM33

VCCCORE_AM35

VCCCORE_AM37

VCCCORE_AM38

VCCCORE_G30

RSVD_K32

RSVD_AK32

VCCOPC_AB62

VCCOPC_P62

VCCOPC_V62

VCC_OPC_1P8_H63

VCC_OPC_1P8_G61

VCCOPC_SENSE

VSSOPC_SENSE

VCCEOPIO_AE62

VCCEOPIO_AG62

VCCEOPIO_SENSE

VSSEOPIO_SENSE

KBL-R U42

<$LOCATION>

<MATERIAL>

12 OF 20

REV = 1

KBL_R_U42

CPU POWER 1 OF 4

VCCIO_AK28

VCCIO_AK30

VCCIO_AL30

VCCIO_AL42

VCCIO_AM28

VCCIO_AM30

VCCIO_AM42

VCCSA_AK23

VCCSA_AK25

VCCSA_G23

VCCSA_G25

VCCSA_G27

VCCSA_G28

VCCSA_J22

VCCSA_J23

VCCSA_J27

VCCSA_K23

VCCSA_K25

VCCSA_K27

VCCSA_K28

VCCSA_K30

VCCIO_SENSE

VSSIO_SENSE

VSSSA_SENSE

VCCSA_SENSE

3

AK28

AK30

AL30

AL42

AM28

AM30

AM42

AK23

AK25

G23

G25

G27

G28

J22

J23

J27

K23

K25

K27

K28

K30

AM23

AM22

H21

H20

VCCCORE_G32

VCCCORE_G33

VCCCORE_G35

VCCCORE_G37

VCCCORE_G38

VCCCORE_G40

VCCCORE_G42

VCCCORE_J30

VCCCORE_J33

VCCCORE_J37

VCCCORE_J40

VCCCORE_K33

VCCCORE_K35

VCCCORE_K37

VCCCORE_K38

VCCCORE_K40

VCCCORE_K42

VCCCORE_K43

VCC_SENSE

VSS_SENSE

VIDALERT#

VIDSCK

VIDSOUT

VCCSTG_G20

C12089

10p 50V

0201

VCCIO_SENSE [58]

VSSIO_SENSE [58]

VSSSA_SENSE [66]

VCCSA_SENSE [66]

VCORE

G32

G33

G35

G37

G38

G40

G42

J30

J33

J37

J40

K33

K35

K37

K38

K40

K42

K43

E32

E33

B63

A63

D64

G20

H_CPU_SVIDALERT_N

H_CPU_SVIDCLK

H_CPU_SVIDDAT

VCCSTG

VCCIO

6.3V

0402

C12020 1u

C12090

10p 50V

0201

VCC_CORE_SENSE [66]

VSS_CORE_SENSE [66]

+VCCSTG is control by SLP_S0,

but it can overwrite by XDP, that

means it need power for XDP intrafece

6.3V

0402

C12021 1u

C12043

10u 6.3V

0402

6.3V

0402

C12022 1u

R12005 220 0201

R12006 0 0201

R12007 0 0201

6.3V

0402

C12023 1u

C12044

10u 6.3V

0402

C12045

10u 6.3V

0402

U SPECIFIC

2

C12050

22u 6.3V

0603

C12046

10u 6.3V

0402

0201

Microsoft Confidential

Microsoft Confidential

Microsoft Confidential

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

C12051

22u 6.3V

0603

C12047

10u 6.3V

0402

VCCST_CPU

R12004 56

R12003 100

A

A

A

0201

Title:

Title:

Title:

Engineer:

Engineer:

Engineer:

VCCSA

C12048

10u 6.3V

0402

SVID_ALERT# [66]

VIDSCLK [66]

VIDSOUT [66]

C12034

47u 6.3V

0603

VCCSA

C12069

10u 6.3V

0402

12. CPU(3)_SKL POWER1

12. CPU(3)_SKL POWER1

12. CPU(3)_SKL POWER1

Surface

Surface

Surface

12 79Tuesday, May 01, 2018

12 79Tuesday, May 01, 2018

1

12 79Tuesday, May 01, 2018

C12033

47u 6.3V

0603

DNP

C12070

10u 6.3V

0402

1.0.0.1

1.0.0.1

1.0.0.1

4V

0603

C12001 22u

D D

4V

0402

C12010 10u

C C

B B

A A

Page 13

5

Vinafix.com

KBL_R_U42

A48

A53

A58

A62

A66

AA63

AA64

AA66

AA67

AA69

AA70

AA71

AC64

AC65

AC66

AC67

AC68

AC69

AC70

AC71

J43

J45

J46

J48

J50

J52

J53

J55

J56

J58

J60

K48

K50

K52

K53

K55

K56

K58

K60

L62

L63

L64

L65

L66

L67

L68

L69

L70

L71

M62

N63

N64

N66

N67

N69

J70

J69

U10001M

CPU POWER 2 OF 4

VCCCORE_A48

VCCCORE_A53

VCCGT_A58

VCCGT_A62

VCCGT_A66

VCCGT_AA63

VCCGT_AA64

VCCGT_AA66

VCCGT_AA67

VCCGT_AA69

VCCGT_AA70

VCCGT_AA71

VCCGT_AC64

VCCGT_AC65

VCCGT_AC66

VCCGT_AC67

VCCGT_AC68

VCCGT_AC69

VCCGT_AC70

VCCGT_AC71

VCCCORE_J43

VCCCORE_J45

VCCCORE_J46

VCCCORE_J48

VCCCORE_J50

VCCCORE_J52

VCCGT_J53

VCCGT_J55

VCCGT_J56

VCCGT_J58

VCCGT_J60

VCCCORE_K48

VCCCORE_K50

RSVD_K52

VCCGT_K53

VCCGT_K55

VCCGT_K56

VCCGT_K58

VCCGT_K60

VCCGT_L62

VCCGT_L63

VCCGT_L64

VCCGT_L65

VCCGT_L66

VCCGT_L67

VCCGT_L68

VCCGT_L69

VCCGT_L70

VCCGT_L71

VCCGT_M62

VCCGT_N63

VCCGT_N64

VCCGT_N66

VCCGT_N67

VCCGT_N69

VCCGT_SENSE

VSSGT_SENSE

VCCGT_N70

VCCGT_N71

VCCGT_R63

VCCGT_R64

VCCGT_R65

VCCGT_R66

VCCGT_R67

VCCGT_R68

VCCGT_R69

VCCGT_R70

VCCGT_R71

VCCGT_T62

VCCGT_U65

VCCGT_U68

VCCGT_U71

VCCGT_W63

VCCGT_W64

VCCGT_W65

VCCGT_W66

VCCGT_W67

VCCGT_W68

VCCGT_W69

VCCGT_W70

VCCGT_W71

VCCGT_Y62

VCCCORE_AK42

VCCCORE_AK43

VCCCORE_AK45

VCCCORE_AK46

VCCCORE_AK48

VCCCORE_AK50

RSVD_AK52

VCCGTX_AK53

VCCGTX_AK55

VCCGTX_AK56

VCCGTX_AK58

VCCGTX_AK60

VCCGTX_AK70

VCCCORE_AL43

VCCCORE_AL46

VCCCORE_AL50

VCCGTX_AL53

VCCGTX_AL56

VCCGTX_AL60

VCCCORE_AM48

VCCCORE_AM50

VCCCORE_AM52

VCCGTX_AM53

VCCGTX_AM56

VCCGTX_AM58

VCCGTX_AU58

VCCGTX_AU63

VCCGTX_BB57

VCCGTX_BB66

VCCGTX_SENSE

VSSGTX_SENSE

N70

N71

R63

R64

R65

R66

R67

R68

R69

R70

R71

T62

U65

U68

U71

W63

W64

W65

W66

W67

W68

W69

W70

W71

Y62

AK42

AK43

AK45

AK46

AK48

AK50

AK52

AK53

AK55

AK56

AK58

AK60

AK70

AL43

AL46

AL50

AL53

AL56

AL60

AM48

AM50

AM52

AM53

AM56

AM58

AU58

AU63

BB57

BB66

AK62

AL61

VCORE

D D

C C

VCCGT_SENSE[66]

VSSGT_SENSE[66]

4

VCCGTVCCGT

VCORE

VCCGT

3

2

1

Place on primary side, beside the package

C13017

10u 6.3V

0402

C13322

10u 6.3V

0402

C13018

10u 6.3V

0402

C13323

10u 6.3V

0402

C13019

10u 6.3V

0402

C13335

10u 6.3V

0402

C13020

10u 6.3V

0402

C13336

10u 6.3V

0402

C13021

10u 6.3V

0402

C13337

10u 6.3V

0402

C13022

10u 6.3V

0402

C13338

10u 6.3V

0402

C13023

10u 6.3V

0402

C13024

10u 6.3V

0402

C13025

10u 6.3V

0402

C13026

10u 6.3V

0402

Place on secondary side

under the package

C13027

10u 6.3V

0402

VCCGT

C13028

10u 6.3V

0402

VCORE

KBL-R U42

<$LOCATION>

<MATERIAL>

13 OF 20

REV = 1

REMOVED GTX Connections

C13164

1u

6.3V

0201

C13165

1u

6.3V

0201

C13166

1u

6.3V

0201

VCCGT

Place on primary side, beside the package

C13083

10u 6.3V

0402

C13090

10u 6.3V

0402

B B

VCORE

C13190

47u 6.3V

0603

C13197

47u 6.3V

0603

C13084

10u 6.3V

0402

C13091

6.3V

10u

0402

C13191

47u 6.3V

0603

C13198

47u 6.3V

0603

C13330

10u 6.3V

0402

C13085

10u 6.3V

0402

C13097

10u 6.3V

0402

C13192

47u 6.3V

0603

C13199

47u 6.3V

0603

C13332

10u 6.3V

0402

C13086

10u 6.3V

0402

C13098

10u 6.3V

0402

C13193

47u 6.3V

0805

C13200

47u 6.3V

0603

DNP

C13333

10u 6.3V

0402

C13087

10u 6.3V

0402

C13099

10u 6.3V

0402

C13194

47u 6.3V

0805

C13201

47u 6.3V

0603

C13329

10u 6.3V

0402

C13088

10u 6.3V

0402

C13195

47u 6.3V

0603

C13202

47u 6.3V

0603

C13331

10u 6.3V

0402

C13089

10u 6.3V

0402

C13196

47u 6.3V

0603

C13203

47u 6.3V

0603

C13334

10u 6.3V

0402

VCCGT

Place on primary side, beside the package

C13300

22u

0603

C13306

22u

0603

DNP

6.3V

6.3V

C13301

22u

0603

C13307

22u

0603

DNP

6.3V

6.3V

C13302

22u

0603

C13308

22u

0603

DNP

6.3V

6.3V

C13303

22u

0603

C13309

22u

0603

DNP

6.3V

6.3V

C13304

22u

0603

C13310

22u

0603

DNP

6.3V

6.3V

C13311

22u

0603

C13314

22u

0603

DNP

6.3V

6.3V

C13312

22u

0603

C13315

22u

0603

DNP

6.3V

6.3V

C13313

22u

0603

DNP

C13316

22u

0603

DNP

6.3V

6.3V

C13317

22u

0603

DNP

6.3V

C13167

1u

6.3V

0201

C13168

1u

6.3V

0201

C13169

1u

6.3V

0201

DNP

DNP

C13343

10u 6.3V

0402

C13348

10u 6.3V

0402

DNP

DNP

C13341

10u 6.3V

0402

C13346

10u 6.3V

0402

C13340

10u 6.3V

0402

DNP

C13345

10u 6.3V

0402

A A

DNP

VCORE

C13339

6.3V

10u

0402

DNP

C13344

6.3V

10u

0402

DNP

Place on secondary side

under the package

C13171

1u

0201

6.3V

5

C13172

1u

0201

6.3V

C13170

1u

0201

6.3V

DNP

DNP

C13342

10u 6.3V

0402

C13347

10u 6.3V

0402

VCORE

Place on secondary side

under the package

C13173

1u

0201

6.3V

C13174

1u

0201

6.3V

4

C13175

1u

0201

6.3V

VCCGT

Place on primary side, beside the package

C13122

47u 6.3V

DNP

3

0603

C13123

47u 6.3V

0805

DNP

C13131

47u 6.3V

0805

DNP

C13106

47u 6.3V

0603

C13107

47u 6.3V

0603

C13108

47u 6.3V

2

C13109

47u 6.3V

0603

DNP

DNP

0603

U SPECIFIC

C13305

47u 6.3V

0805

DNP

C13318

47u 6.3V

0603

DNP

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

C13319

47u 6.3V

0805

DNP

Microsoft Conf idential

Microsoft Conf idential

Microsoft Conf idential

C

C

C

C13320

47u 6.3V

0603

DNP

Title:

Title:

Title:

Engineer:

Engineer:

Engineer:

A

A

A

C13321

47u 6.3V

0805

DNP

13. CPU(4)_SKL_POWER2

13. CPU(4)_SKL_POWER2

13. CPU(4)_SKL_POWER2

Surface

Surface

Surface

13 79Tuesday, May 01, 2018

13 79Tuesday, May 01, 2018

1

13 79Tuesday, May 01, 2018

1.0.0.1

1.0.0.1

1.0.0.1

Page 14

5

Vinafix.com

U10001P

KBL_R_U42

GND 1 OF 3

A5

VSS_A5

A67

VSS_A67

A70

VSS_A70

AA2

D D

C C

AG16

AG17

AG18

AG19

AG20

AG21

AG71

B B

AA4

AA65

AA68

AB15

AB16

AB18

AB21

AB8

AD13

AD16

AD19

AD20

AD21

AD62

AD8

AE64

AE65

AE66

AE67

AE68

AE69

AF1

AF10

AF15

AF17

AF2

AF4

AF63

AH13

AH6

AH63

AH64

AH67

AJ15

AJ18

AJ20

AJ4

AK11

AK16

AK18

AK21

AK22

AK27

AK63

AK68

AK69

AK8

AL2

AL28

AL32

AL35

AL38

AL4

AL45

AL48

AL52

AL55

AL58

AL64

VSS_AA2

VSS_AA4

VSS_AA65

VSS_AA68

VSS_AB15

VSS_AB16

VSS_AB18

VSS_AB21

VSS_AB8

VSS_AD13

VSS_AD16

VSS_AD19

VSS_AD20

VSS_AD21

VSS_AD62

VSS_AD8

VSS_AE64

VSS_AE65

VSS_AE66

VSS_AE67

VSS_AE68

VSS_AE69

VSS_AF1

VSS_AF10

VSS_AF15

VSS_AF17

VSS_AF2

VSS_AF4

VSS_AF63

VSS_AG16

VSS_AG17

VSS_AG18

VSS_AG19

VSS_AG20

VSS_AG21

VSS_AG71

VSS_AH13

VSS_AH6

VSS_AH63

VSS_AH64

VSS_AH67

VSS_AJ15

VSS_AJ18

VSS_AJ20

VSS_AJ4

VSS_AK11

VSS_AK16

VSS_AK18

VSS_AK21

VSS_AK22

VSS_AK27

VSS_AK63

VSS_AK68

VSS_AK69

VSS_AK8

VSS_AL2

VSS_AL28

VSS_AL32

VSS_AL35

VSS_AL38

VSS_AL4

VSS_AL45

VSS_AL48

VSS_AL52

VSS_AL55

VSS_AL58

VSS_AL64

VSS_AL65

VSS_AL66

VSS_AM13

VSS_AM21

VSS_AM25

VSS_AM27

VSS_AM43

VSS_AM45

VSS_AM46

VSS_AM55

VSS_AM60

VSS_AM61

VSS_AM68

VSS_AM71

VSS_AM8

VSS_AN20

VSS_AN23

VSS_AN28

VSS_AN30

VSS_AN32

VSS_AN33

VSS_AN35

VSS_AN37

VSS_AN38

VSS_AN40

VSS_AN42

VSS_AN58

VSS_AN63

VSS_AP10

VSS_AP18

VSS_AP20

VSS_AP23

VSS_AP28

VSS_AP32

VSS_AP35

VSS_AP38

VSS_AP42

VSS_AP58

VSS_AP63

VSS_AP68

VSS_AP70

VSS_AR11

VSS_AR15

VSS_AR16

VSS_AR20

VSS_AR23

VSS_AR28

VSS_AR35

VSS_AR42

VSS_AR43

VSS_AR45

VSS_AR46

VSS_AR48

VSS_AR5

VSS_AR50

VSS_AR52

VSS_AR53

VSS_AR55

VSS_AR58

VSS_AR63

VSS_AR8

VSS_AT2

VSS_AT20

VSS_AT23

VSS_AT28

VSS_AT35

VSS_AT4

VSS_AT42

VSS_AT56

VSS_AT58

AL65

AL66

AM13

AM21

AM25

AM27

AM43

AM45

AM46

AM55

AM60

AM61

AM68

AM71

AM8

AN20

AN23

AN28

AN30

AN32

AN33

AN35

AN37

AN38

AN40

AN42

AN58

AN63

AP10

AP18

AP20

AP23

AP28

AP32

AP35

AP38

AP42

AP58

AP63

AP68

AP70

AR11

AR15

AR16

AR20

AR23

AR28

AR35

AR42

AR43

AR45

AR46

AR48

AR5

AR50

AR52

AR53

AR55

AR58

AR63

AR8

AT2

AT20

AT23

AT28

AT35

AT4

AT42

AT56

AT58

4

AT63

AT68

AT71

AU10

AU15

AU20

AU32

AU38

AV1

AV68

AV69

AV70

AV71

AW10

AW12

AW14

AW16

AW18

AW21

AW23

AW26

AW28

AW30

AW32

AW34

AW36

AW38

AW41

AW43

AW45

AW47

AW49

AW51

AW53

AW55

AW57

AW6

AW60

AW62

AW64

AW66

AW8

AY66

B10

B14

B18

B22

B30

B34

B39

B44

B48

B53

B58

B62

B66

B71

BA1

BA10

BA14

BA18

BA2

BA23

BA28

BA32

BA36

F68

BA45

U10001Q

KBL_R_U42

GND 2 OF 3

VSS_AT63

VSS_AT68

VSS_AT71

VSS_AU10

VSS_AU15

VSS_AU20

VSS_AU32

VSS_AU38

VSS_AV1

VSS_AV68

VSS_AV69

VSS_AV70

VSS_AV71

VSS_AW10

VSS_AW12

VSS_AW14

VSS_AW16

VSS_AW18

VSS_AW21

VSS_AW23

VSS_AW26

VSS_AW28

VSS_AW30

VSS_AW32

VSS_AW34

VSS_AW36

VSS_AW38

VSS_AW41

VSS_AW43

VSS_AW45

VSS_AW47

VSS_AW49

VSS_AW51

VSS_AW53

VSS_AW55

VSS_AW57

VSS_AW6

VSS_AW60

VSS_AW62

VSS_AW64

VSS_AW66

VSS_AW8

VSS_AY66

VSS_B10

VSS_B14

VSS_B18

VSS_B22

VSS_B30

VSS_B34

VSS_B39

VSS_B44

VSS_B48

VSS_B53

VSS_B58

VSS_B62

VSS_B66

VSS_B71

VSS_BA1

VSS_BA10

VSS_BA14

VSS_BA18

VSS_BA2

VSS_BA23

VSS_BA28

VSS_BA32

VSS_BA36

VSS_F68

VSS_BA45

VSS_BA49

VSS_BA53

VSS_BA57

VSS_BA6

VSS_BA62

VSS_BA66

VSS_BA71

VSS_BB18

VSS_BB26

VSS_BB30

VSS_BB34

VSS_BB38

VSS_BB43

VSS_BB55

VSS_BB6

VSS_BB60

VSS_BB64

VSS_BB67

VSS_BB70

VSS_C1

VSS_C25

VSS_C5

VSS_D10

VSS_D11

VSS_D14

VSS_D18

VSS_D22

VSS_D25

VSS_D26

VSS_D30

VSS_D34

VSS_D39

VSS_D44

VSS_D45

VSS_D47

VSS_D48

VSS_D53

VSS_D58

VSS_D6

VSS_D62

VSS_D66

VSS_D69

VSS_E11

VSS_E15

VSS_E18

VSS_E21

VSS_E46

VSS_E50

VSS_E53

VSS_E56

VSS_E6

VSS_E65

VSS_E71

VSS_F1

VSS_F13

VSS_F2

VSS_F22

VSS_F23

VSS_F27

VSS_F28

VSS_F32

VSS_F33

VSS_F35

VSS_F37

VSS_F38

VSS_F4

VSS_F40

VSS_F42

VSS_BA41

BA49

BA53

BA57

BA6

BA62

BA66

BA71

BB18

BB26

BB30

BB34

BB38

BB43

BB55

BB6

BB60

BB64

BB67

BB70

C1

C25

C5

D10

D11

D14

D18

D22

D25

D26

D30

D34

D39

D44

D45

D47

D48

D53

D58

D6

D62

D66

D69

E11

E15

E18

E21

E46

E50

E53

E56

E6

E65

E71

F1

F13

F2

F22

F23

F27

F28

F32

F33

F35

F37

F38

F4

F40

F42

BA41

3

U10001R

KBL_R_U42

GND 3 OF 3

F8

G10

G22

G43

G45

G48

G5

G52

G55

G58

G6

G60

G63

G66

H15

H18

H71

J11

J13

J25

J28

J32

J35

J38

J42

J8

K16

K18

K22

K61

K63

K64

K65

K66

K67

K68

K70

K71

L11

L16

L17

KBL-R U42

<$LOCATION>

<MATERIAL>

18 OF 20

REV = 1

VSS_F8

VSS_G10

VSS_G22

VSS_G43

VSS_G45

VSS_G48

VSS_G5

VSS_G52

VSS_G55

VSS_G58

VSS_G6

VSS_G60

VSS_G63

VSS_G66

VSS_H15

VSS_H18

VSS_H71

VSS_J11

VSS_J13

VSS_J25

VSS_J28

VSS_J32

VSS_J35

VSS_J38

VSS_J42

VSS_J8

VSS_K16

VSS_K18

VSS_K22

VSS_K61

VSS_K63

VSS_K64

VSS_K65

VSS_K66

VSS_K67

VSS_K68

VSS_K70

VSS_K71

VSS_L11

VSS_L16

VSS_L17

VSS_L18

VSS_L2

VSS_L20

VSS_L4

VSS_L8

VSS_N10

VSS_N13

VSS_N19

VSS_N21

VSS_N6

VSS_N65

VSS_N68

VSS_P17

VSS_P19

VSS_P20

VSS_P21

VSS_R13

VSS_R6

VSS_T15

VSS_T17

VSS_T18

VSS_T2

VSS_T21

VSS_T4

VSS_U10

VSS_U63

VSS_U64

VSS_U66

VSS_U67

VSS_U69

VSS_U70

VSS_V16

VSS_V17

VSS_V18

VSS_W13

VSS_W6

VSS_W9

VSS_Y17

VSS_Y19

VSS_Y20

VSS_Y21

L18

L2

L20

L4

L8

N10

N13

N19

N21

N6

N65

N68

P17

P19

P20

P21

R13

R6

T15

T17

T18

T2

T21

T4

U10

U63

U64

U66

U67

U69

U70

V16

V17

V18

W13

W6

W9

Y17

Y19

Y20

Y21

2

1

KBL-R U42

A A

<$LOCATION>

<MATERIAL>

16 OF 20

REV = 1

5

4

KBL-R U42

<$LOCATION>

<MATERIAL>

17 OF 20

REV = 1

14. CPU(5)_GND

14. CPU(5)_GND

Title:

Title:

Title:

Microsoft Confidential

Microsoft Confidential

Microsoft Confidential

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

B

B

U SPECIFIC

3

2

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

A

A

A

Engineer:

Engineer:

Engineer:

14. CPU(5)_GND

Surface

Surface

Surface

14 79Friday, April 27, 2018

14 79Friday, April 27, 2018

1

14 79Friday, April 27, 2018

1.0.0.1

1.0.0.1

1.0.0.1

Page 15

5

Vinafix.com

Vinafix.com

4

3

2

1

KBL_R_U42

RSVD_TP_BB68

RSVD_TP_BB69

RSVD_TP_AK13

RSVD_TP_AK12

RSVD_BB2

RSVD_BA3

TP5

TP6

RSVD_D5

RSVD_D4

RSVD_B2

RSVD_C2

RSVD_B3

RSVD_A3

RSVD_AW1

RSVD_E1

RSVD_E2

RSVD_BA4

RSVD_BB4

RSVD_A4

RSVD_C4

TP4

RSVD_A69

RSVD_B69

RSVD_AY3

RSVD_D71

RSVD_C70

RSVD_C54

RSVD_D54

TP1

TP2

VSS_AY71

ZVM#

RSVD_TP_AW71

RSVD_TP_AW70

MSM#

PROC_SELECT#

BB68

BB69

AK13

AK12

BB2

BA3

AU5

AT5

D5

D4

B2

C2

B3

A3

AW1

E1

E2

BA4

BB4

A4

C4

BB5

A69

B69

AY3

D71

C70

C54

D54

AY4

BB3

AY71

AR56

AW71

AW70

AP56

C64

RSVD_TP_AK13

RSVD_TP_AK12

SMD RND 22.8mil

GTP15002

GTP15003

SMD RND 22.8mil

GTP15004

SMD RND 22.8mil

ZVM# and MSM# may need to

control the VCCOPC and VCCEOPIO

E68

B67

D65

D67

E70

C68

D68

C67

F71

G69

F70

G68

H70

G71

H69

G70

E63

F63

E66

F66

E60

E8

AY2

AY1

D1

D3

K46

K45

AL25

AL27

C71

B70

F60

A52

BA70

BA68

J71

J68

F65

G65

F61

E61

U10001S

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

CFG[18]

CFG[19]

CFG_RCOMP

ITP_PMODE

RSVD_AY2

RSVD_AY1

RSVD_D1

RSVD_D3

RSVD_K46

RSVD_K45

RSVD_AL25

RSVD_AL27

RSVD_C71

RSVD_B70

RSVD_F60

RSVD_A52

RSVD_TP_BA70

RSVD_TP_BA68

RSVD_J71

RSVD_J68

VSS_F65

VSS_G65

RSVD_F61

RSVD_E61

KBL-R U42

<$LOCATION>

<MATERIAL>

19 OF 20

REV = 1

RESERVED SIGNALS-1

GTP15001

SMD RND 22.8mil

CFG0[18]

CFG1[18]

CFG2[18]

CFG3[18]

D D

CFG4

0 enable eDP

Default

C C

B B

1

Disable eDP

CFG4[18]

CFG5[18]

CFG6[18]

CFG7[18]

CFG8[18]

CFG9[18]

CFG10[18]

CFG11[18]

CFG12[18]

CFG13[18]

CFG14[18]

CFG15[18]

CFG16[18]

CFG17[18]

CFG18[18]

CFG19[18]

AW69

AW68

AU56

AW48

U10001T

C7

U12

U11

H11

KBL-R U42

<$LOCATION>

<MATERIAL>

20 OF 20

REV = 1

KBL_R_U42

RSVD_AW69

RSVD_AW68

RSVD_AU56

RSVD_AW48

XTAL24_OUT

RSVD_U12

RSVD_U11

RSVD_H11

R15001 49.9

R15002

1K

0201

RSVD/XTAL

0201

ITP_PMODE[18]

RSVD_F6

XTAL24_IN

RSVD_C11

RSVD_B11

RSVD_A11

RSVD_D12

RSVD_C12

RSVD_F52

F6

E3

C11

B11

A11

D12

C12

F52

XTAL_24M_OUT

CFG_RCOMP

XTAL_24M_IN

R1504 1M

0201S_P28-W35

X150124MHz

R1503 0

0201S_P28-W35

C1503

A A

5

50V

0201S_P33

10p

4

3 1

GND

X948599-001

24

C1502

50V

10p

0201S_P33

15. CPU(6)_CFG_RESERVED

15. CPU(6)_CFG_RESERVED

Title:

Title:

Title:

Microsoft Confidential

Microsoft Confidential

Microsoft Confidential

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

B

B

U SPECIFIC

3

2

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

A

A

A

Engineer:

Engineer:

Engineer:

15. CPU(6)_CFG_RESERVED

Surface

Surface

Surface

1.0.0.1

1.0.0.1

1.0.0.1

15 79Friday, April 27, 2018

15 79Friday, April 27, 2018

1

15 79Friday, April 27, 2018

Page 16

5

Vinafix.com

U16001

H9CCNNN BLTBLAR-NUD

M_A_CAA0

M_A_CAA1

M_A_CAA2

M_A_CAA3

M_A_CAA4

M_A_CAA5

M_A_CAA6

M_A_CAA7

M_A_CAA8

M_A_CAA9

D D

M_A_DIM0_CLKP1[11,16]

M_A_DIM0_CLKN 1[11,16]

M_A_DIM0_CKE2[11,16]

M_A_DIM0_CKE3[11,16] M_A_DIM0_CKE1[11,16]

M_A_DIM0_CS0_N[11,16]

M_A_DIM0_CS1_N[11,16]

M_A_DQSP2[11]

M_A_DQSN2[11]

C C

B B

V0P6DX_LPDDR3

A A

M_A_DQSP0[11]

M_A_DQSN0[11]

M_A_DQSP3[11]

M_A_DQSN3[11]

M_A_DQSP1[11]

M_A_DQSN1[11]

C16072

1u

6.3V

0402

distributed along terminations. Shown in blue

Figure 4-57 in PDG2.0

C16073

1u

6.3V

0402

C16074

1u

6.3V

0402

R2

P2

N2

N3

M3

F3

E3

E2

D2

C2

J3

J2

K3

K4

L3

L4

L8

G8

P8

D8

A1

A2

A12

A13

B1

B13

T1

T13

U1

U2

U12

U13

L10

L11

G10

G11

P10

P11

D10

D11

B2

B5

C5

E4

E5

F5

H2

J12

K2

L6

M5

N4

N5

R4

R5

T2

T3

T4

T5

C3

D3

F4

G3

G4

J4

M4

P3

B6

B12

C6

D12

E6

F6

F12

G6

G9

H10

K10

L9

M6

M12

N6

P12

R6

T6

T12

C16075

1u

6.3V

0402

CA0

CA1

CA2

CA3

CA4

CA5

CA6

CA7

CA8

CA9

CK

CK#

CKE0

CKE1

CS#0

CS#1

DM0

DM1

DM2

DM3/NC

DNU1

DNU2

DNU3

DNU4

DNU5

DNU6

DNU7

DNU8

DNU9

DNU10

DNU11

DNU12

DQS0

DQS0#

DQS1

DQS1#

DQS2/NC

DQS2#/NC

DQS3/NC

DQS3#/NC

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSSCA1

VSSCA2

VSSCA3

VSSCA4

VSSCA5

VSSCA6

VSSCA7

VSSCA8

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSSQ10

VSSQ11

VSSQ12

VSSQ13

VSSQ14

VSSQ15

VSSQ16

VSSQ17

VSSQ18

VSSQ19

TBL1601

C16076

1u

6.3V

0402

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16/NC

DQ17/NC

DQ18/NC

DQ19/NC

DQ20/NC

DQ21/NC

DQ22/NC

DQ23/NC

DQ24/NC

DQ25/NC

DQ26/NC

DQ27/NC

DQ28/NC

DQ29/NC

DQ30/NC

DQ31/NC

VDD1_1

VDD1_3

VDD1_5

VDD1_7

VDD1_9

VDD1_2

VDD1_4

VDD1_6

VDD1_8

VDD1_10

VDD2_1

VDD2_2

VDD2_3

VDD2_4

VDD2_5

VDD2_6

VDD2_7

VDD2_8

VDD2_9