Microchip Technology Inc PIC16C925-CL, PIC16C926-I-L, PIC16C926-CL, PIC16C925-I-L, PIC16LC926-I-L Datasheet

PIC16C925/926

Data Sheet

64/68-Pin CMOS Microcontrollers

with LCD Driver

2001 Microchip Technology Inc. Preliminary DS39544A

“All rights reserved. Copyright © 2001, Microchip Technology

Incorporated, USA. Information contained in this publication

regarding device applications and the like is intended through

suggestion only and may be superseded by updates. No representation or warranty is given and no liability is assumed by

Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or

other intellectual property rights arising from such use or otherwise. Use of Microchip’s products as critical components in

life support systems is not authorized except with express

written approval by Microchip. No licenses are conveyed,

implicitly or otherwise, under any intellectual property rights.

The Microchip logo and name are registered trademarks of

Microchip Technology Inc. in the U.S.A. and other countries.

All rights reserved. All other trademarks mentioned herein are

the property of their respective companies. No licenses are

conveyed, implicitly or otherwise, under any intellectual property rights.”

Trademarks

The Microchip name, logo, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, K

EELOQ, SEEVAL, MPLAB and The

Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and

other countries.

Total Endurance, ICSP, In-Circuit Serial Programming, FilterLab, MXDEV, microID, FlexROM, fuzzyLAB, MPASM,

MPLINK, MPLIB, PICDEM, ICEPIC, Migratable Memory,

FanSense, ECONOMONITOR, SelectMode and microPort

are trademarks of Microchip Technology Incorporated in the

U.S.A.

Serialized Quick T erm Programming (SQTP) is a service mark

of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

© 2001, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

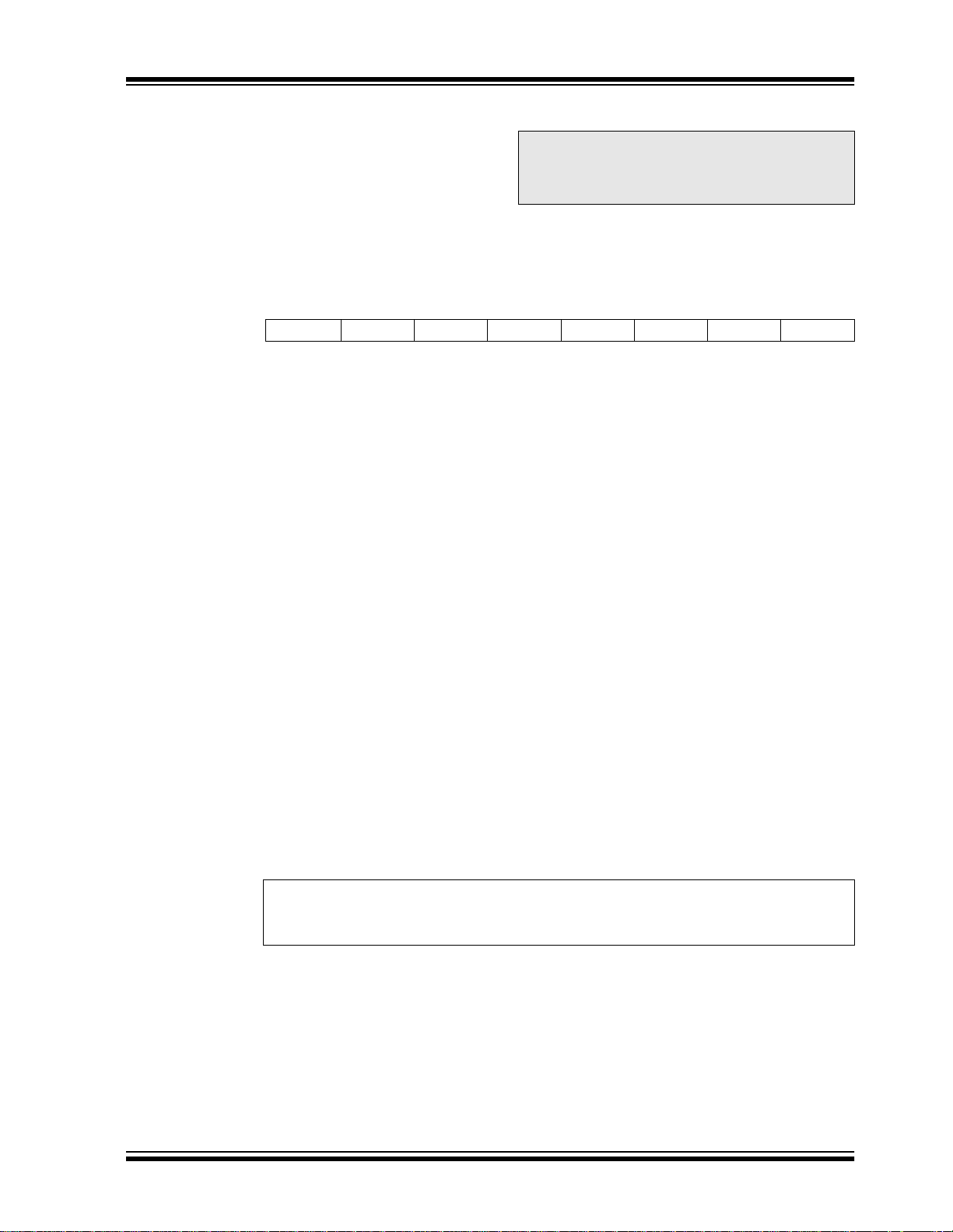

Microchip received QS-9000 quality system

certification for its worldwide headquarters,

design and wafer fabrication facilities in

Chandler and Tempe, Arizona in July 1999. The

Company’s quality system processes and

procedures are QS-9000 compliant for its

PICmicro

devices, Serial EEPROMs and microperipheral

products. In addition, Microchip’s quality

system for the design and manufacture of

development systems is ISO 9001 certified.

®

8-bit MCUs, KEELOQ

®

code hoppin g

DS39544A - page ii Preliminary 2001 Microchip Technology Inc.

PIC16C925/926

64/68-Pin CMOS Microcontrollers with LCD Driver

High Performance RISC CPU:

• Only 35 single word instructions to learn

• All single cycle instructions except for program

branches which are two-cycle

• Operating speed: DC - 20 MHz clock input

DC - 200 ns instruction cycle

• Up to 8K x 14-bit words of EPROM program memory,

336 bytes general purpose registe r s (SRA M),

60 special function registers

• Pinout compatible with PIC16C923/924

Peripheral Features:

• 25 I/O pins with individual direction control and

25-27 input only pins

• Timer0 module: 8-bit timer/counter with program-

mable 8-bit prescaler

• Timer1 module: 16-bit timer/counte r, can be incre-

mented during SLEEP via external cryst al/clo ck

• Timer2 module: 8-bit timer/counter with 8-bit

period register, prescaler, and postscaler

• One Capture, Compare, PWM module

• Synchronous Serial Port (SSP) module with

two modes of operation:

- 3-wire SPI™ (supports all 4 SPI modes)

2

C™ Slave mode

-I

• Programmable LCD timing module:

- Multiple LCD timing sources available

- Can drive LCD panel while in SLEEP mode

- Static, 1/2, 1/3, 1/4 multiplex

- Static drive and 1/3 bias capability

- 16 bytes of dedicated LCD RAM

- Up to 32 segments, up to 4 commons

Analog Features:

• 10-bit 5-channel Analog -to-Digital Converter (A/D)

• Brown-out Reset (BOR)

Special Microcontroller Features:

• Power-on Reset (POR)

• Power-up Timer (PWRT) and Oscillator Start-up

Timer (OST)

• Watchdog Timer (WDT) with its own on-chip RC

oscillator for reliable operation

• Programmable code protection

• Selectable oscilla tor opti ons

• In-Circuit Serial Programming™ (ICSP™) via

two pins

• Processor read access to program memo ry

CMOS Technology:

• Low power, high speed CMOS/EPROM

technology

• Fully static design

• Wide operating voltage range: 2.5V to 5.5V

• Commercial and Industrial temperature ranges

• Low power consumption

Common Segment Pixels

13232

23162

33090

429116

2001 Microchip Technology Inc. Preliminary DS39544A-page 1

PIC16C925/926

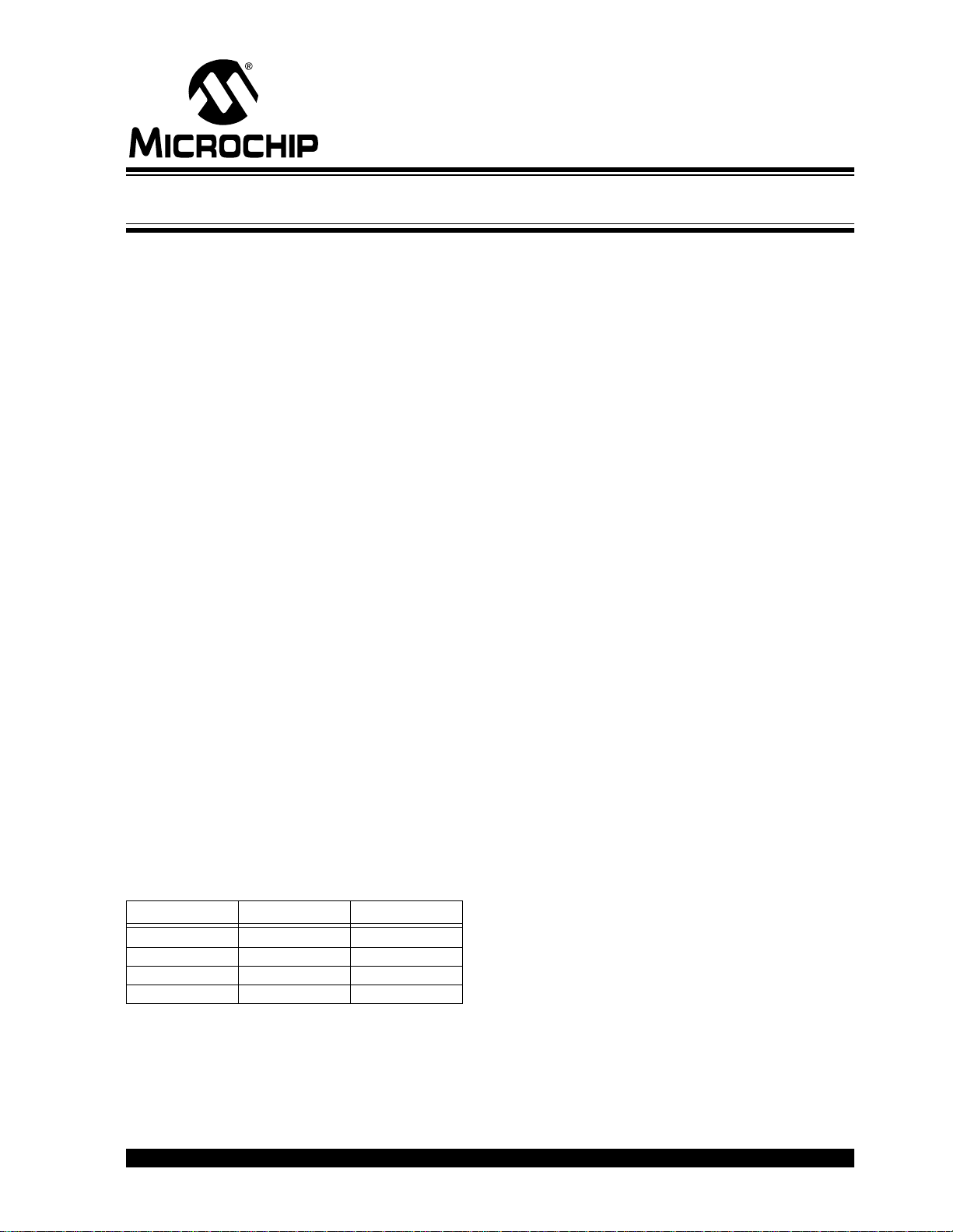

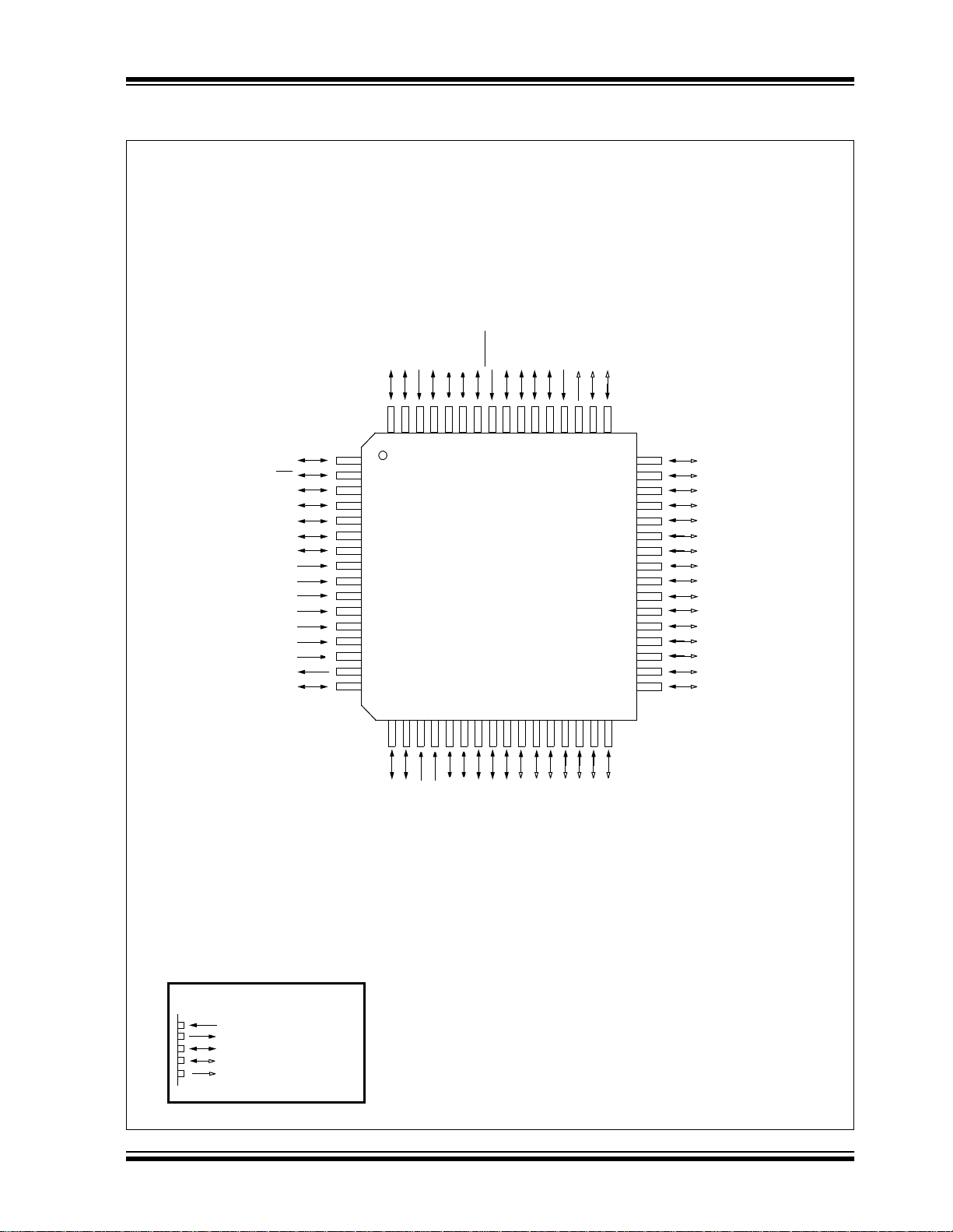

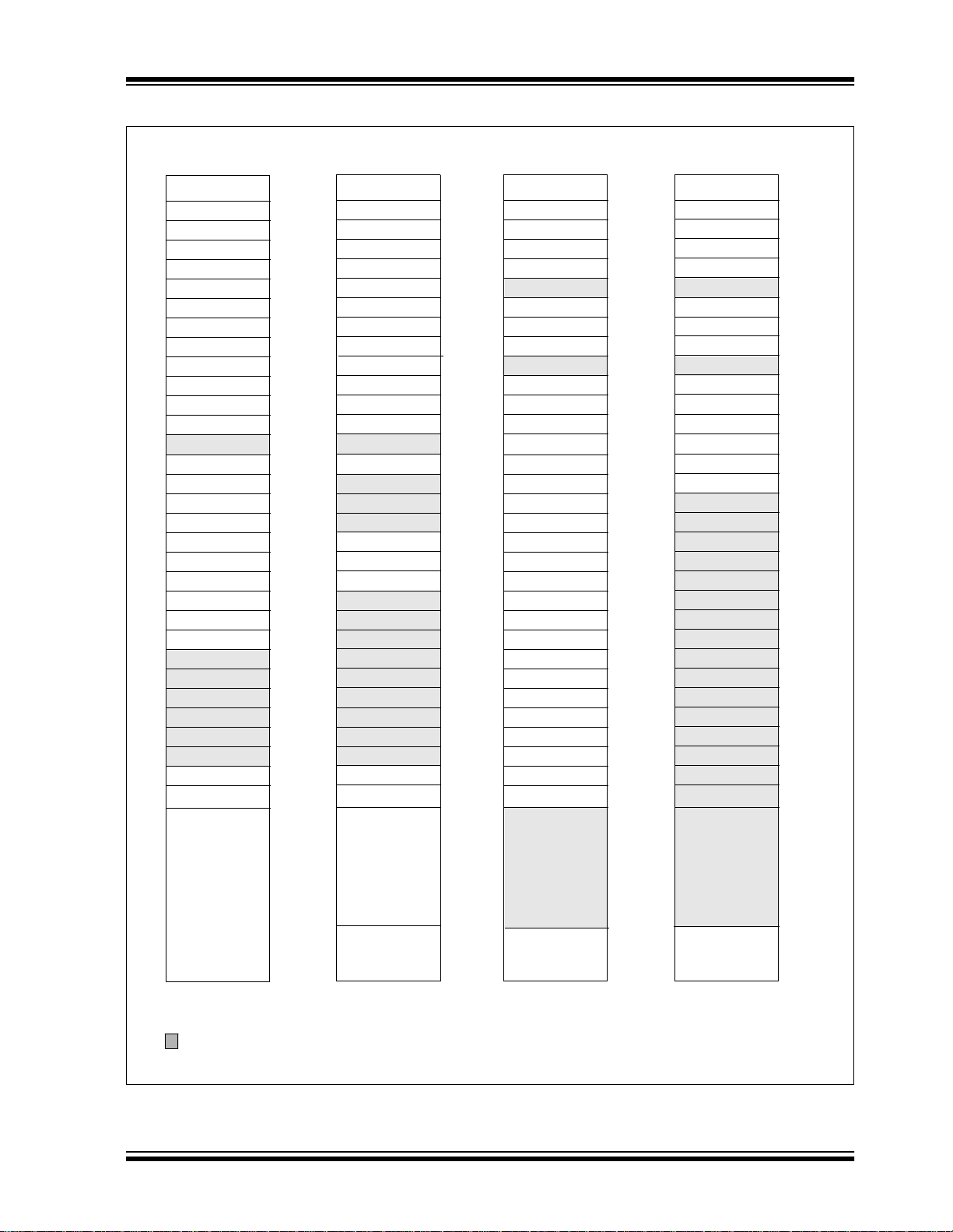

Pin Diagrams

PLCC, CLCC

REF-

/VPP

SS

RA3/AN3/VREF+

RA1/AN1

RA0/AN0

RB2

RB3

MCLR

N/C

RB4

RB5

RB7

RB6

VDDCOM0

RD7/SEG31/COM1

RA2/AN2/V

V

RD6/SEG30/COM2

RA4/T0CKI

RA5/AN4/SS

RC3/SCK/SCL

RC4/SDI/SDA

OSC1/CLKIN

OSC2/CLKOUT

RC0/T1OSO/T1CKI

RB1

RB0/INT

RC5/SDO

C1

C2

LCD2

V

LCD3

V

VDD

A

VDD

VSS

987654321

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

2728293031323334353637383940414243

RC1/T1OSI

PIC16C92X

LCD1

V

VLCDADJ

RC2/CCP1

RD0/SEG00

RD1/SEG01

68676665646362

RE7/SEG27

RD2/SEG02

RD3/SEG03

RD4/SEG04

RE0/SEG05

RE1/SEG06

RE2/SEG07

RE3/SEG08

RE4/SEG09

RE5/SEG10

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

RE6/SEG11

RD5/SEG29/COM3

RG6/SEG26

RG5/SEG25

RG4/SEG24

RG3/SEG23

RG2/SEG22

RG1/SEG21

RG0/SEG20

RG7/SEG28

RF7/SEG19

RF6/SEG18

RF5/SEG17

RF4/SEG16

RF3/SEG15

RF2/SEG14

RF1/SEG13

RF0/SEG12

LEGEND:

Input Pin

Output Pin

Input/Output Pin

Digital Input/LCD Output Pin

LCD Output Pin

DS39544A-page 2 Preliminary 2001 Microchip Technology Inc.

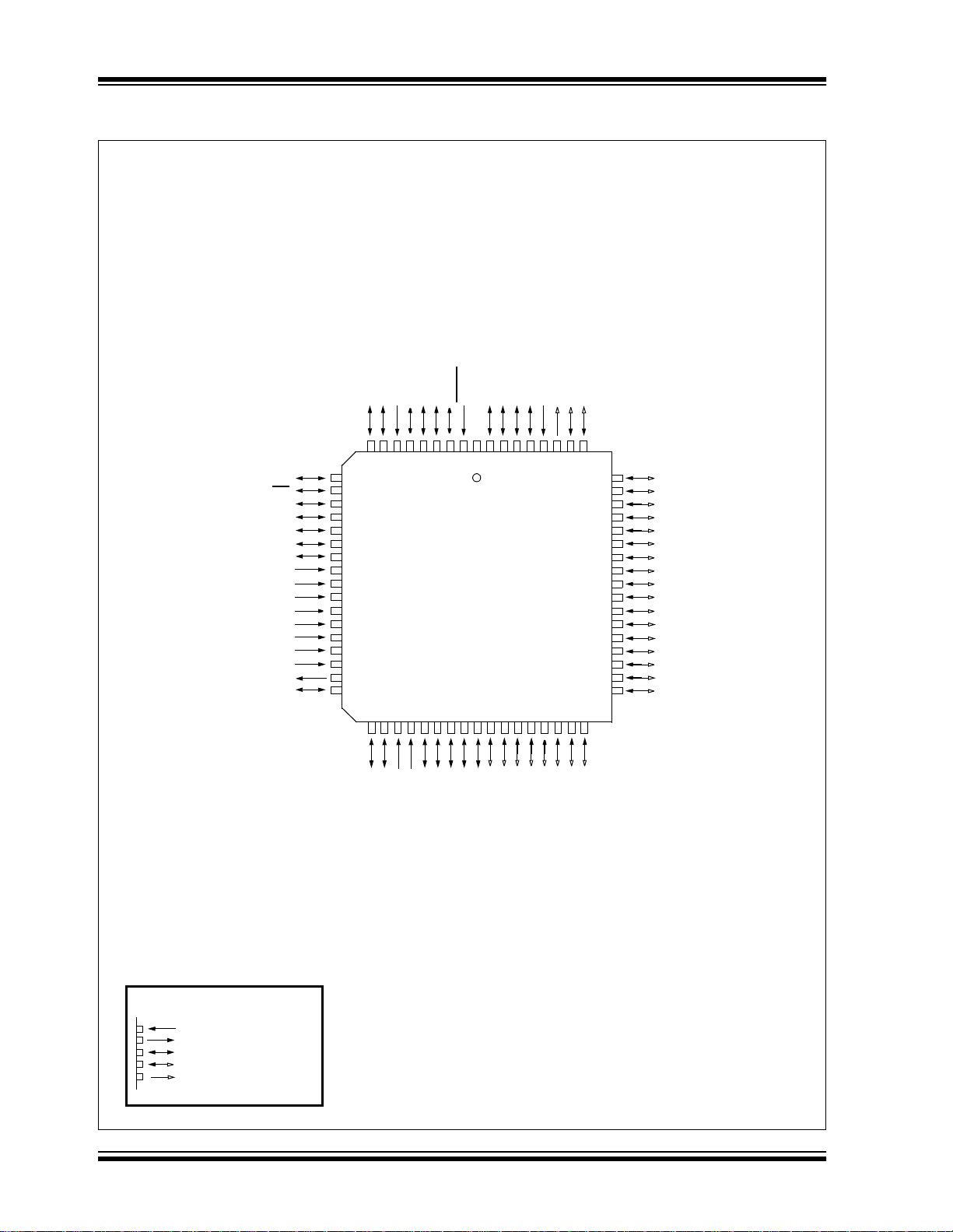

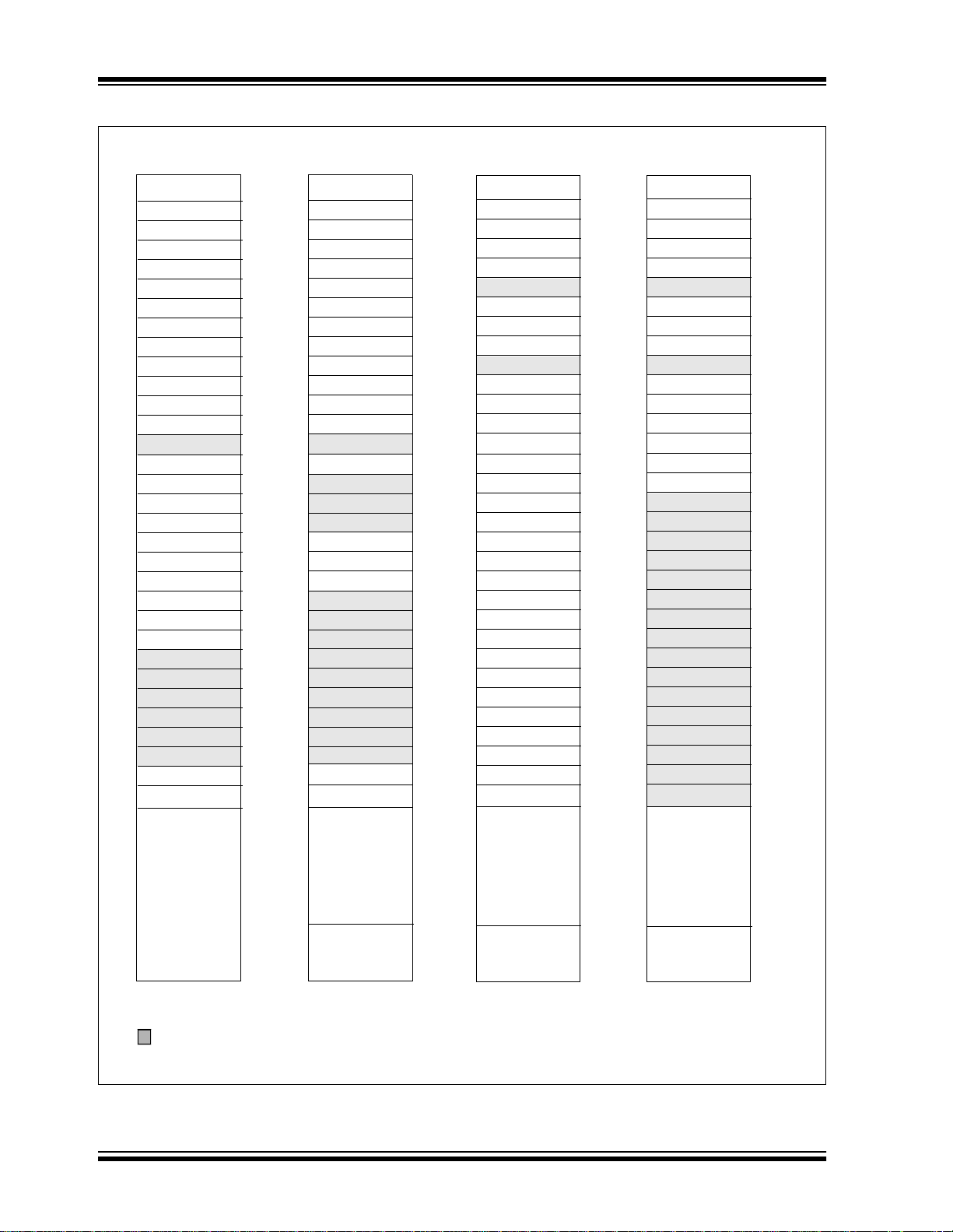

Pin Diagrams (Continued)

TQFP

PIC16C925/926

REF-

RA4/T0CKI

RA5/AN4/SS

RC3/SCK/SCL

RC4/SDI/SDA

OSC1/CLKIN

OSC2/CLKOUT

RC0/T1OSO/T1CKI

RB1

RB0/INT

RC5/SDO

C1

C2

LCD2

V

LCD3

V

V

DD

VSS

SS

RA3/AN3/VREF+

RA1/AN1

RA2/AN2/V

V

646362616059585756555453525150

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

171819202122232425262728293031

MCLR/VPP

RA0/AN0

RB2

RB4

RB5

RB3

RB7

PIC16C92X

DD

COM0

V

RD7/SEG31/COM1

RB6

RD6/SEG30/COM2

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

RD5/SEG29/COM3

RG6/SEG26

RG5/SEG25

RG4/SEG24

RG3/SEG23

RG2/SEG22

RG1/SEG21

RG0/SEG20

RF7/SEG19

RF6/SEG18

RF5/SEG17

RF4/SEG16

RF3/SEG15

RF2/SEG14

RF1/SEG13

RF0/SEG12

LCD1

V

VLCDADJ

RC2/CCP1

RC1/T1OSI

LEGEND:

Input Pin

Output Pin

Input/Output Pin

Digital Input/LCD Output Pin

LCD Output Pin

2001 Microchip Technology Inc. Preliminary DS39544A-page 3

RD0/SEG00

RD1/SEG01

RE0/SEG05

RE1/SEG06

RE2/SEG07

RE3/SEG08

RE4/SEG09

RE6/SEG11

RD2/SEG02

RD3/SEG03

RD4/SEG04

RE5/SEG10

PIC16C925/926

Table of Contents

1.0 Device Overview ...................................................................................................................................................5

2.0 Memory Organization ..........................................................................................................................................11

3.0 Reading Program Memory.................................................................................................................................. 27

4.0 I/O Ports ..............................................................................................................................................................29

5.0 Timer0 Module ....................................................................................................................................................41

6.0 Timer1 Module ....................................................................................................................................................47

7.0 Timer2 Module ....................................................................................................................................................51

8.0 Capture/Compare/PWM (CCP) Module ..............................................................................................................53

9.0 Synchronous Serial Port (SSP) Module ..............................................................................................................59

10.0 Analog-to-Digital Converter (A/D) Module ...........................................................................................................75

11.0 LCD Module ........................................................................................................................................................83

12.0 Special Features of the CPU............................................................................................................................... 97

13.0 Instruction Set Summary ...................................................................................................................................113

14.0 Development Support .......................... ...... ..... ........................................ ..... ...... ...... .........................................133

15.0 Electrical Characteristics ...................................................................................................................................139

16.0 DC and AC Characteristics Graphs and Tables ................................................................................................159

17.0 Packaging Information ......................................................................................................................................161

Appendix A: Revision History.................................................................................................................................... 167

Appendix B: Device Differences ............................................................................................................................... 167

Appendix C: Conversion Considerations .................................................................................................................. 168

Index .......................................................................................................................................................................... 169

On-Line Support......................................................................................................................................................... 175

Reader Response...................................................................................................................................................... 176

PIC16C925/926 Product Identifica tio n Syst em........................................... ....................................... ........................ 177

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or c omm ents regarding th is publication, p lease c ontact the M a rketing Communications Department via

E-mail at docerrors@mail.microchip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-4150.

We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision

of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

• The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

Customer Notification System

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

DS39544A-page 4 Preliminary 2001 Microchip Technology Inc.

PIC16C925/926

1.0 DEVICE OVERVIEW

This document cont a ins dev ice -sp ec ifi c info rm ation for

the following devices:

1. PIC16C925

2. PIC16C926

The PIC16C925/926 series is a family of low cost, high

performanc e, CM OS , f u ll y stati c, 8 -b it m ic roc o nt ro ll ers

with an integrated LCD Driver module, in the

PIC16CXXX mid-range family.

For the PIC16C925/926 family, there are two device

“types” as indicated in the device number:

1. C, as in PIC16C926. These devices operate

over the standard voltage range.

2. LC, as in PIC16LC926. These devices operate

over an extended volta ge rang e.

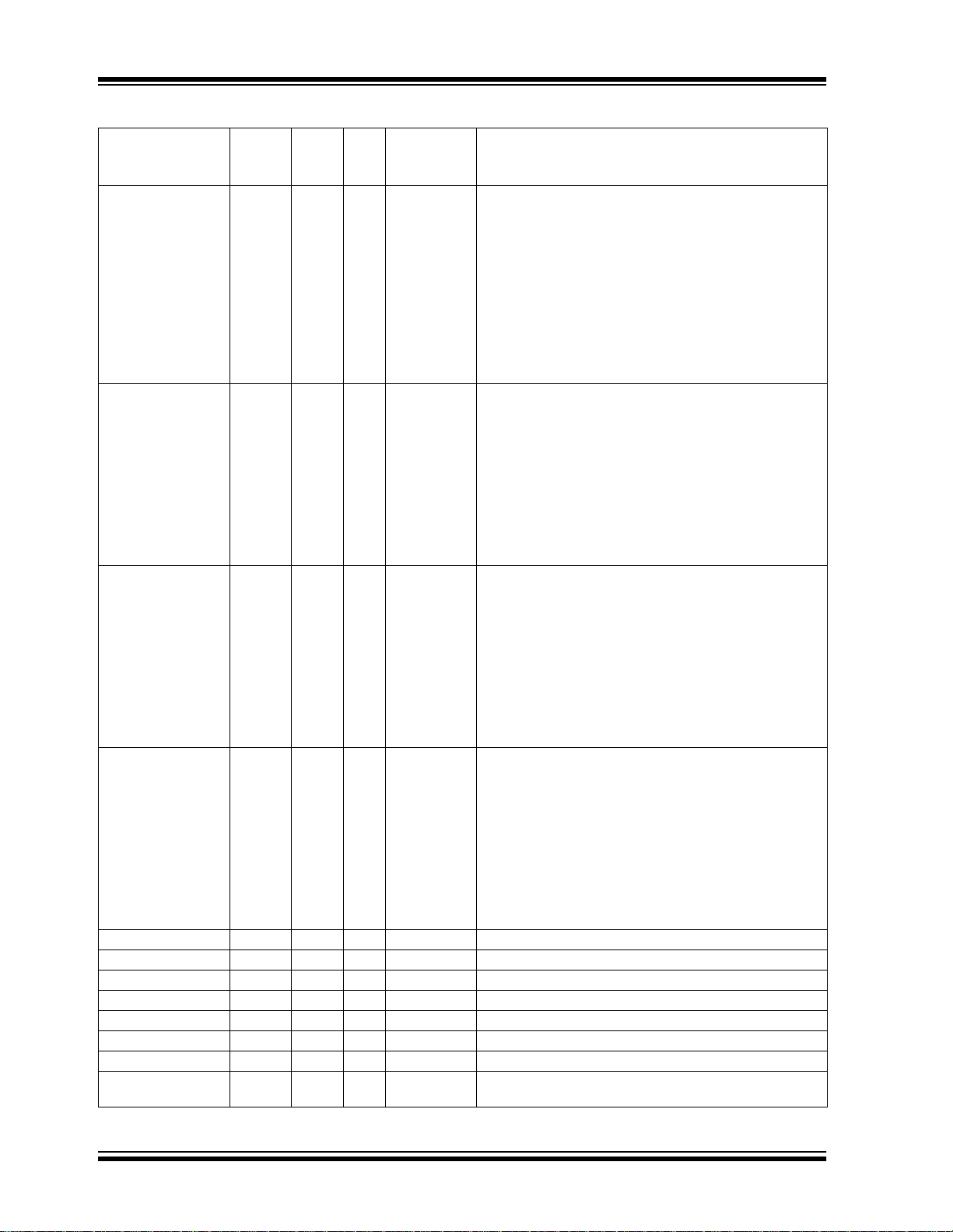

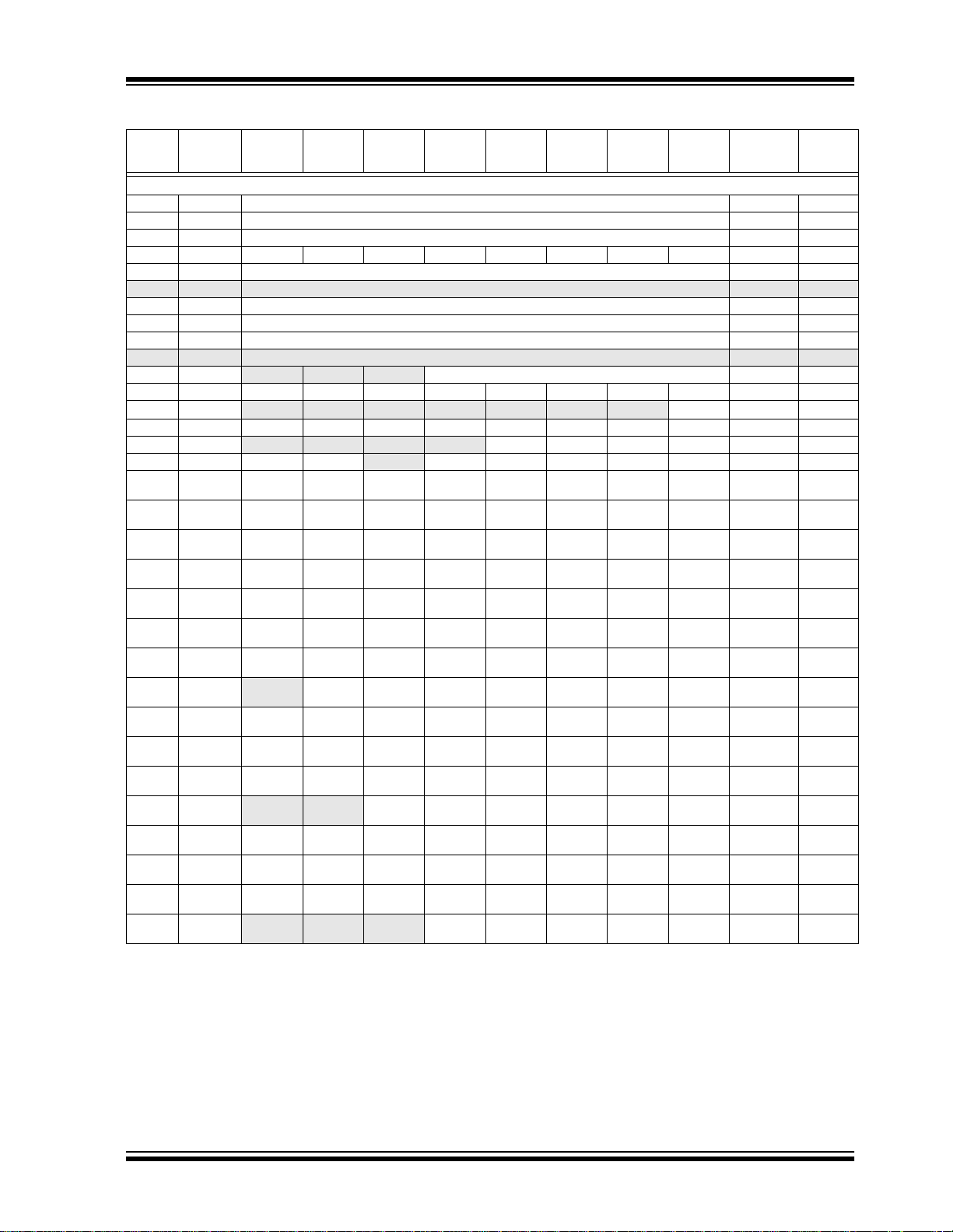

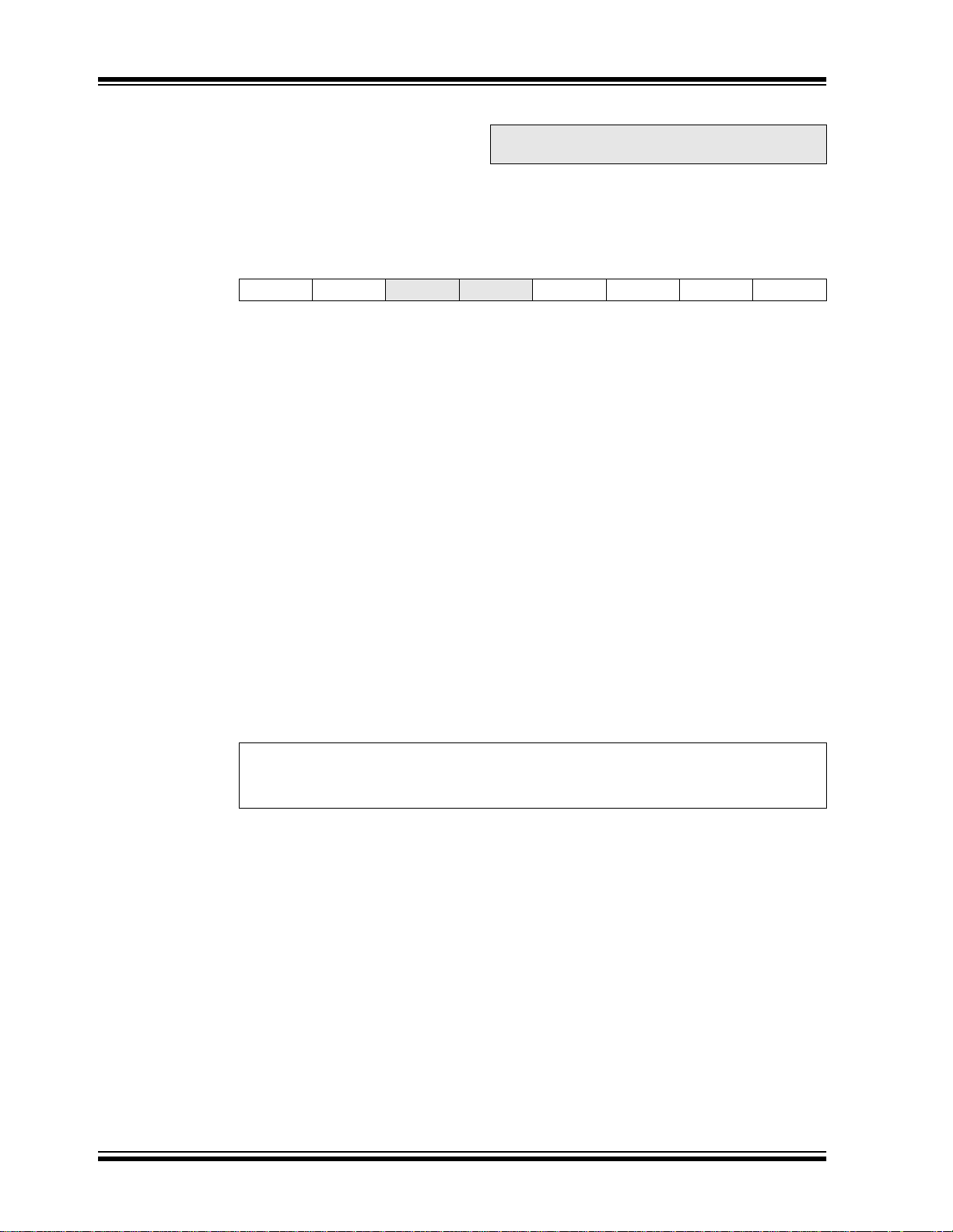

TABLE 1-1: PIC16C925/926 DEVICE FEATURES

Features PIC16C925 PIC16C926

Operating Frequency DC-20 MHz DC-20 MHz

EPROM Program Memory (words) 4K 8K

Data Memory (bytes) 176 336

Timer Module(s) TMR0,TMR1,TMR2 TMR0,TMR1,TMR2

Capture/Compa re/PW M Mo dul e(s ) 1 1

Serial Port(s)

2

C, USART)

(SPI/I

Parallel Slave Port ——

A/D Converter (10-bit) Channels 5 5

LCD Module 4 Com, 32 Seg 4 Com, 32 Seg

Interrupt Sources 9 9

I/O Pins 25 25

Input Pins 27 27

Voltage Range (V) 2.5-5.5 2.5-5.5

In-Circuit Serial Programming Yes Yes

Brown-out Reset Yes Yes

Packages

68-pin CLCC (CERQUAD)

These devices c ome in 64-pin and 68-pin p ackages, as

well as die form. Both configurations offer identical

peripheral devices and other features. The only difference between the PIC16C925 and PIC16C926 is the

additional EPROM and data memory offered in the latter. An overview of features is presented in Table 1-1.

A UV-erasab le, CERQUAD package d version (compa tible with PLCC) is also available for both the

PIC16C925 and PIC16C926. This version is ideal for

cost effective code development.

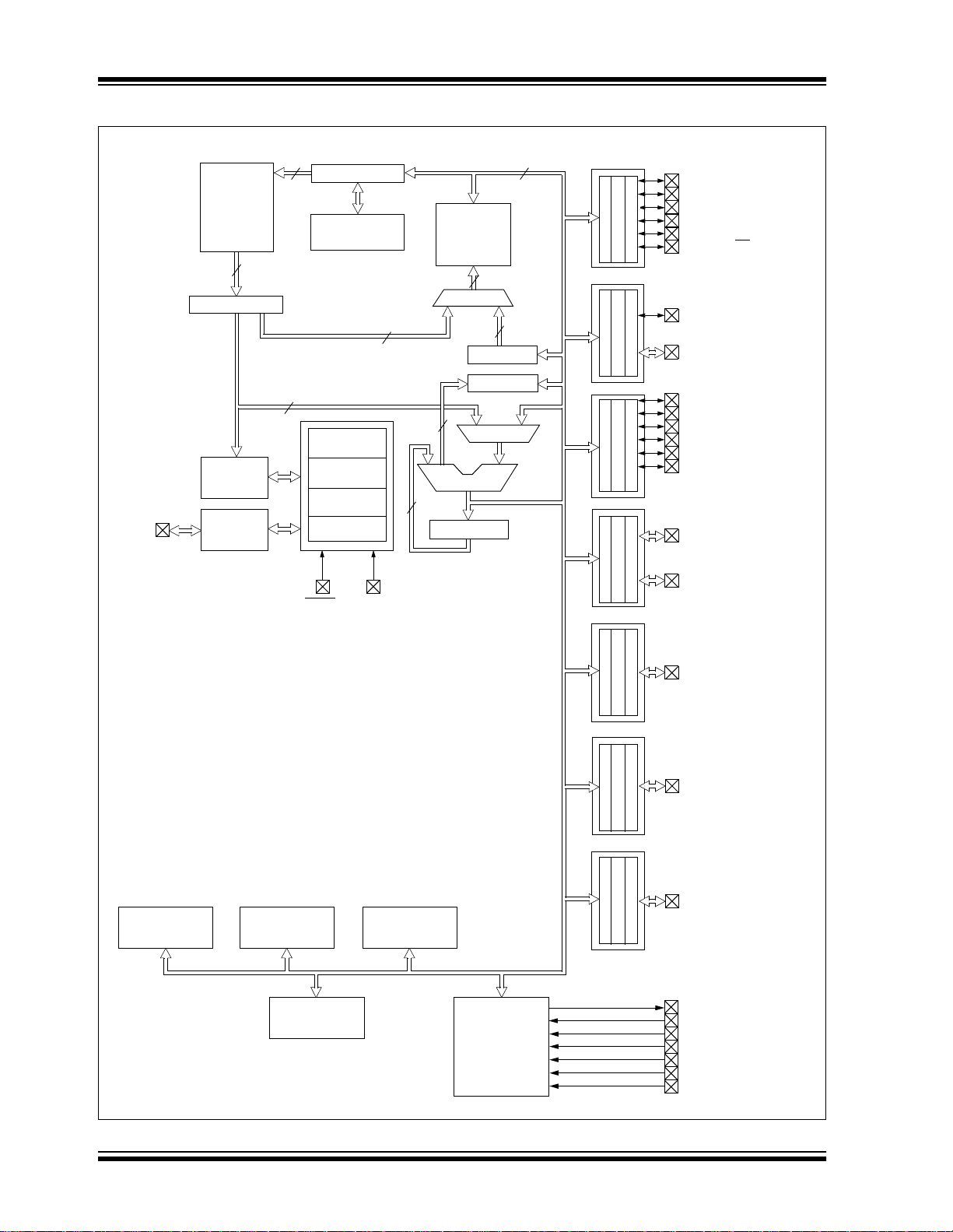

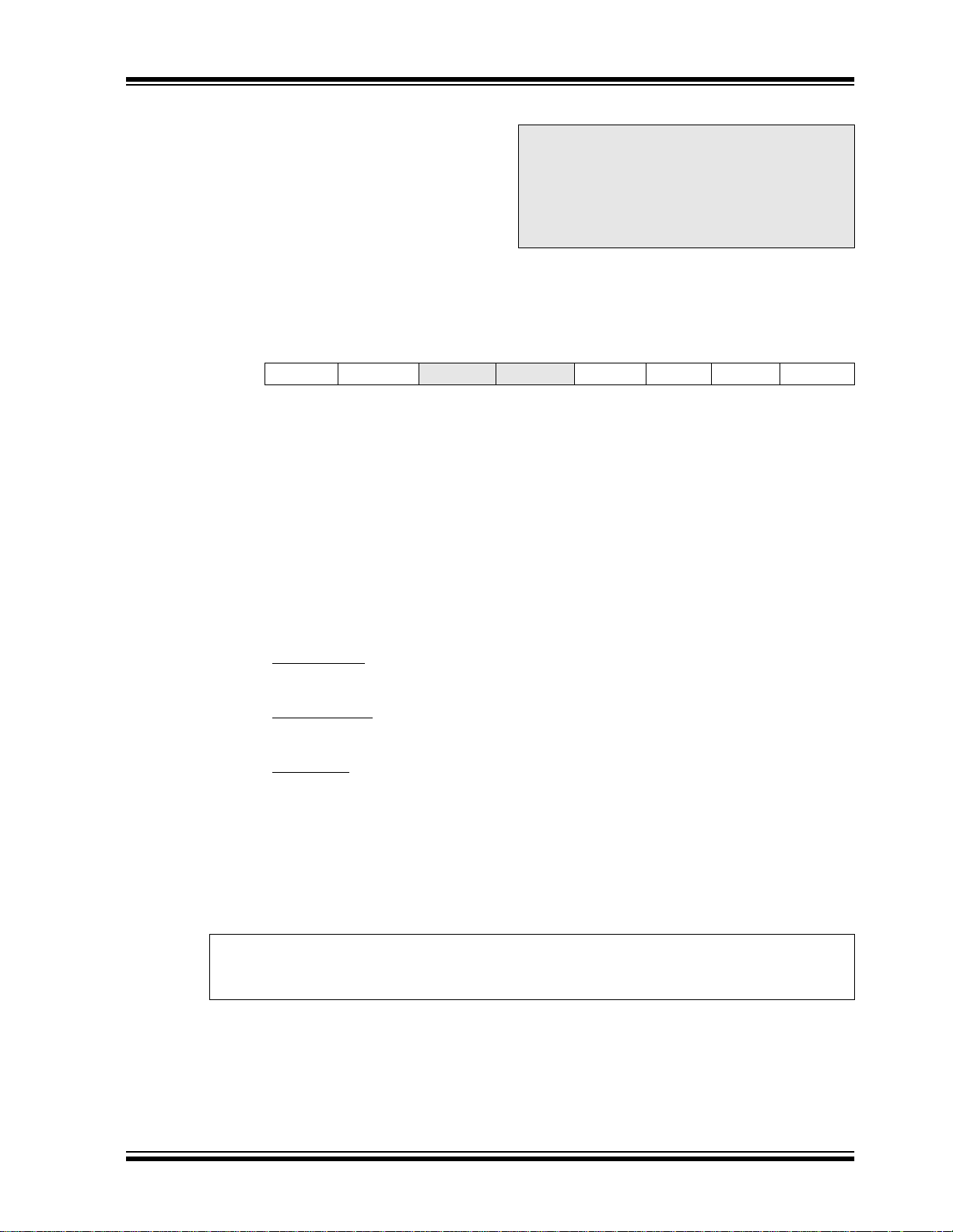

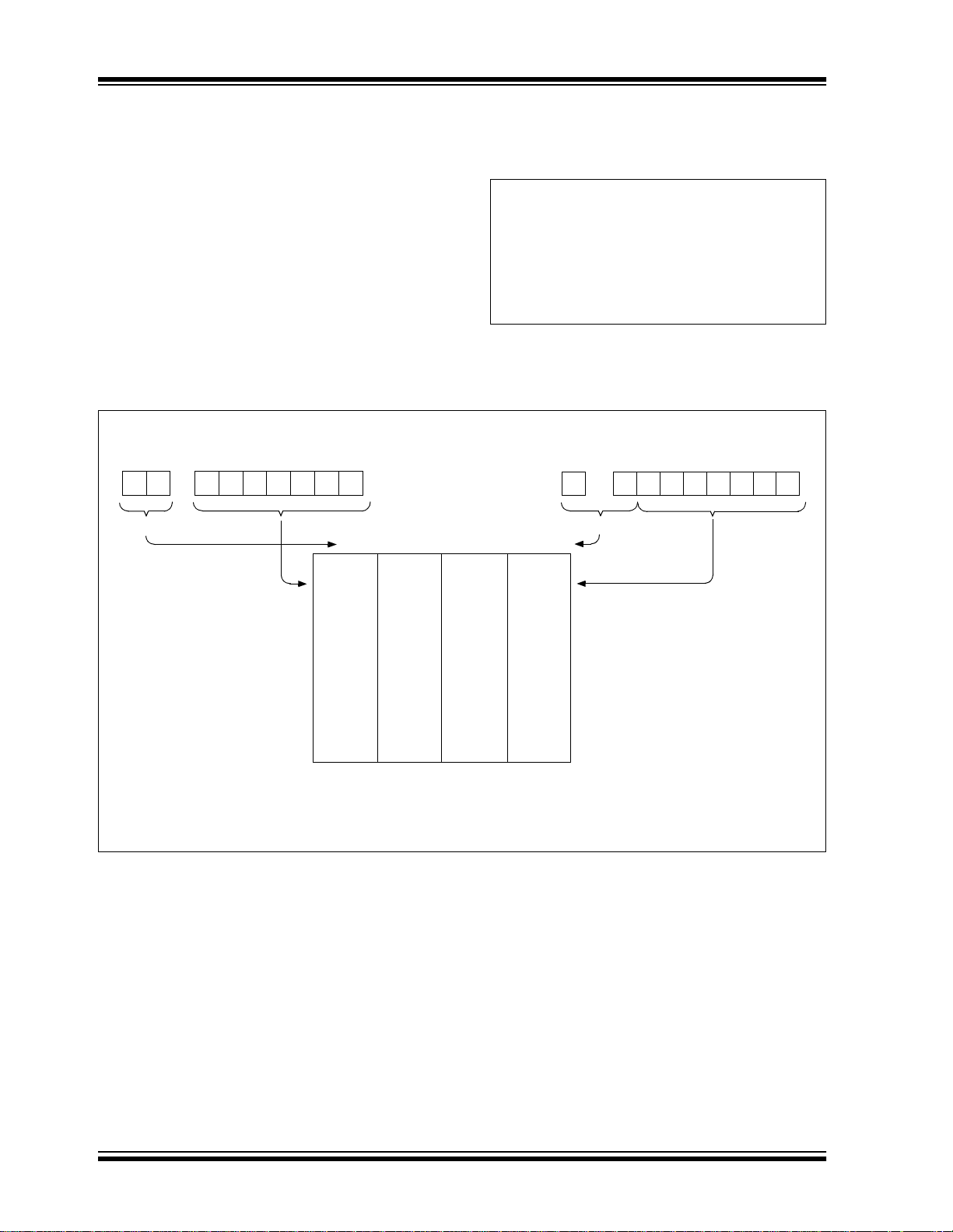

A block diagram for the PIC16C925/926 family architecture is presented in Figure 1-1.

2

C SPI/I2C

SPI/I

64-pin TQFP

68-pin PLCC

Die

64-pin TQFP

68-pin PLCC

68-pin CLCC (CERQUAD)

Die

2001 Microchip Technology Inc. Preliminary DS39544A-page 5

PIC16C925/926

FIGURE 1-1: PIC16C925/926 BLOCK DIAGRAM

Program

Bus

OSC1/CLKIN

OSC2/CLKOUT

EPROM

Program

Memory

14

Instruction reg

Instruction

Decode &

Control

Timing

Generation

13

Program Counter

8 Level Stack

Direct Addr

8

Power-up

Oscillator

Start-up Timer

Power-on

Watchdog

MCLR

(13-bit)

Timer

Reset

Timer

V

DD, VSS

RAM Addr

7

8

Data Bus

RAM

File

Registers

Addr MUX

FSR reg

STATUS reg

3

ALU

W reg

9

MUX

Indirect

8

8

Addr

PORTA

PORTB

PORTC

PORTD

PORTE

RA0/AN0

RA1/AN1

RA2/AN2

RA3/AN3/VREF

RA4/T0CKI

RA5/AN4/SS

RB0/INT

RB1-RB7

RC0/T1OSO/T1CKI

RC1/T1OSI

RC2/CCP1

RC3/SCK/SCL

RC4/SDI/SDA

RC5/SDO

RD0-RD4/SEGnn

RD5-RD7/SEGnn/COMn

Timer0

A/D

Synchronous

Serial Port

Timer1, Timer2,

CCP1

LCD

PORTF

PORTG

RE0-RE7/SEGnn

RF0-RF7/SEGnn

RG0-RG7/SEGnn

COM0

VLCD1

VLCD2

VLCD3

C1

C2

VLCDADJ

DS39544A-page 6 Preliminary 2001 Microchip Technology Inc.

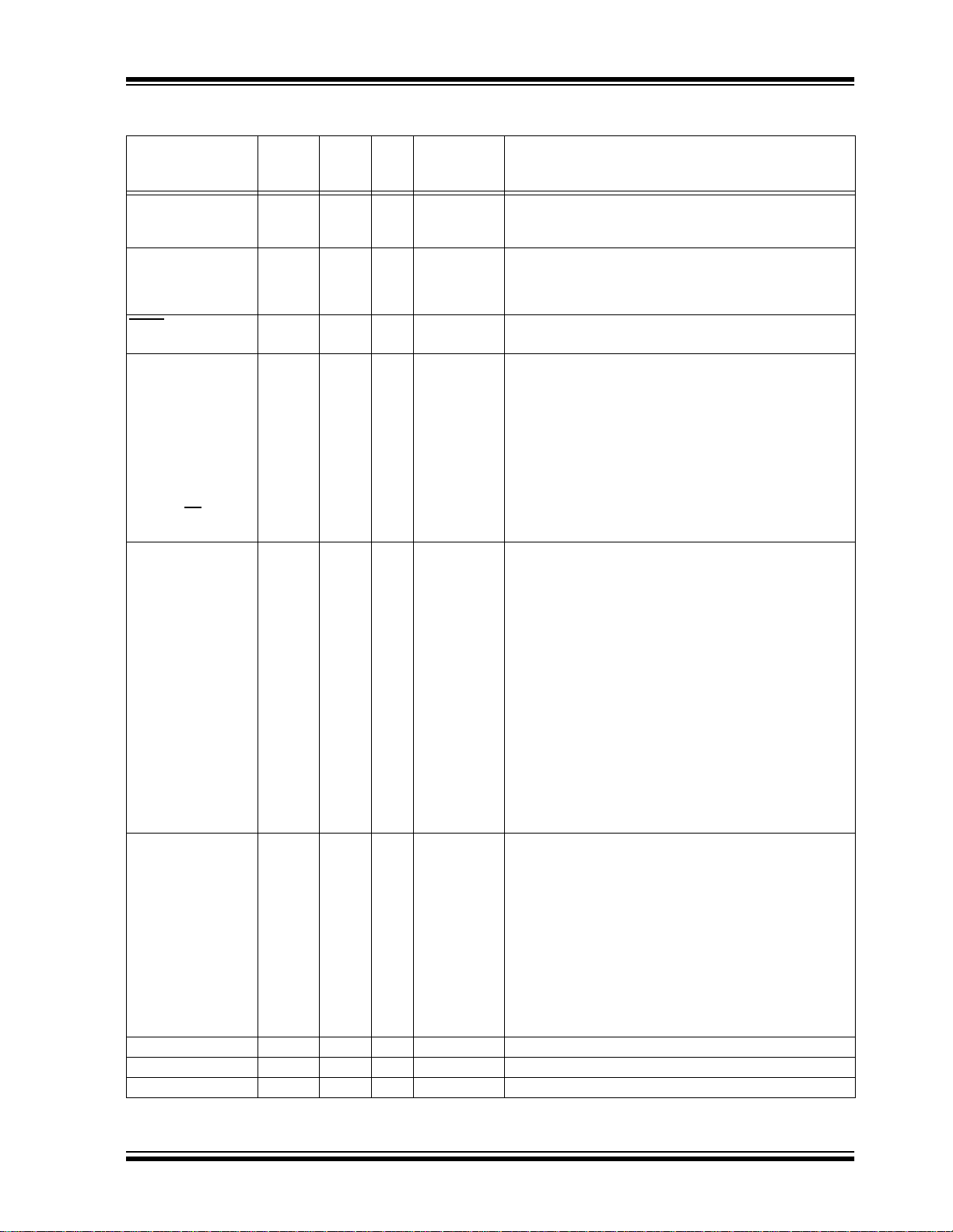

TABLE 1-2: PIC16C925/926 PINOUT DESCRIPTION

PIC16C925/926

PLCC,

Pin Name

OSC1/CLKIN 24 14 I ST/CMOS Oscillator crystal input or external clock source input. This

OSC2/CLKOUT 25 15 O — Oscillator crystal output. Connects to crystal or resonator in

/VPP 2 57 I/P ST Master Clear (Reset) input or programming voltage input. This

MCLR

RA0/AN0 5 60 I/O TTL RA0 can also be Analog input0.

RA1/AN1 6 61 I/O TTL RA1 can also be Analog input1.

RA2/AN2 8 63 I/O TTL RA2 can also be Analog input2.

RA3/AN3/V

RA4/T0CKI 10 1 I/O ST RA4 can also be the clock input to the Timer0

RA5/AN4/SS

RB0/INT 13 4 I/O TTL/ST RB0 can also be the external interrupt pin. This buffer is a

RB1 12 3 I/O TTL

RB2 4 59 I/O TTL

RB3 3 58 I/O TTL

RB4 68 56 I/O TTL Interrupt-on-change pin.

RB5 67 55 I/O TTL Interrupt-on-change pin.

RB6 65 53 I/O TTL/ST Interrupt-on-change pin. Serial programming clock. This

RB7 66 54 I/O TTL/ST Interrupt-on-change pin. Serial programming data. This

RC0/T1OSO/T1CKI 26 16 I/O ST RC0 can also be the Timer1 oscillator output or Timer1

RC1/T1OSI 27 17 I/O ST RC1 can also be the Timer1 oscillator input.

RC2/CCP1 28 18 I/O ST RC2 can also be the Capture1 input/Compare1

RC3/SCK/SCL 14 5 I/O ST RC3 can also be the synchronous serial clock input/

RC4/SDI/SDA 15 6 I/O ST RC4 can also be the SPI Data In (SPI mode) or

RC5/SDO 16 7 I/O ST RC5 can also be the SPI Data Out (SPI mode).

C1 17 8 P LCD Voltage Generation.

C2 18 9 P LCD Voltage Generation.

COM0 63 51 L Comm on Driver0.

Legend: I = input O = output P = power L = LCD Driver

REF 9 64 I/O TTL RA3 can also be Analog input3 or A/D Voltage

— = Not used TTL = TTL input ST = Schmitt Trigger input

CLCC

Pin#

11 2 I/O TTL RA5 can be the slave select for the synchronous serial port

TQFP

Pin#

Pin

Type

Buffer

Type

Description

buffer is a Schmitt Trigger input when configured in RC

oscillator mode and a CMOS input otherwise.

crystal oscillator mode. In RC mode, OSC2 pin outputs

CLKOUT, which has 1/4 the frequency of OSC1 and denotes

the instruction cycle rate.

pin is an active low RESET to the device.

PORTA is a bi-directional I/O port.

Reference.

timer/counter. Output is open drain type.

or Analog input4.

PORTB is a bi-directional I/O port. PORTB can be software

programmed for internal weak pull-ups on all inputs.

Schmitt Trigger input when configured as an

external interrupt.

buffer is a Schmitt Trigger input when used in Serial

Programming mode.

buffer is a Schmitt Trigger input when used in Serial

Programming mode.

PORTC is a bi-directional I/O port.

clock input.

output/PWM1 output.

2

output for both SPI and I

2

data I/O (I

C mode).

C modes.

2001 Microchip Technology Inc. Preliminary DS39544A-page 7

PIC16C925/926

TABLE 1-2: PIC16C925/926 PINOUT DESCRIPTION (CONTINUED)

Pin Name

RD0/SEG00 31 21 I/O/L ST Segment Driver 00/Digital input/output.

RD1/SEG01 32 22 I/O/L ST Segment Driver 01/Digital input/output.

RD2/SEG02 33 23 I/O/L ST Segment Driver 02/Digital input/output.

RD3/SEG03 34 24 I/O/L ST Segment Driver 03/Digital input/output.

RD4/SEG04 35 25 I/O/L ST Segment Driver04/Digital input/output.

RD5/SEG29/COM3 60 48 I/L ST Segment Driver29/Common Driver 3/Digital input.

RD6/SEG30/COM2 61 49 I/L ST Segment Driver30/Common Driver 2/Digital input.

RD7/SEG31/COM1 62 50 I/L ST Segment Driver31/Common Driver 1/Digital input.

RE0/SEG05 37 26 I/L ST Segment Driver 05.

RE1/SEG06 38 27 I/L ST Segment Driver 06.

RE2/SEG07 39 28 I/L ST Segment Driver 07.

RE3/SEG08 40 29 I/L ST Segment Driver 08.

RE4/SEG09 41 30 I/L ST Segment Driver 09.

RE5/SEG10 42 31 I/L ST Segment Driver 10.

RE6/SEG11 43 32 I/L ST Segment Driver 11.

RE7/SEG27 36 - I/L ST Segment Driver 27 (not available on 64-pin devices).

RF0/SEG12 44 33 I/L ST Segm ent Driver 12.

RF1/SEG13 45 34 I/L ST Segm ent Driver 13.

RF2/SEG14 46 35 I/L ST Segm ent Driver 14.

RF3/SEG15 47 36 I/L ST Segm ent Driver 15.

RF4/SEG16 48 37 I/L ST Segm ent Driver 16.

RF5/SEG17 49 38 I/L ST Segm ent Driver 17.

RF6/SEG18 50 39 I/L ST Segm ent Driver 18.

RF7/SEG19 51 40 I/L ST Segm ent Driver 19.

RG0/SEG20 53 41 I/L ST Segment Driver 20.

RG1/SEG21 54 42 I/L ST Segment Driver 21.

RG2/SEG22 55 43 I/L ST Segment Driver 22.

RG3/SEG23 56 44 I/L ST Segment Driver 23.

RG4/SEG24 57 45 I/L ST Segment Driver 24.

RG5/SEG25 58 46 I/L ST Segment Driver 25.

RG6/SEG26 59 47 I/L ST Segment Driver 26.

RG7/SEG28 52 — I/L ST Segment Driver 28 (not available on 64-pin devices).

VLCDADJ 30 20 P — LCD Voltage Generation.

VDD 21 — P — Analog Power (PLCC and CLCC packages only).

A

LCD12919P— LCD Voltage.

V

LCD21910P— LCD Voltage.

V

V

LCD32011P— LCD Voltage.

DD 22, 64 12, 52 P — Digital power.

V

SS 7, 23 13, 62 P — Ground reference.

V

NC 1 —— — These pins are not internally connected. These pins should be

Legend: I = input O = output P = power L = LCD Driver

— = Not used TTL = TTL input ST = Schmitt Trigger input

PLCC,

CLCC

Pin#

TQFP

Pin#

Pin

Type

Buffer

Type

Description

PORTD is a digital input/output port. These pins are also used

as LCD Segment and/or Common Drivers.

PORTE is a Digital input or LCD Segment Driver port.

PORTF is a Digital input or LCD Segment Driver port.

PORTG is a Digital input or LCD Segment Driver port.

left unconnected.

DS39544A-page 8 Preliminary 2001 Microchip Technology Inc.

PIC16C925/926

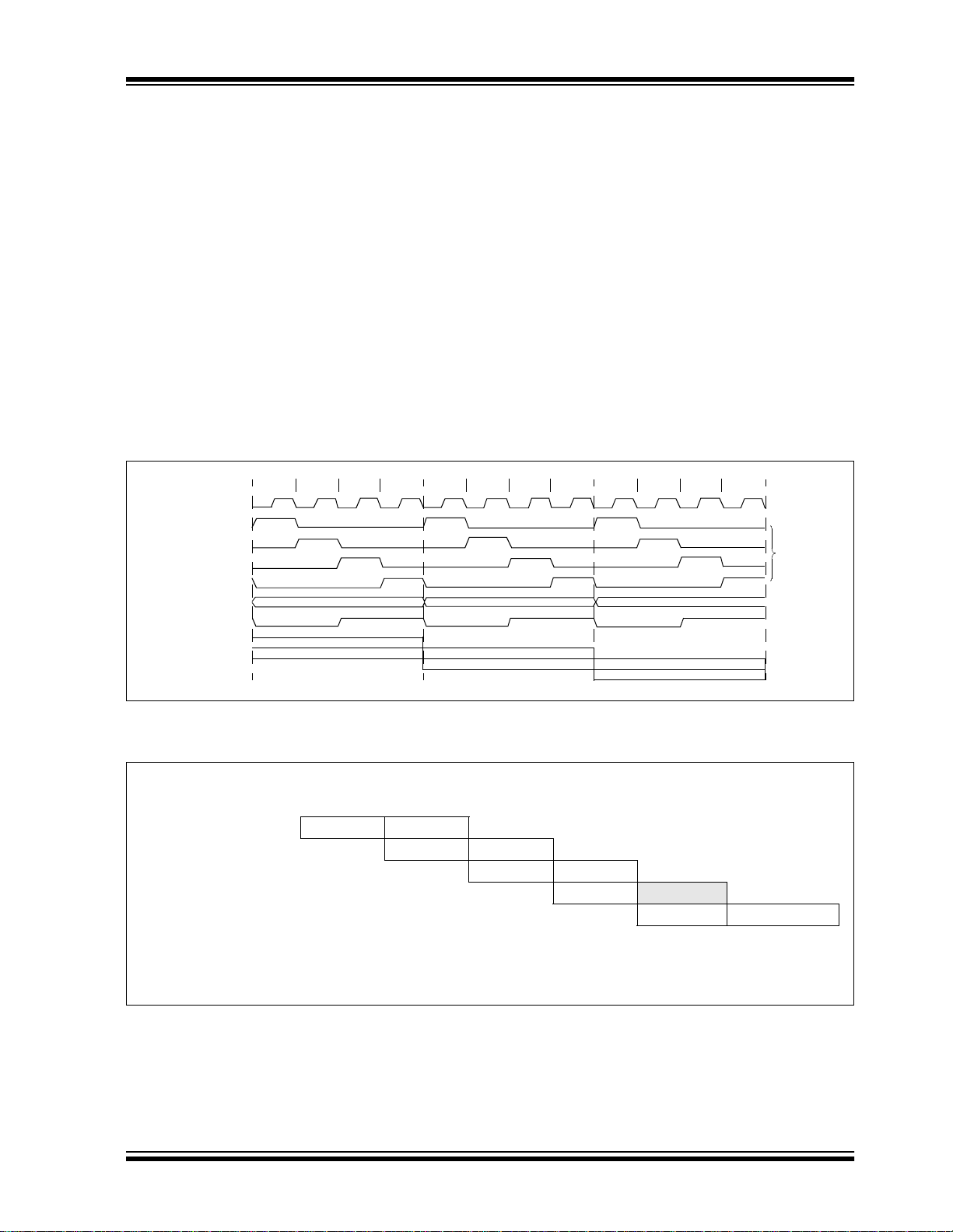

1.1 Clocking Scheme/Instruction

Cycle

The clock input (from OSC1) is internally divided by

four to generate four non-overlapping quadrature

clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the

instruction is fetched from the program memory and

latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1

through Q4. The clocks and instruction execution flow

are shown in Figure1-2.

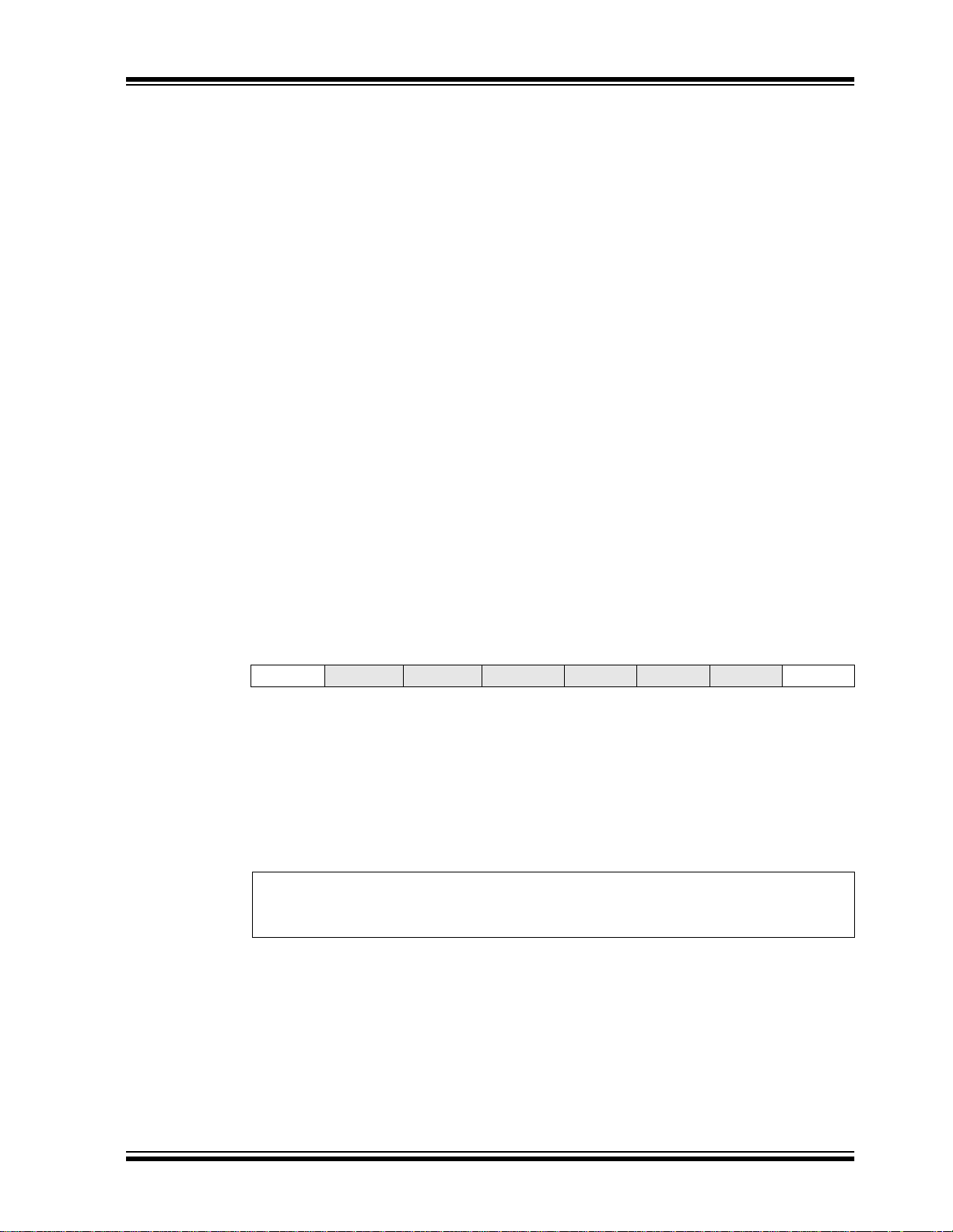

FIGURE 1-2: CLOCK/INSTRUCTION CYCLE

Q2 Q3 Q4

OSC1

Q1

Q2

Q3

Q4

PC

OSC2/CLKOUT

(RC mode)

Q1

PC PC+1 PC+2

Fetch INST (PC)

Execute INST (PC-1) Fetch INST (PC+1)

Q1

Execute INST (PC) Fetch INST (PC+2)

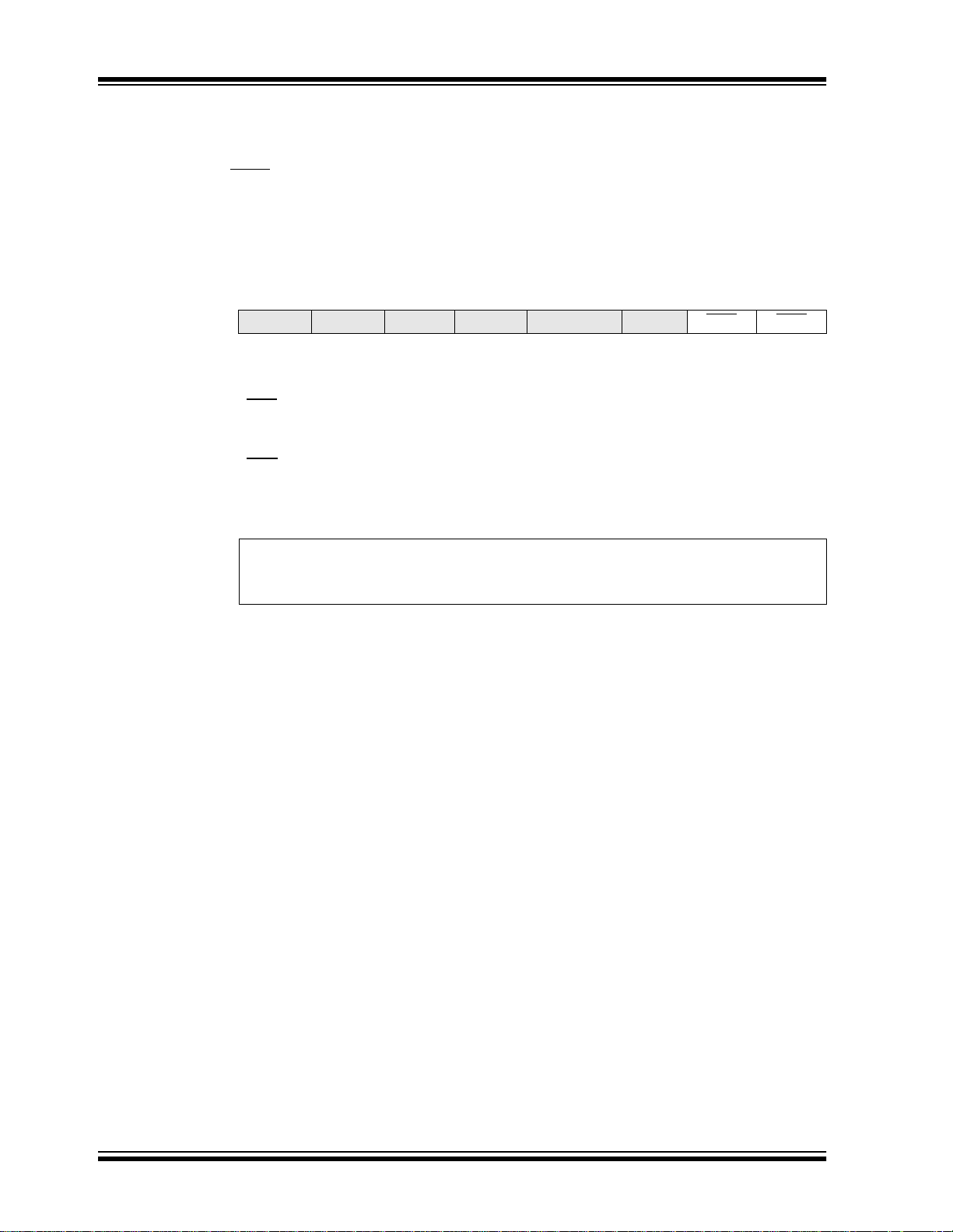

1.2 Instruction Flow/Pipelining

An “Instruction Cycle” consists of four Q cycles (Q1,

Q2, Q3 and Q4). The instruc tio n fetch and execute are

pipelined, such that fetch takes one instruction cycle,

while decode and execute takes another instruction

cycle. However, due to the pipelining, each instruction

effectively executes in one cycle. If an instruction

causes the program counter to change (e.g. GOTO),

then two cycles are req uired to c omplete the ins truction

(Example 1-1).

A fetch cycle begins with the program counter (PC)

incrementing in Q1.

In the execution cy cle, the fetch ed instruction i s latched

into the “Instruction Register” in cycle Q1. This instruction is then decoded and executed during the Q2, Q3,

and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

Q2 Q3 Q4

Q2 Q3 Q4

Q1

Execute INST (PC+1)

Internal

Phase

Clock

EXAMPLE 1-1: INSTRUCTION PIPELINE FLOW

TCY0TCY1TCY2TCY3TCY4TCY5

1. MOVLW 55h

2. MOVWF PORTB

3. CALL SUB_1

4. BSF PORTA, BIT3 (Forced NOP)

5. Instruction @ address SUB_1

All instructions are s ingle cycle, exce pt for any program br anches. These t ake two cycl es, since the fetch in struction

is “flushed” from the pipeline while the new instruction is being fetched and then executed.

2001 Microchip Technology Inc. Preliminary DS39544A-page 9

Fetch 1 Execute 1

Fetch 2 Execute 2

Fetch 3 Execute 3

Fetch 4 Flush

Fetch SUB_1 Execute SUB_1

PIC16C925/926

NOTES:

DS39544A-page 10 Preliminary 2001 Microchip Technology Inc.

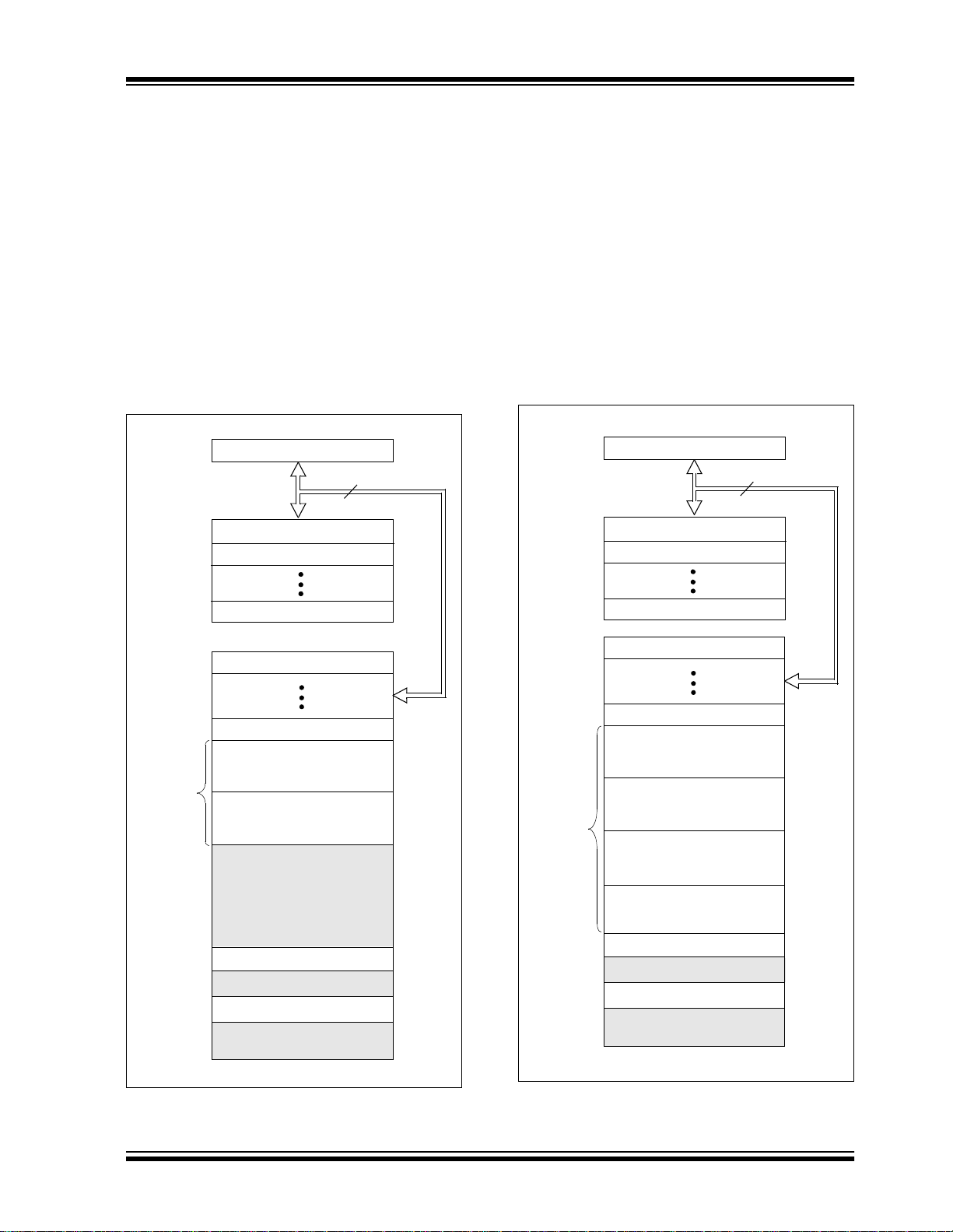

2.0 MEMORY ORGANIZATION

2.1 Program Memory Organization

The PIC16C925/926 family has a 13-bit program

counter capable of addressing an 8K x 14 program

memory space.

For the PIC16C925, only the first 4K x 14 (0000h0FFFh) are physically implemented. Accessing a location above the physically implemented addresses will

cause a wraparound. The RESET vector is at 0000h

and the interrupt vector is at 0004h.

PIC16C925/926

FIGURE 2-1: PROGRAM MEMORY MAP

AND STACK FOR

PIC16C925

PC<12:0>

CALL, RETURN

RETFIE, RETLW

On-chip

Program

Memory

Stack Level 1

Stack Level 2

Stack Level 8

RESET Vector

Interrupt Vector

Page 0

Page 1

Reads

0000h-0FFFh

ID Locations

Reserved

Configuration Word

Reserved

13

0000h

0004h

0005h

07FFh

0800h

0FFFh

1000h

1FFFh

2000h

2003h

2004h

2007h

3FFFh

FIGURE 2-2: PROGRAM MEMORY MAP

AND STACK FOR

PIC16C926

PC<12:0>

CALL, RETURN

RETFIE, RETLW

On-chip

Program

Memory

Stack Level 1

St ac k Lev el 2

Stac k Lev el 8

RESET Vector

Interru pt Vector

Page 0

Page 1

Page 2

Page 3

ID Locations

Reserved

Configuration Wo rd

Reserved

13

0000h

0004h

0005h

07FFh

0800h

0FFFh

1000h

17FFh

1800h

1FFFh

2000h

2003h

2004h

2007h

3FFFh

2001 Microchip Technology Inc. Preliminary DS39544A-page 11

PIC16C925/926

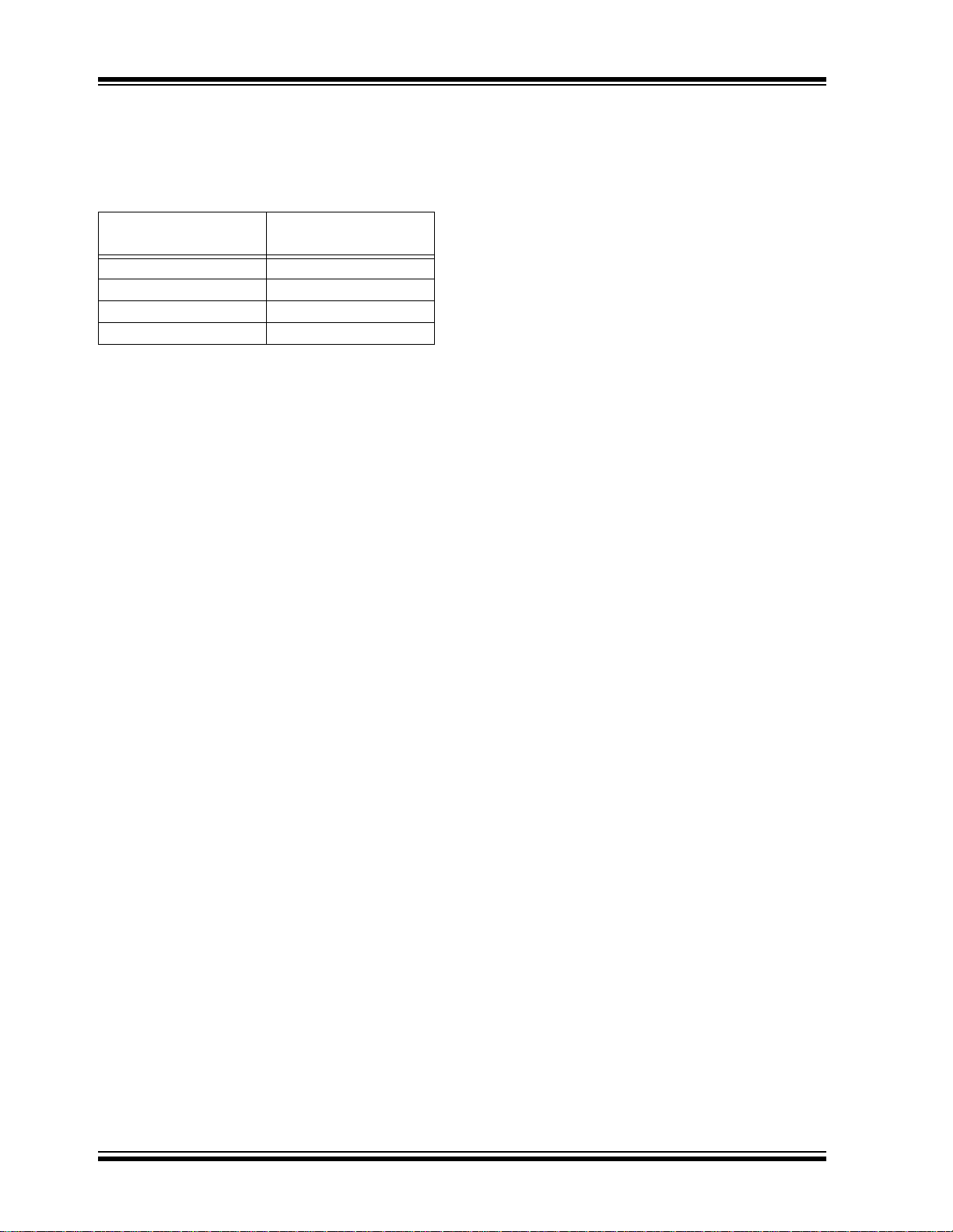

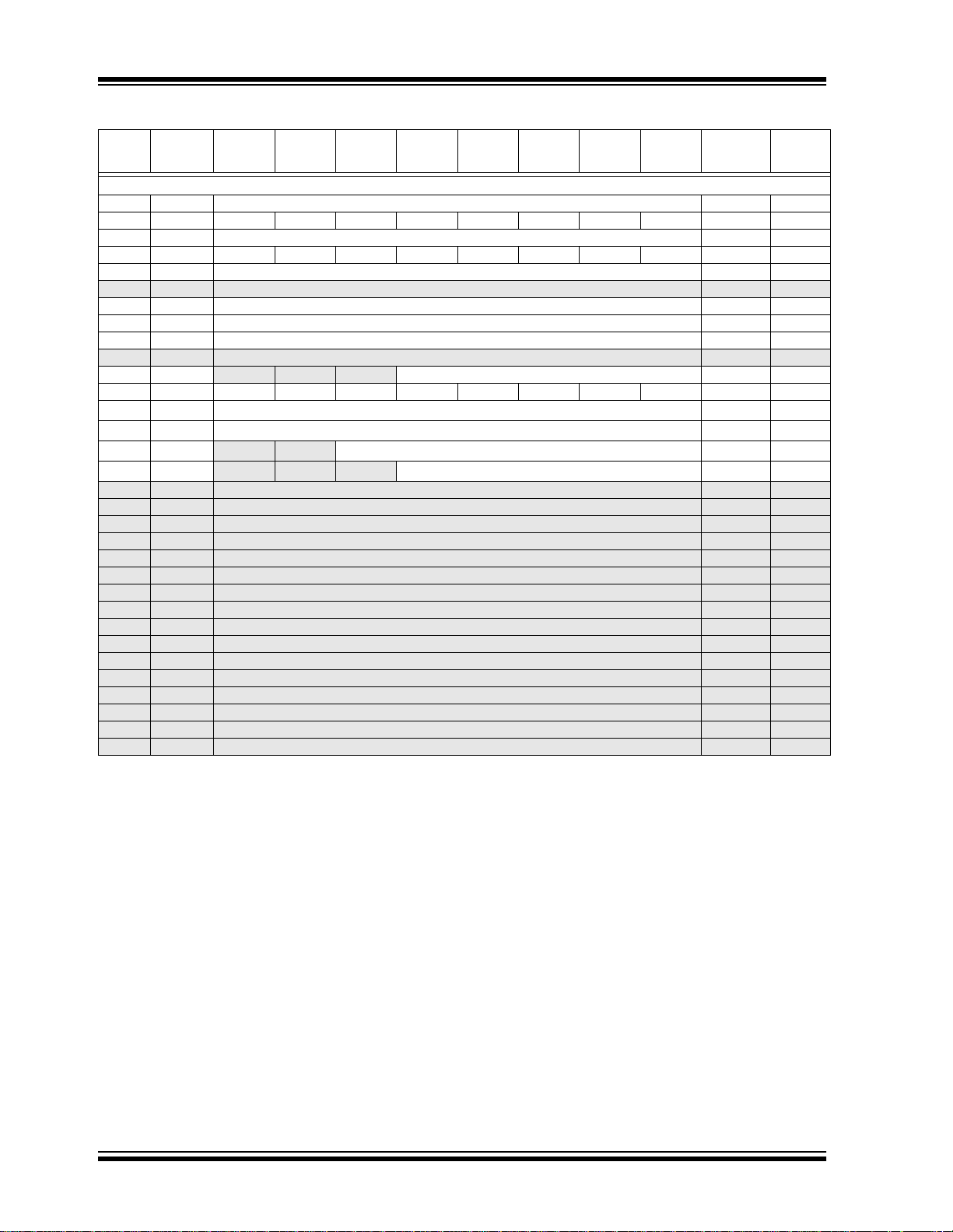

2.2 Data Memory Organization

The data memory is partitioned into four banks which

contain the General Purpose Reg isters a nd the Special

Function Registers. Bits RP1 and RP0 are the bank

select bits.

RP1:RP0

(STATUS<6:5>)

11

10

01

00

The lower locations of each Bank are reserved for the

Special Function Registers. Above the Special Function Registers are General Purpose Registers implemented as static RAM. All four banks contain special

function registers. Some “high use” special function

registers are mirrored in other banks for code reduc tion

and quicker access.

Bank

3 (180h-1FFh)

2 (100h-17Fh)

1 (80h-FFh)

0 (00h-7Fh )

2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be acces sed either directly, or indirectly through the File Select Register FSR

(Section 2.6).

The following General Purp ose Register s are not physically implemented:

• F0h-FFh of Bank 1

• 170h-17Fh of Bank 2

• 1F0h-1FFh of Bank 3

These locations are used for common access across

banks.

DS39544A-page 12 Preliminary 2001 Microchip Technology Inc.

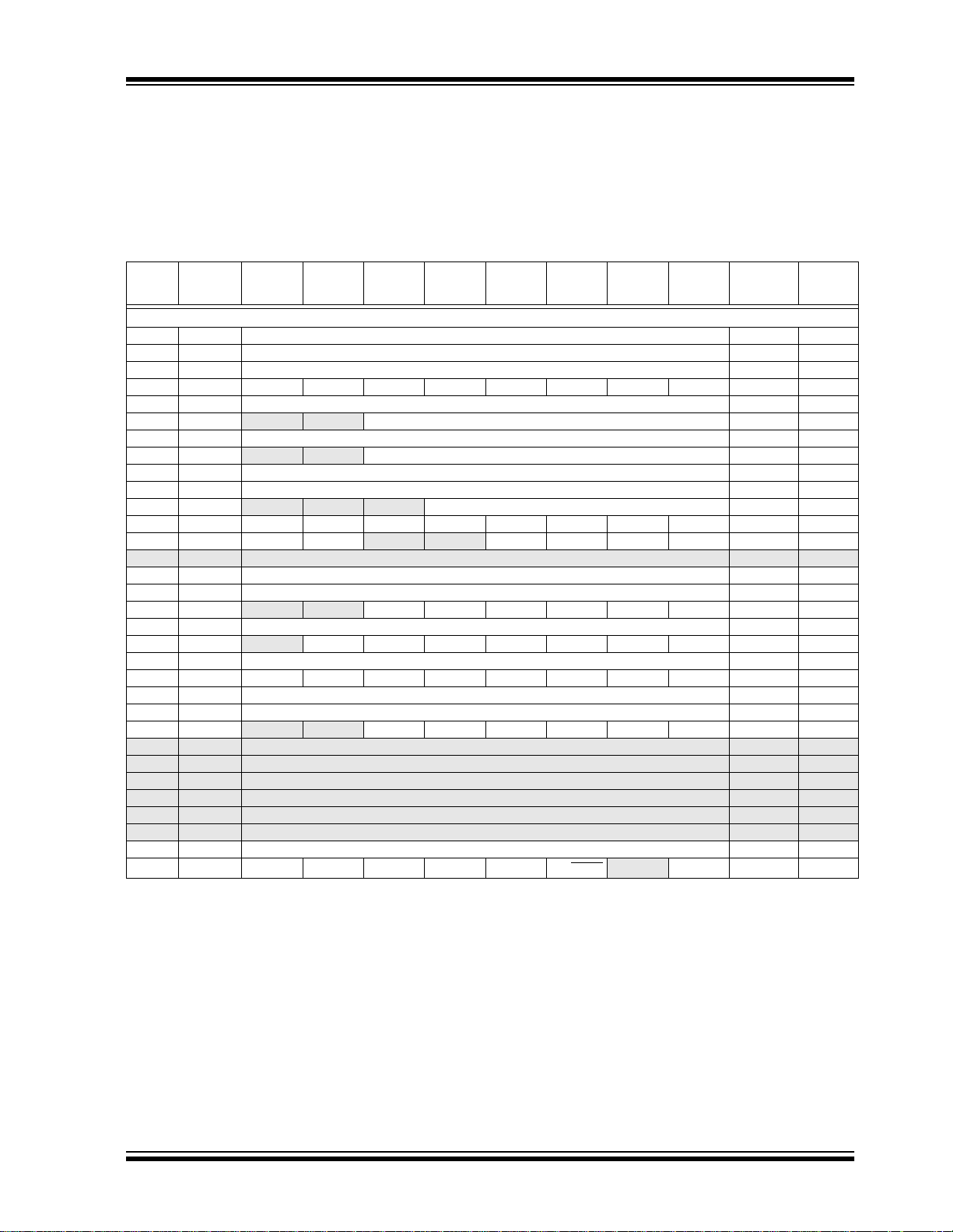

FIGURE 2-3: REGISTER FILE MAP — PIC16C925

PIC16C925/926

Indirect addr.(*)

TMR0

PCL

STATUS

FSR

PORTA

PORTB

PORTC

PORTD

PORTE

PCLATH

INTCON

PIR1

TMR1L

TMR1H

T1CON

TMR2

T2CON

SSPBUF

SSPCON

CCPR1L

CCPR1H

CCP1CON

ADRESH

ADCON0

File

Address

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Bh

0Ch

0Dh

0Eh

0Fh

10h

11h

12h

13h

14h

15h

16h

17h

18h

19h

1Ah

1Bh

1Ch

1Dh

1Eh

1Fh

20h

Indirect addr.(*)

OPTION

PCL

STATUS

FSR

TRISA

TRISB

TRISC

TRISD

TRISE

PCLATH

INTCON

PIE1

PCON

PR2

SSPADD

SSPSTAT

ADRESL

ADCON1

File

Address

80h

81h

82h

83h

84h

85h

86h

87h

88h

89h

8Ah

8Bh

8Ch

8Dh

8Eh

8Fh

90h

91h

92h

93h

94h

95h

96h

97h

98h

99h

9Ah

9Bh

9Ch

9Dh

9Eh

9Fh

A0h

Indirect addr.(*)

TMR0

PCL

STATUS

FSR

PORTB

PORTF

PORTG

PCLATH

INTCON

PMCON1

LCDSE

LCDPS

LCDCON

LCDD00

LCDD01

LCDD02

LCDD03

LCDD04

LCDD05

LCDD06

LCDD07

LCDD08

LCDD09

LCDD10

LCDD11

LCDD12

LCDD13

LCDD14

LCDD15

File

Address

100h

101h

102h

103h

104h

105h

106h

107h

108h

109h

10Ah

10Bh

10Ch

10Dh

10Eh

10Fh

110h

111h

112h

113h

114h

115h

116h

117h

118h

119h

11Ah

11Bh

11Ch

11Dh

11Eh

11Fh

120h

Indirect addr.(*)

OPTION

PCL

STATUS

FSR

TRISB

TRISF

TRISG

PCLATH

INTCON

PMDATA

PMADR

PMDATH

PMADRH

File

Address

180h

181h

182h

183h

184h

185h

186h

187h

188h

189h

18Ah

18Bh

18Ch

18Dh

18Eh

18Fh

190h

191h

192h

193h

194h

195h

196h

197h

198h

199h

19Ah

19Bh

19Ch

19Dh

19Eh

19Fh

1A0h

General

Purpose

General

Purpose

Register

7Fh

Bank 0

Un implemented data memory locations, read as ’0’.

* Not a physical register.

2001 Microchip Technology Inc. Preliminary DS39544A-page 13

Register

accesses

70h - 7Fh

Bank 1

EFh

F0h

FFh

accesses

70h - 7Fh

Bank 2

16Fh

170h

17Fh

accesses

70h - 7Fh

Bank 3

1EFh

1F0h

1FFh

PIC16C925/926

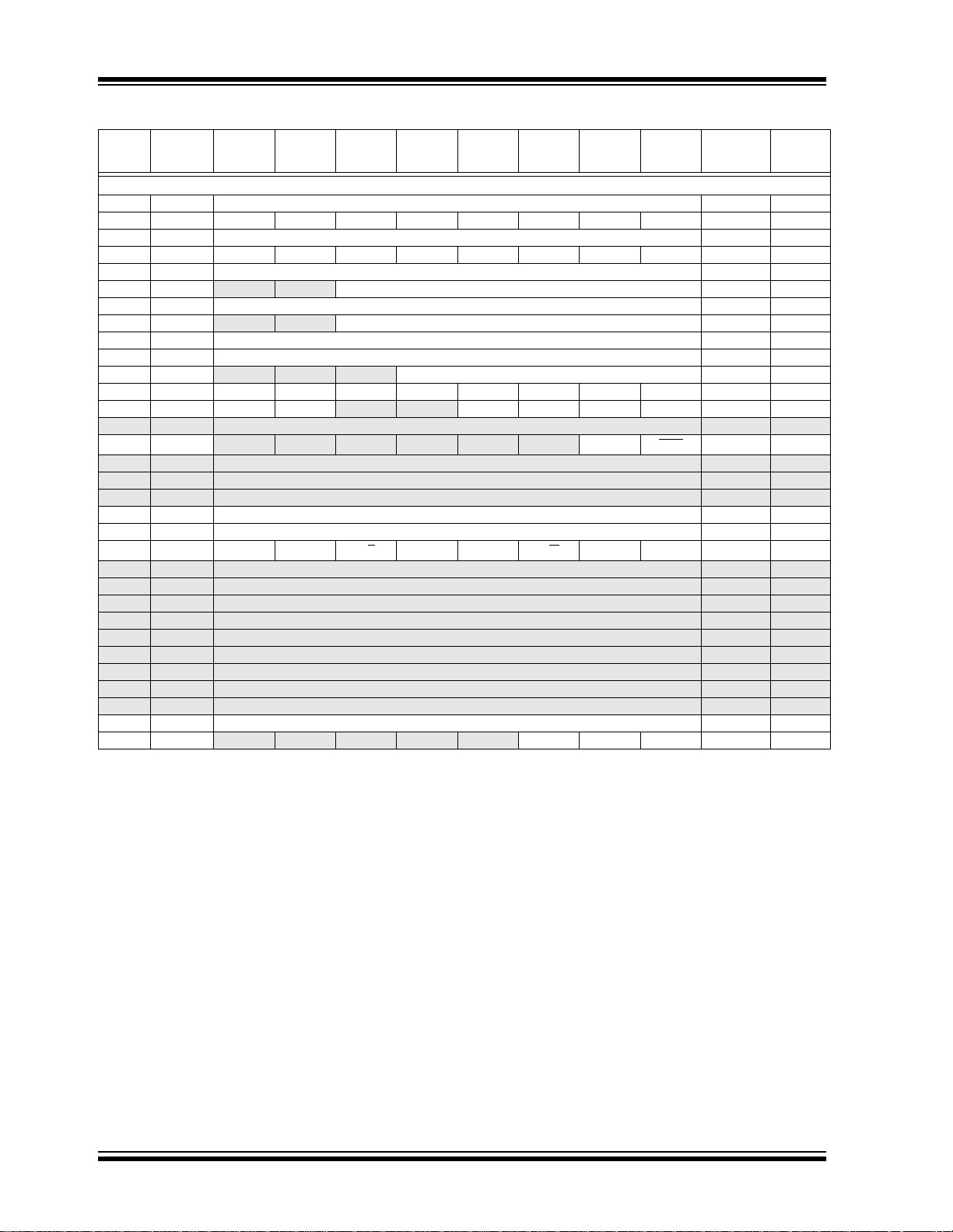

FIGURE 2-4: REGISTER FILE MAP— PIC16C926

Indirect addr.(*)

TMR0

PCL

STATUS

FSR

PORTA

PORTB

PORTC

PORTD

PORTE

PCLATH

INTCON

PIR1

TMR1L

TMR1H

T1CON

TMR2

T2CON

SSPBUF

SSPCON

CCPR1L

CCPR1H

CCP1CON

ADRESH

ADCON0

General

Purpose

Register

96 Bytes

Bank 0

File

Address

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Bh

0Ch

0Dh

0Eh

0Fh

10h

11h

12h

13h

14h

15h

16h

17h

18h

19h

1Ah

1Bh

1Ch

1Dh

1Eh

1Fh

20h

7Fh

Indirect addr.(*)

OPTION

PCL

STATUS

FSR

TRISA

TRISB

TRISC

TRISD

TRISE

PCLATH

INTCON

PIE1

PCON

PR2

SSPADD

SSPSTAT

ADRESL

ADCON1

General

Purpose

Register

80 Bytes

accesses

70h - 7Fh

Bank 1

File

Address

80h

81h

82h

83h

84h

85h

86h

87h

88h

89h

8Ah

8Bh

8Ch

8Dh

8Eh

8Fh

90h

91h

92h

93h

94h

95h

96h

97h

98h

99h

9Ah

9Bh

9Ch

9Dh

9Eh

9Fh

A0h

BFh

C0h

EFh

F0h

FFh

Indirect addr.(*)

TMR0

PCL

STATUS

FSR

PORTB

PORTF

PORTG

PCLATH

INTCON

PMCON1

LCDSE

LCDPS

LCDCON

LCDD00

LCDD01

LCDD02

LCDD03

LCDD04

LCDD05

LCDD06

LCDD07

LCDD08

LCDD09

LCDD10

LCDD11

LCDD12

LCDD13

LCDD14

LCDD15

General

Purpose

Register

80 Bytes

accesses

70h - 7Fh

Bank 2

File

Address

100h

101h

102h

103h

104h

105h

106h

107h

108h

109h

10Ah

10Bh

10Ch

10Dh

10Eh

10Fh

110h

111h

112h

113h

114h

115h

116h

117h

118h

119h

11Ah

11Bh

11Ch

11Dh

11Eh

11Fh

120h

16Fh

170h

17Fh

Indirect addr.(*)

OPTION

PCL

STATUS

FSR

TRISB

TRISF

TRISG

PCLATH

INTCON

PMDATA

PMADR

PMDATH

PMADRH

General

Purpose

Register

80 Bytes

accesses

70h - 7Fh

Bank 3

File

Address

180h

181h

182h

183h

184h

185h

186h

187h

188h

189h

18Ah

18Bh

18Ch

18Dh

18Eh

18Fh

190h

191h

192h

193h

194h

195h

196h

197h

198h

199h

19Ah

19Bh

19Ch

19Dh

19Eh

19Fh

1A0h

1EFh

1F0h

1FFh

Unimplemented data memory locations, read as ’0’.

* Not a physical register.

DS39544A-page 14 Preliminary 2001 Microchip Technology Inc.

PIC16C925/926

2.3 Special Function Registers

The Special Function Registers (SFRs) are registers

used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM.

The special function regi sters can be classified into tw o

sets, core and peripheral. Those registers associated

with the “core” functions are described in this section.

Those related to the operation of the peripheral

features are described in the section of that peripheral

feature.

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bank 0

00h INDF Addressing this location uses contents of FSR to address data memory (not a physical register)

01h TMR0 Timer0 Module Register

02h PCL Program Counter (PC) Least Significant Byte

03h STATUS IRP RP1 RP0 TO PD Z DC C

04h FSR Indirect Data Memory Address Pointer

05h PORTA

06h PORTB PORTB Data Latch when writt en: PORTB pins when read

07h PORTC

08h PORTD PORTD Data Latch when written: PORTD pins when read

09h PORTE PORTE pins when read

0Ah PCLATH

0Bh INTCON GIE PEIE TMR0IE INTE RBIE TMR0IF INTF RBIF

0Ch PIR1 LCDIF ADIF

0Dh — Unimplemented — —

0Eh TMR1L Holding register for the Least Significant Byte of the 16-bit TMR1 Register

0Fh TMR1H Holding register for the Most Significant Byte of the 16-bit TMR1 Register

10h T1CON

11h TMR2 Timer2 Module Register

12h T2CON

13h SSPBUF Synchronous Ser i al Po rt Receive Buffer/Transmit Register

14h SSPCON WCOL SSPOV SSPEN CKP SSPM3 SSPM2 SSPM1 SSPM0

15h CCPR1L Capture/Compare/PWM Register (LSB)

16h CCPR1H Capture/Compare/PWM Register (MSB)

17h CCP1CON

18h — Unimplemented — —

19h — Unimplemented — —

1Ah — Unimplemented — —

1Bh — Unimplemented — —

1Ch — Unimplemented — —

1Dh — Unimplemented — —

1Eh ADRESH A/D Result Register High

1Fh ADCON0 ADCS1 ADCS0 CHS2 CHS1 CHS0 GO/DONE

Legend:

Note 1: These pixels do not display, but can be used as general purpose RAM.

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0'.

Shaded locations are unimplemented, read as ‘0’.

— — PORTA Data Latch when written: PORTA pins when read --0x 0000 29

— — PORTC Data Latch when written: PORTC pins when read --xx xxxx 33

— — — Write Buffer for the upper 5 bits of the Program Counter ---0 0000 25

— — SSPIF CCP1IF TMR2IF TMR1IF 00-- 0000 23

— — T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON --00 0000 47

— TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 -000 0000 52

— — CCP1X CCP1Y CCP1M3 CCP1M2 CCP1M1 CCP1M0 --00 0000 53

— ADON 0000 0000 75

Value on

Power-on

Reset

0000 0000 26

xxxx xxxx 41

0000 0000 25

0001 1xxx 19

xxxx xxxx 26

xxxx xxxx 31

0000 0000 34

0000 0000 36

0000 000x 21

xxxx xxxx 47

xxxx xxxx 47

0000 0000 51

xxxx xxxx 64, 72

0000 0000 60

xxxx xxxx 58

xxxx xxxx 58

xxxx xxxx 80, 81

Details on

page

2001 Microchip Technology Inc. Preliminary DS39544A-page 15

PIC16C925/926

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bank 1

80h INDF Addressing this location uses contents of FSR to address data memory (not a physical register)

81h OPTION RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0

82h PCL Program Counter (PC) Least Significant Byte

83h STATUS IRP RP1 RP0 TO PD Z DC C

84h FSR Indirect Data Memory Address Pointer

85h TRISA

86h TRISB PORTB Data Direction Register

87h TRISC

88h TRISD PORTD Data Direction Register

89h TRISE PORTE Data Direction Register

8Ah PCLATH

8Bh INTCON GIE PEIE TMR0IE INTE RBIE TMR0IF INTF RBIF

8Ch PIE1 LCDIE ADI E

8Dh — Unimplemented — —

8Eh PCON

8Fh — Unimplemented — —

90h — Unimplemented — —

91h — Unimplemented — —

92h PR2 Timer2 Period Register

93h SSPADD Synchronous Serial Port (I

94h SSPSTAT SMP CKE D/A

95h — Unimplemented — —

96h — Unimplemented — —

97h — Unimplemented — —

98h — Unimplemented — —

99h — Unimplemented — —

9Ah — Unimplemented — —

9Bh — Unimplemented — —

9Ch — Unimplemented — —

9Dh — Unimplemented — —

9Eh ADRESL A/D Result Register Low

9Fh ADCON1

Legend:

Note 1: These pixels do not display, but can be used as general purpose RAM.

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0'.

Shaded locations are unimplemented, read as ‘0’.

— — PORTA Data Direction Register --11 1111 29

— — PORTC Data Direction Register --11 1111 33

— — — Write Buffer for the upper 5 bits of the PC ---0 0000 25

— — SSPIE CCP1IE TMR2IE TMR1IE 00-- 0000 24

— — — — — — POR BOR ---- --0- 24

2

C mode) Address Register 0000 0000 69, 72

PSR/WUA BF 0000 0000 59

— — — — — PCFG2 PCFG1 PCFG0 ---- -000 76

Value on

Power-on

Reset

0000 0000 26

1111 1111 20

0000 0000 25

0001 1xxx 19

xxxx xxxx 26

1111 1111 31

1111 1111 34

1111 1111 36

0000 000x 21

1111 1111 51

xxxx xxxx 79

Details on

page

DS39544A-page 16 Preliminary 2001 Microchip Technology Inc.

PIC16C925/926

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bank 2

100h INDF Addressing this location uses contents of FSR to address data memory (not a physical register)

101h TMR0 Timer0 Module Register

102h PCL Program Counter (PC) Least Significant Byte

103h STATUS IRP RP1 RP0 TO PD Z DC C

104h FSR Indirect Data Memory Address Pointer

105h — Unimplemented — —

106h PORTB PORTB Data Latch when writt en: PORTB pins when read

107h PORTF PORTF pins when read

108h PORTG PORTG pins when read

109h — Unimplemented — —

10Ah PCLATH

10Bh INTCON GIE PEIE TMR0IE INTE RBIE TMR0IF INTF RBIF

10Ch PMCON1

10Dh LCDSE SE29 SE27 SE20 SE16 SE12 SE9 SE5 SE0

10Eh LCDPS

10Fh LCDCON LCDEN SLPEN

110h LCDD00 SEG07

111h LCDD01 SEG15

112h LCDD02 SEG23

113h LCDD03 SEG31

114h LCDD04 SEG07

115h LCDD05 SEG15

116h LCDD06 SEG23

117h LCDD07

118h LCDD08 SEG07

119h LCDD09 SEG15

11Ah LCDD10 SEG23

11Bh LCDD11

11Ch LCDD12 SEG07

11Dh LCDD13 SEG15

11Eh LCDD14 SEG23

11Fh LCDD15

Legend:

Note 1: These pixels do not display, but can be used as general purpose RAM.

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0'.

Shaded locations are unimplemented, read as ‘0’.

— — — Write Buffer for the upper 5 bits of the PC ---0 0000 25

reserved — — — — — —

— — — — LP3 LP2 LP1 LP0 ---- 0000 84

— VGEN CS1 CS0 LMUX1 LMUX0 00-0 0000 83

COM0

COM0

COM0

COM0

COM1

COM1

COM1

SEG31

COM1

COM2

COM2

COM2

SEG31

COM2

COM3

COM3

COM3

SEG31

COM3

SEG06

COM0

SEG14

COM0

SEG22

COM0

SEG30

COM0

SEG06

COM1

SEG14

COM1

SEG22

COM1

SEG30

(1)

COM1

SEG06

COM2

SEG14

COM2

SEG22

COM2

SEG30

(1)

COM2

SEG06

COM3

SEG14

COM3

SEG22

COM3

SEG30

(1)

COM3

SEG05

COM0

SEG13

COM0

SEG21

COM0

SEG29

COM0

SEG05

COM1

SEG13

COM1

SEG21

COM1

SEG29

COM1

SEG05

COM2

SEG13

COM2

SEG21

COM2

SEG29

(1)

COM2

SEG05

COM3

SEG13

COM3

SEG21

COM3

SEG29

(1)

COM3

SEG04

COM0

SEG12

COM0

SEG20

COM0

SEG28

COM0

SEG04

COM1

SEG12

COM1

SEG20

COM1

SEG28

COM1

SEG04

COM2

SEG12

COM2

SEG20

COM2

SEG28

COM2

SEG04

COM3

SEG12

COM3

SEG20

COM3

SEG28

(1)

COM3

SEG03

COM0

SEG11

COM0

SEG19

COM0

SEG27

COM0

SEG03

COM1

SEG11

COM1

SEG19

COM1

SEG27

COM1

SEG03

COM2

SEG11

COM2

SEG19

COM2

SEG27

COM2

SEG03

COM3

SEG11

COM3

SEG19

COM3

SEG27

COM3

SEG02

COM0

SEG10

COM0

SEG18

COM0

SEG26

COM0

SEG02

COM1

SEG10

COM1

SEG18

COM1

SEG26

COM1

SEG02

COM2

SEG10

COM2

SEG18

COM2

SEG26

COM2

SEG02

COM3

SEG10

COM3

SEG18

COM3

SEG26

COM3

SEG01

COM0

SEG09

COM0

SEG17

COM0

SEG25

COM0

SEG01

COM1

SEG09

COM1

SEG17

COM1

SEG25

COM1

SEG01

COM2

SEG09

COM2

SEG17

COM2

SEG25

COM2

SEG01

COM3

SEG09

COM3

SEG17

COM3

SEG25

COM3

RD

SEG00

COM0

SEG08

COM0

SEG16

COM0

SEG24

COM0

SEG00

COM1

SEG08

COM1

SEG16

COM1

SEG24

COM1

SEG00

COM2

SEG08

COM2

SEG16

COM2

SEG24

COM2

SEG00

COM3

SEG08

COM3

SEG16

COM3

SEG24

COM3

Value on

Power-on

Reset

0000 0000 26

xxxx xxxx 41

0000 0000 25

0001 1xxx 19

xxxx xxxx 26

xxxx xxxx 31

0000 0000 37

0000 0000 38

0000 000x 21

1--- ---0 27

1111 1111 94

xxxx xxxx 92

xxxx xxxx 92

xxxx xxxx 92

xxxx xxxx 92

xxxx xxxx 92

xxxx xxxx 92

xxxx xxxx 92

xxxx xxxx 92

xxxx xxxx 92

xxxx xxxx 92

xxxx xxxx 92

xxxx xxxx 92

xxxx xxxx 92

xxxx xxxx 92

xxxx xxxx 92

xxxx xxxx 92

Details on

page

2001 Microchip Technology Inc. Preliminary DS39544A-page 17

PIC16C925/926

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bank 3

180h INDF Addressing this location uses contents of FSR to address data memory (not a physical register)

181h OPTION RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0

182h PCL Program Counter’s (PC) Least Significant Byte

183h STATUS IRP RP1 RP0 TO PD Z DC C

184h FSR Indirect Data Memory Address Pointer

185h — Unimplemented — —

186h TRISB PORTB Data Direction Register

187h TRISF PORTF Data Directi on Register

188h TRISG PORTG Data Direction Register

189h — Unimplemented — —

18Ah PCLATH

18Bh INTCON GIE PEIE TMR0IE INTE RBIE TMR0IF INTF RBIF

18Ch PMDATA Data Register Low Byte

18Dh PMADR Address Register Low Byte

18Eh PMDATH

18Fh PMADRH

190h — Unimplemented — —

191h — Unimplemented — —

192h — Unimplemented — —

193h — Unimplemented — —

194h — Unimplemented — —

195h — Unimplemented — —

196h — Unimplemented — —

197h — Unimplemented — —

198h — Unimplemented — —

199h — Unimplemented — —

19Ah — Unimplemented — —

19Bh — Unimplemented — —

19Ch — Unimplemented — —

19Dh — Unimplemented — —

19Eh — Unimplemented — —

19Fh — Unimplemented — —

Legend:

Note 1: These pixels do not display, but can be used as general purpose RAM.

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0'.

Shaded locations are unimplemented, read as ‘0’.

— — — Write Buffer for the upper 5 bits of the PC ---0 0000 25

— — Data Regist er Hi gh Byt e xxxx xxxx 27

— — —

Address Register High Byte

Value on

Power-on

Reset

0000 0000 26

1111 1111 20

0000 0000 25

0001 1xxx 19

xxxx xxxx 26

1111 1111 31

1111 1111 37

1111 1111 38

0000 000x 21

xxxx xxxx 27

xxxx xxxx 27

xxxx xxxx

Details on

page

27

DS39544A-page 18 Preliminary 2001 Microchip Technology Inc.

PIC16C925/926

2.3.1 STATUS REGISTER

The STATUS register, shown in Register2-1, contains

the arithmetic st atus of th e ALU, the RE SET statu s and

the bank select bits for data memory.

The STATUS register can be the destination for any

instruction, as with any other register. If the STATUS

register is the destination for an instruction that affects

the Z, DC or C bits, then the write to these three bits is

disabled. These bit s are set or cleared ac cording to the

device logic. Furthermore, the TO

writable. Therefore, the result of an instruction with the

STATUS register as dest ination may be di fferent than

intended.

and PD bits are not

For example, CLRF STATUS will clear the upper-three

bits and set the Z bit. This leaves the STATUS register

as 000u u1uu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF,

SWAPF and MOVWF instructions are used to alter the

STATUS register because these instructions do not

affect the Z, C or DC bits from the ST ATUS reg ister . For

other instructions, no t affecting any status bi ts, see the

“Instruction Set Summary.”

Note: The C and DC bits operate as a borrow

and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF

instructions for examples.

REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

R/W-0 R/W-0 R/W-0 R-1 R-1 R/W-x R/W-x R/W-x

IRP RP1 RP0 TO

bit 7 bit 0

bit 7 IRP: Register Bank Select bit (used for indirect addressing)

1 = Bank 2, 3 (100h - 1FFh)

0 = Bank 0, 1 (00h - FFh)

bit 6-5 RP1:RP0: Register Bank Select bits (used for direct addressing)

11 = Bank 3 (180h - 1FFh)

10 = Bank 2 (100h - 17Fh)

01 = Bank 1 (80h - FFh)

00 = Bank 0 (00h - 7Fh)

bit 4 TO: Time-out bit

1 = After power-up, CLRWDT instruction, or SLEEP instruction

0 = A WDT time-out occurred

bit 3 PD

bit 2 Z: Zero bit

bit 1 DC: Digit carry/borrow bit (ADDWF, ADDLW,SUBLW,SUBWF instructions)

bit 0 C: Carry/borrow

: Power-down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

(for borrow

1 = A carry-out from the 4th low order bit of the result occurred

0 = No carry-out from the 4th low order bit of the result

(for borrow

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

the polarity is reversed)

bit (ADDWF, ADDLW,SUBLW,SUBWF instructions)

the polarity is reversed)

PD ZDCC

Note: A subtraction is executed by adding the two’s complement of the second operand.

For rotate (RRF, RLF) instructions, thi s bi t is l oad ed w ith ei the r th e h igh or low order

bit of the source register.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

2001 Microchip Technology Inc. Preliminary DS39544A-page 19

PIC16C925/926

2.3.2 OPTION REGISTER

The OPTION register is a readable and writable register, which contains various control bits to configure the

TMR0/WDT prescaler, the external RB0/INT pin interrupt, TMR0, and the weak pull-ups on PORTB.

REGISTER 2-2: OPTION REGISTER (ADDRESS 81h, 181h)

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1

RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0

bit 7 bit 0

Note: To achieve a 1:1 prescaler assignment for

the TMR0 register, assign the prescaler to

the Watchdog Timer.

bit 7 RBPU

bit 6 INTEDG: Interrupt Edge Select bit

bit 5 T0CS: TMR0 Clock Source Select bit

bit 4 T0SE: TMR0 Source Edge Select bit

bit 3 PSA: Prescaler Assignment bit

bit 2-0 PS2:PS0: Prescaler Rate Select bits

: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

1 = Interrupt on rising edge of RB0/INT pin

0 = Interrupt on falling edge of RB0/INT pin

1 = Transition on RA 4/T0CKI pin

0 = Internal instruction cycle clock (CLKOUT)

1 = Increment on high-to-low transition on RA4/T0CKI pin

0 = Increment on low-to-high transition on RA4/T0CKI pin

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

Bit Value TMR0 Rate WDT Rate

000

001

010

011

100

101

110

111

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

1 : 256

1 : 1

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

DS39544A-page 20 Preliminary 2001 Microchip Technology Inc.

PIC16C925/926

2.3.3 INTCON REGISTER

The INTCON Register is a readabl e and writ able register which contains various enable and flag bits for the

TMR0 register overflow, RB Port change and external

RB0/INT pin interrupts.

Note: Interrupt flag bit s are set whe n an in terrupt

condition occurs, regardless of the state of

its corresponding enable bit or the global

enable bit, GIE (INTCON<7>).

REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-x

GIE PEIE TMR0IE INTE RBIE TMR0IF INTF RBIF

bit 7 bit 0

bit 7 GIE: Global Interrupt Enable bit

1 = Enables all unmasked interrupts

0 = Disables all interrupts

bit 6 PEIE/GEIL: Peripheral Interrupt Enable bit

1 = Enables all unmasked peripheral interrupts

0 = Disables all peripheral interrupts

bit 5 TMR0IE: TMR0 Overflow Interrupt Enable bit

1 = Enables the TMR0 overflow interrupt

0 = Disables the TMR0 overflow interrupt

bit 4 INTE: RB0/INT0 External Interrupt Enable bit

1 = Enables the RB0/INT external interrupt

0 = Disables the RB0/INT external interrupt

bit 3 RBIE: RB Port Change Interrupt Enable bit

1 = Enables the RB port change interrupt

0 = Disables the RB port change interrupt

bit 2 TMR0IF: TMR0 Overflow Interrupt Flag bit

1 = TMR0 register has overflowed (must be cleared in software)

0 = TMR0 register did not overflow

bit 1 INTF: RB0/INT0 External Interrupt Flag bit

1 = The RB0/INT external interrupt occurred (must be cleared in software)

0 = The RB0/INT external interrupt did not occur

bit 0 RBIF: RB Port Change Interrupt Flag bit

1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)

0 = None of the RB7:RB4 pins have changed state

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR reset ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

2001 Microchip Technology Inc. Preliminary DS39544A-page 21

PIC16C925/926

2.3.4 PIE1 REGISTER

This register contains the individual enable bits for the

peripheral interrupts.

REGISTER 2-4: PIE1 REGISTER (ADDRESS 8Ch)

R/W-0 R/W-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0

LCDIE ADIE

bit 7 bit 0

bit 7 LCDIE: LCD Interrupt Enable bit

1 = Enables the LCD interrupt

0 = Disables the LCD interrupt

bit 6 ADIE: A/D Converter Interrupt Enable bit

1 = Enables the A/D interrupt

0 = Disables the A/D interrupt

bit 5-4 Unimplemented: Read as ‘0’

bit 3 SSPIE: Synchronous Serial Port Interrupt Enable bit

1 = Enables the SSP interrupt

0 = Disables the SSP interrupt

bit 2 CCP1IE: CCP1 Interrupt Enable bit

1 = Enables the CCP1 interrupt

0 = Disables the CCP1 interrupt

bit 1 TMR2IE: TMR2 to PR2 Match Interrupt Enable bit

1 = Enables the TMR2 to PR2 match interrupt

0 = Disables the TMR2 to PR2 match interrupt

bit 0 TMR1IE: TMR1 Overflow Interrupt Enable bit

1 = Enables the TMR1 overflow interrupt

0 = Disables the TMR1 overflow interrupt

— — SSPIE CCP1IE TMR2IE TMR1IE

Note: Bit PEIE (INTCON<6>) must be set to

enable any peripheral interrupt.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

DS39544A-page 22 Preliminary 2001 Microchip Technology Inc.

2.3.5 PIR1 REGISTER

This register contains the individual flag bits for the

peripheral interrupts.

Note: Interrupt flag bits are se t w he n an interrupt

condition occurs, re gardless of the state of

its corresponding enable bit or the global

enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an

interrupt.

REGISTER 2-5: PIR1 REGISTER (ADDRESS 0Ch)

R/W-0 R/W-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0

LCDIF ADIF

bit 7 bit 0

bit 7 LCDIF: LCD Interrupt Flag bit

1 = LCD interrupt has occurred (must be cleared in software)

0 = LCD interrupt did not occur

bit 6 ADIF: A/D Converter Interrupt Flag bit

1 = An A/D conversion completed (must be cleared in software)

0 = The A/D conversion is not complete

bit 5-4 Unimplemented: Read as ‘0’

bit 3 SSPIF: Master Synchronous Serial Port Interrupt Flag bit

1 = The transmission/reception is complete (must be cleared in software)

0 = Waiting to transmit/receive

bit 2 CCP1IF: CCP1 Interrupt Flag bit

Capture mode:

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 register capture occurred

Compare mode:

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

PWM mode:

Unused in this mode

bit 1 TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

1 = TMR2 to PR2 match occurred (must be cleared in software)

0 = No TMR2 to PR2 match occurred

bit 0 TMR1IF: TMR1 Overflow Interrupt Flag bit

1 = TMR1 register overflowed (must be cleared in software)

0 = TMR1 register did not overflow

— — SSPIF CCP1IF TMR2IF TMR1IF

PIC16C925/926

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR rese t ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

2001 Microchip Technology Inc. Preliminary DS39544A-page 23

PIC16C925/926

2.3.6 PCON REGISTER

The Power Control (PCON) register contains a flag bit

to allow differentiation between a Power-on Reset

(POR) to an external MCLR

For various RESET conditions, see Table 12-4 and

Table 12-5.

REGISTER 2-6: PCON REGISTER (ADDRESS 8Eh)

bit 7-2 Unimplemented: Read as '0'

bit 1 POR

bit 0 BOR

Reset or WDT Reset.

U-0 U-0 U-0 U-0 U-0 U-0 R/W-0 R/W-1

— — — — — — POR BOR

bit 7 bit 0

: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

: Brown-out Reset Status bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

DS39544A-page 24 Preliminary 2001 Microchip Technology Inc.

PIC16C925/926

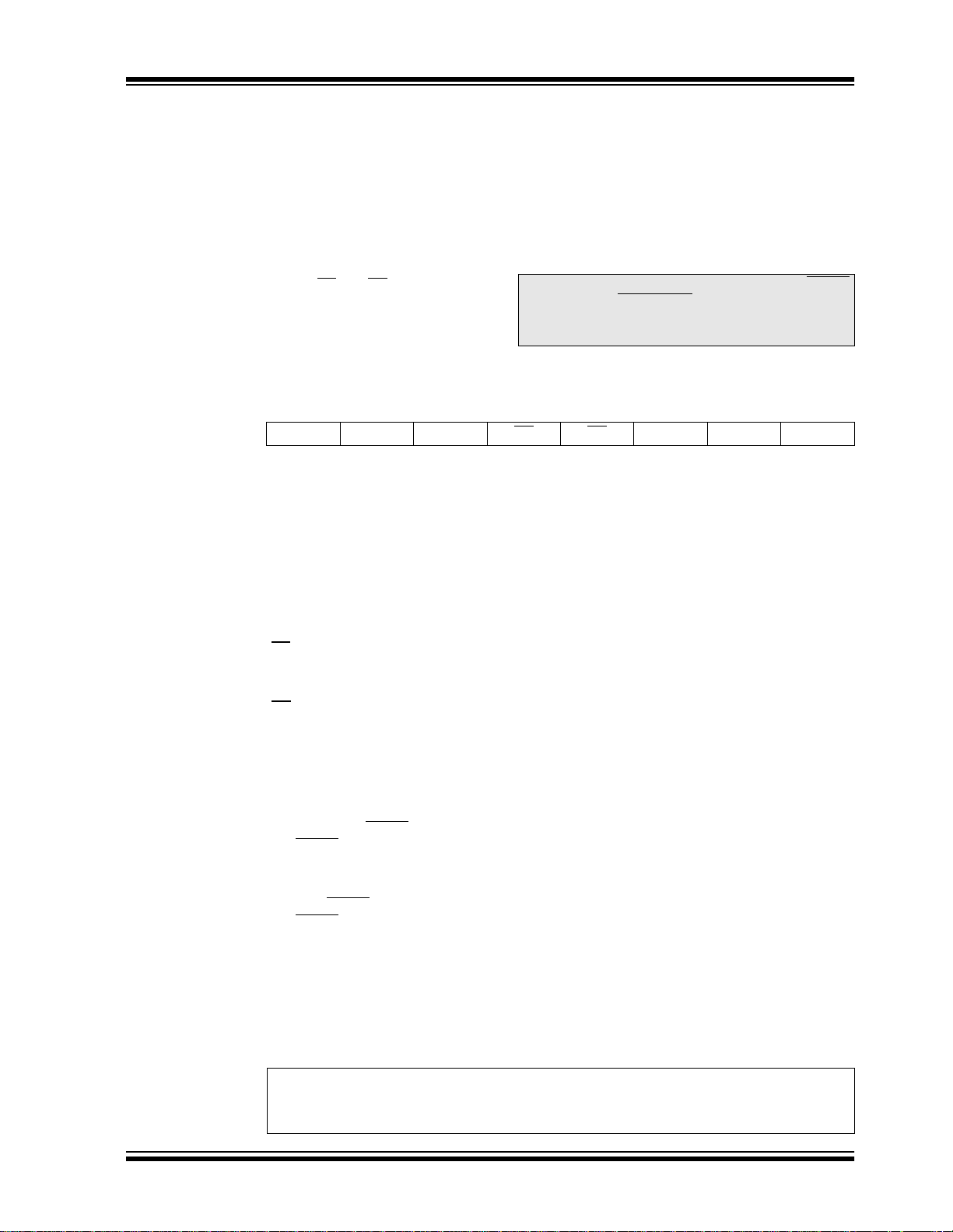

2.4 PCL and PCLATH

The program counter (PC) is 13-bits wid e. The low byte

comes from the PCL register, which is a readable and

writable register. The upper bits (PC<12:8>) are not

readable, but are indirectly writable through the

PCLA TH reg is ter. On any RESET, the up per bi t s of the

PC will be cleared. Fig ure2-5 shows the two situations

for the loading of the PC. The up per ex ample in th e figure shows how the PC is loaded on a write to PCL

(PCLATH<4:0> → PCH). The lower exampl e i n th e fi gure shows how the PC is loaded during a CALL or GOTO

instruction (PCLATH<4:3> → PCH).

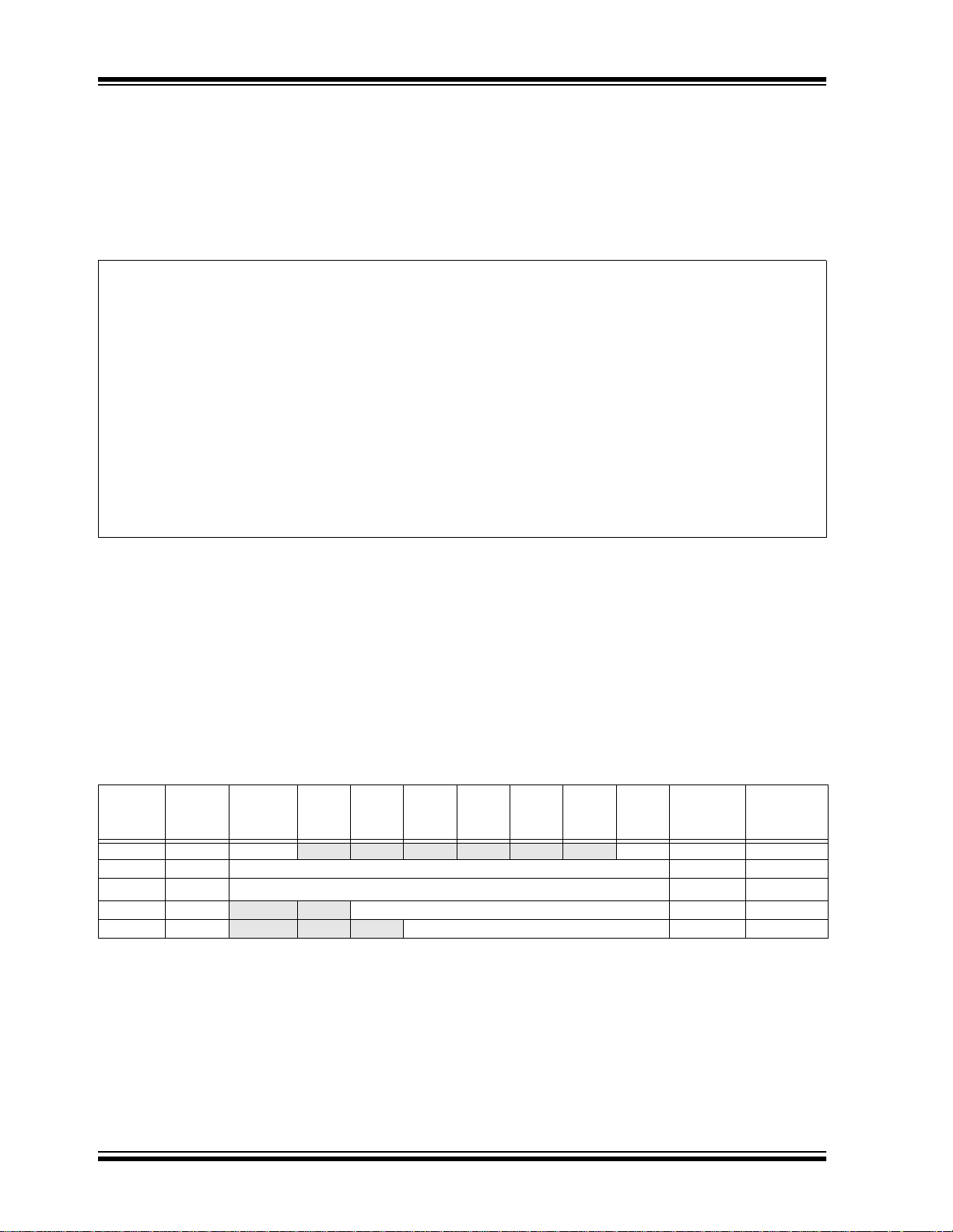

FIGURE 2-5: LOADING OF PC IN

DIFFERENT SITUATIONS

PCH PCL

12 8 7 0

PC

PCLATH<4:0>

5

PCLATH

PCH PCL

12 11 10 0

PC

2

87

PCLATH<4:3>

PCLATH

11

2.4.1 COMPUTED GOTO

A computed GOTO is accomplish ed by adding an offset

to the program counter (ADDWF PCL). When doing a

table read using a computed GOTO method, care

should be exercise d i f the t able loca tio n cros ses a PCL

memory boundary (each 256 byte block). Refer to the

application note “I mplementing a Table Read” (AN556).

2.4.2 STACK

The PIC16CXXX family has an 8-level deep x 13-bit

wide hardware stack. The stack space is not part of

either program or data space and the stack pointer is not

readable or writable. The PC is PUSHed onto the stack

when a CALL instruction is executed, or an interrupt

causes a branch. The stack is POPed in the event of a

RETURN, RETLW or a RETFIE instruction execution.

PCLATH is not affected by a PUSH or POP operation.

The stack opera tes as a circular buf fer . This means that

after the st ack h as be en PUSHed ei ght ti mes, th e nin th

push overwrites the v alue tha t was stored fro m the first

push. The tenth pus h ov erwri t es the se co nd p us h (an d

so on).

8

Instruction with

PCL as

Destination

ALU Result

GOTO, CALL

Opcode <10:0>

Note 1: There are no status bits to indicate stack

overflow or stack underflow conditions.

2: There are no instructions/mnemonics

called PUSH or POP. These are actions

that occur from the execution of the

CALL, RETURN, RETLW, and RETFIE

instructions, or the vectoring to an

interrupt address.

2.5 Program Memory Paging

PIC16C925/926 devices are capable of addressing a

continuous 8K word block of program memory. The

CALL and GOTO instructions provide only 11-bits of

address to allow branching within any 2K program

memory page. When doing a CALL or GOTO instruction,

the upper 2-bits of the address are provided by

PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensu re tha t the p age select bits are

programmed so that the desired program memory

page is addressed. If a return from a CALL instruction

(or interrupt) is executed, the en tire 13-bit PC is pushed

onto the stack. Therefore, manipulation of the

PCLATH<4:3> bits is not required for the RETURN

instructions (which POPs the address from the stack).

Note: The contents of the PCLATH register are

unchanged after a RETURN or RETFIE

instruction is executed. The user must

rewrite the PCLATH for any subsequent

CALL or GOTO instructions.

Example 2-1 shows the calling of a subroutine in

page 1 of the prog ram memory. This example assumes

that PCLATH is saved and restored by the Interrupt

Service Routine (if interrupts are used).

EXAMPLE 2-1: CALL OF A SUBROUTINE

IN PAGE 1 FROM PAGE 0

ORG 0x500

BCF PCLATH,4

BSF PCLATH,3 ;Select page 1 (800h-FFFh)

CALL SUB1_P1 ;Call subroutine in

: ;page 1 (800h-FFFh)

:

:

ORG 0x900

SUB1_P1: ;called subroutine

: ;page 1 (800h-FFFh)

:

RETURN ;return to Call subroutine

;in page 0 (000h-7FFh)

2001 Microchip Technology Inc. Preliminary DS39544A-page 25

PIC16C925/926

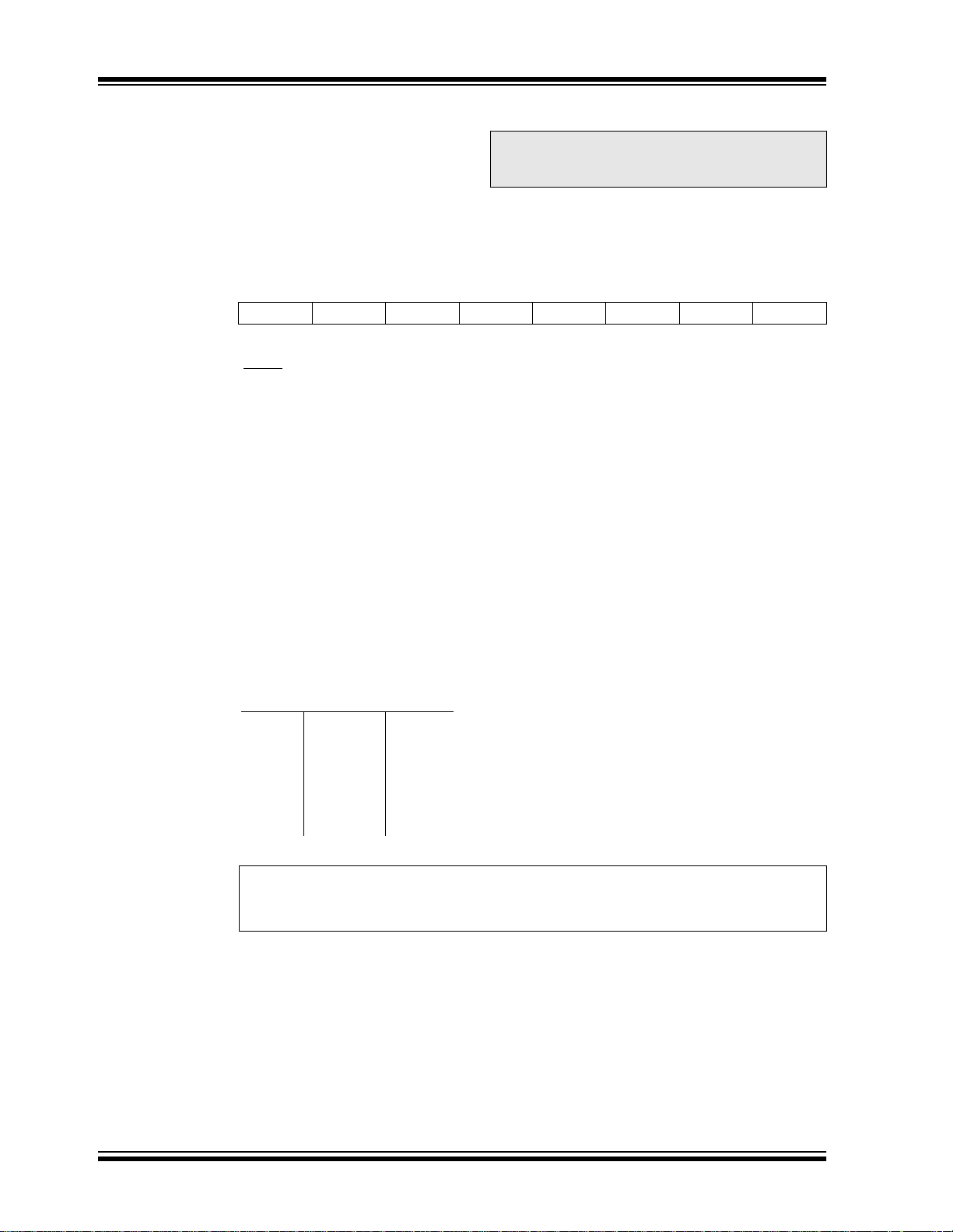

2.6 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physi cal register. Addressing

the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruc tion using the INDF register actual ly

accesses the register pointed to by the File Sele ct Register (FSR). Reading the INDF register itself, indirectly

(FSR = ’0’), w ill produc e 00h . W rit ing to the INDF re gister indirectly results in a no operation (although status

bits may be affected). An effective 9-bit address is

obtained by co ncatenating the 8-bit FSR re gister and

the IRP bit (STATUS<7>), as shown in Figure 2-6.

FIGURE 2-6: DIRECT/INDIRECT ADDRESSING

RP1:RP0 6

Bank Select Location Select

From Opcode

00h

0

00 01 10 11

A simple program to clear RAM locations 20h-2Fh

using indirect addressing is shown in Example 2-2.

EXAMPLE 2-2: INDIRECT ADDRESSING

MOVLW 0x20 ;initialize pointer

NEXT CLRF INDF ;clear INDF register

CONTINUE

MOVWF FSR ;to RAM

INCF FSR,F ;inc pointer

BTFSS FSR,4 ;all done?

GOTO NEXT ;no clear next

: ;yes continue

Indirect AddressingDirect Addressing

IRP FSR Register

Bank Select

7

Location Select

00h

0

Data

Memory

7Fh

Bank 0 Bank 1 Bank 2 Bank 3

Note: For memory map detail, see Figure 2-3.

7Fh

DS39544A-page 26 Preliminary 2001 Microchip Technology Inc.

PIC16C925/926

3.0 READING PROGRAM MEMORY

The Program Memory is readable during normal operation over the entire V

addressed through Special Function R egisters ( SFR).

Up to 14-bit numbers can be stored in memory for use

as calibration param eters, serial nu mbers, packe d 7-bit

ASCII, etc. Executing a pro gram m em ory location containing data tha t forms an inval id instructi on result s in a

NOP.

There are five SFRs used to read the program and

memory. These registers are:

• PMCON1

• PMDATA

• PMDATH

• PMADR

• PMADRH

The program memory allows word reads. Program

memory access allows for checksum calculation and

reading calibration t abl es .

DD range. It is indirectly

When interfacing to the program memory block, the

PMDATH:PMDATA registers form a two-byte word,

which holds the 14-bit data for reads. The

PMADRH:PMADR registers form a two-byte word,

which holds the 13-bit address of the location being

accessed. These devices can have from 4K words to

8K words of program memory, with an address range

from 0h to 3FFFh.

The unused upper bits in both the PMDATH and

PMADRH registers are not implemented and read as

“0’s”.

3.1 PMADR

The address registers can address up to a maxim um of

8K words of program memory.

When selecting a program address value, the MSByte

of the address is written to the PMADRH register and

the LSByte is written to the PMADR regi ster . The upper

MSbits of PMADRH must always be clear.

3.2 PMCON1 Register

PMCON1 is the control register for memory accesses.

The control bit RD initiates read operations. This bit

cannot be cleared, only set , in sof tware. It is cleared in

hardware at the completion of the read operation.

REGISTER 3-1: PMCON1 REGISTER (ADDRESS 10Ch)

R-1 U-0 U-0 U-0 U-x U-0 U-0 R/S-0

r — — — — — — RD

bit 7 bit 0

bit 7 Reserved: Read as ‘1’

bit 6-1 Unimplemented: Read as ‘0’

bit 0 RD: Read Control bit

1 = Initiates a read, RD is cleared in hardware. The RD bit can only be set (not cleared)

in software.

0 = Does not initiate a read

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR reset ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

2001 Microchip Technology Inc. Preliminary DS39544A-page 27

PIC16C925/926

3.3 Reading the Program Memory

A program memory loca tion may be read by wri ting two

bytes of the address to the PMADR and PMADRH registers, and then setting control bit RD (PMCON1<0>).

Once the read control bit is set, the microcontroller will

data is available in the PMDATA and PMDATH registers after the NOP instruction. Therefore, it can be read

as two bytes in the f ollowin g instruct ions. The PMDATA

and PMDA TH re gisters w ill hold this value unti l another

read operation.

use the next two instruction cy cles to read the data. The

EXAMPLE 3-1: PROGRAM READ

BSF STATUS, RP1 ;

BSF STATUS, RP0 ; Bank 3

MOVLW MS_PROG_PM_ADDR ;

MOVWF PMADRH ; MS Byte of Program Address to read

MOVLW LS_PROG_PM_ADDR ;

MOVWF PMADR ; LS Byte of Program Address to read

BCF STATUS, RP0 ; Bank 2

BSF PMCON1, RD ; PM Read

;

BSF STATUS, RP0 ; Bank 3

;

NOP ; Any instructions here are ignored as program

;

MOVF PMDATA, W ; W = LS Byte of Program PMDATA

MOVF PMDATH, W ; W = MS Byte of Program PMDATA

; First instruction after BSF PMCON1,RD executes normally

; memory is read in second cycle after BSF PMCON1,RD

3.4 Operation During Code Protect

If the progra m memory is not co de prot ected, the pro gram memory control can read anywhere within the

program memory.

If the entire program memory is code protected, the

program memory control can re ad anywh ere within the

program memory.

TABLE 3-1: REGISTERS ASSOCIATED WITH PROGRAM MEMORY

Address Name Bit 7 Bit 6 Bit 5 Bit 4 B it 3 Bit 2 Bit 1 Bit 0

10Ch PMCON1 (1)

18Ch PMDATA Data Register Low Byte xxxx xxxx uuuu uuuu

18Dh PMADR Address Register Low Byte xxxx xxxx uuuu uuuu

18Eh PMDATH — — Data Register High Byte xxxx xxxx uuuu uuuu

18Fh PMADRH — — — Address Register High Byte xxxx xxxx uuuu uuuu

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented, read as '0'.

Shaded cells are not used during FLASH access.

Note 1: This bit always reads as a ‘1’.

— — — — — — RD 1--- ---0 1--- ---0

If only part of the program memory is code protected,

the program memory control can read the unprotected

segment and cannot read the protected segment. The

protected area cannot be read, because it may be

possible to write a downloading routine into the

unprotected segment.

Value o n:

POR, BOR

Value on

all other

RESETS

DS39544A-page 28 Preliminary 2001 Microchip Technology Inc.

Loading...

Loading...