Page 1

Service

SR7500 /

SR8500 /

A1B/A1S/K1G/L1G

/N1B/N1G/N1S/U1B

A1B/A1S/L1G/N1B

/N1G/N1S/U1B

Manual

2nd EDITION

• 1, 25 and 27 pages were changed.

AV SURROUND RECEIVER SR7500

INPUT SELECTOR

DISP MULTI AUT O TUNED ST SPKR A B V-OF F

SLEEP

AUTO

STANDBY

POWER ON/OFF PHONES

TABLE OF CONTENTS

SECTION PAGE

1. TECH NI CAL SPEC I FI CA TIONS ........................................................................................... 1

2. TECHNICAL DESCRIPTION ................................................................................................ 4

3. POWER AMPLIFIER AD JUST MENT ................................................................................... 8

4. SERVICE MODE................................................................................................................... 9

5. SYSTEM ERROR ...............................................................................................................11

6. UPDATE FIRMWARE.......................................................................................................... 12

7. WIRING DI A GRAM ............................................................................................................. 19

8. BLOCK DIAGRAM ..............................................................................................................21

9. SCHEMATIC DIAGRAM...................................................................................................... 23

10. PARTS LOCATION..............................................................................................................45

11. IC DATA............................................................................................................................... 61

12. EXPLODED VIEW AND PARTS LIST................................................................................. 85

13. ELECTRICAL PARTS LIST................................................................................................. 97

SURR DIRECT

DISC 6.1 MTX 6.1

AV Surround Receiver

PS7500 /

PS8500 /

F1N

F1N

AV Surround Amplifi er

VOLUME

SURROUND

PEAK ANALOG

ATT

DIGITAL

DIGITAL

NIGHT

LCR

LFE

AAC

PCM

SL S SR

ENTER

DOWN

UP

PS7500 / PS8500

AUX 1 INPUT

AUDIOS-VIDEODIGITAL VIDEO L R

SR7500 / SR8500

Please use this service manual with referring to the user guide ( D.F.U. ) without fail.

SR7500 / SR8500

PS7500 / PS8500

Part no. 90M10BW855012

2nd Issue 2004.11

MJI

Page 2

MARANTZ DESIGN AND SERVICE

Using superior design and selected high grade components,

Only original

MARANTZ

parts can insure that your

MARANTZ

MARANTZ

product will continue to perform to the specifi cations for which

company has created the ultimate in stereo sound.

it is famous.

Parts for your

MARANTZ

ORDERING PARTS :

equipment are generally available to our National Marantz Subsidiary or Agent.

Parts can be ordered either by mail or by Fax.. In both cases, the correct part number has to be specifi ed.

The following information must be supplied to eliminate delays in processing your order :

1. Complete address

2. Complete part numbers and quantities required

3. Description of parts

4. Model number for which part is required

5. Way of shipment

6. Signature : any order form or Fax. must be signed, otherwise such part order will be considered as null and void.

USA

MARANTZ AMERICA, INC

1100 MAPLEWOOD DRIVE

ITASCA, IL. 60143

USA

PHONE : 630 - 741 - 0300

FAX : 630 - 741 - 0301

AUSTRALIA

QualiFi Pty Ltd,

24 LIONEL ROAD,

MT. WAVERLEY VIC 3149

AUSTRALIA

PHONE : +61 - (0)3 - 9543 - 1522

FAX : +61 - (0)3 - 9543 - 3677

EUROPE / TRADING

MARANTZ EUROPE B.V.

P. O. BOX 8744, BUILDING SILVERPOINT

BEEMDSTRAAT 11, 5653 MA EINDHOVEN

THE NETHERLANDS

PHONE : +31 - 40 - 2507844

FAX : +31 - 40 - 2507860

THAILAND

MRZ STANDARD CO., LTD

746 - 754 MAHACHAI ROAD.,

WANGBURAPAPIROM, PHRANAKORN,

BANGKOK, 10200 THAILAND

PHONE : +66 - 2 - 222 9181

FAX : +66 - 2 - 224 6795

CANADA

MARANTZ CANADA INC.

5-505 APPLE CREEK BLVD.

MARKHAM, ONTARIO L3R 5B1

CANADA

PHONE : 905 - 415 - 9292

FAX : 905 - 475 - 4159

SINGAPORE

WO KEE HONG DISTRIBUTION PTE LTD

No.1 JALAN KILANG TIMOR

#08-03 PACIFIC TECH CENTRE

SINGAPORE 159303

PHONE : +65 6376 0338

FAX : +65 6376 0166

NEW ZEALAND

WILDASH AUDIO SYSTEMS NZ

14 MALVERN ROAD MT ALBERT

AUCKLAND NEW ZEALAND

PHONE : +64 - 9 - 8451958

FAX : +64 - 9 - 8463554

JAPAN

MARANTZ JAPAN, INC.

35- 1, 7- CHOME, SAGAMIONO

SAGAMIHARA - SHI, KANAGAWA

JAPAN 228-8505

PHONE : +81 42 748 1013

FAX : +81 42 741 9190

Technical

TAIWAN

PAI- YUING CO., LTD.

6 TH FL NO, 148 SUNG KIANG ROAD,

TAIPEI, 10429, TAIWAN R.O.C.

PHONE : +886 - 2 - 25221304

FAX : +886 - 2 - 25630415

SHOCK, FIRE HAZARD SERVICE TEST :

MALAYSIA

WO KEE HONG ELECTRONICS SDN. BHD.

2ND FLOOR BANGUNAN INFINITE CENTRE

LOT 1, JALAN 13/6, 46200 PETALING JAYA

SELANGOR DARUL EHSAN, MALAYSIA

PHONE : +60 - 3 - 7954 8088

FAX : +60 - 3 - 7954 7088

KOREA

MK ENTERPRISES LTD.

ROOM 604/605, ELECTRO-OFFICETEL, 16-58,

3GA, HANGANG-RO, YONGSAN-KU, SEOUL

KOREA

PHONE : +822 - 3232 - 155

FAX : +822 - 3232 - 154

CAUTION : After servicing this appliance and prior to returning to customer, measure the resistance between either primary AC

cord connector pins ( with unit NOT connected to AC mains and its Power switch ON ), and the face or Front Panel of product and

controls and chassis bottom.

Any resistance measurement less than 1 Megohms should cause unit to be repaired or corrected before AC power is applied, and

verifi ed before it is return to the user/customer.

Ref. UL Standard No. 1492.

In case of diffi culties, do not hesitate to contact the Technical

Department at above mentioned address.

041015MJI

Page 3

1. TECHNICAL SPECIFICATIONS

FM TUNER SECTION [SR7500/SR8500]

Frequency Range.............................................87.5 - 108.0 MHz

Usable Sensitivity ........................................ IHF 1.8 µV/16.4 dBf

Signal to Noise Ratio............................... Mono/Stereo 75/70 dB

Distortion.................................................Mono/Stereo 0.2/0.3 %

Stereo Separation ....................................................1 kHz 45 dB

Alternate Channel Selectivity ............................± 300 kHz 60 dB

Image Rejection ....................................................98 MHz 70 dB

Tuner Output Level ....................... 1 kHz, ± 75 kHz Dev 800 mV

AM TUNER SECTION [SR7500/SR8500]

Frequency Range...................................531 - 1602 kHz [/A/K/N]

...................................... 520 - 1710 kHz [/L/U]

Signal to Noise Ratio.......................................................... 50 dB

Usable Sensitivity..................................................... Loop 400µV

Distortion.............................................400 Hz, 30 % Mod. 0.5 %

Selectivity............................................................± 20 kHz 70 dB

AUDIO SECTION

[SR7500/PS7500]

Power Output (20 Hz - 20 kHz/THD=0.08%)

Front L&R................................................8 ohms 105 W / Ch

Center.....................................................8 ohms 105 W / Ch

Surround L&R.........................................8 ohms 105 W / Ch

Surround Back ........................................ 8 ohms 105 W / Ch

Front L&R................................................6 ohms 130 W / Ch

Center.....................................................6 ohms 130 W / Ch

Surround L&R.........................................6 ohms 130 W / Ch

Surround Back ........................................ 6 ohms 130 W / Ch

[SR8500/SR7500]

Power Output (20 Hz - 20 kHz/THD=0.08%)

Front L&R................................................8 ohms 110 W / Ch

Center.....................................................8 ohms 110 W / Ch

Surround L&R.........................................8 ohms 110 W / Ch

Surround Back ........................................ 8 ohms 110 W / Ch

VIDEO

Television Format ....................................................... NTSC/PAL

Input Level/Impedance....................................... 1 Vp-p/75 ohms

Output Level/Impedance.................................... 1 Vp-p/75 ohms

Video Frequency Response ....................5 Hz to 8 MHz (- 1 dB)

Video Frequency (Component) ..............5 Hz to 80 MHz (- 1 dB)

S/N .....................................................................................60 dB

GENERAL

Power Requirement.................................AC 240 V 50/60 Hz [/A]

.................................AC 100 V 50/60 Hz [/F]

......................................AC 220 V 50 Hz [/K]

......................................AC 110 V 60 Hz [/L]

..................................... AC 230 V 50 Hz [/N]

..................................... AC 120 V 60 Hz [/U]

Power Consumption............................ 600 W [SR7500/PS7500]

............................ 620 W [SR8500/PS8500]

Weight ...............................14.8 kg (32.6 Ibs) [SR7500/PS7500]

...............................15.0 kg (33.1 Ibs) [SR8500/PS8500]

ACCESSORIES

Remote Control Unit RC8500SR .............................................. 1

AAA-size batteries.................................................................... 3

Microphone MC-10................................................................... 1

Front AUX Jack Cover.............................................................. 1

AC cable................................................................................... 1

FM Antenna [SR7500/SR8500]................................................. 1

AM Loop Antenna [SR7500/SR8500] ....................................... 1

Front L&R................................................6 ohms 145 W / Ch

Center.....................................................6 ohms 145 W / Ch

Surround L&R.........................................6 ohms 145 W / Ch

Surround Back ........................................ 6 ohms 145 W / Ch

Input Sensitivity/Impedance .......................... 168 mV/ 47 kohms

Signal to Noise Ratio

Analog Input / Source Direct......................................... 105 dB

Frequency Response

Analog Input / Source Direct............8 Hz - 100 kHz (± 3 dB)

Digital Input / 96 kHz PCM................ 8 Hz - 45 kHz (± 3 dB)

1

Page 4

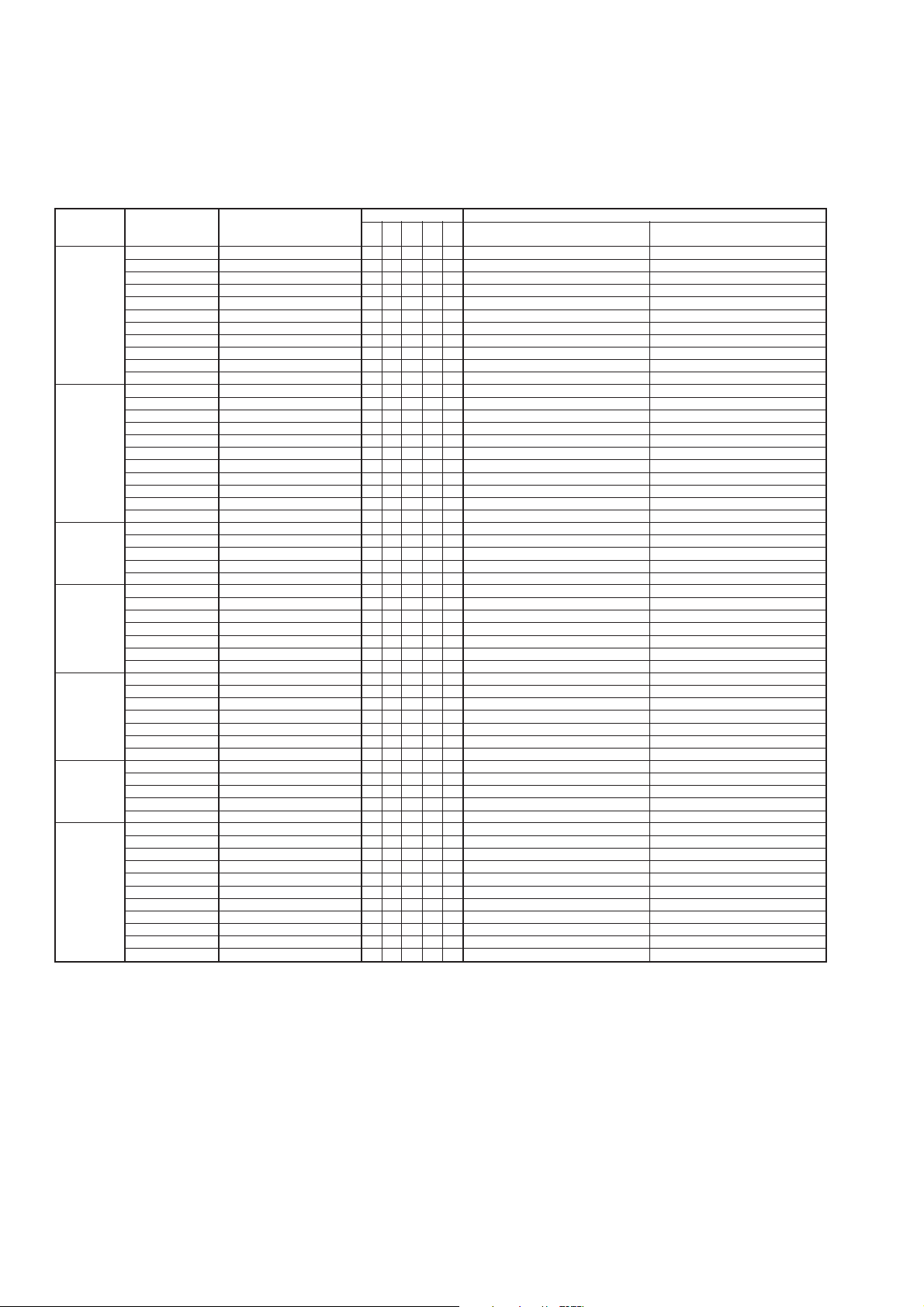

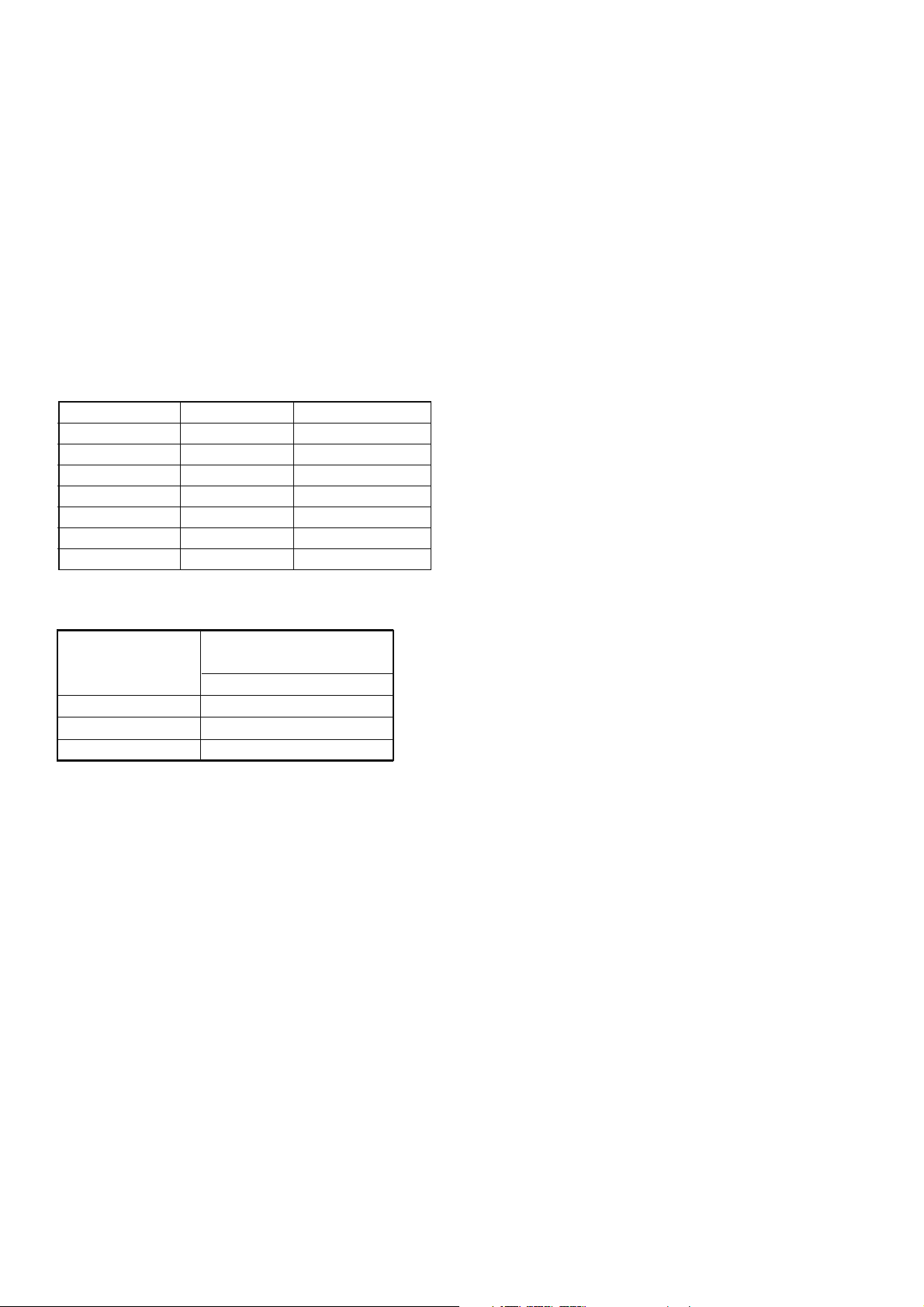

The relation between the selected surround mode and the input signal

The surround mode is selected with the surround mode buttons on SR7500/SR8500/PS7500/PS8500 or the remote control

unit. However, the sound you hear is subject to the relationship between the selected surround mode and input signal. That

relationship is as follows;

Surround Mode Input Signal Decoding

AUTO Dolby Surr. EX Dolby Digital EX

PURE DIRECT Dolby D Surr. EX Dolby Digital EX

EX/ES Dolby D Surr. EX Dolby Digital EX

DOLBY Dolby D Surr. EX Dolby Digital 5.1

(PLIIx movie) Dolby D (5.1ch) Dolby Digital 5.1

(PLIIx music) Dolby D (2ch) Pro Logic IIx

(PLIIx game) Dolby D (2ch Surr) Pro Logic IIx

DTS DTS-ES DTS 5.1

(Neo:6 Cinema) DTS 96/24 DTS 96/24

(Neo:6 Music) DTS (5.1ch) DTS 5.1

CSII Cinema PCM (Audio) CS

CSII Music HDCD

CS

II

Mono Analog CS

STEREO Dolby Surr. EX Stereo

Dolby D (5.1ch) Dolby Digital 5.1

Dolby D(2ch) Dolby Digital 2.0

Dolby D (2ch Surr) Pro Logic IIx movie

DTS-ES DTS-ES

DTS 96/24 DTS 96/24

DTS (5.1ch) DTS 5.1

PCM(Audio) PCM (Stereo)

PCM 96kHz PCM (96kHz Stereo)

HDCD

*

Analog Stereo

Dolby D (5.1ch) Dolby Digital 5.1

Dolby D (2ch) Dolby Digital 2.0

Dolby D (2ch Surr) Pro Logic IIx movie

DTS-ES DTS-ES

DTS 96/24 DTS 96/24

DTS (5.1ch) DTS 5.1

PCM (Audio) PCM (Stereo)

PCM 96kHz PCM (96kHz Stereo)

HDCD

*

Analog Stereo

Dolby D (5.1ch) Dolby Digital EX

DTS-ES DTS-ES

DTS 96/24 DTS-ES

DTS(5.1ch) DTS-ES

PCM (Audio) Pro Logic IIx

HDCD

*

Analog Pro Logic IIx

PCM (Audio) Neo:6

Analog Neo:6

Dolby D (2ch) Neo:6

Dolby D (2ch Surr) Neo:6

*

Dolby D (2ch) CS

Dolby D (2ch Surr) CS

Dolby D (5.1ch) Stereo

Dolby D (2ch) Stereo

Dolby D (2ch Surr) Stereo

DTS-ES Stereo

DTS 96/24 Stereo

DTS (5.1ch) Stereo

PCM (Audio) Stereo

PCM 96kHz Stereo

HDCD

*

Analog Stereo

Stereo

Stereo

Pro Logic IIx

II

CS

II

II

II

II

Stereo

Output Channel Front information display

SL SBL

L/R C

OOOOO2 DIGITAL EX L, C, R, SL, SR, S, LFE

OOO-O2 DIGITAL L, C, R, SL, SR, LFE

O

-- - -2 DIGITAL L, R

OOOO-2

OOOOO

OOO-O

OOO-O

O

- - - - PCM L, R

O

- - - - PCM L, R

O

- - - - PCM, HDCD L, R

O

- - - - ANALOG OOOOO2 DIGITAL EX L, C, R, SL, SR, S, LFE

OOO-O2 DIGITAL L, C, R, SL, SR, LFE

O

-- - -2 DIGITAL L, R

OOOO-2

OOOOO

OOO-O

OOO-O

O

- - - - PCM L, R

O

- - - - PCM L, R

O

- - - - PCM, HDCD L, R

O

- - - - ANALOG OOOOO2 DIGITAL EX L, C, R, SL, SR, S, LFE

OOOOO2 DIGITAL L, C, R, SL, SR, LFE

OOOOO

OOOOO

OOOOO

OOOOO2 DIGITAL EX L, C, R, SL, SR, S, LFE

OOOOO2 DIGITAL L, C, R, SL, SR, LFE

OOOO-2

OOOO-2

OOOO

OOOO

OOOO

OOO-O

OOO-O

OOO-O

OOOO

OOOO

OOOO-2

OOOO-2

OOOOO

OOOOO

OOOOO

OOOOO2 DIGITAL L, R

OOOOO2 DIGITAL , 2 SURROUND L, R, S

O

-- -O2

O

-- -O2

O

-- - -2 DIGITAL L, R

O

-- -O2

O

-- -Odts, ES L, C, R, SL, SR, S, LFE

O

-- -Odts 96/24 L, C, R, SL, SR, LFE

O

-- -Odts L, C, R, SL, SR, LFE

O

- - - - PCM L, R

O

- - - - PCM L, R

O

- - - - PCM, HDCD L, R

O

- - - - ANALOG -

SubW

SR SBR

Signal format indicators Channel status

DIGITAL , 2 SURROUND L, R, S

dts, ES L, C, R, SL, SR, S, LFE

dts 96/24 L, C, R, SL, SR, LFE

dts L, C, R, SL, SR, LFE

DIGITAL , 2 SURROUND L, R, S

dts, ES L, C, R, SL, SR, S, LFE

dts 96/24 L, C, R, SL, SR, LFE

dts L, C, R, SL, SR, LFE

dts , ES L, C, R, SL, SR, S, LFE

dts 96/24 L, C, R, SL, SR, LFE

dts L, C, R, SL, SR, LFE

DIGITAL L, R

DIGITAL , 2 SURROUND L, R, S

- PCM L, R

- PCM, HDCD L, R

- ANALOG dts, ES L, C, R, SL, SR, S, LFE

dts 96/24 L, C, R, SL, SR, LFE

dts L, C, R, SL, SR, LFE

- PCM L, R

- ANALOG -

DIGITAL L, R

DIGITAL , 2 SURROUND L, R, S

PCM L, R

PCM, HDCD L, R

ANALOG -

DIGITAL EX L, C, R, SL, SR, S, LFE

DIGITAL L, C, R, SL, SR, LFE

DIGITAL , 2 SURROUND L, R, S

*

*

: SR8500 only

: PS8500 only

2

Page 5

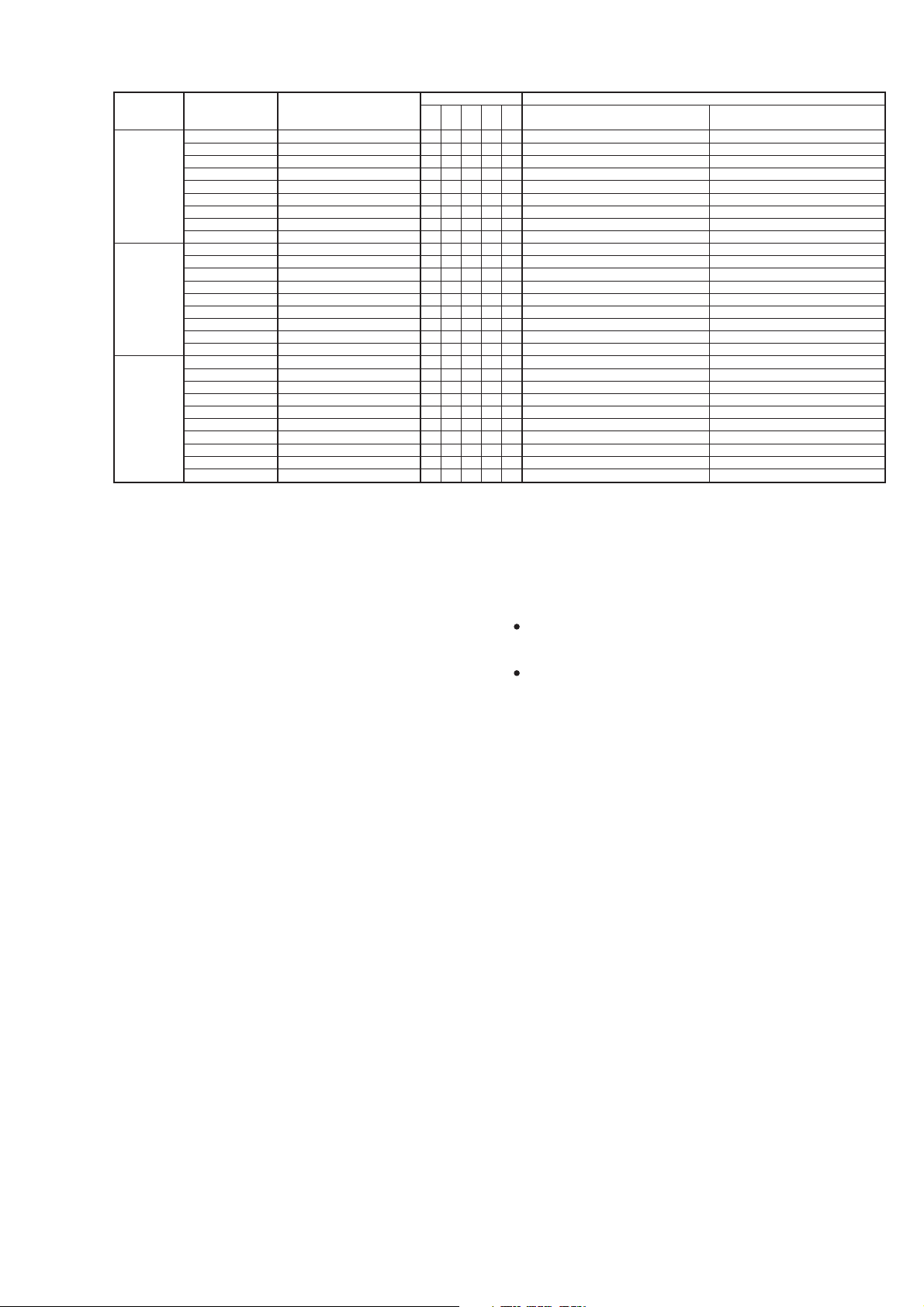

*

: SR8500 only

Output Channel Front information display

Surround Mode Input Signal Decoding

L/R C

SL SBL

SubW

Signal format indicators Channel status

SR SBR

Virtual Dolby Surr. EX Virtual

O

-- - -2 DIGITAL EX L, C, R, SL, SR, S, LFE

Dolby D (5.1ch) Virtual

O

-- - -2 DIGITAL L, C, R, SL, SR, LFE

Dolby D (2ch) Virtual

O

-- - -2 DIGITAL L, R

Dolby D (2ch Surr) Virtual

O

-- - -2 DIGITAL , 2 SURROUND L, R, S

DTS-ES Virtual

O

- - - - dts, ES L, C, R, SL, SR, LFE

DTS (5.1ch) Virtual

O

- - - - dts L, C, R, SL, SR, LFE

PCM (Audio) Virtual

O

- - - - PCM L, R

HDCD

*

Virtual

O

- - - - PCM, HDCD L, R

Analog Virtual

O

- - - - ANALOG -

Multi Ch. Dolby Surr. EX Multi Channel Stereo

OOOOO2 DIGITAL EX L, C, R, SL, SR, S, LFE

Stereo Dolby D (5.1ch) Multi Channel Stereo

OOO-O2 DIGITAL L, C, R, SL, SR, LFE

Dolby D (2ch) Multi Channel Stereo

OOOO-2

DIGITAL L, R

Dolby D (2ch Surr) Multi Channel Stereo

OOOO-2

DIGITAL , 2 SURROUND L, R, S

DTS-ES DTS-ES

OOOOO

dts, ES L, C, R, SL, SR, S, LFE

DTS (5.1ch) DTS 5.1

OOO-O

dts L, C, R, SL, SR, LFE

PCM (Audio) Multi Channel Stereo

OOOO

- PCM L, R

HDCD

*

Multi Channel Stereo

OOOO

- PCM, HDCD L, R

Analog Multi Channel Stereo

OOOO

- ANALOG -

THX Dolby Surr. EX THX Surround EX + Dolby Digital

OOOOO2 DIGITAL EX L, C, R, SL, SR, S, LFE

Dolby D (5.1ch) THX + Dolby Digital

OOO-O2 DIGITAL L, C, R, SL, SR, LFE

Dolby D (2ch) THX + Pro Logic IIx

OOOO-2

DIGITAL L, R

Dolby D (2ch Surr) THX + Pro Logic IIx

OOOO-2

DIGITAL , 2 SURROUND L, R, S

DTS-ES THX + DTS-ES

OOOOO

dts, ES L, C, R, SL, SR, S, LFE

DTS 96/24 THX + DTS

OOO-O

dts 96/24 L, C, R, SL, SR, LFE

DTS (5.1ch) THX + DTS

OOO-O

dts L, C, R, SL, SR, LFE

PCM (Audio) THX + Pro Logic IIx

OOOO

- PCM L, R

HDCD

*

THX + Pro Logic IIx

OOOO

- PCM, HDCD L, R

Analog THX + Pro Logic

II

x

OOOO

- ANALOG -

: PS8500 only

*

Note:

• Dolby Digital (2 ch: Lt/Rt): signal with Dolby

Surround flag Speakers are full set.

• No sound outputs from the surround speaker,

center speaker and subwoofer if the DVD disc has

no surround data.

Abbreviations

L/R : Front speakers

C : Center speaker

SL/SR : Surround speakers

SBL/SBR : Surround Back speakers

SubW : Sub woofer speaker

DolbyDigital(2chSurr):

ドルビーサラウンド処理されたドルビーデ

ジタル2ch信号

: サブウーファー他のスピーカーのLarge/

*

Smallによってサブウーファー出力は異な

ります。

L/R: フロントスピーカー

C: センタースピーカー

SL/SR: サラウンドスピーカー

SBL/SBR: サラウンドバックスピーカー

SubW: サブウーファースピーカー

3

Page 6

2. TECHNICAL DESCRIPTION

THX® is an exclusive set of standards and

technologies established by the world-renowned

film production company, Lucasfilm Ltd. THX

resulted from George Lucas’ desire to reproduce

the movie soundtrack as faithfully as possible both

in the movie theater and in the home theater.

THX engineers developed patented technologies

to accurately translate the sound from a movie

theater environment into the home, correcting the

tonal and spatial errors that occur.

When the THX mode of the SR7500 is on, three

distinct THX technologies are automatically

added:

Re-Equalization-restores the correct tonal balance

for watching a movie in a home environment.

These sounds are otherwise mixed to be brighter

for a large movie theater. Re-EQ compensates for

this and prevents the soundtracks from being

overly bright and harsh when played in a home

theater.

Timbre Matching-filters the information going to

the surround speakers so they more closely match

the tonal characteristics of the sound coming from

the front speakers.

This ensures seamless panning between the front

and surround speakers.

Adaptive Decorrelation-slightly changes one

surround channel’s time and phase relationship

with respect to the other surround channel.

This expands the listening position and creates

with only two surround speakers the same

spacious surround experience as in a movie

theater with multiple surround speakers.

The Marantz SR7500 was required to pass a

rigorous series of quality and performance tests, in

addition to incorporating the technologies

explained above, in order to be THX certified by

Lucasfilm Ltd.

THX requirements cover every aspect of

performance including pre-amplifier and power

amplifier performance and operation, and

hundreds of other parameters in both the digital

and analog domain.

Movies which have been encoded in Dolby Digital,

DTS, Dolby Pro Logic, stereo and Mono will all

benefit from the THX mode when being viewed.

The THX mode should only be activated when

watching movies which were originally produced

for a movie theater environment.

This is because they were originally mixed for a

small room environment.

THX is a trademark or registered trademark of THX

Ltd. Surround EX is a jointly developed technology

of THX and Dolby Laboratories, Inc. and is a

trademark of Dolby Laboratories, Inc. Used under

authorization. All rights reserved.

THX Surround EX—Dolby DIgital Surround EX is a

joint development of Dolby Laboratories and THX

Ltd.

In a movie theater, film soundtracks that have been

encoded with Dolby Digital Surround EX

technology are able to reproduce an extra channel

which has been added during the mixing of the

program. This channel, called Surround Back,

places sounds behind the listener in addition to the

currently available front left, front center, front

right, surround right, surround left and subwoofer

channels. This additional channel provides the

opportunity for more detailed imaging behind the

listener and brings more depth, spacious

ambience and sound localization than ever before.

Movies that were created using the Dolby Digital

Surround EX technology, when released into the

home consumer market may exhibit wording to that

effect on the packaging. A list of movies created

using this technology can be found on the Dolby

web site at www.dolby.com. A list of available

DVD software titles encoded with this technology

an be found at www.thx.com.

Only receiver and controller products bearing the

THX Surround EX logo, when in the THX Surround

EX mode, faithfully reproduce this new technology

in the home. This product may also engage the

THX Surround EX mode during the playback of 5.1

channel material that is not Dolby Digital Surround

EX eocnded. In such case, the information

delivered to the Surround Back channel will be

program dependent and may or may not be very

pleasing depending on the particular soundtrack

and the tastes of the individual listener.

“SURROUND EX™” is a trademark of Dolby

Laboratories. Used under authorization.

4

Page 7

DTS was introduced in 1994 to provide 5.1

channels of discrete digital audio into home theater

systems.

DTS brings you premium quality discrete

multichannel digital sound to both movies and

music.

DTS is a multichannel sound system designed to

create full range digital sound reproduction.

The no compromise DTS digital process sets the

standard of quality for cinema sound by delivering

an exact copy of the studio master recordings to

neighborhood and home theaters.

Now, every moviegoer can hear the sound exactly

as the moviemaker intended.

DTS can be enjoyed in the home for either movies

or music on of DVD’s, LD’s, and CD’s.

“DTS” and “DTS Digital Surround” are registered

trademarks of Digital Theater Systems, Inc.

the subtlety and integrity of the original stereo

recording.

DTS-ES Extended Surround is a new multichannel

digital signal format developed by Digital Theater

Systems Inc. While offering high compatibility with

the conventional DTS Digital Surround format,

DTS-ES Extended Surround greatly improves the

360-degree surround impression and space

expression thanks to further expanded surround

signals. This format has been used professionally

in movie theaters since 1999.

In addition to the 5.1 surround channels (FL, FR,

C, SL, SR and LFE), DTS-ES Extended Surround

also offers the SB (Surround Back) channel for

surround playback with a total of 6.1 channels.

DTS-ES Extended Surround includes two signal

formats with different surround signal recording

methods, as DTS-ES Discrete 6.1 and DTS-ES

Matrix 6.1.

“DTS”, “DTS-ES and “Neo:6” are trademarks of

Digital Theater Systems, Inc.

The advantages of discrete multichannel systems

over matrix are well known.

But even in homes equipped for discrete

multichannel, there remains a need for high-quality

matrix decoding. This is because of the large

library of matrix surround motion pictures available

on disc and on VHS tape; and analog television

broadcasts.

The typical matrix decoder of today derives a

center channel and a mono surround channel from

two-channel matrix stereo material. It is better than

a simple matrix in that it includes steering logic to

improve separation, but because of its mono,

band-limited surround it can be disappointing to

users accustomed to discrete multichannel.

Neo:6 offers several important improvements as

follow,

• Neo:6 provides up to six full-band channels of

matrix decoding from stereo matrix material.

Users with 6.1 and 5.1 systems will derive six

and five separate channels, respectively,

corresponding to the standard home-theater

speaker layouts.

• Neo:6 technology allows various sound

elements within a channel or channels to be

steered separately, and in a way which follows

naturally from the original presentation.

The stereo CD is a 16-bit medium with sampling at

44.1 kHz. Professional audio has been 20- or 24bit for some time, and there is increasing interest in

higher sampling rates both for recording and for

delivery into the home. Greater bit depths provide

extended dynamic range. Higher sampling rates

allow wider frequency response and the use of

anti-alias and reconstruction filters with more

favorable aural characteristics.

DTS 96/24 allows for 5.1channel sound tracks to

be encoded at a rate of 96kHz/24bits on DVDVideo titles.

When DVD-video appeared, it became possible to

deliver 24-bit, 96 kHz audio into the home, but only

in two channels, and with serious limitations on

picture. This capability has had little use.

DVD-audio allows 96/24 in six channels, but a new

player is needed, and only analog outputs are

provided, necessitating the use of the D/A

converters and analog electronics provided in the

player.

5

Page 8

DTS 96/24 offers the following:

1. Sound quality transparent to the original 96/24

master.

2.Full backward compatibility with all existing

decoders. (Existing decoders will output a 48

kHz signal)

3.No new player required: DTS 96/24 can be

carried on DVD-video, or in the video zone of

DVD-audio, accessible to all DVD players.

4. 96/24 5.1-channel sound with full-quality fullmotion video, for music programs and motion

picture soundtracks on DVD-video.

“DTS” and “DTS 96/24” are trademarks of Digital

Theater Systems, Inc.

Dolby Digital identifies the use of Dolby Digital

audio coding for such consumer formats as DVD

and DTV. As with film sound, Dolby Digital can

provide up to five full-range channels for left,

center, and right screen channels, independent left

and right surround channels, and a sixth (“.1”)

channel for low-frequency effects.

Dolby Surround Pro Logic II is an improved matrix

decoding technology that provides better spatiality

and directionality on Dolby Surround program

material; provides a convincing three-dimensional

soundfield on conventional stereo music

recordings; and is ideally suited to bring the

surround experience to automotive sound. While

conventional surround programming is fully

compatible with Dolby Surround Pro Logic

decoders, soundtracks will be able to be encoded

specifically to take full advantage of Pro Logic

playback, including separate left and right

surround channels. (Such material is also

compatible with conventional Pro Logic decoders.)

About Dolby Pro Logic IIx

Dolby Pro Logic IIx technology delivers a natural

and immersing 7.1-channel listening experience to

the home theater environment. A product of

Dolby's expertise in surround sound and matrix

decoding technologies, Dolby Pro Logic II x is a

complete surround sound solution that maximizes

the entertainment experience from stereo as well

as 5.1-channel encoded sources.

Dolby Pro Logic IIx is fully compatible with Dolby

Surround Pro Logic technology and can optimally

decode the thousands of commercially available

Dolby Surround encoded video cassettes and

television programs with enhanced depth and

spatiality. It can also process any high-quality

stereo or Advanced Resolution 5.1-channel music

content into a seamless 6.1- or 7.1-channel

listening experience.

The Dolby Headphone technology provides a

surround sound listening experience over headphones.

When listening to multichannel content such as

DVD movies over headphones, the listening

experience is fundamentally different than

listening to speakers. Since the headphone

speaker drivers are covering the pinna of the ear,

the listening experience differs greatly from

traditional speaker playback. Dolby utilizes

patented headphone perspective curves to solve

this problem and provides a non-fatiguing,

immersive, home theater listening experience.

II

II

Dolby Headphone also delivers exceptional 3D

audio from stereo material.

Manufactured under license from Dolby

Laboratories. “Dolby”, “Pro Logic”, and the doubleD symbol are trademarks of Dolby Laboratories.

Dolby Digital EX creates six full-bandwidth output

channels from 5.1-channel sources. This is done

using a matrix decoder that derives three surround

channels from the two in the original recording.

For best results, Dolby Digital EX should be used

with movies soundtracks recorded with Dolby

Digital Surround EX.

6

Page 9

Circle Surround II (CS-II) is a powerful and

versatile multichannel technology. CS-II is

designed to enable up to 6.1 multichannel surround

sound playback from mono, stereo, CS encoded

sources and other matrix encoded sources. In all

cases the decoder extends it into 6 channels of

surround audio and a LFE/subwoofer signal. The

CS-II decoder creates a listening environment that

places the listener “inside” music performances

and dramatically improves both hi-fi audio

conventional surround-encoded video material.

CS-II provides composite stereo rear channels to

greatly improve separation and image positioning–

adding a heightened sense of realism to both audio

and A/V productions.

CS-II is packed with other useful feature like dialog

clarity (SRS Dialog) for movies and cinema-like

bass enrichment (TruBass). CS-II can enable the

dialog to become clearer and more discernable in

movies and it enables the bass frequencies

contained in the original programming to more

closely achieve low frequencies–overcoming the

low frequency limitations of the speakers by full

octave.

HDCD system manufactured under license from

Microsoft. This product is covered by one or more

of the following: In the United States 5,479,168

5,638,074 5,640,161 5,808,574 5,838,274

5,854,600 5,864,311 5,872,531 and in Australia

669,114 with other patents pending.

Circle Surround II , Dialog Clarity, TruBass, SRS

and symbol are trademarks of SRS Labs, Inc.

Circle Surround II, Dialog Clarity and TruBass

technology are incorporated under license from

SRS Labs, Inc.

(SR8500 only)

HDCD® (High Definition Compatible Digital ®) is a

patented process for delivering on Compact Disc

the full richness and details of the original

microphone feed.

HDCD encoded CDs sound better because they

are encoded with 20-bits of real musical

information as compared to 16-bits for all other

CDs.

HDCD overcomes the limitation of the 16-bit CD

format by using a sophisticated system to encode

the additional four bits onto the CD while remaining

completely compatible with the CD format.

When listening to HDCD recordings, you hear

more dynamic range, a focused 3-D sound stage,

and extremely natural vocal and musical timbre.

With HDCD, you get the body, depth and emotion

of the original performance not a flat, digital

imitation.

7

Page 10

3. POWER AMPLIFIER ADJUSTMENT

Idling Current Alignment

1. Each of the measurement points are provided with the

two test points. Set a digital Voltage meter to DC voltage

input, connect the meter to the test points at both contact points.

2. After the setup above, turn on the main switch.

3. Adjust variable resistors (VR41, VR42…VR71) accord-

ing to the digital voltmeter readings. The target setting

value is the following table for each channel.

Settings: Master Volume — Minimum

Speaker out — No Load

Top lid — OPEN

Channel Alignment Point Measurement Point

Front L VR41 CN41

Center VR61 CN61

Front R VR51 CN51

Surround L VR42 CN42

Surround R VR52 CN52

Surround Back L VR62 CN62

Surround Back R VR71 CN71

Time Table of Idling Current Rise

Ambient temperature

After Turning ON

10 min. 2.4 mV ± 0.3 mV

20 min. 2.4 mV ± 0.3 mV

30 min. 2.4 mV ± 0.3 mV

20 to 30 degrees centigrade

Measurement Voltage

8

Page 11

4. SERVICE MODE

4. SERVICE MODE

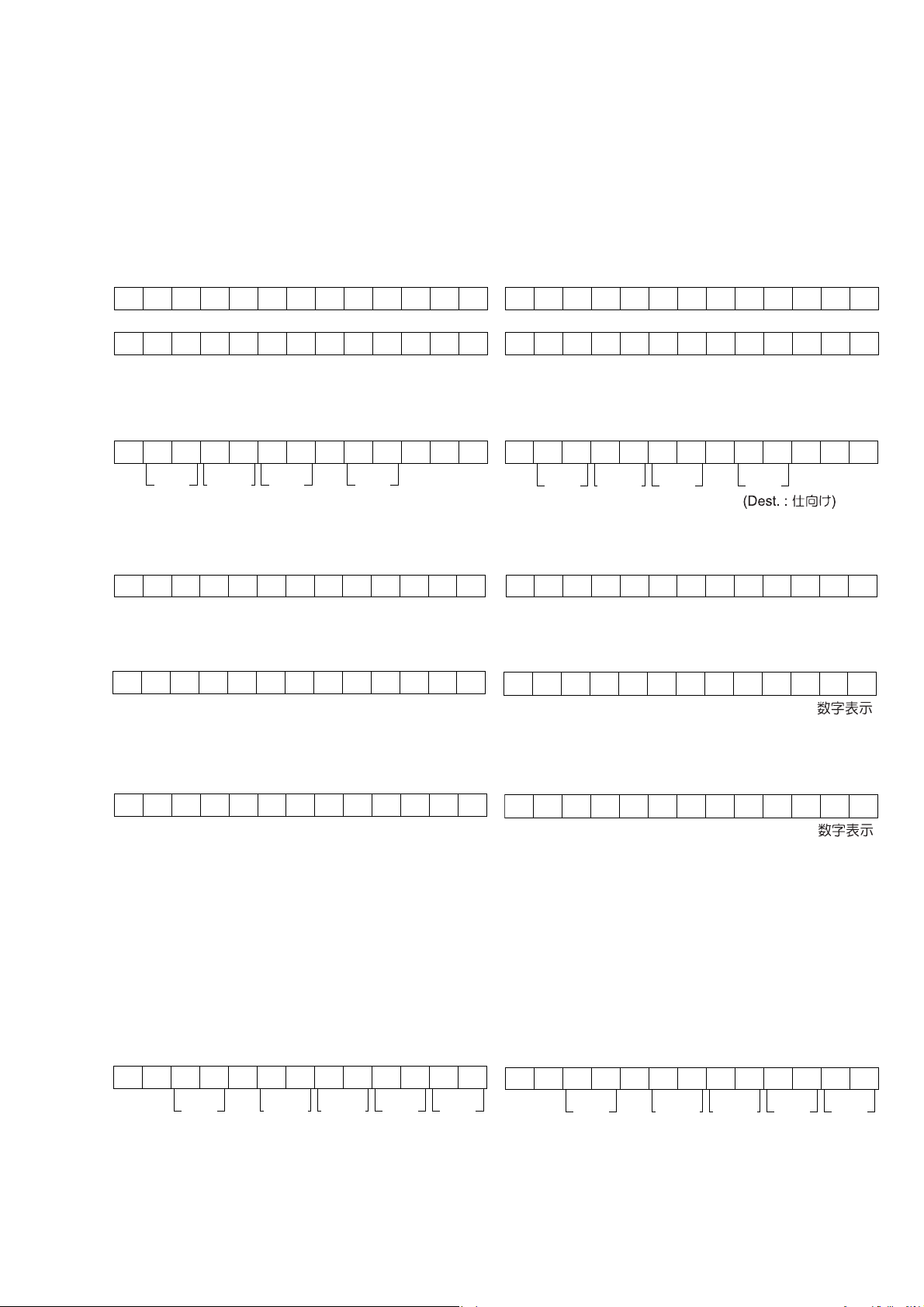

Microprocessor (IC36), DSP(IC20 )Version and FLD Segment Check Mode.

1. While the power is on, PURE DIRECT, MRAC and 7.1CH

INPUT buttons simultaneously more than 3 seconds.

The FL display shows “SERVICE MODE” for 2 seconds

then shows the model name.

SERVI CE MODE

SR8500

2. Press ENTER button, The software version of the micro-

processor (IC36) is displayed in the format below.

V040805 1U

Year

Month Date Dest.

(Dest. : Destination)

3. Press ENTER button again, The software Serial Number

that is wirtten in the factory is displayed.

Microprocessor (IC36), DSP(IC20 )ƷVersion

ໜ༔ǛᄩᛐƢǔȢȸȉưƢŵ

1.

ǻȃȈƷᩓเǛλǕLJƢŵ

7.1CH IN PUT

“SERVICE MODE”

ᆔӸƕᘙᅆƞǕLJƢŵ

ƷȜǿȳǛӷƴኖ3ᅺˌɥƠLJƢŵ

ƱᘙᅆƕЈLJƢŵƴኖ2ᅺࢸƴೞ

PURE DIRECTŴ MRAC

ᘙᅆӏƼ

SERVI CE MODE

SR8500

2. ENTER

ȳƕഏƷǑƏƴᘙᅆƞǕLJƢŵ

ȜǿȳǛƠLJƢŵȞǤdzȳᲢ

IC36

ᲣƷȐȸǸȧ

V040805 1U

Year

3.

ENTER

Software Serial No.

Month Date Dest.

ȜǿȳǛƠLJƢŵئưƖᡂLjฎLjƷ

ƕᘙᅆƞǕLJƢ

FL

Ŵ

MZXXXXXX XXXXX

4. Press ENTER button again, The software Type Number

is displayed.

SOFT TYPE XX

(XX is displayed in Hex)

5. Press ENTER button again, The Code Group Type

Number is displayed.

CODE TYPEXXXX

(XXXX is displayed in Hex)

6. Press ENTER button again, The left half, right half and

center of the label area in the FLD light on and off each

other.

7. Press ENTER button again, The segments of the character area in the FLD fl ick in checker pattern.

8. Press ENTER button again, All the FL segments turns

off.

9. Press ENTER button again. Every time ENTER button

is pressed, DSP code is indicated in turn from NO.1 to

NO.28.

MZXXXXXX XXXXX

4. ENTER

Soft ware Type

ȜǿȳǛƠLJƢŵȞǤdzȳᲢ

ƕᘙᅆƞǕLJƢŵ

IC36

ᲣƷ

SOFT T YPE XX

(XX: Hex

5. ENTER

ǕLJƢŵ

ȜǿȳǛƠLJƢŵ

Code Group Type

ƕᘙᅆƞ

CODE T YP E X X XX

(XXXX: Hex

6. ENTER

Ўƕʩʝƴໜ༔ǛጮǓᡉƠLJƢŵ

7. ENTER

๒ƠLJƢŵ

8. ENTER

9. ENTER

DSP Code IDƕNO.1

Ƣŵ

ȜǿȳǛƠLJƢŵFLᘙᅆƷӫŴŴɶځᢿ

ȜǿȳǛƠLJƢŵFLƷ

ȜǿȳǛƠLJƢŵFLƕμෞ໊ƠLJƢŵ

ȜǿȳǛƠLJƢŵ

Ɣǒ

Character

ENTER

NO.28

ȜǿȳǛƢࡇƴ

LJưƴᘙᅆƞǕLJ

ᢿЎƕໜ

)

)

CD01 01020101

SIGDev. TYP Ver.No.

No. : DISP CODE ID Dev. : Device ID SIG. : CODE SIG ID

TYP. : CODE TYPE ID Ver. : Version

10. Press ENTER button again to quit this mode.

CD01 01020101

SIGDev. TYP Ver.No.

No. : DISP CODE ID Dev. : Device ID SIG. : CODE SIG ID

TYP. : CODE TYPE ID Ver. : Version

10ENTER

LJƢŵ

9

ȜǿȳǛƠLJƢŵǵȸȓǹȢȸȉƸᚐᨊƞǕ

Page 12

Note: Step4, 5 is to check if CPU software is capable of

DSP code. “Software Type No” is to show what “DSP

Code Group” CPU is capable of. And vice versa.

Step 9 is to manage the 40 codes for DSP.

• When the unit is once turned into Service Mode, the

unit keeps this mode until the main power is turned

off. (Turning into stand-by mode does not make it

quit from Service Mode.) When the unit quits from

Service Mode, Information in the memory is also

cleared and the unit returns to the status when it is

out from the factory.

Product Reset

To reset the back up memory of the unit into the default status, follow the procedure below.

1. Turn of the unit and press SPEAKERS A/B and MULTI

button simultaneously more than 1.5 seconds.

2. After “DEFAULT” is displayed on FLD, power is turned

off once and turned of again, EEPROM is cleared to

the default status, µ-com is reset and the unit returns to

the normal status. (Software Serial Number will not be

cleared.)

Note: When the unit is shipped from the factory, the proce-

dure above must be done to set the unit to initial sta-

Personal notes:

10

Page 13

5. SYSTEM ERROR

ီࠝ౨Јᘙᅆŵ

ီࠝ౨Јᘙᅆŵ

ီࠝ౨Јᘙᅆŵ

ီࠝ౨Јᘙᅆŵ

ီࠝ౨Јᘙᅆŵ

ီࠝ౨Јᘙᅆŵ

ӭီࠝ౨Јᘙᅆŵ

5. SYSTEM ERROR

When the microcomputer detects a trouble, the following information is displayed on the FLD.

• After the error contents indication, Surround Mode is

initialized and returned Factory mode.

• The contents of the ERROR indication are the followings.

1. Trouble in DSP

If communication with DSP is troubled more than 2

seconds.

CHECK DSP ROM

Indication is keep and sound is mute.

2. Trouble in DSP Code

The trouble of DSP Code was found.

CHECK DSP ROM

3. Trouble in EEP-ROM

If data from EEPROM does not match.

CHECK E2P

4. Trouble in EEP-ROM IF

If communication with EEPROM is troubled more than 2

seconds.

ᙌԼϋᢿưƷီࠝႆဃƴϼྸŴᘙᅆǛᘍƍLJƢŵɼƴӲ

Device

ƱƷᡫီࠝǛ౨ЈƠLJƢŵ

ERROR

ƷཞƴǓLJƢŵ

ERROR

1. DSP

DSP

ᘙᅆࢸŴ

ᘙᅆƷϋܾƸɦᚡưƢŵ

ီࠝ౨Јᘙᅆŵ

ƱƷᡫɥƷɧφӳǛኖ ᅺ౨ЈƠƨŵ

SurroundMode

ƸИ҄ƞǕئЈᒵ

CHECK DSP ROM

ᘙᅆཞƸƦƷLJLJư᪦٣Ƹ /WVG ཞ

2. DSP Code

DSPCode

ီࠝ౨Јᘙᅆŵ

ƷီࠝǛ౨ЈƠƨŵ

CHECK DSP ROM

3. EEP-ROM

EEPROMData

ီࠝ౨Јᘙᅆŵ

ƷɧૢӳǛ౨ЈƠƨŵ

CHECK E2P

4. EEP-ROM IF

EEPROM

ီࠝ౨Јᘙᅆŵ

ƱƷᡫɧφӳƕኖ ᅺˌɥဃơƨŵ

CHECK E2P I F

5. Trouble in RS-232C

If communication of Panja with RS232C is troubled more

than 2 seconds.

CHECK 2 32C

6. Trouble in 5V Supply

If 5V supply to DATA DIR is troubled.

CHECK POW5

7. Trouble in Protection

CPU turns off the speaker output.

PROTECT

CHECK E2P I F

5. RS-232C

Panja

ɥ౨ЈƠƨŵ

ီࠝ౨Јᘙᅆŵ

ᡫƴRSCƱƷᡫɧφӳǛኖ ᅺˌ

CHECK 2 32C

6. 5V

ီࠝ౨Јᘙᅆŵ

DATADIR

ƷီࠝǛ౨ЈƠƨŵ

CHECK POW5

7. Protection

Speaker

ӭီࠝ౨Јᘙᅆŵ

ƔǒǛЈщǛഥNJLJƢŵ

PROTECT

11

Page 14

6. UPDATE FIRMWARE

ƷǢȃȗȇȸȈ૾ඥ

6. UPDATE FIRMWARE

Software for CPU and DSP can be updated.

Have update application software. (“UpgradeDSP.exe” and

“H8Download.exe”)

There are two mode of download, regarding to the target of

software as bellow.

Mode 1: Update DSP’s software to Flash-ROM.

This mode is to update the software for DSP.

The target devise is Flash-ROM (IC20) on CUP11762Z

(DSP PCB).

The Unit needs to be set update condition, by three front

keys.

Mode 2: Update CPU’s software to internal Flash-ROM.

This mode is to update the software for DSP.

The target devise is internal fl ash ROM of CPU (IC36) on

CUP11762Z (DSP PCB).

The Unit needs to be set to writing condition, by pushing

internal switch from back-panel.

The following items are required for updating.

RS232C Dsub-9 pin cable (female to female/Straight type)

Windows PC (98, NT, ME, 2000) with RS-232C port.

Update software to CPU.

Update software to DSP.

Use RS232C Dsub-9 pin cable (female to female/Straight

type) to connect PC and the unit.

COM port on PC needs to be set by dialog box for each program. COM port can be set from COM1 to COM5.

CPU ƓǑƼ DSP ǽȕȈǦǧǢƷǢȃȗȇȸȈǛᘍƍLJƢ

ǽȕȈǦǧǢƷǢȃȗȇȸȈƴƸUpgradeDSP.exe Ʊ

H8Download.exe ƕ࣏ᙲưƢŵ

ǢȃȗȇȸȈƴƸഏƷʚƭƷȢȸȉƕƋǓLJƢŵ

Mode 1:DSP ဇ Flash-ROM ƷǢȃȗȇȸȈ

ƜƷȢȸȉƸ

ȉưƢŵ

DSP ƷǽȕȈǦǧǢǛǢȃȗȇȸȈƢǔȢȸ

CUP11762(DSP PCB) ƷؕெɥƴƋǔ Flash-ROM (IC20)

ƷǽȕȈǦǧǢǛǢȃȗȇȸȈƠLJƢŵ

ஜೞ

[PS7500 / PS8500] ƷȕȭȳȈȑȍȫƴƋǔ 3 ƭƷȜ

ǿȳǛƠƯǢȃȗȇȸȈȢȸȉƴƠLJƢŵ

Mode 2:CPU Ʒϋᢿ Flash-ROM ƷǢȃȗȇȸȈ

ƜƷȢȸȉƸ

ȉưƢŵ

CPU ƷǽȕȈǦǧǢǛǢȃȗȇȸȈƢǔȢȸ

CUP11762(DSP PCB) ƷؕெɥƴƋǔ CPU(IC36) Ʒϋᢿ

Flash-ROM ƷǽȕȈǦǧǢǛǢȃȗȇȸȈƠLJƢŵ

[PS7500 / PS8500]

ஜೞ

ƠƯǢȃȗȇȸȈȢȸȉƴƠLJƢŵ

ǢȃȗȇȸȈƴƸɦᚡƷೞ֥ƕ࣏ᙲưƢŵ

ƷȪǢȑȍȫƔǒϋᢿǹǤȃȁǛ

( ࣏ᙲೞ֥ )

RS-232C ǹȈȬȸȈDZȸȖȫ (9Pin ȡǹ -9Pin ȡǹ )

Windows PC Serial Port ˄Ɩ (OS: 98,NT,ME,2000)

CPU ဇǢȃȗȇȸȈǽȕȈǦǧǢ

DSP ဇǢȃȗȇȸȈǽȕȈǦǧǢ

RS-232C DZȸȖȫưஜೞƱዓƢǔ PC Ʒ COM ȝȸȈဪӭ

ǛᚨܭƠƯƘƩƞƍŵ

COM ȝȸȈဪӭƸ COM1 Ɣǒ COM5 LJưᚨܭưƖLJƢŵ

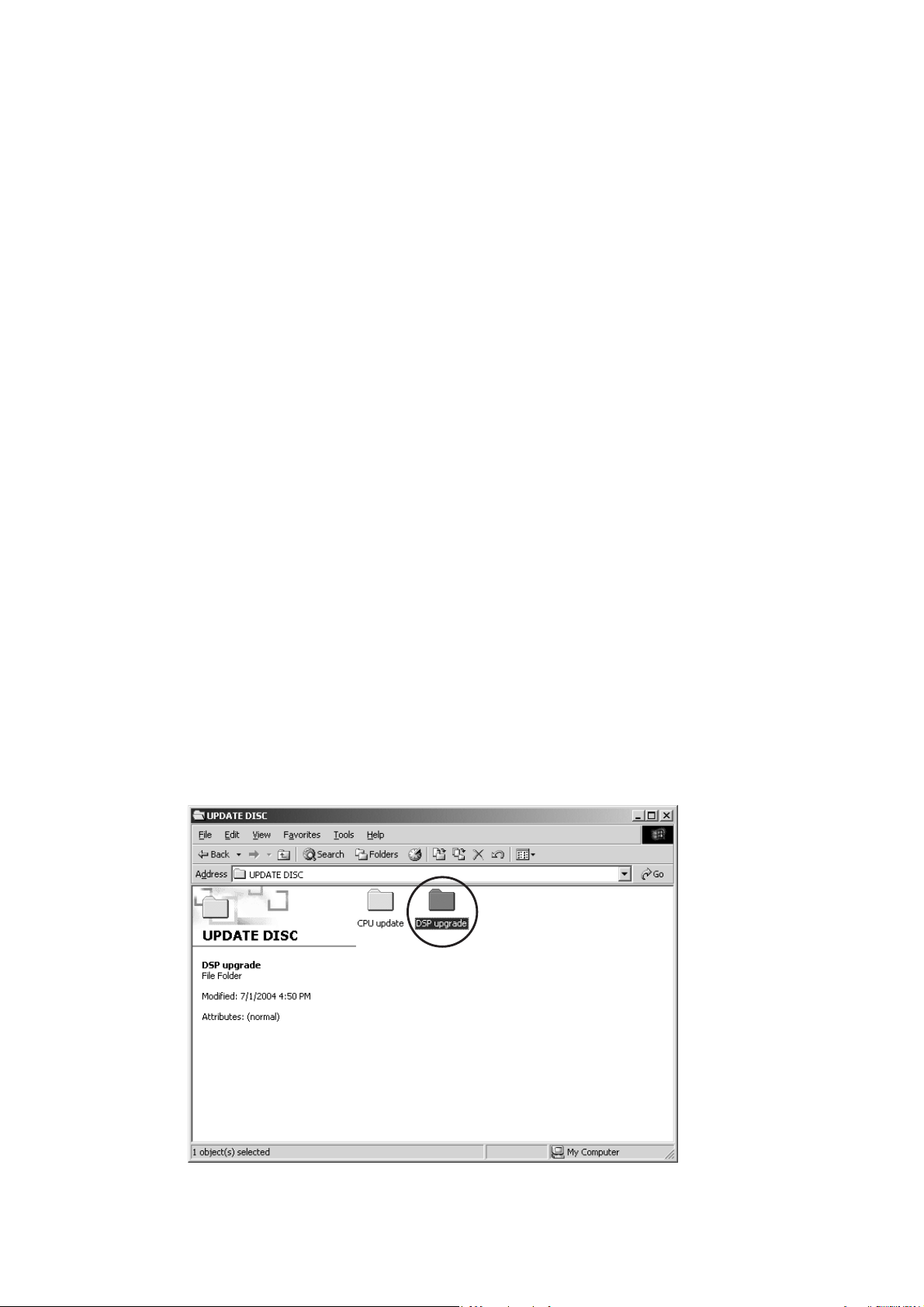

Download Firmware for DSP (Mode 1)

1. Put the “DSP upgrade” folder into anywhere on your PC’

s hard disc.

2. Connect PC and the unit with the RS-232C cable.

DSP

ƷǢȃȗȇȸȈ૾ඥ (Mode 1)

1. "DSP upgrade" ȕǩȫȀǛ PC ƷȏȸȉȇǣǹǯƴdzȔȸ

ƠLJƢŵ

2. ஜೞƱ PC Ǜ RS-232C ưዓƠLJƢŵ

3. Turn on the unit.

3. ஜೞƷᩓเǛλǕLJƢŵ

12

Page 15

4. [SR7500 / SR8500]

දᚡ

Press ENTER, SURROUND MODE and T-MODE

buttons simultaneously more than 5 seconds to turn the

unit into Loading Mode.

[PS7500 / PS8500]

Press ENTER, SURROUND MODE and SLEEP buttons

simultaneously more than 5 seconds to turn the unit into

Loading Mode.

5. “LOADING MODE” will be shown on FLD.

4. ENTER, SURROUND MODE, SLEEP

ƴ

5 ᅺˌɥƠዓƚƯ Loading Mode ƴƠLJƢŵ [PS7500

Ʒ 3 ƭƷȜǿȳǛӷ

/ PS8500]

ȇǣǹȗȬǤƴ "LOADING MODE" ƱᘙᅆƞǕLJƢŵ

5. FL

6. Launch “UpgradeDSP.exe” on PC.

Note: yy_mm_dd is release date of software.

6. PC Ɣǒ "UpgradeDSP.exe" ǛȀȖȫǯȪȃǯƠƯឪѣƠLJ

Ƣŵ

දᚡ : ȕǡǤȫӸƷ yy_mm_dd ƸǽȕȈǦǧǢƷႆᘍଐǛ

ƋǒǘƠLJƢŵ

7. Click Port setting, and select the COM Port No.

7. Port setting ǛǯȪȃǯƠŴCOM ȝȸȈဪӭǛᢠ৸ƠLJƢŵ

13

Page 16

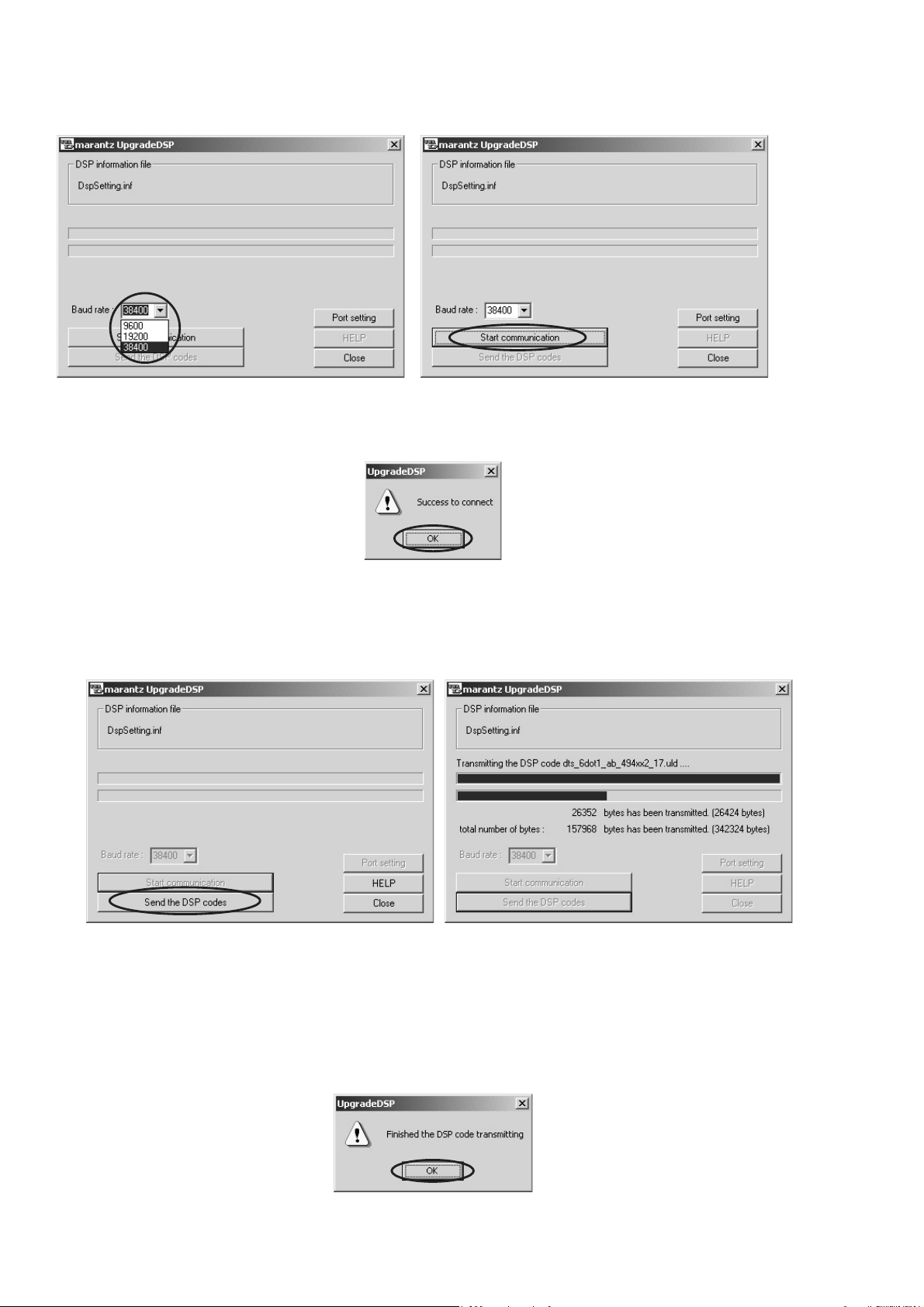

8. Set the Baud rate to 38400 then click Start communi-

cation button.

8. Baud rate Ǜ 38400 ƴᚨܭƠŴStart communication Ǜǯ

ȪȃǯƠLJƢŵ

9. If the connection is made successfully, a dialog box saying “Success to connect” appears and “CONNECTED” is

displayed on FLD.

10. Click Send the DSP codes button on the dialog box.

Progress status of updating will be shown on PC and

LOADING is displayed on FLD.

9. ᡫዓƴыƢǔƱɦᚡƷȀǤǢȭǰȜȃǯǹƕᘙᅆƞ

ǕŴ

FL ȇǣǹȗȬǤƴƸ "CONNECTED" ƕᘙᅆƞǕLJƢŵ

10. Send the DSP codes ǛǯȪȃǯƠLJƢŵǢȃȗȇȸ

ȈƷǹȆȸǿǹȐȸƕᘙᅆƞǕŴ

FL ȇǣǹȗȬǤƴƸ

"LOADING" ƕᘙᅆƞǕLJƢŵ

11. If updating is completed successfully, “COMPLETED” is

displayed on FLD. And a dialog box saying “Finished the

DSP code transmitting” appears.

12. Click OK and then Application is closed automatically.

13. Turn off the unit.

14

11. ǢȃȗȇȸȈƕыƢǔƱFL ȇǣǹȗȬǤƴ

"COMPLETED" ƱᘙᅆƞǕLJƢŵӷƴ "Finished the

DSP code transmitting" ƷȀǤǢȭǰȜȃǯǹƕᘙᅆƞǕ

LJƢŵ

12. OK ǛǯȪȃǯƢǔƱᐯѣႎƴǢȗȪDZȸǷȧȳƕơLJ

Ƣŵ

13. ஜೞƷᩓเǛЏǓLJƢŵ

Page 17

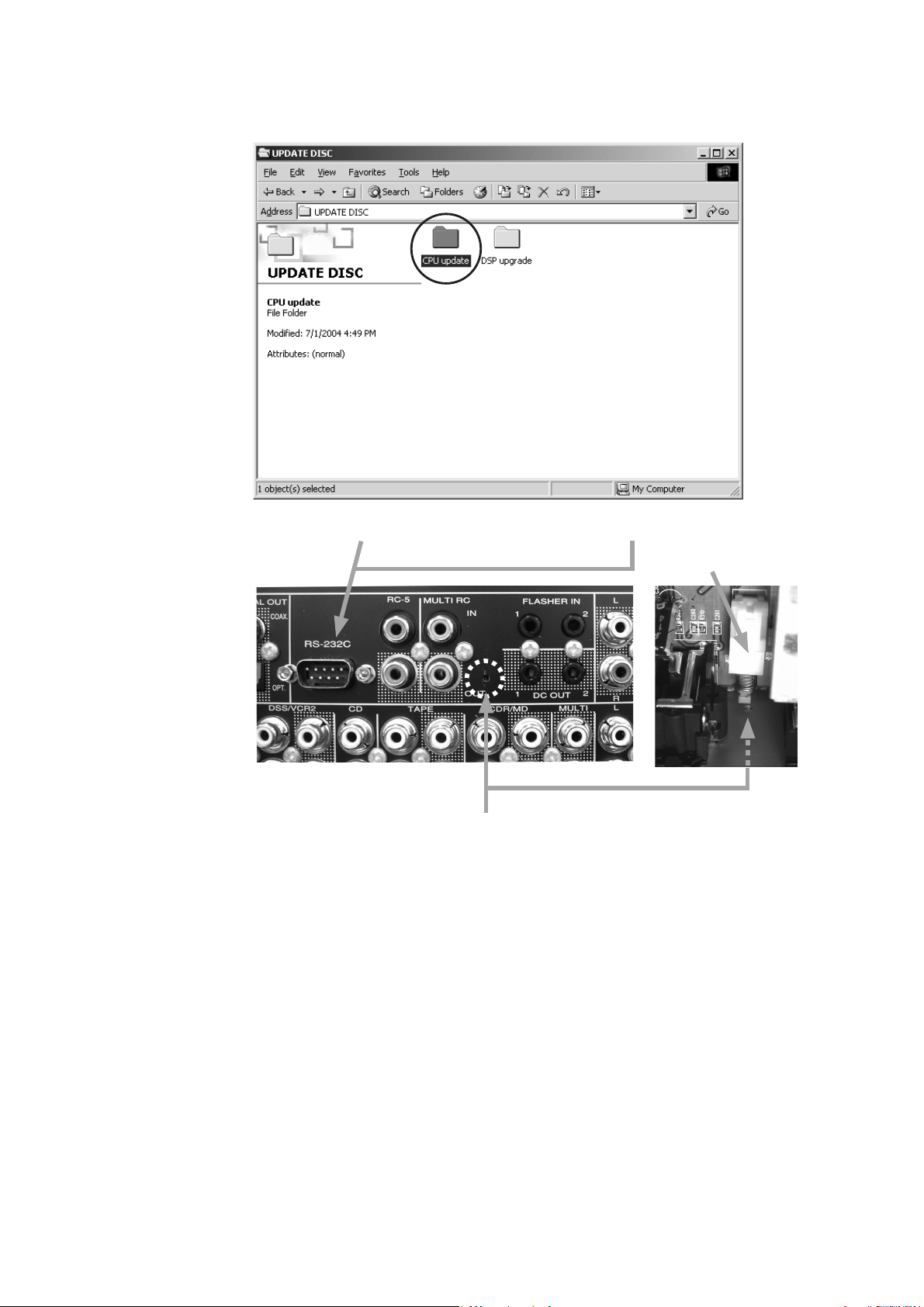

Download Firmware for CPU (Mode 2)

ƷǢȃȗȇȸȈ૾ඥ

දᚡ

1. Put the “CPU update” folder into anywhere on your PC’s

hard disc.

ƷǢȃȗȇȸȈ૾ඥ (Mode 2)

CPU

1. "CPU update" ȕǩȫȀǛ PC ƷȏȸȉȇǣǹǯƴdzȔȸƠ

LJƢŵ

2. Connect PC and the unit with the RS-232C cable.

Hole of rear panel

ȪǢȑȍȫƴƋǔᆭ

3. Insert a thin rot to the hole and push the switch (SW10)

inside to turn on the switch.

4. Turn on the power of the unit.

Note: When the unit is into boot mode, stand-by LED is

not lights up.

2. ஜೞƱ PC Ǜ RS-232C ưዓƠLJƢŵ

SW10

3. ኬƍొǛƍஜೞƷȪǢȑȍȫƴƋǔᆭƔǒǹǤȃȁ

(SW10) ǛƠLJƢŵ

4. ஜೞƷᩓเǛλǕLJƢŵ

දᚡ : ஜೞƸȖȸȈȢȸȉƴƳǓŴStand-by LED Ƹໜ໊Ơ

LJƤǜŵ

15

Page 18

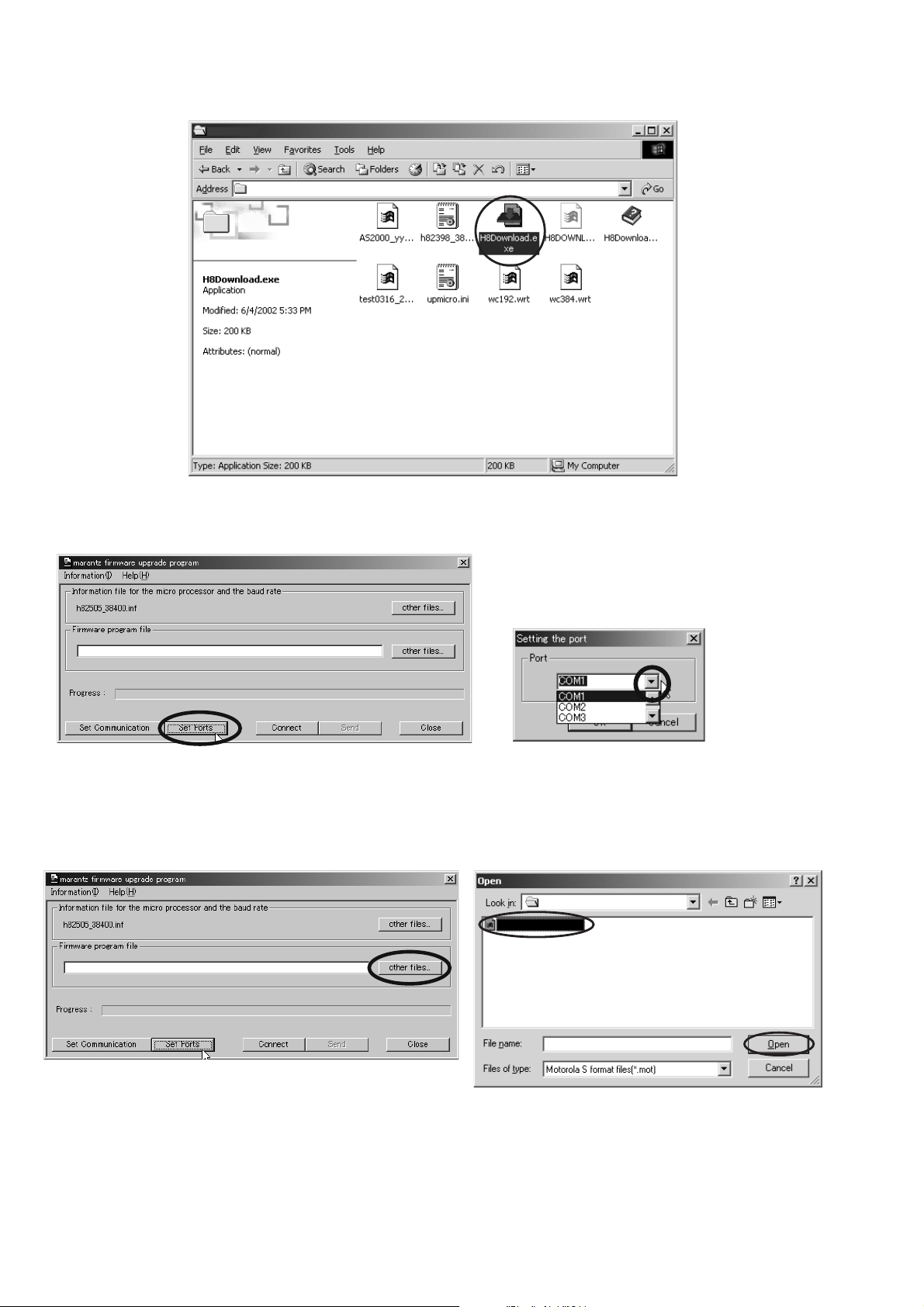

5. Launch "H8Download.exe" on PC.

H8FW2505

H8FW2505

H8FW2505

5. PC Ɣǒ "H8Download.exe" ǛȀȖȫǯȪȃǯƠƯឪѣƠLJ

Ƣŵ

6. Click Set Ports, and select the COM Port No.

7. Click other fi les... button in the dialog box to specify the

fi le (SR8500_yymmdd.mot) to be uploading. yymmdd in

fi lename is release date of software.

6. Set Ports ǛǯȪȃǯƠŴCOM ȝȸȈဪӭǛᢠ৸ƠLJƢŵ

7. other fi les… ǛǯȪȃǯƠƯŴǢȃȗȇȸȈȕǡǤȫ

(SR8500_yymmdd.mot) Ǜᢠ৸ƠƖLJƢŵ

H8FW2505

SR8500_yymmdd.mot

16

SR8500_yymmdd.mot

Page 19

8. Click Connect button. If the connection with the H8 µ-P

is successfully made, a dialogue box saying "Success to

the H8 micro processor connection" appears. (If the connection fails, error message will appear.)

8. Connect ǛǯȪȃǯƠLJƢŵH8 u-P ƱᡫዓƴыƢǔ

Ʊ

"Success to the H8 micro processor connection" ƷȀǤ

ǢȭǰƕᘙᅆƞǕLJƢŵ ᡫƴڂƢǔƱǨȩȸȡȃǻȸ

ǸƕᘙᅆƞǕLJƢŵ

9. Click Send button to start update.

h82505_38400.inf

10. If the fi rmware is updated successfully, a dialog box saying "Finished the fi rmware program sending” appears.

9. Send ǛǯȪȃǯƠǢȃȗȇȸȈǛڼƠLJƢŵ

10. ǽȕȈǦǧǢƷǢȃȗȇȸȈƕыƢǔƱŴ"Finished the

fi rmware program sending" ƷȀǤǢȭǰȜȃǯǹƕᘙᅆ

ƞǕLJƢŵ

17

Page 20

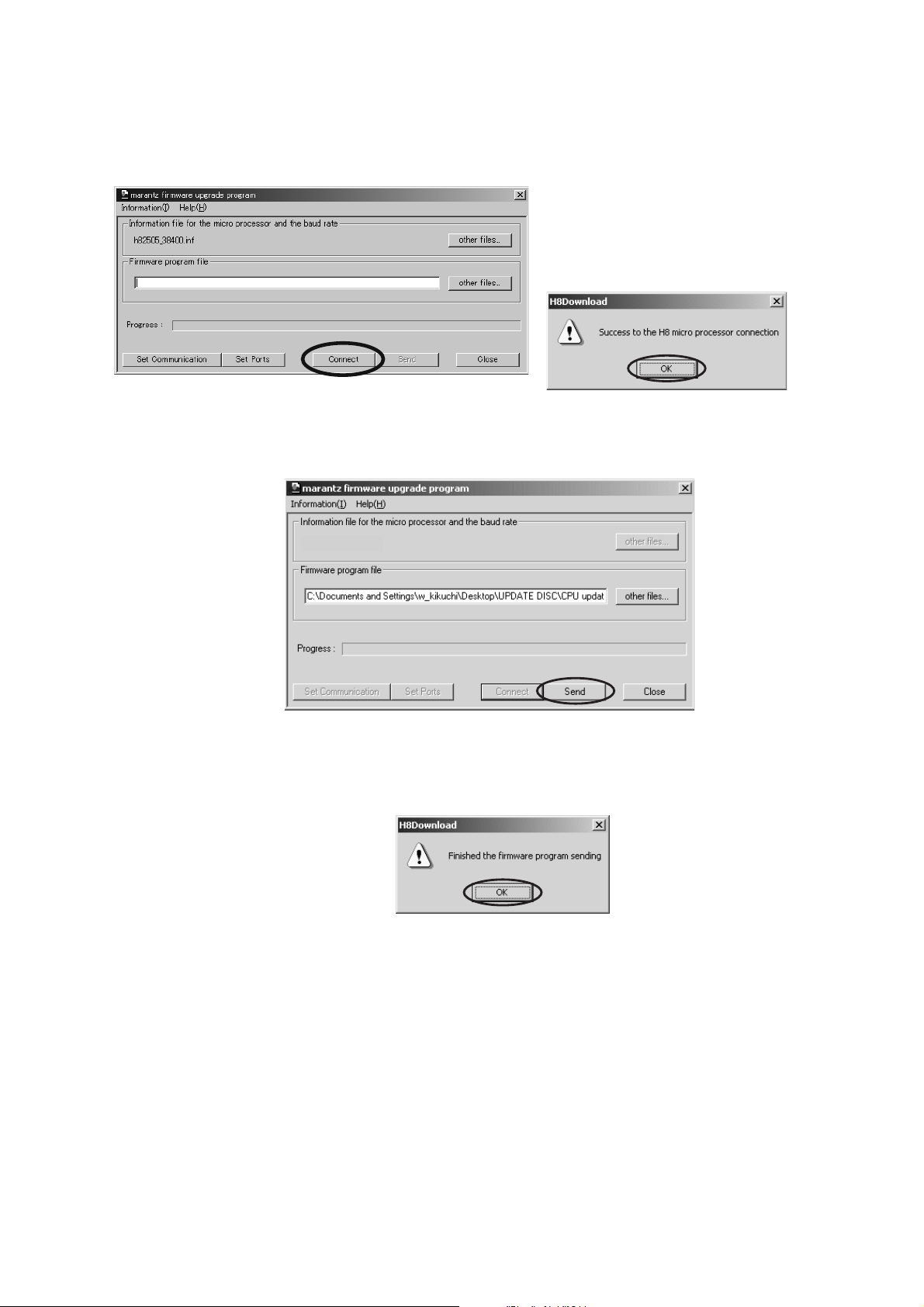

11. Click Close button to close the application.

ȐȸǸȧȳƷᄩᛐ

h82505_38400.inf

11. Close ǛǯȪȃǯƠƯǢȗȪDZȸǷȧȳǛơLJƢŵ

12. Disconnect Mains power cord.

13. Turn off the internal switch that has been turned on at

step 3.

14. Turn on the unit.

Firmware Version Check

To check the versions of the fi rmware, see "Microprocessor

(CPU), DSP Version and FLD Segment Check Mode" in

"SERVICE MODE" section.

12. ஜೞƷᩓเǛЏǓLJƢŵ

13. 3 ƷǹǤȃȁᲢSW10ᲣǛƠƯȖȸȈȢȸȉǛᚐᨊƠ

LJƢŵ

14. ᩓเǛλǕLJƢŵ

ȐȸǸȧȳƷᄩᛐ

ǽȕȈǦǧǢƷȐȸǸȧȳǛᄩᛐƠLJƢŵᄩᛐ૾ඥƸ

"SERVICE MODE" ϋƷ"Microprocessor (CPU), DSP

Version and FLD Segment Check Mode"ǛӋༀƠƯƘƩƞƍŵ

18

Page 21

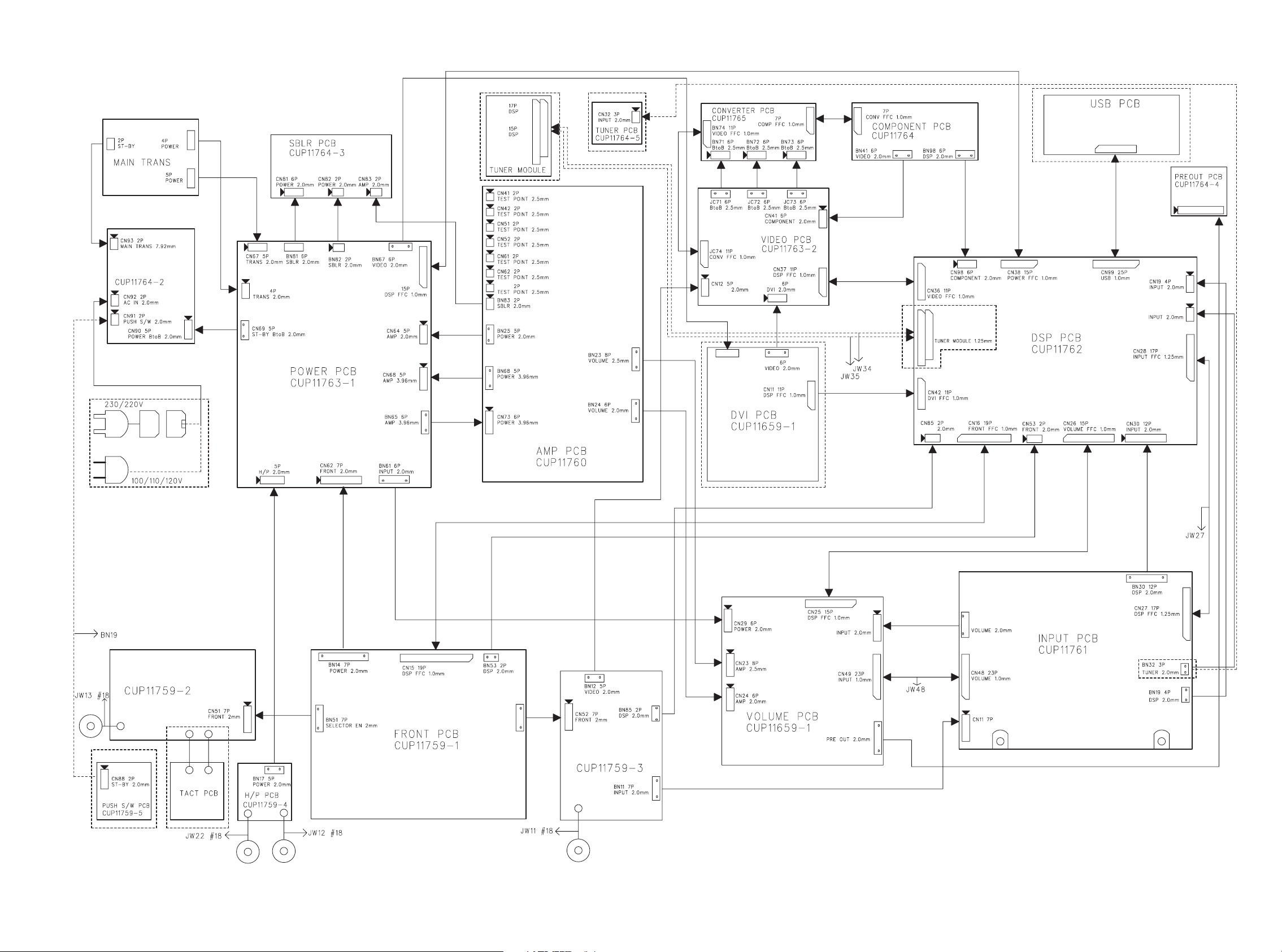

7. WIRING DIAGRAM

SR7500/SR8500 Only PS7500/PS8500 Only

STANDBY PCB

CN66

CN65

CN71

AUX1

CN12 6P

POWER 2.0mm

CN71

CN21

BN13

CN42

AUX1

CN34 15P/P17

CN46 4P

BN22 15P

VOLUME 2.0mm

SELECTOR PCB

CN63

BN52 7P

AUX1 2mm

AUX1 PCB

SR8500/PS8500 Only

CN47 6P

CN22 15P

BN47 6P

AUX1 2.0mm

A, F, K, L, N only

U only

19 20

Page 22

8. BLOCK DIAGRAM

SR7500/SR8500 only

USB MODULE

SR8500/PS8500 only

DVI PART

SR8500/PS8500 only

2221

Page 23

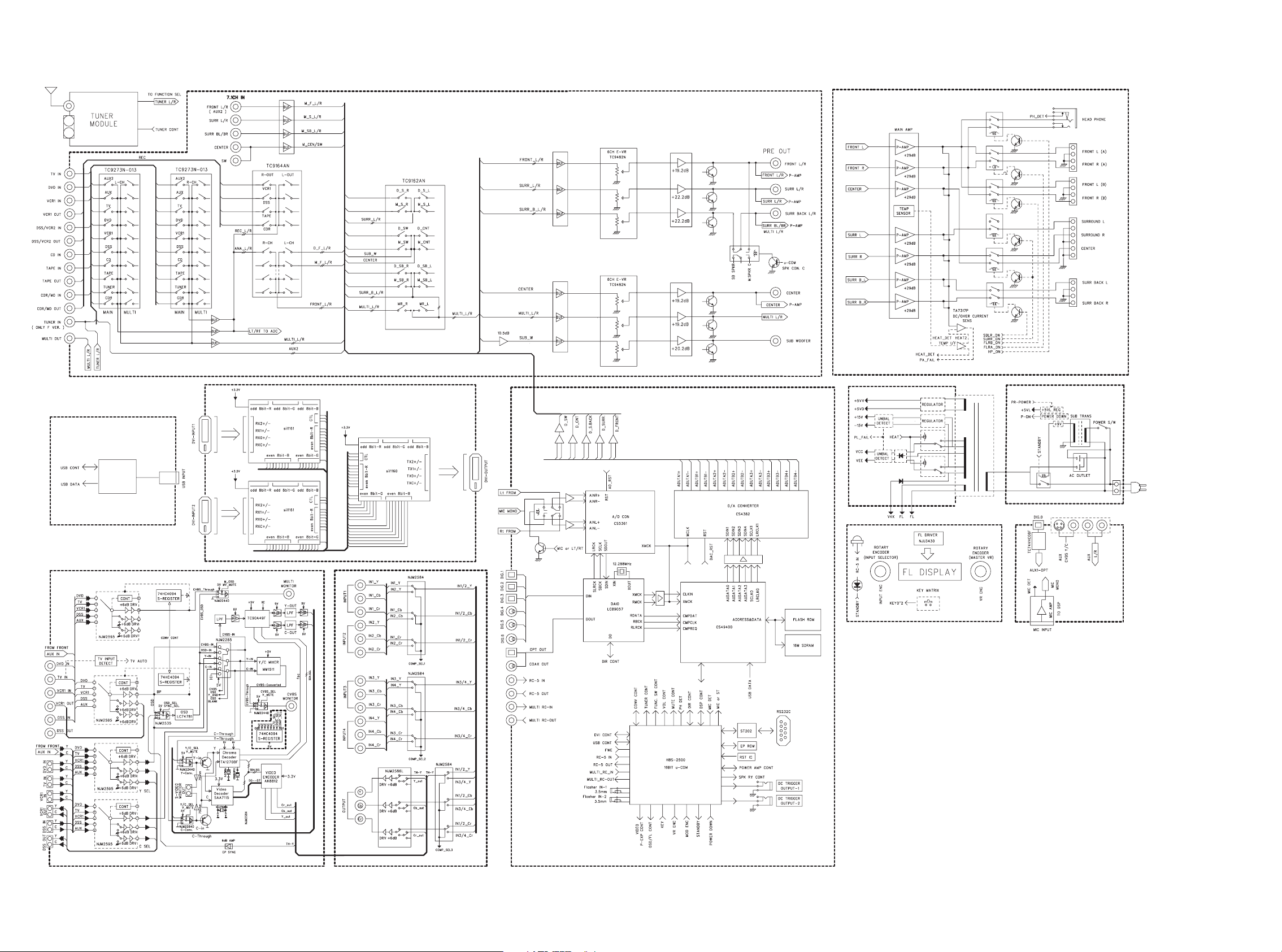

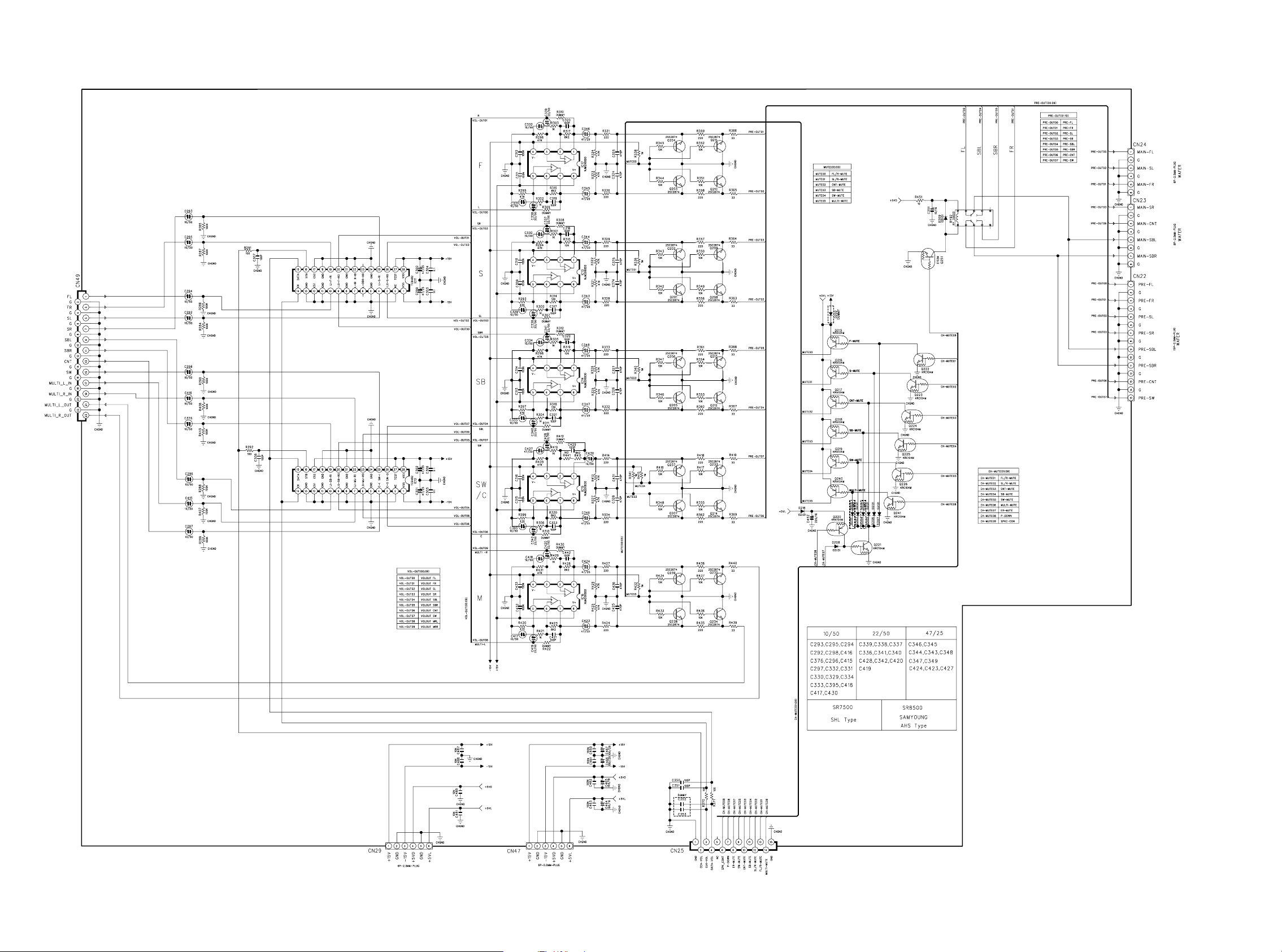

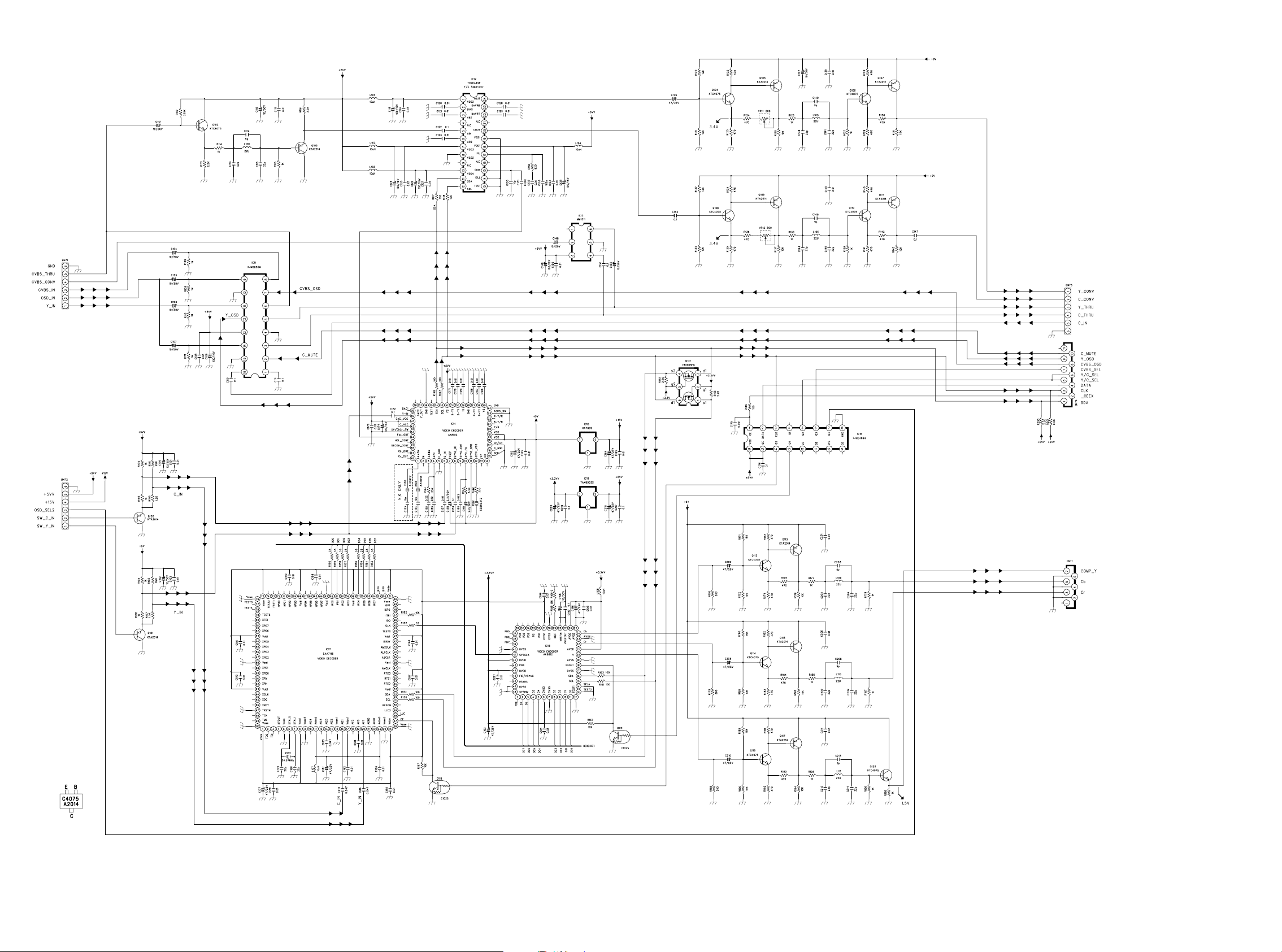

9. SCHEMATIC DIAGRAM

INPUT PCB

FROM TUNER PCB (F VERSION)

FROM DSP PCB (OTHER VERSION)

FROM AUX1 PCB FROM DSP PCB

CN11

FROM DSP PCB

FROM DSP PCB

FROM VOLUME PCB

23 24

FROM VOLUME PCB

Page 24

TO FRONT PCB

DSP PCB - 1/2

L102

HM102T

TO COMPONENT PCB

TO POWER PCBTO VOLUME PCBTO VIDEO PCB

R380

10k

TO TUNER MODULE

TO INPUT PCB

C325

C323

C322

0.1

0.1

0.1

R360

C324

10

0.1

TO INPUT PCBTO DVI PCB

2625

Page 25

DSP PCB - 2/2

TO AUX1 PCB

TO USB PCB

TO INPUT PCB

TO FRONT PCBTO INPUT PCB

27 28

Page 26

FROM INPUT PCB

VOLUME PCB

FROM PREOUT PCB FROM AMP PCB FROM AMP PCB

TO POWER PCB

FROM INPUT PCB

FROM DSP PCB

3029

Page 27

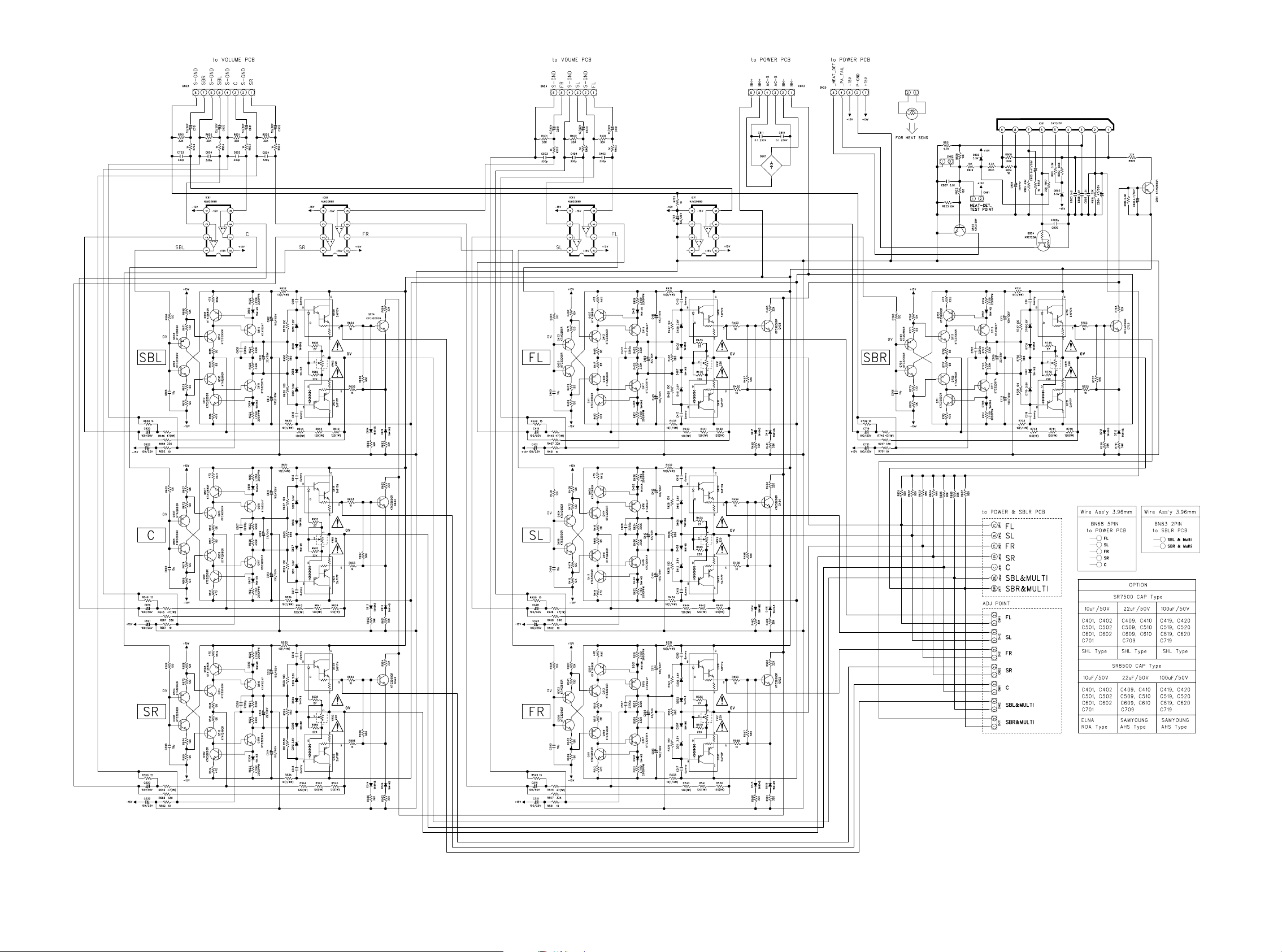

AMP PCB

CN82

31 32

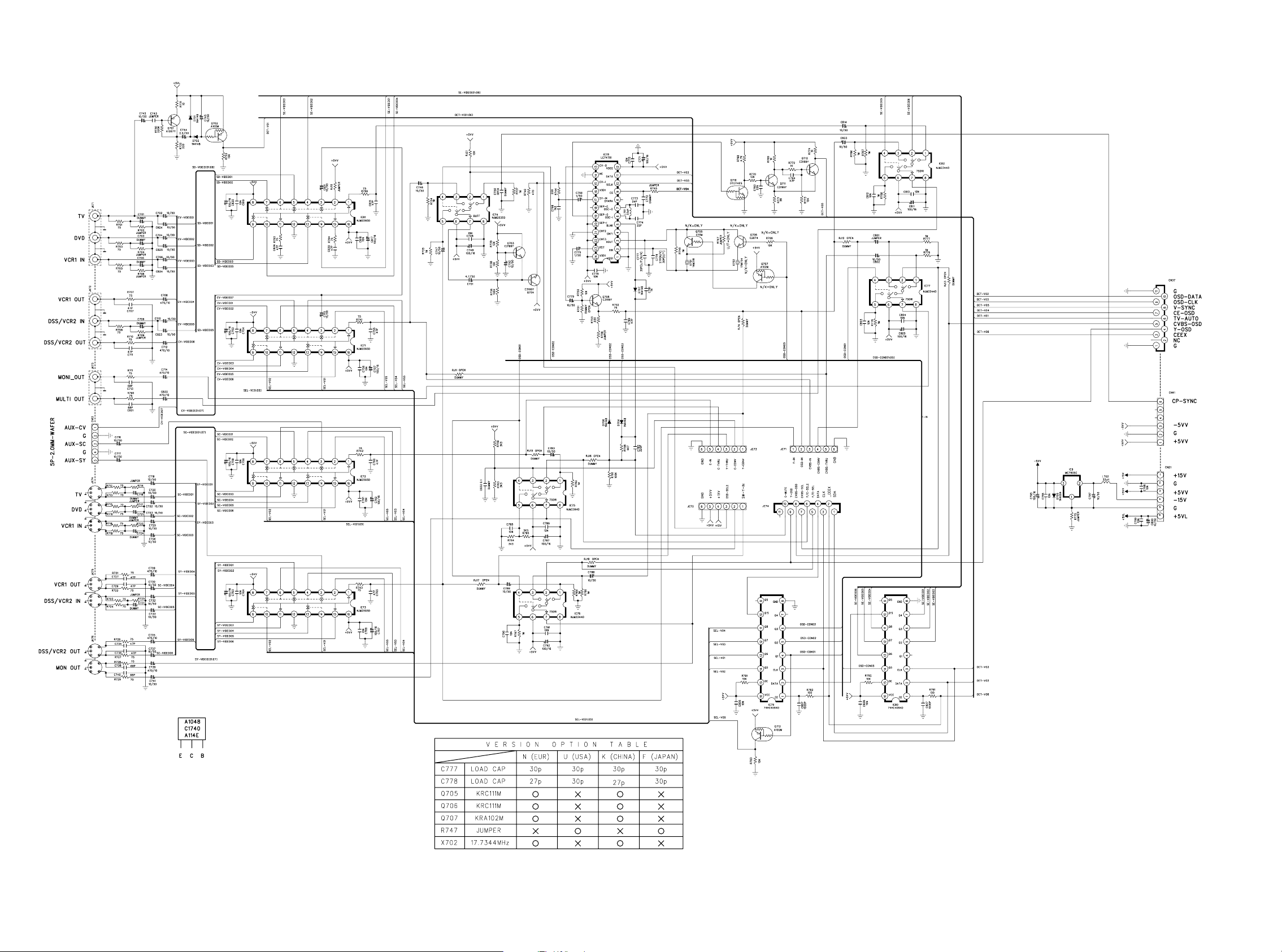

Page 28

VIDEO PCB

TO DSP PCB

TO

COMPONENT

PCB

FROM AUX1 PCB

TO CONVERTER

PCB

TO CONVERTER

PCB

SW-C-IN

TO CONVERTER PCB

TO CONVERTER PCB

TO

POWER PCB

3433

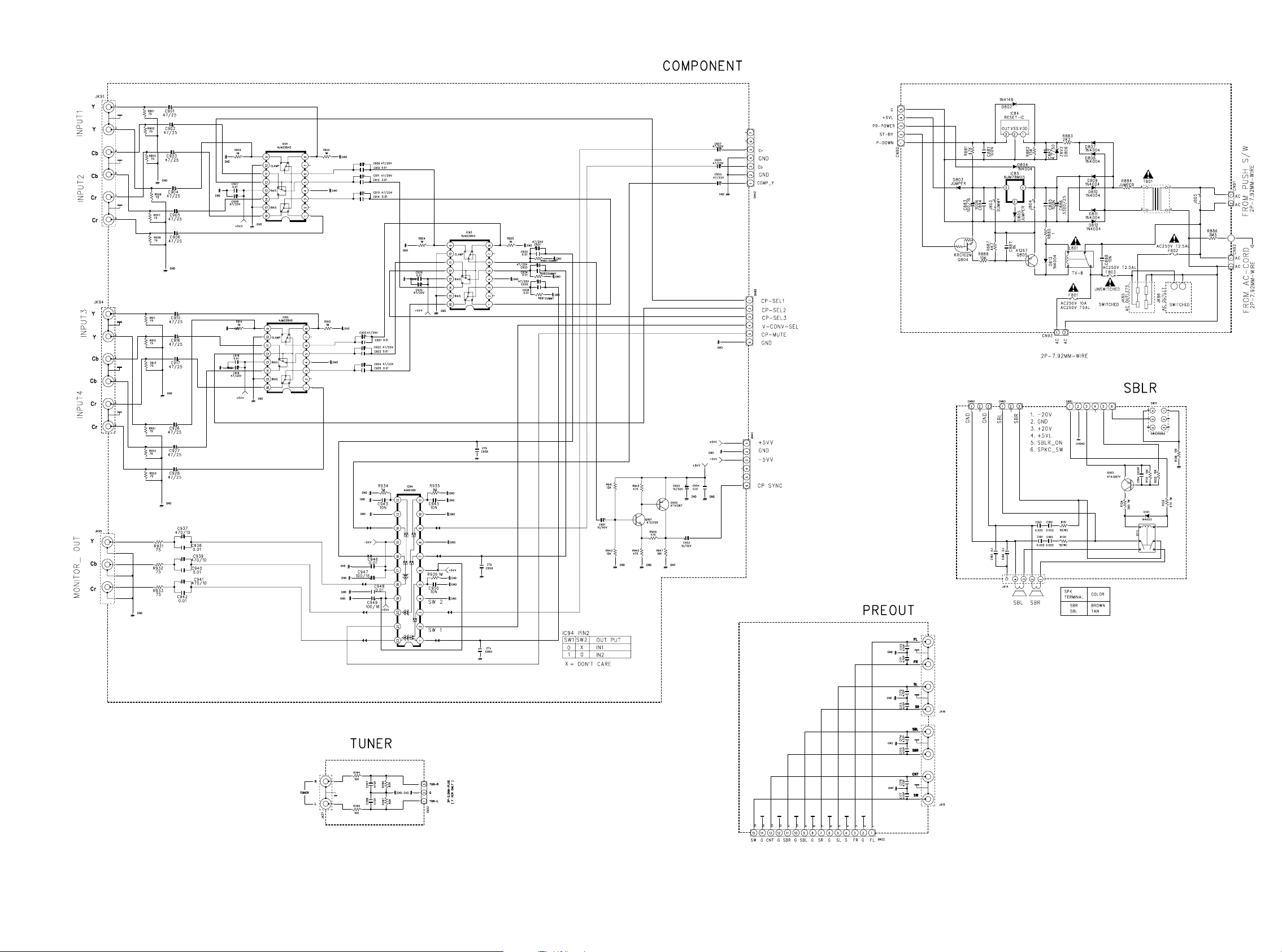

Page 29

COMPONENT PCB

STANDBY

STANDBY PCB

TO POWER PCB

CN71

FROM CONVERTER PCB

FROM DSP PCB (2/2)

FROM VIDEO PCB

PRE OUT PCB

FROM MAIN TRANS

SBLR PCB

TO POWER PCBTO AMP PCB

TUNER PCB

FROM INPUT PCB

PS7500/PS8500 Only

FROM VOLUME PCB

35 36

Page 30

VIDEO CONVERTER PCB

TO VIDEO PCB

TO VIDEO PCB

TO VIDEO PCB

TO VIDEO PCB

TO COMPONENT PCB

3837

Page 31

JK11

DATA2-

DATA2+

GND

DATA4-

DATA4+

DDC_CLK

DDC_DATA

NC

DATA1-

DATA1+

GND

DATA3-

DATA3+

+5V

DVI-INPUT1

GND

HPD

DATA0-

DATA0+

GND

DATA5-

DATA5+

GND

CLK+

CLK-

DVI PCB

1

2

3

4

5

DDC_CLK_1

6

DDC_DATA_1

7

8

9

10

11

12

13

+5V_1

14

15

HPD_1

16

17

18

19

20

21

22

23

24

GND

GND

C111 0.1u

GND

RX1-DATA

+3.3VDI

L101 10uH

C109 0.1u

GND GND

C112 0.1u

GND

C110 47u/16

0.1uC113

GND

C108 0.1u

R106 390

R107 10K

GNDGND

GNDGNDGNDGNDGNDGND

R108 10K

GND

C107

47u/16

76

OGND

77

QO23

78

OVCC

79

AGND

80

RX2+

81

RX2-

82

AVCC

83

AGND

84

AVCC

85

RX1+

86

RX1-

87

AGND

88

AVCC

89

AGND

90

RX0+

91

RX0-

92

AGND

93

RXC+

94

RXC-

95

AVCC

96

EXT_RES

97

PVCC

98

PGND

99

MODE

100

SCL

HS_DJTR2PD3SDA/ST4PIXS5GND6VCC7I2C_MODE#(STAG_OUT#)

1

R101 0

GND

R102 10K

C106

0.1u

GND

67

68

69

VCC

GND

QO1670QO1771QO1872QO1973QO2074QO2175QO22

IC11

SiI1161

EVEN 8Bit B

SCDT9PDO#10QE011QE112QE213QE314QE415QE516QE617QE718OVCC19OGND20QE821QE922QE1023QE1124QE1225QE13

8

GND GND

0

10K

R104

R105

R103 10K

GND

RX_PD_1

8642

22

RN11

13 75

C101 0.1u

B[0]

B[1]

B[2]

B[3]

CN11

11

DVI_CONT2

10

DVI_CONT1

9

DVI_RX_PD2

8

DVI_RX_PD1

7

GND

FPGA_RST

6

DVI_TX_PD

5

DVI_+5V_2

4

DVI_+5V_1

3

2

GND

1

TO DSP PCB

R185

R184

100

C105

0.1u

GNDGND

GND

51

57

58

59

61

QO252QO353QO454QO555QO656QO7

QO860QO9

QO1062QO1163QO1264QO1365QO1466QO15

OVCC

OGND

8642

13 75

B[5]

B[6]

B[7]

B[4]

ODD 8Bit BODD 8Bit GODD 8Bit R

EVEN 8Bit G

22

RN12

EVEN 8Bit R

GND

SIL1161-1

QO1

QO0

HSYNC

VSYNC

DE

OGND

ODCK

OVCC

CTL3

CTL2

CTL1

GND

VCC

QE23

QE22

QE21

QE20

QE19

QE18

QE17

QE16

OVCC

OGND

QE15

QE14

C102 0.1u

C104 0.1u

GND

50

RN18

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

GND GND GND

GND

22

1375

13

75

RN16 22

1375

13

75

RN15

22

0.1u

C103

RN14

22

13

75

1375

RN13

22

8642

RN17

22

8642

8642

8642

8642

8642

C[6]

C[5]

C[4]

C[3]

C[2]

C[1]

C[0]

R[7]

R[6]

R[5]

R[4]

R[3]

R[2]

R[1]

R[0]

G[7]

G[6]

G[5]

G[4]

G[3]

G[2]

G[1]

G[0]

RX_PD_2

RX_PD_1

DDC_CLK_1

DDC_CLK_2

DDC_DATA_2

DDC_DATA_1

+5V_2

+5V_1

HPD_2

HPD_1

DOC_CLK

DOC_DATA

+5V

HPD

GND

IC18

74VHC08TTR

RY11

678910

RY12

678910

8 9 10 11 12 13 14

GND

12345

GND

12345

GND

D101

D102

Q101

1N4148

1N4148

A102S

1234567

+3.3VDI

+5VV

C199

0.1u

GND

RY13

RY14

12345

678910

DOC_DATA DOC_CLK

GND

12345

678910

HPD +5V

GND

Q103

D103

A102S

D104

1N4148

1N4148

+5VV

100

JK12

DATA2-

DATA2+

GND

DATA4-

DATA4+

DDC_CLK

DDC_DATA

NC

DATA1-

DATA1+

GND

DATA3-

DATA3+

+5V

DVI-INPUT2

GND

HPD

DATA0-

DATA0+

GND

DATA5-

DATA5+

GND

CLK+

CLK-

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

GND

DDC_CLK_2

DDC_DATA_2

+5V_2

HPD_2

GND

C131 0.1u

GND

+3.3VDI

10uH

L121

C129 0.1u

GND

C132 0.1u

GND

GND

0.1u

C133

GND

47u/16

C130

C128 0.1u

GND

R126 390

R127 10K

GND

GND

GND

GND

GND

GND

GND

10K

R128

GND

100

C127

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

47u/16

OGND

QO23

OVCC

AGND

RX2+

RX2AVCC

AGND

AVCC

RX1+

RX1AGND

AVCC

AGND

RX0+

RX0AGND

RXC+

RXCAVCC

EXT_RES

PVCC

PGND

MODE

SCL

GND

75

QO22

HS_DJTR

1

2

R121 0

R122 10K

RX_PD_2

GND

67

68

69

71

GND

QO1670QO17

QO1872QO1973QO2074QO21

VCC7I2C_MODE#(STAG_OUT#)

SCDT9PDO#10QE011QE1

PD3SDA/ST4PIXS5GND

6

8

GND

10K

R124

R125

R123 10K

0.1u

22

RN21

C121

GND

C126

0.1u

GND

65

VCC

QO1466QO15

ODD 8Bit G

IC12

SiI1161

EVEN 8Bit B

QE213QE314QE415QE516QE617QE718OVCC19OGND

12

0

8642

13 75

B[3]

B[2]

B[1]

B[0]

Q102

C102S

GND

64

DIO965DIO8

ODD 8Bit G

IC16

B[3]

B[4]

B[5]

GND

C188 0.1u

GNDGND

56

57

58

VCC

GND

DIO1559DIO1460DIO1361DIO1262DIO1163DIO10

ODD 8Bit R

GND

GND

R181 10K

C182 0.1u

GND

0.1u

C180

R182 0

GND

B[0]

B[1]

B[2]

GND

+3.3VDI

C125

0.1u

GND

GND

57

58

51

52

56

59

61

QO353QO454QO555QO6

QO2

QO7

QO860QO9

QO1062QO1163QO1264QO13

OVCC

OGND

GND

8642

13 75

B[7]

B[6]

B[5]

B[4]

ODD 8Bit BODD 8Bit R

EVEN 8Bit G

QE821QE922QE1023QE1124QE1225QE13

20

22

RN22

EVEN 8Bit R

GND

SIL1161-2

QO1

QO0

HSYNC

VSYNC

DE

OGND

ODCK

OVCC

CTL3

CTL2

CTL1

GND

VCC

QE23

QE22

QE21

QE20

QE19

QE18

QE17

QE16

OVCC

OGND

QE15

QE14

0.1u

C122

0.1u

C124

GND

50

RN28

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

GND

GND

GND

GND

22

1

3

75

13

75

RN26 22

1375

1375

RN25

22

0.1u

C123

RN24

22

1375

13

75

RN23

22

8642

RN27

22

8642

8642

8642

8642

8642

C[6]

C[5]

C[4]

C[3]

C[2]

C[1]

C[0]

R[7]

R[6]

R[5]

R[4]

R[3]

R[2]

R[1]

R[0]

G[7]

G[6]

G[5]

G[4]

G[3]

G[2]

G[1]

G[0]

L182

10uH

0.1u

C191

C190

47u/16

GND

GND

C194

76

HSYNC

77

VSYNC

78

DE

79

GND

80

GNDGND GND

IDCK

C192

81

IVCC

0.1u

82

CTL3

83

CTL2

84

CTL1

85

PVCC2

86

C193

0.1u

0.1u

PGND2

87

RSVD

88

VCC

89

GND

90

DIE23

91

DIE22

92

DIE21

93

DIE20

94

DIE19

95

DIE18

96

DIE17

97

DIE16

98

IVCC

99

DIE15

EVEN 8Bit G

100

DIE14

G[6]

G[7]

C[6]

C[5]

C[4]

C[3]

GND

C[2]

C[1]

C[0]

GND

R[7]

R[6]

R[5]

R[4]

R[3]

R[2]

R[1]

R[0]

GND

GND

C189 0.1u

66

67

68

NCC

GND

DIO769DIO670DIO571DIO472DIO373DIO274DIO175DIO0

ODD 8Bit B

EVEN 8Bit R

DIE132DIE123DIE114DIE105DIE96DIE87GND8VCC9DIE710DIE611DIE512DIE413DIE314DIE215DIE116DIE017IVCC18PVCC119PGND120RSVD21RSVD22RSVD23RSVD24EDGE25PIXS

1

G[4]

G[5]

SiI160

EVEN 8Bit B

GND GND

GND

C181 0.1u

G[0]

G[1]

G[2]

G[3]

B[6]

B[7]

51

DIO2052DIO1953DIO1854DIO1755DIO16

DIO21

DIO22

DIO23

AGND

TX2+

TX2AVCC

TX1+

TX1AGND

TX0+

TX0AVCC

AGND

AVCC

TXC+

TXCAGND

EXT_SWING

GND

VCC

RSVD

RSVD

RSVD

C187

GNDGND

PD

Q104

C102S

GND

+3.3VDI

L181

10uH

0.1u

C186

47u/16

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

C184 0.1u

R183 510

GND

GND GND GND GND

C183 0.1u

C185

0.1u

GND

GND

GND

GND

JK13

1

DATA2-

2

DATA2+

3

GND

4

DATA4-

5

DATA4+

6

DDC_CLK

7

DDC_DATA

8

NC

9

DATA1-

10

DATA1+

11

GND

12

DATA3-

13

DATA3+

14

+5V

15

GND

16

HPD

17

DATA0-

18

DATA0+

19

GND

20

DATA5-

21

DATA5+

22

GND

23

CLK+

24

CLK-

DVI-OUTPUT

+3.3VDI +5VV

IC17

KIA278R33

1

2

IN

OUT

GND

CTL

3

C198

4

10k

0.1u

C197

47/16

GND

R191

C196

0.1u

C195

47/16

GNDGNDGNDGND

12345

BN13

-15V

GND

+15V

+5VV

TO VIDEO PCB

6

GND

+5VL

+5VL

FROM POWER PCB

GND GNDGND GND

CN12

6

GND

12345

-15V

GND

+15V

+5VV

39 40

Page 32

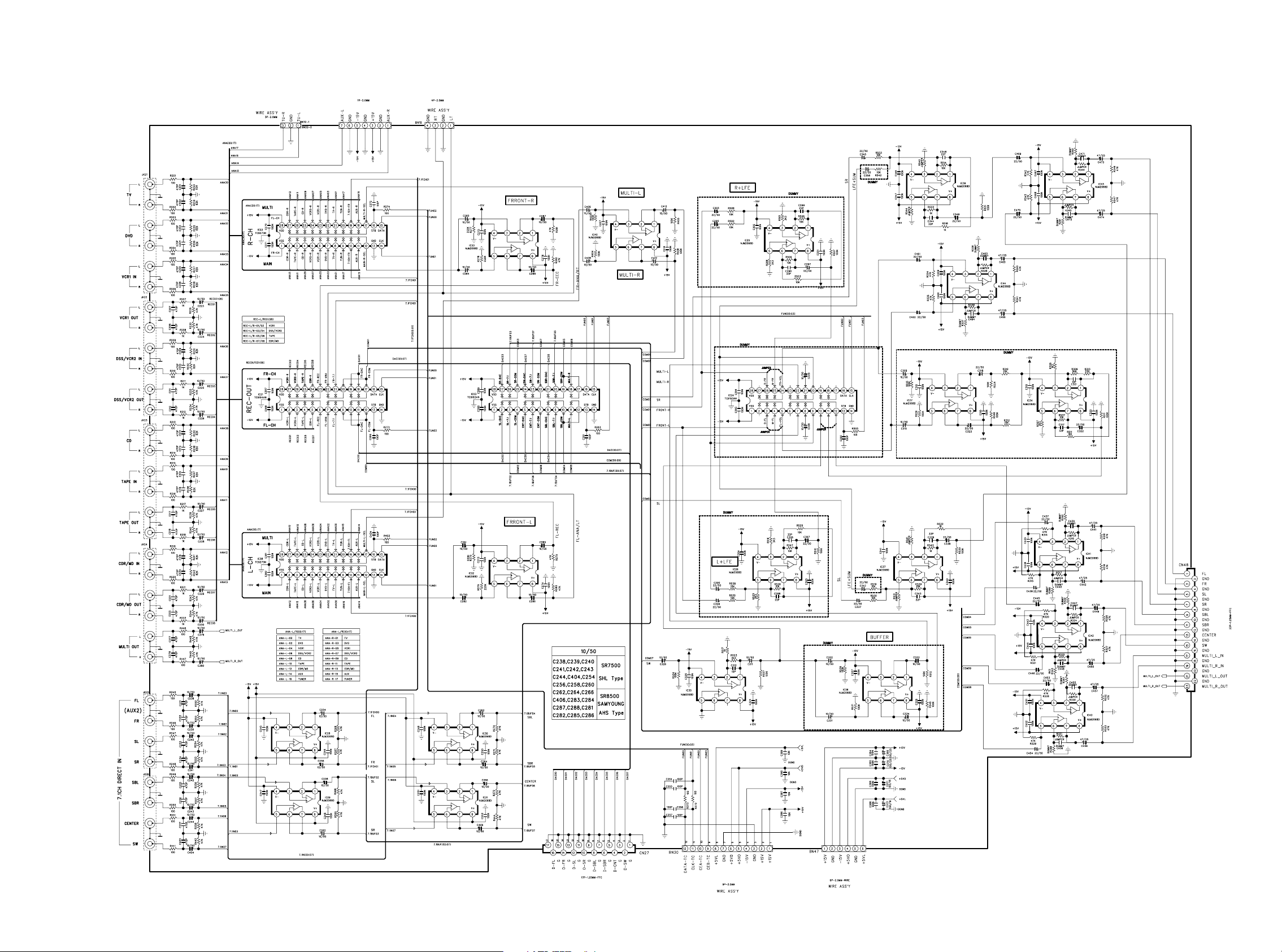

SELECTOR PCB

U VERSION ONLY

FRONT PCB

FROM FRONT PCB

FROM SELECTER PCB

FROM POWER PCB

FROM DSP PCB

FROM AUX1 PCB

AUX1 PCB

FROM FRONT PCB

TO DSP PCB

AUX1

FROM VIDEO PCB

H/P

PUSH S/W

POWER ON/OFF

H/P PCB

A, K, L, F, N VERSION ONLY

PUSH PCB

TO DSP PCB

FROM POWER PCB

PCB

STANDBY

FROM

4241

Page 33

POWER PCB

to

STANDBY

PCB

43 44

Page 34

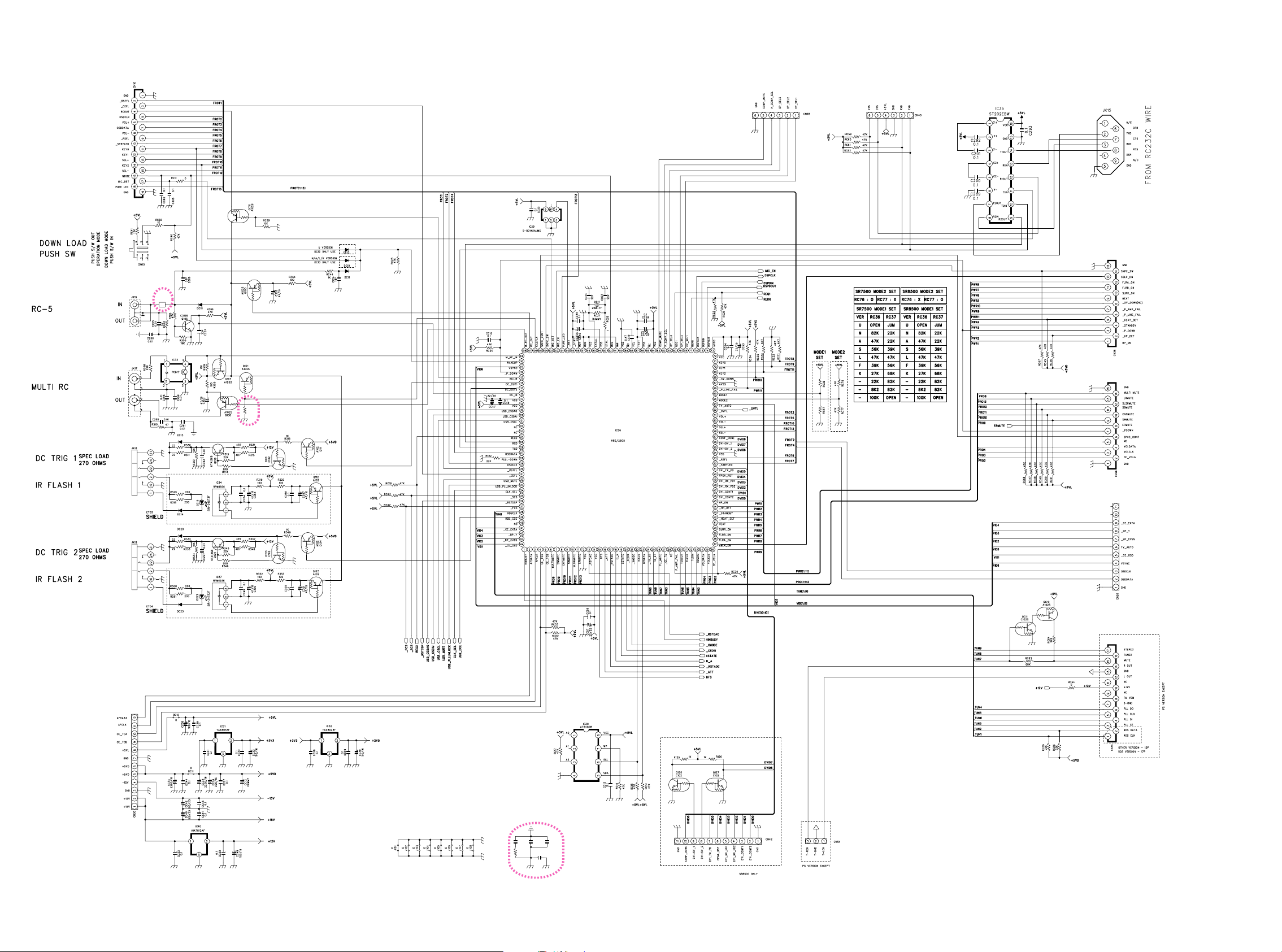

10. PARTS LOCATION

INPUT PCB

IC38

IC33

IC21

IC32

IC22

IC30IC28

IC31IC29

IC40

IC23

IC25

IC24

IC26 IC37

IC35

IC36

IC39

IC34IC27

IC43

IC42

IC41

IC45

IC44

4645

Page 35

Q719 Q721

Q723

Q707

Q715 Q713

Q709

Q711

Q717

Q620 Q622 Q619 Q621 Q520 Q522 Q519 Q521 Q420 Q422 Q419 Q421

Q608

Q616 Q614

Q624 Q623 Q524 Q523 Q424 Q423

Q610

Q612

Q618

Q607

Q615 Q613

Q609

Q611

Q617

Q508

Q516 Q514

Q510

Q512

Q518

Q507

Q515 Q513

Q509

Q511

Q517

Q408

Q416 Q414

Q410

Q412

Q418

Q407

Q415 Q413

Q409

Q411

IC81

Q417

AMP PCB

Q703 Q705

IC71 IC61 IC51 IC41

Q604 Q606

Q603 Q605

Q504 Q506

Q503 Q505

Q404 Q406

Q403 Q405

Q801 Q803 Q804

PREOUT PCB

47 48

Page 36

IC18

IC19

IC15

Q100

IC17

IC14

Q106

Q104

Q119

Q118Q101

Q112

Q110

IC16

VIDEO CONVERTER PCB A

Q113

Q108

IC12

Q114

Q115

Q116

Q117

IC11

Q120

Q106 Q105

Q108

Q109

Q122

DSP PCB A

IC11

IC12

IC35

Q121

Q107

IC33

Q110 Q111

IC34

Q123 Q124

IC37

QC12 QC11

IC13

Q103

IC38

IC17

IC18

IC31

IC40

Q100

IC32

Q102

Q101

IC15

IC14

IC19

IC21

QC10

IC30

IC39

IC22

IC23

IC28

IC36

IC24

IC25

IC26

IC27

Q126

Q127

Q121

Q111

Q107

Q105 Q109

Q102

Q103

VIDEO CONVERTER PCB B

5049

Page 37

IC16

IC11IC12IC16

DSP PCB B

IC20

Q112

Q125

DVI PCB

Q103

Q104

Q101

Q102

IC17

IC18

51 52

Page 38

VIDEO PCB

IC73

Q713

IC76

IC79

IC80

IC72

IC77 IC82

IC75

Q707

IC09

Q706 Q705

IC71

IC74

Q708

Q710IC78

Q711

Q712

IC81

Q701

Q704Q703

Q702

Q807 Q806

SELECTOR PCB

PUSH S/W PCB

5453

Page 39

FRONT PCB

IC81

Q801

IC84

IC83

AUX1 PCB

H/P PCB

Q103

SBLR PCB

TUNER PCB

55 56

Page 40

Q206Q205

Q212

Q213

VOLUME PCB

Q251

IC12

IC11

IC16

Q237Q207

Q233Q214

Q239Q238

Q235Q234

Q202Q201

Q209Q208

IC17IC13IC15IC14

Q204Q203

Q211Q210

Q222Q215

Q223Q216

Q224Q217

Q225Q218

Q226Q219

Q241Q240

Q221Q220

Q902Q901

COMPONENT PCB

IC94

IC92

IC93

IC91

5857

Page 41

POWER PCB

Q611

Q612

IC61

IC62

IC63

IC64

Q613

Q614

Q615

Q606

Q607

Q608

Q616

Q603

Q604

Q609Q610

Q602

Q601

STANDBY PCB

IC85

Q805

Q804

59 60

Page 42

11. IC DATA

Pin Descriptions

Input Pins

Pin Name Pin # Type Description

DIE23-

DIE0

See

SiI 160

Pin

Diagram

In Input Even Data[23:0] corresponds to 24-bit pixel data for 1-pixel/clock input mode and to the

first 24-bit pixel data for 2-pixels/clock mode.

Input data is synchronized with Input data clock (IDCK).

Data can be latched on the rising of the falling edge of IDCK depending on whether EDGE is

high or low, respectively.

Refer to TFT Panel Data Mapping in this document and DSTN Panel Data Mapping

application note (SiI-AN-0007-A), which tabulates the relationship between the input data to

the transmitter and output data from the Receiver

DIO23-

DIO0

See

SiI 160

Pin

Diagram

In Input Odd Data[23:0] corresponds to the second 24-bit pixel data for 2-pixels/clock mode. Tie

all pins to low when not in use.

Input data is synchronized with Input data clock (IDCK).

Data can be latched on the rising of the falling edge of IDCK depending on whether EDGE is

high or low, respectively

Dual Link is not supported. Refer to TFT Panel Data Mapping in this document and DSTN

Panel Data Mapping application note (SiI-AN-0007-A), which tabulates the relationship

between the input data to the transmitter and output data from the Receiver

IDCK 80 In Input Data Clock. Input data and control signals can be valid either on the falling or the rising

edge of IDCK as selected by the EDGE pin.

DE 78 Out Input Data Enable. This signal qualifies the active data area. DE is always required by the

transmitter and must be high during active display time and low during blanking time.

HSYNC

VSYNC

76

77

InInHorizontal Sync input control signal.

Vertical Sync input control signal.

CTL1

CTL2

CTL3

84

83

82

In

In

In

General Input control signal 1.

General Input control signal 2.

General Input control signal 3.

Configuration Pins

Pin Name Pin # Type Description

EDGE 24 In Data/Control Latching Edge. A LOW level indicates that all input signals(DIE/DIO[23:0],

HSYNC, VSYNC, DE and CTL[3:1] are latched on the falling edge of IDCK, while a HIGH

level(3.3V) indicates that all input signals are latched on the rising edge of IDCK.

PIXS 25 In Pixel Select. A LOW level indicates one pixel (up to 24-bits) per clock mode using DIE[23:0].

A HIGH level (3.3V) indicates two pixels (up to 48-bits) per clock mode using DIE[23:0] for

the first pixel and DIO[23:0] for the second pixel.

Power Management Pins

Pin Name Pin # Type Description

PD 26 In Power Down (active LOW). A HIGH level indicates normal operation. A LOW level indicates

power down mode. During power down mode, all data (DIE/DIO[23:0]), data enable (DE), clock

(IDCK) and control signals (HSYNC, VSYNC, CTL[3:1]), input buffers are disabled, all output

buffers are tri-stated and all internal circuitry is powered down.

IC16 (DVI PCB) : SiI 160

Functional Description

The SiI 160 is a DVI 1.0 compliant PanelLink transmitter in a compact package. It provides 48 bits for data

to allow for panel support up to UXGA. Figure 2 shows the functional blocks of the chip.

IC16 (DVI PCB) : SiI 160

EXT_SWING

DIE[23:0]

DIO[23:0]

DE

24

24

DATA

HSYNC

VSYNC

Encoder

0

Swing

Control

Tx0+

Tx0

Tx0-

HSYNC

VSYNC

CTL1

CTL2

CTL3

EDGE

PIXS

IDCK

Capture

Logic

DATA

Data

Encoder

CTL1

DATA

CTL2

Encoder

CTL3

Jitter

Filter

Figure 2. Functional Block Diagram

PLL

Tx1+

1

Tx1

Tx1-

Tx2+

2

Tx2

Tx2-

TxC+

TxC

TxC-

6261

Page 43

IC16 (DVI PCB) : SiI 160

Differential Signal Data Pins

Pin Name Pin # Type Description

TX0+

TX0-

TX1+

TX1-

TX2+

TX2-

TXC+

TXC-

EXT_SWING 32 Analog Voltage Swing Adjust. A resistor should tie this pin to AVCC. This resistor determines the

40

Analog

39

Analog

43

Analog

42

Analog

46

Analog

45

Analog

3534Analog

Analog

TMDS Low Voltage Differential Signal input data pairs.

These pins are tri-stated when PD is asserted.

TMDS Low Voltage Differential Signal input clock pair.

These pins are tri-stated when PD is asserted.

amplitude of the voltage swing. A 510Ω resistor is recommended for remote display

applications. For notebook computers, 680Ω is recommended.

Reserved Pins

Pin Name Pin # Type Description

RSVD 20 In

RSVD 21 In

RSVD 22 In

RSVD 23 In

RSVD 27 In

RSVD 28 In

RSVD 29 In

RSVD 87 In

Reserved. Must be tied HIGH for normal operation.

Reserved. Must be tied LOW for normal operation.

Reserved. Must be tied HIGH for normal operation.

Reserved. Must be tied HIGH for normal operation.

Reserved. Must be tied HIGH for normal operation.

Reserved. Must be tied HIGH for normal operation.

Reserved. Must be tied HIGH for normal operation.

Reserved. Must be tied HIGH for normal operation.

Power and Ground Pins

Pin Name Pin # Type Description

VCC 8,30,56,88 Power Digital Core VCC, must be set to 3.3V.

GND 7,31,57,67,79,89 Ground Digital Core GND.

IVCC 17,66,81,98 Power Input VCC, must be set to 3.3V.

AVCC 36,38,44 Power Analog VCC must be set to 3.3V.

AGND 33,37,41,47 Ground Analog GND.

PVCC1 18 Power Primary PLL Analog VCC must be set to 3.3V.

PVCC2 85 Power Filter PLL Analog VCC must be set to 3.3V.

PGND1 19 Ground PLL Analog GND. PGND1 should not be directly

PGND2 86 Ground PLL Analog GND. PGND2 should not be directly

connected to PGND2 before being connected to the

GROUND plane. They should be connected

individually to the GROUND plane.

connected to PGND1 before being connected to the

GROUND plane. They should be connected

individually to the GROUND plane.

63

Page 44

IC11 IC12 (DVI PCB) : SiI 1161

unctional Description

he SiI 1161 is a DVI 1.0 compliant PanelLink receiver in a compact package. It provides 24 or 48 bits for data

utput, and allows for panel support up to UXGA. Figure 1 shows the functional blocks of the chip.

PIXS

HS_DJTR

OCK_INV

SCL

SDA

EXT_RES

Control Registers

-----------

Termination

and

Equalization

Control

RX2+

RX2-

RX1+

RX1-

RX0+

RX0-

RXC+

RXC-

PDO#

STAG_OUT#

ST

VCR

VCR

VCR

VCR

Data Recovery

CH2

Data Recovery

CH1

Data Recovery

CH0

PLL

SYNC2

SYNC1

SYNC0

Channel

SYNC

Decoder

Panel

Interface

Logic

QE[23:0]

QO[23:0]

ODCK

DE

HSYNC

VSYNC

SCDT

CTL[3:1]

Figure 1. Functional Block Diagram

he PanelLink TMDS core accepts as inputs the three TMDS differential data lines and the differential clock. The

ore senses the signals on the link and properly decodes them providing accurate pixel data. The core outputs

he necessary sync signals (HSYNC, VSYNC), clock (ODCK), and a DE signal that goes high when the active

egion of the video is present.

he SCDT signal is output when there is active video on the DVI link and the PLL in the TMDS has locked on to

he video. SCDT can be used to trigger external circuitry, indicating that an active video signal is present or used

o place the device in power down when no signal is present (by tying it to PDO#). The EXT_RES component is

sed for impedance matching.

64

Page 45

IC11 IC12 (DVI PCB) : SiI 1161

Pin Descriptions

Output Pins

Pin Name Pin # Type Description

QE23-

QE0

QO23-

QO0

ODCK 44 Out Output Data Clock. This output can be inverted using the OCK_INV pin. A low level on PD# or

DE 46 Out Output Data Enable. This signal qualifies the active data area. A HIGH level signifies active

HSYNC

VSYNC

CTL1

CTL2

CTL3

See

SiI 1161

Pin

Diagram

See

SiI 1161

Pin

Diagram

48

47

40

41

42

Out Output Even Data[23:0] corresponds to 24-bit pixel data for one pixel per clock input mode

and to the first 24-bit pixel data for two pixels per clock mode.

Output data is synchronized with output data clock (ODCK).

Refer to the TFT Panel Data Mapping section, which tabulates the relationship between the

input data to the transmitter and output data from the receiver.

A low level on PD# or PDO# will put the output drivers into a high impedance (tri-state) mode.

A weak internal pull-down device brings each output to ground.

Out Output Odd Data[23:0] corresponds to the second 24-bit pixel data for two pixels per clock

mode. During one pixel per clock mode, these outputs are driven low.

Output data is synchronized with output data clock (ODCK).

Refer to the TFT Panel Data Mapping section, which tabulates the relationship between the

input data to the transmitter and output data from the receiver.

A low level on PD# or PDO# will put the output drivers into a high impedance (tri-state) mode.

A weak internal pull-down device brings each output to ground.

PDO# will put the output driver into a high impedance (tri-state) mode. A weak internal pulldown device brings the output to ground.

display time and a LOW level signifies blanking time. This output signal is synchronized with

the output data. A low level on PD# or PDO# will put the output driver into a high impedance