Page 1

Page 2

--1--

Marantz Technical Service Manual

1. FORWARD

This document defines the design and performance requirements for HYUNDAI IT

E-SERIES MODEL 26” ,32”,37”,42”,46” LCD COLOR TV

It is capable of displaying maximum 1366X768 resolution image.

The LCD TV screen comes equipped with a dedicated terminal board

which is designed to a Accommodate an image signal from a variety

of multimedia source such as DVD players,VCRs Camcoders and set-top box,CATV

2. GENERAL DESCRIPTION

2.1 Features

This digital Terrestrial receiver is suited for DVB-T standard reception of

Free digital Terrestrial program and has the following features;

<iDTV Incase>

* Full DVB-T compliant

* High quality video and CD quality sound by MPEG-2 standard

* 3000 pre-programmable station (video:2000ch,audio;1000ch)

* User friendly and well –defined On Screen Display

* Parent lock and favorite select function

* EPG(Electronic Program Guide)Function

* Full infrared remote control

* Automatic scan for added channel

* NIT scan function

* Manual and automatic scan programming

* Display signal strength meter on the screen

* Optical connector for SPDIF Output

* Output for Audio L/R

* PIG (Picture in Graphic) function

* High resolution graphic with 256 colors

* Channel delete, move, edit and add function

* Software up grade with RS232C

<Others>

* There are 7 languages OSD as English, Deutsch, Français, Nederland, Italiano,

Español, Suomi

* A choice of WIDE, ZOOM and advanced 4:3 and 14:9

AUTO size aspect ratios

* High luminance and contrast ratio, low reflection and wide viewing angle

* PIP (Picture-In-Picture)

* Auto Volume Limit

* Noise Reduction

* Sound Mode Setting(7 Equalizer : 100Hz,3200Hz,1.0KHz, 3.0KHz,10KHz)

* Picture Mode Setting

Page 3

* Full multimedia capability

* TELETEXT(252pages : only ATV)

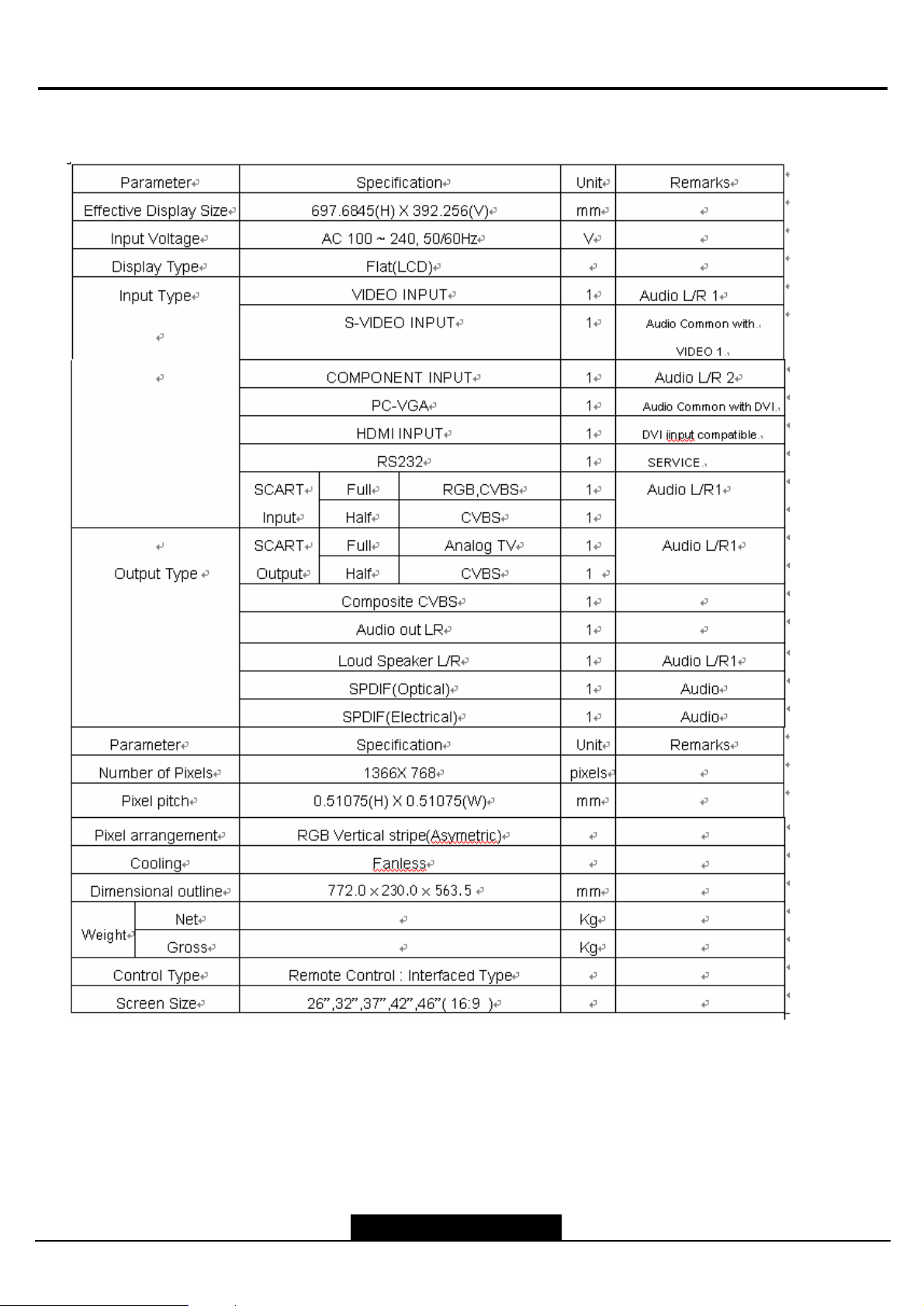

2.3 General Specification

The LCD TV is a Color Active Matrix Liquid Crystal Display with an integral

Cold Cathode Flourscent Lamp(CCFL) backlight system.

The matrix employs a-Si Thin Film Transistor as the active element.

It is a transmissive display type which is operated in the normally black mode.

It has a 31.51 inch diagonally measured active display area with WXGA resolution.

(768 vertical by 1366 horizontal pixel array) Each pixel is divided into

Red, Green and Blue sub-pixels or dots which are arranged in vertical stripes.

Gray scale or the luminance of the sub-pixel color is determined with

a 8-bit gray scale signal for each dot, Therefore it can present a palette

of more than 16.7M(true) Colors.

It has been designed to apply the 8Bit 1 port LVDS interface.

It is intended to support LCD TV, PCTV where high brightness,

super wide viewing angle, high color gamut, high color depth and fast response

time are important

--2--

Page 4

--3--

Marantz Technical Service Manual

2.4 General Features( REFER 32”)

Page 5

3. A/V Circuit BLOCK Diagram

3.1 PC Mode

P C inputs, R, G, B , H, and V signals, are entered through D-Sub 15pin (DSUB1).

When PC is selected in MCU, the signals are entered into the SCALER, MST-6151DA

(USC01).

MST6151DA is controlled using the MCU VCT49X3R(US02) Bus line of pin

41/42/43/47/48/49/50.

PC input resolution is Fh : 31~70k and Fv: 56~85Hz, and the maximum input resolution

is 1360x768 at 60Hz.

Because MST6151DA Scaler has AD converter, data is operated RGB 24 bits.

If the resolution is above the specifications, an out of range message is displayed on the

center of the screen.

However, even if the resolution is within the specified range, if the input timing is different

from the timing indicated

on the manual, unsupported video, a message can be displayed.

The Geometry Adjust function, which is used to adjust the picture position and size,

should be carried out in the Windows desktop screen,or full cross hatch.

The component signals, 480p, 720p, and 1080i, from the set-top box with a D-Sub out

port, may be has not good image quality.

Sound L R signal of pc mode is entered pin117,118 of VCT49X3R. and sound processor

is included in VCT49X3R.

Ouput Sound signal is outputted through pin 123,124 of MST6151DA ,and then this

signal is entered audio amp YDA138E.

PC input and DVI input share a single audio jack

3.2 HDMI Mode

HDMI inputs (LVDS signal), 8bit, are entered through HDMI 19pin (CNG02). When HDMI

is selected by MCU,

the LVDS signals are entered into digital port of the SCALER MST-6151DA (USC01).

MST6151DA is controlled using the MCU Bus line of pin 41/42/43/47/48/49/50.

the maximum resolution is 1360x768 at 65Hz. If the resolution is above the specifications,

an out of range message

is displayed on the center of the screen. However, even if the resolution is within the

specified range,

if the input timing is different from the timing indicated on the manual, unsupported

video, a message can be displayed.

In hdmi mode, this model support 480p(60), 576p(50), 720p(50/60), 1080i(50/60) ,and

pc timing on the manual.

3.3 COMPONENT Mode

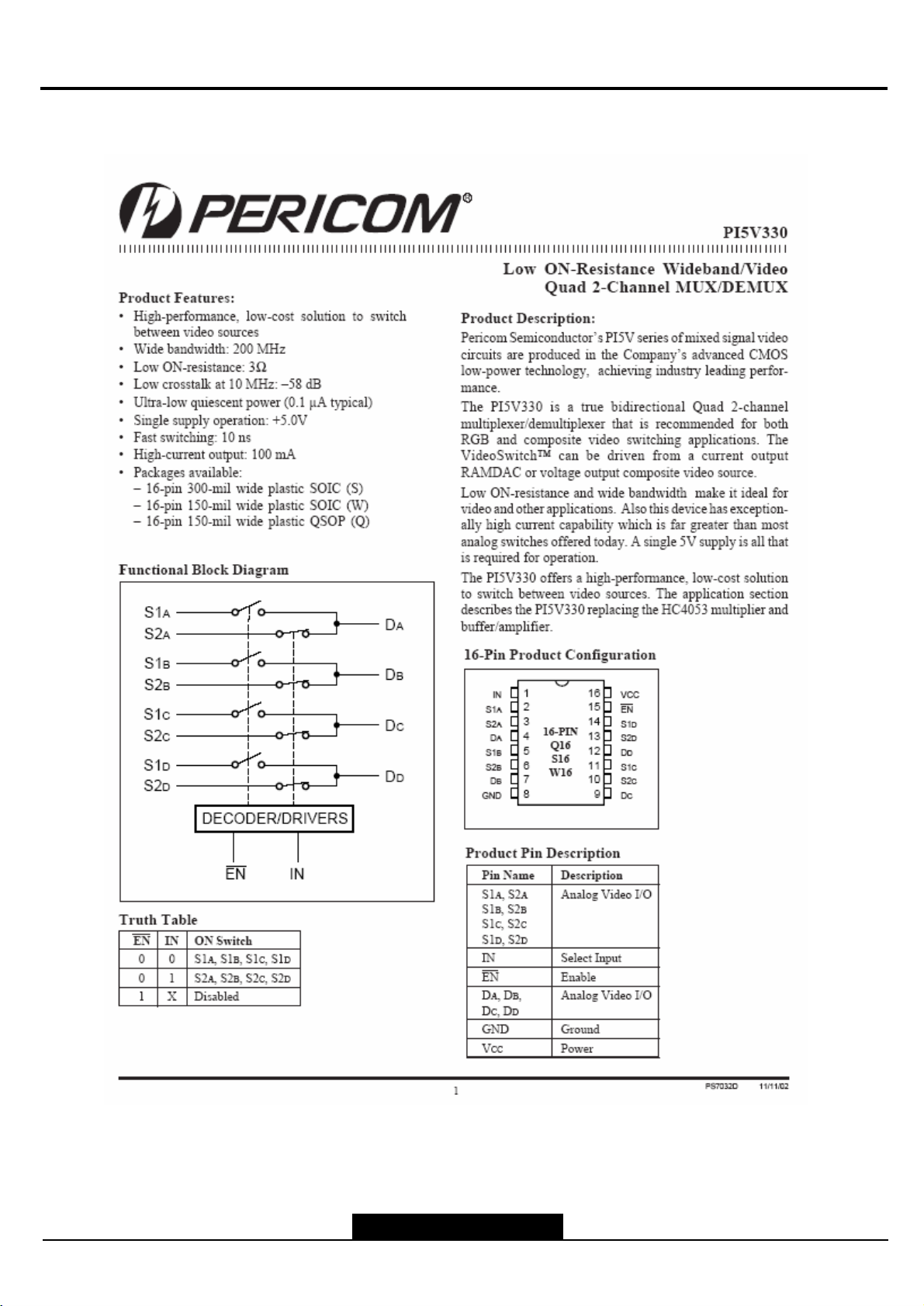

Component signals Y, Pb(Cb),Pr(Cr) are entered port0 of mux PI5V330SWE(UC01).

mux PI5V330SWE is controlled by mcu.

When pin 1 of mux is low, component signal is outputted, and then Component signals

--4--

Page 6

Marantz Technical Service Manual

are entered into

The SCALER, MST-6151(USC01)DA.

The Component signals are composed of 480p (50/60Hz) for SD, 576p(60Hz),720p

(50/60Hz) for HD, and 1080i (50/ 60Hz).

Component audio signal is entered audio mux TEA6422(UX01). Mux TEA6422 is

controlled by SCL,SDA line of MCU VCT49X3R.

3.4 S-Video

S-Video signals are entered as Y/ C signals, which is composed of Luminance and color

signals.

The PAL/SECAM are automatically detected by the video decoders VCT49X3R.

video decorder is included in VCT49X3R (US02).

Video signal is operated 656 format( 8bit), and YUV 8bit signal is entered scaler

video port.

S-Video input and composite video input share a single audio jack.

Therefore, while the pictures for the two inputs can be viewed at the same time, only one

of the sounds can be heard.

S-video and composite audio signal is entered audio mux TEA6422(UX01).

Mux TEA6422 is controlled by SCL,SDA line of MCU VCT49X3R.

3.5 Video

Video signal is a composite signal that combines the Luminance (Y) and color (CHROMA) .

It is entered to the scaler IC, MST-6151DA (USC01).

Video signal is operated 656 format( 8bit) as S-video , and YUV 8bit signal is entered

scaler video port.

3.6 Scart Mode

Scart mode is separated full scart mode , half scart mode.

Full scart mode support CVBS video signal and RGB signal with audio signal.

half scart mode support CVBS video signal with audio signal.

Y-C Mode Signals is not Supported.

pin 8 high will auto select the SCART input. With a voltage range of 4.5V to 7.0V a compatible set

will

select AV input in 16x9 mode. With a voltage range of 9.5v to 12.0v the set will select AV input in

4x3 mode.

pin 16 is used to select between composite or RGB input modes using the same SCART.

With a voltage of 1-3V DC (with respect to pin 18) RGBS input mode is selected.

With a voltage range of 0-0.4V composite mode is selected

3.7 IDTV Mode

--5--

Page 7

DTV Y Pb Pr signal is inputted from digital board assy .

DTV signals Y, Pb(Cb),Pr(Cr) are entered port1 of mux PI5V330SWE(UC01).

mux PI5V330SWE is controlled by mcu.

When pin 1 of mux is high, dtv signal is outputted, and then dtv signals are entered

into The SCALER, MST-6151(USC01)DA.

dtv signals are composed of 576i. dtv audio signal is entered audio mux TEA6422(UX01).

Mux TEA6422 is controlled by SCL,SDA line of MCU VCT49X3R.

3.8 Analog TV Mode

Rf signal from tuner(UX02) is generated IF. And IF signal is entered saw filter TFS96F(US01)

Output signal from saw filter is entered VCT49X3R. this signal is separated CVBS video and

audio signal in VCT49X3R.

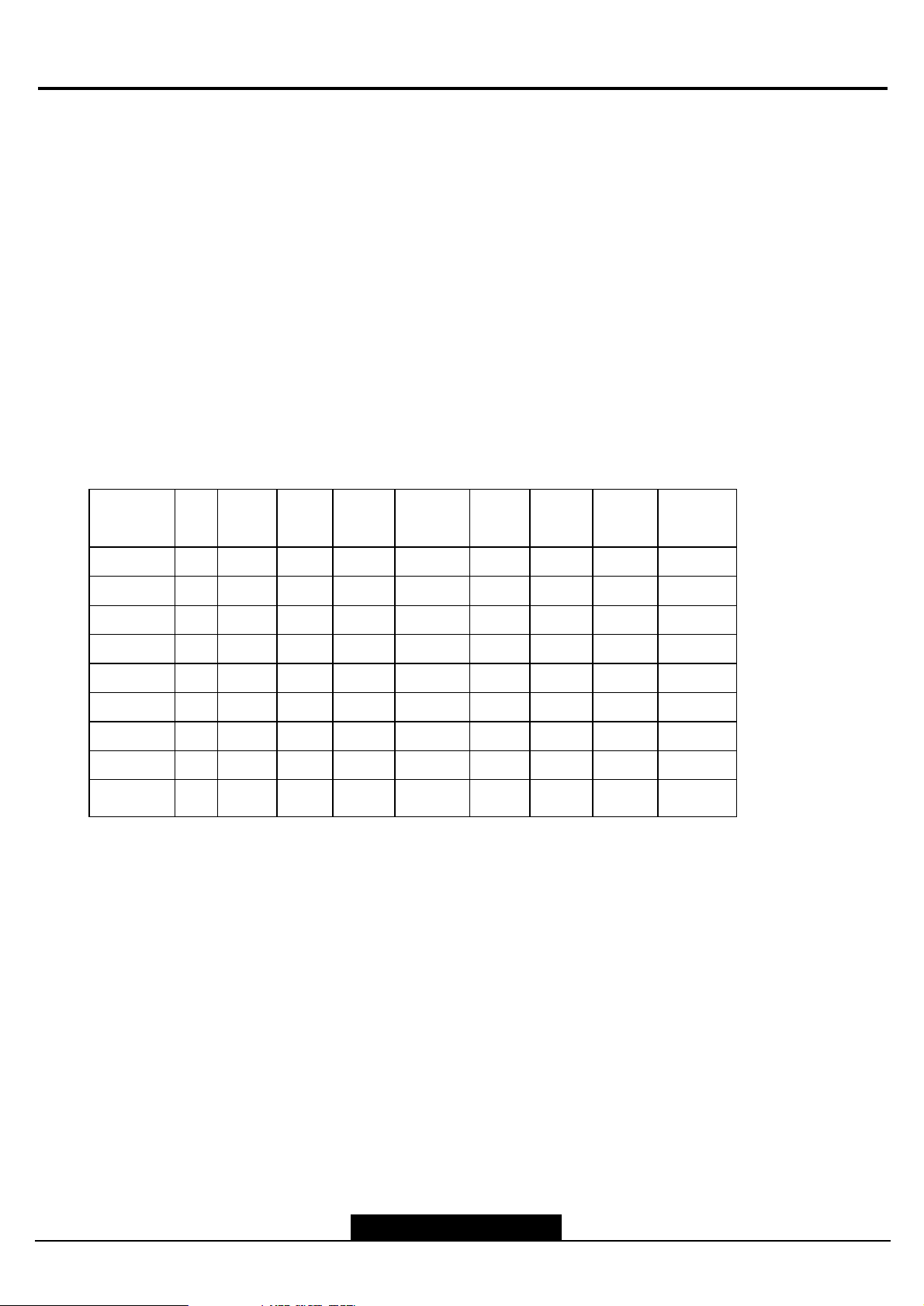

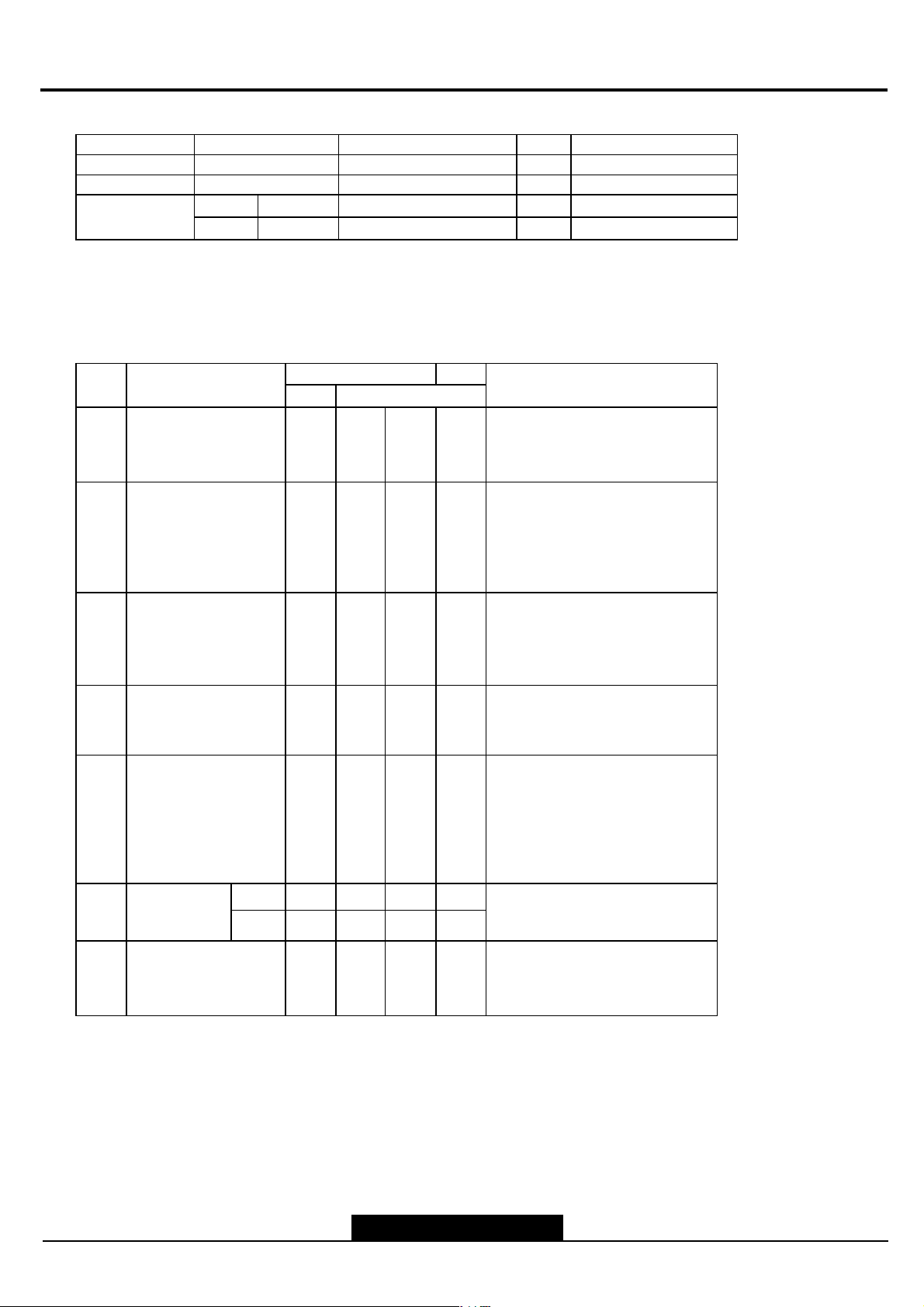

3.9 Supported PIP/POP Table

Sub\Main

PC X X X X O O O O O

HDMI X X X X O O O O O

iDTV X X X X O O O O O

COMP X X X X O O O O O

S-VIDEO O O O O X X X X X

VIDEO O O O O X X X X X

FScart O O O O X X X X X

HScart O O O O X X X X X

ANALOG

TV

PC HDMI iDTV

O O O O X X X X X

COMP

S-VIDEO

VIDEO

FScart

HScart

ANALOG

TV

X: Not supported, O: Supported

3.10 Scaler Output

Scaler output signals is R, G, B (each 8bits) LVDS signal .

This signal sent to the logic B/D in the LCD module.

3.11 Audio part

--6--

Page 8

Marantz Technical Service Manual

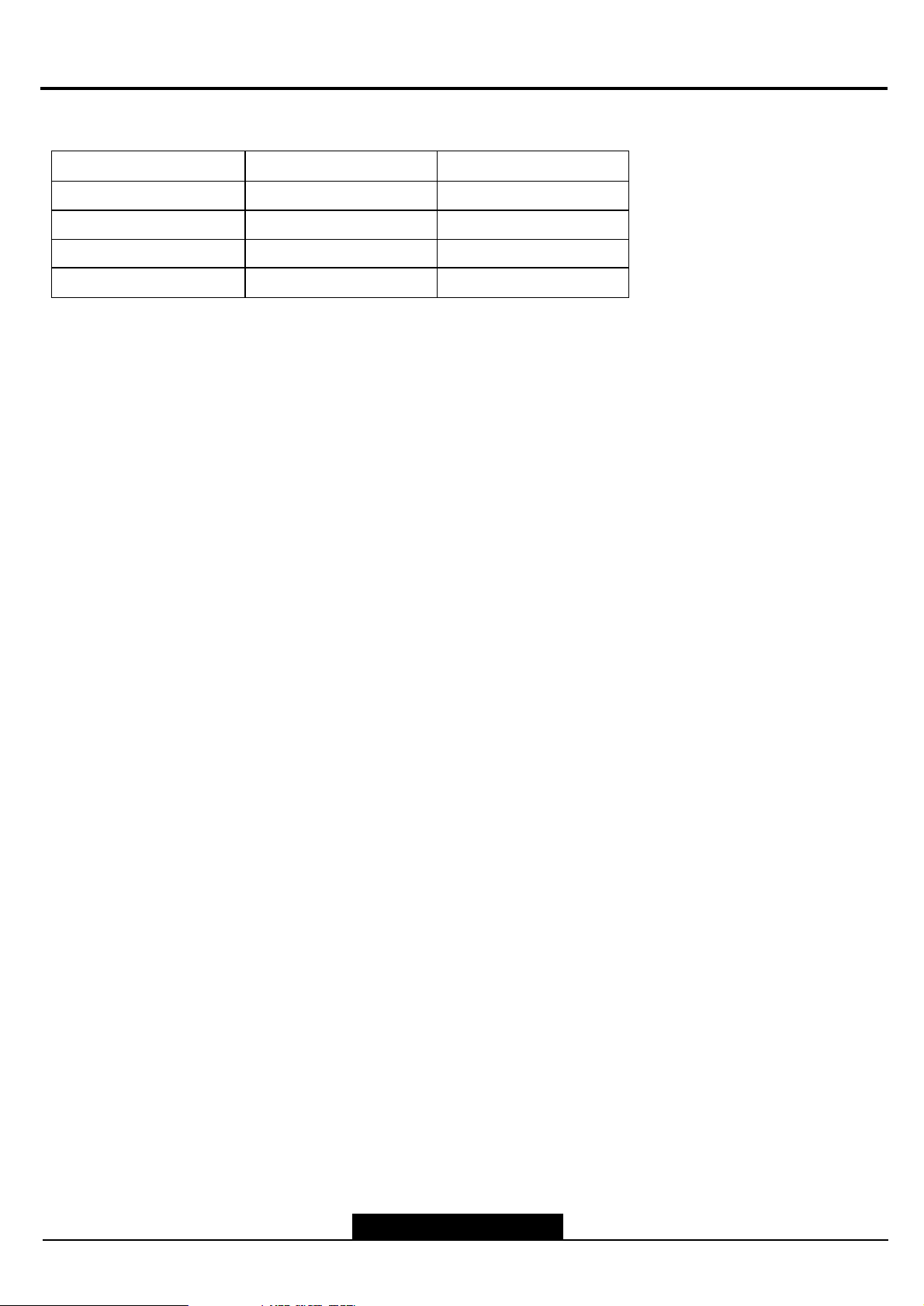

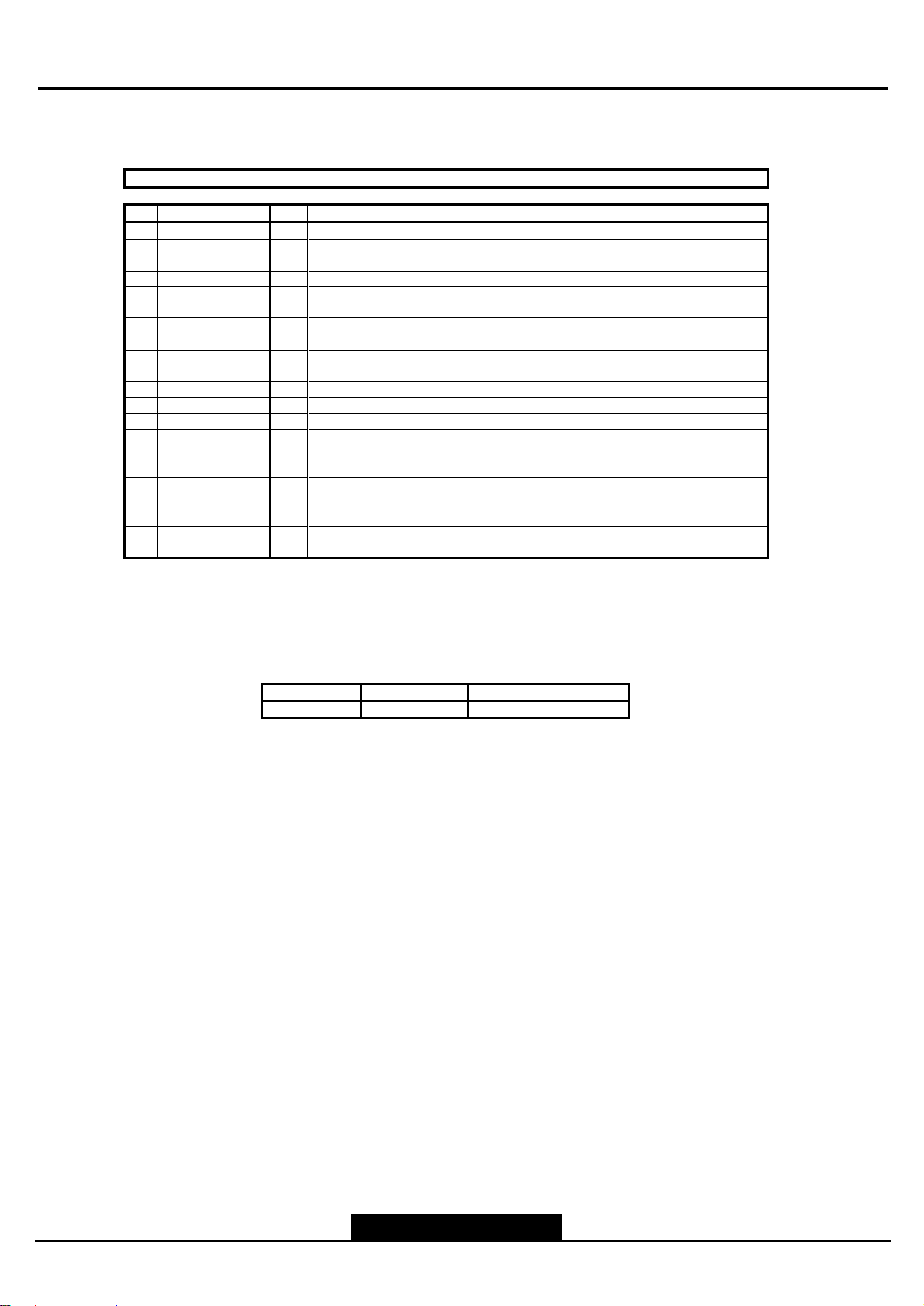

Audio input port for each mode:

Input Port Remark

PC /HDMI

Scart

CVBS /S-Video

COMPONENT

RCA L/R 1EA Shared

Scart Jack L/R

RCA L /R 1EA PAL

RCA L /R 2EA

Full and half

Audio input signal for PC/HDMI,COMPONENT,S-VIDEO,SCART and CVBS modes is entered

into the

audio processor IC(VCT49X3R), The audio processor (VCT49X3R) to control volume,

and left/right balance and mono/stereo and Sound effect.

The L/ R audio signal sent by VCT49X3R is amplified in the amplifier, YDA138E

(UAU01),and sent to the speaker.

YDA138E Support 10W(based on impedance 8 ohm of output for L/R).

4

. To use Service Mode

4.1 ENTERED INTO AGING MODE

1) REMOCON CONTROL

SET UP :MENU + S. MODE + SLEEP + MUTE Then go to number 5

Then go to number 3(Aging Option) ON

SET UP REMOVE :EXIT

4.2 CHECKING MCU VERSION

1) REMOCON CONTROL

- SET UP :MENU + S. MODE + SLEEP + MUTE Then You will see MCU VERSION

- GO TO Number 6

4

. 3 FACTORY RESET

1) REMOCON CONTROL

- SET UP :MENU + S. MODE + SLEEP + MUTE Then go to number 7(FACTORY RESET)

- PRESS ENTER AND RIGHT KEY

--7--

Page 9

4. 4 IN CASE DTV

Go to DTV Source Then Press MENU and move DTV CHANNEL and move FACTORY

SET and Press ENTER

4.5. Exit Service menu

- press exit key

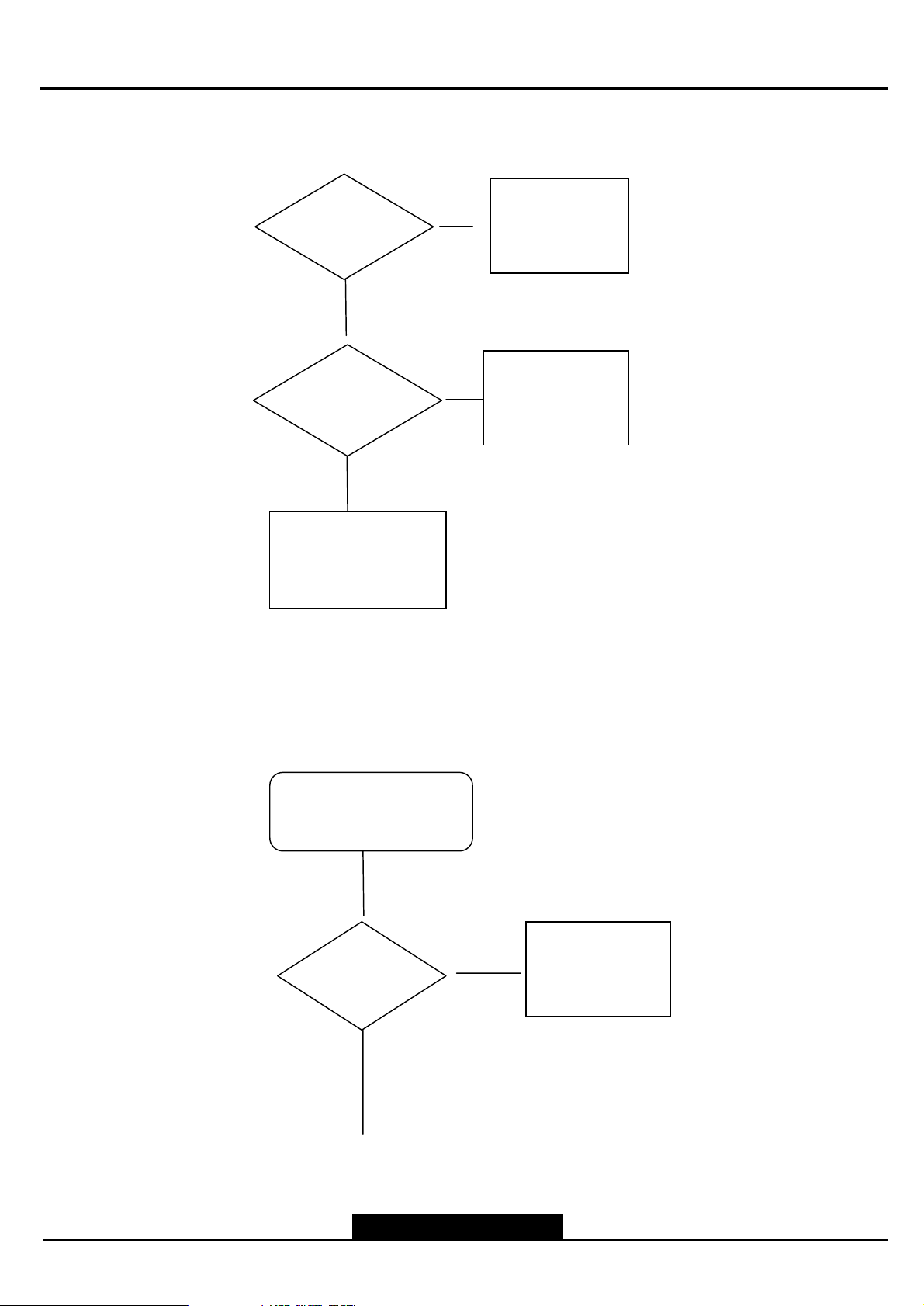

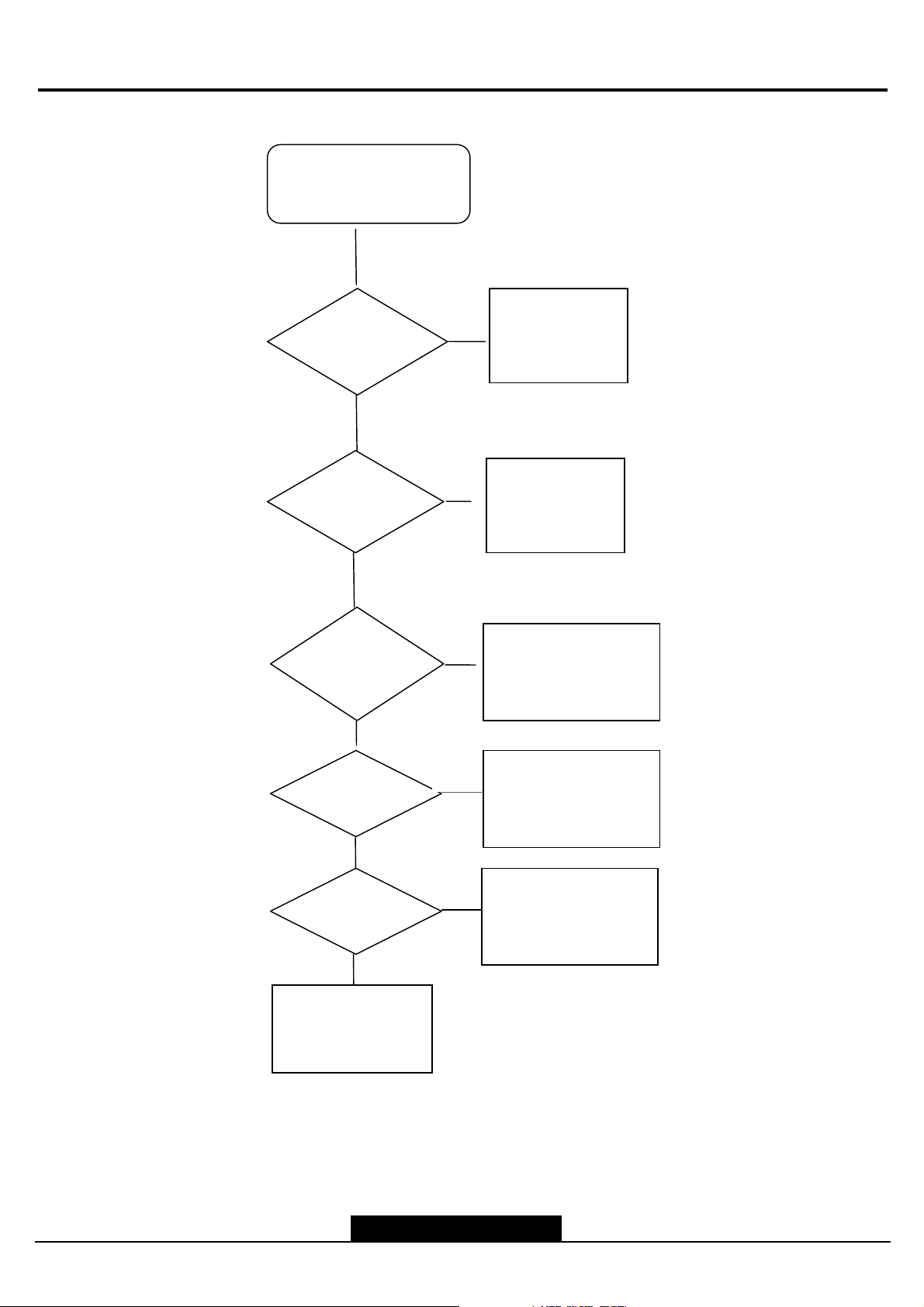

5.Trouble Shooting Guide

--8--

Page 10

Marantz Technical Service Manual

CHECK

UP09

D1.8V?

YES

NO

TROUBLE IN

UP09,USC01

CHECK UP10

MD1.8V?(IN USE

MD)

YES

CHECK END

DTV B/D CHECK

NO

TROUBLE IN

UP10

UMD01

YES

CHECK

R45,R44

(D5V D12V?)

YES

--9--

NO

TROUBLE IN

CON2

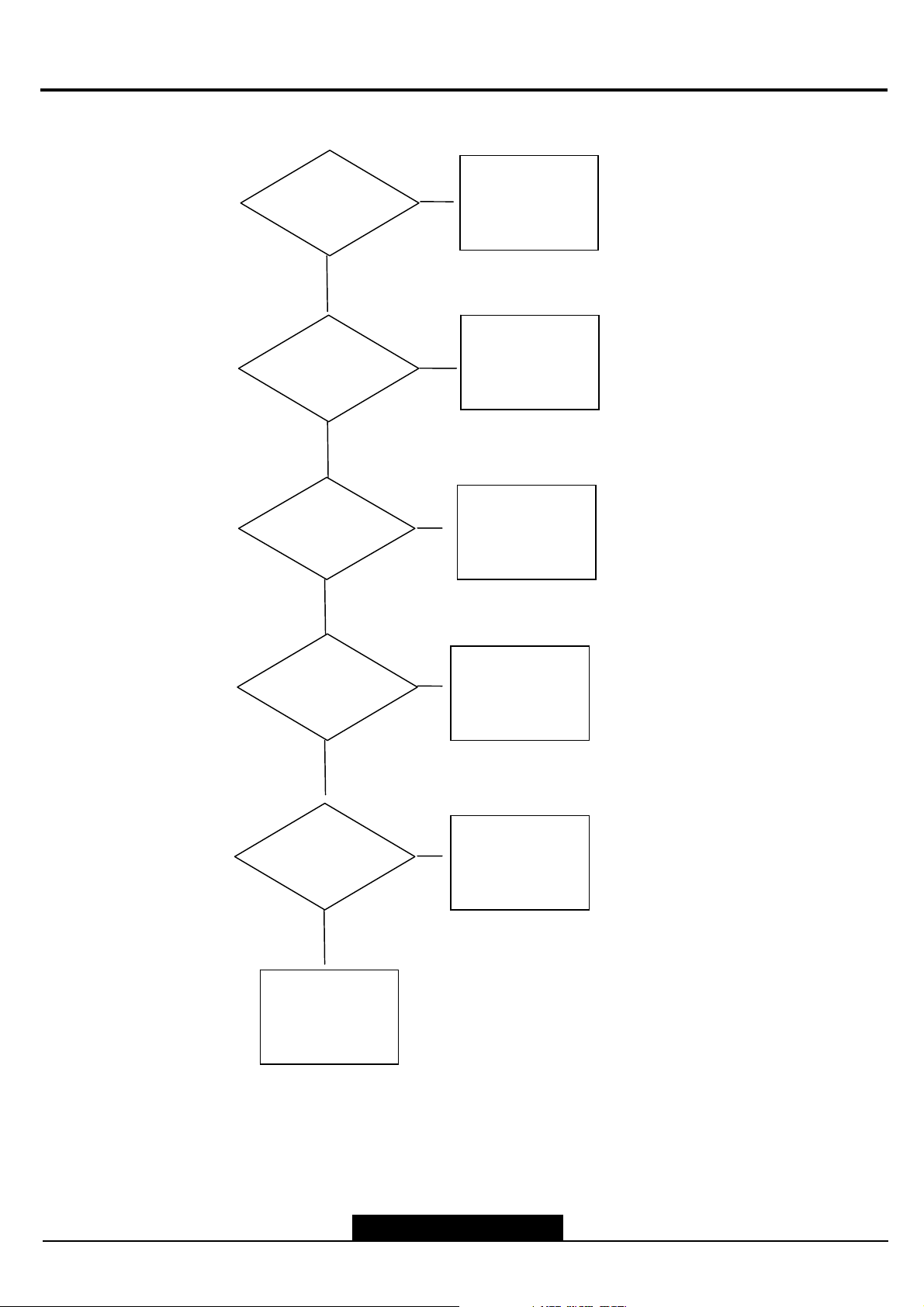

Page 11

LVDS

NO RASTER

YES

NO POWER

CHECK

YES

PANEL AND

YES

CHECK PANEL

VCC OR BL_ON?

YES

NO

NO

NO

PANEL AND

LVDS CABLE

TROUBLE IN

PANEL OR

UP01

TROUBLE IN UP01

PIN2 OF CNP01

CHECK US02

OUTPUT?

YES

CHECK USC01

OUTPUT?

CHECK END

NO

TROUBLE IN US02

TROUBLE IN USC01

--10--

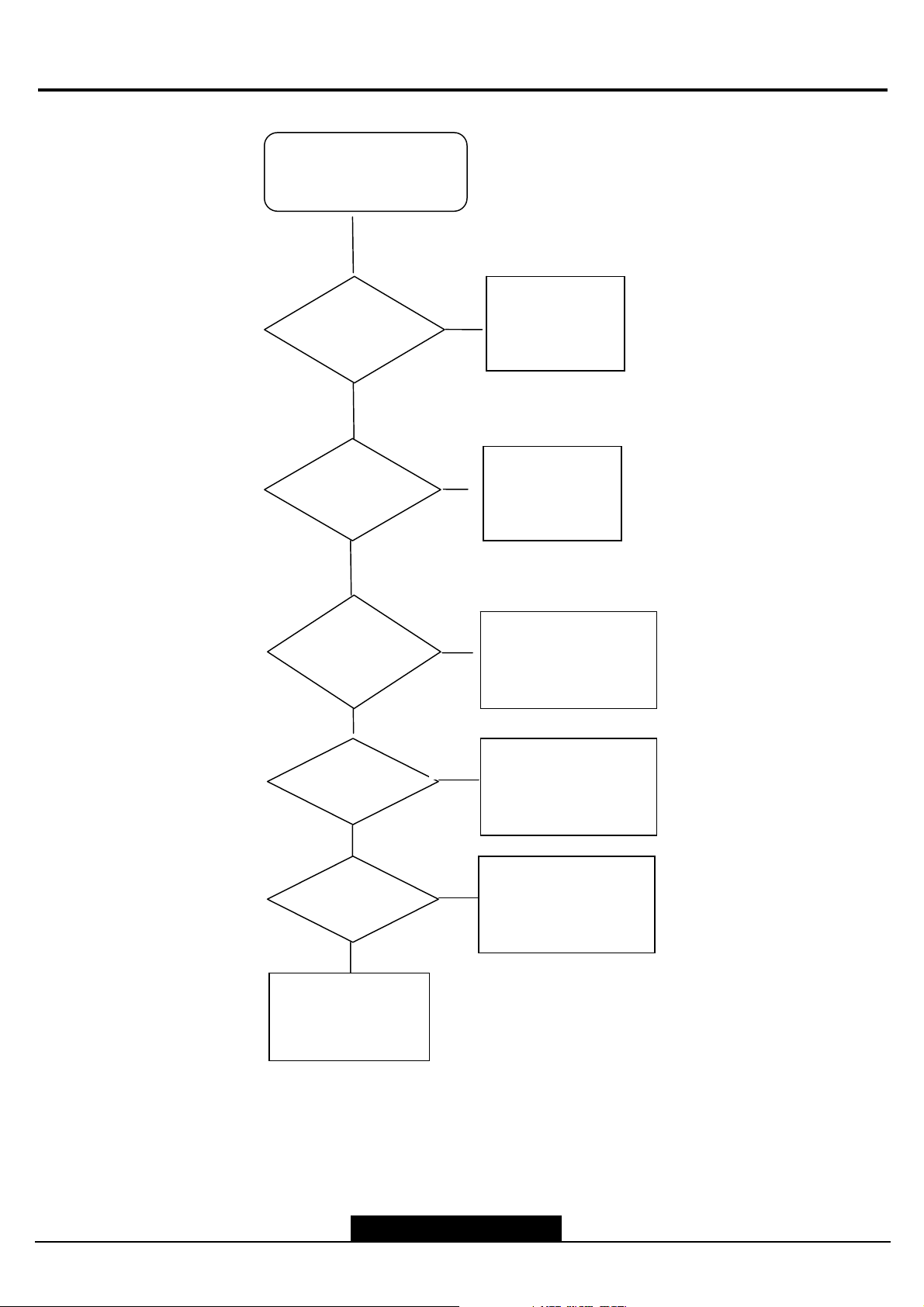

Page 12

Marantz Technical Service Manual

CHECK

ICDT1

(33V)?

YES

CHECK ICDT2

2.5V?,

YES

CHECK 33V

YES

NO

NO

NO

TROUBLE IN T1

U3,U4,U5

TROUBLE IN U3

TROUBLE IN

TUNER

CHECK

RX,TX

YES

CHECK T1,U3

JP5

YES

CHECK END

NO

NO

TROUBLE IN

CON02 PIN2

U3

,UG05

TROUBLE IN

TUNER

JP5

,U3,T1

--11--

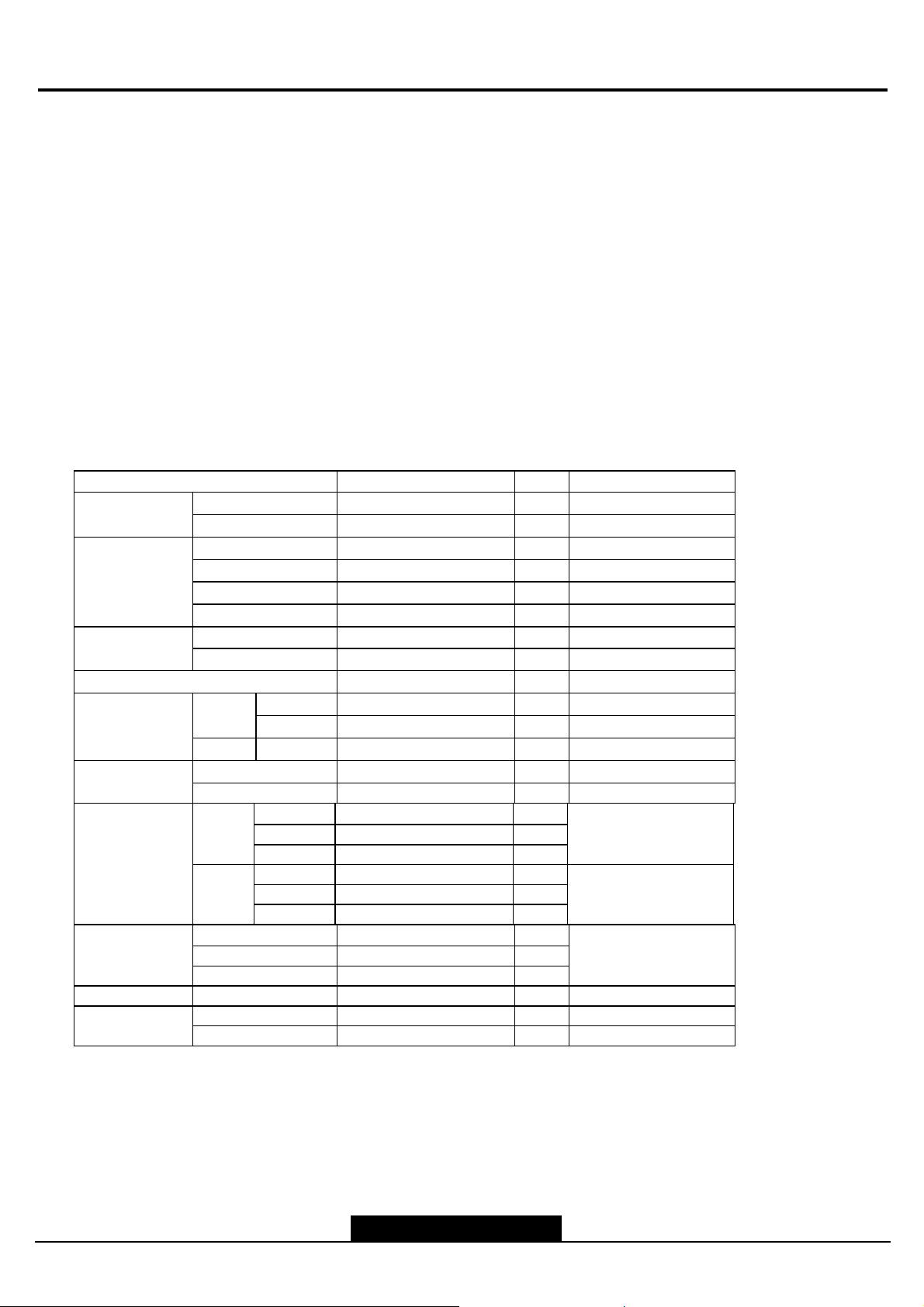

Page 13

UX01

NO SOUND

YES

AUDIO SOUND

INPUT?

YES

AUDIO MUX

YES

CHECK US02

INPUT OR OUTPUT

YES

NO

NO

NO

TROUBLE IN

INPUT

TROUBLE IN

AUDIO MUX

UX01

TROUBLE IN US02

AUDIO AMP

UAU01

YES

CHECK MUTE

VOLUME

CHECK END

NO

NO

TROUBLE IN AUDIO

AMP UAU01 OR AMP

VCC

TROUBLE IN MUTE

OR VOLUME OR

SPEAKER CABLE

--12--

Page 14

Marantz Technical Service Manual

6. TV/ VIDEO System

<Digital>

6.1 Front –End(Tuner/Demodulator)

Input Frequency Range : VHF 174~230Mhz:ch5~ch12

230~470Mhz:ch71~ch99

UHF 470~860Mhz :ch21~ch69

RF Input(for aerial)connector : female IEC 169-2

Channel bandwidth German : 8Mhz/7Mhz (combine UHF/VHF)

Others : 8Mhz (UHF only)

Input Impeadance 75ohms

OFDM Spectrum 2k and 8k carrier non hierarchical

Modulation Mode 16QAM,64QAM

Guard Interval Modes 1/32,1/16,1/8,1/4 active symbol duration

FEC Modes Rate 1/2, 2/3, 3/4, 5/6, 7/8

6.2 Transport Demultiplexer

Demultiplexer According to ISO/IEC 13818-1

Max.Input Stream 60Mbps(serial)/7.5Mbps(parallel)

PID Handling Capability 32PID

SI Filtering According DVB-SI Spec.(ETS 300 468)

< Analog >

6.3 ATV STANDARD

- TV system : PAL B/G, D/K, I, L, M

- RF signal :

VHF, UHF, CABLE TV

- Sound modulation: AM/FM-Mono, FM-Stereo (A2, D/K), NICAM

- Color system : PAL, SECAM

* APPLICATION

· Receiving System : (PAL STANDARD SYSTEM )

· Channel VHF : Low BAND : E2(48.25MHz) ~ S6(140.25MHz)

High BAND : S7(147.25MHz) ~ S36(423.25MHz)

UHF BAND : S37(431.25MHz) ~ C57(863.25MHz)

· Intermediate Frequency PIF : 38.9MHz (PAL B/G, I, D/K, SECAM L)

33.9MHz (SECAM L’)

SIF : 33.4MHz (B/G), 32.9MHz( I), 32.4MHz( D/K )

40.4MHz (SECAM L’)

--13--

Page 15

· Input Impedance : UHF/VHF Terminal (75) Ω, Unbalanced

· Band Change – Over System : (PLL Control System)

· Tuning System : (Electronic Tuning System With PLL)

6.4 Power Indicator LED

The LCD TV shall make use of an LED type indicator located on the front of the LCD TV.

The LED Color shall indicate the power states as follows.

* Power ON-LED is Green

* Power Off(Stand-by)- LED is Red( <1.8 watts)

6.5 Signal Input / Output specification

Parameter Specification Unit Remarks

Speaker

Audio

Consumption

Composit Video Input 1 Vp-p

Scart Input

S- Video Input

Component

Input

PC Input

Audio Input L, R 0.5 Vrms Mono or stereo

DVI Input

Impedance 8(L) + 8(R) Ω

Output 10 W

Freq. Character 0.1 ~ 12 KHz

T.H.D < 10 %

HUM < 1 V

Output 10(L) + 10(R) W

Max 125+10% W NOTE 1 Power

ST-BY <2.0 W

Full

Half CVBS 1 Vp-p

COMP

DTV

H Frequency 31 ~ 70(TTL Level) KHz

V Frequency 56 ~ 85(TTL Level) Hz

H Frequency 31 ~ 70(TTL Level) KHz

V Frequency 60(TTL Level) Hz

RGB 0.7 Vp-p

CVBS 1 Vp-p

Y 1 Vp-p

C 0.286 Vp-p

Y 1 Vp-p

Pb 0.7 Vp-p

Pr 0.7 Vp-p

Y 1 Vp-p

Pb 0.7 Vp-p

Pr 0.7 Vp-p

RGB 0.7 Vp-p

1920 * 1080i

1280 * 720p

720 * 576p

720 * 576p

VGA ~ XGA & HDTV

(1080i, 720p, 576p)

--14--

Page 16

Marantz Technical Service Manual

VIDEO Out put Composite 1.0 Vp-p

Audio Output L,R 0.5 Vrms

Woofer out put LOUD 0.5 Vrms

Scart Output

Full CVBS 1 Vp-p

Half CVBS 1 Vp-p

NOTE 1 .Power source : AC230V 50Hz

.It is measured on full screen white pattern

6.6 TV Input

* DEMOD. CHARACTERISTICS

NO. ITEM

1-1 Video Output Level 2.0 2.3 2.6 Vp-p * Video Signal : PAL( 87.5%),

Video Freq. Response

1 MHz 2 MHz 3 MHz 4

MHz 4.43 MHz -1.0

1-2

1-3 Luminance S/N Ratio 40 47 - dB

MIN.

-1.5

-2.5

-3.0

-4.0

SPECIFICATIONS

-0.0

-0.0

-0.0

-0.0

-1.0

+1.5

+2.0

+2.5

+3.0

+3.0

UNIT

NOTES

* Input Level : 70dBuV

SECAM ( 90%)

AM Mod. STD Color Bar

* Input Level : 70dBuV * PALl:

87.5% AM Mod. * SECAM : 90%

AM Mod. * FULL Sweepl *

dB

Reference : 0.5 MHZ

* Input Level : VHF,UHF : 70dBuV *

Setting of S/N Meter - HPF :

100KHz, - LPF : 5.0MHz * Video

Signal : 87.5% AM Mod.100%

White

Video Signal : 100% White Sig. AT.

NOISE LIMIT

1-4

SENSITIVITY

AFT ALIGNMENT

1-5

ACCURACY

Chroma

1-6

Distortion

DP -10 5 10 DEG

DG -10 5 10 %

- 43 51 dBuV

+50 0 -50 KHz

1-7 BURST LEVEL 20.0 30 36 % * Video Signal: 87.5% Mod.

S/N = 30dB

* Alignment Center : 1.9V * IF Input

Level : 90dBuV * P/S : -10dB *

Standard Color Bar : PAL(87.5%)

SECAM L’ (90%) * Center

Frequency : PAL ( 38.9 MHz)

SECAM L’ (90%)

* Input Level : 70dBuV * Video

Signal: 87.5% AM Mod. RAMP

Signal

* Input Level : 70dBuV

Standard Color

Bar Sig.

--15--

Page 17

1-8 SIF OUTPUT LEVEL 70 75

dBuV

1-9 AUDIO S/N RATIO 40 50

AUDIO DISTORTION

1-10

1-11

1-12

RESPONSE

AUDIO

FREQ.

RES-PONSE

10KHz

AUDIO OUTPUT

LEVEL

50Hz

- 4

- 0.6 3.5 %

- 3

- 1

0.3 .06 .08 Vrms

0 + 3

dB * Video Signal: 87.5% Mod.

dB

6.7 Analog R.G.B Input (PC)

6.7.1 Timing

* Input Level : 70dBuV * Video

Signal: Standard Color Bar Sig. *

CH : S20

* P/S Ratio : -10dB

* 1KHz±50KHz Dev.

Standard Color Bar Sig. * Use

CCITT FILTER

* 1KHz±50KHz Dev.

Color Bar : 87.5% Mod.

De-emphasis ON

* 50Hz ~ 10KHz *

* Standard

*

1KHz±50KHz

Dev *Standard Color Bar *

De-emphasis ON

1KHz±50KHz Dev * Standard

*

Color Bar : 87.5% Mod.

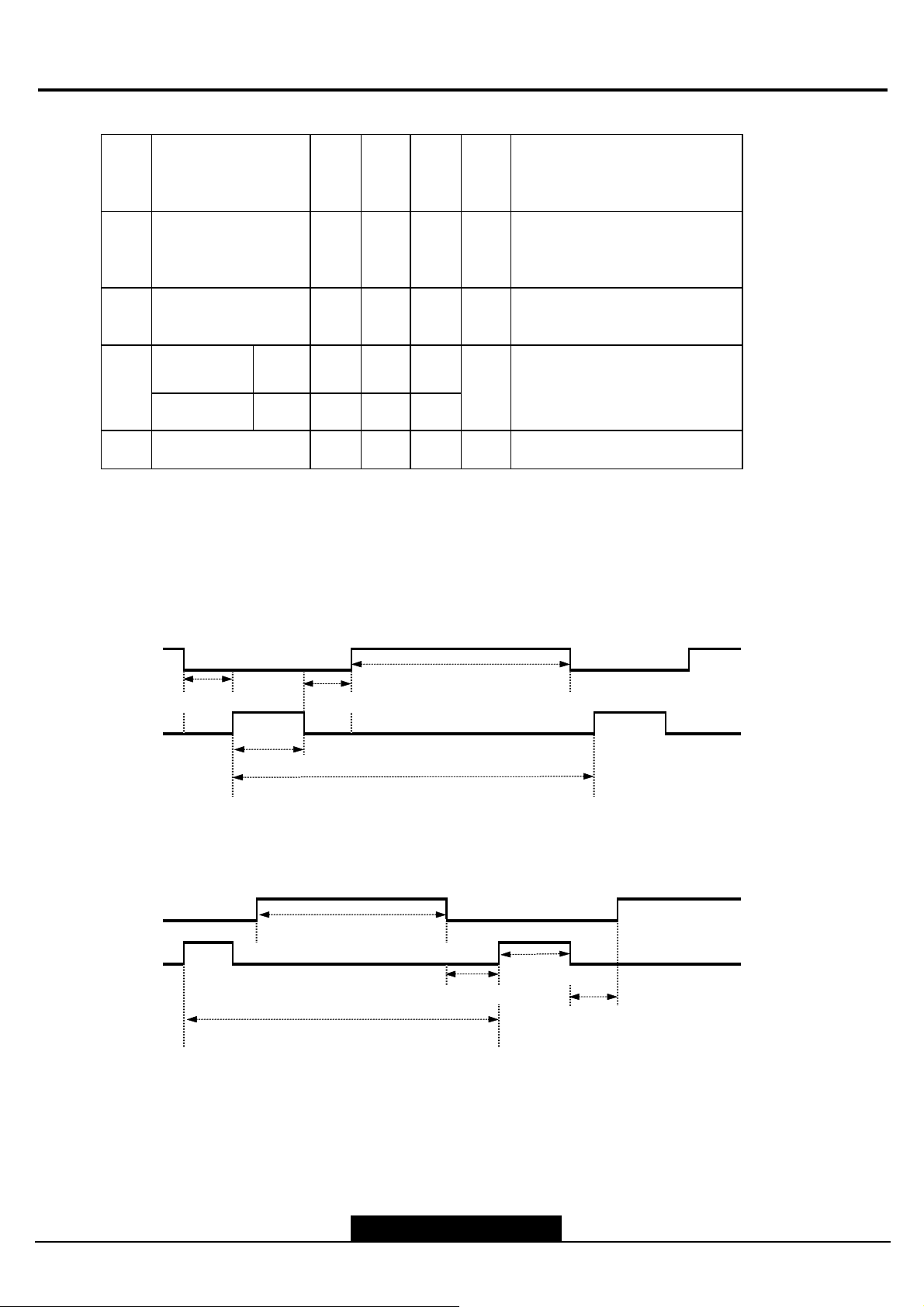

* Timing Chart

This monitor shall be capable of displaying following video timing chart.

Display Time (T4)

Front Porch (T5) Back Porch (T3)

Sync W idth (T2) High Level : 2.4V min

Time Total (T1) Low Level : 0.4V max

Fig. 3.2 - H-Sync

Display Time (T4)

Sync W idth (T2)

Front Porch (T5)

Back Porch (T 3)

Time T otal (T1)

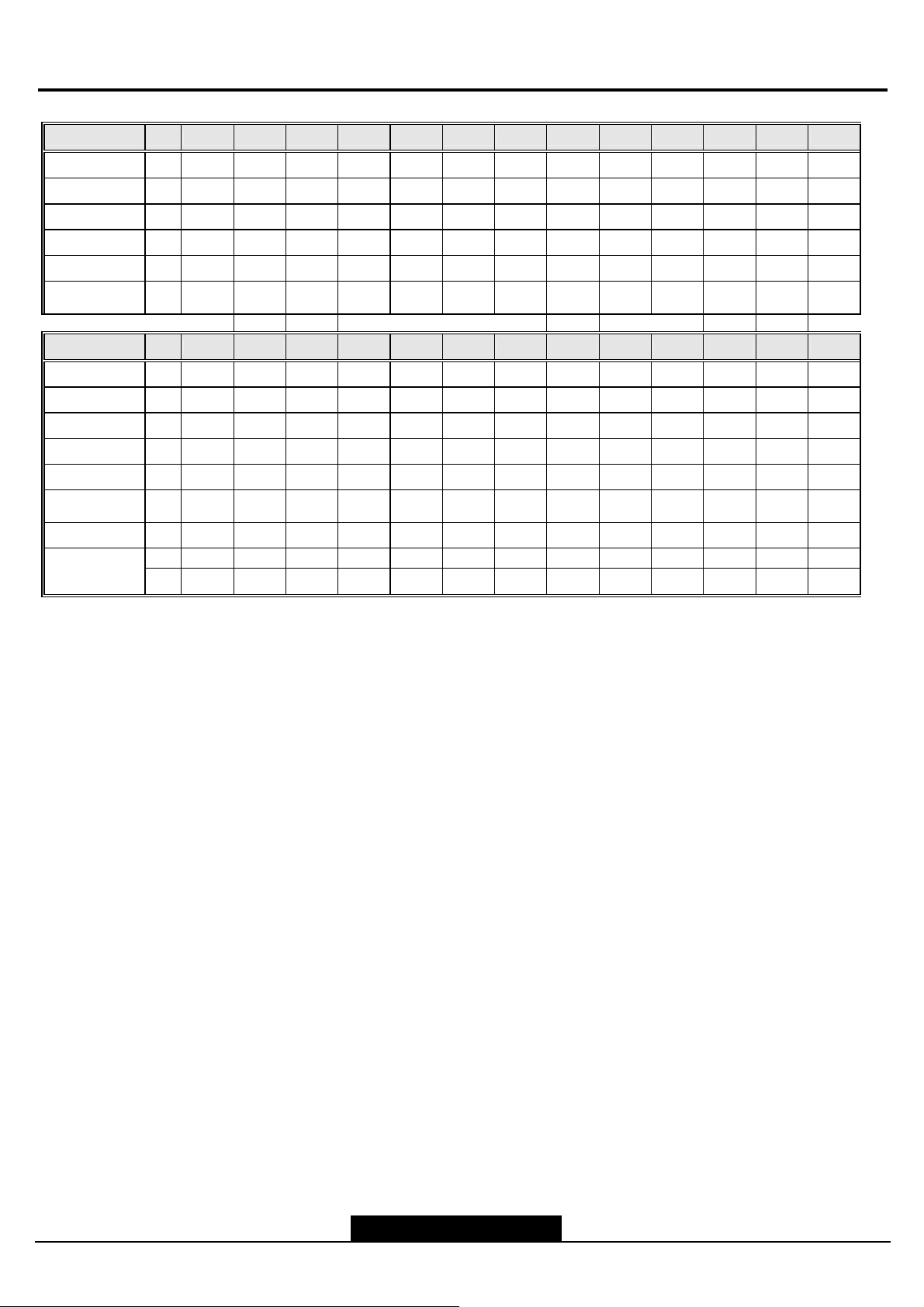

6.7.2 Preset-Mode Timing

The timing shown in the following table will be factory preset for display.

- preset mode table

Fig. 3.3 - V-Sync

--16--

Page 18

Marantz Technical Service Manual

Horizontal Pixel 640 720 640 640 800 800 800 832 1024 1024 1024 1366 1280

Frequency KHz 31.469 31.469 37.861 37.500 37.879 46.875

Period (T1) ㎲ 31.778 31.778

Sync Width (T2) ㎲ 3.813 3.813 1.270 2.032 3.200 1.616

Back Porch (T3) ㎲ 1.887 1.907

Active (T4) ㎲ 25.422 25.422 20.317 20.317 20.000 16.162

Front Porch

(T5)

Vertical Lines 350 400 480 480 600 600 600 624 768 768 768 768 1024

Frequency Hz 70 70.080

Period (T1) ㎳ 14.268 14.268 13.735 13.333 16.579 13.333

Sync Width (T2) ㎳ 0.064 0.064

Back Porch (T3) ㎳ 1.906 1.080

Active (T4) ㎳ 11.122 12.711

Front Porch

(T5)

Interlaced Y/N N N N N N N N N N N N N N

Sync Polar H + - - - + + + + - - + + +

V - + - - + + + + - - + + +

㎲ 0.636 0.636

㎳ 1.176 0.413

26.413

3.810

0.508

72.809

0.079

0.528

12.678

0.026

26.667 26.400 21.333

3.810 2.200 3.232

0.508 1.000 0.323

75.000 60.316 75.000

0.080 0.106 0.064

0.427 0.607 0.448

12.800 15.840 12.800

0.027 0.026 0.021

48.077 49.725

20.800 20.111

2.400 1.117

1.280 3.910

16.000 14.524

1.120 0.559

72.188 74.550

13.853 13.414

0.125 0.060

0.478 0.784

12.480 12.549

0.770 0.021

48.363 56.476 60.023 61.27 63.981

20.677 17.707 16.660 16.321 15.630

2.092 1.813 1.219 0.451 1.037

2.462 1.920 2.235 2.294 2.296

15.754 13.653 13.003 12.843 11.852

0.369 0.320 0.203 0.734 0.445

60.004 70.069 75.029 74.994 60.020

16.666 14.272 13.328 13.334 16.661

0.124 0.106 0.050 0.082 0.047

0.600 0.513 0.466 0.506 0.594

15.880 13.599 12.795 12.535 16.005

0.062 0.053 0.017 0.212 0.015

--17--

Page 19

7. Input connector Characteristics

7.1 PC connector cable

The Pin assignments shall be listed as below.

PIN No. Assignment

1 Red

2 Green

3 Blue

4 GND

5 GND

6 Red GND

7 Green GND

8 Blue GND

9 BLANK

10 SYNC GND

11 GND

12 SDA

13 H-SYNC

14 V-SYNC

15 SCL

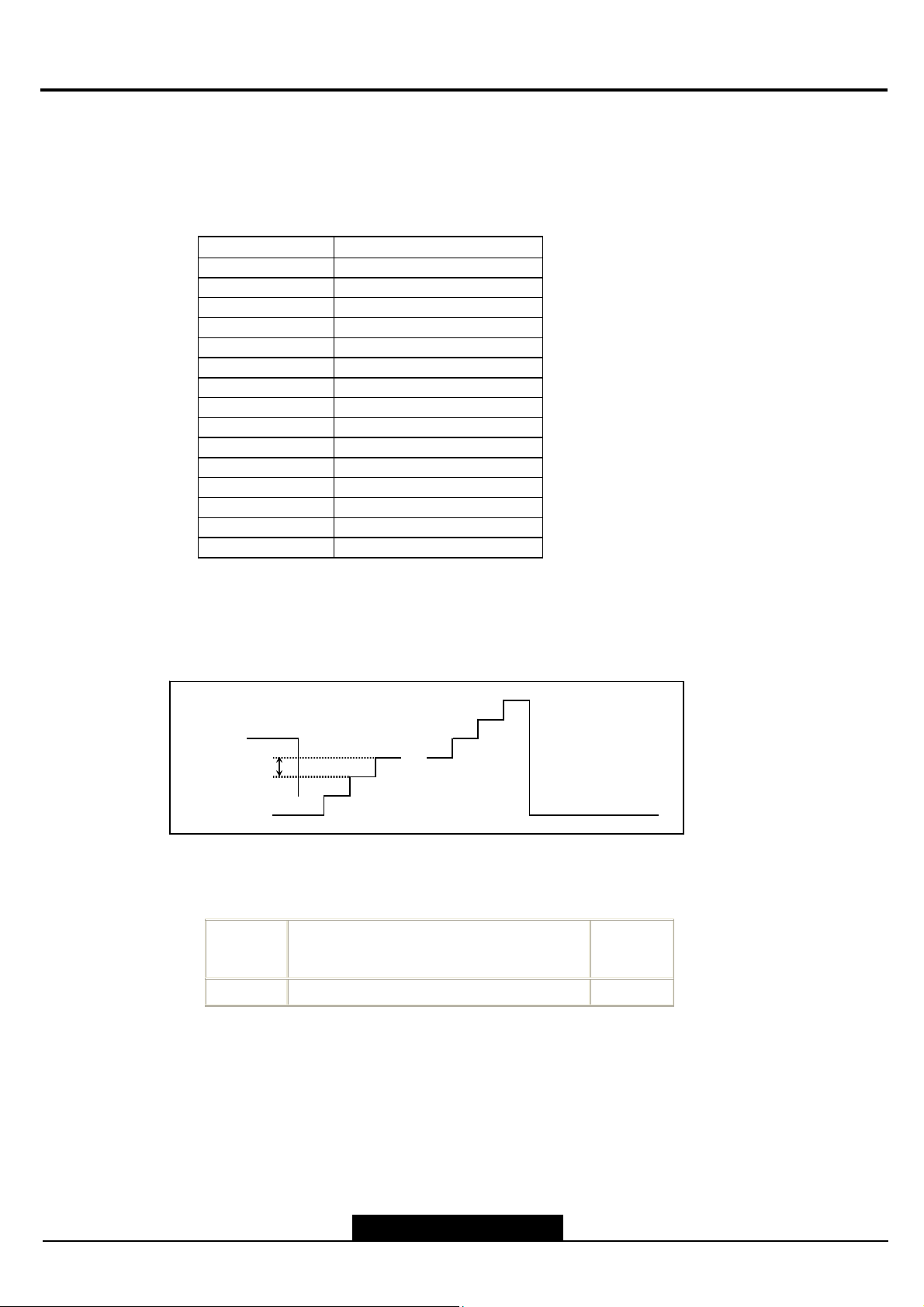

- Video signals on 75 ohm termination to the ground

Red, Green & Blue Video (refer to Fig.3.1)

Level : 0 to 0.7 Vp-p Polarity : Positive

2.74mV

Blanking

7.2 SCART (EURO) Connector

Pin

number

1 Right audio out (500mV rms Lo Z)

Fig. 3.1 - Video Signal

Description

700mV

Video

--18--

Page 20

Marantz Technical Service Manual

2 Right audio in (500mV rms Hi Z)

3 Left audio out (500mV rms Lo Z)

4 Audio ground

5 Blue video ground GND

6 Left audio in (500mV rms Hi Z)

7 Blue video in (700mV p-p 75R) INPUT

8 Source switching / 16x9 [note 1]

9 Green video ground GND

10 Data bus

11 Green video in (700mV p-p 75R) INPUT

12 Data bus

13 Red video ground GND

14 Data bus ground

15 Red video in (700mV p-p 75R)

16 Fast blanking (<0.5V off , >1V on) [note 2]

C

IN

IN

17 Composite video ground GND

18 Fast blanking ground

19 Composite video out (1V inc syncs) OUTPUT

20 Composite video in (1V inc syncs)

21 Chassis ground

(pictured looking at solder side of plug)

Y

IN

IN

--19--

Page 21

Note 1: (Pin 8 usage)

On many TV's taking pin 8 high will auto select the SCART input. With a voltage range of 4.5V to

7.0V

a compatible set will select AV input in 16x9 mode. With a voltage range of 9.5v to 12.0v

the set will select AV input in 4x3 mode.

It has come to my attention that certain newer sets (notably those containing Sony CXA2069A

chipset)

implement a third intermediate switching level. Details are sketchy,

but it would appear to select a letterbox format rather than full 4:3 or full 16:9.

Note 2 :

On some devices pin 16 is used to select between composite or RGB input modes using the

same SCART.

With a voltage of 1-3V DC (with respect to pin 18) RGBS input mode is selected.

The switching signal needs to be able to source upto 20mA.

With a voltage range of 0-0.4V composite mode is selected

Scart supports CVBS Signals , RGB(Full-Scart) and Audio Right Left ,

and Y-C Mode Signals is not Supported.

(Pin 16 usage)

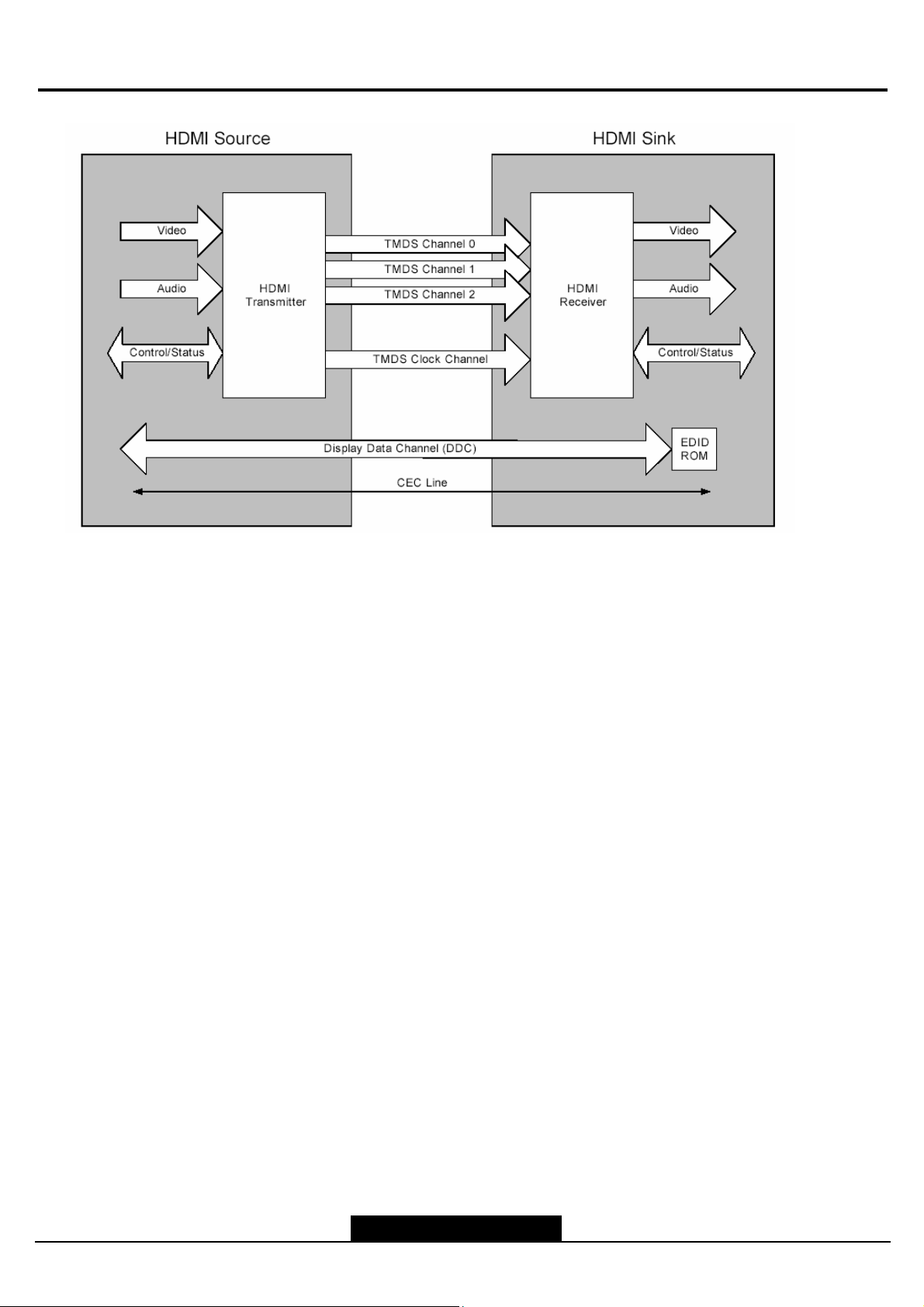

7.3 HDMI (High-Definition Multimedia Interface)

7.3.1 Overview

-HDMI system architecture is defined to consist of Sources and Sinks.

A given device may have one or more HDMI inputs and one or more HDMI outputs.

Each HDMI input on these devices shall follow all of the rules for an HDMI Sink

and each HDMI output shall follow all of the rules for an HDMI Source.

- As shown in Figure 12-1 HDMI Block Diagram the HDMI cable and connectors

carry four differential pairs that make up the TMDS data and clock channels.

These channels are used to carry video, audio and auxiliary data. In addition,

HDMI carries a VESA DDC channel. The DDC is used for configuration and status

exchange between a single Source and a single Sink.

The optional CEC protocol provides high-level control functions between

all of the various audiovisual products in a user’s environment.

--20--

Page 22

Marantz Technical Service Manual

12-1 HDMI Block Diagram

- Audio, video and auxiliary data is transmitted across the three TMDS data channels.

The video pixel clock is transmitted on the TMDS clock channel and is used by the

receiver

as a frequency reference for data recovery on the three TMDS data channels.

- Video data is carried as a series of 24-bit pixels on the three TMDS data channels.

TMDS encoding converts the 8 bits per channel into the 10 bit DC-balanced, transition

minimized

sequence which is then transmitted serially across the pair at a rate of 10 bits per pixel

clock period.

- Video pixel rates can range from 25MHz to 165MHz. Video formats with rates below

25MHz

can be transmitted using a pixel-repetition scheme. The video pixels can be encoded in

either RGB,

BCR 4:4:4 or YCBCR 4:2:2 formats. In all three cases, up to 24 bits per pixel can be

YC

transferred.

- Basic audio functionality consists of a single IEC 60958 audio stream at sample rates of

32kHz, 44.1kHz

or 48kHz. This can accommodate any normal stereo stream. Optionally, HDMI can carry a

single such

--21--

Page 23

stream at sample rates up to 192KHz or from two to four such streams (3 to 8 audio

channels) at sample

rates up to 96KHz. HDMI can also carry IEC 61937 compressed (e.g. surround-sound)

stream at sample

rates up to 192kHz.

- The DDC is used by the Source to read the Sink’s Enhanced Extended Display

Identification Data

(E-EDID) in order to discover the Sink.s configuration and/or capabilities.

7.3.2 Connectors and Cables

- A device.s external HDMI connection shall be presented via one of the two specified

HDMI connectors,

Type A or Type B. This connector can be attached directly to the device or can be

attached via a cable

adapter that is shipped with the device.

- The Type A connector carries all required HDMI signals, including a single TMDS link.

The Type B

connector is slightly larger and carries a second TMDS link, which is necessary to support

very high-

resolution computer displays requiring dual link bandwidth. A passive cable adapter

between Type A and

Type B connectors is specified.

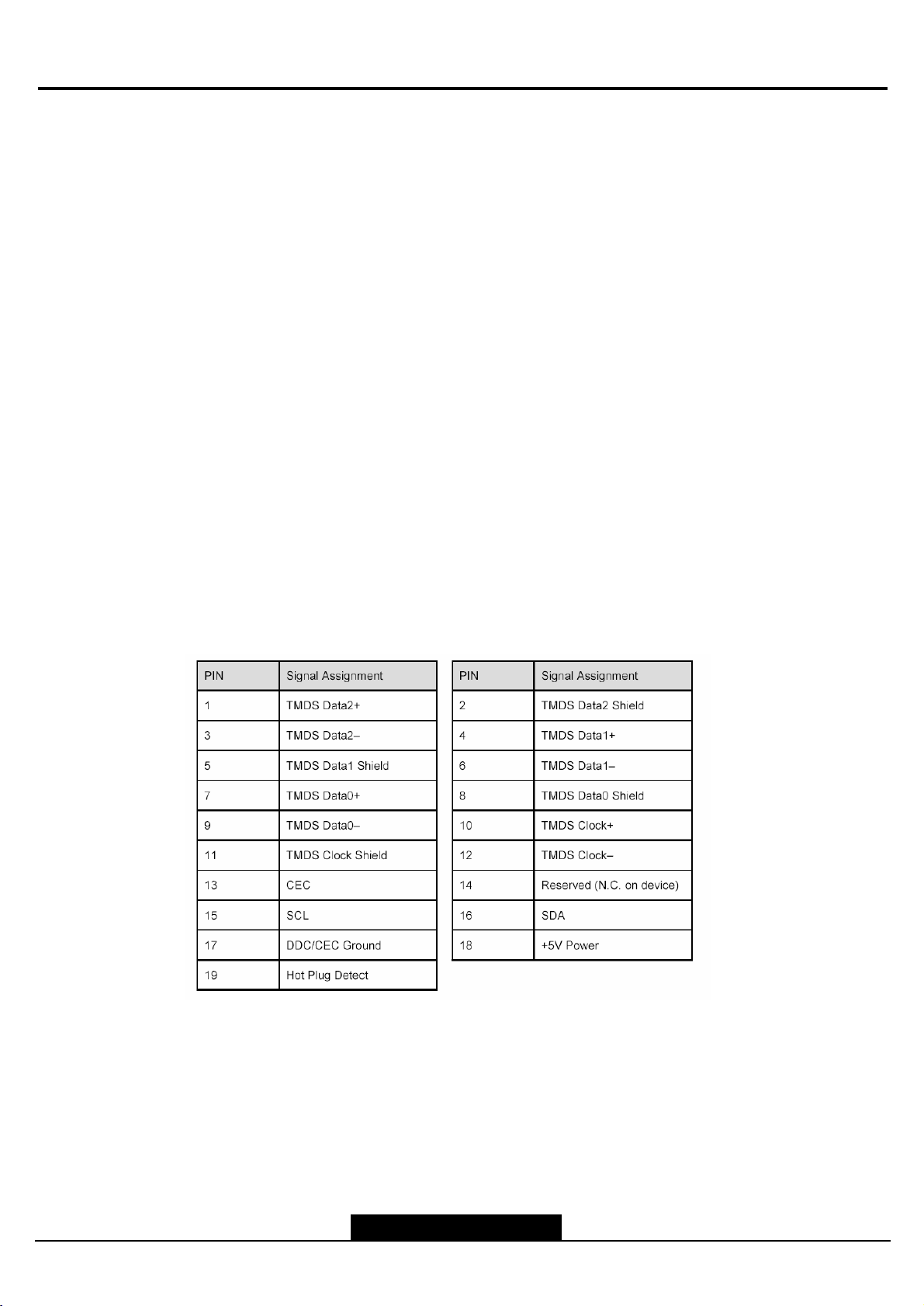

7.3.3 Connectors Pin Assignment

Type A connector Pin Assingment

--22--

Page 24

Marantz Technical Service Manual

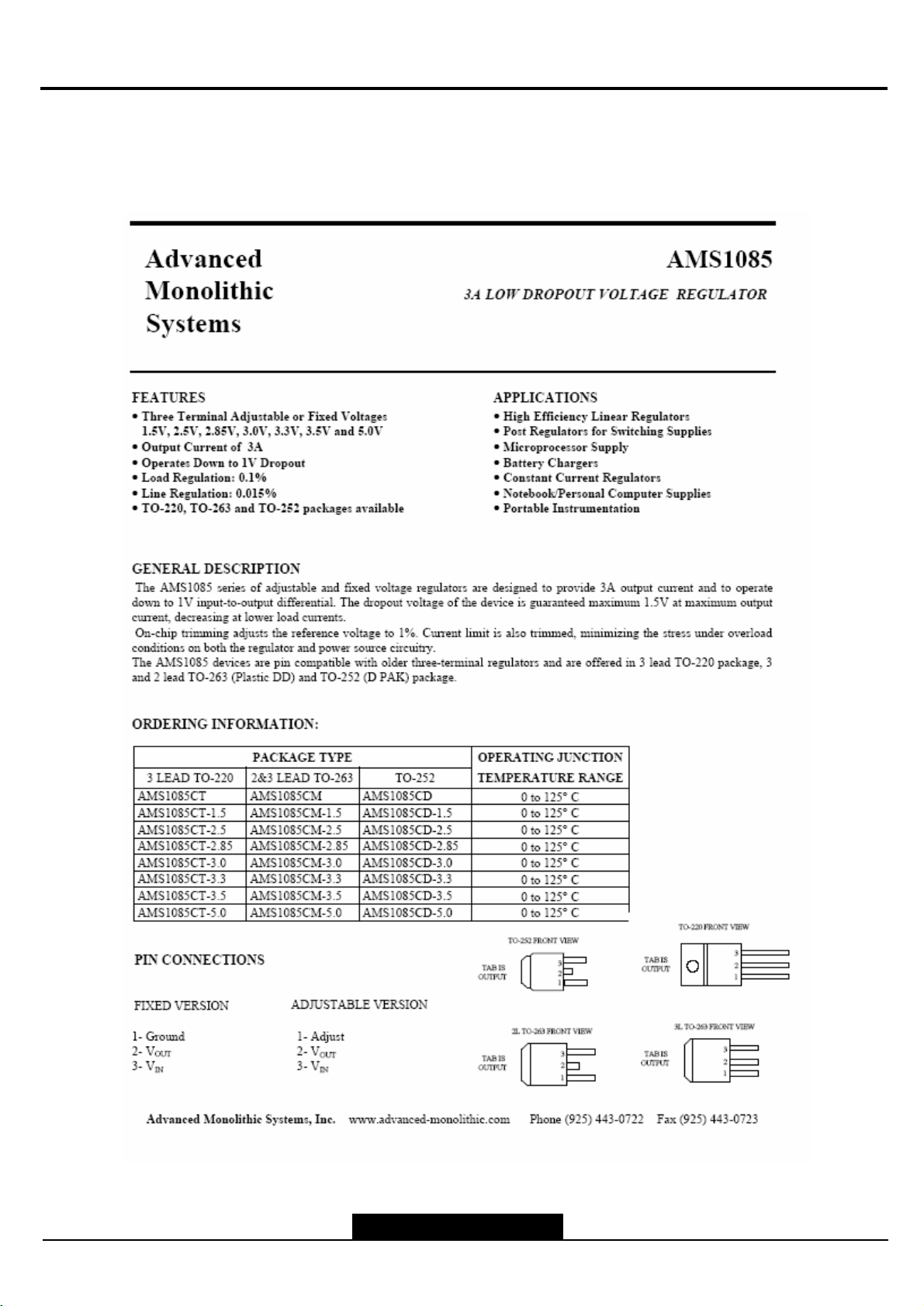

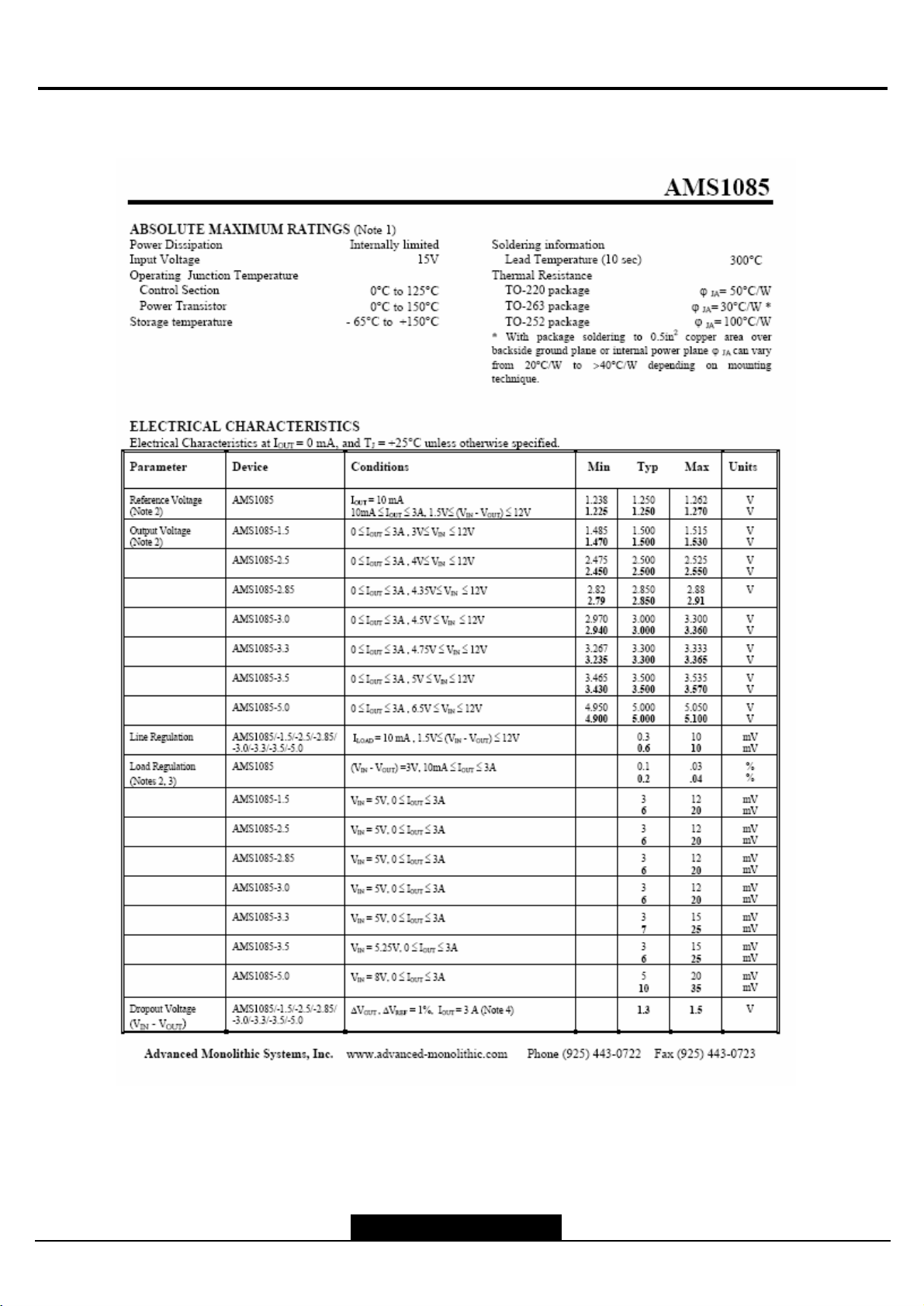

AMS1085

--23--

Page 25

--24--

Page 26

Marantz Technical Service Manual

--25--

Page 27

--26--

Page 28

Audio

8X

De

-

emphasis

8X

Ü

Í DAC

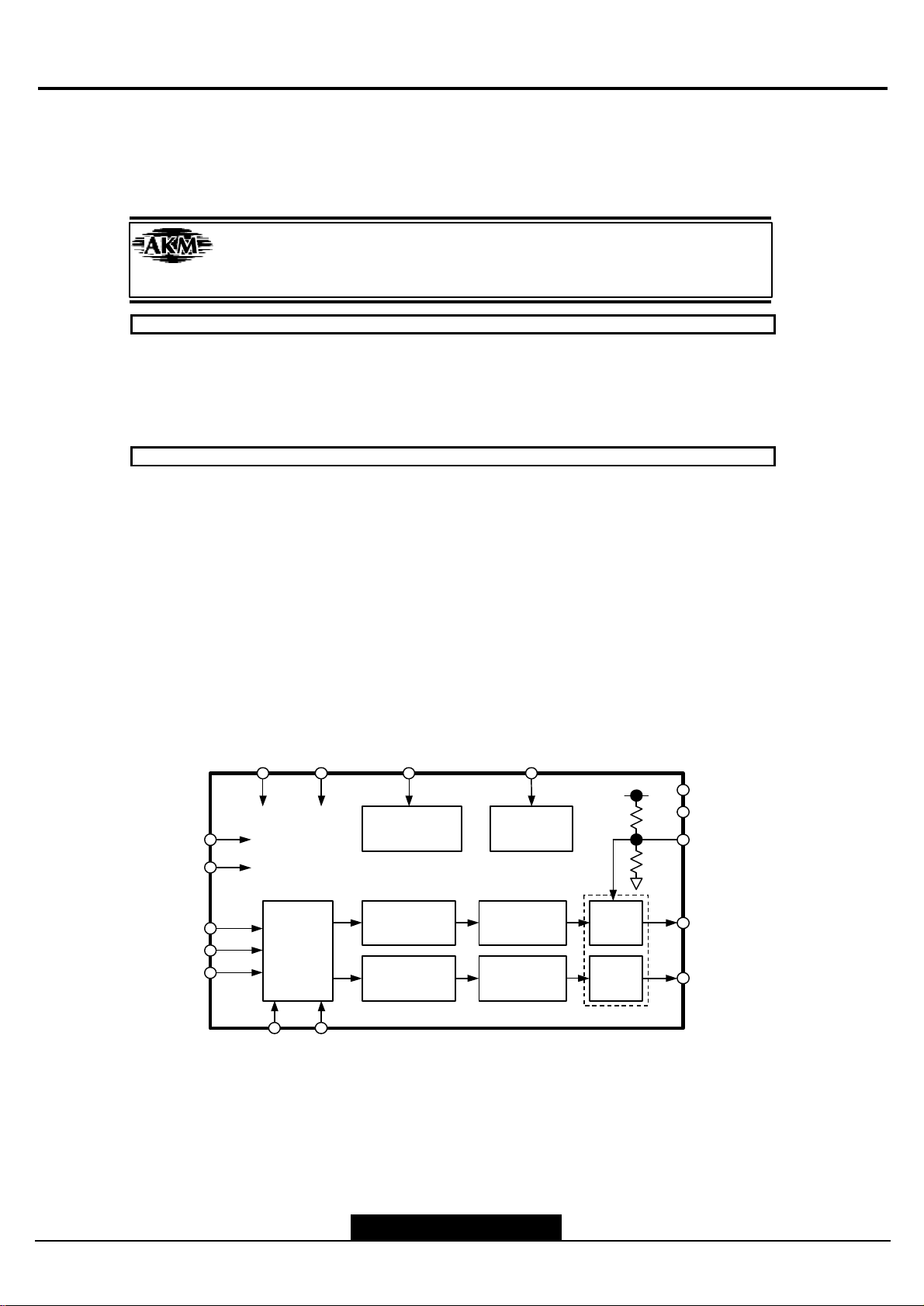

AK4386

Marantz Technical Service Manual

AK4386

ASAHI KASEI [AK4386]

The AK4386 is a 24bit low voltage & low power stereo DAC. The AK4386 uses the Advanced Multi-Bit ∆Σ

architecture, this architecture achieves DR=100dB at 3V operation. The AK4386 integrates a

combination of SCF and CTF filters increasing performance for systems with excessive clock jitter. The

AK4386 is suitable for the portable audio system like MP3 and the home audio systems like STB and TV,

etc as low power and small package. The AK4386 is offered in a space saving 16pin TSSOP package.

o Sampling Rate: 8kHz ¢ 96kHz

o 24-Bit 8 times FIR Digital Filter

o SCF with high tolerance to clock jitter

o Single-ended output buffer

o Digital de-emphasis for 44.1kHz sampling

o I/F Format: 24-Bit MSB justified, 16/24-Bit LSB justified, I2S Compatible

o Master Clock:

o CMOS Input Level

o THD+N: ó86dB

o DR, S/N: 100dB(@VDD=3.0V)

o Power Supply: 2.2 to 3.6V

o Ta = ó40 ¢ 85pC

o 16pin TSSOP

100dB 96kHz 24-Bit 2ch

GENERAL DESCRIPTION

FEATURES

512/768/1024/1536fs for Half Speed (8kHz ¢ 24kHz)

256/384/512/768fs for Normal Speed (8kHz ¢ 48kHz)

128/192/256/384fs for Double Speed (48kHz ¢ 96kHz)

PDN

LRCK

BICK

SDTI

MS0280-E-00 2003/12

Data

Interface

DEMTEST

Control

Interpolator

Interpolator

-1-

MCLK

Clock

Divider

∆Σ

Modulator

∆Σ

Modulator

SCF

CTF

SCF

CTF

VDD

VSS

VCOM

LOUT

ROUT

--27--

Page 29

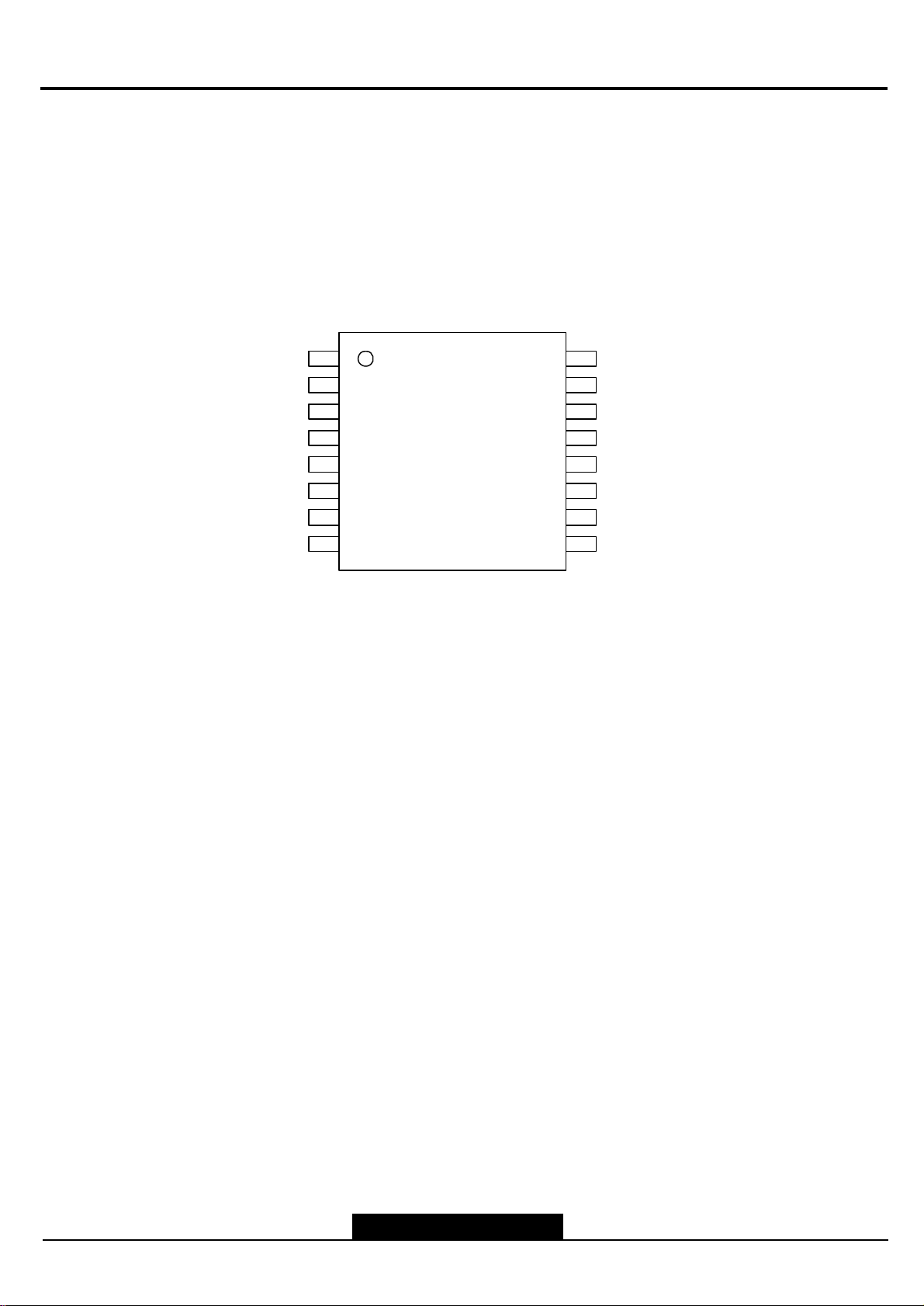

ASAHI KASEI [AK4386]

nOrdering Guide

AK4386VT

AKD4386 Evaluation Board for AK4386

n Pin Layout

MCLK

BICK

SDTI

LRCK

PDN

DFS0

DFS1

DEM

−40∼

+85°C 16pin TSSOP (0.65mm pitch)

1

2

3

4

Top View

5

6

7

8

16

15

14

13

12

11

10

9

TEST

DIF1

VDD

VSS

VCOM

LOUT

ROUT

DIF0

MS0280-E-00 2003/12

-2-

--28--

Page 30

Marantz Technical Service Manual

ASAHI KASEI [AK4386]

No.Pin Name I/OFunction

1MCLK IMaster Clock Input Pin

2BICK IAudio Serial Data Clock Pin

3SDTI IAudio Serial Data Input Pin

4LRCK IInput Channel Clock Pin

5PDN I

6DFS0 ISampling Speed Select 0 Pin

7DFS1 ISampling Speed Select 1 Pin

8DEM I

9DIF0 IAudio Interface Format 0 Pin

10ROUT O Rch Analog Output Pin

11LOUT O Lch Analog Output Pin

12VCOM O

13VSS -Ground Pin

14VDD 15DIF1 IAudio Interface Format 1 Pin

16TEST I

PIN/FUNCTION

Full Power Down Mode Pin

“L” : Power down, “H” : Power up

De-emphasis Filter Enable Pin

“L” : OFF, “H” : ON (De-emphasis of fs=44.1kHz is enable.)

Common Voltage Output Pin, 0.55 × VDD

Normally connected to VSS with a 4.7µF (min. 1µF, max. 10µF) electrolytic

capacitor.

Power Supply Pin, 2.2 ∼ 3.6V

TEST Pin

This pin should be connected to VDD.

Note: All digital input pins should not be left floating.

n Handling of Unused Pin

The unused output pins should be processed appropriately as below.

Classification Pin Name Setting

Analog LOUT, ROUT This pin should be open.

MS0280-E-00 2003/12

-3-

--29--

Page 31

HY5DU281622ET

HY5DU281622ET

DESCRIPTION

The Hynix HY5DU281622ET is a 134,217,728-bit CMOS Double Data Rate(DDR) Synchronous DRAM, ideally suited for

the point-to-point applications which require high densities and high bandwidth.

The Hynix 8Mx16 DDR SDRAMs offer fully synchronous operations referenced to both rising and falling edges of the

clock. While all addresses and control inputs are latched on the rising edges of the CK (falling edges of the /CK), Data,

Data strobes and Write data masks inputs are sampled on both rising and falling edges of it. The data paths are internally pipelined and 2-bit prefetched to achieve very high bandwidth. All input and output voltage levels are compatible

with SSTL_2.

FEATURES

2.8V +/- 0.1V VDD and VDDQ power supply

supports 400/375/350/333/300MHz

2.5V +/- 5% VDD and VDDQ power supply

supports 275/250/200/166MHz

All inputs and outputs are compatible with SSTL_2

interface

JEDEC Standard 400 mil x 875 mil 66 Pin TSOP II,

with 0.65mm pin pitch

Fully differential clock inputs (CK, /CK) operation

Double data rate interface

Source synchronous - data transaction aligned to

bidirectional data strobe (UDQS,LDQS)

Data outputs on DQS edges when read (edged DQ)

Data inputs on DQS centers when write (centered

DQ)

Data(DQ) and Write masks(DM) latched on the both

rising and falling edges of the data strobe

All addresses and control inputs except Data, Data

strobes and Data masks latched on the rising edges

of the clock

Write mask byte controls by DM (UDM,LDM)

Programmable /CAS Latency 5, 4 and 3 are sup-

ported

Programmable Burst Length 2, 4 and 8 with both

sequential and interleave mode

Internal 4 bank operation with single pulsed /RAS

tRAS Lock-Out function are supported

Auto refresh and self refresh are supported

4096 refresh cycles / 32ms

Full strength, Half strength and Weak Impedance

driver options controlled by EMRS

ORDERING INFORMATION

Part No.

HY5DU281622ET-25

HY5DU281622ET-26375MHz750Mbps/pin

HY5DU281622ET-28350MHz700Mbps/pin

HY5DU281622ET-30333MHz666Mbps/pin

HY5DU281622ET-33300MHz600Mbps/pin

HY5DU281622ET-36

HY5DU281622ET-4250MHz500Mbps/pin

HY5DU281622ET-5200MHz400Mbps/pin

Power

Supply

VDD/VDDQ=2.8V

VDD/VDDQ=2.5V

Clock

Frequency

400MHz800Mbps/pin

275MHz550Mbps/pin

Max Data Rate interface Package

--30--

SSTL_2

400 x 875mil

66 Pin TSOP II

2

Page 32

Marantz Technical Service Manual

PIN CONFIGURATION (Top View)

HY5DU281622ET

VDD

DQ0

VDDQ

DQ1

DQ2

VSSQ

DQ3

DQ4

VDDQ

DQ5

DQ6

VSSQ

DQ7

NC

VDDQ

LDQS

NC

VDD

NC

LDM

/WE

/CAS

/RAS

/CS

NC

BA0

BA1

A10/AP

A0

A1

A2

A3

VDD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

0.65mm pin pitch

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

400mil X 875mil

66pin TSOP -II

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

VSS

DQ15

VSSQ

DQ14

DQ13

VDDQ

DQ12

DQ11

VSSQ

DQ10

DQ9

VDDQ

DQ8

NC

VSSQ

UDQS

NC

VREF

VSS

UDM

/CK

CK

CKE

NC

NC

A11

A9

A8

A7

A6

A5

A4

VSS

ROW AND COLUMN ADDRESS TABLE

ITEMS 8Mx16

Organization 2M x 16 x 4banks

Row Address A0 - A11

Column Address A0-A8

Bank Address BA0, BA1

Auto Precharge Flag A10

Refresh 4K

--31--

Page 33

PIN DESCRIPTION

PIN TYPE DESCRIPTION

HY5DU281622ET

CK, /CKInput

CKEInput

/CSInput

BA0, BA1Input

A0 ~ A11Input

/RAS, /CAS, /WEInput

UDM, LDMInput

UDQS, LDQS I/O

DQ0 ~ DQ15I/OData input / output pin : Data Bus

VDD/VSS SupplyPower supply for internal circuits and input buffers.

VDDQ/VSSQ SupplyPower supply for output buffers for noise immunity.

V REF SupplyReference voltage for inputs for SSTL interface.

NCNCNo connection.

Clock: CK and /CK are differential clock inputs. All address and control input signals are

sampled on the crossing of the positive edge of CK and negative edge of /CK. Output

(read) data is referenced to the crossings of CK and /CK (both directions of crossing).

Clock Enable: CKE HIGH activates, and CKE LOW deactivates internal clock signals, and

device input buffers and output drivers. Taking CKE LOW provides PRECHARGE POWER

DOWN and SELF REFRESH operation (all banks idle), or ACTIVE POWER DOWN (row

ACTIVE in any bank). CKE is synchronous for POWER DOWN entry and exit, and for SELF

REFRESH entry and exit. CKE is asynchronous for output disable. CKE must be maintained high throughout READ and WRITE accesses. Input buffers, excluding CK, /CK and

CKE are disabled during POWER DOWN. Input buffers, excluding CKE are disabled during

SELF REFRESH. CKE is an SSTL_2 input, but will detect an LVCMOS LOW level after Vdd

is applied.

Chip Select : Enables or disables all inputs except CK, /CK, CKE, DQS and DM. All commands are masked when CS is registered high. CS provides for external bank selection on

systems with multiple banks. CS is considered part of the command code.

Bank Address Inputs: BA0 and BA1 define to which bank an ACTIVE, Read, Write or PRECHARGE command is being applied.

Address Inputs: Provide the row address for ACTIVE commands, and the column address

and AUTO PRECHARGE bit for READ/WRITE commands, to select one location out of the

memory array in the respective bank. A10 is sampled during a precharge command to

determine whether the PRECHARGE applies to one bank (A10 LOW) or all banks (A10

HIGH). If only one bank is to be precharged, the bank is selected by BA0, BA1. The

address inputs also provide the op code during a MODE REGISTER SET command. BA0

and BA1 define which mode register is loaded during the MODE REGISTER SET command

(MRS or EMRS).

Command Inputs: /RAS, /CAS and /WE (along with /CS) define the command being

entered.

Input Data Mask: DM is an input mask signal for write data. Input data is masked when

DM is sampled HIGH along with that input data during a WRITE access. DM is sampled

on both edges of DQS. Although DM pins are input only, the DM loading matches the DQ

and DQS loading. LDM corresponds to the data on DQ0-Q7; UDM corresponds to the data

on DQ8-Q15

Data Strobe: Output with read data, input with write data. Edge aligned with read data,

centered in write data. Used to capture write data. LDQS corresponds to the data on

DQ0-Q7; UDQS corresponds to the data on DQ8-Q15

--32--

Page 34

Marantz Technical Service Manual

K4S643232H

SDRAM 64Mb H-die (x32)

CMOS SDRAM

512K x 32Bit x 4 Banks

FEATURES

? JEDEC standard 3.3V power supply

? LVTTL compatible with multiplexed address

? Four banks operation

? MRS cycle with address key programs

-. CAS latency (2 & 3)

-. Burst length (1, 2, 4, 8 & Full page)

-. Burst type (Sequential & Interleave)

? All inputs are sampled at the positive going edge of the system clock.

? Burst read single-bit write operation

? DQM (x4,x8) & L(U)DQM (x16) for masking

? Auto & self refresh

? 15.6us refresh duty cycle

GENERAL DESCRIPTION

The K4S643232H is 67,108,864 bits synchronous high data rate Dynamic RAM organized as 4 x 524,288 words by 32 bits, fabricated

with SAMSUNG s high performance CMOS technology. Synchronous design allows precise cycle control with the use of system clock.

I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst length and programmable

latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.

Ordering Information

Part No. Orgainization Max Freq. Interface Package

K4S643232H-TC/L70512K x 32 143MHzLVTTL86pin TSOP

K4S643232H-TC/L60512K x 32166MHzLVTTL86pin TSOP

K4S643232H-TC/L55512K x 32183MHzLVTTL86pin TSOP

K4S643232H-TC/L50512K x 32200MHzLVTTL86pin TSOP

Organization Row Address Column Address

1Mx32A0~A10A0-A7

Row & Column address configuration

3 -

--33--

Page 35

SDRAM 64Mb H-die (x32)

Package Physical Dimension

CMOS SDRAM

0.10

0.004

MAX

#86

#1

0.61

( )

0.024

#44

#43

22.62

MAX

0.891

22.22

0.20

0.0079

0.875

+0.07

-0.03

0.003

-0.001

0.10

0.004

0.50

0.0197

0.21

0.008

0.05

0.002

86Pin TSOP Package Dimension

1.00

0.039

0.10

0.004

0.25

0.010

0.125

0.005

1.20

0.047

TYP

+0.075

-0.035

+0.003

-0.001

MAX

0.05

0.002

0~8 C

MIN

- 4 -

--34--

Page 36

Marantz Technical Service Manual

SDRAM 64Mb H-die (x32)

FUNCTIONAL BLOCK DIAGRAM

Bank Select

CLK

ADD

Data Input Register

512K x 32

512K x 32

512K x 32

512K x 32

Column Decoder

Latency & Burst Length

CMOS SDRAM

LWE

LDQM

DQi

LCKE

LRASLCBRLWE

CLKCKECS RAS CAS WE DQM

LCASLWCBR

Timing Register

Programming Register

-

--35--

Page 37

SDRAM 64Mb H-die (x32)

PIN FUNCTION DESCRIPTION

Pin Name Input Function

CLK System clock Active on the positive going edge to sample all inputs.

CS Chip select

CKE Clock enable

A0 ~ A10 Address

BA0,1 Bank select address

RAS Row address strobe

CAS Column address strobe

WE Write enable

DQM0 ~ 3 Data input/output mask

DQ0 ~ 31 Data input/output Data inputs/outputs are multiplexed on the same pins.

VDD/VSS Power supply/ground Power and ground for the input buffers and the core logic.

VDDQ/VSSQ Data output power/ground

NC No Connection This pin is recommended to be left No connection on the device.

Disables or enables device operation by masking or enabling all inputs except

CLK, CKE and DQM.

Masks system clock to freeze operation from the next clock cycle.

CKE should be enabled at least one cycle prior to new command.

Disables input buffers for power down mode.

Row/column addresses are multiplexed on the same pins.

Row address : RA0 ~ RA10, Column address : CA0 ~ CA7

Selects bank to be activated during row address latch time.

Selects bank for read/write during column address latch time.

Latches row addresses on the positive going edge of the CLK with RAS low.

Enables row access & precharge.

Latches column addresses on the positive going edge of the CLK with CAS low.

Enables column access.

Enables write operation and row precharge.

Latches data in starting from CAS, WE active.

Makes data output Hi-Z, tSHZ after the clock and masks the output.

Blocks data input when DQM active.

Isolated power supply and ground for the output buffers to provide improved noise

immunity.

CMOS SDRAM

- 7 -

--36--

Page 38

Marantz Technical Service Manual

K6X4008T1F

K6X4008T1F Family CMOS SRAM

512K×8 bit Low Power and Low Voltage CMOS Static RAM

FEATURES

• Process Technology: Full CMOS

• Organization: 512K×8

• Power Supply Voltage: 2.7~3.6V

• Low Data Retention Voltage: 2V(Min)

• Three State Outputs

• Package Type: 32-SOP-525, 32-TSOP2-400F/R

32-TSOP1-0813.4F

GENERAL DESCRIPTION

The K6X4008T1F families are fabricated by SAMSUNG′s

advancedfullCMOS process technology. The families support

various operating temperature range and have various package types for user flexibility of system design. The families also

support low data retention voltage for battery back-up operation

with low data retention current.

PRODUCT FAMILY

Product Family Operating Temperature

K6X4008T1F-B Commercial(0~70°C)

K6X4008T1F-F Industrial(-40~85°C) 10µA

K6X4008T1F-QAutomotive(-40~125°C)

1. This parameter is measured in the voltage range of 3.0V~3.6V with 30pF test load.

2. This parameter is measured with 30pF test load.

Vcc

Range

2.7~3.6V

Speed

551)/702)/85ns

702)/85ns

PIN DESCRIPTION

A18

1

A16

2

3

A14

4

A12

A7

5

A6

6

A5

7

32-SOP

A4

8

32-TSOP2

A3

9

(Forward)

A2

10

A1

11

A0

12

I/O1

13

I/O2

14

I/O3

15

VSS

16

A11

1

A9

2

A8

3

A13

4

WE

5

A17

6

A15

7

VCC

8

A18

9

A16

10

A14

11

A12

12

A7

13

A6

14

A5

15

A4

16

Name Function Name Function

A0~A18 Address Inputs Vcc Power

WE Write Enable Input Vss Ground

CS Chip Select InputI/O1~I/O8 Data Inputs/Outputs

OE Output Enable Input

VCC

32

A15

31

A17

30

WE

29

A13

28

A8

27

A9

26

A11

25

OE

24

23

A10

22

CS

21

I/O8

20

I/O7

19

I/O6

18

I/O5

17

I/O4

32-STSOP1

(Forward)

VCC

A15

A17

WE

A13

A11

A10

I/O8

I/O7

I/O6

I/O5

I/O4

32

31

30

29

28

A8

27

A9

26

32-TSOP2

25

24

23

22

21

20

19

18

17

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

(Reverse)

OE

A10

CS

I/O8

I/O7

I/O6

I/O5

I/O4

VSS

I/O3

I/O2

I/O1

A0

A1

A2

A3

OE

CS

1

A18

A16

2

3

A14

4

A12

A7

5

A6

6

A5

7

A4

8

A3

9

A2

10

A1

11

A0

12

I/O1

13

I/O2

14

I/O3

15

VSS

16

Power Dissipation

Standby

(ISB1, Max)

FUNCTIONAL BLOCK DIAGRAM

Row

Addresses

I/O1 Data

I/O8

CS

WE

OE

10µA

20µA

Control

logic

Operating

(ICC2, Max)

25mA

Clk gen.

Row

select

cont

Data

cont

PKG Type

32-SOP-525, 32-TSOP1-0813.4F

32-TSOP2-400F/R

32-SOP-525, 32-TSOP1-0813.4F

32-TSOP2-400F

Precharge circuit.

Memory array

I/O Circuit

Column select

Column Addresses

SAMSUNG ELECTRONICS CO., LTD. reserves the right to change products and specifications without notice.

2

Revision 1.0

September 2003

--37--

Page 39

K6X4008T1F Family

PRODUCT LIST

Commercial Products(0~70°°C) Industrial Products(-40~85 °°C) Automotive Products(-40~125°°C)

Part Name Function Part Name Function Part Name Function

K6X4008T1F-GB55

K6X4008T1F-GB70

K6X4008T1F-GB85

K6X4008T1F-YB55

K6X4008T1F-YB70

K6X4008T1F-YB85

K6X4008T1F-VB55

K6X4008T1F-VB70

K6X4008T1F-VB85

K6X4008T1F-MB55

K6X4008T1F-MB70

K6X4008T1F-MB85

1. Operating voltage range is 3.0V~3.6V

1)

32-SOP, 55ns, LL

32-SOP, 70ns, LL

32-SOP, 85ns, LL

1)

32-sTSOP1-F, 55ns, LL

32-sTSOP1-F, 70ns, LL

32-sTSOP1-F, 85ns, LL

1)

32-TSOP2-F, 55ns, LL

32-TSOP2-F, 70ns, LL

32-TSOP2-F, 85ns, LL

1)

32-TSOP2-R, 55ns, LL

32-TSOP2-R, 70ns, LL

32-TSOP2-R, 85ns, LL

K6X4008T1F-GF55

K6X4008T1F-GF70

K6X4008T1F-GF85

K6X4008T1F-YF55

K6X4008T1F-YF70

K6X4008T1F-YF85

K6X4008T1F-VF55

K6X4008T1F-VF70

K6X4008T1F-VF85

K6X4008T1F-MF55

K6X4008T1F-MF70

K6X4008T1F-MF85

FUNCTIONAL DESCRIPTION

CS OE WE I/O Mode Power

H

1)

X

L H H High-Z Output Disabled Active

L L H Dout Read Active

L

1. X means don′t care (Must be in low or high state)

1)

X

1)

X

L Din Write Active

1)

32-SOP, 55ns, LL

32-SOP, 70ns, LL

32-SOP, 85ns, LL

1)

32-sTSOP1-F, 55ns, LL

32-sTSOP1-F, 70ns, LL

32-sTSOP1-F, 85ns, LL

1)

32-TSOP2-F, 55ns, LL

32-TSOP2-F, 70ns, LL

32-TSOP2-F, 85ns, LL

1)

32-TSOP2-R, 55ns, LL

32-TSOP2-R, 70ns, LL

32-TSOP2-R, 85ns, LL

K6X4008T1F-GQ70

K6X4008T1F-GQ85

K6X4008T1F-YQ70

K6X4008T1F-YQ85

K6X4008T1F-VQ70

K6X4008T1F-VQ85

32-SOP, 70ns, L

32-SOP, 85ns, L

32-sTSOP1-F, 70ns, L

32-sTSOP1-F, 85ns, L

32-TSOP2-F, 70ns, L

32-TSOP2-F, 85ns, L

High-Z Deselected Standby

ABSOLUTE MAXIMUM RATINGS

1)

Item Symbol Ratings Unit Remark

Voltage on any pin relative to Vss VIN, VOUT -0.2 to VCC+0.3(max. 3.9V) V Voltage on Vcc supply relative to Vss VCC -0.2 to 3.9 V Power Dissipation PD 1.0 W Storage temperature TSTG -65 to 150 °C -

0 to 70 °C K6F4008T1F-B

Operating Temperature TA

-40 to 85 °C K6F4008T1F-F

-40 to 125 °C K6F4008T1F-Q

1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation should be

restricted to recommended operating condition. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

--38--

Page 40

Marantz Technical Service Manual

K6X4008T1F Family

-0.2

1)

2)

Vcc+0.2

3)

- 0.6 V

V

RECOMMENDED DC OPERATING CONDITIONS

Item Symbol Min Typ Max Unit

Supply voltage Vcc 2.7 3.0/3.3 3.6 V

Ground Vss 0 0 0 V

Input high voltage VIH 2.2 Input low voltage VIL

Note:

1.Commercial Product: TA=0 to 70°C, otherwise specified

Industrial Product: TA=-40 to 85°C, otherwise specified

Automotive Product: TA=-40 to 125°C, otherwise specified

2. Overshoot: VCC+2.0V in case of pulse width ≤ 30ns

3. Undershoot: -2.0V in case of pulse width ≤ 30ns

4. Overshoot and undershoot are sampled, not 100% tested.

CAPACITANCE

Input capacitance CIN VIN=0V - 8 pF

Input/Output capacitance CIO VIO=0V - 10 pF

1. Capacitance is sampled, not 100% tested.

1)

(f=1MHz, TA=25°C)

Item Symbol Test Condition Min Max Unit

DC AND OPERATING CHARACTERISTICS

Item Symbol Test Conditions Min Typ Max Unit

Input leakage current ILI VIN=Vss to Vcc -1 - 1 µA

Output leakage current ILO CS=VIH or OE=VIH or WE=VIL VIO=Vss to Vcc -1 - 1 µA

Operating power supply current ICC IIO=0mA,CS=VIL, VIN=VIL or VIH, Read - - 2 mA

Cycle time=1µs, 100% duty, IIO=0mACS≤0.2V,VIN≤0.2V or VIN≥Vcc-0.2V

Average operating current

Output low voltage VOL IOL=2.1mA - -0.4 V

Output high voltage VOH IOH=-1.0mA 2.4 - - V

Standby Current(TTL) ISB CS=VIH, Other inputs = VIL or VIH - -0.3mA

Standby Current (CMOS) ISB1 CS≥Vcc-0.2V, Other inputs=0~Vcc

ICC1

Cycle time=Min, 100% duty, IIO=0mA,CS=VIL, VIN=VIHor VIL

ICC2

K6X4008T1F-B - - 10 µA

K6X4008T1F-F - - 10 µA

K6X4008T1F-Q - - 20 µA

- - 3 mA

- - 25mA

--39--

Page 41

K6X4008T1F Family

AC OPERATING CONDITIONS

TEST CONDITIONS(Test Load and Input/Output Reference)

Input pulse level: 0.4 to 2.2V

Input rising and falling time: 5ns

Input and output reference voltage: 1.5V

Output load(see right): CL=100pF+1TTL

1. 55ns,70ns product

CL1)=30pF+1TTL

AC CHARACTERISTICS

(VCC=2.7~3.6V, Commercial product: TA=0 to 70°C, Industrial product: TA=-40 to 85°C, Automotive product: TA=-40 to 125°C)

Parameter List Symbol

Min Max Min Max Min Max

Read cycle time tRC 55 - 70 - 85 - ns

Address access time tAA - 55 - 70 - 85 ns

Chip select to output tCO - 55 - 70 - 85 ns

Output enable to valid output tOE - 25 - 35 - 40 ns

Read

Chip select to low-Z output tLZ 10 - 10 - 10 - ns

Output enable to low-Z output tOLZ 5 - 5 - 5 - ns

Chip disable to high-Z output tHZ 0 20 0 25 0 25 ns

Output disable to high-Z output tOHZ 0 20 0 25 0 25 ns

Output hold from address change tOH 10 - 10 - 10 - ns

Write cycle time tWC 55 - 70 - 85 - ns

Chip select to end of write tCW 45 - 60 - 70 - ns

Address set-up time tAS 0 - 0 - 0 - ns

Address valid to end of write tAW 45 - 60 - 70 - ns

Write pulse width tWP 40 - 55 - 55 - ns

Write

Write recovery time tWR 0 - 0 - 0 - ns

Write to output high-Z tWHZ 0 20 0 25 0 25 ns

Data to write time overlap t DW 25 - 30 - 35 - ns

Data hold from write time tDH 0 - 0 - 0 - ns

End write to output low-Z tOW 5 - 5 - 5 - ns

1. Voltage range is 3.0V~3.6V for commercial and industrial product.

55ns

1)

1)

CL

1. Including scope and jig capacitance

Speed Bins

70ns 85ns

Units

DATA RETENTION CHARACTERISTICS

Item Symbol Test Condition Min

Vcc for data retention VDR CS≥Vcc-0.2V 2.0 - 3.6 V

K6X4008T1F-B -

Data retention current IDR Vcc=3.0V,CS≥Vcc-0.2V

Data retention set-up time tSDR

Recovery time tRDR 5 - -

1. Typical values are measured at TA = 25°C and not 100% tested.

See data retention waveform

K6X4008T1F-F - 10 µA

K6X4008T1F-Q - 20 µA

0 - -

Typ

0.5

1)

Max Unit

10 µA

--40--

ms

Page 42

Marantz Technical Service Manual

MST6151DA-LF

ЪЫЯМЛОЫН

Ч²°«¬-«°°±®¬-«°¬±ЛИЩЯъприрР

Р¿²»´ -«°°±®¬-«°¬±НИЩЯ

Ч²¬»¹®¿¬»¼¬©±у°±®¬¬®·°´»уЯЬЭсРФФ

Ч²¬»¹®¿¬»¼ЬКЧсШЬЭРсШЬУЧ½±³°´·¿²¬®»½»·ª»®

ЗЛКмоо¼·¹·¬¿´ª·¼»±·²°«¬°±®¬Ь«¿´¸·¹¸у¯«¿´·¬§-½¿´·²¹»²¹·²»Ю«·´¬у·²нуЬª·¼»±¼»у·²¬»®´¿½»®

К·¼»±у±ª»®у¹®¿°¸·½РЧР

К·¼»±у¾§у¹®¿°¸·½-°´·¬-½®»»²

УН¬¿®ЯЭЫуо¿¼ª¿²½»¼°·½¬«®»с½±´±® °®±½»--·²¹

»²¹·²»

Ы³¾»¼¼»¼С²у-½®»»²Ь·-°´¿§Э±²¬®±´´»®шСНЬч

»²¹·²»

Ю«·´¬у·²¼«¿´у´·²µФКЬН¬®¿²-³·¬¬»®

луК±´¬¬±´»®¿²¬·²°«¬Ф±©ЫУЧ¿²¼°±©»®-¿ª·²¹º»¿¬«®»Н«°°±®¬-РЙУъЩРС½±²¬®±´ориу°·²РПЪР°¿½µ¿¹»

Я²¿´±¹ОЩЮсЗР¾Р®Ч²°«¬Р±®¬-

Ь«¿´¿²¿´±¹°±®¬--«°°±®¬«°¬±пклУ¸¦

Н«°°±®¬РЭОЩЮ ·²°«¬«°¬±ЛИЩЯакрШ¦

Н«°°±®¬ШЬМКОЩЮсЗР¾Р®сЗЭ¾Э®«°¬±прирР

С²у½¸·°¸·¹¸у°»®º±®³¿²½»РФФН«°°±®¬Э±³°±-·¬»Н§²½¿²¼НСЩ

шН§²½у±²уЩ®»»²ч-»°¿®¿¬±®

Я«¬±³¿¬·½½±´±®½¿´·¾®¿¬·±²

ЬКЧсШЬЭРсШЬУЧЭ±³°´·¿²¬Ч²°«¬Р±®¬

С°»®¿¬»-«°¬±пклУШ¦ш«°¬±ЛИЩЯакрШ¦ч

Н·²¹´»´·²µ±²у½¸·°ЬКЧптр½±³°´·¿²¬®»½»·ª»®

Ш·¹¸у¾¿²¼©·¼¬¸Ь·¹·¬¿´ Э±²¬»²¬Р®±¬»½¬·±²

шШЬЭРчптп½±³°´·¿²¬®»½»·ª»®

Ш·¹¸Ь»º·²·¬·±²У«´¬·³»¼·¿Ч²¬»®º¿½»шШЬУЧч

птр½±³°´·¿²¬®»½»·ª»®©·¬¸ЧоН¿²¼НсРЬЧЪ

¼·¹·¬¿´¿«¼·±±«¬°«¬Ф±²¹у½¿¾´»¬±´»®¿²¬®±¾«-¬®»½»·ª·²¹

Ê·¼»±×²°«¬Ð±®¬

М©±мжожоЮМклкиу¾·¬¼·¹·¬¿´ª·¼»± ·²°«¬°±®¬С²»мжожоЮМкрппку¾·¬¼·¹·¬¿´ª·¼»± ·²°«¬°±®¬

Н«°°±®¬пку¾·¬ЗЛКмжожо·²¬»®´¿½»¼с

°®±¹®»--·ª»ª·¼»±·²°«¬«°¬±прир·сйорР

ß«¬±óݱ²º·¹«®¿¬·±²ñß«¬±óÜ»¬»½¬·±²

Я«¬± ·²°«¬-·¹²¿´º±®³¿¬шНСЩф Э±³°±-·¬»ф

Н»°¿®¿¬»¼ ШНЗТЭфКНЗТЭф¿²¼ЬЫчф¿²¼·²°«¬

³±¼»ш¿´´РЭъМК³±¼»-ч¼»¬»½¬·±²

Я«¬±у¬«²·²¹º«²½¬·±²·²½´«¼·²¹°¸¿-·²¹ф

°±-·¬·±²·²¹ф±ºº-»¬ф ¹¿·²ф¿²¼¶·¬¬»®¼»¬»½¬·±²

Н§²½Ь»¬»½¬·±²º±® ШсКН§²½

Ü«¿´ Ø·¹¸óл®º±®³¿²½»Í½¿´·²¹Û²¹·²»-

Ú«´´§Ð®±¹®¿³³¿¾´»-¸®·²µñ¦±±³½¿°¿¾·´·¬·»Ò±²´·²»¿®ª·¼»±-½¿´·²¹ -«°°±®¬-ª¿®·±«³±¼»-·²½´«¼·²¹Ð¿²±®¿³¿

Ú´»¨·¾´»·²¼»°»²¼»²¬½±²¬®±´ ±º-¸¿®°²»--º±®

ÌÊ¿²¼ ¹®¿°¸·½©·²¼±©-

Ê·¼»±Ð®±½»--·²¹ ú ݱ²ª»®-·±²

íóܳ±¬·±²¿¼¿°¬·ª»ª·¼»±¼»ó·²¬»®´¿½»®©·¬¸

»¼¹»ó±®·»²¬»¼¿¼¿°¬·ª»¿´¹±®·¬¸³º±®-³±±¬¸

´±©ó¿²¹´»»¼¹»ß«¬±³¿¬·½íæî°«´´ó¼±©²úîæî°«´´ó¼±©²

¼»¬»½¬·±²¿²¼ ®»½±ª»®§

Ð×Щ·¬¸°®±¹®¿³³¿¾´»-·¦»¿²¼ ´±½¿¬·±²ô

-«°°±®¬-³«´¬·³»¼·¿¿°°´·½¿¬·±²К·¼»±у±ª»®у¹®¿°¸·½±ª»®´¿§

К·¼»±у¾§у¹®¿°¸·½-°´·¬-½®»»²

Ъ®¿³»®¿¬»½±²ª»®-·±²º±®¾±¬¸³¿·²©·²¼±©

¿²¼-«¾©·²¼±©

УН¬¿® о²¼Щ»²»®¿¬·±²Я¼ª¿²½»¼ Э±´±®Ы²¹·²»

шУН¬¿®ЯЭЫуоч¿«¬±³¿¬·½°·½¬«®»»²¸¿²½»³»²¬

¹·ª»-ж

Þ®·´´·¿²¬¿²¼º®»-¸½±´±®

ײ¬»²-·º·»¼½±²¬®¿-¬¿²¼¼»¬¿·´Ê·ª·¼ -µ·²¬±²»

͸¿®°»¼¹»

Û²¸¿²½»¼¼»°¬¸±ºº·»´¼°»®½»°¬·±²

ß½½«®¿¬»¿²¼·²¼»°»²¼»²¬½±´±®½±²¬®±´

ײ¼»°»²¼»²¬°·½¬«®»½±²¬®±´º±® ¾±¬¸³¿·²

©·²¼±©¿²¼-«¾©·²¼±©

-ÎÙÞ½±³°´·¿²½»¿´´±©-»²¼ó«-»®¬±

»¨°»®·»²½»¬¸»-¿³»½±´±®-¿-ª·»©»¼ ±²ÝÎÌ¿²¼±¬¸»® ¼·-°´¿§Ð®±¹®¿³³¿¾´»ïðó¾·¬ÎÙÞ¹¿³³¿ÝÔËÌ

íóܪ·¼»±²±·-»®»¼«½¬·±²

оррлУН¬¿®Н»³·½±²¼«½¬±®фЧ²½тЯ´´®·¹¸¬-®»-»®ª»¼т

--41--

P

Page 43

Ѳóͽ®»»²ÑÍÜݱ²¬®±´´»®

пксолк½±´±®°¿´»¬¬»

олкслпопу¾·¬с°·¨»´º±²¬

поисолкслпому¾·¬с°·¨»´º±²¬

Н«°°±®¬-¬»¨¬«®»º«²½¬·±²

Н«°°±®¬-мХ¿¬¬®·¾«¬»с½±¼»

Ш±®·¦±²¬¿´¿²¼ª»®¬·½¿´ -¬®»¬½¸±ºСНЬ³»²«Н«°°±®¬-¾«¬¬±²º«²½¬·±²

Р¿¬¬»®²¹»²»®¿¬±®º±® °®±¼«½¬·±²¬»-¬

Н«°°±®¬-СНЬУЛИ¿²¼¿´°¸¿¾´»²¼·²¹

½¿°¿¾·´·¬§

Н«°°±®¬-¾´·²µ·²¹¿²¼ -½®±´´·²¹º±®½´±-»¼

½¿°¬·±²¿°°´·½¿¬·±²-

Ü·¹·¬¿´ß«¼·±×²¬»®º¿½»

ЧоН¼·¹·¬¿´¿«¼·±·²°«¬

ЧоН¼·¹·¬¿´¿«¼·±±«¬°«¬

НсРЬЧЪ¼·¹·¬¿´¿«¼·±±«¬°«¬

ШЬУЧ¿«¼·±½¸¿²²»´ °®±½»--·²¹½¿°¿¾·´·¬§

Р®±¹®¿³³¿¾´»¼»´¿§º±®¿«¼·±сª·¼»±

-§²½¸®±²·¦¿¬·±²

ФКЬНР¿²»´Ч²¬»®º¿½»

Н«°°±®¬-¼«¿´ ´·²µ«°¬±пнлУШ¦ ¼±¬½´±½µº±®

НИЩЯ

Н«°°±®¬-о¼¿¬¿±«¬°«¬º±®³¿¬-жМ¸·²»ъМЧ

¼¿¬¿³¿°°·²¹Э±³°¿¬·¾´»©·¬¸МЧЯсЫЧЯ

Й·¬¸кси¾·¬- ±°¬·±²О»¼«½»¼ -©·²¹º±®ФКЬНº±® ´±©ЫУЧ

Н«°°±®¬-º´»¨·¾´»-°®»¿¼-°»½¬®«³º®»¯«»²½§

©·¬¸нкрШ¦¢пптиУШ¦¿²¼«°¬±олы

³±¼«´¿¬·±²

Û¨¬»®²¿´ ݱ²²»½¬·±²ñݱ³°±²»²¬

Н«°°±®¬-му©·®»¼±«¾´»у¼¿¬¿у®¿¬»¼·®»½¬УЭЛ

¾«ноу¾·¬¼¿¬¿¾«-º±®»¨¬»®²¿´НЬО±®ЬЬО

НЬОЯУº®¿³»¾«ºº»®

Я´´ -§-¬»³½´±½µ- -§²¬¸»-·¦»¼º®±³¿-·²¹´»

»¨¬»®²¿´½´±½µ

ЩЫТЫОЯФЬЫНЭОЧРМЧСТ

М¸»УНМкплпЬЯ·-¿¸·¹¸°»®º±®³¿²½»¿²¼º«´´§·²¬»¹®¿¬»¼ ¹®¿°¸·½- °®±½»--·²¹ЧЭ-±´«¬·±²º±®³«´¬·уº«²½¬·±²

ФЭЬ³±²·¬±®сМК©·¬¸®»-±´«¬·±²-«°¬±НИЩЯтЧ¬·-½±²º·¹«®»¼©·¬¸¿²·²¬»¹®¿¬»¼¬®·°´»уЯЬЭсРФФф¿²·²¬»¹®¿¬»¼

ЬКЧсШЬЭРсШЬУЧ®»½»·ª»®ф¿ª·¼»±¼»у·²¬»®´¿½»®ф¬©±¸·¹¸¯«¿´·¬§-½¿´·²¹»²¹·²»-ф¿²±²у-½®»»²¼·-°´¿§

½±²¬®±´´»®ф¿²¼¿¾«·´¬у·²±«¬°«¬½´±½µ¹»²»®¿¬±®тЮ§«-»±º»¨¬»®²¿´º®¿³»¾«ºº»®фРЧР·- °®±ª·¼»¼º±®³«´¬·³»¼·¿

¿°°´·½¿¬·±²-тЧ¬-«°°±®¬- ¼»у·²¬»®´¿½»¼º«´´у-½®»»²ª·¼»±фª·¼»±у±²у¹®¿°¸·½±ª»®´¿§ф-°´·¬-½®»»²фº®¿³»®¿¬»

½±²ª»®-·±²ф¿²¼¿-°»½¬®¿¬·±½±²ª»®-·±²º±®ª¿®·±«-ª·¼»± -±«®½»-тМ±º«®¬¸»® ®»¼«½»-§-¬»³½±-¬-ф¬¸»

УНМкплпЬЯ¿´-±·²¬»¹®¿¬»-·²¬»´´·¹»²¬°±©»®³¿²¿¹»³»²¬½±²¬®±´½¿°¿¾·´·¬§º±®¹®»»²у³±¼»®»¯«·®»³»²¬-¿²¼

-°®»¿¼ó-°»½¬®«³-«°°±®¬º±®ÛÓ׳¿²¿¹»³»²¬ò

--42--

Page 44

Marantz Technical Service Manual

РЧТЬЧЯЩОЯУшУНМкплпЬЯч

ÙÒÜ

ЬКЧБЩх

ЬКЧБЩу

ЯКЬЬБЬКЧ

ЬКЧБЮх

ЬКЧБЮу

ÙÒÜ

ЬКЧБЭХх

ЬКЧБЭХу

ЯКЬЬБЬКЧ

ÎÛÈÌ

ЯКЬЬБРФФ

ЩТЬ

ЬЬЭЬБЬЯ

ЬЬЭЬБЭХ

ÙÒÜ

ЯКЬЬБЯЬЭ

ШНЗТЭп

КЗНТЭп

ЮЧТпР

ЮЧТпУ

НСЩЧТп

ЩЧТпР

ЩЧТпУ

ОЧТпР

ОЧТпУ

ЮЧТрУ

ЮЧТрР

ЩЧТрУ

ЩЧТрР

НСЩЧТр

ОЧТрУ

ОЧТрР

ЯКЬЬБЯЬЭ

ÙÒÜ

ШНЗТЭр

КНЗТЭр

ÎÓ×Ü

ÎÛÚÐ

ОЫЪУ

КЧБЬЯМЯЕиГ

КЧБЬЯМЯЕзГ

КЧБЬЯМЯЕпрГ

КЧБЬЯМЯЕппГ

КЧБЬЯМЯЕпоГ

КЧБЬЯМЯЕпнГ

КЧБЬЯМЯЕпмГ

КЧБЬЯМЯЕплГ

ЯКЬЬБЯРФФ

ЩТЬ

ЩРСЕлГ

ЩРСЕмГ

ï

î

í

ì

ë

ê

é

è

ç

ïð

ïï

ïî

ïí

ïì

ïë

ïê

ïé

ïè

ïç

îð

îï

îî

îí

îì

îë

îê

îé

îè

îç

íð

íï

íî

íí

íì

íë

íê

íé

íè

íç

ìð

ìï

ìî

ìí

ìì

ìë

ìê

ìé

ìè

ìç

ëð

ëï

ëî

з² ï

ïëê

ïëë

ïëì

ïëí

ïëî

ïëï

ïëð

ïìç

ïìè

ïìé

ïìê

ïìë

ïìì

ïìí

ïìî

ïìï

ïìð

ïíç

ïíè

ïíé

ïíê

ïíë

ïíì

ïíí

ïíî

ïíï

ïíð

ïîç

ïîè

ïîé

ïîê

ïîë

ïîì

ïîí

ïîî

ïîï

ïîð

ïïç

ïïè

ïïé

ïïê

ïïë

ïïì

ïïí

ïïî

ïïï

ïïð

ïðç

ïðè

ïðé

ïðê

ïðë

КЬЬЭ

ЩТЬ

КЬЬУ

ЬПНЕрГ

УЬЯМЯЕрГ

УЬЯМЯЕпГ

УЬЯМЯЕоГ

УЬЯМЯЕнГ

УЬЯМЯЕмГ

УЬЯМЯЕлГ

УЬЯМЯЕкГ

УЬЯМЯЕйГ

УЬЯМЯЕиГ

УЬЯМЯЕзГ

УЬЯМЯЕпрГ

УЬЯМЯЕппГ

ЩТЬ

КЬЬУ

УЬЯМЯЕпоГ

УЬЯМЯЕпнГ

УЬЯМЯЕпмГ

УЬЯМЯЕплГ

ЬПНЕпГ

ЬПУЕрГ

ЩТЬ

КЬЬЭ

УЯЬОЕппГ

УЯЬОЕпрГ

УЯЬОЕзГ

УЯЬОЕиГ

ЩТЬ

КЬЬУ

УЯЬОЕйГ

УЯЬОЕкГ

УЯЬОЕлГ

УЯЬОЕмГ

УЯЬОЕнГ

УЯЬОЕоГ

УЯЬОЕпГ

УЯЬОЕрГ

ЙЫЖ

ЭЯНЖ

ЩТЬ

КЬЬУ

ОЯНЖ

ЮЯЬОЕрГ

ЮЯЬОЕпГ

ЯКЬЬБРФФо

ЩТЬ

УЭФХ

УЭФХЖ

УЭФХЫ

оррлУН¬¿®Н»³·½±²¼«½¬±®фЧ²½тЯ´´®·¹¸¬-®»-»®ª»¼т

--43--

PDF created with pdfFactory trial version www.pdffactory.com

Page 45

РЧТЬЫНЭОЧРМЧСТ

ÓÝËײ¬»®º¿½»

з²Ò¿³» з²Ì§°» Ú«²½¬·±² з²

ШЙОЫНЫМ Í½¸³·¬¬Ì®·¹¹»®×²°«¬

©ñëÊ󬱴»®¿²¬

ЬЮЛНЕнжрГ ×ñÑ©ñëÊ󬱴»®¿²¬ УЭЛму¾·¬ЬЬОЬ·®»½¬¾«-ем³Я¼®·ª·²¹ -¬®»²¹¬¸ йлуйо

ßÔÛ ×©ñëÊ󬱴»®¿²¬ ÓÝËÞ«-ßÔÛô¿½¬·ª»¸·¹¸ êç

ÎÜÆ ×©ñëÊ󬱴»®¿²¬ ÓÝËÞ«-ÎÜÆô¿½¬·ª»¸·¹¸ éð

ÉÎÆ ×©ñëÊ󬱴»®¿²¬ ÓÝËÞ«-ÉÜÆô¿½¬·ª»¸·¹¸ éï

×ÒÌ Ñ«¬°«¬ ÓÝËÞ«-ײ¬»®®«°¬åì³ß¼®·ª·²¹-¬®»²¹¬¸ êè

Ø¿®¼©¿®»Î»-»¬ô¿½¬·ª»¸·¹¸ êé

ß²¿´±¹×²¬»®º¿½»

з²Ò¿³» з²Ì§°» Ú«²½¬·±² з²

ÎÓ×Ü Ó·¼óͽ¿´»Ê±´¬¿¹»Þ§°¿-- íè

ÎÛÚРײ¬»®²¿´ßÜÝ̱°Ü»ó½±«°´·²¹Ð·² íç

ÎÛÚÓ ×²¬»®²¿´ßÜÝÞ±¬¬±³Ü»ó½±«°´·²¹Ð·² ìð

ÎÛÈÌ ß²¿´±¹ ײ°«¬ Ы¨¬»®²¿´О»-·-¬»®нзр±¸³¬±ЯКЬЬБЬКЧ ïï

ШНЗТЭр ͽ¸³·¬¬Ì®·¹¹»®×²°«¬

©ñëÊ󬱴»®¿²¬

КНЗТЭр ͽ¸³·¬¬Ì®·¹¹»®×²°«¬

©ñëÊ󬱴»®¿²¬

Я²¿´±¹ШНЗТЭЧ²°«¬º®±³Э¸¿²²»´р íê

Я²¿´±¹КНЗТЭЧ²°«¬º®±³Э¸¿²²»´р íé

ЮЧТрУ ß²¿´±¹ ײ°«¬ λº»®»²½»Ù®±«²¼º±®ß²¿´±¹ Þ´«»×²°«¬º®±³Ý¸¿²²»´ð îé

ЮЧТрР ß²¿´±¹ ײ°«¬ ß²¿´±¹ Þ´«»×²°«¬º®±³Ý¸¿²²»´ð îè

ЩЧТрУ ß²¿´±¹ ײ°«¬ λº»®»²½»Ù®±«²¼º±®ß²¿´±¹Ù®»»²×²°«¬º®±³Ý¸¿²²»´ðîç

ЩЧТрР ß²¿´±¹ ײ°«¬ ß²¿´±¹Ù®»»²×²°«¬º®±³Ý¸¿²²»´ð íð

НСЩЧТр ß²¿´±¹ ײ°«¬ ͧ²½Ñ²Ù®»»²×²°«¬º®±³Ý¸¿²²»´ð íï

ОЧТрУ ß²¿´±¹ ײ°«¬ λº»®»²½»Ù®±«²¼º±®ß²¿´±¹Î»¼ ײ°«¬º®±³Ý¸¿²²»´ð íî

ОЧТрР ß²¿´±¹ ײ°«¬ ß²¿´±¹Î»¼ ײ°«¬º®±³Ý¸¿²²»´ð íí

ШНЗТЭп ͽ¸³·¬¬Ì®·¹¹»®×²°«¬

©ñëÊ󬱴»®¿²¬

КНЗТЭп ͽ¸³·¬¬Ì®·¹¹»®×²°«¬

©ñëÊ󬱴»®¿²¬

ЮЧТпУ ß²¿´±¹ ײ°«¬ λº»®»²½»Ù®±«²¼º±®ß²¿´±¹ Þ´«»×²°«¬º®±³Ý¸¿²²»´ï îï

ЮЧТпР ß²¿´±¹ ײ°«¬ ß²¿´±¹ Þ´«»×²°«¬º®±³Ý¸¿²²»´ï îð

НСЩЧТп ß²¿´±¹ ײ°«¬ ͧ²½Ñ²Ù®»»²×²°«¬º®±³Ý¸¿²²»´ï îî

ЩЧТпУ ß²¿´±¹ ײ°«¬ λº»®»²½»Ù®±«²¼º±®ß²¿´±¹Ù®»»²×²°«¬º®±³Ý¸¿²²»´ïîì

Я²¿´±¹ШНЗТЭЧ²°«¬º®±³Э¸¿²²»´п ïè

Я²¿´±¹КНЗТЭЧ²°«¬º®±³Э¸¿²²»´п ïç

оррлУН¬¿®Н»³·½±²¼«½¬±®фЧ²½тЯ´´®·¹¸¬-®»-»®ª»¼т

--44--

Page 46

Marantz Technical Service Manual

з²Ò¿³» з²Ì§°» Ú«²½¬·±² з²

ЩЧТпР ß²¿´±¹ ײ°«¬ ß²¿´±¹Ù®»»²×²°«¬º®±³Ý¸¿²²»´ï îí

ОЧТпУ ß²¿´±¹ ײ°«¬ λº»®»²½»Ù®±«²¼º±®ß²¿´±¹Î»¼ ײ°«¬º®±³Ý¸¿²²»´ï îê

ОЧТпР ß²¿´±¹ ײ°«¬ ß²¿´±¹Î»¼ ײ°«¬º®±³Ý¸¿²²»´ï îë

ÜÊ×ײ¬»®º¿½»

з²Ò¿³» з²Ì§°» Ú«²½¬·±² з²

ЬКЧБОх ײ°«¬ ÜÊ× ×²°«¬Ý¸¿²²»´Î»¼õ îðé

ЬКЧБОу ײ°«¬ ÜÊ× ×²°«¬Ý¸¿²²»´Î»¼ó îðè

ЬКЧБЩх ײ°«¬ ÜÊ× ×²°«¬Ý¸¿²²»´Ù®»»²õî

ЬКЧБЩу ײ°«¬ ÜÊ× ×²°«¬Ý¸¿²²»´Ù®»»²óí

ЬКЧБЮх ײ°«¬ ÜÊ× ×²°«¬Ý¸¿²²»´Þ´«»õë

ЬКЧБЮу ײ°«¬ ÜÊ× ×²°«¬Ý¸¿²²»´Þ´«»óê

ЬКЧБЭХх ײ°«¬ ÜÊ× ×²°«¬Ý´±½µõè

ЬКЧБЭХу ײ°«¬ ÜÊ× ×²°«¬Ý´±½µóç

Ê·¼»±×²¬»®º¿½»

з²Ò¿³» з²Ì§°» Ú«²½¬·±² з²

КЧБЭХ ×²°«¬©ñëÊ󬱴»®¿²¬ Ü·¹·¬¿´Ê·¼»± ײ°«¬Ý´±½µ ëí

КЧБЬЯМЯЕплжрГЧ²°«¬©слКу¬±´»®¿²¬ Ь·¹·¬¿´К·¼»± Ч²°«¬Ь¿¬¿ЕплжрГ миумпфкпулм

Ü·¹·¬¿´ß«¼·±×²¬»®º¿½»

з²Ò¿³» з²Ì§°» Ú«²½¬·±² з²

ЯЛУЭХ Ñ«¬°«¬ ß«¼·± Ó¿-¬»® Ý´±½µÑ«¬°«¬ ïèè

ßËÍÜ Ñ«¬°«¬ ß«¼·±Í»®·¿´Ü¿¬¿Ñ«¬°«¬åì³ß¼®·ª·²¹-¬®»²¹¬¸ ïèç

ЯЛНЭХ Ñ«¬°«¬ ß«¼·±Í»®·¿´Ý´±½µÑ«¬°«¬åì³ß¼®·ª·²¹ -¬®»²¹¬¸ ïçð

ßËÉÍ Ñ«¬°«¬ ɱ®¼Í»´»½¬Ñ«¬°«¬åì³ß¼®·ª·²¹-¬®»²¹¬¸ ïçï

ЯЛУЛМЫ Ñ«¬°«¬ ß«¼·±Ñ«¬°«¬Ó«¬»Ý±²¬®±´ ïçî

НРЬЧЪС Ñ«¬°«¬ НсРЬЧЪЯ«¼·±С«¬°«¬ем³Я¼®·ª·²¹-¬®»²¹¬¸ ïçí

ЯЧУЭХ ×²°«¬ ß«¼·± Ó¿-¬»® Ý´±½µ×²°«¬ ïçê

ß×ÍÜ ×²°«¬ ß«¼·±Í»®·¿´Ü¿¬¿×²°«¬ ïçé

ЯЧНЭХ ×²°«¬ ß«¼·±Í»®·¿´Ý´±½µ×²°«¬ ïçè

ß×ÉÍ ×²°«¬ ɱ®¼Í»´»½¬×²°«¬ ïçç

--45--

Page 47

ФКЬНЧ²¬»®º¿½»

з²Ò¿³» з²Ì§°» Ú«²½¬·±² з²

ФКЯрУ Ñ«¬°«¬ ЯуФ·²µТ»¹¿¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïéï

ФКЯрР Ñ«¬°«¬ ЯуФ·²µР±-·¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïéð

ФКЯпУ Ñ«¬°«¬ ЯуФ·²µТ»¹¿¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïêç

ФКЯпР Ñ«¬°«¬ ЯуФ·²µР±-·¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïêè

ФКЯоУ Ñ«¬°«¬ ЯуФ·²µТ»¹¿¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïêé

ФКЯоР Ñ«¬°«¬ ЯуФ·²µР±-·¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïêê

ФКЯнУ Ñ«¬°«¬ ЯуФ·²µТ»¹¿¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïêï

ФКЯнР Ñ«¬°«¬ ЯуФ·²µР±-·¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïêð

ФКЯЭХУ Ñ«¬°«¬ ЯуФ·²µТ»¹¿¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïêë

ФКЯЭХР Ñ«¬°«¬ ЯуФ·²µР±-·¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïêì

ФКЮрУ Ñ«¬°«¬ ЮуФ·²µТ»¹¿¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïèé

ФКЮрР Ñ«¬°«¬ ЮуФ·²µР±-·¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïèê

ФКЮпУ Ñ«¬°«¬ ЮуФ·²µТ»¹¿¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïèï

ФКЮпР Ñ«¬°«¬ ЮуФ·²µР±-·¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïèð

ФКЮоУ Ñ«¬°«¬ ЮуФ·²µТ»¹¿¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïéç

ФКЮоР Ñ«¬°«¬ ЮуФ·²µР±-·¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïéè

ФКЮнУ Ñ«¬°«¬ ЮуФ·²µТ»¹¿¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïéë

ФКЮнР Ñ«¬°«¬ ЮуФ·²µР±-·¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïéì

ФКЮЭХУ Ñ«¬°«¬ ЮуФ·²µТ»¹¿¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïéé

ФКЮЭХР Ñ«¬°«¬ ЮуФ·²µР±-·¬·ª»ФКЬНЬ·ºº»®»²¬·¿´Ь¿¬¿С«¬°«¬ ïéê

ÙÐÑײ¬»®º¿½»

з²Ò¿³» з²Ì§°» Ú«²½¬·±² з²

ÐÉÓð Ñ«¬°«¬ ÙÐÑ©·¬¸ÐÉÓÚ«²½¬·±²åì³ß¼®·ª·²¹-¬®»²¹¬¸ îðð

ÐÉÓï Ñ«¬°«¬ ÙÐÑ©·¬¸ÐÉÓÚ«²½¬·±²åì³ß¼®·ª·²¹-¬®»²¹¬¸ îðï

ЩРСЕпГ ×ñÑ ЩРСсЪЧЫФЬ·²°«¬ем³Я¼®·ª·²¹ -¬®»²¹¬¸ éè

ЩРСЕоГ ×ñÑ ЩРСсЬ·¹·¬¿´КНЗТЭЧ²°«¬ем³Я¼®·ª·²¹ -¬®»²¹¬¸ éé

ЩРСЕнГ ×ñÑ ЩРСсЬЬЭ Э´±½µº±®ОСУ éê

ЩРСЕмГ ×ñÑ ЩРСсЬЫЧ²°«¬ем³Я¼®·ª·²¹ -¬®»²¹¬¸ ëî

ЩРСЕлГ ×ñÑ ЩРСсЬ·¹·¬¿´ШНЗТЭЧ²°«¬ем³Я¼®·ª·²¹-¬®»²¹¬¸ ëï

оррлУН¬¿®Н»³·½±²¼«½¬±®фЧ²½тЯ´´®·¹¸¬-®»-»®ª»¼т

--46--

Page 48

Marantz Technical Service Manual

ЬОЯУЧ²¬»®º¿½»

з²Ò¿³» з²Ì§°» Ú«²½¬·±² з²

УКОЫЪ ×²°«¬ О»º»®»²½»К±´¬¿¹»º±®ЬЬОНЬОЯУЧ²¬»®º¿½»прм

УЭФХЫ Ñ«¬°«¬ ЬОЯУУ»³±®§Э´±½µЫ²¿¾´» ïðë

УЭФХЖ Ñ«¬°«¬ ЬОЯУУ»³±®§½´±½µЭ±³°´»³»²¬¿®§сЧ²°«¬

øº±® ¼·ºº»®»²¬·¿´½´±½µ-÷

ÓÝÔÕ Ñ«¬°«¬ ЬОЯУУ»³±®§Э´±½µ ïðé

ÎßÍÆ Ñ«¬°«¬ α©ß¼¼®»--ͬ®±¾»ô¿½¬·ª»´±© ïïî

ÝßÍÆ Ñ«¬°«¬ ݱ´«³²ß¼¼®»--ͬ®±¾»ô¿½¬·ª»´±© ïïë

ÉÛÆ Ñ«¬°«¬ É®·¬»Û²¿¾´»ô¿½¬·ª»´±© ïïê

ЬПУЕпжрГ Ñ«¬°«¬ Ü¿¬¿Ó¿-µÞ§¬»Û²¿¾´» прпфпнн

ЬПНЕнжрГ Ñ«¬°«¬ Ü¿¬¿Í¬®±¾» ипфпррфпнмфплн

ЮЯЬОЕпжрГ Ñ«¬°«¬ Ó»³±®§Þ¿²µß¼¼®»-- ппрфппп

УЯЬОЕппжрГ Ñ«¬°«¬ Ó»³±®§ß¼¼®»-- пнрупойфпомуппй

УЬЯМЯЕнпжрГ ×ñÑ Ó»³±®§Ü¿¬¿ иоуилфииуззф

ïðê

пнлупнифпмпупло

Ó·-½òײ¬»®º¿½»

з²Ò¿³» з²Ì§°» Ú«²½¬·±² з²

È×Ò Ý®§-¬¿´Ñ-½·´´¿¬±®×²°«¬Ý®§-¬¿´Ñ-½·´´¿¬±®×²°«¬ îðí

ÈÑËÌ Ý®§-¬¿´Ñ-½·´´¿¬±®Ñ«¬°«¬Ý®§-¬¿´Ñ-½·´´¿¬±®Ñ«¬°«¬ îðî

ЬЬЭЬБЬЯ ×ñÑ©ñëÊ󬱴»®¿²¬ ШЬЭРН»®·¿´Ю«-Ь¿¬¿сЬЬЭ¼¿¬¿±ºЬКЧ °±®¬ем³Я¼®·ª·²¹

-¬®»²¹¬¸

ЬЬЭЬБЭХ Ч²°«¬©слКуМ±´»®¿²¬ ШЬЭРН»®·¿´Ю«- Э´±½µсЬЬЭ Э´±½µ±ºЬКЧР±®¬ ïë

ЬЬЭОБЬЯ ×ñÑ©ñëÊ󬱴»®¿²¬ ÜÜÝÜ¿¬¿º±®ÎÑÓ êî

ЮЗРЯНН Ú±®Û¨¬»®²¿´ Þ§°¿-- Ý¿°¿½·¬±® ïëè

ïì

б©»®Ð·²-

з²Ò¿³» з²Ì§°» Ú«²½¬·±² з²

ЯКЬЬБЬКЧ нтнКР±©»® ÜÊ×б©»® ìôïð

ЯКЬЬБЯЬЭ нтнКР±©»® ßÜÝб©»® пйфнм

ЯКЬЬБРФФ нтнКР±©»® ÐÔÔб©»® ïî

ЯКЬЬБРФФо нтнКР±©»® ÐÔÔб©»® ïðç

ЯКЬЬБЯРФФ птиКР±©»® ß«¼·±ÐÔÔб©»® ìç

ЯКЬЬБУРФФ нтнКР±©»® ÐÔÔб©»® îðì

оррлУН¬¿®Н»³·½±²¼«½¬±®фЧ²½тЯ´´®·¹¸¬-®»-»®ª»¼т

--47--

Page 49

S29AL008D

This document has not been approved. Sharing this document with non-Spansion employees violates QS9000/TS16949 requirements.

S29AL008D

8 Megabit (1 M x 8-Bit/512 K x 16-Bit)

CMOS 3.0 Volt-only Boot Sector Flash Memory

Data Sheet

Distinctive Characteristics

Architectural Advantage

Single power supply operation

?.7 to 3.6 volt read and write operations for battery-

powered applications

Manufactured on 200nm process technology

ompatible with 0.32 and 230nm Am29LV160 뾅탆

devices

Flexible sector architecture

ne 16 Kbyte, two 8 Kbyte, one 32 Kbyte, and fifteen 뾑

64 Kbyte sectors (byte mode)

ne 8 Kword, two 4 Kword, one 16 Kword, and fifteen 뾑

32 Kword sectors (word mode)

upports full chip erase뾖

ector Protection features:뾖

hardware method of locking a sector to prevent 뾃

any program or erase operations within that sector

ectors can be locked in-system or via programming 뾖

equipment

emporary Sector Unprotect feature allows code 뾗

changes in previously locked sectors

Unlock Bypass Program Command

educes overall programming time when issuing 뾕

multiple program command sequences

Top or bottom boot block configurations

available

Embedded Algorithms

mbedded Erase algorithm automatically 뾇

preprograms and erases the entire chip or any

combination of designated sectors

mbedded Program algorithm automatically writes 뾇

and verifies data at specified addresses

Compatibility with JEDEC standards

inout and software compat뾒 ible with single-power

supply Flash

uperior inadvertent write protection뾖

Performance Characteristics

High performance

ccess times as fast as 55 ns뾃

xtended temperature range (-40 to +125)뾇캜캜

Ultra low power consumption (typical values

at 5 MHz)

?00 nA Automatic Sleep mode current

?00 nA standby mode current

? mA read current

?5 mA program/erase current

Cycling endurance: 1,000,000 cycles per

sector typical

Data retention: 20 years typical

eliable operation for the life of the system뾕

Package option

48-ball FBGA

48-pin TSOP

44-pin SO

Software Features

Data# Polling and toggle bits

rovides a software method of detecting program or 뾒

erase operation completion

Erase Suspend/Erase Resume

uspends an erase operation to read data from, or 뾖

program data to, a sector that is not being erased,

then resumes the erase operation

Hardware Features

Ready/Busy# pin (RY/BY#)

rovides a hardware method of detecting program or 뾒

erase cycle completion

Hardware reset pin (RESET#)

ardware method to reset the device to reading array 뾊

data

--48--

PDF created with pdfFactory trial version www.pdffactory.com

Page 50

Marantz Technical Service Manual

2

Notice On Data Sheet Designations

Spansion LLC issues data sheets with Advance Information or Preliminary designations to advise

readers of product information or intended specifications throughout the product life cycle, including development, qualification, initial production, and full production. In all cases, however,

readers are encouraged to verify that they have the latest information before finalizing their design. The following descriptions of Spansion data sheet designations are presented here to highlight their presence and definitions.

Advance Information

The Advance Information designation indicates that Spansion LLC is developing one or more specific products, but has not committed any design to production. Information presented in a document with this designation is likely to change, and in some cases, development on the product

may discontinue. Spansion LLC therefore places the following conditions upon Advance Information content:

his document contains information on one or more products under development at Spansion LLC. The 밫

information is intended to help you evaluate this product. Do not design in this product without contacting the factory. Spansion LLC reserves the right to change or discontinue work on this proposed

product without notice.

Preliminary

The Preliminary designation indicates that the product development has progressed such that a

commitment to production has taken place. This designation covers several aspects of the product life cycle, including product qualification, initial production, and the subsequent phases in the

manufacturing process that occur before full production is achieved. Changes to the technical

specifications presented in a Preliminary document should be expected while keeping these aspects of production under consideration. Spansion places the following conditions upon Preliminary content:

his document states the current technical specifications regarding the Spansion product(s) described 밫

herein. The Preliminary status of this document indicates that product qualification has been completed,

and that initial production has begun. Due to the phases of the manufacturing process that require

maintaining efficiency and quality, this document may be revised by subsequent versions or modifications due to changes in technical specifications.

Combination

Some data sheets will contain a combination of products with different designations (Advance Information, Preliminary, or Full Production). This type of document will distinguish these products

and their designations wherever necessary, typically on the first page, the ordering information

page, and pages with DC Characteristics table and AC Erase and Program table (in the table

notes). The disclaimer on the first page refers the reader to the notice on this page.

Full Production (No Designation on Document)

When a product has been in production for a period of time such that no changes or only nominal

changes are expected, the Preliminary designation is removed from the data sheet. Nominal

changes may include those affecting the number of ordering part numbers available, such as the

addition or deletion of a speed option, temperature range, package type, or VIO range. Changes

may also include those needed to clarify a description or to correct a typographical error or incorrect specification. Spansion LLC applies the following conditions to documents in this category:

his document states the current technical specifications regarding the Spansion product(s) described 밫

herein. Spansion LLC deems the products to have been in sufficient production volume such that subsequent versions of this document are not expected to change. However, typographical or specification

corrections, or modifications to the valid combinations offered may occur.

--49--

Page 51

General Description

The S29AL008D is an 8 Mbit, 3.0 volt-only Flash memory organized as 1,048,576

bytes or 524,288 words. The device is offered in 48-ball FBGA, 44-pin SO, and

48-pin TSOP packages. For more information, refer to publication number 21536.

The word-wide data (x16) appears on DQ15Q0; the byte-wide (x8) data ap뺻 -

pears on DQ7Q0. This device requires only a single, 3.0 volt V뺻

perform read, program, and erase operations. A standard EPROM programmer

can also be used to program and erase the device.

This device is manufactured using Spansion 200nm process technology, and of뭩 -

fers all the features and benefits of the Am29LV800B, which was manufactured

using 0.32 process technology. 탆

The standard device offers access times of 70, 90, and 120 ns, allowing high

speed microprocessors to operate without wait states. To eliminate bus contention the device contains separate chip enable (CE#), write enable (WE#) and

output enable (OE#) controls.

The device requires only a single 3.0 volt power supply for both read and write

functions. Internally generated and regulated voltages are provided for the program and erase operations.

The device is entirely command set compatible with the JEDEC single-power-

supply Flash standard. Commands are written to the command register using

standard microprocessor write timings. Register contents serve as input to an internal state-machine that controls the erase and programming circuitry. Write

cycles also internally latch addresses and data needed for the programming and

erase operations. Reading data out of the device is similar to reading from other

Flash or EPROM devices.

Device programming occurs by executing the program command sequence. This

initiates the Embedded Program algorithmn internal algorithm that auto뾞 -

matically times the program pulse widths and verifies proper cell margin. The

Unlock Bypass mode facilitates faster programming times by requiring only two

write cycles to program data instead of four.

Device erasure occurs by executing the erase command sequence. This initiates

the Embedded Erase algorithmn internal algorithm that automatically 뾞

preprograms the array (if it is not already programmed) before executing the

erase operation. During erase, the device automatically times the erase pulse

widths and verifies proper cell margin.

The host system can detect whether a program or erase operation is complete by

observing the RY/BY# pin, or by reading the DQ7 (Data# Polling) and DQ6 (toggle) status bits. After a program or erase cycle is completed, the device is ready

to read array data or accept another command.

The sector erase architecture allows memory sectors to be erased and reprogrammed without affecting the data contents of other sectors. The device is fully

erased when shipped from the factory.