Page 1

Service

74 CD7 /02G

CD-7 FN KGL

Manual

TABLE OF CONTENTS

SECTION PAGE

1. TECHNICAL SPECIFICATIONS...............................................................................................................1

2. SERVICING HINTS ....................................................................................................................................2

3. SERVICINE TOOLS ...................................................................................................................................2

4. SERVICE MODE .........................................................................................................................................3

5. MICROPROCESSOR AND IC DATA .......................................................................................................4

6. WIRING DIAGRAM .....................................................................................................................................7

7. BLOCK DIAGRAM ......................................................................................................................................9

8. FLAG NO. .................................................................................................................................................. 10

9. SCHEMATIC DIAGRAM AND PARTS LOCATIONS .......................................................................... 11

10. EXPLODED VIEW AND MECHANISM PARTS LIST.......................................................................... 27

11. TRAY MECHANISM ADJUSTMENTS................................................................................................... 33

12. BALANCED JACKS ................................................................................................................................. 37

13. DIGITAL FILTER...................................................................................................................................... 38

14. EXPLANATION OF DSP......................................................................................................................... 39

15. ELECTRICAL PARTS LIST .................................................................................................................... 41

Compact disc player

Please use this service manual with referring to the user guide ( D.F.U. ) without fail.

修理の際は、必ず取扱説明書を準備し操作方法を確認の上作業を行ってください。

Printed in Japan

R

model CD-7

4822 725 51186

First Issue 1999.03

355K855010 MIT

Page 2

MARANTZ DESIGN AND SERVICE

Using superior design and selected high grade components, MARANTZ company has created the ultimate in stereo sound.

Only original MARANTZ parts can insure that your MARANTZ product will continue to perform to the specifications for which

it is famous.

Parts for your

MARANTZ equipment are generally available to our National Marantz Subsidiary or Agent.

ORDERING PARTS :

Parts can be ordered either by mail or by Fax.. In both cases, the correct part number has to be specified.

The following information must be supplied to eliminate delays in processing your order :

1. Complete address

2. Complete part numbers and quantities required

3. Description of parts

4. Model number for which part is required

5. Way of shipment

6. Signature : any order form or Fax. must be signed, otherwise such part order will be considered as null and void.

USA CANADA EUROPE / TRADING

MARANTZ AMERICA, INC.

440 MEDINAH ROAD

ROSELLE, ILLINOIS 60172

USA

PHONE : 630 - 307 - 3100

FAX : 630 - 307 - 2687

USA CANADA

SUPERSCOPE TECHNOLOGIES, INC.

MARANTZ PROFESSIONAL PRODUCTS

2640 WHITE OAK CIRCLE, SUITE A

AURORA, ILLINOIS 60504 USA

PHONE : 630 - 820 - 4800

FAX : 630 - 820 - 8103

LENBROOK INDUSTRIES LIMITED

633 GRANITE COURT,

PICKERING, ONTARIO L1W 3K1

CANADA

PHONE : 905 - 831 - 6333

FAX : 905 - 831 - 6936

TC ELECTRONICS CANADA LTD.

540 FIRING AVE.

BAIE D’URFÉ, QUEBEC H9X 3T2

CANADA

PHONE : 514 - 457 - 4044

FAX : 514 - 457 - 5524

MARANTZ EUROPE B. V.

P.O.BOX 80002

BUILDING SFF2

5600 JB EINDHOVEN

THE NETHERLANDS

PHONE : +31 - 40 - 2732241

FAX : +31 - 40 - 2735578

KOREA

MK ENTERPRISES LTD.

2F SHINHAN BLDG., 247-17 SEOKYO-DONG

MAPO-KU, SEOUL

KOREA

PHONE : +82 - 2 - 323 - 2155

FAX : +82 - 2 - 323 - 2154

BRAZIL

MARANTZ BRAZIL

CAIXA POSTAL 21462

CEP 04698-970

SAO PAULO, SP, BRAZIL

PHONE : 0800 - 123123

FAX : +55 11 534. 8988

(Discagem Direta Gratuita)

AUSTRALIA / NEW ZEALAND

SCAN AUDIO PTY. LTD.

52 CROWN STREET, RICHMOND 3121

VICTORIA

AUSTRALIA

PHONE : +61 - 3 - 9429 - 2199

FAX : +61 - 3 - 9429 - 9309

JAPAN

Technical

MARANTZ JAPAN, INC.

35- I , 7- CHOME, SAGAMIONO

SAGAMIHARA - SHI, KANAGAWA

JAPAN 228-8505

PHONE : +81 42 748 1013

F AX : +81 42 748 9190

THAILAND

MRZ STANDARD CO., LTD.

746 - 754 MAHACHAI RD.,

WANGBURAPAPIROM, PHRANAKORN,

BANGKOK, 10200 THAILAND

PHONE : +66 - 2 - 222 - 9181

FAX : +66 - 2 - 224 - 6795

TAIWAN

P Al- YUING CO., LTD.

6 TH FL NO, 148 SUNG KIANG ROAD,

TAIPEI, 10429, TAIWAN R.O.C.

PHONE : +886 (2) 5221304

F AX : +886 (2) 5630415

日本マランツ株式会社

本社〒 228-8505

神奈川県相模原市相模大野7 - 35 - 1

営業本部〒 150-0022

東京都渋谷区恵比寿南1 - 11 - 9

MALAYSIA

WO KEE HONG ELECTRONICS SDN. BHD.

NO. 102 JALAN SS 21/35, DAMANSARA

UTAMA, 47400 PETALING JAYA

SELANGOR DARUL EHSAN,

MALAYSIA

PHONE : +60 3 - 7184666

FAX : +60 3 - 7173828

SINGAPORE

FORWARD MARKETING (S) PTE. LTD.

23, LORONG 8, TOA PAYOH,

SINGAPORE 319257.

PHONE : +65 2583640

FAX : +65 3564047

SHOCK, FIRE HAZARD SERVICE TEST :

CAUTION : After servicing this appliance and prior to returning to customer, measure the resistance between either primary AC

cord connector pins ( with unit NOT connected to A C mains and its Power switch ON ), and the face or F ront Panel of product and

controls and chassis bottom.

Any resistance measurement less than 1 Megohms should cause unit to be repaired or corrected before A C po wer is applied, and

verified before it is return to the user/customer.

Ref. UL Standard No. 1492.

In case of difficulties, do not hesitate to contact the Technical

Department at above mentioned address.

981110MIT

Page 3

1. TECHNICAL SPECIFICA TIONS

Audio Characteristics

Channels ........................................................ 2 channels

Sampling frequency (CD mode) ........................ 44.1 kHz

Sampling frequency (D/A mode) ............. 32/44.1/48 kHz

Quantization .................................... 16-bit linear/channel

Error correction...

Cross-interleave read solomon code (CIRC)

D/A conversion ..................................1-bit linear/channel

Wow & flutter ..................................... Precision of quartz

Optical Readout System

Laser........................................... AIGaAs semiconductor

Wavelength.......................................................... 780 nm

Frequency Characteristics

Frequency range ....................................... 2 Hz - 20 kHz

Dynamic range .................................................... > 98 dB

S/N ratio............................................................. > 102 dB

Channel separation (1 kHz) ...............................> 100 dB

THD (1 kHz)........................................................ 0.002 %

Analog output

Output level (cinch JACKS) ...................... 2.2 V RMS

Output impedance..................................... 250 ohms

Digital output

Output level (cinch JACK) .............. 0.5 Vp-p/75 ohms

Output level (optical JACK)...........................-19 dBm

Digital input

Input level (cinch JACK)................. 0.5 Vp-p/75 ohms

Input level (optical JACK).............................. -19 dBm

Power Supply

Power requirement

K version ............................. 110 / 220V AC 50/60 Hz

/02 version ........................................ 230V AC 50 Hz

Power Consumption .............................................19 W

Cabinet, etc.

Dimensions

Width............................................................. 454 mm

Height............................................................ 139 mm

Depth ............................................................ 344 mm

Netweight............................................................. 16.6 kg

Operating temperatures........................... +5 °C ~ +35 °C

Operating humidity ................. 5 % ~ 90 % (without dew)

Accessories

Remote control unit (RC-7CD) ...................................... 1

AAA (R03) Batteries ...................................................... 2

Stereo audio cable with cinch pins ................................ 1

AC power cord ............................................................... 1

オーディオ特性オーディオ特性

オーディオ特性

オーディオ特性オーディオ特性

チャンネル .............................. 2チャンネル

周波数特性 ................. 2Hz〜20,000Hz,+0‑1.2dB

ダイナミックレンジ ......................... 98dB以上

S/N比 ......................................... 102dB

チャンネルセパレーション ............... 100dB(1kHz)

高調波歪率 ............................ 0.002%(1kHz)

ワウフラッター ............................. 水晶精度

誤り訂正方式 ............... クロス・インターリーブ・

リードソロモン・コード(CIRC)

音声出力

アンバランス ...................... 2.2VRMSステレオ

バランス .......................... 3.8VRMSステレオ

デジタル出力

ピンジャック .......................... 0.5Vp‑p/75Ω

光出力(角型光コネクター) .................... ‑19dBm

デジタル入力

ピンジャック .......................... 0.5Vp‑p/75Ω

光出力(角型光コネクター) .................... ‑19dBm

光学読み取り方式光学読み取り方式

光学読み取り方式

光学読み取り方式光学読み取り方式

レーザー .............................. AlGaAs半導体

波長 .......................................... 780nm

信号方式信号方式

信号方式

信号方式信号方式

サンプリング周波数(CDモード) ............... 44.1kHz

(D/A モード) .......... 32/44.1/48kHz

量子化 .................. 16ビットリニア/チャンネル

電源部電源部

電源部

電源部電源部

電源 ................................ AC100V50/60Hz

消費電力(電気用品取締法) ....................... 25W

キャビネット・その他キャビネット・その他

キャビネット・その他

キャビネット・その他キャビネット・その他

最大外形寸法(幅×高さ×奥行き) ..... 454×139×344mm

質量 ......................................... 16.6kg

許容動作温度 .......................... +5℃〜+35℃

許容動作湿度 ............... 5%〜90%(結露のないこと)

付属品付属品

付属品

付属品付属品

リモートコントロール送信機(RC‑7CD) ............... 1

外形寸法(幅×高さ×奥行き) ......... 44×17.5×239mm

質量(電池なし) ................................. 175g

単四電池(SUM‑4) ................................. 2個

RCAピンコード ................................... 1組

電源コード ...................................... 1本

Improvement may result in changes in specifications and

design without notice.

1

Page 4

2. SERVICING HINTS

3. SERVICE TOOLS

Audio signals disc 4822 397 30184

Disc without errors (SBC444)+

Disc with DO errors, black spots and fingerprints (SBC444A) 4822 397 30245

Disc (65 min 1kHz) without no pause 4822 397 30155

Max. diameter disc (58.0 mm) 4822 397 60141

Torx screwdrivers

Set (straight) 4822 395 50145

Set (square) 4822 395 50132

13th order filter 4822 395 30204

Allen wrench (No. 3)

2

Page 5

4. SERVICE MODE

1. How to enter into the Service Mode

Turn the power on while pressing [PLAY]+[OPEN/

CLOSE] buttons together.

2. Mode 0 (display “P 00”)

Condition: [FOCUS OFF], [SPINDLE OFF], [RADIAL

OFF], [MUTE ON]

• While pressing [ ](Remote Control unit only) button,

the sledge moves outside.

And, release from this button. The sledge return to

neutral position.

• Press [NEXT ] button, the function will change to

“Mode 1”.

3. Mode 1 (display “P 01”)

Condition: [FOCUS ON], [SPINDLE OFF], [RADIAL OFF],

[MUTE ON]

• Press [NEXT ] button, the function will change to

“Mode 2”.

• Press [PREV ] button, the function will change to

“Mode 0”.

4. Mode 2 (display “P 02”)

Condition: [FOCUS ON], [SPINDLE ON], [RADIAL OFF],

[MUTE ON]

• Press [NEXT ] button, the function will change to

“Mode 3”.

• Press [PREV ] button, the function will change to

“Mode 1”.

5. Mode 3 (display “P 03”)

Condition: [FOCUS ON], [SPINDLE ON], [RADIAL ON],

[MUTE OFF]

• Press [PREV ] button, the function will change to

“Mode 2”.

✱ The following button operations are available at the

Service Mode.

1) While pressing [STOP] button, FL display shows all

segments.

2)The same as Normal operation is performed by

pressing [PLAY] button.

However if some default is detected, display shows an

error code. (For example: “Err 10”) Refer to the “Table

1 ERROR CODE”.

6. Canceling the Service Mode

The Service Mode is canceled by turning the power off.

4.4.

サービスモードサービスモード

4.

サービスモード

4.4.

サービスモードサービスモード

1. サービスモードへの入り方

[PLAY]と[OPEN/CLOSE]ボタンを押しながら電源を入れま

す。

2. モード0(表示P00)

状態:[FOCUSOFF][SPINDLEOFF] [RADIALOFF][MUTE

ON]

• リモコンの[ ]ボタンを押している間だけスレッドが

外周へ移動します。ボタンを放すと原点に戻ります。

• [NEXT ]ボタンを押すとモード1へ移行します。

3. モード1(表示P01)

状態:[FOCUSON][SPINDLEOFF][RADIALOFF][MUTEON]

• [NEXT ]ボタンを押すとモード2へ移行します。

• [PREV ]ボタンを押すとモード0へ移行します。

4. モード2(表示P02)

状態:[FOCUSON][SPINDLEON][RADIALOFF] [MUTEON]

• [NEXT ]ボタンを押すとモード3へ移行します。

• [PREV ]ボタンを押すとモード1へ移行します。

5. モード3(表示P03)

状態:[FOCUSON][SPINDLEON][RADIALON] [MUTEOFF]

• [PREV ]ボタンを押すとモード2へ移行します。

* サービスモードの全ての状態で以下のボタンが有効です。

1) [STOP]ボタンを押している間だけFLが全点灯します。

2) [PLAY]ボタンを押すと通常と同じ動作となります。た

だし、動作中、異常が確認された時にエラー番号が表示

されます。(例:Err10)

下記の表を参考にしてください。

6. サービスモードの解除

電源を切るとサービスモードが解除されます。

Table 1

Error Code Error

Err 02 FOCUS Error

Err 07 SUB CODE Error

Err 08 T. O. C. Error

Err 09 DECODER Error

Err 10 RADIAL Error

Err 11, 12 SLEDGE Error

Err 13 SPINDLE Error

Err 16 ~ 20 SEARCH Error

Err 30 DOOR Error

Err 31 TRAY Error

Err 32 ~ 47 BUTTON INPUT Error

ERROR CODE

3

Page 6

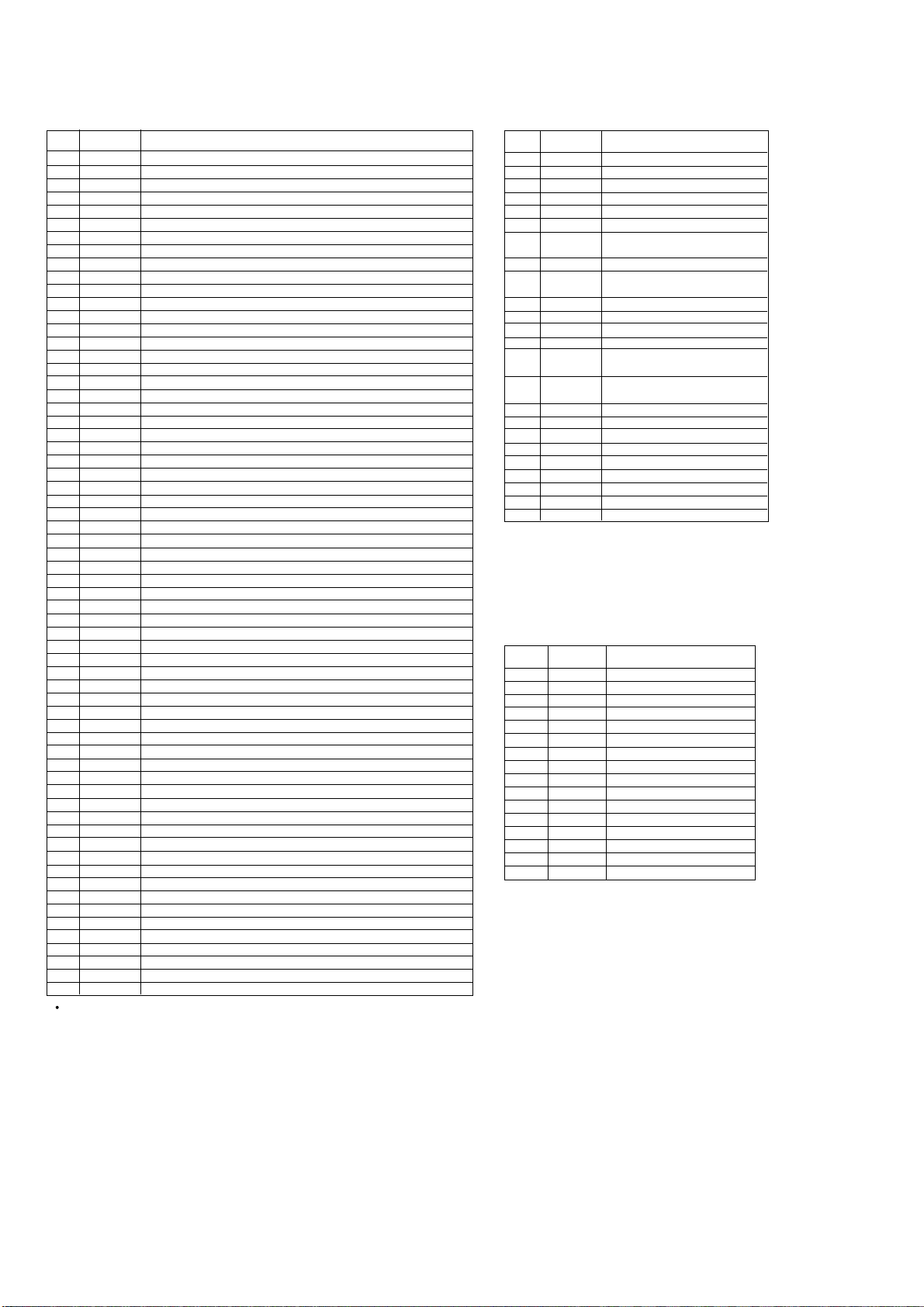

5. MICROPROCESSOR AND IC DATA

Q102 : SAA7372GP

PIN SYMBOL DESCRIPTION

1 VSSA1 *analog ground 1

2 VDDA1 * analog supply voltage 1

3 D1 unipolar current input (central diode signal input)

4 D2 unipolar current input (central diode signal input)

5 D3 unipolar current input (central diode signal input)

6 VRL reference voltage input for ADC

7 D4 unipolar current input (central diode signal input)

8 R1 unipolar current input (satellite diode signal input)

9 R2 unipolar current input (satellite diode signal input)

10 IrefT current reference output for ADC calibration

11 VRH reference voltage output from ADC

12 VSSA2 * analog ground 2

13 SELPLL selects whether internal clock multiplier PLL is used

14 ISLICE current feedback output from data slicer

15 HFIN comparator signal input

16 VSSA3 * analog ground 3

17 HFREF comparator common mode input

18 Iref reference current output pin (nominally 0.5VDD )

19 VDDA2 * analog supply voltage 2

20 TEST1 test control input 1; this pin should be tied LOW

21 CRIN crystal/resonator input

22 CROUT crystal/resonator output

23 TEST2 test control input 2; this pin should be tied LOW

24 CL16 16.9344 MHz system clock output

25 CL11 11.2896 or 5.6448 MHz clock output (3-state)

26 RA radial actuator output

27 FO focus actuator output

28 SL sledge control output

29 TEST3 test control input 3; this pin should be tied LOW

30 VDDD1(P) * digital supply voltage 1 for periphery

31 DOBM bi-phase mar k output (externally buffered; 3-state)

32 VSSD1 * digital ground 1

33 MOTO1 motor output 1; versatile (3-state)

34 MOTO2 motor output 2; versatile (3-state)

35 SBSY subcode block sync output (3-state)

36 SFSY subcode frame sync output (3-state)

37 RCK subcode clock input

38 SUB P-to-W subcode output bits (3-state)

39 VSSD2 * digital ground 2

40 V5 versatile output pin 5

41 V4 versatile output pin 4

42 V3 versatile output pin 3 (open-drain)

43 KILL kill output (programmable; open-drain)

44 EF C2 error flag; output only defined in CD ROM modes and 1fs modes (3-state)

45 DATA serial data output (3-state)

46 WCLK word clock output (3-state)

47 VDDD2(P) * digital supply voltage 2 for periphery

48 SCLK serial bit clock output (3-state)

49 VSSD3 * digital ground 3

50 CL4 4.2336 MHz microcontroller clock output

51 SDA microcontroller interface data I/O line (open-drain output)

52 SCL microcontroller interface clock line input

53 RAB microcontroller interface R/W and load control line input (4-wire bus mode)

54 SILD microcontroller interface R/W and load control line input (4-wire-bus mode)

55 n.c. not connected

56 VSSD4 * digital ground 4

57 RESET power-on reset input (active LOW)

58 STATUS servo interrupt request line/decoder status register output (open-drain)

59 VDDD3(C) * digital supply voltage 3 for core

60 C2FAIL indication of correction failure output (open-drain)

61 CFLG correction flag output (open-drain)

62 V1 versatile input pin 1

63 V2 versatile input pin 2

64 LDON laser drive on output (open-drain)

Note : All supply pins must be connected to the same external power supply voltage.

7000 : TDA1302T

PIN SYMBOL DESCRIPTION

1 O4 output of diode current amplifier 4

2 O6 output of diode current amplifier 6

3 O3 output of diode current amplifier 3

4 O1 output of diode current amplifier 1

5 O5 output of diode current amplifier 5

6 O2 output of diode current amplifier 2

7 LDON control pin for switching the laser

ON and OFF

8 VDDL laser supply voltage

9 RFE equalized output voltage of sum

signal of amplifiers 1 to 4

10 RF unequalized output

11 HG control pin for gain switch

12 LS control pin for speed switch

13 CL external capacitor

14 ADJ reference input normally

connected to ground via a resistor

15 GND 0 V supply; substrate connection

(ground)

16 LO current output to the laser diode

17 MI laser monitor diode input

18 VDD amplifier supply voltage

19 I2 photo detector input 2 (central)

20 I5 photo detector input 5 (satellite)

21 I1 photo detector input 1 (central)

22 I3 photo detector input 3 (central)

23 I6 photo detector input 6 (satellite)

24 I4 photo detector input 4 (central)

Q103/Q104 : TDA7073AT

PIN SYMBOL DESCRIPTION

1 IN1- negative input 1

2 IN1+ positive input 1

3 n.c. not connected

4 n.c. not connected

5 VP positive supply voltage

6 IN2+ positive input 2

7 IN2- negative input 2

8 n.c. not connected

9 OUT2+ positive output 2

10 GND2 ground 2

11 n.c. not connected

12 OUT2- negative output 2

13 OUT1- negative output 1

14 GND1 ground 1

15 n.c. not connected

16 OUT1+ positive output 1

4

Page 7

Q304 : TDA1315H

)

)

g

g)

g)

)

)

L

)

)

y

g

g

g

)

)

)

)

y

y

y

y

y

g

)

)

(

g

)

y

g

g

g

(

g

)

)

,

,

)

)

)

)

)

g

)

g

g

)

)

)

)

)

)

)

)

)

(

)

SYMBOL PIN PADCELL DESCRIPTION

RC

fil

V

ref

V

DDA

V

SSA

IECIN1 5 E007 high sensitivity IEC input

IECIN0 6 IPP04 TTL level IEC input

IECSEL 7 IUP04 select IEC input 0 or 1 (0 = IECIN0; 1 = IECIN1); this input has an internal pull-up

IECO 8 OPFH3 digital audio output for optical and transformer link

IECOEN 9 IUP04 digital audio output enable (0 = enabled; 1 = disabled/3-state); this input has an

TESTB 10 IPP04 enable factory test input (0 = normal application; 1 = scan mode)

TESTC 11 IPP04 enable factory test input (0 = normal application; 1 = observation outputs)

UNLOCK 12 OPP41A PLL out-of-lock (0 = not locked; 1 = locked); this output can drive an LED

FS32 13 OPP41A indicates sample frequency = 32 kHz (active LOW); this output can drive an LED

FS44 14 OPP41A indicates sample frequency = 44.1 kHz (active LOW); this output can drive an LED

FS48 15 OPP41A indicates sample frequency = 48 kHz (active LOW); this output can drive an LED

CHMODE 16 OPP41A use of channel status block (0 = professional use; 1 = consumer use); this output

V

DDD2

V

SSD2

RESET 19 IDP09 initialization after power-on, requires only an external capacitor connected to V

PD 20 IPP04 enable power-down input in the standby mode (0 = normal application; 1 = standby

CTRLMODE 21 IUP04 select microcontroller/stand-alone mode (0 = microcontroller; 1 = stand-alone); this

LADDR 22 IPP04 microcontroller interface address switch input (0 = 000001; 1 = 000010)

LMODE 23 IPP09 microcontroller interface mode line input

LCLK 24 IPP09 microcontroller interface clock line input

LDATA 25 IOF24 microcontroller interface data line input/output

STROBE 26 IDP04 strobe for control register (active HIGH); this input has an internal pull-down resistor

UDAVAIL 27 OPF23 synchronization for output user data (0= data available; 1 = no data)

TESTA 28 IPP04 enable factory (scan) test input (0 = normal application; 1 = test clock enable)

COPY 29 OPP41A copyright status bit (0 = copyright asserted; 1 = no copyright asserted); this output

INVALID 30 IOD24 validity of audio sample input/output (0 = valid sample; 1 = invalid sample); this pin

DEEM 31 OPF23 pre-emphasis output bit (0 = no pre-emphasis; 1 = pre-emphasis)

MUTE 32 IUP04 audio mute input (0 = permanent mute; 1 = mute on receive error); this pin has an

I2SSEL 33 IUP04 select auxiliary input or normal input in transmit mode

SDAUX 34 IPP04 auxiliary serial data input; I

SD 35 IOF24 serial audio data input/output; I

WS 36 IOF24 word select input/output; I

SCK 37 IOF29 serial audio clock input/output; I

2

SOEN 38 IUP04 serial audio output enable (0 = enabled; 1 = disabled/3-state); this input has an

I

SYSCLKI 39 IPP09 system clock input (transmit mode)

SYSCLKO 40 OPFA3 system clock output (receive mode)

V

SSD1

V

DDD1

CLKSEL 43 IUP04 select system clock (0 = 384f

RC

int

1 E029 PLL loop filter input

2 E029 decoupling internal reference voltage output

3 E008 analog supply voltage

4 E004 analog ground

resistor

internal pull-up resistor

17 E008 digital supply voltage 2

18 E009 digital ground 2

41 E009 digital ground 1

42 E008 digital supply voltage 1

44 E029 integrating capacitor output

can drive an LED

this is a Schmitt-trigger input with an internal pull-down resistor

mode)

input has an internal pull-up resistor

can drive an LED

has an internal pull-down resistor

internal pull-up resistor

2

S-bus

2

S-bus

2

S-bus

2

S-bus

internal pull-up resistor

; 1 = 256fs); this input has an internal pull-up resistor

s

DDD

QD03/QD53 : TDA1541A/S2

PINNING

SYMBOL PIN DESCRIPTION

(1)

LE/WS

(1)

BCK

DATA L

(1)

/DATA

(1)

DATA R

GND(A) 5 analog ground

AOR 6 right channel output

DECOU 7 to 13 decoupling

GND (D) 14 digital ground

V

DD2

COSC 16,17 oscillator

DECOU 18 to 24 decoupling

AOL 25 left channel output

V

DD1

(1)

OB/TWC

V

DD

Note

1. See Table 1 data selection input.

latch enable input/ word select

1

input

2 bit clock input

data left channel input/ data

3

input (selected format)

4 data right channel input

15 −15 V supply voltage

26 −5 V supply voltage

27 mode select input

28 +5 V supply voltage

: µ: µ

QF01

Q507/Q509 : DSP56004

4 9 5 29

General

Serial

Purpose

Audio

Input/

Interface

Output

(SAI)

24-Bit

DSP56000

Core

Internal

Data

Bus

Switch

OnCETM Port

Clock

PLL

Gen.

;

43

IRQA, IRQB, NMI, RESET

Interrupt

Control

4

Address

Generation

Unit

Program

Decode

Controller

Program Control Unit

Power Inputs

V

CCP

3

V

CCQ

2

V

CCA

V

CCD

2

V

CCS

Ground

GND

P

GND

GND

GND

GND

3

Q

4

A

2

D

3

S

Serial

Host

Interface

(SHI)

GDB

PDB

XDB

YDB

External

Memory

Interface

(EMI)

Program

Address

Generator

DSP56004

Program

Memory*

PAB

XAB

YAB

24 × 24 + 56 → 56-bit MAC

*Refer to Table 1 for memory configurations.

Port B

Serial Host

Interface

Serial Audio

Interface

PCAP

PINIT

PLL

EXTAL

MA0ÐMA14

MD0ÐMD7

15

8

MA15/MCS3

MA16/MCS2/MCAS

MA17/MCS1/MRAS

MCS0

Port A

External Memory

Interface

MWR

MRD

MODC/NMI

MODB/IRQB

MODA/IRQA

RESET

Mode/Interrupt

Control

Reset

80 signals

OnCEª

16-Bit Bus

24-Bit Bus

X Data

Memory*

Data ALU

Two 56-Bit Accumulators

Port C

Rec0

Rec1

Tran0

Tran1

Tran2

4

GPIO

Port

Y Data

Memory*

MOSI/HA0

SS/HA2

MISO/SDA

SCK/SCL

HREQ

WSR

SCKR

SDI0

SDI1

WST

SCKT

SDO0

SDO1

SDO2

GPIO0ÐGPIO3

DSCK/OS1

DSI/OS0

DSO

DR

: µPD78076 MAIN

: µ: µ

Pin No. Port Name Function In/Out Active To/From Description

1 STRB P120 Out High Q304 Strobe signal for control resister for Q304(TDA1315H

2 LMOD P121 Out Low Q304 Interface mode line for Q304(TDA1315H

3 OPEN P122 ----4 GND P123 GND GND

5 FS32 P124 In Low Q304 Samplin

6 FS48 P125 In Low Q304 Sampling frequency input (L = 48KHz Receivin

7COAX/OPTP126 Out Low Q304 Digital input select signal (L = Optical , H = Coaxal

8 DMUT P127 Out Low Q304 Digital muting control signal for Q304(TDA1315H

9 GND IC GND GND

10 5MHzXTA

11 5MHzXTALX1 XF01 Clock in (5MHz

12 +5V Vdd +5V Power supply +5V

13 OPEN XT2 --- ----14 +5V XT1 +5V Power suppl

15 REST RESET In Low QF02 Reset si

16 RC5I INTP0 In ZY01 Remote control si

17 OPEN INTP1 --- ----18 CD7R P02 Out Low Q102 CD7 Reset si

19 SILD P03 Out Low Q102 Strobe signal for servo part of Q102(SAA7372GP

20 RAB7 P03 Out Low Q102 Strobe signal for digital part of Q102(SAA7372GP

21 LOCK INTP5 In Low Q304 Unlock signal of Q304(TDA1315H

22 MSCP INTP6 In Low GND GND

23 +5V Avdd +5V Power suppl

24 +5V Avref0 In +5V Power suppl

25 KEY0 ANI0 In Level Tact SwitchKe

26 KEY1 ANI1 In Level Tact SwitchKe

27 KEY2 ANI2 In Level Tact SwitchKe

28 GND ANI3 GND GND

29 MUTE ANI4 Out Hi

30 PAUS ANI5 Out High Q507 Mute of pause on time for DSP Q507(DSP56004

31 OPEN ANI6

32 RELY2 ANI7 Out Hi

33 GND Avss GND GND

34 OPEN P130 In/Out --- ----35 OPEN P131 Out --- ----36 +5V Avref In +5V Power suppl

37 STRD P70 Out Low QY01 Strobe si

38 SIOD SO2 Out QY01 Serial data for QY01

39 CLKD SCK2 Out Low QY01 Serial clock for QY01

40 GND Vss GND GND

41 OPEN SI1 In --- ----42 OPEN SO1 --- ----43 OPEN SCK1 --- ----44 OPEN P23

45 OPEN P24 --- ----46 OPEN SB0 ----47 OPEN SB1 In/Out --- ----48 SDA SCK0 Out Q102/Q304 Serial data si

49 SCL A0 Q102/Q304 Serial clock si

50 OPEN A1 --- ----51 OPEN A2 --- ----52 OPEN A3 --- ----53 OPEN A4 --- ----54 OPEN A5 --- ----55 OPEN A6 --- ----56 OPEN A7 --- ----57 GND D0 GND

58 GND D1 GND

59 GND D2 GND

60 GND D3 GND

61 GND D4 GND

62 GND D5 GND

63 GND D6 GND

64 GND D7 GND

65 OPEN A8 --- ----66 OPEN A9 --- ----67 OPEN A10 --- ----68 OPEN A11 --- ----69 OPEN A12 --- ----70 OPEN A13 --- ----71 GND Vss GND GND

72 OPEN A14

73 RA11 A15 Out Hi

74 16WD P60 In Low GND Audio data select signal input (L = 16Bit

75 FMUT P61 Out High QN05 Mute of switching on time killer

76 RSD2 P62 Out Low Q309

77 RSD1 P63 Out Low Q507 Reset of Q507

78 NSSH RD Out Low Q508

79 FIL3 WR Out High Q508,QY09Filter 3 select signal (H = select of filter 3

80 FIL2 P66 Out High Q508,QY08Filter 2 select signal (H = select of filter 2

81 FIL1 P67 Out High QY07 Filter 1 select signal (H = select of filter 1

82 OPTI P100 In High Q303 Optical input select ( H = OPT , L = COAX1

83 OPEN TO6 --- ----84 OPEN P102 --- ----85 RELY1 P103 Out Hi

86 MSL1 P30 In HighHigh Level ----87 MSL2 P31 In Low GND Level ----88 OPEN P32 --- ----89 CDRW P33 Out Hi

90 SLSW P34 In Low VAM1201 Sled

91 TROS P35 In Low TRAY Tray in/out detect switch (L = out end

92 TRIS P36 In Low TRAY Tray in/out detect switch (L = in end

93 TRUS P37 In Low TRAY Tray up/down detect switch (L = up end

94 TRDS P90 In Low TRAY Tray up/down detect switch (L = down end

95 TROM P91 Out High QM10 Tray motor control signal (H = tray out

96 TRIM P93 Out High QM09 Tray motor control signal (H = tray in

97 TRDM P94 Out High QM12 Tray motor control signal (H = tray down

98 TRUM P95 Out High QM11 Tray motor control signal (H = tray up

99 AMUT P95 Out Low NC -----

100 DA/CD P96 Out Low Q504 Mode select

X2 XF01 Clock out (5MHz

h Q507 Mute signal for DSP Q507(DSP56004

CD7L)-----

h QY51 Display on/off control signal (L = off , H = on

---

---

RA12)-----

h Q506 Audio data select signal output (L = 16Bit

Q509 Reset of Q309,Q509

QY10Noise shaper on/off signal (L = on , H = off

h D301 Audio muting control signal of poer on/off(H=mute on

h NC -----

frequency input (L = 32KHz Receivin

+5V

nal input for QF02

nal input for ZY01

nal for Q102(SAA7372GP

+5V

+5V

Sensor

Sensor

Sensor

+5V

nal for QY01

-----

nal for Q102/Q304

nal for Q102/Q304

GND

GND

GND

GND

GND

GND

GND

GND

e detect switch (L = in end

L = D/A Mode , H = CD Mode

5 6

Page 8

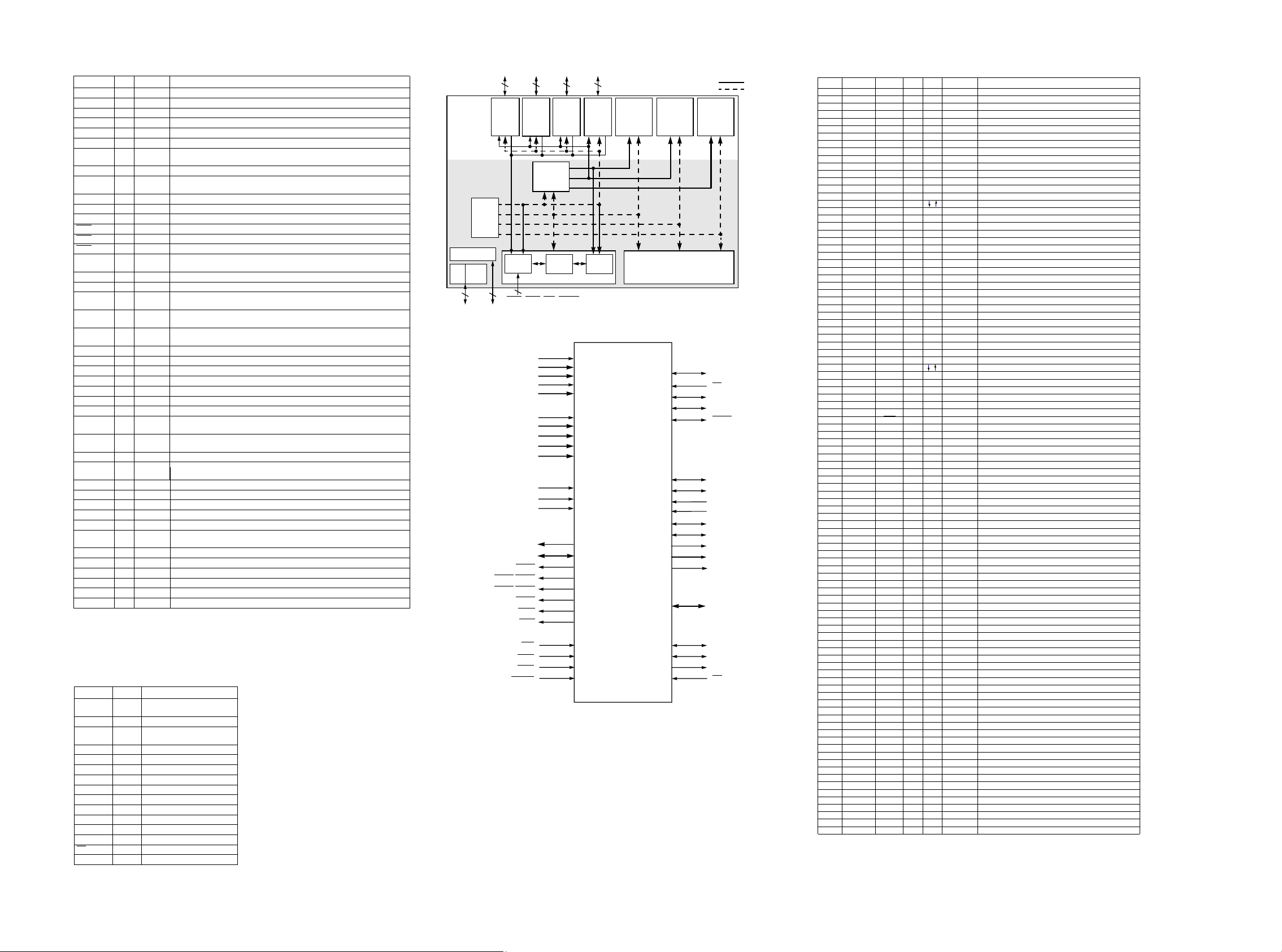

6. WIRING DIAGRAM

7 8

Page 9

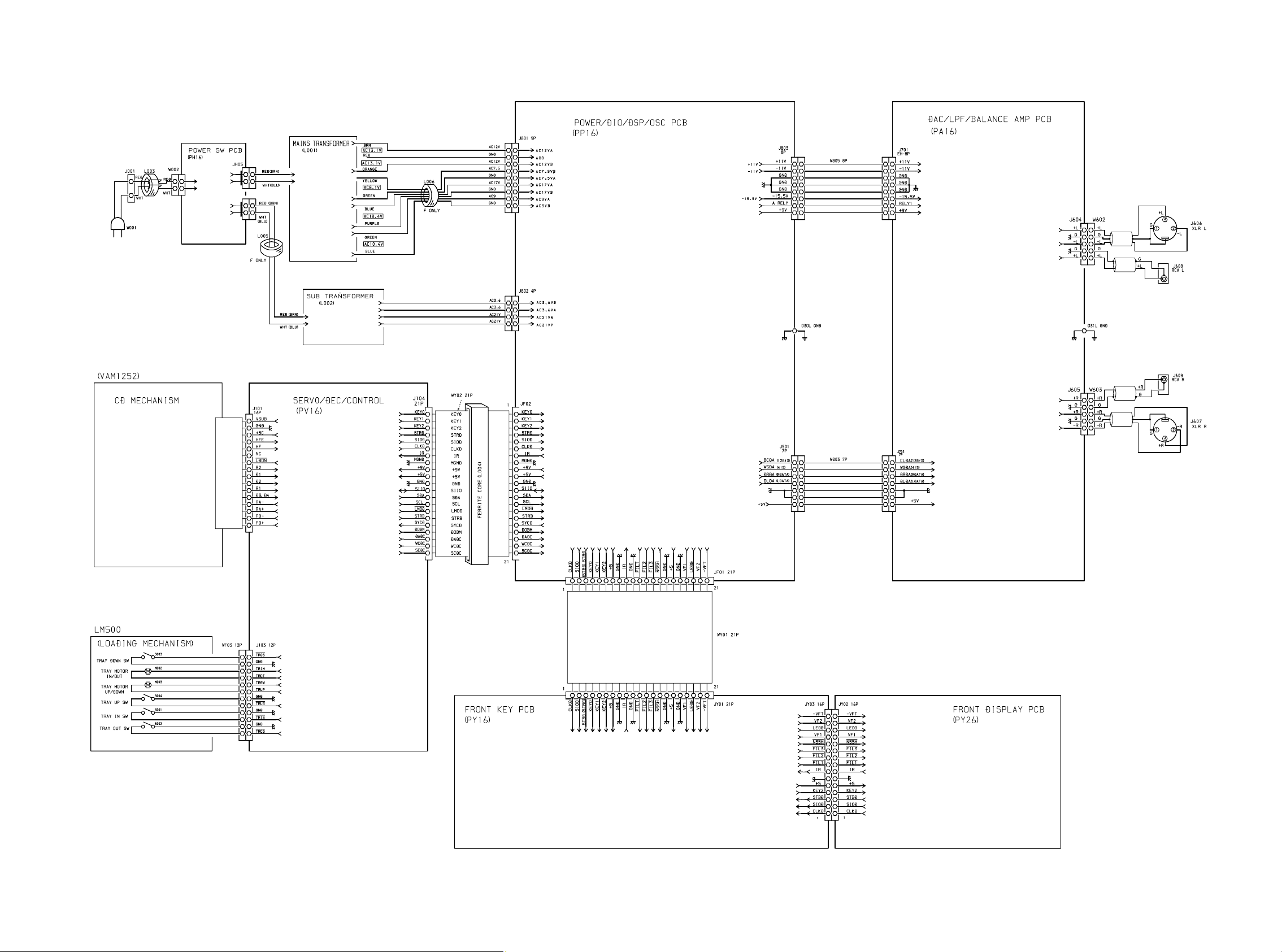

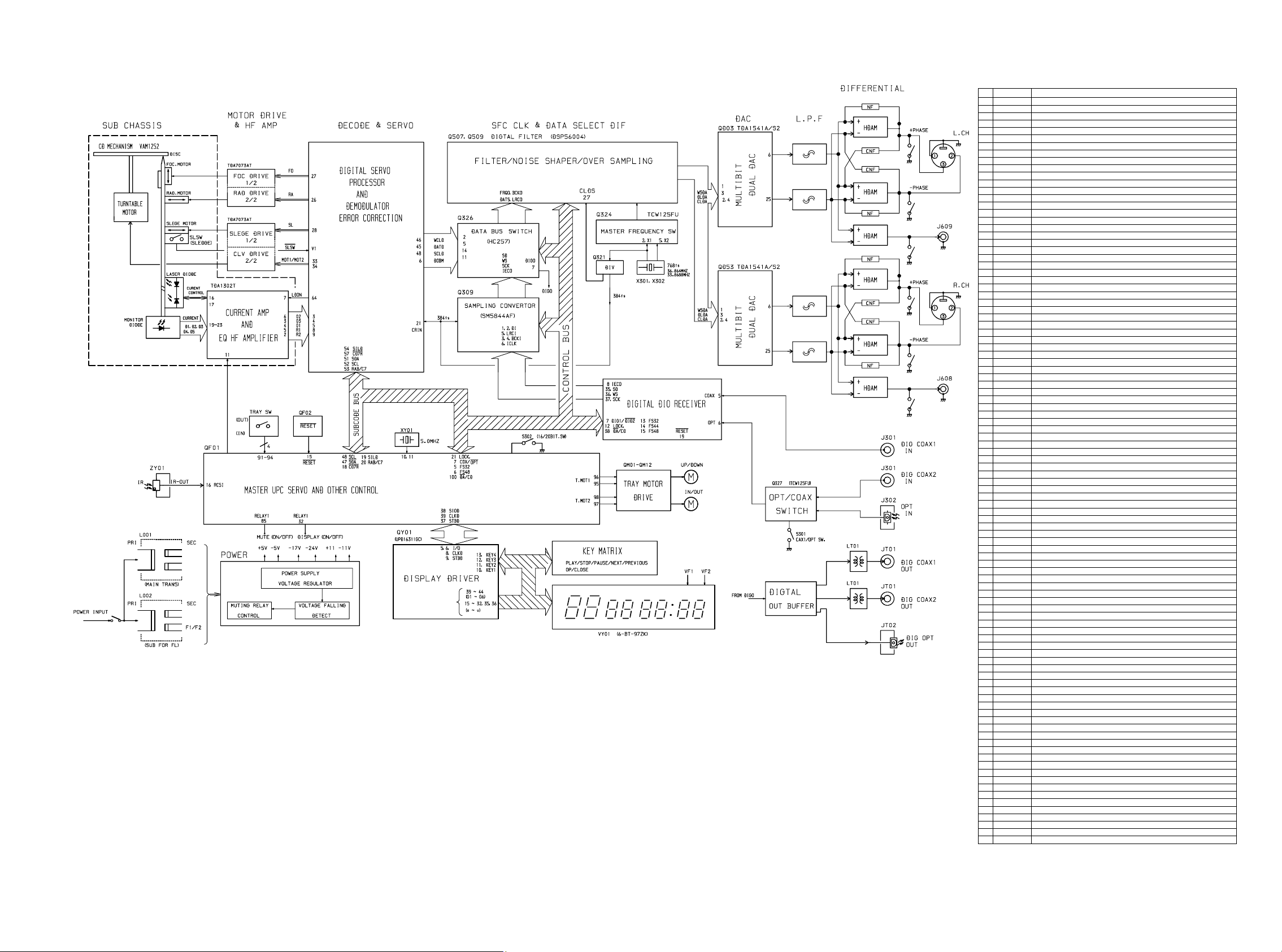

7. BLOCK DIAGRAM

g

g

g

g

)

)

)

g

(

(

(

(

(

g

(

(

g

g

(

(

(

(

)

(

(

(

(

(

(

(

(

(

(

(

(

(

(

g

g

y

g

g

(

g

(

(

(

Q103

Q104

Q102 SAA7372GP

Q304 TDA1315

8. FLAG No.

No. Flag Name Function

0 MT-OUT Motor Drive Output

1 HF-OUT TDA1302T HF si

2

3 HF-HPF HF Si

4 LDON Laser Diode Control Si

5

6 RA Radial Motor Control Si

7 FO Focus Motor Control Signal(PDM

8 SL Slegde Motor Control Signal(PDM

9

10 DIGO Di

11 CDR7 CD7

12 SILD CD7

13 RAB7 CD7

14 SCDC CD7

15 WCDC CD7

16 SIIO Servo pcb and Main pcb comunicatein

17

18 LRCK SM5844AF

19

20

21 DADC CD7

22 36MHz Samplin

23 33MHz Samplin

24 SDA From CPU

25 SCL From CPU

26

27 REST CPU

28 RCDK Main pcb SIIO Latch pulse for

29 RCDG SERVO PCB SIIO Latch pulse for QF06

30

31

32

33

34

35 OSC CPU

36 OSC CPU

37

38

39

40

41 LOCK TDA1315H

42 EMPA TDA1315H

43 DACD CD7

44

45

46

47

48 DMUT from CPU

49

50 FS32 TDA1315H

51 FS44 TDA1315H

52 FS48 TDA1315H

53 SD TDA1315H

54 WS TDA1315H

55 SCK TDA1315H

56 FRQ2 CD7

57 UNLOCK TDA1315H

58

59 COAX2 Di

60 OPT0 Di

61

62

63

64

65

66 OUT+ Correct phase AUDIO SIGNAL

67 OUT- Inverse phase AUDIO SIGNAL

68

69 REMU Rela

70

71

72

73

74

75

76

77

78

79 768FS Master clock selectin

80 256FS Master clock divided output

81 128FS Master clock divided output

82 4FS 176.4KHz before Word select si

83 WSDA Word select for DSP

84 FMUT Filter select switchin

85 CLDA DSP

86 BCEN DSP

87 BCDA for DAC

88

89

90

91

92

93

94

95

96

97

98

99

nal HPF Output

ital Audio Output Signal

SAA7372) Reset Pulse

SAA7372) Servo Parte enable Signal

SAA7372) Decorde and DSP parte enable signal

SAA7372) data clock out signal

SAA7372) data word clock out signal

SAA7372) data out(16bit) signal

QF01) Power on reset

QF01) self clock

QF01) self clock

SAA7372) data out signal

SAA7372) Operating clock out signal

tal I/O input COAX2 signal

tal I/O input OPTICAL signal

mute by POWER ON/OFF and selecting FILTER mode

Q509) data clock signal

Q509) data clock enable signal for DAC

nal output

nal

nal(PDM

Q309) word clock signal

frequency 48KHz/32KHz Master clock

frequency 44KHz Master clock

QF01) TO TDA1315H(Q304) data signal

QF01) TO TDA1315H(Q304) clock signal

Q501,Q502,Q503

Q304) unlock delayed output signal

Q304) Deemphasis output signal

QF01) to TDA1315H(Q304) muting signal

Q304) 32k Sampling detected signal

Q304) 44.1k Sampling detected signal

Q304) 48k Sampling detected signal

Q304) data output signal

Q304) Word select output signal

Q304) data clock output signal

Q304) unlock output signal

output

Q509) and DAC(QD03,QD53) 176.4KHz

on time unenable for DAC

QD03,QD53) data clock 5.6448MHz

nal

signal

9 10

Page 10

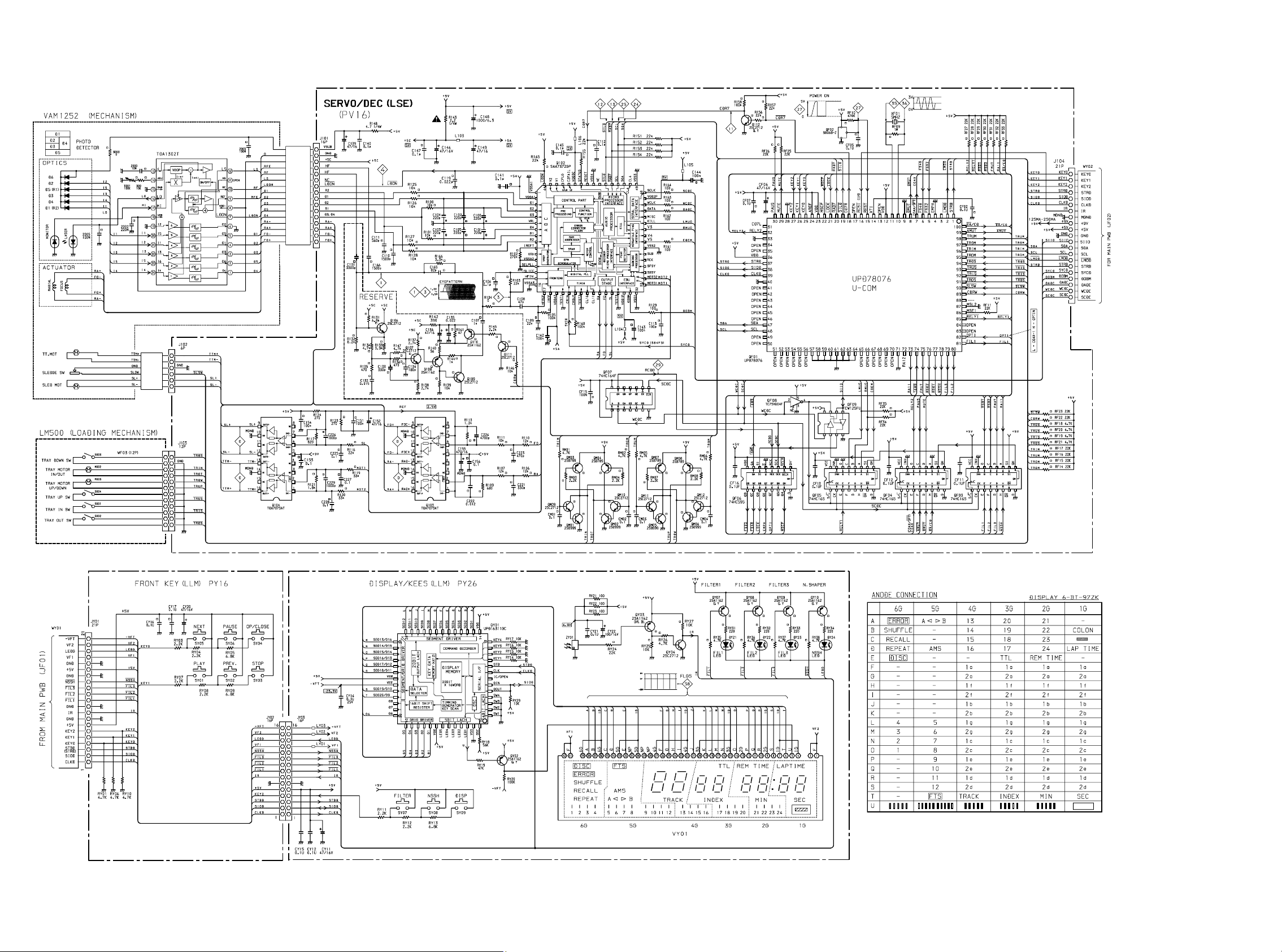

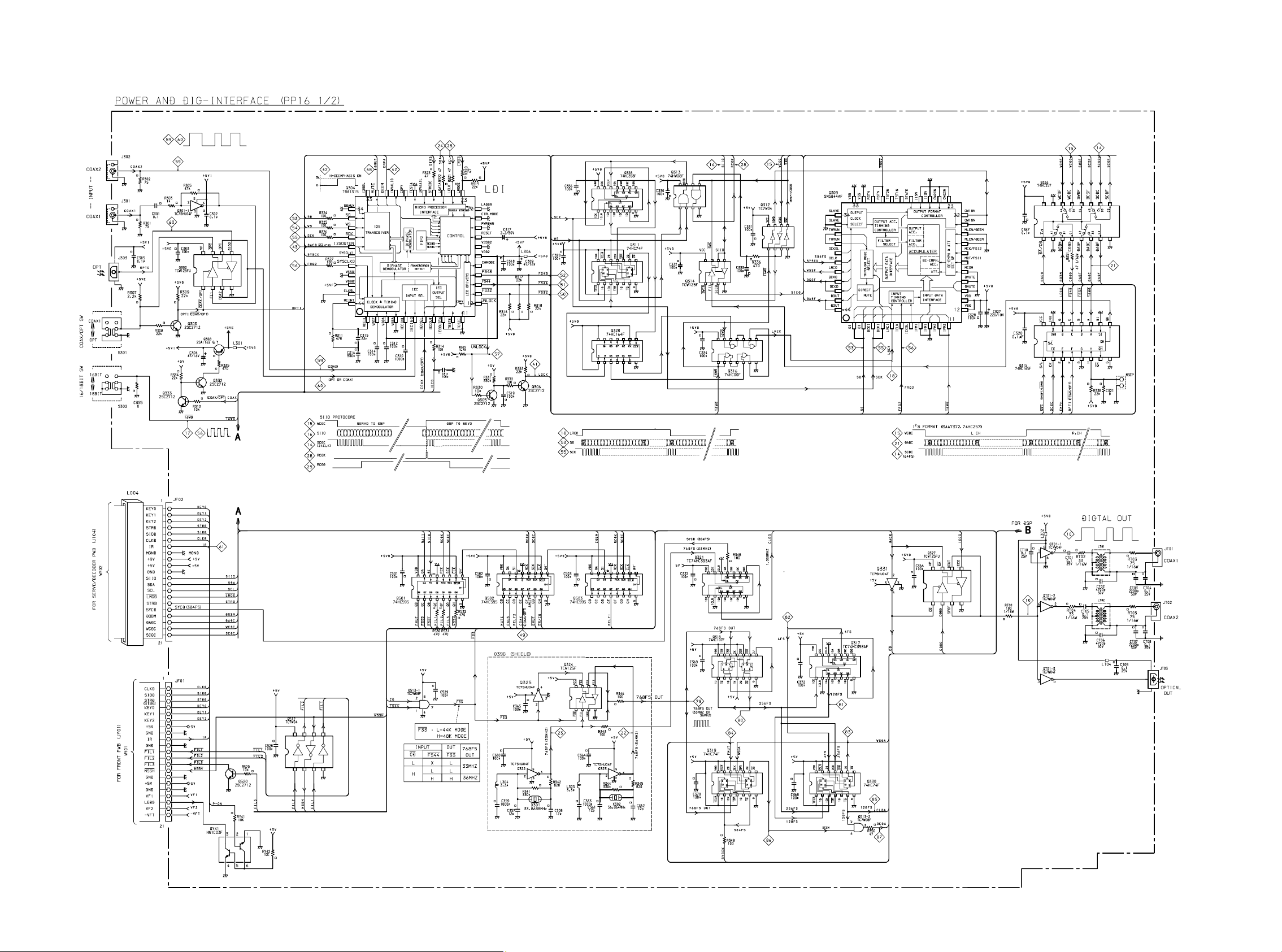

9. SCHEMATIC DIAGRAM AND PARTS LOCATION

11 12

Page 11

13 14

Page 12

15 16

Page 13

17 18

Page 14

19 20

Page 15

PP16

Q332 Q333 Q304

Q308

Q303 Q301 Q327

Q305 Q306 Q315

Q328 Q311

Q320 Q316

Q306

Q503

Q502

Q501

Q329

Q504

Q505

Q510

Q507

Q506

Q512

Q509

Q508

Q326

Q330

Q317

Q318 Q331

Q319 Q513

Q322

Q324 Q325

Q323

Q321

Q856 Q855 Q857 Q853 Q851 Q852 Q812 Q813 Q811

QT01

QY61

21 22

QN01 QN04

QN02 QN03 QY11 QN05 QY51

QY12

Q802

Q801

Q802

QN13

Q520

QY41

Page 16

PA16

Q777 Q776

Q757 Q756

Q638

Q637

Q775 Q773 Q774 Q772

Q755 Q753 Q754 Q752

Q636 Q634 Q635 Q633 Q631

Q477 Q476 Q475 Q473 Q474 Q427 Q471

QD80 QD79 QD78 QD76 QD77 QD75 QD74

QD60 QD59 QD58 QD56 QD57 QD55 QD54

Q457 Q456 Q455 Q453Q454 Q452 Q451

QD53

QD01

QD51

QD52

Q608

Q607 Q606 Q604 Q605 Q603 Q601

Q727 Q726

Q707 Q706

23 24

Q725 Q723 Q724 Q722 Q721

Q705 Q703 Q704 Q702 Q701

Q427 Q426 Q425 Q423 Q424 Q427 Q421

QD20 QD19 QD18 QD16 QD17 QD15 QD14

QD10 QD09 QD08 QD06 QD07 QD05 QD04

Q407 Q406 Q405 Q403Q404 Q402 Q401

QD03

QD21

QD22

Page 17

PV16

QM01 ~ QM12

QF02

Q112 Q106 ~ Q111 Q102

PY16

QY01 QY02 QY04 QY03

QY07 ~ QY10

QF06

QF01

QF05 QF04

QF03

Q103 Q104

QF07 QF08

PH16 PY26

25 26

Page 18

10. EXPLODED VIEW AND PARTS LIST

010D

001D

012D

PH16

KVERSION

901G

909Gx3

901G

991G

( /02, K ) ONLY

J001

W001

L608

(F)VERSION

920G

L606

L609

(/02) VERSI O N

L607

908G

111G

110G

x2

x2

016D

007D

002D

015D

097Bx 2

145B

L OADER ASSY.

A0 0 1

139Bx 2

140B

101G

100G

011D

026Dx4

997G

002G

020D

022D

130B

024D

028G

005G

L002

015G

L001

PH16

032Gx4

034Gx2

L003

010Gx2

014G

033G

930G

031Gx2

022L

006G

PA1 6

048G

040G

052G

055Gx7

036Gx3

039G

056Gx2

051G

024D

050G

x6

PP16

087G

FRONT PANEL ASSY.

001B

( 003B)

( 002B)

007B

097B

Z00 3

146B

090B

100Bx 3

010B

096B

097B

015Bx3

097B

075B

085B

020B

030B

040B

111Bx 2

050B

017B

(004B)

061Bx 4

060Bx 4

PY26

VY0 1

062Bx 4

070B

110B

121B

080B

PY1 6

995G

090G

095Gx4

005G

001G

( /02, K ) ONLY

996G

003G

019D

SYMBOL

5104

5110

5126

5127

5128

5130

5148

5150

5157

5159

5404

022D

021D

026Dx4

+F.H.M.SCREW

+B.H.M.SCREW

+B . H. T AP T I TE SCREW W/WASHER

+B.H.TAP TITE SCREW(W/)

+B . H. T AP T I TE SCREW(B T YPE)

+P . H. T AP T I T E S CREW(B TYPE)

+F . H. TAP TI TE SCREW(B TYPE)

+P . H. T AP T I T E S CREW(S TYPE)

+B . H. T AP T I T E S CREW(S TYPE)

SPRING WASHER

27 28

Page 19

(VERS. :VERSION, U:U.S.A., F:JAPAN, K:FAR EAST, /

**

POS.

NO

VERS.

COLOR

PART NO.

(FOR PCS)

DESCRIPTION

:EUROPE)

PART NO.

(MJI)

POS.

NO

VERS.

COLOR

PART NO.

(FOR PCS)

DESCRIPTION

PART NO.

(MJI)

002B 4822 459 05285 FRONT PANEL 355K248110

003B 4822 426 10823 ESCUTCHEON, FRONT SIDE

PIECE LEFT GLD

004B 4822 426 10824 ESCUTCHEON, FRONT SIDE

PIECE RIGHT GLD

007B 4822 454 13454 BADGE, META-LETTER

MARANTZ SILVER

010B 4822 463 11251 BUSHING, POWER BUTTON 355K259040

013B 4822 492 71359 SPRING, RETAINER BUTTON

GROUND

015B 4822 463 11252 RETAINER, BUSH BUTTON

PLAY STOP PAUSE

017B 4822 532 40221 RETAINER, BUSH BUTTON

OPEN/CLOSE

020B 4822 410 12398 BUTTON, ASSY PLAY GLD 355K270520

030B 4822 410 12399 BUTTON, ASSY STOP GLD 355K270530

040B 4822 410 12401 BUTTON, ASSY PAUSE GLD 355K270540

050B 4822 410 12402 BUTTON ASSY, OPEN/CLOSE 355K270550

060B 4822 492 71357 SPRING, BUTTON LARGE 270K115010

061B 4822 462 71931 BUFFER, 270K056010

070B 4822 463 11253 BUSHING, FILTER

BUTTON/LED

075B 4822 463 11254 BUSHING, TRACK BUTTON 355K259030

080B 4822 410 12403 BUTTON, FILTER 355K270170

085B 4822 410 12404 BUTTON, TRACK 355K270160

096B 4822 450 10643 WINDOW, GLASS,PINK

SMOKE

130B 4822 410 12405 BUTTON, POWER ASSY GLD 355K270510

146B 4822 442 01801 ESCUTCHEON, TRAY LID

GLASS

355K063110

355K063120

208J251010

270K115030

355K104120

270K104010

355K259020

355K158010

355K063030

PACKING

001T F USER GUIDE 355K851110

001T K USER GUIDE 355K851350

001T /02 4822 736 16822 USER GUIDE 355K851310

Z003 4822 219 10702 REMOTE COMMANDER,

RC-D7CD

ZK355K0010

001D LID, TOP COVER 355K257110

002D ESCUTCHEON, LOUVER TOP

COVER GLD

020D SIDE PANEL, LEFT GLD 355K249110

021D SIDE PANEL, RIGHT GLD 355K249120

024D 4822 454 30488 ESCUTCHEON, SIDE PANEL 270K063050

028G 4822 402 11299 LINK, POWER SW. LINK 355K121010

095G 4822 462 42132 LEG, U D60 163J057220

100G SCREW, 001G + A001 PIVOT 355K010010

A001 4822 691 10787 LOADER ASSY VAM1252 355K304520

J001 4822 265 11399 JACK, 2P AC INLET SOT-16C YJ04002360

J081 K 4822 265 10092 JACK, AC ADAPTER.SMK

S-16116

L001 F MAINS TRANSFORMER 100V TS46010010

L001 K MAINS TRANSFORMER

110/220V

L001 /02 4822 146 11139 MAINS TRANSFORMER 230V TS46010020

L002 F SUB TRANSFORMER 100V TS13521010

L002 K SUB TRANSFORMER TS13521040

110/220V

L002 /02 4822 146 11141 SUB TRANSFORMER 230V TS13521020

L003 FERRITE CORE,

TFCK-23-11-14

L004 FERRITE CORE,

HF70SH28X2X10

L005 F FERRITE CORE,

ZCAT1518-0730

L006 F FERRITE CORE,

ZCA1518-0730

231J063110

YJ04001240

TS46010040

FC50230010

FC90280010

FC50150020

FC50150020

NOT STANDARD SPARE

PARTS

001S PACKING CASE, HI-FI GL 355K801020

002S CUSHION, FRONT 270K809010

003S CUSHION, REAR 270K809020

009S PROTECTOR, COVER 355K269010

Z001 BATTERY, UM-4NEPH/2S ZF24302000

Z002 CONNECTIVE CORD,

RCA CABLE ASSY

ZD01000680

W001 F 4822 321 11337 MAINS CORD, 125V ZC01802080

W001 K MAINS CORD, 2.5A 250V ZC01803090

W001 /02 4822 321 11439 MAINS CORD, 10A 250V ZC01803080

29

Page 20

(VERS. :VERSION, U:U.S.A., F:JAPAN, K:FAR EAST, /

**

POS.

NO

VERS.

COLOR

PART NO.

(FOR PCS)

DESCRIPTION

:EUROPE)

PART NO.

(MJI)

POS.

NO

VERS.

COLOR

PART NO.

(FOR PCS)

DESCRIPTION

PART NO.

(MJI)

A001 4822 691 10787 LOADER ASSY VAM1252 355K304520

012M 4822 528 81163 PULLEY, WIRE WHEEL F 167K262010

013M 4822 530 70043 RG RING E, WHEEL 64002500R0

014M 4822 528 81387 PULLEY, WIRE WHEEL R 221K262010

015M 4822 530 70043 RG RING E, WHEEL R 64002500R0

020M 4822 528 81238 PULLEY, MIDDLE TRAY DRIVE 167K262050

021M 4822 530 70043 RG RING E, E MIDDLE PULLEY 64002500R0

022M 4822 528 81166 PULLEY, MOTOR 167K262040

024M COVER, MOTOR 225K053010

025M 4822 358 30762 BELT, MOTOR 167K264010

026M 4822 358 31065 BELT, TRAY DRIVE 221K264010

027M 4822 321 30374 JOINT, WIRE ROPE 221K125010

028M 4822 492 33161 SPRING, WIRE TENSION 221K115030

045M 4822 528 30392 CAM, CLAMPER DRIVE 221K054010

046M 4822 530 70043 RG RING E, E 045M + 070M 64002500R0

047M 4822 528 81164 PULLEY, CLAMPER MIDDLE 167K262020

048M 4822 530 70043 RG RING E, E MIDDLE PULLEY 64002500R0

049M 4822 528 81166 PULLEY, MOTOR 167K262040

051M 4822 358 30762 BELT, MOTOR 167K264010

052M 4822 358 30763 BELT, CAM DRIVE 167K264020

073M 4822 492 70628 SPRING, DOWN ADJUSTER 167K115060

074M SHAFT, CLAMPER BEARING 221K112010

075M 4822 530 70043 RG RING E, BEARING SHAFT 64002500R0

076M 4822 535 93105 SHAFT, L/R ADJUSTER 221K112020

077M 4822 492 70631 SPRING, L/R ADJUSTER 221K115050

078M 4822 530 70122 RG RING E, E ADJUSTER END 64000200R0

079M 4822 532 52236 WASHER 221K012010

080M 4822 535 92575 SHAFT, TO DRIVE 160M,162M 167K112040

081M 4822 402 61335 LEVER, CLAMPER DRIVE K 221K354520

084M 4822 492 70629 SPRING, CLAMPER

PULL DOWN

086M COLLAR, TO 080M 225K055010

087M LEVER, CLAMPER 221K354010

088M 4822 528 90837 ROLLER 221K358030

089M 4822 535 93288 SHAFT 221K112150

090M 4822 256 91866 HOLDER, CLAMPER ARM 221K271010

092M 4822 528 90836 ROLLER 221K358020

093M 4822 532 51467 STOPPER 316Y114010

094M 4822 256 10563 CLAMPER, MAGNET CASE 355K005010

095M 4822 526 10726 MAGNET 355K305010

096M 4822 528 90783 COVER, YOKE FOR MAGNET 221K053010

221K115020

155M 4822 441 12323 CASE, TRAY BLK 167K064140

157M 4822 535 92576 SHAFT, TRAY GUIDE PINS 167K112050

160M 4822 402 61089 LEVER, TRAY LIFT LEFT 167K354500

161M 4822 492 70633 SPRING, TRAY LIFT LEFT 221K115070

162M 4822 402 61091 LEVER, TRAY LIFT RIGHT 167K354510

163M 4822 492 70632 SPRING, TRAY LIFT RIGHT 221K115060

164M 4822 418 10424 TRAY, U/D DISC BLK 355K163010

165M 4822 418 10425 TRAY, SINGLE VAM1252 355K163020

166M 4822 532 11697 BUSHING, TRAY GUIDE 167K259010

167M 4822 532 21323 BUSHING, TRAY GUIDE 167K259020

168M 4822 532 11698 BUSHING, DISC BUFFER 167K259040

169M BUFFER, SILENCER SHEET 355K056010

501M 4822 691 10788 MECHANISM, VAM 1252 355K304600

502M 4822 691 10789 CASE, MECHA VAM 1252 355K064010

503M SHAFT, SUB-FIX AND TRAY

GUIDE

506M 4822 532 21452 BUSHING, SUSPENSION

RUBBER

507M 4822 492 11745 SPRING, SUSPENSION 355K115010

508M 4822 530 70561 RETAINER, SUSPENSION

SPRING STOPPER

512M 4822 530 80349 SPRING WASHER, FOR 504M 54040302N0

513M SPACER, 502M,TO 169M,170M 291K118030

M002 4822 361 60467 D.C MOTOR, TRAY DRIVE MM00800010

M003 4822 361 60447 D.C MOTOR, CLAMPER DRIVE MM01200130

S001 4822 277 21132 SLIDE SW., TRAY IN END SMK SS01020590

S002 4822 277 21132 SLIDE SW., TRAY OUT END

SMK

S003 4822 277 21132 SLIDE SW., CLAMPER DOWN

END SENSOR

S004 4822 271 30712 MINI SW., CLAMPER UP END

SENSOR

221K112040

221K259010

221K104020

SS01020590

SS01020590

SM01020550

100M 4822 462 71811 BUFFER, CLAMPER 167K056110

101M 4822 462 71809 BUFFER, CLAMPER TOP 158K056140

102M 4822 466 61927 BUFFER, CLAMPER TOP 225K056030

106M 4822 256 91867 HOLDER, TRAY FRONT

SUPPORT

108M 4822 532 30509 BUSHING, FRONT GUIDE 225K259010

120M SHAFT, TRAY GUIDE 221K112060

121M BUFFER, TRAY IN-END 221K056040

122M BUFFER, TRAY 0UT-END 221K056050

123M BUFFER, TRAY IN-END 221K056060

125M 4822 256 91196 HOLDER, SLIDE BEARING K 167K271500

134M STOPPER, TRAY ADJUST 221K114010

138M 4822 256 91195 HOLDER, SLIDE GUIDE RIGHT 167K271010

140M BRACKET, TRAY LEFT SIDE

141M BRACKET, TRAY RIGHT SIDE

142M STAY, REINFORCEMENT L/R

144M BRACKET, ADDITIONAL

221K271020

30

Page 21

140M

028M

013M

125M

012M

124M

175M

027M

123M

160M

025M

168Mx4

015M

026M

021M

121M

161M

014M

020M

155M

157M

164M

165M

169M

122M

144M

167M

166M

167M

076M

074M

134M

132M

120M

022M

086M

077M

084M

M0 0 2

087M

068M

162M

024M

090M

080M

163M

S0 0 4

081M

073M

046M

079M

075M

045M

089M

085M

092M

093M

101M

078M

100M

102M

096M

095M

094M

088M

142M

141M

138M

108M

103M

506Mx4

513M

502M

507Mx 4

508Mx 4

106Mx2

503Mx2

001M

PV1 6

M0 0 3

049M

501M

047M

048M

040M

051M

060M

S003

010M

052M

A001

LOADER

ASSY

31 32

Page 22

11. TRAY MECHANISM ADJUSTMENTS

1. When mounting tray and tray case

(when replacing tray case because of damage etc.)

a) When the tra y has been positioned improperly with a de vi-

ated clearance to the front panel window , re-mo v e the tr a y

lid, loosen screws A and adjust by moving the tray frame

within the range of the holes play.

A

Tray

Tray lid Retainer

Tray case

A

Tray lid Glass

2.When the tray Is disengaged to the lower side

Tray

When the tray is pushed downward without the sub-chassis

(VAM1252), it will be disengaged. So care will be necessary.

(Closing the tray without the sub-chassis also disengages

A

the tray.)

Mount the tray referring to the figures below.

a) Bring down the lev er and put the tray on the protrusion of

lever .

3.When replacing the sub-chassis (VAM1252)

a) The height of the sub-chassis turn table is different one by

one. Adjust each turn table height so that the magnet

clamper does not touch the clamper metal strap as shown

in the figure.

Standard ( 1.5+0.3 / -0 mm)

0.3

1.5 ± mm

0

Clamper

metal strap

DISC

Clamper metal

Strap height

adjustment screw

4.Others

a) For the loading wire winding, refer to the figure be-low.

Wind from inside to outside (1 2 3).

Wind form

inside to outside

1

2

3

b) When the magnet clamper (094M) is replaced, bent the

narrowest tab and remove the clamper.

Bend the narrowest tab.

For the tray tilt adjustment. refer to the figure below.

Tray case

a

b

Mechanism chassis

a = b = 29.0 ± 0.2

a - b ±0.2

Front side

Adjust the tilt with screws A.

b) The operating pow er of the tray is set to 250 - 350g r (P ower

OFF).

250 ~ 350gr

Tray

Lever

b) While holding the tray, bring down the opposite lever and

put the tray on the protrusion of the lever.

Protrusion

Note :

If both the levers are brought do wn at the same time, the tra y

cannot be raised. The levers should be brought down one by

one.

If the tray is forced to move to the original position, the two

pins injected into the tray case may be bent.

b) After replacing the sub-chassis, readjust so that the mag-

net clamper does not touch the clamper metal strap at

right and left sides. (The clamper metal strap should not

be touched to other straps.)

Clamper arm

adjustment

screw

Clamper arm

Clamper

Bend the narrowest tab

33 34

Page 23

11.11.

トト

レレ

ーー

メメ

カカ

ニニ

ズズ

ムム

のの

調調

11.

ト

レ

ー

メ

カ

ニ

ズ

トト

ト

トト

ニニ

レレ

レ

レレ

ーー

ー

ーー

ズズ

ケケ

ケ

ケケ

ム

ムム

ーー

ー

ーー

A

11.11.

トト

レレ

ーー

メメ

カカ

1.1.

トト

レレ

ーー

おお

よよ

ー

ーー

お

おお

よ

よよ

びび

び

びび

1.

ト

レ

1.1.

トト

レレ

(破損等でトレーケースを交換した場合等)

a)トレーのフ ロントパネル窓に対する位置の狂いが発生した時

はトレー蓋を外し、 ネジAをゆるめ穴のガタ の範囲で トレー

枠を動かし調整して下さい。

の

のの

スス

ス

スス

調

調調

取取

取

取取

りり

り

りり

整整

整

整整

付付

付

付付

けけ

け

けけ

時時

時

時時

2.2.

2.

2.2.

トト

ト

トト

レレ

レ

レレ

ーー

ー

ーー

がが

が

がが

下下

下

下下

側側

側

側側

にに

に

にに

外外

外

外外

Tray

れれ

れ

れれ

たた

た

たた

時時

時

時時

3.3.

ササ

ブブ

シシ

ャャ

ーー

シシ

((

3.

サ

ブ

シ

3.3.

1.5 ± mm

ャ

ササ

ブブ

シシ

ャャ

a)サブシャ ーシの夕一ンテーブル高さ は1 台ずつ違いますので、

ターンテーブルの高さに合わせて下図のように、マグネ ットク

ランパーがクランパ ー金具に接触しないように、 クランパー金

具高さ調整ネジを調整して下さい。

規格 (1.5+0.3/-0mm)

0.3

0

ー

ーー

シ

シシ

VAM1252VAM1252

(

VAM1252

((

VAM1252VAM1252

))

をを

交交

換換

)

を

交

換

))

をを

交交

換換

Clamper

metal strap

しし

し

しし

たた

た

たた

時時

時

時時

4.4.

そそ

のの

他他

4.

そ

の

他

4.4.

そそ

のの

他他

a)ローディングワイヤーの巻き付けは下図参照ください。

内から外に巻く(123)。

Tray

Tray lid Retainer

Tray case

A

Tray lid Glass

トレーの傾きについては下図を参考にしてください。

Tray case

a

Mechanism chassis

a = b = 29.0 ± 0.2

a - b ±0.2

Front side

次の条件では、 トレーが下側に外れるので注意願います。サ

ブシ ャーシ(VAM1252)が無い状態 にてトレーを 下側に押す

と外れます。

A

(サブ シャ ー シ が無い状態にてCLOSEした時も同様です。)

下図の要領にて取り付けてください 。

a)レバーを下げて、レバーの突起にトレーをのせます。

Tray

Lever

b)サブシャーシ交換後、 マグネットクランパーがクラ ンパー金

b

b)のせたら、トレーを押さえたまま反対側のレバーを下げて、

突起にのせます。

Protrusion

DISC

具に左右接触しないように、クランパーアーム調整ネジを再

調整して下さい。(その際、クラ ンパー金具と他の金具とが

接 しない様にする事)

Clamper metal

Strap height

adjustment screw

1

2

3

b)マグネットクランパ ー (094M )の交換は1ケ所曲がる構造

の爪となっていますので、爪を 傾けて取り外 し、取 り付けて

ください。一番幅の細い爪が傾きます。

Bend the narrowest tab

Wind form

inside to outside

傾き もネジA にて調整し ます。

b)トレーの動作力は、250〜3 50grの設定です。

(電源OFF時)

250 ~ 350gr

Clamper arm

[[

注注

意意

]]

[

注

意

]

[[

注注

意意

]]

左右、2つのレバーを一度に下げても、 トレーは上げられません

ので 、必ず片方づつ下げて作業してください 。 トレーを無理に元

の位置まで戻すと、トレーケースに圧入されている2 本のピンが曲

がる危険があ り ます。

35 36

adjustment

screw

Clamper arm

Clamper

Page 24

12. B ALANCED J ACKS

12.BALANCED12.BALANCED

12.BALANCED

12.BALANCED12.BALANCED

端端

端

端端

子子

子

子子

にに

に

にに

つつ

つ

つつ

いい

い

いい

てて

て

てて

13. DIGITAL FILTER

13.13.

13.

13.13.

デデ

デ

デデ

ジジ

ジ

ジジ

タタ

タ

タタ

ルル

ル

ルル

フフ

フ

フフ

ィィ

ィ

ィィ

ルル

ル

ルル

タタ

タ

タタ

ーー

ー

ーー

にに

に

にに

つつ

つ

つつ

いい

い

いい

てて

て

てて

1. The balanced output connector uses a XLR connector.

2. The XLR connector for professional use is internally wired in

either of the following two systems.

1. USA system (PIN 2 = COLD, PIN 3 = HOT)

COLD

GND

12

3

HOT

2. European system (PIN 2 = HOT, PIN 3 = COLD)

HOT

COLD

3 The CD-7 uses the USA system of 1.

When a preamp or main amplifier adopting the European

system is connected using a cable with XLR balanced connectors, the reproduced signal may be inverted of phase.

In this case, correct the wiring of the one of the XLR connectors on the extremities of the cable to the USA system by

exchanging the connections of pins 2 and 3.

This will make it possible to play the signal with the correct

phase.

12

3

GND

1BALANCED端子には XLR コネクターを使用しています。

2XLRコネクターの接続方法は、プロフェッショナル用としてタ

イプが二通りあります。

1.USA方式(2PIN=COLD3PIN=HOT)

2.ヨーロッパ方式(2PIN=HOT3 PIN=COLD)

3CD‑7では、1. の USA 方式を採用しています。

XLRBALANCEDケーブルを使用する場合、ヨーロッパ方式を採用

しているプリアンプやメインアンプで再生した場合、信号が逆

位相になる場合があります。

その場合は、片側のXLRコネクターの2PINと3PINをUSA方式

となるようにつなぎ換えてください。

これで信号は正しい位相で再生されます。

FILTER-1

For playing m usic with smooth depth, such as analog records.

FILTER-2

A sound between FILTER-1 and FILTER-3.

FILTER-3

A well-balanced, standard sound for all sources.

Changing the Filter Type

FILTER-1 is selected automatically when the power is turned

on.

Press the FIL TER b utton to switch to FILTER-2, again to switch

to FILTER-3, and a third time to switch back to FILTER-1.

FILTER‑1

インパルス応答では、プリエコーの少ない特性です。アナログ

レコードのような滑らかな奥行きのある音質傾向です。

FILTER‑2

インパルス応答では、プリエコー、アフターエコー共に少ない

特性です。フィルター(FILTER‑1とFILTER‑3)の両方の特性を

合せ持ったバランスの音質傾向です。

FILTER‑3

インパルス応答では、プリエコー、アフターエコーが均等にあ

る特性です。ソースを選ばないリファレンス的な音質傾向です。

フィルタータイプ変更(FILTER)

電源スイッチON後の状態は、優先的にFILTER‑1 がセレクトさ

れています。

FILTER ボタンを一度押す度に、FILTER‑2、FILTER‑3 と切替わ

り、三度めに FILTER‑1 に戻ります。

選択した FILTER のインジケーターが点燈します。

37 38

Page 25

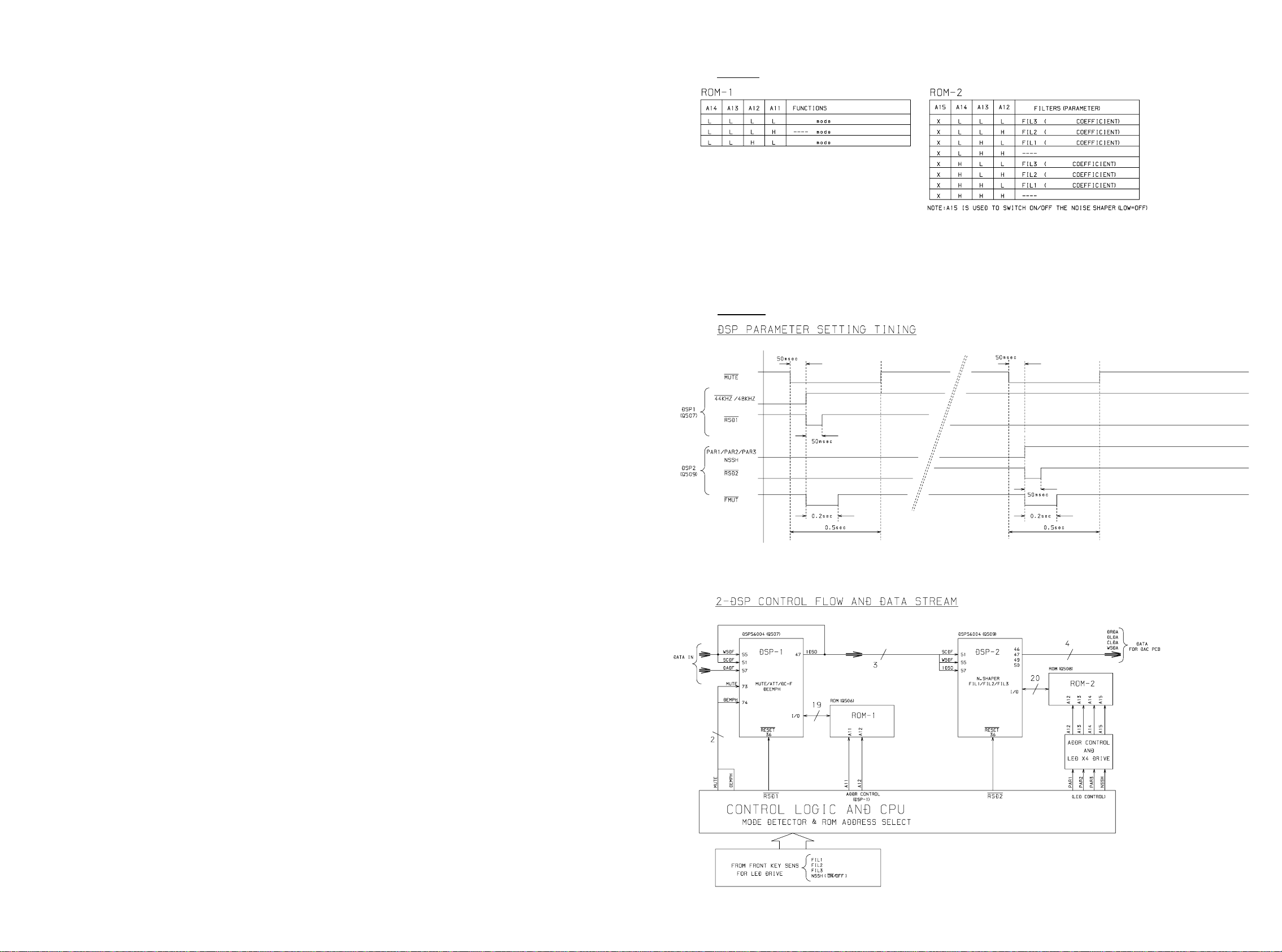

14. EXPLANATION OF DSP

14.DSP14.DSP

14.DSP

14.DSP14.DSP

の説明の説明

の説明

の説明の説明

Table 1

The digital processing for DSP-1/DSP-2 (DSP56004) is the

following compositions.

1. DSP-1 (Q507)

Mute (32-Sample<cosine curve> approx. 0.7mS)

-12dB attenuation (It is not available for CD-7)

De-emphasis (44k / 48k mode)

DC-Filter ON/OFF (It is fixed for CD-7)

Signal format (IIS-IN/OUT)

2. DSP-2 (Q509)

Digital filter (4fs<FIR>, 3Type-mode)

Noise shaper (first order) and Round

Offset of Output-DATA

Signal format (IIS-IN/OUT)

Procedure of DSP

The DSP56004 (Q507/Q509) loads data of ROM (Q506/Q508)

at that moment of the product is POWER ON. The all parameters of default setting will be done approx. 0.5 seconds. And

then, each DSP device starts digital processing by each parameter.

The product is set in Filter-1 of CD-mode initially when POWER

ON.

When the filter and the noise shaper is shifted and the sampling frequency is shifted to other frequency except 44.1kHz,

Those parameters are changed to other parameters.

REMARK : The change of the sampling frequency depend on

the input of digital signal.

These changes of parameters are based on the function tables

of ROM-1 and ROM-2 (Figure 1). Each function of DSP-1 and

DSP-2 actuates individually.

If signals are confirmed at the input or output pins of DSP, that

is actuated for DSP.

The setting confirmation of each mode after the parameter

updated, which will be able to refer to the impulse signals of

timing chart (Figure 2).

When mute or de-emphasis is switched, the parameters is not

changed.

Because these switches control the pins of DSP devise (Q507)

directly.

Then, the following status are confirmed by the pin control

status.

DSP56004によるデジタル処理は以下2ブロック構成になっていま

す。

1.DSP1(Q507)

●ミュート機能(コサインカーブによる32‑Sample約0.7mS)。

●‑12dBアッテネーション機能(CD‑7 使用せず)。

●ディエンファシス機能(44k/48k)。

●DC‑Filter機能。ON/OFF 可能(CD‑7 では固定)。

●信号フォーマット(IIS‑IN/OUT)。

2.DSP2(Q509)

●デジタルフィルター機能(FIRによる4fs、3Type‑mode)。

●ノイズシェーパー機能(firstorder)及びラウンド。

●Output‑DATAのオフセット機能。

●信号フォーマット(IIS‑IN/OUT)。

DSPの動作説明

DSP56004(Q507/Q509)は電源ON にした時、リセット状態から立ち

上がる際にROM(Q506/Q508)のデータをロードします。

この間約0.5secでディフォルトのパラメーターの設定を全て完了

します。

完了すると各DSPはそれぞれのパラメーターによるデジタル処理

を開始します。

電源ONにした時はイニシャルで CD‑ モードの Filter‑1 が設定さ

れます。

操作ボタンによるFilterとノイズシェーパーの変更及びサンプリ

ング周波数の切り換えの場合に限り、新たなパラメーターによる

デジタル処理に切り変わります。

これらのパラメーターの変更はROM‑1とROM‑2の真理表(Table1)

によって決定されます。真理表からわかるように、それぞれの機

能はDSP‑1と DSP‑2 によって、個別に動作します。

また、DSPが動作してるかどうかは、DSPの入出力ピンに信号が出

ていることで確認できます。パラメーターの更新がされてそれぞ

れのモードに設定されたかどうかは、パラメーターの更新シーケ

ンスのタイムチャート(Figure2)のインパルス信号の特性によっ

て確認をします。

ミュートとディエンファシスのON/OFFではパラメーターの再設定

は行いません。これらの切り換えはDSP(Q507)の端子を直接コン

トロールしています。従って、Pinをコントロールする事により

下記の状態を確認できます。

ミュート :Pin73(Q507)=Highでオン、Lowでオフ。

ディエンファシス :Pin74(Q507)=High でオン、Lowでオフ。

Figure 1

44kHz

48kHz

44.1kHz

44.1kHz

44.1kHz

48kHz

48kHz

48kHz

Mute Pin 73(Q507) : High = on, Low = off

De-emphasis Pin 74(Q507) : High = on, Low = off

39 40

Page 26

15. ELECTRICAL PARTS LIST

**

ASSIGNMENT OF COMMON PARTS CODES.

RESISTORS

R

: 1) GD05 × × × 140, Carbon film fixed resistor, ±5% 1/4W

R

: 2) GD05 × × × 160, Carbon film fixed resistor, ±5% 1/6W

Examples ;

Resistance value

➀

0.1 Ω.... 001 10 Ω .... 100 1 kΩ .... 102 100 kΩ.... 104

0.5 Ω.... 005 18 Ω .... 180 2.7 kΩ ....272 680 kΩ.... 684

1 Ω.... 010 100 Ω .... 101 10 kΩ .... 103 1 MΩ.... 105

6.8 Ω.... 068 390 Ω .... 391 22 kΩ .... 223 4.7 MΩ.... 475

Note : Please distinguish 1/4W from 1/6W by the shape of parts

used actually.

CAPACITORS

C

: CERAMIC CAP.

3) DD1 × × × × 370, Ceramic capacitor

Examples ;

Tolerance (Capacity deviation)

➁

±0.25 pF .... 0

Tolerance of COMMON PARTS handled here are as follows :

C

Examples ;

C

Examples ;

Examples ;

NOTE

0.5 pF 5 pF ....±0.25 pF

12 pF 560 pF ....±5%

Capacity value

➂

0.5 pF .... 005 3 pF ....030 100 pF .... 101

1.5 pF .... 015 47 pF ....470 560 pF .... 561

: CERAMIC CAP.

4) DK16 × × × 300, High dielectric constant ceramic

Capacity value

➃

100 pF .... 101 1000 pF .... 102 10000 pF ....103

470 pF .... 471 2200 pF .... 222

: 5) ELECTROLY CAP. ( ), 6) FILM CAP. ( )

5) EA × × × × × × 10, Electrolytic capacitor

Capacity value

➄

0.1 µF....104 4.7 µF ....475 100 µF ....107

0.33 µF....334 10 µF ....106 330 µF....337

Working voltage

➅

6) DF15 × × × 350 Plastic film capacitor

DF15 × × × 310 One-way type, Mylar ±5% 50V

DF16 × × × 310 Plastic film capacitor

Capacity value

➆

0.001 µF(1000 pF) ....... 102 0.1 µF ....104

0.0018 µF........................ 182 0.56 µF....564

0.01 µF........................ 103 1 µF.... 105

0.015 µF........................ 153

: 1) The above CODES ( R , R , C , C and

C ) are omitted on the schematic diagram in some

2) On the occasion, be confirmed the common parts on

3) Refer to “Common Parts List” for the other common

{

➂

{

{

➅

{

Resistance value

Disc type

Temp.coeff.P350 N1000, 50V

Capacity value

Tolerance

capacitor

Disc type

Temp.chara. 2B4, 50V

Capacity value

One-way lead type, Tolerance ±20%

Working voltage

Capacity value

2200 µF....228

One-way type, Mylar ±10% 50V

Capacity value

➀

{

➁

±0.5 pF .... 1

±5% .... 5

6 pF 10 pF ....±0.5 pF

1 pF .... 010 10 pF ....100 220 pF .... 221

➃

{

➄

1 µF....105 22 µF ....226 1100 µF....118

6.3V....006 25V ....025

10V....010 35V ....035

16V....016 50V ....050

➆

case.

the parts list.

parts (RI05, DD4, DK4).

(VERS. :VERSION, U:U.S.A., F:JAPAN, K:FAR EAST, /

VERS.

NOTE ON SAFETY FOR FUSIBLE RESISTOR :

The suppliers and their type numbers of fusible resistors

are as follows;

1. KOA Corporation

Part No. (MJI) Type No. (KOA) Description

NH05 × × × 140 RF25S × × × × ΩJ(±5% 1/4W)

NH05 × × × 120 RF50S × × × × ΩJ(±5% 1/2W)

NH85 × × × 110 RF73B2A × × × × ΩJ(±5% 1/10W)

NH95 × × × 140 RF73B2E × × × × ΩJ(±5% 1/4W)

2. Matsushita Electronic Components Co., Ltd

Part No. (MJI) Type No. (MEC) Description

NF05 × × × 140 ERD-2FCJ × × × (±5% 1/4W)

RF05 × × × 140

NF02 × × × 140

RF02 × × × 140

Examples ;

{

Resistance value

ERD-2FCG

{

Resistance value

Resistance value

0.1 Ω.... 001 10 Ω .... 100 1 kΩ ....102 100 kΩ.... 104

0.5 Ω.... 005 18 Ω .... 180 2.7 kΩ ....272 680 kΩ.... 684

1 Ω.... 010 100 Ω .... 101 10 kΩ .... 103 1 MΩ.... 105

6.8 Ω.... 068 390 Ω .... 391 22 kΩ .... 223 4.7 MΩ.... 475

{

Resistance value

(0.1 Ω − 10 kΩ)

× × × (±2% 1/4W)

{

Resistance value

ABBREVIATION AND MARKS

ANT. : ANTENNA BATT. : BATTERY

CAP. : CAPACITOR CER. : CERAMIC

CONN. : CONNECTING DIG. : DIGITAL

HP : HEADPHONE MIC. : MICROPHONE

µ-PRO : MICROPROCESSOR REC. : RECORDING

RES. : RESISTOR SPK : SPEAKER

SW : SWITCH TRANSF. : TRANSFORMER

TRIM. : TRIMMING TRS. : TRAMSISTOR

VAR. : VARIABLE X’TAL : CRYSTAL

NOTE ON SAFETY :

Symbol Fire or electrical shock hazard. Only original

parts should be used to replaced any part marked with

symbol . Any other component substitution (other

than original type), may increase risk of fire or electrical

shock hazard.

安全上の注意安全上の注意

安全上の注意

安全上の注意安全上の注意

::

:

::

がついている部品は、安全上重要な部品です。必ず

指定されている部品番号の部品を使用して下さい。

41 42

SM970926ACT

POS.

COLOR

NO

CD01 4822 124 41539 ELECT 47µF ±20% 16V OA47601620

CD02 4822 126 11687 CER. 0.1µF +80%-20% CHIP DK98104200

CD03 F FILM 680pF ±5% 100V CHIP OF55681540

CD03 K /02 4822 121 70319 FILM 470pF ±5% 50V OF15471030

CD05

4822 121 10867 FILM 0.1µF ±5% 100V CHIP OF55104540

CD18

CD19 4822 126 12061 CER. 0.1µ F ±10% 25V CHIP DK56104200

CD20 F 4822 124 22238 ELECT 100µF 25V OA10702550

CD20 K /02 4822 124 80119 ELECT 100µF 25V OA10702540

CD21 4822 126 11687 CER. 0.1µF +80%-20% CHIP DK98104200

CD22 4822 124 22238 ELECT 100µF 25V OA10702550

CD23 4822 126 11687 CER. 0.1µF +80%-20% CHIP DK98104200

CD24 4822 124 22238 ELECT 100µF 25V OA10702550

CD27 4822 123 30361 MICA 56pF 500WV CHIP DF95560500

CD28 4822 126 14578 MICA 1200pF 100WV CHIP DF95122510

CD29 4822 126 14579 MICA 1000pF 100WV CHIP DF95102510

CD37 4822 123 30361 MICA 56pF 500WV CHIP DF95560500

CD38 4822 126 14578 MICA 1200pF 100WV CHIP DF95122510

CD39 4822 126 14579 MICA 1000pF 100WV CHIP DF95102510

CD51 4822 126 11687 CER. 0.1µF +80%-20% CHIP DK98104200

CD53 F FILM 680pF ±5% 100V CHIP OF55681540

CD53 K /02 4822 121 70319 FILM 470pF ±5% 50V OF15471030

CD55

4822 121 10867 FILM 0.1µF ±5% 100V CHIP OF55104540

CD68

CD69 4822 126 12061 CER. 0.1µF ±10% 25V CHIP DK56104200

CD70 F 4822 124 22238 ELECT 100µF 25V OA10702550

CD70 K /02 4822 124 80119 ELECT 100µF 25V OA10702540

CD71 4822 126 11687 CER. 0.1µF +80%-20% CHIP DK98104200

CD72 4822 124 22238 ELECT 100µF 25V OA10702550

CD73 4822 126 11687 CER. 0.1µF +80%-20% CHIP DK98104200

CD74 4822 124 22238 ELECT 100µF 25V OA10702550

CD77 4822 123 30361 MICA 56pF 500WV CHIP DF95560500

CD78 4822 126 14578 MICA 1200pF 100WV CHIP DF95122510

CD79 4822 126 14579 MICA 1000pF 100WV CHIP DF95102510

CD87 4822 123 30361 MICA 56pF 500WV CHIP DF95560500

CD88 4822 126 14578 MICA 1200pF 100WV CHIP DF95122510

CD89 4822 126 14579 MICA 1000pF 100WV CHIP DF95102510

C401 4822 126 14578 MICA 1200pF 100WV CHIP DF95122510

C402 4822 126 14579 MICA 1000pF 100WV CHIP DF95102510

C403 4822 126 14579 MICA 1000pF 100WV CHIP DF95102510

C405 4822 123 30361 MICA 56pF 500WV CHIP DF95560500

C407 F 4822 124 22242 ELECT 470µF 25V OA47702550

C407 K /02 4822 124 80958 ELECT 470µF 16V OA47701640

C408 F 4822 124 22242 ELECT 470µF 25V OA47702550

C408 K /02 4822 124 80958 ELECT 470µF 16V OA47701640

C421 4822 126 14578 MICA 1200pF 100WV CHIP DF95122510

C422 4822 126 14579 MICA 1000pF 100WV CHIP DF95102510

C423 4822 126 14579 MICA 1000pF 100WV CHIP DF95102510

C425 4822 123 30361 MICA 0.1µF +-80%-20% CHIP DF95560500

C427 F 4822 124 22242 ELECT 470µF 25V OA47702550

C427 K /02 4822 124 80958 ELECT 470µF 16V OA47701640

C428 F 4822 124 22242 ELECT 470µF 25V OA47702550

C428 K /02 4822 124 80958 ELECT 470µF 16V OA47701640

C451 4822 126 14578 MICA 1200pF 100WV CHIP DF95122510

C452 4822 126 14579 MICA 1000pF 100WV CHIP DF95102510

C453 4822 126 14579 MICA 1000pF 100WV CHIP DF95102510

C455 4822 123 30361 MICA 56pF 500WV CHIP DF95560500

C457 F 4822 124 22242 ELECT 470µF 25V OA47702550

C457 K /02 4822 124 80958 ELECT 470µF 16V OA47701640

C458 F 4822 124 22242 ELECT 470µF 25V OA47702550

C458 K /02 4822 124 80958 ELECT 470µF 16V OA47701640

C471 4822 126 14578 MICA 1200pF 100WV CHIP DF95122510

C472 4822 126 14579 MICA 1000pF 100WV CHIP DF95102510

PART NO.

(FOR PCS)

PA16-DAC/HDAM

CIRCUIT BOARD

PA16-CAPACITORS

:EUROPE)

DESCRIPTION

PART NO.

(MJI)

VERS.

POS.

COLOR

NO

C473 4822 126 14579 MICA 1000pF 100WV CHIP DF95102510

C475 4822 123 30361 MICA 56pF 500WV CHIP DF95560500

C477 F 4822 124 22242 ELECT 470µF 25V OA47702550

C477 K /02 4822 124 80958 ELECT 470µF 16V OA47701640

C478 F 4822 124 22242 ELECT 470µF 25V OA47702550

C478 K /02 4822 124 80958 ELECT 470µF 16V OA47701640

C602 4822 123 30361 MICA 56pF 500WV CHIP DF95560500

C603 4822 123 30422 MICA 33pF 500WV CHIP DF95330500

C604 4822 124 80123 ELECT 220µF 16V OA22701640

C605 4822 124 80123 ELECT 220µF 16V OA22701640

C606 4822 126 11759 CER. 100pF ±5% 50V CHIP DD95101300

C611 F 4822 124 22242 ELECT 470µF 25V OA47702550

C611 K /02 4822 124 80958 ELECT 470µF 16V OA47701640

C612 F 4822 124 22242 ELECT 470µF 25V OA47702550

C612 K /02 4822 124 80958 ELECT 470µF 16V OA47701640

C632 4822 123 30361 MICA 56pF 500WV CHIP DF95560500

C633 4822 123 30422 MICA 33pF 500WV CHIP DF95330500

C634 4822 124 80123 ELECT 220µF 16V OA22701640

C635 4822 124 80123 ELECT 220µF 16V OA22701640

C636 4822 126 11759 CER. 100pF ±5% 50V CHIP DD95101300

C637 F 4822 124 22242 ELECT 470µF 25V OA47702550

C637 K /02 4822 124 80958 ELECT 470µF 16V OA47701640

C638 F 4822 124 22242 ELECT 470µF 25V OA47702550

C638 K /02 4822 124 80958 ELECT 470µF 16V OA47701640

C702 4822 123 30361 MICA 56pF 500WV CHIP DF95560500

C703 4822 123 30422 MICA 33pF 500WV CHIP DF95330500

C704 4822 124 80123 ELECT 220µF 16V OA22701640

C705 4822 124 80123 ELECT 220µF 16V OA22701640

C712 4822 123 30361 MICA 56pF 500WV CHIP DF95560500

C713 4822 123 30422 MICA 33pF 500WV CHIP DF95330500

C714 4822 124 80123 ELECT 220µF 16V OA22701640

C715 4822 124 80123 ELECT 220µF 16V OA22701640

C716 4822 126 11759 CER. 100pF ±5% 50V CHIP DD95101300

C717 4822 126 11759 CER. 100pF ±5% 50V CHIP DD95101300

C721 F 4822 124 22242 ELECT 470µF 25V OA47702550

C721 K /02 4822 124 80958 ELECT 470µF 16V OA47701640

C722 F 4822 124 22242 ELECT 470µF 25V OA47702550

C722 K /02 4822 124 80958 ELECT 470µF 16V OA47701640

C736 4822 126 11759 CER. 100pF ±5% 50V CHIP DD95101300

C737 4822 126 11759 CER. 100pF ±5% 50V CHIP DD95101300

C752 4822 123 30361 MICA 56pF 500WV CHIP DF95560500

C753 4822 123 30422 MICA 33pF 500WV CHIP DF95330500

C754 4822 124 80123 ELECT 220µF 16V OA22701640

C755 4822 124 80123 ELECT 220µF 16V OA22701640

C756 F 4822 124 22242 ELECT 470µF 25V OA47702550

C756 K /02 4822 124 80958 ELECT 470µF 16V OA47701640

C757 F 4822 124 22242 ELECT 470µF 25V OA47702550

C757 K /02 4822 124 80958 ELECT 470µF 16V OA47701640

C772 4822 123 30361 MICA 56pF 500WV CHIP DF95560500

C773 4822 123 30422 MICA 3pF 500WV CHIP DF95330500

C774 4822 124 80123 ELECT 220µF 16V OA22701640

C775 4822 124 80123 ELECT 220µF 16V OA22701640

RD11 4822 116 90503 150Ω ±5% 1/10W CHIP NI05151110

RD12 4822 116 90503 150Ω ±5% 1/10W CHIP NI05151110

RD13 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

RD14 4822 116 83352 560Ω ±5% 1/10W CHIP NI05561110

RD15 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

RD16 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

RD17 4822 116 83229 33kΩ ±1% 1/10W CHIP NI01333110

RD18 4822 116 83352 560Ω ±5% 1/10W CHIP NI05561110

RD19 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

RD20 10.0Ω ±1% 1/4W GM114100G0

RD21 10.0Ω ±1% 1/4W GM114100G0

RD22 1.62kΩ ±1% 1/4W GM11416210

RD31 4822 116 90503 150Ω ±5% 1/10W CHIP NI05151110

RD32 4822 116 90503 150Ω ±5% 1/10W CHIP NI05151110

PART NO.

(FOR PCS)

DESCRIPTION

PA16-RESISTORS

PART NO.

(MJI)

Page 27

(VERS. :VERSION, U:U.S.A., F:JAPAN, K:FAR EAST, /

**

POS.

NO

VERS.

COLOR

PART NO.

(FOR PCS)

DESCRIPTION

:EUROPE)

PART NO.

(MJI)

POS.

NO

VERS.

COLOR

PART NO.

(FOR PCS)

DESCRIPTION

PART NO.

(MJI)

RD33 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

RD34 4822 116 83352 560Ω ±5% 1/10W CHIP NI05561110

RD35 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

RD36 4822 111 90893 100Ω±5% 1/10W CHIP NI05101110

RD37 4822 116 83229 33kΩ ±1% 1/10W CHIP NI01333110

RD38 4822 116 83352 560Ω ±5% 1/10W CHIP NI05561110

RD39 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

RD40 10.0Ω ±1% 1/4W GM114100G0

RD41 10.0Ω ±1% 1/4W GM114100G0

RD42 1.62kΩ ±1% 1/4W GM11416210

RD51 4822 116 90503 150Ω ±5% 1/10W CHIP NI05151110

RD52 4822 116 90503 150Ω ±5% 1/10W CHIP NI05151110

RD53 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

RD54 4822 116 83352 560Ω ±5% 1/10W CHIP NI05561110

RD55 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

RD56 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

RD57 4822 116 83229 33kΩ ±1% 1/10W CHIP NI01333110

RD58 4822 116 83352 560Ω ±5% 1/10W CHIP NI05561110

RD59 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

RD60 10.0Ω ±1% 1/4W GM114100G0

RD61 10.0Ω ±1% 1/4W GM114100G0

RD62 1.62kΩ ±1% 1/4W GM11416210

RD81 4822 116 90503 150Ω ±5% 1/10W CHIP NI05151110

RD82 4822 116 90503 150Ω ±5% 1/10W CHIP NI05151110

RD83 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

RD84 4822 116 83352 560Ω ±5% 1/10W CHIP NI05561110

RD85 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

RD86 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

RD87 4822 116 83229 33kΩ±1% 1/10W CHIP NI01333110

RD88 4822 116 83352 560Ω ±5% 1/10W CHIP NI05561110

RD89 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

RD90 10.0Ω ±1% 1/4W GM114100G0

RD91 10.0Ω ±1% 1/4W GM114100G0

RD92 1.62kΩ ±1% 1/2W GM11416210

R401 1.47kΩ ±1% 1/4W GM11414710

R402 3.01kΩ ±1% 1/4W GM11430110

R404 4822 116 90503 150Ω ±5% 1/10W CHIP NI05151110

R405 4822 116 90503 150Ω ±5% 1/10W CHIP NI05151110

R406 4822 111 90893 100Ω±5% 1/10W CHIP NI05101110

R407 4822 116 83352 560Ω ±5% 1/10W CHIP NI05561110

R408 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

R409 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

R410 4822 116 83229 33kΩ ±1% 1/10W CHIP NI01333110

R411 4822 116 83352 560Ω ±5% 1/10W CHIP NI05561110

R412 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

R413 10.0Ω ±1% 1/4W GM114100G0

R414 10.0Ω±1% 1/4W GM114100G0

R421 1.47kΩ ±1% 1/4W GM11414710

R422 3.01kΩ ±1% 1/4W GM11430110

R424 4822 116 90503 150Ω ±5% 1/10W CHIP NI05151110

R425 4822 116 90503 150Ω ±5% 1/10W CHIP NI05151110

R426 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

R427 4822 116 83352 560Ω ±5% 1/10W CHIP NI05561110

R428 4822 111 90893 100Ω +-5% 1/10W CHIP NI05101110

R429 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

R430 4822 116 83229 33kΩ ±1% 1/10W CHIP NI01333110

R431 4822 116 83352 560Ω ±5% 1/10W CHIP NI05561110

R432 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110

R433 10.0Ω ±1% 1/4W GM114100G0

R434 10.0Ω ±1% 1/4W GM114100G0

R451 1.47kΩ ±1% 1/4W GM11414710

R452 3.01kΩ ±1% 1/4W GM11430110

R454 4822 116 90503 150Ω ±5% 1/10W CHIP NI05151110

R455 4822 116 90503 150Ω ±5% 1/10W CHIP NI05151110

R456 4822 111 90893 100Ω ±5% 1/10W CHIP NI05101110