Page 1

Information Manual

January 1998

DSP1611/17/18/27/28/29

Digital Signal Processor

For additional information, contact your Microelectronics Group Account Manager or the following:

INTERNET:

E-MAIL:

N. AMERICA: Microelectronics Group, Lucent Technologies Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18103

ASIA PACIFIC: Microelectronics Group, Lucent Technologies Singapore Pte. Ltd., 77 Science Park Dr ive, #03-18 Cintech III, Singapore 118256

CHINA: Microelectronics Group, Lucent Technologies (China) Co., Ltd., A-F2, 23/F, Zao Fong Universe Buildi ng, 1800 Zhong Shan Xi Road,

JAPAN: Microelectronics Group, Lucent Technologies Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan

EUROPE: Data Requests: MICROELECTRONICS GROUP DATALINE:

Lucent Technologies Inc. reserves the rig ht to mak e changes to the product(s) or i nformat ion cont ained herein without notice. No liability is ass um ed as a res ult of th eir use or a ppli catio n. N o

rights under any patent accompany the sale of any such produc t(s) or information.

Copyright © 1998 Lucent Technologies Inc.

All Rights Reserved

MN97-030WDSP

http://www.lucent.com/micro

docmaster@micro.lucent.com

1-800-372-2447

Tel. (65) 778 8833

Shanghai 200233 P. R. China

Tel. (81) 3 5421 1600

Technical Inquiries: GERMANY:

, FAX 610-712-4106 (In CANADA:

, FAX (65) 777 7495

, FAX (81) 3 5421 1700

FRANCE:

ITAL Y:

(39) 2 6601 1800

1-800-553-2448

Tel. (86) 21 6440 0468, ext. 316

(49) 89 95086 0

(33) 1 41 45 77 00

(Munich), UNITED KING DOM:

(Paris), SWEDEN:

(Milan), SPAIN:

, FAX 610-712-4106)

, FAX (86) 21 6440 0652

Tel. (44) 1189 324 299

(46) 8 600 7070

(34) 1 807 1441

(Madrid)

, FAX (44) 1189 328 148

(44) 1344 865 900

(Stockholm), FINLAND:

(Bracknell),

(358) 9 4354 2800

(Helsin ki ),

DRAFT COPY

Page 2

A Word About Trademarks . . .

The following Lucent Technologies Inc. trademarks are used in this manual:

Tapdance®FlashDSP

The following trademarks, owned by entities other than Lucent Technologies Inc., are used in this manual:

IEEE

is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

Intel

is a registered trademark of Intel Corporation.

Motorola

MS-DOS

TI

UNIX

X-Windows

is a registered trademark of Motorola, Inc.

and

Windows

is a registered trademark of Texas Instruments, Inc.

is a registered trademark licensed exclusively through X/Open Company Ltd.

is a trademark of Massachusetts Institute of Technology.

®

are registered trademarks of Microsoft Corporation.

ii DRAFT COPY Lucent Technologies Inc.

Page 3

Foreword

This manual contains detailed information on the design and application of the DSP1611/17/18/27/28/29 Digital

Signal Processor family, which includes the

FlashDSP

DSP1628-ST, and DSP1629-ST support software libraries, the

numerous DSP1611/17/18/27/28/29-specific hardware support tools are also available to aid in developing software and integrating the devices into systems.

Additional information on the digital signal processor product line is available in the form of manuals, data sheets,

and application notes.

1629 development devices. The DSP1611-ST, DSP1618-ST, DSP1617-ST, DSP1627-ST,

FlashDSP

®

1618,

FlashDSP

FlashDSP

1627,

FlashDSP

1600-HDS Development System, and

1628, and

Conventions Used in this Manual

In general, all registers writable or readabl e by DSP instructions are low er case. D e vice flags , I/O pins, and nonprogram-accessible registers are generally upper case. For clarity, register names and DSP instructions are printed in

boldface

cized, such as

when used in written descriptions. Variable names that are to be replaced by specific names are itali-

filename

. Instruction set notation conventions are defined in Chapter 4.

Lucent Technologies Inc. DRAFT COPY iii

Page 4

DSP1611/17/18/27/28/29 Digital Signal Processor

INFORMATION MANUAL

CONTENTS

➤ 1 Introduction.................................................................................................................................................. 1-1

➤ 1.1 General Description .......................................................................................................................... 1-2

➤ 1.1.1 Architecture ........................................................................................................................ 1-2

➤ 1.1.2 Instruction Set .................................................................................................................... 1-3

➤ 1.2 Typical Applications........................................................................................................................... 1-3

➤ 1.3 Application Support........................................................................................................................... 1-4

➤ 1.3.1 Support Software Library ................................................................................................... 1-4

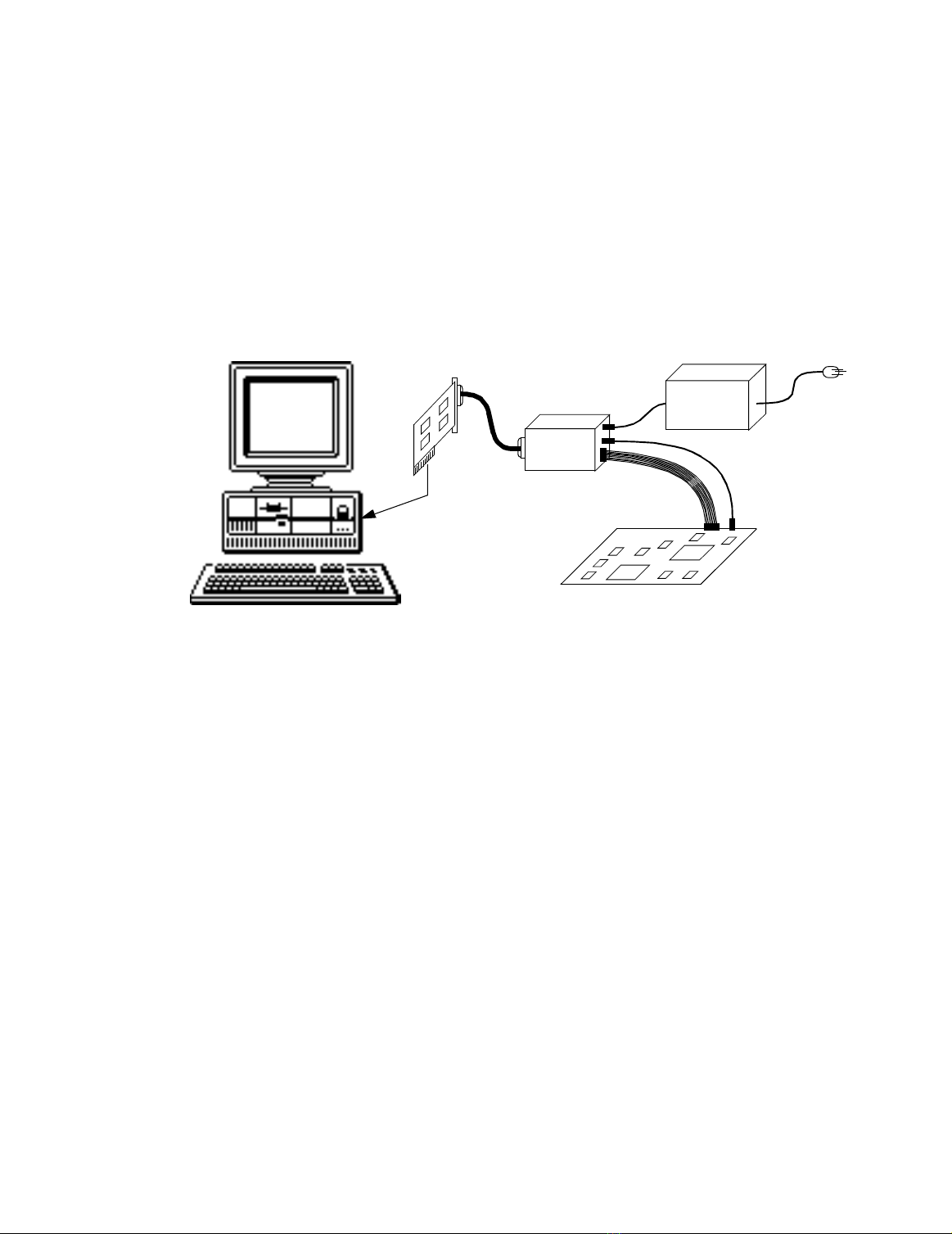

➤ 1.3.2 Hardware Development System ......................................................................................... 1-4

➤ 1.4 Manual Organization......................................................................................................................... 1-6

➤ 1.4.1 Applicable Documentation .................................................................................................1-7

➤ 2 Hardware Architecture ......................................................................................................... ........................ 2-1

➤ 2.1 Device Architecture Overview........................................................................................................... 2-1

➤ 2.1.1 Harvard Architecture .......................................................................................................... 2-1

➤ 2.1.2 Concurrent Operations ....................................................................................................... 2-2

➤ 2.1.3 Device Architecture ............................................................................................................ 2-4

➤ 2.1.4 Memory Space and B ank Switching ................................................................................ 2-12

➤ 2.1.5 Internal Instruction Pipeline .............................................................................................. 2-13

➤ 2.2 Core Architecture Overview............................................................................................................ 2-16

➤ 2.2.1 Data Arithmetic Unit ......................................................................................................... 2-16

➤ 2.2.2 Y Space Address Arithmetic Unit (YAAU) ........................................................................ 2-17

➤ 2.2.3 X Space Address Arithmetic Unit (XAAU) ........................................................................ 2-18

➤ 2.2.4 Cache ............................................................................................................................... 2-18

➤ 2.2.5 Control ............................................................................................................................. 2-18

➤ 2.3 Internal Memories ........................................................................................................................... 2-19

➤ 2.4 External Memor y Interface (EMI).................................................................................................... 2-19

➤ 2.5 Bit Manipulation Unit (BMU)............................................................................................................ 2-20

➤ 2.6 Serial Input/Output (SIO) Units ....................................................................................................... 2-20

➤ 2.7 Parallel Input/Output (PIO) (DSP1617 Only)................................................................................... 2-21

➤ 2.8 Parallel Host Interface (PHIF) (DSP1611/18/27/28/29 Only).......................................................... 2-21

➤ 2.9 Bit Input/Output (BIO) ..................................................................................................................... 2-22

➤ 2.10 JTAG ............................................................................................................................................... 2-22

➤ 2.11 Timer............................................................................................................................................... 2-22

➤ 2.12 Hardware Development System (HDS) Module.............................................................................. 2-23

➤ 2.13 Clock Synthesis (DSP1627/28/29 Only) ......................................................................................... 2-23

➤ 2.14 Power Management........................................................................................................................ 2-23

➤ 3 Software Architecture.................................................................................................................................. 3-1

➤ 3.1 Register View of the DSP1611/17/18/27/28/29................................................................................. 3-1

➤ 3.1.1 Types of Registers .............................................................................................................. 3-1

➤ 3.1.2 Register Length Definition .................................................................................................. 3-5

➤ 3.1.3 Register Reset Values ........................................................................................................ 3-6

➤ 3.1.4 Flags .................................................................................................................................. 3-7

➤ 3.2 Memory Space and Addressing........................................................................................................ 3-8

➤ 3.2.1 Y-Memory Space ................................................................................................................ 3-8

iv Lucent Technologies Inc.

Page 5

➤ 3.2.2 X-Memory Space ............................................................................................................. 3-10

➤ 3.3 Arithmetic and Precision ................................................................................................................. 3-21

➤ 3.4 Interrupts......................................................................................................................................... 3-27

➤ 3.4.1 Introduction ...................................................................................................................... 3-27

➤ 3.4.2 Interrupt Sources ............................................................................................................. 3-29

➤ 3.4.3 Outputs of Interrupts ........................................................................................................ 3-31

➤ 3.4.4 Interrupt Operation ........................................................................................................... 3-32

➤ 3.4.5 Trap Description ............................................................................................................... 3-38

➤ 3.4.6 Powerdown with the AWAIT State .................................................................................... 3-40

➤ 3.4.7 Interrupts in DSP16A-Compatible Mode (DSP1617 Only) ............................................... 3-42

➤ 3.4.8 Timing Examples, DSP16A-Compatible Mode (DSP1617 Only) ..................................... 3-44

➤ 3.5 Clock Synthesis (DSP1627, DSP1628, and DSP1629 Only).......................................................... 3-47

➤ 3.5.1 PLL Control Signals ......................................................................................................... 3-48

➤ 3.5.2 PLL Programming Examples ........................................................................................... 3-50

➤ 3.5.3 Latency ............................................................................................................................ 3-50

➤ 3.6 Power Management............................................................................................................ ............ 3-52

➤ 3.6.1 powerc Control Register Bits ........................................................................................... 3-52

➤ 3.6.2 STOP Pin ......................................................................................................................... 3-56

➤ 3.6.3 The pllc Register Bits (DSP1627/28/29 Only) ................................................................. 3-56

➤ 3.6.4 AWAIT Bit of the alf Register ........................................................................................... 3-56

➤ 3.6.5 Power Management Sequencing ..................................................................................... 3-57

➤ 3.6.6 Power Management Examples ........................................................................................ 3-58

➤ 4 Instruction Set ............................................................................................................................................. 4-1

➤ 4.1 Notation............................................................................................................................................. 4-2

➤ 4.2 Instruction Cycle Timing.................................................................................................................... 4-2

➤ 4.3 Addressing Modes ............................................................................................................................ 4-3

➤ 4.3.1 Register Indirect Addressing .............................................................................................. 4-3

➤ 4.3.2 Compound Addressing ......................................................................................................4-5

➤ 4.3.3 Direct Data Addressing ...................................................................................................... 4-7

➤ 4.4 Processor Flags................................................................................................................................ 4-9

➤ 4.5 Instruction Set................................................................................................................................. 4-11

➤ 4.5.1 Control Instructions .......................................................................................................... 4-12

➤ 4.5.2 Cache Instructions ........................................................................................................... 4-14

➤ 4.5.3 Data Move Instructions .................................................................................................... 4-15

➤ 4.5.4 Special Function Group ................................................................................................... 4-19

➤ 4.5.5 Multiply/ALU Group .......................................................................................................... 4-22

➤ 4.5.6 F3 ALU Instructions ......................................................................................................... 4-29

➤ 4.5.7 BMU Instructions .............................................................................................................. 4-30

➤ 4.5.8 Assembler Ambiguities ..................................................................................................... 4-35

➤ 5 Core Architecture ........................................................................................................................................ 5-1

➤ 5.1 Data Arithmetic Unit.......................................................................................................................... 5-1

➤ 5.1.1 Inputs and Outputs ............................................................................................................. 5-2

➤ 5.1.2 Multiplier Functions ............................................................................................................ 5-2

➤ 5.1.3 ALU .................................................................................................................................... 5-2

➤ 5.1.4 Accumulators ..................................................................................................................... 5-3

➤ 5.1.5 Counters ............................................................................................................................ 5-4

➤ 5.1.6 DAU Pseudorandom Sequence Generator (PSG) ............................................................. 5-7

➤ 5.1.7 Control Registers ............................................................................................................... 5-9

➤ 5.2 X Address Arithmetic Unit (XAAU).................................................................................................. 5-11

➤ 5.2.1 Inputs and Outputs ........................................................................................................... 5-11

v Lucent Technologies Inc.

Page 6

➤ 5.2.2 X-Memory Spac e Segment Selection .............................................................................. 5-11

➤ 5.2.3 Register Descriptions ....................................................................................................... 5-12

➤ 5.3 Y Address Arithmetic Unit (YAAU) .................................................................................................. 5-13

➤ 5.3.1 Inputs and Outputs ........................................................................................................... 5-13

➤ 5.3.2 Y-Memory Space .............................................................................................................. 5-14

➤ 5.3.3 Register Descriptions ....................................................................................................... 5-14

➤ 5.3.4 Addressing Modes ........................................................................................................... 5-14

➤ 5.4 Cache and Control.......................................................................................................................... 5-17

➤ 5.4.1 Cache ............................................................................................................................... 5-17

➤ 5.4.2 Control ............................................................................................................................. 5-19

➤ 6 External Memor y Interface.......................................................................................................................... 6-1

➤ 6.1 EMI Function..................................................................................................................................... 6-1

➤ 6.2 Programmable Features.................................................................................................................. 6-13

➤ 6.3 Functional Timing............................................................................................................................ 6-14

➤ 6.3.1 Timing Action with Wait-States ........................................................................................ 6-15

➤ 6.4 Timing Examples ............................................................................................................................ 6-17

➤ 6.4.1 CKO Timing ...................................................................................................................... 6-17

➤ 6.4.2 Write, Read, Read, W = 0 ................................................................................................ 6-18

➤ 6.4.3 Read, Write, Write, W = 0 ................................................................................................ 6-19

➤ 6.4.4 Read, Write, W = 0, Compound Address ......................................................................... 6-20

➤ 6.4.5 Read W = 1, Read W = 2 ................................................................................................. 6-21

➤ 6.4.6 Write W = 1 ...................................................................................................................... 6-22

➤ 6.4.7 Read, Read with Delayed Enable .................................................................................... 6-23

➤ 6.4.8 Write, Read, with Delayed Enable .................................................................................... 6-24

➤ 6.5 Boot-Up from External ROM ........................................................................................................... 6-25

➤ 6.6 Memory Sequencer......................................................................................................................... 6-26

➤ 6.7 Downloading Code into External Program Memory........................................................................ 6-28

➤ 7 Serial I/O ..................................................................................................................................................... 7-1

➤ 7.1 SIO Operation................................................................................................................................... 7-2

➤ 7.1.1 Active Clock Generator ...................................................................................................... 7-2

➤ 7.1.2 Input Section ...................................................................................................................... 7-4

➤ 7.1.3 Output Section ................................................................................................................... 7-6

➤ 7.2 User-Controlled Features.................................................................................................................. 7-9

➤ 7.2.1 The sioc Register .............................................................................................................. 7-9

➤ 7.2.2 Loopback Control ............................................................................................................. 7-11

➤ 7.2.3 Power Management ......................................................................................................... 7-11

➤ 7.3 Serial I/O Pin Descriptions.............................................................................................................. 7-12

➤ 7.4 Codec Interface............................................................................................................. .................. 7-13

➤ 7.5 Serial I/O Programming Example .............................................................................................. ..... 7-14

➤ 7.5.1 Program Segment ............................................................................................................ 7-14

➤ 7.6 Multiprocessor Mode Description .................................................................................................... 7-15

➤ 7.6.1 Multiprocessor Mode Overview ........................................................................................ 7-15

➤ 7.6.2 Detailed Multiprocessor Mode Description ...................................................................... 7-17

➤ 7.6.3 Suggested Multiprocessor Configuration ......................................................................... 7-24

➤ 7.6.4 Multiprocessor Mode Initialization .................................................................................... 7-25

➤ 7.7 Serial Interface #2........................................................................................................................... 7-26

➤ 7.7.1 SIO2 Features .................................................................................................................. 7-26

➤ 7.7.2 Programmable Features ................................................................................................... 7-27

➤ 7.7.3 Instructions Using the SIO2 ............................................................................................. 7-27

vi Lucent Technologies Inc.

Page 7

➤ 8 Parallel I/O (DSP1617 Only)........................................................................................................................ 8-1

➤ 8.1 PIO Operation................................................................................................................................... 8-2

➤ 8.1.1 Active Mode ....................................................................................................................... 8-2

➤ 8.1.2 PIO Interaccess Timing ...................................................................................................... 8-5

➤ 8.1.3 Passive Mode ..................................................................................................................... 8-6

➤ 8.1.4 Peripheral Mode (Host Interface) ....................................................................................... 8-9

➤ 8.2 Programmer Interface ..................................................................................................................... 8-14

➤ 8.2.1 pioc Register Settings ..................................................................................................... 8-16

➤ 8.2.2 Latent Reads .................................................................................................................... 8-17

➤ 8.2.3 Power Management ......................................................................................................... 8-19

➤ 8.3 Interrupts and the PIO..................................................................................................................... 8-19

➤ 8.4 PIO Signals..................................................................................................................................... 8-21

➤ 8.4.1 PIO Pin Multiplexing ......................................................................................................... 8-22

➤ 8.5 PIO Loopback Test Mode................................................................................................................ 8-22

➤ 9 Parallel Host Interface (PHIF) (DSP1611/18/27/28/29 Only)....................................................................... 9-1

➤ 9.1 PHIF Operation................................................................................................................................. 9-2

➤ 9.1.1

➤ 9.1.2

➤ 9.1.3

➤ 9.1.4

Intel

Mode, 16-Bit Read ..................................................................................................... 9-3

Intel

Mode, 16-Bit Write ..................................................................................................... 9-4

Motorola

Motorola

Mode, 16-Bit Read .............................................................................................. 9-5

Mode, 16-Bit Write .............................................................................................. 9-6

➤ 9.1.5 8-Bit Transfers .................................................................................................................... 9-7

➤ 9.1.6 Accessing the PSTAT Register ........................................................................................... 9-7

➤ 9.2 Programmer Interface ....................................................................................................................... 9-8

➤ 9.2.1 phifc Register Settings ...................................................................................................... 9-8

➤ 9.2.2 Power Management ......................................................................................................... 9-10

➤ 9.3 Interrupts and the PHIF................................................................................................................... 9-10

➤ 9.4 PHIF Pin Multiplexing...................................................................................................................... 9-11

➤ 9.5 Overall Functional Timing ............................................................................................................... 9-12

➤ 10 Bit I/O Unit................................................................................................................................................. 10-1

➤ 10.1 BIO Hardware Function................................................................................................................... 10-1

➤ 10.1.1 BIO Configured as Inputs ................................................................................................. 10-2

➤ 10.1.2 BIO Configured as Outputs .............................................................................................. 10-2

➤ 10.1.3 Pin Desc riptions ............................................................................................................... 10-3

➤ 10.1.4 BIO Pin M u ltiplexing ......................................................................................................... 10-4

➤ 10.2 Software View................................................................................................................................. 10-4

➤ 10.2.1 Registers .......................................................................................................................... 10-5

➤ 10.2.2 Flags ................................................................................................................................ 10-6

➤ 10.2.3 Instructions ....................................................................................................................... 10-6

➤ 10.2.4 Examples ......................................................................................................................... 10-6

➤ 11 The JTAG Test Access Port....................................................................................................................... 11-1

➤ 11.1 Overview of the JTAG Architecture ................................................................................................. 11-1

➤ 11.2 Overview of the JTAG Instructions.................................................................................................. 11-3

➤ 11.3 Elements of the JTAG Test Logic .................................................................................................... 11-4

➤ 11.3.1 The Test Access Port (TAP) ............................................................................................. 11-4

➤ 11.3.2 The TAP Controller ........................................................................................................... 11-5

➤ 11.3.3 The Instruction Register—JIR .......................................................................................... 11-7

➤ 11.3.4 The Boundar y-Scan Register—JBSR .............................................................................. 11-8

➤ 11.3.5 The Bypass R egister— JBPR ......................................................................................... 11-16

➤ 11.3.6 The Device Identification Register—JIDR ...................................................................... 11-16

➤ 11.3.7 The JTAG Data Register—jtag ...................................................................................... 11-19

vii Lucent Technologies Inc.

Page 8

➤ 11.3.8 The JTAG Control R egister— JCON ............................................................................... 11-19

➤ 11.3.9 The JTAG Output S tage—JOUT .................................................................................... 11-19

➤ 11.4 The JTAG Instruction Set.............................................................................................................. 11-19

➤ 11.4.1 The EXTEST Instruction ................................................................................................ 11-19

➤ 11.4.2 The INTEST Instruction ................................................................................................. 11-19

➤ 11.4.3 The SAMPLE Instruction ................................................................................................ 11-20

➤ 11.4.4 The BYPASS Instruction ................................................................................................ 11-20

➤ 11.4.5 The IDCOD E Ins truction ................................................................................................ 11-20

➤ 12 Timer ......................................................................................................................................................... 12-1

➤ 12.1 Hardware View................................................................................................................................ 12-1

➤ 12.2 Programmable Features and Operation.......................................................................................... 12-2

➤ 12.2.1 timerc Register Enc oding ................................................................................................ 12-2

➤ 12.2.2 timer0 Register ................................................................................................................ 12-3

➤ 12.2.3 The inc Register .............................................................................................................. 12-3

➤ 12.2.4 Initialization Conditions .................................................................................................... 12-3

➤ 12.3 Program Example ........................................................................................................................... 12-4

➤ 12.4 Timing............................................................................................................................................. 12-5

➤ 13 Bit Manipulation Unit (BMU ) ...................................................................................................................... 13-1

➤ 13.1 Hardware View................................................................................................................................ 13-1

➤ 13.2 Software View................................................................................................................................. 13-2

➤ 13.2.1 Instruction Set .................................................................................................................. 13-2

➤ 13.2.2 Shifting Operations ........................................................................................................... 13-2

➤ 13.2.3 Normalization ................................................................................................................... 13-4

➤ 13.2.4 Extraction ......................................................................................................................... 13-5

➤ 13.2.5 Insertion ........................................................................................................................... 13-6

➤ 13.2.6 Shuffle Accumulators ....................................................................................................... 13-8

➤ 13.2.7 Instruction Encoding ........................................................................................................ 13-9

➤ 13.2.8 Software Example .......................................................................................................... 13-10

➤ 14 Error Correction Coprocessor (DS P1618/28 Only)................................................................................... 14-1

➤ 14.1 System Description......................................................................................................................... 14-1

➤ 14.2 Hardware Architecture .................................................................................................................... 14-3

➤ 14.2.1 Branch Metric Un it ........................................................................................................... 14-3

➤ 14.2.2 Update Unit ...................................................................................................................... 14-4

➤ 14.2.3 Traceback Unit ................................................................................................................. 14-4

➤ 14.2.4 Interrupts and Flags ......................................................................................................... 14-5

➤ 14.2.5 Traceback RAM ................................................................................................................ 14-5

➤ 14.3 DSP Decoding Operation Sequence .............................................................................................. 14-6

➤ 14.4 Operation of the ECCP ................................................................................................................... 14-7

➤ 14.5 Software Architecture...................................................................................................................... 14-8

➤ 14.5.1 R-Field Registers ............................................................................................................. 14-8

➤ 14.5.2 ECCP Inter nal Memory-Mapped Registers .................................................................... 14-10

➤ 14.5.3 ECCP Interrupts and Flags ............................................................................................ 14-17

➤ 14.5.4 Traceback RAM .............................................................................................................. 14-17

➤ 14.6 ECCP Instruction Timing............................................................................................................... 14-19

➤ 14.6.1 ResetECCP Instruction .................................................................................................. 14-19

➤ 14.6.2 UpdateMLSE Instr u ction with Soft Decision .................................................................. 14-19

➤ 14.6.3 UpdateMLSE Instr u ction with Hard Decision ................................................................. 14-21

➤ 14.6.4 UpdateConv Instruction with Soft D e cisions .................................................................. 14-22

➤ 14.6.5 UpdateConv Instruction with Har d Deci sion ................................................................... 14-23

➤ 14.6.6 TraceBack Instruction ..................................................................................................... 14-23

viii Lucent Technologies Inc.

Page 9

➤ 15 Interface Guide.......................................................................................................................................... 15-1

➤ 15.1 Pin Information................................................................................................................................ 15-1

➤ 15.2 Signal Descriptions......................................................................................................................... 15-5

➤ 15.2.1 System Interface .............................................................................................................. 15-5

➤ 15.2.2 External Memory Interface ............................................................................................... 15-6

➤ 15.2.3 Serial Interface #1 ............................................................................................................ 15-7

➤ 15.2.4 PIO/PHIF or Serial Interface #2 and Control I/O Interface ............................................... 15-9

➤ 15.2.5 Control I/O Interface ....................................................................................................... 15-11

➤ 15.2.6 JTAG Test Interface ........................................................................................................ 15-11

➤ 15.3 Resetting DSP161X and DSP162X Devices................................................................................. 15-12

➤ 15.3.1 Powerup Reset ............................................................................................................... 15-12

➤ 15.3.2 Using the TAP to Reset the TAP Controller .................................................................... 15-12

➤ 15.3.3 RSTB Pin Reset ............................................................................................................. 15-13

➤ 15.4 Mask-Programmable Options ....................................................................................................... 15-14

➤ 15.4.1 Input Clock Options ........................................................................................................ 15-14

➤ 15.4.2 ROM Secur ity Options (DSP1617/18/27/28/29 Only) .................................................... 15-14

➤ 15.5 Additional Electrical Characteristics and Requirements for Crystal.............................................. 15-15

➤ A Instruction Encoding....................................................................................................................................A-1

➤ A.1 Instruction Encoding Formats ...........................................................................................................A-1

➤ A.2 Field Descriptions .............................................................................................................................A-4

➤ B Instruction Set Summary.............................................................................................................................B-1

➤ goto JA....................................................................................................................................................... B-1

➤ goto B......................................................................................................................................................... B-2

➤ if CON goto/call/return................................................................................................................................ B-3

➤ call JA......................................................................................................................................................... B-4

➤ icall............................................................................................................................................................. B-5

➤ do K {.......................................................................................................................................................... B-6

➤ redo K......................................................................................................................................................... B-7

➤ R = IM16..................................................................................................................................................... B-8

➤ SR = IM9 .................................................................................................................................................. B-10

➤ R = aS[l].................................................................................................................................................... B-11

➤ aT[l] = R.................................................................................................................................................... B-12

➤ R = Y ........................................................................................................................................................ B-13

➤ Y = R ........................................................................................................................................................ B-14

➤ Z : R.......................................................................................................................................................... B-15

➤ DR = *(OFFSET) ...................................................................................................................................... B-16

➤ *(OFFSET) = DR ...................................................................................................................................... B-17

➤ if CON F2 ................................................................................................................................................. B-18

➤ ifc CON F2................................................................................................................................................ B-19

➤ F1 Y ....................................................................................................................................................... B-20

➤ F1 Y = a0[l] ............................................................................................................................................ B-22

➤ F1 Y = a1[l] ............................................................................................................................................ B-22

➤ F1 x = Y ................................................................................................................................................. B-24

➤ F1 y[l] = Y............................................................................................................................................... B-26

➤ F1 y = Y x = *pt++[i] ............................................................................................................................ B-28

➤ F1 y = a0 x = *pt++[i]........................................................................................................................... B-30

➤ F1 y = a1 x = *pt++[i]........................................................................................................................... B-30

➤ F1 aT[l] = Y ............................................................................................................................................ B-32

➤ F1 Y = y[l]............................................................................................................................................... B-34

➤ F1 Z : y[l]................................................................................................................................................ B-36

ix Lucent Technologies Inc.

Page 10

Information Manual

April 1998

DSP160X DIGITAL SIGNAL PROCESSOR

➤ F1 Z : aT[l] ............................................................................................................................................. B-38

➤ F1 Z : y x = *pt++[i].............................................................................................................................. B-40

➤ aD = aS OP aT......................................................................................................................................... B-42

➤ aD = aS OP p........................................................................................................................................... B-43

➤ aD = aS<h,l> OP IM16............................................................................................................................. B-44

➤ aD = a SHIFT aS ................................................................................................................................... B-46

S

➤ aD = aS SHIFT arM.................................................................................................................................. B-47

➤ aD = aS SHIFT IM16................................................................................................................................ B-48

➤ aD = exp (aS)........................................................................................................................................... B-49

➤ aD = norm (aS, arM) ................................................................................................................................ B-50

➤ aD = extracts (aS, arM)............................................................................................................................ B-51

➤ aD = extractz (aS, arM)............................................................................................................................ B-51

➤ aD = extracts (aS, IM16) .......................................................................................................................... B-52

➤ aD = extractz (aS, IM16) .......................................................................................................................... B-52

➤ aD = insert (aS, arM)................................................................................................................................ B -53

➤ aD = insert (aS, IM16).............................................................................................................................. B-54

➤ aD = aS : aaT........................................................................................................................................... B-55

Lucent Technologies Inc. x

Page 11

DSP1611/17/18/ 27/28/29 Digital Signal Processor

INFORMATION MANUAL

FIGURES

➤ Figure 1-1.In-Circuit Emulation with the

FlashDSP

1600—JCS....................................................................... 1-5

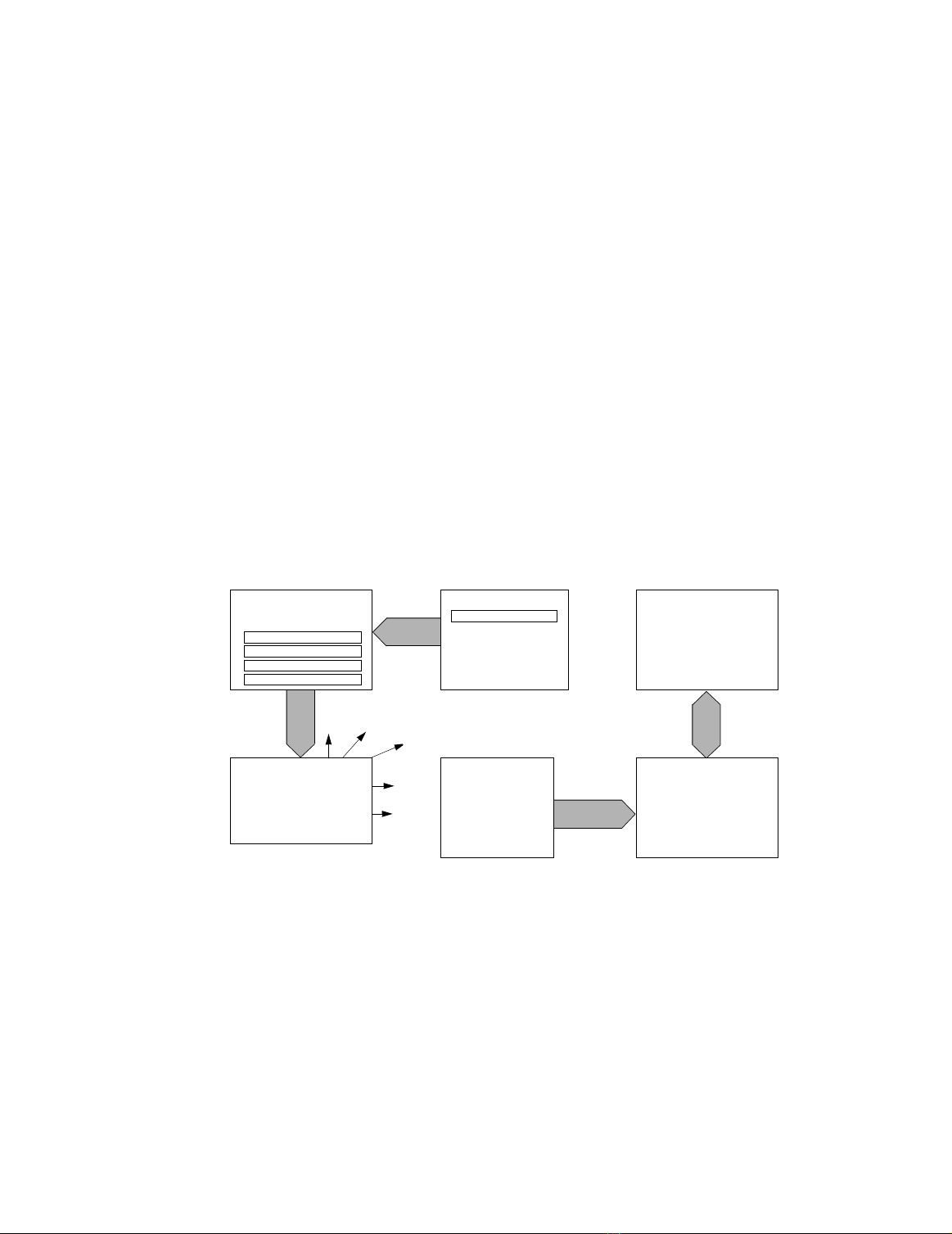

➤ Figure 2-1.Harvard Architecture ...................................................................................................................... 2-1

➤ Figure 2-2.Concurrent Operations in the DSP1611/17/18/27/28/29................................................................ 2-2

➤ Figure 2-3.DSP1611 Block Diagram................................................................................................................ 2-4

➤ Figure 2-4.DSP1617 Block Diagram................................................................................................................ 2-5

➤ Figure 2-5.DSP1618 Block Diagram................................................................................................................ 2-6

➤ Figure 2-6.DSP1627 Block Diagram................................................................................................................ 2-7

➤ Figure 2-7.DSP1628 Block Diagram................................................................................................................ 2-8

➤ Figure 2-8.DSP1629 Block Diagram................................................................................................................ 2-9

➤ Figure 2-9.Hardware Block Diagram for Internal Pipeline ............................................................................. 2-13

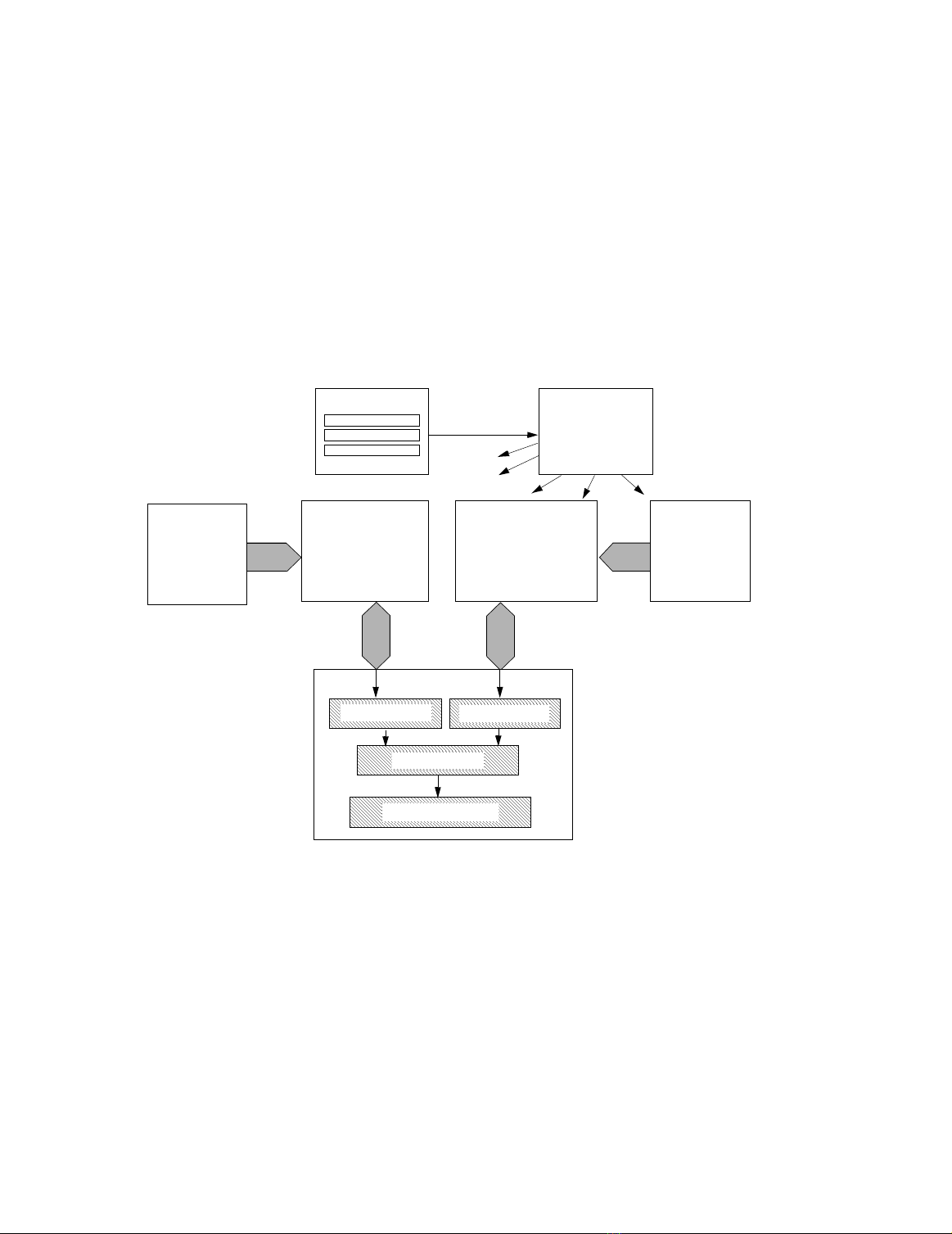

➤ Figure 2-10.DSP1600 Core Functions........................................................................................................... 2-16

➤ Figure 3-1.Program-Accessible Registers, DSP1611/17/18/27/28/29............................................................. 3-4

➤ Figure 3-2.Data (Y) Memory Space................................................................................................................. 3-8

➤ Figure 3-3.Instruction/Coefficient (X) Memory Space.................................................................................... 3-10

➤ Figure 3-4.p Register to Accumulator Bit Alignment, auc[1:0] = 00............................................................... 3-23

➤ Figure 3-5.p Register to Accumulator Bit Alignment, auc[1:0] = 01............................................................... 3-24

➤ Figure 3-6.p Register to Accumulator Bit Alignment, auc[1:0] = 10............................................................... 3-25

➤ Figure 3-7.Register to Accumulator Bit Alignment, auc[1:0] = 11.................................................................. 3-26

➤ Figure 3-8.Interrupt Operation....................................................................................................................... 3-28

➤ Figure 3-9.DSP16A-Compatible Interrupts (DSP1617 Only)......................................................................... 3-30

➤ Figure 3-10.Timing Diagram of a Simple Interrupt ........................................................................................ 3-33

➤ Figure 3-11.Interrupt Disable Latency ........................................................................................................... 3-35

➤ Figure 3-12.Interrupt Request Circuit Diagram.............................................................................................. 3-36

➤ Figure 3-13.Timing Diagram of Concurrent Interrupts .................................................................................. 3-37

➤ Figure 3-14.Timing Diagram of User Trap..................................................................................................... 3-39

➤ Figure 3-15.Timing Diagram of Entering and Exiting Powerdown Mode....................................................... 3-40

➤ Figure 3-16.Timing Sequence of Concurrent Internal and External Interrupts, DSP16A-Compatible Mode. 3-44

➤ Figure 3-17.Timing Sequences of Concurrent Internal and External Interrupts, DSP16A Compatible Mode 3-45

➤ Figure 3-18.Timing Sequence of Concurrent External Interrupts, DSP16A Compatible Mode..................... 3-46

➤ Figure 3-19.Clock Source Block Diagram...................................................................................................... 3-47

➤ Figure 3-20.Power Management Using the

➤ Figure 3-21.Power Management Using the

powerc

powerc

Register (DSP1611/17/18 Only).................................. 3-54

Register (DSP1627/28/29 Only).................................. 3-55

➤ Figure 4-1.Compound Addressing................................................................................................................... 4-6

➤ Figure 4-2.Direct Data Addressing .................................................................................................................. 4-8

➤ Figure 4-3.Compound Addressing with Accumulators or

y

Register............................................................. 4-28

➤ Figure 4-4.BMU Shifting Operations.............................................................................................................. 4-31

➤ Figure 4-5.Extraction ..................................................................................................................................... 4-32

➤ Figure 4-6.Case 1. Source aS and Destination Accumulators Different....................................................... 4-33

➤ Figure 4-7.Case 2. Source aS and aD Destination Accumulators the Same................................................ 4-33

➤ Figure 4-8.Shuffle Instruction......................................................................................................................... 4-34

➤ Figure 5-1.DAU—Data Arithmetic Unit ............................................................................................................ 5-1

➤ Figure 5-2.Conditional Instructions Using Counter Conditionals..................................................................... 5-4

➤ Figure 5-3.The ifc CON F2 Instruction............................................................................................................. 5-6

xi Lucent Technologies Inc.

Page 12

➤ Figure 5-4.DAU Pseudorandom Sequence Generator.................................................................................... 5-8

➤ Figure 5-5.XAAU—X Address Arithme tic Unit............................................................................................... 5-11

➤ Figure 5-6.YAAU—Y Address Arithme tic Unit............................................................................................... 5-13

➤ Figure 5-7.Direct Data Addressing ................................................................................................................ 5-15

➤ Figure 5-8.Use of the rb and re Registers ..................................................................................................... 5-16

➤ Figure 6-1.External Memory Interface ............................................................................................................. 6-1

➤ Figure 6-2.EMI Example................................................................................................................................ 6-14

➤ Figure 6-3.CKO Timing.................................................................................................................................. 6-17

➤ Figure 6-4.Write, Read, Read, W = 0 ............................................................................................................ 6-18

➤ Figure 6-5.Read, Write, Write, W = 0............................................................................................................. 6-19

➤ Figure 6-6.Read, Write, W = 0....................................................................................................................... 6-20

➤ Figure 6-7.Read, Read.................................................................................................................................. 6-21

➤ Figure 6-8.Write W = 1 .................................................................................................................................. 6-22

➤ Figure 6-9.Read, Read, with Delayed Enable ............................................................................................... 6-23

➤ Figure 6-10.Write, Read, with Delayed Enable, No Hold Time...................................................................... 6-24

➤ Figure 6-11.External ROM Boot-Up............................................................................................................... 6-25

➤ Figure 7-1.Serial I/O Internal Data Path .......................................................................................................... 7-1

➤ Figure 7-2.SIO Clocks ..................................................................................................................................... 7-2

➤ Figure 7-3.SIO Active Mode Clock Timing....................................................................................................... 7-3

➤ Figure 7-4.SIO Passive Mode Input Timing, 16-bit Words .............................................................................. 7-4

➤ Figure 7-5.SIO Active Mode Input Timing, 16-bit Words ................................................................................. 7-5

➤ Figure 7-6.SIO Passive Mode Output Timing, 16-bit Words............................................................................ 7-6

➤ Figure 7-7.SIO Active Mode Output Timing, 16-bit Words .............................................................................. 7-7

➤ Figure 7-8.SIO Passive Mode Output Timing, 8-bit Words.............................................................................. 7-8

➤ Figure 7-9.DSP1611/17/18/27/28/29 to Lucent Technologies CSP1027 Codec Interface............................ 7-13

➤ Figure 7-10.DSP1611/17/18/27/28/29 to Lucent Technologies T7525 Codec Interface............................... 7-13

➤ Figure 7-11.Multiprocessor Connections....................................................................................................... 7-15

➤ Figure 7-12.Destination Address Communication ......................................................................................... 7-16

➤ Figure 7-13.Protocol Channel Communication.............................................................................................. 7-16

➤ Figure 7-14.DSP1611/17/18/27/28/29 Multiprocessor Connections.............................................................. 7-17

➤ Figure 7-15.Multiprocessor Mode time slots.................................................................................................. 7-18

➤ Figure 7-16.Multiprocessor Mode Output Timing .......................................................................................... 7-19

➤ Figure 7-17.DSP1611/17/18/27/28/29 Multiprocessor Communications....................................................... 7-23

➤ Figure 7-18.SIO2—PIO/PHIF Multiplexing .................................................................................................... 7-26

➤ Figure 8-1.Parallel I/O Unit.............................................................................................................................. 8-1

➤ Figure 8-2.Active Mode Input Timing (Minimum Width PIDS) ......................................................................... 8-3

➤ Figure 8-3.Active Mode Output Timing (Minimum Width PODS)..................................................................... 8-4

➤ Figure 8-4.PIO Interaccess Timing.................................................................................................................. 8-5

➤ Figure 8-5.Passive Mode Input Timing............................................................................................................ 8-7

➤ Figure 8-6.Passive Mode Output Timing ......................................................................................................... 8-8

➤ Figure 8-7.The DSP as a Microprocessor Peripheral...................................................................................... 8-9

➤ Figure 8-8.Peripheral Mode Input Timing...................................................................................................... 8-11

➤ Figure 8-9.Peripheral Output Mode Timing ................................................................................................... 8-12

➤ Figure 8-10.Polling PSTAT Timing ................................................................................................................ 8-13

➤ Figure 8-11.PIO Latent Reads Hardware ...................................................................................................... 8-18

➤ Figure 8-12.PIO Latent Reads Timing........................................................................................................... 8-18

➤ Figure 9-1.Parallel Host Interface.................................................................................................................... 9-1

➤ Figure 9-2.

➤ Figure 9-3.

➤ Figure 9-4.

Intel

Mode, 16-Bit Read.................................................................................................................. 9-3

Intel

Mode, 16-Bit Write.................................................................................................................. 9-4

Motorola

Mode, 16-Bit Read .......................................................................................................... 9- 5

xii Lucent Technologies Inc.

Page 13

➤ Figure 9-5.

Motorola

Mode, 16-Bit Write........................................................................................................... 9-6

➤ Figure 9-6.Overall PHIF Read Cycle ............................................................................................................. 9-12

➤ Figure 10-1.BIO Block Diagram..................................................................................................................... 10-1

➤ Figure 10-2.BIO Configured as Inputs........................................................................................................... 10-2

➤ Figure 10-3.BIO Configured as Outputs ........................................................................................................ 10-3

➤ Figure 10-4.Logic Flow Diagram for BIO Configuration................................................................................. 10-4

➤ Figure 11-1.The JTAG Block Diagram........................................................................................................... 11-1

➤ Figure 11-2.The TAP Controller State Diagram ............................................................................................. 11-2

➤ Figure 11-3.Timing Diagram Example........................................................................................................... 11-6

➤ Figure 11-4.The JTAG Instruction Register/Decoder Structure..................................................................... 11-7

➤ Figure 11-5.The Simplest Boundary-Scan Register Cell............................................................................. 11-11

➤ Figure 11-6.Cell Interconnections for a 3-State Pin..................................................................................... 11-13

➤ Figure 11-7.Bidirectional Cell....................................................................................................................... 11-14

➤ Figure 11-8.Cell Interconnections for a Bidirectional Pin............................................................................. 11-15

➤ Figure 11-9.The Device Identification Register, JIDR.................................................................................. 11-16

➤ Figure 12-1.Timer Block Diagram.................................................................................................................. 12-1

➤ Figure 12-2.Timing Examples........................................................................................................................ 12-5

➤ Figure 13-1.BMU Block Diagram................................................................................................................... 13-1

➤ Figure 13-2.Logical Right Shift ...................................................................................................................... 13-2

➤ Figure 13-3.Left Shifts ................................................................................................................................... 13-3

➤ Figure 13-4.Arithmetic Right Shift.................................................................................................................. 13-3

➤ Figure 13-5.Extraction ................................................................................................................................... 13-5

➤ Figure 13-6.Insertion, Case 1. Source and Destination Accumulators Different........................................... 13-6

➤ Figure 13-7.Insertion, Case 2. Source and Destination Accumulators Are the Same.................................. 13-7

➤ Figure 13-8.Shuffle Accumulators ................................................................................................................. 13-8

➤ Figure 14-1.Error Correction Coprocessor Block Diagram/Programming Model........................................... 14-2

➤ Figure 14-2.DSP Core Operation Sequence ................................................................................................. 14-6

➤ Figure 14-3.ECCP Operation Sequence ....................................................................................................... 14-7

➤ Figure 14-4.Register Block Diagram.............................................................................................................. 14-8

xiii Lucent Technologies Inc.

Page 14

DSP1611/17/18 /27/28/29 Digital Signal Processor

INFORMATION MANUAL

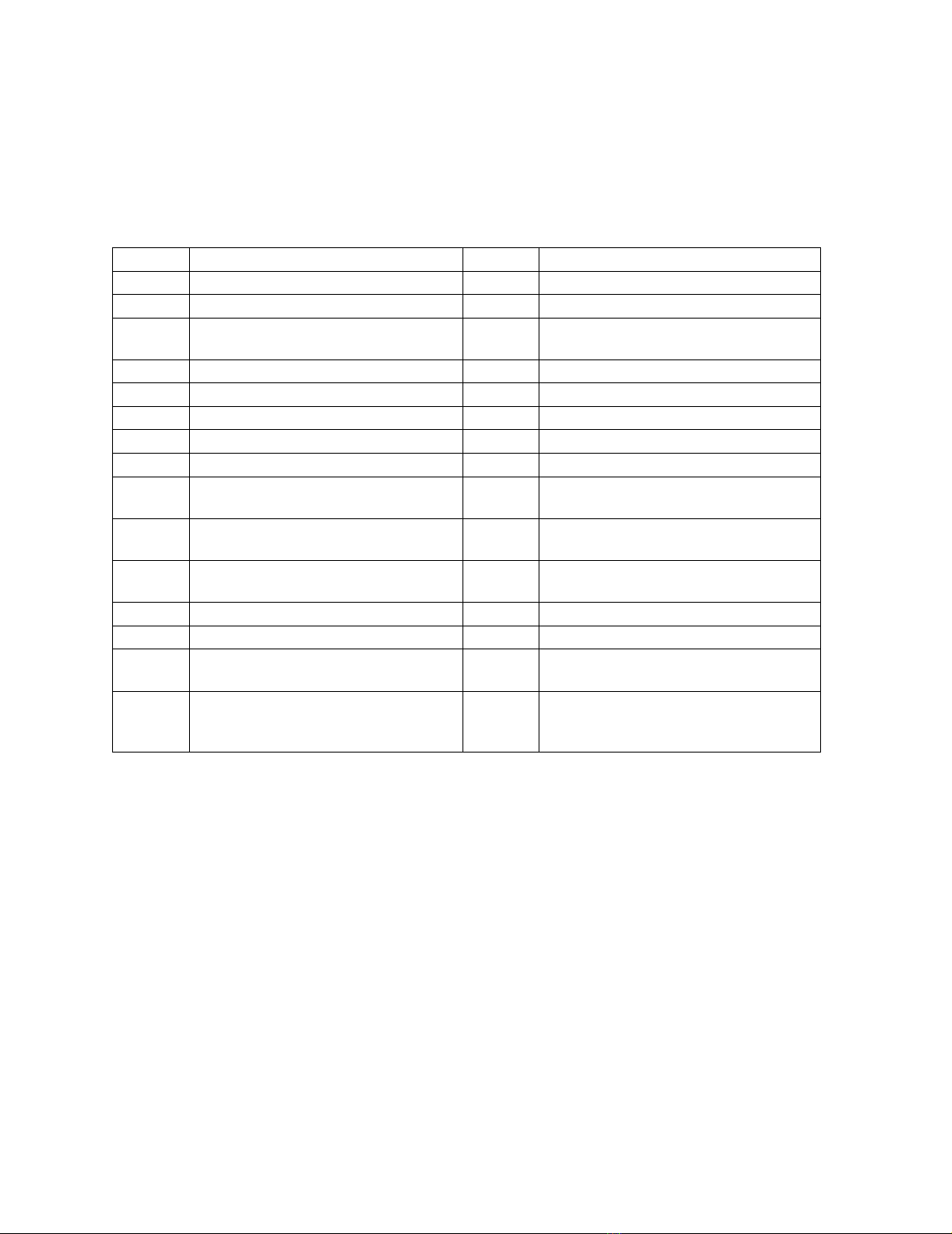

TABLES

➤ Table 2-1. Pipeline Flow for Concurrent Operations .................................................................................... 2-3

➤ Table 2-2. Symbols Used in the Block Diagrams ...................................................................................... 2- 10

➤ Table 2-3. Memory Space.......................................................................................................................... 2-12

➤ Table 2-4. Single-Cycle Instruction Internal Pipeline.................................................................................. 2-14

➤ Table 2-5. Two-Cycle Fetch Internal Pipeline ............................................................................................ 2- 15

➤ Table 3-1. Program-Accessible Registers by Function ............................................................................... 3-1

➤ Table 3-2. Program-Accessible Registers by Type, Listed Alphabetically .................................................. 3-2

➤ Table 3-3. Registers Nonaccessible by Program, Accessible Through Pins .............................................. 3-5

➤ Table 3-4. Register Length Definition .......................................................................................................... 3-5

➤ Table 3-5. Register Reset Values ............................................................................................................... 3-6

➤ Table 3-6. Flag Definitions .......................................................................................................................... 3-7

➤ Table 3-7. Data Memory Map (Y-M e mory Space) ...................................................................................... 3-9

➤ Table 3-8. DSP1611 Instruction/Coefficient Memory Map (X-Memory Space) ......................................... 3-11

➤ Table 3-9. DSP1617 Instruction/Coefficient Memory Map (X-Memory Space) ......................................... 3-12

➤ Table 3-10. DSP1618 Instruction/Coefficient Memory Map (X-Memory Space) ......................................... 3-12

➤ Table 3-11. DSP1618x24 Instruction/Coefficient Memory Map (X-Memory Space) ................................... 3-13

➤ Table 3-12. DSP1627 Instruction/Coefficient Memory Map (X-Memory Space) ......................................... 3-14

➤ Table 3-13. DSP1627x32 Instruction/Coefficient Memory Map (X-Memory Space) ................................... 3-15

➤ Table 3-14. DSP1628x08 Instruction/Coefficient Memory Map (X-Memory Space) ................................... 3-16

➤ Table 3-15. DSP1628x16 Instruction/Coefficient Memory Map (X-Memory Space) ................................... 3-17

➤ Table 3-16. DSP1629x10 Instruction/Coefficient Memory Map (X-Memory Space) ................................... 3-18

➤ Table 3-17. DSP1629x16 Instruction/Coefficient Memory Map (X-Memory Space) ................................... 3-19

➤ Table 3-18. Interrupts in X-Memory Space ................................................................................................. 3-20

➤ Table 3-19. Arithmetic Unit Control (

➤ Table 3-20. Vector Table ............................................................................................................................. 3-31

➤ Table 3-21. Interrupt

Control (

➤ Table 3-22. Interrupt Status (

➤ Table 3-23. Interrupt Control (

➤ Table 3-24. Interrupt Status (

➤ Table 3-25. Latency Times for Switching Between CKI and PLL-Based Clocks.......................................... 3-50

➤ Table 3-26. Phase-Locked Loop Control (

➤ Table 3-27. PLL Electrical Specifications and

➤ Table 3-28. powerc Fields (DSP1617) ........................................................................................................ 3-53

➤ Table 3-29. powerc Fields (DSP1611, DSP1627, and DSP1629) .............................................................. 3-53

➤ Table 3-30. powerc Fields (DSP1618 and DSP1628) ................................................................................. 3-53

➤ Table 3-31. powerc Control Register Fields Description.............................................................................. 3-53

➤ Table 4-1. Compound Addressing Instructions ............................................................................................ 4-5

➤ Table 4-2. Direct Data Addressing ............................................................................................................... 4-7

➤ Table 4-3. Flags (Conditional Mnemonics)................................................................................................. 4-10

➤ Table 4-4. Control Instructions ................................................................................................................... 4-12

➤ Table 4-5. Replacement Table for Control Function Instructions............................................................... 4-12

➤ Table 4-6. Example of Execution of Cache Instruction .............................................................................. 4-14

➤ Table 4-7. Replacement Table for Cache Instructions............................................................................... 4-14

auc

) Register ..................................................................................... 3-22

inc

) Register (All Except DSP1618/28) ........................................................ 3-34

ins

) Register (All Except DSP1618/28)........................................................ 3-34

inc

) Register (DSP1618/28) ......................................................................... 3-34

ins

) Register (DSP1618/28)........................................................................... 3-35

pllc

) Register.............................................................................. 3-51

pllc

Register Settings .......................................................... 3- 51

xiv Lucent Technologies Inc.

Page 15

➤ Table 4-8. Data Move Instruction Summary............................................................................................... 4-15

➤ Table 4-9. Replacement Table for Data Move Instructions ....................................................................... 4-16

➤ Table 4-10. Special Function Statements .................................................................................................... 4-20

➤ Table 4-11. Replacement Table for Special Function Instructions............................................................... 4-20

➤ Table 4-12. Multiply/ALU Instructions .......................................................................................................... 4-23

➤ Table 4-13. Replacement Table for Multiply/ALU Instructions..................................................................... 4-24

➤ Table 4-14. Instruction for Loading the x and y Registers into the Squaring Mode..................................... 4-25

➤ Table 4-15. F3 ALU Instructions .................................................................................................................. 4-29

➤ Table 4-16. Replacement Table for ALU Instructions .................................................................................. 4-29

➤ Table 4-17. Replacement Table for BMU Instructions ................................................................................. 4-30

➤ Table 4-18. Summary of Ambiguous DSP1600 Commands Requiring a Mnemonic................................... 4-36

➤ Table 5-1. Counter Conditionals .................................................................................................................. 5-4

➤ Table 5-2. c0—c2 Register Functions ......................................................................................................... 5-6

➤ Table 5-3. Arithmetic Unit Control (auc) Register........................................................................................ 5-9

➤ Table 5-4. Processor Status Word (psw) Register .................................................................................... 5-10

➤ Table 5-5. Replacement Table for Cache Instruction Encoding................................................................. 5-18

➤ Table 5-6. Control and Status Descriptions ............................................................................................... 5-19

➤ Table 5-7. Interrupt Control (inc) Register (DSP1611/17/27/29) ............................................................... 5-19

➤ Table 5-8. Interrupt Status (ins) Register (DSP1611/17/27/29)................................................................. 5-19

➤ Table 5-9. Interrupt Control (inc) Register (DSP1618/28) ......................................................................... 5-19

➤ Table 5-10. Interrupt Status (ins) Register (DSP1618/28)........................................................................... 5-19

➤ Table 5-11. alf Register ............................................................................................................................... 5-20

➤ Table 6-1. DSP1611 Instruction/Coefficient Memory Map (X-Memory Space) ........................................... 6-3

➤ Table 6-2. DSP1617 Instruction/Coefficient Memory Map (X-Memory Space) ........................................... 6-4