Linear Technology LTC1735-1 Datasheet

FEATURES

LTC1735-1

High Efficiency

Synchronous Step-Down

Switching Regulator

U

DESCRIPTIO

■

Dual N-Channel MOSFET Synchronous Drive

■

Programmable/Synchronizable Fixed Frequency

■

V

Range: 0.8V to 7V

OUT

■

Wide VIN Range: 3.5V to 36V Operation

■

Very Low Dropout Operation: 99% Duty Cycle

■

OPTI-LOOPTM Compensation Minimizes C

■

±

1% Output Voltage Accuracy

■

Power Good Output Voltage Monitor

■

Internal Current Foldback

■

Output Overvoltage Crowbar Protection

■

Latched Short-Circuit Shutdown Timer

OUT

with Defeat Option

■

Optional Programmable Soft-Start

■

Remote Output Voltage Sense

■

Logic Controlled Micropower Shutdown: IQ < 25µA

■

Available in 16-Lead Narrow SSOP and SO Packages

U

APPLICATIO S

■

Notebook and Palmtop Computers, PDAs

■

Power Supply for Mobile Pentium® III Processor with

SpeedStepTM Technology

■

Cellular Telephones and Wireless Modems

, LTC and LT are registered trademarks of Linear Technology Corporation.

Burst Mode and OPTI-LOOP are trademarks of Linear Technology Corporation.

Pentium is a registered trademark of Intel Corporation. SpeedStep is a trademark of Intel

Corporation.

The LTC®1735-1 is a synchronous step-down switching

regulator controller optimized for CPU power. OPTI-LOOP

compensation allows the transient response to be optimized over a wide range of output capacitance and ESR

values.

The operating frequency (synchronizable up to 500kHz) is

set by an external capacitor allowing maximum flexibility

in optimizing efficiency. The output voltage is monitored

by a power good window comparator that indicates when

the output is within 7.5% of its programmed value, conforming to Intel Mobile CPU Specifications.

Protection features include internal foldback current limiting, output overvoltage crowbar and optional shortcircuit shutdown. Soft-start is provided by an external

capacitor that can be used to properly sequence supplies.

The operating current level is user-programmable via an

external current sense resistor. Wide input supply range

allows operation from 3.5V to 30V (36V maximum).

Pin defeatable Burst ModeTM operation provides high

efficiency at low load currents while 99% duty cycle

provides low dropout operation.

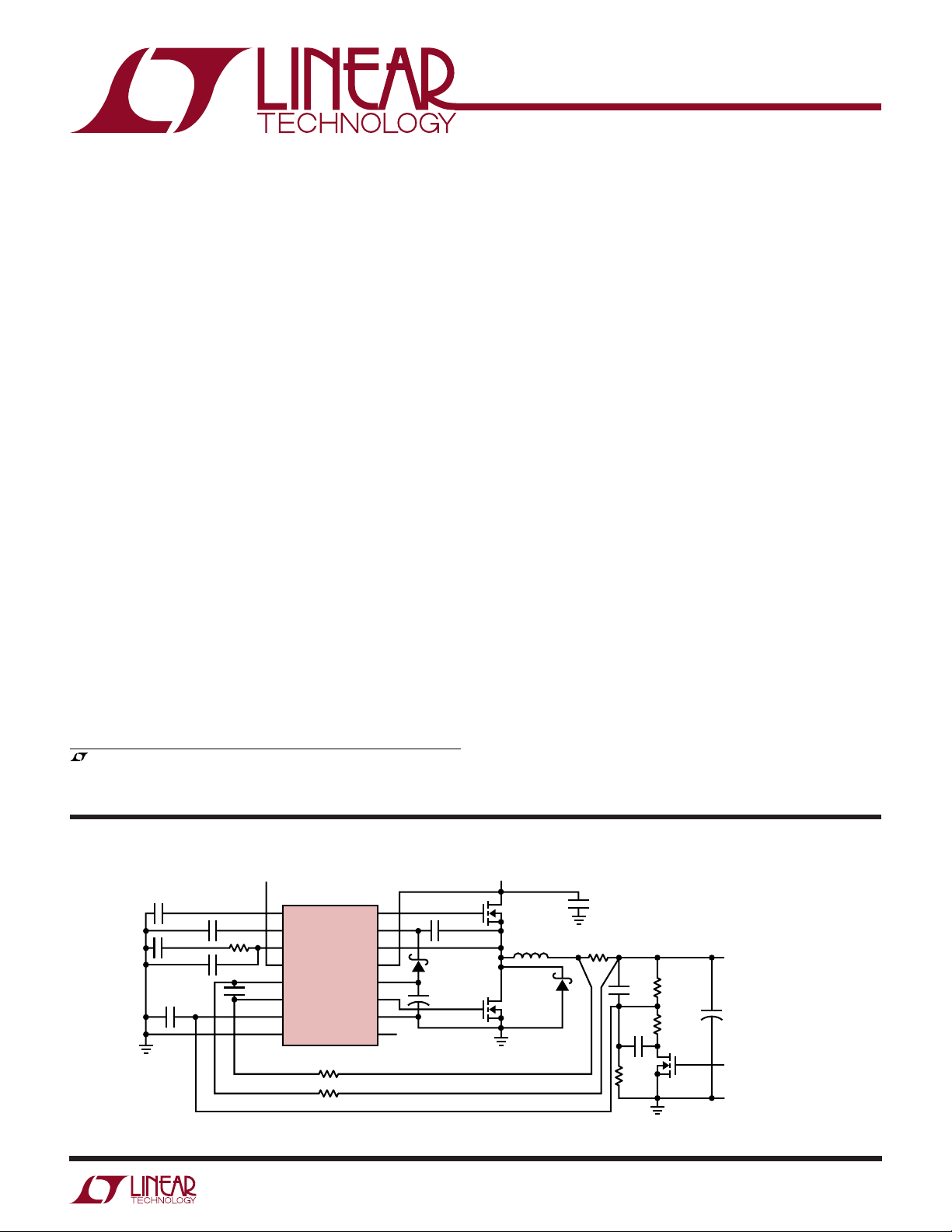

TYPICAL APPLICATIO

C

47pF

OSC

C

SS

C

47pF

C2

330pF

R

C

C1

Figure 1. CPU Core DC/DC Converter with Dynamic Voltage Selection from SpeedStep Enabled Processors

0.1µF

C1

47pF

33k

1000pF

1

2

3

4

5

6

7

8

C

RUN/SS

I

TH

PGOOD

SENSE

SENSE

V

SGND

OSC

OSENSE

U

LTC1735-1

–

+

10Ω

10Ω

BOOST

INTV

PGND

EXTV

SW

V

V

IN

4.5V TO 24VPGOOD

16

TG

15

14

13

IN

12

CC

11

BG

10

9

5V

CC

(OPTIONAL)

+

0.22µF

C

B

D1

CMDSH-3

4.7µF

Q1

FDS6680A

L1

1.2µH

MBRS340T3

Q2, Q3

FDS6680A

×2

D2

C

IN

22µF

50V

CERAMIC

×2

R

SENSE

0.004Ω

: MARCON THCR70E1H226ZT

C

IN

: PANASONIC EEFUE06181R

C

OUT

L1: PANASONIC ETQP6RZ1R20HFA

: IRC CRF2010-01-R004J

R

SENSE

R1

10k

47pF

0.5%

+

R3

33.2k

47pF

1%

Q4

R2

14.3k

0.5%

2N7002

1735-1 F01

V

OUT

1.35V TO 1.60V

12A

C

OUT

180µF

4V

PANASONIC SP

×4

V

= 1: V

SEL

OUT

= 0: V

V

SEL

OUT

GND

= 1.60V

= 1.35V

1

LTC1735-1

WW

W

U

ABSOLUTE AXI U RATI GS

(Note 1)

Input Supply Voltage (VIN)........................ 36V to –0.3V

Topside Driver Supply Voltage (BOOST)... 42V to –0.3V

Switch Voltage (SW) ................................... 36V to –5V

INTVCC, EXTVCC (BOOST, SW) Voltages..... 7V to –0.3V

SENSE+, SENSE–,

PGOOD Voltages................ 1.1(INTV

ITH, V

OSENSE

, C

Voltages .....................2.7V to –0.3V

OSC

RUN/SS Voltage ....................(INTVCC + 0.3V) to –0.3V

Peak Driver Output Current <10µs (TG, BG) .............. 3A

INTVCC Output Current ......................................... 50mA

Operating Ambient Temperature Range

LTC1735C-1 ............................................ 0°C to 85°C

LTC1735I-1 ........................................ –40°C to 85°C

Junction Temperature (Note 2)............................. 125°C

Storage Temperature Range ................. –65°C to 150°C

Lead Temperature (Soldering, 10 sec)..................300°C

+ 0.3V) to –0.3V

CC

UUW

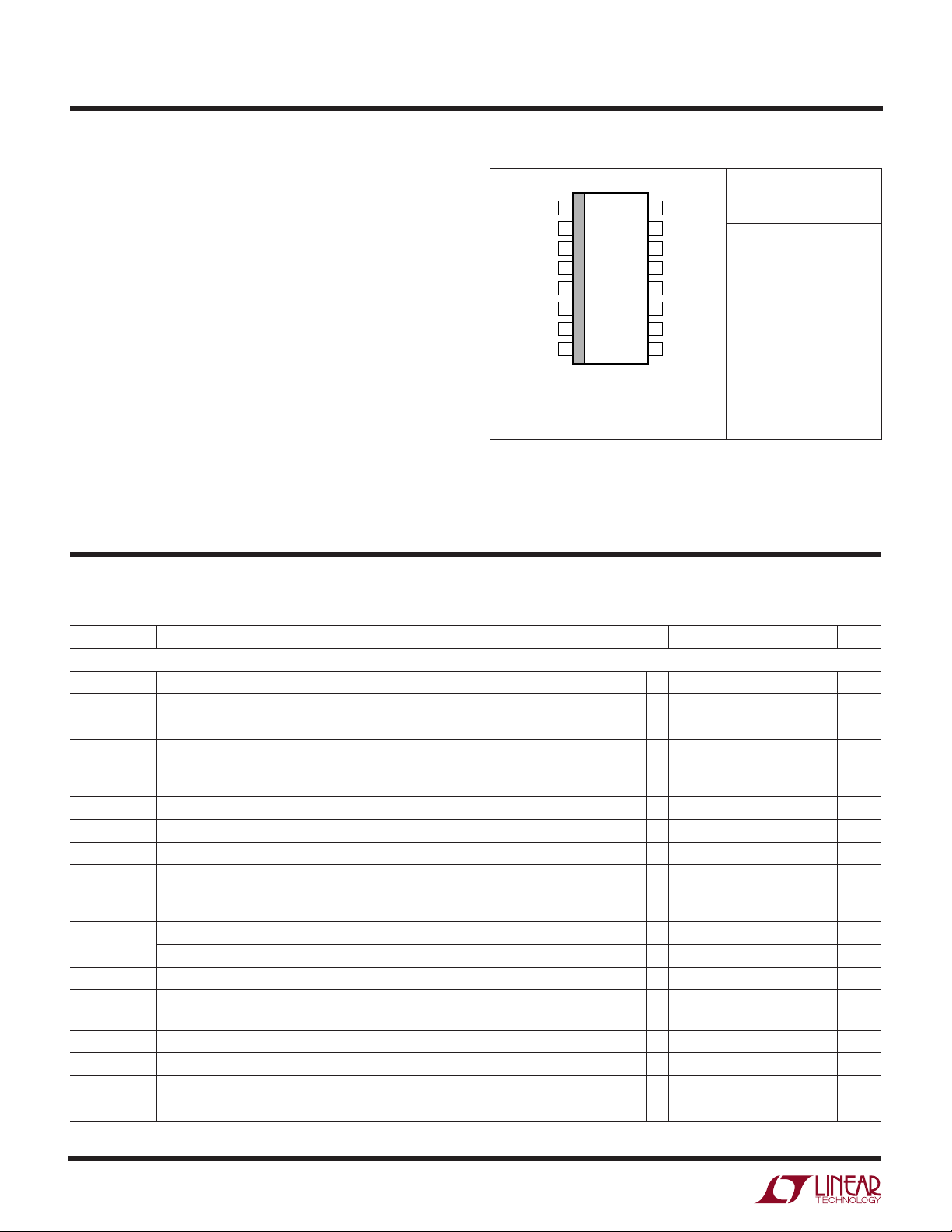

PACKAGE/ORDER I FOR ATIO

TOP VIEW

1

C

OSC

2

RUN/SS

3

I

TH

4

PGOOD

–

5

SENSE

+

6

SENSE

7

V

OSENSE

8

SGND

GN PACKAGE

16-LEAD PLASTIC SSOP

T

= 125°C, θJA = 130°C/W (GN)

JMAX

T

= 125°C, θJA = 110°C/W (S)

JMAX

Consult factory for Military grade parts.

16

TG

15

BOOST

14

SW

13

V

IN

12

INTV

CC

11

BG

10

PGND

9

EXTV

CC

S PACKAGE

16-LEAD PLASTIC SO

ORDER PART

NUMBER

LTC1735CGN-1

LTC1735CS-1

LTC1735IGN-1

LTC1735IS-1

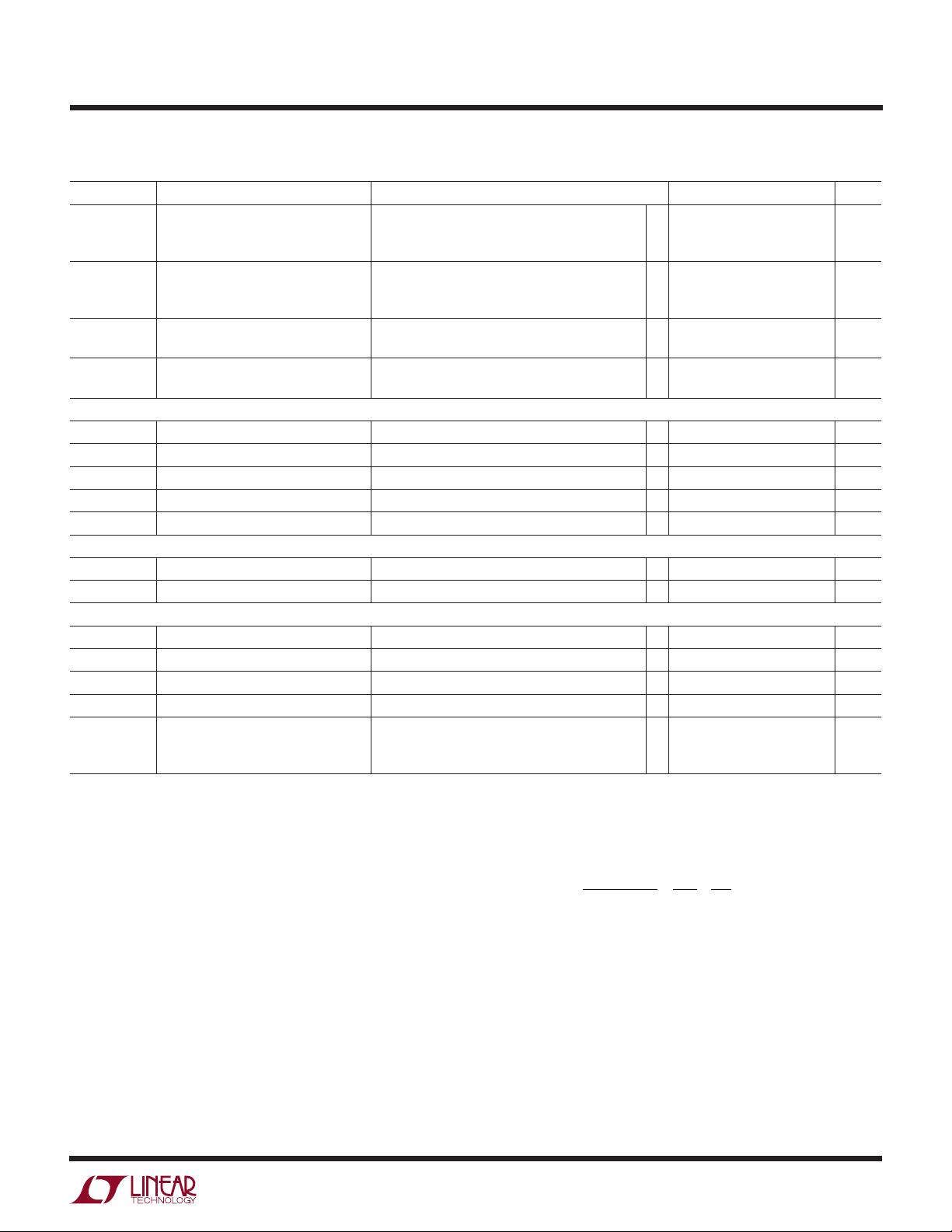

ELECTRICAL CHARACTERISTICS

temperature range, otherwise specifications are at TA = 25°C. VIN = 15V, V

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

Main Control Loop

I

VOSENSE

V

OSENSE

∆V

LINEREG

∆V

LOADREG

DF Max Maximum Duty Factor In Dropout 98 99.4 %

g

m

V

OVL

I

Q

V

RUN/SS

I

RUN/SS

I

SCL

UVLO Undervoltage Lockout Measured at VIN Pin (Ramping Negative) ● 3.5 3.9 V

∆V

SENSE(MAX)

I

SENSE

t

ON(MIN)

Feedback Current (Note 3) –4 –25 nA

Feedback Voltage (Note 3) ● 0.792 0.8 0.808 V

Reference Voltage Line Regulation VIN = 3.6V to 30V (Note 3) 0.001 0.02 %/V

Output Voltage Load Regulation (Note 3)

Transconductance Amplifier g

Feedback Overvoltage Lockout ● 0.84 0.86 0.88 V

Input DC Supply Current (Note 5)

Normal Mode 3.6V < V

Shutdown V

Run Pin Start Threshold V

Run Pin Begin Latchoff Threshold V

Soft-Start Charge Current V

RUN/SS Discharge Current Soft Short Condition, V

Maximum Current Sense Threshold V

SENSE Pins Total Source Current V

Minimum On-Time Tested with a Square Wave (Note 4) 160 200 ns

m

The ● denotes specifications which apply over the full operating

= 5V unless otherwise noted.

RUN/SS

Measured in Servo Loop; V

Measured in Servo Loop; V

< 30V 450 µA

IN

= 0V 15 25 µA

RUN/SS

, Ramping Positive 1.0 1.5 1.9 V

RUN/SS

, Ramping Positive 4.1 4.5 V

RUN/SS

= 0V –0.7 –1.2 µA

RUN/SS

= 4.5V

V

RUN/SS

= 0.7V ● 60 75 85 mV

OSENSE

SENSE

–

= V

+

= 0V 60 80 µA

SENSE

= 0.7V ● 0.1 0.3 %

ITH

= 2V ● –0.1 –0.3 %

ITH

1.3 mmho

= 0.5V, 0.5 2 4 µA

OSENSE

2

LTC1735-1

ELECTRICAL CHARACTERISTICS

temperature range, otherwise specifications are at TA = 25°C. VIN = 15V, V

The ● denotes specifications which apply over the full operating

= 5V unless otherwise noted.

RUN/SS

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

TG Transition Time: (Note 7)

TG t

TG t

r

f

Rise Time C

Fall Time C

= 3300pF 50 90 ns

LOAD

= 3300pF 50 90 ns

LOAD

BG Transition Time: (Note 7)

BG t

BG t

r

f

Rise Time C

Fall Time C

TG/BG T1D Top Gate Off to Synchronous C

= 3300pF 50 90 ns

LOAD

= 3300pF 40 80 ns

LOAD

= 3300pF Each Driver 100 ns

LOAD

Gate-On Delay Time

TG/BG T2D Synchronous Gate Off to Top C

= 3300pF Each Driver 70 ns

LOAD

Gate-On Delay Time

Internal VCC Regulator

V

INTVCC

V

LDO(INT)

V

LDO(EXT)

V

EXTVCC

V

EXTVCC(HYS)

Internal VCC Voltage 6V < VIN < 30V, V

INTVCC Load Regulation ICC = 0mA to 20mA, V

EXTVCC Drop Voltage ICC = 20mA, V

EXTVCC

= 4V 5.0 5.2 5.4 V

EXTVCC

= 4V 0.2 1 %

EXTVCC

= 5V 130 200 mV

EXTVCC Switchover Voltage ICC = 20mA, EXTVCC Ramping Positive ● 4.5 4.7 V

EXTVCC Hysteresis 0.2 V

Oscillator

f

OSC

fH/f

OSC

Oscillator Frequency (Note 6), C

= 43pF 265 300 335 kHz

OSC

Maximum Sync Frequency Ratio 1.3

PGOOD Pin

V

PG(SYNC)

V

PG(FC)

V

PGL

I

PGOOD

V

PG

Note 1: Absolute Maximum Ratings are those values beyond which the life

of the device may be impaired.

Note 2: T

dissipation P

LTC1735CS-1, LTC1735IS-1: TJ = TA + (PD • 110 °C/W)

LTC1735CGN-1, LTC1735IGN-1: T

Note 3: The LTC1735-1 is tested in a feedback loop that servos V

to the balance point for the error amplifier (V

Note 4: The minimum on-time condition corresponds to an inductor

peak-to-peak ripple current >40% of I

PGOOD Threshold for Sync Ramping Negative 0.9 1.2 V

PGOOD Threshold for Force Cont. 0.76 0.8 0.84 V

PGOOD Voltage Low I

PGOOD Pull-Up Current V

PGOOD Trip Level V

= 2mA 110 200 mV

PGOOD

= 0.85V –0.17 µA

PGOOD

With Respect to Set Output Voltage

OSENSE

V

V

Ramping Negative –6.0 –7.5 –9.5 %

OSENSE

Ramping Positive 6.0 7.5 9.5 %

OSENSE

Note 5: Dynamic supply current is higher due to the gate charge being

delivered at the switching frequency. See Applications Information.

is calculated from the ambient temperature TA and power

J

according to the following formulas:

D

= TA + (PD • 130°C/W)

J

= 1.2V).

ITH

OSENSE

Note 6: Oscillator frequency is tested by measuring the C

current (I

) and applying the formula:

OSC

.()

f kHz

()

OSC

8 477 10

=

CpF I I

OSC CHG DIS

()

–

8

11

+

11

1

+

Note 7: Rise and fall times are measured using 10% to 90% levels.

Delay times are measured using 50% levels.

(see Minimum On-Time

MAX

OSC

charge

Considerations in the Applications Information section).

3

LTC1735-1

UW

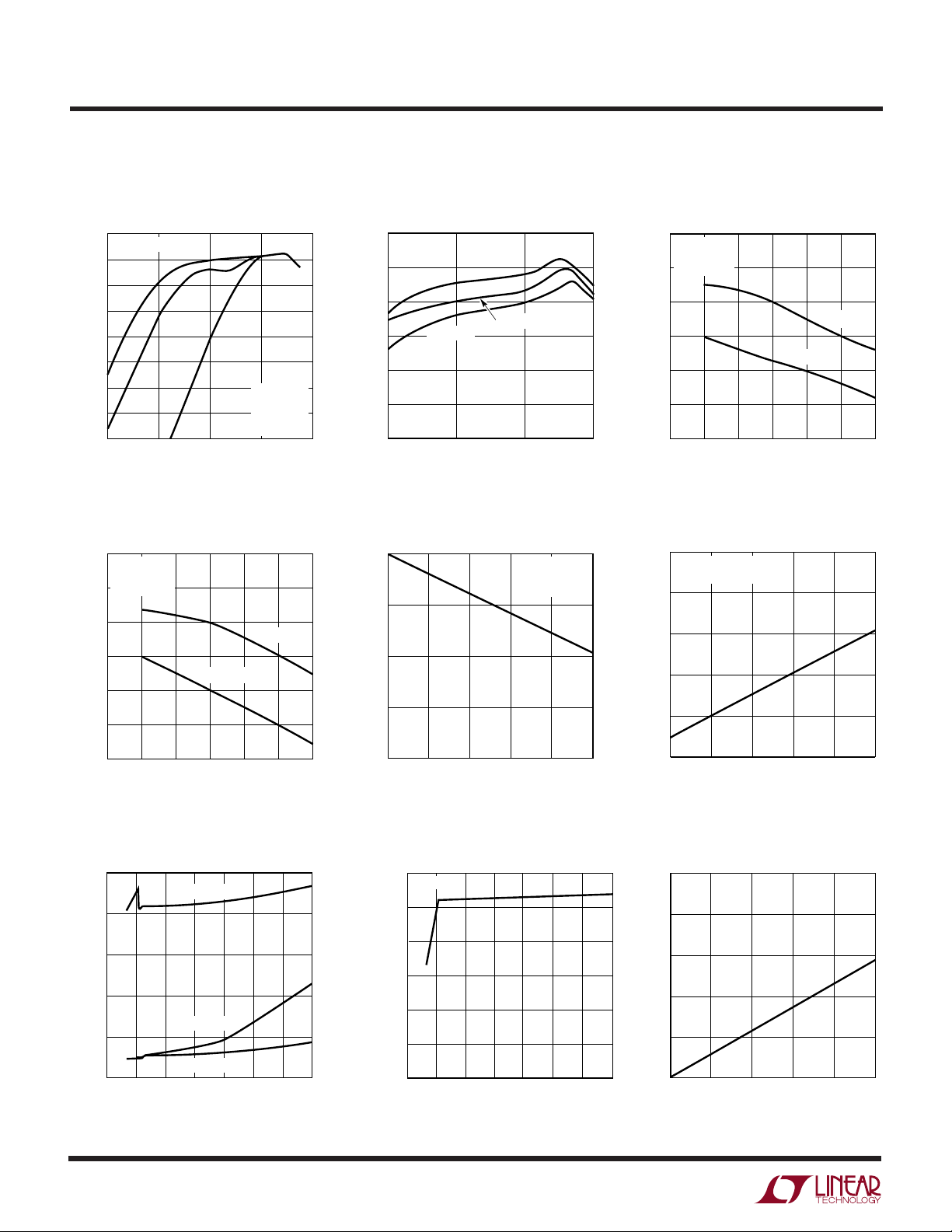

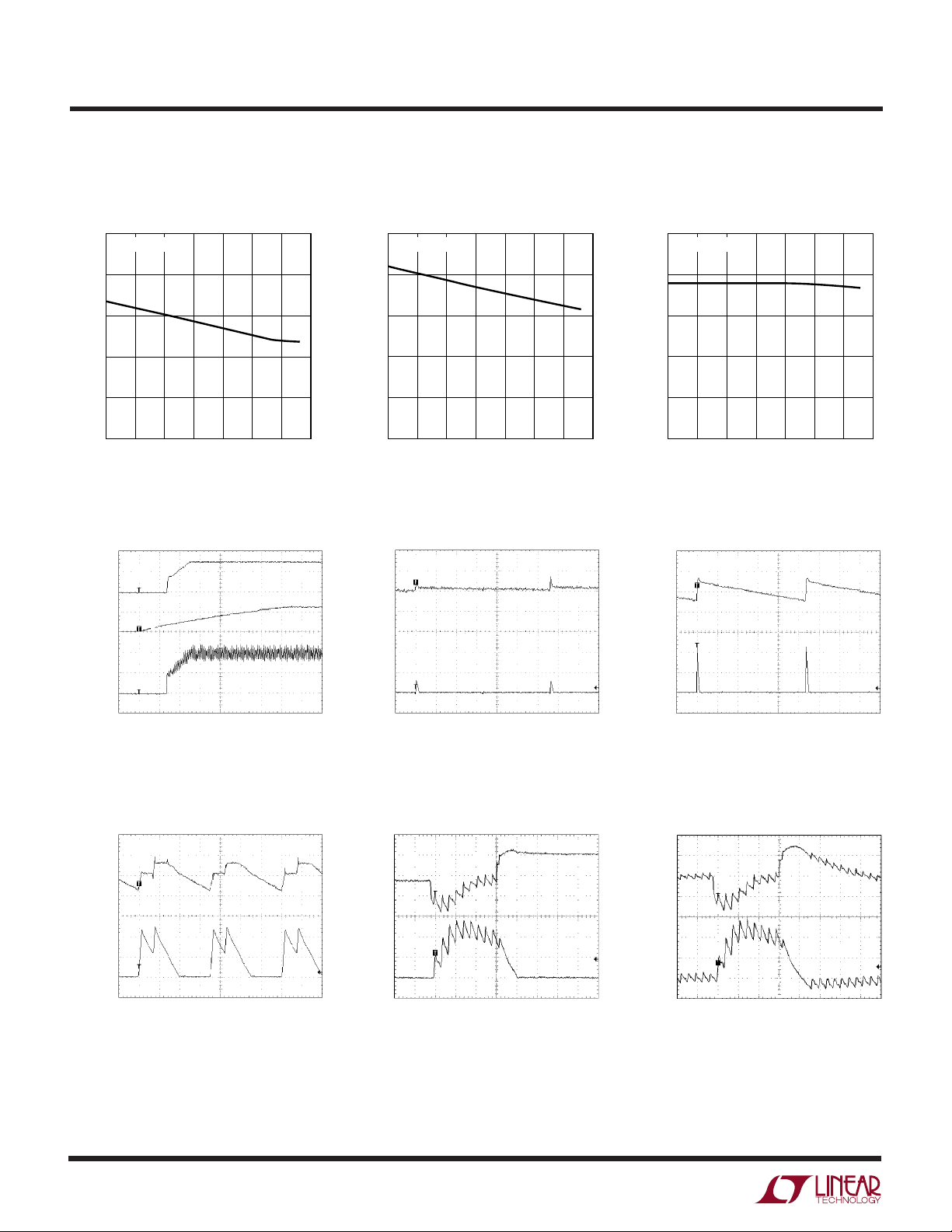

TYPICAL PERFOR A CE CHARACTERISTICS

Efficiency vs Load Current

(3 Operating Modes)

100

EXTVCC OPEN

90

BURST

80

70

60

50

EFFICIENCY (%)

40

30

20

0.001

0.01

SYNC

CONT

0.1

LOAD CURRENT (A)

VIN = 10V

V

= 3.3V

OUT

= 0.01Ω

R

S

f

= 300kHz

O

1

1735-1 G01

10

Efficiency vs Load Current

100

EXTVCC = 5V

= 1.6V

V

OUT

90

VIN = 5V

80

70

EFFICIENCY (%)

60

50

40

10mA 100mA 1A 10A

VIN = 24V

LOAD CURRENT (A)

VIN = 15V

1735-1 G02

Efficiency vs Input Voltage

100

EXTVCC = 5V

= 1.6V

V

OUT

95

FIGURE 1

90

85

EFFICIENCY (%)

80

75

70

0

10 15 20

5

INPUT VOLTAGE (V)

I

OUT

I

= 0.5A

= 5A

OUT

25 30

1735-1 G03

100

EXTVCC OPEN

= 1.6V

V

OUT

95

FIGURE 1

90

85

I

EFFICIENCY (%)

80

75

70

0

5

OUT

10 15 20

INPUT VOLTAGE (V)

Input and Shutdown Currents

vs Input Voltage

500

EXTVCC OPEN

400

300

200

INPUT CURRENT (µA)

100

0

05

SHUTDOWN

EXTVCC = 5V

20

15

10

INPUT VOLTAGE (V)

= 0.5A

25

I

OUT

= 5A

25 30

1735-1 G04

30

1735-1 G07

VIN – V

Dropout Voltage

OUT

vs Load CurrentLoad RegulationEfficiency vs Input Voltage

0

–0.1

(%)

OUT

–0.2

NORMALIZED V

–0.3

–0.4

0

2

4

LOAD CURRENT (A)

FCB = 0V

= 15V

V

IN

FIGURE 1

6

8

10

1735-1 G05

500

400

300

(mV)

OUT

– V

200

IN

V

100

R

SENSE

V

OUT

0

0

= 0.005Ω

= 5V – 5% DROP

2468

LOAD CURRENT (A)

10

1735-1 G06

EXTVCC Switch Drop

INTVCC Line Regulation

100

SHUTDOWN CURRENT (µA)

80

60

40

20

0

35

6

1mA LOAD

5

4

3

VOLTAGE (V)

CC

2

INTV

1

0

0

510

INPUT VOLTAGE (V)

20 30 35

15 25

1735-1 G08

vs INTVCC Load Current

500

400

(mV)

300

CC

– INTV

200

CC

EXTV

100

0

10

0

INTVCC LOAD CURRENT (mA)

30

40

20

50

1735-1 G09

4

UW

V

RUN/SS

(V)

0

0

V

ITH

(V)

0.5

1.0

1.5

2.0

2.5

1

234

1735-1 G15

56

V

OSENSE

= 0.7V

TYPICAL PERFOR A CE CHARACTERISTICS

Maximum Current Sense Threshold

vs Normalized Output Voltage

(Foldback)

80

70

60

50

40

30

20

10

MAXIMUM CURRENT SENSE THRESHOLD (mV)

0

0

25

NORMALIZED OUTPUT VOLTAGE (%)

50

75

100

1735-1 G10

Maximum Current Sense Threshold

vs V

RUN/SS

80

V

60

40

20

MAXIMUM CURRENT SENSE THRESHOLD (mV)

0

0

= 1.6V

SENSE(CM)

1234

V

(V)

RUN/SS

56

1735-1 G11

LTC1735-1

Maximum Current Sense Threshold

vs Sense Common Mode Voltage

80

76

72

68

64

MAXIMUM CURRENT SENSE THRESHOLD (mV)

60

1

0

2

COMMON MODE VOLTAGE (V)

3

4

5

1735-1 G12

Maximum Current Sense Voltage

vs ITH Voltage

90

80

70

60

50

40

30

20

10

0

–10

–20

MAXIMUM CURRENT SENSE VOLTAGE (V)

–30

0.5

0

1

V

ITH

SENSE Pins Total Source Current

100

50

(µA)

0

SENSE

I

–50

–100

0

24

V

COMMON MODE VOLTAGE (V)

SENSE

(V)

1.5

2

1735-1 G13

1735-1 G16

2.5

Maximum Current Sense Threshold

vs Temperature

80

V

75

70

65

MAXIMUM CURRENT SENSE THRESHOLD (mV)

60

–40

= 1.6V

SENSE(CM)

–15 10 35 60

TEMPERATURE (°C)

85 110 135

1735-1 G18

ITH Voltage vs Load Current

2.5

VIN = 10V

= 3.3V

V

OUT

= 0.01Ω

R

SENSE

2.0

= 300kHz

f

O

CONTINUOUS

1.5

VOLTAGE (V)

1.0

TH

I

0.5

6

0

MODE

SYNCHRONIZED f = f

Burst Mode

OPERATION

0

234

1

LOAD CURRENT (A)

O

56

1735-1 G17

V

vs V

ITH

RUN/SS

Output Current vs Duty Cycle

100

(%)

MAX

80

/I

OUT

60

40

20

f

SYNC

AVERAGE OUTPUT CURRENT I

0

0

I

OUT/IMAX

(SYNCHRONIZED)

= f

O

40 60 80

20

DUTY CYCLE (%)

(FREE RUN)

I

OUT/IMAX

100

1735-1 G14

5

LTC1735-1

UW

TYPICAL PERFOR A CE CHARACTERISTICS

Oscillator Frequency

vs Temperature

300

C

= 47pF

OSC

290

280

270

FREQUENCY (kHz)

260

250

–40 –15

10

TEMPERATURE (°C)

Start-Up

V

OUT

1V/DIV

V

RUN/SS

5V/DIV

RUN/SS Pin Current

vs Temperature

0

V

= 0V

RUN/SS

–1

–2

–3

RUN/SS CURRENT (µA)

–4

60

35

85

110

1735-1 G19

135

–5

V

OUT

10mV/DIV

–40 –15

V

10

TEMPERATURE (°C)

OUT(RIPPLE)

I

= 10mA I

LOAD

60

35

85

(Synchronized)

110

1735-1 G20

FIGURE 1

135

PGOOD Pin Current

vs Temperature

0

V

PGOOD

–0.2

–0.4

–0.6

PGOOD PIN CURRENT (µA)

–0.8

–1.0

–40 –15

V

OUT(RIPPLE)

(Burst Mode Operation)

LOAD

V

OUT

20mV/DIV

= 0.85V

35

10

TEMPERATURE (°C)

= 50mA

60

85

110

1735-1 G21

FIGURE 1

135

5A/DIV

V

OUT

20mV/DIV

5A/DIV

I

L

V

= 15V 5ms/DIV 1735-1 G22

IN

V

= 1.6V

OUT

R

= 0.16Ω

LOAD

V

OUT(RIPPLE)

(Burst Mode Operation)

I

= 1.5A

LOAD

I

L

= 15V 5µs/DIV 1735-1 G25

V

IN

V

= 1.6V

OUT

I

L

5A/DIV

= 15V 50µs/DIV 1735-1 G24

V

IN

V

= 1.6V

OUT

5A/DIV

I

L

EXT SYNC f = f

VIN = 15V

V

= 1.6V

OUT

10µs/DIV 1735-1 G23

O

Load Step

(Burst Mode Operation)

FIGURE 1 FIGURE 1 FIGURE 1

V

OUT

50mV/DIV

5A/DIV

I

L

10mA TO 10µs/DIV

11A LOAD STEP

V

= 15V

IN

= 1.6V

V

OUT

1735-1 G26

50mV/DIV

Load Step (Continuous Mode)

V

OUT

I

L

5A/DIV

0A TO 10µs/DIV

11A LOAD STEP

PGOOD = 0V

= 15V

V

IN

V

= 1.6V

OUT

1735-1 G27

6

UUU

PI FU CTIO S

C

(Pin 1): External capacitor C

OSC

ground sets the operating frequency.

RUN/SS (Pin 2): Combination of Soft-Start and Run

Control Inputs. A capacitor to ground at this pin sets the

ramp time to full current output. The time is approximately

1.25s/µF. Forcing this pin below 1.5V causes the device to

be shut down. In shutdown all functions are disabled.

Latchoff overcurrent protection is also invoked via this pin

as described in the Applications Information section.

ITH (Pin 3): Error Amplifier Compensation Point. The

current comparator threshold increases with this control

voltage. Nominal voltage range for this pin is 0V to 2.4V.

PGOOD (Pin 4): Open-Drain Logic Output and Forced

Continuous/Synchronization Input. The PGOOD pin is

pulled to ground when the voltage on the V

not within ±7.5% of its nominal set point. If power good

indication is not needed, this pin can be tied to ground to

force continuous synchronous operation. Clocking this

pin with a signal above 1.5V

oscillator to the external clock. Synchronization only

occurs while the main output is in regulation (PGOOD not

internally pulled low). When synchronized, Burst Mode

operation is disabled but cycle skipping is allowed at low

load currents. This pin requires a pull-up resistor for

power good indication. Do not connect this pin directly to

an external source (or INTVCC). Do not exceed INTVCC on

this pin.

SENSE– (Pin 5): The (–) Input to the Current Comparator.

SENSE+ (Pin 6): The (+) Input to the Current Comparator.

Built-in offsets between SENSE+ and SENSE– pins in

conjunction with R

threshold.

V

OSENSE

external resistive divider across the output.

(Pin 7): Receives the feedback voltage from an

SENSE

synchronizes the internal

P-P

set the inductor current trip

from this pin to

OSC

OSENSE

pin is

LTC1735-1

SGND (Pin 8): Small-Signal Ground. All small-signal

components such as C

the loop compensation resistors and capacitor(s) should

single-point tie to this pin. This pin should, in turn, connect

to PGND.

EXTVCC (Pin 9): Input to the Internal Switch Connected to

INTVCC. This switch closes and supplies VCC power whenever EXTVCC is higher than 4.7V. See EXTVCC connection

in Applications Information section. Do not exceed 7V on

this pin and ensure EXTVCC is ≤ VIN.

PGND (Pin 10): Driver Power Ground. This pin connects

to the source of the bottom N-channel MOSFET, the anode

of the Schottky diode and the (–) terminal of CIN.

BG (Pin 11): High Current Gate Drive for the Bottom

N-Channel MOSFET. Voltage swing at this pin is from

ground to INTV

INTVCC (Pin 12): Output of the Internal 5.2V Low Dropout

Regulator and EXTVCC Switch. The driver and control

circuits are powered from this voltage. Decouple to power

ground with a 1µF ceramic capacitor placed directly adja-

cent to the IC together with a minimum of 4.7µF tantalum

or other low ESR capacitor.

V

(Pin 13): Main Supply Pin. This pin must be closely

IN

decoupled to power ground.

SW (Pin 14): Switch Node Connection to Inductor and

Bootstrap Capacitor. Voltage swing at this pin is from a

Schottky diode (external) voltage drop below ground to

VIN.

BOOST (Pin 15): Supply to Topside Floating Driver. The

bootstrap capacitor is returned to this pin. Voltage swing

at this pin is from a diode drop below INTVCC to VIN +

INTVCC.

TG (Pin 16): High Current Gate Drive for Top N-Channel

MOSFET. This is the output of a floating driver with a

voltage swing equal to INTVCC superimposed on the

switch node voltage SW.

CC

.

, CSS, the feedback divider plus

OSC

7

LTC1735-1

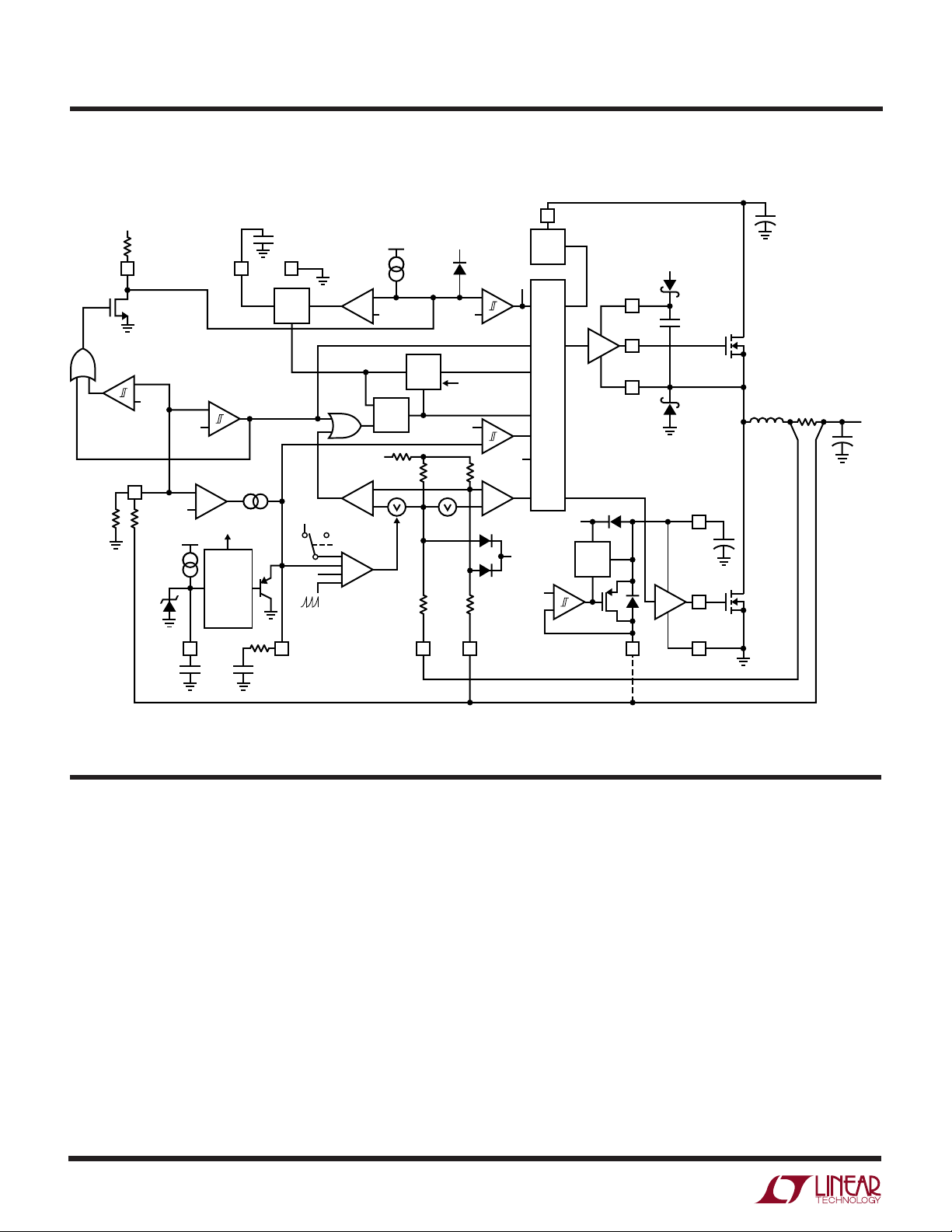

UU

W

FU CTIO AL DIAGRA

INTV

CC

100k

PGOOD

4 8

–

+

0.74V

V

OSENSE

7

R1

R2

1.2µA

6V

RUN/SS

C

0.8V

SS

0.86V

V

FB

2

+

–

–

EA

+

CURRENT

LATCHOFF

OSC

g

=1.3m

m

SD

RUN

SOFT-

START

OVER-

C

C

OV

+

C

OSC

SGNDC

1

SYNC

OSC

Ω

0.86V

)

4(V

FB

SLOPE COMP

R

C

I

TH

C

ICMP

BURST

DISABLE

FC

A

2.4V

I

1

–

+

1.2V

FORCE BOT

S

R

–

+

BUFFERED

SENSE

Q

2k

I

TH

0.17µA

DROP

OUT

DET

TOP ON

45k

+– –+

30k 30k

+

3mV

INTV

0.55V

0.8V

CC

BOT

–

+

+

–

45k

–

I

+

SENSE

V

IN

V

13

IN

UVL

0.8V

REF

FC

F

TOP

SWITCH

LOGIC

B

SD

IREV

2

INTV

–

4.8V

BOT

V

IN

CC

5.2V

LDO

REG

+

–

EXTV

CC

BOOST

15

TG

16

SW

14

9563

INTV

CC

D

B

C

B

D

1

INTV

CC

12

C

INTVCC

BG

11

PGND

10

+

C

IN

R

L

SENSE

V

OUT

+

C

OUT

+

U

OPERATIO

Main Control Loop:

The LTC1735-1 uses a constant frequency, current mode

step-down architecture. During normal operation, the top

MOSFET is turned on each cycle when the oscillator sets

the RS latch, and turned off when the main current

comparator I1 resets the RS latch. The peak inductor

current at which I1 resets the RS latch is controlled by the

voltage on Pin ITH, which is the output of error amplifier

EA. Pin V

OSENSE

to receive an output feedback voltage VFB from the external

resistive divider. When the load current increases, it

causes a slight decrease in VFB relative to the 0.8V reference, which in turn causes the ITH voltage to increase until

, described in the Pin Functions, allows EA

(Refer to Functional Diagram)

1735-1 FD

the average inductor current matches the new load current. While the top MOSFET is off, the bottom MOSFET is

turned on until either the inductor current starts to reverse,

as indicated by current comparator I2, or the beginning of

the next cycle.

The top MOSFET driver is powered from a floating bootstrap capacitor CB. This capacitor is normally recharged

from INTVCC through an external Schottky diode when the

top MOSFET is turned off. As VIN decreases towards V

OUT

,

the converter will attempt to turn on the top MOSFET continuously (“dropout’’). A dropout counter detects this condition and forces the top MOSFET to turn off for about 500ns

every tenth cycle to recharge the bootstrap capacitor.

8

OPERATIO

LTC1735-1

U

(Refer to Functional Diagram)

The main control loop is shut down by pulling Pin 2 (RUN/

SS) low. Releasing RUN/SS allows an internal 1.2µA

current source to charge soft-start capacitor CSS. When

CSS reaches 1.5V, the main control loop is enabled with the

ITH voltage clamped at approximately 30% of its maximum

value. As CSS continues to charge, ITH is gradually released allowing normal operation to resume. If V

not reached 70% of its final value when CSS has charged

to 4.1V, latchoff can be invoked as described in the

Applications Information section.

The internal oscillator can be synchronized to an external

clock applied though a series resistor to the PGOOD pin

and can lock to a frequency between 90% and 130% of its

nominal rate set by capacitor C

An overvoltage comparator OV guards against transient

overshoots (>7.5%) as well as other more serious

conditions that may overvoltage the output. In this case,

the top MOSFET is turned off and the bottom MOSFET is

turned on until the overvoltage condition is cleared.

Foldback current limiting for an output shorted to ground

is provided by amplifier A. As V

the buffered ITH input to the current comparator is gradually

pulled down to a 0.86V clamp. This reduces peak inductor

current to about 1/4 of its maximum value.

Low Current Operation

The LTC1735-1 has three low current modes controlled

by the PGOOD pin. Burst Mode operation is selected when

the PGOOD pin is above 0.8V (typically tied through a

resistor to INTVCC). During Burst Mode operation, if the

error amplifier drives the ITH voltage below 0.86V, the

buffered ITH input to the current comparator will be

clamped at 0.86V. The inductor current peak is then held

at approximately 20mV/R

output current). If ITH then drops below 0.5V, the Burst

Mode comparator B will turn off both MOSFETs to maximize efficiency. The load current will be supplied solely by

the output capacitor until ITH rises above the 60mV

hysteresis of the comparator and switching is resumed.

Burst Mode operation is disabled by comparator F when

the PGOOD pin is brought below 0.8V. This forces

SENSE

.

OSC

drops below 0.6V,

OSENSE

(about 1/4 of maximum

OUT

has

continuous operation and assists in controlling voltage

regulation. If the output voltage is not within 7.5% of its

nominal value the PGOOD open-drain output will be

pulled low and Burst Mode operation will be disabled.

Foldback Current, Short-Circuit Detection

and Short-Circuit Latchoff

The RUN/SS capacitor, CSS, is used initially to limit the

inrush current of the switching regulator. After the controller has been started and been given adequate time to

charge up the output capacitors and provide full load

current, CSS is used as a short-circuit time-out circuit. If

the output voltage falls to less than 70% of its nominal

output voltage, CSS begins discharging on the assumption

that the output is in an overcurrent and/or short-circuit

condition. If the condition lasts for a long enough period

as determined by the size of the CSS, the controller will be

shut down until the RUN/SS pin voltage is recycled. This

built-in latchoff can be overridden by providing a current

>5µA at a compliance of 5V to the RUN/SS pin. This

current shortens the soft-start period but also prevents net

discharge of C

circuit condition. Foldback current limiting is activated

when the output voltage falls below 70% of its nominal

level whether or not the short-circuit latchoff circuit is

enabled.

INTVCC/EXTVCC Power

Power for the top and bottom MOSFET drivers and most

of the internal circuitry of the LTC1735-1 is derived from

the INTVCC pin. When the EXTVCC pin is left open, an

internal 5.2V low dropout regulator supplies the INTV

power from VIN. If EXTVCC is raised above 4.7V, the

internal regulator is turned off and an internal switch

connects EXTVCC to INTVCC. This allows a high efficiency

source, such as the primary or a secondary output of the

converter itself, to provide the INTVCC power. Voltages up

to 7V can be applied to EXTVCC for additional gate drive

capability.

To provide clean start-up and to protect the MOSFETs,

undervoltage lockout is used to keep both MOSFETs off

until the input voltage is above 3.5V.

during an overcurrent and/or short-

SS

CC

9

Loading...

Loading...