LG Display LC470EUF-PEF1 Specification

Product Specification

LCM ENGINEERING

SPECIFICATION

LC470EUF

Ver. 1.0

*MODEL LC470EUF

SUFFIX PEF1

Update Aug. 09, 2012

( ) Preliminary Specification

( ● ) Final Specification

1/40

Product Specification

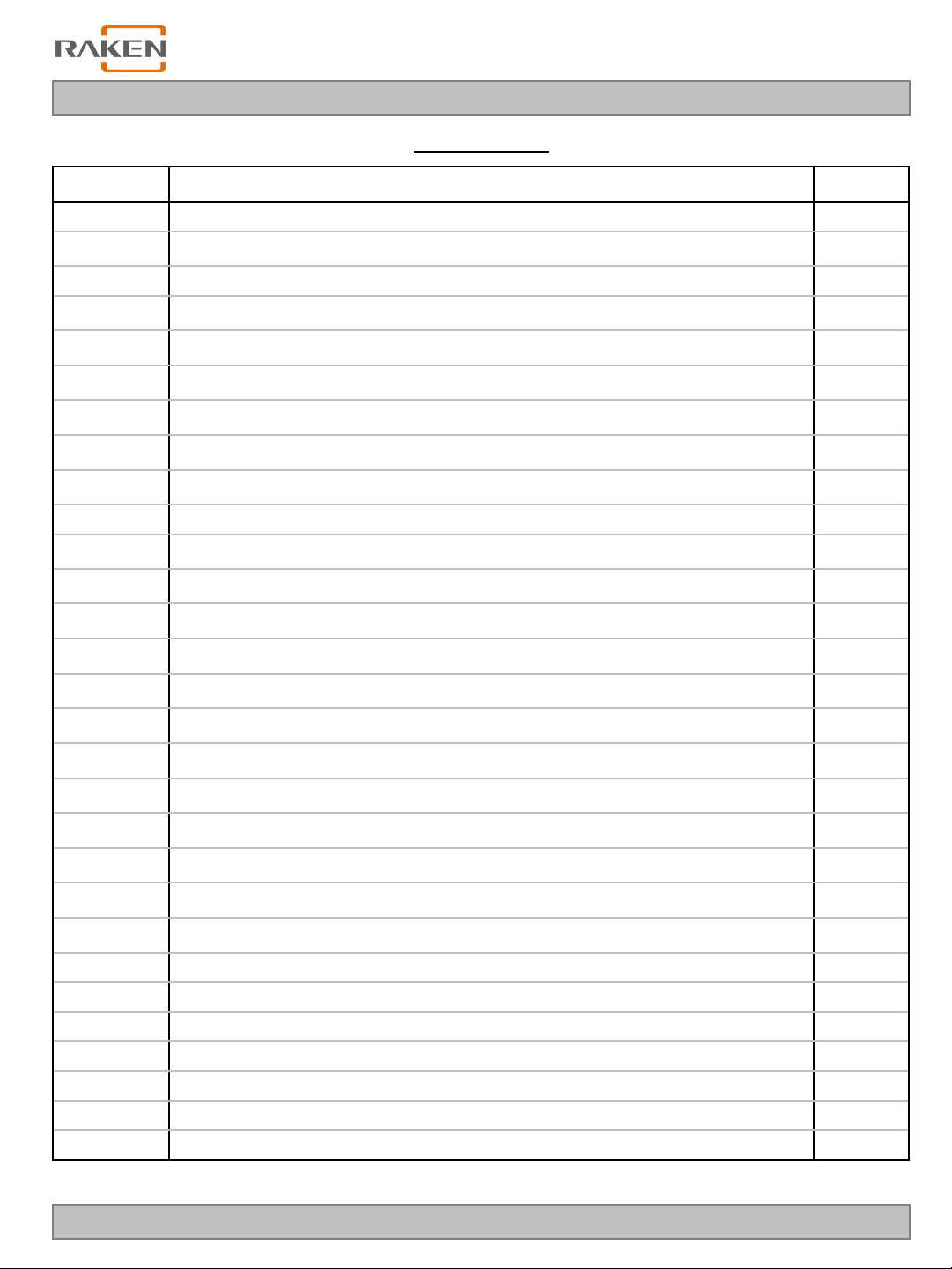

CONTENTS

LC470EUF

Number ITEM

COVER 1

CONTENTS

RECORD OF REVISIONS 3

1 GENERAL DESCRIPTION

2 ABSOLUTE MAXIMUM RATINGS

3 ELECTRICAL SPECIFICATIONS

3-1 ELECTRICAL CHARACTERISTICS

3-2 INTERFACE CONNECTIONS

3-3 SIGNAL TIMING SPECIFICATIONS

3-4 LVDS SIGNAL SPECIFICATIONS 12

3-5 COLOR DATA REFERENCE

3-6 POWER SEQUENCE

4 OPTICAL SPECIFICATIONS

5 MECHANICAL CHARACTERISTICS

6 RELIABILITY

Page

2

4

5

6

6

8

11

15

16

17

23

26

7 INTERNATIONAL STANDARDS

7-1 SAFETY

7-2 EMC

7-3 ENVIRONMENT

8 PACKING

8-1 INFORMATION OF LCM LABEL

8-2 PACKING FORM

9 PRECAUTIONS 29

9-1 MOUNTING PRECAUTIONS 29

9-2 OPERATING PRECAUTIONS 29

9-3 ELECTROSTATIC DISCHARGE CONTROL 30

9-4 PRECAUTIONS FOR STRONG LIGHT EXPOSURE 30

9-5 STORAGE 30

9-6 OPERAGING CONDITION GUIDE 30

Ver. 1.0

27

27

27

27

28

28

28

2/40

Product Specification

RECORD OF REVISIONS

Revision No. Revision Date Page Description

1.0 Aug , 09, 2012 - Preliminary Specification (First Draft)

LC470EUF

Ver. 1.0

3/40

LC470EUF

Product Specification

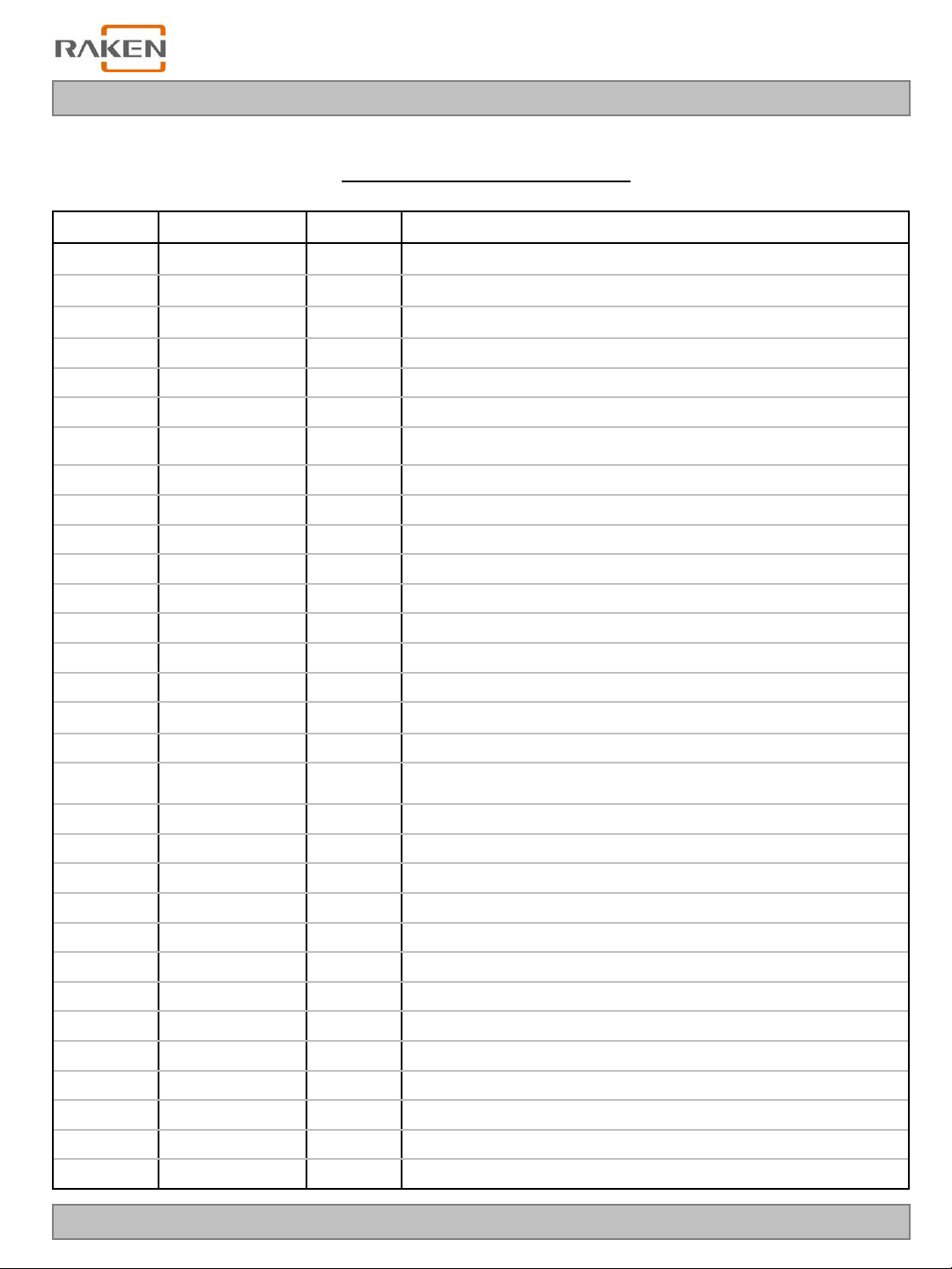

1. General Description

The LC470EUF is a Color Active Matrix Liquid Crystal Display with an integral Light Emitting Diode (LED)

backlight system. The matrix employs a-Si Thin Film Transistor as the active element.

It is a transmissive display type which is operating in the normally black mode. It has a 46.96 inch diagonally

measured active display area with WUXGA resolution (1080 vertical by 1920 horizontal pixel array).

Each pixel is divided into Red, Green and Blue sub-pixels or dots which are arrayed in vertical stripes.

Gray scale or the luminance of the sub-pixel color is determined with a 10-bit gray scale signal for each dot.

Therefore, it can present a palette of more than 1.06Bilion colors.

It has been designed to apply the 10-bit 4-port LVDS interface.

It is intended to support LCD TV, PCTV where high brightness, super wide viewing angle, high color gamut,

high color depth and fast response time are important.

EPI (RGB)

Control

Signals

Power Signals

Source Driver Circuit

S1 S1920

G1

TFT - LCD Panel

(1920 × RGB × 1080 pixels)

[Gate In Panel]

G1080

LVDS

2Port

LVDS

2Port

LVDS

Select

Bit

Select

+12.0V

CN2

(41pin)

CN1

(51pin)

LVDS 3,4

LVDS 1,2

Option

signal

I2C

EEPROM

SCL

SDA

Timing Controller

LVDS Rx + DGA + ODC

Integrated

Power Circuit

Block

CN2

PWM

(4 pin)

PWM_OUT

1~3

Scanning

Block 1

LED Anode

LED Cathode

CN1(8Pin), CN2 (8pin)

General Features

Active Screen Size 46.96 inch (1192.78mm) diagonal

Outline Dimension 1059.5(H) X 616.2(V) X 9.4(B) X 20.7(D) (TBD)

Pixel Pitch 0.5415 mm x 0.5415 mm

Pixel Format 1920 horiz. by 1080 vert. Pixels, RGB stripe arrangement

Color Depth 10bit(D), 1.06Billon colors

Luminance, White 400 cd/m2 (Center 1point ,Typ.)

Scanning

Block 2

Scanning

Block 3

Viewing Angle (CR>10) Viewing angle free ( R/L 178 (Min.), U/D 178 (Min.))

Power Consumption Total 82.1W (Typ.) [Logic=8.4W with T-Con, LED BLU=73.7W(IF_cathode=105mA)]

Weight 11.0 Kg (Typ.) (TBD)

Display Mode Transmissive mode, Normally black

Surface Treatment Hard coating(2H), Anti-glare treatment of the front polarizer (Haze < 1%)

Ver. 1.0

4/40

LC470EUF

Product Specification

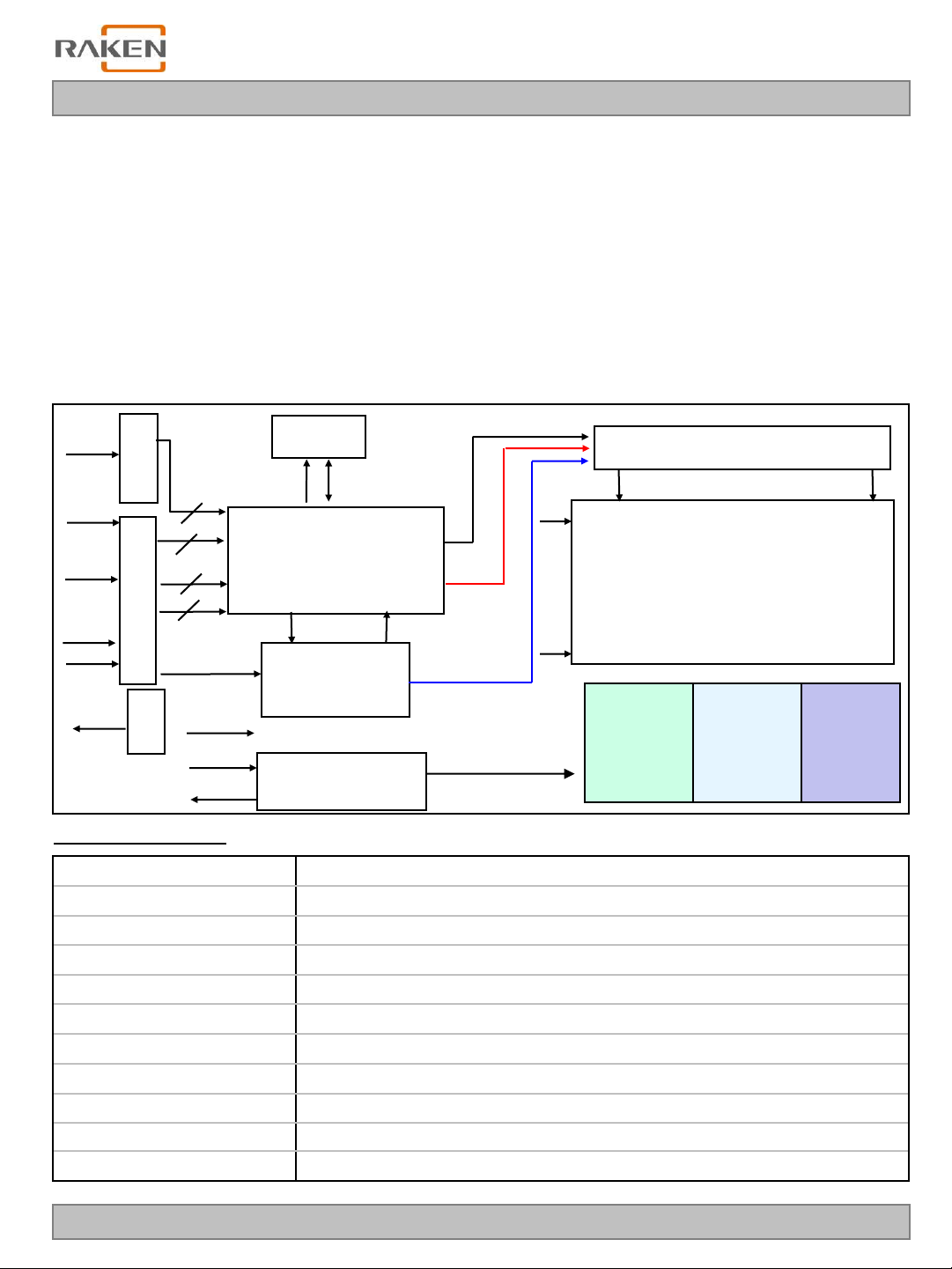

2. Absolute Maximum Ratings

The followingitems are maximumvalueswhich, ifexceeded,may cause faulty operation or permanent damage

to the LCD module.

Table 1. ABSOLUTE MAXIMUM RATINGS

Parameter Symbol

Unit Note

Min Max

Power Input Voltage LCD Circuit VLCD -0.3 +14.0 VDC

LED Input Voltage Forward Voltage VF - +73.9 VDC

T-Con Option Selection Voltage VLOGIC -0.3 +4.0 VDC

Value

Operating Temperature TOP 0 +50

Storage Temperature TST -20 +65

Panel Front Temperature TSUR - +68

°C

°C

°C

Operating Ambient Humidity HOP 10 90 %RH

Storage Humidity HST 10 90 %RH

Note

1. Ambient temperature condition (Ta = 25 2 °C )

2. Temperature and relative humidity range are shown in the figure below.

Wet bulb temperature should be Max 39°C, and no condensation of water.

3. Gravity mura can be guaranteed below 40°C condition.

4. The maximum operating temperatures is based on the test condition that the surface temperature

of display area is less than or equal to 68°C with LCD module alone in a temperature controlled chamber.

Thermal management should be considered in final product design to prevent the surface temperature of

display area from being over 68℃. The range of operating temperature may be degraded in case of

improper thermal management in final product design.

90%

1

2,3

4

2,3

Ver. 1.0

Wet Bulb

Temperature [°C]

20

10

0

10 20 30 40 50 60 70 800-20

Dry Bulb Temperature [°C]

30

40

50

60

60%

40%

10%

Storage

Operation

Humidity [(%)RH]

5/40

LC470EUF

Product Specification

3. Electrical Specifications

3-1. Electrical Characteristics

It requires two power inputs. One is employed to power for the LCD circuit. The other Is used for the LED

backlight.

Table 2. ELECTRICAL CHARACTERISTICS

Parameter Symbol

Min Typ Max

Circuit :

Power Input Voltage VLCD 10.8 12.0 13.2 VDC

Value

Unit Note

Power Input Current ILCD

Power Consumption PLCD - 8.4 10.9 Watt 1

Rush current IRUSH - - 5.0 A 3

Note

1. The specified current and power consumption are under the V

- 700 910 mA 1

- 1010 1313 mA 2

=12.0V, Ta=25 2°C, fV=120Hz

LCD

condition, and mosaic pattern(8 x 6) is displayed and fVis the frame frequency.

2. The current is specified at the maximum current pattern.

3. The duration of rush current is about 2ms and rising time of power input is 0.5ms (min.).

4. Ripple voltage level is recommended under ± 5% of typical voltage

White : 1023 Gray

Black : 0 Gray

Ver. 1.0

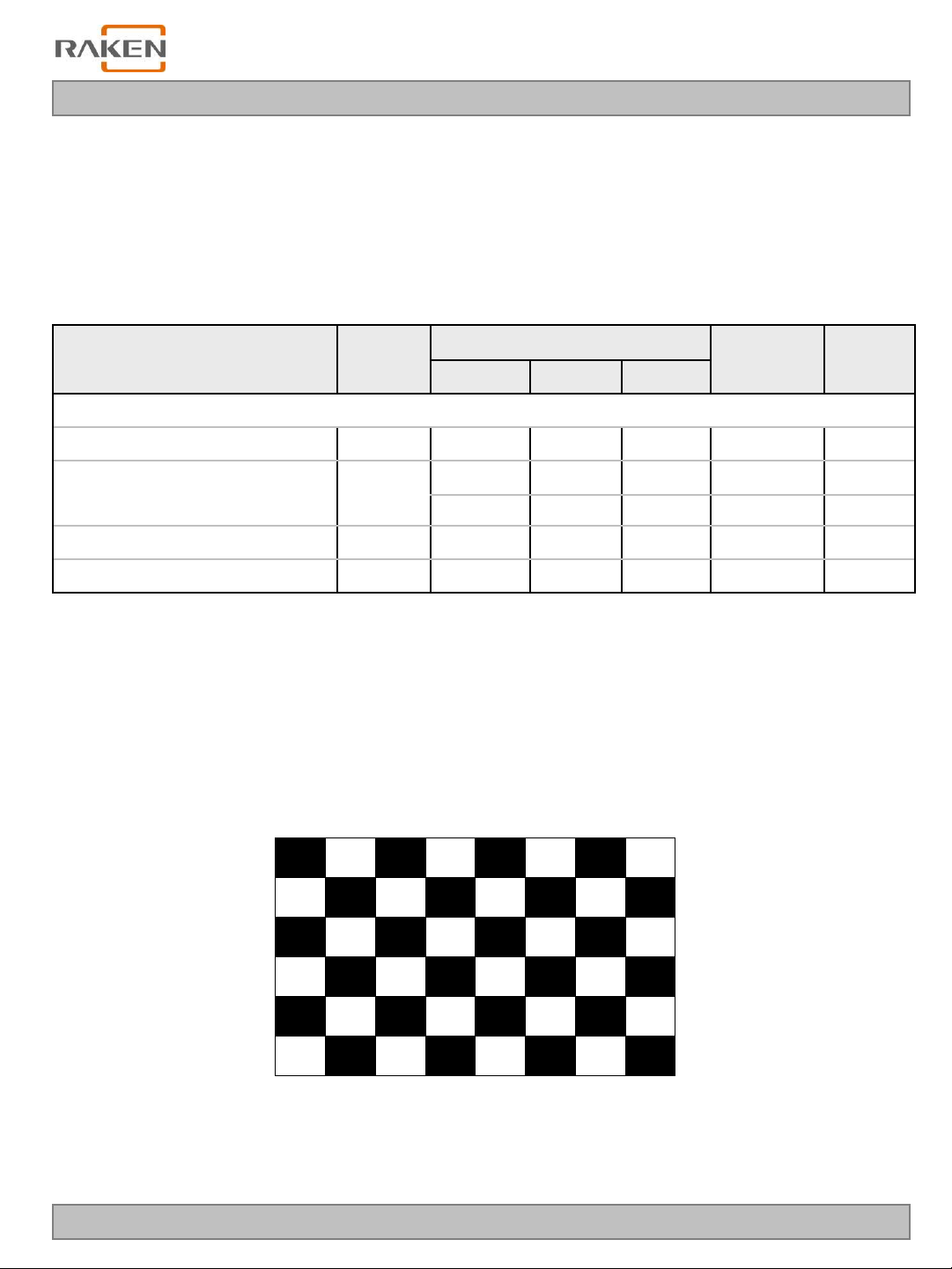

Mosaic Pattern(8 x 6)

6/40

Product Specification

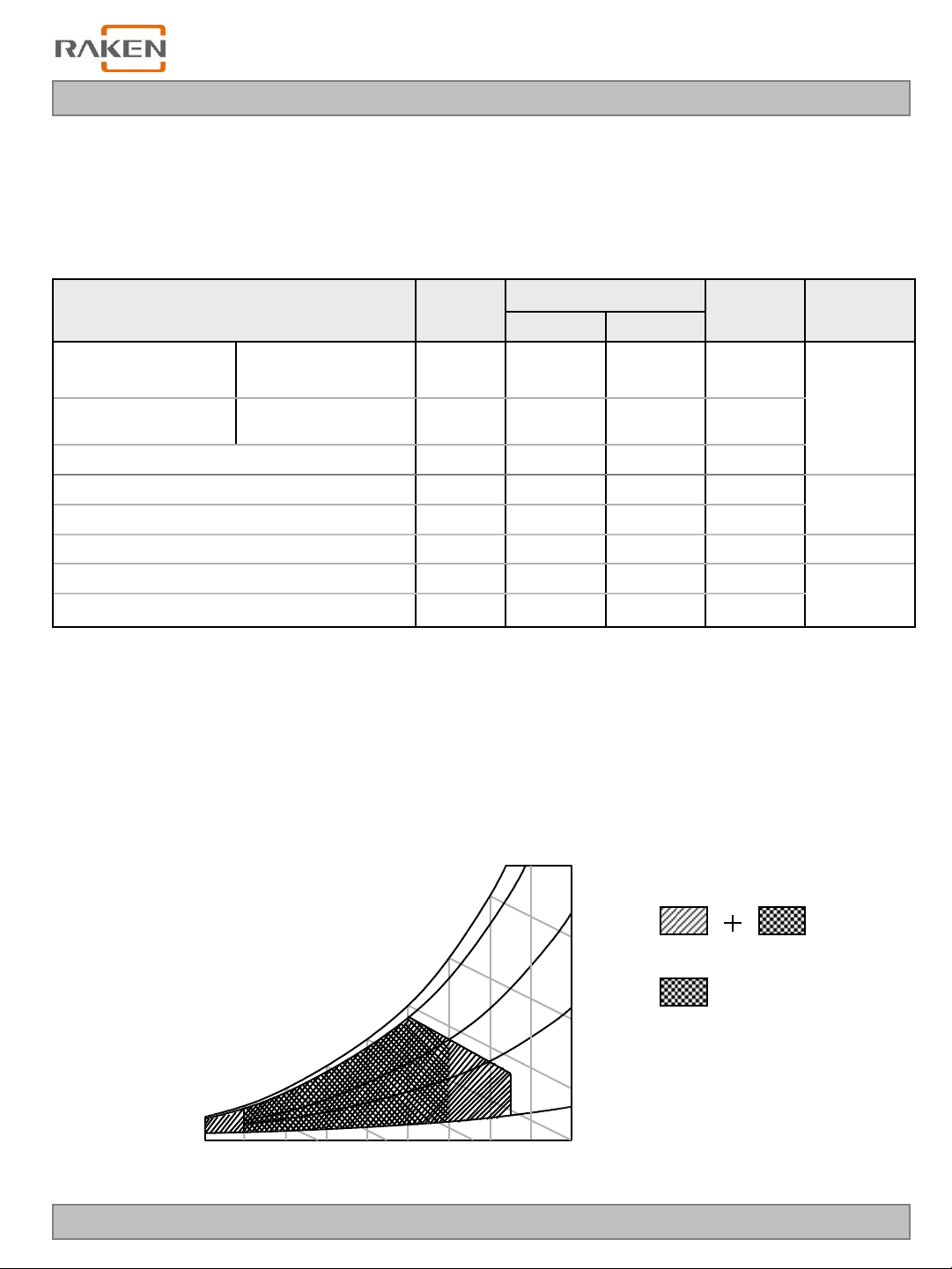

Table 3. ELECTRICAL CHARACTERISTICS (Continue)

LC470EUF

Notes :

Parameter Symbol

Backlight Assembly :

Forward Current

(one array)

Forward Voltage V

Forward Voltage Variation

Power Consumption P

Burst Dimming Duty On duty 1 100 %

Burst Dimming Frequency 1/T 95 182 Hz 8

LED Array

Life Time - - Hrs 7

Anode I

Cathode I

F (anode)

F (cathode)

F

△V

F

BL

Min Typ Max

99.75 105 110.25 mAdc

53.1 58.5 63.9 Vdc 4

- 73.7 80.5 W 6

Values

630 mAdc

1.7 Vdc 5

Unit Note

± 5%

2, 3

The design of the LED driver must have specifications for the LED array in LCD Assembly.

The electrical characteristics of LED driver are based on Constant Current driving type.

The performance of the LED in LCM, for example life time or brightness, is extremely influenced by the

characteristics of the LED Driver. So, all the parameters of an LED driver should be carefully designed.

When you design or order the LED driver, please make sure unwanted lighting caused by the mismatch of the

LED and the driver (no lighting, flicker, etc) has never been occurred. When you confirm it, the LCD–

Assembly should be operated in the same condition as installed in your instrument.

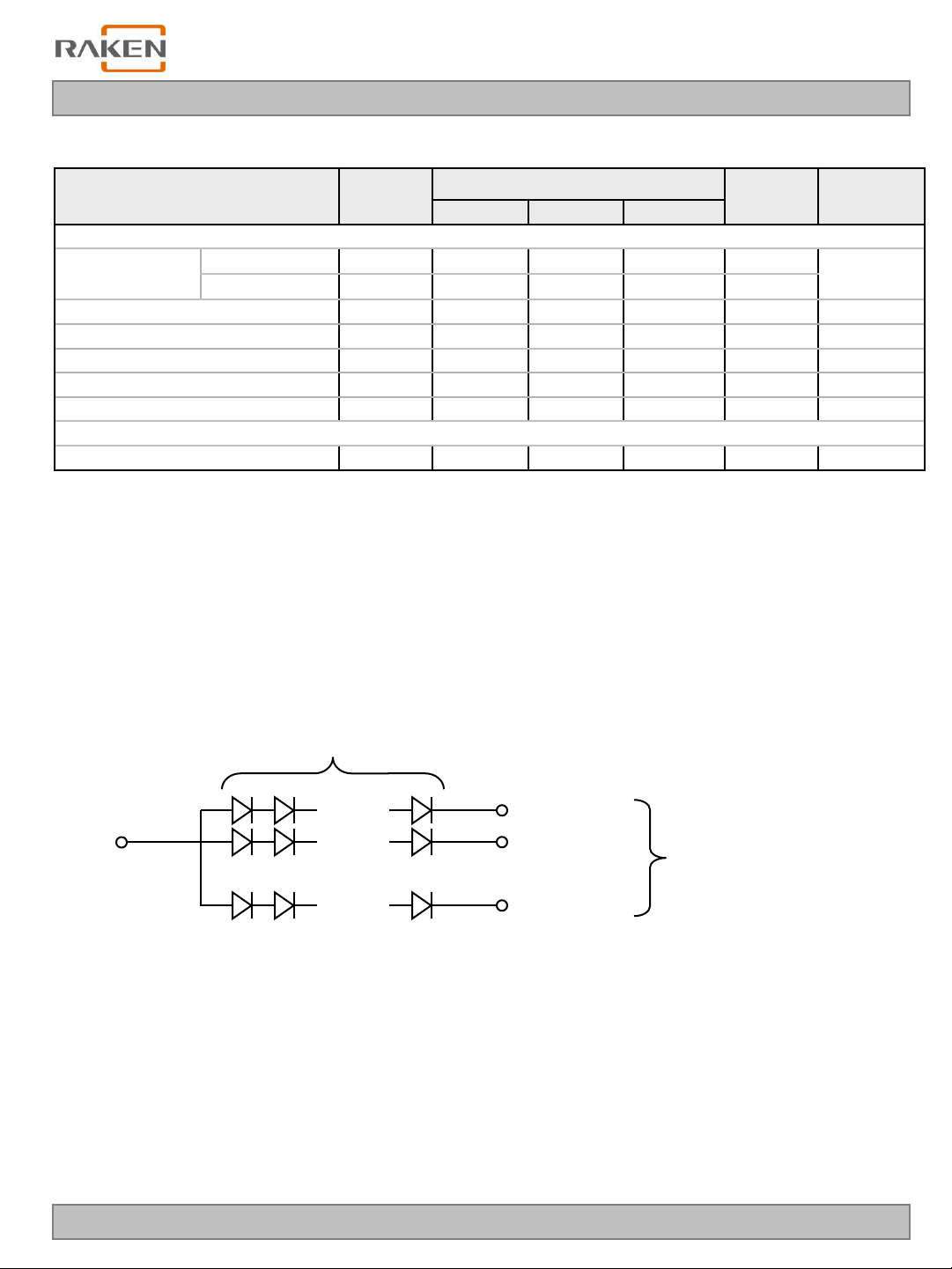

1. Electrical characteristics are based on LED Array specification.

2. Specified values are defined for a Backlight Assembly. (IBL :2 LED array/LCM)

3. Each LED array has one anode terminal and six cathode terminals.

The forward current(IF) of the anode terminal is 630mA and it supplies 105mA into six strings, respectively

9 (LED Pakage / 1string)

Anode

°° °

°° °

°° °

°° °

Cathode #1

Cathode #2

6 (LED String / 1 Array)

Cathode #6

4. The forward voltage(VF) of LED array depends on ambient temperature (Appendix-V)

5. ΔVFmeans Max VF-Min VFin one Backlight. So V

variation in a Backlight isn‟t over Max. 1.7V

F

6. Maximum level of power consumption is measured at initial turn on.

Typical level of power consumption is measured after 1hrs aging at 25 2°C.

7. The life time(MTTF) is determined as the time at which brightness of the LED is 50% compared to that of

initial value at the typical LED current on condition of continuous operating at 25 2°C, based on duty 100%.

8. The reference method of burst dimming duty ratio.

It is recommended to use synchronous V-sync frequency to prevent waterfall

(Vsync * 1 =Burst Frequency)

Though PWM frequency is over 182Hz (max252Hz), function of backlight is not affected.

Ver. 1.0

7/40

LC470EUF

Product Specification

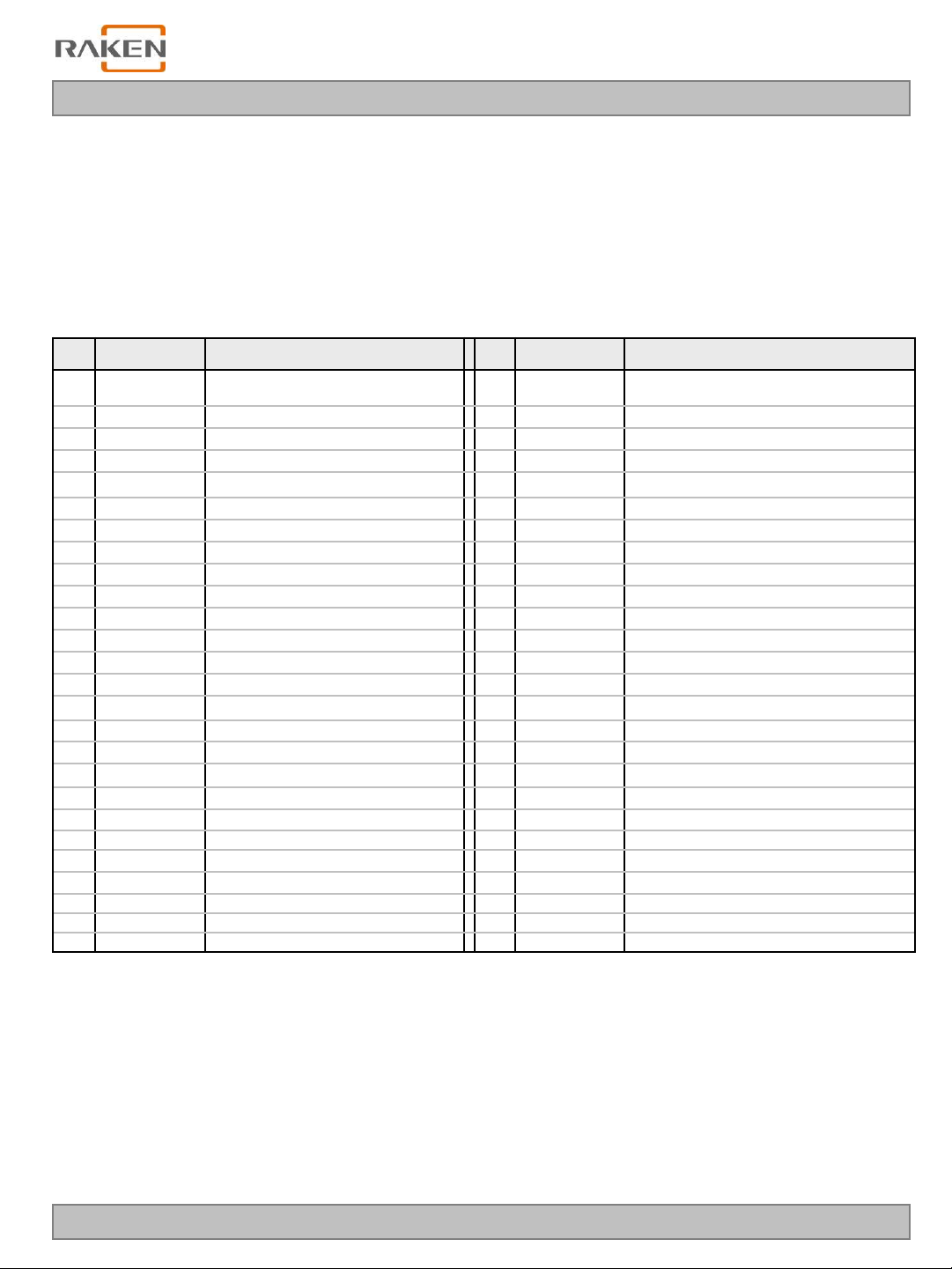

3-2. Interface Connections

This LCD module employs two kinds of interface connection, 51-pin connector and 41-pin connector are used

for the module electronics and Two 8-pin connectors are used for the integral backlight system.

3-2-1. LCD Module

- LCD Connector(CN1): FI-RE51S-HF(manufactured by JAE)

- Mating Connector : FI-R51HL(JAE) or compatible

Table 4-1. MODULE CONNECTOR(CN1) PIN CONFIGURATION

No Symbol Description No Symbol Description

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

PCID_EN

NC

NC

SDA SDA (For Local Dimming)

SCL SCL (For Local Dimming)

NC

LVDS Select

NC

NC

NC

GND

R1AN

R1AP

R1BN

R1BP

R1CN

R1CP

GND

R1CLKN

R1CLKP

GND

R1DN

R1DP

R1EN

R1EP

NC or GND

„H‟ : PCID Enable, „L‟ or NC: PCID

Disable (3D Mode Only)

No Connection (Note 4)

No Connection (Note 4)

No Connection (Note 4)

‘H’ =JEIDA , ‘L’ or NC = VESA

No Connection (Note 4)

No Connection (Note 4)

No Connection (Note 4)

Ground

FIRST LVDS Receiver Signal (A-)

FIRST LVDS Receiver Signal (A+)

FIRST LVDS Receiver Signal (B-)

FIRST LVDS Receiver Signal (B+)

FIRST LVDS Receiver Signal (C-)

FIRST LVDS Receiver Signal (C+)

Ground

FIRST LVDS Receiver Clock Signal(-)

FIRST LVDS Receiver Clock Signal(+)

Ground

FIRST LVDS Receiver Signal (D-)

FIRST LVDS Receiver Signal (D+)

FIRST LVDS Receiver Signal (E-)

FIRST LVDS Receiver Signal (E+)

No Connection or Ground

27

Bit Select

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

- - -

R2AN

R2AP

R2BN

R2BP

R2CN

R2CP

GND

R2CLKN

R2CLKP

GND

R2DN

R2DP

R2EN

R2EP

NC or GND

NC or GND

GND Ground (Note 6)

GND Ground

GND Ground

NC No connection

VLCD Power Supply +12.0V

VLCD Power Supply +12.0V

VLCD Power Supply +12.0V

VLCD Power Supply +12.0V

‘H’ or NC= 10bit(D) , ‘L’ = 8bit

SECOND LVDS Receiver Signal (A-)

SECOND LVDS Receiver Signal (A+)

SECOND LVDS Receiver Signal (B-)

SECOND LVDS Receiver Signal (B+)

SECOND LVDS Receiver Signal (C-)

SECOND LVDS Receiver Signal (C+)

Ground

SECOND LVDS Receiver Clock Signal(-)

SECOND LVDS Receiver Clock Signal(+)

Ground

SECOND LVDS Receiver Signal (D-)

SECOND LVDS Receiver Signal (D+)

SECOND LVDS Receiver Signal (E-)

SECOND LVDS Receiver Signal (E+)

No Connection or Ground

No Connection or Ground

Note

Ver. 1.0

1. All GND (ground) pins should be connected together to the LCD module‟s metal frame.

2. All VLCD(power input) pins should be connected together.

3. All Input levels of LVDS signals are based on the EIA 644 Standard.

4. #2~#3,#6 & #8~#10 NC (No Connection): These pins are used only for LGD (Do not connect)

5. LVDS pin (pin No. #24,25,40,41) are used for 10Bit(D) of the LCD module.

If used for 8Bit(R), these pins are no connection.

6. Specific pin No. #44 is used for “No signal detection” of system signal interface.

It should be GND for NSB (No Signal Black) while the system interface signal is not.

If this pin is “H”, LCD Module displays AGP (Auto Generation Pattern).

7. Specific pin (pin No. #4, #5) is used for Controlling Local Dimming register in the LCM Module

8/40

Product Specification

- LCD Connector(CN2): FI-RE41S-HF(manufactured by JAE)

- Mating Connector : FI-RE41HL(JAE) or compatible

Table 4-2. MODULE CONNECTOR(CN2) PIN CONFIGURATION

No Symbol Description No Symbol Description

1

2

3

4 NC

5

6

7

8

9

10

11

12

13 RB3P

14

15

16

17

18 RCLK3P

19

20

21

NC

NC

NC

NC

NC

NC

NC

GND

RA3N

RA3P

RB3N

RC3N

RC3P

GND

RCLK3N

GND

RD3N

RD3P

No connection 22

No connection 23

No connection 24 GND Ground

No connection

No connection

No connection 27

No connection 28

No connection 29 RB4P

Ground

THIRD LVDS Receiver Signal (A-)

THIRD LVDS Receiver Signal (A+)

THIRD LVDS Receiver Signal (B-)

THIRD LVDS Receiver Signal (B+)

THIRD LVDS Receiver Signal (C-)

THIRD LVDS Receiver Signal (C+)

Ground

THIRD LVDS Receiver Clock Signal(-)

THIRD LVDS Receiver Clock Signal(+)

Ground

THIRD LVDS Receiver Signal (D-)

THIRD LVDS Receiver Signal (D+)

25 GND Ground

26

30

31

32

33

34 RCLK4P

35

36

37

38

39

40 GND Ground

41 GND Ground

-

RE3N

RE3P

RA4N

RA4P

RB4N

RC4N

RC4P

GND

RCLK4N

GND

RD4N

RD4P

RE4N

RE4P

THIRD LVDS Receiver Signal (E-)

THIRD LVDS Receiver Signal (E+)

FORTH LVDS Receiver Signal (A-)

FORTH LVDS Receiver Signal (A+)

FORTH LVDS Receiver Signal (B-)

FORTH LVDS Receiver Signal (B+)

FORTH LVDS Receiver Signal (C-)

FORTH LVDS Receiver Signal (C+)

Ground

FORTH LVDS Receiver Clock Signal(-)

FORTH LVDS Receiver Clock Signal(+)

Ground

FORTH LVDS Receiver Signal (D-)

FORTH LVDS Receiver Signal (D+)

FORTH LVDS Receiver Signal (E-)

FORTH LVDS Receiver Signal (E+)

LC470EUF

Note : 1. All GND (ground) pins should be connected together to the LCD module‟s metal frame.

2. LVDS pin (pin No. #22,23,38,39) are used for 10Bit(D) of the LCD module.

If used for 8Bit(R), these pins are no connection.

CN1 CN2

#1 #51 #1 #41

CN1 CN2

#1 #51

#1 #41

Rear view of LCM

Ver. 1.0

9/40

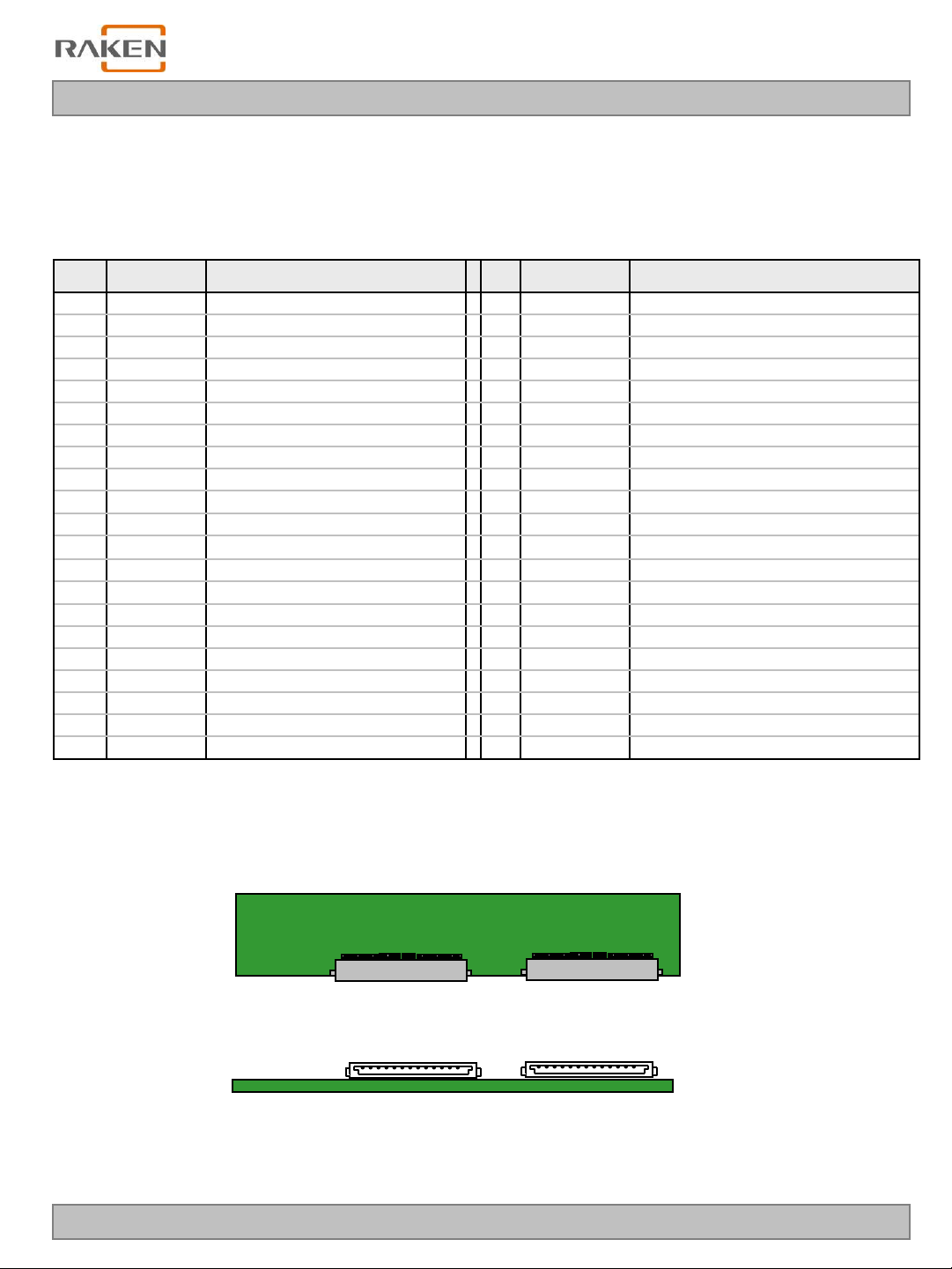

3-2-2. Backlight Module

LC470EUF

Product Specification

[ CN201 ]

1) LED Array assy Connector (Plug)

: HS100-L08N-N62 (black color, manufactured by UJU)

2) Mating Connector (Receptacle)

: IS100-L08T-C46 (black color, manufactured by UJU)

[ CN202 ]

1) LED Array assy Connector (Plug)

: HS100-L08N-N62-A (natural color, manufactured by UJU)

2) Mating Connector (Receptacle)

: IS100-L08T-C46-A (natural color, manufactured by UJU)

Table 5. BACKLIGHT CONNECTOR PIN CONFIGURATION(CN201,CN202)

No Symbol

1

2

3

4

5

6

7

8

L1 Cathode

L2 Cathode

L3 Cathode

L4 Cathode

L5 Cathode

L6 Cathode

N.C

Anode_L

Description

LED Input Current

LED Output Current

LED Output Current

LED Output Current

LED Output Current

LED Output Current

Open

LED Input Current for

L1~L6

Note

No Symbol

1

2

3

4

5

6

7

8

Anode_R

N.C

R6 Cathode LED Output Current

R5 Cathode LED Output Current

R4 Cathode LED Output Current

R3 Cathode LED Output Current

R2 Cathode LED Output Current

R1 Cathode LED Output Current

Description

LED Input Current for

R1~R6

Open

Note

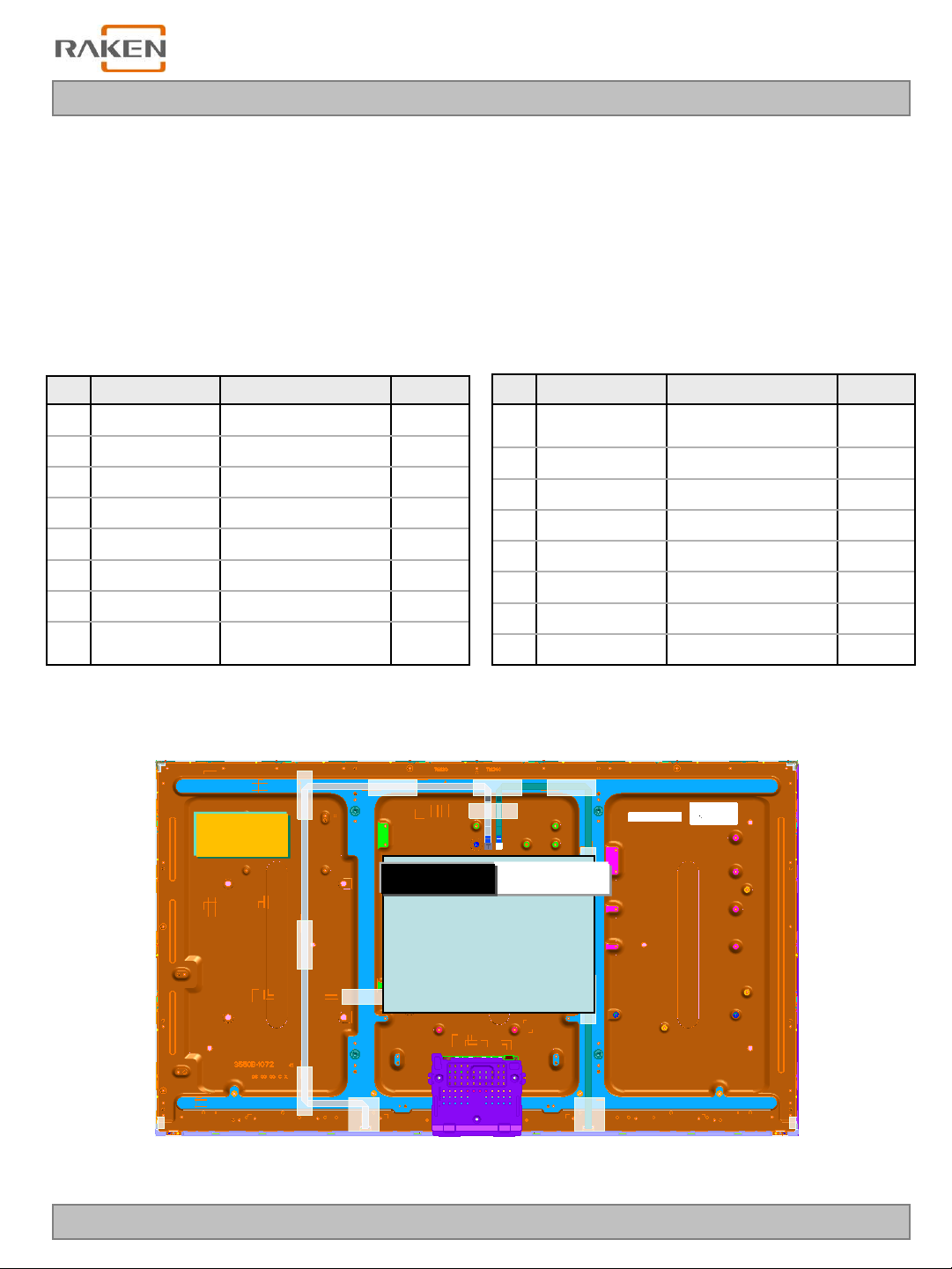

◆ Rear view of LCM

Ver. 1.0

Rear

87654321

CN201(B) CN202(W)

Buyer LPB

87654321

10/40

LC470EUF

Product Specification

3-3. Signal Timing Specifications

Table 6 shows the signal timing required at the input of the LVDS transmitter. All of the interface signal

timings should be satisfied with the following specification for normal operation.

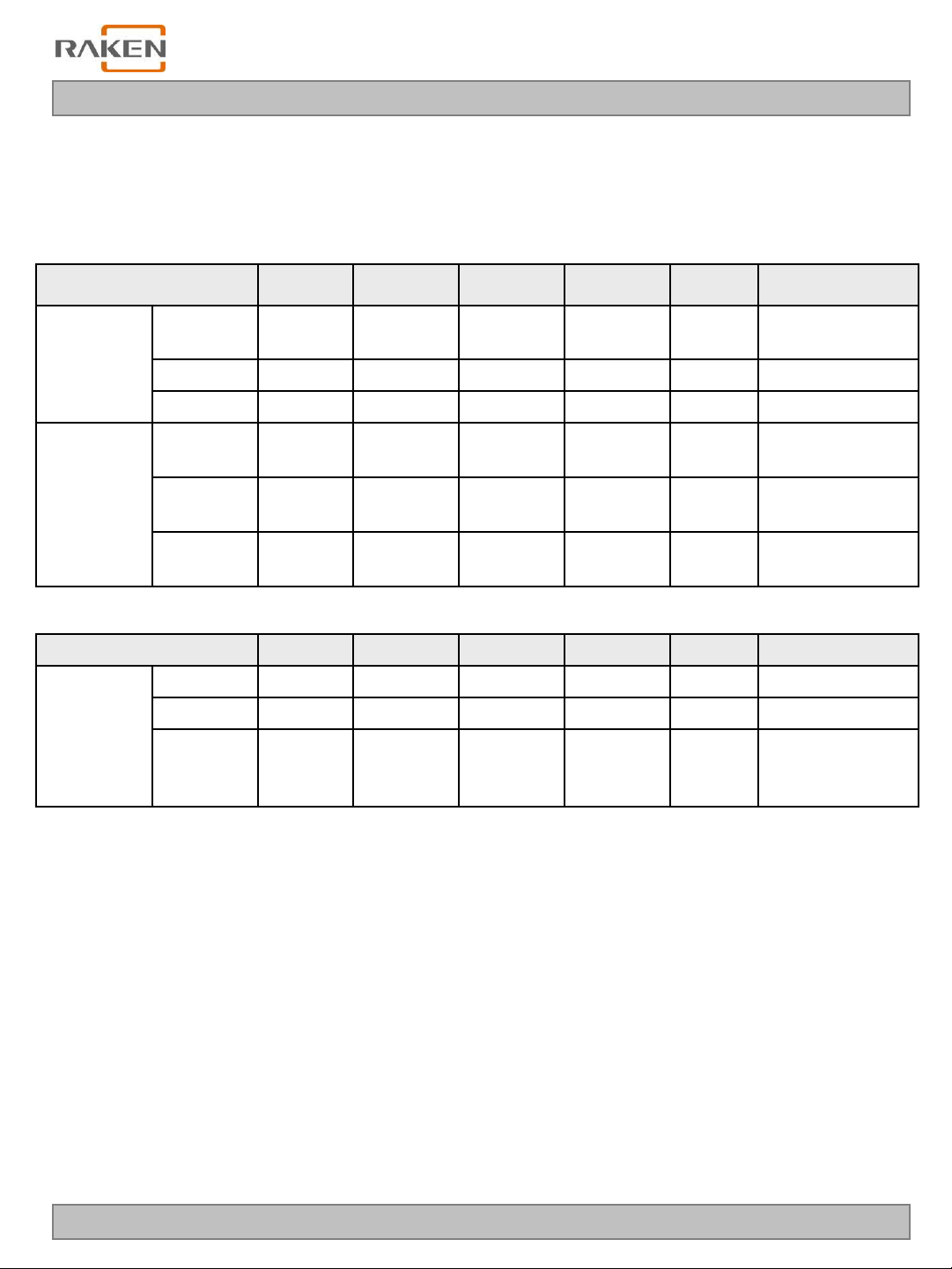

Table 6. TIMING TABLE (DE Only Mode)

ITEM Symbol Min Typ Max Unit Note

Horizontal

Vertical

Frequency

Display

Period

Blank tHB 40 70 200 tCLK 1

Total tHP 520 550 680 tCLK

Display

Period

Blank tVB

Total tVP

ITEM Symbol Min Typ Max Unit Note

DCLK fCLK 66.97 74.25 78.00 MHz

Horizontal fH 121.8 135 140 KHz 2

Vertical fV

tHV 480 480 480 tCLK 1920 / 4

tVV 1080 1080 1080 Lines

20

(228)

1100

(1308)

108

(95)

45

(270)

1125

(1350)

120

(100)

86

(300)

1166

(1380)

122

(104)

Lines 1

Lines

Hz

NTSC

(PAL)

2

Note:1. The input of HSYNC & VSYNC signal does not have an effect on normal operation (DE Only Mode).

If you use spread spectrum of EMI, add some additional clock to minimum value for clock margin.

2. The performance of the electro-optical characteristics may be influenced by variance of the vertical

refresh rate and the horizontal frequency

※ Timing should be set based on clock frequency.

Ver. 1.0

11/40

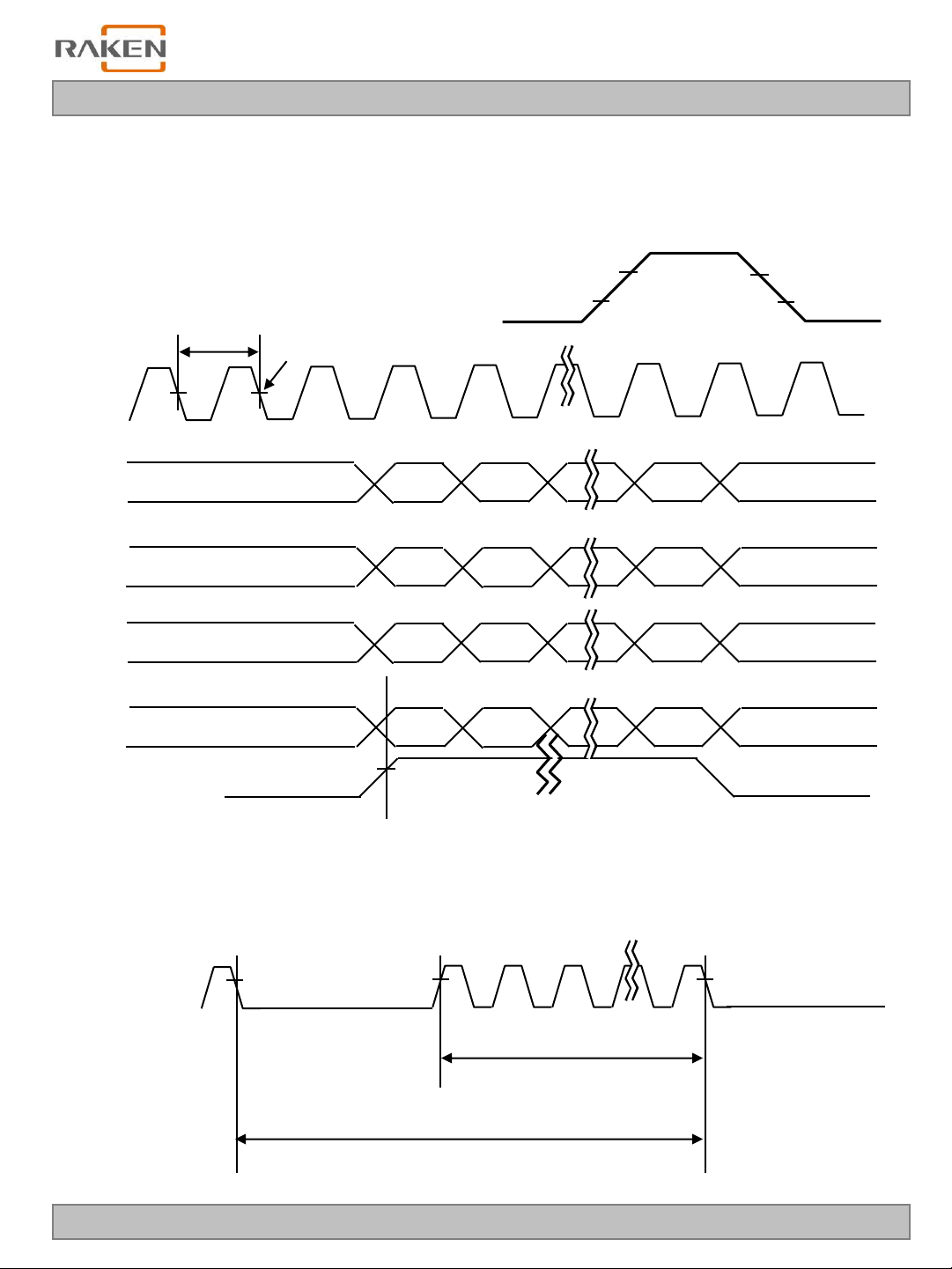

3-4. LVDS Signal Specification

3-4-1. LVDS Input Signal Timing Diagram

LC470EUF

Product Specification

DCLK

First data

Second data

Third data

Forth data

DE(Data Enable)

tCLK

0.5 VDD

Invalid data

Invalid data

Invalid data

Invalid data

DE, Data

Valid data

Pixel 0

Valid data

Pixel 1

Valid data

Pixel 2

Valid data

Pixel 3

Pixel 4

Pixel 5

Pixel 6

Pixel 7

0.7VDD

0.3VDD

Invalid data

Invalid data

Invalid data

Invalid data

DE(Data Enable)

Ver. 1.0

* tHB = tHFP + tWH +tHBP

* tVB = tVFP + tWV +tVBP

1 1080

tVV

tVP

12/40

Loading...

Loading...