LG KE990d Service Manual

Date: April, 2008 / Issue 1.0

Service Manual

Model : KE990d

Service Manual

KE990d

Internal Use Only

Z3X-BOX.COM

- 153 -

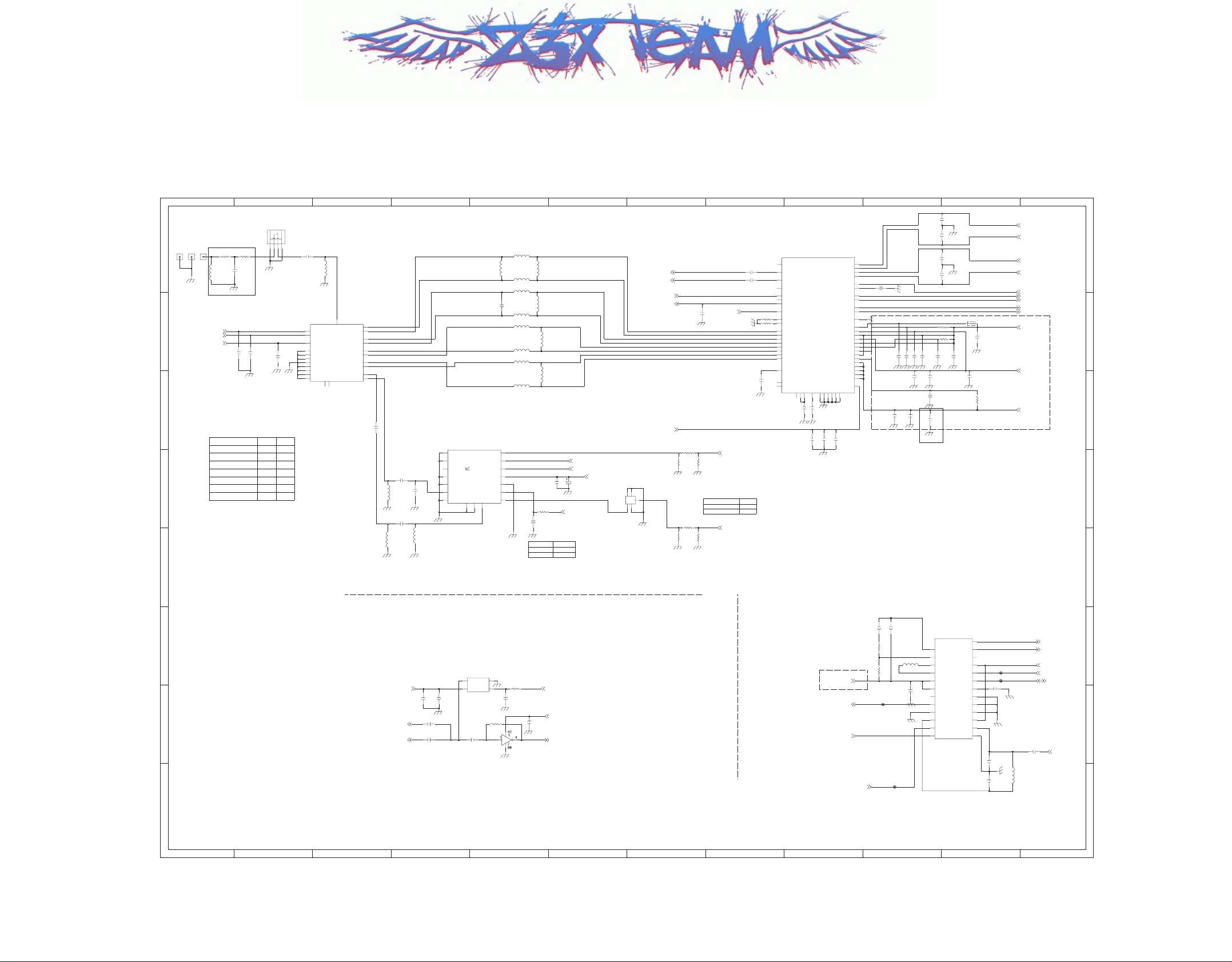

7. CIRCUIT DIAGRAM

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

1

1 7

ANT1000ANT101 ANT102

A

A

B

B

ANT_SEL0

ANT_SEL1

VREG_RF_SMPS

L100

0

C104

C102

NA

NA

C

ANTENNA SWITCH MODULE LOGIC

GSM 850/GSM 900 TX

GSM 1800/GSM 1900 TX

GSM 850 RX

GSM 900 RX

GSM 1800 RX

D

D

GSM 1900 RX

WCDMA

2

2

KMS-518

SW100

ACG1

L101

C113

1000p

G2

120pC101

L102

22nH

PQ

11

19

VC1

ANT

20

VC2

21

VDD

9

GND1

C114

1000p

12

1000p

13

14

16

18

22

10

C195

GSM1800_RX1

GND2

GSM1800_RX2

GND3

GSM1900_RX1

GND4

GSM1900_RX2

GND5

GND6

GND7

GSM1800_1900_TX

NC123NC2

GSM850_900_TX

GND8

LMSP43QA-538

24

FL100

ANT_SEL1

ANT_SEL0

LOW

HIGH

HIGH

LOW

LOW

LOW

LOW

LOW

LOW

LOW

LOW

LOW

LOW

LOW

GSM

E

E

3

3

GSM850_RX1

GSM850_RX2

GSM900_RX1

GSM900_RX2

4

4 8 12

850GSM

EGSM

1

2

3

4

5

6

7

8

15

17

C717

4.7p

6.8pC136

C138

L112

NA

15nH

C146 2.7p

C142

L113

5.6nH

5.6nH

DCS

PCS

14

GND6

13

GND5

12

VCC

U101

11

TQM7M5003

GND4

10

GND3

9

GSM_OUT

8

GND8

GND2

17

GND7

16

DCS_PCS_IN

TX_EN

VBATT

GND1

VRAMP

DCS_PCS_OUT

GSM_IN

15

5

5

L199 27nH

L198

L109 NA

L111 NA

L105 6.8nH

L108

27nH

6.8nHL103

6.8nHL106

6.8nH

L197

47nH

L110

NA

R117 2.2K

C143

68p

GSM_PA_BAND

LOW

HIGH

L104

18nH

L107

12nH

22nH

C719

C718

NA

1

2

BS

3

4

5

6

7

C137

1u

MODE

GSM850/900

DCS/PCS

GSM_PA_BAND

GSM_PA_EN

C135

33u

GSM_PA_RAMP

6

6

+VPWR

3

G12G2

G3

O1

4

EFCH836MTDB1

FL101

IN

5

1

DCS_PCS_TX

GSM_TX

TX_ON

DAC_REF

VREG_MSMP_2.7V

7

C116

12p

R111

68

R112

R113

10 dB

100

100

R114

68

R118

R119

100

100

10dB

SSBDT_RTR

DCS_PCS_TX

GSM_TX

8

46

DA_HB1_OUT

44

6pC106

DA_HB2_OUT

5p

C108

43

DA_LB1_OUT

42

DA_LB2_OUT

24

RF_ON

56

VCNTRL

54

DAC_REF

14

SBDT

R100

(1%)

12K

3

R_BIAS1

27

R_BIAS2

(1%)

R101

30

680

GCELL_INN

31

GCELL_INP

32

EGSM_INP

33

EGSM_INN

38

DCS_INP

39

DCS_INN

36

GPCS_INP

37

GPCS_INN

26

WLNA_IN

C197

21

22p

TEST

55

OPEN

9

U100

RTR6275-CHARTERED

V_TUNE2

WLNA_OUT

WMIX_INN

WMIX_INP

GND1

1

18

29

35

34

C199

22p

NA C112

VTUNE-Connected directly to GND

C132

0.01u

GND22GND3

22

C133

22p

PWD_DET_IN

GND4

GND5

25

23

C134

1000p

TX_QP

TX_QN

V_TUNE1

RX_QP

RX_QN

VDDA1

VDDA2

VDDA3

VDDA4

VDDA5

VDDA6

VDDA7

VDDA8

VDDA9

VDDA10

VDDA11

VDDA12

VDDA13

VDDA14

PGND

57

TX_IP

TX_IN

TCXO

RX_IP

RX_IN

VDDM

51

50

53

52

7

5

VTUNE-Connected directly to GND

12

13

10

11

40

4

6

8

9

15

16

19

20

28

49

48

47

45

41

17

10

10

C100

180p

C103

180p

C107

180p

C110

3300p

C111

C131

100p

180p

R107 2.7

0.1u

0.1uC119

C120 0.1u

C123 0.1u

C121 0.1u

C122

C127

C126

100p

22p

C128

22p

C129

0.1u

22u

C130

near to 48pin

11

119

RX_IP

RX_IM

RX_QP

R102

5.1R104

0

22u

C118

0.1uC124

C125

1u

10

R109

RX_QM

VREG_RF_SMPS

VREG_SYNTH_2.6V

VREG_RF_SMPS

TX_IP

TX_IM

TX_QP

TX_QM

RTR6275_TCXO

12

A

A

B

B

CC

C

SMPS circuit for RF

D

D

E

E

FM RADIO

C151

C150

0.01u

0.1u

F F

F

G

G

H

H

1

1

22

3

3

TCXO_PM

RTR6275_TCXO

TCXO

Z3X-BOX.COM

X100

GNDOUT

3

VCC4VCONT

19.2MHz

C140

C139

1000p

0.1u

C144

1000p

C147 1000p

C148

8200p

TC7SH04FS

4

4

2

1

U102

Rev. 1.1

100ohmR115

C141

0.01u

100KR120

5

TRK_LO_ADJVREG_TCXO_2.85V

VREG_BT_2.85V

C145

1000p

TCXO_BT

6 11

7

7

8

VREG_MMC_3.0V

FM_INTX

FM_BUSEN

9

9

SLEEP_CLK

10K

R121

100K

R122

TP102

TP103

10

10

L120

47nH

C158

1u

U103 TEA5766UK

VAFR

A1

VAFL

CPOUT

A2 E4

LOOPSW

MPXOUT

A3

VREFDIG

LO1

A4

LO2

CLOCK

A5

VCCVCO

DATA

A6

TMUTE

VCC

B1

SWPORT

INTX

AGND

RFIN1

FREQIN

BUSEN

DGND2

DGND1

RFGND

ISS

VDD

RFIN2

B2

B5

B6

C1

C2

E6

E5

E3

TP100

E2

TP101

E1

C157

D6

0.1u

D5

D3

D2

D1

C6

C5

C171

56p

C172

27p

FM_AUDIO_R

FM_AUDIO_L

VREG_MSMP_2.7V

I2C_SCL

C166

100p

L127

100nH

118

I2C_SDA

FM_ANT

126

12

F

G

G

H

H

- 154 -

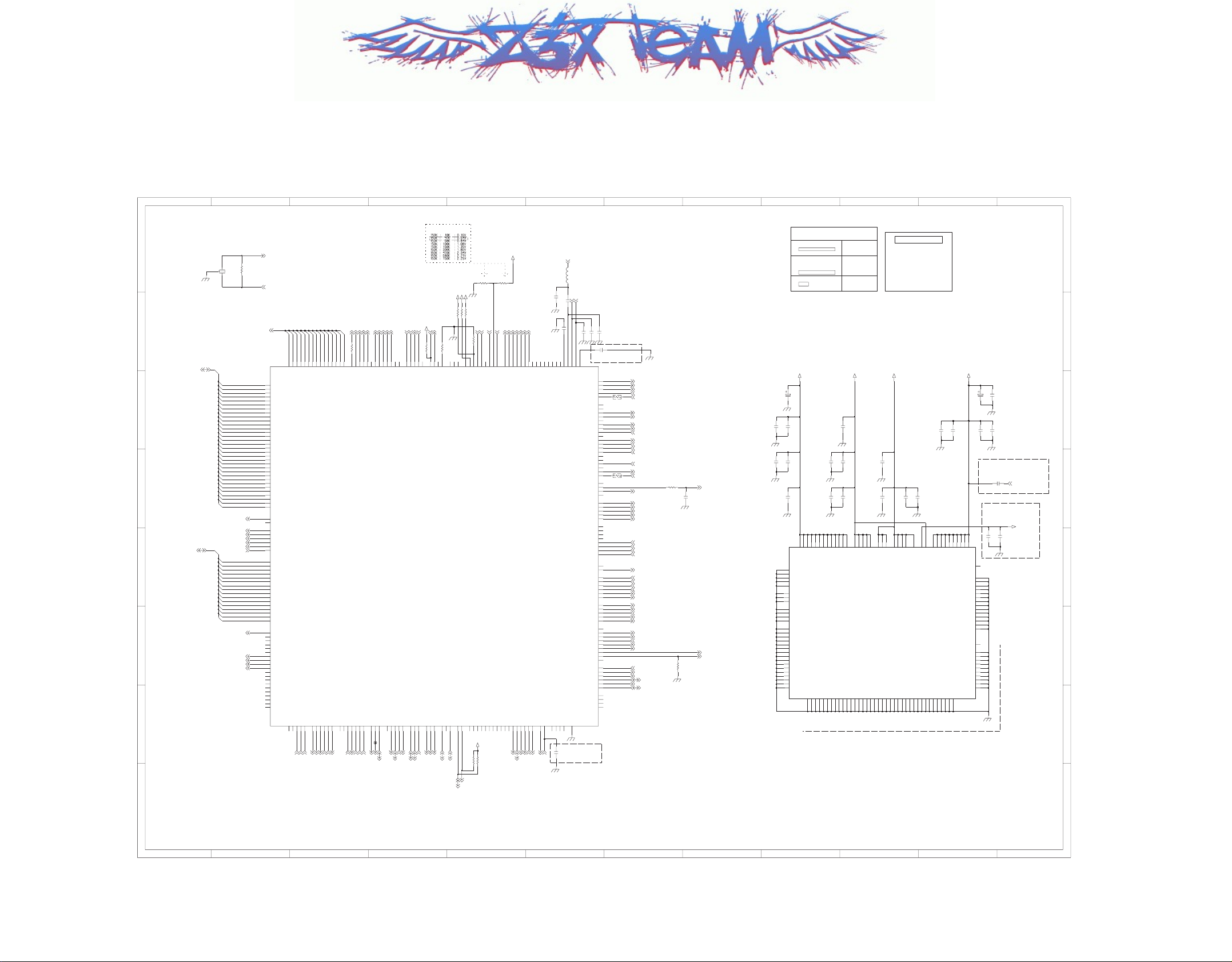

7. CIRCUIT DIAGRAM

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

1 910

21

3 910

43

5

52

6

6

7

7

PCB_Rev_ADC

USB 48M CLK

A

B

B

SDRAM_DATA[0:31]

C

C

D

D

EBI2_DATA[0:15]

E

E

F

F

G

G

H

H

( +/- 2500ppm for USB Peripheral )

ICRT20S48M0X514CR X200

2

MMP_PWR_EN

EBI2_ADDR[14]

EBI2_ADDR[13]

EBI2_ADDR[12]

EBI2_ADDR[11]

13

48MHz

SDRAM_DATA[31]

SDRAM_DATA[30]

SDRAM_DATA[29]

SDRAM_DATA[28]

SDRAM_DATA[27]

SDRAM_DATA[26]

SDRAM_DATA[25]

SDRAM_DATA[24]

SDRAM_DATA[23]

SDRAM_DATA[22]

SDRAM_DATA[21]

SDRAM_DATA[20]

SDRAM_DATA[19]

SDRAM_DATA[18]

SDRAM_DATA[17]

SDRAM_DATA[16]

SDRAM_DATA[15]

SDRAM_DATA[14]

SDRAM_DATA[13]

SDRAM_DATA[12]

SDRAM_DATA[11]

SDRAM_DATA[10]

SDRAM_DATA[9]

SDRAM_DATA[8]

SDRAM_DATA[7]

SDRAM_DATA[6]

SDRAM_DATA[5]

SDRAM_DATA[4]

SDRAM_DATA[3]

SDRAM_DATA[2]

SDRAM_DATA[1]

SDRAM_DATA[0]

MMP_CS_N

NAND_CLE

NAND_CS_N

EBI2_OE_N

EBI2_WE_N

NAND_ALE

NAND_READY

EBI2_DATA[15]

EBI2_DATA[14]

EBI2_DATA[13]

EBI2_DATA[12]

EBI2_DATA[11]

EBI2_DATA[10]

EBI2_DATA[9]

EBI2_DATA[8]

EBI2_DATA[7]

EBI2_DATA[6]

EBI2_DATA[5]

EBI2_DATA[4]

EBI2_DATA[3]

EBI2_DATA[2]

EBI2_DATA[1]

EBI2_DATA[0]

R200

1M

SDRAM_ADDR[0:14]

USB_XTAL_IN

USB_XTAL_OUT

SDRAM_ADDR[0]

V1

T8

A1_22

T6

A1_24_GPIO79

A1_21

T4

A1_20

R8

A1_19

T2

A1_18

T1

A1_17

R6

A1_16

R4

A1_15

W4

GPIO_74

V6

GPIO_73

Y2

GPIO_72

Y1

GPIO_71

E1

GPIO_70

R11

GPIO_69

V4

GPIO_68

U6

GPIO_67

L6

SDRAM1_D15

L8

SDRAM1_D14

K4

SDRAM1_D13

J1

SDRAM1_D12

K6

SDRAM1_D11

J2

SDRAM1_D10

J4

SDRAM1_D9

P4

SDRAM1_D8

H4

SDRAM1_D7

G2

SDRAM1_D6

J6

SDRAM1_D5

AB4

SDRAM1_D4

D1

SDRAM1_D3

AB2

SDRAM1_D2

D2

SDRAM1_D1

E2

SDRAM1_D0

AC15

XMEM2_CS_N1

AF14

LCD_CS_N_GPIO38

AF10

UB2_N

W14

XMEM2_CS_N0

AF7

OE2_N

AF4

WE2_N

AE10

LB2_N_A2_0

T14

NAND2_FLASH_READY_GPIO33

AA10

D2_15

AC9

D2_14

W10

D2_13

AA9

D2_12

AE7

D2_11

AC8

D2_10

W9

D2_9

AA8

D2_8

AC7

D2_7

AF5

D2_6

AA7

D2_5

AE5

D2_4

AC6

D2_3

AE4

D2_2

AF3

D2_1

AC5

D2_0

AF13

A2_20_GPIO34

AA14

A2_19

T13

A2_18

AC14

A2_17

AE14

A2_16

W13

A2_15

AC13

A2_14

AA13

A2_13

AF12

A2_12

AE12

A2_11

AC12

A2_10

AA12

A2_9

W12

A2_8

T12

A2_7

AC11

A2_6

AA11

A2_5

AC10

A2_4

W11

A2_3

AF9

A2_2

AE9

A2_1

KEYSENSE4_N_GPIO48

U21

SDRAM_ADDR[1]

SDRAM_ADDR[2]

SDRAM_ADDR[3]

SDRAM_ADDR[4]

SDRAM_ADDR[5]

SDRAM_ADDR[6]

M4

N11

N8

L1

L4

A1_3M8A1_4

A1_5

A1_6

A1_1

A1_2

KEYSENSE0_N_GPIO62

KEYSENSE1_N_GPIO63

KEYSENSE2_N_GPIO46

KEYSENSE3_N_GPIO47

GPIO45A4GPIO49

P19

R21

D14

R23

KEY_ROW[2]

KEY_ROW[1]

KEY_ROW[0]

MMP_RESET_IN_N

SDRAM_ADDR[7]

SDRAM_ADDR[8]

SDRAM_ADDR[9]

SDRAM_ADDR[10]

SDRAM_ADDR[11]

SDRAM_ADDR[12]

SDRAM_ADDR[13]

SDRAM_ADDR[14]

N6

N1

P1

P2

P8

P11

A1_7N2A1_8

A1_9

A1_10

A1_11P6A1_12

A1_13

UART1_RFR_N_PA_POWER_CTL_M_GPIO98

GPIO50A7GPIO51

GPIO52

GPIO53

F9

B7

L12

P16

P21

D10

WM_EN

KEY_COL[1]

KEY_COL[0]

WHEEL_SW_L

WHEEL_SW_R

SDRAM_CLK

SDRAM_RAS_N

SDRAM_CLK_EN

SDRAM_CAS_N

SDRAM_CS_N

R207 51

Y4

AA2

K8

U8

N4

G1

AB1

A1_14

XMEM1_HWAIT_N

SDRAM1_CLK_EN

ROM1_CLK_SDRAM1_CLK

ROM1_ADV_N_SDRAM1_RAS_N

XMEM1_CS_N2_SDRAM1_CS_N0

XMEM1_LWAIT_N_SDRAM1_CAS_N

UART1_CTS_N_GPIO97

UART1_DP_RX_DATA_GPIO96

UART1_DP_TX_DATA_GPIO95

UART2_RFR_N_GPIO91

GPIO39

GPIO44

GPIO64

F4

F7

D8

G6

L26

F14

M23

TP200

USIM_CLK

UART_TXD

UART_RXD

CAM_MODE2_N

CAM_COVER_DET

TOUCH_PENIRQ_N

SDRAM_DQM[0]

SDRAM_DQM[1]

SDRAM_DQM[2]

SDRAM_WE_N

SDRAM_DQM[3]

BUFF_TCXO

M6

W6

D18

V2

U4

V8

L2

TCXO

OE1_N

XMEM1_CS_N0

LB1_N_SDRAM1_DQM0

UB1_N_SDRAM1_DQM1

WE1_N_SDRAM1_WE_N

A1_23_SDRAM1_DQM2_GPIO78

A1_25_SDRAM1_DQM3_GPIO75

UART3_DP_TX_DATA_GPIO84

UART2_CTS_N_GPIO90

UART2_DP_TX_DATA_GPIO88

UART3_CTS_N_GPIO86

UART3_DP_RX_DATA_GPIO85

GPIO40

GPIO42

E4

D6

D7

L23

M21

M19

PS_HOLD

PM_INT_N

USIM_RST_N

USIM_DATA

TOUCH_I2C_SCL

TOUCH_I2C_SDA

VREG_MSMP_2.7V

USB_XTAL_IN

SLEEP_CLK

USB_XTAL_OUT

RESOUT_N

RESET_IN_N

NA

R209

R208 100K

A10

B10

AE17

A16

B16

F13

F11

AA4

RESIN_N

WDOG_EN

RESOUT_N

USB_XTAL48_IN

SLEEP_XTAL_IN

RESOUT_N_EBI1

USB_XTAL48_OUT

SLEEP_XTAL_OUT

U200-1

MSM6280_A

USB_DAT_VP

USB_OE_TP_N

USB_SE0_VM

SBST

MMC_CMD_GPIO30

MMC_DATA_SDCC_DAT0_GPIO32

MMC_CLK_SDCC_CLK_GPIO31

L14

H14

N26

N25

N23

H26

M16

USB_OE_N

USB_SE0

USB_DAT

SSBDT_RTR

MSM_MICROSD_CLK

MSM_MICROSD_CMD

MSM_MICROSD_DATA[0]

SBDT

J23

VREG_MSME_1.8V

R203 NA

U23

T21

Y23

MODE0

MODE1

MODE2

SBCK

I2C_SDA_GPIO26

L21

K21

SSBDT_PM

I2C_SDA

VREG_MSMP_2.7V

51KR205

51KR204

AE21

I2C_SCL_GPIO27

N16

VREG_MSMP_2.7V

R217

2.2K

I2C_SCL

VREG_MSMP_2.7V

R201

R202

47K

150K

1%

1%

VREG_MSMP_2.7V

VBAT_TEMP

R206 100K

AE22

AD1

BOOT_MODE

BOOT_MODE2

BOOT_MODE3

AMUX_OUT

V21

AA23

HKAIN0

VBAT_SENSE

RMT_ADC

W21

V19

HKAIN1

HKAIN2

HKAIN3

RCV+

RCV-

MICBIAS

SPK_L

SPK_R

HP_R

HP_L

T15

AC18

AC17

Y21

AB23

W17

AA17

AF18

AE18

AA18

HPH_L

HPH_R

HKAIN4

HKAIN5

EAR1OP

EAR1ON

MICBIAS

AUXOUT

LINE_OP

LINE_ON

Z3X-BOX.COM

SYNTH1_GPIO41

RINGER_GPIO18

GPIO17

GPIO19

CAMIF_DATA0_GPIO83

CAMIF_DATA1_GPIO81

CAMIF_DATA2_AUX_TRST_N_GPIO54

CAMIF_DATA3_AUX_TCK_GPIO55

CAMIF_DATA4_AUX_TMS_GPIO56

CAMIF_DATA5_AUX_TDI_GPIO57

CAMIF_DATA6_AUX_TDO_GPIO58

CAMIF_DATA7_GPIO59

CAMIF_DATA8_GPIO60

CAMIF_DATA9_GPIO61

F20

CAMIF_HSYNC_GPIO15

CAMIF_PCLK_GPIO82

CAMIF_VSYNC_GPIO16

B3

J25

J26

J19

F16

L15

C25

D22

D20

D21

R218

2.2K

E23

K23

H23

K26

G21

LCD_BL_CTRL

CODEC_I2C_SCL

MMC_SELECT_N

CODEC_I2C_SDA

L19

EAR_SENSE_N

LIN_PWM_FREQ

MIC2P

L200

100nH

C200

MIC1P

MIC1N

0.1uC235

10p

0.1u

C236

C203 NA

AF20

AE20

AF21

AF22

AC21

AC22

AC20

AC19

AA19

LINE_L_IP

HPH_VREF

XMEM1_CS_N3_SDRAM1_CS_N1_GPIO77

PA_POWER_CTL

P25

AD26

GSM_PA_RAMP

AA20

AF19

AE19

MIC1P

MIC2P

AUXIP

MIC1N

AUXIN

MIC2N

CCOMP

SDCC_DAT1_GPIO99

LINE_L_IN

LINE_R_IP

LINE_R_IN

SDCC_DAT2_GPIO100

SDCC_DAT3_GPIO101

MDP_VSYNC_SECONDA_GPIO104

MDP_VSYNC_PRIMARY_GPIO105

WDOG_STB_SBCK1_GPIO0

SBDT1_GPIO1

PA_ON1_GPIO2

GRFC9_GPIO12

CAMCLK_PO_GP_MN_GPIO13

USB_RX_DATA_GPIO29

XMEM2_CS_N2_GPIO35

XMEM2_CS_N3_GPIO36

LCD_EN_GPIO37

SYNTH2_GPIO65

XMEM1_CS_N1_GPIO76

UART3_RFR_N_GPIO87

UART2_DP_RX_DATA_GPIO89

SYNTH0_GP_PDM0_GPIO92

SBST1_GPIO93

TX_AGC_ADJ

TRK_LO_ADJ

TCXO_EN_GPIO94

Q_OUT_N

I_OUT_N

DAC_REF

Q_IM_CH1

Q_IP_CH1

I_IM_CH1

I_IP_CH1

Q_IM_CH0

Q_IP_CH0

I_IM_CH0

I_IP_CH0

GP_PDM2_PA_RAN_GE1

GP_PDM1_PA_RAN_GE0

AUX_PCM_CLK_GRFC14_GPIO80

AUX_PCM_DIN_GRFC13_GPIO14

AUX_PCM_DOUT_GRFC12_GPIO103

AUX_PCM_SYNC_GRFC11_GPIO102

TX_ON_GRFC10

GRFC8_GPIO11

GRFC7_GPIO10

GRFX6_GPIO9

GRFC5_AUX_SBST_GPIO8

GRFC4_AUX_SBCK_GPIO7

GRFC3_GPIO6

GRFC2_GPIO5

GRFC1_AUX_SBDT_GPIO4

GRFC0_GPIO3

BT_CLK_GPIO25

BT_SBST_GPIO24

BT_SBCK_GPIO23

BT_SBDT_GPIO22

BT_TX_RX_N_GPIO21

BT_DATA_GPIO20

MDDIC_DATP

MDDIC_DATN

MDDIC_STBP

MDDIC_STBN

VDD_EF_USE

MDDIH_DATN

MDDIH_DATP

MDDIH_STBN

MDDIH_STBP

GSM_PA_DAC_REF

R16

B19

B20

A19

A20

If you are not Qfuse (security),

this pin can be grounded as in MSM6275

C232

Place near

0.1u

MSM pin AD26

10%

GSM_PA_PWR_CTL_REF

GPIO28

GPIO43

GPIO66

PA_ON0

Q_OUT

TRST_N

NAC204

C237 NA

0.1uC238

Place near

10%

MSM pin W18

(CODEC VSS)

F25

M25

M26

AE3

AD2

H25

F26

H11

D5

J21

A6

N19

W15

AA15

AE13

H9

B6

F8

AA1

Y6

L25

H6

F18

H18

H13

L13

F19

F17

A12

B12

A13

B13

I_OUT

F12

W23

V23

V25

W25

AA25

Y25

AB25

AC25

D17

H17

H15

D16

TCK

F15

TMS

D15

TDI

A17

TDO

H16

RTCK

K19

N21

G4

J8

H12

B4

T23

T19

D11

H10

F10

D9

A8

B8

G23

F23

E26

E25

H21

R19

A22

A23

B22

B23

R215 0

0R210

MSM_MICROSD_DATA[1]

MSM_MICROSD_DATA[2]

MSM_MICROSD_DATA[3]

LCD_MAKER_ID

LCD_VSYNC_OUT

LIN_INVERTER

LIN_MOTOR_EN

LCD_IF_MODE

USB_SELECT_N

CAM_MODE3_N

LCD_LDO_EN

MICROSD_DETECT

HOOK_SENSE_N

RMT_INT

HP_AMP_EN

LCD_RESET_N

MMP_INT_N

TCXO_EN

TX_QM

TX_QP

TX_IM

TX_IP

DAC_REF

RX_QM

RX_QP

RX_IM

RX_IP

LIN_PWM_MAG

JTAG_TRST_N

JTAG_TCK

JTAG_TMS

JTAG_TDI

JTAG_TDO

JTAG_RTCK

MMP_HPCM_CLK

MMP_HPCM_DI

MMP_HPCM_DO

MMP_HPCM_FSYNC

TX_ON

ANT_SEL1

ANT_SEL0

CAM_MODE1_N

FM_INTX

FM_BUSEN

BT_CLK

BT_SBST

BT_SBCK

BT_SBDT

BT_TX_RX_N

BT_DATA

2KR211

R213

NA

84

8 12

MODE

MODE2 MODE1 MODE0

0 0 0

0 1 0

BOOT_MODE2 BOOT_MODE

X 0

0 1

1 1

BOOT_MODE3

0

1

VREG_MSMC_1.2V

C239

4.7u

C210

C211

0.01u

0.01u

C217

C218

1000p

1000p

TRK_LO_ADJ

C223

33nF

GSM_PA_BAND

GSM_PA_EN

AF11

AF15

A18

W16

W18

W26

AB26

AC16

AC26

AD25

AF23

AF24

F1

K1

M1

R1

U1

AF6

R26

B17

A15

A9

A21

D13

D19

P26

U19

V26

C224

1u

C2

VSS_PAD1_0

VSS_PAD1_1

VSS_PAD1_2

VSS_PAD1_3

VSS_PAD1_4

VSS_PAD2_0

VSS_PAD2_1

VSS_PAD2_2

VSS_PAD3_0

VSS_PAD3_1

VSS_PAD3_2

VSS_PAD3_3

VSSA1

VSSA2

VSSA3

VSSA4

VSSA5

VSSA6

VSSA7

VSSA8

VSSA9

VSSA10

VSSA11

VSSA12

VSSA13

VSSA14

VSSA15

VSSA16

H2

W2

VDD_DIG_1

VDD_DIG_0

A1

VDD_DIG_2

VSS1

( Default Pull-Down)

Native, ARM JTAG

Native, MSM JTAG

NOR boot

8-bit, NAND boot

16-bit, NAND boot

Normal boot

Trusted boot

VREG_MSME_1.8V

C212

0.1u

C219

C220

0.01u

0.01u

C225

C226

1000p

1u

B14

B11

AE8

AE16

VDD_DIG_3

VDD_DIG_4

T25

G25

VDD_DIG_5

VDD_DIG_6

VDD_DIG_7

D25

B24

VDD_DIG_8

VDD_DIG_9

VDD_DIG_10

VDD_DIG_11

B5

VDD_DIG_12

AC2

w18 (Analog VSS guard ring for CODEC)

VSS5

VSS6

VSS7

VSS8

VSS9

VSS3

VSS4

VSS2

VSS10

VSS11

F6

B1

B2

A2

D4

F21

B25

B26

A26

D23

A25

K2

M2

AE6

F2

VDD_PAD1_1

VDD_PAD1_2R2VDD_PAD1_3U2VDD_PAD1_4

VDD_PAD2_0

VDD_PAD1_0

U200-2

MSM6280_B

VSS12H8VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

L11

L16

H19

K10

M12

M11

HKADC[0] - AMUX_OUT

HKADC[1] - VBATT_SENSE

HKADC[2] - HDET1

HKADC[3] - REMOTE_ADC

HKADC[4] - PCB_Rev_ADC

HKADC[5] - VBATT_TEMP

PMIC_AUXIN[1]

PMIC_AUXIN[2] - PA_THERM

VREG_MSMP_2.7V

C221

0.01u

C227

1000p

AE11

AE15

R25

K25

B15

VDD_PAD2_1

VDD_PAD2_2

VDD_PAD3_0

VDD_PAD3_1

VSS20

VSS21

VSS22

VSS23

VSS24

N12

N13

N14

M13

M14

M15

ADC

C228

C229

0.1u

0.1u

B18

VDD_PLL

VDD_PAD3_2B9VDD_PAD3_3A3VDD_PAD4_0

VSS26

VSS27

VSS28

VSS29

VSS30

VSS25

P12

P13

P14

P15

N15

for VSS_THERMAL

11

11 12

VREG_MSMA_2.6V

C213

C214

0.01u

0.01u

VSS32

D12

R14

P23

U25

VDDA1

VDDA2

(VDD_DAC_REF)

VSS33

VSS34

T11

R15

VDDA3

VSS35

AA16

U26

Y26

AA26

AE23

AE24

VDDA8

VDDA9

VDDA4

VDDA5

VDDA6

VDDA7

RESERVED

(PLLOUT_TEST)

VSS_DIG_0

VSS_DIG_1

VSS_DIG_2

VSS_DIG_3

VSS_DIG_4

VSS_DIG_5

VSS_DIG_6

VSS_DIG_7

VSS_DIG_8

VSS_DIG_9

VSS_DIG_10

VSS_DIG_11

VSS_DIG_12

VSS_DIG

VSS39

VSS41

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS36

VSS37W8VSS38

T16

W19

B21

VDD_MDDI

VSS31

R12

R13

(CAD : 10uF=>Input MSMA_2.6V)

C233

C234

10u

1u

C216

C215

0.1u

0.1u

2200p cap => place between

D12(VDDA1) and F12(DAC_REF)

C222

2200p

Near to B18 (VDD_PLL)

C230

0.1u

10%

AF17

VDDA10

C26

C1

H1

W1

AC1

AF8

AF16

T26

G26

D26

A24

A14

A11

A5

AC23

AA21

NC

AA6

AC4

AE1

AE2

AE25

AE26

AF1

AF2

AF25

AF26

DAC_REF

VREG_MSMA_2.6V

C231

0.01u

A

AA

B

B

C

C

D

D

E

E

F

F

G

G

H

H

1

1

2

43

3

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

122

- 155 -

7. CIRCUIT DIAGRAM

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

0.1uC318

HCS0N

HCS1N

HRDN

HWRN

HGINTN

HA11

HA12

HA13

HA14

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

NCSN

NALE

NCLE

NREN

NWEN

NRBN

ND0

ND1

ND2

ND3

ND4

ND5

ND6

ND7

ND15

SPICLK

SPICS

SPIDO

SPIDI

UARTTX

UARTRX

UARTRTS

UARTCTS

SCL

SDA

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

TVDATA

TVREF

FB300

1uC319

MMP_VDD_CORE_1.0V

D8

E10

AVDD_PLL

VDDCORE1F4VDDCORE2

XTALIN

VENBYPIN

VENBYPOUT

E13

E11

H14

MMP_XTAL_IN

4

J11

L7

VDDCORE4

VDDCORE3

XTALOUT

J14

MMP_XTAL_OUT

MMP_VDD_1.9V

VREG_MSMP_2.7V

R300 0

L6

D9

D10

VDDQ1D7VDDQ2

VDD_PMU

AVSS_PLL

GND1

F6

F11

H4

G4

VDD_HOST

VDD_SERIAL

GND2F7GND3

F8

F9

CAM_VDD_IO_2.7V

M8

K10

VDD_CIS

VDD_NAND

VDD_GENERAL

U302

ZR3453

GND4G6GND5

GND6

G7

1 8

1

A

A

VREG_USB_3.3V

VREG_MMC_3.0V

C301

0.1u

B

B

C

C

D

D

E

E

F

F

G

G

H

H

MMP_VDD_1.9V

C308

C311

C310

10p

0.1u

2 4

C302

0.1u

10u

CAM_VDD_IO_2.7V

C303

C304

0.1u

0.1u

LCD_VDD_2.8V

C312

0.1u

MMP_STROBE_READY

MMP_CAM_PWR_EN

C305

0.1u

C313

0.1u

TV_OUT

MMP_VDD_CORE_1.0V

C306

0.1u

VREG_MSMP_2.7V

C314

0.1u

VREG_MSMP_2.7V

R310

MMP_INT_N

MMP_I2C_SDA

MMP_CAM_RESET_N

MMP_STROBE_CHARGE

MICROSD_DETECT

100K

R331

27Mhz XTAL

FA-238_27MHz_9PF

X300

34

12

27MHz

C339

8p

C307

10p

C315

10p

10K

EBI2_ADDR[11]

EBI2_ADDR[12]

EBI2_ADDR[13]

EBI2_ADDR[14]

EBI2_DATA[0:15]

CAM_VDD_IO_2.7V

R320 100K

MMP_I2C_SCL

MMP_CAM_INT

C334

330p

C340

8p

C300

10u

C309

10u

MMP_CS_N

NAND_ALE

EBI2_OE_N

EBI2_WE_N

EBI2_DATA[0]

EBI2_DATA[1]

EBI2_DATA[2]

EBI2_DATA[3]

EBI2_DATA[4]

EBI2_DATA[5]

EBI2_DATA[6]

EBI2_DATA[7]

EBI2_DATA[8]

EBI2_DATA[9]

EBI2_DATA[10]

EBI2_DATA[11]

EBI2_DATA[12]

EBI2_DATA[13]

EBI2_DATA[14]

EBI2_DATA[15]

TP302

C331

22p

L300

2.2uH

MMP_XTAL_IN

MMP_XTAL_OUT

3

3

CAM_VDD_IO_2.7V

C335

330p

R313 NA

R319 10K

0R311

CAM_VDD_IO_2.7V

1KR322

R321 1K

NAR333

TP303

75

R338

R339

392ohm 1%

B8

A8

B7

B9

A7

A10

A9

C8

C7

D12

C10

C12

C13

C14

B14

C11

B13

A14

A13

B12

A12

B11

A11

C9

B10

L13

M13

L12

L11

K13

M14

L14

L10

J12

H12

K14

G12

J13

H13

K11

N2

K3

L2

J3

M4

N3

M1

L1

N14

P14

P2

M3

P7

N1

P1

M5

N6

M6

P5

N5

G14

F13

390

52

5

LCD_VDD_2.8V

VREG_MMC_3.0V

MMP_VDD_USB_3.3V

VREG_USB_3.3V

0

R301

FB301

1uC317

0.1uC316

D6

G2

K4

H11

G11

VDD_LCD

VDD_MMC

AVDD_USBT

AVDD_VDACI

AVDD_VDACP

Z3X-BOX.COM

GND12J6GND13

GND7

GND8G9GND9

GND10H8GND11

H6

H7

H9

G8

L4

AVDD_USBC

GND14J7GND15

J8

MMP_TCK

D11

D13

TCK

GND16

J9

MMP_TDO

MMP_TDI

E12

E14

TDI

TDO

AGND_VDAC

F12

MMP_TMS

MMP_TRSTN

D14

TMS

TRSTN

K5

MMP_RESET_IN_N

R308 0

F14

G13

TEST

RESETN

HPCMCLK

AGND_USBCL5AGND_USBT

USB_SELECT_N

SDAT0

SDAT1

SDAT2

SDAT3

VMCLK

VPCLK

VHREF

LCS0N

LCS1N

HPCMFS

HPCMDO

HPCMDI

AMCLK

ABCLK

UVBUS

URSET

SCMD

SCLK

SWP

VIDA

VIDB

VIDC

VIDD

VIDE

VIDF

VIDG

VIDH

VIDJ

VIDK

VIDL

VIDM

VIDN

VIDO

VIDP

LD10

LD11

LD12

LD13

LD14

LD15

LD16

LD17

LRDN

LWRN

LACT

ADO

6 11

6

F1

F2

E5

F3

H2

G1

G3

P12

P10

M12

K12

VVS

P8

N8

P9

M10

N10

N9

N11

P11

N12

VIDI

N7

L8

P13

L9

N13

M11

M9

B5

LD0

A5

LD1

B6

LD2

B4

LD3

A4

LD4

C3

LD5

A3

LD6

A2

LD7

A1

LD8

B2

LD9

B1

B3

C1

C2

C5

C6

D3

D1

A6

D2

D5

C4

D4

LA0

E1

LCK

E4

LHS

E3

LVS

E2

H3

H1

J2

J1

N4

M2

K2

AFS

K1

L3

ADI

P3

UDP

P4

UDN

J4

P6

UID

M7

R340

3.4K

1%

33R312

R325 0

R326 0

R329

33

0R335

3.3K

TP300

TP301

R345

100K

MSM_USB_D-

MMP_USB_D-

MMP_MICROSD_DATA[0]

MMP_MICROSD_DATA[1]

MMP_MICROSD_DATA[2]

MMP_MICROSD_DATA[3]

MMP_MICROSD_CMD

MMP_MICROSD_CLK

MMP_CAM_MCLK

MMP_CAM_PCLK

MMP_CAM_HSYNC

MMP_CAM_VSYNC

MMP_CAM_DATA[0]

MMP_CAM_DATA[1]

MMP_CAM_DATA[2]

MMP_CAM_DATA[3]

MMP_CAM_DATA[4]

MMP_CAM_DATA[5]

MMP_CAM_DATA[6]

MMP_CAM_DATA[7]

MMP_LCD_DATA[0]

MMP_LCD_DATA[1]

MMP_LCD_DATA[2]

MMP_LCD_DATA[3]

MMP_LCD_DATA[4]

MMP_LCD_DATA[5]

MMP_LCD_DATA[6]

MMP_LCD_DATA[7]

MMP_LCD_DATA[8]

MMP_LCD_DATA[9]

MMP_LCD_DATA[10]

MMP_LCD_DATA[11]

MMP_LCD_DATA[12]

MMP_LCD_DATA[13]

MMP_LCD_DATA[14]

MMP_LCD_DATA[15]

MMP_LCD_CS_N

MMP_LCD_RD_N

MMP_LCD_WE_N

MMP_LCD_ADS

MMP_LCD_VSYNC_IN

MMP_LCD_VSYNC_OUT

0R324

NAR327

MMP_A_MCLK

MMP_A_BCLK

MMP_A_LRCLK

MMP_ADO_DACDAT

MMP_ADI_ADCDAT

MMP_USB_D+

MMP_USB_D-

VREG_5V

C336

0.01u

+VPWR

10

9

8

7

6

7

7 9

MMP_HPCM_CLK

MMP_HPCM_FSYNC

MMP_HPCM_DO

MMP_HPCM_DI

U304FSUSB30UMX

1

SEL

HSD1+

2

VCC

HSD2+

3

_OE

D+

4

HSD1-

GND

5

HSD2-

D-

MSM_USB_D+

MMP_USB_D+

USB_D+

USB_D-

MMP_LCD_DATA[0]

MMP_LCD_DATA[1]

MMP_LCD_DATA[2]

MMP_LCD_DATA[3]

MMP_LCD_DATA[4]

MMP_LCD_DATA[5]

MMP_LCD_DATA[6]

MMP_LCD_DATA[7]

MMP_LCD_DATA[8]

MMP_LCD_DATA[9]

MMP_LCD_DATA[10]

MMP_LCD_DATA[11]

MMP_LCD_DATA[12]

MMP_LCD_DATA[13]

MMP_LCD_DATA[14]

MMP_LCD_DATA[15]

8

LCD_LDO_EN

MMP_PWR_EN

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

FL300 ICVE10184E150R500FR

9

INOUT_A1

INOUT_B1

8

INOUT_A2

INOUT_B2

7

INOUT_A3

INOUT_B3

6

INOUT_A4

INOUT_B4

G15G2

10

ICVE10184E150R500FRFL301

9

INOUT_B1

INOUT_A1

8

INOUT_B2

INOUT_A2

7

INOUT_B3

INOUT_A3

6

INOUT_B4

INOUT_A4

G110G2

5

ICVE10184E150R500FRFL302

9

INOUT_A1

INOUT_B1

8

INOUT_A2

INOUT_B2

7

INOUT_A3

INOUT_B3

6

INOUT_B4

INOUT_A4

G110G2

5

FL303 ICVE10184E150R500FR

9

INOUT_A1

INOUT_B1

8

INOUT_B2

INOUT_A2

7

INOUT_B3

INOUT_A3

6

INOUT_B4

INOUT_A4

G15G2

10

LCD LDO

C329

1u

+VPWR

9 12

10

10

11

LCD INTERFACE

LCD_VDD_2.8V

LCD_DATA[0]

LCD_DATA[1]

LCD_DATA[2]

LCD_DATA[3]

LCD_DATA[4]

LCD_DATA[5]

LCD_DATA[6]

LCD_DATA[7]

LCD_DATA[8]

LCD_DATA[9]

LCD_DATA[10]

LCD_DATA[11]

LCD_DATA[12]

LCD_DATA[13]

LCD_DATA[14]

LCD_DATA[15]

VA300

ICVN0505X150FR

LCD_DATA[10]

LCD_DATA[11]

LCD_DATA[12]

LCD_DATA[13]

LCD_DATA[14]

LCD_DATA[15]

LCD_DATA[0]

LCD_DATA[1]

LCD_DATA[2]

LCD_DATA[3]

LCD_DATA[4]

LCD_DATA[5]

LCD_DATA[6]

LCD_DATA[7]

LCD_DATA[8]

LCD_DATA[9]

C321

C320

0.1u

NA

CN300

1

40

2

39

38

3

37

4

5

36

6

35

7

34

8

33

9

32

10

31

11

30

12

29

13

28

14

27

15

26

16

25

17

24

18

23

19

22

20

21

ENBY0036001

1.0T, Socket

GB042-40S-H10-E3000

MMP_LCD_VSYNC_IN

LCD_MAKER_ID

WLED_PWR

WLED_1

WLED_2

WLED_3

WLED_4

WLED_5

LCD_IF_MODE

R314 51

R316 51

R317 51

VA301

22pC325

22pC322

C323 22p

C324 22p

LCD connector change : 35pin ZIF -> 40pin BTB

LCD BACKLIGHT CHARGE PUMP

LCD_VDD_2.8V

1

VIN3VOUT

U303 R1114D191D-TR-F

1

VDD VOUT

4

NC

6

CE

C337

1u

150mA

BH28PB1WHFVU300

SEL5STBY

6

BGND2GND

4

C330

1u

MMP_VDD_1.9V

3

2

GND1

5

GND2

C338

1u

LCD_BL_CTRL

+VPWR

AAT3169IFO-T1U301

C1+

C1-

IN

EN_SET

GND

PGND

OUTCP

C328

7

C2+

1u

8

C2-

6

11

D1

12

D2

13

D3

14

D4

1

D5

2

D6

WLED_PWR+VPWR

WLED_1

WLED_2

WLED_3

WLED_4

WLED_5

C333

1u

C327

4

1u

5

9

3

10

15

C332

100K

1u

R336

12

A

A

B

B

C

C

MMP_LCD_ADS

MMP_LCD_CS_N

51R315

LCD_RESET_N

MMP_LCD_RD_N

MMP_LCD_WE_N

MMP_LCD_VSYNC_OUT

0R318

OTP Program Pin

LCD_VSYNC_OUT

C326

22p

D

D

E

E

F

F

G

G

H

H

SWITCH FOR USB2.0

1 6

1 8

2

3

3

5 11

5

64

78

72

9

10

10

119

12

12

- 156 -

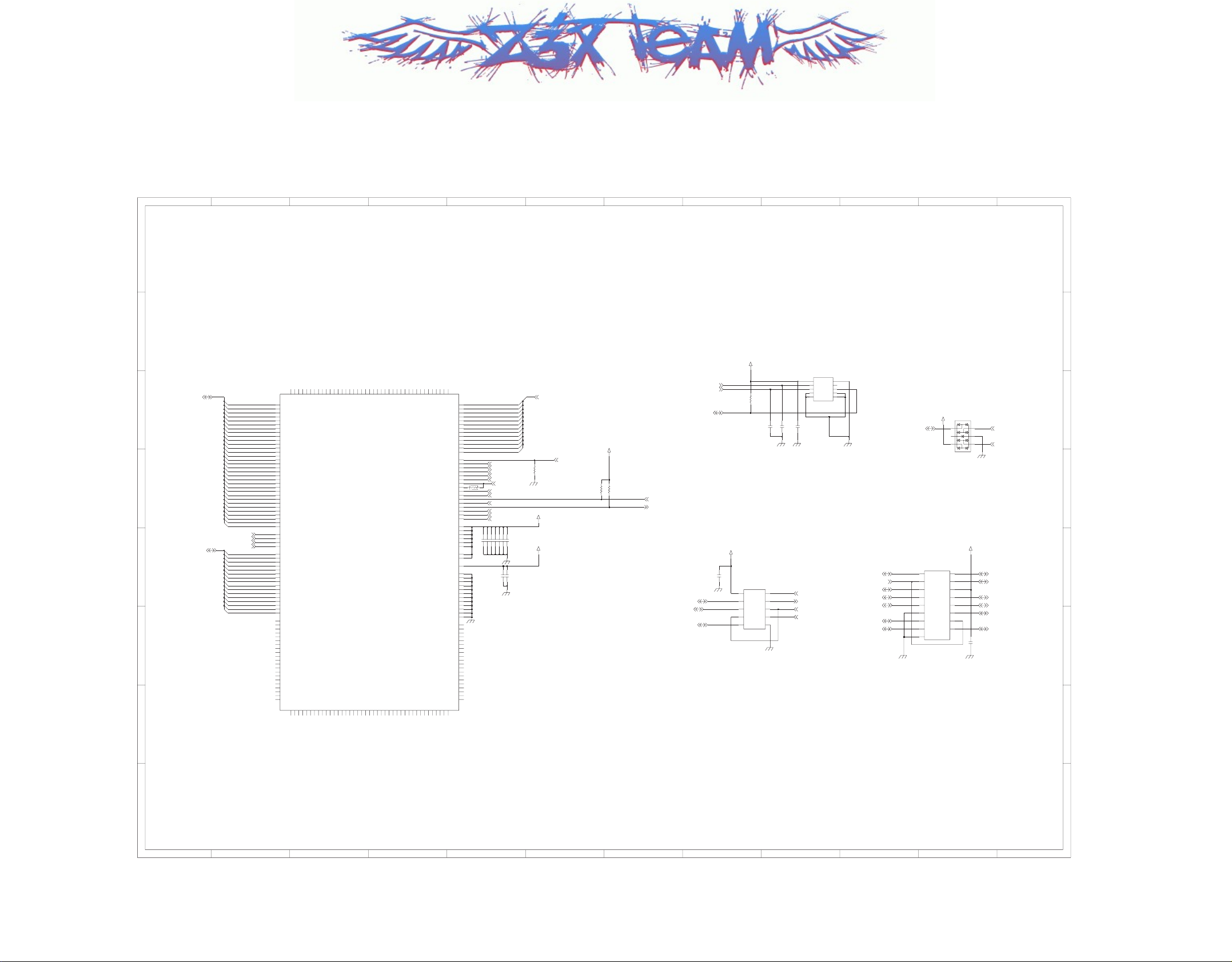

7. CIRCUIT DIAGRAM

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

1

1

A

A

B

B

2

32

3

4

4

5

5 11

6

6

7

7 11

8

8

9

9

1010

12

12

MEMORY (2Gbit 70n NAND FLASH + 1Gbit SDRAM)

VREG_USIM_3.0V

J400

1

4

C1

C5

2

USIM_P_RST_N

MSM_MICROSD_CMD

MICROSD_CMD

MMP_MICROSD_CMD

USIM_P_CLK

USIM_P_DATA

R400

15K

C401

C400

33p

33p

USIM

+VPWR

C412

0.01u

U400

SLAS4717EPMTR2G

101

NO2

VCC

2

COM2

NO1

3

COM1

IN2

4

NC2

IN1

5

NC1

GND

MSM_MICROSD_CLK

9

8

MMC_SELECT_N

7

MMP_MICROSD_CLK

6

MICRO SD SELECT MSM AND MMP

W4

W11

W12

W13

W14

Y1

NC110

NC49

Y4

Y11

Y12

Y13

Y14

C3

NC111

NC112

NC113

NC114

NC115

NC116

NC117Y2NC118Y3NC119

NC120

NC121

NC122

NC123

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

_WP

_WEN

_RAS

_WED

_CAS

CLK

_CS1

_CS2

ALE

CLE

_CE

_RE

RY__BY

CKE

BA0

BA1

VCCD1

VCCD2

VCCD3

VCCD4

VCCD5

VCCD6

VCCQD1

VCCQD2

VCCN2

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

NC63

NC64

NC65

NC66

NC67

NC68

NC69

NC70

NC71

NC72

NC73

NC74

NC75

NC76

NC77

NC78

NC79

NC80

NC81

NC50

NC51

NC52

NC53

H2

H3

H4

G10

NC82

NC54

NC55

NC56

NC57J3NC58

NC60

NC61

NC62

NC59

J2

J4

J6

J5

H5

H6

J10

J11

SDRAM_ADDR[0]

D3

SDRAM_ADDR[1]

E3

SDRAM_ADDR[2]

E2

SDRAM_ADDR[3]

D12

SDRAM_ADDR[4]

C12

SDRAM_ADDR[5]

D11

SDRAM_ADDR[6]

C11

SDRAM_ADDR[7]

D10

SDRAM_ADDR[8]

C10

SDRAM_ADDR[9]

E4

SDRAM_ADDR[10]

D9

SDRAM_ADDR[11]

C9

SDRAM_ADDR[12]

L6

K6

EBI2_WE_N

D5

SDRAM_RAS_N

D6

SDRAM_WE_N

E6

SDRAM_CAS_N

C8

SDRAM_CLK

E5

D7

M3

M4

M9

M10

M2

D8

C4

D4

C7

D2

D13

V3

V8

V12

V4

V9

K12

C6

F7

G2

G13

L13

P2

P13

R8

U2

U6

U10

U13

J12

J13

K1

K2

K3

K4

K5

K10

K11

K13

K14

L1

L2

L3

L4

L5

L14

M5

M6

N2

SDRAM_CS_N

R404

0

NAND_ALE

NAND_CLE

EBI2_OE_N

SDRAM_CLK_EN

SDRAM_ADDR[13]

SDRAM_ADDR[14]

0.1uC403

0.1uC408

0.1uC405

0.1uC406

C404 0.1u

C407 0.1u

C410

0.01u

Z3X-BOX.COM

SDRAM_ADDR[0:12]

VREG_MSMP_2.7V

RESOUT_N

R401

100K

R403

R402

10K

100K

VREG_MSME_1.8V

0.1u

VREG_MSMP_2.7V

C409

C411

0.1u

NAND_CS_N

NAND_READY

T13

U1

U3

U14

V1

V2

V13

V14

NC100

NC39

W2

W3

NC101

NC102

NC103

NC104

NC105

NC106

NC107

NC108W1NC109

U402

NC44G4NC45

NC46

NC47

NC48

NC40

NC41

NC42

NC43

G5

G6

G7

G8

G9

G3

F11

F12

F13

N10

N11

N12

N13

P7

P8

R2

R7

R9

T2

N3

N6

SDRAM_DATA[0:31]

C

C

D

D

EBI2_DATA[0:15]

E

E

F

F

G

G G

SDRAM_DATA[0]

SDRAM_DATA[1]

SDRAM_DATA[2]

SDRAM_DATA[3]

SDRAM_DATA[4]

SDRAM_DATA[5]

SDRAM_DATA[6]

SDRAM_DATA[7]

SDRAM_DATA[8]

SDRAM_DATA[9]

SDRAM_DATA[10]

SDRAM_DATA[11]

SDRAM_DATA[12]

SDRAM_DATA[13]

SDRAM_DATA[14]

SDRAM_DATA[15]

SDRAM_DATA[16]

SDRAM_DATA[17]

SDRAM_DATA[18]

SDRAM_DATA[19]

SDRAM_DATA[20]

SDRAM_DATA[21]

SDRAM_DATA[22]

SDRAM_DATA[23]

SDRAM_DATA[24]

SDRAM_DATA[25]

SDRAM_DATA[26]

SDRAM_DATA[27]

SDRAM_DATA[28]

SDRAM_DATA[29]

SDRAM_DATA[30]

SDRAM_DATA[31]

SDRAM_DQM[0]

SDRAM_DQM[1]

SDRAM_DQM[2]

SDRAM_DQM[3]

EBI2_DATA[0]

EBI2_DATA[1]

EBI2_DATA[2]

EBI2_DATA[3]

EBI2_DATA[4]

EBI2_DATA[5]

EBI2_DATA[6]

EBI2_DATA[7]

EBI2_DATA[8]

EBI2_DATA[9]

EBI2_DATA[10]

EBI2_DATA[11]

EBI2_DATA[12]

EBI2_DATA[13]

EBI2_DATA[14]

EBI2_DATA[15]

N9

NC88

NC83N4NC84

NC85N5NC86

NC87

U4

DQ0

T4

DQ1

T5

DQ2

V5

DQ3

U5

DQ4

T6

DQ5

V6

DQ6

U7

DQ7

T9

DQ8

T10

DQ9

V10

DQ10

T11

DQ11

U11

DQ12

V11

DQ13

T12

DQ14

U12

DQ15

P3

DQ16

R3

DQ17

P4

DQ18

R4

DQ19

P5

DQ20

R5

DQ21

P6

DQ22

R6

DQ23

P9

DQ24

P10

DQ25

R10

DQ26

P11

DQ27

R11

DQ28

P12

DQ29

R12

DQ30

R13

DQ31

U8

DQM0

T8

DQM1

V7

DQM2

U9

DQM3

M11

IO1

M13

IO2

L10

IO3

L12

IO4

J9

IO5

H12

IO6

H10

IO7

G12

IO8

M12

IO9

L9

IO10

L11

IO11

K9

IO12

H13

IO13

H11

IO14

H9

IO15

G11

IO16

A1

NC1

A2

NC2

A3

NC3

A4

NC4

A11

NC5

A12

NC6

A13

NC7

A14

NC8

B1

NC9

B2

NC10

B3

NC11

B4

NC12

B11

NC13

B12

NC14

B13

NC15

B14

NC16

C1

NC17

C2

NC18

C5

NC19

C13

NC20

C14

NC21

NC22

NC23

NC24E1NC25

NC26

NC27

E7

E8

E9

D1

E10

D14

T3

NC89

NC90

NC91

NC92

NC93

NC94

NC95

NC96

NC97

NC98T7NC99

TYA000BC00HOGG

NC30

NC31

NC32

NC33

NC34

NC35

NC36F8NC37

NC28

NC29

E11

NC38

F2

F3

F4

F5

F6

F9

E12

F10

E13

C2

3

C3

7

GND1

GND4

89

GND2

GND3

C402

1u

MICROSD_CLK

5

C6

6

C7

10

MMP_MICROSD_DATA[0]

MMC_SELECT_N

MSM_MICROSD_DATA[1]

MICROSD_DATA[1]

MMP_MICROSD_DATA[1]

MSM_MICROSD_DATA[2]

VREG_USIM_3.0V

D400

1

USIM_P_DATA USIM_P_CLK

6

2345

+VPWR

C413

0.01u

USIM_P_RST_N

MICROSD_DATA[0]

MSM_MICROSD_DATA[0]

MMP_MICROSD_DATA[3]

MICROSD_DATA[3]

MSM_MICROSD_DATA[3]

MMP_MICROSD_DATA[2]MICROSD_DATA[2]

PLR0504F

MAX4701ETE+TU401

1

16

NC1

COM1

15

2

NO1

IN1_IN2

3

14

NO2

V+

13

4

NC4

COM2

5

12

NC2

COM4

6

11

GND

NO4

7

10

NO3

IN3_IN4

9

8

NC3

COM3

17

PGND

A

A

B

B

C

C

D

D

E

E

F

F

G

H

1

H

HH

2

2

3

41

4

5

6

7

7

8

8

95 10

103

11

11

12

129

Loading...

Loading...