Page 1

Internal Use Only

North/Latin America http://aic.lgservice.com

Europe/Africa http://eic.lgservice.com

Asia/Oceania http://biz.lgservice.com

LED TV

SERVICE MANUAL

CHASSIS : LD34E

MODEL: 84LA980V 84LA980V-ZD

CAUTION

BEFORE SERVICING THE CHASSIS,

READ THE SAFETY PRECAUTIONS IN THIS MANUAL.

Printed in KoreaP/NO : MFL678022302 (1309-REV00)

Page 2

CONTENTS

CONTENTS .............................................................................................. 2

SAFETY PRECAUTIONS ........................................................................ 3

SERVICING PRECAUTIONS .................................................................... 4

SPECIFICATION ....................................................................................... 6

ADJUSTMENT INSTRUCTION .............................................................. 13

EXPLODED VIEW .................................................................................. 23

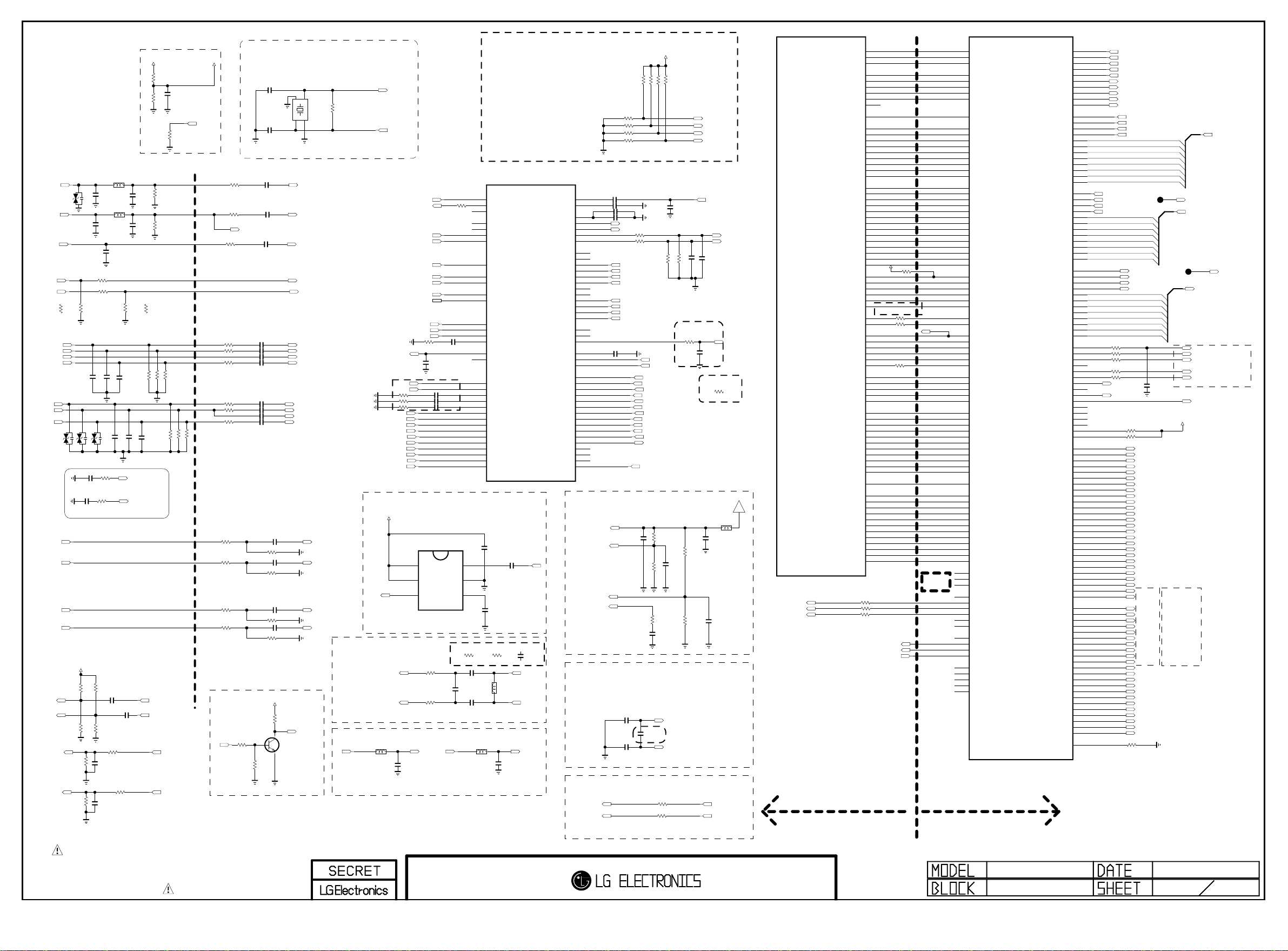

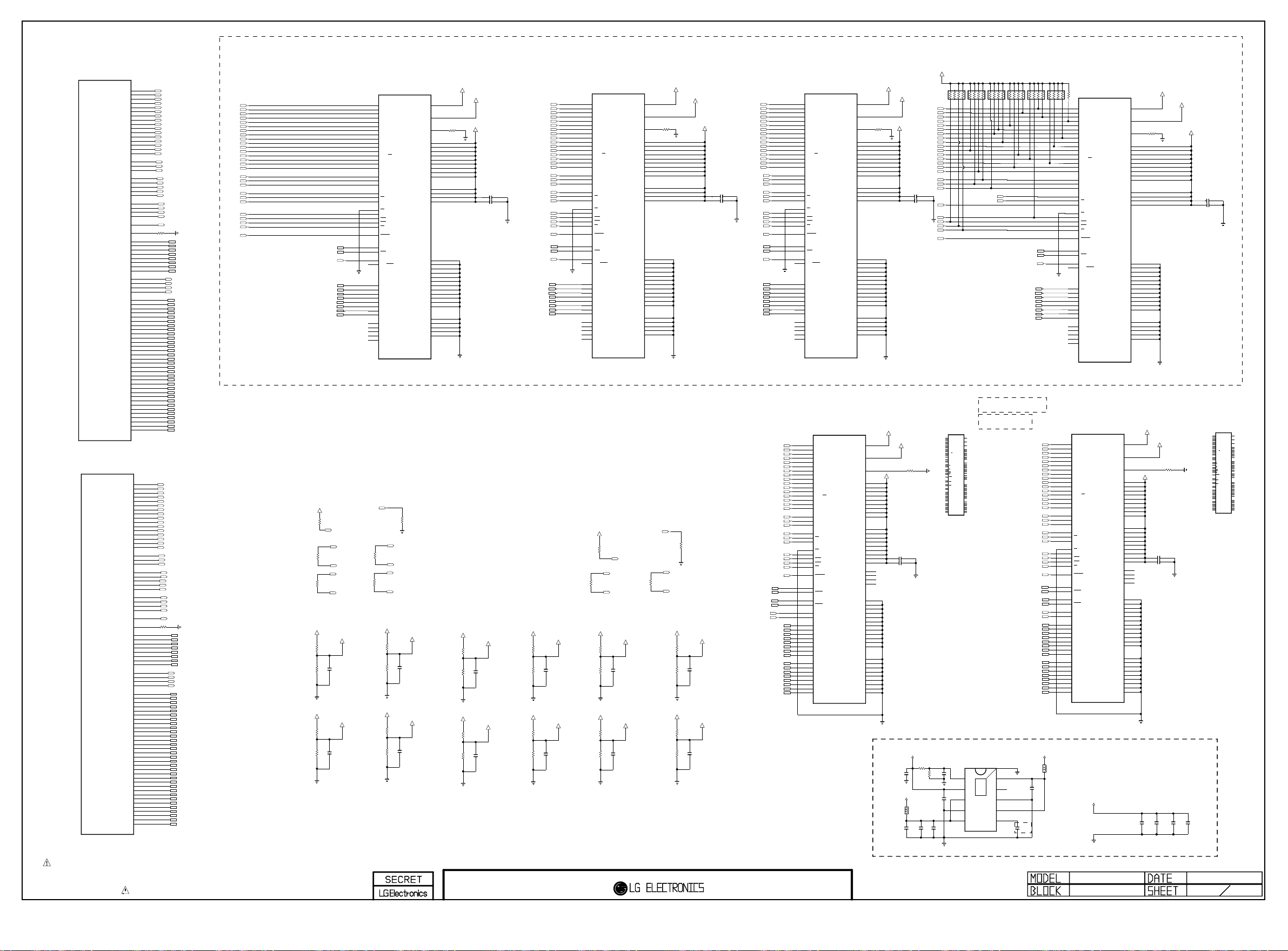

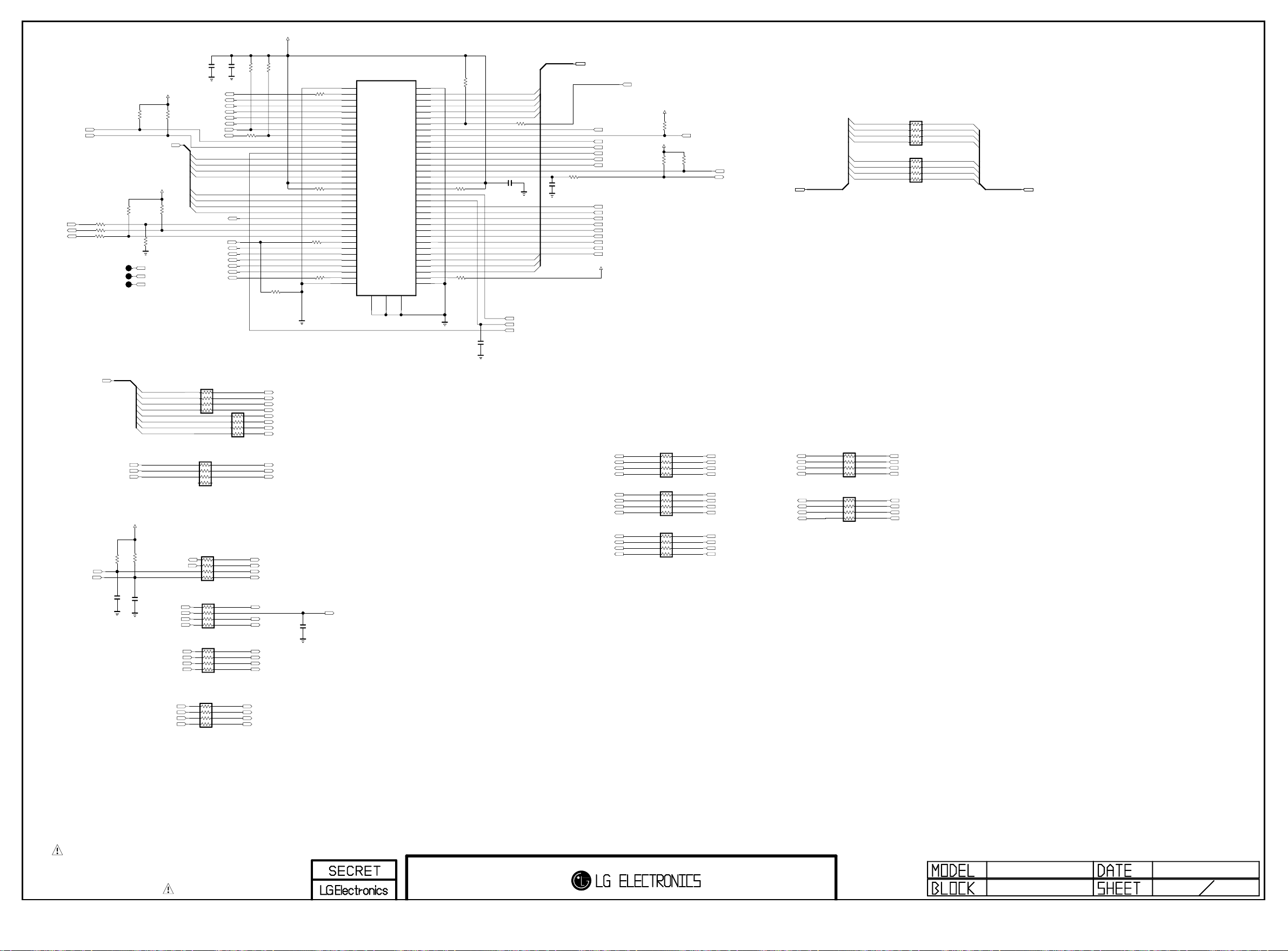

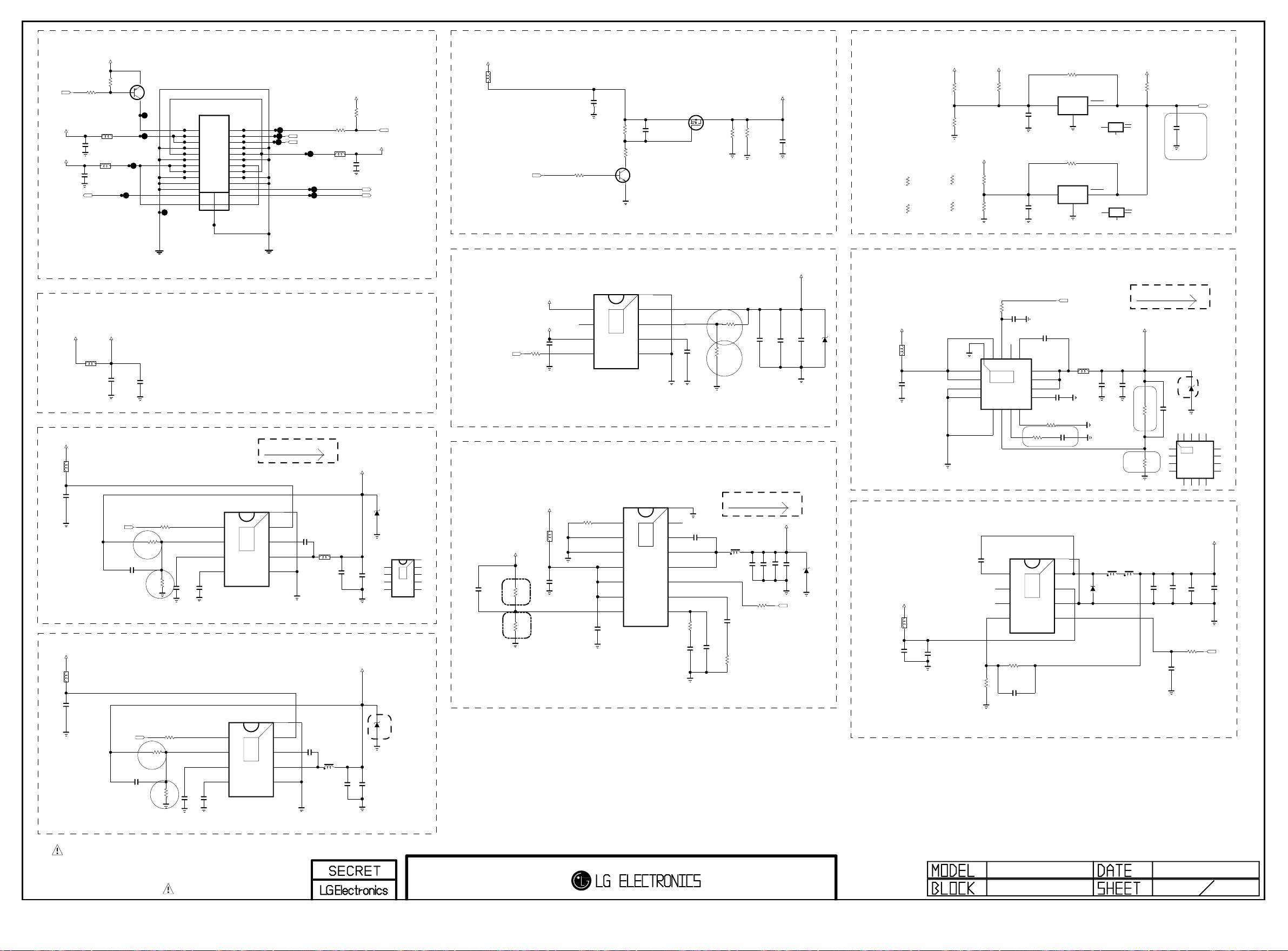

SCHEMATIC CIRCUIT DIAGRAM ..............................................................

Only for training and service purposes

- 2 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 3

SAFETY PRECAUTIONS

IMPORTANT SAFETY NOTICE

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These parts are identified by in the

Schematic Diagram and Exploded View.

It is essential that these special safety parts should be replaced with the same components as recommended in this manual to prevent

Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

General Guidance

An isolation Transformer should always be used during the

servicing of a receiver whose chassis is not isolated from the AC

power line. Use a transformer of adequate power rating as this

protects the technician from accidents resulting in personal injury

from electrical shocks.

It will also protect the receiver and it's components from being

damaged by accidental shorts of th e cir cuitry that may be

inadvertently introduced during the service operation.

If any fuse (or Fusible Resistor) in this TV receiver is blown,

replace it with the specified.

When replacing a high wattage resistor (Oxide Metal Film Resistor,

over 1 W), keep the resistor 10 mm away from PCB.

Keep wires away from high voltage or high temperature parts.

Before returning the receiver to the customer,

always perform an AC leakage current check on the exposed

metallic parts of the cabinet, such as antennas, terminals, etc., to

be sure the set is safe to operate without damage of electrical

shock.

Leakage Current Cold Check(Antenna Cold Check)

With the instrument AC plug removed from AC source, connect an

electrical jumper across the two AC plug prongs. Place the AC

switch in the on position, connect one lead of ohm-meter to the AC

plug prongs tied together and touch other ohm-meter lead in turn to

each exposed metallic parts such as antenna terminals, phone

jacks, etc.

If the exposed metallic part has a return path to the chassis, the

measured resistance should be between 1 MΩ and 5.2 MΩ.

When the exposed metal has no return path to the chassis the

reading must be infinite.

An other abnormality exists that must be corrected before the

receiver is returned to the customer.

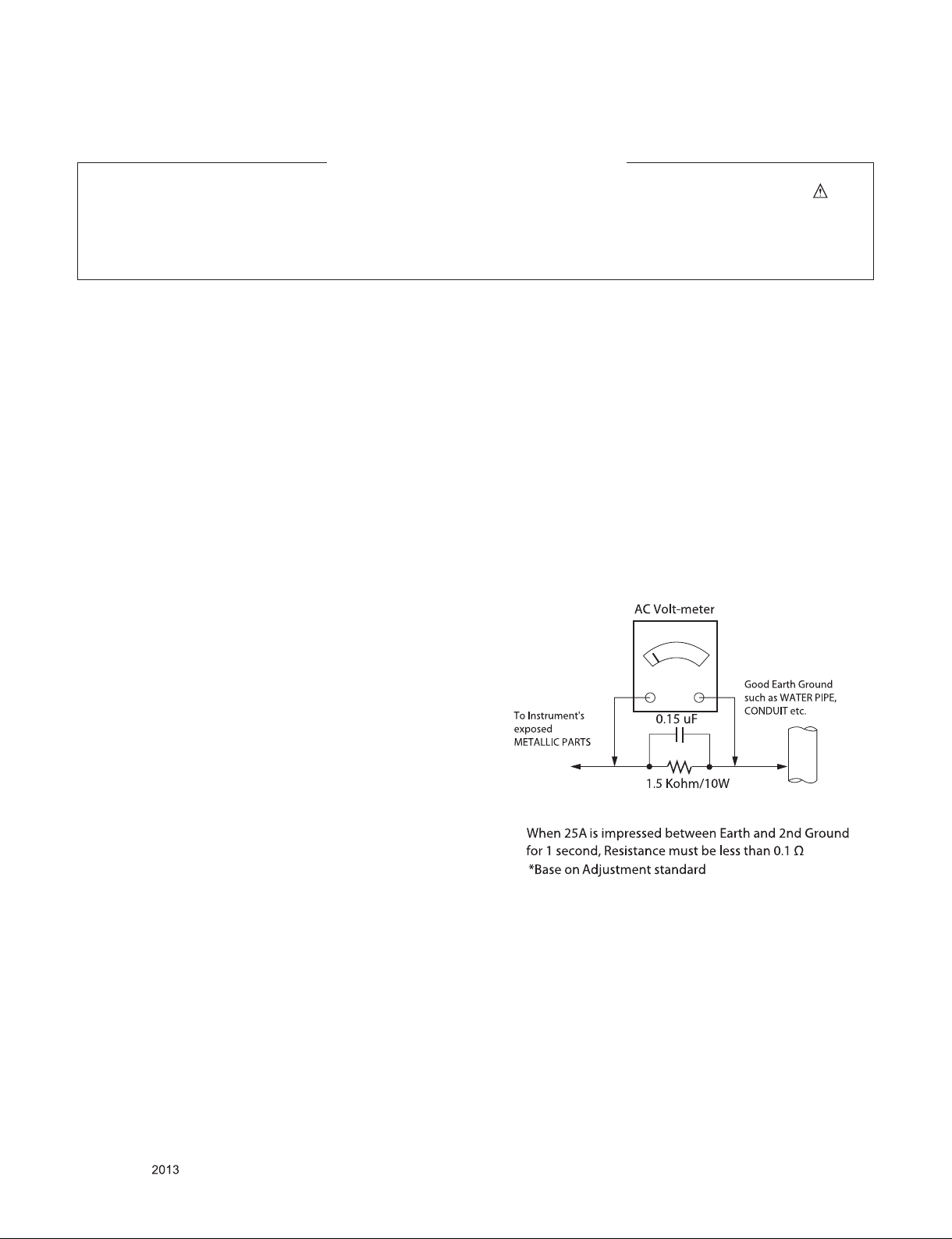

Leakage Current Hot Check (See below Figure)

Plug the AC cord directly into the AC outlet.

Do not use a line Isolation Transformer during this check.

Connect 1.5 K / 10 watt resistor in parallel with a 0.15 uF capacitor

between a known good earth ground (Water Pipe, Conduit, etc.)

and the exposed metallic parts.

Measure the AC voltage across the resistor using AC voltmeter

with 1000 ohms/volt or more sensitivity.

Reverse plug the AC cord into the AC outlet and repeat AC voltage

measurements for each exp ose d metallic par t. Any voltage

measured must not exceed 0.75 volt RMS which is corresponds to

0.5 mA.

In case any measurement is out of the limits specified, there is

possibility of shock hazard and the set must be checked and

repaired before it is returned to the customer.

Leakage Current Hot Check circuit

Only for training and service purposes

- 3 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 4

SERVICING PRECAUTIONS

CAUTION: Before servicing receivers covered by this service

manual and its supplements and addenda, read and follow the

SAFETY PRECAUTIONS on page 3 of this publication.

NOTE: If unforeseen circumstances create conict between the

following servicing precautions and any of the safety precautions

on page 3 of this publication, always follow the safety precautions. Remember: Safety First.

General Servicing Precautions

1. Always unplug the receiver AC power cord from the AC power

source before;

a. Removing or reinstalling any component, circuit board

module or any other receiver assembly.

b. Disconnecting or reconnecting any receiver electrical plug

or other electrical connection.

c. Connecting a test substitute in parallel with an electrolytic

capacitor in the receiver.

CAUTION: A wrong part substitution or incorrect polarity

installation of electrolytic capacitors may result in an explosion hazard.

2. Test high voltage only by measuring it with an appropriate

high voltage meter or other voltage measuring device (DVM,

FETVOM, etc) equipped with a suitable high voltage probe.

Do not test high voltage by "drawing an arc".

3. Do not spray chemicals on or near this receiver or any of its

assemblies.

4. Unless specied otherwise in this service manual, clean

electrical contacts only by applying the following mixture to the

contacts with a pipe cleaner, cotton-tipped stick or comparable

non-abrasive applicator; 10 % (by volume) Acetone and 90 %

(by volume) isopropyl alcohol (90 % - 99 % strength)

CAUTION: This is a ammable mixture.

Unless specied otherwise in this service manual, lubrication

of contacts in not required.

5. Do not defeat any plug/socket B+ voltage interlocks with which

receivers covered by this service manual might be equipped.

6. Do not apply AC power to this instrument and/or any of its

electrical assemblies unless all solid-state device heat sinks

are correctly installed.

7. Always connect the test receiver ground lead to the receiver

chassis ground before connecting the test receiver positive

lead.

Always remove the test receiver ground lead last.

8. Use with this receiver only the test xtures specied in this

service manual.

CAUTION: Do not connect the test xture ground strap to any

heat sink in this receiver.

Electrostatically Sensitive (ES) Devices

Some semiconductor (solid-state) devices can be damaged easily by static electricity. Such components commonly are called

Electrostatically Sensitive (ES) Devices. Examples of typical ES

devices are integrated circuits and some eld-effect transistors

and semiconductor “chip” components. The following techniques

should be used to help reduce the incidence of component damage caused by static by static electricity.

1. Immediately before handling any semiconductor component or

semiconductor-equipped assembly, drain off any electrostatic

charge on your body by touching a known earth ground. Alternatively, obtain and wear a commercially available discharging wrist strap device, which should be removed to prevent

potential shock reasons prior to applying power to the unit

under test.

2. After removing an electrical assembly equipped with ES

devices, place the assembly on a conductive surface such as

aluminum foil, to prevent electrostatic charge buildup or exposure of the assembly.

3. Use only a grounded-tip soldering iron to solder or unsolder

ES devices.

4. Use only an anti-static type solder removal device. Some solder removal devices not classied as “anti-static” can generate

electrical charges sufcient to damage ES devices.

5. Do not use freon-propelled chemicals. These can generate

electrical charges sufcient to damage ES devices.

6. Do not remove a replacement ES device from its protective

package until immediately before you are ready to install it.

(Most replacement ES devices are packaged with leads electrically shorted together by conductive foam, aluminum foil or

comparable conductive material).

7. Immediately before removing the protective material from the

leads of a replacement ES device, touch the protective material to the chassis or circuit assembly into which the device will

be installed.

CAUTION: Be sure no power is applied to the chassis or circuit, and observe all other safety precautions.

8. Minimize bodily motions when handling unpackaged replacement ES devices. (Otherwise harmless motion such as the

brushing together of your clothes fabric or the lifting of your

foot from a carpeted oor can generate static electricity sufcient to damage an ES device.)

General Soldering Guidelines

1. Use a grounded-tip, low-wattage soldering iron and appropriate tip size and shape that will maintain tip temperature within

the range or 500 °F to 600 °F.

2. Use an appropriate gauge of RMA resin-core solder composed

of 60 parts tin/40 parts lead.

3. Keep the soldering iron tip clean and well tinned.

4. Thoroughly clean the surfaces to be soldered. Use a mall wirebristle (0.5 inch, or 1.25 cm) brush with a metal handle.

Do not use freon-propelled spray-on cleaners.

5. Use the following unsoldering technique

a. Allow the soldering iron tip to reach normal temperature.

(500 °F to 600 °F)

b. Heat the component lead until the solder melts.

c. Quickly draw the melted solder with an anti-static, suction-

type solder removal device or with solder braid.

CAUTION: Work quickly to avoid overheating the circuit

board printed foil.

6. Use the following soldering technique.

a. Allow the soldering iron tip to reach a normal temperature

(500 °F to 600 °F)

b. First, hold the soldering iron tip and solder the strand

against the component lead until the solder melts.

c. Quickly move the soldering iron tip to the junction of the

component lead and the printed circuit foil, and hold it there

only until the solder ows onto and around both the component lead and the foil.

CAUTION: Work quickly to avoid overheating the circuit

board printed foil.

d. Closely inspect the solder area and remove any excess or

splashed solder with a small wire-bristle brush.

Only for training and service purposes

- 4 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 5

IC Remove/Replacement

Some chassis circuit boards have slotted holes (oblong) through

which the IC leads are inserted and then bent at against the circuit foil. When holes are the slotted type, the following technique

should be used to remove and replace the IC. When working with

boards using the familiar round hole, use the standard technique

as outlined in paragraphs 5 and 6 above.

Removal

1. Desolder and straighten each IC lead in one operation by

gently prying up on the lead with the soldering iron tip as the

solder melts.

2. Draw away the melted solder with an anti-static suction-type

solder removal device (or with solder braid) before removing

the IC.

Replacement

1. Carefully insert the replacement IC in the circuit board.

2. Carefully bend each IC lead against the circuit foil pad and

solder it.

3. Clean the soldered areas with a small wire-bristle brush.

(It is not necessary to reapply acrylic coating to the areas).

"Small-Signal" Discrete Transistor

Removal/Replacement

1. Remove the defective transistor by clipping its leads as close

as possible to the component body.

2. Bend into a "U" shape the end of each of three leads remaining on the circuit board.

3. Bend into a "U" shape the replacement transistor leads.

4. Connect the replacement transistor leads to the corresponding

leads extending from the circuit board and crimp the "U" with

long nose pliers to insure metal to metal contact then solder

each connection.

Power Output, Transistor Device

Removal/Replacement

1. Heat and remove all solder from around the transistor leads.

2. Remove the heat sink mounting screw (if so equipped).

3. Carefully remove the transistor from the heat sink of the circuit

board.

4. Insert new transistor in the circuit board.

5. Solder each transistor lead, and clip off excess lead.

6. Replace heat sink.

Diode Removal/Replacement

1. Remove defective diode by clipping its leads as close as possible to diode body.

2. Bend the two remaining leads perpendicular y to the circuit

board.

3. Observing diode polarity, wrap each lead of the new diode

around the corresponding lead on the circuit board.

4. Securely crimp each connection and solder it.

5. Inspect (on the circuit board copper side) the solder joints of

the two "original" leads. If they are not shiny, reheat them and

if necessary, apply additional solder.

3. Solder the connections.

CAUTION: Maintain original spacing between the replaced

component and adjacent components and the circuit board to

prevent excessive component temperatures.

Circuit Board Foil Repair

Excessive heat applied to the copper foil of any printed circuit

board will weaken the adhesive that bonds the foil to the circuit

board causing the foil to separate from or "lift-off" the board. The

following guidelines and procedures should be followed whenever this condition is encountered.

At IC Connections

To repair a defective copper pattern at IC connections use the

following procedure to install a jumper wire on the copper pattern

side of the circuit board. (Use this technique only on IC connections).

1. Carefully remove the damaged copper pattern with a sharp

knife. (Remove only as much copper as absolutely necessary).

2. carefully scratch away the solder resist and acrylic coating (if

used) from the end of the remaining copper pattern.

3. Bend a small "U" in one end of a small gauge jumper wire and

carefully crimp it around the IC pin. Solder the IC connection.

4. Route the jumper wire along the path of the out-away copper

pattern and let it overlap the previously scraped end of the

good copper pattern. Solder the overlapped area and clip off

any excess jumper wire.

At Other Connections

Use the following technique to repair the defective copper pattern

at connections other than IC Pins. This technique involves the

installation of a jumper wire on the component side of the circuit

board.

1. Remove the defective copper pattern with a sharp knife.

Remove at least 1/4 inch of copper, to ensure that a hazardous

condition will not exist if the jumper wire opens.

2. Trace along the copper pattern from both sides of the pattern

break and locate the nearest component that is directly connected to the affected copper pattern.

3. Connect insulated 20-gauge jumper wire from the lead of the

nearest component on one side of the pattern break to the

lead of the nearest component on the other side.

Carefully crimp and solder the connections.

CAUTION: Be sure the insulated jumper wire is dressed so the

it does not touch components or sharp edges.

Fuse and Conventional Resistor

Removal/Replacement

1. Clip each fuse or resistor lead at top of the circuit board hollow

stake.

2. Securely crimp the leads of replacement component around

notch at stake top.

Only for training and service purposes

- 5 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 6

SPECIFICATION

NOTE : Specifications and others are subject to change without notice for improvement

.

1. Application range

This specification is applied to the LED TV used LD34E

chassis.

2. Requirement for Test

Each part is tested as below without special appointment.

1) Temperature: 25 °C ± 5 °C(77 °F ± 9 °F), CST: 40 °C ± 5 °C

2) Relative Humidity: 65 % ± 10 %

3) Power Voltage

: Standard input voltage (AC 100-240 V~, 50/60 Hz)

* Standard Voltage of each products is marked by models.

4) Specification and performance of each parts are followed

ea ch drawing and s pe cificatio n b y p art number in

accordance with BOM.

5) The receiver must be operated for about 20 minutes prior to

the adjustment.

3. Test method

1) Performance: LGE TV test method followed

2) Demanded other specification

- Safety : CE, IEC specification

- EMC : CE, IEC

- Wireless : Wireless HD Specification (Option)

4. Model General Specification

No. Item Specication Remarks

DTV & Analog (Total 37 countries)

DTV (MPEG2/4, DVB-T) : 30 countries

Germany, Netherland, Switzerland, Hungary, Austria, Slovenia, Bulgaria, France, Spain, Italy, Belgium, Russia, Luxemburg, Greece,

Czech, Croatia, Turkey, Moroco, Ireland, Latvia, Estonia, Lithuania,

Poland, Portugal, Romania, Albania, Bosnia, Serbia, Slovakia, Beralus

1 Market

EU(PAL Market-36Countries)/CIS

+ Morocoo(Africa)

DTV (MPEG2/4, DVB-T2) : 8 countries

UK(Ireland), Sweden, Denmark, Finland, Norway, Ukraine, Kazakhstan, Russia

DTV (MPEG2/4, DVB-C) : 37 countries

Germany, Netherland, Switzerland, Hungary, Austria, Slovenia, Bulgaria, France, Spain, Italy, Belgium, Russia, Luxemburg, Greece,

Czech, Croatia, Turkey, Moroco, Ireland, Latvia, Estonia, Lithuania,

Poland, Portugal, Romania, Albania, Bosnia, Serbia, Slovakia, Beralus, UK, Sweden, Denmark, Finland, Norway, Ukraine, Kazakhstan

DTV (MPEG2/4, DVB-S/S2) : 30 countries

Germany, Netherland, Switzerland, Hungary, Austria, Slovenia, Bulgaria, France, Spain, Italy, Belgium, Russia, Luxemburg, Greece,

Czech, Croatia, Turkey, Moroco, Ireland, Latvia, Estonia, Lithuania,

Poland, Portugal, Romania, Albania, Bosnia, Serbia, Slovakia, Beralus, UK, Sweden, Denmark, Finland, Norway, Ukraine, Kazakhstan

Supported satellite : 29 satellites

ABS1 75.0E/ AMOS 4.0W/ ASIASATS 105.5E/ ASTRA1LHMKR

19.2E/ ASTRA2ABD 28.2E/ ASTRA3AB 23.5E/ ASTRA4A 4.8E/

ATLANTICBIRD2 8.0W/ ATLANTICBIRD3 5.0W/ BADR 26.0E/ EUROBIRD3 33.0E/ EUROBIRD9A 9.0E/ EUTELSATW2A 10.E/ EUTELSATW3A 7.0E/ EUTELSATW4W7 36.0E/ EUTELSESAT 16.0E/

EXPRESSAM1 40.0E/ EXPRESAM3 140.0E/ EXPRESSAM33

96.5E/ HELLASAT2 39.0E/ HISPASAT1CDE 30.0W/ HOTBIRD

13.0E/ INTELSAT10&7 68.5E/ INTELSAT15 85.2E/ INTELSAT904

60.0E/ NILESAT 7.0W/ THOR 0.8W/ TURKSAT 42.0E/ YAMAL201

90.0E

Only for training and service purposes

- 6 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 7

No. Item Specication Remarks

2 Broadcasting system 1) PAL-BG/DK/I/I’

2) SECAM L/L’, DK, BG, I

3) DVB-T/T2, C, S/S2

1 ) Digital TV

- VHF, UHF

- C-Band, Ku-Band

3 Program coverage

4 Receiving system

2) Analogue TV

-VHF : E2 to E12

-UHF : E21 to E69

-CATV : S1 to S20

-HYPER : S21 to S47

Analog : Upper Heterodyne

Digital : COFDM, QAM

► DVB-T

- Guard Interval(Bitrate_Mbit/s)

1/4, 1/8, 1/16, 1/32

- Modulation : Code Rate

QPSK : 1/2, 2/3, 3/4, 5/6, 7/8

16-QAM : 1/2, 2/3, 3/4, 5/6, 7/8

64-QAM : 1/2, 2/3, 3/4, 5/6, 7/8

► DVB-T2

- Guard Interval(Bitrate_Mbit/s)

1/4, 1/8, 1/16, 1/32, 1/128, 19/128, 19/256,

- Modulation : Code Rate

QPSK : 1/2, 2/5, 2/3, 3/4, 5/6

16-QAM : 1/2, 2/5, 2/3, 3/4, 5/6

64-QAM : 1/2, 2/5, 2/3, 3/4, 5/6

256-QAM : 1/2, 2/5, 2/3, 3/4, 5/6

5 Input Voltage AC 100 ~ 240 V, 50/60 Hz

► DVB-C

- Symbolrate : 4.0Msymbols/s to 7.2 Msymbols/s

- Modulation : 16QAM, 64-QAM, 128-QAM and 256-QAM

► DVB-S/S2

- symbolrate :

DVB-S2 (8PSK / QPSK) : 2 ~ 45 Msymbol/s

DVB-S (QPSK) : 2 ~ 45 Msymbol/s

- viterbi

DVB-S mode : 1/2, 2/3, 3/4, 5/6, 7/8

DVB-S2 mode : 1/2, 2/3, 3/4, 3/5, 4/5, 5/6, 8/9, 9/10

Only for training and service purposes

- 7 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 8

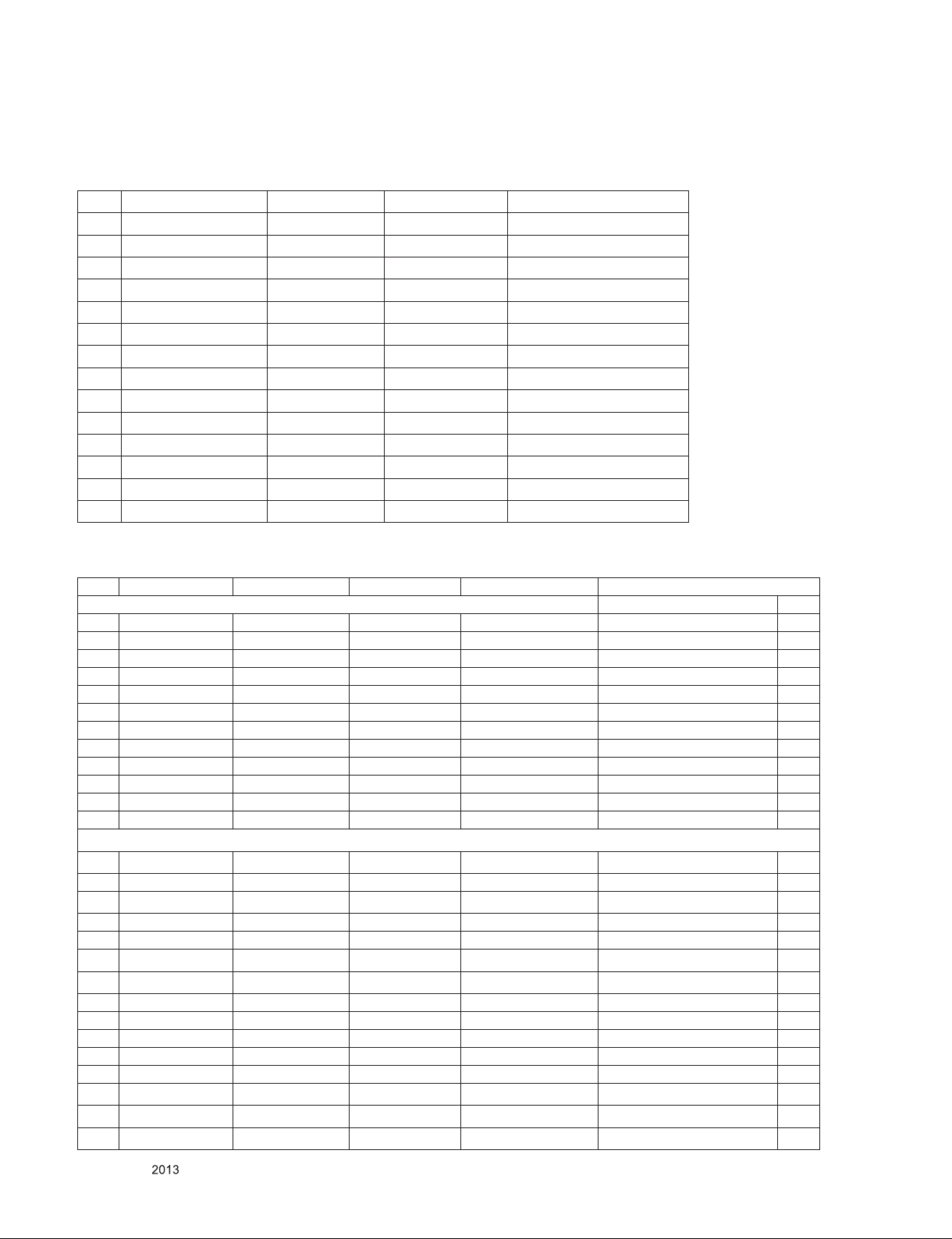

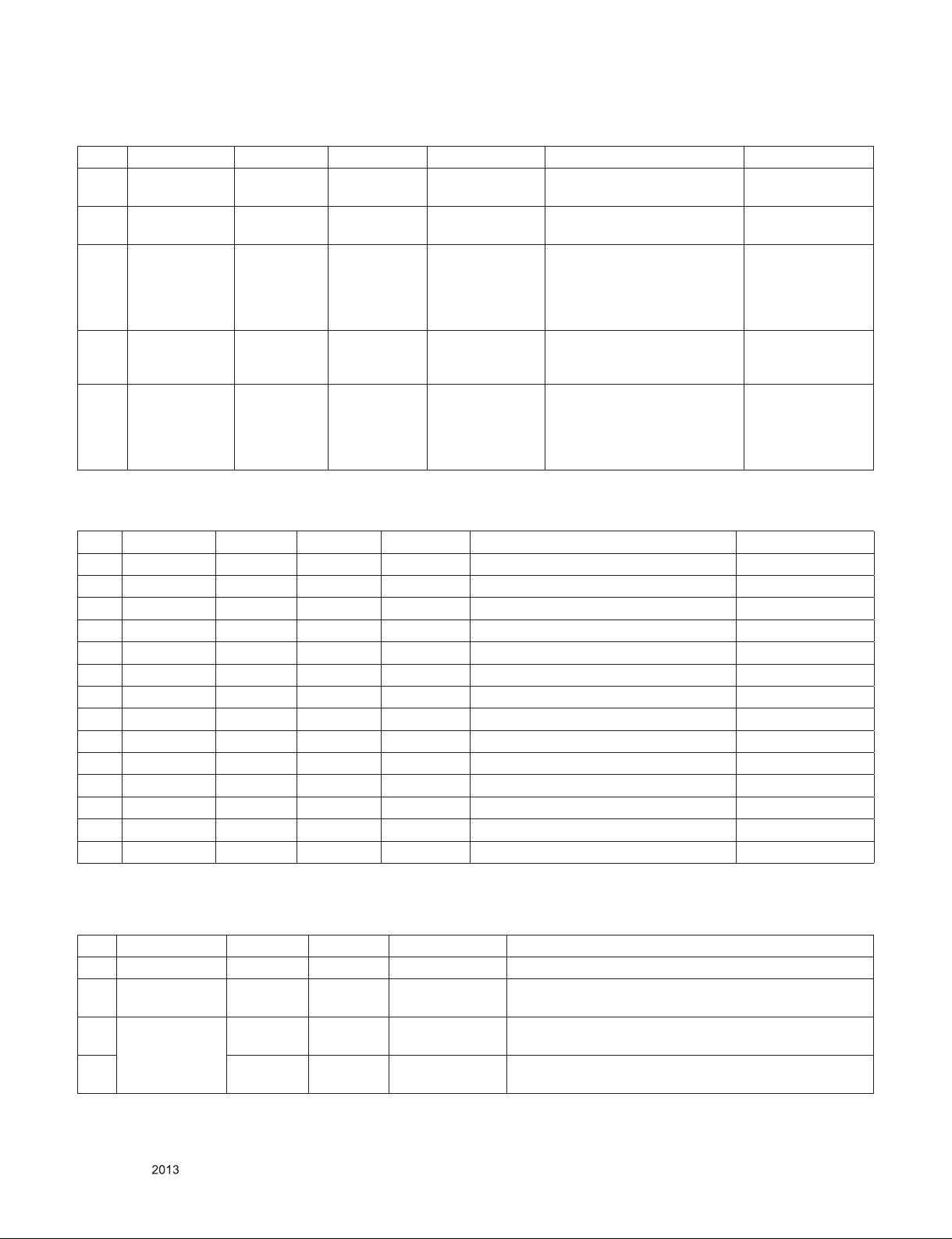

5. External input format

5.1. 2D Mode

(1) Component input(Y, CB/PB, CR/PR)

No. Resolution H-freq(kHz) V-freq(Hz)

1. 720×480 15.73 60.00 SDTV, DVD 480i

2. 720×480 15.63 59.94 SDTV, DVD 480i

3. 720×480 31.47 59.94 480p

4. 720×480 31.50 60.00 480p

5. 720×576 15.625 50.00 SDTV 576i

6. 720×576 31.25 50.00 SDTV 576p

7. 1280×720 45.00 50.00 HDTV 720p

8. 1280×720 44.96 59.94 HDTV 720p

9. 1280×720 45.00 60.00 HDTV 720p

10. 1920×1080 31.25 50.00 HDTV 1080i

11. 1920×1080 33.75 60.00 HDTV 1080i

12. 1920×1080 33.72 59.94 HDTV 1080i

13. 1920×1080 56.250 50 HDTV 1080p

14. 1920×1080 67.5 60 HDTV 1080p

(2) HDMI Input (PC/DTV)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed

HDMI-PC DDC

1 640*350 31.468 70.09 25.17 EGA Х

2 720*400 31.469 70.08 28.32 DOS O

3 640*480 31.469 59.94 25.17 VESA(VGA) O

4 800*600 37.879 60.31 40.00 VESA(SVGA) O

5 1024*768 48.363 60.00 65.00 VESA(XGA) O

6 1152*864 54.348 60.053 80 VESA O

7 1280*1024 63.981 60.020 108 VESA(SXGA) O

8 1360*768 47.712 60.015 85.5 VESA(WXGA) O

9 1920*1080 67.5 60.00 148.5 WUXGA(Reduced Blanking) O

10 3840*2160 67.5 30.00 297.00 UD

11 3840*2160 56.25 25.00 297.00 UD

12 3840*2160 54.0 24.00 297.00 UD

HDMI-DTV

1 720*480 31.47 60 27.027 SDTV 480P

2 720*480 31.47 59.94 27.00 SDTV 480P

3 1280*720 45.00 60.00 74.25 HDTV 720P

4 1280*720 44.96 59.94 74.176 HDTV 720P

5 1920*1080 33.75 60.00 74.25 HDTV 1080I

6 1920*1080 33.72 59.94 74.176 HDTV 1080I

7 1920*1080 67.500 60 148.50 HDTV 1080P

8 1920*1080 67.432 59.939 148.352 HDTV 1080P

9 1920*1080 27.000 24.000 74.25 HDTV 1080P

10 1920*1080 26.97 23.976 74.176 HDTV 1080P

11 1920*1080 33.75 30.000 74.25 HDTV 1080P

12 1920*1080 33.71 29.97 74.176 HDTV 1080P

13 3840*2160 67.5 30.00 297.00 UDTV 2160P

14 3840*2160 56.25 25.00 297.00 UDTV 2160P

15 3840*2160 54.0 24.00 297.00 UDTV 2160P

Only for training and service purposes

- 8 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 9

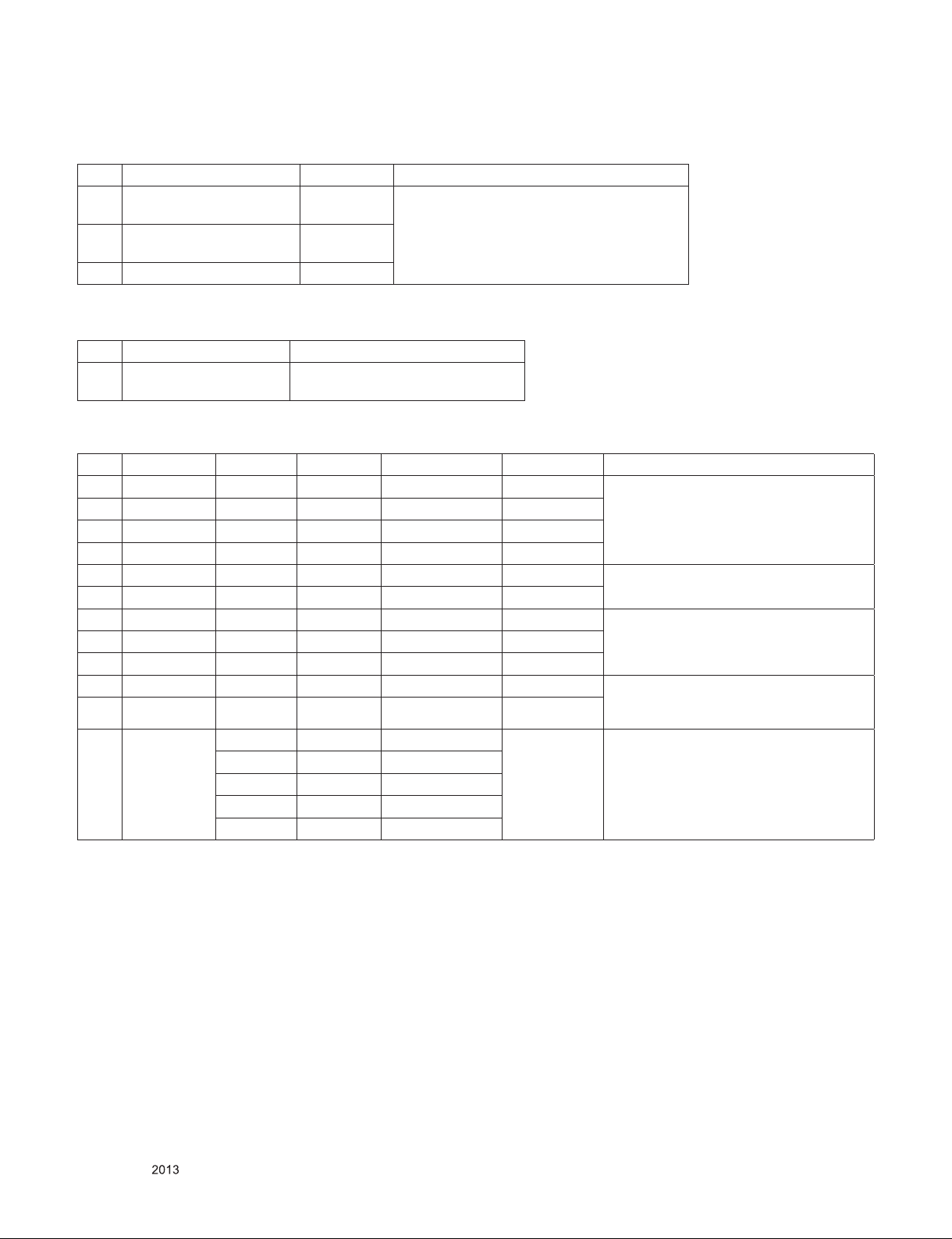

5.2. 3D Mode

(1) RF Input(3D supported mode manually)

No. Resolution Proposed 3D input proposed mode

1 HD - DTV

2 SD - DTV

3 SD - ATV(CVBS/SCART)

(2) RF Input(3D supported mode automatically)

No. Signal 3D input proposed mode

1 Frame Compatible

(3) HDMI 1.3 (3D supported mode manually)

No Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed 3D input proposed mode

1 720*480 31.5 60 27.03 SDTV 480P

2 720*576 31.25 50 27 SDTV 576P

3 1280*720 45.00 60.00 74.25 HDTV 720P

4 1280*720 37.500 50 74.25 HDTV 720P

5 1920*1080 33.75 60.00 74.25 HDTV 1080I

6 1920*1080 28.125 50.00 74.25 HDTV 1080I

7 1920*1080 27.00 24.00 74.25 HDTV 1080P

8 1920*1080 28.12 25 74.25 HDTV 1080P

9 1920*1080 33.75 30.00 74.25 HDTV 1080P

10 1920*1080 67.50 60.00 148.5 HDTV 1080P 2D to 3D, Side by Side(Half), Top & Bottom,

11 1920*1080 56.250 50 148.5 HDTV 1080P

53.95 23.976 297.00

54 24.00 296.703

12 3840*2160

56.25 25.00 297.00

61.43 29.970 297.00

67.5 30.00 296.703

1080I

720P

576P

576I

Side by Side(Half),

Top & Bottom

2D to 3D

Side by Side(Half)

Top & Bottom

HDTV 2160P

2D to 3D, Side by Side(Half), Top & Bottom,

Checker Board, Frame Sequential, Row

Interleaving, Column Interleaving

2D to 3D, Side by Side(Half), Top & Bottom

2D to 3D, Side by Side(Half), Top & Bottom,

Checker Board, Row Interleaving, Column

Interleaving

Checker Board, Single Frame Sequential,

Row Interleaving, Column Interleaving

2D to 3D,

Top & Bottom(half), Side by Side(half)

Only for training and service purposes

- 9 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 10

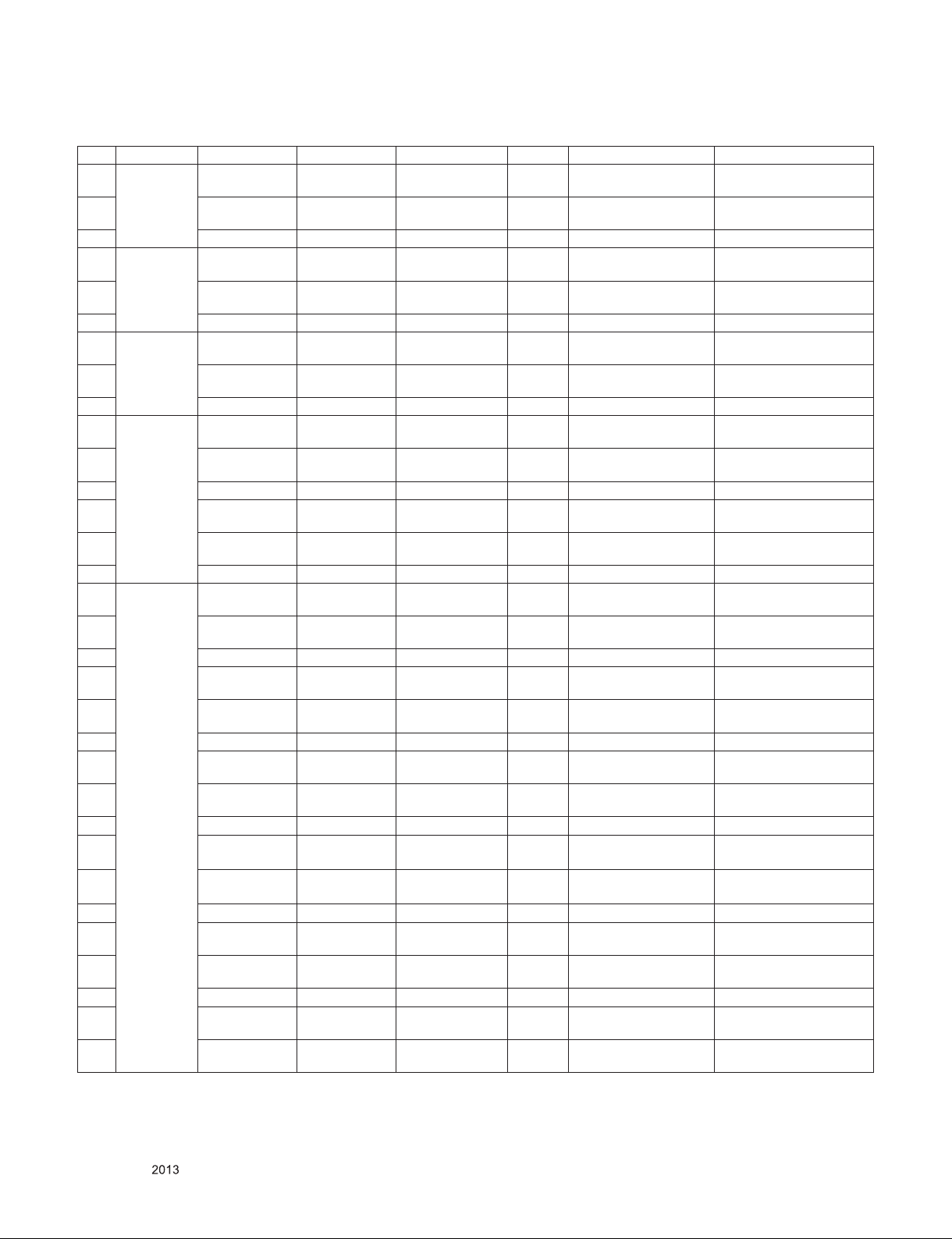

(4) HDMI 1.4b (3D supported mode automatically)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) VIC 3D input proposed mode Proposed

1

640*480

2 62.938/63 59.94/ 60 50.35/50.4 1

3 31.469 / 31.5 59.94/ 60 50.35/50.4 1 Side-by-side(Full) (SDTV 480P)

4

720*480

5 62.938/63 59.94 / 60 54/54.06 2,3

6 31.469 / 31.5 59.94 / 60 54/54.06 2,3 Side-by-side(Full) (SDTV 480P)

7

720*576

8 62.5 50 54 17,18

9 31.25 50 54 17,18 Side-by-side(Full) (SDTV 576P)

10

11 75 50 148.5 19

12 37.500 50 148.5 19 Side-by-side(Full) (HDTV 720P)

1280*720

13 44.96 / 45 59.94 / 60 74.18/74.25 4

14 89.91/90 59.94 / 60 148.35/148.5 4

15 44.96 / 45 59.94 / 60 148.35/148.5 4 Side-by-side(Full) (HDTV 720P)

16

17 67.432/67.50 59.94 / 60 148.35/148.5 5

18 33.72 / 33.75 59.94 / 60 148.35/148.5 5 Side-by-side(Full) (HDTV 1080I)

19 28.125 50.00 74.25 20

20 56.25 50.00 148.5 20

21 28.125 50.00 148.5 20 Side-by-side(Full) (HDTV 1080I)

22 26.97 / 27 23.97 / 24 74.18/74.25 32

23 43.94/54 23.97 / 24 148.35/148.5 32

24 26.97 / 27 23.97 / 24 148.35/148.5 32 Side-by-side(Full) (HDTV 1080P)

1920*1080

25 28.12 25 74.25 33

26 56.24 25 148.5 33

27 28.12 25 148.5 33 Side-by-side(Full) (HDTV 1080P)

28 33.716 / 33.75 29.976 / 30.00 74.18/74.25 34

29 67.432 / 67.5 29.976 / 30.00 148.35/148.5 34

30 33.716 / 33.75 29.976 / 30.00 148.35/148.5 34 Side-by-side(Full) (HDTV 1080P)

31 56.250 50 148.5 31

32 67.43 / 67.5 59.94 / 60 148.35/148.50 16

31.469 / 31.5 59.94/ 60 25.125/25.2 1

31.469 / 31.5 59.94 / 60 27.00/27.03 2,3

31.25 50 27 17,18

37.500 50 74.25 19

33.72 / 33.75 59.94 / 60 74.18/74.25 5

Top-and-Bottom

Side-by-side(half)

Frame packing

Line alternative

Top-and-Bottom

Side-by-side(half)

Frame packing

Line alternative

Top-and-Bottom

Side-by-side(half)

Frame packing

Line alternative

Top-and-Bottom

Side-by-side(half)

Frame packing

Field alternative

Top-and-Bottom

Side-by-side(half)

Frame packing

Line alternative

Top-and-Bottom

Side-by-side(half)

Frame packing

Line alternative

Top-and-Bottom

Side-by-side(half)

Frame packing

Field alternative

Top-and-Bottom

Side-by-side(half)

Frame packing

Field alternative

Top-and-Bottom

Side-by-side(half)

Frame packing

Line alternative

Top-and-Bottom

Side-by-side(half)

Frame packing

Line alternative

Top-and-Bottom

Side-by-side(half)

Top-and-Bottom

Side-by-side(half)

Secondary(SDTV 480P)

Secondary(SDTV 480P)

Secondary(SDTV 480P)

(SDTV 480P)

Secondary(SDTV 480P)

Secondary(SDTV 480P)

Secondary(SDTV 480P)

(SDTV 480P)

Secondary(SDTV 576P)

Secondary(SDTV 576P)

Secondary(SDTV 576P)

(SDTV 576P)

Primary(HDTV 720P)

Primary(HDTV 720P)

Primary(HDTV 720P)

(HDTV 720P)

Primary(HDTV 720P)

Primary(HDTV 720P)

Primary(HDTV 720P)

(HDTV 720P)

Secondary(HDTV 1080I)

Primary(HDTV 1080I)

Primary(HDTV 1080I)

(HDTV 1080I)

Secondary(HDTV 1080I)

Primary(HDTV 1080I)

Primary(HDTV 1080I)

(HDTV 1080I)

Primary(HDTV 1080P)

Primary(HDTV 1080P)

Primary(HDTV 1080P)

(HDTV 1080P)

Primary(HDTV 1080P)

Primary(HDTV 1080P)

Primary(HDTV 1080P)

(HDTV 1080P)

Secondary(HDTV 1080P)

Secondary(HDTV 1080P)

Secondary(HDTV 1080P)

(HDTV 1080P)

Primary(HDTV 1080P)

Secondary(HDTV 1080P)

Primary(HDTV 1080P)

Secondary(HDTV 1080P)

Only for training and service purposes

- 10 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 11

(5) HDMI-PC Input (3D) (3D supported mode manually)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed mode Proposed

1 1024*768 48.36 60 65

2 1360*768 47.71 60 85.5

3 1920*1080 67.500 60 148.50

54

4 3840*2160

5 3840*2160 - - 297 2D to 3D

(6) Component Input ( 3D) (3D supported mode manually)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock 3D input proposed mode Proposed

1 1280*720 37.5 50 74.25 2D to 3D, Side by Side(half), Top & Bottom HDTV 720P

2 1280*720 45.00 60.00 74.25 2D to 3D, Side by Side(half), Top & Bottom HDTV 720P

3 1280*720 44.96 59.94 74.176 2D to 3D, Side by Side(half), Top & Bottom HDTV 720P

4 1920*1080 33.75 60.00 74.25 2D to 3D, Side by Side(half), Top & Bottom HDTV 1080I

5 1920*1080 33.72 59.94 74.176 2D to 3D, Side by Side(half), Top & Bottom HDTV 1080I

6 1920*1080 28.12 50 74.25 2D to 3D, Side by Side(half), Top & Bottom HDTV 1080I

7 1920*1080 67.500 60 148.50 2D to 3D, Side by Side(half), Top & Bottom HDTV 1080P

8 1920*1080 67.432 59.94 148.352 2D to 3D, Side by Side(half), Top & Bottom HDTV 1080P

9 1920*1080 27.000 24.000 74.25 2D to 3D, Side by Side(half), Top & Bottom HDTV 1080P

10 1920*1080 28.12 25 74.25 2D to 3D, Side by Side(half), Top & Bottom HDTV 1080P

11 1920*1080 56.25 50 74.25 2D to 3D, Side by Side(half), Top & Bottom HDTV 1080P

12 1920*1080 26.97 23.976 74.176 2D to 3D, Side by Side(half), Top & Bottom HDTV 1080P

13 1920*1080 33.75 30.000 74.25 2D to 3D, Side by Side(half), Top & Bottom HDTV 1080P

14 1920*1080 33.71 29.97 74.176 2D to 3D, Side by Side(half), Top & Bottom HDTV 1080P

56.25

67.5

24

25

30

296.703

297

296.703

2D to 3D, Side by Side(half)

Top & Bottom

2D to 3D, Side by Side(half)

Top & Bottom

2D to 3D, Side by Side(half)

Top & Bottom, Checker Board,

Single Frame Sequential,

Row Interleaving,

Column Interleaving

HDTV 2160P

HDTV 768P

HDTV 768P

HDTV 1080P

2D to 3D,

Top & Bottom(half),

Side by Side(half),

640*350

720*400

640*480

800*600

1152*864

(7) USB, DLNA - Movie (3D) (3D supported mode manually)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed mode

1 Under 704x480 - - - 2D to 3D

Over 704x480

2

interlaced

3

Over 704x480

progressive

4 - others -

- - - 2D to 3D, Side by Side(Half), Top & Bottom

- 50 / 60 -

2D to 3D, Side by Side(Half), Top & Bottom, Checker Board,

Row Interleaving, Column Interleaving, Frame Sequential

2D to 3D, Side by Side(Half), Top & Bottom, Checker Board,

Row Interleaving, Column Interleaving

- 11 -

Only for training and service purposes

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 12

(8) USB, DLNA -Photo (3D) (3D supported mode manually)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed mode

1 Under 320x240 - - - 2D to 3D

2 Over 320x240 - - - 2D to 3D, Side by Side(Half), Top & Bottom

(9) USB, DLNA (3D) (3D supported mode automatically)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed mode

1 1080p 33.75 30 74.25

Side by Side(Half), Top & Bottom, Checker Board,

MPO(Photo), JPS(Photo)

(10) Miracast, Widi (3D supported mode manually)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed mode

1 1024x768p - 30 / 60 -

2D to 3D, Side by Side(Half), Top & Bottom2. 1280x720p - 30 / 60 -

3 1920x1080p 30 / 60

4 Others - 2D to 3D

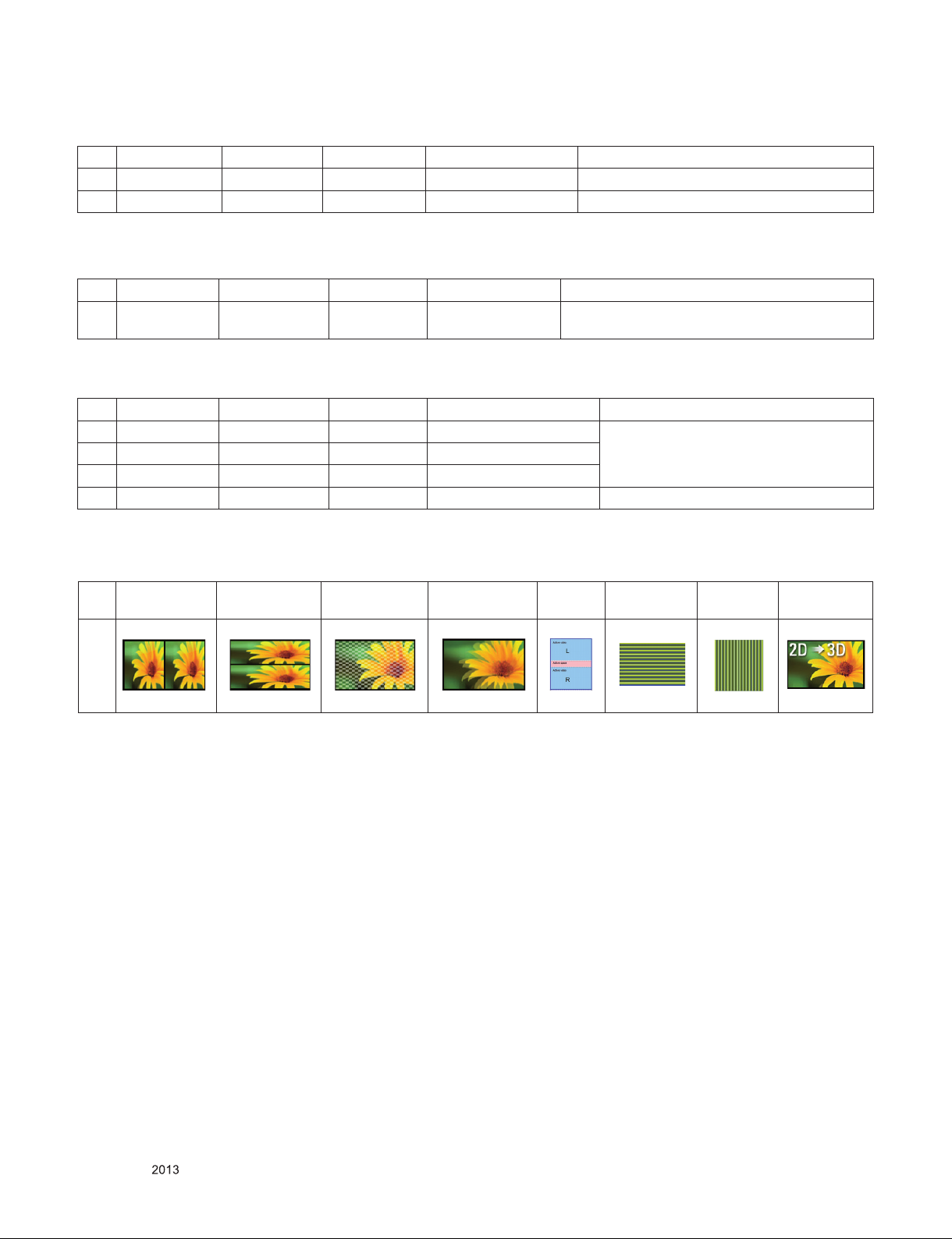

■ Remark: 3D Input mode

No. Side by Side Top & Bottom Checker board

Single Frame

Sequential

Frame

Packing

Line

Interleaving

Column

Interleaving

2D to 3D

1

ii.

iii.

iv.

v.

vi.

Only for training and service purposes

- 12 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 13

ADJUSTMENT INSTRUCTION

1. Application Range

This specification sheet is applied to all of the LED TV with

LD34E chassis.

2. Designation

(1) Because this is not a hot chassis, it is not necessary to

use an isolation transformer. However, the use of isolation

transformer will help protect test instrument.

(2) Adjustment must be done in the correct order.

(3) The adjustment must be performed in the circumstance of

25 °C ± 5 °C of temperature and 65 % ± 10 % of relative

humidity if there is no specific designation.

(4) The input voltage of the receiver must keep AC 100-240

V~, 50/60 Hz.

(5) The receiver must be operated for about 5 minutes prior to

the adjustment when module is in the circumstance of over

15.

In case of keeping module is in the circumstance of 0 °C, it

should be placed in the circumstance of above 15 °C for 2

hours.

In case of keeping module is in the circumstance of below

-20 °C, it should be placed in the circumstance of above 15

°C for 3 hours.

[Caution]

When still image is displayed for a period of 20 minutes or

longer (Especially where W/B scale is strong. Digital pattern

13ch and/or Cross hatch pattern 09ch), there can some

afterimage in the black level area.

3. Automatic Adjustment

3.1. ADC Adjustment

3.1.1. Overview

ADC adjustment is needed to find the optimum black level

and gain in Analog-to-Digital device and to compensate RGB

deviation.

3.1.3. Adjustment

(1) Adjustment method

- Using RS- 232, ad just items in the other shown in

"3.1.3.3)"

(2) Adj. protocol

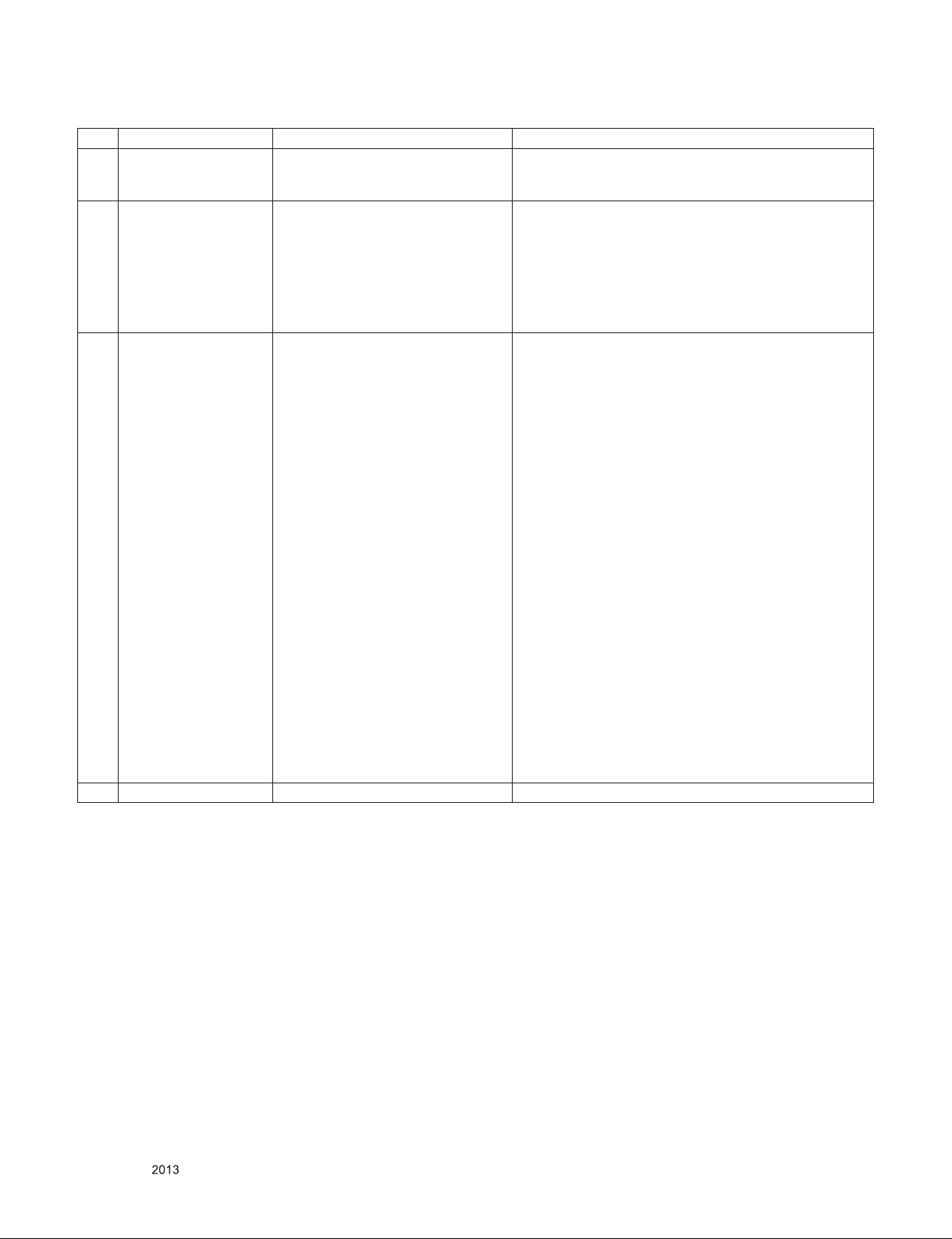

Protocol Command Set ACK

Enter adj. mode aa 00 00 a 00 OK00x

Source change

Begin adj. ad 00 10

Return adj. result

Read adj. data

Conrm adj. ad 00 99

End adj. aa 00 90 a 00 OK90x

xb 00 04

xb 00 06

(main)

ad 00 20

(sub )

ad 00 21

b 00 OK04x (Adjust 480i, 1080p Comp1 )

b 00 OK06x (Adjust 1920*1080 SCART RGB)

OKx (Case of Success)

NGx (Case of Fail)

(main)

000000000000000000000000007c007b006dx

(Sub)

000000070000000000000000007c00830077x

NG 03 00x (Fail)

NG 03 01x (Fail)

NG 03 02x (Fail)

OK 03 03x (Success)

Ref.) ADC Adj. RS232C Protocol_Ver1.0

(3) Adj. order

- aa 00 00 [Enter ADC adj. mode]

- xb 00 04 [Change input source to Component1 (480i&

1080p)]

- ad 00 10 [Adjust 480i&1080p Comp1]

- xb 00 06 [Change input source to RGB(1024*768)]

- ad 00 10 [Adjust 1920*1080 SCART RGB]

- ad 00 90 End adj.

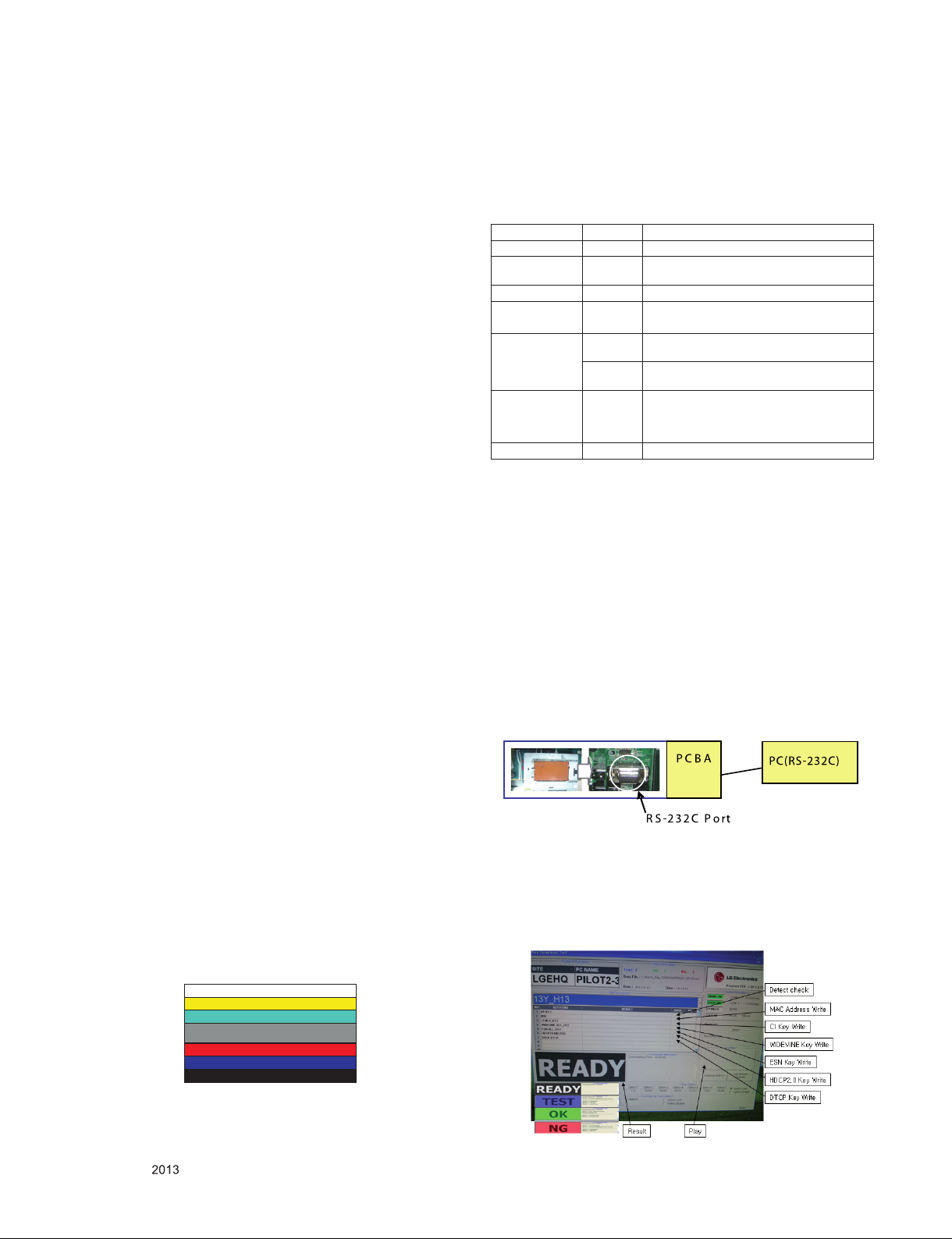

3.2. MAC address D/L, CI+ key D/L, Widevine

key D/L, ESN key D/L, HDCP key D/L,

DTCP key D/L

Connect: PCBA Jig → RS-232C Port== PC → RS-232C Port

Communication Prot connection

3.1.2. Equipment & Condition

(1) USB to RS-232C Jig

(2) MSPG-925 Series Pattern Gen erator (MSPG-925FA,

pattern - 65)

- Resolution : 480i Comp1

1080P Comp1

1920*1080P SCART RGB

- Pattern : Horizontal 100% Color Bar Pattern

- Pattern level : 0.7 ± 0.1 Vp-p

- Image

Only for training and service purposes

- 13 -

▪ Com 1,2,3,4 and 115200(Baudrate)

Mode check: Online Only

▪ Check the test process: DETECT → MAC → CI → Widevine

→ ESN → HDCP → DTCP

▪ Play: START

▪ Result: Ready, Test, OK or NG

▪ Printer Out (MAC Address Label)

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 14

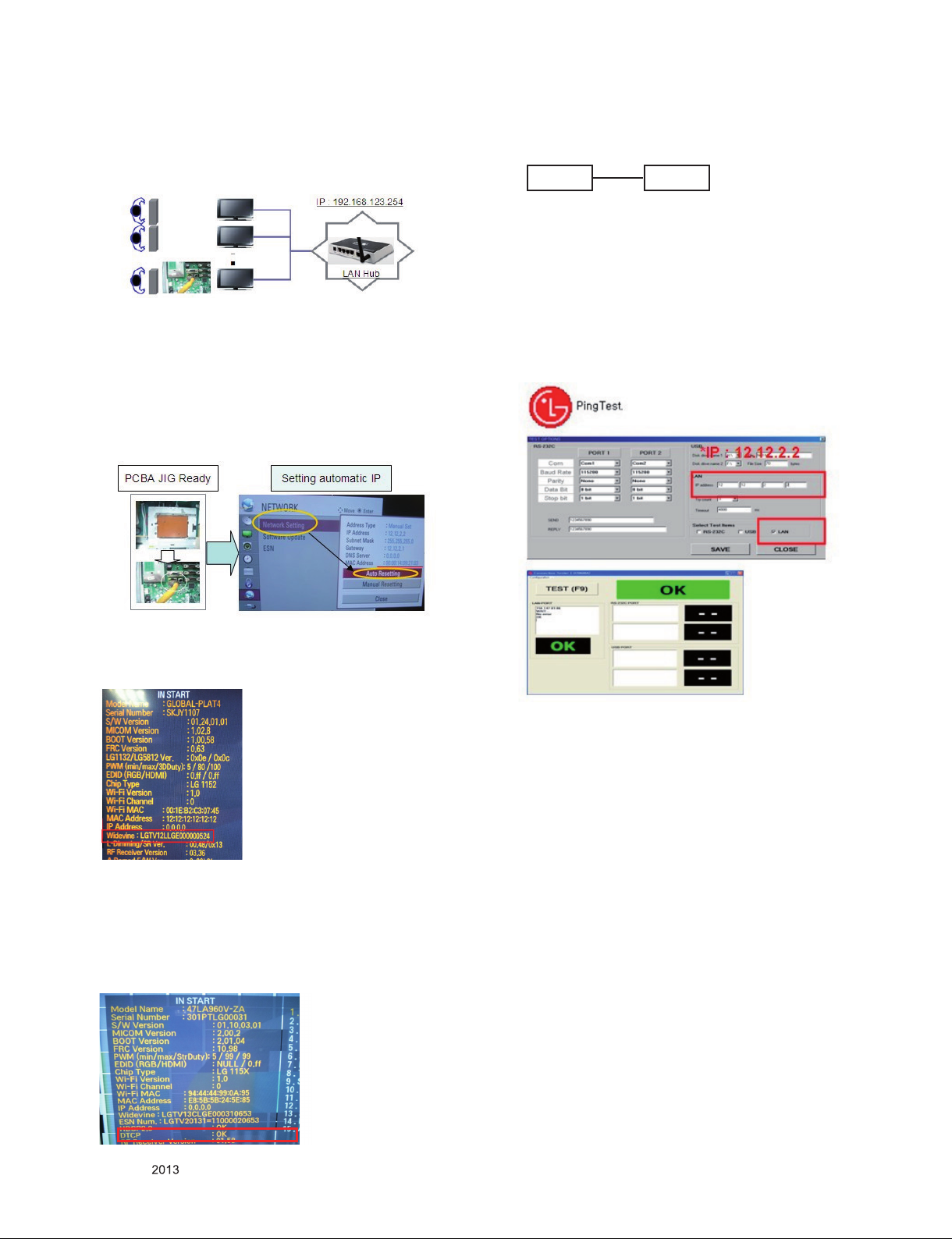

3.3. LAN Inspection

3.3.1. Equipment & Condition

▪ Each other connection to LAN Port of IP Hub and Jig

3.3.2. LAN inspection solution

▪ LAN Port connection with PCB

▪ Network setting at MENU Mode of TV

▪ Setting automatic IP

▪ Setting state confirmation

→ If automatic setting is finished, you confirm IP and MAC

Address.

3.4. LAN PORT INSPECTION(PING TEST)

Connect SET → LAN port == PC → LAN Port

SET PC

3.4.1. Equipment setting

(1) Play the LAN Port Test PROGRAM.

(2) Input IP set up for an inspection to Test Program.

*IP Number : 12.12.2.2

3.4.2. LAN PORT inspection(PING TEST)

(1) Play the LAN Port Test Program.

(2) Connect each other LAN Port Jack.

(3) Play Test (F9) button and confirm OK Message.

(4) Remove LAN cable.

3.3.3. WIDEVINE key Inspection

- Confirm key input data at the "IN START" MENU Mode.

3.3.4. DTCP Inspection

- Confirm Key input at the “IN START” MENU Mode

- Below DTCP check on “IN START” MENU is enabled only

for Models which “DTCP key” tool option is “ON”

- Only EU suffix mod els DT CP key option is on. (ex .

47LA790V-ZA.KEUYLJG)

Only for training and service purposes

- 14 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 15

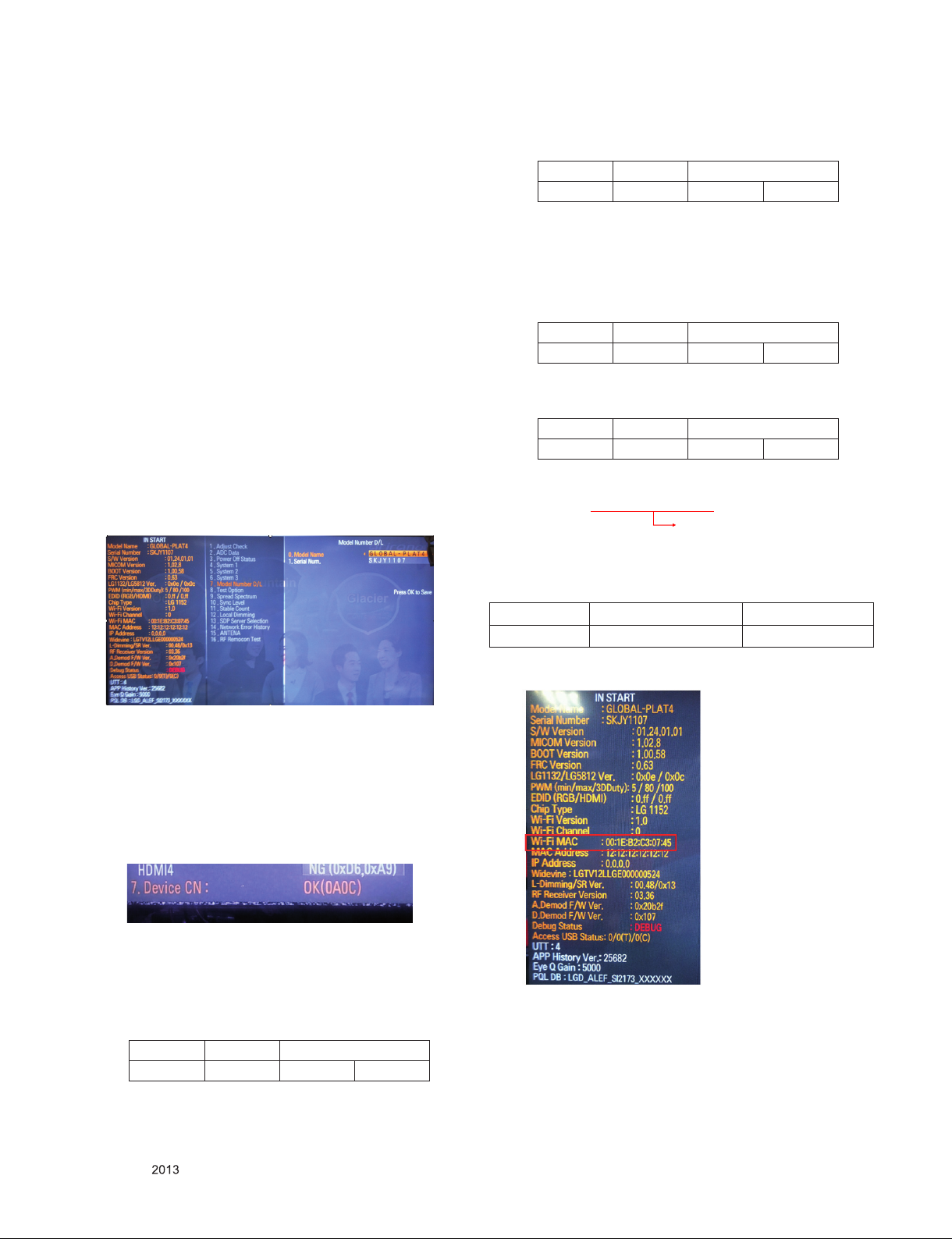

3.5. Model name & Serial number Download

3.5.1. Model name & Serial number D/L

▪ Press "Power on" key of service remote control.

(Baud rate : 115200 bps)

▪ Connect RS-232C Signal to USB Cable to USB.

▪ Write Serial number by use USB port.

▪ Must check the serial number at Instart menu.

3.5.2. Method & notice

(1) Serial number D/L is using of scan equipment.

(2) Setting of scan equipment operated by Manufacturing

Technology Group.

(3) Serial number D/L must be conformed when it is produced

in production line, because serial number D/L is mandatory

by D-book 4.0.

* Manual Download (Model Name and Serial Number)

If the TV set is downloaded by OTA or service man, sometimes

model name or serial number is initialized.(Not always)

It is impossible to download by bar code scan, so It need

Manual download.

1) Press the "Instart" key of Adjustment remote control.

2) Go to the menu "7.Model Number D/L" like below photo.

3) Input the Factory model name(ex 47LM960V-ZB) or Serial

number like photo.

2) Check the key download for transmitted command

(RS232: ci 00 10)

CMD 1 CMD 2 Data 0

C I 1 0

3) Result value

- Normally status for download : OKx

- Abnormally status for download : NGx

3.6.2. Check the method of CI+ key value(RS232)

1) Into the main ass’y mode(RS232: aa 00 00)

CMD 1 CMD 2 Data 0

A A 0 0

2) Check the mothed of CI+ key by command

(RS232: ci 00 20)

CMD 1 CMD 2 Data 0

C I 2 0

3) Result value

i 01 OK 1d1852d21c1ed5dcx

CI+ Key Value

3.7. WIFI MAC ADDRESS CHECK

(1) Using RS232 Command

H-freq(kHz) V-freq.(Hz)

Transmission [A][I][][Set ID][][20][Cr] [O][K][X] or [NG]

4) Check the model name Instart menu. → Factory name

displayed. (ex 47LM960V-ZB)

5) Check the Diagnost ics.(DTV country only) → Buyer

model displayed. (ex 47LM960V-ZB)

3.6. CI+ Key checking method

* Check the Section 3.2

Check whether the key was downloaded or not at ‘In Start’

menu. (Refer to below).

=> Check the Download to CI+ Key value in LGset.

3.6.1. Check the method of CI+ Key value

(1) Check the method on Instart menu

(2) Check the method of RS232C Command

1) Into the main ass’y mode(RS232: aa 00 00)

CMD 1 CMD 2 Data 0

A A 0 0

(2) Check the menu on in-start

Only for training and service purposes

- 15 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 16

4. Manual Adjustment

* ADC adjustment is not needed because of OTP(Auto ADC

adjustment)

4.1. EDID(The Extended Display Identification

Data)/DDC(Display Data Channel) download

4.1.1. Overview

It is a VESA regulation. A PC or a MNT will display an optimal

resolution through information sharing without any necessity

of user input. It is a realization of "Plug and Play".

4.1.2. Equipment

- Since embedded EDID data is used, EDID download JIG,

HDMI cable and D-sub cable are not need.

- Adjustment remote control

4.1.3. Download method

(1) Press "ADJ" key on the Adjustment remote control then

select "12.EDID D/L", By pressing "Enter" key, enter EDID

D/L menu.

(2) Select "Start" button by pressing "Enter" key, HDMI1/

HDMI2/ HDMI3 are writing and display OK or NG.

For HDMI EDID

DVI-D to HDMI or HDMI to HDMI

ⓓ Model Name(Hex): LGTV

Cf) TV set’s model name in EDID data is below.

MODEL NAME(HEX)

LG TV 00 00 00 FC 00 4C 47 20 54 56 0A 20 20 20 20 20 20 20 (LG TV)

ⓔ Checksum(LG TV): Changeable by total EDID data.

EDID C/S data

check sum (Hex)

Block 0 42

Block 1

FHD

HDMI

23 (HDMI1)

13 (HDMI2)

ⓕ Vendor Specific(HDMI)

INPUT MODEL NAME(HEX)

HDMI1 78030C001000801E

HDMI2 78030C002000801E

(1) EDID

# HDMI 1(C/S : E8 E0)

EDID Block 0, Bytes 0-127 [00H-7FH]

0 1 2 3 4 5 6 7 8 9 A B C D E F

00 00 FF FF FF FF FF FF 00 1E 6D 01 00 01 01 01 01

10 01 17 01 03 80 A0 5A 78 0A EE 91 A3 5 4 4C 99 26

20 0 F 50 54 A1 08 00 31 40 45 40 61 40 71 40 81 80

30 01 01 01 01 01 01 02 3A 80 18 71 3 8 2D 40 58 2C

40 45 00 40 84 63 00 00 1E 66 21 50 B0 51 0 0 1B 30

50 40 70 36 00 40 84 63 00 00 1E 00 00 00 FD 00 3A

60 3E 1E 53 10 00 0A 20 20 20 20 20 20 00 00 00 FC

70 00 4C 47 20 54 56 0A 20 20 20 20 20 20 20 01 E8

4.1.4. EDID DATA

▪ HDMI

0x00 0x01 0x02 0x03 0x04 0x05 0x06 0x07 0x08 0x09 0x0A 0x0B 0x0C 0x0D 0x0E 0x0F

0x00 00 FF FF FF FF FF FF 00 1E 6D

ⓒ

0x10

0x20 0F 50 54 A1 08 00 31 40 45 40 61 40 71 40 81 80

0x30 01 01 01 01 01 01 02 3A 80 18 71 38 2D 40 58 2C

0x40 45 00 40 84 63 00 00 1E 66 21 50 B0 51 00 1B 30

0x50 40 70 36 00 40 84 63 00 00 1E 00 00 00 FD 00 3A

0x60 3E 1E 53 10 00 0A 20 20 20 20 20 20

0x70

0x80 02 03 3A F1 4E 10 9F 04 13 05 14 03 02 12 20 21

0x90 22 15 01 29 3D 06 C0 15 07 50

0xA0

0xB0

0xC0 2D 40 58 2C 45 00 40 84 63 00 00 1E 01 1D 80 18

0xD0 71 1C 16 20 58 2C 25 00 40 84 63 00 00 9E 01 1D

0xE0 00 72 51 D0 1E 20 6E 28 55 00 40 84 63 00 00 1E

0xF0 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

01 03 80 A0 5A 78 0A EE 91 A3 54 4C 99 26

ⓓ

ⓕ

ⓕ

E3 05 03 01 02 3A 80 18 71 38

▪ Detail EDID Options are below

- HDMI1 ~ HDMI3

- In the data of EDID, bellows may be different by S/W or

Input mode.

ⓐ Product ID

MODEL NAME HEX EDID Table DDC Function

HD/FHD Model 0001 01 00 Analog/Digital

ⓑ Serial No: Controlled on production line.

ⓒ Month, Year: Controlled on production line:

ex) Monthly : ‘01’ → ‘01’, Year : ‘2013’ → ‘17’

ⓐ ⓑ

ⓓ

01

09 57 07 ⓕ

ⓔ1

ⓔ2

EDID Block 1, Bytes 128-255 [80H-FFH]

0 1 2 3 4 5 6 7 8 9 A B C D E F

80 02 03 3E F1 4E 10 9F 04 13 05 14 03 02 12 20 21

90 22 15 01 29 3D 06 C0 15 07 50 09 57 07 7C 03 0C

A0 00 10 00 B8 3C 20 C0 8E 01 02 03 04 01 4F 3F FC

B0 08 10 18 10 06 10 16 10 28 10 E3 05 03 01 02 3A

C0 80 18 71 38 2D 40 58 2C 45 00 40 84 63 00 00 1E

D0 01 1D 80 18 71 1C 16 20 58 2C 25 00 40 84 63 00

E0 00 9E 01 1D 00 72 51 D0 1E 20 6E 28 55 00 40 84

F0 63 00 00 1E 00 00 00 00 00 00 00 00 00 00 00 E0

# HDMI 2(C/S : E8 D0)

EDID Block 0, Bytes 0-127 [00H-7FH]

0 1 2 3 4 5 6 7 8 9 A B C D E F

00 00 FF FF FF FF FF FF 00 1E 6D 01 00 01 01 01 01

10 01 17 01 03 80 A0 5A 78 0A EE 91 A3 54 4C 99 26

20 0F 50 54 A1 08 00 31 40 45 40 61 40 71 40 81 80

30 01 01 01 01 01 01 02 3A 80 18 71 38 2D 40 58 2C

40 45 00 40 84 63 00 00 1E 66 21 50 B0 51 00 1B 30

50 40 70 36 00 40 84 63 00 00 1E 00 00 00 FD 00 3A

60 3E 1E 53 10 00 0A 20 20 20 20 20 20 00 00 00 FC

70 00 4C 47 20 54 56 0A 20 20 20 20 20 20 20 01 E8

EDID Block 1, Bytes 128-255 [80H-FFH]

0 0 1 2 3 4 5 6 7 8 9 A B C D E F

80 02 03 3E F1 4E 10 9F 04 13 05 14 03 02 12 20 21

90 22 15 01 29 3D 06 C0 15 07 50 09 57 07 7C 03 0C

A0 00 10 00 B8 3C 20 C0 8E 01 02 03 04 01 4F 3F FC

B0 08 10 18 10 06 10 16 10 28 10 E3 05 03 01 02 3A

C0 80 18 71 38 2D 40 58 2C 45 00 40 84 63 00 00 1E

D0 01 1D 80 18 71 1C 16 20 58 2C 25 00 40 84 63 00

E0 00 9E 01 1D 00 72 51 D0 1E 20 6E 28 55 00 40 84

F0 63 00 00 1E 00 00 00 00 00 00 00 00 00 00 00 D0

Only for training and service purposes

- 16 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 17

# HDMI 3(C/S : E8 C0)

EDID Block 0, Bytes 0-127 [00H-7FH]

0 0 1 2 3 4 5 6 7 8 9 A B C D E F

00 00 FF FF FF FF FF FF 00 1E 6D 01 00 01 01 01 01

10 01 17 01 03 80 A0 5A 78 0A EE 91 A3 54 4C 99 26

20 0F 50 54 A1 08 00 31 40 45 40 61 40 71 40 81 80

30 01 01 01 01 01 01 02 3A 80 18 71 38 2D 40 58 2C

40 45 00 40 84 63 00 00 1E 66 21 50 B0 51 00 1B 30

50 40 70 36 00 40 84 63 00 00 1E 00 00 00 FD 00 3A

60 3E 1E 53 10 00 0A 20 20 20 20 20 20 00 00 00 FC

70 00 4C 47 20 54 56 0A 20 20 20 20 20 20 20 01 E8

EDID Block 1, Bytes 128-255 [80H-FFH]

0 0 1 2 3 4 5 6 7 8 9 A B C D E F

80 02 03 3E F1 4E 10 9F 04 13 05 14 03 02 12 20 21

90 22 15 01 29 3D 06 C0 15 07 50 09 57 07 7C 03 0C

A0 00 10 00 B8 3C 20 C0 8E 01 02 03 04 01 4F 3F FC

B0 08 10 18 10 06 10 16 10 28 10 E3 05 03 01 02 3A

C0 80 18 71 38 2D 40 58 2C 45 00 40 84 63 00 00 1E

D0 01 1D 80 18 71 1C 16 20 58 2C 25 00 40 84 63 00

E0 00 9E 01 1D 00 72 51 D0 1E 20 6E 28 55 00 40 84

F0 63 00 00 1E 00 00 00 00 00 00 00 00 00 00 00 C0

4.2. White Balance Adjustment

4.2.1. Overview

▪ W/B adj. Objective & How-it-works

(1) Objective: To reduce each Panel's W/B deviation

(2) How-it-works : When R/G/B gain in the OSD is at 192, it

means the panel is at its Full Dynamic Range. In order to

prevent saturation of Full Dynamic range and data, one

of R/G/B is fixed at 192, and the other two is lowered to

find the desired value.

(3) Adjustment condition : normal temperature

1) Surrounding Temperature : 25 °C ± 5 °C

2) Warm-up time: About 5 Min

3) Surrounding Humidity : 20 % ~ 80 %

4) Before White balance adjustment, Keep power on

status, don’t power off

4.2.2. Adj. condition and cautionary items

(1) Lighting condition in surrounding area surrounding lighting

should be lower 10 lux. Try to isolate adj. area into dark

surrounding.

(2) Probe location: Color Analyzer (CA-210) probe should be

within 10cm and perpendicular of the module surface

(80°~ 100°)

(3) Aging time

1) After Aging Start, Keep the Power ON status during 5

Minutes.

2) In case of LCD, Back-light on should be checked using

no signal or Full-white pattern.

4.2.3. Equipment

(1) Color Analyzer: CA-210 (LED Module : CH 14)

(2) Adjustment Computer(During auto adj., RS-232C protocol

is needed)

(3) Adjustment Remote control

(4) Video Signal Generator MSPG-925F 720p/216-Gray

(Model: 217, Pattern: 49)

→ Only when internal pattern is not available

▪ Color Analyzer Matrix should be calibrated using CS-100.

4.2.4. Equipment connection MAP

Co lor Anal yze r

Pro be

RS -232 C

Pattern Gen era to r

Sig nal Sou rce

* If TV internal pattern is used, not needed

RS- 232 C

Co mp ute r

RS- 232 C

4.2.5. Adj. Command (Protocol)

<Command Format>

START 6E A 50 A LEN A 03 A CMD A 00 A VAL A CS STOP

- LEN: Number of Data Byte to be sent

- CMD: Command

- VAL: FOS Data value

- CS: Checksum of sent data

- A: Acknowledge

Ex) [Send: JA_00_DD] / [Ack: A_00_okDDX]

▪ RS-232C Command used during auto-adjustment.

RS-232C COMMAND

[CMD ID DATA]

wb 00 00 Begin White Balance adjustment

wb 00 10 Gain adjustment(internal white pattern)

wb 00 1f Gain adjustment completed

wb 00 20 Offset adjustment(internal white pattern)

wb 00 2f Offset adjustment completed

wb 00 ff

End White Balance adjustment

(internal pattern disappears )

Ex) wb 00 00 -> Begin white balance auto-adj.

wb 00 10 -> Gain adj.

ja 00 ff -> Adj. data

jb 00 c0

...

...

wb 00 1f → Gain adj. completed

*(wb 00 20(Start), wb 00 2f(end)) → Off-set adj.

wb 00 ff → End white balance auto-adj.

▪ Adj. Map

Command

(lower caseASCII)

CMD1 CMD2 MIN MAX

Cool

Medium

Warm

Adj. item

R Gain j g 00 C0

G Gain j h 00 C0

B Gain j i 00 C0

R Cut

G Cut

B Cut

R Gain j a 00 C0

G Gain j b 00 C0

B Gain j c 00 C0

R Cut

G Cut

B Cut

R Gain j d 00 C0

G Gain j e 00 C0

B Gain j f 00 C0

R Cut

G Cut

Explantion

Data Range

(Hex.)

Default

(Decimal)

Only for training and service purposes

- 17 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 18

4.2.6. Adj. method

(1) Auto adj. method

1) Set TV in adj. mode using POWER ON key.

2) Zero calibrate probe then place it on the center of the

Display.

3) Connect Cable.(RS-232C to USB)

4) Select mode in adj. Program and begin adj.

5) When adj. is complete (OK Sign), check adj. status pre

mode. (Warm, Medium, Cool)

6) Remove probe and RS-232C cable to complete adj.

▪ W/B Adj. must begin as start command “wb 00 00” , and

finish as end command “wb 00 ff”, and Adj. offset if need.

(2) Manual adjustment method (84LA98)

1) Set TV in Adj. mode using POWER ON.

2) Zero Calibrate the probe of Color Analyzer, then place it

on the center of LCD module within 10 cm of the surface.

3) Press ADJ key → EZ adjust using adj. R/C → 7. WhiteBalance then press the cursor to the right(key ►). When

right key(►) is pressed 216 Gray internal pattern will be

displayed

4) One of R Gain / G Gain / B Gain should be fixed at 192,

and the rest will be lowered to meet the desired value.

5) Adj. is performed in COOL, MEDIUM, WARM 3 modes

of color temperature.

** G-fix adjustment

Adjust modes(Cool), Fix the G gain to 172(default data)

and change the others (G/B Gain).

Adjust two modes(Medium/Warm), Fix the one of R/G/B

gain to 192(default data) and decrease the others.

▪ If internal pattern is not available, use RF input. In EZ Adj.

menu 7.White Balance, you can select one of 2 Testpattern: ON, OFF. Default is inner(ON). By selecting OFF,

you can adjust using RF signal in 216 Gray pattern

* CASE Medium / Warm

First adjust the coordinate far away from the target

value(x, y).

1. x, y > target

i) Decrease the R, G.

2. x, y < target

i) First decrease the B gain,

ii) Decrease the one of the others.

3. x > target, y < target

i) First decrease B, so make y a little more than the target.

ii) Adjust x value by decreasing the R

4. x < target, y > target

i) First decrease B, so make x a little more than the target.

ii) Adjust y value by decreasing the G

4.2.7. Reference (White balance Adj. coordinate and

color temperature)

▪ Luminance : 216 Gray

▪ Standard color coordinate and temperature using CS-1000

(over 26 inch)

Mode

Cool 0.271 0.270 13000 K 0.0000

Medium 0.285 0.293 9300 K 0.0000

Warm 0.310 0.325 6500 K 0.0000

▪ Standard color coordinate and temperature using CA-210(CH 18)

Mode

Cool 0.271 ± 0.002 0.270 ± 0.002 13000 K 0.0000

Medium 0.285 ± 0.002 0.293 ± 0.002 9300 K 0.0000

Warm 0.310 ± 0.002 0.325 ± 0.002 6500 K 0.0000

Coordinate

x y

Coordinate

x y

Temp ∆uv

Temp ∆uv

* CASE Cool

First adjust the coordinate far away from the target

value(x, y).

1. x, y > target

i) Decrease the R, G.

2. x, y < target

i) First decrease the B gain,

ii) Decrease the one of the others.

3. x > target, y < target

i) First decrease B, so make y a little more than the target.

ii) Adjust x value by decreasing the R

4. x < target, y > target

i) First decrease B, so make x a little more than the target.

ii) Adjust x value by decreasing the G

How to adjust

1. If G gain is adjusted over 172 and R gain and B gain

less than 192 , Adjust is O.K.

2. If G gain is less than 172 , increase G gain by up to

172, and then increase R gain and B gain same

amount of increasing G gain.

3. If R gain or B gain is over 255 , Readjust G gain less

than 172, Conform to R gain is 255 or B gain is 255

Only for training and service purposes

- 18 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 19

4.2.8. EDGE LED White balance table

(1) EDGE LED module change color coordinate because of

aging time.

(2) Apply under the color coordinate table, for compensated

aging time.

(3) Normal line(Edge, Direct)

- Gumi (Mar ~ Dec) & Global

NC4.0

Aging time

(Min)

1 0-2 281 287 295 310 320 342

2 3-5 280 285 294 308 319 340

3 6-9 278 284 292 307 317 339

4 10-19 276 281 290 304 315 336

5 20-35 275 277 289 300 314 332

6 36-49 274 274 288 297 313 329

7 50-79 273 272 287 295 312 327

8 80-119 272 271 286 294 311 326

9 Over 120 271 270 285 293 310 325

Cool Medium Warm

X y x y x y

271 270 285 293 313 329

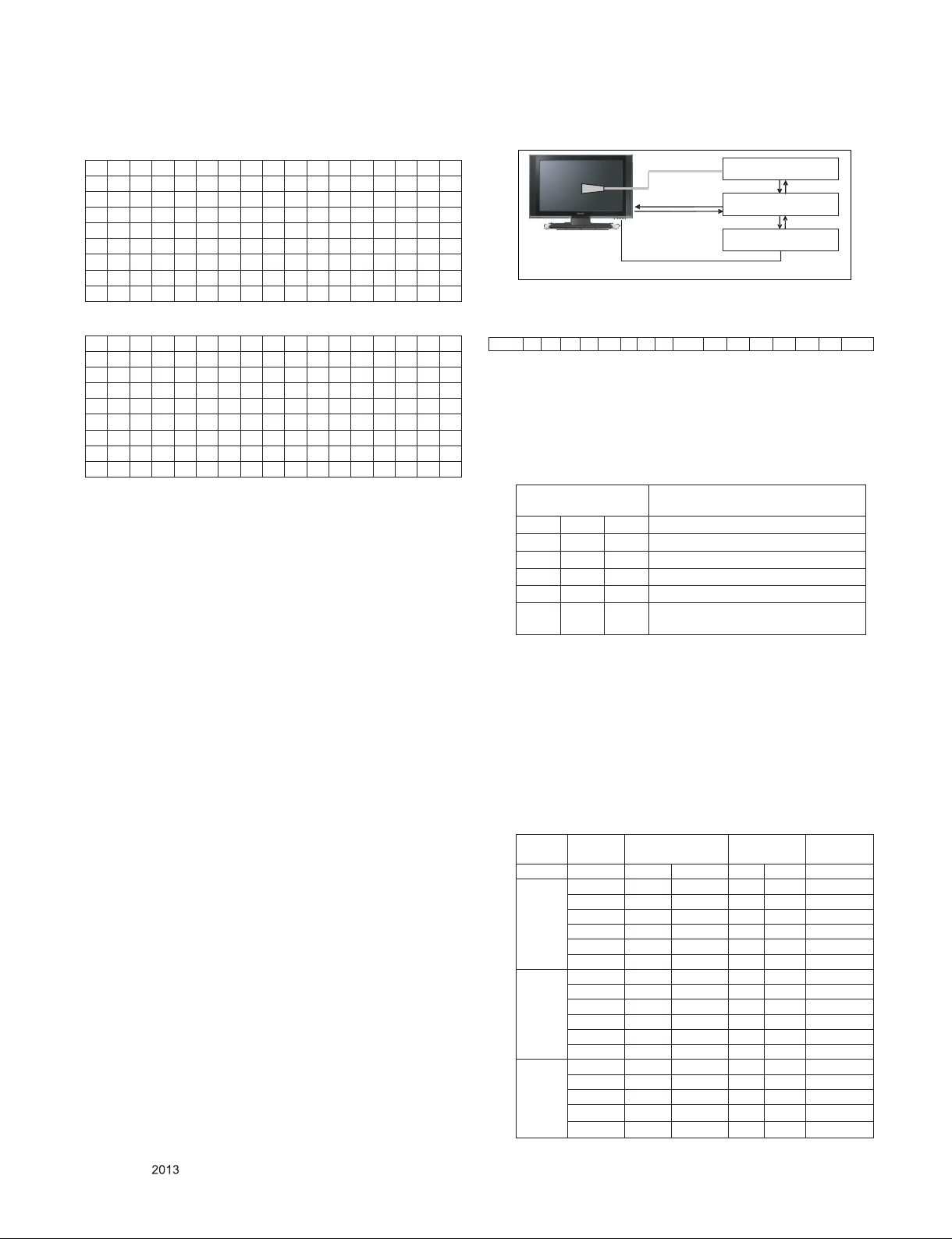

4.3. Local Dimming Function Check

Step 1) Turn on TV.

Step 2) Press “TILT” key on the Adj. R/C

Step 3) At the Local Dimming mode, module Edge Backlight

moving left to right. Back light of IOP module moving

Step 4) confirm the Local Dimming mode.

Step 5) Press “exit” key.

(4) Aging Chamber

NC4.0

Aging time

(Min)

1 0-5 280 285 294 308 319 340

2 6-10 276 280 290 303 315 335

3 11-20 272 275 286 298 311 330

4 21-30 269 272 283 295 308 327

5 31-40 267 268 281 291 306 323

6 41-50 266 265 280 288 305 320

7 51-80 265 263 279 286 304 318

8 81-119 264 261 278 284 303 316

9 Over 120 264 260 278 283 303 315

Cool Medium Warm

X y x y x y

271 270 285 293 313 329

(5) Gumi winter table(Jan, Fab) - Gumi producing model use only

(Normal line)

NC4.0

Aging time

(Min)

1 0-2 283 292 297 315 322 347

2 3-5 282 290 296 313 321 345

3 6-9 280 288 294 311 319 343

4 10-19 277 284 291 307 316 339

5 20-35 275 279 289 302 314 334

6 36-49 274 275 288 298 313 330

7 50-79 273 272 287 295 312 327

8 80-119 272 271 286 294 311 326

9 Over 120 271 270 285 293 310 325

Cool Medium Warm

X y x y x y

271 270 285 293 313 329

4.4. Magic Motion Remote control test

(1) Equipment : RF Remote control for test, IR-KEY-Code

Remote control for test

(2) You must confirm the battery power of RF-Remote control

before test(recommend that change the battery per every lot)

(3) Sequence (test)

1) if you select the ‘start key(wheel)’ on the controller, you

can pairing with the TV SET.

2) You can check the cursor on the TV Screen, when select

the ‘Wheel Key’ on the control.

3) You must remove the pairing with the TV Set by select

‘Back + Home Key’ on the control.

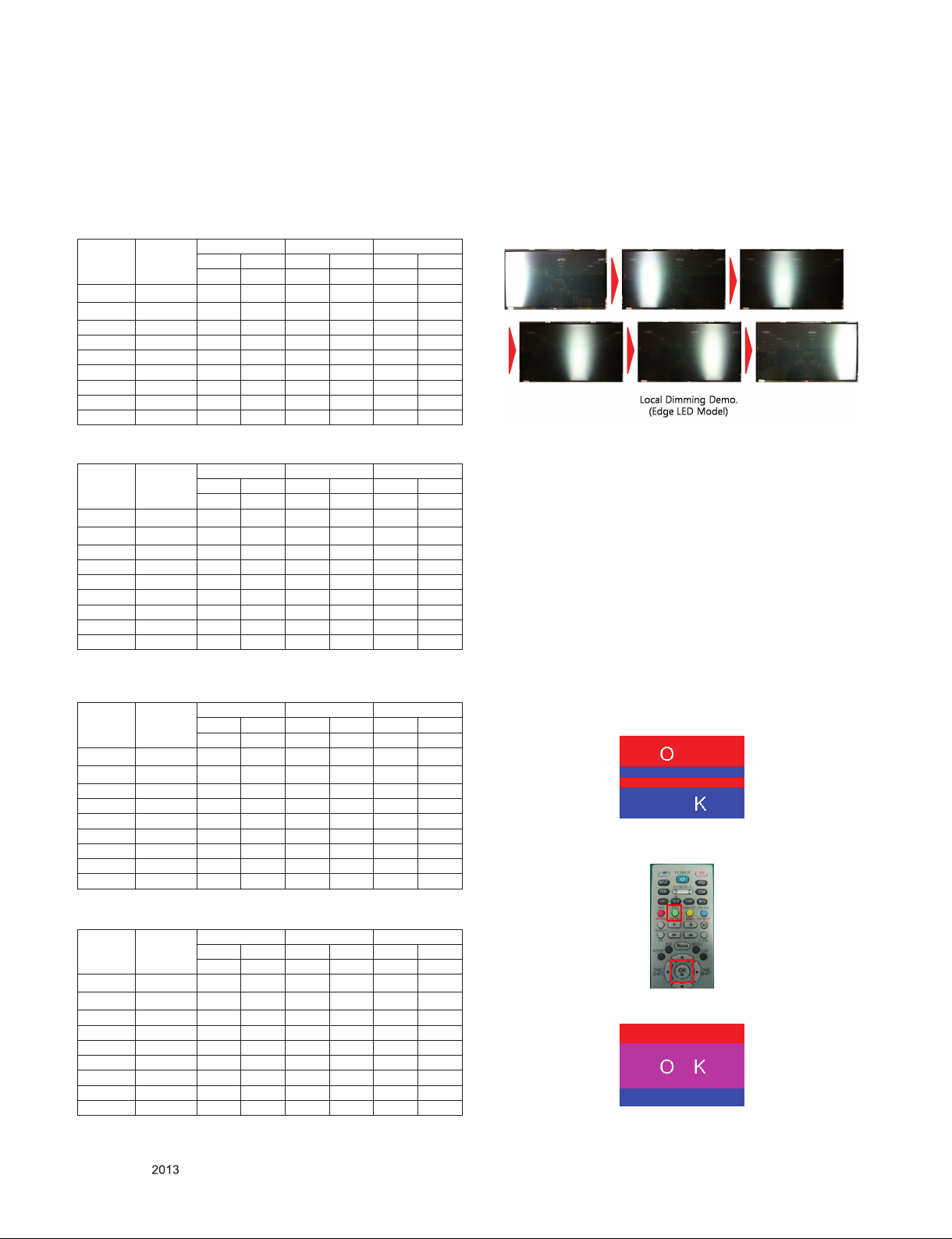

4.5. 3D function test

(Pattern Generator MSHG-600, MSPG-6100[Support HDMI1.4])

* HDMI mode NO. 872 , pattern No.83

(1) Please input 3D test pattern like below.

(2) When 3D OSD appear automatically, then select green

key.

(aging chamber)

NC4.0

Aging time

(Min)

1 0-5 280 285 294 308 319 340

2 6-10 276 280 290 303 315 335

3 11-20 272 275 286 298 311 330

4 21-30 269 272 283 295 308 327

5 31-40 267 268 281 291 306 323

6 41-50 266 265 280 288 305 320

7 51-80 265 263 279 286 304 318

8 81-119 264 261 278 284 303 316

9 Over 120 264 260 278 283 303 315

Cool Medium Warm

X y x y x y

271 270 285 293 313 329

Only for training and service purposes

- 19 -

(3) Don't wear a 3D Glasses, check the picture like below.

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 20

4.6. Wi-Fi Test

Step 1) Turn on TV

Step 2) Select Network Connection option in Network Menu.

Step 3) Select Start Connection button in Network Connection.

Step 4) If the system finds any AP like blow PIC, it is working

well.

4.8. Inspection of light scattering

▪ Test Method

(1) Push “Power only” key.

(2) Push “HDMI” hot key.

(3) Inspect whether light scattering is occurred in internal

black pattern or not.

(4) Push “Power only” key.

4.9. Option selection per country

4.9.1. Overview

- Option selection is only done for models in Non-EU.

4.7. LNB voltage and 22KHz tone check

(only for DVB-S/S2 model)

▪ Test method

(1) Set TV in Adj. mode using POWER ON.

(2) Connect cable between satellite ANT and test JIG.

(3) Press Yellow key(ETC+SWAP) in Adj Remote control to

make LNB on.

(4) Check LED light ‘ON’ at 18 V menu.

(5) Check LED light ‘ON’ at 22 KHz tone menu.

(6) Press Blue key(ETC+PIP INPUT) in Adjustment Remote

control to make LNB off.

(7) Check LED light ‘OFF’ at 18 V menu.

(8) Check LED light ‘OFF’ at 22 KHz tone menu.

▪ Test result

(1) After press LNB On key, ‘18 V LED’ and ‘22 KHz tone

LED’ should be ON.

(2) After press LNB OFF key, ‘18 V LED’ and ‘22 KHz tone

LED’ should be OFF.

4.9.2. Method

(1) Press ADJ key on the Adjustment Remote Control, then

select Country Group Meun

(2) Depending on destination, select Country Group Code 04

or Country Group EU then on the lower Country option,

select US, CA, MX. Selection is done using +, - or ►◄

key.

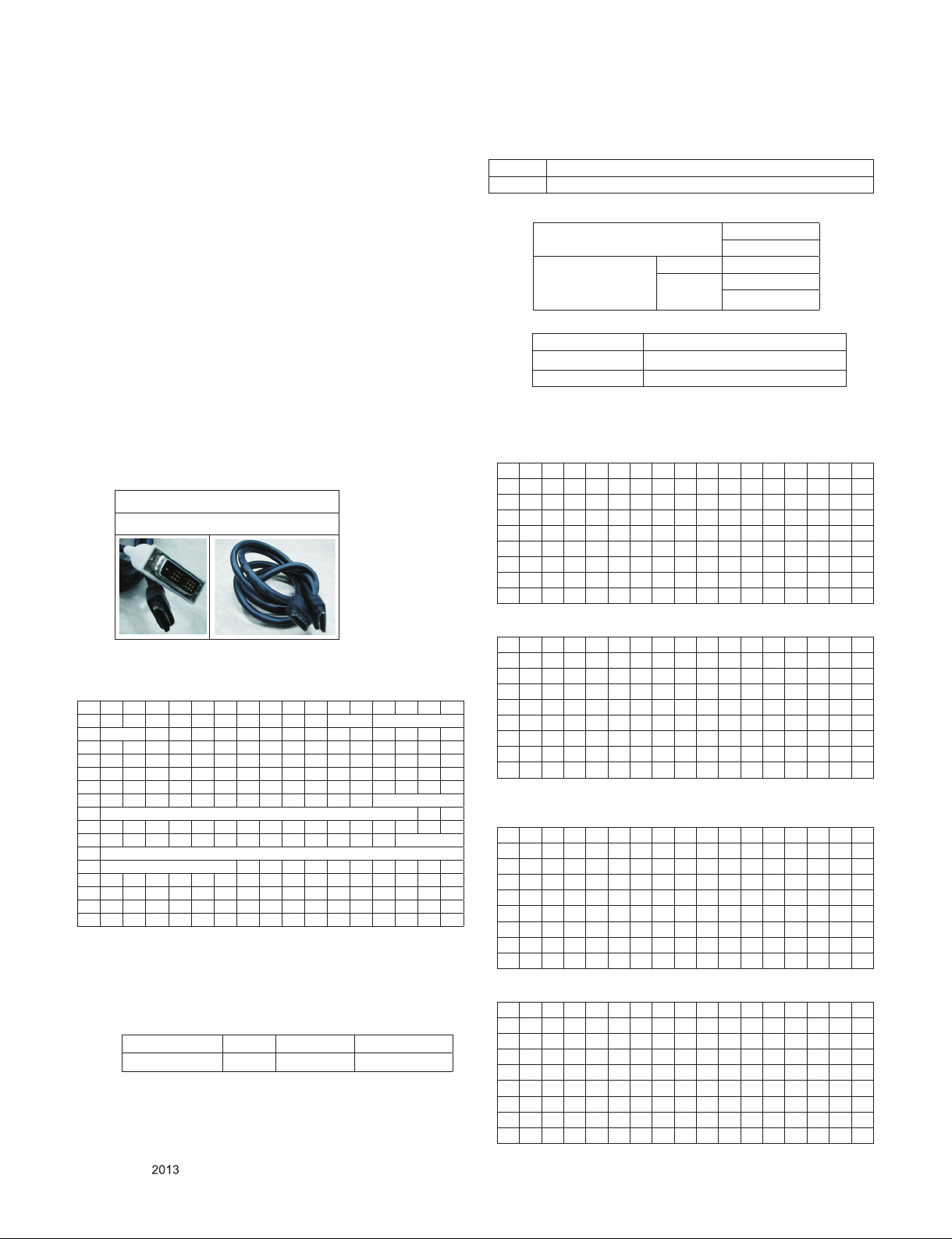

4.10. MHL Test

(1) Turn on TV

(2) Select HDMI4 mode using input Menu.

(3) Set MHL Zig(M1S0D3617) using MHL input, output and

power cord.

(4) Connect HDMI cable between MHL Zig and HDMI4 port.

(5) Check LED light of Zig and Module of Set.

Result) If, the LED light is green and the Module sho ws

normal stream → OK, Else → NG

Only for training and service purposes

- 20 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 21

4.11. HDMI ARC Function Inspection

(1) Test equipment

- Optic Receiver Speaker

- MSHG-600 (SW: 1220 ↑)

- HDMI Cable (for 1.4 version)

4.14. GND and Internal Pressure check

4.14.1. Method

(1) GND & Internal Pressure auto-check preparation

- Check that Power cord is fully inserted to the SET.

(If loose, re-insert)

(2) Test method

1) Insert the HDMI Cable to the HDMI ARC port from the

master equipment (HDMI1)

2) Check the sound from the TV Set

3) Check the Sound from the Speaker or using AV & Optic

TEST program (It’s connected to MSHG-600)

* Remark: Inspect in Power Only Mode and check SW

version in a master equipment

(2) Perform GND & Internal Pressure auto-check

- Unit fully inserted Power cord, Antenna cable and A/V

arrive to the auto-check process.

- Connect D-terminal to AV JACK TESTER

- Auto CONTROLLER(GWS103-4) ON

- Perform GND TEST

- If NG, Buzzer will sound to inform the operator.

- If OK, changeover to I/P check automatically.

(Remove CORD, A/V form AV JACK BOX.)

- Perform I/P test

- If NG, Buzzer will sound to inform the operator.

- If OK, Good lamp will lit up and the stopper will allow the

pallet to move on to next process.

4.14.2. Checkpoint

▪ TEST voltage

- GND: 1.5 KV / min at 100 mA

- SIGNAL: 3 KV / min at 100 mA

▪ TEST time: 1 second

▪ TEST POINT

- GND TEST = POWER CORD GND & SIGNAL CABLE

METAL GND

- Internal Pressure TEST = POWER CORD GND & LIVE &

NEUTRAL

▪ LEAKAGE CURRENT: At 0.5 mArms

5. Audio

No. Item Min Typ Max Unit Remark

Audio practical

max Output, L/R

1.

(Distortion=10%

max Output)

Speaker (8 Ω

2.

Impedance)

9.0 10.0 12.0 W

8.5 8.9 9.8 Vrms

10.0 15.0 W

Measurement condition

Auto Volume :Off

Audio EQ : Off

Clear Voice : Off

Virtual Surround:Off

4.12. Ship-out mode check(In-stop)

▪ After final inspection, press "IN-STOP" key of the Adjustment

remote control and check that the unit goes to Stand-by

mode.

4.13. Tool Option selection

- Method: Press ADJ key on the Adj. R/C, then select Tool option.

Only for training and service purposes

- 21 -

Measurement condition:

(1) RF input: Mono, 1 KHz sine wave signal, 100 % Modulation

(2) CVBS, Component: 1 KHz sine wave signal 0.5 Vrms

(3) RGB PC: 1 KHz sine wave signal 0.7 Vrms

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 22

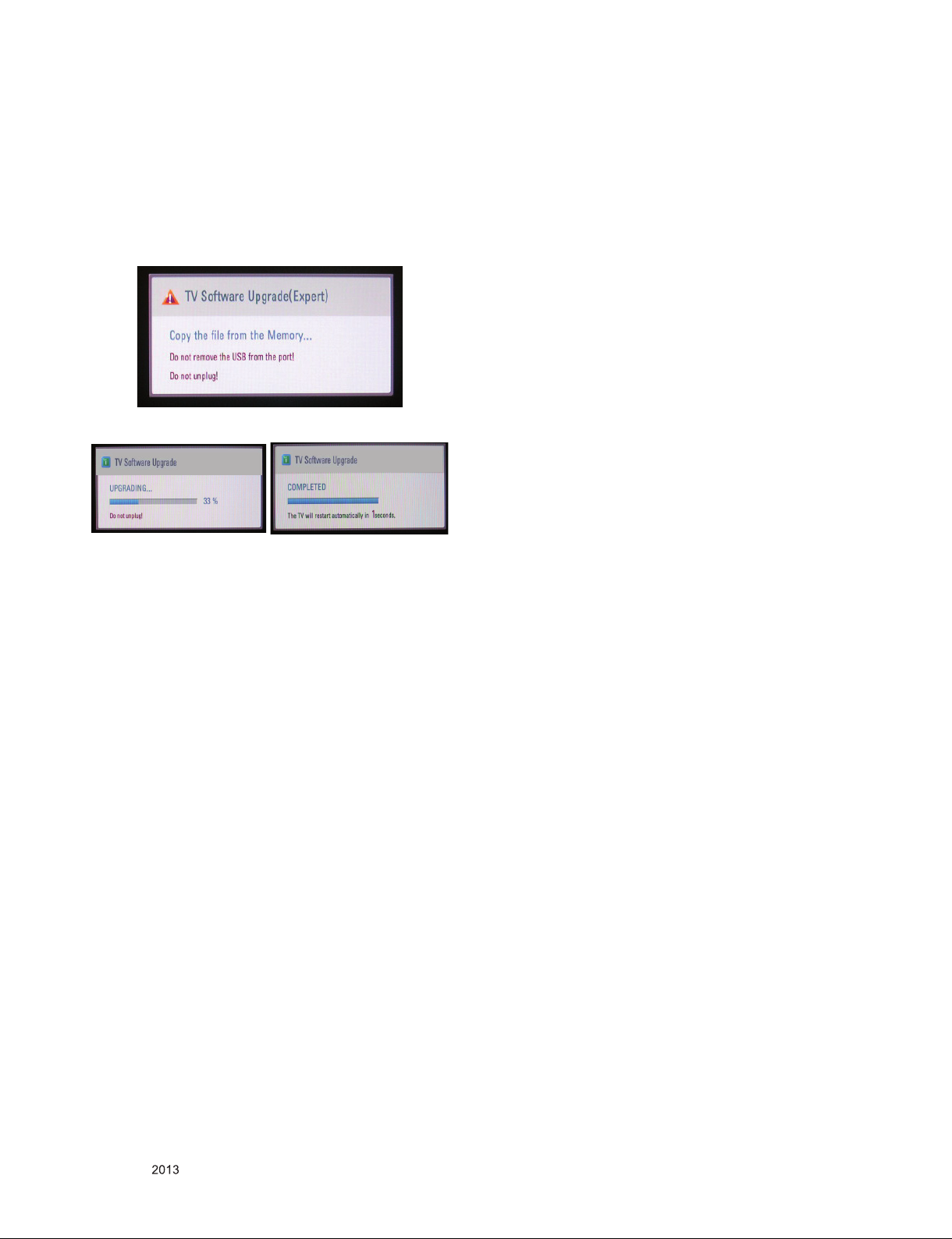

6. USB S/W Download(Service only)

(1) Put the USB Stick to the USB socket.

(2) Automatically detecting update file in USB Stick.

- If your downloaded program version in USB Stick is Low,

it didn't work. But your downloaded version is High, USB

data is automatically detecting.(Download Version High &

Power only mode, Set is automatically Download)

(3) Show the message "Copying files from memory".

(4) Updating is starting.

(5) Updating Completed, The TV will restart automatically.

(6) If your TV is turned on, check your updated version and

Tool option. (explain the Tool option, next stage)

* If downloading version is more high than your TV have, TV

can lost all channel data. In this case, you have to channel

recover. if all channel data is cleared, you didn’t have a DTV/

ATV test on production line.

* After downloading, have to adjust Tool Option again.

(1) Push "IN-START" key in service remote control.

(2) Select "Tool Option 1" and push "OK" key.

(3) Punch in the number. (Each model has their number)

Only for training and service purposes

- 22 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 23

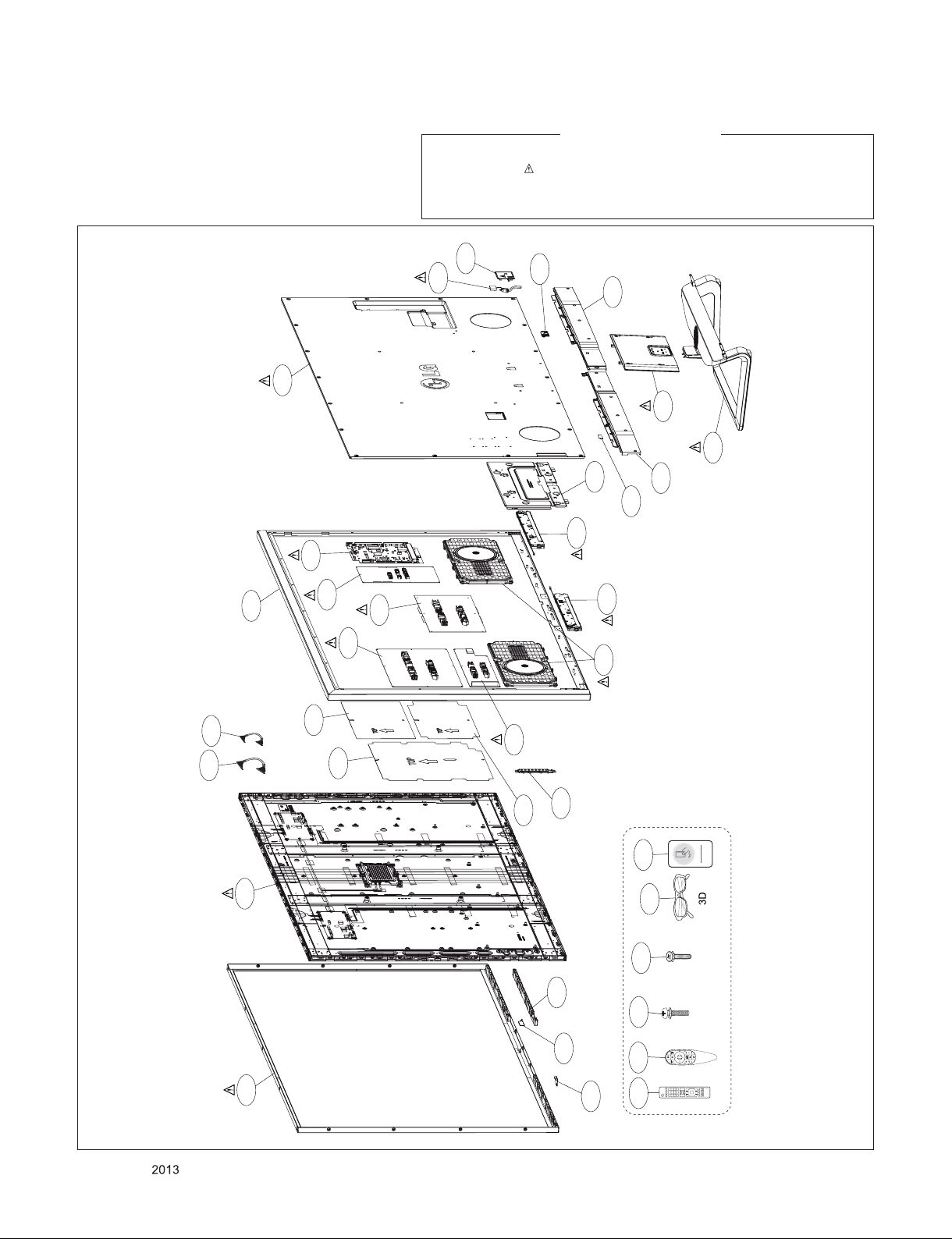

EXPLODED VIEW

IMPORTANT SAFETY NOTICE

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These

parts are identified by in the Schematic Diagram and EXPLODED VIEW.

It is essenti al that these special safet y parts shoul d be replac ed with the same compo nents as

recommended in this manual to prevent X-RADIATION, Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

320

400

540

541

531

532

700

710

570

121

810

122

420

910

900

410

560

120

LV2

LV1

200

300

Only for training and service purposes

840

830

- 23 -

530

820

510

310

580

500

AT1

A10

A9

A22

A2

AG1

Set + Stand

Stand Base

+ Body

(Option)

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 24

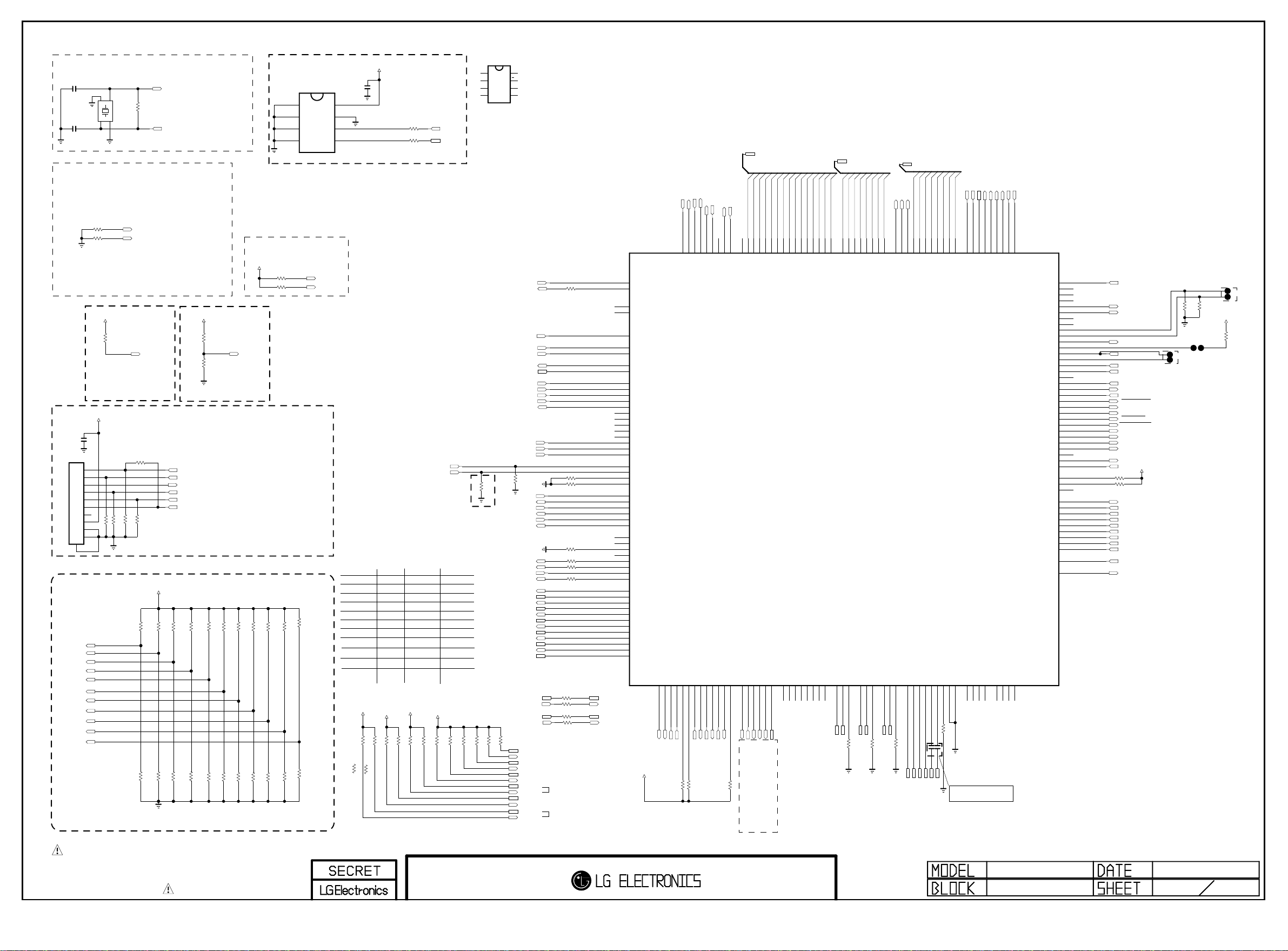

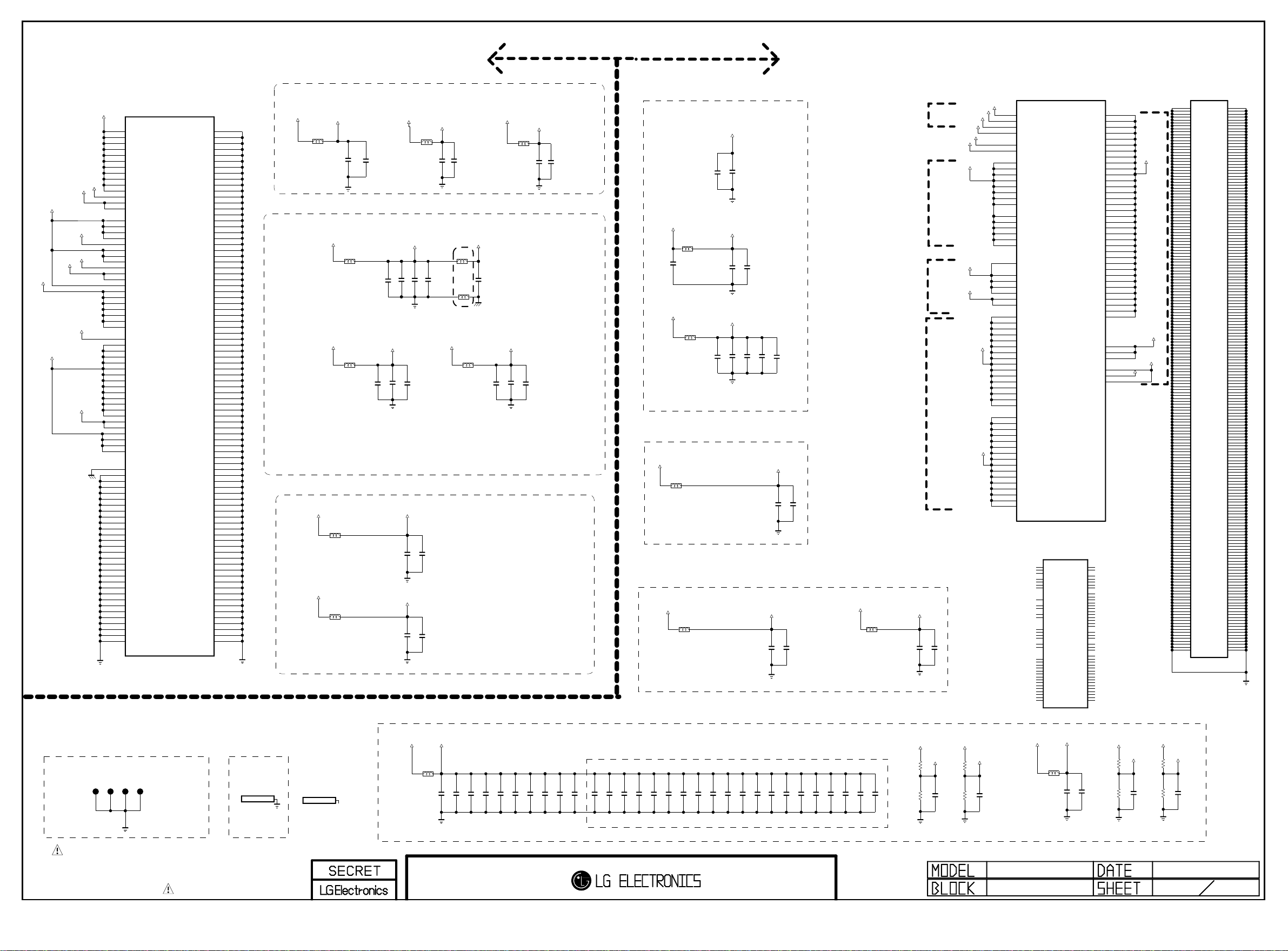

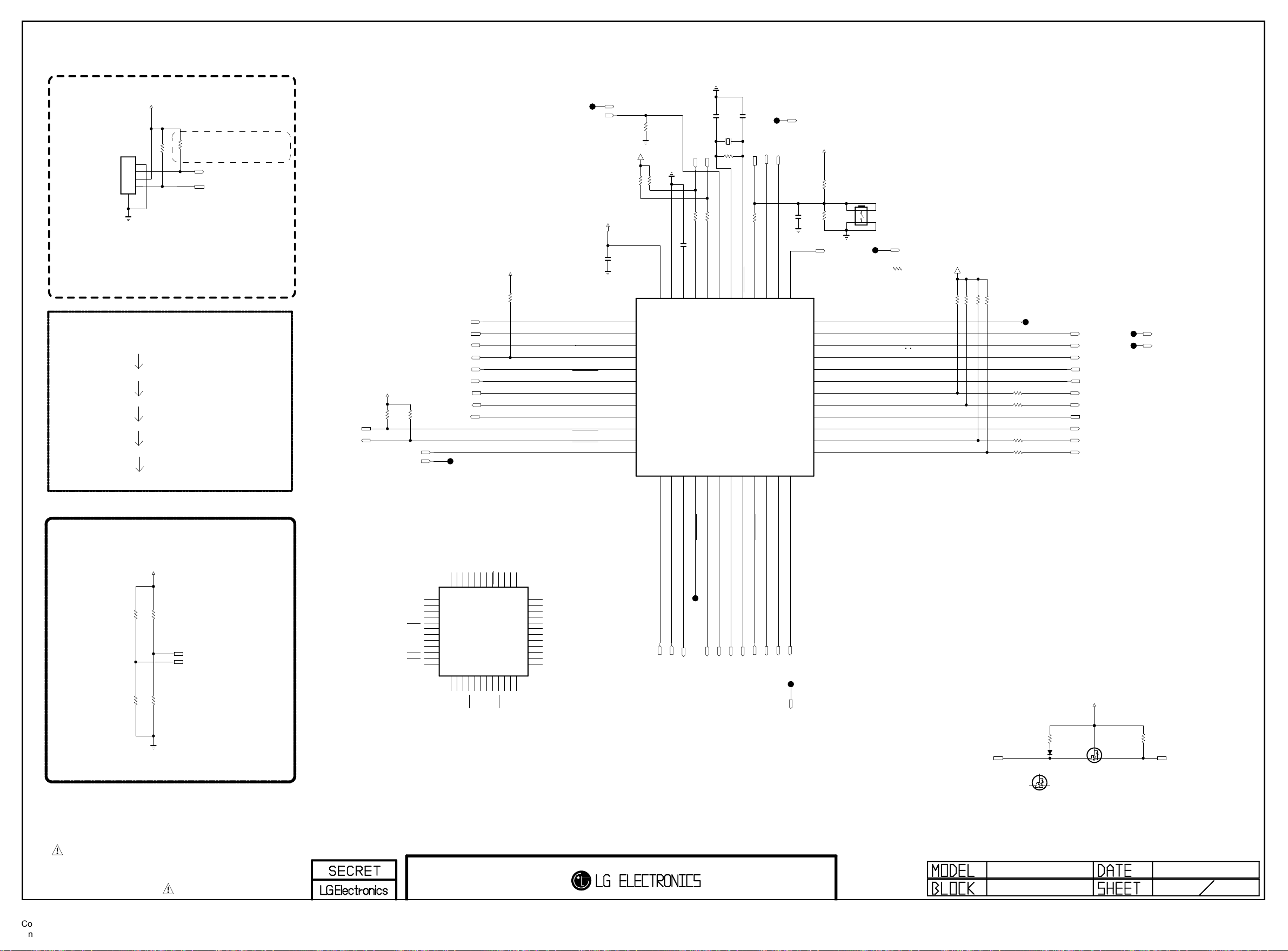

System Configuration

Copyright © 2013 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

Clock for LG1154D

MAIN Clock(24Mhz)

8pF

C100

8pF

C101

System Clock for Analog block(24Mhz)

PLL SET[1:0] : internal pull up

"00" : CPU(1200Mhz),M0 / M1 DDR(792,792 Mhz)

"01" : CPU(1056Mhz),M0 / M1 DDR(672,672 Mhz)

"10" : CPU(1056Mhz),M0 / M1 DDR(792,792 Mhz)

"11" : CPU( 960Mhz),M0 / M1 DDR(792,792 Mhz)

T32

0.1uF

P100

12505WS-10A00

T32

1

2

3

4

5

6

7

8

9

10

11

Model Option

HW_OPT_0

HW_OPT_1

HW_OPT_2

HW_OPT_3

HW_OPT_4

HW_OPT_5

HW_OPT_6

HW_OPT_7

HW_OPT_8

HW_OPT_9

HW_OPT_10

X-TAL_1

GND_1

1

2

24MHz

4

3

GND_2

X-TAL_2

OPT

R100 33

R101 33

OPT

+3.3V_NORMAL

INSTANT boot MODE

"1 : Instant boot

"0 : normal

3.3K

R150

(internal pull down)

OPT

INSTANT_MODE0

+3.3V_NORMAL

OPT

OPT

R160 10K

R163 10K

AREA option1

FRC option

Pannel Resol

OLED option

EPI PANEL version

reserved

CP BOX

T2 support

satellite support

AREA option2

EPI selection

X100

R166 10K

1M

R108

PLLSET1

PLLSET0

INSTANT_BOOT

OPT

R167

33

OPT

OPT

R168 10K

TAIWAN

R110 10K

NON_TAIWAN

R109 10K

+3.3V_NORMAL

10K

OPT

R112

10K

R111

XIN_MAIN

XO_MAIN

+3.3V_NORMAL

BOOT MODE

"0 : EMMC

"1 : TEST MODE

3.3K

R117

OPT

3.3K

R118

BOOT_MODE0

Jtag I/F For Main

TRST_N0

TDI0

TDO0

TMS0

TCK0

SOC_RESET

FHD

OPT

R114 10K

UD

R113 10K

R116 10K

R115 10K

OPT

V13_MODULE

R120 10K

V12_MODULE

R119 10K

R122 10K

R121 10K

OP MODE[1:0]

"00" : Normal Mode

"01/10/11" : Internal Test mode

+3.3V_NORMAL

OPT

R133 33

R134 33

OPT

BOOT_MODE

CP_BOX

R124 10K

NON_CP_BOX

R123 10K

AJ_JA

DVB_S_TUNER

R126 10K

R128 10K

DVB_T2_TUNER

R125 10K

R127 10K

NON_DVB_S_TUNER

NON_DVB_T2_TUNER

R129 10K

NON_AJ_JA

R130 10K

NVRAM

EEPROM_RENESAS

IC102

R1EX24256BSAS0A

A0

1

A1

2

A2

A0’h

3

VSS

4

OPM1

OPM0

D13

R131 10K

NON_D13

R132 10K

VCC

8

WP

7

SCL

6

SDA

5

C103

0.1uF

MODEL_OPT_0

MODEL_OPT_2

MODEL_OPT_3

MODEL_OPT_4

MODEL_OPT_5

MODEL_OPT_6

MODEL_OPT_7

MODEL_OPT_8

MODEL_OPT_9

MODEL_OPT_10

+3.3V_TU

R135

3.3K

KR_PIP_NOT

1.5K

KR_PIP

R135-*1

+3.3V_NORMAL

Write Protection

- Low : Normal Operation

- High : Write Protection

R139 33

R140 33

Area1

ReservedMODEL_OPT_1

Panel

Reserved

Module

Reserved

CP BOX

T2 Tuner

S Tuner

Area2

D13(HEVC)

+3.3V_TU

+3.3V_NORMAL

R137

3.3K

R138

3.3K

R136

3.3K

KR_PIP_NOT

1.5K

KR_PIP

R136-*1

R141

Support

Support

Support

3.3K

HIGH

Taiwan

FHD

V13

Enable

AJ_JA

R142

3.3K

I2C_SCL5

I2C_SDA5

D13_INT

EPHY_INT

non Taiwan

Not Support

Not Support

non AJ_JA

Not Support

+3.3V_NORMAL

R144

3.3K

R143

3.3K

LOW

Default

UD

Default

V12

Default

Disable

I2C PULL UP

R145

3.3K

R146

EEPROM_ST

IC102-*1

M24256-BRMN6TP

E0

1

E1

2

E2

3

VSS

4

R164331/16W

5%

I2C_SCL_MICOM_SOC

I2C_SDA_MICOM_SOC

3.3K

R148

R147

3.3K

VCC

8

WC

7

SCL

6

SDA

5

XIN_MAIN

XO_MAIN

SOC_RESET

H13A_SCL

H13A_SDA

TRST_N0

PLLSET1

PLLSET0

BOOT_MODE

R149

10K

SOC_RX

SOC_TX

M_REMOTE_RX

M_REMOTE_TX

M_REMOTE_RTS

M_REMOTE_CTS

SOC_SPI0_CS0

SOC_SPI0_MOSI

SOC_SPI0_MISO

SOC_SPI0_SCLK

I2C_SCL1

I2C_SDA1

I2C_SCL2_SOC

I2C_SDA2_SOC

I2C_SCL4

I2C_SDA4

I2C_SCL5

I2C_SDA5

I2C_SCL6

I2C_SDA6

I2C_SDA_MICOM

I2C_SCL_MICOM

I2C_SDA2

I2C_SCL2

3.3K

I2C_SDA1

I2C_SCL1

I2C_SDA_MICOM_SOC

I2C_SCL_MICOM_SOC

I2C_SDA2_SOC

I2C_SCL2_SOC

I2C_SDA4

I2C_SCL4

I2C_SDA5

I2C_SCL5

I2C_SDA6

I2C_SCL6

OPM1

OPM0

TMS0

TCK0

TDI0

TDO0

560

R152

R151 33

R174 33

R165 4.7K

HEVC

R107 33

HEVC

R156 33

HEVC

R158 33

R10533

33

R106

R10233

33

R104

I2C for tuner

I2C for tuner

A26

XIN

B26

XOUT

B27

XTAL_BYPASS

AT37

H13DA_XTAL

AU16

PORES_N

AD34

OPM1

AD33

OPM0

AT26

H13DA_SCL

AU26

H13DA_SDA

AP9

TRST_N0

AN9

TMS0

AP11

TCK0

AN11

TDI0

AN10

TDO0

AM10

TRST_N1

AM9

TMS1

AM11

TCK1

AM12

TDI1

AL11

TDO1

AL9

PLLSET1

AL10

PLLSET0

AE34

BOOT_MODE

Y33

EXT_INTR3/GPIO70

W32

EXT_INTR2/GPIO69

W33

EXT_INTR1/GPIO68

W34

EXT_INTR0/GPIO67

AU12

UART0_RXD

AT12

UART0_TXD

AU13

UART1_RXD

AT13

UART1_TXD

AP12

UART1_RTS

AR12

UART1_CTS

AE35

SPI_CS0/GPIO36

AE36

SPI_DO0/GPIO38

AF36

SPI_DI0/GPIO39

AF35

SPI_SCLK0/GPIO37

AG34

SPI_CS1

AF33

SPI_DO1

AG33

SPI_DI1

AG32

SPI_SCLK1

AR15

SCL0/GPIO66

AP15

SDA0/GPIO65

AR16

SCL1/GPIO64

AP16

SDA1/GPIO79

AP17

SCL2/GPIO78

AR17

SDA2/GPIO77

AP6

SCL3

AR6

SDA3

AH32

SCL4

AJ33

SDA4

AH34

SCL5

AH33

SDA5

I2C_SDA_MICOM_SOC

I2C_SCL_MICOM_SOC

I2C_SDA2_SOC

I2C_SCL2_SOC

+3.3V_NORMAL

CAM_CE1_N

CAM_CE2_N

CAM_CD1_N/GPIO76

F33

F34

D32

E32

/PCM_CE1

/PCM_CE2

CAM_CD1_N

CI

USB_CTL3

/USB_OCD3

/USB_OCD2

USB_CTL2

K35

K36

K37

L35

EB_CS3/GPIO93

EB_CS2/GPIO92

EB_CS1/GPIO91

EB_CS0/GPIO90

EB_WE_N

EB_BE_N1

EB_OE_N

H35

H36

J35

J36

H37

EB_WE_N/GPIO95

EB_WAIT/GPIO94

EB_OE_N/GPIO82

EB_BE_N1/GPIO81

EB_ADDR[0-14]

EB_BE_N0

EB_ADDR[13]

EB_ADDR[14]

EB_ADDR[12]

G37

G36

G35

F36

EB_BE_N0/GPIO80

EB_ADDR15/GPIO89

EB_ADDR14/GPIO88

EB_ADDR13/GPIO103

EB_ADDR12/GPIO102

EB_ADDR[8]

EB_ADDR[6]

EB_ADDR[7]

EB_ADDR[9]

EB_ADDR[11]

EB_ADDR[10]

F35

E36

E37

E35

D37

EB_ADDR9/GPIO99

EB_ADDR8/GPIO98

EB_ADDR7/GPIO97

EB_ADDR11/GPIO101

EB_ADDR10/GPIO100

EB_ADDR[4]

EB_ADDR[5]

EB_ADDR[3]

D36

D35

C36

C35

EB_ADDR6/GPIO96

EB_ADDR5/GPIO111

EB_ADDR4/GPIO110

EB_ADDR3/GPIO109

EB_ADDR[0]

EB_ADDR[1]

EB_ADDR[2]

EB_DATA[7]

B37

B36

B35

C32

EB_ADDR2/GPIO108

EB_ADDR1/GPIO107

EB_ADDR0/GPIO106

EB_DATA[0-7]

EB_DATA[5]

EB_DATA[6]

B33

A33

EB_DATA7/GPIO105

EB_DATA6/GPIO104

EB_DATA5/GPIO119

IC100

LG1154D_H13D

CAM_CD2_N/GPIO75

CAM_VS1_N/GPIO86

CAM_VS2_N/GPIO85

CAM_IREQ_N/GPIO73

CAM_RESET

CAM_INPACK/GPIO74

CAM_VCCEN_N/GPIO87

CAM_WAIT_N/GPIO84

CAM_REG_N/GPIO72

CAM_IOIS16_N/GPIO83

SC_CLK/GPIO130

SC_DETECT/GPIO133

SC_VCCEN/GPIO129

SC_VCC_SEL/GPIO128

SC_RST/GPIO131

SC_DATA/GPIO132

SD_CLK/GPIO125

SD_CMD/GPIO124

SD_CD_N/GPIO123

SD_WP_N/GPIO122

SD_DATA3/GPIO121

SD_DATA2/GPIO120

SD_DATA1/GPIO135

SD_DATA0/GPIO134

USB2_2_DP0

USB2_2_DM0

USB2_2_TXRTUNE

G32

G33

F32

G34

D33

H32

E33

D34

H33

T33

U33

T32

V32

V33

V34

A25

C25

B25

E25

D25

E24

D24

C24

L37

L36

K34

1%

200

CAM_CD2_N

R153

10K

PCM_RESET

CAM_IREQ_N

CAM_INPACK_N

CI

R154

10K

CAM_REG_N

CAM_WAIT_N

PCM_5V_CTL

R155

10K

CI

SMARTCARD_CLK/SD_EMMC_DATA[0]

SMARTCARD_DET/SD_EMMC_DATA[3]

interface

Only SMART CARD

SMARTCARD_DATA/SD_EMMC_CLK

SMARTCARD_VCC/SD_EMMC_CMD

SMARTCARD_RST/SD_EMMC_DATA[2]

SMARTCARD_PWR_SEL/SD_EMMC_DATA[1]

R157

USB2_HUB_IC_IN_DM

USB2_HUB_IC_IN_DP

EB_DATA[2]

EB_DATA[4]

EB_DATA[3]

EB_DATA[0]

EB_DATA[1]

C33

A34

B34

C34

A36

EB_DATA4/GPIO118

EB_DATA3/GPIO117

EB_DATA2/GPIO116

EB_DATA1/GPIO115

EB_DATA0/GPIO114

USB2_1_DP0

USB2_1_DM0

USB2_1_TXRTUNE

USB2_0_DP

M37

M36

K33

AU7

1%

200

R159

WIFI_DP

USB_DM2

USB_DP2

EMMC_DATA[0-7]

EMMC_CLK

EMMC_CMD

EMMC_RST

Y37

Y36

W35

EMMC_CLK

EMMC_CMD

EMMC_RESETN

USB2_0_DM

USB2_0_TXRTUNE

USB3_DP0

AT7

AP7

P37

WIFI_DM

R161 200 1%

USB3_DP

EMMC_DATA[5]

EMMC_DATA[7]

EMMC_DATA[6]

T36

W36

V35

EMMC_DATA7

EMMC_DATA6

EMMC_DATA5

USB3_DM0

USB3_RX0P

USB3_RX0M

P36

N36

N37

USB3_DM

USB3_RX0P

USB3_RX0M

EMMC_DATA[4]

EMMC_DATA[3]

EMMC_DATA[2]

V37

V36

U35

EMMC_DATA4

EMMC_DATA3

EMMC_DATA2

USB3_TX0P

USB3_TX0M

USB3_RESREF

R36

R37

N34

1%

200

R162

C105 0.1uF

C104 0.1uF

USB3_TX0M

USB3_TX0P

U36

EMMC_DATA1

USB3_REFPADCLKM

P33

EPHY_MDIO

EPHY_EN

EPHY_MDC

EPHY_REFCLK

EPHY_CRS_DV

EMMC_DATA[1]

EMMC_DATA[0]

U37

AU11

AU8

AT8

AR8

AR10

AT10

RMII_MDC

RMII_MDIO

RMII_CRS_DV

RMII_REF_CLK

NC_1

NC_2

NC_3

L32

L33

M31

AJ31

RMII_TXEN

NC_4

J32

EMMC_DATA0

USB3_REFPADCLKP

P32

AC-coupling CAP

Place near by LG1154D

EPHY_RXD1

EPHY_TXD0

EPHY_TXD1

AU10

AT11

AR11

RMII_TXD1

RMII_TXD0

RMII_RXD1

GPIO136

GPIO137

GPIO138

J33

K32

J34

EPHY_RXD0

RMII_RXD0

GPIO31

GPIO30

GPIO29

GPIO28