Page 1

Internal Use Only

North/Latin America http://aic.lgservice.com

Europe/Africa http://eic.lgservice.com

Asia/Oceania http://biz.lgservice.com

PLASMA TV

SERVICE MANUAL

CHASSIS : PB41A

MODEL : 60PB6500 60PB6500-SA

CAUTION

BEFORE SERVICING THE CHASSIS,

READ THE SAFETY PRECAUTIONS IN THIS MANUAL.

Printed in KoreaP/NO : MFL68122504 (1402-REV00)

Page 2

CONTENTS

CONTENTS .............................................................................................. 2

SAFETY PRECAUTIONS ........................................................................ 3

SPECIFICATION ....................................................................................... 4

ADJUSTMENT INSTRUCTION ................................................................ 5

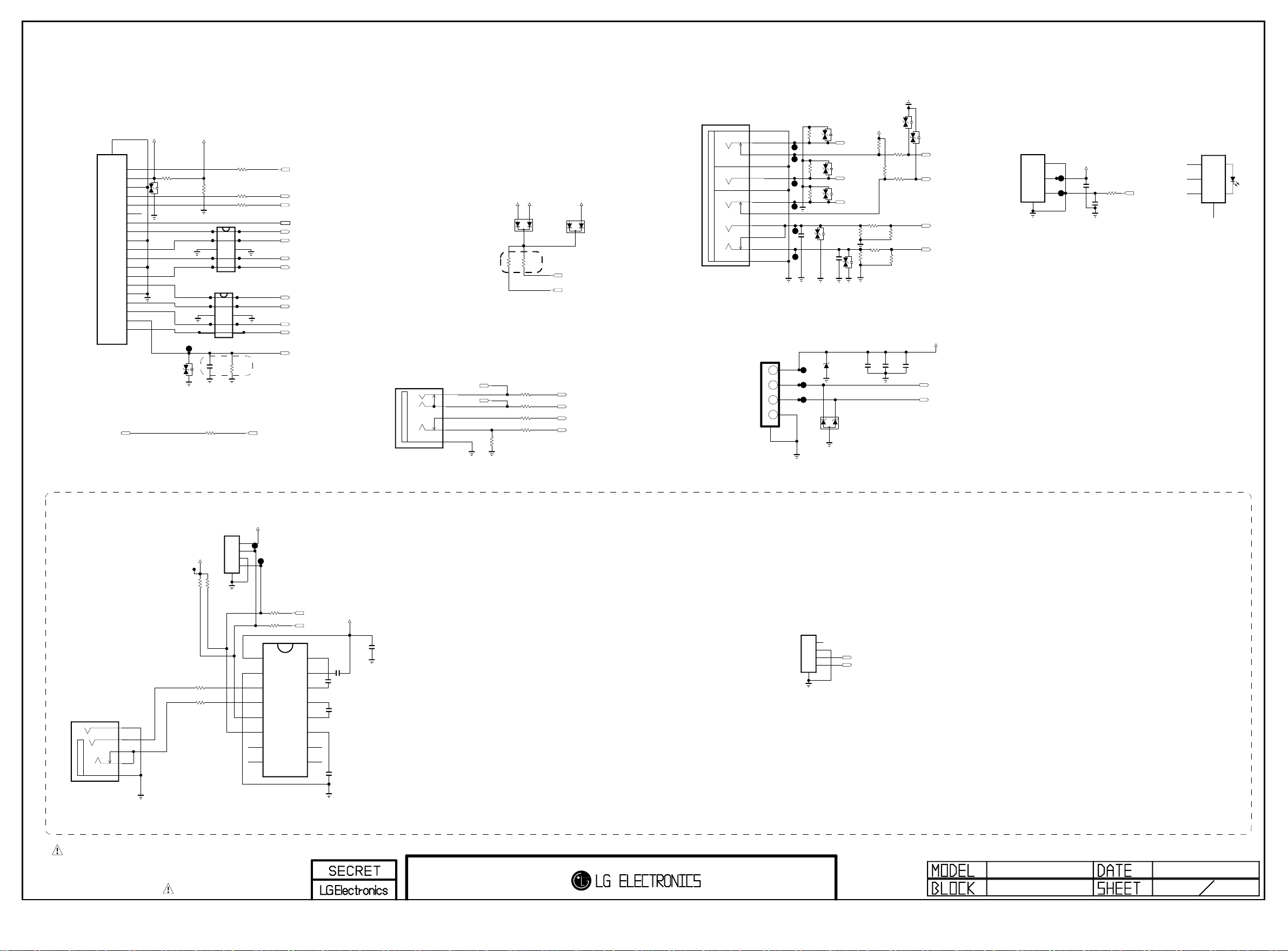

BLOCK DIAGRAM .................................................................................. 11

EXPLODED VIEW .................................................................................. 12

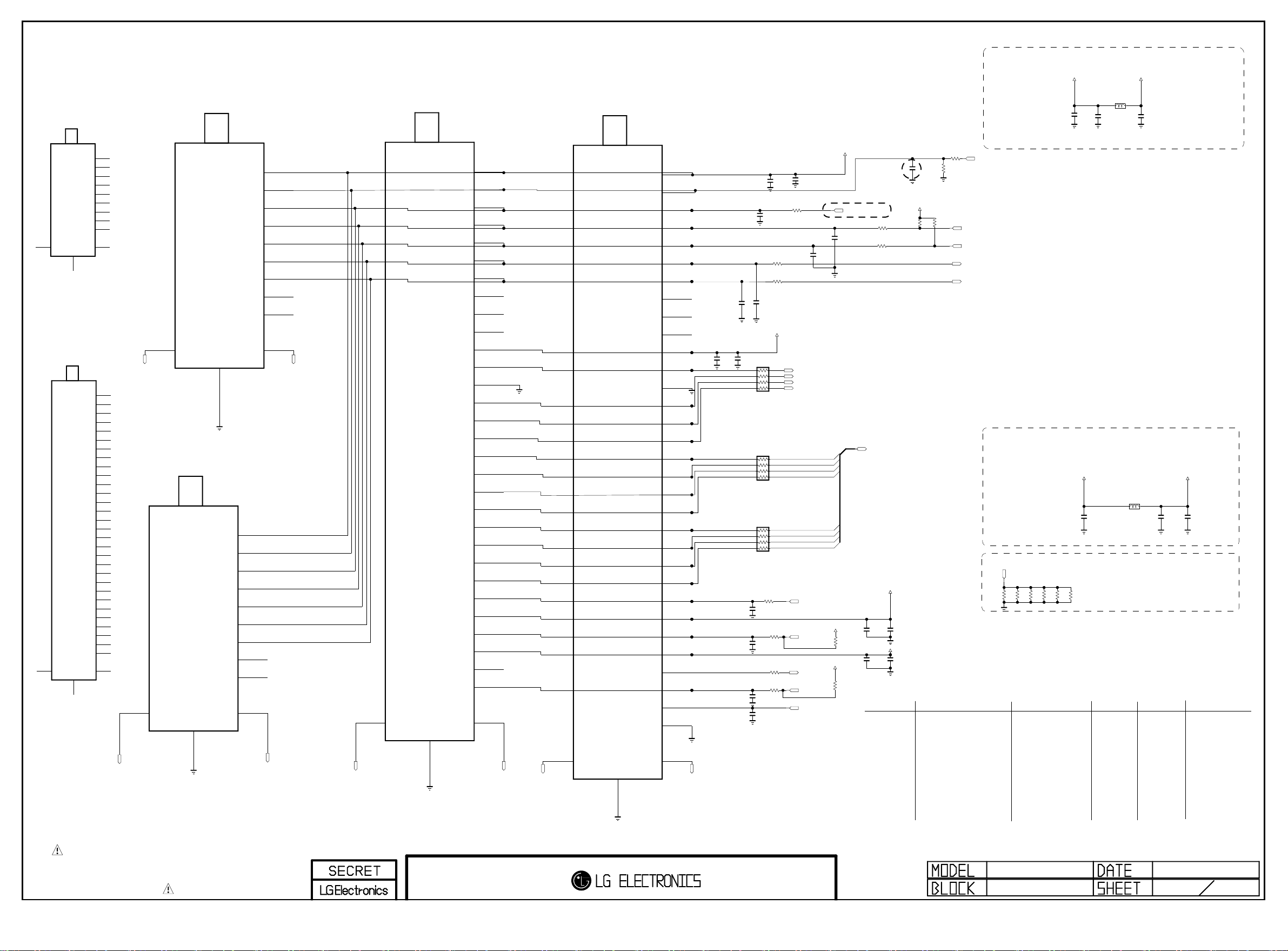

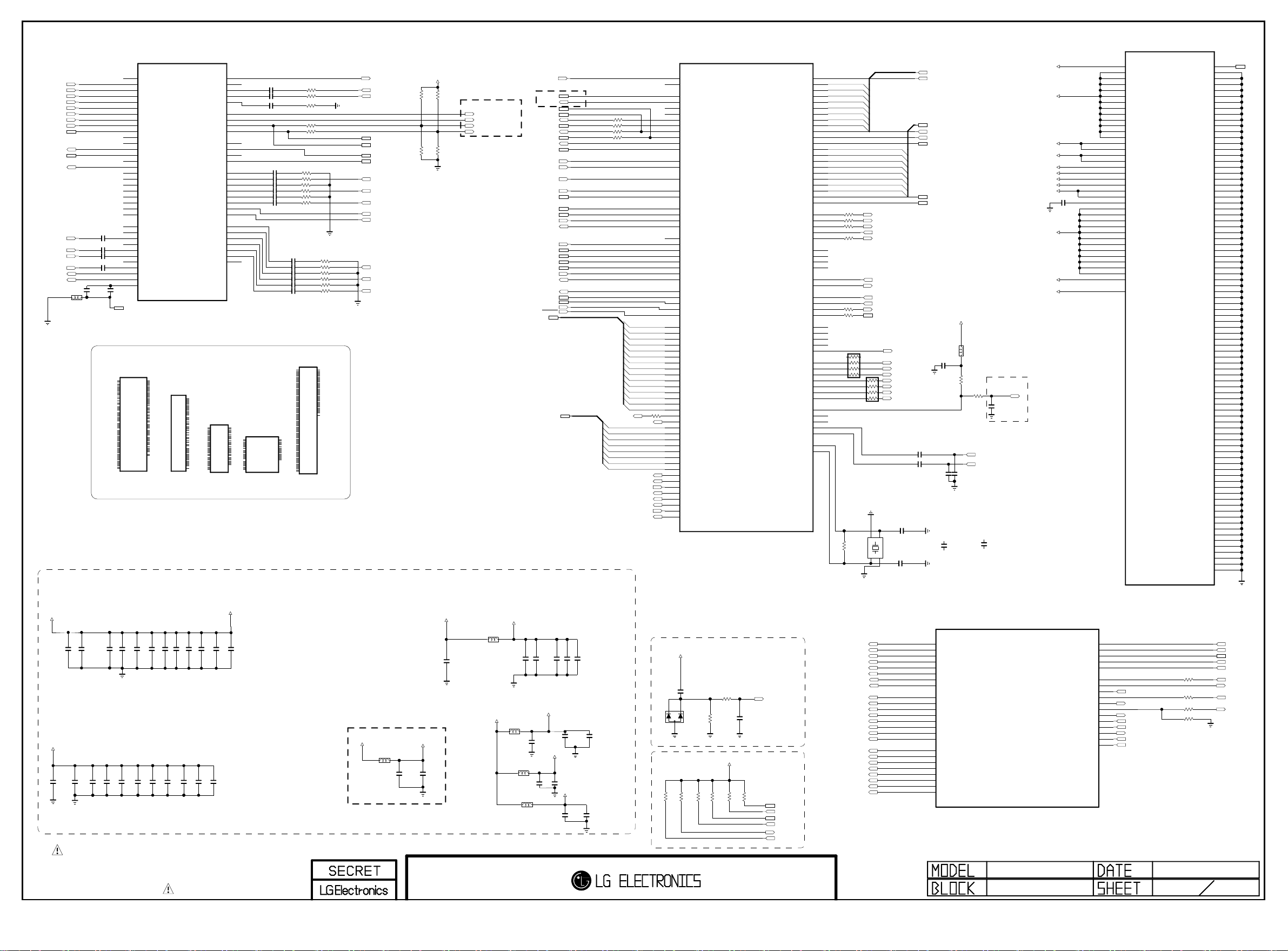

SCHEMATIC CIRCUIT DIAGRAM ..............................................................

Only for training and service purposes

- 2 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 3

AC Volt-meter

SAFETY PRECAUTIONS

IMPORTANT SAFETY NOTICE

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These parts are identified by in the

Schematic Diagram and Exploded View.

It is essential that these special safety parts should be replaced with the same components as recommended in this manual to prevent

Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

General Guidance

An isolation Transformer should always be used during the

servicing of a receiver whose chassis is not isolated from the AC

power line. Use a transformer of adequate power rating as this

protects the technician from accidents resulting in personal injury

from electrical shocks.

It will also protect the receiver and it's components from being

damaged by accidental shorts of th e circuitry that may be

inadvertently introduced during the service operation.

If any fuse (or Fusible Resistor) in this TV receiver is blown,

replace it with the specified.

When replacing a high wattage resistor (Oxide Metal Film Resistor,

over 1 W), keep the resistor 10 mm away from PCB.

Keep wires away from high voltage or high temperature parts.

Before returning the receiver to the customer,

always perform an AC leakage current check on the exposed

metallic parts of the cabinet, such as antennas, terminals, etc., to

be sure the set is safe to operate without damage of electrical

shock.

Leakage Current Cold Check(Antenna Cold Check)

With the instrument AC plug removed from AC source, connect an

electrical jumper across the two AC plug prongs. Place the AC

switch in the on position, connect one lead of ohm-meter to the AC

plug prongs tied together and touch other ohm-meter lead in turn to

each exposed metallic parts such as antenna terminals, phone

jacks, etc.

If the exposed metallic part has a return path to the chassis, the

measured resistance should be between 1 MΩ and 5.2 MΩ.

When the exposed metal has no return path to the chassis the

reading must be infinite.

An other abnormality exists that must be corrected before the

receiver is returned to the customer.

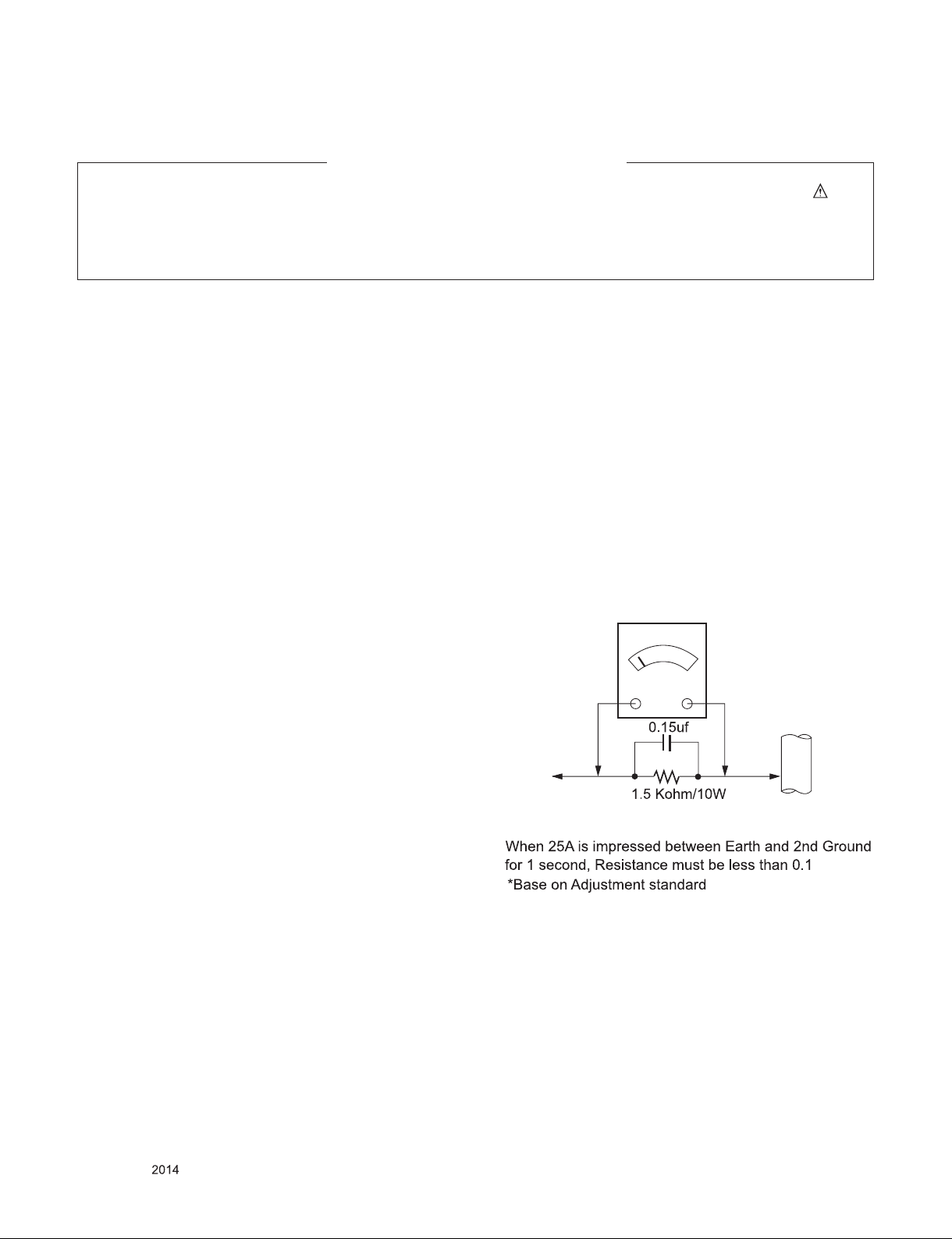

Leakage Current Hot Check (See below Figure)

Plug the AC cord directly into the AC outlet.

Do not use a line Isolation Transformer during this check.

Connect 1.5 K / 10 watt resistor in parallel with a 0.15 uF capacitor

between a known good earth ground (Water Pipe, Conduit, etc.)

and the exposed metallic parts.

Measure the AC voltage across the resistor using AC voltmeter

with 1000 ohms/volt or more sensitivity.

Reverse plug the AC cord into the AC outlet and repeat AC voltage

measurements for each exp ose d metallic par t. Any voltage

measured must not exceed 0.75 volt RMS which is corresponds to

0.5 mA.

In case any measurement is out of the limits specified, there is

possibility of shock hazard and the set must be checked and

repaired before it is returned to the customer.

Leakage Current Hot Check circuit

Good Earth Ground

such as WATER PIPE,

To Instrument's

exposed

METALLIC PARTS

CONDUIT etc.

Only for training and service purposes

- 3 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 4

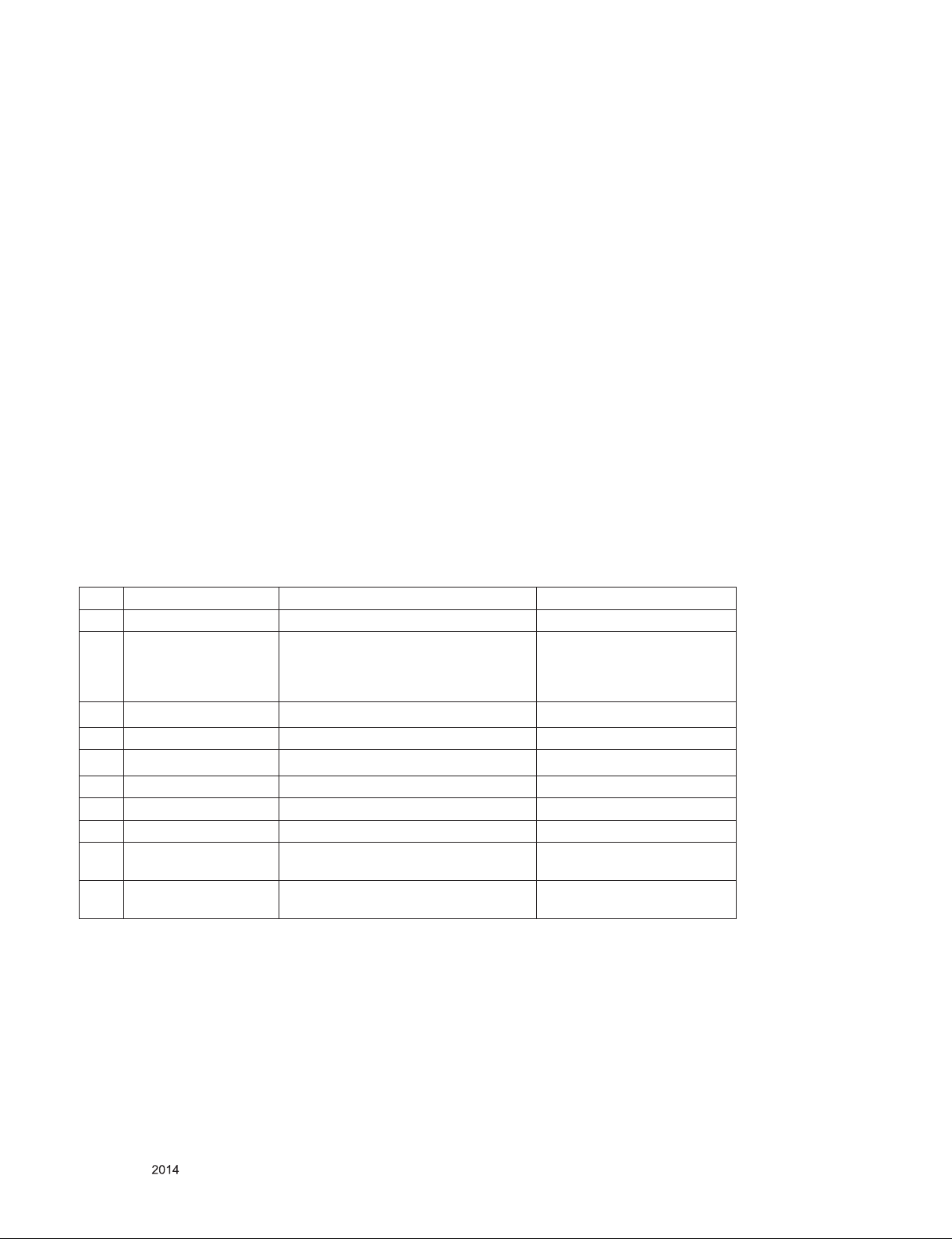

SPECIFICATION

NOTE : Specifications and others are subject to change without notice for improvement

1. Application range

This spec sheet is applied all of the 42” 50”, 60” PDP TV with PB41A chassis.

2. Requirement for Test

Each part is tested as below without special appointment.

(1) Temperature: 25 °C ± 5 °C(77 °F ± 9 °F),

(2) Relative Humidity: 65 % ± 10 %

(3) Power Voltage

: Standard input voltage (AC 100-240 V~, 50/60 Hz)

* Standard Voltage of each products is marked by models.

(4) Specification and performance of each parts are followed each drawing and specification by part number in accordance with

BOM.

(5) The receiver must be operated for about 5 minutes prior to the adjustment.

3. Test method

(1) Performance: LGE TV test method followed

(2) Demanded other specification

- Safety : CE, IEC specification

- EMC : CE, IEC

.

4. Model General Specification

No Item Specication Remark

1 Receiving System 1) DVB-T2 / NTSC-M / PAL-M / PAL-N

2 Available Channel 1) VHF : 2~13

2) UHF : 14~69

3) DTV : 2~69

4) CATV : 1~125

3 Input Voltage 1) AC 110 ~ 240V 50/60Hzz

4 Market Colombia

60 inch Wide(1920 × 1080)

6 Aspect Ratio 16:9

7 Tuning System FS

8 Module PDP60R6#### (1920 × 1080)

9 Operating Environment 1) Temp : 0 ~ 40 deg

2) Humidity : ~ 80 %

10 Storage Environment 1) Temp : -20 ~ 60 deg

2) Humidity : ~ 85 %

DTV : DVB-T2

Only for training and service purposes

- 4 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 5

ADJUSTMENT INSTRUCTION

1. Application Range

This spec. sheet applies to PB41A chassis applied PDP TV all

models manufactured in TV factory.

2. Specification

(1) Because this is not a hot chassis, it is not necessary to

use an isolation transformer. However, the use of isolation

transformer will help protect test instrument.

(2) Adjustment must be done in the correct order. But it is

flexible when its factory local problem occurs.

(3) T he adjustment must be performed in the circumstance of

25 °C ± 5 °C of temperature and 65 % ± 10 % of relative

humidity if there is no specific designation.

(4) The input voltage of the receiver must keep AC 100-220

V~, 50/60 Hz.

(5) Before adjustment, execute Heat-Run for 5 minutes.

■ After Receive 10 0% Full white pattern (06CH) then

process Heat-run

(or “8. Test pattern” condition of Ez-Adjust status)

■ How to make set white pattern

1) Press Power ON button of Service Remocon

2) Press ADJ button of Service remocon. Select “10. Test

pattern” and, after select “White” using navigation

button, and then you can see 100% Full White pattern.

* In this status you can maintain Heat-Run useless any

pattern generator

* Notice: if you maintain one picture over 20 minutes

(Especiall y sharp dis tinction black with white

pattern – 13Ch, or Cross hatch pattern – 09Ch)

then it can appear image stick near black level.

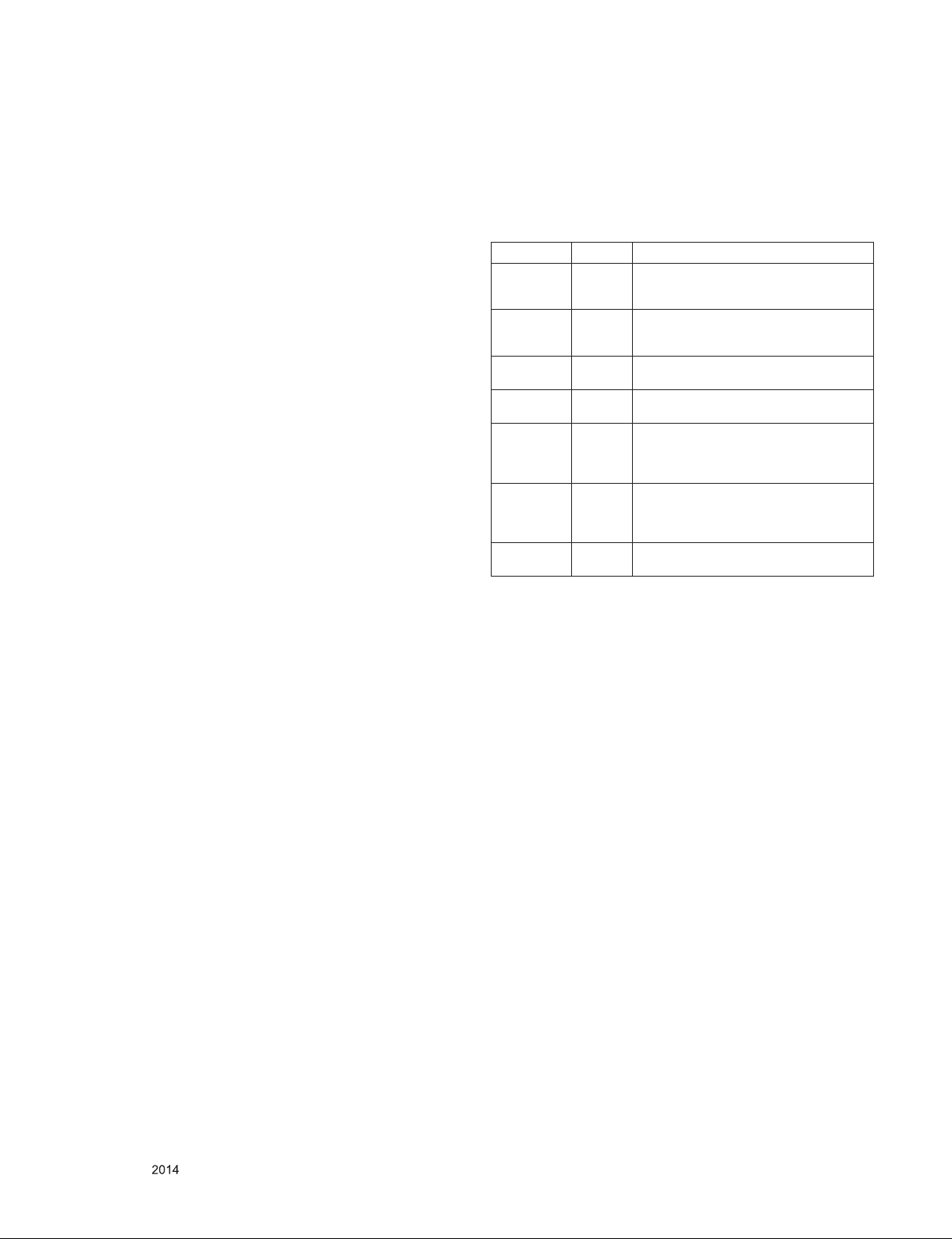

4. PCB Assembly Adjustment

4.1. Using RS-232C

- Adjust 3 items at 3.1. PCB assembly adjustments

" 4.1. ■ Adjustment sequence" one after the order.

■ Adjustment sequence

Order command Set response

1. Inter the

Adjustment

mode

2. Change

the Source

3. Start

Adjustment

4. Return the

Response

5. Read

Adjustment

data

6. Conrm

Adjustment

7. End of

Adjustment

■ Necessary items before Adjustment items

● Pattern Generator : (MSPG-925FA)

● Adjust 480i comp1

(MSPG-925FA:model :209, pattern :65) - comp1 Mode

● Adjust 1080p comp1

(MSPG-925FA:model :225 , pattern :65) - comp1 Mode

aa 00 00 a 00 OK00x

XB 00 40

XB 00 60

ad 00 10

( main )

ad 00 20

( main )

ad 00 30

ad 00 99 NG 03 00x (Failed condition)

ad 00 90 d 00 OK90x

b 00 OK40x (Adjust 480i Comp1 )

(Adjust 1080p Comp1)

b 00 OK60x (Adjust 1080p RGB)

OKx ( Success condition )

NGx ( Failed condition )

(main : component1 480i, RGB 1080p)

000000000000000000000000007c007b006dx

(main : component1 1080p)

000000070000000000000000007c00830077x

NG 03 01x (Failed condition)

NG 03 02x (Failed condition)

OK 03 03x (Success condition)

< See ADC Adjustment RS232C Protocol_Ver1.0 >

3. Adjustment items

3.1. PCB Assembly adjustment

■ Adjust 480i Comp

■ Adjust 1080p Comp

● If it is necessary, it can adjustment at Manufacture Line

● You can see set adju stm ent status at “9. ADJUST

CHECK” of the “In-start menu”

3.2. Set Assembly Adjustment

■ EDID (The Extended Display Identification Data )

■ Color Temperature (White Balance) Adjustment

■ Make sure RS-232C control

■ Selection Factory output option

Only for training and service purposes

* If you want more information then see the below Adjustment

method (Factory Adjustment)

■ Adjustment sequence

● aa 00 00: Enter the ADc Adjustment mode.

● xb 00 40: change the mode to component1 (No actions)

● ad 00 10: Adjust 480i comp

● ad 00 10: Adjust 1080p comp

● xb 00 90: Endo of Adjustmennt

- 5 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 6

5. Factory Adjustment

-> PU41A : USE INTERNAL ADC(LM1) : using internal pattern.

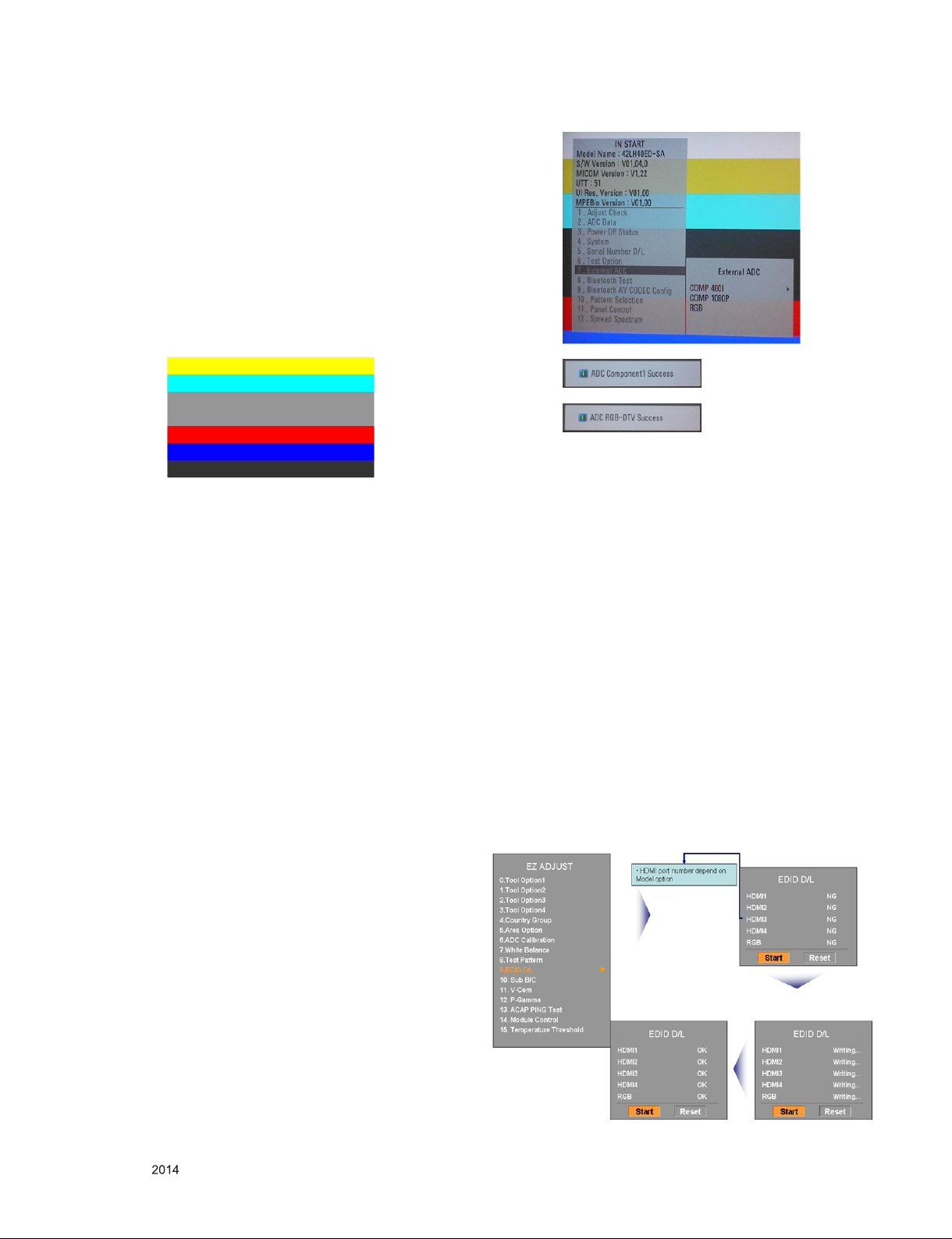

5.1. Auto Adjust Component 480i/1080p

■ Summary : Adjustment component 480i/1080i is Gain and

Black level setting at Analog to Digital converter,

and compensate the RGB deviation

■ Using instrument

● Adjustment remocon, 801GF(802B, 802F, 802R ) or

MSPG925FA pattern generator

( It can output 480i/1080 i horizontal 100% color bar

pa tt ern signal, an d i ts ou tput level must se tt in g

0.7V±0.1V p-p correctly)

< Adjustment pattern : 480i / 1080p 60Hz Pattern >

● You must make it sure its resolution and pattern cause

every instrument can have different setting

● Adjustment method 480i Comp1, Adjust 1080p Comp

(Factory adjustment)

● ADC 480i Component adjustment

- Check connection of Component

- MSPG-925FA -> Model: 209, Pattern 65

● Set Component 480i mode and 100% Horizontal Color

Bar Pattern(HozTV31Bar), then set TV set to Component

mode and its screen to “NORMAL”

● ADC 1080p Component adjustment

- Check connection Component

- MSPG-925FA -> Model: 225, Pattern 65

● Set Component 1080p mode and 100% Horizontal Color

Bar Pattern(HozTV31Bar), then set TV set to Component

mode and its screen to “NORMAL”

● After get each the signal, wait more a second and enter

the “IN-START” with press IN-START key of Service

remocon. After then select “7. External ADC” with

navigator button and press “Enter”.

● After Then Press key of Service remocon “Right Arrow

(VOL+)”

● You can see “ADC Component Success”

● Component1 1080p Adjust is same method.

● Component 1080p Adjustment in Component input mode

* caution : Set Volume 0 after adjustment

5.2. Use Internal ADC(S7R)

- A DJ( E Z ADJ UST ) - > 6.A DC C ali bra tio n - > A DC

Calibration(START)

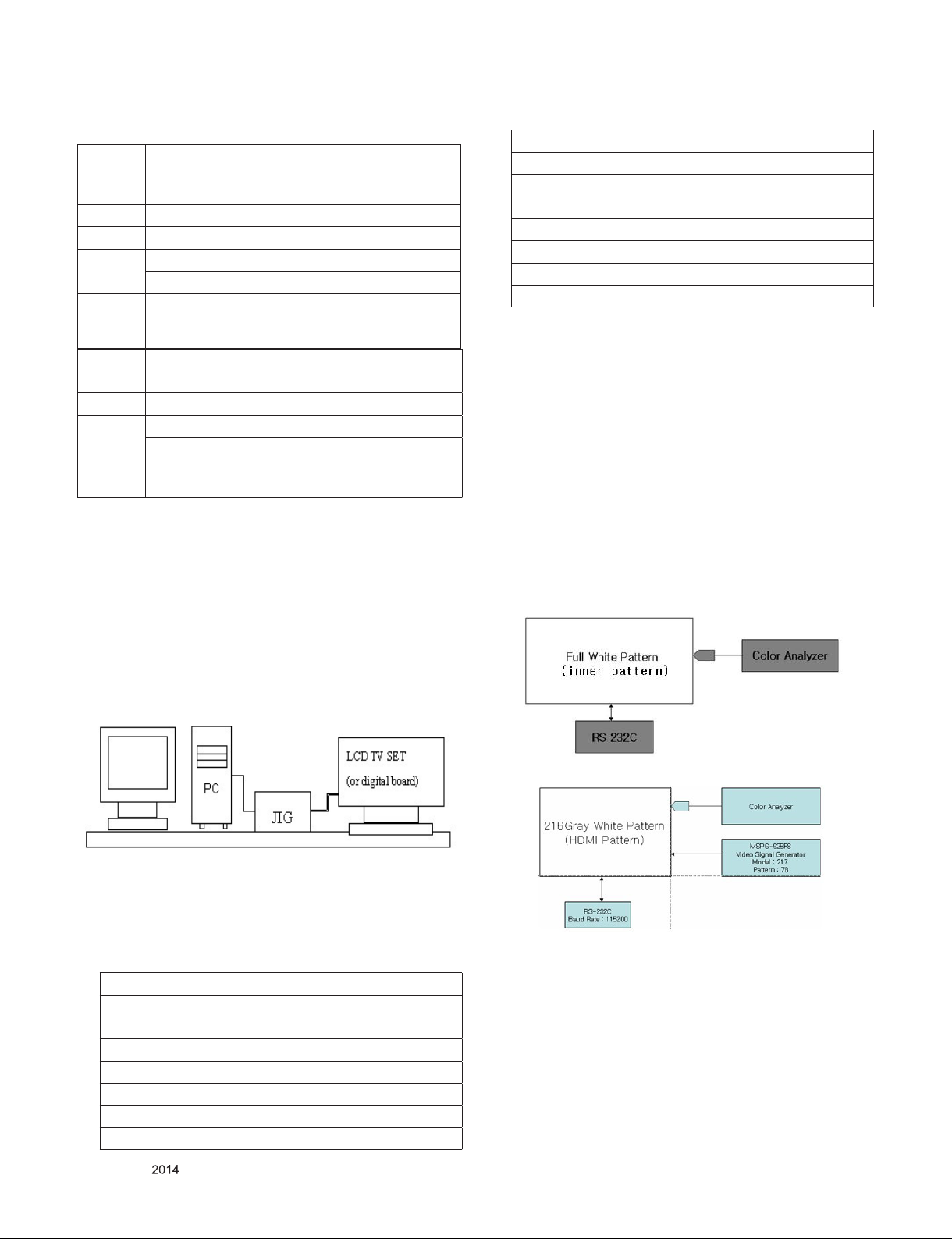

* EDID (The Extended Display Id entification Data)/DDC

(Display Data Channel) Download.

■ Summary

● It is established in VESA, for communication between

PC and Monitor without order from user for building

user condition. It helps to make easily use realize

“Plug and Play” function.

● For EDID data write, we use DDC2B protocol.

- Auto Download

■ After enter Service Mode by pushing “ADJ” key,

■ Enter EDID D/L mode.

■ Enter “START” by pushing “OK” key.

* Caution:

- Neve r conn ect HD MI & D-sub Cable when the user

downloading .

- Use the proper cables below for EDID Writing

Only for training and service purposes

- 6 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 7

* Edid data and Model option download(RS232)

NO Enter

download MODE

Item download ‘Mode In’ download

CMD 1 A A

CMD 2 E E

Data 0 0 *Note1

0 *Note2

When transfer the

‘Mode In’,

Carry the command.

Item Adjust ‘Mode Out’’ Adjustment Conrmation

CMD 1 A A

CMD 2 E E

Data 0 9 9

0 9

- Manual Download

■ Write HDMI EDID data

● Using instruments

- Jig. (PC Serial to D-Sub connection) for PC, DDC

adjustment.

- S/W for DDC recording (EDID data write and read)

- D-sub jack

- Additional HDMI cable connection Jig.

● Preparing and setting.

- Set instruments and Jig. Like pic.5), then turn on PC

and Jig.

- Operate DDC write S/W (EDID write & read)

- It will operate in the DOS mode.

EDID data Model

option download

Automatically download

(The use of a internal

Data)

To check Download

on Assembly line.

02 03 21 F1 4D 10 9F 04 13 05 14 03 02 12 20 22

15 01 26 15 07 50 09 57 07 67 03 0C 00 10 00 B8

2D 02 3A 80 18 71 38 2D 40 58 2C 45 00 40 84 63

00 00 1E 01 1D 80 18 71 1C 16 20 58 2C 25 00 40

84 63 00 00 9E 01 1D 00 72 51 D0 1E 20 6E 28 55

00 40 84 63 00 00 1E 0E 1F 00 80 51 00 1E 30 40

80 37 00 40 84 63 00 00 1C 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 66

- See Working Guide if you want more information about EDID

communication.

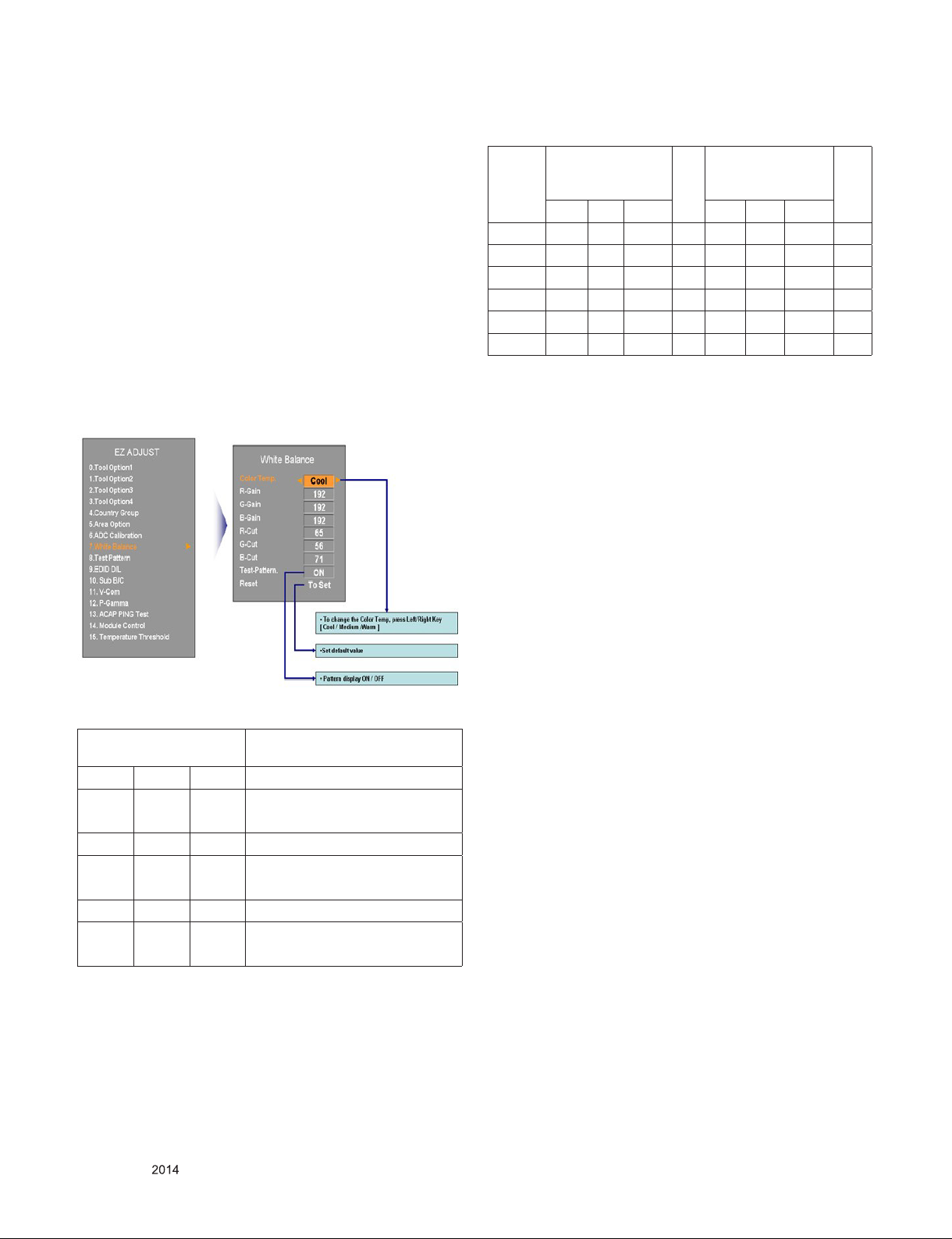

- Adjustment Color Temperature(White balance)

■ Using Instruments

● Color Analyzer: CA-210 (CH 10)

- Using LCD color temperature, Color Analyzer (CA-

210) must use CH 10, which Matrix compensated

(White, Red, Green, Blue compensation) with CS-

2100. See the Coordination bellowed one.

● Auto-adjustment Equipment (It needs when Auto-adjustment – It is availed communicate with RS-232C : Baud

rate: 115200)

● Video Signal Generator MSPG-925F 720p, 216Gray

(Model: 217, Pattern 78)

■ Connection Diagram (Auto Adjustment)

● Using Inner Pattern

< For write EDID data, setting Jig and another instruments >

■ EDID data (Model name = LG TV)

<FHD>

- MODEL NAME : 60PB6500

- AC3 (C/S : 0x96, 0x66)

- HDMI

00 FF FF FF FF FF FF 00 1E 6D 01 00 01 01 01 01

01 18 01 03 80 A0 5A 78 0A EE 91 A3 54 4C 99 26

0F 50 54 A1 08 00 31 40 45 40 61 40 81 80 01 01

01 01 01 01 01 01 02 3A 80 18 71 38 2D 40 58 2C

45 00 40 84 63 00 00 1E 66 21 50 B0 51 00 1B 30

40 70 36 00 40 84 63 00 00 1E 00 00 00 FD 00 3A

3E 1E 53 10 00 0A 20 20 20 20 20 20 00 00 00 FC

00 4C 47 20 54 56 0A 20 20 20 20 20 20 20 01 96

Only for training and service purposes

- 7 -

● Using HDMI input

< connection Diagram for Adjustment White balance >

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 8

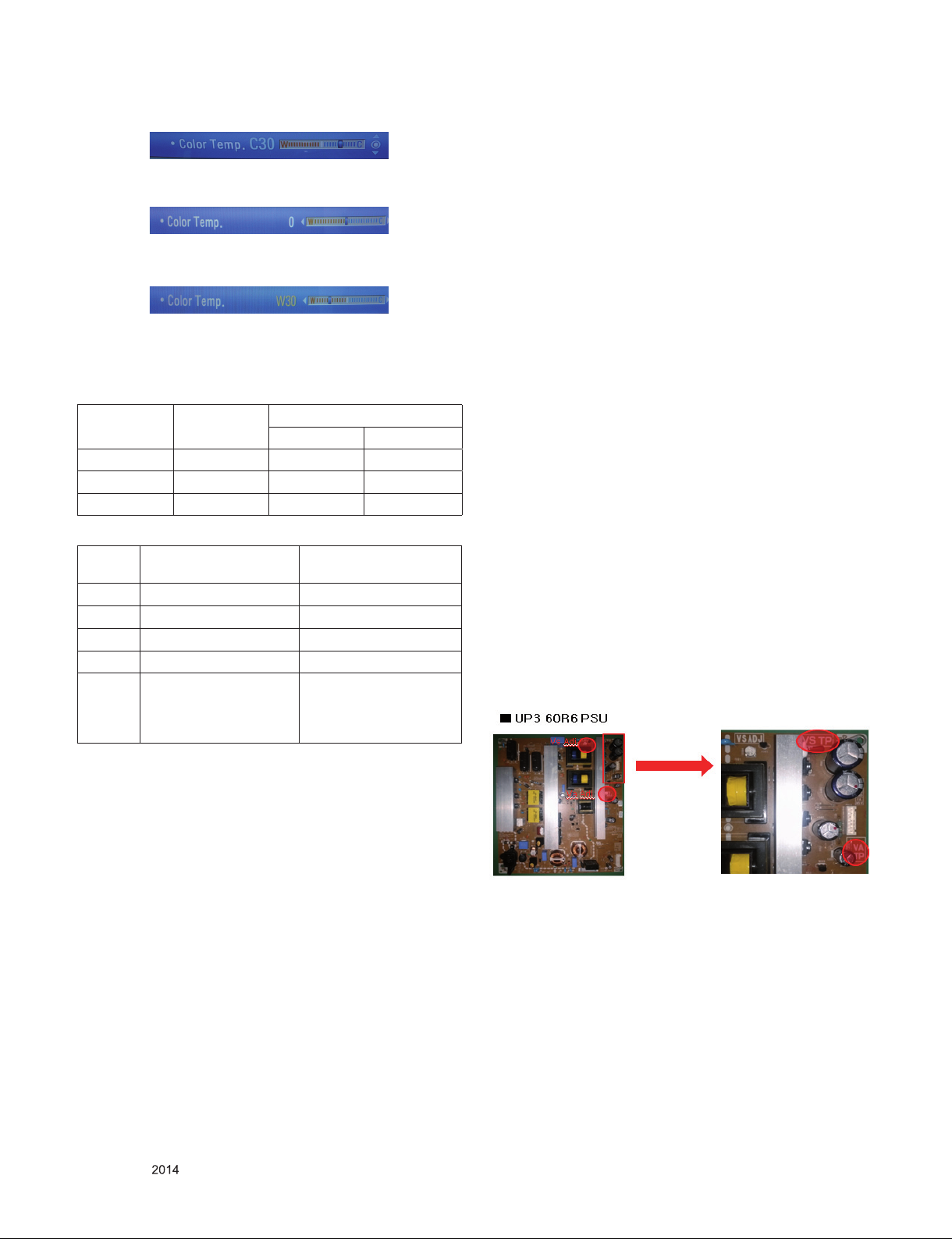

■ White Balance Adjustment

If you can’t adjust with inner pattern, then you can adjust

it using HDMI pattern. You can select option at “Ez-Adjust

Menu – 7. White Balance” there items “NONE, INNER,

HDMI”. It is normally setting at inner basically. If you can’t

adjust using inner pattern you can select HDMI item, and

you can adjust.

In manual Adjust case, if you press ADJ button of service

remocon, and enter “Ez-Adjust Menu – 7. White Balance”,

then automatically inner pattern operates. (In case of

“Inner” originally “Test-Pattern. On” will be selected in The

“Test-Pattern. On/Off”.

● Connect all cables and equipments like Pic.5)

● Set Baud Rate of RS-232C to 115200. It may set 115200

orignally.

● Connect RS-232C cable to set

● Connect HDMI cable to set

■ RS-232C Command (Commonly apply)

RS-232C COMMAND

[CMD ID DATA]

wb 00 00 White Balance adjustment start.

wb 00 10 Start of adjust gain

(Inner white pattern)

wb 00 1f End of gain adjust

wb 00 20 Start of offset adjust

(Inner white pattern)

wb 00 2f End of offset adjust

wb 00 ff End of White Balance adjust

(Inner pattern disappeared)

● “wb 00 00”: Start Auto-adjustment of white balance.

● “wb 00 10”: Start Gain Adjustment (Inner pattern)

● “jb 00 c0” :

● …

● “wb 00 1f”: End of Adjustment

* If it needs, offset adjustment (wb 00 20-start, wb 00 2f-

end)

● “wb 00 ff”: End of white balance adjustment (inner pattern

disappear)

Meaning

■ Adjustment Mapping information

RS-232C

COMMAND

[CMD ID DATA]

Cool Mid Warm Cool Mid Warm

R Gain jg Ja jd 00 184 192 192 192

G Gain jh Jb je 00 187 183 159 192

B Gain ji Jc jf 00 192 161 95 192

R Cut 64 64 64 127

G Cut 64 64 64 127

B Cut 64 64 64 127

● When Color temperature (White balance) Adjustment

(Automatically)

- Press “Power only key” of service remocon and operate

automatically adjustment.

- Set BaudRate to 115200.

● You must start “wb 00 00” and finish it “wb 00 ff”.

● If it needs, then adjustment “Offset”.

■ White Balance Adjustment (Manual adjustment)

● Test Equipment: CA-210

- Using PDP color temperature, Color Analyzer (CA-210)

must use CH 10, which Matrix compensated (White, Red,

Green, Blue compensation) with CS-2100. See the

Coordination bellowed one.

● Manual adjustment sequence is like bellowed one.

- Turn to “Ez-Adjust” mode with press ADJ button of service

remocon.

- Select “10.Test Pattern” with CH+/- button and press

enter. Then set will go on Heat-run mode. Over 30

minutes set let on Heat-run mode.

- Let CA-210 to zero calibration and must has gap more

10cm from center of PDP module when adjustment.

- Press “ADJ” button of service remocon and select

“7.White-Balance” in “Ez-Adjust” then press “►” button of

navigation key. (When press “►” button then set will go to

full white mode)

- Adjust at three mode (Cool, Medium, Warm)

- If “cool” mode

Let B-Gain to 192 and R, G, B-Cut to 64 and then control

R, G gain adjustment High Light adjustment.

- If “Medium” and “Warm” mode Let R-Gain to 192 and R,

G, B-Cut to 64 and then control G, B gain adjustment

High Light adjustment.

- All of the three mode

Let R-Gain to 192 and R, G, B-Cut to 64 and then control

G, B gain adjustment High Light adjustment.

- With volume button (+/-) you can adjust.

- After all adjustment finished, with Enter (■ key) turn to

Ez-Adjust mode. Then with ADJ button, exit from

adjustment mode

* Attachment: White Balance adjustment coordination and

color temperature.

● Using CS-1000 Equipment.

- COOL : T=11000K, ∆uv=0.000, x=0.276 y=0.283

- MEDIUM : T=9300K, ∆uv=0.000, x=0.285 y=0.293

- WARM : T=6500K, ∆uv=0.000, x=0.313 y=0.329

M

I

N

CENTER

(DEFAULT)

M

A

X

Only for training and service purposes

- 8 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 9

● When tester will measure on Cool condition, adjust W30 on

TV display menu.

● When tester will measure on medium condition, adjust 0 on

TV display menu.

● When tester will measure on warm condition, adjust W30 on

TV display menu.

● Using CA-210 Equipment. (10 CH)

- Contrast value: 216 Gray

Color

temperature

COOL CA-210 0.276 ± 0.002 0.283 ± 0.002

MEDIUM CA-210 0.285 ± 0.002 0.293 ± 0.002

WARM CA-210 0.313 ± 0.002 0.329 ± 0.002

- Brightness spec.

Item White average

Min 27.41 -15

Typ 34.55

Max +15

Unit cd/m² %

Remark - 100% Window White

Pattern

- 100IRE(255Gray)

- Picture: Vivid(Medium)

Test

Equipment

brightness

Color Coordination

x y

Brightness uniformity

- 85IRE(216Gray) 100%

Window White Pattern

- Picture: Vivid(Medium)

6. GND and ESD Testing

6.1. Prepare GND and ESD Testing.

■ Check the connection between set and power cord

6.2. Operate GND and ESD auto-test.

■ Fully connected (Between set and power cord) set enter the

Auto-test sequence.

■ Connect D-Jack AV jack test equipment.

■ Turn on Auto-controller(GWS103-4)

■ Start Auto GND test.

■ If its result is NG, then notice with buzzer.

■ If its result is OK, then automatically it turns to ESD Test.

■ Operate ESD test

■ If its result is NG, then notice with buzzer.

■ If its result is OK, then process next steps. Notice it with

Good lamp and STOPER Down.

6.3. Check Items.

■ Test Voltage

● GND: 1.5KV/min at 100mA

● Signal: 3KV/min at 100mA

■ Test time: just 1 second.

■ Test point

● GND test: Test between Power cord GND and Signal

cable metal GND.

● ESD test: Test between Power cord GND and Live and

neutral.

■ Leakage current: Set to 0.5mA(rms)

6.4. POWER PCB Ass’y Voltage adjustment

(Va, Vs voltage adjustment)

6.4.1. Test equipment : D.M.M 1EA

6.4.2. Connection Diagram for Measuring

: refer to g.1

5.3. Test of RS-232C control.

- Press In-Start button of Service Remocon then set the

“4.Baud Rate” to 115200. Then check RS-232C control and

5.4. Selection of Country option.

- Selection of country option is allowed only North American

model (Not allowed Korean model). It is selection of Country

about Rating and Time Zone.

■ Models: All models which PU31A Chassis (See the rst

page.)

■ Press “In-Start” button of Service Remocon, then enter the

“Option” Menu with “PIP CH-“ Button

■ Select one of these three (USA, CANADA, MEXICO) de-

pends on its market using “Vol. +/-“button.

* Caution : Don’t push The INSTOP KEY after completing the

function inspection.

* Caution : Inspection only PAL M / NTSC

Only for training and service purposes

(g.1) PCB Assy Voltage adjustment

6.4.3. Adjustment method

6.4.3.1. Vs adjustment (refer g.1)

(1) Connect + terminal of D.M.M. to Vs pin of P811, connect

-terminal to GND pin of P811

(2) After turning VR901, voltage of D.M.M adjustment as same

as Vs voltage which on label of panel left/top ( deviation ;

±1.0V)

6.4.3.2. Va adjustment (refer g.1)

(1) After receiving 100% Full White Pattern, HEAT RUN.

(2) Connect + terminal of D.M.M. to Va pin of P811, connect

-terminal to GND pin of P811

(3) After turning VR502,voltage of D.M.M adjustment as same

as Va voltage which on label of panel left/top (deviation;

±1.0V)

- 9 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 10

7. Default Service option.

7.1. ADC-Set.

■ R-Gain adjustment Value (default 128)

■ G-Gain adjustment Value (default 128)

■ B-Gain adjustment Value (default 128)

■ R-Offset adjustment Value (default 128)

■ G-Offset adjustment Value (default 128)

■ B-Offset adjustment Value (default 128)

7.2. White balance. Value.

Center(Default)

COOL Mid Warm

R Gain 192 192 192

G Gain 192 192 192

B Gain 192 192 192

R Cut 64 64 64

G Cut 64 64 64

B Cut 64 64 64

7.3. Temperature Threshold

■ Threshold Down Low 20

■ Threshold Up Low 23

■ Threshold Down High 70

■ Threshold Up High 75

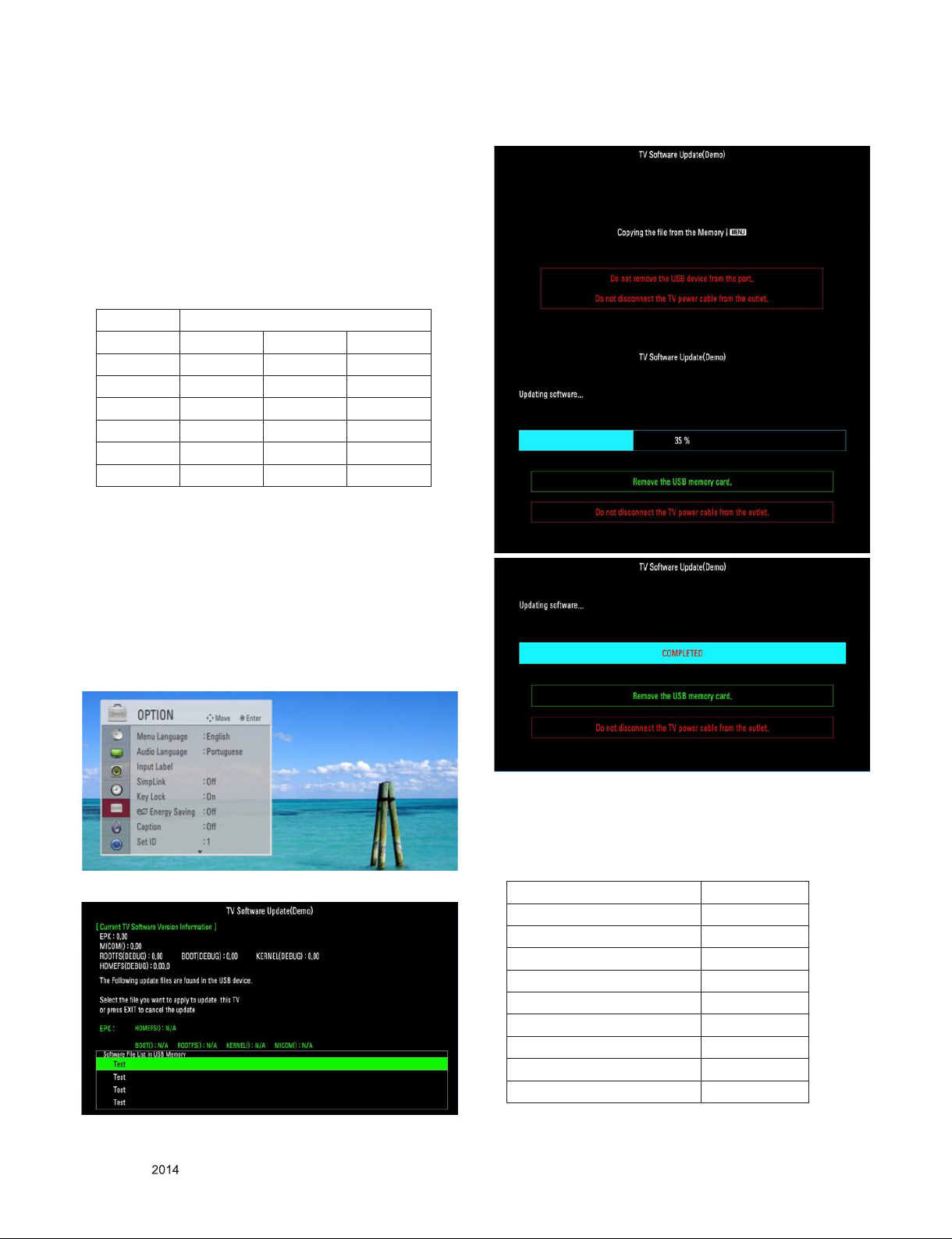

■ Select download le (epk le)

8. USB DOWNLOAD(*.epk le download)

■ Put the USB Stick to the USB socket

■ Press Menu key, and move OPTION

■ Press “FAV” Press 7 times

■ After download is nished, remove the USB stick.

■ Press “IN-START” key of ADJ remote control, check the

S/W version.

9. Tool option

Sufx : WZ,WH,WF,WD,WS 60PB6500-SA

Tool option 1 16411

Tool option 2 2577

Tool option 3 16257

Tool option 4 14184

Tool option 5 51218

Tool option 6 400

Country Group Code 03

Country Group BR

Country BR

Only for training and service purposes

- 10 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

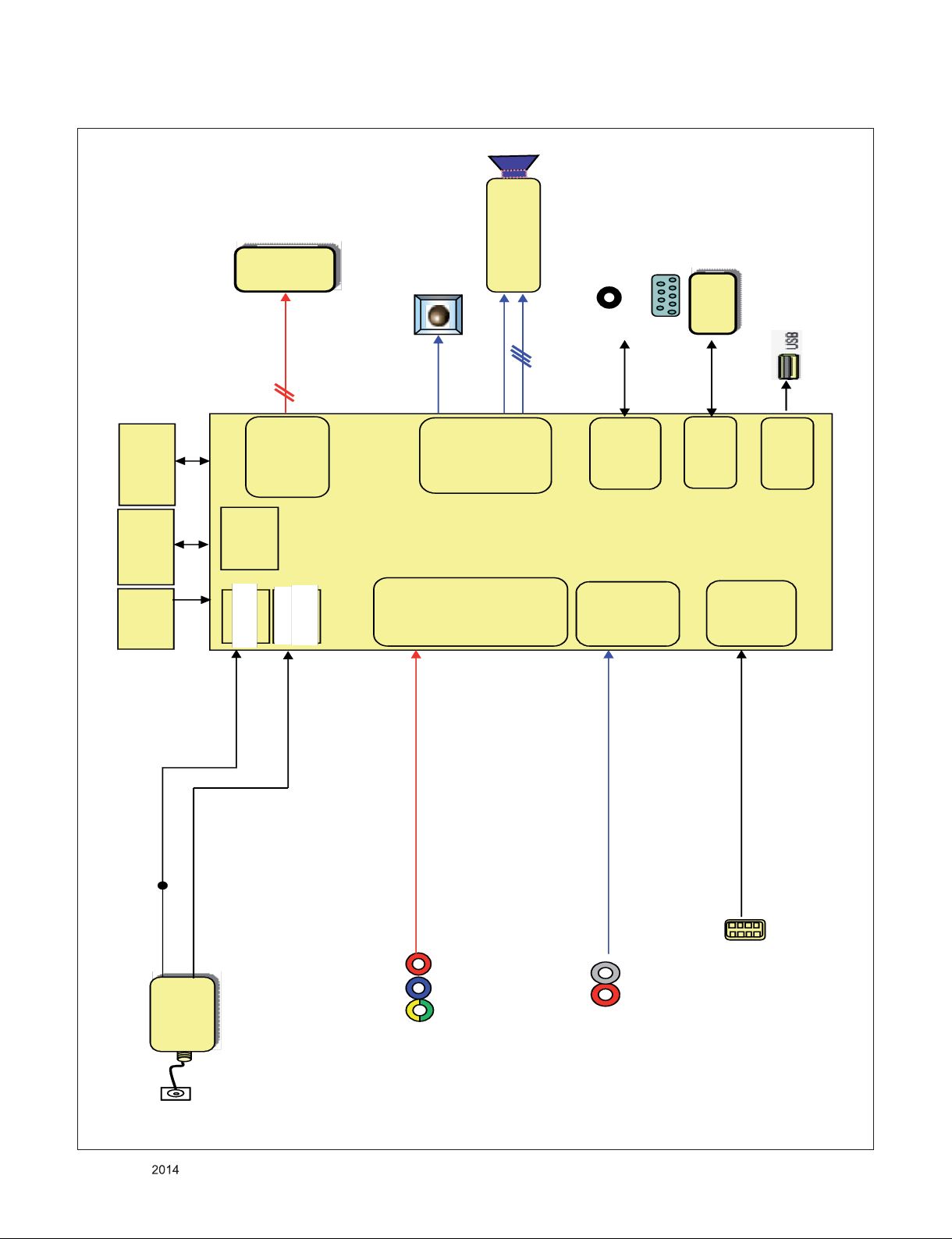

Page 11

LVDS

Con.HDFHD

BLOCK DIAGRAM

115mV

TAS5733

(Digital AMP)

EEPROM

Serial Flash

X-tal

I2S

MCLK

HD/ FHD

LVDS out

Video

HD/SD

64K x 8bit

Encoder

SPDIF Out

DSP

Audio

RS-232C

RS-232C (Commercial)

RX/TX

MODULE

UART

UART

172mV

DDR2

64Mbit

8M x 8bit

Analog

(24MHz)

DEMOD

Demod

M1L

End

Front

Video

Audio

End

Front

HDMI

Side USB

USB2.0

540mV 420mV

RX

L/R

IF(ATSC)

IF(NTSC)

Y(CVBS)/Cb/Cr

TMDS/DDC

IF

NTSC

/ATSC

Air/Cable

Only for training and service purposes

HDMI (Side)

L/R

(Hybrid)

AV/COMP

- 11 -

AV/COMP/DVI

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

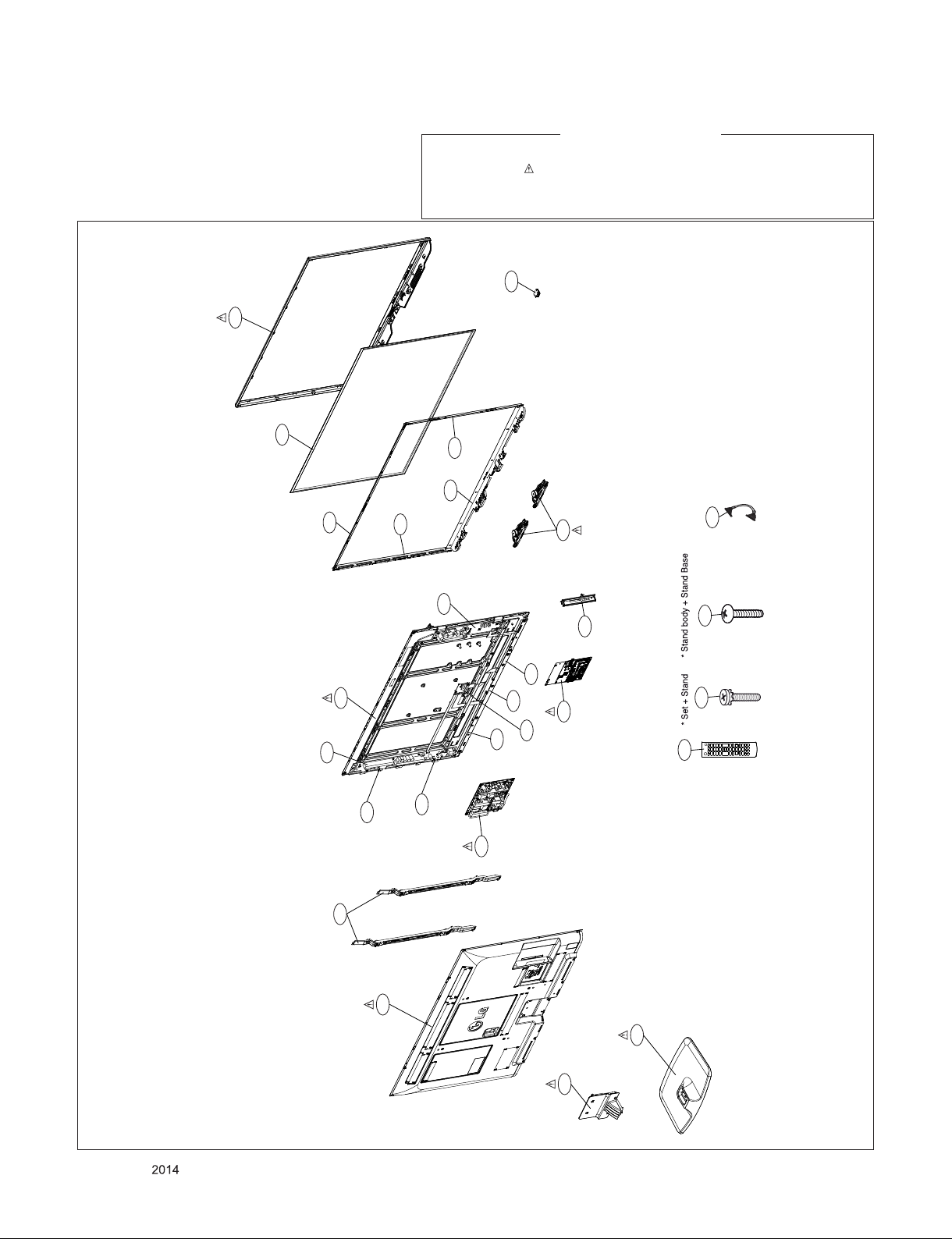

Page 12

300

EXPLODED VIEW

IMPORTANT SAFETY NOTICE

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These

parts are identified by in the Schematic Diagram and EXPLODED VIEW.

It is essential that these special safety parts should be replaced with the same components as

recommended in this manual to prevent X-RADIATION, Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

560

305

301

207

200

202

302

203

208

304

303

580

204

205

120

LV1

A9

601

206

A10

520

201

A2

Only for training and service purposes

240

400

- 12 -

900

910

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

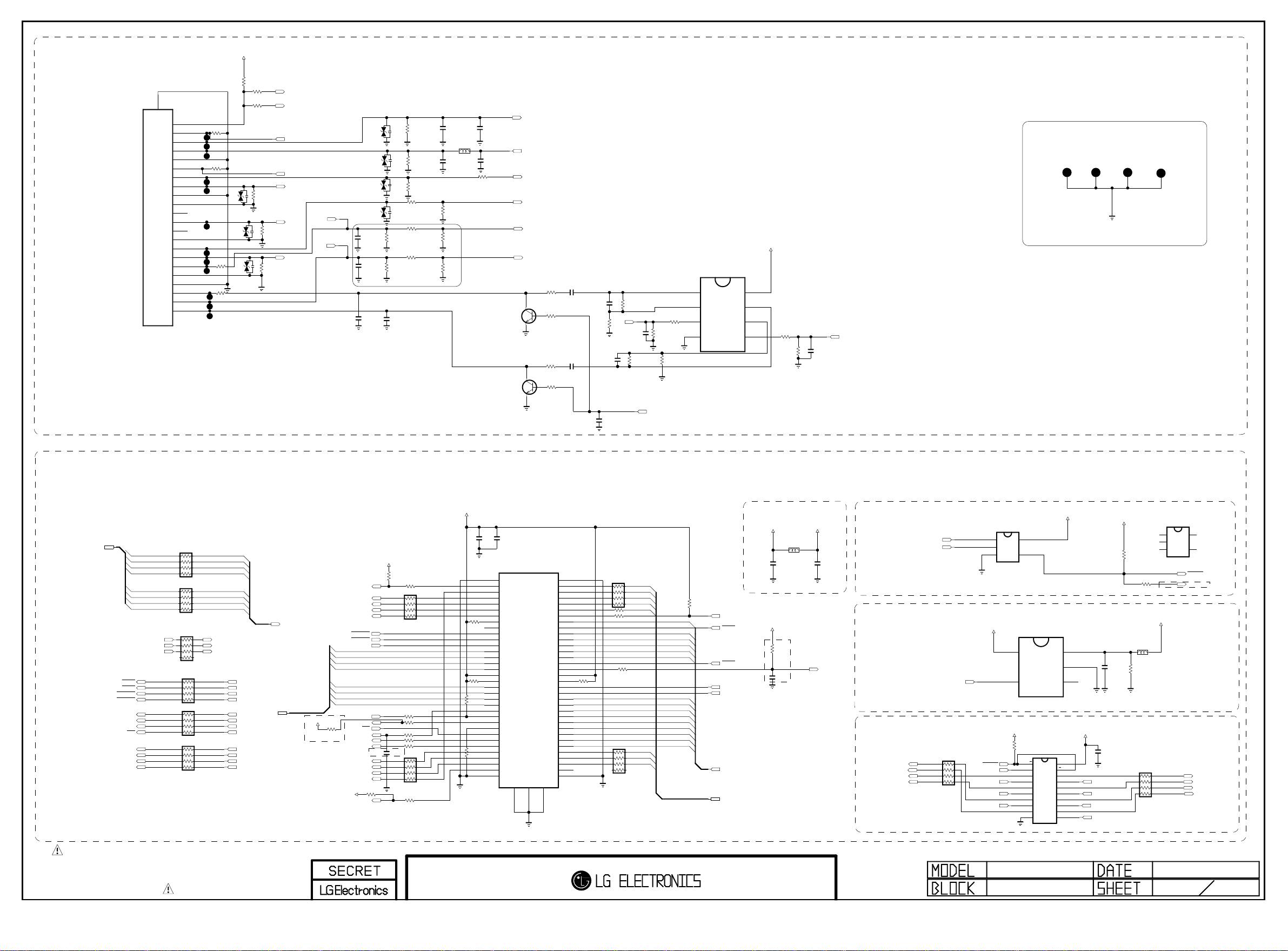

Page 13

<Full SCART>

Copyright © 2014 LG Electronics Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

+3.3V

EU

JK100

PSC008-02

SHIELD

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

AV_DET

COM_GND

SYNC_IN

SYNC_OUT

SYNC_GND2

SYNC_GND1

RGB_IO

R_OUT

RGB_GND

R_GND

D2B_OUT

G_OUT

D2B_IN

G_GND

ID

B_OUT

AUDIO_L_IN

B_GND

AUDIO_GND

AUDIO_L_OUT

AUDIO_R_IN

AUDIO_R_OUT

R169

R168

R170

R166

R104

10K

GROWTH

R105 1K

EU

R171

0

EU

0

EU

VA106

VA103

EU

0

VA104

EU

0

EU

R106

75

1K

EU

R108

75

EU

R107

75

AV2_CVBS_DET

SC1/COMP1_DET

AV2_R_IN1

AV2_L_IN1

SC_DSUB_R+

SC_DSUB_G+

SC_DSUB_B+

AV2_L_IN

AV2_R_IN

C117

1000pF

50V

C118

1000pF

50V

C107

5600pF

50V

EU

VA101

VA102

VA105

VA100

R115

470K

R116

470K

5600pF

R117

75

EU

EU

R147

75

EU

EU

R119

75

EU

EU

R114

10K

EU

EU

R121

10K

R124

10K

AV_COMMON

C108

50V

EU

C109

27pF

50V

EU

EU

L102

CM2012FR22KT

220nH

EU

C139

68pF

50V

R120

2.7K

EU

R126

12K

R127

12K

DTV_R_OUT

C111

220pF

50V

EU

EU

C140

68pF

50V

R123 33

EU

MMBT3904(NXP)

MMBT3904(NXP)

Q102

EU

Q101

EU

AV/SC1_CVBS_IN

DTV/MNT_VOUT

SC_FB_DSUB_VSYNC

SC_ID_DSUB_HSYNC

AV/SC1_L_IN

AV/SC1_R_IN

R138

2K

EU

R137

470

EU

R139

2K

EU

R140

470

EU

C113

10uF

10V

C112

10uF

10V

P_17V

IC101

AZ4580MTR-E1

EU

R149

C114

27pF

15K

50V

EU

EU

SCART1_Lout

R145

6.8K

EU

330pF

EU

C120

EU

C115

R148

27pF

15K

50V

EU

EU

C138

0.1uF

READY

SCART1_MUTE

220K

OUT1

1

IN1-

2

IN1+

R154

5.6K

R158

EU

R152

6.8K

EU

3

VEE

EU

4

VCC

8

OUT2

7

IN2-

6

IN2+

5

5.6K

R153

R159

EU

220K

EU

330pF

C119

SCART1_Rout

EU

PDP L14

EAX65405603

JP112

JP113

JP114

JIG_GND

JP115

<CI SLOT>

BUF1_FE_TS_DATA[0-7]

CI_ADDR[12]

CI_ADDR[13]

CI_ADDR[14]

CI_ADDR[8]

CI_ADDR[9]

CI_ADDR[10]

CI_ADDR[11]

BUF1_FE_TS_DATA[7]

BUF1_FE_TS_DATA[6]

BUF1_FE_TS_DATA[4]

BUF1_FE_TS_DATA[3]

BUF1_FE_TS_DATA[2]

BUF1_FE_TS_DATA[1]

BUF1_FE_TS_DATA[0-7]

BUF1_FE_TS_DATA[0]

BUF1_FE_TS_SYN

BUF1_FE_TS_VAL_ERR

BUF1_FE_TS_CLK

CI_OE

CI_WE

CI_IORD

CI_IOWR

REG

AR109

BUF2_FE_TS_DATA[7]

BUF2_FE_TS_DATA[6]

BUF2_FE_TS_DATA[5]BUF1_FE_TS_DATA[5]

BUF2_FE_TS_DATA[4]

33EU

AR108

BUF2_FE_TS_DATA[3]

BUF2_FE_TS_DATA[2]

BUF2_FE_TS_DATA[1]

BUF2_FE_TS_DATA[0]

33EU

AR110

33

EU

EU

AR105

EU

AR106 33

EU

AR107 33

BUF2_FE_TS_SYN

BUF2_FE_TS_VAL_ERR

BUF2_FE_TS_CLK

33

/PCM_OE

/PCM_WE

/PCM_IORD

/PCM_IOWR

BUF2_FE_TS_DATA[0-7]

PCM_A[12]

PCM_A[13]

PCM_A[14]

/PCM_REG

PCM_A[8]

PCM_A[9]

PCM_A[10]

PCM_A[11]

BUF2_FE_TS_DATA[0-7]

+5V

R129 10K

Close to mstar

Close to mstar

/CI_CD1

CI_TS_DATA[4]

CI_TS_DATA[5]

CI_TS_DATA[6]

CI_TS_DATA[7]

CI_IORD

CI_IOWR

BUF2_FE_TS_SYN

BUF2_FE_TS_DATA[0]

BUF2_FE_TS_DATA[1]

BUF2_FE_TS_DATA[2]

BUF2_FE_TS_DATA[3]

BUF2_FE_TS_DATA[4]

BUF2_FE_TS_DATA[5]

BUF2_FE_TS_DATA[6]

BUF2_FE_TS_DATA[0-7]

BUF2_FE_TS_DATA[7]

PCM_RST

/PCM_WAIT

REG

EU

CI_TS_CLK

CI_TS_VAL

CI_TS_SYNC

CI_TS_DATA[0]

CI_TS_DATA[1]

CI_TS_DATA[2]

CI_TS_DATA[3]

R150

10K

EU

+5V

/CI_CD2

+5V

R151

10K

EU

AR100 33

R100

R101 33

R155 100EU

R156 33

R157 33

C102 2pF

AR102 33

R102

100

EU

R103

100

EU

+5V_CI_ON

C101

C100

0.1uF

22uF

16V

10V

EU

EU

JK102

10067972-000LF

EU

35

36

R111

10K

EU

R112

0

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

65

66

67

68

2

EU

READY

R109

10K

EU

EU

33

EU

EU

EU

EU

R110

0

READY

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

R128 0

18

READY

19

20

21

22

23

24

25

2660

2761

2862

2963

3064

31

32

33

34

G1G2

1

69

AR103

33

EU

R130 33EU

R131 33EU

R132 100

AR104

33

EU

PCM_D[3]

PCM_D[4]

PCM_D[5]

PCM_D[6]

PCM_D[7]

EU

PCM_D[0]

PCM_D[1]

PCM_D[2]

CI_ADDR[10]

CI_ADDR[11]

CI_ADDR[9]

CI_ADDR[8]

CI_ADDR[13]

CI_ADDR[14]

CI_ADDR[12]

CI_ADDR[7]

CI_ADDR[6]

CI_ADDR[5]

CI_ADDR[4]

CI_ADDR[3]

CI_ADDR[2]

CI_ADDR[1]

CI_ADDR[0]

PCM_D[0-7]

R133

10K

EU

<3.3V_CI>

/PCM_CE

CI_OE

CI_WE

BUF2_FE_TS_VAL_ERR

BUF2_FE_TS_CLK

CI_ADDR[0-14]

PCM_D[0-7]

+3.3V

L101

120-ohm

EU

C136

0.1uF

16V

READY

+5V

Close to mstar

R135

10K

EU

EU

C104

0.1uF

16V

+3.3V_CI

C137

0.1uF

16V

EU

/PCM_IRQA

<CI DETECT>

/CI_CD2

/CI_CD1

<CI ENABLE>

<CI SWITCH>

CI_ADDR[5]

CI_ADDR[4]

CI_ADDR[7]

PCM_5V_CTL

AR111

100

1/16W

OR_GARE_CI_PHILIPS

IC104

74LVC1G32GW

1B 5 VCC

3GND2A4 Y

+5V

IN

EN

+3.3V_CI

EU

R165

TC74LCX244FT

10K

EU

CI_DET

PCM_A[0]

PCM_A[1]CI_ADDR[6]

PCM_A[2]

PCM_A[3]

AP2151WG-7

5

4

IC100

1OE

1

1A1

2

2Y4

3

1A2

4

2Y3

5

1A3

6

2Y2

7

1A4

8

2Y1

9

GND

10

IC102

EU

+3.3V_CI

EU

1

2

3

VCC

20

2OE

19

1Y1

18

2A4

17

1Y2

16

2A3

15

1Y3

14

2A2

13

1Y4

12

2A1

11

OUT

GND

FLG

+3.3V_CI

C105

0.1uF

PCM_A[7]

PCM_A[6]

PCM_A[5]

PCM_A[4]

+3.3V_CI

R125

10K

EU

EU

C103

1uF

25V

EU

16V

R134

47

EU

+5V_CI_ON

L100

BLM18PG121SN1D

EU

R1674

100K

EU

AR112

100

1/16W

OR_GARE_CI_TI

IC104-*1

SN74LVC1G32DCKR

VCC

1A5

B

2

GND

Y

3

4

CI_DET

/PCM_CD

EU

CI_ADDR[0]

CI_ADDR[1]

CI_ADDR[2]

CI_ADDR[3]

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FIRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFACTURES SPECIFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

L14

SCART,CI Slot

2013-08-06

1

10

Page 14

<HDMI/MHL>

Copyright © 2014 LG Electronics Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

CK+

D0-

D0_GND

D0+

D1-

D1_GND

D1+

D2-

D2_GND

D2+

5V_HDMI_3

R238

1.8K

D201

ESD_HDMI

BODY_SHIELD

20

JK201

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

<CEC>

CEC_REMOTE

5V_DET_HDMI_2

ESD_HDMI_SEMTECH

ESD_HDMI_SEMTECH

D210

5.6V

READY

R209 100

R244

3.3K

R231

33

R246

33

10

1

9

2

3

8

4

7

6

5

IC208

RCLAMP0524PA

10

1

9

2

3

8

4

7

6

5

IC209

RCLAMP0524PA

C206

R222

0.047uF

300K

25V

MHL Spec

R268

100

CEC_REMOTE_S7

HPD4

DDC_SDA_4

DDC_SCL_4

CEC_REMOTE

CK-_HDMI3

CK+_HDMI3

D0-_HDMI3

D0+_HDMI3

D1-_HDMI3

D1+_HDMI3

D2-_HDMI3

D2+_HDMI3

MHL_CD_SENSE

5V_HDMI_3

R248

R247

2.7K

2.7K

<AV (Growth & SCA)>

GROWTH

JK202

PPJ231-01

AV2_R_IN1

4

AV2_L_IN1

5

7

8

6

R230

75

GROWTH

R286

0

R287

0

R203

0

R234

0

+5V

A2CA1

MMBD6100

D212

GROWTH

GROWTH

GROWTH

GROWTH

+3.3V_ST

A2CA1

MMBD6100

D211

DDC_SDA_4

DDC_SCL_4

AV2_R_IN

AV2_L_IN

AV2_CVBS_DET

AV/SC1_CVBS_IN

<COMPONENT>

JK208

PPJ234-22

3AU04S-305-ZC-(LG)

[YL/GN]FIX

1

[YL/GN]SWITCH

3

[YL/GN]SHUNT

2

[BL]EARTH

4

[BL]SWITCH

5

[RD1]EARTH

6

[RD1]SWITCH

8

[RD1]SHUNT

7

[WH]SWITCH

9

[RD2]SHUNT

10

[RD2]SWITCH

11

[RD2]FIX

12

JK203

USB DOWN STR EAM

R251

75

R252

75

R253

75

C204

50V

1000pF

<SIDE USB>

READY

1234

5

VA216

C205

1000pF

ZD200

SD05

5V

VA208

VA210

VA209

50V

COMP2_Y+

COMP2_Pb+

COMP2_Pr+

R254

470K

VA217

D213

RCLAMP0502BA

READY

+3.3V

R256 10K

R25710K

R255

470K

C200

0.1uF

16V

R259

10K

R265

10K

C201

10uF

10V

R266

1K

R262

12K

12K

R267

1K

R263

VA211

READY

C230

10uF

10V

VA212

AV_CVBS_DET

COMP2_DET

COMP2_L_IN

COMP2_R_IN

+5V_USB

SIDE_USB_DM

SIDE_USB_DP

<SPDIF>

SPDIF-JACK-SOLTEAM

JK204

JST1223-001

1

2

Fiber Optic

3

4

FIX_POLE

GND

VCC

VINPUT

SPDIF-JACK-FOXCONN

JK204-*1

2F01TC1-CLM97-4F

GND

+5V

C219

0.1uF

R285

16V

100

C220

10pF

50V

SPDIF_OUT

1

VCC

2

VIN

3

Fib er Op tic

4

SHI ELD

<FOR COMMERCIAL>

<RS232C>

+3.3V_ST

10K

R276 100

USA

6 M6

1 M1

3 M3_DETECT

4 M4

5 M5_GND

PEJ038-4G6

JK214

R278

+3.3V_ST

P602

12507WS-04L

1

2

3

10K

R279

4

5

IC206

MAX3232

PM_TXD

PM_RXD

1

2

3

4

5

6

7

8

C1+

V+

C1-

C2+

C2-

V-

DOUT2

RIN2

+3.3V_ST

MAX3232

C228

0.1uF

16V

C225

0.1uF

16V

MAX3232

MAX3232

C226

0.1uF

16V

MAX3232

C227

0.1uF

16V

MAX3232

C229

0.1uF

16V

R283 22

R284 22

VCC

GND

DOU T1

RIN 1

ROU T1

DIN 1

DIN2

ROUT2

MAX3232CDR

16

15

14

13

12

11

10

9

JP241

USA

R277

100

USA

<Mstar Debug 4P>

P603

12505WS-04A00

1

2

3

4

5

RGB_DDC_SCL

RGB_DDC_SDA

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FIRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFACTURES SPECIFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

L14

JACK INTERFACE

2013-08-06

2

10

Page 15

<L14 TUNER T2/C/S2>

Copyright © 2014 LG Electronics Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

TU_KR

TU300-*1

TDJH-H101F

B1[+3.3V]

1

NC_1

2

IF_AGC

3

SCL

4

SDA

5

IF[P]

6

IF[N]

7

NC_2

8

NC_3

9

A1

A1

A1

A1

47

SHIELD

47

SHIELD

B1

B1

TU_Thailand

TU301-*1

TDJM-G105D

B1[+3.3V]

1

NC_1

2

AIF_AGC

3

SCL_RF

4

SDA_RF

5

AIF[P]

6

AIF[N]

7

NC_2

8

NC_3

9

NC_4

10

B2[+3.3V]

11

ERROR

12

GND_1

13

MCLK

14

SYNC

15

VAILD

16

D0

17

D1

18

D2

19

D3

20

D4

21

D5

22

D6

23

D7

24

RESET_DEMOD

25

B3[+3.3V]

26

SCL_DEMOD

27

B4[+1.1V]

28

F22_OUTPUT

29

SDA_DEMOD

30

B1

B1

TU_GND

A1

DVB-T/C_Tuner

A1

A1

TU_BR_PA

A1

47

TU300

TDJH-G101D

1

2

3

4

5

6

7

8

9

B1

47

SHIELD

TU303

TDJK-T101F

B1[+3.3V]

1

RF_S/W_CTL

2

IF_AGC

3

SCL

4

SDA

5

IF[P]

6

IF[N]

7

NC_1

8

NC_2

9

B1

B1

TU_GND_B

B1[+3.3V]

NC_1

IF_AGC

SCL

SDA

IF[P]

IF[N]

NC_2

NC_3

B1

TU_GND_B

A1

TU_CO

A1

SHIELD

TU_GND

TU_GND_B

TU_GND

TU302

TDJM-K101F

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

B1

47

SHIELD

B1[+3.3V]

RF_SW_CTL

AIF_AGC

SCL_RF

SDA_RF

AIF[P]

AIF[N]

NC_1

NC_2

NC_3

NC_4

ERROR

GND_1

MCLK

SYNC

VAILD

D0

D1

D2

D3

D4

D5

D6

D7

RESET_DEMOD

B2[+3.3V]

SCL_DEMOD

B3[+1.1V]

NC_5

SDA_DEMOD

B1

TU_GND_B

DVB-T2/C/S2_Tuner

A1

A1

TU_GND

TU301

TDJM-G101D

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

B1

47

47

B1[+3.3V]

NC_1

AIF_AGC

SCL_RF

SDA_RF

AIF[P]

AIF[N]

NC_2

NC_3

NC_4

B2[+3.3V]

ERROR

GND_1

MCLK

SYNC

VALID

D0

D1

D2

D3

D4

D5

D6

D7

RESET_DEMOD

B3[+3.3V]

SCL_DEMOD

B4[+1.1V]

F22_OUTPUT

SDA_DEMOD

LNB

GND

B1

TU_GND_B

C300

100pF

50V

C327

READY

10pF

F_NIM

C302

0.1uF

16V

C301

0.1uF

16V

0.1uF

16V

C328

READY

10pF

F_NIM

AR300 0

F_NIM

AR301 0

F_NIM

AR302 0

F_NIM

R300

R301

C303

20pF

50V

F_NIM

R303

C304

20pF

50V

F_NIM

C305

0.1uF

16V

F_NIM

C306

+3.3V_TU

10

F_NIM

C307

100pF

50V

R306

0

R304

10

R305

10

FE_TS_ERR

BUF1_FE_TS_CLK

BUF1_FE_TS_SYN

BUF1_FE_TS_VAL_ERR

BUF1_FE_TS_DATA[0]

BUF1_FE_TS_DATA[1]

BUF1_FE_TS_DATA[2]

BUF1_FE_TS_DATA[3]

BUF1_FE_TS_DATA[4]

BUF1_FE_TS_DATA[5]

BUF1_FE_TS_DATA[6]

BUF1_FE_TS_DATA[7]

22

F_NIM

R302

51

F_NIM

22

+3.3V_LNA

0.1uF

C324

should be guarded by ground

C308

47pF

50V

C309

47pF

50V

BUF1_FE_TS_DATA[0-7]

DEMOD_RESET

+3.3V_S2_DE

DEMOD_SCL

LNB_TX

DEMOD_SDA

LNB_OUT

READY

R330

2.2K

+3.3V_S2_DE

READY

R331

2.2K

IF_AGC_MAIN

TU300

TU300-1

TU301

TU302

TU303

close to Tuner

RF_SWITCH_CTL

R309 33

R308 33

+3.3V_S2_DE

F_NIM

C310

100pF

50V

+1.2V_TU

C311

100pF

50V

F_NIM

F_NIM

C313

0.1uF

16V

C314

0.1uF

16V

F_NIM

+3.3V_TU

R310

1K

RF_SWITCH_CTL

R322

R323

20K

RF_SWITCH_CTL

R312

1K

1K

C312

0.1uF

16V

TUNER

TDJH-G101D

TDJH=H101F

TDJM-G101D

TDJM-K101F

TDJK-T101F

RF_SWITCH_CTL

TU_SCL

TU_SDA

IF_P_MSTAR

IF_N_MSTAR

<+3.3V_S2_DE>

TU_GND

0

R324

DVB-T/C_Tuner

READY

0

R325

R326

DVB-T/C

ATSC

DVB-S2/T2

+3.3V_TU

C319

22uF

10V

+3.3V_TU

C321

0.1uF

16V

GND seperation for DVB-T2, SVBTVD tuner

READY

READY

READY

READY

0

R327

0

0

0

R329

R328

OPT1 OPT3

L300

UBW2012-121F

C320

0.1uF

16V

BLM18PG121SN1D

OPT2

+3.3V_LNA

C322

22uF

10V

F_NIM

L301

HNIM

HNIM

HNIM

DVB-T2

SBTVD

+3.3V_S2_DE

F_NIM

C323

10uF

10V

X

X

X

F_NIM

C326

0.1uF

16V

OPT4

W/O AD

W/O AD

W/O AD

<+3.3V_LNA>

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FIRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFACTURES SPECIFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

TUNER

L14

Tuner

2013-08-06

3 10

Page 16

<HDMI& AV/COMP >

Copyright © 2014 LG Electronics Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

IC1202

LGE2132(M1A_256M)

NON_BRAZIL

ARC0

RXC0N

RXC0P

RXC1N

RXC1P

RXC2N

RXC2P

RXCCKN

RXCCKP

CEC/GPIO6

DDCDA_CK/GPIO27

DDCDA_DA/GPIO28

DDCDC_CK/GPIO31

DDCDC_DA/GPIO32

HOTPLUGA/GPIO23

HOTPLUGC/GPIO25

RXA0N

RXA0P

RXA1N

RXA1P

RXA2N

RXA2P

RXACKN

RXACKP

EAR_OUTL

EAR_OUTR

AUL1

AUL2

AUL3

AUR1

AUR2

AUR3

AUOUTL0

AUOUTR0

AUVAG

I2S_OUT_BCK/GPIO165

I2S_OUT_MCK/GPIO163

I2S_OUT_SD/GPIO166

I2S_OUT_WS/GPIO164

<BRAZIL OPT>

V10

TS0CLK/GPIO92

T14

TS0DATA[0]/GPIO82

T13

TS0DATA[1]/GPIO83

U13

TS0DATA[2]/GPIO84

V15

TS0DATA[3]/GPIO85

U12

TS0DATA[4]/GPIO86

V13

TS0DATA[5]/GPIO87

U14

TS0DATA[6]/GPIO88

T11

TS0DATA[7]/GPIO89

T12

TS1DATA[0]/GPIO93

TS1DATA[1]/GPIO94

TS1DATA[2]/GPIO95

TS1DATA[3]/GPIO96

TS1DATA[4]/GPIO97

TS1DATA[5]/GPIO98

TS1DATA[6]/GPIO99

TS1DATA[7]/GPIO100

TS1VALID/GPIO101

PM_SPI_SCK/GPIO1

PM_SPI_SCZ0/GPIO0

PM_SPI_SDI/GPIO2

PM_SPI_SDO/GPIO3

SPDIF_IN/GPIO161

SPDIF_OUT/GPIO162

DDCA_CK/UART0_RX

DDCA_DA/UART0_TX

TS0SYNC/GPIO91

TS0VALID/GPIO90

TS1CLK/GPIO103

TS1SYNC/GPIO102

HWRESET

IRIN/GPIO5

PWM0/GPIO71

PWM1/GPIO72

PWM2/GPIO73

PWM3/GPIO74

PWM4/GPIO75

NF_ALE/GPIO146

NF_CEZ/GPIO142

NF_CLE/GPIO141

NF_RBZ/GPIO147

NF_REZ/GPIO144

NF_WEZ/GPIO145

NF_WPZ/GPIO199

IF_AGC

SIFM

SIFP

XOUT

BRAZIL

V12

IC1202-*1

Y14

LGE2131(M1A_128M)

Y16

AA15

Y13

AA16

W12

AA13

W14

W13

Y15

W15

B3

A3

A4

C3

A2

B1

RP

C2

TN

C1

TP

B2

RN

D2

D1

D8

E5

G4

G5

J18

K18

K16

L18

L17

T8

T9

U9

U11

V9

U10

T10

W2

W1

W3

V2

IM

V1

IP

AA2

XIN

Y2

E11

B_DDR3_A[0]

F12

B_DDR3_A[1]

D10

B_DDR3_A[2]

B10

B_DDR3_A[3]

E15

B_DDR3_A[4]

B11

B_DDR3_A[5]

F14

B_DDR3_A[6]

C11

B_DDR3_A[7]

D14

B_DDR3_A[8]

A12

B_DDR3_A[9]

F16

B_DDR3_A[10]

D13

B_DDR3_A[11]

D15

B_DDR3_A[12]

C12

B_DDR3_A[13]

E13

B_DDR3_A[14]

A9

B_DDR3_BA[0]

D16

B_DDR3_BA[1]

A10

B_DDR3_BA[2]

C13

B_DDR3_MCLK

B13

B_DDR3_MCLKZ

E17

B_DDR3_MCLKE

B8

B_DDR3_ODT

C8

B_DDR3_RASZ

B9

B_DDR3_CASZ

D11

B_DDR3_WEZ

F10

B_RESET

D12

B_DDR3_CS0

A19

B_DDR3_DQSL

B18

B_DDR3_DQSU

C16

B_DDR3_DQML

D21

B_DDR3_DQMU

C18

B_DDR3_DQSBL

C17

B_DDR3_DQSBU

A20

B_DDR3_DQL[0]

A16

B_DDR3_DQL[1]

C19

B_DDR3_DQL[2]

C15

B_DDR3_DQL[3]

C20

B_DDR3_DQL[4]

C14

B_DDR3_DQL[5]

B21

B_DDR3_DQL[6]

B15

B_DDR3_DQL[7]

F18

B_DDR3_DQU[0]

D19

B_DDR3_DQU[1]

D17

B_DDR3_DQU[2]

E21

B_DDR3_DQU[3]

E19

B_DDR3_DQU[4]

D20

B_DDR3_DQU[5]

D18

B_DDR3_DQU[6]

F20

B_DDR3_DQU[7]

E9

ZQ

CVBSOUT1

CVBS0

CVBS1

CVBS2

VCOM

USB0_DM

USB1_DM

USB0_DP

USB1_DP

BIN0M

BIN0P

GIN0M

GIN0P

RIN0M

RIN0P

HSYNC0

VSYNC0

BIN1M

BIN1P

GIN1M

GIN1P

RIN1M

RIN1P

SOGIN1

IC1202-*1

LGE2131(M1A_128M)

M4

ARC0

W7

RXC0N

Y8

RXC0P

W8

RXC1N

Y9

RXC1P

AA9

RXC2N

W9

RXC2P

AA7

RXCCKN

Y7

RXCCKP

N2

CEC/GPIO6

E3

DDCDA_CK/GPIO27

E2

DDCDA_DA/GPIO28

W6

DDCDC_CK/GPIO31

AA6

DDCDC_DA/GPIO32

L4

HOTPLUGA/GPIO23

Y6

HOTPLUGC/GPIO25

F1

RXA0N

G3

RXA0P

G1

RXA1N

G2

RXA1P

H3

RXA2N

H2

RXA2P

F3

RXACKN

F2

RXACKP

U4

EAR_OUTL

T4

EAR_OUTR

P2

AUL1

R2

AUL2

T1

AUL3

R3

AUR1

R1

AUR2

T3

AUR3

U2

AUOUTL0

V3

AUOUTR0

T2

AUVAG

BRAZIL

I2S_OUT_BCK/GPIO165

I2S_OUT_MCK/GPIO163

I2S_OUT_SD/GPIO166

I2S_OUT_WS/GPIO164

T6

V5

U5

T5

V4

E4

F4

F7

F5

C4

Y12

B4

AA12

J2

J3

K3

J1

K2

K1

M6

L6

L2

L3

M1

M2

N1

N3

M3

0.047uF

C4480.047uF

EU

EU

EU

EU

C4170.047uF

EU

C4140.047uF

EU

C415

0.047uF

T6

CVBSOUT1

V5

CVBS0

U5

CVBS1

T5

CVBS2

V4

VCOM

USB0_DM

USB1_DM

USB0_DP

USB1_DP

BIN0M

BIN0P

GIN0M

GIN0P

RIN0M

RIN0P

HSYNC0

VSYNC0

BIN1M

BIN1P

GIN1M

GIN1P

RIN1M

RIN1P

SOGIN1

BRAZIL

IC1202-*1

E4

LGE2131(M1A_128M)

F4

F7

F5

U19

LVA4P/TTL_B[0]/HCONV/GPIO170

T20

C4

LVA4M/TTL_B[1]/E_O/GPIO171

T21

Y12

LVA3P/TTL_B[2]/FB/GPIO172

T19

B4

LVA3M/TTL_B[3]/OPT_P/GPIO173

R21

AA12

LVACKP/TTL_B[4]/MCLK/GPIO174

R20

LVACKM/TTL_B[5]/GCLK/GPIO175

J2

R19

LVA2P/TTL_B[6]/GST/GPIO176

J3

P20

LVA2M/TTL_B[7]/POL/GPIO177

K3

P19

J1

LVA1P/TTL_G[0]/EPI0+/GPIO178

N20

K2

LVA1M/TTL_G[1]/EPI0-/GPIO179

N21

K1

LVA0P/TTL_G[2]/EPI1+/GPIO180

N19

M6

LVA0M/TTL_G[3]/EPI1-/GPIO181

M21

L6

LVB4P/TTL_G[4]/EPI2+/GPIO182

M20

LVB4M/TTL_G[5]/EPI2-/GPIO183

L2

M19

LVB3P/TTL_G[6]/EPI3+/GPIO184

L3

L20

LVB3M/TTL_G[7]/EPI3-/GPIO185

M1

L19

M2

LVBCKP/TTL_R[0]/EPI4+/GPIO186

K20

N1

LVBCKM/TTL_R[1]/EPI4-/GPIO187

K21

N3

LVB2P/TTL_R[2]/EPI5+/GPIO188

K19

M3

LVB2M/TTL_R[3]/EPI5-/GPIO189

J21

LVB1P/TTL_R[4]/EPI6+/GPIO190

J20

LVB1M/TTL_R[5]/EPI6-/GPIO191

J19

LVB0P/TTL_R[6]/EPI7+/GPIO192

H20

LVB0M/TTL_R[7]/EPI7-/GPIO193

PM_SPI_SCZ2/GPIO_PM[10]/GPIO17

PM_UART_TX/GPIO_PM[1]/GPIO8

PM_UART_RX/GPIO_PM[5]/GPIO12

GPIO_PM[13]/GPIO20

GPIO_PM[14]/GPIO21

GPIO_PM[15]/GPIO22

GPIO_PM[4]/GPIO11

GPIO_PM[7]/GPIO14

GPIO_PM[8]/GPIO15

D5

SAR0/GPIO35

F8

SAR1/GPIO36

E7

SAR2/GPIO37

E6

SAR3/GPIO38

D6

SAR4/GPIO39

W10

Y10

P3

PM_LED/GPIO4

Y3

GPIO_PM[0]/GPIO7

Y5

W11

D3

AA3

W5

D4

PWM_PM/GPIO200

L15

Y11

R42533

R42633C4490.047uF

R48168C4130.047uF

0

R454

0

R455

R42868EUC4180.047uF

R42933EUC4190.047uF

R43768EUC4160.047uF

EU

R43833

EU

R43568

EU

R436

33

C4370.047uF

R43368

C4390.047uF

R43433

R44568

C4300.047uF

C4330.047uF

R44633

68

R443

C4280.047uF

C429

R44433

BRAZIL

IC1202-*1

LGE2131(M1A_128M)

U3

R4

AUVRM

AVDD_AU33

A6

L11

GND_1

AVDD_DDR0_CLK

A13

L13

GND_2

AVDD_DDR1_CLK

A15

M11

GND_3

AVDD_DDR0_CMD

A18

K13

GND_4

AVDD_DDR1_CMD

B12

C5

GND_5

AVDD_DDR0_D_1

B14

K12

GND_6

AVDD_DDR0_D_2

B16

L12

GND_7

AVDD_DDR0_D_3

B17

C6

GND_8

AVDD_DDR1_D_1

B19

K14

GND_9

AVDD_DDR1_D_2

B20

L14

GND_10

AVDD_DDR1_D_3

C9

B5

GND_11

AVDD_DRAM_1

C10

B6

GND_12

AVDD_DRAM_2

C21

R8

GND_13

AVDD_DVI_USB_MPLL_1

D9

R9

GND_14

AVDD_DVI_USB_MPLL_2

E20

L7

GND_15

AVDD_MOD_1

F9

L8

GND_16

AVDD_MOD_2

F11

P8

GND_17

AVDD_NODIE

F13

K9

GND_18

AVDD_PLL

F15

R5

GND_19

AVDD3P3_DMPLL

F17

P11

GND_20

AVDDL_MOD

F19

C7

GND_21

DVDD_DDR_1

F21

M13

GND_22

DVDD_DDR_2

G8

R6

GND_23

DVDD_NODIE

G9

A7

GND_24

DVDD_RX_1_1

G10

M12

GND_25

DVDD_RX_1_2

G11

B7

GND_26

DVDD_RX_2_1

G12

M14

GND_27

DVDD_RX_2_2

G13

N11

GND_28

VDDC_1

G14

N12

GND_29

VDDC_2

G15

N13

GND_30

VDDC_3

G16

N14

GND_31

VDDC_4

G17

N15

GND_32

VDDC_5

G18

P12

GND_33

VDDC_6

H7

P13

GND_34

VDDC_7

H8

P14

GND_35

VDDC_8

H9

L9

GND_36

VDDP

H10

GND_37

H11

AA10

GND_38

AVDD5V_MHL

H12

GND_39

H13

GND_40

H14

GND_41

H15

GND_42

H16

GND_43

H17

GND_44

H18

GND_45

J7

GND_46

J8

GND_47

J9

GND_48

J10

GND_49

J11

GND_50

J12

GND_51

J13

GND_52

J14

GND_53

K8

GND_54

K10

GND_55

K11

GND_56

L10

GND_57

M5

GND_58

M7

GND_59

M8

GND_60

M9

GND_61

M10

GND_62

N4

GND_63

N5

GND_64

N6

GND_65

N7

GND_66

N8

GND_67

N9

GND_68

N10

GND_69

P4

GND_70

P5

GND_71

P6

GND_72

P7

GND_73

P9

GND_74

P10

GND_75

P15

GND_76

P16

GND_77

P17

GND_78

P18

GND_79

R10

GND_80

R11

GND_81

R12

GND_82

R13

GND_83

R14

GND_84

K7

GND_EFUSE

DTV/MNT_VOUT

AV/SC1_CVBS_IN

COMP2_Y+

MODEL_OPT_7

MODEL_OPT_3

SIDE_USB_DM

SIDE_USB_DP

SC_DSUB_B+

SC_DSUB_G+

SC_DSUB_R+

SC_ID_DSUB_HSYNC

SC_FB_DSUB_VSYNC

COMP2_Pb+

COMP2_Y+

COMP2_Pr+

R485

10K

READY

R487

10K

READY

+3.3V

R486

10K

READY

R488

10K

READY

I2S_I/F

AUD_SCK

AUD_MASTER_CLK_0

AUD_LRCH

AUD_LRCK

D0-_HDMI3

D0+_HDMI3

D1-_HDMI3

D1+_HDMI3

D2-_HDMI3

D2+_HDMI3

CK-_HDMI3

CK+_HDMI3

CEC_REMOTE_S7

DDC_SCL_4

DDC_SDA_4

HPD4

AV/SC1_L_IN

COMP2_L_IN

AV/SC1_R_IN

COMP2_R_IN

SCART1_Lout

SCART1_Rout

2.2uF

BLM18SG121TN1D

L403

1uF

C421

C4032.2uF

C4562.2uF

C404

C4582.2uF

4.7uF

C422

Y1

GPIO78

W4

GPIO79

K17

I2C_SCKM3/I2C_DDCR_CK/GPIO77

J15

I2C_SDAM3/I2C_DDCR_DA/GPIO76

U8

SDAM2/GPIO55

T7

SCKM2/GPIO56

U7

SCKM0/GPIO58

V7

SDAM0/GPIO59

F6

I2S_IN_BCK/GPIO159

G6

I2S_IN_SD/GPIO160

AA4

I2C_SCKM1/GPIO80

Y4

I2C_SDAM1/GPIO81

J6

ET_TXD[0]/GPIO62

K6

EXT_TX_CLK/GPIO64

G7

I2S_IN_WS/GPIO158

J4

ET_COL/GPIO60

J5

ET_TXD[1]/GPIO61

H19

LCK/GPIO194

G20

LDE/GPIO195

G19

LHSYNC/GPIO196

G21

LVSYNC/GPIO197

J17

UART2_RX/GPIO69

J16

UART2_TX/GPIO70

E8

UART3_TX/GPIO52

D7

UART3_RX/GPIO53

U6

GPIO46[CTS]

V6

GPIO47[RTS]

K15

UART1_TX/GPIO48

L16

UART1_RX/GPIO49

H5

ET_TX_EN/GPIO63

K5

ET_RXD[0]/GPIO65

K4

ET_MDC/GPIO66

H6

ET_MDIO/GPIO67

L5

ET_RXD[1]/GPIO68

U17

PCMADR[0]/NF_AD[0]/GPIO130

R18

PCMADR[1]/NF_AD[1]/GPIO129

V17

PCMADR[2]/NF_AD[2]/GPIO127

R16

PCMADR[3]/NF_AD[3]/GPIO126

U16

PCMADR[4]/NF_AD[4]/GPIO104

T17

PCMADR[5]/NF_AD[5]/GPIO106

W18

PCMADR[6]/NF_AD[6]/GPIO107

U20

PCMADR[7]/NF_AD[7]/GPIO108

Y19

PCMADR[8]/GPIO113

AA19

PCMADR[9]/GPIO115

AA20

PCMADR[10]/GPIO119

W21

PCMADR[11]/GPIO117

V20

PCMADR[12]/GPIO109

Y17

PCMADR[13]/GPIO112

V18

PCMADR[14]/GPIO111

V19

PCMCD_N/GPIO135

W19

PCMCE_N/GPIO120

U18

PCMDATA[0]/GPIO131

V16

PCMDATA[1]/GPIO132

W17

PCMDATA[2]/GPIO133

Y20

PCMDATA[3]/GPIO125

R15

PCMDATA[4]/GPIO124

AA18

PCMDATA[5]/GPIO123

T15

PCMDATA[6]/GPIO122

Y21

PCMDATA[7]/GPIO121

W20

PCMIORD_N/GPIO116

V21

PCMIOWR_N/GPIO114

Y18

PCMIRQA_N/GPIO110

T16

PCMOE_N/GPIO118

R17

PCMREG_N/GPIO128

T18

PCM_RESET/GPIO134

W16

PCMWAIT_N/GPIO105

U15

PCMWE_N/GPIO198

AA9

AA7

AA6

AUVRM

LGE2131(M1A_128M)

M4

W7

Y8

W8

Y9

W9

Y7

N2

E3

E2

W6

L4

Y6

F1

G3

G1

G2

H3

H2

F3

F2

U4

T4

P2

R2

T1

R3

R1

T3

U2

V3

T2

BRAZIL

IC1202-*1

PM_SPI_SCZ1/GPIO_PM[6]/GPIO13

#POWER FOR MAIN#

<VDDC 1.05V> <Normal Power 3.3V>

+1.10V_VDDC

10uFC455

10uFC457

10uF

C465

C467 1uF

0.1uF

0.1uF

0.1uF

C478

C480

C474

C472 1uF

C482 0.1uF

<DDR3 1.5V>

+1.5V_DDR

C436

10uF

C432

0.1uF

C442

0.1uF

C4003

0.1uF

C4004

C444

0.1uF

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FIRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFACTURES SPECIFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

0.1uF

C445

0.1uF

C446

1uF

C491

0.1uF

C492

C484 0.1uF

10uF

+1.10V_VDDC

C487 0.1uF

C493

10uF

C490 0.1uF

+1.10V

BLM18PG121SN1D

L404

10uF

10V

C409

+1.10V_VDDC

C410

0.1uF

+3.3V

C431 0.1uF

L401

BLM18PG121SN1D

<STby 3.3V>

+3.3V_ST

AV_CVBS_DET

AV2_CVBS_DET

DEMOD_RESET

MODEL_OPT_0

MODEL_OPT_1

MODEL_OPT_2

/MHL_OCP_DET

SC1/COMP1_DET

MHL_OCP_EN

/AMP_RESET

MODEL_OPT_4

RF_SWITCH_CTL

MODEL_OPT_5

MODEL_OPT_6

PCM_A[0-14]

VDD33

10uFC434

L400

BLM18PG121SN1D

C407

10uF

10V

L406

BLM18PG121SN1D

C408

10uF

10V

L407

BLM18PG121SN1D

LNB_CTL

I2C_SCL

I2C_SDA

DEMOD_SDA

DEMOD_SCL

P_SCL

P_SDA

AMP_SCL

AMP_SDA

TU_SCL

TU_SDA

TUNER_I2C

COMP2_DET

AMP_MUTE

UART_TXD

UART_RXD

USB1_CTL

USB1_OCD

CI_DET

PCM_D[0-7]

PCM_D[0-7]

10uFC435

C438 0.1uF

C441 0.1uF

C440 0.1uF

C4002 SHOULD NEAR MAIN IC

AVDD_NODIE

C401

0.1uF

AVDD_DMPLL

C423

0.1uF

AVDD_AU33

C427

C424

10uF

0.1uF

10V

for SYSTEM EEPROM

DEMOD_I2C

22

22

22

22

/PCM_CD

PCM_D[0]

PCM_D[1]

PCM_D[2]

PCM_D[3]

PCM_D[4]

PCM_D[6]

PCM_D[7]

DECAP FOR SOC

(HIDDEN - UCC)

C412

0.1uF

R404

R406

R420

R421

PCM_A[0]

PCM_A[1]

PCM_A[2]

PCM_A[3]

PCM_A[4]

PCM_A[5]

PCM_A[6]

PCM_A[7]

PCM_A[8]

PCM_A[9]

PCM_A[10]

PCM_A[11]

PCM_A[12]

PCM_A[13]

PCM_A[14]

/PCM_CE

PCM_D[5]

/PCM_IORD

/PCM_IOWR

/PCM_IRQA

/PCM_OE

/PCM_REG

PCM_RST

/PCM_WAIT

/PCM_WE

R419

22 EU

R464

2.2K

<GPIO & CI>

LGE2132(M1A_256M)

Y1

GPIO78

W4

GPIO79

K17

I2C_SCKM3/I2C_DDCR_CK/GPIO77

J15

I2C_SDAM3/I2C_DDCR_DA/GPIO76

U8

SDAM2/GPIO55

T7

SCKM2/GPIO56

U7

SCKM0/GPIO58

V7

SDAM0/GPIO59

F6

I2S_IN_BCK/GPIO159

G6

I2S_IN_SD/GPIO160

AA4

I2C_SCKM1/GPIO80

Y4

I2C_SDAM1/GPIO81

J6

ET_TXD[0]/GPIO62

K6

EXT_TX_CLK/GPIO64

G7

I2S_IN_WS/GPIO158

J4

ET_COL/GPIO60

J5

ET_TXD[1]/GPIO61

H19

LCK/GPIO194

G20

LDE/GPIO195

G19

LHSYNC/GPIO196

G21

LVSYNC/GPIO197

J17

UART2_RX/GPIO69

J16

UART2_TX/GPIO70

E8

UART3_TX/GPIO52

D7

UART3_RX/GPIO53

U6

GPIO46[CTS]

V6

GPIO47[RTS]

K15

UART1_TX/GPIO48

L16

UART1_RX/GPIO49

H5

ET_TX_EN/GPIO63

K5

ET_RXD[0]/GPIO65

K4

ET_MDC/GPIO66

H6

ET_MDIO/GPIO67

L5

ET_RXD[1]/GPIO68

U17

PCMADR[0]/NF_AD[0]/GPIO130

R18

PCMADR[1]/NF_AD[1]/GPIO129

V17

PCMADR[2]/NF_AD[2]/GPIO127

R16

PCMADR[3]/NF_AD[3]/GPIO126

U16

PCMADR[4]/NF_AD[4]/GPIO104

T17

PCMADR[5]/NF_AD[5]/GPIO106

W18

PCMADR[6]/NF_AD[6]/GPIO107

U20

PCMADR[7]/NF_AD[7]/GPIO108

Y19

PCMADR[8]/GPIO113

AA19

PCMADR[9]/GPIO115

AA20

PCMADR[10]/GPIO119

W21

PCMADR[11]/GPIO117

V20

PCMADR[12]/GPIO109

Y17

PCMADR[13]/GPIO112

V18

PCMADR[14]/GPIO111

V19

PCMCD_N/GPIO135

W19

PCMCE_N/GPIO120

U18

PCMDATA[0]/GPIO131

V16

PCMDATA[1]/GPIO132

W17

PCMDATA[2]/GPIO133

Y20

PCMDATA[3]/GPIO125

R15

PCMDATA[4]/GPIO124

AA18

PCMDATA[5]/GPIO123

T15

PCMDATA[6]/GPIO122

Y21

PCMDATA[7]/GPIO121

W20

PCMIORD_N/GPIO116

V21

PCMIOWR_N/GPIO114

Y18

PCMIRQA_N/GPIO110

T16

PCMOE_N/GPIO118

R17

PCMREG_N/GPIO128

T18

PCM_RESET/GPIO134

W16

PCMWAIT_N/GPIO105

U15

PCMWE_N/GPIO198

+3.3V_ST

<SOC_RESET>

C497

10uF

10V

D400

BAW56 GEANDE

R403

100K

R474

R451

2.2K

R450

2.2K

2.2K

R452

1.8K

IC1202

NON_BRAZIL

TS0DATA[0]/GPIO82

TS0DATA[1]/GPIO83

TS0DATA[2]/GPIO84

TS0DATA[3]/GPIO85

TS0DATA[4]/GPIO86

TS0DATA[5]/GPIO87

TS0DATA[6]/GPIO88

TS0DATA[7]/GPIO89

TS0SYNC/GPIO91

TS0VALID/GPIO90

TS1CLK/GPIO103

TS1DATA[0]/GPIO93

TS1DATA[1]/GPIO94

TS1DATA[2]/GPIO95

TS1DATA[3]/GPIO96

TS1DATA[4]/GPIO97

TS1DATA[5]/GPIO98

TS1DATA[6]/GPIO99

TS1DATA[7]/GPIO100

TS1SYNC/GPIO102

TS1VALID/GPIO101

PM_SPI_SCZ1/GPIO_PM[6]/GPIO13

R408

10

C402

0.1uF

+3.3V

R453

1.8K

PM_SPI_SCK/GPIO1

PM_SPI_SCZ0/GPIO0

PM_SPI_SDI/GPIO2

PM_SPI_SDO/GPIO3

SPDIF_IN/GPIO161

SPDIF_OUT/GPIO162

DDCA_CK/UART0_RX

DDCA_DA/UART0_TX

NF_ALE/GPIO146

NF_CEZ/GPIO142

NF_CLE/GPIO141

NF_RBZ/GPIO147

NF_REZ/GPIO144

NF_WEZ/GPIO145

NF_WPZ/GPIO199

SOC_RESET

TS0CLK/GPIO92

HWRESET

IRIN/GPIO5

PWM0/GPIO71

PWM1/GPIO72

PWM2/GPIO73

PWM3/GPIO74

PWM4/GPIO75

IF_AGC

SIFM

SIFP

XOUT

I2C_SDA

I2C_SCL

P_SDA

P_SCL

UART_RXD

UART_TXD

<VCC &GND>

AA10

R4

L11

L13

M11

K13

C5

K12

L12

C6

K14

L14

B5

B6

R8

R9

L7

L8

P8

K9

R5

P11

C7

M13

R6

A7

M12

B7

M14

N11

N12

N13

N14

N15

P12

P13

P14

L9

C469

AVDD_AU33

+1.5V_DDR

AVDD_NODIE

VDD33

AVDD_NODIE

VDD33

AVDD_DMPLL

+1.10V_VDDC

+1.10V_VDDC

+1.10V_VDDC

VDD33

AVDD5V_MHL

IF_AGC_MAIN

1uF

C411

V10

CI_TS_DATA[0]

T14

CI_TS_DATA[1]

T13

CI_TS_DATA[2]

U13

CI_TS_DATA[3]

V15

CI_TS_DATA[4]

U12

CI_TS_DATA[5]

V13

CI_TS_DATA[6]

U14

CI_TS_DATA[7]

T11

T12

V12

Y14

BUF1_FE_TS_DATA[0]

Y16

BUF1_FE_TS_DATA[1]

AA15

BUF1_FE_TS_DATA[2]

Y13

BUF1_FE_TS_DATA[3]

AA16

BUF1_FE_TS_DATA[4]

W12

BUF1_FE_TS_DATA[5]

AA13

BUF1_FE_TS_DATA[6]

W14

BUF1_FE_TS_DATA[7]

W13

Y15

W15

B3

R414 33

A3

R407

A4

R405

C3

A2

R413 33

B1

RP

C2

TN

C1

TP

B2

RN

D2

D1

D8

E5

G4

G5

J18

K18

K16

L18

L17

T8

T9

U9

U11

V9

U10

T10

W2

W1

W3

V2

IM

V1

IP

AA2

XIN

Y2

R447

/SPI_CS

33

SPI_SCK

22

SCART1_MUTE

EU

SPI_SDI

SPI_SDO

5V_DET_HDMI_2

SPDIF_OUT

SOC_RESET

IR

R41522

RGB_DDC_SCL

R41622

RGB_DDC_SDA

AR400

22

AR401

22

Close to MSTAR

C451 8pF

GND_2

X-TAL_2

4

3

1

X400

24MHz

C452 8pF

1M

X-TAL_12GND_1

PCM_5V_CTL

PF_ALE

/PF_CE0

/PF_CE1

/F_RB

/PF_OE

/PF_WE

/PF_WP

X-TAL_8pF

X-TAL_8pF

CI_TS_DATA[0-7]

CI_TS_CLK

BUF1_FE_TS_DATA[0-7]

CI_TS_SYNC

CI_TS_VAL

BUF1_FE_TS_CLK

BUF1_FE_TS_SYN

BUF1_FE_TS_VAL_ERR

C462

0.1uF

C461

0.1uF

READY

C425

33pF

+3.3V

0.1uF

L410

C468

BLM18PG121SN1D

R469

10K

R471

ANALOG SIF

Close to MSTAR

DTV_IF

IF_N_MSTAR

IF_P_MSTAR

READY

C426

33pF

C451-*1

10pF

X-TAL_10pF

NON_A_DEMODE

AGC 1.25V

100 OHM SERIAL

A_DEMODE 0ohm

Close to MSTAR

100

0.047uF

25V

C452-*1

10pF

X-TAL_10pF

IC1202

LGE2132(M1A_256M)

AVDD_AU33

AVDD_DDR0_CLK

AVDD_DDR1_CLK

AVDD_DDR0_CMD

AVDD_DDR1_CMD

AVDD_DDR0_D_1

AVDD_DDR0_D_2

AVDD_DDR0_D_3

AVDD_DDR1_D_1

AVDD_DDR1_D_2

AVDD_DDR1_D_3

AVDD_DRAM_1

AVDD_DRAM_2

AVDD_DVI_USB_MPLL_1

AVDD_DVI_USB_MPLL_2

AVDD_MOD_1

AVDD_MOD_2

AVDD_NODIE

AVDD_PLL

AVDD3P3_DMPLL

AVDDL_MOD

DVDD_DDR_1

DVDD_DDR_2

DVDD_NODIE

DVDD_RX_1_1

DVDD_RX_1_2

DVDD_RX_2_1

DVDD_RX_2_2

VDDC_1

VDDC_2

VDDC_3

VDDC_4

VDDC_5

VDDC_6

VDDC_7

VDDC_8

VDDP

NON_BRAZIL

AVDD5V_MHL

AUVRM

GND_1

GND_2

GND_3

GND_4

GND_5

GND_6

GND_7

GND_8

GND_9

GND_10

GND_11

GND_12

GND_13

GND_14

GND_15

GND_16

GND_17

GND_18

GND_19

GND_20

GND_21

GND_22

GND_23

GND_24

GND_25

GND_26

GND_27

GND_28

GND_29

GND_30

GND_31

GND_32

GND_33

GND_34

GND_35

GND_36

GND_37

GND_38

GND_39

GND_40

GND_41

GND_42

GND_43

GND_44

GND_45

GND_46

GND_47

GND_48

GND_49

GND_50

GND_51

GND_52

GND_53

GND_54

GND_55

GND_56

GND_57

GND_58

GND_59

GND_60

GND_61

GND_62

GND_63

GND_64

GND_65

GND_66

GND_67

GND_68

GND_69

GND_70

GND_71

GND_72

GND_73

GND_74

GND_75

GND_76

GND_77

GND_78

GND_79

GND_80

GND_81

GND_82

GND_83

GND_84

GND_EFUSE

U3

AUVRM

A6

A13

A15

A18

B12

B14

B16

B17

B19

B20

C9

C10

C21

D9

E20

F9

F11

F13

F15

F17

F19

F21

G8

G9

G10

G11

G12

G13

G14

G15

G16

G17

G18

H7

H8

H9

H10

H11

H12

H13

H14

H15

H16

H17

H18

J7

J8

J9

J10

J11

J12

J13

J14

K8

K10

K11

L10

M5

M7

M8

M9

M10

N4

N5

N6

N7

N8

N9

N10

P4

P5

P6

P7

P9

P10

P15

P16

P17

P18

R10

R11

R12

R13

R14

K7

<LVDS & PM/SAR>

IC1202

LGE2132(M1A_256M)

RXA0RXA0+

RXA1RXA1+

RXA2-

RXA2+

RXACKRXACK+

RXA3-

RXA3+

RXA4-

RXA4+

RXB0-

RXB0+

RXB1-

RXB1+

RXB2-

RXB2+

RXBCKRXBCK+

RXB3-

RXB3+

RXB4-

RXB4+

U19

NON_BRAZIL

LVA4P/TTL_B[0]/HCONV/GPIO170

T20

LVA4M/TTL_B[1]/E_O/GPIO171

T21

LVA3P/TTL_B[2]/FB/GPIO172

T19

LVA3M/TTL_B[3]/OPT_P/GPIO173

R21

LVACKP/TTL_B[4]/MCLK/GPIO174

R20

LVACKM/TTL_B[5]/GCLK/GPIO175

R19

LVA2P/TTL_B[6]/GST/GPIO176

P20

LVA2M/TTL_B[7]/POL/GPIO177

P19

LVA1P/TTL_G[0]/EPI0+/GPIO178

N20

LVA1M/TTL_G[1]/EPI0-/GPIO179

N21

LVA0P/TTL_G[2]/EPI1+/GPIO180

N19

LVA0M/TTL_G[3]/EPI1-/GPIO181

M21

LVB4P/TTL_G[4]/EPI2+/GPIO182

M20

LVB4M/TTL_G[5]/EPI2-/GPIO183

M19

LVB3P/TTL_G[6]/EPI3+/GPIO184

L20

LVB3M/TTL_G[7]/EPI3-/GPIO185

L19