LG 55EC9300-NA, 55EC9310-NB Schematic

55EC9300

55EC9310

Internal Use Only

OLED TV

샤 시 명 : EA42D

모 델 명 : 55EC9300/55EC9310

55EC9300-NA/55EC9310-NB

주 의 : 제품을 점검하시기 전에 이 책자의 안전수칙을 잘 읽어보시고

조작하시기 바랍니다.

Printed in KoreaP/NO : MFL68260402 (1409-REV00)

차 례

차례 .............................................................................. 2

안전을 위한 주의사항 .......................................................... 3

제품규격 .......................................................................... 4

조정규격 .......................................................................... 9

분해도 .......................................................................... 16

회로도 ..............................................................................

Only for training and service purposes

- 2 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

서비스를 하고자 할 경우는 이 샤시에 요구되는 수칙 이외의 다른

노출된금속부분

1000ohm,10W

어스

AC전압계

방법으로 실시하거나 익숙하지 않은 자가 수리에 임하여서는 안된다.

안전을 위한 주의사항

※ 일반사항

1. 서비스를 할 때는 기본적인 포선에 주의를 기울이고 만일 단락회

로가 발견되면 단락회로에 의해 과열 되었거나 손상된 모든 부품

을 교환해야 한다.

2. 서비스를 한 후는 절연충, 절연지, 쉴드(SHIELD) R-C 복합소

자로 된 모든 보호용 소자들이 확실히 조립되었는지를 확인한다.

3. 수상기를 장시간 시청하지 않을 때는 전원코드를 전원 콘센트에

서 뽑는다.

4. 본 수상기 동작시 25.5KV 이상의 고압이 걸리므로 백커버를 연 상

태에서 동작 시키면 수상기로부터 감전의 위험이 있다.

수리를 할 때는 고압에 대한 조의사항과 충분한 예비지식이 있는

사람이 취급하여야 한다.

5. 서비스를 완료한 후는 쇼크의 위험으로 부터 사용자를 보호하기

위하여 다음의 누설 전류를 검사하여야 한다.

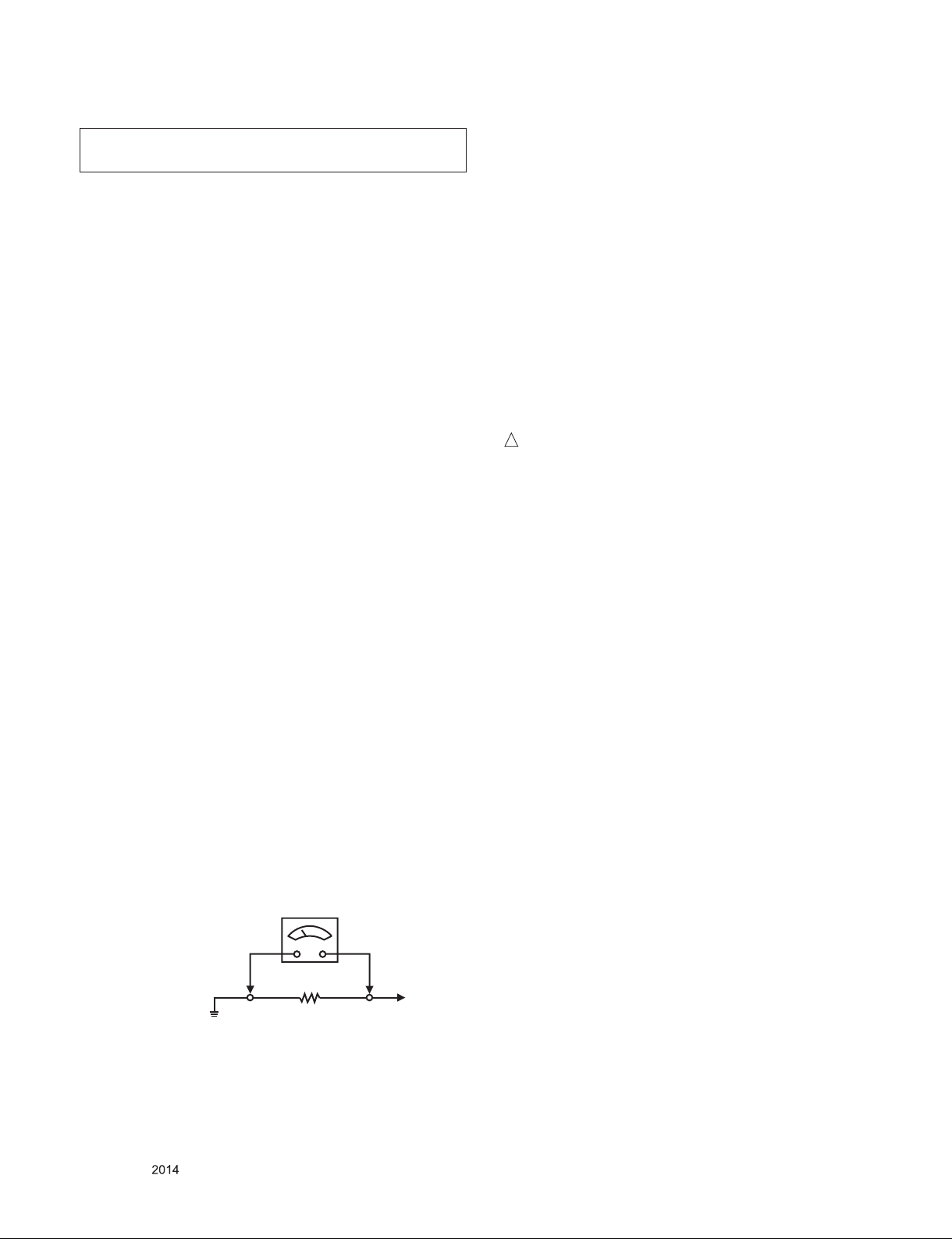

※ 누설 전류(COLD CHECK)

1. AC전원을 뽑고 플러그 양단을 선으로 연결시킨다.

2. 전원 스위치를 켠다.

3. 절연 시험기의 한쪽 단자를 플러그에 연결하고 다른 한쪽의 리드

를 노출된 금속 즉, 안테나, 스크류, 가변 조정기의 축 등에 접촉

시켜서 측정한다. 노출된 금속부분이 샤시에 접속된 경우 및 노출

된 금속부분이 샤시에 접속되어 있지 않을 경우의 저항치가 무한

대(∞) 이어야 한다.

안전을 위한 주의사항

※ 서비스시의 주의사항

1. 부품 또는 회로기판을 삽입할 때는 납땜하기 전에 리드선을 단자

에 고정 시켜야 한다.

2. 고전력 저항을 삽입할 때는 (금속산화피막 저항 또는 금속피막 저

항) 기판으로 부터 약 10mm 정도 띄어서 삽입한다.

3. 고압 또는 고온도를 갖는 부품에는 리드선을 멀리해야 한다.

4. 본 샤시는 절연 샤시(COLD CHASSIS)나 서비스의 안전을 위하

여 절연 트랜스를 사용하는 것이 좋다. 전원부를 수리할 경우는 반

드시 절연트랜스를 사용할 것.

5. 수상기가 동작하는 동안 선을 연결시키거나 제거하지 말 것.

!

6. 표시의 부품은 제품의 안정성을 유지하기 위해 중요한 부품입

니다.

따라서 교환시 반드시 지정 부품을 사용해 주십시요.

※ 누설 전류(HOT CHECK)

1. 전원 플러그를 전원에 직접 연결한다.

(이때 시험을 하는 동안 절연트랜스는 사용하지 않는다.)

2. 1.0KΩ, 10W 저항의 한쪽을 수상기의 노출된 금속부에 연결하

고 다른 한쪽은 접지(수도 파이프 등 접지가 양호한 장소) 시킨

다.(그림참조)

3. AC 전압계(1000Ω VOLT 또는 그 이상 민감한 것)를 사용하여 저

항 양단간의 전압을 측정한다.

4. 수상기의 각 노출된 부위의 전압을 각각 측정한다.

5. 전원 플러그를 바꾸어 꽂고 (극성반대) 상기 측정을 반복한다.

6. 어떤 지점에서도 그 전위는 0.75V를 넘지 않아야 하고 누설전류는

0.75mA를 초과해서는 안된다.

• „

<그림> 누설전류 측정회로도(HOT CHECK)

Only for training and service purposes

- 3 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

제품규격

1. 적용 범위

이 사양 시트는 EA42D 샤시가 탑재된 OLED TV에

적용됩니다.

2. 테스트 조건

각 부품은 별도의 지침이 없는 경우 아래의 환경에서 테스트

됩니다.

1) 온도 : 25 ºC ± 5 ºC(77 ± 9 ºF), CST : 40 ± 5 ºC

2) 상대습도 : 65 % ± 10 %

3) 전압

: 입력전압 : AC 220 V~240V, 60 Hz)

4) 각 부품의 사양과 성능에는 BOM에 따른 부품 번호별

그림과 사양이 함께 표시됩니다.

5) 수신기는 조정되기 전에 약 20분 동안 작동되어야 합니다.

3. 테스트 방법

1) 성능 : LGE TV 테스트 방법 준수

2) 기타 필수 사양

- 안전: UL, CSA, CE, IEC 사양

- EMC: FCC, ICES, CE, IEC 사양

- Wireless : Wireless HD 사양 (옵션)

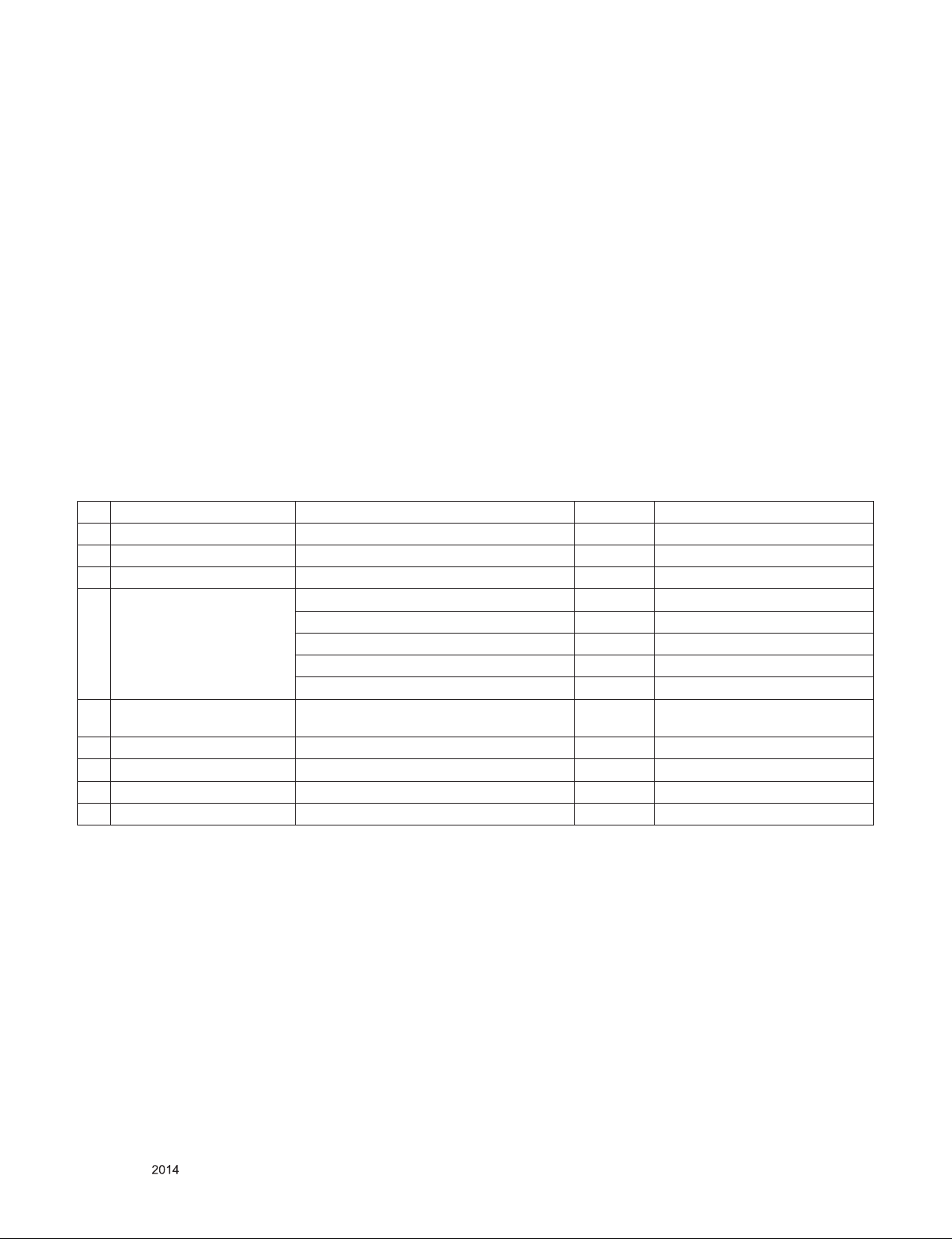

4. 일반 규격

No 항 목 사 양 비 고

1 지역 1)대한민국

2 방송 시스템 1) ATSC / NTSC-M

3 수신 시스템 1) ATSC / NTSC-M

4 가용 채널 1) VHF : 02~13

2) UHF : 14~69

3) DTV : 02-69

4) CATV : 01~135

5) CADTV : 01~135

5 입력 전압 AC 100 ~ 240V 60Hz AC 220~240V, 60Hz on the

label (Korea)

6 화면 크기 55 inch Wide(1920 × 1080) 55EC9300-NA

7 화면 비율 16:9

8 튜닝 시스템 FS

9 OLED 모듈

TBD

LGD 55EC9300-NA

Only for training and service purposes

- 4 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

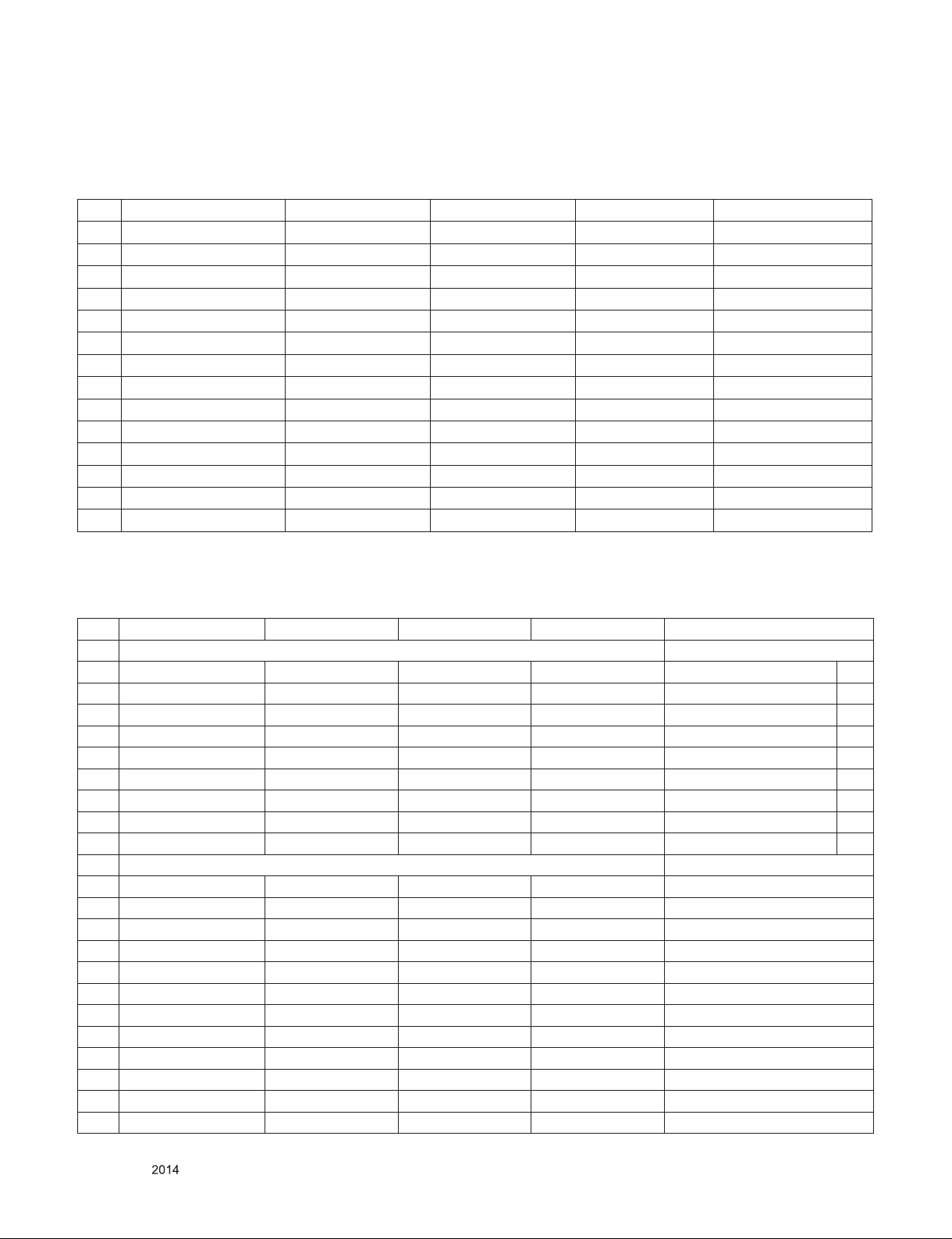

5. 외부 입력 방식

5.1. 2D 모드

5.1.1. Component 입력(Y, CB/PB, CR/PR)

No. Resolution H-freq(kHz) V-freq.(kHz) Pixel clock Proposed

1. 720*480 15.73 60.00 13.5135 SDTV ,DVD 480I

2. 720*480 15.73 59.94 13.50 SDTV ,DVD 480I

3. 720*480 31.50 60.00 27.027 SDTV 480P

4. 720*480 31.47 59.94 27.00 SDTV 480P

5. 1280*720 45.00 60.00 74.25 HDTV 720P

6. 1280*720 44.96 59.94 74.176 HDTV 720P

7. 1920*1080 33.75 60.00 74.25 HDTV 1080I

8. 1920*1080 33.72 59.94 74.176 HDTV 1080I

9. 1920*1080 67.50 60.00 148.50 HDTV 1080P

10. 1920*1080 67.432 59.94 148.352 HDTV 1080P

11. 1920*1080 27.00 24.00 74.25 HDTV 1080P

12. 1920*1080 26.97 23.94 74.176 HDTV 1080P

13. 1920*1080 33.75 30.00 74.25 HDTV 1080P

14. 1920*1080 33.71 29.97 74.176 HDTV 1080P

5.1.2. HDMI 입력(PC/DTV)

No. Resolution H-freq(kHz) V-freq.(kHz) Pixel clock(MHz) Proposed

HDMI-PC DDC

1 640*350 31.468 70.09 25.17 EGA Х

2 720*400 31.469 70.08 28.32 DOS O

3 640*480 31.469 59.94 25.17 VESA(VGA) O

4 800*600 37.879 60.31 40.00 VESA(SVGA) O

5 1024*768 48.363 60.00 65.00 VESA(XGA) O

6 1152*864 54.348 60.053 80.00 VESA O

7 1280*1024 63.981 60.020 108.00 VESA (SXGA) O

8 1360*768 47.712 60.015 85.50 VESA (WXGA) O

9 1920*1080 67.5 60 148.5

HDMI-DTV

1 720*480 31.47 60 27.027 SDTV 480P

2 720*480 31.47 59.94 27.00 SDTV 480P

3 1280*720 45.00 60.00 74.25 HDTV 720P

4 1280*720 44.96 59.94 74.176 HDTV 720P

5 1920*1080 33.75 60.00 74.25 HDTV 1080I

6 1920*1080 33.72 59.94 74.176 HDTV 1080I

7 1920*1080 67.500 60 148.50 HDTV 1080P

8 1920*1080 67.432 59.939 148.352 HDTV 1080P

9 1920*1080 27.000 24.000 74.25 HDTV 1080P

10 1920*1080 26.97 23.976 74.176 HDTV 1080P

11 1920*1080 33.75 30.000 74.25 HDTV 1080P

12 1920*1080 33.71 29.97 74.176 HDTV 1080P

WUXGA(Reduced Blanking)

O

Only for training and service purposes

- 5 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

5.2. 3D 모드

5.2.1. RF 입력

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed Remark

1 1920*1080 45.00 60 74.25 HDTV 1080I Side by Side, Top & Bottom

2 1280*720 45.00 60 74.25 HDTV 720P Side by Side, Top & Bottom

5.2.2. HDMI 입력

5.2.2.1. HDMI 1.3 - DTV (3D supported mode manually)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed Remark

1 1280*720p 45.00 60.00 74.25 Side by Side , Top & Bottom,

2 1920*1080i 33.75 60.00 74.25 Side by Side, Top & Bottom

3 1920*1080p 67.50 60.00 148.50 Side by Side , Top & Bottom

4 1920*1080p 27.00 24.000 74.25 Side by Side , Top & Bottom

5 1920*1080p 33.75 30.000 74.25 Side by Side, Top & Bottom

Single Frame Sequential

Checkerboard, Single Frame Sequential

Row Interleaving, Column Interleaving

Checkerboard

Checkerboard

5.2.2.2. HDMI 1.3 - DTV (3D supported mode manually)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed Remark

1 1280*720p 89.91 / 90.00 59.94 / 60.00 148.35 / 148.50 Mandatory Frame Packing,

2 1280*720p 44.96 / 45.00 59.94 / 60.00 74.18 / 74.25 Mandatory Top & Bottom

3 1920*1080i 33.72 / 33.75 59.94 / 60.00 74.18 / 74.25 Mandatory Side by Side (Half)

4 1920*1080p 43.94 / 54.00 23.97 / 24.00 148.35 / 148.50 Mandatory Frame Packing,

5 1920*1080p 26.97 / 27.00 23.97 / 24.00 74.18 / 74.25 Mandatory Top & Bottom

6 1280*720p 44.96 / 45.00 59.94 / 60.00 74.18 / 74.25 Primary Side by Side (Half)

7 1920*1080i 67.432 / 67.50 59.94 / 60.00 148.35 / 148.50 Primary Frame Packing

8 1920*1080p 67.43 / 67.50 59.94 / 60.00 148.35 / 148.50 Primary Top & Bottom

9 1920*1080p 26.97 / 27.00 23.97 / 24.00 74.18 / 74.25 Primary Side by Side (Half)

10 1920*1080p 67.432 / 67.50 29.976 / 30.00 148.35 / 148.50 Primary Frame Packing,

11 1920*1080p 33.716 / 33.75 29.976 / 30.00 74.18 / 74.25 Primary Top & Bottom

12 1920*1080i 33.72 / 33.75 59.94 / 60.00 74.18 / 74.25 Secondary Top & Bottom

13 1920*1080p 67.43 / 67.50 59.94 / 60.00 148.35 / 148.50 Secondary Side by Side (Half)

14 1920*1080p 33.716 / 33.75 29.976 / 30.00 74.18 / 74.25 Secondary Side by Side (Half)

15 720*480p 62.938 / 63.00 59.94 / 60.00 54.00 / 54.054 Secondary (16:9) Frame Packing,

16 720*480p 31.469 / 31.50 59.94 / 60.00 27.00 / 27.027 Secondary (16:9) Top & Bottom

17 720*480p 31.469 / 31.50 59.94 / 60.00 27.00 / 27.027 Secondary (16:9) Side by Side (Half)

Only for training and service purposes

- 6 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed Remark

18 720*480p 62.938 / 63.00 59.94 / 60.00 54.00 / 54.054 Secondary (4:3) Frame Packing,

19 720*480p 31.469 / 31.50 59.94 / 60.00 27.00 / 27.027 Secondary (4:3) Top & Bottom

20 720*480p 31.469 / 31.50 59.94 / 60.00 27.00 / 27.027 Secondary (4:3) Side by Side (Half)

21 640*480p 62.938 / 63.00 59.94 / 60.00 50.35 / 50.40 Secondary Frame Packing,

22 640*480p 31.469 / 31.50 59.94 / 60.00 25.175 / 25.20 Secondary Top & Bottom

23 640*480p 31.469 / 31.50 59.94 / 60.00 25.175 / 25.20 Secondary Side by Side (Half)

24 1280*720p 89.91 / 90.00 59.94 / 60.00 148.35 / 148.50 Line Alternative

25 1280*720p 44.96 / 45.00 59.94 / 60.00 148.35 / 148.50 Side by Side (Full)

26 1920*1080i 67.432 / 67.50 59.94 / 60.00 148.35 / 148.50 Field Alternative

27 1920*1080i 33.72 / 33.75 59.94 / 60.00 148.35 / 148.50 Side by Side (Full)

28 1920*1080p 43.94 / 54.00 23.97 / 24.000 148.35 / 148.50 Line Alternative

29 1920*1080p 26.97 / 27.00 23.97 / 24.000 148.35 / 148.50 Side by Side (Full)

30 1920*1080p 67.432 / 67.50 29.976 / 30.00 148.35 / 148.50 Line Alternative

31 1920*1080p 33.716 / 33.75 29.976 / 30.00 148.35 / 148.50 Side by Side (Full)

32 720*480p 62.938 / 63.00 59.94 / 60.00 54.00 / 54.054 16:9 Line Alternative

33 720*480p 31.469 / 31.50 59.94 / 60.00 54.00 / 54.054 16:9 Side by Side (Full)

34 720*480p 62.938 / 63.00 59.94 / 60.00 54.00 / 54.054 4:3 Line Alternative

35 720*480p 31.469 / 31.50 59.94 / 60.00 54.00 / 54.054 4:3 Side by Side (Full)

36 640*480p 62.938 / 63.00 59.94 / 60.00 50.35 / 50.40 Line Alternative

37 640*480p 31.469 / 31.50 59.94 / 60.00 50.35 / 50.40 Side by Side (Full)

5.2.3. HDMI-PC 입력 (3D supported mode manually)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed Remark

1 1024*768 48.363 60.004 65.000 Side by Side, Top & Bottom

2 1360*768 47.712 60.015 85.500 Side by Side, Top & Bottom

3 1920*1080 67.50 60.00 148.50 Side by Side, Top & Bottom

Checkerboard, Single Frame Sequential

Row Interleaving, Column Interleaving

5.2.4. USB 입력

5.2.4.1. USB 입력(3D supported mode automatically)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed Remark

1 1920*1080 33.75 30.000 74.25 HDTV 1080p Side by Side, Top & Bottom,

5.2.4.2. USB 입력(3D supported mode manually)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed Remark

1 1920*1080 33.75 30.000 74.25 HDTV 1080p Side by Side, Top & Bottom

Checkerboard, MPO (Photo)

Checkerboard, Single Frame Sequential,

Row Interleaving, Column Interleaving

(Photo : Side by Side, Top & Bottom)

Only for training and service purposes

- 7 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

5.2.5. DLNA 입력

R

L

R

L

5.2.5.1. DLNA 입력(3D supported mode automatically)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed Remark

1 1920*1080 33.75 30.000 74.25 HDTV 1080p Side by Side, Top & Bottom,

Checkerboard, MPO (Photo)

5.2.5.2. DLNA 입력(3D supported mode manually)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed Remark

1 1920*1080 33.75 30.000 74.25 HDTV 1080p Side by Side, Top & Bottom

Checkerboard, Single Frame Sequential,

Row Interleaving, Column Interleaving

(Photo : Side by Side, Top & Bottom)

5.2.6. Component 입력

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed Remark

1 1280*720 44.96 59.94 74.176 HDTV 720P Side by Side, Top & Bottom

2 1920*1080 33.75 60.00 74.25 HDTV 1080I Side by Side, Top & Bottom

3 1920*1080 33.72 59.94 74.176 HDTV 1080I Side by Side, Top & Bottom

4 1920*1080 67.500 60 148.50 HDTV 1080P Side by Side, Top & Bottom

5 1920*1080 67.432 59.94 148.352 HDTV 1080P Side by Side, Top & Bottom

6 1920*1080 27.000 24.000 74.25 HDTV 1080P Side by Side, Top & Bottom

7 1920*1080 26.97 23.976 74.176 HDTV 1080P Side by Side, Top & Bottom

8 1920*1080 33.75 30.000 74.25 HDTV 1080P Side by Side, Top & Bottom

9 1920*1080 33.71 29.97 74.176 HDTV 1080P Side by Side, Top & Bottom

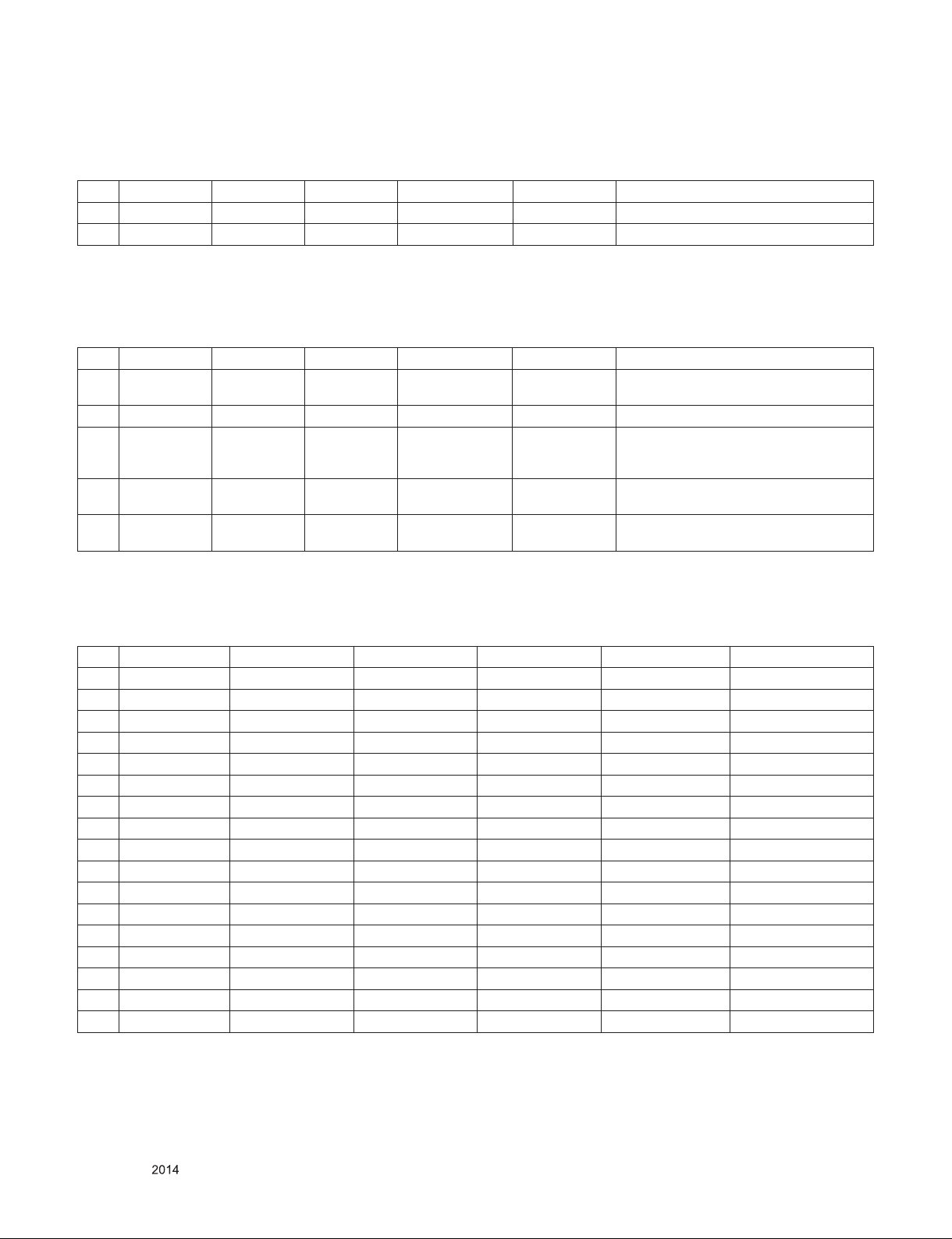

※ Remark: 3D Input mode

No Side by Side Top & Bottom Checkerboard Single Frame

1

Sequential

- 8 -

Only for training and service purposes

Frame Packing Line Interleav-

ing

Column Inter-

leaving

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

조정규격

1. 적용 범위

본 사양 시트는 TV 공장에서 제작된 EA42D 샤시가 탑재된

OLED TV 전 모델에 적용됩니다

2. 사양

(1) 본 샤시는 절연의 비충전형 샤시이므로, 절연형 변압기를

사용하지 않아도 된다.

그러나 절연형 변압기를 사용하면 테스트 기구를 보호하는

데 도움이 됩니다.

(2) 조정 작업은 정확한 순서대로 수행해야 합니다.

(3) 조정은 특별한 지침이 없는 한, 25 ºC ±5 ºC 의 온도와

65 ± 10 %의 상대 습도 환경에서 수행해야 합니다.

(4) 수신기 입력 전압은 100~240V, 50/60Hz를 유지해야

합니다.

(5) 수신기는 모듈을 15℃ 이상 환경에 둔 경우 조정 작업을

수행하기 약 5분 전에 가동해야 합니다. 모듈을 0℃ 온도

환경에 둔 경우 2시간 정도 15 ℃ 이상의 환경에 두어야

합니다. 모듈을 -20 ℃ 이하의 환경에 둔 경우 3시간 정도

15 ℃ 이상의 환경에 두어야 합니다.

※ 주의

정지 화면이 20분 이상 표시되면 (특히 W/B 스케일이

강력하고 디지털 패턴이 13ch이며 Cross Hat 패턴이 09ch인

경우) 블랙레벨 영역에 잔상이 남아 있을 수 있습니다.

3. 조정 항목

3.1. 메인 PCBA 조정

(1) ADC 조정: 컴포넌트

(2) EDID 다운로드: HDMI

4. 메인 PCBA 조정

4.1. ADC 보정

- MAIN SOC (LGExxxx)가 IC 메이커에서 보정되기 때문에

ADC 보정은 필요하지 않습니다.

-수동으로 조정해야 할 경우 부록을 참조하십시오.

4.2. MAC Address, ESN 키 및 Widevine

키, DTCP 키 다운로드

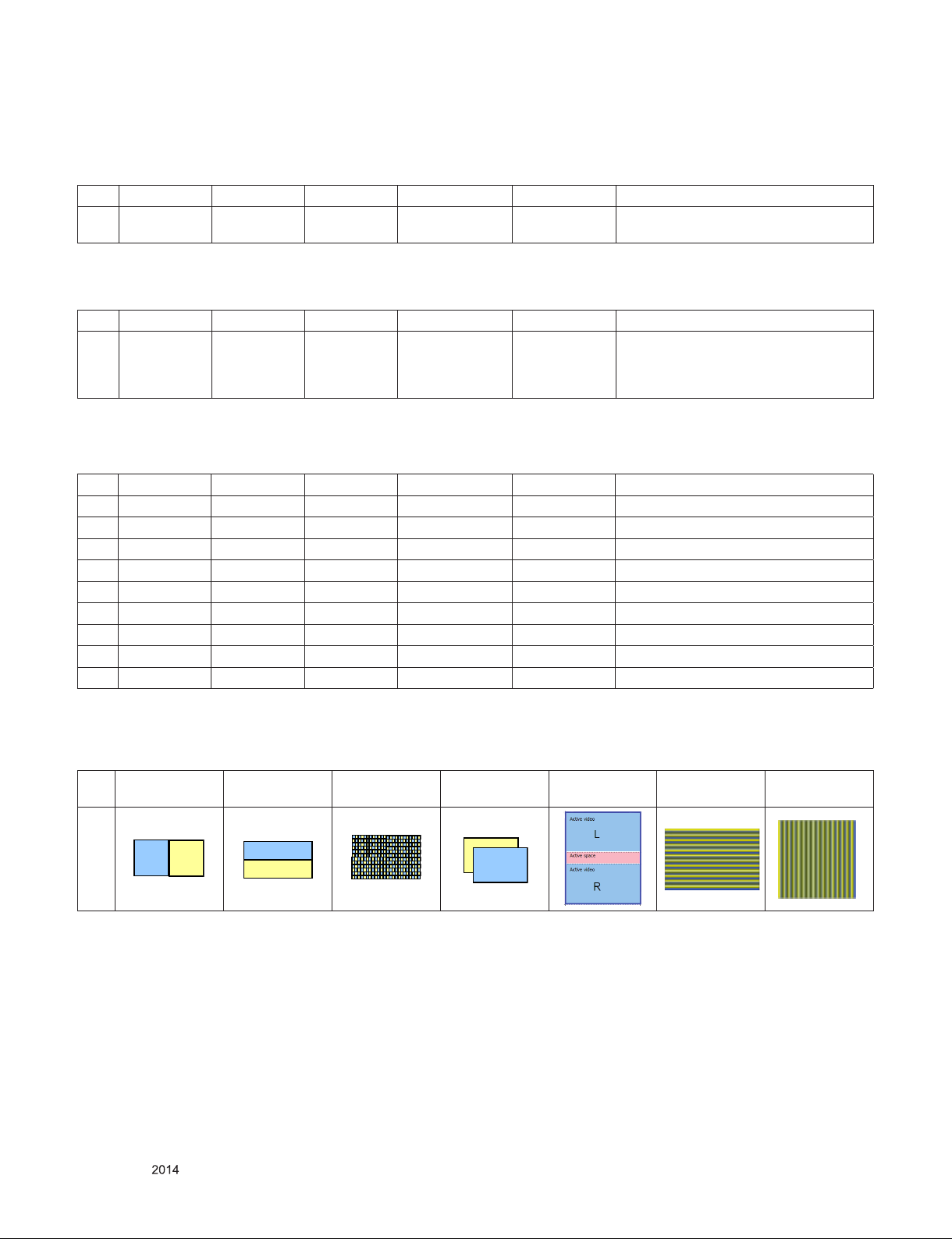

4.2.1. 장비 및 조건

1) 재생파일 : keydownload.exe

4.2.2. 통신 단자 연결

1) 키 작성 : Com 1, 2, 3, 4 및 115200(Baudrate)

2) 바코드 : Com 1, 2, 3, 4 및 9600(Baudrate)

4.2.3. 다운로드 과정

1) 다운로드 항목을 선택합니다.

2) 모드 확인: 온라인만 해당

3) 테스트 과정 확인

- 미국, 캐나다 모델: 검색->MAC_WRITE->WIDEVINE_WRITE

- 대한민국, 멕시코 모델: 검색 -> MAC_WRITE ->

WIDEVINE_WRITE

4) 실행: 시작

5) 결과 확인: 준비, 테스트, OK 또는 NG

4.2.4. 통신 단자 연결

1) 연결: PCBA Jig->RS-232C 단자 == PC->RS-232C 단자

● 위의 조정 항목은 필요한 경우 최종 조립에서 수행할 수도

있습니다. 보드 레벨 및 최종 조립 조정 항목은 In-Start

메뉴에서 확인할 수 있습니다(1. 조정 확인).

3.2. 총조 조정

(1) 화이트 밸런스 조정

(2) RS-232C 기능 검사

(3) 목적지별 출고 시 옵션 설정

(4) Ship-out 모드 설정(In-Stop)

(5) GND 및 HI-POT 테스트

3.3. 부록

(1) 도구 옵션 메뉴, USB 다운로드(소프트웨어 업데이트,

옵션 및 서비스 전용)

(2) ADC 보정과 화이트 밸런스 수동조정

(3) Ship-out 모드조건, 사전 설정 CH 정보

4.2.5. 다운로드

(1) 대한민국모델

(13Y LCD TV + MAC + Widevine + ESN Key +

HDCP1.4 and HDCP2.0)

4.2.6. 검사

- IN START 메뉴에서 다음 키를 선택합니다

Only for training and service purposes

- 9 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

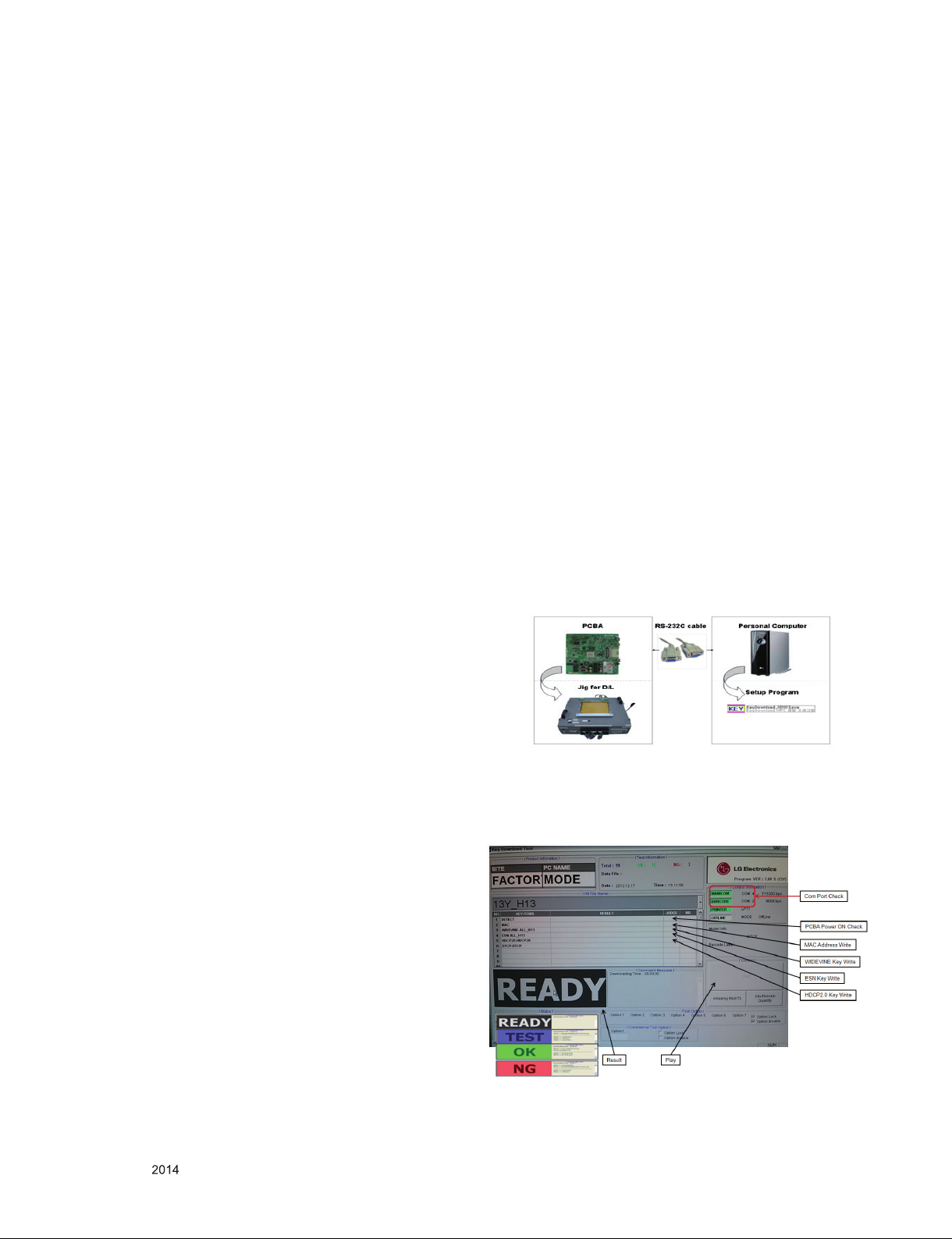

4.3. LAN 단자 검사(핑테스트)

4.3.1. 장비 설정

1) LAN 단자 테스트 프로그램을 실행합니다.

2) 테스트 프로그램 검사를 위해 설정된 IP를 입력합니다.

- IP 번호: 12.12.2.2

4.3.2. LAN 단자 검사(핑 테스트)

1) LAN 단자 테스트 프로그램을 실행합니다.

2) 각 LAN Port 잭을 연결합니다.

3) 테스트 버튼(F9)을 실행하고 OK 메시지를 확인합니다.

4) LAN 케이블을 제거합니다.

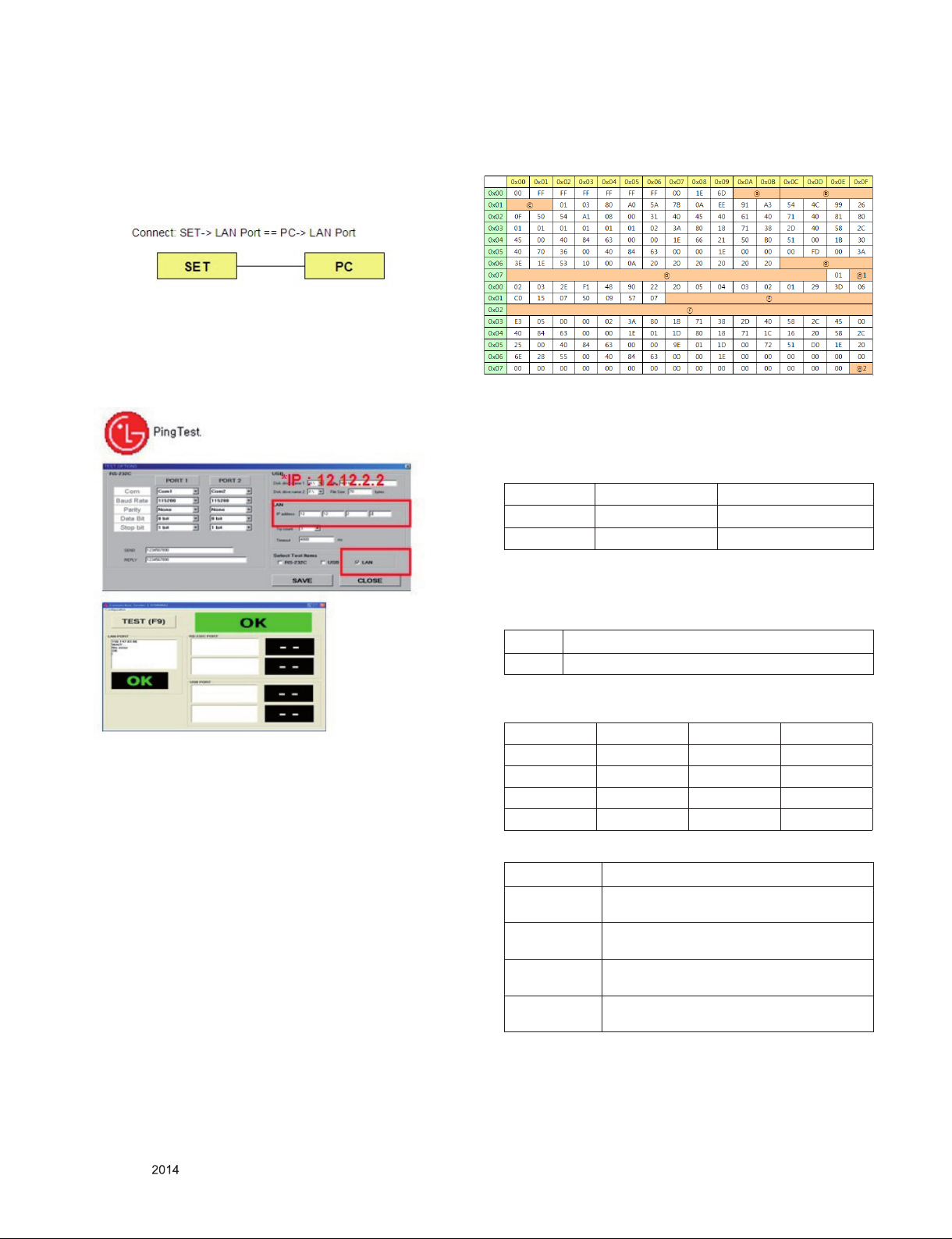

4.4.4. EDID 데이터

4.4.4.1. 3D_10bit_DTS(KR) _ xvYCC : off

▪참조

- HDMI1 ~ HDMI4

- 아래 EDID 데이터는 소프트웨어 또는 입력모드에 따라

다를 수 있습니다.

ⓐ 제품 ID

HEX EDID 표 DDC 기능

0001 0100 아날로그

0001 0100 디지털

ⓑ 시리얼 번호: 생산 라인에서 제어

ⓒ 월, 년도: 생산 라인에서 제어: ex) 월 : '01'->'01'

년 :'2014'->'18'

ⓓ 모델 이름(Hex): LGTV

Chassis MODEL NAME(HEX)

EA42D 00 00 00 FC 00 4C 47 20 54 56 0A 20 20 20 20 20 20 20

4.4. EDID 다운로드

4.4.1. 개요

- VESA 규정입니다. PC 또는 MNT는 사용자 입력을

요구하지 않고 정보 공유를 통해최적의 해상도를

표시합니다. 결과적으로 "플러그 앤 플레이"가 가능합니다.

4.4.2. 장비

(1) EDID 데이터가 포함되어 있으므로 EDID 다운로드 JIG,

HDMI 케이블 및 D-서브 케이블은 필요하지 않습니다.

(2) 리모컨을 사용하여 조정합니다.

4.4.3. 다운로드 방법

(1) 조정 리모컨에서 ADJ 키를 누릅니다.

(2) EDID D/L 메뉴를 선택합니다.

(3) Enter 키를 눌러 EDID 다운로드를 시작합니다.

(4) 다운로드가 성공적으로 수행되면 OK가 표시되고

다운로드가 실패하면 NG가 표시됩니다.

(5) 다운로드가 실패하면 다시 시도하십시오.

※주의 : EDID 다운로드 시 RGB/HDMI 케이블을 제거해야

합니다.

ⓔ Checksum(LG TV) : 총 EDID 데이터에 의해 변경될 수

있음

ⓔ1 ⓔ2 ⓔ3

HDMI1 E7 3A X

HDMI2 E7 2A X

HDMI3 E7 1A X

HDMI4 E7 0A X

ⓕ 공급업체 별(HDMI)

INPUT MODEL NAME(HEX)

HDMI1 78 03 0C 00 10 00 B8 2D 20 C0 0E 01 4F

00 FE 08 10 06 10 18 10 28 10 38 10

HDMI2 78 03 0C 00 20 00 B8 2D 20 C0 0E 01 4F

00 FE 08 10 06 10 18 10 28 10 38 10

HDMI3 78 03 0C 00 30 00 B8 2D 20 C0 0E 01 4F

00 FE 08 10 06 10 18 10 28 10 38 10

HDMI4 78 03 0C 00 30 00 B8 2D 20 C0 0E 01 4F

00 FE 08 10 06 10 18 10 28 10 38 10

Only for training and service purposes

- 10 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

5.1. 화이트 밸런스 조정

5.1.1. 개요

5.1.1.1. W/B 조정 목적 및 작동 방법

(1) 목적 : 각 패널의 W/B 편차 감소

(2) 작동 방법 : OSD의 R/G/B Gain 값이 192가 되면 패널이

최대 동적 범위에 있음을 의미합니다. 최대

동적 범위 및 데이터의 포화를 방지하려면

R/G/B 중 하나를 192로 고정하고 다른 두

값을 낮춰서 원하는 값을 찾아냅니다.

(3) 조정 조건 : 일반 온도

▪ 주변 온도: 25 ℃ ±5 ℃

▪ 워밍업 시간: 약 5분

▪ 주변 습도: 20 % ~ 80 %

▪ 화이트 밸런스 조정 전에 전원을 끄지 말고 켠 상태를

유지하십시오.

5.1.1.2. 조정 조건 및 주의 사항

(1) 주변의 조명 상태는 10lux보다 낮아야 합니다. 조정

영역을 어두운 주변과 구분하십시오.

(2) 프로브 위치 : 색상 분석기(CA-210) 프로브는 모듈

표면에서 10cm 이내에 있고 표면과 수직(80º ~100º)을

이루어야 합니다.

(3) 에이징 시간

- 에이징 시작 후 5분 동안 전원 켜짐 상태를 유지하십시오.

- LCD의 경우 신호 없음 또는 전체 화이트 패턴을 사용하여

백라이트가 켜져 있는지 확인해야 합니다.

5.1.2. 장비

(1) 색상 분석기: CA-210(NCG: CH 9 / WCG: CH12 /

LED: CH14 / OLED : CH : 17)

(2) 조정 컴퓨터(자동 조정 중에 RS-232C 프로토콜 필요)

(3) 조정 리모컨

(4) 비디오 신호 생성기 MSPG-925F 720p/204 회색

(모델: 217, 패턴: 49)

※ 색상 분석기 매트릭스를 보정할 때에는 CS-1000을

사용해야 합니다.

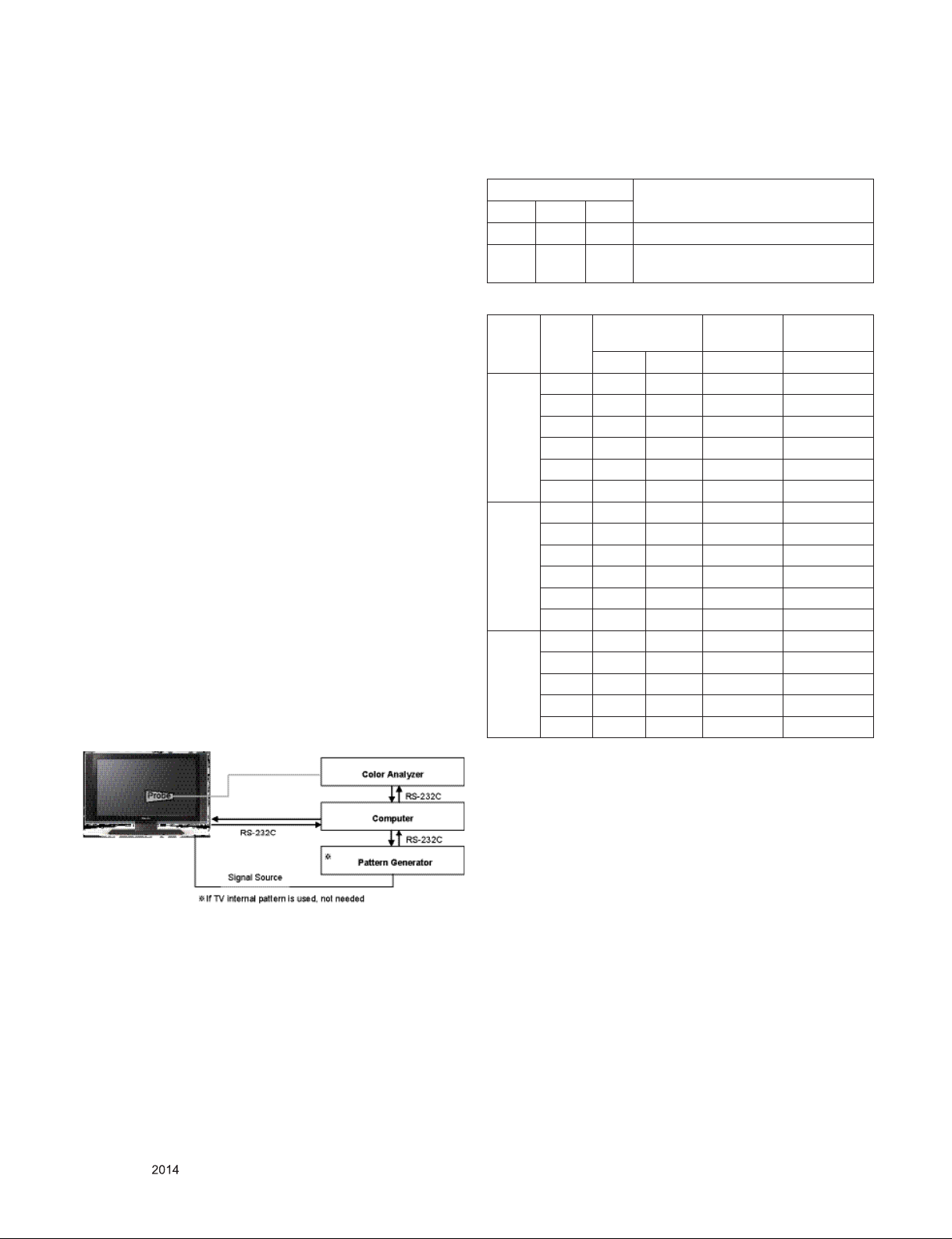

5.1.3. 장비 연결

5.1.4. 조정 명령(프로토콜)

(1) 자동 조정 중에 사용되는 RS-232C 명령

ㅉRS-232C 명령

CMD DATA ID

Wb 00 00 화이트 밸런스 조정 시작

Wb 00 ff 화이트 밸런스 조정 종료

(내부 패턴이 사라짐)

(2) Adjustment Map

Adj.

item

Cool R Gain j g 00 C0

G Gain j h 00 C0

B Gain j i 00 C0

R Cut

G Cut

B Cut

Medium R Gain j a 00 C0

G Gain j b 00 C0

B Gain j c 00 C0

R Cut

G Cut

B Cut

Warm R Gain j d 00 C0

G Gain j e 00 C0

B Gain j f 00 C0

R Cut

G Cut

Command

(lower case ASCII)

CMD1 CMD2 MIN MAX

설 명

Data Range

(Hex.)

Default

(Decimal)

Only for training and service purposes

- 11 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

5.1.5. 조정 방법

5.1.5.1. 자동 WB 보정

(1) P-ONLY 키(또는 POWER ON 키)를 사용하여 ADJ

모드에서 TV를 설정합니다.

(2) 화면 중앙에 광학 프로브를 배치합니다.

- 조정 전 제로 보정 프로브 조건을 확인하는 데 필요합니다.

(3) RS-232C 케이블을 연결합니다.

(4) ADJ 프로그램에서 모드를 선택하고 조정을 시작합니다.

(5) WB 조정이 OK 메시지와 함께 완료되면 사전 설정 모드 (

시원한 느낌, 표준, 따뜻한 느낌)의 조정 상태를 확인합니다.

(6) 프로브와 RS-232C 케이블을 분리합니다.

※ W/B 조정은 시작 명령인 "wb 00 00" 으로 시작하고 종료

명령인 "wb 00 ff" 및 조정 오프셋으로 종료해야 합니다

(필요한 경우).

5.1.6. 참조(화이트 밸런스 조정 좌표 및 색상 온도)

▪ 휘도: 204 회색, 80IRE

▪ CS-1000(26인치 이상)을 사용하는 표준 색상 좌표 및 온도

5.1.7. 참조(화이트 밸런스 조정 좌표 및 색상 온도)

▪ 휘도: 204 회색, 80IRE

▪ CS-1000(26인치 이상)을 사용하는 표준 색상 좌표 및 온도

Mode

Cool 0.277 0.278 11,000K -0.0030

Medium 0.285 0.293 9300K 0.0000

Warm 0.313 0.329 6500K +0.0030

Coordinate

X Y

Temp △uv

5.1.5.2. OLED 화이트 밸런스 테이블

5.1.5.2.1. Cool 모드

(1) 목적 : 휘도향상을 이끌어내기 위해 특별하게 B-gain을

Fix하고 조정해야합니다. 모듈 색온도의 편차를

줄이기 위해 색온도를 조정하세요.

(2) 원칙 : 색순도 없이 화이트 밸런스를 조정하기위해, B

gain을 192 이상으로 조정하고(R gain 또는 G

gain이 255이상이면 G gain은 192이하로

조정할수 있다.) 나머지것들은(R/B Gain)은

변경하세요.

(3) 조정 모드 : 모드 - Cool

5.1.5.2.2. Medium 모드

(1) 목적 : 모듈 색온도의 편차를 줄이기 위해 색온도를

조정하세요.

(2) 원칙 : 색순도 없이 화이트 밸런스를 조정하기위해, 192

(지정된 값)에 B gain을 고정시켜고 나머지 것들은

감소키세요.

(3) 조정 모드 : 모드 - Medium

5.1.5.2.3. Warm 모드

(1) 목적 : 모듈 색온도의 편차를 줄이기 위해 색온도를

조정하세요.

(2) 원칙 : 색순도 없이 화이트 밸런스를 조정하기위해, 192

(지정된 값)에 W gain을 고정시켜고 나머지 것들은

감소키세요.

(3) 조정 모드 : 모드 - Warm

▪ CA-210(CH 17)을 사용하는 표준 색상 좌표 및 온도

Mode

Cool 0.277±0.002 0.278±0.002 11000K -0.0030

Medium 0.285±0.002 0.293±0.002 9300K 0.0000

Warm 0.313±0.002 0.329±0.002 6500K +0.0030

Coordinate

X Y

Temp △uv

5.2. 매직 모션 리모컨 체크

5.2.1. 테스트 장비

▪ RF-확인용 리모컨, IR-KEY-CODE 리모컨

▪ 테스트 전에 AA 배터리를 확인합니다. 검사자가 모든

배터리를 교체하는 것을 권장합니다.

5.2.2. 테스트

(1) RCU에서 시작 키 (Wheel 키)를 눌러 TV와 페어링합니다.

(2) RCU의 Wheel 키를 눌러 화면에서 커서를 확인합니다.

(3) RCU의 Back+ Home 키를 눌러 TV와의 페어링을

중지합니다

5.3. 튜너 서브 디모드 확인(한국 모델)

(1) Power Only 모드에서 조정 리모컨의 "PIP" 키를 누르고

서브 디모드의 DTV 영상을 확인합니다. (M14 디모드)

"PIP" 키를 다시 누르거나 본체를 끄고 켜면 디모드가

메인 디모드로 변경됩니다(LGDT3306). "PIP" 키를

누르면 현재 디모드가 아래와 같이 화면 중앙에 잠시

나타납니다.

Power Only 모드에서 'PIP'를 눌렀을 때 서브 디모드의

채널은 substrate 모드 및 생산 라인에서 20-3채널로

고정되어 있습니다. 이는 다른 채널로 변경되지 않으며,

다른 채널로 강제 변경하는 것은 비정상적 케이스일 수

있습니다. ‘PIP’ 키를 눌러 메인 디모드 모드로

돌아가 주십시오

Only for training and service purposes

- 12 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

5.4. Wi-Fi MAC Address 체크

5.4.1. RS232 명령어 사용

Command Set ACK

Transmission [A][l][][Set ID][]

[20][Cr]

[O][K][x] or

[N][G]

5.4.2. IN START 메뉴 체크

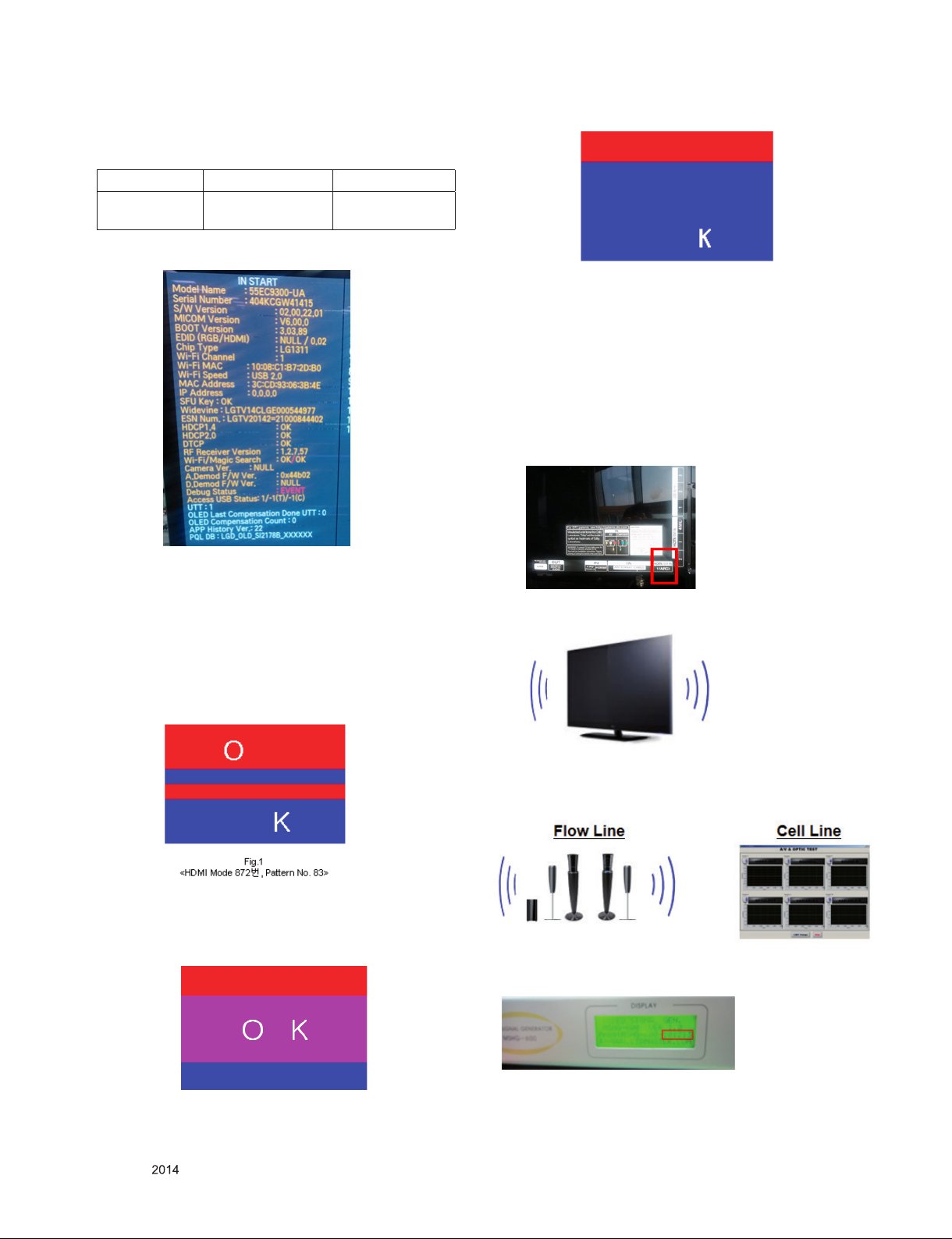

5.5. 3D 패턴 테스트(Only 3D 모델)

5.5.1. 테스트 장비

(1) 패턴 생성기 MSHG-600 또는 MSPG-6100(HDMI 1.4

지원)

(2) 패턴: HDMI 모드(모델 번호 872, 패턴 번호 83)

5.5.2. 테스트 방법

(1) Fig.1과 같은 입력 3D 테스트 신호.

Fig.3

<3D 안경없이 3D 모드에서 NG>

5.6. HDMI ARC 기능 검사

5.6.1. 테스트 장비

▪ 광학 수신기 스피커

▪ MSHG-600(SW: 1220 ↑)

▪ HDMI 케이블(1.4 버전용)

5.6.2. 테스트 방법

(1) 마스터 장비(HDMI1)에서 HDMI ARC 포트에 HDMI

케이블을 삽입합니다.

(2) TV에서 나오는 음성을 체크합니다.

(2) 3D 입력 OSD가 표시되면 ‘OK” 키를 누릅니다.

(3) 그림 2와 같이 3D 안경을 착용하지 않고 패턴을

확인합니다. (3D 안경 없는 3D 모드)

Fig.2

<3D 안경없이 3D 모드에서 OK>

Only for training and service purposes

- 13 -

(3) 스피커에서 나오는 음성을 체크하거나 AV 및 광학 테스트

프로그램을 사용합니다(MSHG-600에 연결).

*비고: Power Only 모드에서 검사하고, 마스터 장비에서

소프트웨어 버전을 확인합니다.

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

5.9. PIP(부화면) / W&R (Watch & Record) 검사

7. GND 및 내부압력 체크

7.1. 방법

(1) 전원 케이블 및 신호 케이블 삽입 조건을 확인합니다.

7.2. GND 및 내부압력 자동 검사

(1) 팰릿이 스테이션으로 이동됩니다(전원 코드/AV 코드가

(2) AV 잭 테스터를 연결합니다.

(3) 컨트롤러(GWS103-4)가 켜집니다.

(4) GND 테스트(자동)

- 테스트에 실패하면 부저음이 작동합니다.

- 테스트를 통과하면 다음 프로세스를 실행합니다(Hi-pot

(1) 목적 : Sub Tuner와 PCBA 간의 연결과 기능을 검사하기

위함

(2) 방법 : 이 검사는 Power-Only 상태에서만 가능함

i) 조정 리모컨의 "PIP" Key 를 누르세요.

ii) Sub Tuner 의 영상이 나타납니다.

iii) 영상 과 음성이 정상적인지 확인해주세요. (*sub Tuner는

DTV 만 지원함)

6. 오디오 출력 체크

6.1. 오디오 입력 조건

(1) RF 입력: 모노, 1KHz 사인파 신호, 100% 변조

(2) CVBS, 컴포넌트: 1KHz 사인파 신호(0.4Vrms)

(5) HI-POT 테스트(자동)

- 테스트에 실패하면 부저음이 작동합니다.

- 테스트를 통과하면 GOOD 램프가 켜지고 자동으로 다음

7.3. 확인 사항

(1) 테스트 전압

- GND : 100mA에서 1.5KV/분

- 신호 : 100mA에서 3KV/분

(2) 테스트 시간 : 1초

(3) 테스트 포인트

(4) 누전: 0.5mArms

단단히 꽂혀 있음).

테스트). (A/V 잭함에서 A/V 코드 제거)

프로세스로 이동됩니다.

- GND 테스트 = POWER CORD GND 및 SIGNAL CABLE GND.

- Hi-pot 테스트 = POWER CORD GND 및 LIVE & NEUTRAL.

6.2. 사양

번호 항목 최소 Typ 최대 단위 비고

1 오디오 실제

최대 출력,

L/R

(왜곡=10%

최대 출력)

9.0

8.5

10.0

8.9

12.0

9.9WVrms

(1) 측정 조건

- EQ/AVL/Clear

Voice : Off

(2) 스피커

(8Ω Impedance)

8. EYE-Q 그린 기능 검사

1단계) TV를 켭니다.

2단계) 조정 리모컨에서 EYE 버튼을 누릅니다.

3단계) 세트 정면에 있는 Eye Q 센서를 손으로 가리고 6초

정도 기다립니다.

4단계) 화면의 센서 데이터를 확인하고 데이터가 10 미만인지

확인합니다. 데이터가 6초 이내에 10 아래로 떨어지지

않으면 Eye Q 센서가 불량인 것입니다. Eye Q 센서를

교체해야 합니다.

5단계) Eye Q 센서에서 손을 뗀 다음 6초 정도 기다립니다.

6단계) 화면에서 "백라이트(xxx)"를 확인하고 데이터가

증가하는지 확인합니다. Eye Q 센서를 교체해야

합니다.

Only for training and service purposes

- 14 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

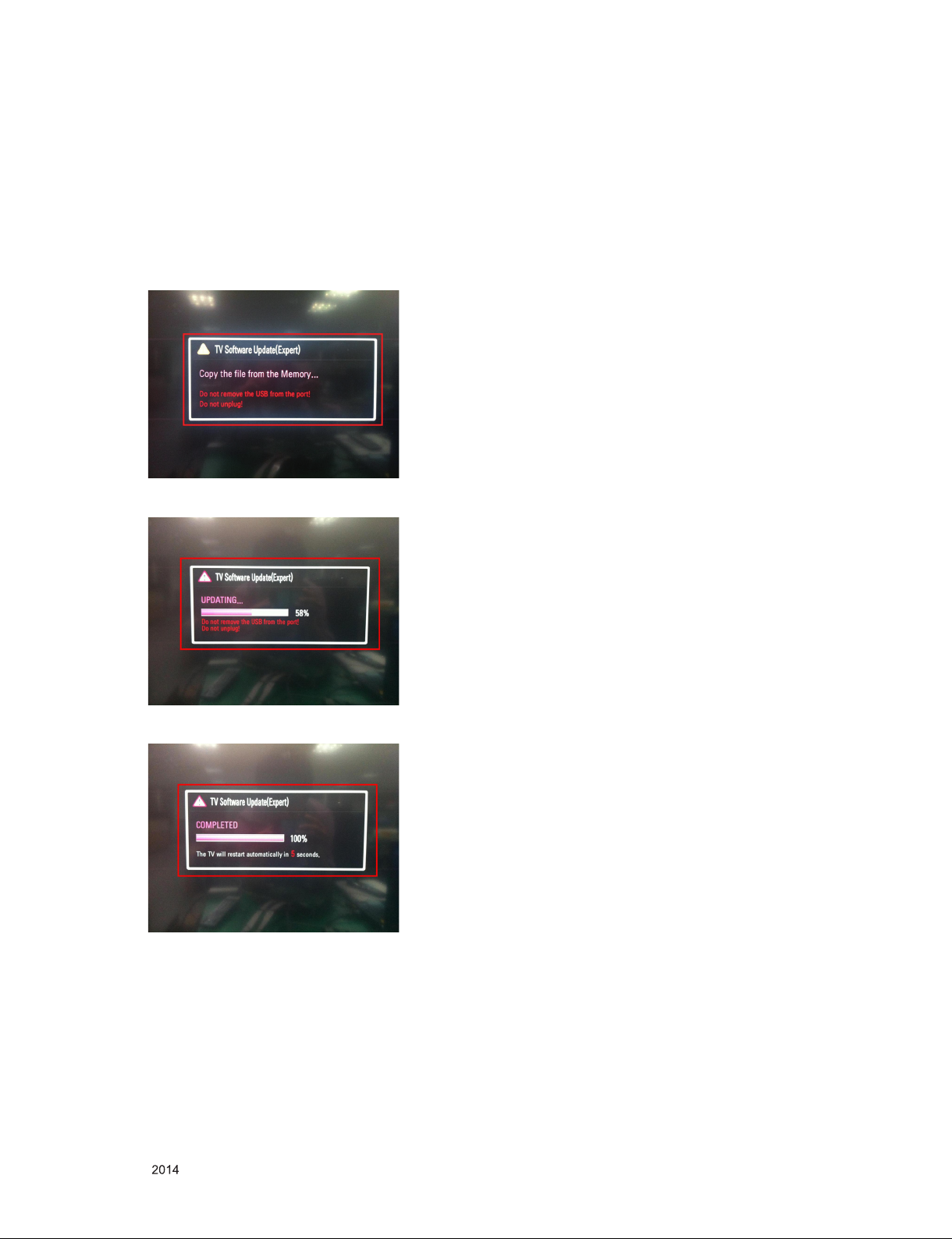

8. USB 소프트웨어 다운로드

(옵션, 서비스에만 해당)

(1) USB 스틱을 USB 소켓에 꽂기

(2) USB 스틱에서 업데이트 파일 자동 검색

- USB 스틱에 다운로드한 프로그램 버전이 TV 세트의

프로그램 버전보다 낮으면 작동하지 않습니다. 그렇지 않은

경우 USB 데이터가 자동으로 검색됩니다.

(3) "메모리에서 파일을 복사하는 중" 메시지를 표시합니다.

(4) 업데이트가 시작됩니다.

(5) 업데이트가 완료되면 TV가 자동으로 다시 시작됩니다.

(6) TV가 켜져 있으면 업데이트된 버전 및 도구 옵션을

확인합니다(다음 단계에서 도구 옵션에 대한 설명 제공).

* 다운로드 중인 버전이 TV에 있는 버전보다 높은 경우 TV의

모든 채널 데이터가 모두 손실될 수 있습니다. 이 경우 채널

복구를 수행해야 합니다. 모든 채널 데이터가 지워지면 생산

라인에서 DTV/ATV 테스트를 하지 않은 것이 됩니다.

* 다운로드한 후에 도구 옵션 설정이 다시 필요합니다.

(1) 서비스 리모컨에서 "IN-START" 키를 누릅니다.

(2) "Tool Option 1"을 선택하고 “OK” 버튼을 누릅니다.

(3) 해당 숫자를 누릅니다. (각 모델에는 고유한 숫자가

지정되어 있습니다.)

Only for training and service purposes

- 15 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

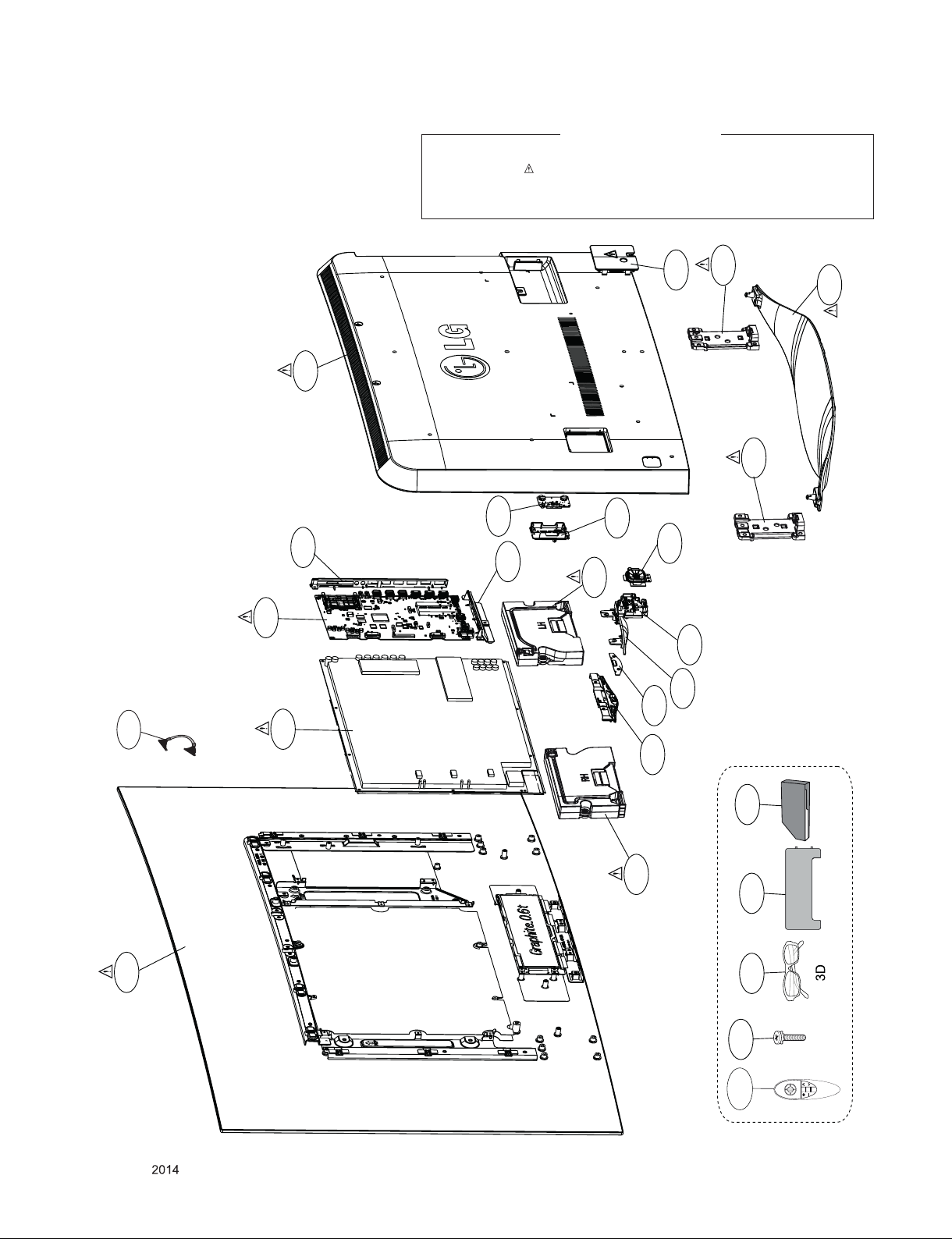

분해도

IMPORTANT SAFETY NOTICE

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These

parts are identified by in the Schematic Diagram and EXPLODED VIEW.

It is essential that these special safety parts should be replaced with the same components as

recommended in this manual to prevent X-RADIATION, Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

710

901

900

400

902

570

521

571

510

522

120

540

511

501

500

LV1

530

502

200

Only for training and service purposes

- 16 -

UM1

121

RC1

AG1

A10

Set + Stand

A22

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

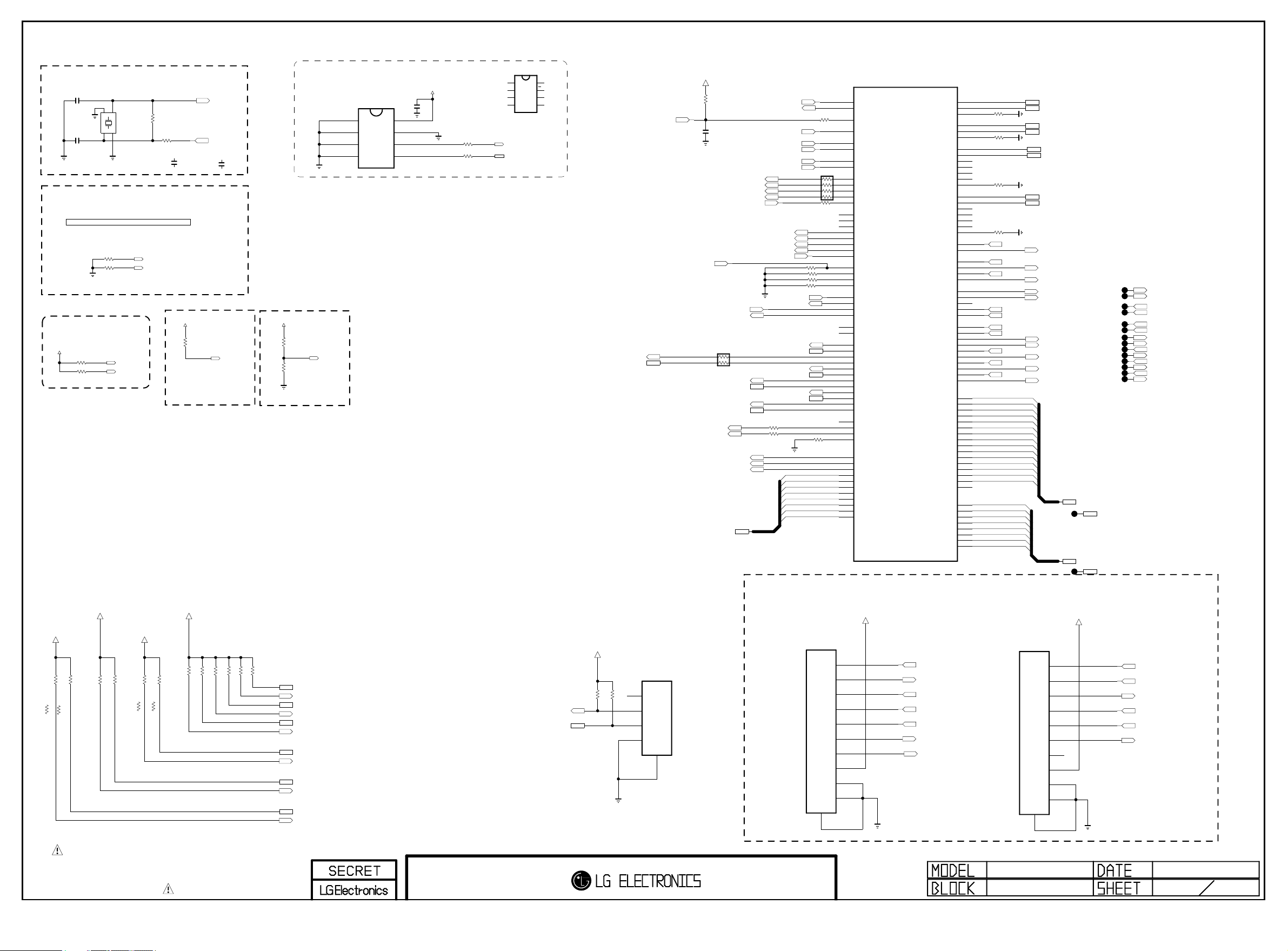

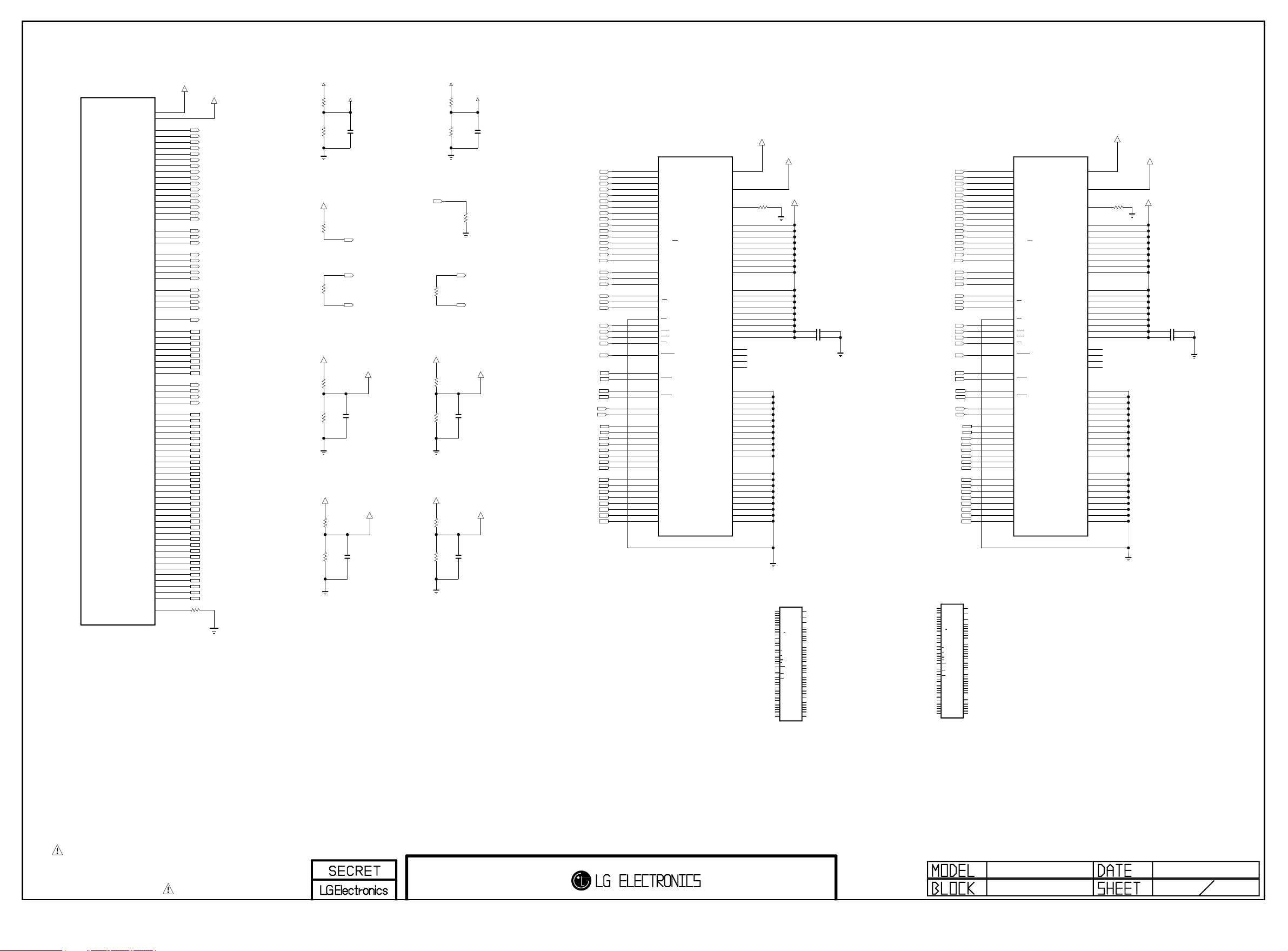

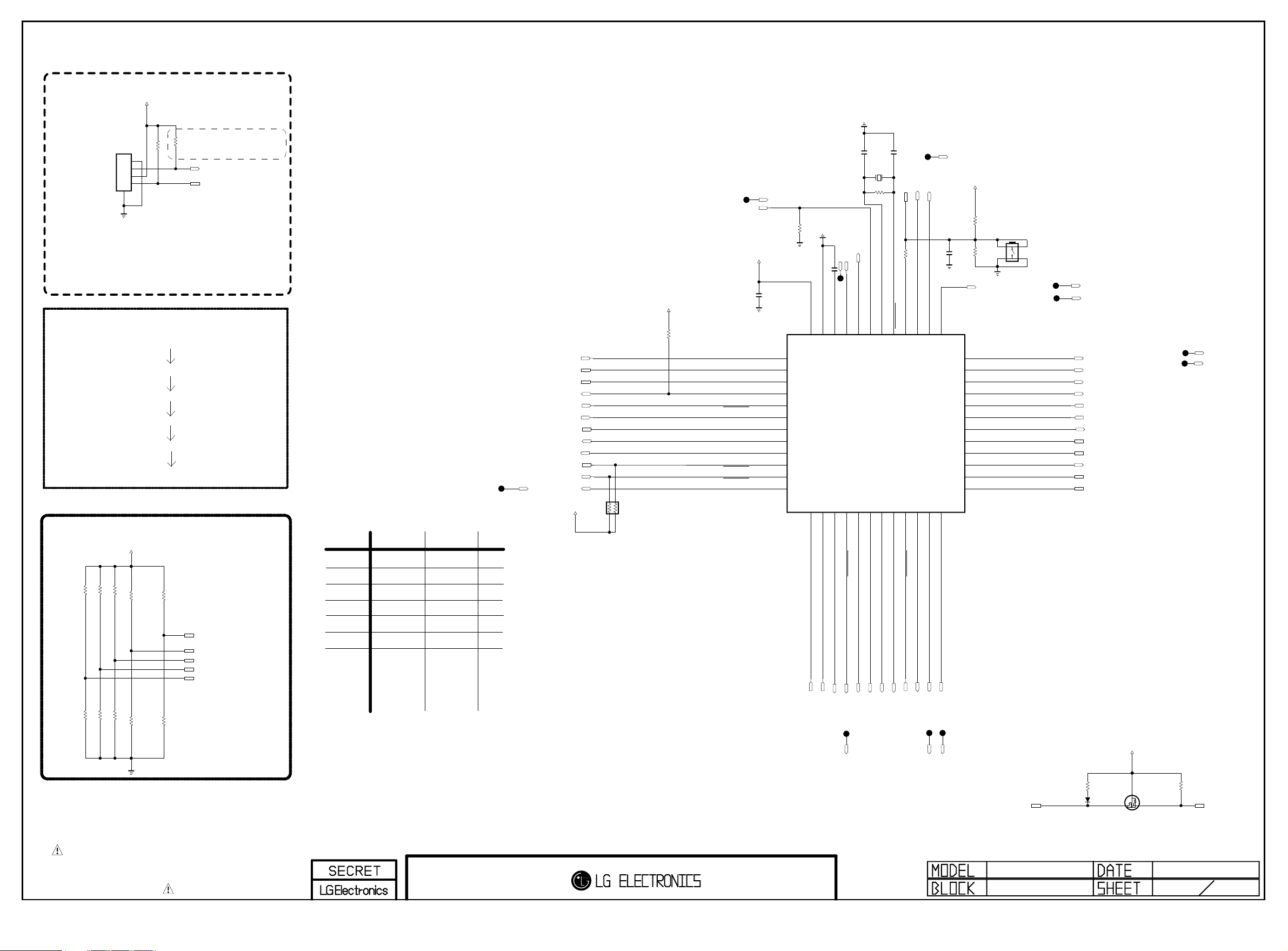

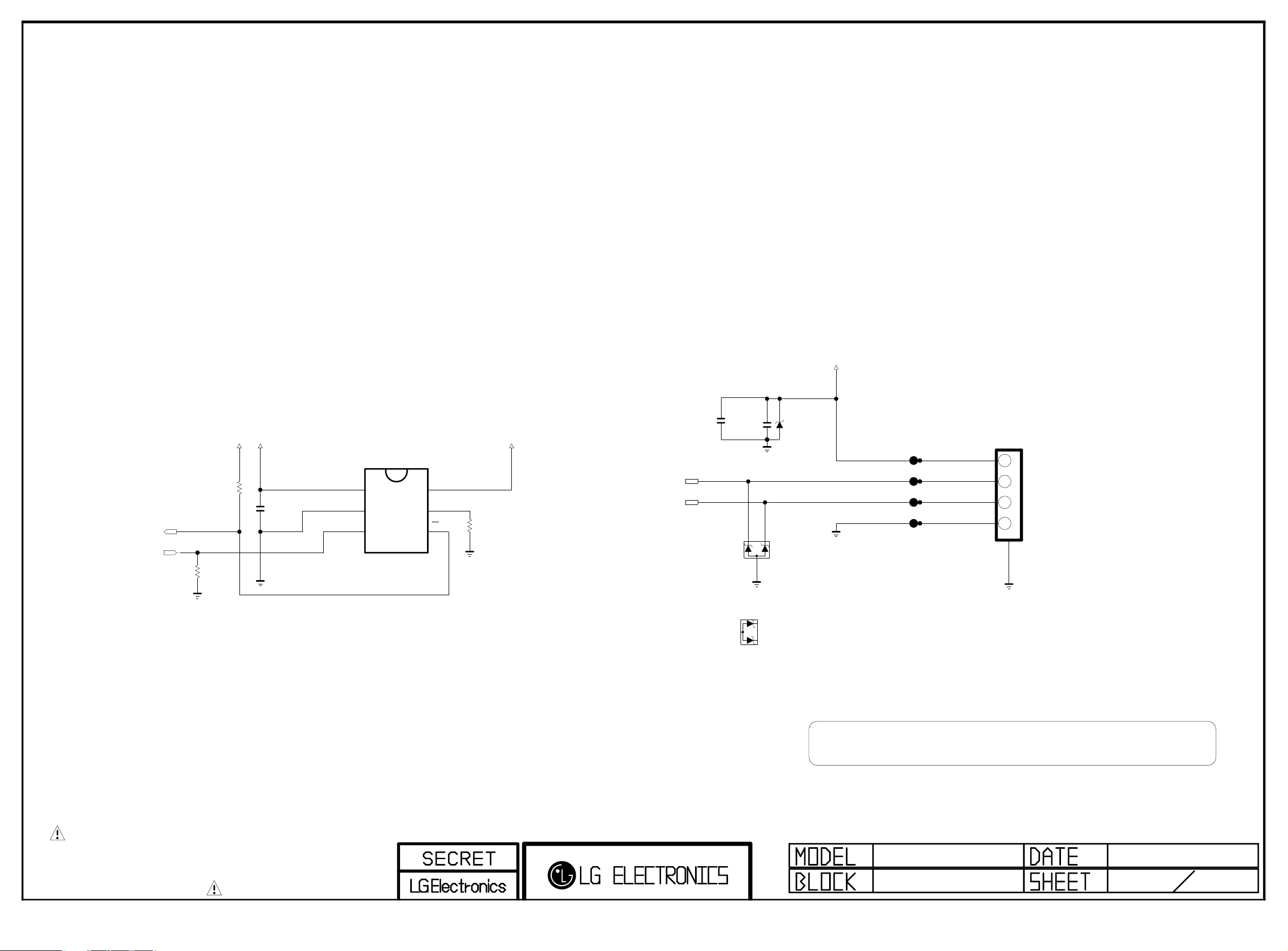

System Configuration

Copyright ⓒ 2014 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LGE Internal Use Only

Clock for M14-A0

MAIN Clock(24Mhz)

LOADCAP_ATSC_PCB

10pF

C101

C102

LOADCAP_ATSC_PCB

System Clock for Analog block(24Mhz)

PLL SET[1:0] : internal pull up

"00" : CPU(1200Mhz),M0 / M1 DDR(792,792 Mhz)

"01" : CPU(1056Mhz),M0 / M1 DDR(672,672 Mhz)

"10" : CPU(1056Mhz),M0 / M1 DDR(792,792 Mhz)

"11" : CPU( 960Mhz),M0 / M1 DDR(792,792 Mhz)

OP MODE[1:0]

"00" : Normal Mode

"01/10/11" : Internal Test mode

+3.3V_NORMAL

R101 3.3K

R102 3.3K

Extenal test only

+3.3V_NORMAL

+3.3V_TUNER

R148

3.3K

R146

3.3K

KR_PIP_NOT

KR_PIP_NOT

1.5K

1.5K

KR_PIP

R146-*1

KR_PIP

R148-*1

10pF

Extenal test only

OPT

OPT

R149

2

3

OPT

R103 3.3K

R104 3.3K

OPT

3.3K

X-TAL_1

GND_1

1

4

X-TAL_2

24MHz

GND_2

OPM1

OPM0

X101

R118

PLLSET1

PLLSET0

+3.3V_TUNER

R150

3.3K

R155

1.2K

KR_PIP_NOT

KR_PIP_NOT

3.3K

KR_PIP

KR_PIP

R155-*1

1M

R180

560

LOADCAP_DVB_PCB

C101-*1

6.8pF

50V

+3.3V_NORMAL

INSTANT boot MODE

"1 : Instant boot

"0 : normal

3.3K

R121

(internal pull down)

OPT

INSTANT_MODE0

+3.3V_NORMAL

R158

R157

R156

3.3K

R156-*1

3.3K

1.2K

XTAL_IN

XTAL_OUT

LOADCAP_DVB_PCB

C102-*1

6.8pF

50V

INSTANT_BOOT

I2C PULL UP

R159

3.3K

3.3K

R160

3.3K

R161

+3.3V_NORMAL

3.3K

R127

OPT

3.3K

R128

BOOT_MODE0

I2C

I2C_1 : AMP

I2C_2 : T-CON,L/DIMING

I2C_3 : MICOM

I2C_4 : S/Demod,T2/Demod, LNB

I2C_5 : NVRAM

I2C_6 : TUNER_MOPLL(T/C,ATV)

R162

3.3K

3.3K

IC103

AT24C256C-SSHL-T

A0

1

A1

2

A2

3

GND

4

NVRAM_ATMEL

BOOT MODE

"0 : EMMC

"1 : TEST MODE

BOOT_MODE

I2C_SDA1

I2C_SCL1

I2C_SDA_MICOM_SOC

I2C_SCL_MICOM_SOC

I2C_SDA2

I2C_SCL2

I2C_SDA4

I2C_SCL4

I2C_SDA5

I2C_SCL5

I2C_SDA6

I2C_SCL6

NVRAM

VCC

8

WP

7

SCL

6

SDA

5

+3.3V_NORMAL

C107

0.1uF

16V

Write Protection

- Low : Normal Operation

- High : Write Protection

R143 33

R144 33

IC103-*1

M24256-BRMN6TP

E0

VCC

1

8

WC

E1

7

2

SCL

E2

6

3

SDA

VSS

5

4

NVRAM_ST

I2C_SCL5

I2C_SDA5

I2C_SCL_MICOM_SOC

I2C_SDA_MICOM_SOC

LOCAL DIMMING I2C CONTROL

+3.3V_NORMAL

OPT

OPT

R105

3.3K

R106

3.3K

LED_SCL

LED_SDA

SOC_RESET

FORCED_JTAG_0

P102

12507WS-04L

1

2

3

4

5

+3.3V_NORMAL

R163

10K

OPT

C104

0.1uF

16V

L/DIM0_VS

L/DIM0_SCLK

L/DIM0_MOSI

IRB_SPI_MOSI/TDO1

IRB_SPI_MISO/TDI1

M_REMOTE_RX

M_REMOTE_TX

1/16W

33

AR100

I2C_SCL4

I2C_SDA4

I2C_SCL6

I2C_SDA6

PWM_DIM2

PWM_DIM

EMMC_CLK

EMMC_CMD

EMMC_RST

EMMC_DATA[0-7]

OPT

XTAL_IN

XTAL_OUT

BOOT_MODE

PLLSET0

PLLSET1

TCK0

TDI0

TRST_N1

IRB_SPI_SS/TMS1

IRB_SPI_CK/TCK1

I2C_SCL1

I2C_SDA1

I2C_SCL2

I2C_SDA2

I2C_SCL5

I2C_SDA5

33

R107

33

R108

OPM0

OPM1

R178 33

OPT

R182 10K

R183 10K

R184 10K

R185 10K

SOC_RX

SOC_TX

EMMC_DATA[7]

EMMC_DATA[6]

EMMC_DATA[5]

EMMC_DATA[4]

EMMC_DATA[3]

EMMC_DATA[2]

EMMC_DATA[1]

EMMC_DATA[0]

12505WS-10A00

JTAG_CPU

B23

A23

R169

AG21

33

AJ18

AB8

AC8

AD8

AE8

AR101

AG30

AG28

AG29

AH29

AJ27

AH27

AG26

AH26

AJ12

AJ13

AH12

AG12

AH23

AG22

AH11

AG11

AG10

AH22

AJ22

AH10

AJ10

AG23

AH24

Y7

Y6

W7

W6

W5

AH7

AJ7

AG8

AH8

AH9

AG9

AJ9

AC6

AC7

AD7

AB7

G32

G33

G31

D31

F33

F32

E32

F31

D33

D32

E31

33

R179

10K

1/16W

5%

Jtag-0 I/F

+3.3V_NORMAL

P103

1

2

3

4

5

6

7

8

9

10

11

IC101

LG1311

XIN_MAIN

XO_MAIN

PORES_N

BOOT_MODE

PLLSET0

PLLSET1

OPM0

OPM1

L_VSOUT_LD/TRST0_N

DIM0_SCLK/TMS0

DIM1_SCLK/TCK0

DIM1_MOSI/TDI0

DIM0_MOSI/TDO0

SPI_CS0

SPI_SCLK0

SPI_DO0

SPI_DI0/TRST1_N

SPI_CS1/TMS1

SPI_SCLK1/TCK1

SPI_DO1/TDO1

SPI_DI1/TDI1

EXT_INTR0

EXT_INTR1

EXT_INTR2

EXT_INTR3

UART0_RXD

UART0_TXD

UART1_RXD

UART1_TXD

UART1_RTS_N

UART1_CTS_N

SCL0

SDA0

SCL1

SDA1

SCL2

SDA2

SCL3

SDA3

SCL4

SDA4

SCL5

SDA5

PWM0

PWM1

PWM2

PWM_IN

EMMC_CLK

EMMC_CMD

EMMC_RESETN

EMMC_DATA7

EMMC_DATA6

EMMC_DATA5

EMMC_DATA4

EMMC_DATA3

EMMC_DATA2

EMMC_DATA1

EMMC_DATA0

USB2_0_DP0

USB2_0_DM0

USB2_0_TXRTUNE

USB2_1_DP0

USB2_1_DM0

USB2_1_TXRTUNE

USB3_DP0

USB3_DM0

USB3_TXP0

USB3_TXM0

USB3_RXP0

USB3_RXM0

USB3_RESREF0

USB3_DP1

USB3_DM1

USB3_TXP1

USB3_TXM1

USB3_RXP1

USB3_RXM1

USB3_RESREF1

HUB_PORT_OVER0

HUB_VBUS_CTRL0

EB_CS3

EB_CS2

EB_CS1

EB_CS0

EB_WE_N

EB_OE_N

EB_WAIT

EB_BE_N1

EB_BE_N0

CAM_CD1_N

CAM_CD2_N

CAM_CE1_N

CAM_CE2_N

CAM_IREQ_N

CAM_RESET

CAM_INPACK_N

CAM_VCCEN_N

CAM_WAIT_N

CAM_REG_N

EB_ADDR0

EB_ADDR1

EB_ADDR2

EB_ADDR3

EB_ADDR4

EB_ADDR5

EB_ADDR6

EB_ADDR7

EB_ADDR8

EB_ADDR9

EB_ADDR10

EB_ADDR11

EB_ADDR12

EB_ADDR13

EB_ADDR14

EB_ADDR15

EB_DATA0

EB_DATA1

EB_DATA2

EB_DATA3

EB_DATA4

EB_DATA5

EB_DATA6

EB_DATA7

L/DIM0_VS

TDI0

L/DIM0_MOSI

L/DIM0_SCLK

TCK0

SOC_RESET

FORCED_JTAG_0

AN9

AM9

AN8

H32

J31

H33

N31

N32

P33

P32

M32

M33

P31

K33

K32

L32

L31

K31

J32

M31

W28

W29

H28

J30

J28

J29

G30

F30

H29

G29

G28

P28

P27

U28

R29

V27

T28

T29

R28

U27

N29

K30

E30

M30

N28

M28

M29

L29

K29

K28

L28

D30

EB_ADDR[10]

F29

EB_ADDR[11]

C32

EB_ADDR[12]

C33

EB_ADDR[13]

C31

EB_ADDR[14]

B33

B32

A32

B31

A31

A30

B30

C30

C29

(TRST0_N)

(TDO0)

(TMS0)

R1712001%

R1722001%

R1732001%

R1742001%

/USB_OCD1

/USB_OCD2

/USB_OCD3

EB_BE_N1

EB_BE_N0

CAM_CD1_N

CAM_CD2_N

CAM_IREQ_N

CAM_INPACK_N

CAM_WAIT_N

EB_ADDR[0]

EB_ADDR[1]

EB_ADDR[2]

EB_ADDR[3]

EB_ADDR[4]

EB_ADDR[5]

EB_ADDR[6]

EB_ADDR[7]

EB_ADDR[8]

EB_ADDR[9]

EB_DATA[0]

EB_DATA[1]

EB_DATA[2]

EB_DATA[3]

EB_DATA[4]

EB_DATA[5]

EB_DATA[6]

EB_DATA[7]

12505WS-10A00

WIFI_DP

WIFI_DM

USB_DP3

USB_DM3

USB_DP1

USB_DM1

USB_DP2

USB_DM2

USB_CTL1

USB_CTL2

USB_CTL3

EB_WE_N

EB_OE_N

/PCM_CE1

/PCM_CE2

PCM_RESET

PCM_5V_CTL

CAM_REG_N

Jtag-1 I/F

+3.3V_NORMAL

P104

OPT

1

2

3

4

5

6

7

8

9

10

11

EB_ADDR[0-14]

TP102

EB_DATA[0-7]

TP103

PAGE 1

TP104

TP105

TP106

TP107

TP108

TP109

TP110

TP111

TP112

TP113

TP114

TP115

TP116

TP117

EB_ADDR[0-14]

EB_DATA[0-7]

EB_WE_N

EB_OE_N

EB_BE_N1

EB_BE_N0

CAM_CD1_N

CAM_CD2_N

/PCM_CE1

/PCM_CE2

CAM_IREQ_N

PCM_RESET

CAM_INPACK_N

PCM_5V_CTL

CAM_WAIT_N

CAM_REG_N

TRST_N1

IRB_SPI_MISO/TDI1

IRB_SPI_MOSI/TDO1

IRB_SPI_SS/TMS1

IRB_SPI_CK/TCK1

SOC_RESET

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FIRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFACTURES SPECIFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

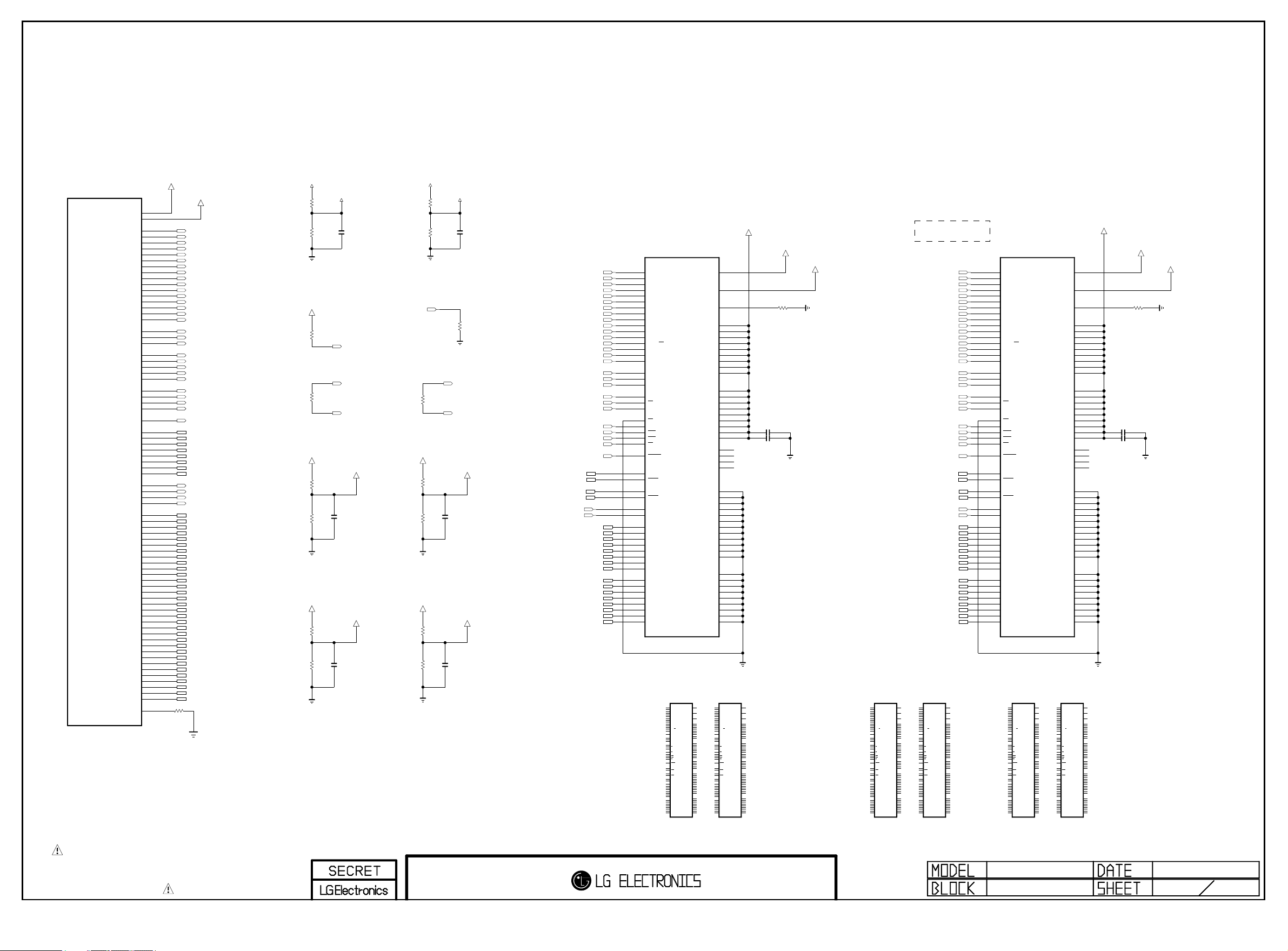

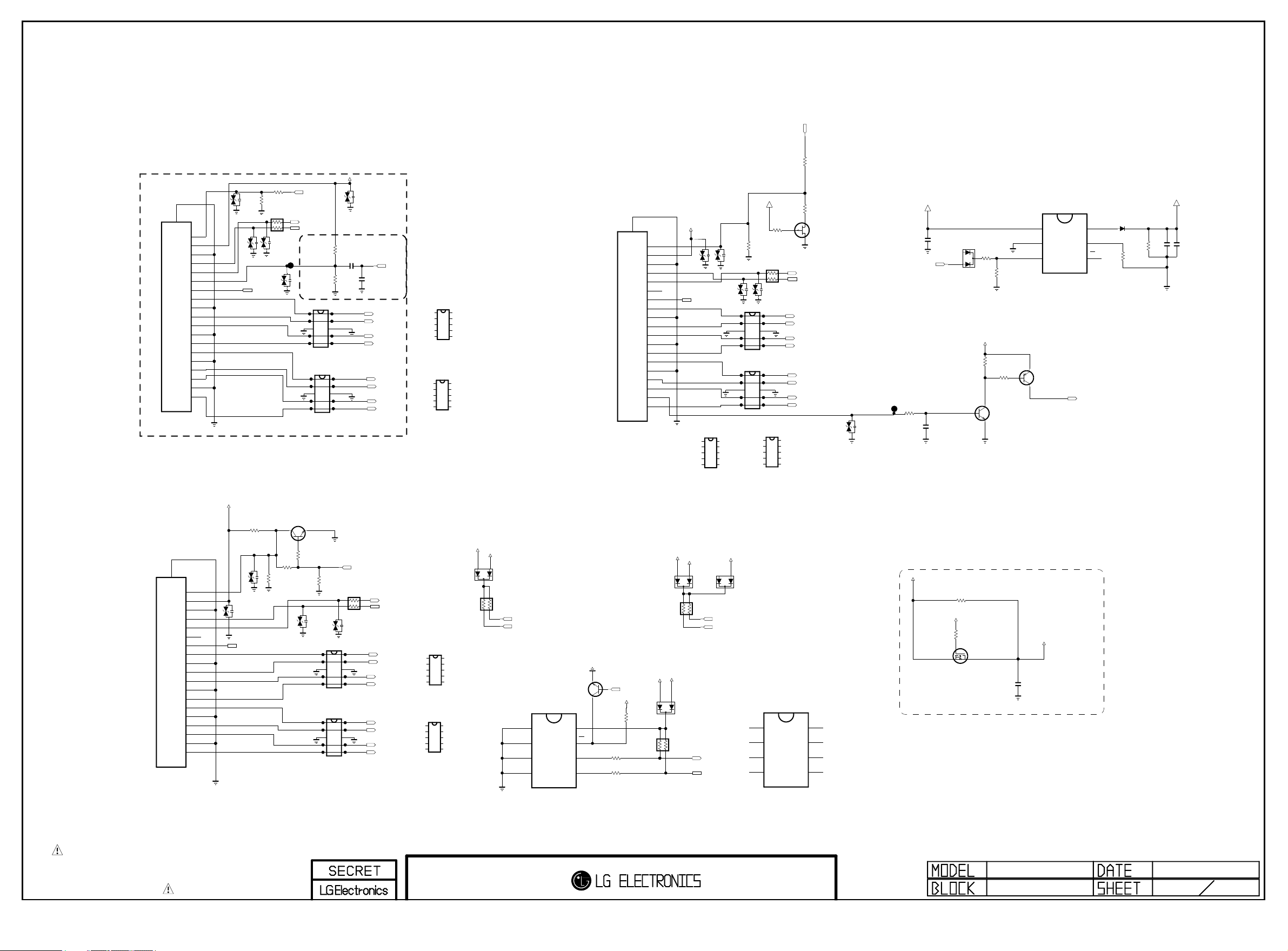

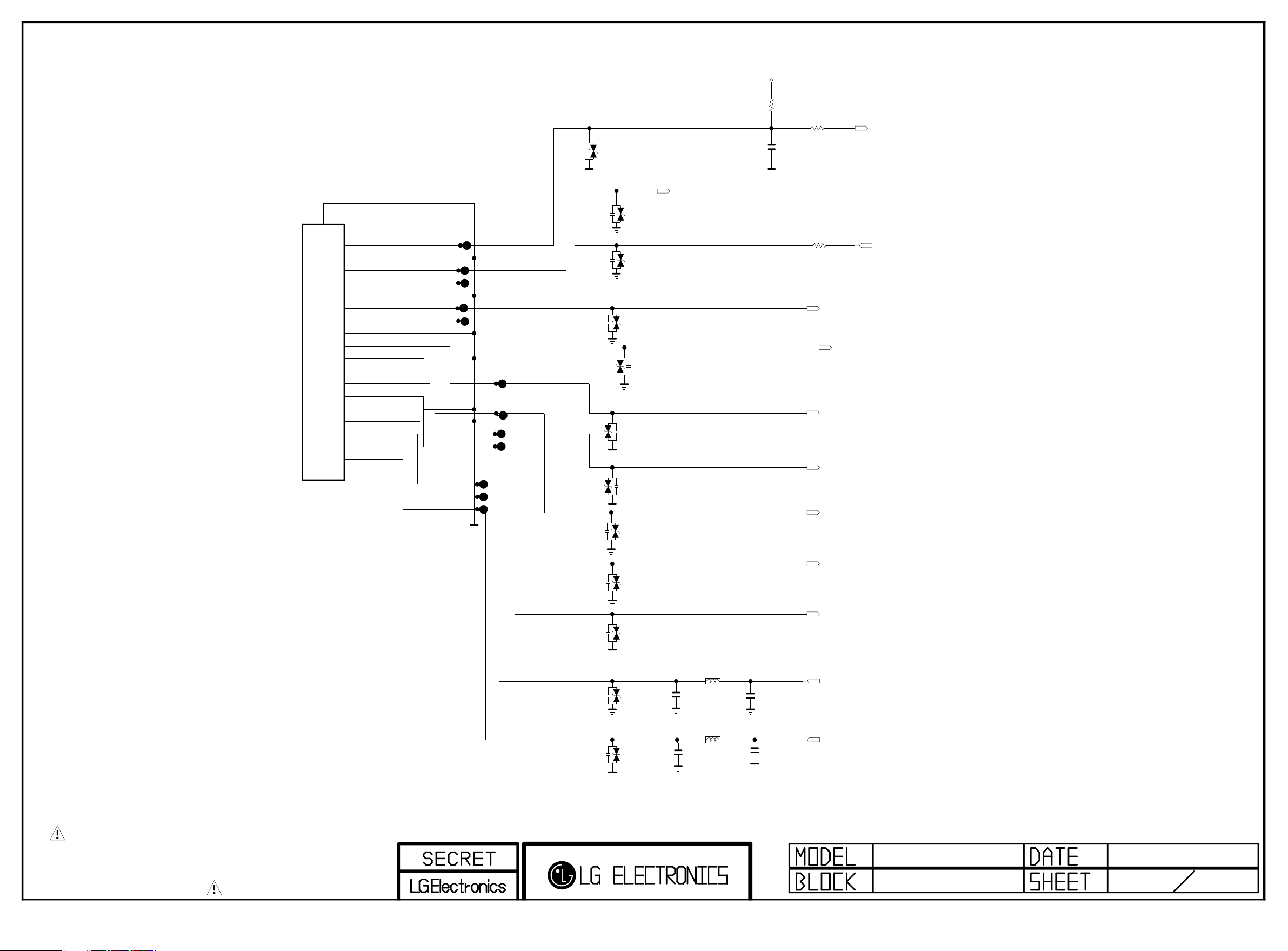

M14-Peripheral

MID_LG1311

M14 Symbol A

2013.04.04

1

31

PAGE 2

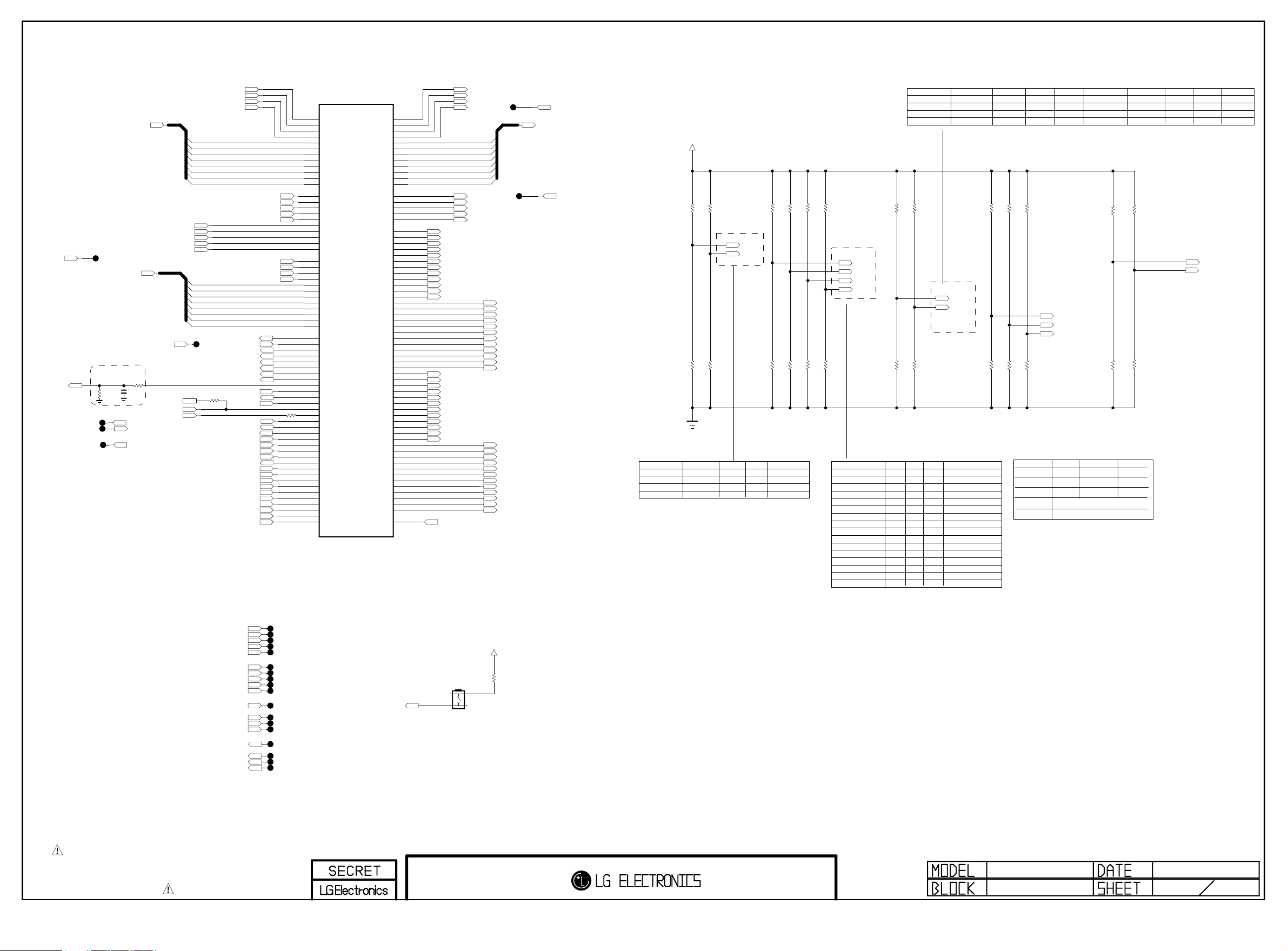

Copyright ⓒ 2014 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LGE Internal Use Only

FE_DEMOD1_TS_DATA[0-7]

TPI_ERR

AMP_RESET_N

TP226

TP227

FE_DEMOD3_TS_SYNC

FE_DEMOD3_TS_DATA

TPI_DATA[0-7]

Near AMP

C200

1000pF

50V

R231

4.7K

TP228

FE_DEMOD1_TS_CLK

FE_DEMOD1_TS_SYNC

FE_DEMOD1_TS_VAL

FE_DEMOD1_TS_ERROR

FE_DEMOD3_TS_CLK

FE_DEMOD3_TS_VAL

SC_DET

R226

100

1/16W

5%

LED_SDA

INSTANT_BOOT

LED_SCL

CAM_SLIDE_DET

CAM_TRIGGER_DET

/RST_HUB

IC101

LG1311

AH30

TP_DVB_CLK

AH32

TP_DVB_SOP

AH31

TP_DVB_VAL

AH33

TP_DVB_ERR

FE_DEMOD1_TS_DATA[7]

FE_DEMOD1_TS_DATA[6]

FE_DEMOD1_TS_DATA[5]

FE_DEMOD1_TS_DATA[4]

FE_DEMOD1_TS_DATA[3]

FE_DEMOD1_TS_DATA[2]

FE_DEMOD1_TS_DATA[1]

FE_DEMOD1_TS_DATA[0]

FE_DEMOD2_TS_CLK

FE_DEMOD2_TS_SYNC

FE_DEMOD2_TS_VAL

FE_DEMOD2_TS_ERROR

FE_DEMOD2_TS_DATA

TPI_CLK

TPI_SOP

TPI_VAL

SC_DET

/RST_PHY

2D/3D_CTL

/TU_RESET1

/TU_RESET2

BT_RESET

HP_DET

OPT

OPC_EN

DEBUG

BIT0

/RST_HUB

COMP1_DET

IR_B_RESET

BIT1

BIT2

BIT3

BIT4

BIT5

BIT6

BIT7

TPI_ERR

TPI_DATA[0]

TPI_DATA[1]

TPI_DATA[2]

TPI_DATA[3]

TPI_DATA[4]

TPI_DATA[5]

TPI_DATA[6]

TPI_DATA[7]

MODEL_OPT_11

TP225

RF_SWITCH_CTL

R224

33

CAM_SLIDE_DET

CAM_TRIGGER_DET

MODEL_OPT_12

AV1_CVBS_DET

MODEL_OPT_8

MODEL_OPT_9

MODEL_OPT_10 EPI_LOCK8/6

AM33

TP_DVB_DATA7

AL32

TP_DVB_DATA6

AL33

TP_DVB_DATA5

AK32

TP_DVB_DATA4

AK33

TP_DVB_DATA3

AK31

TP_DVB_DATA2

AJ30

TP_DVB_DATA1

AJ31

TP_DVB_DATA0

AL31

STPI0_CLK

AN32

STPI0_SOP

AM32

STPI0_VAL

AN31

STPI0_ERR

AM31

STPI0_DATA

AH28

STPI1_CLK

AJ28

STPI1_SOP

AK30

STPI1_VAL

AJ29

STPI1_ERR

AG27

STPI1_DATA

A28

TPI_CLK

B28

TPI_SOP

B29

TPI_VAL

C28

TPI_ERR

A27

TPI_DATA0

B27

TPI_DATA1

C27

TPI_DATA2

B26

TPI_DATA3

C26

TPI_DATA4

B25

TPI_DATA5

A25

TPI_DATA6

C25

TPI_DATA7

AG13

GPIO31

AJ19

GPIO30

AG14

GPIO29

AG15

GPIO28

AJ15

GPIO27

AH19

GPIO26

AH18

GPIO25

AG19

GPIO24

AH5

GPIO23

AJ5

GPIO22

AJ6

GPIO21

AH6

GPIO20

AG6

AG24

AH16

AJ21

AH21

AG16

AJ24

AH17

AG17

AH13

AH15

AG18

AH14

AJ16

AH20

GPIO19

AG5

GPIO18

AF7

GPIO17

AG7

GPIO16

GPIO15

GPIO14

V29

GPIO13

GPIO12

GPIO11

V28

GPIO10

GPIO9

GPIO8

GPIO7

GPIO6

GPIO5

GPIO4

GPIO3

GPIO2

GPIO1

GPIO0

R225

OPT

33

TPIO_CLK

TPIO_SOP

TPIO_VAL

TPIO_ERR

TPIO_DATA0

TPIO_DATA1

TPIO_DATA2

TPIO_DATA3

TPIO_DATA4

TPIO_DATA5

TPIO_DATA6

TPIO_DATA7

EPI_SOE

EPI_MCLK

EPI_GCLK

EPI_EO

EPI_VST

TX_0N

TX_0P

TX_1N

TX_1P

TX_2N

TX_2P

TX_3N

TX_3P

TX_4N

TX_4P

TX_5N

TX_5P

TX_6N

TX_6P

TX_7N

TX_7P

TX_8N

TX_8P

TX_9N

TX_9P

TX_10N

TX_10P

TX_11N

TX_11P

TX_12N

TX_12P

TX_13N

TX_13P

TX_14N

TX_14P

TX_15N

TX_15P

TX_16N

TX_16P

TX_17N

TX_17P

TX_18N

TX_18P

TX_19N

TX_19P

TX_20N

TX_20P

TX_21N

TX_21P

TX_22N

TX_22P

TX_23N

TX_23P

TX_LOCKN

D28

E29

E28

F28

D27

E27

F27

E26

F26

E25

D25

F25

AA5

AB5

AA7

AA6

AB6

AK8

AL8

AK7

AL7

AM6

AN6

AK6

AL6

AK5

AL5

AN4

AN3

AM2

AM1

AM4

AM3

AL4

AL3

AK2

AK1

AK4

AK3

AJ4

AJ3

AH2

AH1

AH4

AH3

AG4

AG3

AF2

AF1

AF4

AF3

AE4

AE3

AD2

AD1

AD4

AD3

AC4

AC3

AB2

AB1

AB4

AB3

AA4

AA3

AM8

TPO_CLK

TPO_SOP

TPO_VAL

TPO_ERR

TPO_DATA[0]

TPO_DATA[1]

TPO_DATA[2]

TPO_DATA[3]

TPO_DATA[4]

TPO_DATA[5]

TPO_DATA[6]

TPO_DATA[7]

EPI_SOE

MCLK_SOC

GCLK_SOC

EO_SOC

GST_SOC

TXB4N/TX0N

TXB4P/TX0P

TXB3N/TX1NFE_DEMOD3_TS_ERROR

TXB3P/TX1P

TXBCLKN/TX2N

TXBCLKP/TX2P

TXB2N/TX3N

TXB2P/TX3P

TXB1N/TX4N

TXB1P/TX4P

TXB0N/TX5N

TXB0P/TX5P

TXD4N/TX12N

TXD4P/TX12P

TXD3N/TX13N

TXD3P/TX13P

TXDCLKN/TX14N

TXDCLKP/TX14P

TXD2N/TX15N

TXD2P/TX15P

TXD1N/TX16N

TXD1P/TX16P

TXD0N/TX17N

TXD0P/TX17P

TPO_DATA[0-7]

TXA4N/TX6N

TXA4P/TX6P

TXA3N/TX7N

TXA3P/TX7P

TXACLKN/TX8N

TXACLKP/TX8P

TXA2N/TX9N

TXA2P/TX9P

TXA1N/TX10N

TXA1P/TX10P

TXA0N/TX11N

TXA0P/TX11P

TXC4N/TX18N

TXC4P/TX18P

TXC3N/TX19N

TXC3P/TX19P

TXCCLKN/TX20N

TXCCLKP/TX20P

TXC2N/TX21N

TXC2P/TX21P

TXC1N/TX22N

TXC1P/TX22P

TXC0N/TX23N

TXC0P/TX23P

TPO_ERR

EPI_SOE

+3.3V_NORMAL

BIT0_1

R201 10K

BIT0_0

R202 10K

BIT [0/1]

0 / 0

0 / 1

1 / 0

1 / 1

TAIWAN/COLOM

CHINA/HONGKONG

ASIA/AFRICA

EU/CIS

BIT1_1

R203 10K

BIT1_0

R204 10K

ATSC

N/AMERICA

KOREA

S/AMERCIA

Model Option

BIT3_1

BIT2_1

R205 10K

R207 10K

BIT0

BIT1

BIT3_0

BIT2_0

R206 10K

R208 10K

JP

JAPAN

BIT4_1

R209 10K

BIT4_0

R210 10K

BIT5_1

R211 10K

BIT5_0

R212 10K

BIT2

BIT3

BIT4

BIT5

BACK-END OPTIONAREA OPTION

BIT[2/3/4/5]DVB

0 / 0 / 0 / 0

0 / 0 / 0 / 1

0 / 0 / 1 / 0

0 / 0 / 1 / 1

0 / 1 / 0 / 0

0 / 1 / 0 / 1

0 / 1 / 1 / 0

0 / 1 / 1 / 1

1 / 0 / 0 / 0

1 / 0 / 0 / 1

1 / 0 / 1 / 0

1 / 0 / 1 / 1

1 / 1 / 0 / 0

1 / 1 / 0 / 1

1 / 1 / 1 / 0

1 / 1 / 1 / 1

BIT6_1

R213 10K

BIT [6/7]

BIT7_1

R215 10K

0 / 0

0 / 1

1 / 0

1 / 1

EU/CIS

T/C

T2/C/S2/ATV_EXT

T2/C

T2/C/S2/ATV_SOC

BIT6

BIT7

BIT6_0

BIT7_0

R214 10K

R216 10K

TYPE

EPI FHD, 120Hz, V14 (8 lane)

EPI FHD, 120Hz, v14_32inch (6 lane)

EPI FHD, 120Hz, V13 (6 lane)

EPI FHD, 120Hz, V12 (6 lane)

EPI FHD, 60Hz, V14_32 inch (6lane)

LVDS FHD, 120Hz

LVDS FHD, 60Hz

LVDS HD, 60Hz

LVDS FHD, 60Hz, CP BOX

LVDS HD, 60Hz SMALL SMART

Vby1 FHD, 120Hz

LVDS FHD, 120Hz OLED

FRC

FHD

PANEL TYPE

OLED

AJJA

T/C

T2/C/ATV_EXT

T2/C/ATV_SOC

T2/C/S2

DDR3_DDP

R219 10K

R217 10K

DDR3_1.5GB

DDR3_2GB

R220 10K

R218 10K

DDR3_NON_DDP

TAIWAN/COL

T/C

T2/C PIP

T2/C

DDR_3G

R221 10K

R222 10K

NON_DDR_3G

MODEL_OPT_8

MODEL_OPT_9

MODEL_OPT_10

MODEL_OPT_11

MODEL_OPT_12

BRAZILKOREA

ISDB PIP

ISDB

ATV_SOC

ATV_EXT

OPT

R227 10K

NORTH AMERICA

ATSC PIP

ATV_SOC

ATV_EXT

OPT

R229 10K

CHINA/HONG

Default Default

ATSC PIP

MODEL_OPT_8

MODEL_OPT_9

MODEL_OPT_10

OPT

OPT

R230 10K

R228 10K

LOW

DDR3

NON_DDP

DDR3

FOR UD

NON_DDR3 3G

NOT GPIO! OLED ECO POWER CTL

HIGH

DDP

1.5GB

2GB

DDR3 3G

JAPAN

MODEL_OPT_11

MODEL_OPT_12

FE_DEMOD2_TS_CLK

FE_DEMOD2_TS_SYNC

FE_DEMOD2_TS_VAL

FE_DEMOD2_TS_ERROR

FE_DEMOD2_TS_DATA

FE_DEMOD3_TS_CLK

FE_DEMOD3_TS_SYNC

FE_DEMOD3_TS_VAL

FE_DEMOD3_TS_ERROR

FE_DEMOD3_TS_DATA

TPI_DATA[0-7]

TPI_CLK

TPI_SOP

TPI_VAL

TPO_DATA[0-7]

TPO_CLK

TPO_SOP

TPO_VAL

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FIRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFACTURES SPECIFIED PARTS BE USED FOR

M14-Display In/Out

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

TP202

TP203

TP204

TP205

TP206

TP207

TP208

TP209

TP210

TP211

TP212

TP213

TP214

TP215

TP221

TP218

TP219

TP220

DEBUG

+3.3V_NORMAL

SW201

JTP-1127WEM

12

3

4

For ISP

R223

3.3K

MID_LG1311

M14 Symbol B

2013.04.04

2

31

PLACE AT JACK SIDE

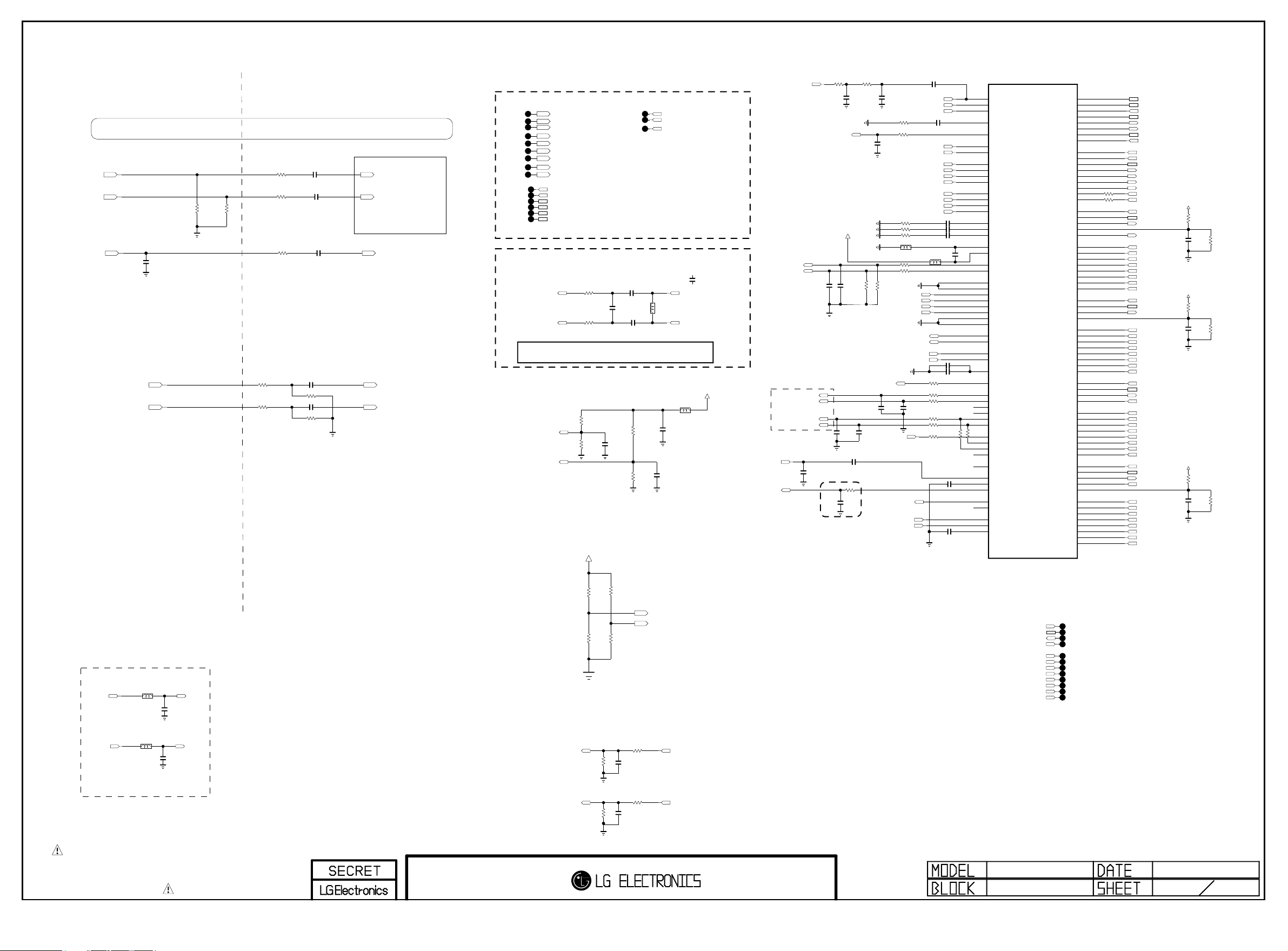

Copyright ⓒ 2014 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LGE Internal Use Only

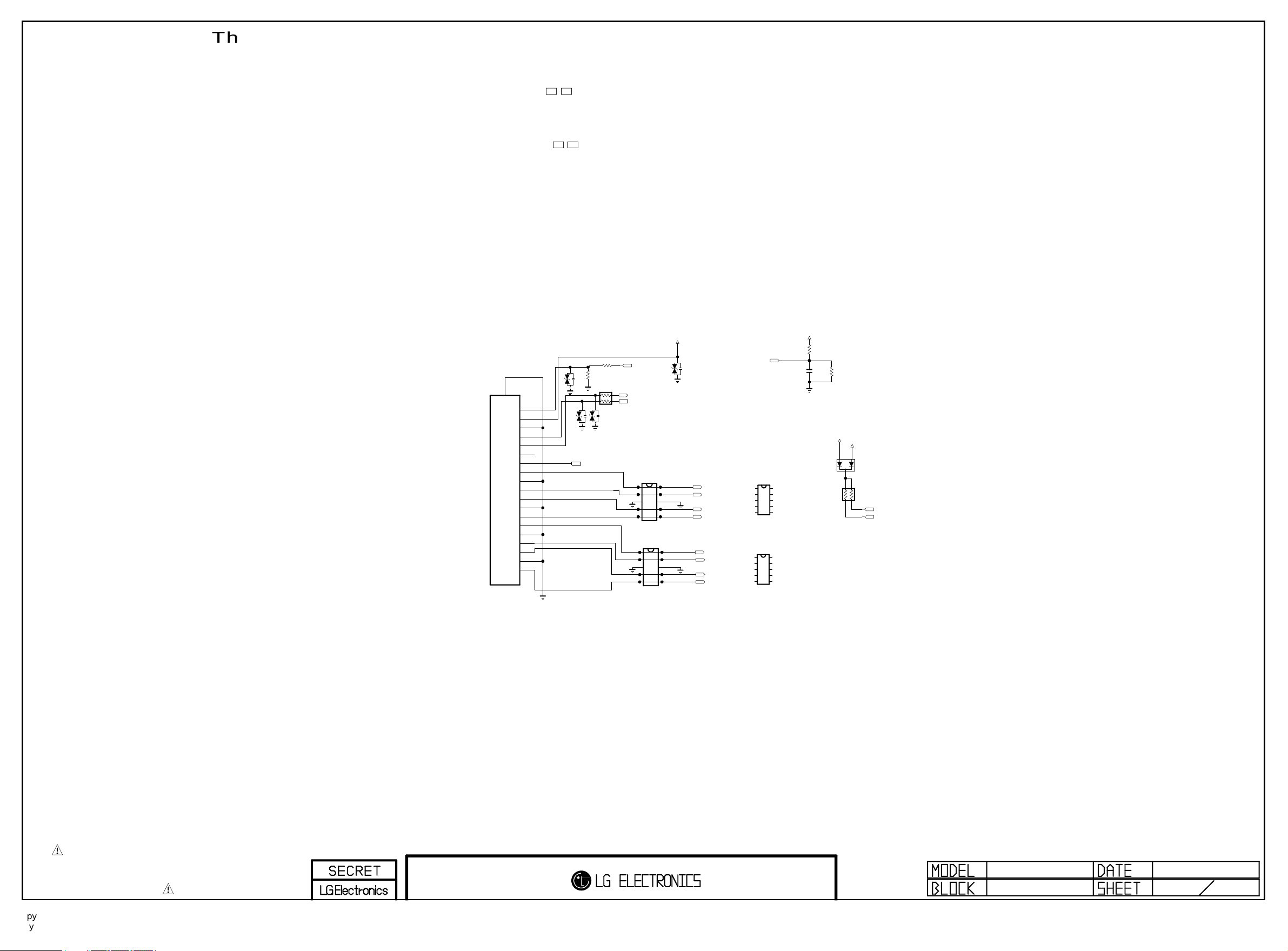

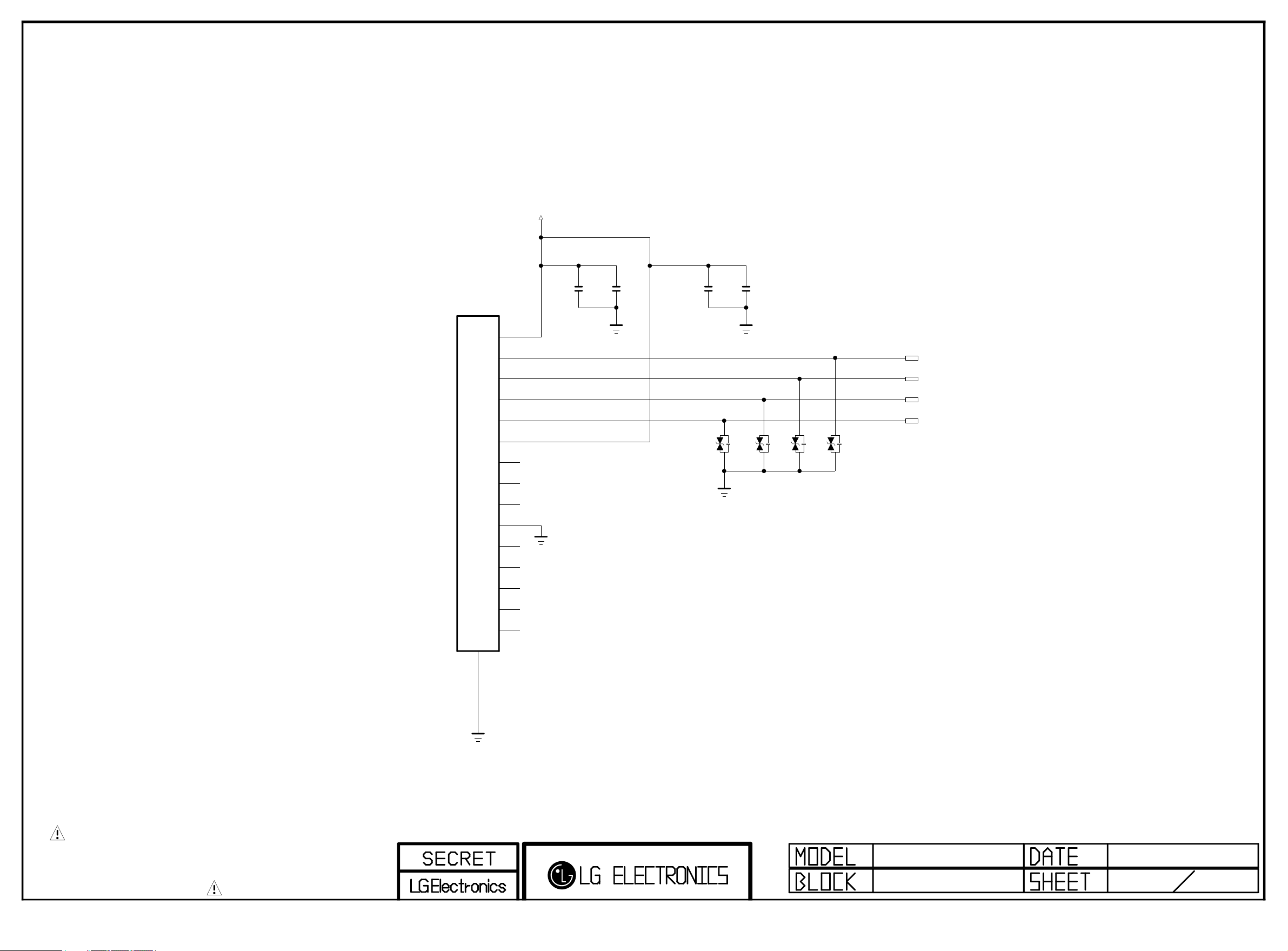

Place JACK Side

AV1_CVBS/COMP1_Y Circuit was moved to 34Page

COMP1_Pb

COMP1_Pr

TU_CVBS

COMP1/AV1/DVI_L_IN

COMP1/AV1/DVI_R_IN

C303

150pF

50V

OPT

1005

75

1%

R318

1005

1%

75

R326

Place SOC Side

33

R333

R335 33

TU_ALL_2178B

R329 100

AUDIO IN

R309 27K

R310 27K

C316 4.7uF

1%

C317 4.7uF

1%

C322 0.047uF

C324 0.047uF

C318 0.047uF

R322 10K

1%

R323 10K

1%

TU_ALL_2178B

COMP2_PB_IN_SOC

COMP2_PR_IN_SOC

TU_CVBS_SOC

AUAD_L_CH3_IN

AUAD_R_CH3_IN

COMP

TP308

TP310

TP311

TP312

TP313

TP314

TP315

TP316

TP317

TP302

TP303

TP304

TP305

TP306

TP307

SC_CVBS_IN_SOC

SC_FB_SOC

SC_ID_SOC

COMP1_PB_IN_SOC

COMP1_Y_IN_SOC

COMP1_Y_IN_SOC_SOY

COMP1_PR_IN_SOC

AUAD_L_CH2_IN

AUAD_R_CH2_IN

SMARTCARD_DATA/SD_EMMC_CLK

SMARTCARD_VCC/SD_EMMC_CMD

SMARTCARD_DET/SD_EMMC_DATA[3]

SMARTCARD_RST/SD_EMMC_DATA[2]

SMARTCARD_PWR_SEL/SD_EMMC_DATA[1]

SMARTCARD_CLK/SD_EMMC_DATA[0]

TP318

TP319

TP320

Placed as close as possible to LG1311

Tuner IF Filter

C331

22pF

TU_ALL_IntDemod

C332

0.01uF

C333

0.01uF

TU_ALL_IntDemod

TU_ALL_IntDemod

ADC_I_INN

To ADC

ADC_I_INP

C331 option

- TU_IntDemod_IF_22p -> EU/AJ All_IndDemod, US/KR/BR/TW/CO 2tuner All

- TU_IntDemod_IF_15p -> US/KR/BR/TW/CO 1tuner All

R344

R345

TU_ALL_IntDemod

51

TU_IntDemod_IF_22p

51

Placed as close as possible to IC101

R37 4

51K

AUAD_L_REF

1%

R37 8

47K

1%

C313

4.7uF

10V

R38 0

51K

1%

AUAD_R_REF

R38 1

47K

1%

DDR3 VENDOR OPTION

+3.3V_NORMAL

SCART_LOUT_SOC

SCART_ROUT_SOC

DTV/MNT_V_OUT_SOC

TU_IntDemod_IF_15p

C331-*1

15pF

50V

IF_N

L303

OPT

IF_P

AVDD25

L307

120-ohm

C354

10uF

10V

C353

4.7uF

10V

SOC_CVBS_OUT

SCART_LOUT_SOC

SCART_ROUT_SOC

TUNER_SIF

IF_AGC

AUD_MASTER_CLK

AUD_LRCH

AUD_SCK

AUD_LRCK

MAIN I2S_I/F

OPT

INT_ADEMOD

R11022

390

INT_ADEMOD

DTV/MNT_V_OUT_SOC

AVDD25

EU

C334

0.01uF

50V

C335

22pF

OPT

TU_ALL_2178B

C312 0.1uF

C309

1000pF

50V

C338

0.1uF

OPT

Close to IC101

INT_ADEMOD

R11023

390

INT_ADEMOD

C11009

68pF

50V

OPT

EU

C336

0.01uF

EU

50V

R351 22K

SPDIF_OUT

C337

33pF

OPT

TU_ALL_IntDemod

R350

470

SOC_CVBS_OUT

C11010

68pF

50V

R356

R353 0

C339

100pF

50V

COMP1_Y_IN_SOC_SOY

COMP2_Y_IN_SOC_SOY

R357 68

R358 68

R359 68

BLM15BD121SN1

R354 0

R355 0

EU

AUAD_L_CH2_IN

AUAD_R_CH2_IN

R352 22K

AUAD_L_CH3_IN

AUAD_R_CH3_IN

C340

22pF

OPT

I2S_AMP

ADC_I_INP

ADC_I_INN

C11011

TU_CVBS_SOC

SC_CVBS_IN_SOC

AV1_CVBS_IN_SOC

C343 0.047uF

68

EU

SC_ID_SOC

SC_FB_SOC

COMP1_Y_IN_SOC

COMP1_PB_IN_SOC

COMP1_PR_IN_SOC

COMP2_Y_IN_SOC

COMP2_PB_IN_SOC

COMP2_PR_IN_SOC

L304

BLM15BD121SN1

EU

EU

AUDA_OUTL

AUDA_OUTR

AUAD_R_REF

AUAD_L_REF

R360 33

R365 100

R366 100

C342

22pF

OPT

R368 100

R369

GOOGLE

R367 0

INT_ADEMOD

0.1uF

16V

0.047uF

C344

C345 0.047uF

C346 0.047uF

C349

0.1uF

L305

16V

10uF 10VC347

C348 2.2uF

10V

100

GOOGLE

R371 0

C351 0.1uF

C352 0.1uF

GOOGLE

R370 0

AL27

AK26

AM27

AL26

AN27

AL25

AM25

AN23

AL22

AK21

AK22

AL24

AK23

AL23

AK24

AL21

AM23

AN25

AM21

AN21

AK16

AL16

AL19

AK19

AN19

AM19

AN17

AM17

AL17

AK17

AK20

AL20

AK18

AL18

AN15

AM15

AN11

AK11

AK10

AL10

AL11

AM11

AK29

AL29

AM29

AK27

AL30

AK28

AL28

AN29

AD5

AE5

AE7

AE6

AD6

IC101

LG1311

CVBS_IN1

CVBS_IN2

CVBS_IN3

CVBS_VCM

BUF_OUT1

SC1_SID

SC1_FB

SOY1_IN

Y1_IN

PB1_IN

PR1_IN

SOY2_IN

Y2_IN

PB2_IN

PR2_IN

ADC1_COM

ADC2_COM

ADC3_COM

AVSS25_COMP_REF

AVDD25_COMP_REF

AUDA_SCART_OUTL

AUDA_SCART_OUTR

AUAD_L_CH1_IN

AUAD_R_CH1_IN

AUAD_L_CH2_IN

AUAD_R_CH2_IN

AUAD_L_CH3_IN

AUAD_R_CH3_IN

AUAD_L_CH4_IN

AUAD_R_CH4_IN

AUDA_OUTL

AUDA_OUTR

AUAD_L_REF

AUAD_R_REF

AUD_VBG_EXT

IEC958OUT

AUDCLK_OUT

DAC_LRCH

DAC_SLRCH

DAC_CLFCH

DAC_SCK

DAC_LRCK

PCMI3LRCH

PCMI3LRCK

PCMI3SCK

AUDCLK_IN

FRC_LRSYNC

AAD_ADC_SIF

AAD_ADC_SIFM

IFAGC

DMD_DAC_OUT

DMD_SIF_OUT

DMD_ADC_INP

DMD_ADC_INN

DMD_ADC_INCOM

SD_CLK

SD_CMD

SD_CD_N

SD_WP_N

SD_DATA3

SD_DATA2

SD_DATA1

SD_DATA0

RMII_REF_CLK

RMII_CRS_DV

RMII_MDIO

RMII_MDC

RMII_TXEN

RMII_TXD1

RMII_TXD0

RMII_RXD1

RMII_RXD0

HDMI_1_SCL

HDMI_1_SDA

HDMI_1_HPD

HDMI_1_5V_DET

HDMI_1_ARC

HDMI_1_RX_0

HDMI_1_RX_0B

HDMI_1_RX_1

HDMI_1_RX_1B

HDMI_1_RX_2

HDMI_1_RX_2B

HDMI_1_RX_C

HDMI_1_RX_CB

HDMI_2_SCL

HDMI_2_SDA

HDMI_2_HPD

HDMI_2_5V_DET

HDMI_2_RX_0

HDMI_2_RX_0B

HDMI_2_RX_1

HDMI_2_RX_1B

HDMI_2_RX_2

HDMI_2_RX_2B

HDMI_2_RX_C

HDMI_2_RX_CB

HDMI_3_SCL

HDMI_3_SDA

HDMI_3_HPD

HDMI_3_5V_DET

HDMI_3_RX_0

HDMI_3_RX_0B

HDMI_3_RX_1

HDMI_3_RX_1B

HDMI_3_RX_2

HDMI_3_RX_2B

HDMI_3_RX_C

HDMI_3_RX_CB

HDMI_4_SCL

HDMI_4_SDA

HDMI_4_CBUS_HPD

HDMI_4_CD_SENSE

HDMI_4_5V_DET

HDMI_4_RX_0

HDMI_4_RX_0B

HDMI_4_RX_1

HDMI_4_RX_1B

HDMI_4_RX_2

HDMI_4_RX_2B

HDMI_4_RX_C

HDMI_4_RX_CB

E22

D22

F22

F24

D24

E24

F23

E23

AK14

AK12

AL12

AK13

AL13

AM13

AN13

AL14

AK15

AE27

AF28

AE29

AF27

AE28

AF33

AF32

AE31

AE30

AD31

AD30

AF31

AF30

AD28

AD29

AC27

AD27

AC31

AC30

AB33

AB32

AA31

AA30

AD32

AD33

AB28

AB27

AB29

AC28

Y32

Y33

W31

W30

V33

V32

Y31

Y30

Y27

AA28

Y28

AA29

AA27

T31

T30

T32

T33

R31

R30

U31

U30

PAGE 3

SMARTCARD_CLK/SD_EMMC_DATA[0]

SMARTCARD_RST/SD_EMMC_DATA[2]

SMARTCARD_VCC/SD_EMMC_CMD

SMARTCARD_PWR_SEL/SD_EMMC_DATA[1]

DDR3_OPT1

DDR3_OPT2

SMARTCARD_DET/SD_EMMC_DATA[3]

SMARTCARD_DATA/SD_EMMC_CLK

EPHY_REFCLK

EPHY_CRS_DV

EPHY_MDIO

EPHY_MDC

EPHY_EN

EPHY_TXD1

EPHY_TXD0

R520733

EPHY_RXD1

R520633

EPHY_RXD0

DDC_SCL_1

DDC_SDA_1

HDMI_HPD_1

SPDIF_OUT_ARC

D0+_HDMI1

D0-_HDMI1

D1+_HDMI1

D1-_HDMI1

D2+_HDMI1

D2-_HDMI1

CK+_HDMI1

CK-_HDMI1

DDC_SCL_2

DDC_SDA_2

HDMI_HPD_2

D0+_HDMI2

D0-_HDMI2

D1+_HDMI2

D1-_HDMI2

D2+_HDMI2

D2-_HDMI2

CK+_HDMI2

CK-_HDMI2

DDC_SCL_3

DDC_SDA_3

HDMI_HPD_3

5V_HDMI_3_SOC

D0+_HDMI3

D0-_HDMI3

D1+_HDMI3

D1-_HDMI3

D2+_HDMI3

D2-_HDMI3

CK+_HDMI3

CK-_HDMI3

DDC_SCL_4

DDC_SDA_4

HDMI_HPD_4

MHL_DET

D0+_HDMI4

D0-_HDMI4

D1+_HDMI4

D1-_HDMI4

D2+_HDMI4

D2-_HDMI4

CK+_HDMI4

CK-_HDMI4

5V_HDMI_1

R372

10

C356

1uF

10V

5V_HDMI_2

R373

10

C357

1uF

10V

5V_HDMI_4

R375

10

C359

1uF

10V

R376

5.1K

R377

5.1K

R379

5.1K

HP_OUT

L308

BLM18PG121SN1D

HP_LOUT_AMP

BLM18PG121SN1D

HP_ROUT_AMP

HP_OUT

L309

HP_OUT

C365

0.22uF

10V

HP_OUT

C366

0.22uF

10V

HP_LOUT

HP_ROUT

Place at JACK SIDE

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FIRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFACTURES SPECIFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

M14-AV In/Out

HP_LOUT_MAIN

HP_ROUT_MAIN

4.7K

4.7K

R384

R382

OPT

OPT

R383 4.7K

R385 4.7K

AUDIO OUT

R303

22K

R304

22K

R311 0

C305

0.01uF

50V

R312 0

C306

0.01uF

50V

DDR3_OPT1

DDR3_OPT2

AUDA_OUTL

AUDA_OUTR

DDC_SCL_3

DDC_SDA_3

HDMI_HPD_3

5V_HDMI_3_SOC

D0+_HDMI3

D0-_HDMI3

D1+_HDMI3

D1-_HDMI3

D2+_HDMI3

D2-_HDMI3

CK+_HDMI3

CK-_HDMI3

MID_LG1311

M14 Symbol C

TP321

TP322

TP323

TP324

TP325

TP326

TP327

TP328

TP329

TP330

TP331

TP332

2013.04.04

3

31

PAGE 4

Copyright ⓒ 2014 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LGE Internal Use Only

IC101

LG1311

M0_DDR_U_CLKP

M0_DDR_U_CLKN

M0_DDR_D_CLKP

M0_DDR_D_CLKN

M0_DDR_RESET_N

M0_DDR_DQS_P0

M0_DDR_DQS_N0

M0_DDR_DQS_P1

M0_DDR_DQS_N1

M0_DDR_DQS_P2

M0_DDR_DQS_N2

M0_DDR_DQS_P3

M0_DDR_DQS_N3

M0_DDR_VREF1

M0_DDR_VREF2

M0_DDR_A0

M0_DDR_A1

M0_DDR_A2

M0_DDR_A3

M0_DDR_A4

M0_DDR_A5

M0_DDR_A6

M0_DDR_A7

M0_DDR_A8

M0_DDR_A9

M0_DDR_A10

M0_DDR_A11

M0_DDR_A12

M0_DDR_A13

M0_DDR_A14

M0_DDR_A15

M0_DDR_BA0

M0_DDR_BA1

M0_DDR_BA2

M0_DDR_CKE

M0_DDR_ODT

M0_DDR_RASN

M0_DDR_CASN

M0_DDR_WEN

M0_DDR_DM0

M0_DDR_DM1

M0_DDR_DM2

M0_DDR_DM3

M0_DDR_DQ0

M0_DDR_DQ1

M0_DDR_DQ2

M0_DDR_DQ3

M0_DDR_DQ4

M0_DDR_DQ5

M0_DDR_DQ6

M0_DDR_DQ7

M0_DDR_DQ8

M0_DDR_DQ9

M0_DDR_DQ10

M0_DDR_DQ11

M0_DDR_DQ12

M0_DDR_DQ13

M0_DDR_DQ14

M0_DDR_DQ15

M0_DDR_DQ16

M0_DDR_DQ17

M0_DDR_DQ18

M0_DDR_DQ19

M0_DDR_DQ20

M0_DDR_DQ21

M0_DDR_DQ22

M0_DDR_DQ23

M0_DDR_DQ24

M0_DDR_DQ25

M0_DDR_DQ26

M0_DDR_DQ27

M0_DDR_DQ28

M0_DDR_DQ29

M0_DDR_DQ30

M0_DDR_DQ31

M0_DDR_ZQCAL

VREF_M0_0

A22

A3

E13

E11

E15

E17

D8

D16

D9

E16

E9

E14

D7

D10

D11

D14

E10

E12

D17

E8

D13

C8

B8

C17

B17

D12

E19

D19

D18

E18

D15

B18

C18

B16

A16

B9

C9

B7

A7

A15

A18

A6

A9

B20

B13

C21

C14

A21

A13

B21

C13

B14

B19

C15

C20

C16

A19

B15

C19

B11

C5

C12

B4

A12

A4

B12

C4

B5

B10

C6

C11

C7

A10

B6

C10

E7

VREF_M0_1

R401 240

M0_DDR_A0

M0_DDR_A1

M0_DDR_A2

M0_DDR_A3

M0_DDR_A4

M0_DDR_A5

M0_DDR_A6

M0_DDR_A7

M0_DDR_A8

M0_DDR_A9

M0_DDR_A10

M0_DDR_A11

M0_DDR_A12

M0_DDR_A13

M0_DDR_A14

M0_DDR_A15

M0_DDR_BA0

M0_DDR_BA1

M0_DDR_BA2

M0_U_CLK

M0_U_CLKN

M0_D_CLK

M0_DDR_CKE

M0_DDR_ODT

M0_DDR_RASN

M0_DDR_CASN

M0_DDR_WEN

M0_DDR_RESET_N

M0_DDR_DQS0

M0_DDR_DQS_N0

M0_DDR_DQS1

M0_DDR_DQS_N1

M0_DDR_DQS2

M0_DDR_DQS_N2

M0_DDR_DQS3

M0_DDR_DQS_N3

M0_DDR_DM0

M0_DDR_DM1

M0_DDR_DM2

M0_DDR_DM3

M0_DDR_DQ0

M0_DDR_DQ1

M0_DDR_DQ2

M0_DDR_DQ3

M0_DDR_DQ4

M0_DDR_DQ5

M0_DDR_DQ6

M0_DDR_DQ7

M0_DDR_DQ8

M0_DDR_DQ9

M0_DDR_DQ10

M0_DDR_DQ11

M0_DDR_DQ12

M0_DDR_DQ13

M0_DDR_DQ14

M0_DDR_DQ15

M0_DDR_DQ16

M0_DDR_DQ17

M0_DDR_DQ18

M0_DDR_DQ19

M0_DDR_DQ20

M0_DDR_DQ21

M0_DDR_DQ22

M0_DDR_DQ23

M0_DDR_DQ24

M0_DDR_DQ25

M0_DDR_DQ26

M0_DDR_DQ27

M0_DDR_DQ28

M0_DDR_DQ29

M0_DDR_DQ30

M0_DDR_DQ31

1%

+1.5V_DDR

R402

R403

+1.5V_DDR

OPT

+1.5V_DDR

R406

R407

+1.5V_DDR

R408

R409

VREF_M0_0

1K 1%

1K 1%

C401

R404

10K

100

R40 5

M0_DDR_VREFCA

1K 1%

C402

0.1uF

1K 1%

M0_DDR_VREFDQ

1K 1%

0.1uF

1K 1%

C403

0.1uF

M0_DDR_CKE

M0_DDR_RESET_N

M0_D_CLK

M0_D_CLKN

+1.5V_DDR

+1.5V_DDR

R411

R412

+1.5V_DDR

R413

R414

VREF_M0_1

R415

1K 1%

R416

1K 1%

R417

10K

M0_U_CLK

100

R41 0

M0_U_CLKN

M0_1_DDR_VREFCA

1K 1%

C406

0.1uF

1K 1%

M0_1_DDR_VREFDQ

1K 1%

0.1uF

1K 1%

C407

C408

0.1uF

M0_DDR_A0

M0_DDR_A1

M0_DDR_A2

M0_DDR_A3

M0_DDR_A4

M0_DDR_A5

M0_DDR_A6

M0_DDR_A7

M0_DDR_A8

M0_DDR_A9

M0_DDR_A10

M0_DDR_A11

M0_DDR_A12

M0_DDR_A13

M0_DDR_A14

M0_DDR_A15

M0_DDR_BA0

M0_DDR_BA1

M0_DDR_BA2

M0_D_CLK

M0_D_CLKN

M0_DDR_CKE

M0_DDR_ODT

M0_DDR_RASN

M0_DDR_CASN

M0_DDR_WEN

M0_DDR_RESET_N

M0_DDR_DQS0

M0_DDR_DQS_N0

M0_DDR_DQS1

M0_DDR_DQS_N1

M0_DDR_DM0

M0_DDR_DM1

M0_DDR_DQ0

M0_DDR_DQ1

M0_DDR_DQ2

M0_DDR_DQ3

M0_DDR_DQ4

M0_DDR_DQ5

M0_DDR_DQ6

M0_DDR_DQ7

M0_DDR_DQ8

M0_DDR_DQ9

M0_DDR_DQ10

M0_DDR_DQ11

M0_DDR_DQ12

M0_DDR_DQ13

M0_DDR_DQ14

M0_DDR_DQ15

IC401

H5TQ4G63AFR-PBC

DDR3

N3

P7

P3

N2

P8

P2

R8

R2

T8

R3

L7

R7

N7

T3

T7

M7

M2

N8

M3

J7

K7

K9

L2

K1

J3

K3

L3

T2

F3

G3

C7

B7

E7

D3

E3

F7

F2

F8

H3

H8

G2

H7

D7

C3

C8

C2

A7

A2

B8

A3

4Gbit

A0

(x16)

A1

DDR_512MB_HYNIX_1600_29n

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC

A13

A14

A15

BA0

BA1

BA2

CK

CK

CKE

CS

ODT

RAS

CAS

WE

RESET

DQSL

DQSL

DQSU

DQSU

DML

DMU

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

VREFCA

VREFDQ

VDD_1

VDD_2

VDD_3

VDD_4

VDD_5

VDD_6

VDD_7

VDD_8

VDD_9

VDDQ_1

VDDQ_2

VDDQ_3

VDDQ_4

VDDQ_5

VDDQ_6

VDDQ_7

VDDQ_8

VDDQ_9

NC_1

NC_2

NC_3

NC_4

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSSQ_1

VSSQ_2

VSSQ_3

VSSQ_4

VSSQ_5

VSSQ_6

VSSQ_7

VSSQ_8

VSSQ_9

ZQ

M0_DDR_VREFCA

M0_DDR_VREFDQ

M8

H1

R418

L8

240

1%

B2

D9

G7

K2

K8

N1

N9

R1

R9

A1

A8

C1

C9

D2

E9

F1

H2

H9

J1

J9

L1

L9

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

+1.5V_DDR

IC401-*1

MT41K256M16HA-125:E

DDR_512MB_MICRON

N3

A0

VREFCA

P7

A1

P3

A2

N2

A3

VREFDQ

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

VDD_1

A9

L7

VDD_2

A10/AP

R7

VDD_3

A11

N7

VDD_4

A12/BC

T3

A13

VDD_5

VDD_6

M7

NC_5

VDD_7

VDD_8

M2

BA0

VDD_9

N8

BA1

M3

BA2

VDDQ_1

J7

CK

VDDQ_2

K7

CK

VDDQ_3

K9

CKE

VDDQ_4

VDDQ_5

L2

CS

VDDQ_6

K1

ODT

VDDQ_7

J3

RAS

VDDQ_8

K3

CAS

VDDQ_9

L3

WE

NC_1

T2

RESET

NC_2

NC_3

NC_4

F3

DQSL

G3

DQSL

C7

DQSU

VSS_1

B7

DQSU

VSS_2

VSS_3

E7

DML

VSS_4

D3

DMU

VSS_5

VSS_6

E3

DQ0

VSS_7

F7

DQ1

VSS_8

F2

DQ2

VSS_9

F8

DQ3

VSS_10

H3

DQ4

VSS_11

H8

DQ5

VSS_12

G2

DQ6

H7

DQ7

VSSQ_1

D7

DQ8

VSSQ_2

C3

DQ9

VSSQ_3

C8

DQ10

VSSQ_4

C2

DQ11

VSSQ_5

A7

DQ12

VSSQ_6

A2

DQ13

VSSQ_7

B8

DQ14

VSSQ_8

A3

DQ15

VSSQ_9

C413 1uF

C414 1uF

M8

H1

L8

ZQ

B2

D9

G7

K2

K8

N1

N9

R1

R9

A1

A8

C1

C9

D2

E9

F1

H2

H9

J1

J9

L1

L9

T7

A14

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

M0_DDR_A0

M0_DDR_A1

M0_DDR_A2

M0_DDR_A3

M0_DDR_A4

M0_DDR_A5

M0_DDR_A6

M0_DDR_A7

M0_DDR_A8

M0_DDR_A9

M0_DDR_A10

M0_DDR_A11

M0_DDR_A12

M0_DDR_A13

M0_DDR_A14

M0_DDR_A15

M0_DDR_BA0M0_D_CLKN

M0_DDR_BA1

M0_DDR_BA2

M0_U_CLK

M0_U_CLKN

M0_DDR_CKE

M0_DDR_ODT

M0_DDR_RASN

M0_DDR_CASN

M0_DDR_WEN

M0_DDR_RESET_N

M0_DDR_DQS2

M0_DDR_DQS_N2

M0_DDR_DQS3

M0_DDR_DQS_N3

M0_DDR_DM2

M0_DDR_DM3

M0_DDR_DQ16

M0_DDR_DQ17

M0_DDR_DQ18

M0_DDR_DQ19

M0_DDR_DQ20

M0_DDR_DQ21

M0_DDR_DQ22

M0_DDR_DQ23

M0_DDR_DQ24

M0_DDR_DQ25

M0_DDR_DQ26

M0_DDR_DQ27

M0_DDR_DQ28

M0_DDR_DQ29

M0_DDR_DQ30

M0_DDR_DQ31

MT41K256M16HA-125:E

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12/BC

T3

A13

M7

NC_5

M2

BA0

N8

BA1

M3

BA2

J7

CK

K7

CK

K9

CKE

L2

CS

K1

ODT

J3

RAS

K3

CAS

L3

WE

T2

RESET

F3

DQSL

G3

DQSL

C7

DQSU

B7

DQSU

E7

DML

D3

DMU

E3

DQ0

F7

DQ1

F2

DQ2

F8

DQ3

H3

DQ4

H8

DQ5

G2

DQ6

H7

DQ7

D7

DQ8

C3

DQ9

C8

DQ10

C2

DQ11

A7

DQ12

A2

DQ13

B8

DQ14

A3

DQ15

IC402-*1

DDR_512MB_MICRON

IC402

H5TQ4G63AFR-PBC

DDR3

N3

4Gbit

A0

P7

(x16)

A1

P3

DDR_512MB_HYNIX_1600_29n

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12/BC

T3

A13

T7

A14

M7

A15

M2

BA0

N8

BA1

M3

BA2

J7

CK

K7

CK

K9

CKE

L2

CS

K1

ODT

J3

RAS

K3

CAS

L3

WE

T2

RESET

F3

DQSL

G3

DQSL

C7

DQSU

B7

DQSU

E7

DML

D3

DMU

E3

DQL0

F7

DQL1

F2

DQL2

F8

DQL3

H3

DQL4

H8

DQL5

G2

DQL6

H7

DQL7

D7

DQU0

C3

DQU1

C8

DQU2

C2

DQU3

A7

DQU4

A2

DQU5

B8

DQU6

A3

DQU7

M8

VREFCA

H1

VREFDQ

L8

ZQ

B2

VDD_1

D9

VDD_2

G7

VDD_3

K2

VDD_4

K8

VDD_5

N1

VDD_6

N9

VDD_7

R1

VDD_8

R9

VDD_9

A1

VDDQ_1

A8

VDDQ_2

C1

VDDQ_3

C9

VDDQ_4

D2

VDDQ_5

E9

VDDQ_6

F1

VDDQ_7

H2

VDDQ_8

H9

VDDQ_9

J1

NC_1

J9

NC_2

L1

NC_3

L9

NC_4

T7

A14

A9

VSS_1

B3

VSS_2

E1

VSS_3

G8

VSS_4

J2

VSS_5

J8

VSS_6

M1

VSS_7

M9

VSS_8

P1

VSS_9

P9

VSS_10

T1

VSS_11

T9

VSS_12

B1

VSSQ_1

B9

VSSQ_2

D1

VSSQ_3

D8

VSSQ_4

E2

VSSQ_5

E8

VSSQ_6

F9

VSSQ_7

G1

VSSQ_8

G9

VSSQ_9

M0_1_DDR_VREFCA

VREFCA

VREFDQ

ZQ

VDD_1

VDD_2

VDD_3

VDD_4

VDD_5

VDD_6

VDD_7

VDD_8

VDD_9

VDDQ_1

VDDQ_2

VDDQ_3

VDDQ_4

VDDQ_5

VDDQ_6

VDDQ_7

VDDQ_8

VDDQ_9

NC_1

NC_2

NC_3

NC_4

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSSQ_1

VSSQ_2

VSSQ_3

VSSQ_4

VSSQ_5

VSSQ_6

VSSQ_7

VSSQ_8

VSSQ_9

M8

H1

L8

B2

D9

G7

K2

K8

N1

N9

R1

R9

A1

A8

C1

C9

D2

E9

F1

H2

H9

J1

J9

L1

L9

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

M0_1_DDR_VREFDQ

+1.5V_DDR

R419

240

1%

C429

C430

1uF

1uF

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FIRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFACTURES SPECIFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

MID_LG1311

M14 DDR3-M0

2013.04.04

4

31

PAGE 5

Copyright ⓒ 2014 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LGE Internal Use Only

IC101

LG1311

M1_DDR_VREF1

M1_DDR_VREF2

M1_DDR_U_CLKP

M1_DDR_U_CLKN

M1_DDR_D_CLKP

M1_DDR_D_CLKN

M1_DDR_RESET_N

M1_DDR_DQS_P0

M1_DDR_DQS_N0

M1_DDR_DQS_P1

M1_DDR_DQS_N1

M1_DDR_DQS_P2

M1_DDR_DQS_N2

M1_DDR_DQS_P3

M1_DDR_DQS_N3

M1_DDR_ZQCAL

M1_DDR_A0

M1_DDR_A1

M1_DDR_A2

M1_DDR_A3

M1_DDR_A4

M1_DDR_A5

M1_DDR_A6

M1_DDR_A7

M1_DDR_A8

M1_DDR_A9

M1_DDR_A10

M1_DDR_A11

M1_DDR_A12

M1_DDR_A13

M1_DDR_A14

M1_DDR_A15

M1_DDR_BA0

M1_DDR_BA1

M1_DDR_BA2

M1_DDR_CKE

M1_DDR_ODT

M1_DDR_RASN

M1_DDR_CASN

M1_DDR_WEN

M1_DDR_DM0

M1_DDR_DM1

M1_DDR_DM2

M1_DDR_DM3

M1_DDR_DQ0

M1_DDR_DQ1

M1_DDR_DQ2

M1_DDR_DQ3

M1_DDR_DQ4

M1_DDR_DQ5

M1_DDR_DQ6

M1_DDR_DQ7

M1_DDR_DQ8

M1_DDR_DQ9

M1_DDR_DQ10

M1_DDR_DQ11

M1_DDR_DQ12

M1_DDR_DQ13

M1_DDR_DQ14

M1_DDR_DQ15

M1_DDR_DQ16

M1_DDR_DQ17

M1_DDR_DQ18

M1_DDR_DQ19

M1_DDR_DQ20

M1_DDR_DQ21

M1_DDR_DQ22

M1_DDR_DQ23

M1_DDR_DQ24

M1_DDR_DQ25

M1_DDR_DQ26

M1_DDR_DQ27

M1_DDR_DQ28

M1_DDR_DQ29

M1_DDR_DQ30

M1_DDR_DQ31

VREF_M1_0

A2

Y1

M5

N5

K5

H5

T4

H4

R4

J5

T5

L5

U4

P4

P5

K4

R5

N4

G4

U5

L4

R3

R2

F3

F2

M4

F5

E4

F4

G5

J4

E2

E3

G2

G1

P2

P3

T2

T1

H1

E1

U1

P1

C2

K2

B3

J3

B1

K1

B2

K3

J2

D2

H3

C3

G3

D1

H2

D3

M2

V3

L3

W2

L1

W1

L2

W3

V2

N2

U3

M3

T3

N1

U2

N3

E5

R501

VREF_M1_1

M1_DDR_A0

M1_DDR_A1

M1_DDR_A2

M1_DDR_A3

M1_DDR_A4

M1_DDR_A5

M1_DDR_A6

M1_DDR_A7

M1_DDR_A8

M1_DDR_A9

M1_DDR_A10

M1_DDR_A11

M1_DDR_A12

M1_DDR_A13

M1_DDR_A14

M1_DDR_A15

M1_DDR_BA0

M1_DDR_BA1

M1_DDR_BA2

M1_U_CLK

M1_U_CLKN

M1_D_CLK

M1_D_CLKN

M1_DDR_CKE

M1_DDR_ODT

M1_DDR_RASN

M1_DDR_CASN

M1_DDR_WEN

M1_DDR_RESET_N

M1_DDR_DQS_N0

M1_DDR_DQS1

M1_DDR_DQS_N1

M1_DDR_DQS2

M1_DDR_DQS_N2

M1_DDR_DQS3

M1_DDR_DQS_N3

M1_DDR_DM0

M1_DDR_DM2

M1_DDR_DM3

M1_DDR_DQ0

M1_DDR_DQ1

M1_DDR_DQ2

M1_DDR_DQ3

M1_DDR_DQ4

M1_DDR_DQ5

M1_DDR_DQ6

M1_DDR_DQ7

M1_DDR_DQ8

M1_DDR_DQ9

M1_DDR_DQ10

M1_DDR_DQ11

M1_DDR_DQ12

M1_DDR_DQ13

M1_DDR_DQ14

M1_DDR_DQ15

M1_DDR_DQ16

M1_DDR_DQ17

M1_DDR_DQ18

M1_DDR_DQ19

M1_DDR_DQ20

M1_DDR_DQ21

M1_DDR_DQ22

M1_DDR_DQ23

M1_DDR_DQ24

M1_DDR_DQ25

M1_DDR_DQ26

M1_DDR_DQ27

M1_DDR_DQ28

M1_DDR_DQ29

M1_DDR_DQ30

M1_DDR_DQ31

240

1%

+1.5V_DDR

R508

R509

+1.5V_DDR

OPT

+1.5V_DDR

R504

R505

+1.5V_DDR

R506

R507

VREF_M1_0

1K 1%

C501

1K 1%

R502

10K

100

R50 3

M1_DDR_VREFCA

1K 1%

C502

0.1uF

1K 1%

M1_DDR_VREFDQ

1K 1%

0.1uF

1K 1%

C503

0.1uF

M1_DDR_RESET_N

M1_D_CLK

M1_D_CLKN

+1.5V_DDR

M1_DDR_CKE

+1.5V_DDR

+1.5V_DDR