LG 42LM6400-SA, 42LM6400, 32LM6200-SA, 32LM6200 Service Manual

Printed in KoreaP/NO : MFL67402918 (1204-REV00)

CHASSIS : LJ22E

MODEL : 42LM6400 42LM6400-SA

CAUTION

BEFORE SERVICING THE CHASSIS,

READ THE SAFETY PRECAUTIONS IN THIS MANUAL.

LED LCD TV

SERVICE MANUAL

North/Latin America http://aic.lgservice.com

Europe/Africa http://eic.lgservice.com

Asia/Oceania http://biz.lgservice.com

Internal Use Only

- 2 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

CONTENTS

CONTENTS .............................................................................................. 2

PRODUCT SAFETY ................................................................................. 3

SPECIFICATION ....................................................................................... 4

ADJUSTMENT INSTRUCTION .............................................................. 14

EXPLODED VIEW .................................................................................. 22

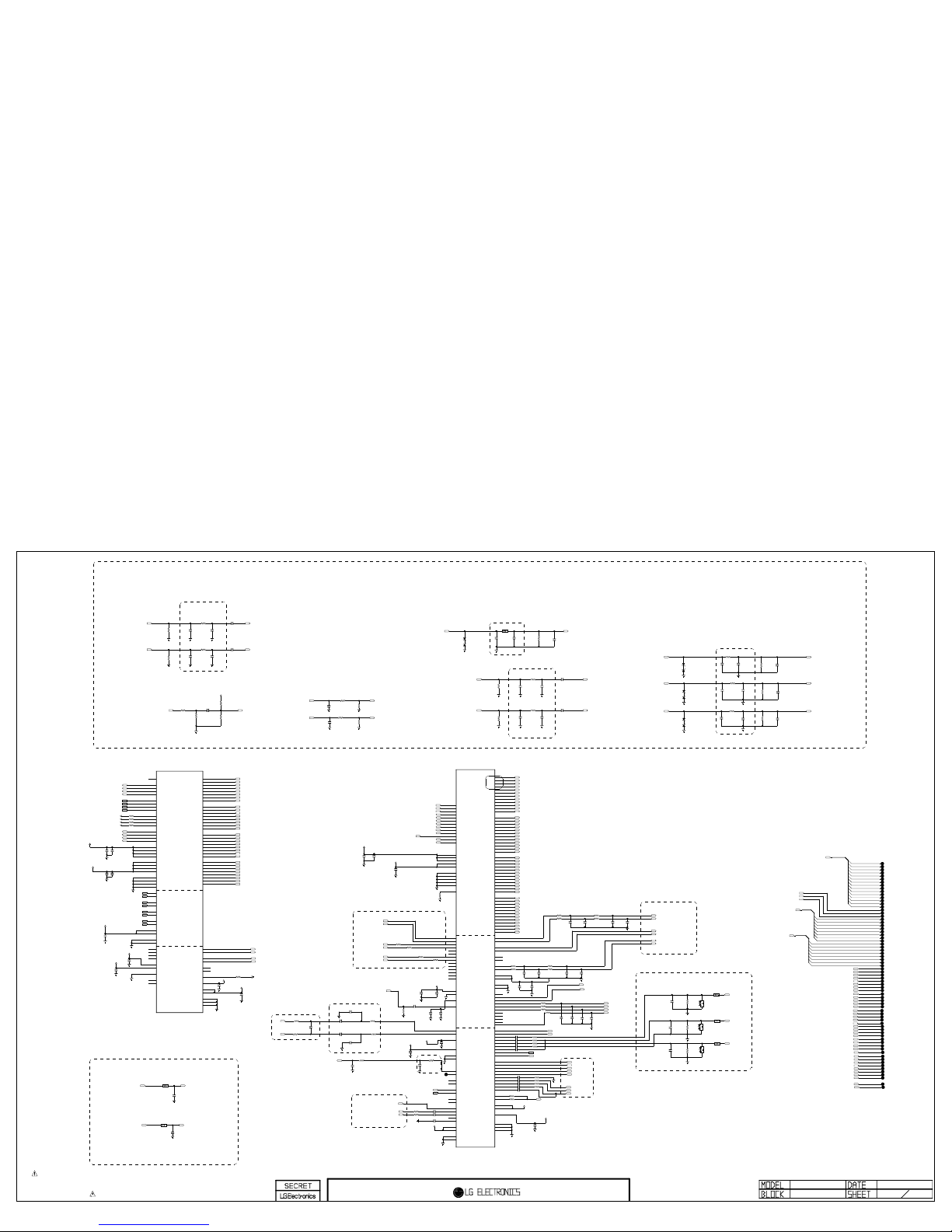

SCHEMATIC CIRCUIT DIAGRAM ..............................................................

- 3 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These parts are identified by in the

Schematic Diagram and Exploded View.

It is essential that these special safety parts should be replaced with the same components as recommended in this manual to prevent

Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

General Guidance

An isolation Transformer should always be used during the

servicing of a receiver whose chassis is not isolated from the AC

power line. Use a transformer of adequate power rating as this

protects the technician from accidents resulting in personal injury

from electrical shocks.

It will also protect the receiver and it's components from being

damaged by accidental shorts of th e cir cuitry that may be

inadvertently introduced during the service operation.

If any fuse (or Fusible Resistor) in this TV receiver is blown,

replace it with the specified.

When replacing a high wattage resistor (Oxide Metal Film Resistor,

over 1 W), keep the resistor 10 mm away from PCB.

Keep wires away from high voltage or high temperature parts.

Before returning the receiver to the customer,

always perform an AC leakage current check on the exposed

metallic parts of the cabinet, such as antennas, terminals, etc., to

be sure the set is safe to operate without damage of electrical

shock.

Leakage Current Cold Check(Antenna Cold Check)

With the instrument AC plug removed from AC source, connect an

electrical jumper across the two AC plug prongs. Place the AC

switch in the on position, connect one lead of ohm-meter to the AC

plug prongs tied together and touch other ohm-meter lead in turn to

each exposed metallic parts such as antenna terminals, phone

jacks, etc.

If the exposed metallic part has a return path to the chassis, the

measured resistance should be between 1 MΩ and 5.2 MΩ.

When the exposed metal has no return path to the chassis the

reading must be infinite.

An other abnormality exists that must be corrected before the

receiver is returned to the customer.

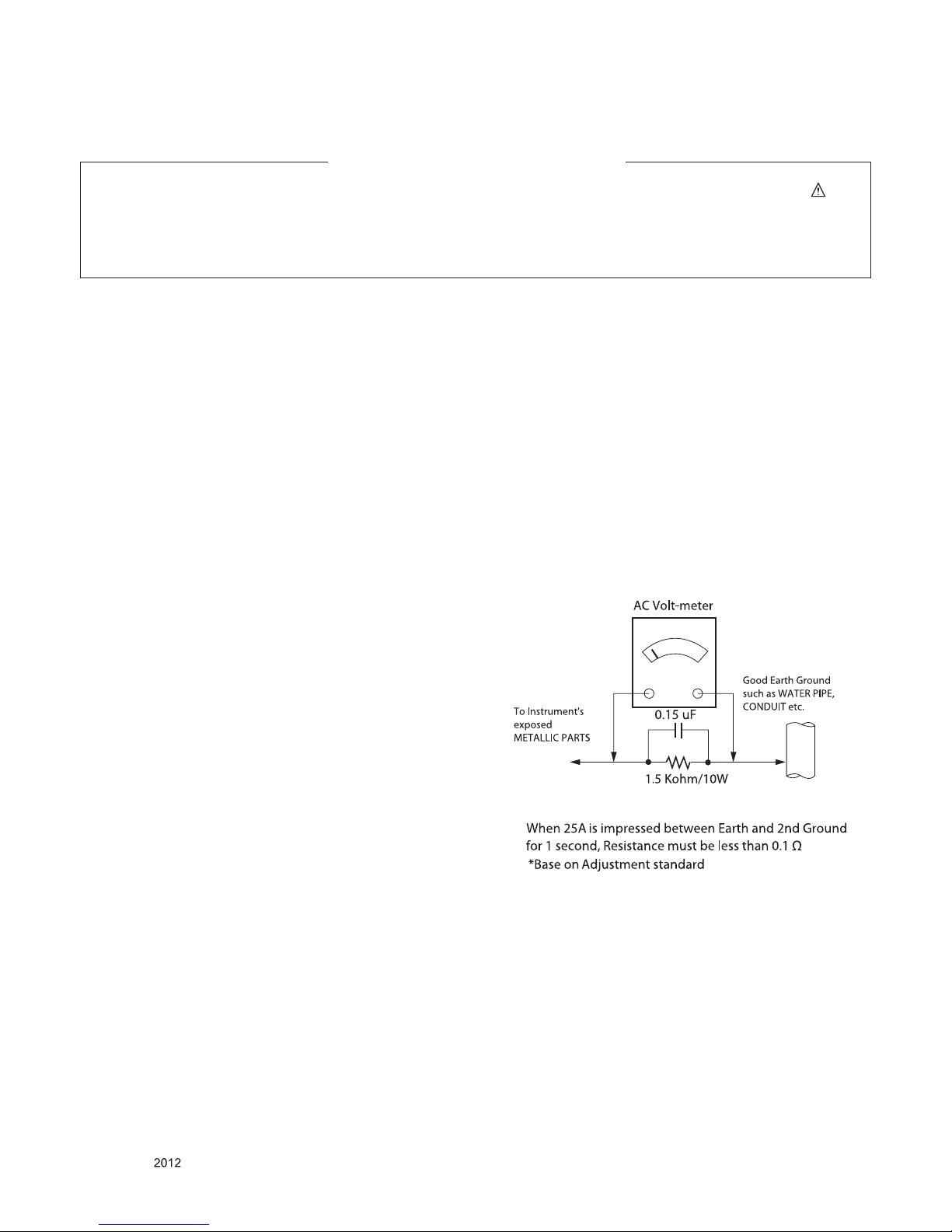

Leakage Current Hot Check (See below Figure)

Plug the AC cord directly into the AC outlet.

Do not use a line Isolation Transformer during this check.

Connect 1.5 K / 10 watt resistor in parallel with a 0.15 uF capacitor

between a known good earth ground (Water Pipe, Conduit, etc.)

and the exposed metallic parts.

Measure the AC voltage across the resistor using AC voltmeter

with 1000 ohms/volt or more sensitivity.

Reverse plug the AC cord into the AC outlet and repeat AC voltage

measurements for each exp ose d metallic par t. Any voltage

measured must not exceed 0.75 volt RMS which is corresponds to

0.5 mA.

In case any measurement is out of the limits specified, there is

possibility of shock hazard and the set must be checked and

repaired before it is returned to the customer.

Leakage Current Hot Check circuit

IMPORTANT SAFETY NOTICE

SAFETY PRECAUTIONS

- 4 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

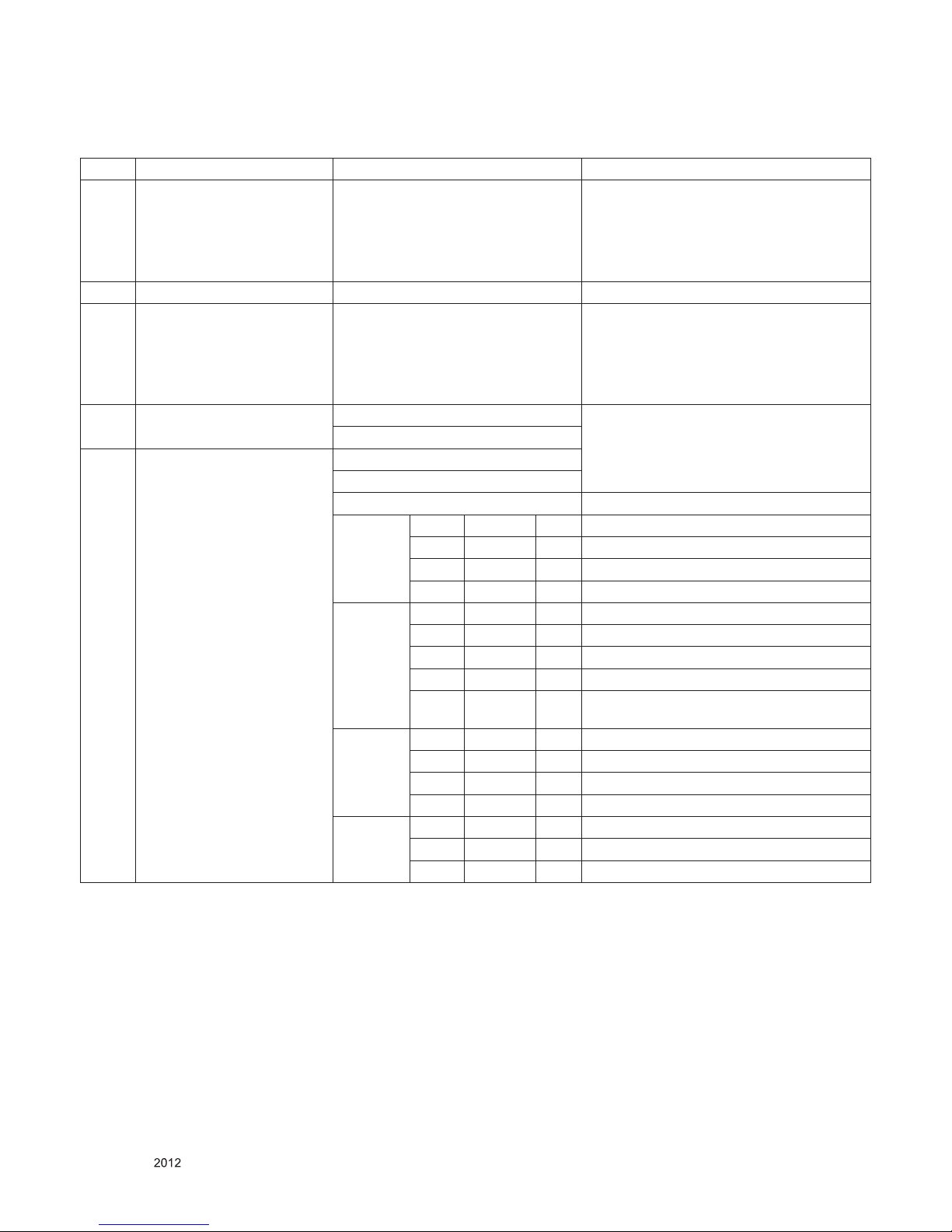

SPECIFICATION

NOTE : Specifications and others are subject to change without notice for improvement

.

1. Application range

This spec sheet is applied all of the 32”,42”,47”,55”,60”, 65”

LCD TV with LJ22E chassis.

2. Test condition

Each part is tested as below without special notice.

1) Temperature : 25 ºC ± 5 ºC (77±9 ºF), CST : 40±5 ºC

2) Relative Humidity: 65 % ± 10 %

3) Power Voltage

- AC 100-240 V~, 50/60 Hz

* Standard Voltage of each products is marked by models.

4) Specification and performance of each parts are followed

ea ch drawing and s pe cificatio n b y p art number in

accordance with BOM.

5) The receiver must be operated for about 20 minutes prior to

the adjustment.

3. Test method

1) Performance: LGE TV test method followed

2) Demanded other specification

- Safety : CE, IEC specification

- EMC : CE, IEC

- 5 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

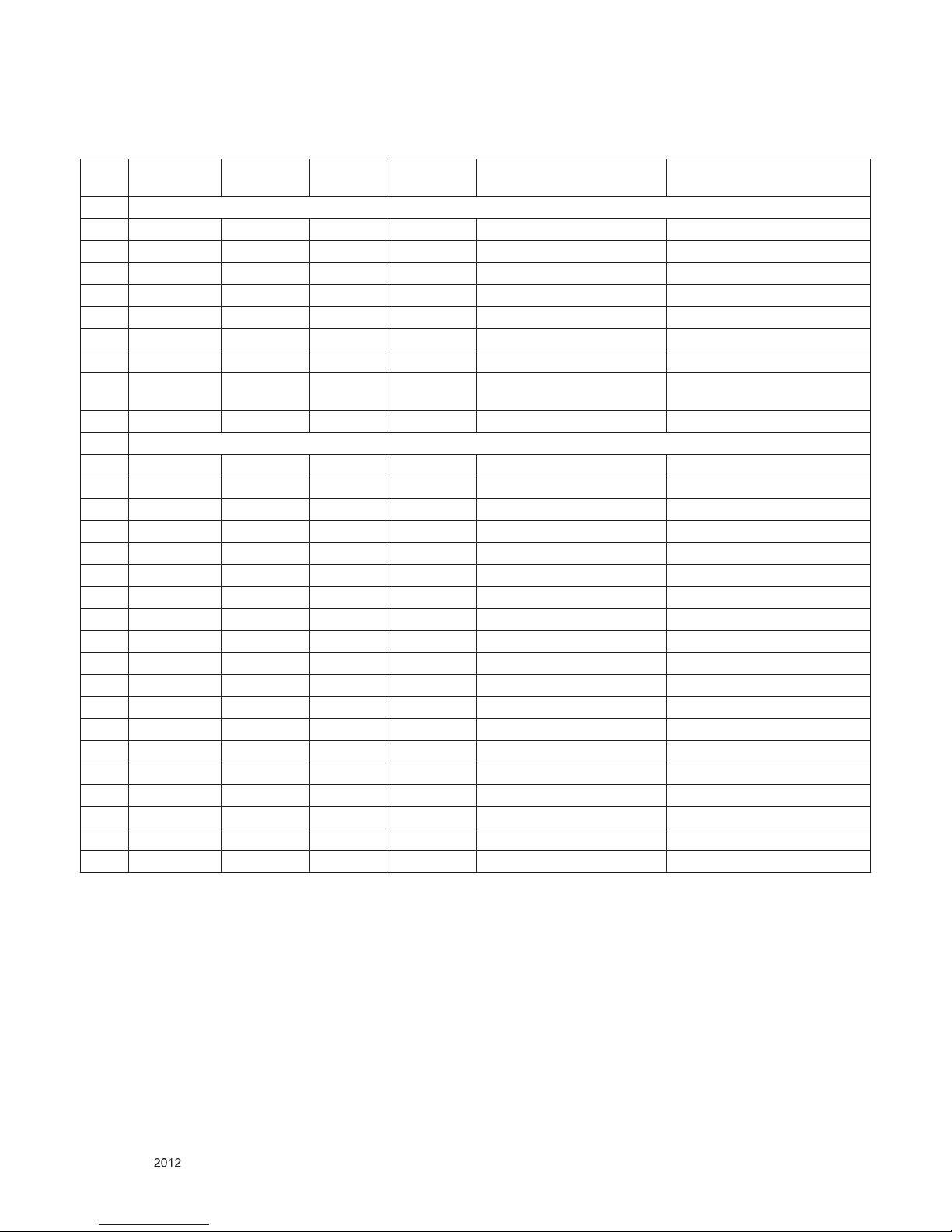

No Item Specication Remark

1. Display Screen Device 32” wide Color Display Module

42” wide Color Display Module

47” wide Color Display Module

55” wide Color Display Module

60” wide Color Display Module

65” wide Color Display Module

Resolution: 1920*1080

Resolution: 1920*1080

Resolution: 1920*1080

Resolution: 1920*1080

Resolution: 1920*1080

Resolution: 1920*1080

2. Aspect Ratio 16:9 All

3. LCD Module 32" TFT WUXGA LCD

42" TFT WUXGA LCD

47” TFT WUXGA LCD

55” TFT WUXGA LCD

60” TFT WUXGA LCD

65” TFT WUXGA LCD

4. Operating Environment 1) Temp. : 0 ~ 40 deg LGE SPEC

2) Humidity : 0 ~ 85%

5. Storage Environment 1) Temp. : -20 ~ 60 deg

2) Humidity : 10 ~ 90%

6. Input Voltage AC100 ~ 240V, 50/60Hz

7. Power Consumption(Max) =

LCD(Module) + Backlight(LED)

FHD

T120Hz

Edge LED

32” 38 W Normal : LC320EUN-SEM1 [32LS5700-SB]

42” 48 W Normal : LC420EUE-SEM1 [42LS5700-SB]

47” 72 W Normal : LC470EUE-SEM1 [47LS5700-SB]

60” W Normal :TBD [60LS5700-SB]

FHD

T120

(M120)Hz

Edge LED

FPR (GPR)

32” 38 W FPR : LC320EUN-SEF2 [32LM6200-SA]

42” 48 W FPR : LC420EUE-SEF1 [42LM6200-SA]

47” 72 W FPR : LC470EUE-SEF1 [47LM6200-SA]

55” 98 W FPR : LC550EUE-SEF1 [55LM6200-SA]

65” Typ : 182

Max : 197

W GPR : T645HB01-V0 [65LM6200-SA]

FHD

T120Hz

Semi-LCM

32 45 W FPR : LC320EUA-PEF1 [32LM6400-SA]

42 62 W FPR : LC420EUG-PEF1 [42LM64/6700-SA]

47 59 W FPR : LC470EUG-PEF1 [47LM64/6700-SA]

55 67.2 W FPR : LC550EUG-KEF1 [55LM64/6700-SA]

FHD

T240Hz

Semi-LCM

42” 60 W FPR : LC420EUH-PEF1 [42LM7600-SA]

47” 83 W FPR : LC470EUH-PEF1 [47LM7600-SA]

55 108 W FPR : LC550EUH-PEF1 [55LM7600-SA]

4. General Specification

- 6 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

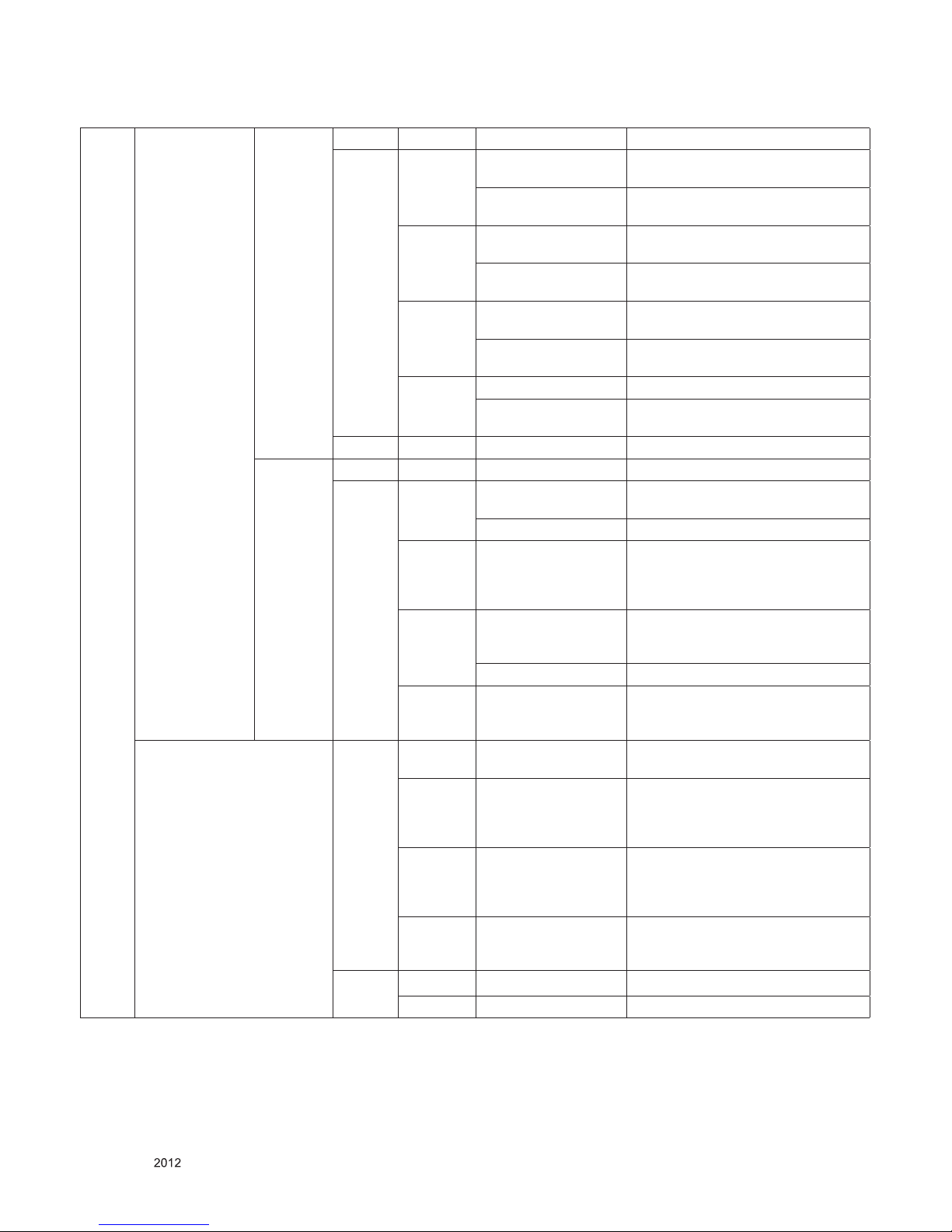

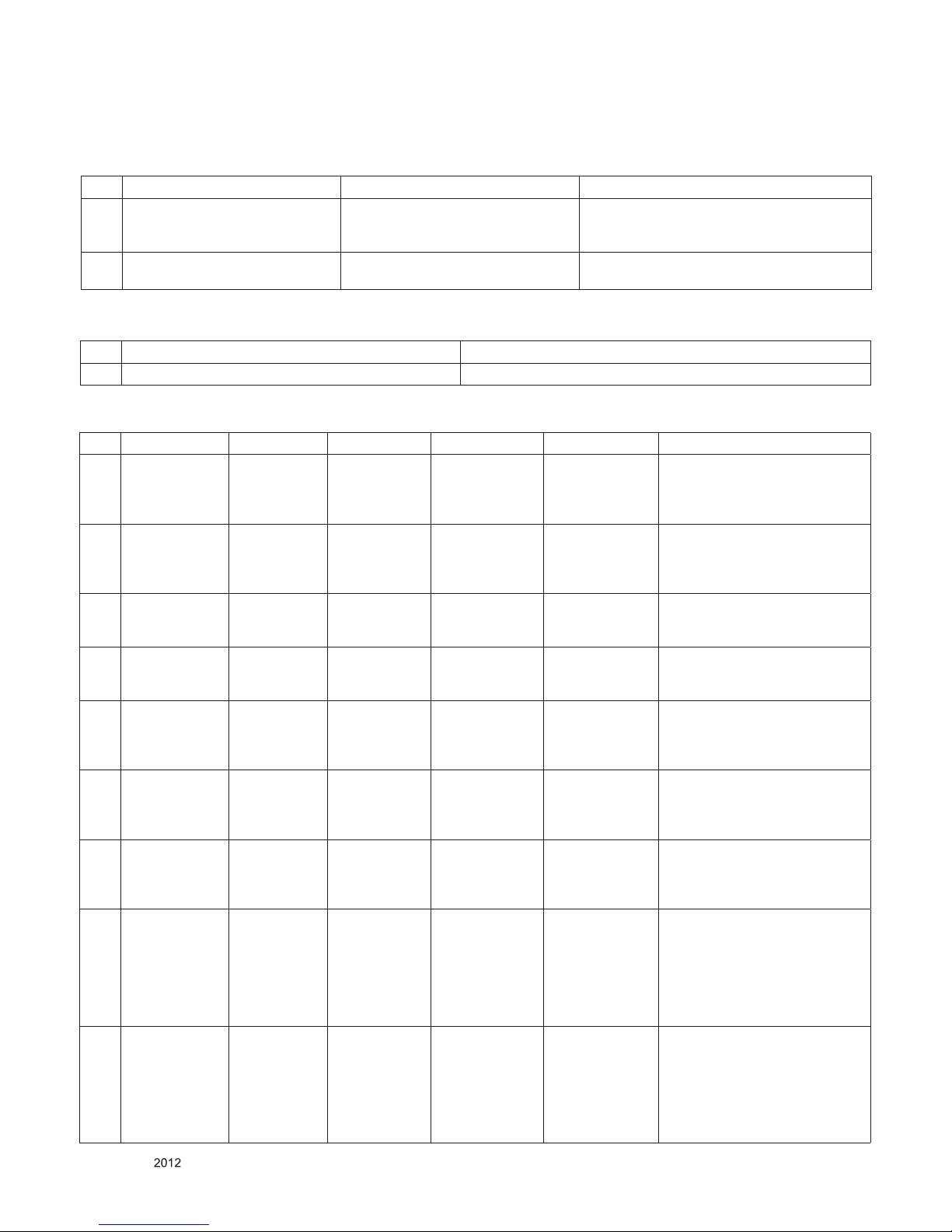

8. LCD Module Size Maker Inch (H) × (V) × (D)

LGD 32” 727.4 x 429.0 x 22.7 LC320EUN-SEM1

LC320EUN-SEF2

715.8 x 423.03 x 23.8

(with Side Sealing)

LC320EUA-PEF1

42” 960.4 x 560.4 x 17.4

LC420EUE-SEF1

LC420EUE-SEM1

949.2 x 554.2 x 16.8 LC420EUG-PEF1

LC420EUH-PEF1

47” 1070.6 x 622.0 x 22.0

LC470EUE-SEF1

LC470EUE-SEM1

1058.7 x 615.8 x 20.7 LC470EUG-PEF1

LC470EUH-PEF1

55” 1244.6 x 720.9 x 22.0 LC550EUE-SEF1

1228.6 x 711.4 x 20.7 LC550EUG-KEF1 : Edge 3D_T120Hz

LC550EUH-KEF1 : Edge 3D_T240Hz

AUO 65” 1508 x 878 x 12.8

Pixel Pitch Maker Inch (H) × (V) × (D)

LGD 32”

0.36375 x 0.36375 LC320EUN-SEM1

LC320EUN-SEF2

0.12125 x 0.12125 LC320EUA-PEF1

42” 0.4845 x 0.4845

LC420EUE-SEF1

LC420EUE-SEM1

LC420EUG-PEF1

LC420EUH-PEF1

47” 0.5415 x 0.5415

LC470EUE-SEF1

LC470EUE-SEM1

LC470EUH-PEF1

0.51415 x 0.51415 LC470EUG-PEF1

55” 0.630 x 0.630 LC550EUE-SEF1 : Edge 3D_T120Hz

LC550EUG-KEF1 : Edge 3D_T120Hz

LC550EUH-KEF1 : Edge 3D_T240Hz

Back Light LGD 32” Edge-LED LC320EUN-SEF2

LC320EUA-KEF1

42” Edge-LED LC420EUE-SEF1

LC420EUG-KEF1

LC420EUE-SEM1

LC420EUH-KEF1

47” Edge-LED LC470EUE-SEF1

LC470EUG-KEF1

LC470EUE-SEM1

LC470EUH-KEF1

55” Edge-LED LC550EUE-SEF1

LC550EUG-KEF1

LC550EUH-KEF1

AUO 32” Edge-LED T320HVN01.0

65” Edge-LED

- 7 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

5. Supported video resolutions

5.1. Component (Y, PB, PR)

5.2. RGB( PC ) : RGB-PC EDID DATA : Refer to adjust specification

No. Resolution H-freq(kHz) V-freq.(kHz) Pixel clock Proposed

1. 720*480 15.73 60 13.5135 SDTV ,DVD 480I

2. 720*480 15.73 59.94 13.5 SDTV ,DVD 480I

3. 720*480 31.50 60 27.027 SDTV 480P

4. 720*480 31.47 59.94 27.00 SDTV 480P

5. 720*576 15.625 50* 13.5 SDTV 576I

6. 720*576 31.25 50* 13.5 SDTV 576P

7. 1280*720 37.5 50* 74.25 HDTV 720P

8. 1280*720 45.00 60.00 74.25 HDTV 720P

9. 1280*720 44.96 59.94 74.176 HDTV 720P

10. 1929*1080 28.125 50* 74.25 HDTV 1080I

11. 1920*1080 33.75 60.00 74.25 HDTV 1080I

12. 1920*1080 33.72 59.94 74.176 HDTV 1080I

13. 1920*1080 56.25 50* 148.5 HDTV 1080P

14. 1920*1080 67.50 60 148.50 HDTV 1080P

15. 1920*1080 67.432 59.94 148.352 HDTV 1080P

16. 1920*1080 27.00 24.00 74.25 HDTV 1080P

17. 1920*1080 26.97 23.976 74.176 HDTV 1080P

18. 1920*1080 33.75 30.00 74.25 HDTV 1080P

19. 1920*1080 33.71 29.97 74.176 HDTV 1080P

No. Resolution H-freq(kHz) V-freq.(kHz) Pixel clock Proposed

1 640*350 31.468 70.09 25.17 EGA X

2 720*400 31.469 70.08 28.32 DOS O

3 640*480 31.469 59.94 25.17 VESA(VGA) O

4 800*600 37.879 60.31 40.00 VESA(SVGA) O

5 1024*768 48.363 60.00 65.00 VESA(XGA) O

6 1152*864 54.348 60.053 VESA

7 1360*768 47.712 60.015 85.50 VESA (WXGA) O

8 1920*1080 67.5 60.00 148.5 WUXGA(CEA861D) O

- 8 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

5.3. HDMI : EDID DATA : Refer to adjust specification

No Resolution H-freq(kHz) V-freq.(Hz)

Pixel

clock(MHz)

Proposed Remark

PC

1 640*350 31.468 70.09 25.17 EGA

2 720*400 31.469 70.08 28.32 DOS

3 640*480 31.469 59.94 25.17 VESA(VGA)

4 800*600 37.879 60.31 40 VESA(SVGA)

5 1024*768 48.363 60.00 65 VESA(XGA)

6 1152*864 54.348 60.053 80.002 VESA(VGA)

7 1360*768 47.712 60.020 84.75 VESA(WXGA)

8 1280*1024 63.981 60.015 109.00 SXGA Only FHD Model

(Support to HDMI-PC)

9 1920*1080 67.5 60.00 158.40 WUXGA(Reduced Blanking) FHD only

DTV

1 720*480 15.73 59.94 13.500 SDTV, DVD 480I(525I)

2 720*480 15.75 60.00 13.514 SDTV, DVD 480I(525I)

3 720*576 15.625 50.00 13.500 SDTV, DVD 576I(625I) 50Hz

4 720*480 31.47 59.94 27 SDTV 480P

5 720*480 31.5 60.00 27.027 SDTV 480P

6 720*576 31.25 50.00 27 SDTV 576P

7 1280*720 44.96 59.94 74.176 HDTV 720P

8 1280*720 45 60.00 74.25 HDTV 720P

9 1280*720 37.5 50.00 74.25 HDTV 720P

10 1920*1080 28.125 50.00 74.25 HDTV 1080I

11 1920*1080 33.72 59.94 74.176 HDTV 1080I

12 1920*1080 33.75 60.00 74.25 HDTV 1080I

13 1920*1080 26.97 23.976 63.296 HDTV 1080P

14 1920*1080 27.00 24.000 63.36 HDTV 1080P

15 1920*1080 33.71 29.97 79.120 HDTV 1080P

16 1920*1080 33.75 30.00 79.20 HDTV 1080P

17 1920*1080 56.25 50.00 148.5 HDTV 1080P

18 1920*1080 67.432 59.94 148.350 HDTV 1080P

19 1920*1080 67.5 60.00 148.5 HDTV 1080P

- 9 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

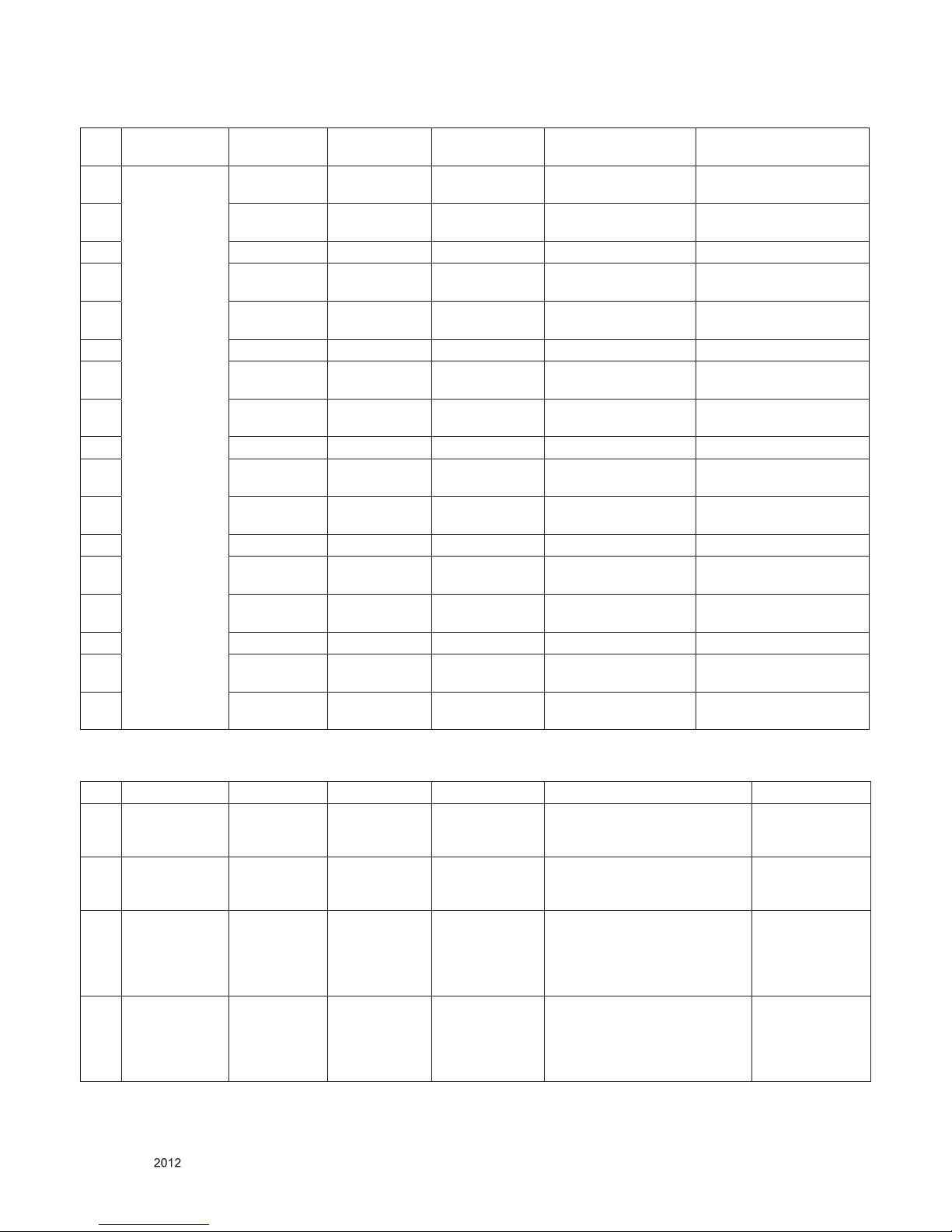

5.4. 3D mode

5.2.1. RF Input

No Resolution Proposed 3D input proposed mode

1 HD 1080I

720P

2D to 3D

Side by Side(Half)

Top & Bottom

2 SD 576P

576I

2D to 3D

5.2.2. RF Input (3D supported mode automatically)

5.2.3. HDMI Input 1.3(3D supported mode manually)

No Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed Remark

1 1280*720 45.00 60.00 74.25 HDTV 720P 2D to 3D

Side by Side(half),

Top & Bottom,

Single Frame Sequential

2 1280*720 37.500 50 74.25 HDTV 720P 2D to 3D

Side by Side(half),

Top & Bottom,

Single Frame Sequential

3 1920*1080 33.75 60.00 74.25 HDTV 1080I 2D to 3D

Side by Side(half),

Top & Bottom

4 1920*1080 28.125 50.00 74.25 HDTV 1080I 2D to 3D

Side by Side(half),

Top & Bottom

5 1920*1080 27.00 24.00 74.25 HDTV 1080P 2D to 3D

Side by Side(half),

Top & Bottom,

Checkerboard

6 1920*1080 28.12 25 74.25 HDTV 1080P 2D to 3D

Side by Side(half),

Top & Bottom,

Checkerboard

7 1920*1080 33.75 30.00 74.25 HDTV 1080P 2D to 3D

Side by Side(half),

Top & Bottom,

Checkerboard

8 1920*1080 56.25 50 148.5 HDTV 1080P 2D to 3D

Side by Side(half),

Top & Bottom,

Checkerboard,

Single Frame Sequential,

Row Interleaving,

Column Interleaving

9 1920*1080 67.50 60.00 148.5 HDTV 1080P 2D to 3D

Side by Side(half),

Top & Bottom,

Checkerboard,

Single Frame Sequential,

Row Interleaving,

Column Interleaving

No Signal 3D input proposed mode

1 Frame Compatible Side by Side(Half), Top & Bottom

- 10 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

5.2.4. HDMI Input 1.4b (3D supported mode automatically)

No Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed

mode

Proposed

1 640*480 31.469 / 31.5 59.94/ 60 25.175/25.2 Top-and-Bottom

Side-by-side(half)

Secondary(SDTV 480P)

Secondary(SDTV 480P)

2 62.938 / 63 59.94/ 60 50.35/50.4 Frame packing

Line alternative

Secondary(SDTV 480P)

(SDTV 480P)

3 31.469 / 31.5 59.94/ 60 50.35/50.4 Side-by-side(Full) (SDTV 480P)

4 720*480 31.25 50 27 Top-and-Bottom

Side-by-side(half)

Secondary(SDTV 480P)

Secondary(SDTV 480P)

5 62.5 50 54 Frame packing

Line alternative

Secondary(SDTV 480P)

(SDTV 480P)

6 31.25 50 54 Side-by-side(Full) (SDTV 480P)

7 720*576 31.25 50 27 Top-and-Bottom

Side-by-side(half)

Secondary(SDTV 576P)

Secondary(SDTV 576P)

8 62.5 50 54 Frame packing

Line alternative

Secondary(SDTV 576P)

(SDTV 576P)

9 31.25 50 54 Side-by-side(Full) (SDTV 576P)

10 15.625 50 27 Top-and-Bottom

Side-by-side(half)

Secondary(SDTV 576I)

Secondary(SDTV 576I)

11 31.25 50 54 Frame packing

Field alternative

Secondary(SDTV 576I)

(SDTV 576I)

12 15.625 50 54 Side-by-side(Full) (SDTV 576I)

13 1280*720 37.5 50 74.25 Top-and-Bottom

Side-by-side(half)

Primary(HDTV 720P)

Primary(HDTV 720P)

14 75 50 148.5 Frame packing

Line alternative

Primary(HDTV 720P)

(HDTV 720P)

15 37.5 50 148.5 Side-by-side(Full) (HDTV 720P)

16 44.96 / 45 59.94 / 60 74.18/74.25 Top-and-Bottom

Side-by-side(half)

Primary(HDTV 720P)

Primary(HDTV 720P)

17 89.91 / 90 59.94 / 60 148.35/148.5 Frame packing

Line alternative

Primary(HDTV 720P)

(HDTV 720P)

18 44.96 / 45 59.94 / 60 148.35/148.5 Side-by-side(Full) (HDTV 720P)

- 11 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

No Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed

mode

Proposed

19 1920*1080 33.72 / 33.75 59.94 / 60 74.18/74.25 Top-and-Bottom

Side-by-side(half)

Secondary(HDTV 1080I)

Primary(HDTV 1080I)

20 67.432 / 67.5 59.94 / 60 148.35/148.5 Frame packing

Field alternative

Primary(HDTV 1080I)

(HDTV 1080I)

21 33.72 / 33.75 59.94 / 60 148.35/148.5 Side-by-side(Full) (HDTV 1080I)

22 28.125 50.00 74.25 Top-and-Bottom

Side-by-side(half)

Secondary(HDTV 1080I)

Primary(HDTV 1080I)

23 56.25 50.00 148.5 Frame packing

Field alternative

Primary(HDTV 1080I)

(HDTV 1080I)

24 28.125 50.00 148.5 Side-by-side(Full) (HDTV 1080I)

25 26.97 / 27 23.97 / 24 74.18/74.25 Top-and-Bottom

Side-by-side(half)

Primary(HDTV 1080P)

Primary(HDTV 1080P)

26 43.94 / 54 23.97 / 24 148.35/148.5 Frame packing

Line alternative

Primary(HDTV 1080P)

(HDTV 1080P)

27 26.97 / 27 23.97 / 24 148.35/148.5 Side-by-side(Full) (HDTV 1080P)

28 28.12 25 74.25 Top-and-Bottom

Side-by-side(half)

Secondary(HDTV 1080P)

Secondary(HDTV 1080P)

29 56.25 25 148.5 Frame packing

Line alternative

Secondary(HDTV 1080P)

(HDTV 1080P)

30 28.125 25 148.5 Side-by-side(Full) (HDTV 1080P)

31 33.716 / 33.75 29.976 / 30.00 74.18/74.25 Top-and-Bottom

Side-by-side(half)

Primary(HDTV 1080P)

Secondary(HDTV 1080P)

32 67.432 / 67.5 29.976 / 30.00 148.35/148.5 Frame packing

Line alternative

Primary(HDTV 1080P)

(HDTV 1080P)

33 33.716 / 33.75 29.976 / 30.00 148.35/148.5 Side-by-side(Full) (HDTV 1080P)

34 56.25 50 148.5 Top-and-Bottom

Side-by-side(half)

Primary(HDTV 1080P)

Secondary(HDTV 1080P)

35 67.43 / 67.5 59.94 / 60 148.35/148.50 Top-and-Bottom

Side-by-side(half)

Primary(HDTV 1080P)

Secondary(HDTV 1080P)

5.2.5. HDMI-PC 3D Input (3D supported mode manually)

No Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed mode Proposed

1 1024*768 48.36 60 65 2D to 3D,

Side by Side(half)

Top & Bottom

HDTV 768P

2 1360*768 47.71 60 85.5 2D to 3D,

Side by Side(half)

Top & Bottom

HDTV 768P

3 1920*1080 67.500 60 148.50 2D to 3D,

Side by Side(half)

Top & Bottom,

Checker Board,

Single Frame Sequential

HDTV 1080P

4 Others - - - 2D to 3D 640*350

720*400

640*480

800*600

1152*864

- 12 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

5.2.6. RGB-PC 3D Input (3D supported mode manually)

No Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed mode Proposed

1 1024*768 48.36 60 65 2D to 3D,

Side by Side(half)

Top & Bottom

HDTV 768P

2 1360*768 47.71 60 85.5 2D to 3D,

Side by Side(half)

Top & Bottom

HDTV 768P

3 1920*1080 67.500 60 148.50 2D to 3D,

Side by Side(half)

Top & Bottom

HDTV 1080P

4 Others - - - 2D to 3D 640*350

720*400

640*480

800*600

1152*864

1280*1024

5.2.7. USB Input (3D) (3D supported mode manually)

No Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed mode Proposed

1 1920*1080 33.75 30 74.25 2D to 3D

Side by Side(Half)*,

Top & Bottom*,

Checkerboard*

Row Interleaving,

Column Interleaving

(Photo : side by Side(half),

Top & Bottom)

HDTV 1080P

5.2.8. DLNA Input (3D)

No Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed mode Proposed

1 1920*1080 33.75 30 74.25 2D to 3D

Side by Side(Half)*,

Top & Bottom*,

Checkerboard*

Row Interleaving,

Column Interleaving

(Photo : side by Side(half), Top

& Bottom)

HDTV 1080P

- 13 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

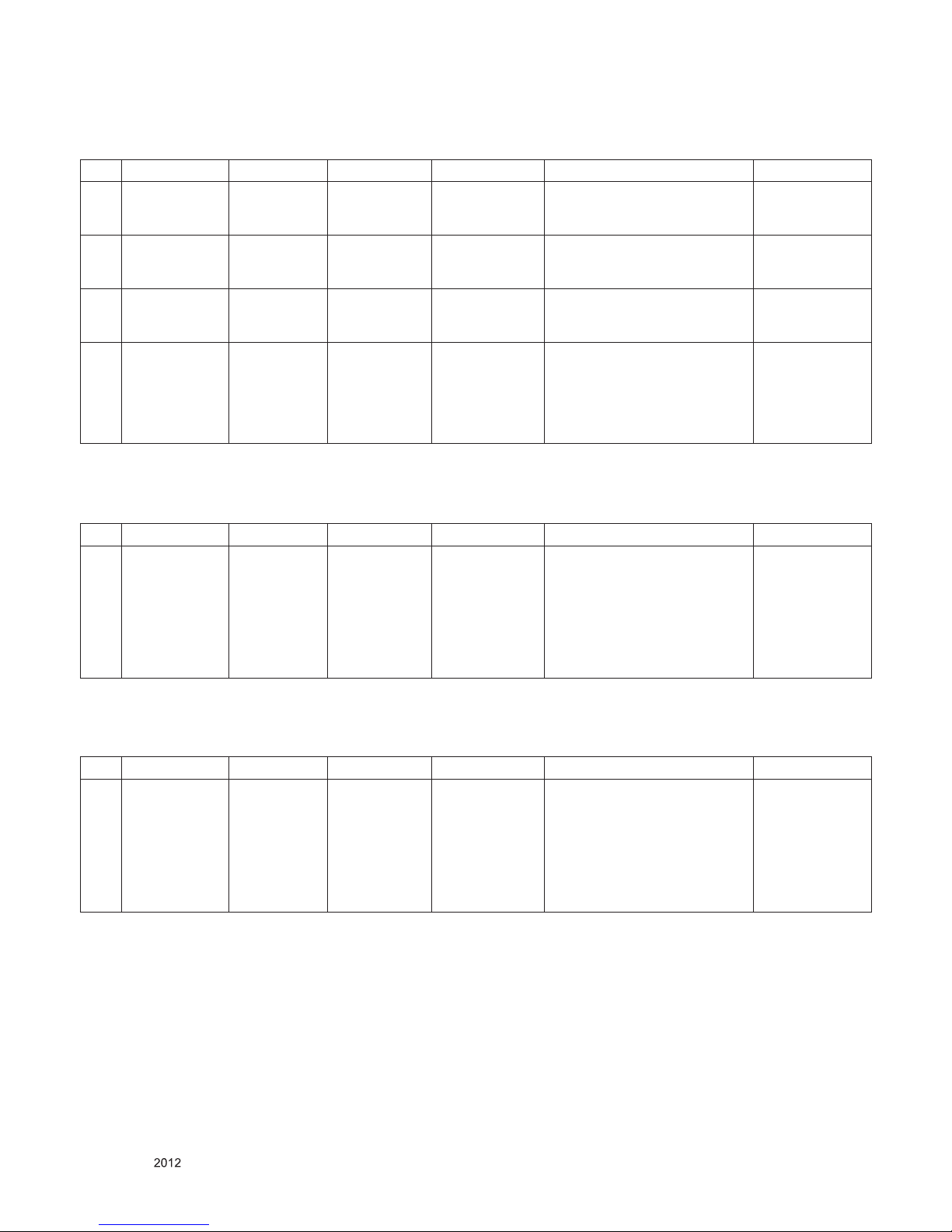

5.2.9. Component 3D Input (3D supported mode manually)

No Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed mode Proposed

1 1280*720 37.5 50 74.25 2D to 3D,

Side by Side(half),

Top & Bottom

HDTV 720P

2 1280*720 45.00 60.00 74.25 2D to 3D,

Side by Side(half),

Top & Bottom

HDTV 720P

3 1280*720 44.96 59.94 74.176 2D to 3D,

Side by Side(half)

Top & Bottom

HDTV 720P

4 1920*1080 33.75 60.00 74.25 2D to 3D,

Side by Side(half)

Top & Bottom

HDTV 1080I

5 1920*1080 33.72 59.94 74.176 2D to 3D,

Side by Side(half)

Top & Bottom

HDTV 1080I

6 1920*1080 28.12 50 74.25 2D to 3D,

Side by Side(half)

Top & Bottom

HDTV 1080I

7 1920*1080 67.500 60 148.50 2D to 3D,

Side by Side(half)

Top & Bottom

HDTV 1080P

8 1920*1080 67.432 59.94 148.352 2D to 3D,

Side by Side(half)

Top & Bottom

HDTV 1080P

9 1920*1080 27.000 24.000 74.25 2D to 3D,

Side by Side(half)

Top & Bottom

HDTV 1080P

10 1920*1080 28.12 25 74.25 2D to 3D,

Side by Side(half)

Top & Bottom

HDTV 1080P

11 1920*1080 56.25 50 74.25 2D to 3D,

Side by Side(half)

Top & Bottom

HDTV 1080P

12 1920*1080 26.97 23.976 74.176 2D to 3D,

Side by Side(half)

Top & Bottom

HDTV 1080P

13 1920*1080 33.75 30.000 74.25 2D to 3D,

Side by Side(half)

Top & Bottom

HDTV 1080P

14 1920*1080 33.71 29.97 74.176 2D to 3D,

Side by Side(half)

Top & Bottom

HDTV 1080P

- 14 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

ADJUSTMENT INSTRUCTION

1. Application Range

This specification sheet is applied all of the LJ22E LCD TV

models, which produced in manufacture department or similar

LG TV factory.

2. Specification

(1) Because this is not a hot chassis, it is not necessary to use

an isolation transformer. However, the use of isolation

transformer will help protect test instrument.

(2) Adjustment must be done in the correct order. But it is

flexible when its factory local problem occurs.

(3) The adjustment must be performed in the circumstance of

25 ±5ºC of temperature and 65±10% of relative humidity if

there is no specific designation.

(4) The input voltage of the receiver must keep 100~220V,

50/60Hz.

(5) Before adjustment, execute Heat-Run for 5 minutes.

▪ After Receive 100% Full white pattern (06CH) then process

Heat-run

(or “8. Test pattern” condition of Ez-Adjust status)

▪ How to make set white pattern

1) Press Power ON button of Service Remocon

2) Pr ess ADJ button of Service remocon. Select “8. Test

pattern” and, after select “White” using navigation button,

and then you can see 100% Full White pattern.

* In this status you can maintain Heat-Run useless any pattern

generator

* Notice : if you mai nt ain one pictu re ov er 20 minutes

(Especially sharp distinction black with white pattern

-13Ch, or Cross hatch pattern – 09Ch) then it can

appear image stick near black level.

3. Adjustment items

3.1. PCB Assembly Adjustment

▪ MAC Address / ESN / Widevine Download

▪ Adjust 1080p Comp1/RGB (Except GP3 BCM MODEL using

ADC OTP)

▪ EDID (The Extended Display Identific ation Data)/D DC

(Display Data Channel) download

* If it is necessary, it can adjustment at Manufacture Line

You can see set adjustment status at “1. ADJUST CHECK”

of the “In-start menu”

3.2. Set Assembly Adjustment

▪ Color Temperature (White Balance) Adjustment

▪ Using RS-232C

▪ PING Test

▪ Selection Factory output option

4. PCB Assembly Adjustment

4.1. MAC Address, ESN Key and Widevine

Key download

4.1.1. Equipment & Condition

1) Play file: keydownload.exe

4.1.2. Communication Port connection

1) Key Write: Com 1,2,3,4 and 115200 (Baudrate)

2) Barcode: Com 1,2,3,4 and 9600 (Baudrate)

4.1.3. Download process

1) Select the download items.

2) Mode check: Online Only

3) Check the test process

- DETECT -> MAC_WRITE -> ESN_WRITE -> WIDEVINE_

WRITE

4) Play : START

5) Check of result: Ready, Test, OK or NG

4.1.4. Communication Port connection

1) Connect: PCBA Jig -> RS-232C Port == PC -> RS-232C

Port

4.1.5. Download

1) 11Y LCD TV + MAC + Widevine + ESN Key

4.1.6. Inspection

- In INSTART menu, check these keys.

- 15 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

4.2. LAN PORT INSPECTION(PING TEST)

4.1.1. Equipment setting

1) Play the LAN Port Test PROGRAM.

2) Input IP set up for an inspection to Test

Program.

*IP Number : 12.12.2.2.

4.2.2. LAN PORT inspection (PING TEST)

1) Play the LAN Port Test Program.

2) connect each other LAN Port Jack.

3) Play Test (F9) button and confirm OK Message.

4) remove LAN CABLE

4.3. Using RS-232C

- Adjust 3 items at 3.1 PCB assembly adjustments “adjustment

sequence” one after the order.

● Adjustment protocol

Order Command Set response

(1) Inter the Adjustment mode aa 00 00 a 00 OK00x

(2) Change the Source xb 00 40

xb 00 60

b 00 OK40x (Adjust 480i Comp1 )

(Adjust 1080p Comp1)

b 00 OK60x (Adjust 1080p RGB)

(3) Start Adjustment ad 00 10

(4) Return the Response OKx ( Success condition )

NGx ( Failed condition )

(5) Read Adjustment data ( main)

ad 00 20

( main )

ad 00 30

(main : component1 480i, RGB 1080p)

000000000000000000000000007c007b006dx

(main : component1 1080p)

000000070000000000000000007c0083

0077x

(6) Conrm Adjustment ad 00 99 NG 03 00x (Failed condition)

NG 03 01x (Failed condition)

NG 03 02x (Failed condition)

OK 03 03x (Success condition)

(7) End of Adjustment ad 00 90 d 00 OK90x

See ADC Adjustment RS232C Protocol_Ver1.0

● Necessary items before Adjustment items

▪ Pattern Generator : (MSPG-925FA)

▪ Adjust 480i Comp1 (MSPG-925FA:model :209 , pattern :65) –

Comp1 Mode

▪ Adjust 1080p Comp1 (MSPG-925FA:model :225 , pattern

:65) – Comp1 Mode

▪ Adjust RGB (MSPG-925FA:model :225 , Pattern :65) – RGB-

PC Mode

If you want more information then see the below Adjustment

method (Factory Adjustment)

● Adjustment sequence

▪ aa 00 00: Enter the ADC Adjustment mode.

▪ xb 00 40: Change the mode to Component1 (No actions)

▪ ad 00 10: Adjust 480i Comp

▪ ad 00 10: Adjust 1080p Comp

▪ xb 00 60: Change to RGB-PC mode(No action)

▪ ad 00 10: Adjust 1080p RGB

▪ xb 00 90: Endo of Adjustmennt

- 16 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

5. Factory Adjustment

5.1. EDID (The Extended Display Identification

Data)/DDC (Display Data Channel) Download

● Summary

▪ It is established in VESA, for communication between PC

and Monitor without order from user for building user

condition. It helps to make easily use realize “Plug and Play”

function. For EDID data write, we use DDC2B protocol.

● Auto Download

▪ After enter Service Mode by pushing “ADJ” key

▪ Enter EDID D/L mode.

▪ Enter “START” by pushing “OK” key.

=> Caution : Never connect HDMI & D-sub Cable when the

user downloading . Use the proper cables below

for EDID Writing.

※ Edid data and Model option download (RS232)

NO Item CMD 1 CMD 2 Data 0

Enter

download

MODE

Download

‘Mode In’

A E 0 0 When transfer the

‘Mode In’,

Carry the command.

Edid data

and

Model

option

download

Download A E *Note1 *Note2 Automatically

download

(The use of a

internal Data)

Adjust

‘Mode Out’

A E 9 0

Adjustment

Conrmation

A E 9 9 To check Download

on Assembly line.

Manual Download

● Write HDMI EDID data

▪ Using instruments

- Jig.(PC Serial to D-Sub connection) for PC, DDC adjustment.

- S/W for DDC recording (EDID data write and read)

- D-sub jack

- Additional HDMI cable connection Jig.

▪ Preparing and setting

- Set instruments and Jig. Like pic.5), then turn on PC and Jig

- Operate DDC write S/W (EDID write & read)

- It will operate in the DOS mode.

Pic.3) For write EDID data, setting Jig and another instruments.

* EDID data for Non 3DTV (LS5700-SB Series) (Model name =

LG TV)

- HDMI EDID table (0x1E : Physical Address)

- HDMI-1 EDID table (0x43, 0x15)

1) HDMI 1 Check sum : 0x43, 0X15 (CEA Block 0x1E :10)

2) HDMI 2 Check sum : 0x43, 0X05 (CEA Block 0x1E :20)

3) HDMI 3 Check sum : 0x43, 0XF5 (CEA Block 0x1E :30)

4) HDMI 4 Check sum : 0x43, 0XE5 (CEA Block 0x1E :40)

- Analog (RGB) EDID table

1) RGB CheckSum : 5C

PC

JI

G

LCD TV SET

(or digital board)

- 17 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

* EDID data for 3DTV (LM6200 Series) (Model name = LG TV)

- HDMI EDID table (0x1E : Physical Address)

HDMI-1 EDID table (0x43, 0x4D)

1) HDMI 1 Check sum : 0x43, 0X4D (CEA Block 0x1E :10)

2) HDMI 2 Check sum : 0x43, 0X3D (CEA Block 0x1E :20)

3) HDMI 3 Check sum : 0x43, 0X2D (CEA Block 0x1E :30)

4) HDMI 4 Check sum : 0x43, 0X1D (CEA Block 0x1E :40)

- Analog (RGB) EDID table

5.2. Adjustment Color Temperature

(White balance)

● Using Instruments

▪ Color Analyzer: CA-210 (CH 14)

- Using LCD color temperature, Color Analyzer (CA-210) must

use CH 14, which Matrix compensated (White, Red, Green,

Blue compensation) with CS-2100. See the Coordination

bellowed one.

▪ Auto-adjustment Equipment (It needs when Auto-adjustment

– It is availed communicate with RS-232C : Baud rate:

115200)

▪ Video Signal Generator MSPG-925F 720p, 216Gray (Model:

217, Pattern 78)

● Connection Diagram (Auto Adjustment)

▪ Using Inner Pattern

▪ Using HDMI input

<Pic.5 Connection Diagram for Adjustment White balance>

● White Balance Adjustment

If you can’t adjust with inner pattern, then you can adjust it

using HDMI pattern. You can select option at “Ez-Adjust Menu

– 7. White Balance” there items “NONE, INNER, HDMI”. It is

normally setting at inner basically. If you can’t adjust using

inner pattern you can select HDMI item, and you can adjust.

In manual Adjust case, if you press ADJ button of service

remocon, and enter “Ez-Adjust Menu – 7. White Balance”,

then automatically inner pattern operates. (In case of “Inner”

originally “Test-Pattern. On” will be selected in The “TestPattern. On/Off”.

▪ Connect all cables and equipments like Pic.5)

▪ Set Baud Rate of RS-232C to 115200. It may set 115200

orignally.

▪ Connect RS-232C cable to set

▪ Connect HDMI cable to set

- 18 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

● RS-232C Command (Commonly apply)

RS-232C COMMAND

Explanation

CMD DATA ID

wb 00 00 White Balance adjustment start

Wb 00 10

Start of adjust gain (Inner white pattern)

wb 00 1f End of gain adjust

wb 00 20

Start of offset adjust(Inner white pattern)

wb 00 2f End of offset adjust

wb 00 ff End of White Balance adjust

(Inner pattern disappeared)

▪ “wb 00 00”: Start Auto-adjustment of white balance.

▪ “wb 00 10”: Start Gain Adjustment (Inner pattern)

▪ “jb 00 c0” :

▪ …

▪ “wb 00 1f”: End of Adjustment

* If it needs, offset adjustment (wb 00 20-start, wb 00 2f-end)

▪ “wb 00 ff”: End of white balance adjustment (inner pattern

disappear)

※ Notice) Adjustment Mapping information

RS-232C COMMAND

[CMD ID DATA]

MIN CENTER

(DEFAULT)

MAX

C50 0 W50 00 C50 0 W50

R Gain Jg ja jd 00 192 192 192 192

G Gain Jh jb je 00 189 175 157 192

B Gain Ji jc jf 153 127 57 192

R Gain 64 64 64 127

G Gain 64 64 64 127

B Gain 64 64 64 127

▪ When Col or temperature (White balance) Adju stmen t

(Automatically)

- Press “Power only key” of service remocon and operate

automatically adjustment.

- Set BaudRate to 115200.

▪ You must start “wb 00 00” and finish it “wb 00 ff”.

▪ If it needs, then adjustment “Offset”.

● White Balance Adjustment (Manual adjustment)

▪ Test Equipment: CA-210

- Using LCD color temperature, Color Analyzer (CA-210) must

use CH 14, which Matrix compensated (White, Red, Green,

Blue compensation) with CS-2100. See the Coordination

bellowed one.

▪ Manual adjustment sequence is like bellowed one.

- Turn to “Ez-Adjust” mode with press ADJ button of service

remocon.

- Select “10.Test Pattern” with CH+/- button and press enter.

Then set will go on Heat-run mode. Over 30 minutes set let

on Heat-run mode.

- Let CA-210 to zero calibration and must has gap more 10cm

from center of LCD module when adjustment.

- Press “ADJ” button of service remocon and select “7.White-

Balance” in “Ez-Adjust” then press “►” button of navigation

key.

(When press “►” button then set will go to full white mode)

- Adjust at three mode (C50, 0, W50)

- If “C50 (cool)” mode

Let B-Gain to 192 and R, G, B-Cut to 64 and then control R, G

gain adjustment High Light adjustment.

- If “0 (Medium)” and “W50(Warm)” mode

Let R-Gain to 192 and R, G, B-Cut to 64 and then control G, B

gain adjustment High Light adjustment.

- All of the three mode

Let R-Gain to 192 and R, G, B-Cut to 64 and then control G, B

gain adjustment High Light adjustment.

- With volume button (+/-) you can adjust.

- After all adjustment finished, with Enter (■ key) turn to

Ez-Adjust mode. Then with ADJ button, exit from adjustment

mode

Attachment: White Balance adjustment coordination and color

temperature.

● Using CS-1000 Equipment.

- C50 (COOL) : T=11000K, △uv=0.000, x=0.276 y=0.283

- 0 (MEDIUM) : T=9300K, △uv=0.000, x=0.285 y=0.293

- W50 (WARM) : T=6500K, △uv=0.000, x=0.313 y=0.329

Using CA-210 Equipment. (14 CH)

- Contrast value: 208 Gray

Color temperature Test Equipment

Color Coordination

x y

C50 CA-210 0.269±0.002 0.273±0.002

0 CA-210 0.285±0.002 0.293±0.002

W50 CA-210 0.313±0.002 0.329±0.002

- 19 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

Using CA-210 Equipment. (18 CH)

White Balance adjustment coordination and color temperature for

Edge LED

Color

Temperature

C50 13,000k K

X=0.269

(±0.002)

Y=0.273

(±0.002)

<Test signal>

Inner pattern

(204 Gray

80IRE)

0 9,300k K

X=0.285

(±0.002)

Y=0.293

(±0.002)

W50 6,500k K

X=0.313

(±0.002)

Y=0.329

(±0.002)

White Balance adjustment table

Color coordination is different according to heat run time.

LSxxxx, LM5xxx, LM6xxx, 42LM7xxx, AUO(65LM6200)

H/R Time(Min)

Cool Medium Warm

x y x x y x

269 273 285 293 313 329

1 0-2 280 287 296 307 320 337

2 3-5 279 285 295 305 319 335

3 6-9 277 284 293 304 317 334

4 10-19 276 283 292 303 316 333

5 20-35 274 280 290 300 314 330

6 36-49 272 277 288 297 312 327

7 50-79 271 275 287 295 311 325

8 80-119 270 274 286 294 310 324

9 Over 120 269 273 285 293 309 323

47/55LM7xxx, 47/55LM8xxx, 47/55LM9xxx

H/R Time(Min)

Cool Medium Warm

x y x x y x

269 273 285 293 313 329

1 0-2 283 293 299 313 320 339

2 3-5 282 291 298 311 319 337

3 6-9 281 290 297 310 318 336

4 10-19 279 289 295 309 316 335

5 20-35 277 284 293 304 314 330

6 36-49 274 279 290 299 311 325

7 50-79 271 277 287 297 308 323

8 80-119 270 274 286 294 307 320

9 Over 120 269 273 285 293 306 319

5.3. EYE-Q function check

(1) Turn on TV

(2) Press EYE key of Adj. R/C

(3) Cover the Eye Q II sensor on the front of the using your

hand and wait for 6 seconds

(4) Confirm that R/G/B value is lower than 10 of the “Raw Data

(Sensor data, Back lignt )” . If after 6 seconds, R/G/B

value is not lower than 10, replace Eye Q II sensor

(5) Remove your hand from the Eye Q II sensor and wait for 6

seconds

(6) Confirm that “ok” pop up.

If change is not seen, replace Eye Q II sensor

5.4. Magic Motion remote controller Check

5.4.1 Test equipment

- RF-remote controller for check, IR-KEY-CODE remote

controller.

- Check AA battery before test. A recommendation is that a

tester change battery every lots.

5.4.2. Test

(1) Make pairing with TV set by pressing “Mute (START) key”

on RCU.

(2) Check a cursor on screen by pressing ‘ENTER” or “OK”

key of RCU

(3) Stop paring with TV set by pressing “VOL+ (STOP) key.

Step2 Step3 Step4

Step5 Step6

- 20 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

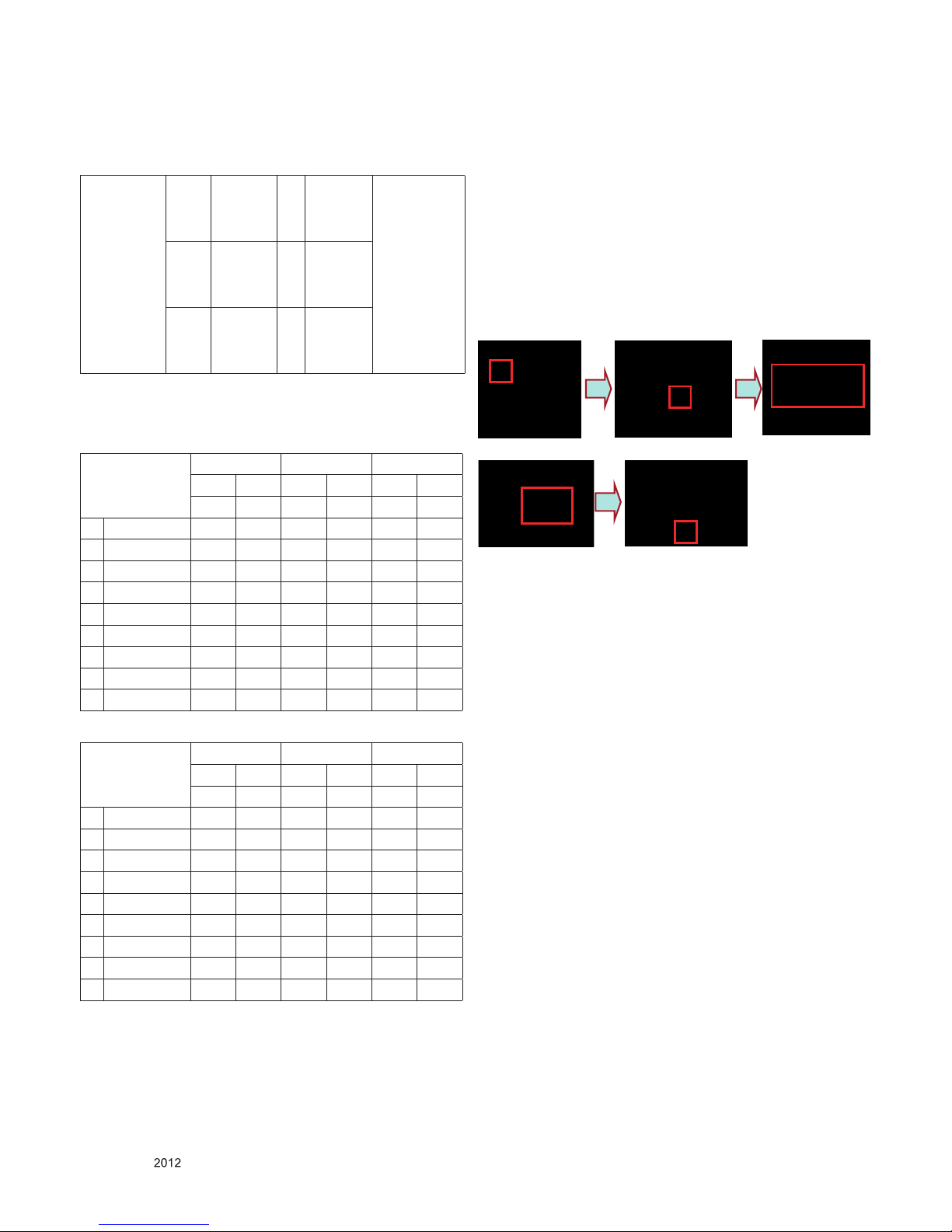

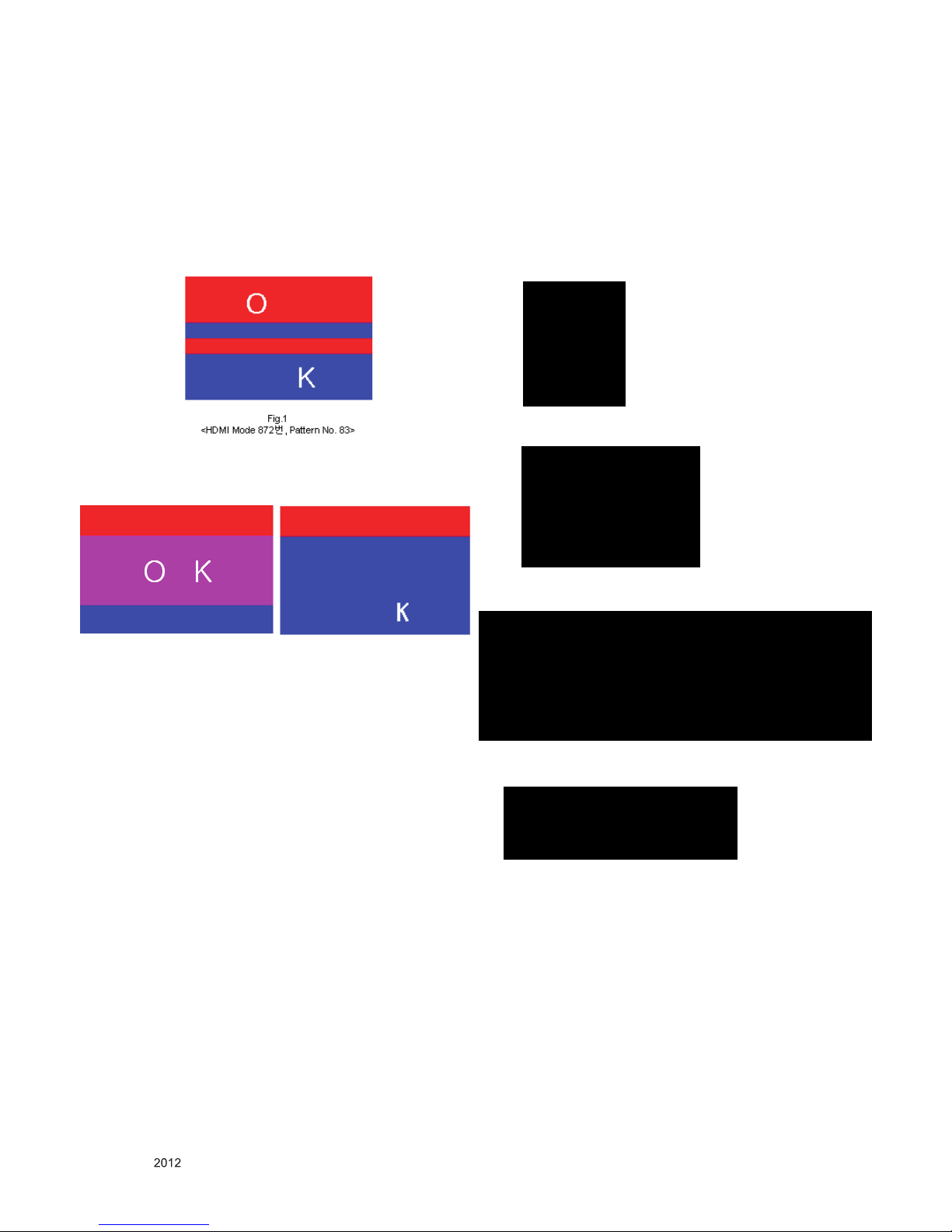

5.5. 3D pattern test (Only for 3D models)

5.5.1. Test equipment

(1) Pattern Generator MSHG-600 or MSPG-6100 (HDMI 1.4

support)

(2) Pattern: HDMI mode (model No. 872, pattern No. 83)

5.5.2. Test method

(1) Input 3D test signal as Fig.1.

(2) Press ‘OK” key as a 3D input OSD is shown.

(3) Check pattern as Fig2 without 3D glasses. (3D mode

without 3D glasses)

Fig.2 Fig.3

<OK in 3D mode without 3D glasses> <NG in 3D mode without 3D glasses>

5.6. HDMI ARC Function Inspection

5.6.1. Test equipment

- Optic Receiver Speaker

- MSHG-600 (SW: 1220 ↑)

- HDMI Cable (for 1.4 version)

5.6.2. Test method

(1) Insert the HDMI Cable to the HDMI ARC port from the

master equipment (HDMI1)

(2) Check the sound from the TV Set

(3) Check the Sound from the Speaker or using AV & Optic

TEST program (It’s connected to MSHG-600)

* Remark: Inspect in Power Only Mode and check SW version

in a master equipment

5.7. Selection of Country option

Selection of country option is allowed only North American

model (Not allowed Korean model). It is selection of Country

about Rating and Time Zone.

▪ Models: All models which use LJ22E Chassis (See the first

page.)

▪ Press “In-Start” button of Service Remocon, then enter the

“Option” Menu with “PIP CH-“ Button

▪ Select one of these three (USA, CANADA, MEXICO) defends

on its market using “Vol. +/-“button.

※ Caution : Don’t push The INSTOP KEY after completing the

function inspection

- 21 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

6. GND and ESD Testing

6.1. Prepare GND and ESD Testing

(1) Check the connection between set and power cord

6.2. Operate GND and ESD auto-test

(1) Fully connected (Between set and power cord) set enter

the Auto-test sequence.

(2) Connect D-Jack AV jack test equipment.

(3) Turn on Auto-controller(GWS103-4)

(4) Start Auto GND test.

(5) If its result is NG, then notice with buzzer.

(6) If its result is OK, then automatically it turns to ESD Test.

(7) Operate ESD test

(8) If its result is NG, then notice with buzzer.

(9) If its result is OK, then process next steps. Notice it with

Good lamp and STOPER Down.Check Items.

(10) Test Voltage

- GND: 1.5KV/min at 100Ma

- Signal: 3KV/min at 100Ma

(11) Test time: just 1 second.

(12) Test point

- GND test: Test between Power cord GND and Signal cable

metal GND.

- ESD test: Test between Power cord GND and Live and

neutral.

(13) Leakage current: Set to 0.5Ma(rms)

7. Default Service option

7.1. ADC-Set

▪ R-Gain adjustment Value (default 128)

▪ G-Gain adjustment Value (default 128)

▪ B-Gain adjustment Value (default 128)

▪ R-Offset adjustment Value (default 128)

▪ G-Offset adjustment Value (default 128)

▪ B-Offset adjustment Value (default 128)

8. USB DOWNLOAD (*.epk file download)

(1) Put the USB Stick to the USB socket

(2) Press Menu key, and move OPTION

(3)

(4) Press “FAV” Press 7 times.

(5) Select download file (epk file)

(6) After download is finished, remove the USB stick.

(7) Press “IN-START” key of ADJ remote control, check the

S/W version

- 22 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

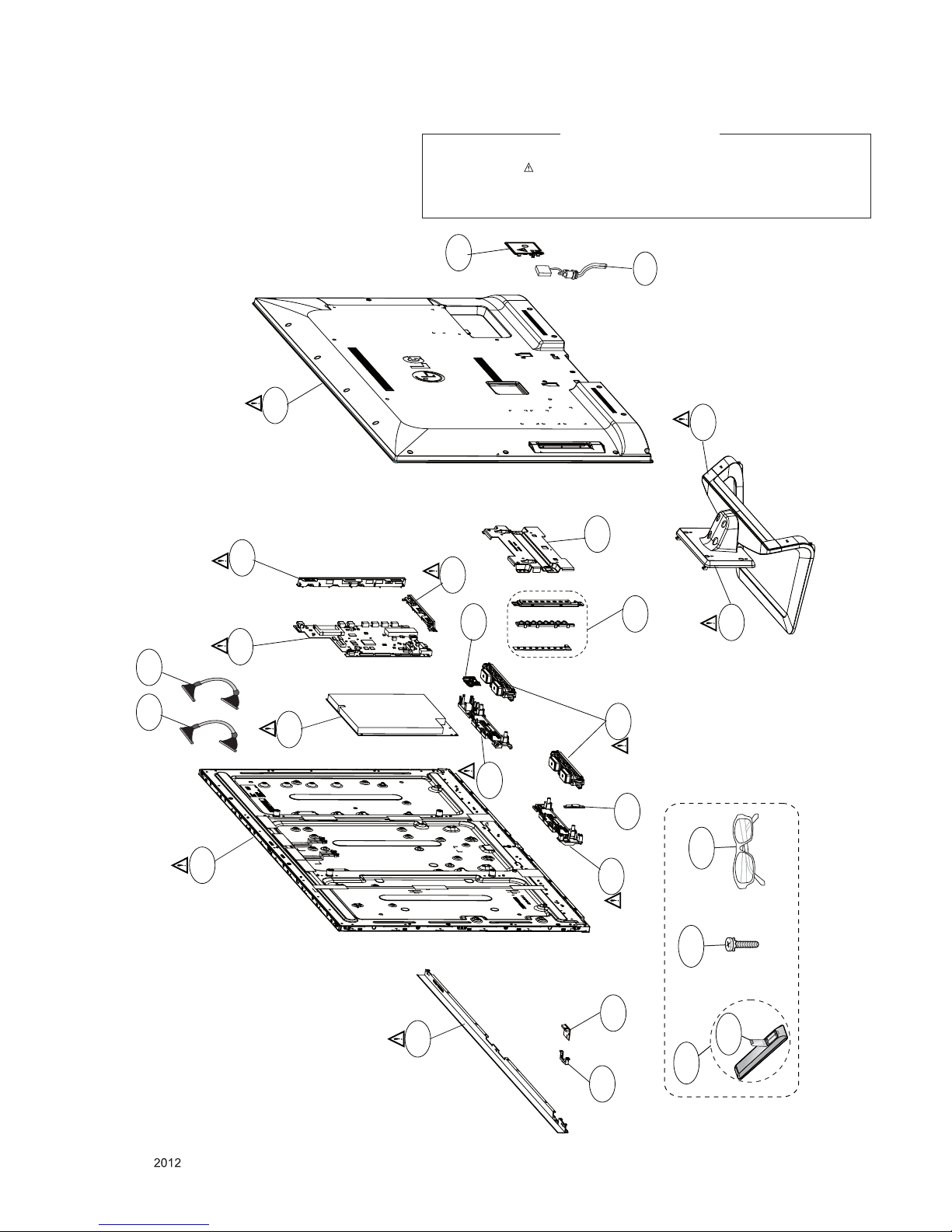

EXPLODED VIEW

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These

parts are identified by in the Schematic Diagram and EXPLODED VIEW.

It is essenti al that these special safet y parts shoul d be replac ed with the same compo nents as

recommended in this manual to prevent X-RADIATION, Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

IMPORTANT SAFETY NOTICE

710

300

501

500

570

560

510

810

700

200

530

540

120

121

122

522

521

400

910

900

A2

A21

A10

AG1

* Set + Stand

* Stand Base + Body

LV1 LV2

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

CI_DATA[5]

CI_DATA[7]

MT5369_TS_OUT[2]

CI_DATA[2]

CI_DATA[4]

CI_ADDR[2]

CI_ADDR[10]

MT5369_TS_OUT[1]

CI_ADDR[13]

FE_TS_DATA[7]

CI_ADDR[5]

EMMC_DATA[7]

EMMC_DATA[6]

FE_TS_DATA[5]

CI_ADDR[8]

CI_DATA[0]

CI_ADDR[6]

CI_ADDR[1]

EMMC_DATA[4]

CI_ADDR[11]

CI_ADDR[12]

CI_DATA[1]

EMMC_DATA[2]

FE_TS_DATA[6]

FE_TS_DATA[0]

CI_ADDR[7]

FE_TS_DATA[4]

MT5369_TS_OUT[4]

CI_DATA[3]

EMMC_DATA[3]

EMMC_DATA[5]

FE_TS_DATA[3]

CI_ADDR[0]

MT5369_TS_OUT[7]

CI_ADDR[3]

CI_DATA[6]

FE_TS_DATA[1]

MT5369_TS_OUT[5]

MT5369_TS_OUT[0]

CI_ADDR[9]

CI_ADDR[14]

FE_TS_DATA[2]

MT5369_TS_OUT[3]

CI_ADDR[4]

MT5369_TS_OUT[6]

MODEL_OPT_2

JTRST#

FE_TS_SYNC

STB_SCL

USB_CTL3

SOC_RX

C116

0.1uF

R150

1K

MODEL_OPT_0

MT5369_TS_VAL

R147

1K

OPT

/CI_CD2

R155

10K

OPT

R166

2.7K

OPT

EMMC_CLK

R151

1K

OPT

MT5369_TS_SYNC

MT5369_TS_IN[1]

R165

4.7K

OSDA0

L/DIM0_MOSI

/USB_OCD3

R172

22

/PCM_CE1

OSDA1

+3.3V_NORMAL

MODEL_OPT_8

MODEL_OPT_6

R148

1K

JTMS

SOC_TX

CI_ADDR[0-14]

FE_TS_VAL

R167

4.7K

L/DIM0_VS

R103

4.7K

MT5369_TS_OUT[0-7]

MT5369_TS_IN[5]

EMMC_DATA[2-7]

R168

4.7K

OPT

R157

4.7K

OPT

R158

33

OPT

MODEL_OPT_1

CI_DATA[0-7]

JTDI

/PCM_IORD

MT5369_MISTRT

MODEL_OPT_1

CI_A_VS1

LED_PWM0

/PCM_REG

MT5369_XTAL_OUT

MT5369_MIVAL_ERR

I2C_SDA5

MT5369_XTAL_IN

AVDD_33SB

JTCLK

MODEL_OPT_5

A_DIM

FE_TS_CLK

USB_CTL2

MT5369_TS_IN[4]

SOC_RESET

/USB_OCD2

MT5369_MCLKI

/USB_OCD1

/PCM_OE

MT5369_TS_CLK

AVDD_33SB

PCM_RST

MODEL_OPT_3

MT5369_TS_IN[6]

USB_CTL1

MODEL_OPT_10

L/DIM0_SCLK

R153

1K

OPT

LED_PWM1

/PCM_IOWR

JTDO

C118

0.1uF

M_REMOTE_TX

OSCL0

VDD3V3

LED_PWM1

/PCM_WE

M_REMOTE_RX

R136 33

MT5369_TS_IN[0]

MODEL_OPT_5

MODEL_OPT_3

MT5369_TS_IN[2]

MT5369_TS_IN[3]

MODEL_OPT_0

+3.3V_NORMAL

ERROR_OUT

MT5369_TS_IN[7]

MODEL_OPT_6

+3.3V_NORMAL

IC104

AT24C256C-SSHL-T

NVRAM_ATMEL

3

A2

2

A1

4

GND

1

A0

5

SDA

6

SCL

7

WP

8

VCC

FE_TS_DATA[0-7]

MODEL_OPT_9

R174

10K

OPCTRL3

/PCM_WAIT

EMMC_CLK

/PCM_IRQA

R169 10K

OPT

R171

22

R170

22

OSCL1

PWM_DIM2

R137 33

R161

4.7K

OPT

R178

4.7K

OPT

PWM_DIM1

/CI_CD1

LED_PWM0

M_RFModule_ISP

+3.3V_NORMAL

IR

R154

1K

C117

0.1uF

I2C_SCL5

+3.3V_NORMAL

STB_SDA

X100

27MHz

MT5369_XTAL_OUTMT5369_XTAL_IN

+3.3V_NORMAL

R143 33

MTK_JTAG

JTMS

+3.3V_NORMAL

R144

10K

R152

1K

MTK_JTAG

JTDO

JTRST#

JTCLK

JTDI

AR100

10K

R149

10K

MTK_JTAG

R146

10K

MTK_JTAG

R145

10K

MTK_JTAG

+3.3V_NORMAL

R139

2.7K

OSDA2

I2C_SDA2

R117 33

+3.3V_NORMAL

R115 33

I2C_SDA6

R188

2.7K

I2C_SCL4

I2C_SDA4

OSCL2

I2C_SCL5

R122 33

R160

2.7K

R116 33

I2C_SDA5

R142

2.7K

OSCL0

I2C_SCL2

STB_SDA

R111 33

R123 33

R134

2.7K

I2C_SDA1

I2C_SCL3

R114 33

R110 33

OSCL1

I2C_SCL6

I2C_SDA3

R113 33

R164

2.7K

OSDA1

R173

2.7K

R156

2.7K

R118 33

R185

2.7K

OSDA0

R177

2.7K

R112 33

I2C_SCL1

R121 33

STB_SCL

R176

10K

SC_ID_SOC

M_RFModule_RESET

R162

10K

R163

10K

/TU_RESET

RF_SWITCH_CTL

AV1_CVBS_DET

OPCTRL3

DSUB_DET

HP_DET

COMP1_DET

SC_DET

OPCTRL_1_SCL

OPCTRL_11_SCL

/S2_RESET

SMARTCARD_VCC

SMARTCARD_RST

SMARTCARD_DATA

SMARTCARD_CLK

SMARTCARD_DET

SMARTCARD_PWR_SEL

SMARTCARD_VCC

SMARTCARD_PWR_SEL

SMARTCARD_RST

SMARTCARD_CLK

SMARTCARD_DATA

SMARTCARD_DET

+3.3V_NORMAL

R140

4.7K

MTK_DVB_T2_TUNER

R106

4.7K

MTK_Int_FRC/URSA5

R135

4.7K

MTK_CP_BOX

R101

4.7K

MTK_FRC3/URSA5

R189

4.7K

MTK_EPI

R186

4.7K

MTK_DVB_C2_TUNER

R125

4.7K

MTK_OPTIC_Tx_IC

R130

4.7K

MTK_3D_DEPTH_IC

R108

4.7K

MTK_FHD

R175

4.7K

MTK_DVB_S_TUNER

R132

4.7K

MTK_DDR_768MB

R190

4.7K

MTK_NON_EPI

R127

4.7K

MTK_NON_OPTIC_Tx_IC

R133

4.7K

MTK_DDR_DEFAULT

R129

4.7K

MTK_NON_3D_DEPTH_IC

R141

4.7K

MTK_NON_DVB_T2_TUNER

R102

4.7K

MTK_NO_FRC/Int_FRC

R138

4.7K

MTK_NON_CP_BOX

R109

4.7K

MTK_HD

R187

4.7K

MTK_NON_DVB_C2_TUNER

R184

4.7K

MTK_NON_DVB_S_TUNER

R107

4.7K

MTK_NO_FRC/FRC3

EPI_LOCK6

OPCTRL_0_SDA

OPCTRL_10_SDA

OPCTRL_1_SCL

OPCTRL_11_SCL

OPCTRL_0_SDA

OPCTRL_10_SDA

C101

0.1uF

16V

R191 22

+3.3V_NORMAL

R192 22

I2C_SCL1

R181 4.7K

I2C_SDA1

+3.3V_NORMAL

MDS62110213

M100

MTK_H/S_3.5T

MDS62110213

M101

MTK_H/S_3.5T

MDS62110213

M102

MTK_H/S_3.5T

MDS62110213

M103

MTK_H/S_3.5T

+3.3V_NORMAL

R159 4.7K

P100

12507WS-12L

MTK_JTAG

1

2

3

4

5

6

7

8

9

10

11

12

13

C120

2.2uF

10V

OPT

R193

10K

NON_EU

OPC_EN

/S2_RESET

R128

1.2K

R131

1.2K

EMMC_DATA[0]

EMMC_DATA[1]

EMMC_CMD

R119

0

IC104-*1

M24256-BRMN6TP

NVRAM_ST

3

E2

2

E1

4

VSS

1

E0

5

SDA

6

SCL

7

WC

8

VCC

C115

24pF

C113

24pF

AMP_RESET_SOC AMP_RESET_N

R124

33

AMP_RESET_BY_SOC

AMP_RESET_SOC

IC105

LGE2112

MT5369_NON_RM

JTCK

AP14

JTDI

AM14

JTDO

AR14

JTMS

AR15

JTRST

AN14

OSDA0

AP12

OSCL0

AN12

OSDA1

AP15

OSCL1

AN15

XTALI

AT34

XTALO

AU34

AVDD33_XTAL_STB

AK27

AVSS33_XTAL_STB

AH26

AVDD33_VGA_STB

AK18

AVSS33_VGA_STB

AK17

AVDD33_PLLGP

AK23

AVSS33_PLLGP

AM27

AVDD10_LDO

AJ20

GPIO0

H32

GPIO1

F37

GPIO2

F36

GPIO3

G37

GPIO4

G36

GPIO5

G35

GPIO6

G34

GPIO7

H34

GPIO8

L34

GPIO9

L32

GPIO10

K33

GPIO11

K32

GPIO12

H33

GPIO13

L35

GPIO14

K36

GPIO15

J32

GPIO16

J34

GPIO17

K34

GPIO18

K35

GPIO19

K37

GPIO20

J36

GPIO21

J37

GPIO22

J35

GPIO23

J33

GPIO24

G33

GPIO25

H35

GPIO26

H31

GPIO27

F34

GPIO28

E36

GPIO29

N33

GPIO30

P32

GPIO31

M35

GPIO32

M37

GPIO33

M33

GPIO34

F35

GPIO35

E35

GPIO36

E37

GPIO37

N32

GPIO38

M34

GPIO39

M36

GPIO40

M32

GPIO41

L33

GPIO42

E33

GPIO43

E32

GPIO44

F32

GPIO45

A29

GPIO46

D31

GPIO47

C31

GPIO48

E30

GPIO49

E31

GPIO50

F31

GPIO51

E29

GPIO52

AP9

GPIO53

AT9

GPIO54

AR9

GPIO55

AU9

ADIN0_SRV

AN23

ADIN1_SRV

AN24

ADIN2_SRV

AP23

ADIN3_SRV

AR23

ADIN4_SRV

AU23

ADIN5_SRV

AT23

ADIN6_SRV

AM24

ADIN7_SRV

AM23

U0TX

AR18

U0RX

AP18

U1RX

AU16

U1TX

AT16

POWE

A35

POOE

C33

POCE1

B34

POCE0

D33

PDD7

D29

PDD6

C30

PDD5

D30

PDD4

B31

PDD3

A31

PDD2

B32

PDD1

A32

PDD0

C32

PARB

D32

PACLE

A34

PAALE

C34

EMMC_CLK

C29

OPWRSB

AM20

ORESET

AM22

OIRI

AU21

FSRC_WR

D27

STB_SCL

AT21

STB_SDA

AR21

DEMOD_RST

T34

DEMOD_TSCLK

T32

DEMOD_TSDATA0

T36

DEMOD_TSDATA1

U36

DEMOD_TSDATA2

T33

DEMOD_TSDATA3

T30

DEMOD_TSDATA4

V33

DEMOD_TSDATA5

V32

DEMOD_TSDATA6

V31

DEMOD_TSDATA7

V30

DEMOD_TSSYNC

T35

DEMOD_TSVAL

T31

CI_INT

N36

CI_TSCLK

T37

CI_TSDATA0

R35

CI_TSSYNC

R37

CI_TSVAL

R36

PVR_TSCLK

R34

PVR_TSVAL

R32

PVR_TSSYNC

R33

PVR_TSDATA0

P33

PVR_TSDATA1

P34

SPI_CLK1

N37

SPI_CLK

P35

SPI_DATA

N34

SPI_CLE

N35

OPWM2

AU12

OPWM1

AT12

OPWM0

AR12

SD_D0

A37

SD_D1

C35

SD_D2

A36

SD_D3

B35

SD_CMD

B36

SD_CLK

B37

LDM_CS

AT11

LDM_CLK

AU11

LDM_VSYNC

AR10

LDM_DO

AM9

LDM_DI

AP10

LED_PWM1

AN22

LED_PWM0

AP21

OPCTRL11

AU20

OPCTRL10

AT20

OPCTRL9

AN18

OPCTRL8

AP20

OPCTRL7

AM18

OPCTRL6

AN19

OPCTRL5

AP19

OPCTRL4

AR19

OPCTRL3

AN21

OPCTRL2

AM19

OPCTRL1

AN20

OPCTRL0

AR20

IC104-*2

R1EX24256BSAS0A

NVRAM_RENESAS

3

A2

2

A1

4

VSS

1

A0

5

SDA

6

SCL

7

WP

8

VCC

R100

10K

AMP_RESET_BY_SOC

C114

0.1uF

16V

C105

0.1uF

OPT

C106

0.1uF

OPT

C100

0.1uF

OPT

C103

0.1uF

OPT

C102

0.1uF

OPT

C104

0.1uF

OPT

R120

1K

PWM1_PULL_DOWN_1K

R126

1K

PWM2_PULL_DOWN_1K

IC100

M24C16-R

HDCP_EEPROM_ST

3

NC_3

2

NC_2

4

VSS

1

NC_1

5

SDA

6

SCL

7

WC

8

VCC

IC100-*1

24LC16B

HDCP_EEPROM_MICRO

3

A2

2

A1

4

VSS

1

A0

5

SDA

6

SCL

7

WP

8

VCC

R105

4.7K

OPT

R104

4.7K

OPT

M_RFModule_ISP

C108

2.2uF

10V

C107

2.2uF

10V

IC105-*1

LGE2112-AL

MT5369_RM

DDRV_44

AC1

DDRV_45

AC2

DDRV_1

A3

DDRV_2

A4

DDRV_5

B4

DDRV_8

C4

DDRV_10

D4

DDRV_4

B3

DDRV_7

C3

DDRV_46

AC3

DDRV_47

AC4

MEMTP

G10

MEMTN

G9

RVREF_B

G13

RVREF_A

G21

ARCKE

F10

ARCLK1

D9

ARCLK1

C9

ARCLK0

A20

ARCLK0

A21

ARODT

E18

ARRAS

F17

ARCAS

E17

ARCS

E16

ARWE

D14

ARRESET

B14

ARBA0

A13

ARBA1

G11

ARBA2

D16

ARCSX

F18

ARA14

C15

ARA13

A15

ARA12

F13

ARA11

C14

ARA10

F11

ARA9

E15

ARA8

D13

ARA7

B15

ARA6

E14

ARA5

F16

ARA4

E13

ARA3

B13

ARA2

A14

ARA1

F14

ARA0

F15

ARDQM0

C19

ARDQS0

C21

ARDQS0

B21

ARDQ0

C23

ARDQ1

B17

ARDQ2

D23

ARDQ3

C17

ARDQ4

D24

ARDQ5

C16

ARDQ6

C24

ARDQ7

D15

ARDQM1

D21

ARDQS1

B20

ARDQS1

C20

ARDQ8

A17

ARDQ9

A23

ARDQ10

D17

ARDQ11

B23

ARDQ12

D20

ARDQ13

D22

ARDQ14

D19

ARDQ15

C22

ARDQM2

A7

ARDQS2

B9

ARDQS2

A9

ARDQ16

C12

ARDQ17

D6

ARDQ18

B12

ARDQ19

C5

ARDQ20

C13

ARDQ21

A5

ARDQ22

A12

ARDQ23

B5

ARDQM3

E10

ARDQS3

C8

ARDQS3

D8

ARDQ24

C6

ARDQ25

D10

ARDQ26

D7

ARDQ27

C11

ARDQ28

C7

ARDQ29

C10

ARDQ30

B7

ARDQ31

B10

AVDD33_MEMPLL

N14

AVSS33_MEMPLL

N15

DVSS_50

R1

DVSS_48

P21

MDS62110214

M104

MTK_H/S_9.5T

8

MID_MAIN_1

2011.12.13

LG FRC2

3D DEPTH

T2 Tuner

MODEL OPTION 8 is just for CP Box

It should not be appiled at MP

NON_3D_Depth_IC

S Tuner

SoC

internal

FRC

SOC -> CI SLOT

NON_OPTIC

CI SLOT -> SOC

SOC -> CI SLOT

MODEL_OPT_9

OPTIC

1

MODEL_OPT_7

MODEL_OPT_3

Support

FHD

Write Protection

- Low : Normal Operation

- High : Write Protection

Disable

Reserved

DDR_768MB

EPI

Reserved

MODEL_OPT_2

DDR

MODEL_OPT_6

HIGH

MODEL_OPT_8

CI SLOT -> SOC

MODEL_OPT_0

Not Support

Default

1

Not Support

CP BOX

MODEL_OPT_5

0

0

CI SLOT -> SOC

Support

Enable

LOW

1

NO_FRC

NVRAM

Model Option

0

Close to eMMC Flash

(IC8100)

MODEL_OPT_10

0

CI SLOT -> SOC

HD

STRAPPING LED_PWM0 LED_PWM1 OPCTRL3

ICE mode + 27M + Serial boot 0 0 0

ICE mode + 27M + ROM to Nand boot 0 0 1

ICE mode + 27M + Rom to eMMC boot 0 1 0

from eMMC pins (share pins w/s NAND)

ICE mode + 27M + ROM to eMMC boot 0 1 1

from SDIO pins

DDR_Default

EXTERNAL DEMOD

-> SOC

MODEL_OPT_1

1

MODEL_OPT_4

3D_Depth_IC

X-TAL

JTAG

I2C

I2C_1 : AMP, L/DIMMING,HDCP KEY

I2C_2 : T-CON

I2C_3 : MICOM

I2C_4 : S/Demod,T2/Demod, LNB

I2C_5 : NVRAM

I2C_6 : TUNER_MOPLL(T/C,ATV)

FOR JAPAN

FOR JAPAN

HDCP EEPROM

Support

Not Support

HEAT SINK SMD GASKET

5V Tolerance

MODEL_OPT_4

MODEL_OPT_4

Crystal Matching Test result

: 27pF -> 20pF -> 24pF

IC

EAX6430790* : LD22* / LC22*

EAX6443420* : LT22* / LJ22* / LA22* / LB22*

MODEL_OPT_7

MODEL_OPT_7

Copyright ⓒ 2012 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LGE Internal Use Only

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

CI_ADDR[3]

CI_DATA[7]

CI_ADDR[4]

CI_DATA[2]

MT5369_TS_OUT[1]

CI_ADDR[7]

CI_ADDR[8]

CI_ADDR[10]

CI_ADDR[14]

CI_DATA[5]

MT5369_TS_OUT[6]

CI_DATA[6]

MT5369_TS_OUT[4]

CI_DATA[3]

CI_ADDR[12]

MT5369_TS_OUT[7]

CI_ADDR[0]

CI_ADDR[5]

MT5369_TS_OUT[2]

CI_ADDR[11]

MT5369_TS_OUT[5]

CI_DATA[0]

CI_ADDR[1]

CI_DATA[1]

CI_DATA[4]

CI_ADDR[13]

CI_ADDR[6]

MT5369_TS_OUT[0]

CI_ADDR[2]

MT5369_TS_OUT[3]

CI_ADDR[9]

C323

0.1uF

MT5369_TS_IN[0]

TP324

C343

100pF

50V

C3690.01uF

HDMI_HPD_3_JACK

TP337

AV1_R_IN_SOC

D0+_HDMI2_JACK

TXA4P

TP353

COMP1_Pr_SOC

R3791.2K

TP321

R358100

SCART_Rout_SOC

TP345

C355

0.047uF

T/C&AT&CHB

DTV/MNT_V_OUT_SOC

C3740.01uF

R323

22

TP378

C397

1200pF

C359 0.047uF

TP374

TXD1P

C398

1200pF

R330

75

1%

C382

0.1uF

C354

0.1uF

/PCM_WE

MT5369_TS_IN[5]

TP375

R311 30K

HP_LOUT_AMP

VDD3V3

TXCCLKP

HP_ROUT_AMP

MT5369_TS_IN[4]

HDMI_HPD_2_JACK

TP372

TXA0N

D2+_HDMI3_JACK

HP_ROUT_MAIN

TP326

C307

0.1uF

C336

1uF

10V

T/C&AT&CHB

R373

0

C384

10pF

50V

TXDCLKN

IF_AGC

C361 1uF

CK+_HDMI4_JACK

TXD0P

R3781.2K

VDD3V3

SC_R_SOC

R3521.2K

HP_OUT

D2-_HDMI3_JACK

TXC1P

PC_R_IN_SOC

C380

0.1uF

DSUB_VSYNC

TXD2N

TP322

TP307

TXB2P

C400

1200pF

TP350

PC_L_IN_SOC

+1.2V_MTK_AVDD

C3710.01uF

AV1_CVBS_IN_SOC

TXC1N

TP329

+1.2V_MTK_AVDD

R341 100

R309

100K

TXD0N

PC_R_IN

EPHY_TDP

C391

27pF

50V

OPT

TP311

R371 100

D2-_HDMI4_JACK

R310 30K

TP318

SCART_Rout_SOC

C386

27pF

50V

OPT

TXB1P

DSUB_HSYNC_SOC

AUD_LRCH

R300

470K

OPT

DDC_SDA_1_SOC

TP313

TXC2N

TP348

C332

0.22uF

10V

HP_OUT

C3660.01uF

TXC0P

SC_B_SOC

CK-_HDMI2_JACK

OSCL2

OSDA2

D1-_HDMI2_JACK

C302

0.1uF

R354

75

1%

DSUB_VSYNC_SOC

C392

27pF

50V

OPT

C395

1200pF

HP_OUT

DDC_SCL_4_JACK

R335 51

T/C&AT&CHB

TXDCLKP

TXA1P

EPHY_RDP

TP365

DAC_3V3

C385

27pF

50V

OPT

PC_L_IN_SOC

SCART_Lout_SOC

5V_HDMI_2_JACK

R368 100

AV1_L_IN_SOC

TP355

+1.2V_MTK_AVDD

C331

0.22uF

10V

HP_OUT

C383

1200pF

HP_OUT

TP300

D1+_HDMI3_JACK

R3701.2K

HP_OUT

SC_G_SOC

TP341

D0-_HDMI1_SOC

DDC_SCL_2_JACK

R343

24K

1%

VDD3V3

VDD3V3

SC_G_SOC

TP370

AV1_R_IN

C341

0.047uF

T/C&AT&CHB

TP308

C393

22pF

OPT

D0+_HDMI1_SOC

R367 100

C387

22pF

OPT

TXA4N

VDD3V3

R372

0

TP330

C308

0.1uF

TP351

TP366

/CI_CD1

C319

10uF

16V

R362100

TP360

TXD3P

D0+_HDMI4_JACK

TP334

MT5369_MISTRT

C3701500pF

R301

470K

OPT

D1+_HDMI1_SOC

D2+_HDMI2_JACK

C314

100pF

50V

OPT

COMP1_Pr_SOC

TXB1N

SC_L_IN_SOC

C340

47pF

50V

C364

0.1uF

ARC

TP317

SC_DET

C344

27pF

50V

OPT

TXA3N

C300

560pF

50V

OPT

SPDIF_OUT

TP359

C301

560pF

50V

OPT

D0-_HDMI4_JACK

C351

0.1uF

IF_P

TU_CVBS

WIFI_DM

TXD4N

R334 51

T/C&AT&CHB

R3500

R357100

TXA1N

TXACLKP

TXC0N

L303

BLM18PG121SN1D

HP_OUT

TUNER_SIF

TP338

/PCM_IRQA

MT5369_MIVAL_ERR

SC_R_SOC

TP320

DDC_SCL_3_JACK

R324

22

C316

0.1uF

TP373

R3511.2K

HP_OUT

MT5369_TS_IN[6]

MT5369_TS_IN[7]

C337 1uF

10V

T/C&AT&CHB

/PCM_REG

TP352

VDD3V3

HDMI_HPD_1_SOC

EPHY_RDN

WIFI_DP

C3720.01uF

C3730.01uF

R308

1.2K

OPT

R366 100

+1.2V_MTK_AVDD

TXA2P

C3670.01uF

D2-_HDMI2_JACK

DSUB_G+

R328

470K

OPT

TP314

DDC_SDA_2_JACK

D1+_HDMI4_JACK

+1.2V_MTK_AVDD

TP335

VDD3V3

C399

1200pF

L302

BLM18PG121SN1D

HP_OUT

D2+_HDMI1_SOC

R353

75

1%

AUDIO_R_OUT_COMMERCIAL

TP356

PCM_5V_CTL

TP336

R31524K

D1+_HDMI2_JACK

MT5369_TS_SYNC

TP328

R322

75

HP_ROUT

MT5369_MCLKI

TP310

R361100

MT5369_TS_VAL

C320

10uF

16V

TP342

CK+_HDMI3_JACK

RGB_DDC_SDA

TXB0N

C390

1200pF

HP_OUT

VDD3V3

R355

75

1%

AUD_LRCK

TP358

HP_LOUT_MAIN

TXC2P

TXB4P

C377

1200pF

HP_OUT

C3680.01uF

TP346

TXB4N

C329

5pF

50V

OPT

EPHY_TDN

TP312

AUD_MASTER_CLK

TXD2P

/PCM_IORD

MT5369_TS_CLK

TP343

TP362

TXACLKN

D2+_HDMI4_JACK

/PCM_CE1

COMP1_Pb_SOC

MT5369_TS_IN[2]

PC_L_IN

R321

75

MT5369_TS_IN[1]

R320

75

TP349

TXA2N

R307 1K

C394

27pF

50V

OPT

C304

0.1uF

DTV/MNT_V_OUT_SOC

R329

470K

OPT

TXCCLKN

TP319

SC_COM_SOC

HDMI_ARC

AV1_R_IN_SOC

R339

2.2K

OPT

AV1_CVBS_IN_SOC

C388

27pF

50V

OPT

HDMI_HPD_4_JACK

R3761.2K

CK-_HDMI4_JACK

D1-_HDMI4_JACK

TP347

CK-_HDMI3_JACK

D0+_HDMI3_JACK

TXB3P

SC_FB_SOC

COMP1_Y_SOC

D1-_HDMI1_SOC

TXB0P

R356100

5V_HDMI_4_JACK

C389

22pF

OPT

CK-_HDMI1_SOC

R374

0

COMP1_Pr

TP377

R3771.2K

C346

10uF

16V

C360 0.047uF

R305

1K

TP367

TP323

C363

1uF

25V

AV1_L_IN

/PCM_OE

TXD3N

C315

100pF

50V

OPT

R3691.2K

HP_OUT

5V_HDMI_3_JACK

TP331

SC_R_IN_SOC

R326

2K

OPT

SC_CVBS_IN_SOC

VDD3V3

C328

0.1uF

SC_COM_SOC

SC_ID_SOC

SC_L_IN_SOC

RGB_DDC_SCL

CK+_HDMI1_SOC

CI_DATA[0-7]

C330

5pF

50V

OPT

C358

0.01uF

50V

MT5369_TS_OUT[0-7]

TP316

D0-_HDMI2_JACK

C345

10uF

16V

CK+_HDMI2_JACK

DDC_SDA_4_JACK

ARC

COMP1_Pb

C303

0.1uF

AV1_CVBS_IN

C3751500pF

R340 100

TP339

SC_FB_SOC

IF_N

R342 10K

T/C&AT&CHB

SC_CVBS_IN_SOC

TXC4N

TP371

R359100

C379

10pF

50V

DDC_SDA_3_JACK

+1.2V_MTK_AVDD

TXA0P

DDC_SCL_1_SOC

DSUB_HSYNC

TXC4P

C378

10pF

50V

TP340

COMP1_Y_SOC

R332 10K

T/C&AT&CHB

C347

0.1uF

AUD_SCK

SC_R_IN_SOC

TP357

C338

560pF

50V

OPT

TP325

PCM_RST

D2-_HDMI1_SOC

D1-_HDMI3_JACK

/PCM_IOWR

SC_B_SOC

TP363

R306

1K

DSUB_VSYNC_SOC

SCART_Lout_SOC

R304

1K

TXC3P

CI_ADDR[0-14]

R303

82

TP315

TP309

TP332

AV1_L_IN_SOC

D0-_HDMI3_JACK

/PCM_WAIT

AUDIO_L_OUT_COMMERCIAL

R363100

5V_HDMI_1_SOC

TP368

TXBCLKN

TXBCLKP

COMP1_Y

TP344

TP361

R3490

OPT

HP_LOUT

CI_A_VS1

DSUB_R+

COMP1_Pb_SOC

/CI_CD2

TP327

TP364

TP369

TXA3P

TXB2N

TXB3N

C342

100pF

50V

TP333

MT5369_TS_IN[3]

C339

560pF

50V

OPT

R325

2K

OPT

R302

180

C352 0.01uF

TXC3N

PC_R_IN_SOC

DSUB_B+

R364100

DSUB_HSYNC_SOC

TXD4P

TP354

C396

33pF

OPT

+5V_NORMAL

TXD1N

C306

0.1uF

MODEL_OPT_10

2D/3D_CTL

MODEL_OPT_2

PCM_5V_CTL

EMMC_RST

MODEL_OPT_8

MODEL_OPT_9

VCOM_DYN

GST_SOC

MCLK_SOC

GCLK_SOC

EO_SOC

PMIC_RESET

C365

0.01uF

C305

1uF

25V

C362

0.1uF

C350

0.1uF

R314

0

R336

0

R331 0

T/C&AT&CHB

R346 0

T/C&AT&CHB

C309

OPT

C311 1uF

10V

C310

33pF

T/C&AT&CHB

C312

33pF

T/C&AT&CHB

C334

47pF

50V

C335

47pF

50V

C333

47pF

50V

USB_DP2

USB_DM2

USB_DP1

USB_DM1

USB_DM3

USB_DP3

IC105

LGE2112

HDMI_CEC

AA32

HDMI_0_SCL

AG33

HDMI_1_SCL

AE33

HDMI_2_SCL

AC33

HDMI_3_SCL

AH32

HDMI_0_SDA

AF33

HDMI_1_SDA

AD33

HDMI_2_SDA

AB33

HDMI_3_SDA

AH33

HDMI_0_PWR5V

AG31

HDMI_1_PWR5V

AE31

HDMI_2_PWR5V

AC31

HDMI_3_PWR5V

AH31

HDMI_0_HPD

AG32

HDMI_1_HPD

AE32

HDMI_2_HPD

AC32

HDMI_3_HPD

AJ32

AVDD12_HDMI_0_RX

AA24

AVDD12_HDMI_1_RX

Y24

AVDD12_HDMI_2_RX

W24

AVDD12_HDMI_3_RX

AB24

AVDD33_HDMI_0_RX

AB29

AVDD33_HDMI_1_RX

AA29

AVDD33_HDMI_2_RX

Y29

AVDD33_HDMI_3_RX

AC29

AVSS33_HDMI_RX_1

AB30

AVSS33_HDMI_RX_2

AD30

AVSS33_HDMI_RX_3

AF31

AVSS33_HDMI_RX_4

AF32

USB_DP_P0

C36

USB_DM_P0

C37

USB_DP_P1

D36

USB_DM_P1

D37

USB_DP_P2

AT13

USB_DM_P2

AU13

USB_DP_P3

AT14

USB_DM_P3

AU14

AVDD33_USB_P0P1

D35

AVDD33_USB_P2P3

AP13

AVSS33_USB_P1

D34

AVSS33_USB_P2

AR13

PCIE11_TXP

W35

PCIE11_TXN

W34

PCIE11_RXN

Y34

PCIE11_RXP

Y35

AVDD12_PCIE11

U24

AVDD33_PCIE11

V24

AVSS12_PCIE11

W30

PCIE11_REFCKN

W36

PCIE11_REFCKP

W37

HDMI_0_RX_0

AG35

HDMI_0_RX_0B

AG34

HDMI_0_RX_1

AG37

HDMI_0_RX_1B

AG36

HDMI_0_RX_2

AF35

HDMI_0_RX_2B

AF34

HDMI_0_RX_C

AH35

HDMI_0_RX_CB

AH34

HDMI_1_RX_0

AE37

HDMI_1_RX_0B

AE36

HDMI_1_RX_1

AD35

HDMI_1_RX_1B

AD34

HDMI_1_RX_2

AC35

HDMI_1_RX_2B

AC34

HDMI_1_RX_C

AE35

HDMI_1_RX_CB

AE34

HDMI_2_RX_0

AB35

HDMI_2_RX_0B

AB34

HDMI_2_RX_1

AA35

HDMI_2_RX_1B

AA34

HDMI_2_RX_2

AA37

HDMI_2_RX_2B

AA36

HDMI_2_RX_C

AC37

HDMI_2_RX_CB

AC36

HDMI_3_RX_0

AK35

HDMI_3_RX_0B

AK34

HDMI_3_RX_1

AJ35

HDMI_3_RX_1B

AJ34

HDMI_3_RX_2

AJ37

HDMI_3_RX_2B

AJ36

HDMI_3_RX_C

AJ33

HDMI_3_RX_CB

AK33

TXVP_0

AT18

TXVN_0

AU18

RXVN_1

AU17

RXVP_1

AT17

PHYLED1

AN16

PHYLED0

AM16

REXT

AD15

AVDD12_REC

AD14

AVDD33_COM

AD16

AVDD33_LD

AD17

AVSS33_LD

AL16

AVSS33_COM

AL15

AVSS12_REC

AL14

IC105

LGE2112

TCON0

F27

TCON1

E27

TCON2

F30

TCON3

F29

TCON4

B27

TCON5

A27

TCON6

B28

TCON7

A28

TCON8

C28

TCON9

D28

TCON10

E28

TCON11

F28

TCON12

B29

AVDD12_LVDS_1

AG6

AVDD12_LVDS_2

AJ6

AVDD12_VPLL

AF6

AVDD33_LVDSB

AE6

AVDD33_LVDSA

AH7

AVSS12_LVDS_2

AJ5

AVSS12_LVDS_1

AG5

AVSS12_VPLL

AF5

AVSS33_LVDSB

AE5

AVSS33_LVDSA

AH5

REXT_VPLL

AG7

AIN0_R_AADC

AU37

AIN0_L_AADC

AU35

AIN1_R_AADC

AT35

AIN1_L_AADC

AT37

AIN2_R_AADC

AU36

AIN2_L_AADC

AP34

AIN3_R_AADC

AT36

AIN3_L_AADC

AR37

AIN4_R_AADC

AR33

AIN4_L_AADC

AP32

AIN5_R_AADC

AR36

AIN5_L_AADC

AP37

AIN6_R_AADC

AR35

AIN6_L_AADC

AP36

AVDD33_AADC

AL31

AVSS33_AADC

AJ28

VMID_AADC

AJ27

MPXP

AN28

ADCINP_DEMOD

AU32

ADCINN_DEMOD

AT32

AVDD33_DEMOD

AD22

AVDD12_DEMOD

AL27

AVSS33_DEMOD

AM28

AVSS12_DEMOD

AJ26

IF_AGC

U35

RF_AGC

U34

LOUTN

AP31

LOUTP

AN30

OSCL2

V35

OSDA2

V34

SC0

AP28

SY0

AR29

CVBS3P

AT30

CVBS2P

AR30

CVBS1P

AR31

CVBS0P

AN29

CVBS_COM

AP30

AVDD33_CVBS_1

AK24

AVDD33_CVBS_2

AK25

AVSS33_CVBS_1

AL25

AVSS33_CVBS_2

AM26

AO3N

AG3

AO3P

AG4

AO4N

AG1

AO4P

AG2

AOCLKN

AF3

AOCLKP

AF4

AO2N

AE3

AO2P

AE4

AO1N

AE1

AO1P

AE2

AO0N

AD1

AO0P

AD2

AE4N

AL3

AE4P

AL4

AE3N

AL1

AE3P

AL2

AECLKN

AK3

AECLKP

AK4

AE2N

AJ3

AE2P

AJ4

AE1N

AJ1

AE1P

AJ2

AE0N

AH3

AE0P

AH4

BO4N

AT2

BO4P

AU2

BO3N

AT1

BO3P

AU1

BOCLKN

AR1

BOCLKP

AR2

BO2N

AP1

BO2P

AP2

BO1N

AN1

BO1P

AN2

BO0N

AM3

BO0P

AM4

BE4N

AT6

BE4P

AU6

BE3N

AP6

BE3P

AR6

BECLKN

AP5

BECLKP

AR5

BE2N

AT4

BE2P

AU4

BE1N

AP4

BE1P

AR4

BE0N

AP3

BE0P

AR3

AR0_ADAC

AN35

AL0_ADAC

AN34

AR1_ADAC

AM32

AL1_ADAC

AM34

AR2_ADAC

AM37

AL2_ADAC

AM33

AR3_ADAC

AM36

AL3_ADAC

AM35

AVDD33_DAC

AG30

AVDD33_DAC1

AF30

AVSS33_DAC

AK30

AVSS33_DAC1

AE30

ALIN

Y33

ASPDIF0

AR16

ASPDIF1

Y32

AOBCK

AR11

AOLRCK

AP11

AOMCLK

AM12

AOSDATA4

AM10

AOSDATA3

AM11

AOSDATA2

AN11

AOSDATA1

AN10

AOSDATA0

AN9

HSYNC

AN25

VSYNC

AM25

RP

AR25

GP

AR24

BP

AU24

COM

AP24

SOG

AT24

VGA_SDA

AR22

VGA_SCL

AP22

COM1

AT26

PB1P

AR26

PR1P

AP26

Y1P

AU26

SOY1

AP25

COM0

AU28

PB0P

AT28

PR0P

AR28

Y0P

AP27

SOY0

AR27

VDACX_OUT

AU30

VDACY_OUT

AP29

AVDD33_VDAC_BG

AD20

AVDD33_VDAC

AD21

AVDD12_RGB

AD19

AVSS33_VDAC_BG