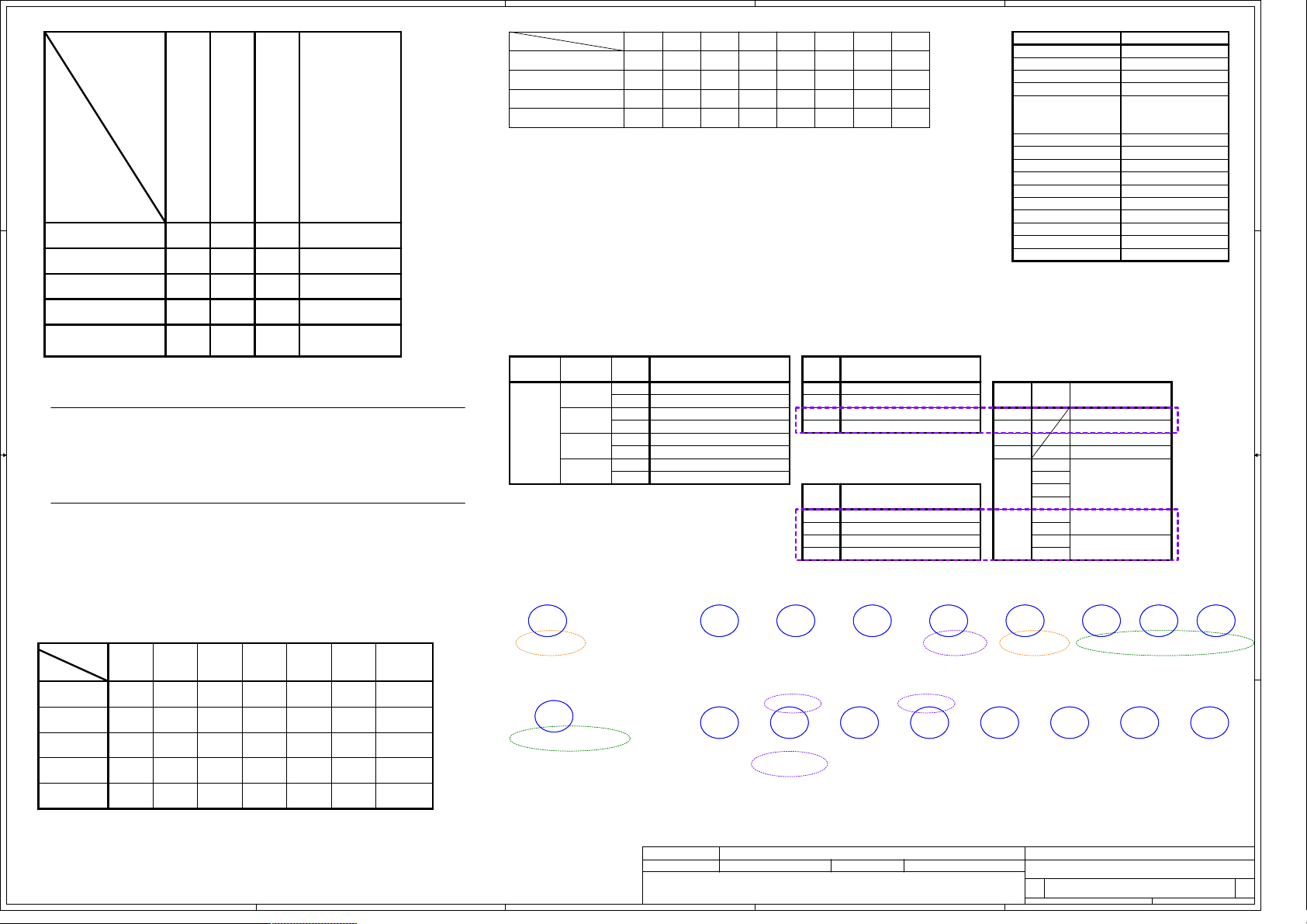

LENOVO YOGA3 AIZY0 Schematics

A

mpal Confidential

Co

del Name : AIZY0

Mo

1 1

File Name : LA-B921PR10

M P/N:43xxxxxxxx

BO

B

C

D

E

Com

2 2

AIZ

Y0 M/B Schematics Document

pal Confidential

Intel Broadwell Y Processor

3 3

2014-09-30

REV:1.0

4 4

curity Classification

curity Classification

curity Classification

Se

Se

Se

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2014/04/10 2017/04/10

2014/04/10 2017/04/10

2014/04/10 2017/04/10

C

mpal Secret Data

mpal Secret Data

mpal Secret Data

Co

Co

Co

Deciphered Date

Deciphered Date

Deciphered Date

mpal Electronics, Inc.

mpal Electronics, Inc.

mpal Electronics, Inc.

Co

Co

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Co

-B921PR10

-B921PR10

-B921PR10

LA

LA

LA

ver Page

ver Page

ver Page

Co

Co

Co

1.0

1.0

1.0

of

136Friday, October 17, 2014

of

136Friday, October 17, 2014

of

136Friday, October 17, 2014

E

5

mpal Confidential

Co

Model Name: AIZY0

File Name: LA-B921PR10

4

3

2

1

D D

eDP Connector

1920 * 1080

uHDMI Connector

Speaker

C C

Digital Array Mic *2

Combo Jack

P.15

MIC BD

IO BD

Realtek ALC233-VB2-CG

WIFI+BT combo

NGFF Half

SPI ROM (8MB)

W25Q64FVSSIQ

Power LED

B B

Battery LED

IO BD

AIZY0 Intel Broadwell Y Block Diagram

Ch0, Ch1

eDP

Click Pad

P.20

P.21

P.15

P.19

P.07

P.23

DDI1

HDAAudio Codec

PCIe

USB2.0

SPI

I2C_1

tel Broadwell-Y

In

30m

m x 16.5mm x 1.05mm

BGA1234

P.04~P12

LPC

USB3.0

USB2.0

SATA

I2C_0

3L 4GB / 8G

DDR

1600MHz 8pcs

P.13~P.14

USB3.0 Connector

USB2.0 Connector

Sensor Hub

ITE IT8350

Touch Panel

Camera 1M HD

Card Reader

Realtek RTS5170

US

B2.0 + DC in

P.19

IO BD

P.16

P.22

P.20

SD BD

P.25

I2C

SD Card Connector

Sensor BD

eCompass

AK8963C

ALS

Sensortek STK2213

G-Sensor

KIONIX KXTJ2-1009

G-Sensor

KIONIX KXTJ2-1009

SD BD

P.16

Power, Novo, Rotation Button

Volume up / down

/ DC

DC

Interface CKT

P.24

IO BD

Thermal Sensor

Power Circuit

A A

P.25~P.33

Nuvoton NCT7718W

P.23

EC

Nuvoton NPCE288

Int. KBD

P.23 P.22

P.17

Hall Sensor

Toshiba TCS20DLR

SSD 128GB / 256GB

NGFF Full

Hall Sensor

Toshiba TCS20DLR

IO BD

P.18

www.schematic-x.blogspot.com

LA-B921PR10

LA-B921PR10

LA-B921PR10

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEE RING DRAWING IS THE PROP RIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEE RING DRAWING IS THE PROP RIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEE RING DRAWING IS THE PROP RIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTE N CONSENT OF COMP AL ELECTRONICS , INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTE N CONSENT OF COMP AL ELECTRONICS , INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTE N CONSENT OF COMP AL ELECTRONICS , INC.

2014/04/10 2017/04/10

2014/04/10 2017/04/10

2014/04/10 2017/04/10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Co

Co

Co

mpal Electronics, Inc.

mpal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

mpal Electronics, Inc.

MB

MB

MB

Block Diagram

Block Diagram

Block Diagram

236Friday, October 17, 2 014

236Friday, October 17, 2 014

1

236Friday, October 17, 2 014

of

of

of

1.0

1.0

1.0

1

tage Rails

Vol

power

plane

A A

State

+5VALW

B+

+1.35V

+3VALW

+5VS

+3VS

+1.5VS

+1.05VS_VTT

+CPU_CORE

+0.675VS

2

STATE

Full ON

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

3

SIGNAL

SLP_S0#

SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS

HIGH HIGH HIGH HIGH

LOW LOW

HIGH

LOWLOWLOW

HIGH

HIGH

ON

ON

ON

ON

ON

OFF

ON

OFFLOW LOW LOW LOW

4

Clock

ON ON

OFF

OFF

OFF

OFF

OFF

OFF

Structure Table

BOM

BTO Item

Connector ME@

76 LEVEL X76@

UNPOP

CPU OPTION CPU1@ ~ CPU8@

EMI POP EMI@

ESD POP ESD@

5

BOM Structure

@

H4G@DRAM Option

E4G@

M4G1@

S8G@ E8G@

M8G@H8G@

@EMI@EMI UNPOP

S4G@

M4G2@

ESD UNPOP @ESD@

WLAN Support ISCT

WLAN No Support ISCT

ISCT@

NoISCT@

S0

S3

S5 S4/AC

S5 S4/ Battery only

B B

S5 S4/AC & Battery

don't exist

EC SM Bus1 address

vice

De

Sm

art Battery

Ch

arger

me Key Button(TS)

Ho

U SM Bus address

CP

De

vice Address

NA NA

C C

Addr ess Addr ess

8b

it:0x60, 7bit:0x30

SMBUS Control Table

Changer

HOST

EC_SMB_CK1

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

SMBCLK

SMBDATA

SML0CLK

SML0DATA

SML1CLK

D D

SML1DATA

NPCE288

+3VLP

NPCE288

+3VS

CPU

+3VALW

CPU

+3VALW

CPU

+3VS

+3VLP

X

X

X

X V

O

O

O

O

O

X

X

V

+3VLP

X

X

X

X

O

O

XX

X

X

XX X

NPCE288

X

X

X

X

+3VS

OO

X

X

EC

SM Bus2 address

vice

De

Th

ermal Sensor NCT7718W

Br

oadwell ULT SML1

U SML0 Bus address

CP

Thermal

HomeKeyBATT

V

+3VALW

X

X

X

sensor

NCT7718W

CPU

X

V

+3VS

X

X

X

XV

V

+3VS

X

X

VX

+3VS

1001100x

Ad

dre ssDevice

US

B 2.0 Port Table

USB 2.0

Port

0

1

2

3

4

5

6

7

HDM

I Logo

45@

ZZZ

45@

ZZZ

I Logo

I Logo

HDM

HDM

RO0000003HM

RO0000003HM

PC

B part

ZZZ003

ZZZ003

PCB 19O LA-B921P REV1 M/B 1

PCB 19O LA-B921P REV1 M/B 1

DA80011R110

DA80011R110

09/30, Change PCB P/N to Rev.1.0

PCB Rev.1A P/N:

DA80011R11A PCB 19O LA-B921P REV1A M/B 1

3 External

USB Port

US

B 2.0 Port (I/O Board)

SB 3.0/2.0 Port (MB)

U

DCIN USB COMBO

rd Reader

Ca

Touch Screen

mera

Ca

Mini Card (WLAN/BT)

nsor Fusion

Se

CPU part

UCPU1

CPU1@

UCPU1

CPU1@

1333/0.6G

1333/0.6G

QGGY

QGGY

SA00007TL00

SA00007TL00

DRA

M

ZZZ3

H4G@

ZZZ3

H4G@

HYNIX

HYNIX

X76581 38L02

X76581 38L02

H5TC4G63AFR-PBA

SA00005AV70

07/01, SA00005HTB0 change to SA000081200

US

Port

SA

Port

UCPU1

CPU2@

UCPU1

CPU2@

1333/0.8G

1333/0.8G

QGGZ

QGGZ

SA00007TM00

SA00007TM00

ZZZ4

M4G2@

ZZZ4

M4G2@

MICRON

MICRON

X76581 38L03

X76581 38L03

MT41K256M16LY-107

SA000081200

B 3.0 Port Table

1

2

SB 3.0 Port (MB)

U

3

4

TA Port Table

3

2

1

NG

0

FF SSD(SATA)

UCPU1

UCPU1

QGGX

QGGX

SA00007TK00

SA00007TK00

ZZZ7

S4G@

ZZZ7

S4G@

SAMSUNG

SAMSUNG

X76581 38L01

X76581 38L01

K4B4G1646Q-HYK0

SA00005JC60

CPU3@

CPU3@

1600/0.8G

1600/0.8G

ZZZ8

ZZZ8

MT41K256M16HA-125:E

SA00005WD60

Port

UCPU1

CPU4@

UCPU1

CPU4@

1Y E0 0.8G

1Y E0 0.8G

QH

QH

SA00007YZ60

SA00007YZ60

07/01, Add QS SA00007YZ40

M4G1@

M4G1@

MICRON

MICRON

X76581 38L04

X76581 38L04

ZZZ9

ZZZ9

SAMSUNG

SAMSUNG

X76581 38L05

X76581 38L05

K4B8G1646Q-MYK0

SA00006AT20

IE Port Table

PC

Lane

1

2

3

4

0

1

5

2

3

0

1

6

2

3

UCPU1

CPU5@

UCPU1

CPU5@

0U E0 1.1G

0U E0 1.1G

QH

QH

SA000084N20

SA000084N20

08/11, Add QS SA000084N0008/11, Add HDMI Logo P/N

S8G@

S8G@

ZZZ10

ZZZ10

X76581 38L07

X76581 38L07

EDJ8416E6MB-GN-F

SA00006AU30

ELPIDA

ELPIDA

E8G@

E8G@

NG

FF WLAN

UCPU1

UCPU1

33 F0 0.8G

33 F0 0.8G

QH

QH

SA00008BP00

SA00008BP00

CPU6@

CPU6@

UCPU1

CPU7@

UCPU1

CPU7@

2V F0 1.1G

2V F0 1.1G

QH

QH

SA00008BU00

SA00008BU00

ZZZ5

M8G@

ZZZ5

M8G@

MICRON

MICRON

X76581 38L08

X76581 38L08

MT41K512M16TNA-125E

SA00006AV20

UCPU1

UCPU1

2R F0 1.2G

2R F0 1.2G

QH

QH

SA00008BI00

SA00008BI00

ZZZ6

H8G@

ZZZ6

H8G@

HYNIX

HYNIX

X76581 38L06

X76581 38L06

H5TC8G63AMR-PBA

SA00006WZ20

CPU8@

CPU8@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL E LECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL E LECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL E LECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

2

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2014/

2014/

2014/

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

04/10 2017/04/10

04/10 2017/04/10

04/10 2017/04/10

Deciphered Date

4

mpal Electronics, Inc.

mpal Electronics, Inc.

mpal Electronics, Inc.

Co

Co

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Co

No

No

No

te List

te List

te List

-B921PR10

-B921PR10

-B921PR10

LA

LA

LA

5

of

336Friday, October 17, 2014

of

336Friday, October 17, 2014

of

336Friday, October 17, 2014

1.0

1.0

1.0

1

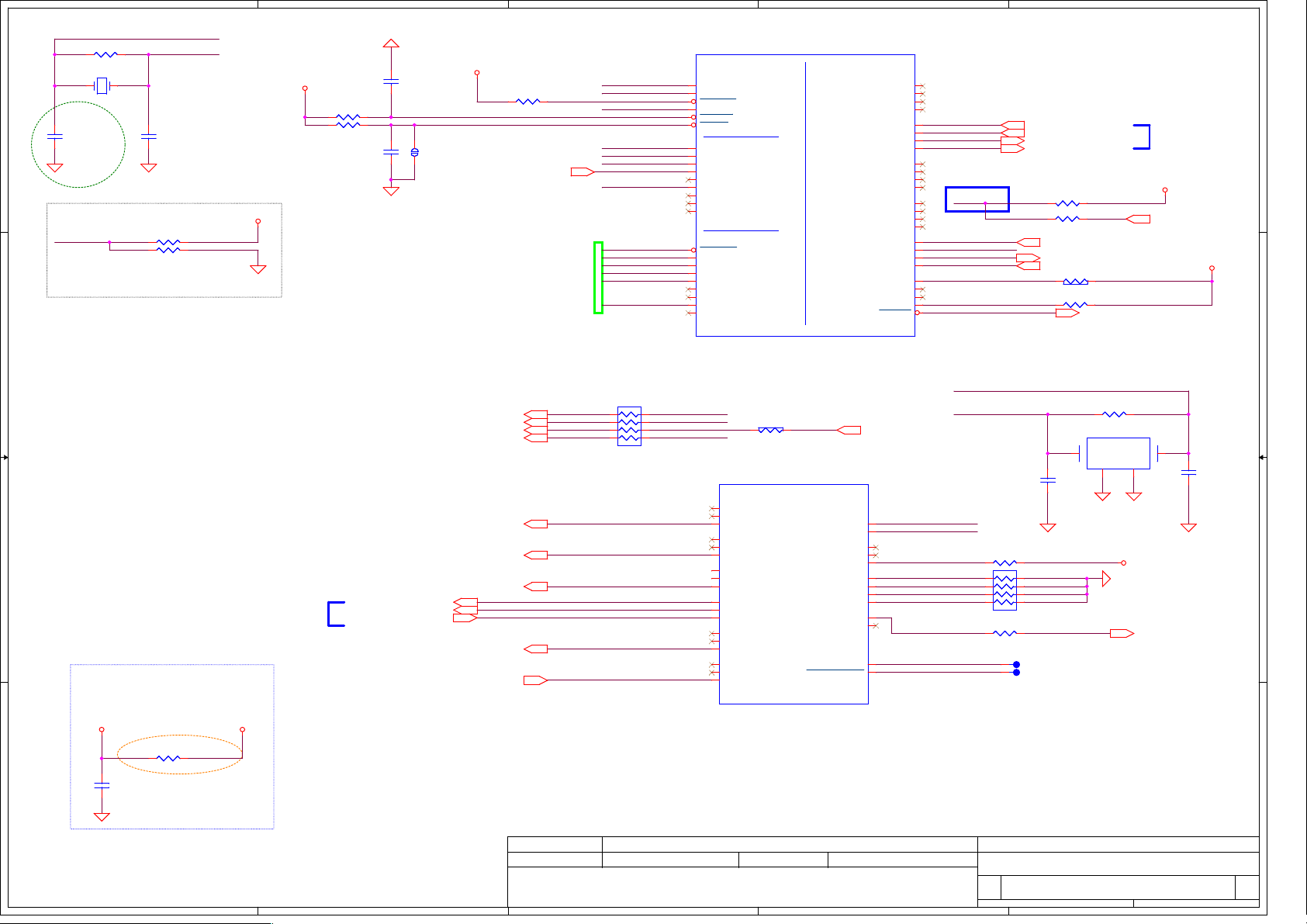

AUXN [20]

AUXP [20]

1

1

24 0_0402_5%@

24 0_0402_5%@

1

2

eD

2

24.9_0402_1%

24.9_0402_1%

2

2

2_CTRL_CK [21]

DDI

2_CTRL_DATA [21]

DDI

DDI

2_HDMI_HPD [21]

EDP_

HPD [20]

P

+VCCIOA_OUT

IN

VPW M

EDP_COMP:

Trace width = 20 mils, Spacing = 25 mil,

Max length = 100 mils

HDMI DDC

5

D D

HDMI

1

RC2 100K_0402_5%@

RC2 100K_0402_5%@

2

ENBKL

4

CPU_

CPU_

CPU_

CPU_

CPU_

CPU_

CPU_

CPU_

DP2_N0[21]

DP2_P0[21]

DP2_N1[21]

DP2_P1[21]

DP2_N2[21]

DP2_P2[21]

DP2_N3[21]

DP2_P3[21]

CPU_DP2_N0

DP2_P0

CPU_

DP2_N1

CPU_

DP2_P1

CPU_

CPU_

DP2_N2

CPU_

DP2_P2

CPU_

DP2_N3

CPU_DP2_P3

ENBKL, BIOS setting default low

RC4

RC4

0_0402_5%

0_0402_5%

1

2

BKCTL

IN

VPW M[20]

ENBKL[1

7]

ENVDD[20]

SENSO

CPU_

PCH_

PCH_

R_HUB_INT#[16,8]

PCH_GPIO53[8]

PCH_

PCH_

PCH_

PCH_

BT

PCH_

GPIO77[8]

GPIO78[8]

GPIO79[8]

_OFF#[19,8]

TP_INT_N[23]

GPIO52[8]

GPIO54[8]

GPIO51[8]

49 0_0402_5%

49 0_0402_5%

RC1

RC1

H_

CATERR#

12

ESD@

ESD@

01

01

CC1

CC1

100P_0402_50V8J

100P_0402_50V8J

08/18, ESD REQUEST

C C

ESD

CPUPWRGD

H_

12

ESD@

ESD@

CC9

CC9

1

1

100P_0402_50V8J

100P_0402_50V8J

07/07, change to mount

10K,3VS

10K,3VS

10K,3VS

10K,3VS

10K,3VS

@10K,3VS

10K,3VS

@10K,3VS

10K,3VS

EDP_

T30

T30

1

2

3

UCPU1A

UCPU1A

AD25

1_TXN_0

DDI

AC25

DDI

1_TXP_0

AD26

DDI

1_TXN_1

AC26

1_TXP_1

DDI

AG25

1_TXN_2

DDI

AE25

DDI

1_TXP_2

AG26

DDI

1_TXN_3

AE26

1_TXP_3

DDI

AD22

DDI

2_TXN_0

AC22

DDI2_TXP_0

AG22

2_TXN_1

DDI

AE22

DDI

2_TXP_1

AD21

DDI

2_TXN_2

AC21

2_TXP_2

DDI

AG21

2_TXN_3

DDI

AE21

DDI

2_TXP_3

BDW-Y-LPDDR3_BGA1234

BDW-Y-LPDDR3_BGA1234

@

@

UCPU1I

UCPU1I

eD

eD

P Sideband

P Sideband

BM41

P_BKLCTL

ED

BR42

P_BKLEN

ED

BN40

ED

P_VDDEN

K35

RQA_N_GPIO77

PI

F31

PI

RQB_N_GPIO78

J34

PI

RQC_N_GPIO79

D38

RQD_N_GPIO80

PI

5

B2

E

PM

M29

IO55

GP

L30

IO52

GP

F35

GP

IO54

H33

GPIO51

C39

IO53

GP

BDW-Y-LPDDR3_BGA1234

BDW-Y-LPDDR3_BGA1234

@

@

UCPU1B

UCPU1B

DDI

DDI

PCI

PCI

ED

ED

P

P

eD

eD

ED

ED

ED

ED

ED

ED

ED

ED

P_RCOMP

ED

P_DISP_UTIL

ED

DDP

DDP

DDP

DDP

Display

Display

P_TXN0

P_TXP0

P_TXN1

P_TXP1

P_TXN2

P_TXP2

P_TXN3

P_TXP3

P_AUXN

P_AUXP

1

1

OF 20

OF 20

B_CTRLCLK

B_CTRLDATA

C_CTRLCLK

C_CTRLDATA

DDP

B_AUXN

C_AUXN

DDP

B_AUXP

DDP

DDP

C_AUXP

B_HPD

DDP

DDP

C_HPD

EDP_HPD

9

9

OF 20

OF 20

AD17

AC17

AG18

AE18

AD18

AC18

AA17

W17

AG16

AE17

AP41

Y21

BP43

BN42

BP41

BR40

Y26

Y25

W26

W25

Y30

Y29

W29

EDP_

CPU_

COMP

INV_PWM

DDI

2_CTRL_CK

DDI

2_CTRL_DATA

2_HDMI_HPD

DDI

HPD

EDP_

TXN0 [20]

EDP_

TXP0 [20]

EDP_

EDP_

TXN1 [20]

EDP_

TXP1 [20]

EDP_

EDP_

RC1

RC1

RC1

RC1

RC125 0_0402_5%@

RC125 0_0402_5%@

closed MCP 1000 mils

CF

T32

T32

H_

CATERR#

T31

2

10K_0402_5%

10K_0402_5%

2

2

2

2

T31

H_

CPUPWRGD

PROCHOT#_R

H_

RCOMP0

SM_

SM_

RCOMP1

SM_

RCOMP2

DDR3

_DRAMRST#

PG_CTRL

DDR_

ESD

PROCHOT#

H_

12

@ESD@

@ESD@

CC9

CC9

2

2

100P_0402_50V8J

100P_0402_50V8J

B B

+1.

35V

12

1

1

RC1

RC1

470_0402_5%

470_0402_5%

_DRAMRST#

DDR3

05VS_VTT

+1.

H_

PROCHOT#[17,25]

DDR3 Compensation Signals:

Trace width = 20 mils, Spacing = 25 mil,

Max length = 500 mils

35V

+1.

1

RC9

RC9

RC13: 120 or 121

2

62_0402_5%

62_0402_5%

H_

PECI[17]

1

RC8

RC8

1

0 56_0402_5%

0 56_0402_5%

RC1

RC1

1

2 200_0402_1%

2 200_0402_1%

RC1

RC1

1

RC1

RC1

3 120_0402_5%

3 120_0402_5%

1

RC1

RC1

5 100_0402_1%

5 100_0402_1%

DDR3

_DRAMRST#[13,14]

41

PR

OC_DETECT

CH3

9

TERR

CA

CK42

I

PEC

CG42

PR

OCPWRGD

1

CH4

OCHOT

PR

CV7

_RCOMP0

SM

CP7

SM

_RCOMP1

CT7

SM

_RCOMP2

AB2

_DRAMRST

SM

BL14

_PG_CNTL1

SM

BDW-Y-LPDDR3_BGA1234

BDW-Y-LPDDR3_BGA1234

@

@

MI

MI

THERMAL

THERMAL

PWR

PWR

DDR3

DDR3

SC

SC

PR

PROC_TMS_CN40

PR

PR

JTAG

JTAG

PR

PR

OC_TCK

OC_TRST

PR

OC_TDI

OC_TDO

BPM

BPM

BPM

BPM_N_3

BPM

BPM

BPM

BPM

2

2

_N_0

_N_1

_N_2

_N_4

_N_5

_N_6

_N_7

OF 20

OF 20

CU4

0

XDP_

1

PRDY_N

XDP_

PREQ_N

XDP_TCK

CPU_

XDP_TMS

CPU_

XDP_TRST_N

CPU_

CPU_

XDP_TDI

CPU_

XDP_TDO

XDP_BPM_N_0

BPM_N_1

XDP_

DY

CR4

EQ

CM41

CN40

CR39

CU36

CU38

CM39

CN38

CK36

CM37

CN36

CR35

CN34

CR34

T33

T33

T34

T34

T40

T40

T41

T41

T51

T51

T56

T56

T57

T57

reserve Via

PU/PD for JTAG signals

_PCH

+3VALW

1

S_PWROK

SY

ESD@

ESD@

CC1

CC1

02

02

100P_0402_50V8J

100P_0402_50V8J

2

RC1

RC1

26 1K_0402_5%@

26 1K_0402_5%@

1

2

S_PWROK [17,8]

SY

08/18, ESD REQUEST

1

CC3

0.1U_0402_16VK7

0.1U_0402_16VK7

1

DDR_PG_CTRL

A A

2

3

CC3

@

@

UC1

UC1

NC

VCC

A

GND

74AUP1G07GW_TSSOP5

74AUP1G07GW_TSSOP5

Y

5

+3VALW

2

1

RC20

5

4

RC20

220K_0402_5%

220K_0402_5%

2

DDR_VTT_PG_CTRL [29]

curity Classification

curity Classification

curity Classification

Se

Se

Se

2014/04/10 2017/04/10

2014/04/10 2017/04/10

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2014/04/10 2017/04/10

3

mpal Secret Data

mpal Secret Data

mpal Secret Data

Co

Co

Co

Deciphered Date

Deciphered Date

Deciphered Date

mpal Electronics, Inc.

mpal Electronics, Inc.

mpal Electronics, Inc.

Co

Co

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

Co

BD

BD

BD

W MCP(1/9) DDI,eDP,PM,XDP

W MCP(1/9) DDI,eDP,PM,XDP

W MCP(1/9) DDI,eDP,PM,XDP

-B921PR10

-B921PR10

-B921PR10

LA

LA

LA

1

1.0

1.0

1.0

of

436Friday, October 17, 2014

of

436Friday, October 17, 2014

of

436Friday, October 17, 2014

5

4

3

2

1

DDR_

A_D[0..63][13]

A_MA[0..15][13]

DDR_

DDR_

A_DQS#[0..7][13]

DDR_

A_DQS[0..7][13]

UCPU1C

D D

C C

B B

A_D0

DDR_

A_D1

DDR_

A_D2

DDR_

DDR_

A_D3

DDR_

A_D4

DDR_

A_D5

DDR_A_D6

A_D7

DDR_

A_D8

DDR_

A_D9

DDR_

DDR_

A_D10

DDR_

A_D11

DDR_

A_D12

DDR_A_D13

A_D14

DDR_

A_D15

DDR_

A_D16

DDR_

DDR_

A_D17

DDR_

A_D18

DDR_

A_D19

DDR_

A_D20

A_D21

DDR_

A_D22

DDR_

A_D23

DDR_

DDR_

A_D24

DDR_

A_D25

DDR_

A_D26

DDR_

A_D27

DDR_A_D28

A_D29

DDR_

A_D30

DDR_

A_D31

DDR_

DDR_

A_D32

DDR_

A_D33

DDR_

A_D34

DDR_

A_D35

A_D36

DDR_

A_D37

DDR_

A_D38

DDR_

DDR_

A_D39

DDR_

A_D40

DDR_

A_D41

DDR_

A_D42

DDR_A_D43

A_D44

DDR_

A_D45

DDR_

A_D46

DDR_

DDR_

A_D47

DDR_

A_D48

DDR_

A_D49

DDR_A_D50

A_D51

DDR_

A_D52

DDR_

A_D53

DDR_

A_D54

DDR_

DDR_

A_D55

DDR_

A_D56

DDR_

A_D57

A_D58

DDR_

A_D59

DDR_

A_D60

DDR_

DDR_

A_D61

DDR_

A_D62

DDR_

A_D63

CT17

CV17

CN14

CP15

CN16

CR16

CM13

CV15

CT13

CP13

CP10

CM10

CN12

CV13

CV10

CT10

CT25

CP25

CN22

CP23

CN24

CV25

CV23

CT23

CN20

CN18

CT21

CT19

CP19

CP21

CV19

CV21

BU2

BW2

BW6

BU4

BW4

BT3

BU6

BT5

BN2

BR2

BN6

BN4

BR6

BR4

BM5

BM3

BT11

BU10

BW12

BW10

BW8

BU8

BU12

BT9

BN8

BR8

BN12

BN10

BR12

BR10

BM11

BM9

UCPU1C

SA_DQ0

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_DQ11

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_DQ26

SA_

SA_

SA_

SA_DQ30

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_DQ45

SA_

SA_

SA_

SA_DQ49

SA_

SA_

SA_

SA_DQ53

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ27

DQ28

DQ29

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ46

DQ47

DQ48

DQ50

DQ51

DQ52

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DDR

DDR

Channel A

Channel A

SA_CLK_N_0

SA_

SA_

CLK_N_1

SA_

SA_

SA_

SA_

SA_

SA_

SA_CS_N_1

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

NO

NOTUSED3

SA_

SA_

SA_

SA_CAA3

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_

SA_DQSN6

SA_

SA_

SA_DQSP1

SA_

SA_

SA_

SA_DQSP5

SA_

SA_

_VREF_CA

SM

_VREF_DQ0

SM

SM

_VREF_DQ1

SM

_VCCDDQG

CLK0

CLK1

CKE0

CKE1

CKE2

CKE3

CS_N_0

ODT0

CAB3

CAB2

CAB1

CAB4

CAB6

CAA5

CAB9

CAB8

CAB5

TUSED4

CAA0

CAA2

CAA4

CAA1

CAB7

CAA7

CAA6

CAB0

CAA9

CAA8

DQSN0

DQSN1

DQSN2

DQSN3

DQSN4

DQSN5

DQSN7

DQSP0

DQSP2

DQSP3

DQSP4

DQSP6

DQSP7

CG4

CG2

CC4

CC6

CH11

CH9

CA12

CA10

CA4

CA2

CA6

CE2

CE4

CC8

CB5

CC2

CF11

CE8

CE12

CF5

CE10

CG8

CG6

CH3

CE6

CB9

CC12

CF3

CG12

CH5

CB3

CF9

CG10

CU16

CR12

CR24

CR20

BV3

BP3

BV9

BP9

CT15

CU12

CU24

CU20

BV5

BP5

BV11

BP11

AP13

AU14

AT13

CC14

DDRA_

ODT0

A_MA0

DDR_

A_MA1

DDR_

DDR_

A_MA2

DDR_

A_MA3

DDR_

A_MA4

DDR_

A_MA5

DDR_A_MA6

A_MA7

DDR_

A_MA8

DDR_

A_MA9

DDR_

DDR_

A_MA10

DDR_

A_MA11

DDR_

A_MA12

DDR_

A_MA13

A_MA14

DDR_

A_MA15

DDR_

DDR_

A_DQS#0

DDR_

A_DQS#1

DDR_

A_DQS#2

DDR_

A_DQS#3

DDR_A_DQS#4

A_DQS#5

DDR_

A_DQS#6

DDR_

A_DQS#7

DDR_

DDR_

A_DQS0

DDR_

A_DQS1

DDR_A_DQS2

A_DQS3

DDR_

A_DQS4

DDR_

A_DQS5

DDR_

A_DQS6

DDR_

DDR_

A_DQS7

T42

T42

T44

T44

10 mil trace width

M_

M_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

+V_DDR_VREF

+V_DDR_VREF

+V_DDR_VREF

CLK_A_DDR#0 [13]

CLK_A_DDR0 [13]

A_CKE0 [13]

A_CKE1 [13]

A_CS0# [13]

A_CS1# [13]

A_RAS# [13]

A_WE# [13]

A_CAS# [13]

A_BS0 [13]

A_BS1 [13]

A_BS2 [13]

CA [13]

DQ0 [13]

DQ1 [14]

B_D0

DDR_

B_D1

DDR_

DDR_

B_D2

DDR_

B_D3

DDR_

B_D4

DDR_B_D5

B_D6

DDR_

B_D7

DDR_

B_D8

DDR_

DDR_

B_D9

DDR_

B_D10

DDR_

B_D11

DDR_B_D12

B_D13

DDR_

B_D14

DDR_

B_D15

DDR_

DDR_

B_D16

DDR_

B_D17

DDR_

B_D18

DDR_

B_D19

B_D20

DDR_

B_D21

DDR_

B_D22

DDR_

DDR_

B_D23

DDR_

B_D24

DDR_

B_D25

DDR_

B_D26

DDR_B_D27

B_D28

DDR_

B_D29

DDR_

B_D30

DDR_

DDR_

B_D31

DDR_

B_D32

DDR_

B_D33

DDR_

B_D34

B_D35

DDR_

B_D36

DDR_

B_D37

DDR_

DDR_

B_D38

DDR_

B_D39

DDR_

B_D40

DDR_

B_D41

DDR_B_D42

B_D43

DDR_

B_D44

DDR_

B_D45

DDR_

DDR_

B_D46

DDR_

B_D47

DDR_

B_D48

DDR_B_D49

B_D50

DDR_

B_D51

DDR_

B_D52

DDR_

B_D53

DDR_

DDR_

B_D54

DDR_

B_D55

DDR_

B_D56

B_D57

DDR_

B_D58

DDR_

B_D59

DDR_

DDR_

B_D60

DDR_

B_D61

DDR_

B_D62

DDR_

B_D63

DDR_

DDR_

DDR_

DDR_

B_D[0..63][14]

B_MA[0..15][14]

B_DQS#[0..7][14]

B_DQS[0..7][14]

UCPU1D

UCPU1D

BK3

DQ0

SB_

BK5

BG6

BJ2

BJ4

BJ6

BG2

BG4

BF3

BF5

BC6

BE2

BE4

BE6

BC2

BC4

BE10

BC10

BE8

BC8

BF11

BC12

BE12

BF9

BJ12

BG12

BJ8

BJ10

BG8

BG10

BK9

BK11

AM1

AH2

AJ3

AM5

AM3

AJ1

AJ5

AH4

AG3

AG1

AD2

AE3

AE1

AG5

AD4

AE5

AM9

AM7

AH8

AJ9

AM11

AJ7

AJ11

AH10

AE11

AG7

AE7

AE9

AG11

AG9

AD8

AD10

SB_

DQ1

SB_

DQ2

DQ3

SB_

DQ4

SB_

SB_

DQ5

SB_

DQ6

DQ7

SB_

DQ8

SB_

SB_

DQ9

SB_DQ10

DQ11

SB_

SB_

DQ12

SB_

DQ13

DQ14

SB_

DQ15

SB_

SB_

DQ16

SB_

DQ17

DQ18

SB_

DQ19

SB_

SB_

DQ20

SB_

DQ21

DQ22

SB_

DQ23

SB_

SB_

DQ24

SB_DQ25

DQ26

SB_

DQ27

SB_

SB_

DQ28

SB_DQ29

DQ30

SB_

SB_

DQ31

SB_

DQ32

DQ33

SB_

DQ34

SB_

SB_

DQ35

SB_

DQ36

DQ37

SB_

DQ38

SB_

SB_

DQ39

SB_

DQ40

DQ41

SB_

DQ42

SB_

SB_

DQ43

SB_DQ44

DQ45

SB_

SB_

DQ46

SB_

DQ47

SB_DQ48

DQ49

SB_

DQ50

SB_

SB_

DQ51

SB_DQ52

DQ53

SB_

SB_

DQ54

SB_

DQ55

DQ56

SB_

DQ57

SB_

SB_

DQ58

SB_

DQ59

DQ60

SB_

DQ61

SB_

SB_

DQ62

SB_

DQ63

DDR

DDR

Channel B

Channel B

SB_

SB_

SB_

SB_

CK_N_0

SB_

CK0

CK_N_1

CK1

SB_

SB_

CKE0

CKE1

SB_

CKE2

SB_

SB_

CKE3

CS_N_0

CS_N_1

ODT0

SB_

SB_

CAB3

SB_

CAB2

CAB1

SB_

SB_

CAB4

SB_

CAB6

CAA5

SB_

SB_

CAB9

SB_CAB8

CAB5

SB_

TUSED

NO

NO

TUSED

SB_CAA0

CAA2

SB_

SB_

CAA4

SB_

CAA3

CAA1

SB_

CAB7

SB_

SB_

CAA7

SB_

CAA6

CAB0

SB_

CAA9

SB_

SB_

CAA8

DQSN0

SB_

DQSN1

SB_

SB_

DQSN2

SB_DQSN3

DQSN4

SB_

SB_

DQSN5

SB_

DQSN6

SB_DQSN7

DQSP0

SB_

SB_

DQSP1

SB_DQSP2

DQSP3

SB_

SB_

DQSP4

SB_

DQSP5

DQSP6

SB_

DQSP7

SB_

AW6

AW4

AP11

AP9

BA2

BA4

AR8

AP5

AR10

AT11

AU10

BA10

AW12

AW10

AY11

BA12

AU2

AT9

AR4

AU8

AR6

AT5

AT3

BA8

AY3

AW2

AY5

AY9

AU4

AU6

AW8

BA6

AR2

BH5

BD5

BD11

BH11

AK2

AF2

AK8

AF8

BH3

BD3

BD9

BH9

AK4

AF4

AK10

AF10

ODT0

DDRB_

DDR_

B_MA0

DDR_

B_MA1

DDR_

B_MA2

DDR_B_MA3

B_MA4

DDR_

B_MA5

DDR_

B_MA6

DDR_

DDR_

B_MA7

DDR_

B_MA8

DDR_

B_MA9

DDR_

B_MA10

B_MA11

DDR_

B_MA12

DDR_

B_MA13

DDR_

DDR_

B_MA14

DDR_

B_MA15

DDR_

B_DQS#0

DDR_B_DQS#1

B_DQS#2

DDR_

B_DQS#3

DDR_

B_DQS#4

DDR_

DDR_

B_DQS#5

DDR_

B_DQS#6

DDR_

B_DQS#7

B_DQS0

DDR_

B_DQS1

DDR_

B_DQS2

DDR_

B_DQS3

DDR_

DDR_

B_DQS4

DDR_

B_DQS5

DDR_

B_DQS6

B_DQS7

DDR_

CLK_B_DDR#0 [14]

M_

CLK_B_DDR0 [14]

M_

DDR_

B_CKE0 [14]

DDR_

B_CKE1 [14]

B_CS0# [14]

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

B_CS1# [14]

B_RAS# [14]

B_WE# [14]

B_CAS# [14]

B_BS0 [14]

B_BS1 [14]

B_BS2 [14]

T43

T43

BDW-Y-LPDDR3_BGA1234

BDW-Y-LPDDR3_BGA1234

@

@

A A

5

3

3

OF 20

OF 20

BDW-Y-LPDDR3_BGA1234

BDW-Y-LPDDR3_BGA1234

@

@

curity Classification

curity Classification

curity Classification

Se

Se

Se

2014/04/10 2017/04/10

2014/04/10 2017/04/10

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2014/04/10 2017/04/10

3

mpal Secret Data

mpal Secret Data

mpal Secret Data

Co

Co

Co

Deciphered Date

Deciphered Date

Deciphered Date

2

4 OF 20

4 OF 20

mpal Electronics, Inc.

mpal Electronics, Inc.

mpal Electronics, Inc.

Co

Co

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Co

BD

BD

BD

W MCP(2/9) DDRIII

W MCP(2/9) DDRIII

W MCP(2/9) DDRIII

-B921PR10

-B921PR10

-B921PR10

LA

LA

LA

536Friday, October 17, 2014

536Friday, October 17, 2014

536Friday, October 17, 2014

1

1.0

1.0

1.0

of

of

of

2

2

PCH_

SATALED# [8]

1

2

2

GN

D

2

1

FF(SSD)

NG

+3VS

NGFF_SSD_PEDET [18]

10K,3VS

10K,3VS

10K,3VS

10K,3VS

2

3

3

GN

D

4

+V1.05S_AXCK_LCPLL

LPC_KBC [17]

CK_

05S_ASATA3PLL

+V1.

1

CC8

CC8

15P

15P

_0402_50V8J

_0402_50V8J

2

3

RTCX1

PCH_

RTCX2

PCH_

INTRUDER#

SM_

PCH_

INTVRMEN

PCH_

SRTCRST#

PCH_

RTCRST#

BIT_CLK

HDA_

SYNC

HDA_

HDA_

RST#

HDA_

SDIN0

HDA_SDOUT

JTAG_RST#

PCH_

JTAG_TCK

PCH_

JTAG_TDI

PCH_

PCH_

JTAG_TDO

PCH_

JTAG_TMS

TCK_JTAGX

PCH_

EM

RP3

RP3

9

9

1

2

3

4

33_8P4R_5%

33_8P4R_5%

EMI@

EMI@

PCI

ECLKREQ0_N

ECLKREQ1_N

PCI

PCI

ECLKREQ2_N

K_PCIE_WLAN#

CL

K_PCIE_WLAN

CL

PCIECLKREQ4_N

ECLKREQ5_N

PCI

UCPU1E

UCPU1E

SATA

C9

CX1

RT

C7

CX2

RT

J5

IN

TRUDER

H6

IN

TVRMEN

D6

TCRST

SR

A8

CRST

RT

L6

_BCLK_I2S0_SCLK

HDA

L4

HDA

_SYNC_I2S0_SFRM

J9

HDA

_RST_N_I2S_MCLK

L10

_SDI0_I2S0_RXD

HDA

L8

_SDI1_I2S1_RXD

HDA

N3

HDA

_SDO_I2S0_TXD

N5

HDA

_DOCK_EN_N_I2S1_TXD

N7

_DOCK_RST_N__I2S1_ SFRM

HDA

N9

S1_SCLK

I2

CM

7

PC

H_TRST

CK17

H_TCK

PC

CL20

H_TDI

PC

CL18

PC

H_TDO

CK15

PC

H_TMS

P17

VD_P17

RS

G26

VD_G26

RS

CL16

JT

AGX

C5

RS

VD_C5

BDW-Y-LPDDR3_BGA1234

BDW-Y-LPDDR3_BGA1234

@

@

SATA

SAT

RT

RT

Audio

Audio

JTAG

JTAG

C

C

SAT

SAT

SAT

SAT

SATA_TN1_PETN6_L2

SAT

SAT

SAT

SAT

SAT

SAT

SAT

A1GP_SATAPHY_PC_GPIO35

I

8

HDA_

RST#

7

BIT_CLK

HDA_

6

SDOUT

HDA_

5

SYNC

HDA_

AD29

AC29

B33

AD30

AC30

H25

AE30

AG30

P25

AC34

AD34

P27

AE29

AG29

D35

AG33

AE33

G30

1

Cl

Cl

ock Signal

ock Signal

2

6 0_0402_5%

6 0_0402_5%

RC6

RC6

UCPU1F

UCPU1F

CL

KOUT_PCIE_N0

CL

KOUT_PCIE_P0

PCIECLKRQ0_N_GPIO18

KOUT_PCIE_N1

CL

CL

KOUT_PCIE_P1

PCIECLKRQ1_N_GPIO19

CL

KOUT_PCIE_N2

CL

KOUT_PCIE_P2

IECLKRQ2_N_GPIO20

PC

CL

KOUT_PCIE_N3

CL

KOUT_PCIEP3

IECLKRQ3_N_GPIO21

PC

CL

KOUT_PCIE_N4

CL

KOUT_PCIE_P4

IECLKRQ4_N_GPIO22

PC

CL

KOUT_PCIE_N5

CLKOUT_PCIE_P5

IECLKRQ5_N_GPIO23

PC

BDW-Y-LPDDR3_BGA1234

BDW-Y-LPDDR3_BGA1234

@

@

XTAL24_IN

AL24_OUT

XT

RS

VD_BK41

RSVD_BK43

FFCLK_BIASREF

DI

TE

STLOW_AC33

STLOW_AD33

TE

STLOW_N14

TE

TE

STLOW_M15

KOUT_LPC_0

CL

KOUT_LPC_1

CL

CL

KOUT_ITPXDP_P

CLKOUT_ITPXDP

CC4

CC4

_0402_6.3V6K

_0402_6.3V6K

2

CC7

CC7

_0402_6.3V6K

_0402_6.3V6K

4

+RT

RP2

RP2

CVCC

1 2

3 1M_0402_5%

3 1M_0402_5%

RC2

RC2

_SDIN0[15]

HDA

1

2

1

2

CMOS

2

CL

CL

SHORT PADS

SHORT PADS

1

@

@

5

RTCX1

1 2

RC2

RC2

1 10M_0402_5%

1 10M_0402_5%

1

1

YC

YC

1 2

32.768KHZ 12.5PF 9H03200031

32.768KHZ 12.5PF 9H03200031

D D

1

CC5

CC5

18P_0402_50V8J

18P_0402_50V8J

2

PCH_

PCH_

1

CC6

CC6

15P_0402_50V8J

15P_0402_50V8J

2

RTCX2

+RT

CVCC

RC2

RC2

RC24 20K_0402_1%

RC24 20K_0402_1%

1U

1U

2 20K_0402_1%

2 20K_0402_1%

1 2

1

1U

1U

10/8, CC5 change 15P to 18P for RTC timing

To enable the integrated voltage regulator for

CVCC

DCPSUS1, DCPSUS2, DCPSUS3 and

DCPSUS4 this signal must be pulled to

VCCRTC through a weak resistor (for

example, 330 KΩ ±

To disable the integrated voltage regulator,

this signal must be pulled down through a

weak resistor (for example, 330 KΩ ±5%)

and the DCPSUS rails must be powered

externally.

5%).

reserve Via

PCH_INTVRMEN

INTVRMEN (+1.05VA)

*

RC26 330K_0402_5%

RC26 330K_0402_5%

7 330K_0402_5%@

7 330K_0402_5%@

RC2

RC2

HIntegrated VRM enable

Integrated VRM disable

L

+RT

1

2

1

2

Closed MCP 1000 mils

C C

RST_AUDIO#[15]

HDA_

HDA_

BITCLK_AUDIO[15]

HDA_

SDOUT_AUDIO[15]

HDA_

SYNC_AUDIO[15]

10K,3VS

10K,3VS

B B

WL

AN

C Battery

RT

20mils W=20mils

W=

+RTCVCC

+RTCBATT

CL

CL

WL

10K,3VS

K_PCIE_WLAN#[1 9]

K_PCIE_WLAN[19]

AN_CLKREQ#[19,8]

10K,3VS

10K,3VS

10K,3VS

IECLKREQ0_N[8]

PC

PC

IECLKREQ1_N[8]

PC

IECLKREQ2_N[8]

PC

IECLKREQ4_N[8]

IECLKREQ5_N[8]

PC

2

A_RN0_PERN6_L3

A_RP0_PERP6_L3

A_TN0_PETN6_L3

SAT

A_TP0_PETP6_L3

A_RN1_PERN6_L2

A_RP1_PERP6_L2

A_TP1_PETP6_L2

SAT

A_RN2_PERN6_L1

A_RP2_PERP6_L1

A_TN2_PETN6_L1

SAT

A_TP2_PETP6_L1

A_RN3_PERN6_L0

A_RP3_PERP6_L0

A_TN3_PETN6_L0

SATA_TP3_PETP6_L0

SAT

A0GP_GPIO34

A2GP_GPIO36

SAT

A3GP_GPIO37

SAT

SAT

A_IREF

VD_R34

RS

VD_R32

RS

SAT

A_RCOMP

SAT

ALED

5

5

OF 20

OF 20

ME_

EN [17]

AR44

AP45

BK41

BK43

A38

AC33

AD33

N14

M15

K15

L14

AE34

AG

34

6 OF 20

6 OF 20

V36

V38

W43

AA43

T37

T39

T43

V42

Y38

W39

T41

W41

W37

Y36

AB42

AA41

F29

H29

D33

L26

L42

R34

R32

L44

C3

0

XT

AL24_IN

XTAL24_OUT

K_BIASREF

XCL

TE

STLOW1

TE

STLOW2

STLOW3

TE

STLOW4

TE

CL

KOUT_LPC0

K_BCLK_ITP#

CL

K_BCLK_ITP

CL

INTEL suggest when no use

need PU, if this pin set GPI

GPIO35

PCH_

PCH_GPIO34

GPIO35

PCH_

GPIO36

PCH_

GPIO37

PCH_

SAT

A_IREF

A_RCOMP

SAT

SATALED#

PCH_

XT

AL24_IN

XT

AL24_OUT

15P_0402_50V8J

15P_0402_50V8J

1

7 3.01K_0402_1%

7 3.01K_0402_1%

RC3

RC3

1

2

3

4

RP4

RP4

0 10K_8P4R_5%

0 10K_8P4R_5%

2

RC3

RC3

8 22_0402_5%

8 22_0402_5%

A_PRX_DTX_N1 [18]

SAT

A_PRX_DTX_P1 [18]

SAT

SAT

A_PTX_DRX_N1 [18]

SAT

A_PTX_DRX_P1 [18]

1

5 10K_0402_5%

5 10K_0402_5%

RC2

RC2

RC1

RC1

RC2

RC2

SATA_COMP:

Trace width = 15 mils, Spacing = 12 mil,

Max length = 500 mils

CC9

CC9

2

8

7

6

5

1

T49

T49

T50

T50

2

1

2

RC2

RC2

8 0_0402_5%@

8 0_0402_5%@

GPIO34 [8]

PCH_

PCH_

GPIO36 [8]

PCH_

GPIO37 [8]

1

27 0_0603_5%

27 0_0603_5%

1

9 3.01K_0402_1%

9 3.01K_0402_1%

RC3

RC3

4 1M_0402_5%

4 1M_0402_5%

YC

YC

1

1

1

2

24MHZ_12PF_7V24000020

24MHZ_12PF_7V24000020

1

RC39 806_0402_1%

RC39 806_0402_1%

1

C5265

C5265

1U_0402_6.3V6K

A A

1U_0402_6.3V6K

2

2

08/21, RC39 change to 806 ohm

Safty suggestion remove EE side ,Keep PWR side

curity Classification

curity Classification

curity Classification

Se

Se

Se

2014/04/10 2017/04/10

2014/04/10 2017/04/10

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2014/04/10 2017/04/10

3

mpal Secret Data

mpal Secret Data

mpal Secret Data

Co

Co

Co

Deciphered Date

Deciphered Date

Deciphered Date

mpal Electronics, Inc.

mpal Electronics, Inc.

mpal Electronics, Inc.

Co

Co

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

Co

BD

BD

BD

W MCP(3/9) SATA,HDA,CLK

W MCP(3/9) SATA,HDA,CLK

W MCP(3/9) SATA,HDA,CLK

-B921PR10

-B921PR10

-B921PR10

LA

LA

LA

1

1.0

1.0

1.0

of

636Thursday, October 23, 2014

of

636Thursday, October 23, 2014

of

636Thursday, October 23, 2014

3

SMBUS

SMBUS

LPC

LPC

SML1ALERT_N_PCHHOT_N_GPIO73

SPI

SPI

SMBALERT_N_GPIO11

L0ALERT_N_GPIO60

SM

C-Link

C-Link

SM

SM

L1CLK_GPIO75

SM

SM

L1DATA_GPIO74

SM

SM

L0DATA

CL

CL

CL

BCLK

BDATA

L0CLK

_CLK

_DATA

_RST

K21

P21

B21

F21

P19

B19

H8

C14

A14

D23

H23

K23

SMBCLK

SM

BDATA

PC

H_GPIO60

SML0CLK

SM

L0DATA

H_GPIO73

PC

L1CLK

SM

SM

L1DATA

C_AD0[17]

LP

LP

C_AD1[17]

LP

C_AD2[17]

C_AD3[17]

LP

LP

C_FRAME#[17]

1 2

4

UCPU1G

UCPU1G

C_AD0

LP

LPC_AD1

LP

C_AD2

LP

C_AD3

LPC_FRAME#

PC

H_SPI_CLK

H_SPI_CS0#

PC

H_SPI_MOSI

PC

PCH_SPI_MISO

PC

H_SPI_WP#

H_SPI_HOLD#

PC

P13

M13

R14

K13

P15

C26

H2

M27

K2

D31

B23

F27

LAD0

LA

D1

LA

D2

D3

LA

LF

RAME

SPI

_CLK

7

_CS0

SPI

SPI

_CS1

7

_CS2

SPI

SPI

_MOSI

_MISO

SPI

SPI

_IO2

J26

_IO3

SPI

5

EMI

PC

D D

VALW_PCH

+3

H_SPI_CLK_R

RC4

RC4

1 1K_0402_1%

1 1K_0402_1%

2 1K_0402_1%

2 1K_0402_1%

RC4

RC4

RC4

RC4

0 33 _0402_5%EMI@

0 33 _0402_5%EMI@

1

2

1

2

2

H_GPIO11 [ 8]

PC

H_GPIO60 [ 8]

PC

H_GPIO73 [ 8]

PC

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,+3VALW_PCH

(EC, Thermal sensor)

1

moodule design 3.3K

7

7

BDW-Y-LPDDR3_BGA12 34

BDW-Y-LPDDR3_BGA12 34

@

@

Closed to ROM

CHKLIST1.0

2 SPI Device = 33 ohm

1 SPI Device = 15 ohm

H_SPI_WP#_R

PC

PC

H_SPI_MOSI_R

H_SPI_MISO_R

PC

H_SPI_HOLD#_R

PC

PC

C C

H_SPI_CS0#_R

RP

RP

41

41

1

8

2

7

3

6

4

5

33_0804_8P4R_5%

33_0804_8P4R_5%

1

RC1

RC1

28 0_0402_5%

28 0_0402_5%

2

PC

PC

PC

PC

PC

H_SPI_CS0#

H_SPI_WP#

H_SPI_MOSI

H_SPI_MISO

H_SPI_HOLD#

SPI ROM FOR ME ( 8MByte )

VALW_PCH

1

8

8

RC4

RC4

33_0402_5%

33_0402_5%

@EMI@

@EMI@

2

1

1

CC1

CC1

22P_0402_50V8J

22P_0402_50V8J

@EMI@

@EMI@

EMI

+3

1

2

CC1

CC1

0

0

0.1U_0402_16VK7

0.1U_0402_16VK7

ROM is Quad SPI

UC2

UC2

H_SPI_CS0#_R

PC

H_SPI_MISO_R

PC

PC

H_SPI_WP#_R

B B

_SPI_MISO[17]

EC

EC

_SPI_MOSI[17]

_SPI_CLK[17]

EC

EC_SPI_CS0#[17]

1

#

CS

2

(IO1)

DO

HO

3

#(IO2)

WP

4

GN

D

5Q64FVSSIQ_SO8

5Q64FVSSIQ_SO8

W2

W2

SPI ROM 8MB

1st: SA000039A30 - Winbond

RP

RP

43

43

1

8

2

7

3

6

4

5

33_0804_8P4R_5%

33_0804_8P4R_5%

C

VC

LD#(IO3)

K

CL

DI

(IO0)

H_SPI_MISO_R

PC

PC

H_SPI_MOSI_R

PC

H_SPI_CLK_R

H_SPI_CS0#_R

PC

8

7

6

5

H_SPI_HOLD#_R

PC

PC

H_SPI_CLK_R

H_SPI_MOSI_R

PC

OF 20

OF 20

moodule design 499 ohm

CRB 2.2K

SML1 Bus BIOS set Native,

it's OD pin

SML1 Bus :EC/Thermal Sensor

FootPrint :DMN66D0LDW-7_SOT363-6

L1CLK

SM

2N7002KDWH_SOT363-6

2N7002KDWH_SOT363-6

1A

1A

QC

QC

SM

L1DATA

QC1B 2N7002KDWH_SOT363-6

QC1B 2N7002KDWH_SOT363-6

L1CLK

SM

L1DATA

SM

RC4

RC4

RC5

RC5

1

2

3

4

9 2.2K_0402_ 5%@

9 2.2K_0402_ 5%@

0 2.2K_0402_ 5%@

0 2.2K_0402_ 5%@

SM

SM

SM

SM

SM

SM

BCLK

BDATA

L0CLK

L0DATA

L1DATA

L1CLK

+3

VS

2

@

@

6

5 0_0402_5%

5 0_0402_5%

RC4

RC4

6 0_0402_5%

6 0_0402_5%

RC4

RC4

42

42

RP

RP

2.2K_0804_8P4R_5%

2.2K_0804_8P4R_5%

1

1

1

@

@

3

1

2

1

2

8

7

6

5

2

2

1

5

1

4

EC

EC

RC4

RC4

3

3

2.2K_0402_5%

2.2K_0402_5%

2

4

4

RC4

RC4

2.2K_0402_5%

2.2K_0402_5%

2

_SMB_CK2

_SMB_DA2

+3VALW_PCH

VS

+3

_SMB_CK2 [17,23]

EC

VS

+3

EC

_SMB_DA2 [17,23]

A A

curity Class ification

curity Classificat ion

curity Classificat ion

Se

Se

Se

2014/

2014/

2014/

04/10 2017/04/10

04/10 2017/04/10

sued D ate

sued D ate

sued D ate

Is

Is

Is

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DI SCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DI SCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DI SCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

04/10 2017/04/10

3

mpal Secret Data

mpal Secret Data

mpal Secret Data

Co

Co

Co

Deciphered Date

Deciphered Date

Deciphered Date

mpal Electronics, Inc.

mpal Electronics, Inc.

mpal Electronics, Inc.

Co

Co

Title

Title

Title

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet of

2

Date: Sheet of

Co

BD

BD

BD

W MCP(4/9) LPC,SPI,SMBUS

W MCP(4/9) LPC,SPI,SMBUS

W MCP(4/9) LPC,SPI,SMBUS

LA

LA

LA

-B921PR10

-B921PR10

-B921PR10

1

1.0

1.0

1.0

of

736Friday, Octob er 17, 2014

736Friday, Octob er 17, 2014

736Friday, Octob er 17, 2014

5

Note: SUSACK# and SUSWARN# can be tied together if

EC does not want to involve in the handshake mechanism

for the Deep Sleep state entry and exit

CAN be NC ,if not support Deep Sx

+3

VS

1 8

2 7

3

4

D D

C C

B B

A A

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

RC65 10K_0402_5%

RC65 10K_0402_5%

+3VALW_PCH

RC136 1K_0402_5%

RC136 1K_0402_5%

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

PC

PC

6

PC

5

SY

RP

RP

65 10K_8P4R_5%

65 10K_8P4R_5%

8

PC

7

PC

6

PC

5

PC

64 10K_8P4R_5%@

64 10K_8P4R_5%@

RP

RP

08/21, change to unpop

8

PC

7

PC

6

PCH_GPIO93

5

PC

63 10K_8P4R_5%@

63 10K_8P4R_5%@

RP

RP

08/21, change to unpop

8

PC

7

PC

6

PC

5

PC

RP

RP

62 10K_8P4R_5%@

62 10K_8P4R_5%@

08/21, change to unpop

8

7

PCH_GPIO48

6

5

RP45 10K_8P4R_5%

RP45 10K_8P4R_5%

8

7

PC

6

KB_

5

RP

RP

46 10K_8P4R_5%

46 10K_8P4R_5%

8

PC

7

PC

6

EC_SCI#

5

47 10K_8P4R_5%

47 10K_8P4R_5%

RP

RP

8

7

6

5

48 10K_8P4R_5%

48 10K_8P4R_5%

RP

RP

8

PC

7

6

5

49 10K_8P4R_5%@

49 10K_8P4R_5%@

RP

RP

8

7

SER

6

5

RP

RP

50 10K_8P4R_5%

50 10K_8P4R_5%

8

7

6

PCH_GPIO71

5

PCH_GPIO16

RP51 10K_8P4R_5%

RP51 10K_8P4R_5%

8

PCH_GPIO33

7

PCH_GPIO50

6

PCH_GPIO76

5

PCH_GPIO49

RP52 10K_8P4R_5%@

RP52 10K_8P4R_5%@

08/21, change to unpop

2

1

2

8

PCH_GPIO12

7

PCH_GPIO8

6

5

PCH_GPIO30

RP54 10K_8P4R_5%

RP54 10K_8P4R_5%

8

7

PCH_GPIO61

6

5

PCH_GPIO29

RP55 10K_8P4R_5%@

RP55 10K_8P4R_5%@

8

SENSOR_HUB_RST#

7

PCH_GPIO13

6

SENSOR_HUB_INT#_R

5

PCH_GPIO25

RP57 10K_8P4R_5%

RP57 10K_8P4R_5%

8

7

PCH_GPIO28

6

PCH_GPIO9

5

PCH_GPIO10

RP59 10K_8P4R_5%

RP59 10K_8P4R_5%

H_GPIO64

H_GPIO68

H_GPIO69

S_RESET#

H_GPIO0

H_GPIO1

H_GPIO2

H_GPIO3

H_GPIO91

H_GPIO92

H_GPIO94

H_GPIO84

H_GPIO85

H_GPIO89

H_GPIO90

H_GPIO32

RST#

H_GPIO67

H_GPIO65

H_GPIO38

IRQ

5

+3

IECLKREQ4_N [6]

PC

AN_CLKREQ# [19,6]

WL

PC

IECLKREQ2_N [6]

IECLKREQ1_N [6]

PC

H_GPIO36 [6]

PC

H_GPIO53 [4]

PC

PC

H_GPIO78 [4]

H_GPIO77 [4]

PC

PC

H_GPIO79 [4]

BT_OFF# [19,4]

H_GPIO52 [4]

PC

PC

H_GPIO51 [4]

IECLKREQ5_N [6]

PC

PCH_GPIO37 [6]

IECLKREQ0_N [6]

PC

PCH_SATALED# [6]

PCH_GPIO34 [6]

PCH_GPIO54 [4]

PCH_PCIE_WAKE#

PCH_GPIO73 [7]

PCH_GPIO60 [7]

@10K,3VS XDP

VALW_PCH

1

RC5

RC5

200K_0402_5%

200K_0402_5%

2

ESD

1

2

1

1

_PRES ENT

AC

H_PWROK

PC

@ESD@

@ESD@

CC9

CC9

5

5

100P_0402_50V8J

100P_0402_50V8J

S_PWROK[17,4]

SY

H_PWROK[17]

PC

_RSMRST#[17]

EC

N_OUT#[17]

PBT

_PRES ENT[17]

AC

ESD

_RSMRST#

EC

1

6

6

CC9

CC9

1000P_0402_50V7K

1000P_0402_50V7K

ESD@

ESD@

2

ESD

S_RESET#

SY

1

@ESD@

@ESD@

CC97

CC97

100P_0402_50V8J

100P_0402_50V8J

2

NG

FF_SSD_PRESENT#[18]

SEN

SOR_HUB_INT#[16,4]

SENSOR_HUB_RST#[16]

VSLP1[1 8]

DE

10K,3VS

@10K,3VS

+3VS

1

2

3

4

+3VALW_PCH

1

RC64 10K_0402_5%

RC64 10K_0402_5%

1

RC146 10K_0402_5%

RC146 10K_0402_5%

1

RC67 10K_0402_5%

RC67 10K_0402_5%

1

RC147 10K_0402_5%

RC147 10K_0402_5%

1

RC148 10K_0402_5%@

RC148 10K_0402_5%@

+3VS

RC137 1K_0402_5%@

RC137 1K_0402_5%@

+3VALW_PCH

1

2

3

4

4

1

5 0_0402_5%

5 0_0402_5%

RC5

RC5

1

7 10K_0402_5%

7 10K_0402_5%

RC5

RC5

08/18, change to mount

10K,3VS

10K,+3VALW_PCH

10K,+3VALW_PCH

@1K,+3VALW_PCH

10K,3VS

10K,3VS

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,+3VALW_PCH

1

RC62 0_0402_5%@

RC62 0_0402_5%@

10K,3VS

10K,3VS

10K,3VS

10K,+3VALW_PCH10K,+3VALW_PCH

1

RC138 0_0402_5%@

RC138 0_0402_5%@

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,3VS

10K,3VS@10K,3VS

1

RC6

RC6

3 0_0402_5%

3 0_0402_5%

EC

_SCI#[1 7]

5]

SPKR[1

8

PCH_GPIO87

7

PCH_GPIO17

6

PCH_GPIO83

5

PCH_GPIO70

RP61 10K_8P4R_5%@

RP61 10K_8P4R_5%@

2

2

2

2

2

1

2

8

PCH_GPIO44

7

PCH_GPIO26

6

PCH_GPIO45

5

PCH_GPIO24

RP58 10K_8P4R_5%@

RP58 10K_8P4R_5%@

08/21, change to unpop

4

T5

T5

10K,3VS

2

2

10K,+3VALW_PCH

10K,+3VALW_PCH

T5

T5

@10K,+3VALW_PCH

2

2

2

PCH_GPIO72

PCH_GPIO27

DDR_ID

SU

SACK#_R

8

8

S_RESET#

SY

S_PWROK

SY

PC

H_PWROK

WROK _R

AP

PLT_RST#

H_

EC

_RSMRST#

PC

H_GPIO30

N_OUT#

PBT

_PRES ENT

AC

H_GPIO72

PC

SL

P_S0_N

3

3

PCH_GPIO29

PCH_GPIO76

H_GPIO8

PC

PC

H_GPIO12

H_GPIO15

PC

PC

H_GPIO16

PCH_GPIO17

H_GPIO24

PC

PC

H_GPIO27

H_GPIO28

PC

PC

H_GPIO26

M_ID0

RA

RA

M_ID1

M_ID2

RA

RA

M_ID3

PCH_GPIO44

ID

DDR_

PC

H_GPIO48

H_GPIO49

PC

PC

H_GPIO50

PCH_GPIO71

H_GPIO13

PC

SEN

SOR_HUB_INT#_R

H_GPIO25

PC

PC

H_GPIO45

SENSOR_HUB_RST#

PC

H_GPIO9

H_GPIO10

PC

PC

H_GPIO33

PCH_GPIO70

H_GPIO38

PC

EC

_SCI#

SPKR

PCH_GPIO11 [7]

DDR_ID

PU 10K to +3VALW_PCH (DDR3L)

PU down 10K (LP-DDR3)

SPKR

DPWROK: Tired toghter with RSMRST#

that do not support Deep Sx

UCPU1H

UCPU1H

9

D1

SU

6

E2

SYS_

A22

SYS_

F9

PC

J22

APW

3

M2

TRST

PL

F7

RSMRST

D8

SU

M2

1

PW

M17

AC

H17

BAT

G2

2

P_S0

SL

J18

SLP_WLAN_N_GPIO29

BDW-Y-LPDDR3_BGA1234

BDW-Y-LPDDR3_BGA1234

@

@

J30

C18

J14

K25

N26

H31

C22

K17

M25

B15

F25

F23

F15

D15

L18

B29

K29

B31

F33

D29

E14

M19

F17

P23

L22

D17

B17

E30

R36

K31

J41

A34

System Power Management

System Power Management

SACK

RESET

PWROK

H_PWROK

ROK

SWARN_N_SUSPWRDNACK_GPIO30

RBTN

PRESENT_GPIO31

LOW_N_GPIO72

UCPU1J

UCPU1J

BUSY_N_USB3PHY_PC_GPIO76

BM

IO8

GP

LAN_PHY_PWR_CTRL_GPIO12

GPIO15

GP

IO16

GP

IO17

IO24

GP

IO27

GP

IO28

GP

GP

IO26

GP

IO56

GPIO

GPIO

IO57

GP

IO58

GP

GPIO59

GP

IO44

GP

IO47

IO48

GP

IO49

GP

IO50

GP

HS

IOPC_PCIEPHY _PC_GPIO71

GP

IO13

GP

IO14

IO25

GP

IO45

GP

IO46

GP

GP

IO9

GP

IO10

VSLP0_GPIO33

DE

IO_POWER_EN_GPIO70

SD

DEVSLP1_GPI O38

DE

VSLP2_GPIO39

SPKR

_GPIO81

BDW-Y-LPDDR3_BGA1234

BDW-Y-LPDDR3_BGA1234

@

@

3

DSWODVREN - On Die DSW VR Enable

HEnable(DEFAULT)

*

Disable

L

1 2

RC5

RC5

2 330K_0402_5%

2 330K_0402_5%

1 2

RC5

RC5

6 330K_0402_5%@

G14

DS

J7

9

F1

KE

B3

5

D25

B27

A18

H1

9

P_S4

N2

2

P_S3

G1

8

P_A

D2

7

9

K1

OF 20

OF 20

ERMTRIP

TH

RCIN_N_GPIO82

SERIRQ

H_OPI_RCOMP

RS

VD_AJ14

VD_AL18

RS

RT1_TXD_GPIO1

C0_SDA_GPIO4

C0_SCL_GPIO5

C1_SDA_GPIO6

C1_SCL_GPIO7

IO_CLK_GPIO64

IO_D0_GPIO66

IO_D1_GPIO67

IO_D2_GPIO68

IO_D3_GPIO69

OF 20

OF 20

10

10

+3VALW_PCH

WODVREN

WROK

DP

H_PCIE_WAKE#

PC

H_GPIO32

PC

H_GPIO61

PC

PM

_SLP_S5#

_SLP_S4#

PM

_SLP_S3#

PM

_SLP_A#

PM

SL

P_SUS_N

SLP_LAN_N

CG

C34

E34

AB4

AJ14

AL18

D40

G34

L36

K33

L34

M31

F37

H35

M35

F39

N43

N41

P29

H38

N39

N30

N36

R42

J37

M33

N34

H40

R40

R38

J39

P31

1

RC117

RC117

10K_0402_5%

10K_0402_5%

X76@

X76@

2

1

RC121

RC121

10K_0402_5%

10K_0402_5%

X76@

X76@

2

40

RAM_ID2

WVRMEN

DS

WROK

DP

WA

IO32_CLKRUN

GP

S_STAT_N_GPIO61

SU

SCLK_GPIO62

SU

SLP_S5_N_GPIO63

SL

SL

SL

P_SUS

SL

SLP_LAN

8

8

CP

CP

U/MISC

U/MISC

PC

LPIO

LPIO

GS

PI0_CS_N__GPIO83

GS

PI0_CLK_GPIO84

PI0_MISO_GPIO85

GS

PI0_MOSI_GPIO86

GS

GSPI1_CS_N_GPIO87

GS

PI1_CLK_GPIO88

GS

PI1_MISO_GPIO89

PI_MOSI_GPIO90

GS

RT0_RXD_GPIO91

UA

RT0_TXD_GPIO92

UA

UA

RT0_RTS_N_GPIO93

UA

RT0_CTS_N_GPIO94

UA

RT1_RXD_GPIO0

UA

RT1_RST_N_GPIO2

UA

RT1_CTS_N_GPIO3

UA

I2

I2

I2

I2

SD

SDIO_CMD_GPIO65

SD

SD

SD

SD

+3VALW_PCH

1

RC116

RC116

10K_0402_5%

10K_0402_5%

X76@

X76@

2

RAM_ID3

1

RC120

RC120

10K_0402_5%

10K_0402_5%

X76@

X76@

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL E LECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL E LECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL E LECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

6 330K_0402_5%@

1 2

4 0_0402_5%

4 0_0402_5%

RC5

RC5

1K,+3VALW_PCH

10K,3VS

@10K,+3VALW_PCH

2

2

T5

T5

T54

T54

5

5

T5

T5

.05VS_VTT

+1

1

RC60

RC60

1K_0402_1%

1K_0402_1%

+3VALW_PCH

1

RC118

RC118

10K_0402_5%

10K_0402_5%

X76@

X76@

2

1

RC122

RC122

10K_0402_5%