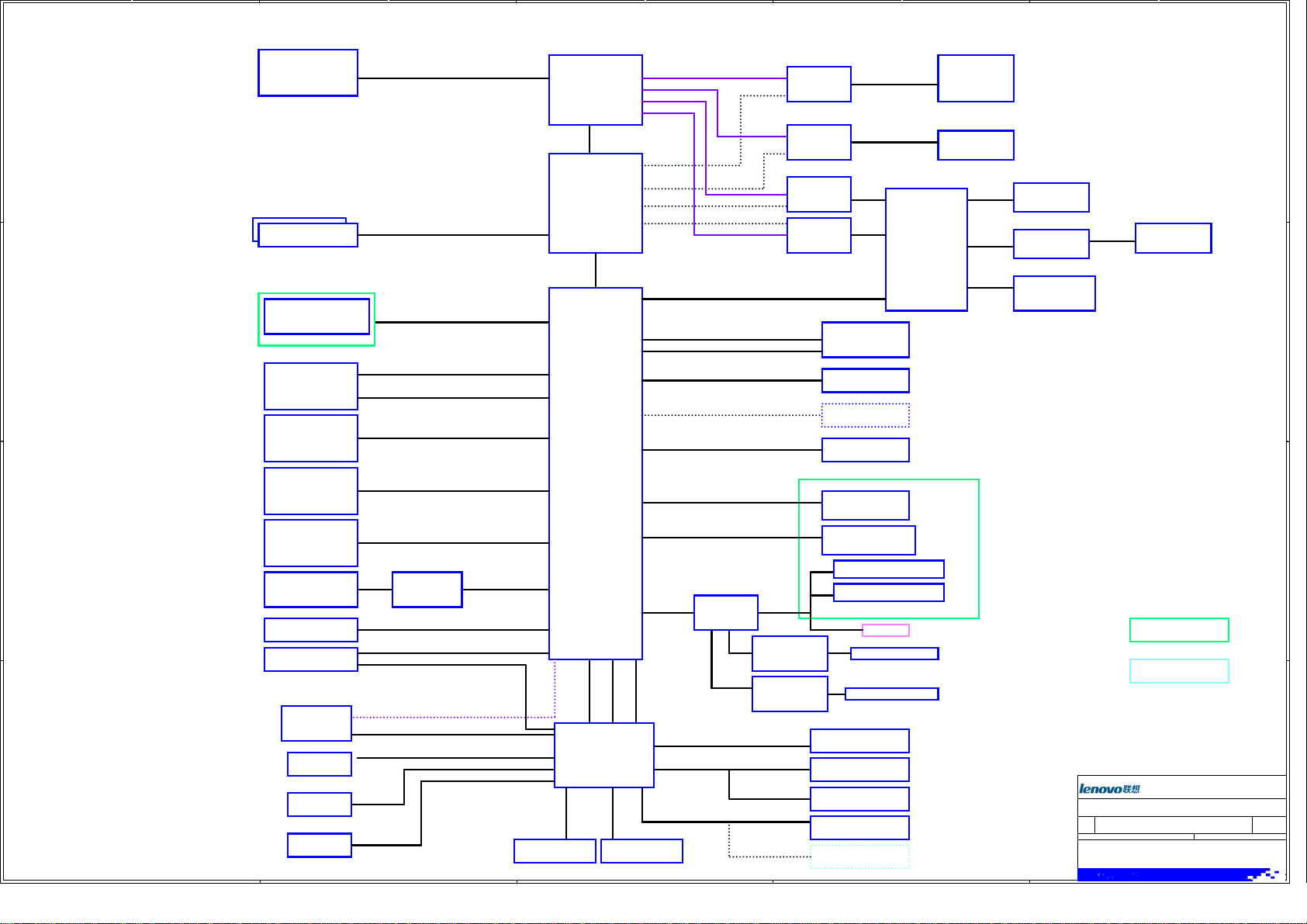

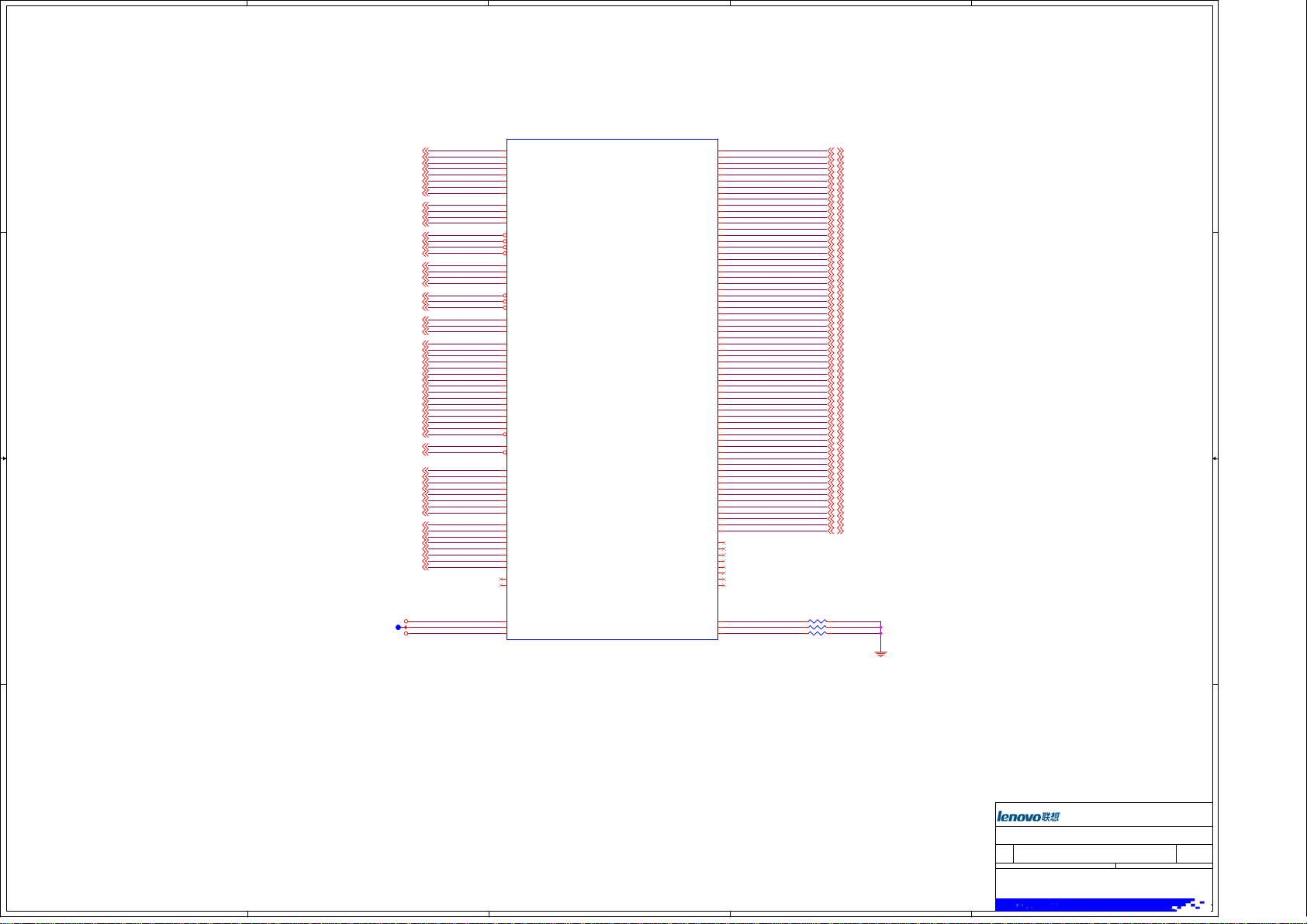

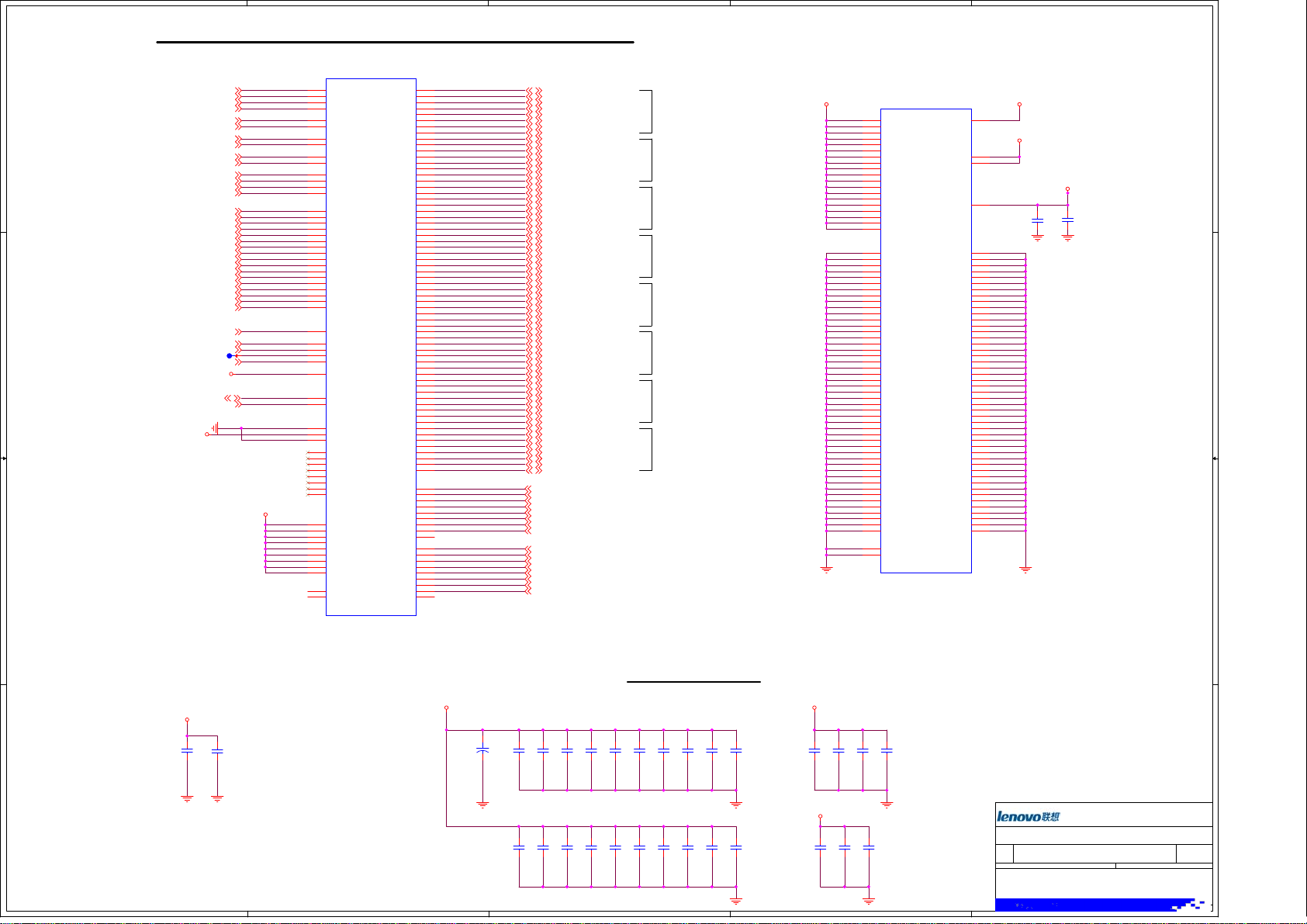

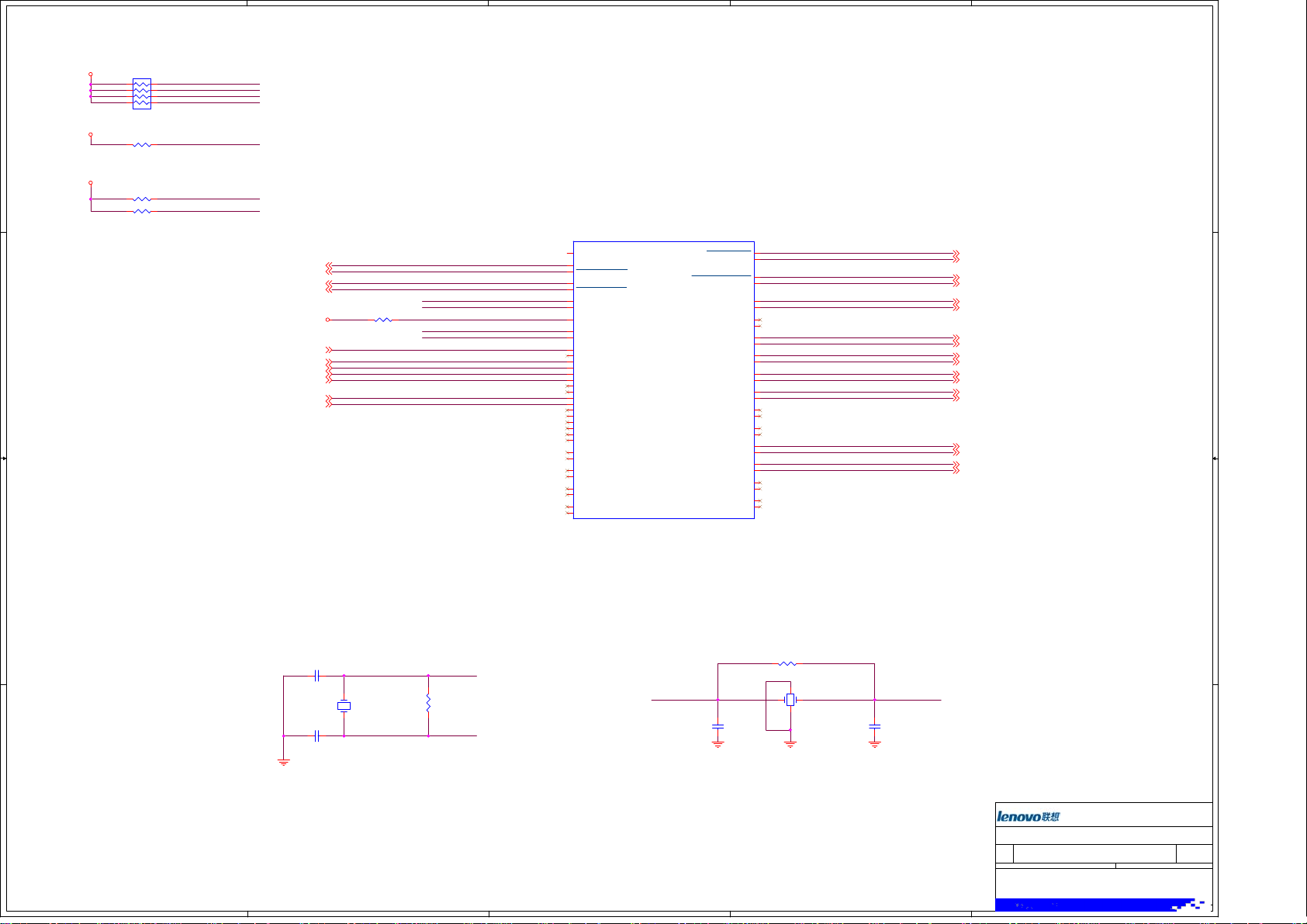

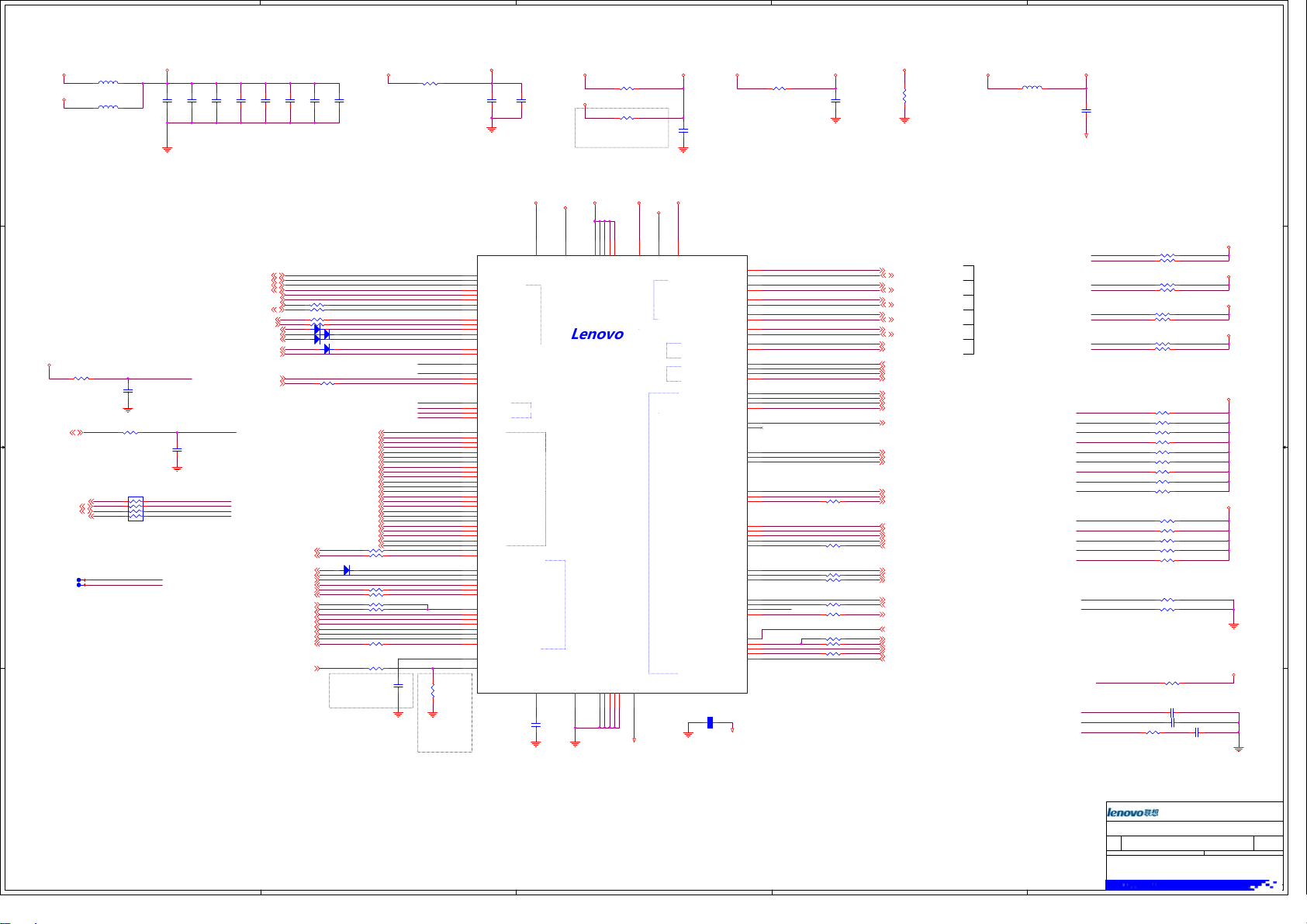

Lenovo Skylake-H schematics

5

4

3

2

1

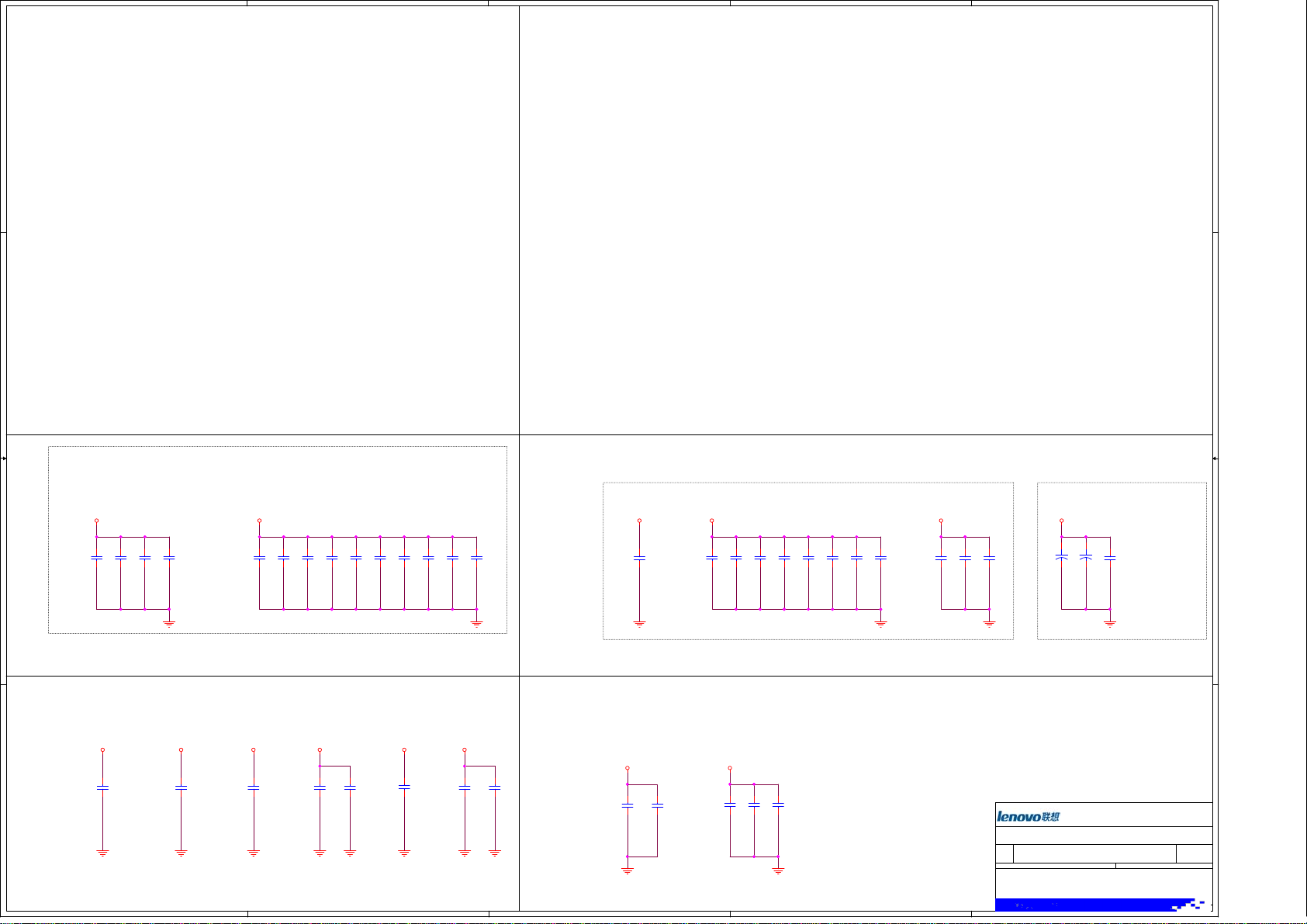

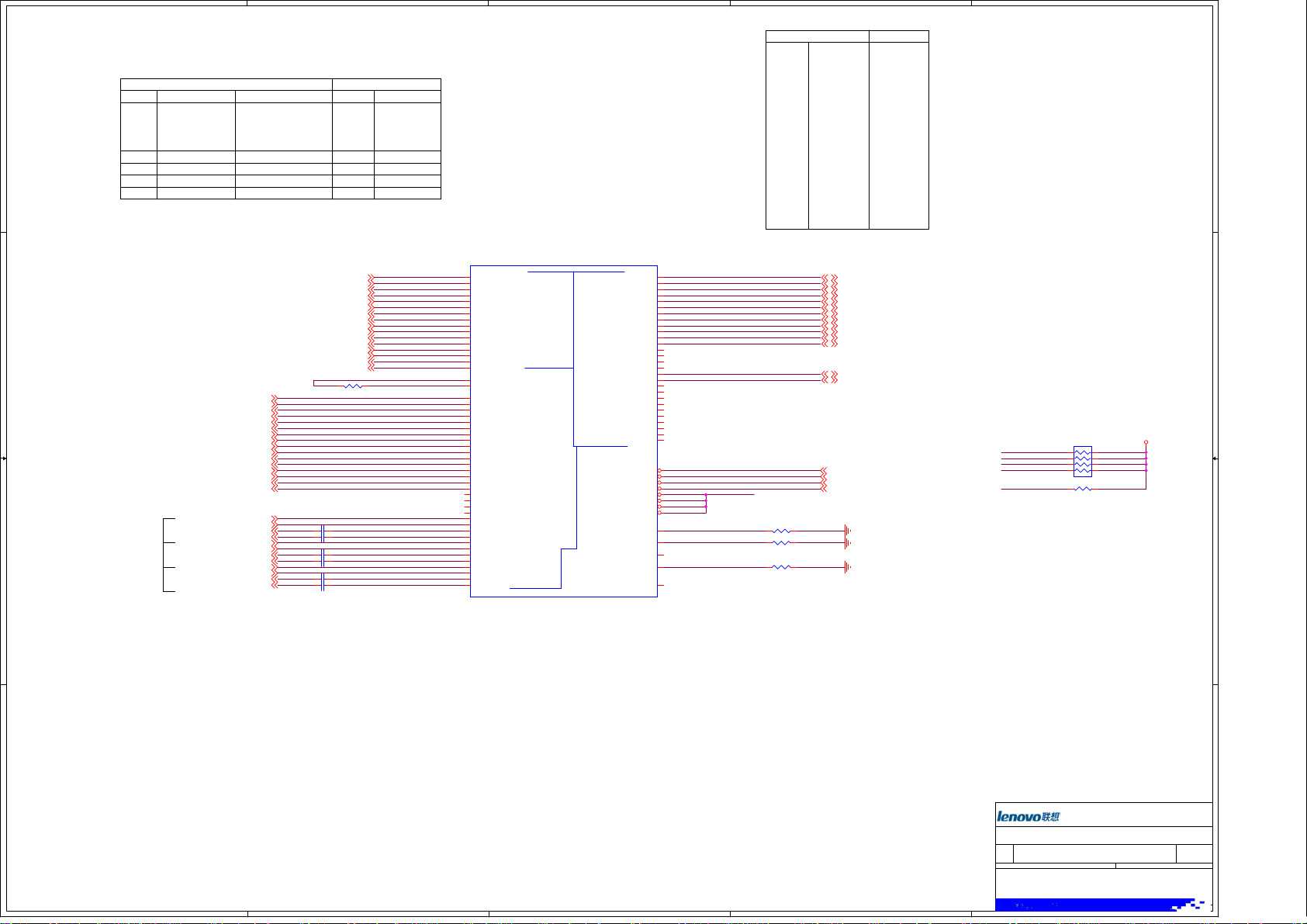

Schematic Block Diagram

VRAM GDDR5

PAGE63‐‐70

D D

DDR4DIMMX4

PAGE12~16

GDDR5

DDR42133MT/S

DUALCHANNEL2DIMM

nVIDIA

dGPU

N16E-GX

PAGE51‐‐62

PCIEGen316X

INTELProcessor

Skylake‐H

4+4e/4+2

BGA

42X28mm

PAGE2‐‐9

DMIX4

8GB/S

eDP

DDID

DDIB

DDIC

MUX

PS8331B

MUX

PS8331B

MUX

PS8331B

MUX

PS8331B

PAGE30

PAGE32

PAGE34

PAGE35

EDPLanesx4

DPLanesx4

DDI

DDI

PCIE4X PORT1

Card Reader

C C

B B

Bayhub OZ620FJ1LN

NGFF WLAN

2230 Conn,

(TYPE E)

WLAN/BT

LAN

Killer

E2400-RIVL-RL

NGFF SSD 1

2280 Conn,

(TYPE M)

NGFF SSD 2

2280 Conn,

(TYPE M)

PAGE41

PAGE27

PAGE42

PAGE42

PCIE1X

PORT6

PCIE1X

PORT7

USB2.0 PORT5

PCIE1X

PORT8

PORT13

PCIE4X

PORT9

PCIE4X

INTELSKYLAKE

PCH‐H

FCBGA

23X23mm

PAGE17‐‐25

PORT3

USB3.0

PORT2

USB2.0

PORT3USB2.0

USB2.0 PORT9

PORT4USB2.0

PORT1USB2.0

PORT6USB2.0

USB Conn,2

W/ CHARGER

HD CAMERA

FPR Conn

Keyboard

USB2.0 Conn,

JUSB3

USB2.0 Conn,

JUSB4

PAGE39

PAGE31

PAGE45

PAGE47

INTEL

ARDP

PANEL

17"FHD/UHD

GSYNC

DISPLAYPORT

PAGE36,37

PAGE31

PAGE33

USB3.1

HDMICONN,HDMI1.4b

PAGE40

TPS65982

PAGE38

USBCONN,1

PAGE39

TYPE‐CCONN,TYPE‐C

PAGE38

HP/MIC COMBO JACK

2.5"SATAHDD/SSD SATA PORT4

PAGE43

SPIBIOS

TOUCHPAD PS2

A A

PAGE45

LC

IT8376VG/CX

PAGE46

TURBObutton

LIDswitch

LED

5

SATARedriver

PS8527C

4

PAGE42

SPI

SMBUS

I2C

I2C

IntKBDDebug

PAGE50

I2C

EC

IT8376VG/CX

PAGE26

SMbus

80PortDebugCard

HDA CODEC

LPCSMBUS

PAGE50

3

PWM

SMBUS

I2C

ALC3268

PAGE28

SMARTAMP

TAS5766DCA

AMP

TPA3113D2PWPR

MIC JACK

PAGE29

PAGE29

SPEAKER CONN,

Subwoofer CONN,

FAN

Battery

THERMALSENSOR

IRsensorsTMP006A

RGBsensorCS5032

DMIC

PAGE73

PAGE44

PAGE44

IO DB

SENSOR DB

LENOVO.CRDN

LENOVO.CRDN

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number

Size Document Number

Size Document Number

Custom

Custom

Custom

Skylake-H

Skylake-H

Skylake-H

Date: Sheet

Date: Sheet

Date: Sheet

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

2

LENOVO.CRDN

Rev

Rev

Rev

V0.3

V0.3

V0.3

199Wednesday, January 27, 2016

199Wednesday, January 27, 2016

199Wednesday, January 27, 2016

of

of

of

1

5

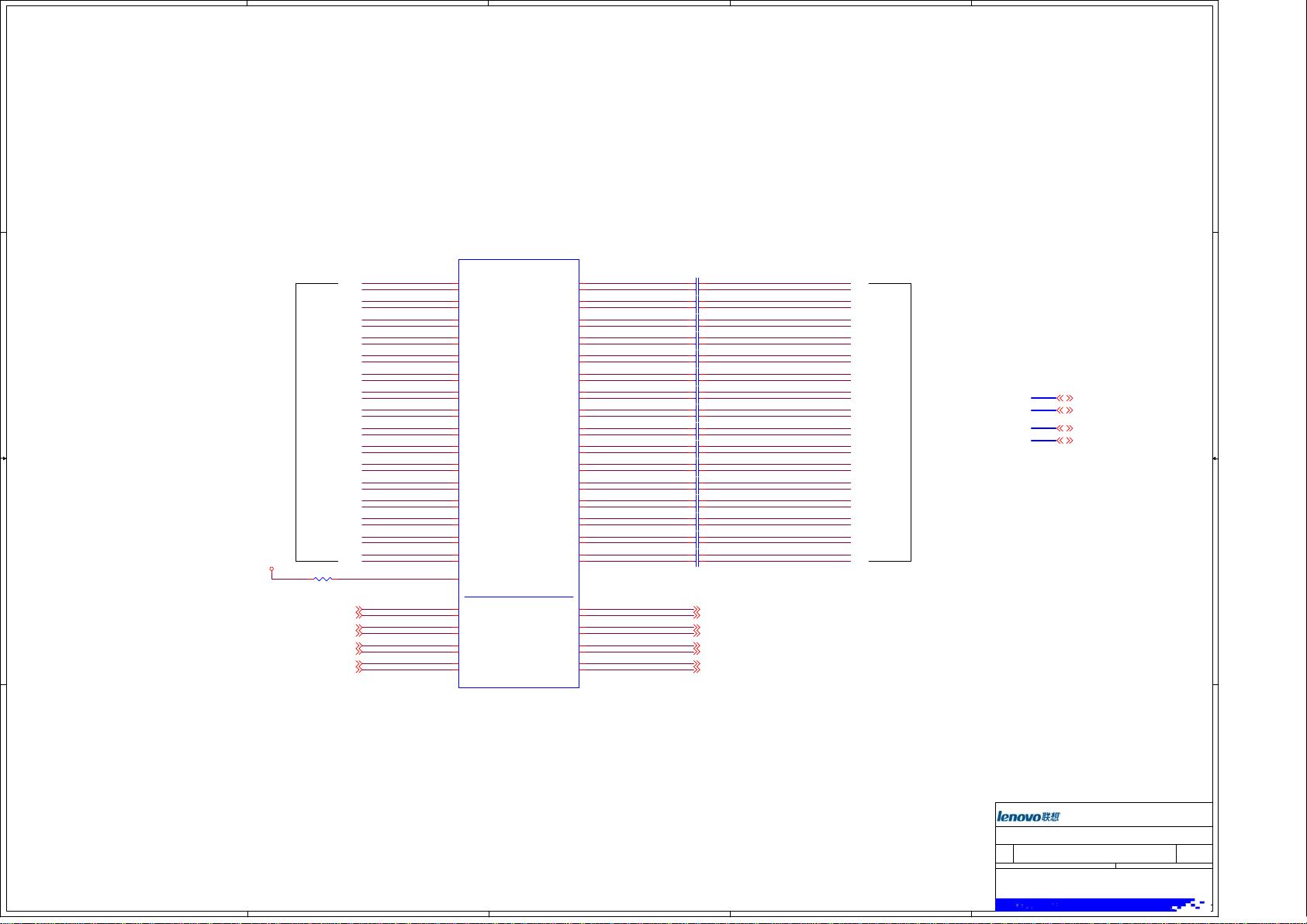

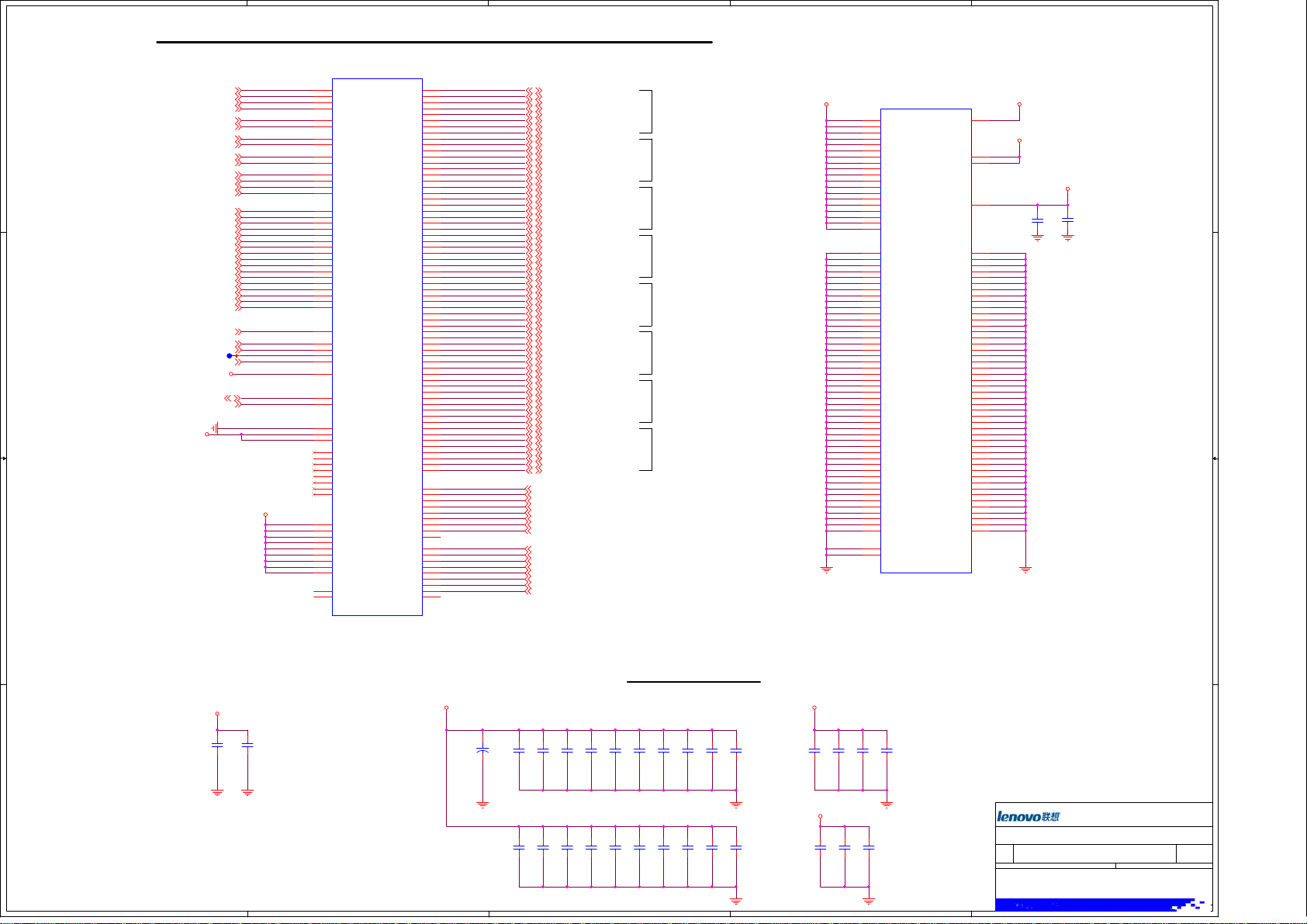

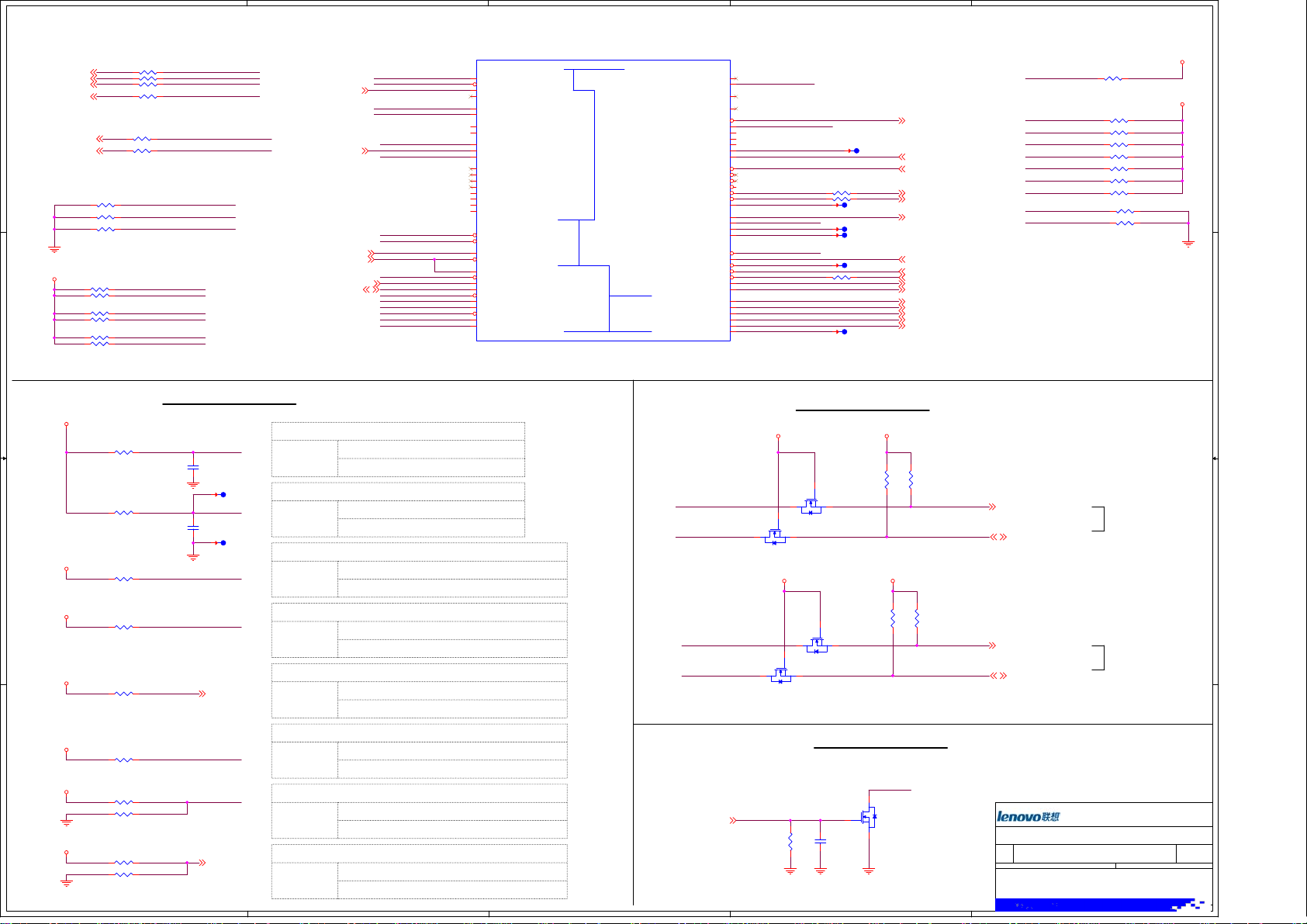

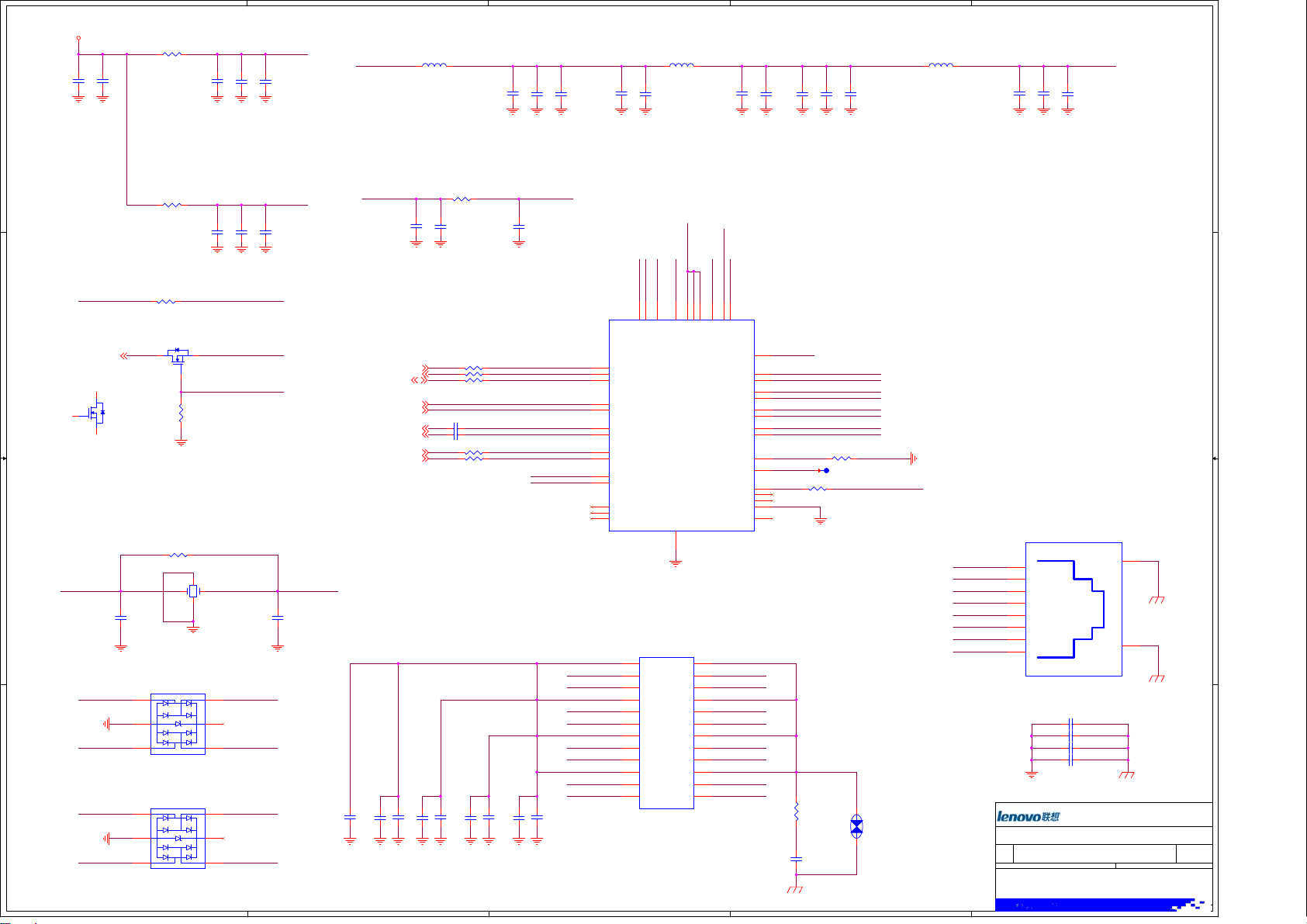

D D

C C

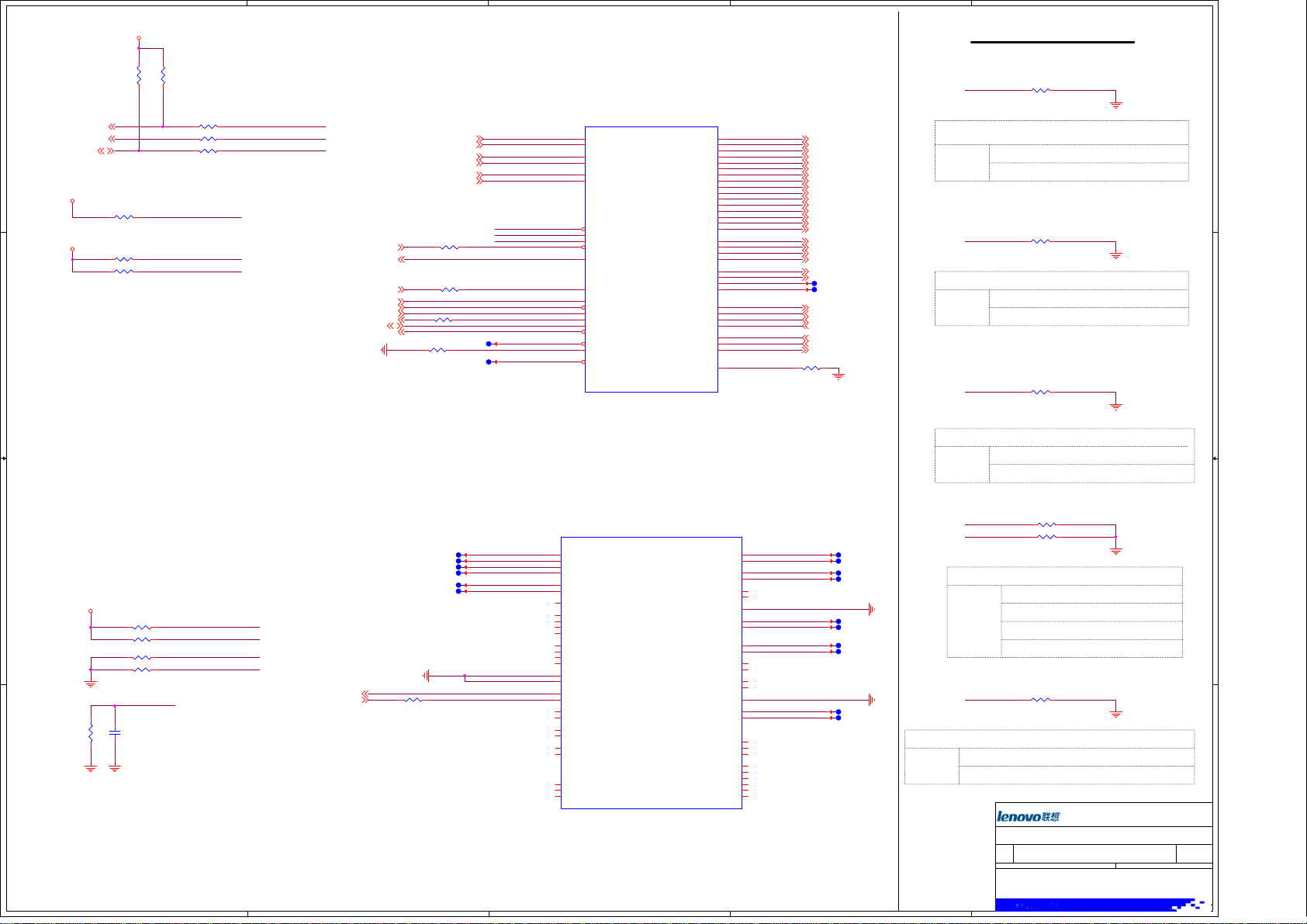

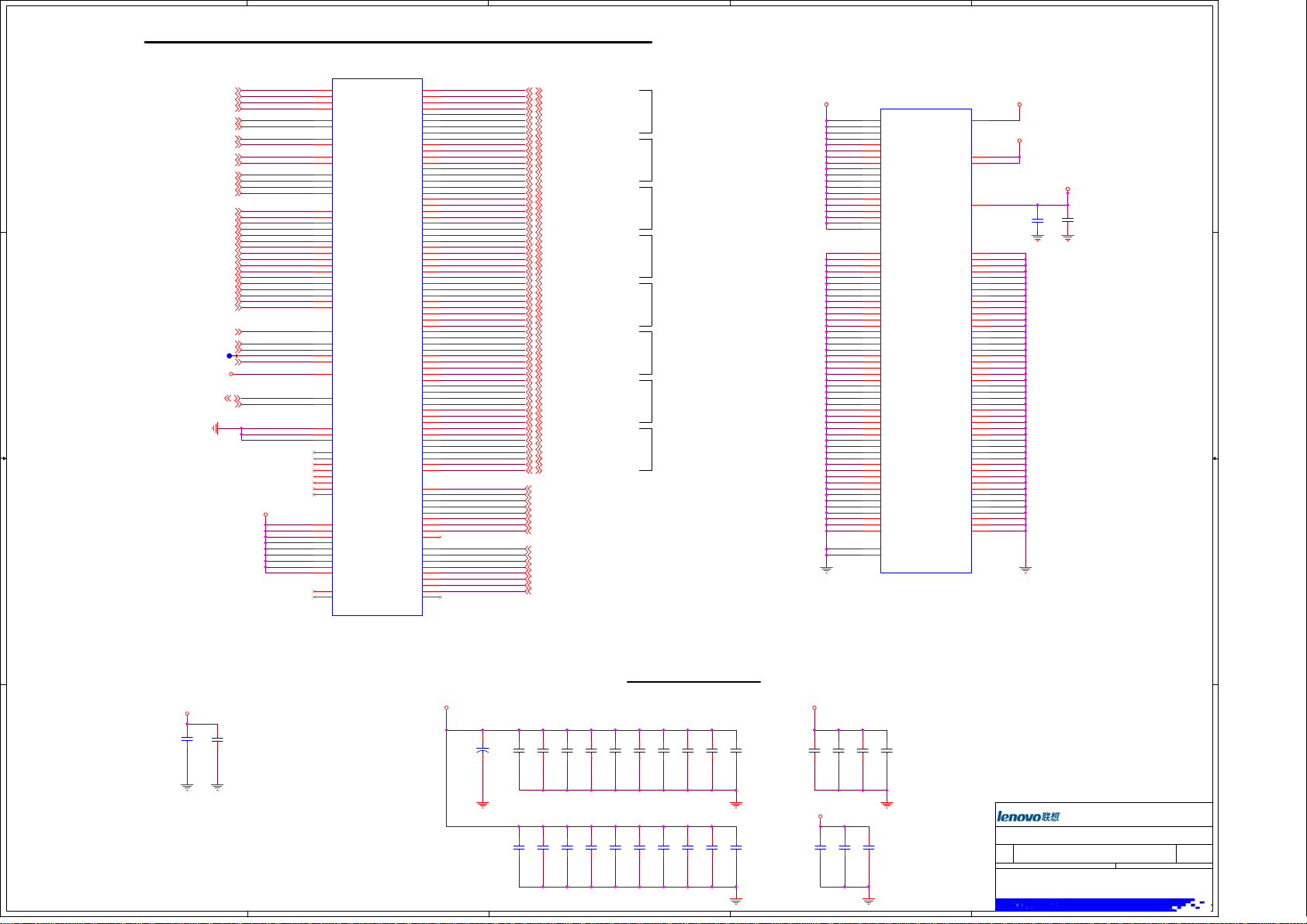

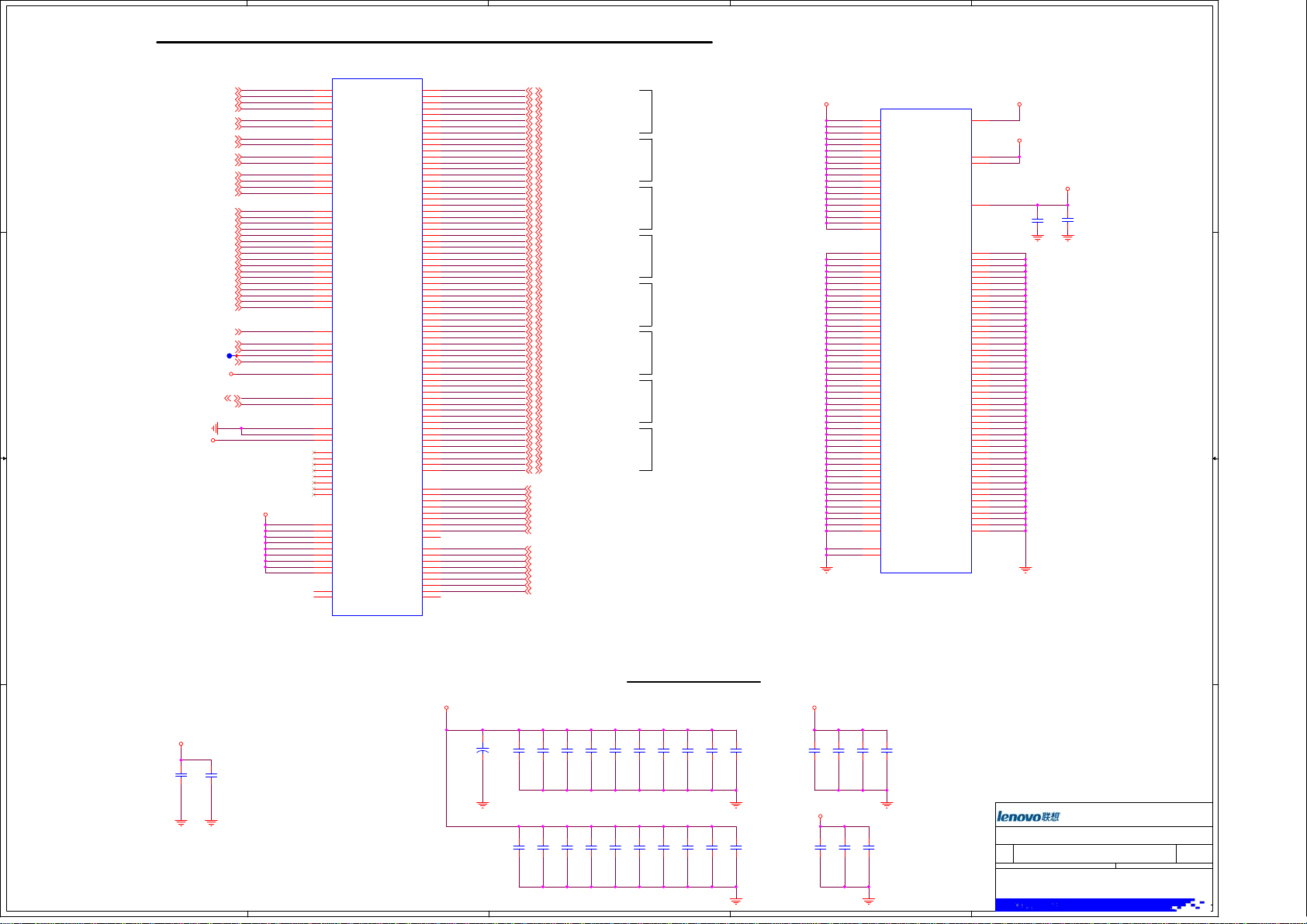

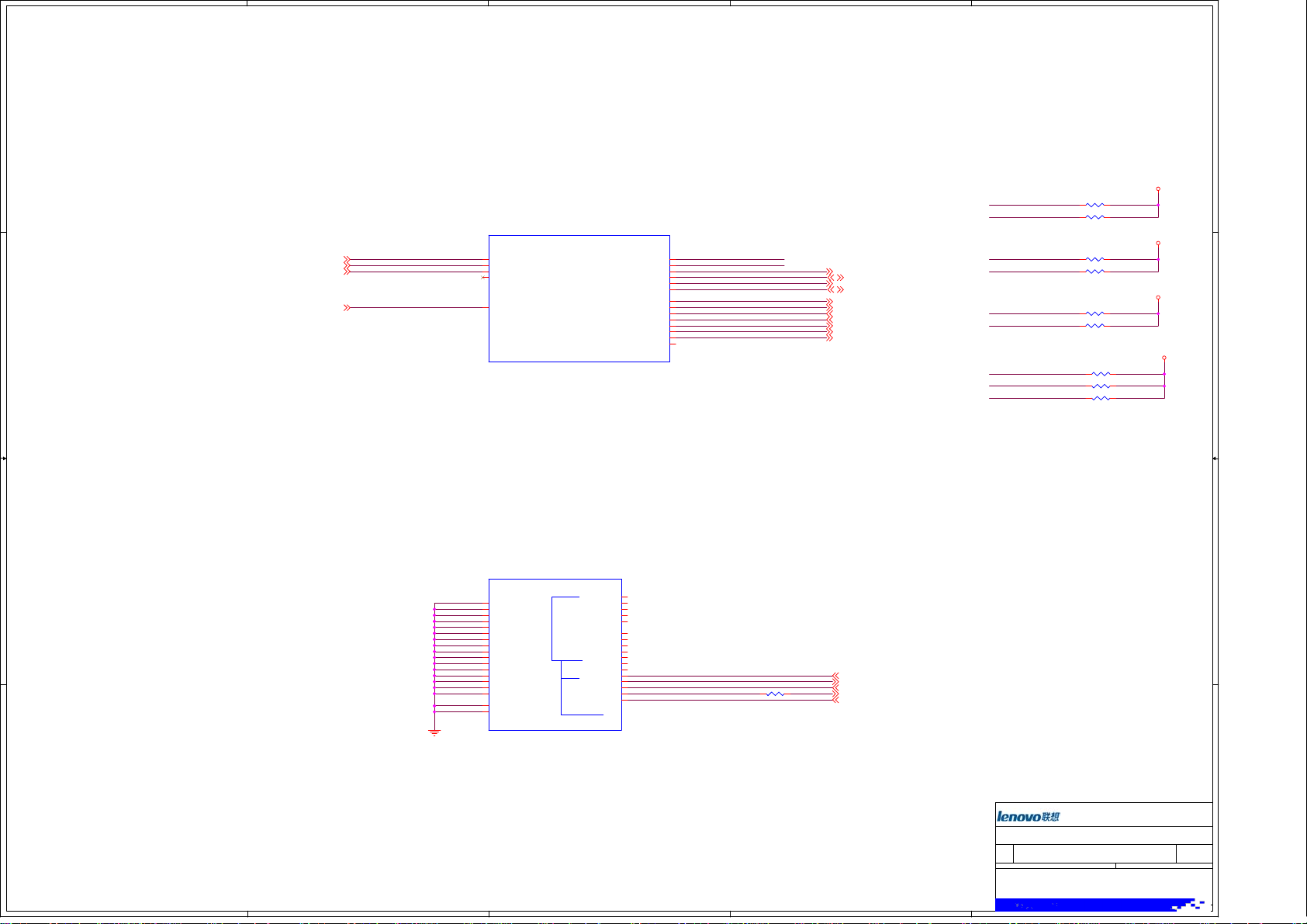

dGPU PEG

BRD Note:

B B

W=12mils;S=15mils;L<=400mils

+VCCIO

1 2

R1 24.9_0402_1%

DMI_IT_MR_0_DP18

DMI_IT_MR_0_DN18

DMI_IT_MR_1_DP18

DMI_IT_MR_1_DN18

DMI_IT_MR_2_DP18

DMI_IT_MR_2_DN18

DMI_IT_MR_3_DP18

DMI_IT_MR_3_DN18

4

PEG_PRX_GTX_P15

PEG_PRX_GTX_N15

PEG_PRX_GTX_P14

PEG_PRX_GTX_N14

PEG_PRX_GTX_P13

PEG_PRX_GTX_N13

PEG_PRX_GTX_P12

PEG_PRX_GTX_N12

PEG_PRX_GTX_P11

PEG_PRX_GTX_N11

PEG_PRX_GTX_P10

PEG_PRX_GTX_N10

PEG_PRX_GTX_P9

PEG_PRX_GTX_N9

PEG_PRX_GTX_P8

PEG_PRX_GTX_N8

PEG_PRX_GTX_P7

PEG_PRX_GTX_N7

PEG_PRX_GTX_P6

PEG_PRX_GTX_N6

PEG_PRX_GTX_P5

PEG_PRX_GTX_N5

PEG_PRX_GTX_P4

PEG_PRX_GTX_N4

PEG_PRX_GTX_P3

PEG_PRX_GTX_N3

PEG_PRX_GTX_P2

PEG_PRX_GTX_N2

PEG_PRX_GTX_P1

PEG_PRX_GTX_N1

PEG_PRX_GTX_P0

PEG_PRX_GTX_N0

PEG_RCOMP

E25

D25

E24

F24

E23

D23

E22

F22

E21

D21

E20

F20

E19

D19

E18

F18

D17

E17

F16

E16

D15

E15

F14

E14

D13

E13

F12

E12

D11

E11

F10

E10

G2

D8

E8

E6

F6

D5

E5

J8

J9

?

PEG_RXP[0]

PEG_RXN[0]

PEG_RXP[1]

PEG_RXN[1]

PEG_RXP[2]

PEG_RXN[2]

PEG_RXP[3]

PEG_RXN[3]

PEG_RXP[4]

PEG_RXN[4]

PEG_RXP[5]

PEG_RXN[5]

PEG_RXP[6]

PEG_RXN[6]

PEG_RXP[7]

PEG_RXN[7]

PEG_RXP[8]

PEG_RXN[8]

PEG_RXP[9]

PEG_RXN[9]

PEG_RXP[10]

PEG_RXN[10]

PEG_RXP[11]

PEG_RXN[11]

PEG_RXP[12]

PEG_RXN[12]

PEG_RXP[13]

PEG_RXN[13]

PEG_RXP[14]

PEG_RXN[14]

PEG_RXP[15]

PEG_RXN[15]

PEG_RCOMP

DMI_RXP[0]

DMI_RXN[0]

DMI_RXP[1]

DMI_RXN[1]

DMI_RXP[2]

DMI_RXN[2]

DMI_RXP[3]

DMI_RXN[3]

SKYLAKE_HALO

BGA1440

U1C

PEG_TXP[0]

PEG_TXN[0]

PEG_TXP[1]

PEG_TXN[1]

PEG_TXP[2]

PEG_TXN[2]

PEG_TXP[3]

PEG_TXN[3]

PEG_TXP[4]

PEG_TXN[4]

PEG_TXP[5]

PEG_TXN[5]

PEG_TXP[6]

PEG_TXN[6]

PEG_TXP[7]

PEG_TXN[7]

PEG_TXP[8]

PEG_TXN[8]

PEG_TXP[9]

PEG_TXN[9]

PEG_TXP[10]

PEG_TXN[10]

PEG_TXP[11]

PEG_TXN[11]

PEG_TXP[12]

PEG_TXN[12]

PEG_TXP[13]

PEG_TXN[13]

PEG_TXP[14]

PEG_TXN[14]

PEG_TXP[15]

PEG_TXN[15]

DMI_TXP[0]

DMI_TXN[0]

DMI_TXP[1]

DMI_TXN[1]

DMI_TXP[2]

DMI_TXN[2]

DMI_TXP[3]

DMI_TXN[3]

B25

A25

B24

C24

B23

A23

B22

C22

B21

A21

B20

C20

B19

A19

B18

C18

A17

B17

C16

B16

A15

B15

C14

B14

A13

B13

C12

B12

A11

B11

C10

B10

B8

A8

C6

B6

B5

A5

D4

B4

3

PCIE ReversedPCIE Reversed

PEG_PTX_GRX_P15

PEG_PTX_GRX_N15

PEG_PTX_GRX_P14

PEG_PTX_GRX_N14

PEG_PTX_GRX_P13

PEG_PTX_GRX_N13

PEG_PTX_GRX_P12

PEG_PTX_GRX_N12

PEG_PTX_GRX_P11

PEG_PTX_GRX_N11

PEG_PTX_GRX_P10

PEG_PTX_GRX_N10

PEG_PTX_GRX_P9

PEG_PTX_GRX_N9

PEG_PTX_GRX_P8

PEG_PTX_GRX_N8

PEG_PTX_GRX_P7

PEG_PTX_GRX_N7

PEG_PTX_GRX_P6

PEG_PTX_GRX_N6

PEG_PTX_GRX_P5

PEG_PTX_GRX_N5

PEG_PTX_GRX_P4

PEG_PTX_GRX_N4

PEG_PTX_GRX_P3

PEG_PTX_GRX_N3

PEG_PTX_GRX_P2

PEG_PTX_GRX_N2

PEG_PTX_GRX_P1

PEG_PTX_GRX_N1

PEG_PTX_GRX_P0

PEG_PTX_GRX_N0

12

C1 0.22U_0402_10V6K

12

C2 0.22U_0402_10V6K

12

C3 0.22U_0402_10V6K

12

C4 0.22U_0402_10V6K

12

C5 0.22U_0402_10V6K

12

C6 0.22U_0402_10V6K

12

C7 0.22U_0402_10V6K

12

C8 0.22U_0402_10V6K

12

C9 0.22U_0402_10V6K

12

C10 0.22U_0402_10V6K

12

C11 0.22U_0402_10V6K

12

C12 0.22U_0402_10V6K

12

C13 0.22U_0402_10V6K

12

C14 0.22U_0402_10V6K

12

C15 0.22U_0402_10V6K

12

C16 0.22U_0402_10V6K

12

C17 0.22U_0402_10V6K

12

C18 0.22U_0402_10V6K

12

C19 0.22U_0402_10V6K

12

C20 0.22U_0402_10V6K

12

C21 0.22U_0402_10V6K

12

C22 0.22U_0402_10V6K

12

C23 0.22U_0402_10V6K

12

C24 0.22U_0402_10V6K

12

C25 0.22U_0402_10V6K

12

C26 0.22U_0402_10V6K

12

C27 0.22U_0402_10V6K

12

C28 0.22U_0402_10V6K

12

C29 0.22U_0402_10V6K

12

C30 0.22U_0402_10V6K

12

C31 0.22U_0402_10V6K

12

C32 0.22U_0402_10V6K

DMI_MT_IR_0_DP

DMI_MT_IR_0_DN 18

DMI_MT_IR_1_DP

DMI_MT_IR_1_DN

DMI_MT_IR_2_DP

DMI_MT_IR_2_DN

DMI_MT_IR_3_DP

DMI_MT_IR_3_DN

PEG_PTX_C_GRX_P15

PEG_PTX_C_GRX_N15

PEG_PTX_C_GRX_P14

PEG_PTX_C_GRX_N14

PEG_PTX_C_GRX_P13

PEG_PTX_C_GRX_N13

PEG_PTX_C_GRX_P12

PEG_PTX_C_GRX_N12

PEG_PTX_C_GRX_P11

PEG_PTX_C_GRX_N11

PEG_PTX_C_GRX_P10

PEG_PTX_C_GRX_N10

PEG_PTX_C_GRX_P9

PEG_PTX_C_GRX_N9

PEG_PTX_C_GRX_P8

PEG_PTX_C_GRX_N8

PEG_PTX_C_GRX_P7

PEG_PTX_C_GRX_N7

PEG_PTX_C_GRX_P6

PEG_PTX_C_GRX_N6

PEG_PTX_C_GRX_P5

PEG_PTX_C_GRX_N5

PEG_PTX_C_GRX_P4

PEG_PTX_C_GRX_N4

PEG_PTX_C_GRX_P3

PEG_PTX_C_GRX_N3

PEG_PTX_C_GRX_P2

PEG_PTX_C_GRX_N2

PEG_PTX_C_GRX_P1

PEG_PTX_C_GRX_N1

PEG_PTX_C_GRX_P0

PEG_PTX_C_GRX_N0

18

18

18

18

18

18

18

2

dGPU PEG

1

PEG_PRX_GTX_N[0..15]

PEG_PRX_GTX_P[0..15]

PEG_PTX_C_GRX_N[0..15]

PEG_PTX_C_GRX_P[0..15]

51

51

51

51

3 OF 14 ?

SKL_H_BGA_BGA

A A

5

4

REV = 1

LENOVO.CRDN

LENOVO.CRDN

1

LENOVO.CRDN

29

29

29

of

of

Rev

Rev

Rev

V0.3

V0.3

V0.3

9Wednesday, January 27, 2016

9Wednesday, January 27, 2016

9Wednesday, January 27, 2016

Title

Title

Title

PROCESSOR-PEG/DMI

PROCESSOR-PEG/DMI

PROCESSOR-PEG/DMI

Size Document Number

Size Document Number

Size Document Number

C

C

C

Skylake-H

Skylake-H

Skylake-H

Date: Sheet

Date: Sheet

Date: Sheet of

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

3

2

5

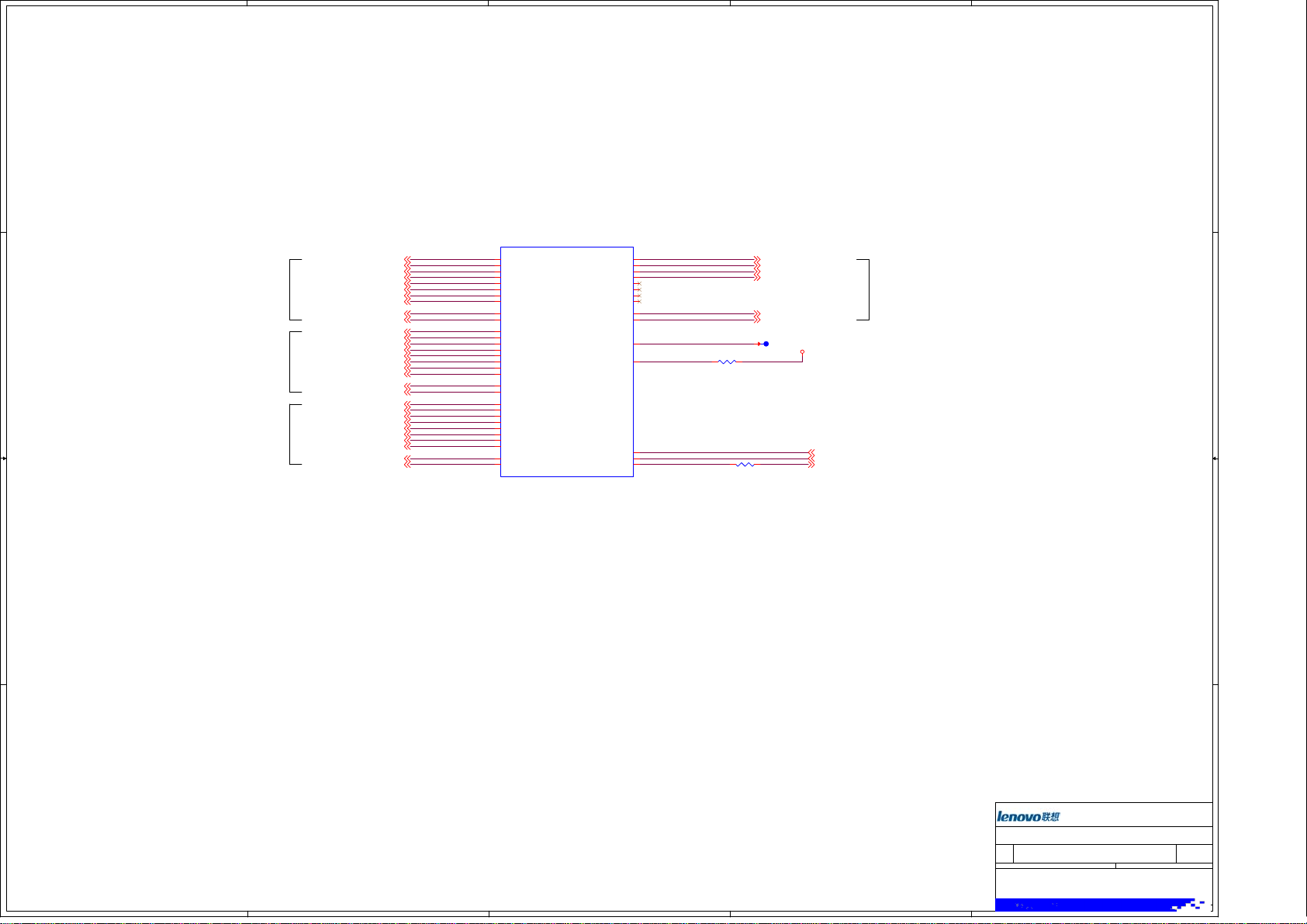

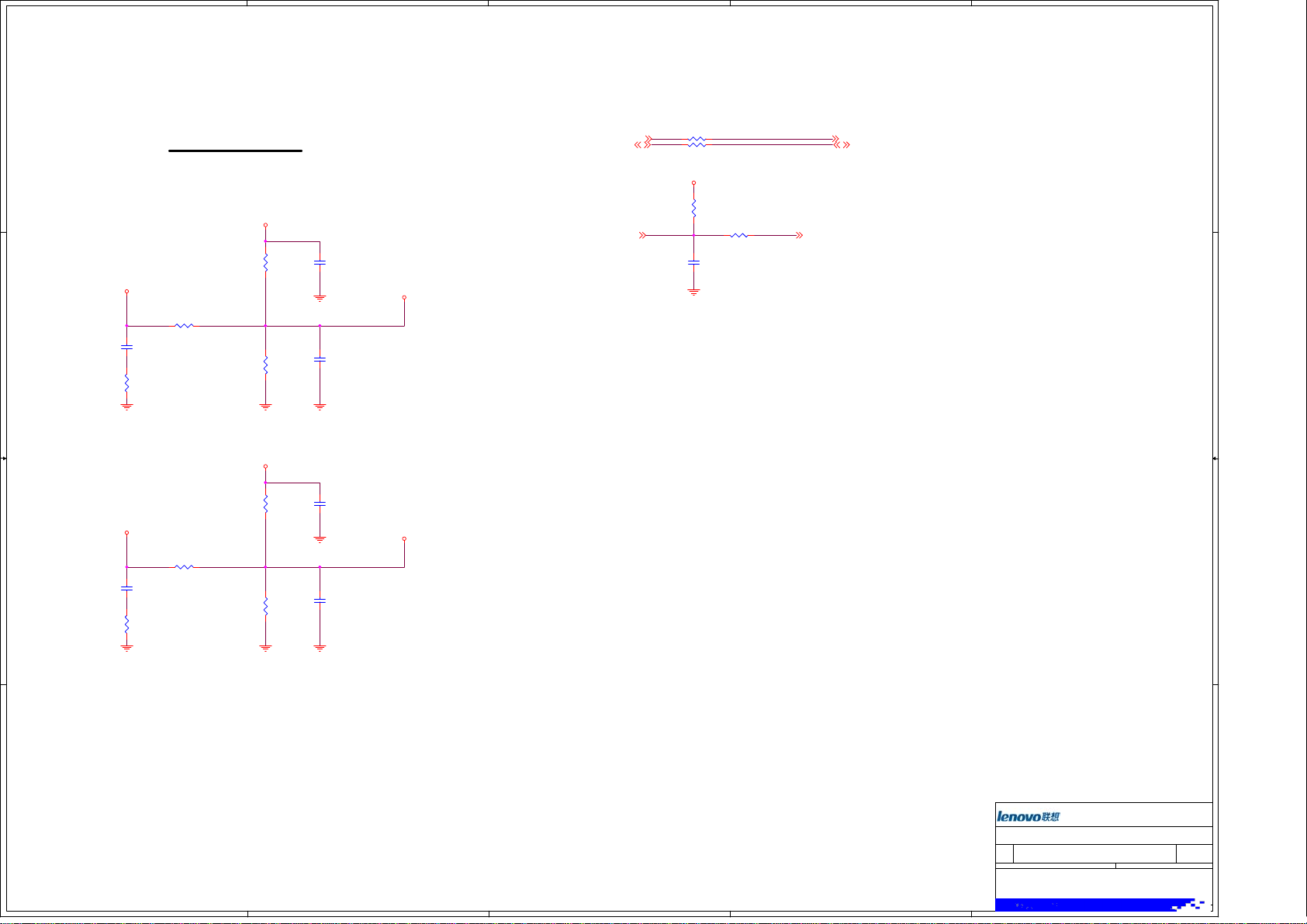

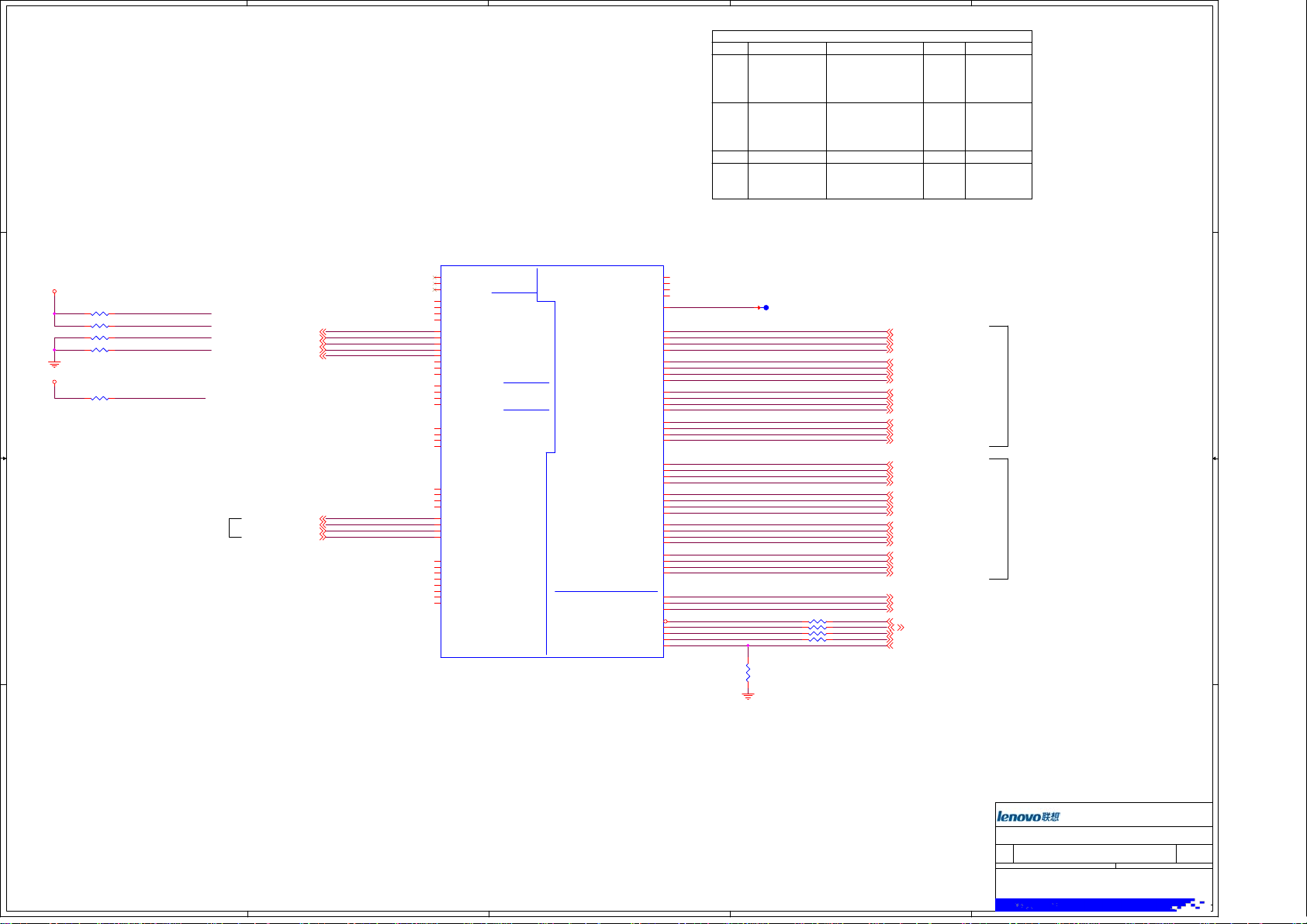

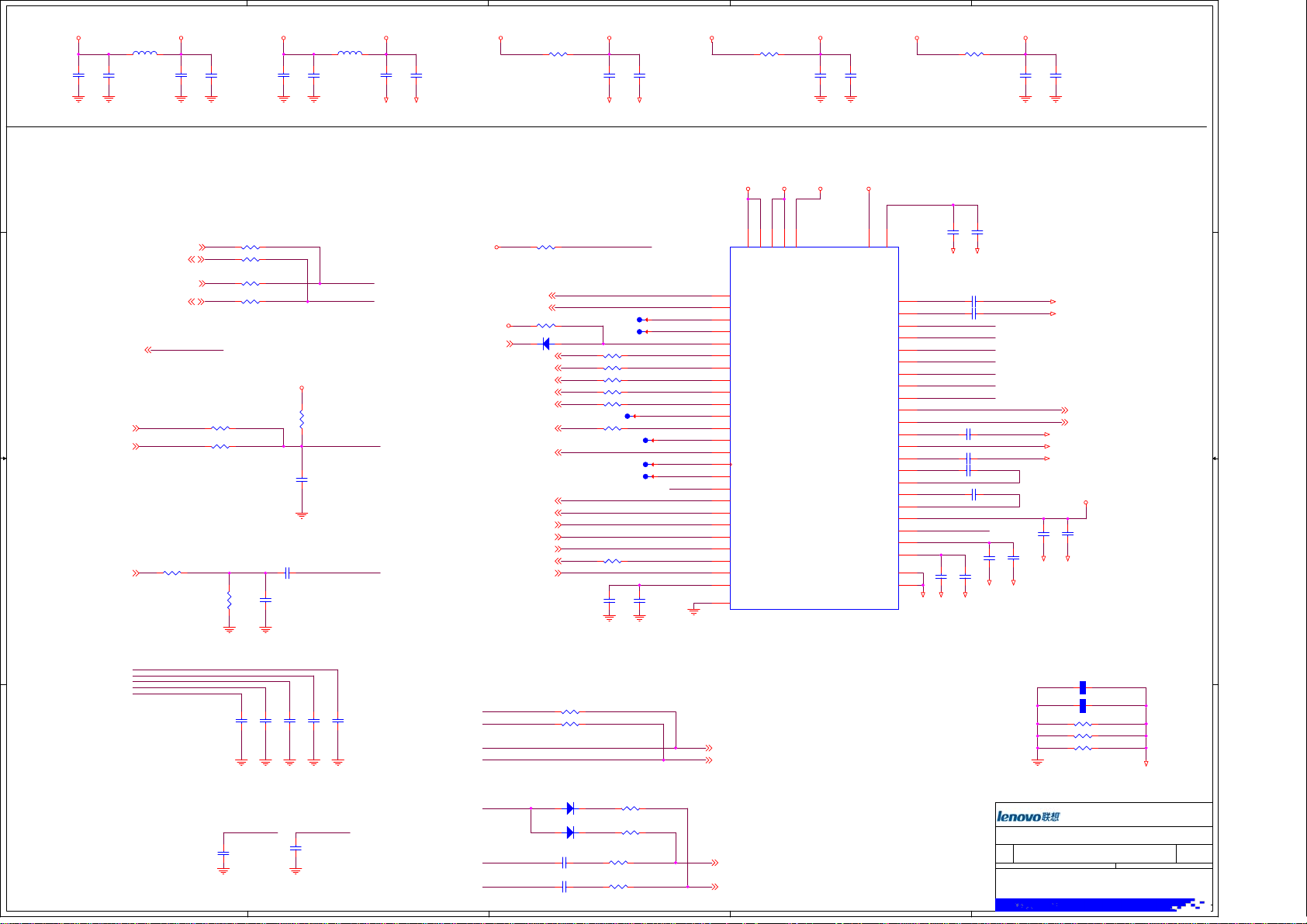

D D

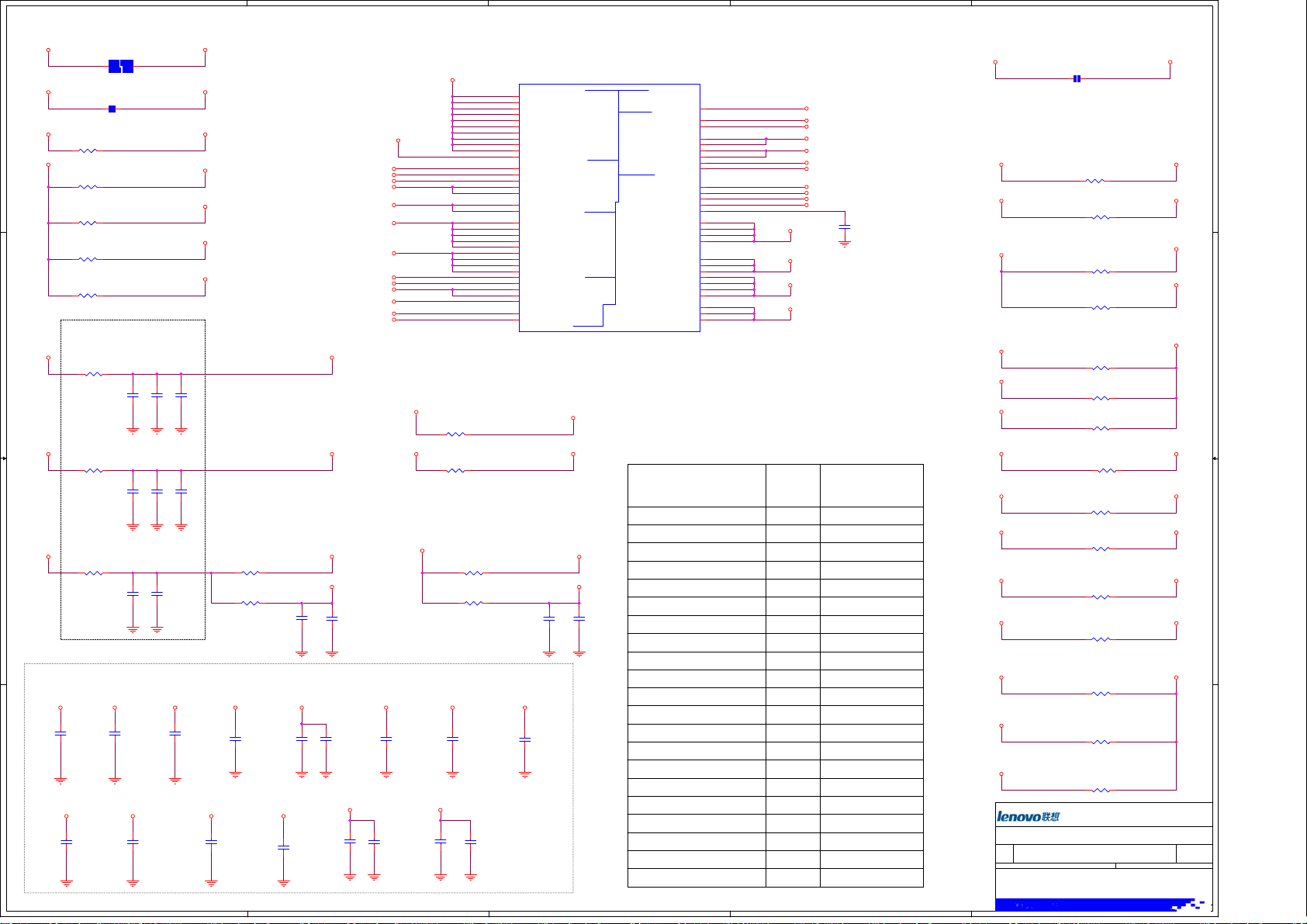

DDI B TO AR DPSNK0

C C

DDI C TO AR DPSNK1

DDI D TO DP Port

4

?

SKYLAKE_HALO

4 OF 14

SKL_H_BGA_BGA

BGA1440

CPU_DPB_TX0_DP34

CPU_DPB_TX0_DN34

CPU_DPB_TX1_DP34

CPU_DPB_TX1_DN34

CPU_DPB_TX2_DP34

CPU_DPB_TX2_DN34

CPU_DPB_TX3_DP34

CPU_DPB_TX3_DN34

CPU_DPB_AUX_DP34

CPU_DPB_AUX_DN34

CPU_DPC_TX0_DP35

CPU_DPC_TX0_DN35

CPU_DPC_TX1_DP35

CPU_DPC_TX1_DN35

CPU_DPC_TX2_DP35

CPU_DPC_TX2_DN35

CPU_DPC_TX3_DP35

CPU_DPC_TX3_DN35

CPU_DPC_AUX_DP35

CPU_DPC_AUX_DN35

CPU_DPD_TX0_DP32

CPU_DPD_TX0_DN32

CPU_DPD_TX1_DP32

CPU_DPD_TX1_DN32

CPU_DPD_TX2_DP32

CPU_DPD_TX2_DN32

CPU_DPD_TX3_DP32

CPU_DPD_TX3_DN32

CPU_DPD_AUX_DP32

CPU_DPD_AUX_DN32

K36

K37

J35

J34

H37

H36

J37

J38

D27

E27

H34

H33

F37

G38

F34

F35

E37

E36

F26

E26

C34

D34

B36

B34

F33

E33

C33

B33

A27

B27

DDI1_TXP[0]

DDI1_TXN[0]

DDI1_TXP[1]

DDI1_TXN[1]

DDI1_TXP[2]

DDI1_TXN[2]

DDI1_TXP[3]

DDI1_TXN[3]

DDI1_AUXP

DDI1_AUXN

DDI2_TXP[0]

DDI2_TXN[0]

DDI2_TXP[1]

DDI2_TXN[1]

DDI2_TXP[2]

DDI2_TXN[2]

DDI2_TXP[3]

DDI2_TXN[3]

DDI2_AUXP

DDI2_AUXN

DDI3_TXP[0]

DDI3_TXN[0]

DDI3_TXP[1]

DDI3_TXN[1]

DDI3_TXP[2]

DDI3_TXN[2]

DDI3_TXP[3]

DDI3_TXN[3]

DDI3_AUXP

DDI3_AUXN

3

U1D

EDP_TXP[0]

EDP_TXN[0]

EDP_TXP[1]

EDP_TXN[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXP

EDP_AUXN

EDP_DISP_UTIL

EDP_RCOMP

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

?

REV = 1

D29

E29

F28

E28

B29

A29

B28

C28

C26

B26

A33

EDP_UTIL

D37

EDP_RCOMP

BRD Note:

W=20mils;S=25mils;L<=100mils

G27

AUD_AZACPU_SCLK

G25

AUD_AZACPU_SDO

G29

AUD_AZACPU_SDI_R

1 2

R2 24.9_0402_1%

CAD Note:

Intergrated Codec for DP/HDMI

1 2

R3 22_0402_5%

CPU_EDP_TX0_DP

CPU_EDP_TX0_DN

CPU_EDP_TX1_DP

CPU_EDP_TX1_DN

CPU_EDP_AUX_DP

CPU_EDP_AUX_DN

1

TP1

+VCCIO

2

30

30

30

30

30

30

AUD_AZACPU_SCLK

AUD_AZACPU_SDO

AUD_AZACPU_SDI

DDI2 TO eDP

19

19

19

1

B B

A A

LENOVO.CRDN

LENOVO.CRDN

1

LENOVO.CRDN

39

39

39

of

of

Rev

Rev

Rev

V0.3

V0.3

V0.3

9Wednesday, January 27, 2016

9Wednesday, January 27, 2016

9Wednesday, January 27, 2016

Title

Title

Title

Processor--eDP/TBT/DP

Processor--eDP/TBT/DP

Processor--eDP/TBT/DP

Size Document Number

Size Document Number

Size

Document Number

C

C

C

Skylake-H

Skylake-H

Skylake-H

Date: Sheet

Date: Sheet

Date: Sheet of

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

5

4

3

2

5

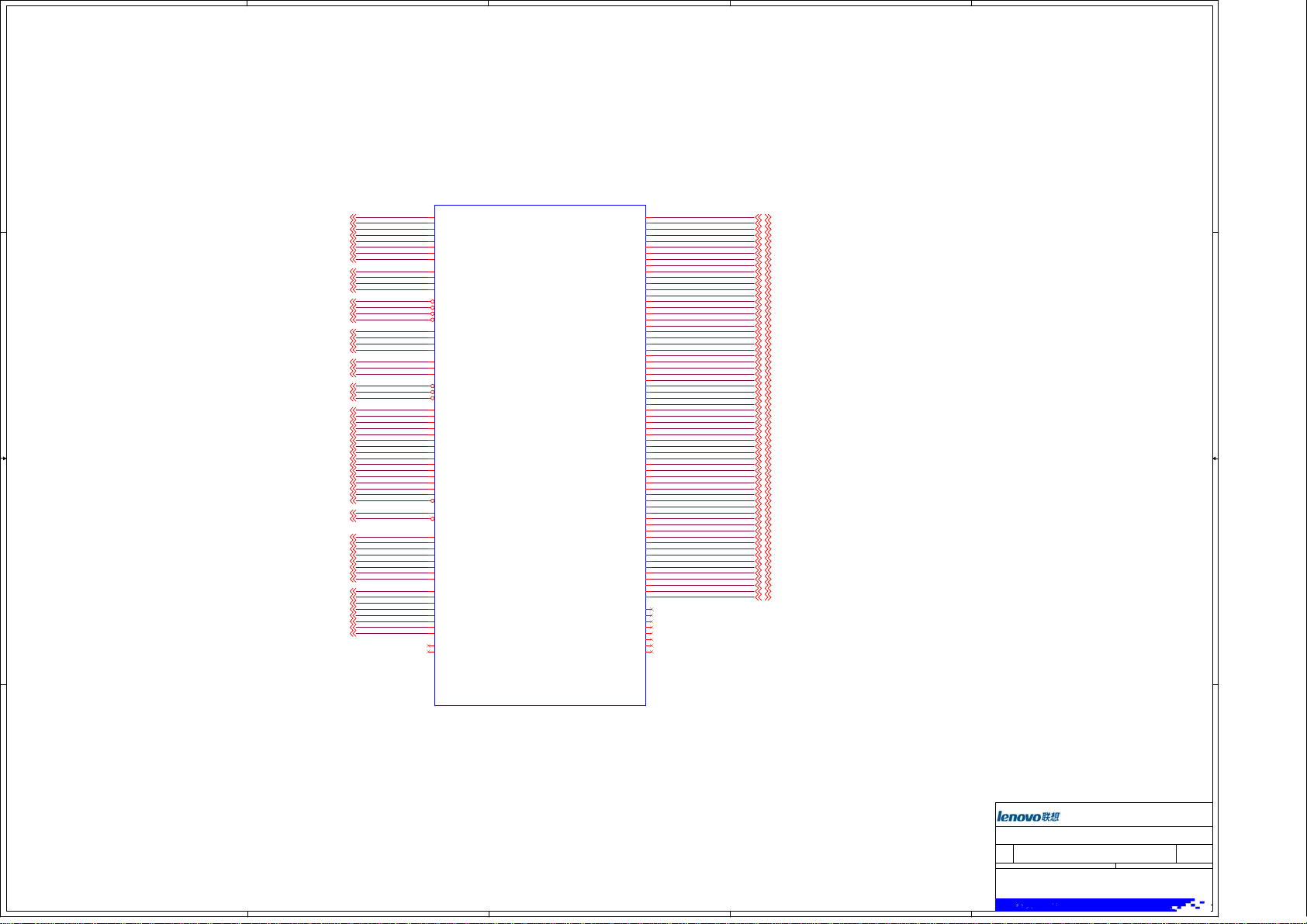

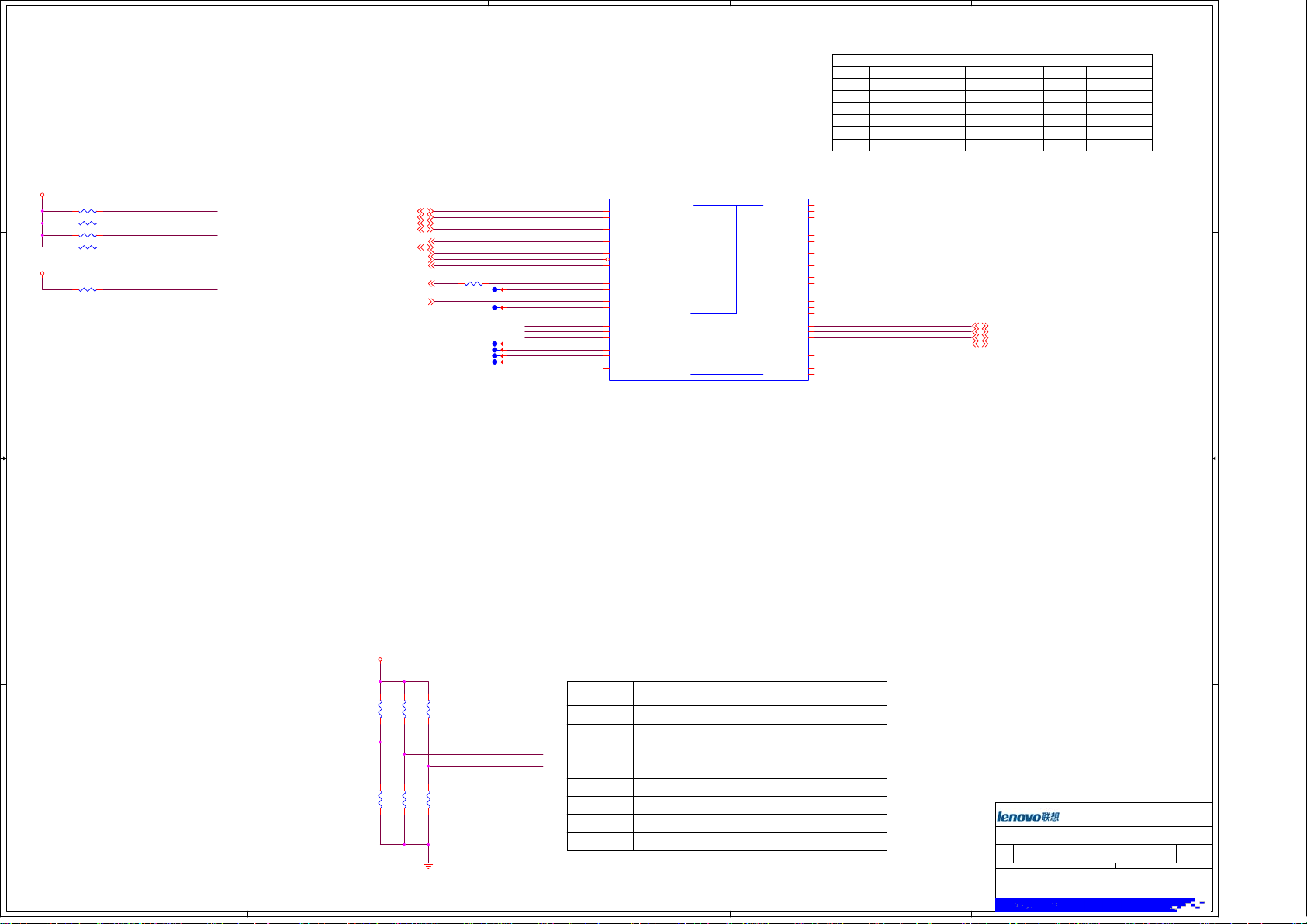

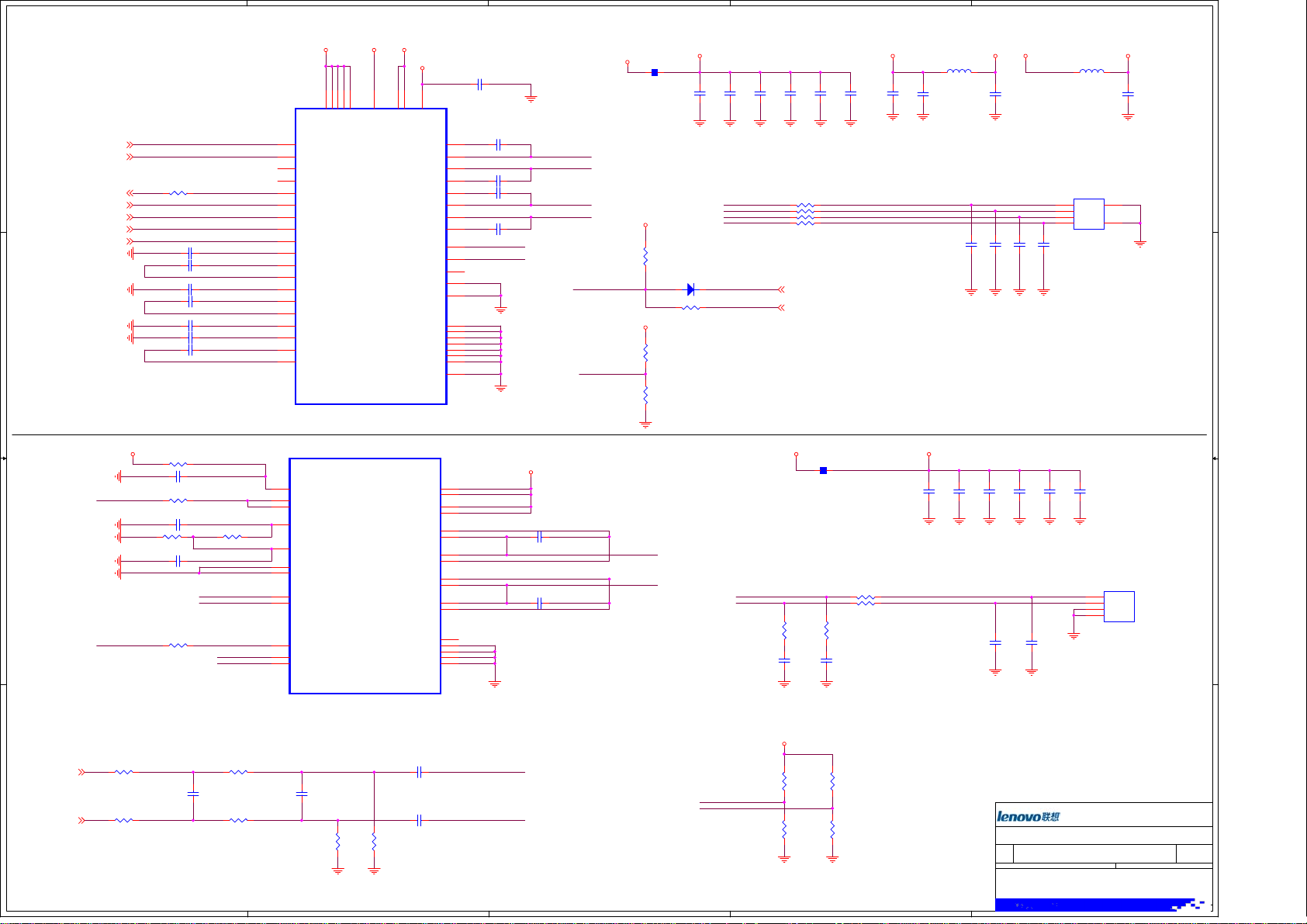

D D

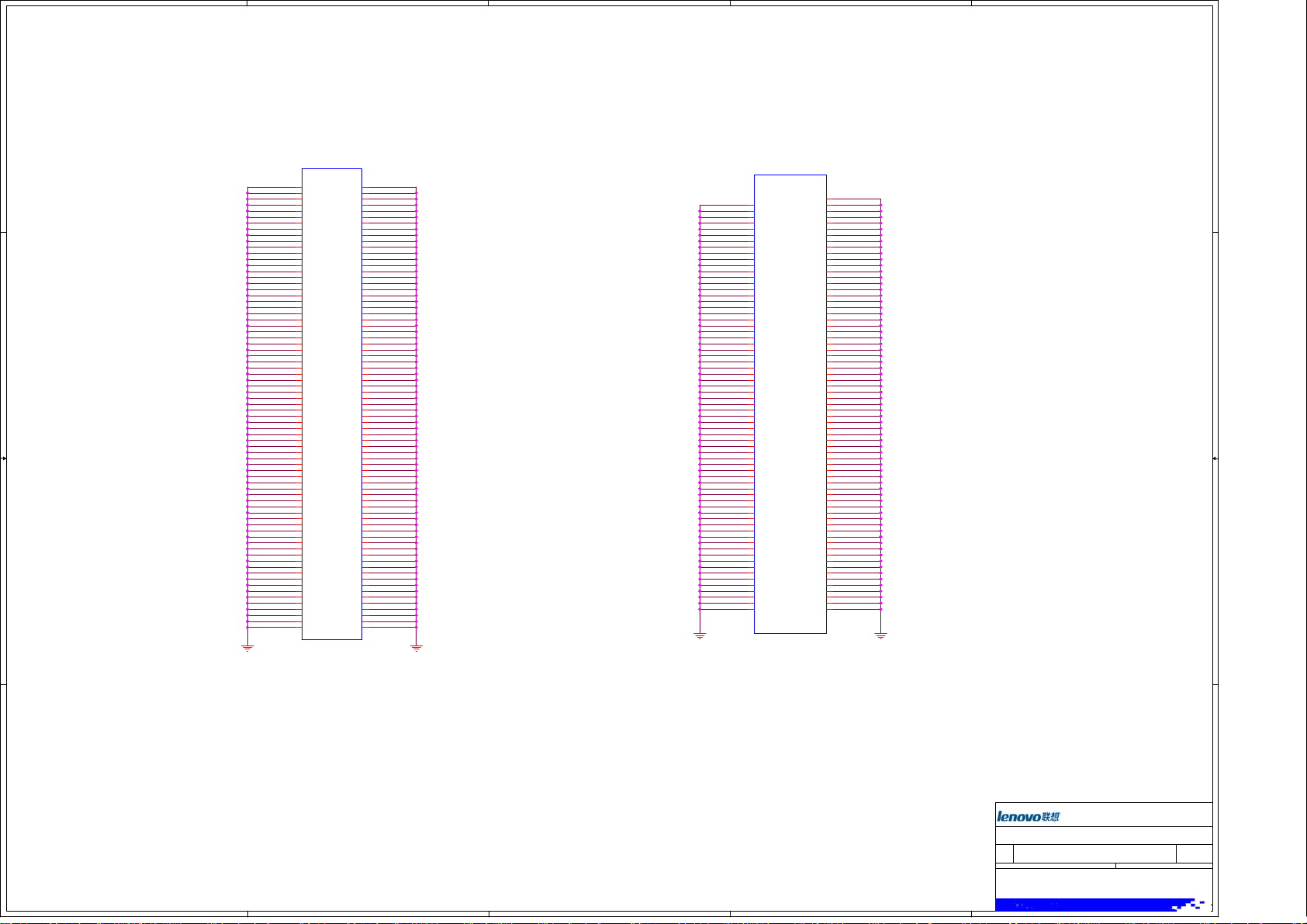

M_A_DIM0_CK_DDR0_DP12

M_A_DIM0_CK_DDR0_DN12

M_A_DIM0_CK_DDR1_DN12

M_A_DIM0_CK_DDR1_DP12

M_A_DIM1_CK_DDR2_DP13

M_A_DIM1_CK_DDR2_DN13

M_A_DIM1_CK_DDR3_DP13

M_A_DIM1_CK_DDR3_DN13

M_A_DIM0_CKE012

M_A_DIM0_CKE112

M_A_DIM1_CKE213

M_A_DIM1_CKE313

M_A_DIM0_CS0_N12

M_A_DIM0_CS1_N12

M_A_DIM1_CS2_N13

M_A_DIM1_CS3_N13

M_A_DIM0_ODT012

M_A_DIM0_ODT112

C C

B B

M_A_DIM1_ODT213

M_A_DIM1_ODT313

M_A_BA012,13

M_A_BA112,13

M_A_BG012,13

M_A_A16_RAS_N12,13

M_A_A14_WE_N12,13

M_A_A15_CAS_N12,13

M_A_A012,13

M_A_A112,13

M_A_A212,13

M_A_A312,13

M_A_A412,13

M_A_A512,13

M_A_A612,13

M_A_A712,13

M_A_A812,13

M_A_A912,13

M_A_A10_AP12,13

M_A_A1112,13

M_A_A1212,13

M_A_A1312,13

M_A_BG112,13

M_A_ACT_N12,13

DDR0_A_PARITY12,13

DDR0_A_ALERT_N12,13

M_A_DQS_DN012,13

M_A_DQS_DN112,13

M_A_DQS_DN212,13

M_A_DQS_DN312,13

M_A_DQS_DP412,13

M_A_DQS_DP512,13

M_A_DQS_DP612,13

M_A_DQS_DP712,13

M_A_DQS_DP012,13

M_A_DQS_DP112,13

M_A_DQS_DP212,13

M_A_DQS_DP312,13

M_A_DQS_DN412,13

M_A_DQS_DN512,13

M_A_DQS_DN612,13

M_A_DQS_DN712,13

4

?

SKYLAKE_HALO

AG1

DDR0_CKP[0]

AG2

DDR0_CKN[0]

AK1

DDR0_CKN[1]

AK2

DDR0_CKP[1]

AL3

DDR0_CLKP[2]

AK3

DDR0_CLKN[2]

AL2

DDR0_CLKP[3]

AL1

DDR0_CLKN[3]

AT1

DDR0_CKE[0]

AT2

DDR0_CKE[1]

AT3

DDR0_CKE[2]

AT5

DDR0_CKE[3]

AD5

DDR0_CS#[0]

AE2

DDR0_CS#[1]

AD2

DDR0_CS#[2]

AE5

DDR0_CS#[3]

AD3

DDR0_ODT[0]

AE4

DDR0_ODT[1]

AE1

DDR0_ODT[2]

AD4

DDR0_ODT[3]

AH5

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

AH1

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

AU1

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

AH4

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

AG4

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

AD1

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

AH3

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

AP4

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

AN4

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

AP5

DDR0_MA[3]

AP2

DDR0_MA[4]

AP1

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

AP3

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

AN1

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

AN3

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

AT4

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

AH2

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

AN2

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

AU4

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

AE3

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

AU2

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

AU3

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

AG3

DDR0_PAR

AU5

DDR0_ALERT#

BR5

DDR0_DQSN[0]

BL3

DDR0_DQSN[1]

BG3

DDR0_DQSN[2]/DDR0_DQSN[4]

BD3

DDR0_DQSN[3]/DDR0_DQSN[5]

AB3

DDR0_DQSP[4]/DDR1_DQSP[0]

V3

DDR0_DQSP[5]/DDR1_DQSP[1]

R3

DDR0_DQSP[6]/DDR1_DQSP[4]

M3

DDR0_DQSP[7]/DDR1_DQSP[5]

BP5

DDR0_DQSP[0]

BK3

DDR0_DQSP[1]

BF3

DDR0_DQSP[2]/DDR0_DQSP[4]

BC3

DDR0_DQSP[3]/DDR0_DQSP[5]

AA3

DDR0_DQSN[4]/DDR1_DQSN[0]

U3

DDR0_DQSN[5]/DDR1_DQSN[1]

P3

DDR0_DQSN[6]/DDR1_DQSN[4]

L3

DDR0_DQSN[7]/DDR1_DQSN[5]

AY3

DDR0_DQSP[8]

BA3

DDR0_DQSN[8]

BGA1440

3

U1A

DDR0_DQ[0]

DDR0_DQ[1]

DDR0_DQ[2]

DDR0_DQ[3]

DDR0_DQ[4]

DDR0_DQ[5]

DDR0_DQ[6]

DDR0_DQ[7]

DDR0_DQ[8]

DDR0_DQ[9]

DDR0_DQ[10]

DDR0_DQ[11]

DDR0_DQ[12]

DDR0_DQ[13]

DDR0_DQ[14]

DDR0_DQ[15]

DDR0_DQ[16]/DDR0_DQ[32]

DDR0_DQ[17]/DDR0_DQ[33]

DDR0_DQ[18]/DDR0_DQ[34]

DDR0_DQ[19]/DDR0_DQ[35]

DDR0_DQ[20]/DDR0_DQ[36]

DDR0_DQ[21]/DDR0_DQ[37]

DDR0_DQ[22]/DDR0_DQ[38]

DDR0_DQ[23]/DDR0_DQ[39]

DDR0_DQ[24]/DDR0_DQ[40]

DDR0_DQ[25]/DDR0_DQ[41]

DDR0_DQ[26]/DDR0_DQ[42]

DDR0_DQ[27]/DDR0_DQ[43]

DDR0_DQ[28]/DDR0_DQ[44]

DDR0_DQ[29]/DDR0_DQ[45]

DDR0_DQ[30]/DDR0_DQ[46]

DDR0_DQ[31]/DDR0_DQ[47]

DDR0_DQ[32]/DDR1_DQ[0]

DDR0_DQ[33]/DDR1_DQ[1]

DDR0_DQ[34]/DDR1_DQ[2]

DDR0_DQ[35]/DDR1_DQ[3]

DDR0_DQ[36]/DDR1_DQ[4]

DDR0_DQ[37]/DDR1_DQ[5]

DDR0_DQ[38]/DDR1_DQ[6]

DDR0_DQ[39]/DDR1_DQ[7]

DDR0_DQ[40]/DDR1_DQ[8]

DDR0_DQ[41]/DDR1_DQ[9]

DDR0_DQ[42]/DDR1_DQ[10]

DDR0_DQ[43]/DDR1_DQ[11]

DDR0_DQ[44]/DDR1_DQ[12]

DDR0_DQ[45]/DDR1_DQ[13]

DDR0_DQ[46]/DDR1_DQ[14]

DDR0_DQ[47]/DDR1_DQ[15]

DDR0_DQ[48]/DDR1_DQ[32]

DDR0_DQ[49]/DDR1_DQ[33]

DDR0_DQ[50]/DDR1_DQ[34]

DDR0_DQ[51]/DDR1_DQ[35]

DDR0_DQ[52]/DDR1_DQ[36]

DDR0_DQ[53]/DDR1_DQ[37]

DDR0_DQ[54]/DDR1_DQ[38]

DDR0_DQ[55]/DDR1_DQ[39]

DDR0_DQ[56]/DDR1_DQ[40]

DDR0_DQ[57]/DDR1_DQ[41]

DDR0_DQ[58]/DDR1_DQ[42]

DDR0_DQ[59]/DDR1_DQ[43]

DDR0_DQ[60]/DDR1_DQ[44]

DDR0_DQ[61]/DDR1_DQ[45]

DDR0_DQ[62]/DDR1_DQ[46]

DDR0_DQ[63]/DDR1_DQ[47]

DDR0_ECC[0]

DDR0_ECC[1]

DDR0_ECC[2]

DDR0_ECC[3]

DDR0_ECC[4]

DDR0_ECC[5]

DDR0_ECC[6]

DDR0_ECC[7]

2

BR6

M_A_DQ0

BT6

M_A_DQ1

BP3

M_A_DQ2

BR3

M_A_DQ3

BN5

M_A_DQ4

BP6

M_A_DQ5

BP2

M_A_DQ6

BN3

M_A_DQ7

BL4

M_A_DQ8

BL5

M_A_DQ9

BL2

M_A_DQ10

BM1

M_A_DQ11

BK4

M_A_DQ12

BK5

M_A_DQ13

BK1

M_A_DQ14

BK2

M_A_DQ15

BG4

M_A_DQ16

BG5

M_A_DQ17

BF4

M_A_DQ18

BF5

M_A_DQ19

BG2

M_A_DQ20

BG1

M_A_DQ21

BF1

M_A_DQ22

BF2

M_A_DQ23

BD2

M_A_DQ24

BD1

M_A_DQ25

BC4

M_A_DQ26

BC5

M_A_DQ27

BD5

M_A_DQ28

BD4

M_A_DQ29

BC1

M_A_DQ30

BC2

M_A_DQ31

AB1

M_A_DQ32

AB2

M_A_DQ33

AA4

M_A_DQ34

AA5

M_A_DQ35

AB5

M_A_DQ36

AB4

M_A_DQ37

AA2

M_A_DQ38

AA1

M_A_DQ39

V5

M_A_DQ40

V2

M_A_DQ41

U1

M_A_DQ42

U2

M_A_DQ43

V1

M_A_DQ44

V4

M_A_DQ45

U5

M_A_DQ46

U4

M_A_DQ47

R2

M_A_DQ48

P5

M_A_DQ49

R4

M_A_DQ50

P4

M_A_DQ51

R5

M_A_DQ52

P2

M_A_DQ53

R1

M_A_DQ54

P1

M_A_DQ55

M4

M_A_DQ56

M1

M_A_DQ57

L4

M_A_DQ58

L2

M_A_DQ59

M5

M_A_DQ60

M2

M_A_DQ61

L5

M_A_DQ62

L1

M_A_DQ63

BA2

BA1

AY4

AY5

BA5

BA4

AY1

AY2

12,13

M_A_DQ0

M_A_DQ1

12,13

12,13

M_A_DQ2

12,13

M_A_DQ3

M_A_DQ4

12,13

12,13

M_A_DQ5

M_A_DQ6

12,13

M_A_DQ7

12,13

12,13

M_A_DQ8

M_A_DQ9

12,13

M_A_DQ10

12,13

12,13

M_A_DQ11

M_A_DQ12

12,13

12,13

M_A_DQ13

12,13

M_A_DQ14

M_A_DQ15

12,13

12,13

M_A_DQ16

M_A_DQ17

12,13

M_A_DQ18

12,13

12,13

M_A_DQ19

12,13

M_A_DQ20

12,13

M_A_DQ21

12,13

M_A_DQ22

M_A_DQ23

12,13

M_A_DQ24

12,13

12,13

M_A_DQ25

M_A_DQ26

12,13

12,13

M_A_DQ27

12,13

M_A_DQ28

M_A_DQ29

12,13

12,13

M_A_DQ30

M_A_DQ31

12,13

M_A_DQ32

12,13

12,13

M_A_DQ33

M_A_DQ34

12,13

M_A_DQ35

12,13

12,13

M_A_DQ36

M_A_DQ37

12,13

12,13

M_A_DQ38

12,13

M_A_DQ39

M_A_DQ40

12,13

12,13

M_A_DQ41

M_A_DQ42 12,13

M_A_DQ43

12,13

12,13

M_A_DQ44

12,13

M_A_DQ45

M_A_DQ46

12,13

12,13

M_A_DQ47

M_A_DQ48

12,13

M_A_DQ49

12,13

12,13

M_A_DQ50

M_A_DQ51

12,13

12,13

M_A_DQ52

12,13

M_A_DQ53

M_A_DQ54

12,13

M_A_DQ55

12,13

M_A_DQ56

12,13

M_A_DQ57

12,13

M_A_DQ58

12,13

M_A_DQ59 12,13

12,13

M_A_DQ60

M_A_DQ61

12,13

M_A_DQ62 12,13

12,13

M_A_DQ63

1

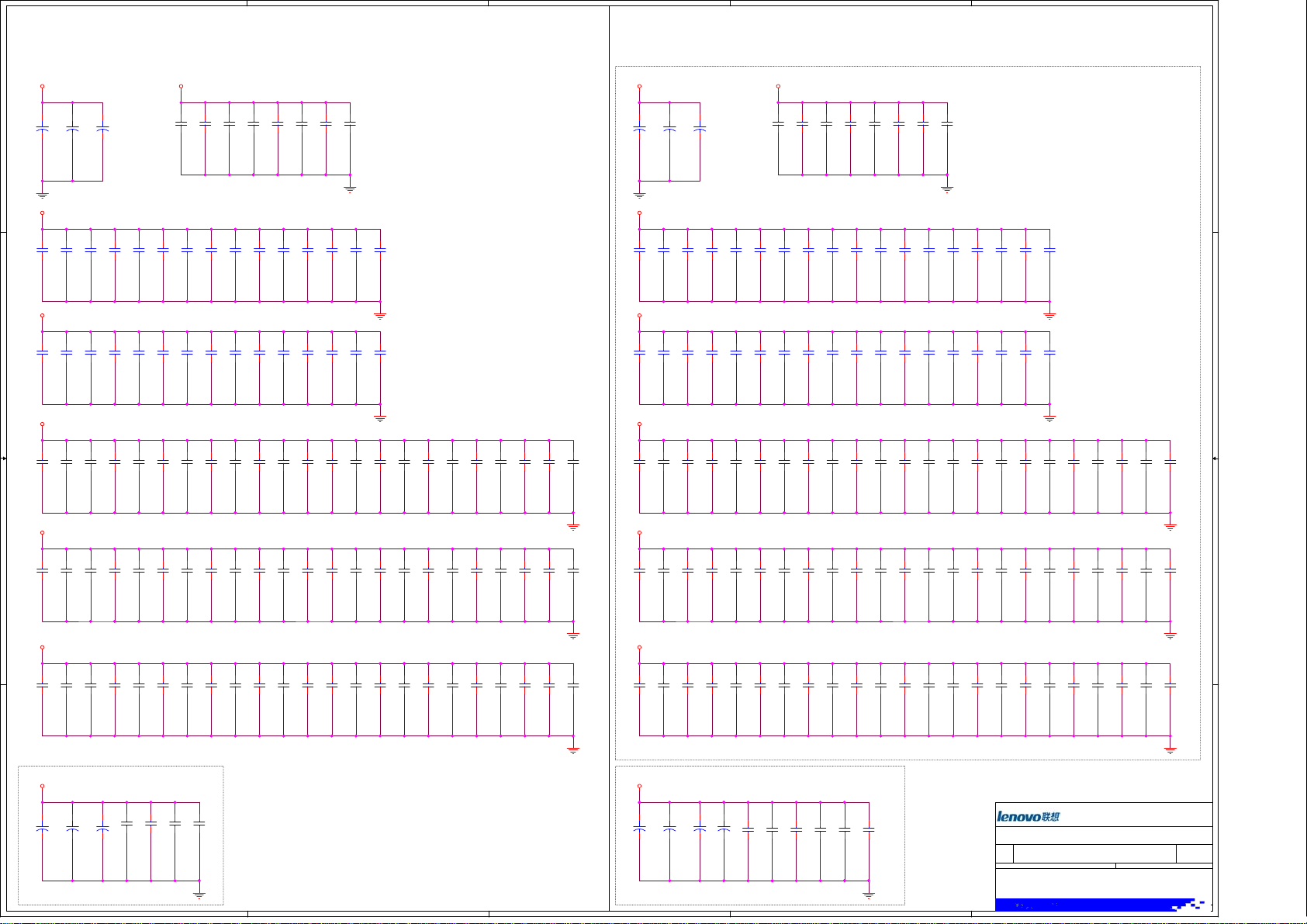

DDR CHANNEL A

?

A A

5

4

1 OF 14

SKL_H_BGA_BGA

REV = 1

3

LENOVO.CRDN

LENOVO.CRDN

1

LENOVO.CRDN

49

49

49

of

of

of

Rev

Rev

Rev

V0.3

V0.3

V0.3

9Wednesday, January 27, 2016

9Wednesday, January 27, 2016

9Wednesday, January 27, 2016

Title

Title

Title

PROCESSOR-MEM_CH A

PROCESSOR-MEM_CH A

PROCESSOR-MEM_CH A

Document Number

Size Document Number

Size Document Number

Size

C

C

C

Skylake-H

Skylake-H

Skylake-H

Date: Sheet

Date: Sheet

Date: Sheet

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

2

5

4

3

2

1

D D

M_B_DIM0_CK_DDR0_DP14

M_B_DIM0_CK_DDR0_DN14

M_B_DIM0_CK_DDR1_DN14

M_B_DIM0_CK_DDR1_DP14

M_B_DIM1_CK_DDR2_DP15

M_B_DIM1_CK_DDR2_DN15

M_B_DIM1_CK_DDR3_DP15

M_B_DIM1_CK_DDR3_DN15

M_B_DIM0_CKE014

M_B_DIM0_CKE114

M_B_DIM1_CKE215

M_B_DIM1_CKE315

M_B_DIM0_CS0_N14

M_B_DIM0_CS1_N14

M_B_DIM1_CS2_N15

M_B_DIM1_CS3_N15

M_B_DIM0_ODT014

M_B_DIM0_ODT114

M_B_DIM1_ODT215

M_B_DIM1_ODT315

M_B_A16_RAS_N14,15

M_B_A14_WE_N14,15

M_B_A15_CAS_N14,15

M_B_BA014,15

M_B_BA114,15

M_B_BG014,15

C C

B B

+V_CPU_VREF_CA

+V_CPU_VREF_DQ_CHB

M_B_A014,15

M_B_A114,15

M_B_A214,15

M_B_A314,15

M_B_A414,15

M_B_A514,15

M_B_A614,15

M_B_A714,15

M_B_A814,15

M_B_A914,15

M_B_A10_AP14,15

M_B_A1114,15

M_B_A1214,15

M_B_A1314,15

M_B_BG114,15

M_B_ACT_N14,15

DDR1_B_PARITY14,15

DDR1_B_ALERT_N14,15

M_B_DQS_DN014,15

M_B_DQS_DN114,15

M_B_DQS_DN214,15

M_B_DQS_DN314,15

M_B_DQS_DN414,15

M_B_DQS_DN514,15

M_B_DQS_DN614,15

M_B_DQS_DN714,15

M_B_DQS_DP014,15

M_B_DQS_DP114,15

M_B_DQS_DP214,15

M_B_DQS_DP314,15

M_B_DQS_DP414,15

M_B_DQS_DP514,15

M_B_DQS_DP614,15

M_B_DQS_DP714,15

1

+V_CPU_VREF_DQ_CHA

TP124

AM9

DDR1_CKP[0]

AN9

DDR1_CKN[0]

AM8

DDR1_CKN[1]

AM7

DDR1_CKP[1]

AM11

DDR1_CLKP[2]

AM10

DDR1_CLKN[2]

AJ10

DDR1_CLKP[3]

AJ11

DDR1_CLKN[3]

AT8

DDR1_CKE[0]

AT10

DDR1_CKE[1]

AT7

DDR1_CKE[2]

AT11

DDR1_CKE[3]

AF11

DDR1_CS#[0]

AE7

DDR1_CS#[1]

AF10

DDR1_CS#[2]

AE10

DDR1_CS#[3]

AF7

DDR1_ODT[0]

AE8

DDR1_ODT[1]

AE9

DDR1_ODT[2]

AE11

DDR1_ODT[3]

AH10

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

AH11

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

AF8

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

AH8

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

AH9

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

AR9

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

AJ9

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

AK6

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

AK5

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

AL5

DDR1_MA[3]

AL6

DDR1_MA[4]

AM6

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

AN7

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

AN10

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

AN8

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

AR11

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

AH7

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

AN11

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

AR10

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

AF9

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

AR7

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

AT9

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

AJ7

DDR1_PAR

AR8

DDR1_ALERT#

BP9

DDR1_DQSN[0]/DDR0_DQSN[2]

BL9

DDR1_DQSN[1]/DDR0_DQSN[3]

BG9

DDR1_DQSN[2]/DDR0_DQSN[6]

BC9

DDR1_DQSN[3]/DDR0_DQSN[7]

AC9

DDR1_DQSN[4]/DDR1_DQSN[2]

W9

DDR1_DQSN[5]/DDR1_DQSN[3]

R9

DDR1_DQSN[6]

M9

DDR1_DQSN[7]

BR9

DDR1_DQSP[0]/DDR0_DQSP[2]

BJ9

DDR1_DQSP[1]/DDR0_DQSP[3]

BF9

DDR1_DQSP[2]/DDR0_DQSP[6]

BB9

DDR1_DQSP[3]/DDR0_DQSP[7]

AA9

DDR1_DQSP[4]/DDR1_DQSP[2]

V9

DDR1_DQSP[5]/DDR1_DQSP[3]

P9

DDR1_DQSP[6]

L9

DDR1_DQSP[7]

AW9

DDR1_DQSP[8]

AY9

DDR1_DQSN[8]

BN13

DDR_VREF_CA

BP13

DDR0_VREF_DQ

BR13

DDR1_VREF_DQ

?

?

SKYLAKE_HALO

BGA1440

2 OF 14 REV = 1

U1B

DDR1_DQ[0]/DDR0_DQ[16]

DDR1_DQ[1]/DDR0_DQ[17]

DDR1_DQ[2]/DDR0_DQ[18]

DDR1_DQ[3]/DDR0_DQ[19]

DDR1_DQ[4]/DDR0_DQ[20]

DDR1_DQ[5]/DDR0_DQ[21]

DDR1_DQ[6]/DDR0_DQ[22]

DDR1_DQ[7]/DDR0_DQ[23]

DDR1_DQ[8]/DDR0_DQ[24]

DDR1_DQ[9]/DDR0_DQ[25]

DDR1_DQ[10]/DDR0_DQ[26]

DDR1_DQ[11]/DDR0_DQ[27]

DDR1_DQ[12]/DDR0_DQ[28]

DDR1_DQ[13]/DDR0_DQ[29]

DDR1_DQ[14]/DDR0_DQ[30]

DDR1_DQ[15]/DDR0_DQ[31]

DDR1_DQ[16]/DDR0_DQ[48]

DDR1_DQ[17]/DDR0_DQ[49]

DDR1_DQ[18]/DDR0_DQ[50]

DDR1_DQ[19]/DDR0_DQ[51]

DDR1_DQ[20]/DDR0_DQ[52]

DDR1_DQ[21]/DDR0_DQ[53]

DDR1_DQ[22]/DDR0_DQ[54]

DDR1_DQ[23]/DDR0_DQ[55]

DDR1_DQ[24]/DDR0_DQ[56]

DDR1_DQ[25]/DDR0_DQ[57]

DDR1_DQ[26]/DDR0_DQ[58]

DDR1_DQ[27]/DDR0_DQ[59]

DDR1_DQ[28]/DDR0_DQ[60]

DDR1_DQ[29]/DDR0_DQ[61]

DDR1_DQ[30]/DDR0_DQ[62]

DDR1_DQ[31]/DDR0_DQ[63]

DDR1_DQ[32]/DDR1_DQ[16]

DDR1_DQ[33]/DDR1_DQ[17]

DDR1_DQ[34]/DDR1_DQ[18]

DDR1_DQ[35]/DDR1_DQ[19]

DDR1_DQ[36]/DDR1_DQ[20]

DDR1_DQ[37]/DDR1_DQ[21]

DDR1_DQ[38]/DDR1_DQ[22]

DDR1_DQ[39]/DDR1_DQ[23]

DDR1_DQ[40]/DDR1_DQ[24]

DDR1_DQ[41]/DDR1_DQ[25]

DDR1_DQ[42]/DDR1_DQ[26]

DDR1_DQ[43]/DDR1_DQ[27]

DDR1_DQ[44]/DDR1_DQ[28]

DDR1_DQ[45]/DDR1_DQ[29]

DDR1_DQ[46]/DDR1_DQ[30]

DDR1_DQ[47]/DDR1_DQ[31]

DDR1_DQ[48]

DDR1_DQ[49]

DDR1_DQ[50]

DDR1_DQ[51]

DDR1_DQ[52]

DDR1_DQ[53]

DDR1_DQ[54]

DDR1_DQ[55]

DDR1_DQ[56]

DDR1_DQ[57]

DDR1_DQ[58]

DDR1_DQ[59]

DDR1_DQ[60]

DDR1_DQ[61]

DDR1_DQ[62]

DDR1_DQ[63]

DDR1_ECC[0]

DDR1_ECC[1]

DDR1_ECC[2]

DDR1_ECC[3]

DDR1_ECC[4]

DDR1_ECC[5]

DDR1_ECC[6]

DDR1_ECC[7]

DDR CHANNEL B

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

SKL_H_BGA_BGA

BT11

BR11

BT8

BR8

BP11

BN11

BP8

BN8

BL12

BL11

BL8

BJ8

BJ11

BJ10

BL7

BJ7

BG11

BG10

BG8

BF8

BF11

BF10

BG7

BF7

BB11

BC11

BB8

BC8

BC10

BB10

BC7

BB7

AA11

AA10

AC11

AC10

AA7

AA8

AC8

AC7

W8

W7

V10

V11

W11

W10

V7

V8

R11

P11

P7

R8

R10

P10

R7

P8

L11

M11

L7

M8

L10

M10

M7

L8

AW11

AY11

AY8

AW8

AY10

AW10

AY7

AW7

G1

H1

J2

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

DDR_RCOMP0

DDR_RCOMP1

DDR_RCOMP2

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6 14,15

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53 14,15

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

R4 121_0402_1%

R5 75_0402_1%

R6 100_0402_1%

12

12

12

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

14,15

BRD Note:DDR_RCOMP*

W=15mils;S=20mils;L<=500mils

A A

LENOVO.CRDN

LENOVO.CRDN

1

LENOVO.CRDN

59

59

59

of

of

of

Rev

Rev

Rev

V0.3

V0.3

V0.3

9Wednesday, January 27, 2016

9Wednesday, January 27, 2016

9Wednesday, January 27, 2016

Title

Title

Title

PROCESSOR-MEM_CH B

PROCESSOR-MEM_CH B

PROCESSOR-MEM_CH B

Size

Document Number

Size Document Number

Size Document Number

C

C

C

Skylake-H

Skylake-H

Skylake-H

Date: Sheet

Date: Sheet

Date: Sheet

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

5

4

3

2

5

4

3

2

1

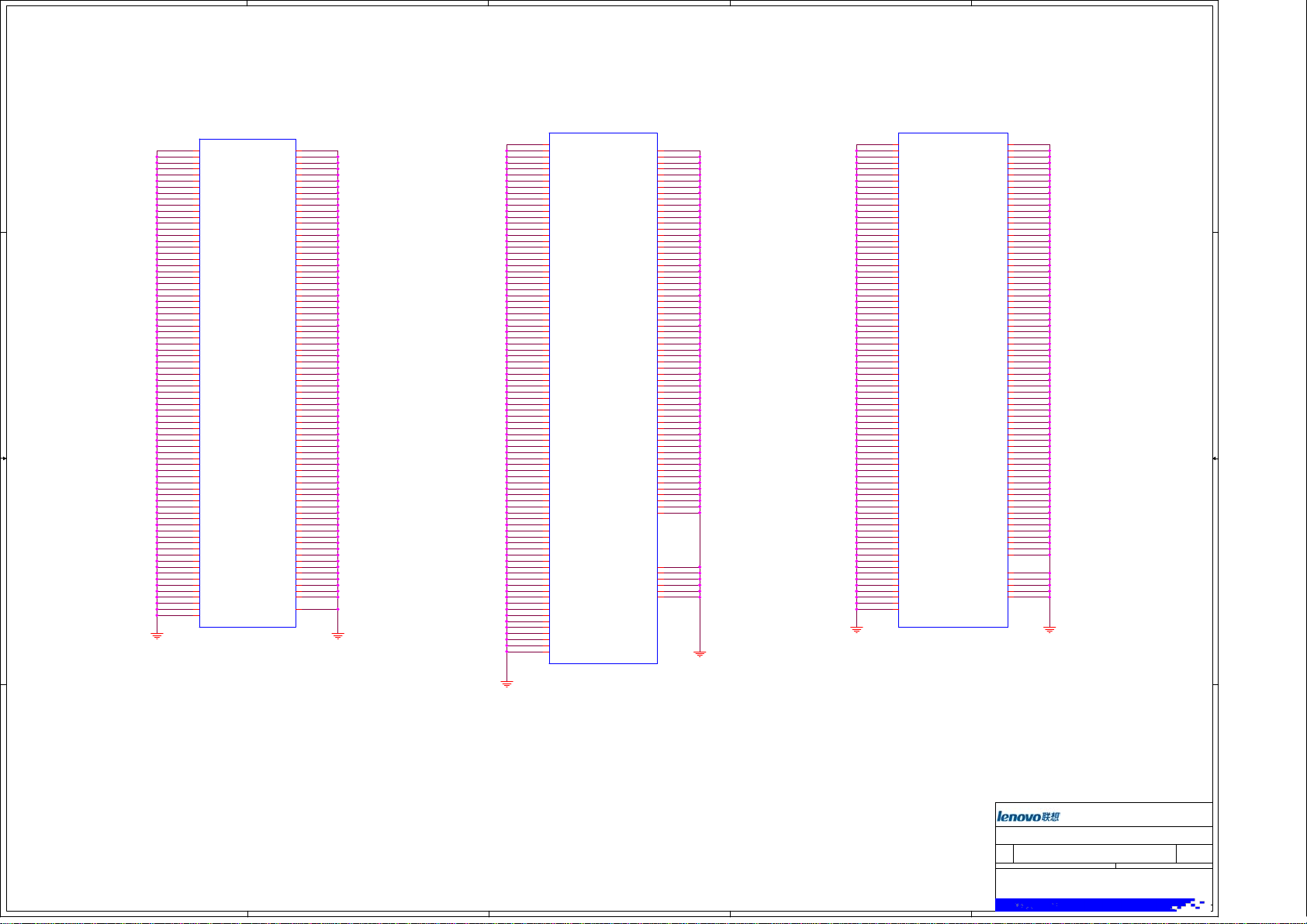

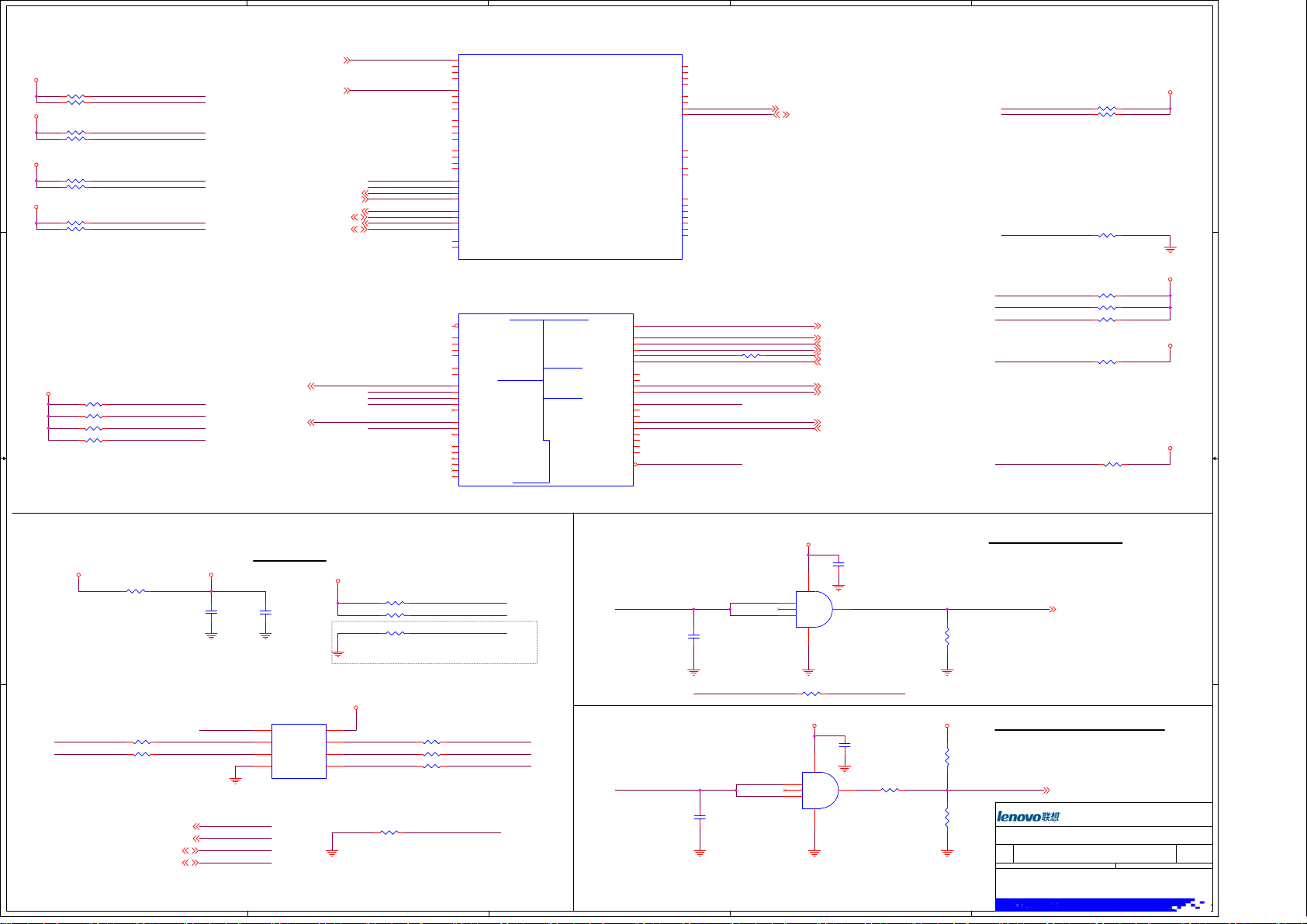

+1.0V_VCCST

12

R8

R7

56.2_0402_1%

100_0402_1%

1 2

D D

C C

CPU_SVIDALERT_N83,86

CPU_SVIDCLK83,86

CPU_SVIDDATA83,86

+1.0V_VCCSTG

+1.0V_VCCST

12

R11 1K_0402_5%

12

R14 1K_0402_5%

12

R15 1K_0402_5%

BRD Note: SVID

S=18mils;Z=50ohm

1 2

R9 220_0402_5%

1 2

R46 0_0402_5%

1 2

R48 0_0402_5%

H_PROCHOT_N

H_VCCST_PWRGD

H_THRMTRIP_N

CPU_SVID_ALERT_N

CPU_SVID_CLK

CPU_SVID_DATA

?

SKYLAKE_HALO

BCLKP

BCLKN

PCI_BCLKP

PCI_BCLKN

CLK24P

CLK24N

VIDALERT#

VIDSCK

VIDSOUT

PROCHOT#

DDR_VTT_CNTL

VCCST_PWRGD

PROCPWRGD

RESET#

PM_SYNC

PM_DOWN

PECI

THERMTRIP#

SKTOCC#

PROC_SELECT#

CATERR#

5 OF 14

SKL_H_BGA_BGA

BGA1440

BH31

BH32

BH29

BR30

BT13

BT31

BP35

BM34

BP31

BT34

BR33

BM30

B31

A32

D35

C36

E31

D31

H13

J31

BN1

CK_CPU_BCLK_P22

CK_CPU_BCLK_N22

CK_CPU_PCIBCLK_P22

CK_CPU_PCIBCLK_N22

CK_CPU_24M_P22

CK_CPU_24M_N22

CPU_SVID_ALERT_N

CPU_SVID_CLK

CPU_SVID_DATA

12

TP115

TP4

H_PROCHOT_N_R

DDR_VTT_PG_CTRL

H_VCCST_PWRGD_R

H_PWRGD

CPU_PLTRST_N

H_PM_SYNC

H_PM_DOWN_R

H_PECI

H_THRMTRIP_N

1

H_SKTOCC_N

PROC_SELECT_N

1

H_CATERR_N

H_PROCHOT_N44

DDR_VTT_PG_CTRL49

H_VCCST_PWRGD49

H_PWRGD19

CPU_PLTRST_N20

H_PM_SYNC20

H_PM_DOWN20

H_PECI20,26

H_THRMTRIP_N20,71

R13 499_0402_1%

1 2

R17 60.4_0402_1%

1 2

R18 22_0402_5%

1 2

R21 0_0402_5%@

PROC_TDO

PROC_TMS

PROC_TCK

PROC_TRST#

PROC_PREQ#

PROC_PRDY#

CFG_RCOMP

REV = 1

U1E

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[17]

CFG[16]

CFG[19]

CFG[18]

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

PROC_TDI

?

BN25

BN27

BN26

BN28

BR20

BM20

BT20

BP20

BR23

BR22

BT23

BT22

BM19

BR19

BP19

BT19

BN23

BP23

BP22

BN22

BR27

BT27

BM31

BT30

BT28

BL32

BP28

BR28

BP30

BL30

BP27

BT25

CFG0

CFG0

CFG1

CFG1

CFG2

CFG2

CFG3

CFG3

CFG4

CFG4

CFG5

CFG5

CFG6

CFG6

CFG7

CFG7

CFG8

CFG8 50

CFG9

CFG9

CFG10

CFG10

CFG11

CFG11

CFG12

CFG12

CFG13

CFG13

CFG14

CFG14

CFG15

CFG15

CFG17

CFG17

CFG16

CFG16

CFG19

CFG19

CFG18

1

1

R22

49.9_0402_1%

CFG18

XDP_BPM0_N

XDP_BPM1_N

TP2

TP3

XDP_TDO

XDP_TDI

XDP_TMS

XDP_TCK

XDP_TRST_N

XDP_PREQ_N

XDP_PRDY_N

12

XDP_BPM0_N

XDP_BPM1_N

XDP_BPM2_N

XDP_BPM3_N

CFG_RCOMP

BRD Note:

Placed near CPU within 1.1 inch

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

PROCESSOR CFG STRAPS

CFG0

Stall reset sequence after PCU

PLL lock until de-asserted

CFG0

CFG2

PEG16x Static Lane Reversal Strap

CFG2

CFG4

12

R10 1K_0402_5%@

1:Normal(Default)

0:Stall

12

R12 1K_0402_5%

1:Normal

0:Reversed(Default)

12

R23 1K_0402_5%

*

*

Embedded Display Port Presence Strap

CFG4

1:Disable

0:Enable(Default)

*

?

BN35

BN33

AE29

AA14

BR35

BR31

BH30

BR1

BL34

D1

E1

E3

E2

BT2

J24

H24

N29

R14

A36

A37

H23

J23

F30

E30

B30

C30

G3

J3

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

PROC_TRIGIN

PROC_TRIGOUT

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

SKL_H_BGA_BGA

1

TP_SKL_D1

TP5

1

TP_SKL_E1

TP7

1

TP_SKL_E3

TP9

1

TP_SKL_E2

B B

A A

BRD Note:

Placed within 1.1 inch of CPU pins

+1.0V_VCCST

12

R24 51_0402_5%

12

R25 51_0402_5%@

12

R27 51_0402_5%

12

R29 51_0402_5%@

H_PWRGD

1

R30

C33

@

@

10K_0402_5%

100P_0402_50V8J

2

1 2

5

XDP_TDO

XDP_PREQ_N

XDP_TCK

XDP_TRST_N

CAD Note:

CRB use 30R;DG use 0R

PCH_2_CPU_TRIGGER23

CPU_2_PCH_TRIGGER23

4

R31 33_0402_5%

TP10

1

TP_SKL_BR1

TP11

1

TP_SKL_BT2

TP12

PCH_2_CPU_TRIGGER

12

CPU_2_PCH_TRIGGER_R CFG7

11 OF 14

3

SKYLAKE_HALO

BGA1440

REV = 1

U1K

BM33

RSVD_TP

BL33

RSVD_TP

BJ14

RSVD_TP

BJ13

RSVD_TP

BK28

RSVD

BJ28

RSVD

BJ18

VSS

BJ16

RSVD_TP

BK16

RSVD_TP

BK24

RSVD_TP

BJ24

RSVD_TP

BK21

RSVD

BJ21

RSVD

BT17

RSVD

BR17

RSVD

BK18

VSS

BJ34

RSVD_TP

BJ33

RSVD_TP

G13

RSVD

AJ8

RSVD

BL31

RSVD

B2

NCTF

B38

NCTF

BP1

NCTF

BR2

NCTF

C1

NCTF

C38

?

NCTF

TP_SKL_BM33

TP_SKL_BL33

TP_SKL_BJ14

TP_SKL_BJ13

TP_SKL_BJ16

TP_SKL_BK16

TP_SKL_BK24

TP_SKL_BJ24

TP_SKL_BJ34

TP_SKL_BJ33

1

TP6

1

TP8

1

TP13

1

TP14

1

TP20

1

TP22

1

TP25

1

TP27

1

TP35

1

TP37

PEG TRAINNING

CFG7

2

CFG6

CFG5

PEG CONFIG Straps

CFG[6:5]

1: follow RESET# deassertion

0: Wait for BIOS for training

Title

Title

Title

Size Document Number

Size Document Number

Size

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet of

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

12

R26 1K_0402_5%@

12

R28 1K_0402_5%@

11: x16 (Default))

10: x8, x8

01: Reserved

00: x8,x4,x4

12

R32 1K_0402_5%@

LENOVO.CRDN

LENOVO.CRDN

LENOVO.CRDN

PROCESSOR-CLK/PM/STRAP/TP

PROCESSOR-CLK/PM/STRAP/TP

PROCESSOR-CLK/PM/STRAP/TP

Document Number

Skylake-H

Skylake-H

Skylake-H

1

*

*

Rev

Rev

Rev

V0.3

V0.3

V0.3

69

69

69

9Wednesday, January 27, 2016

9Wednesday, January 27, 2016

9Wednesday, January 27, 2016

of

of

5

4

3

2

1

D D

C C

B B

FOR H4+4e

BJ17

BJ19

BJ20

BK17

BK19

BK20

BL16

BL17

BL18

BL19

BL20

BL21

BM17

BN17

BJ23

BJ26

BJ27

BK23

BK26

BK27

BL23

BL24

BL25

BL26

BL27

BL28

BM24

BL15

BM16

BL22

BM22

BP15

BR15

BT15

BP16

BR16

BT16

BN15

BM15

BP17

BN16

BM14

BL14

BJ35

BJ36

AT13

AW13

AU13

AY13

BT29

BR25

BP25

?

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCCOPC_SENSE

VSSOPC_SENSE

RSVD

RSVD

VCCEOPIO

VCCEOPIO

VCCEOPIO

RSVD

RSVD

RSVD

VCCEOPIO_SENSE

VSSEOPIO_SENSE

RSVD

RSVD

VCC_OPC_1P8

VCC_OPC_1P8

RSVD

RSVD

ZVM#

MSM#

ZVM2#

MSM2#

OPC_RCOMP

OPCE_RCOMP

OPCE_RCOMP2

SKL_H_BGA_BGA

SKYLAKE_HALO

BGA1440

U1J

REV = 1

?

AA13

AA31

AA32

AA33

AA34

AA35

AA36

AA37

AA38

AB29

AB30

AB31

AB32

AB35

AB36

AB37

AB38

AC13

AC14

AC29

AC30

AC31

AC32

AC33

AC34

AC35

AC36

AD13

AD14

AD31

AD32

AD33

AD34

AD35

AD36

AD37

AD38

AE13

AE14

AE30

AE31

AE32

AE35

AE36

AE37

AE38

AF35

AF36

AF37

AF38

K13

K14

L13

N13

N14

N30

N31

N32

N35

N36

N37

N38

P13

SKYLAKE_HALO

BGA1440

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

7 OF 14

SKL_H_BGA_BGA

U1G

VCC_SENSE

VSS_SENSE

REV = 1

V32

VCC

V33

VCC

V34

VCC

V35

VCC

V36

VCC

V37

VCC

V38

VCC

W13

VCC

W14

VCC

W29

VCC

W30

VCC

W31

VCC

W32

VCC

W35

VCC

W36

VCC

W37

VCC

W38

VCC

Y29

VCC

Y30

VCC

Y31

VCC

Y32

VCC

Y33

VCC

Y34

VCC

Y35

VCC

Y36

VCC

L14

VCC

P29

VCC

P30

VCC

P31

VCC

P32

VCC

P33

VCC

P34

VCC

P35

VCC

P36

VCC

R13

VCC

R31

VCC

R32

VCC

R33

VCC

R34

VCC

R35

VCC

R36

VCC

R37

VCC

R38

VCC

T29

VCC

T30

VCC

T31

VCC

T32

VCC

T35

VCC

T36

VCC

T37

VCC

T38

VCC

U29

VCC

U30

VCC

U31

VCC

U32

VCC

U33

VCC

U34

VCC

U35

VCC

U36

VCC

V13

VCC

V14

VCC

V31

VCC

P14

VCC

AG37

AG38

?

CPU_CORE

CPU_VCORE_VCC_SENSE

CPU_VCORE_VSS_SENSE

CPU_VCORE_VCC_SENSE

CPU_VCORE_VSS_SENSE

83

83

CPU_CORE

?10 OF 14

CPU_VCORE_VSS_SENSE

R59

@

49.9_0402_1%

CPU_VCORE_VCC_SENSE

A A

5

4

3

2

1 2

LENOVO.CRDN

LENOVO.CRDN

1

LENOVO.CRDN

79

79

79

of

of

of

Rev

Rev

Rev

V0.3

V0.3

V0.3

9Wednesday, January 27, 2016

9Wednesday, January 27, 2016

9Wednesday, January 27, 2016

Title

Title

Title

PROCESSOR-POWER

PROCESSOR-POWER

PROCESSOR-POWER

Size Document Number

Size Document Number

Size Document Number

C

C

C

Skylake-H

Skylake-H

Skylake-H

Date: Sheet

Date: Sheet

Date: Sheet

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

5

4

3

2

1

+VCCGT

83

83

89

89

?

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

9 OF 14

SKL_H_BGA_BGA

SKYLAKE_HALO

U1I

BGA1440

VCCPLL_OC

VCCPLL_OC

VCCSA_SENSE

VSSSA_SENSE

VCCIO_SENSE

VSSIO_SENSE

REV = 1

R53 0_0603_5%

R54 0_0603_5%

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQC

VCCST

VCCSTG

VCCSTG

VCCPLL

VCCPLL

?

12

12

D D

C C

B B

+VCCSA

+VCCIO

J30

K29

K30

K31

K32

K33

K34

K35

L31

L32

L35

L36

L37

L38

M29

M30

M31

M32

M33

M34

M35

M36

AG12

G15

G17

G19

G21

H15

H16

H17

H19

H20

H21

H26

H27

J15

J16

J17

J19

J20

J21

J26

J27

+1.0V_VCCST_VCCSFR

AA6

AE12

AF5

AF6

AG5

AG9

AJ12

AL11

AP6

AP7

AR12

AR6

AT12

AW6

AY6

J5

J6

K12

K6

L12

L6

R6

T6

W6

Y12

BH13

G11

H30

H29

G30

H28

J28

M38

M37

H14

J14

+1.0V_VCCST

+1.0V_VCCSFR

+1.2V_CPU_VDDQ

PJ15 JUMP_43X118

+VCCVDDQ_CLK

CPU_VCCSA_VCC_SENSE

CPU_VCCSA_VSS_SENSE

CPU_VCCIO_VCC_SENSE

CPU_VCCIO_VSS_SENSE

@

2

+1.0V_VCCST

+1.0V_VCCSTG

+1.0V_VCCSFR

112

+VCCSFR_OC

CPU_VCCSA_VCC_SENSE

CPU_VCCSA_VSS_SENSE

CPU_VCCIO_VCC_SENSE

CPU_VCCIO_VSS_SENSE

+1.2V_VDDQ

AK31

AK32

AK33

AK34

AK35

AK36

AK37

AK38

AL13

AL29

AL30

AL31

AL32

AL35

AL36

AL37

AL38

AM13

AM14

AM29

AM30

AM31

AM32

AM33

AM34

AM35

AM36

AN13

AN14

AN31

AN32

AN33

AN34

AN35

AN36

AN37

AN38

AP13

AP14

AP29

AP30

AP31

AP32

AP35

AP36

AP37

AP38

AR29

AR30

AR31

AR32

AR33

AR34

AR35

AR36

AT14

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AU14

AU29

AU30

AU31

AU32

AU35

AU36

AU37

AU38

AJ29

AJ30

AJ31

AJ32

AJ33

AJ34

AJ35

AJ36

?

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

SKL_H_BGA_BGA

SKYLAKE_HALO

BGA1440

FOR H4+4e

U1N

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGT_SENSE

VSSGT_SENSE

VCCGTX_SENSE

VSSGTX_SENSE

?14 OF 14

REV = 1

AF29

AF30

AF31

AF32

AF33

AF34

AG13

AG14

AG31

AG32

AG33

AG34

AG35

AG36

AH13

AH14

AH29

AH30

AH31

AH32

AJ13

AJ14

AH38

AH37

AH36

AH35

CPU_VCCGT_VCC_SENSE

CPU_VCCGT_VSS_SENSE

CPU_VCCGT_VCC_SENSE

CPU_VCCGT_VSS_SENSE

?

SKYLAKE_HALO

BG34

VCCGT

BG35

VCCGT

BG36

VCCGT

BH33

VCCGT

BH34

VCCGT

BH35

VCCGT

BH36

VCCGT

BH37

VCCGT

BH38

VCCGT

BJ37

VCCGT

BJ38

VCCGT

BL36

VCCGT

BL37

VCCGT

BM36

VCCGT

BM37

VCCGT

BN36

VCCGT

BN37

VCCGT

BN38

VCCGT

BP37

VCCGT

BP38

VCCGT

BR37

VCCGT

BT37

VCCGT

BE38

VCCGT

BF13

VCCGT

BF14

VCCGT

BF29

VCCGT

BF30

VCCGT

BF31

VCCGT

BF32

VCCGT

BF35

VCCGT

BF36

VCCGT

BF37

VCCGT

BF38

VCCGT

BG29

VCCGT

BG30

VCCGT

BG31

VCCGT

BG32

VCCGT

BG33

VCCGT

BC36

VCCGT

BC37

VCCGT

BC38

VCCGT

BD13

VCCGT

BD14

VCCGT

BD29

VCCGT

BD30

VCCGT

BD31

VCCGT

BD32

VCCGT

BD33

VCCGT

BD34

VCCGT

BD35

VCCGT

BD36

VCCGT

BE31

VCCGT

BE32

VCCGT

BE37

VCCGT

86

86

SKL_H_BGA_BGA

BGA1440

U1H

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

REV = 1

+VCCGT+VCCGT

AV29

AV30

AV31

AV32

AV33

AV34

AV35

AV36

AW14

AW31

AW32

AW33

AW34

AW35

AW36

AW37

AW38

AY29

AY30

AY31

AY32

AY35

AY36

AY37

AY38

BA13

BA14

BA29

BA30

BA31

BA32

BA33

BA34

BA35

BA36

BB13

BB14

BB31

BB32

BB33

BB34

BB35

BB36

BB37

BB38

BC29

BC30

BC31

BC32

BC35

BE33

BE34

BE35

BE36

?8 OF 14

+VCCVDDQ_CLK+1.2V_CPU_VDDQ

1 2

R52 0_0402_5%

A A

LENOVO.CRDN

LENOVO.CRDN

1

LENOVO.CRDN

89

89

89

of

of

Rev

Rev

Rev

V0.3

V0.3

V0.3

9Wednesday, January 27, 2016

9Wednesday, January 27, 2016

9Wednesday, January 27, 2016

Title

Title

Title

PROCESSOR-POWER

PROCESSOR-POWER

PROCESSOR-POWER

Size Document Number

Size Document Number

Size Document Number

C

C

C

Skylake-H

Skylake-H

Skylake-H

Date: Sheet

Date: Sheet

Date: Sheet of

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

5

4

3

2

5

4

3

2

1

D D

C C

B B

Y38

Y37

Y14

Y13

Y11

Y10

Y9

Y8

Y7

W34

W33

W12

W5

W4

W3

W2

W1

V30

V29

V12

V6

U38

U37

U6

T34

T33

T14

T13

T12

T11

T10

T9

T8

T7

T5

T4

T3

T2

T1

R30

R29

R12

P38

P37

P12

P6

N34

N33

N12

N11

N10

N9

N8

N7

N6

N5

N4

N3

N2

N1

M14

M13

M12

M6

L34

L33

L30

L29

K38

K11

K10

K9

K8

K7

K5

K4

K3

K2

SKL_H_BGA_BGA

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

?

SKYLAKE_HALO

BGA1440

6 OF 14

U1F

NCTFVSS

REV = 1

K1

VSS

J36

VSS

J33

VSS

J32

VSS

J25

VSS

J22

VSS

J18

VSS

J10

VSS

J7

VSS

J4

VSS

H35

VSS

H32

VSS

H25

VSS

H22

VSS

H18

VSS

H12

VSS

H11

VSS

G28

VSS

G26

VSS

G24

VSS

G23

VSS

G22

VSS

G20

VSS

G18

VSS

G16

VSS

G14

VSS

G12

VSS

G10

VSS

G9

VSS

G8

VSS

G6

VSS

G5

VSS

G4

VSS

F36

VSS

F31

VSS

F29

VSS

F27

VSS

F25

VSS

F23

VSS

F21

VSS

F19

VSS

F17

VSS

F15

VSS

F13

VSS

F11

VSS

F9

VSS

F8

VSS

F5

VSS

F4

VSS

F3

VSS

F2

VSS

E38

VSS

E35

VSS

E34

VSS

E9

VSS

E4

VSS

D33

VSS

D30

VSS

D28

VSS

D26

VSS

D24

VSS

D22

VSS

D20

VSS

D18

VSS

D16

VSS

D14

VSS

D12

VSS

D10

VSS

D9

VSS

D6

VSS

D3

VSS

C37

VSS

C31

VSS

C29

VSS

C27

VSS

D38

?

BT32

BT26

BT24

BT21

BT18

BT14

BT12

BR36

BR34

BR29

BR26

BR24

BR21

BR18

BR14

BR12

BP34

BP33

BP29

BP26

BP24

BP21

BP18

BP14

BP12

BN34

BN31

BN30

BN29

BN24

BN21

BN20

BN19

BN18

BN14

BN12

BM38

BM35

BM28

BM27

BM26

BM23

BM21

BM13

BM12

BL29

BK29

BK15

BK14

BJ32

BJ31

BJ25

BJ22

BH14

BH12

BG38

BG13

BG12

BF33

BF12

BE29

BC34

BC12

BB12

C17

C13

C9

BT9

BT5

BR7

BP7

BN9

BN7

BN4

BN2

BM9

BM6

BM2

BH9

BH8

BH5

BH4

BH1

BE6

BD9

SKYLAKE_HALO

?

BGA1440

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SKL_H_BGA_BGA

U1L

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

REV = 1

?

SKYLAKE_HALO

BGA1440

BB4

VSS

BA38

BA37

BA12

BA11

BA10

AY34

AY33

AY14

AY12

AW30

AW29

AW12

AV38

AV37

AU34

AU33

AU12

AU11

AU10

AT30

AT29

AR38

AR37

AR14

AR13

AP34

AP33

AP12

AP11

AP10

AN30

AN29

AN12

AM38

AM37

AM12

AL34

AL33

AL14

AL12

AL10

BB3

BB2

BB1

BA9

BA8

BA7

BA6

AW5

AW4

AW3

AW2

AW1

AU9

AU8

AU7

AU6

AT6

AR5

AR4

AR3

AR2

AR1

AP9

AP8

AN6

AN5

AM5

AM4

AM3

AM2

AM1

AL9

AL8

AL7

AL4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

13 OF 14

SKL_H_BGA_BGA

C25

VSS

C23

VSS

C21

VSS

C19

VSS

C15

VSS

C11

VSS

C8

VSS

C5

VSS

BM29

VSS

BM25

VSS

BM18

VSS

BM11

VSS

BM8

VSS

BM7

VSS

BM5

VSS

BM3

VSS

BL38

VSS

BL35

VSS

BL13

VSS

BL6

VSS

BK25

VSS

BK22

VSS

BK13

VSS

BK6

VSS

BJ30

VSS

BJ29

VSS

BJ15

VSS

BJ12

VSS

BH11

VSS

BH10

VSS

BH7

VSS

BH6

VSS

BH3

VSS

BH2

VSS

BG37

VSS

BG14

VSS

BG6

VSS

BF34

VSS

BF6

VSS

BE30

VSS

BE5

VSS

BE4

VSS

BE3

VSS

BE2

VSS

BE1

VSS

BD38

VSS

BD37

VSS

BD12

VSS

BD11

VSS

BD10

VSS

BD8

VSS

BD7

VSS

BD6

VSS

BC33

VSS

BC14

VSS

BC13

VSS

BC6

VSS

BB30

VSS

BB29

VSS

BB6

VSS

BB5

VSS

C2

BT36

BT35

BT4

BT3

BR38

U1M

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

REV = 1

AK30

VSS

AK29

VSS

AK4

VSS

AJ38

VSS

AJ37

VSS

AJ6

VSS

AJ5

VSS

AJ4

VSS

AJ3

VSS

AJ2

VSS

AJ1

VSS

AH34

VSS

AH33

VSS

AH12

VSS

AH6

VSS

AG30

VSS

AG29

VSS

AG11

VSS

AG10

VSS

AG8

VSS

AG7

VSS

AG6

VSS

AF14

VSS

AF13

VSS

AF12

VSS

AF4

VSS

AF3

VSS

AF2

VSS

AF1

VSS

AE34

VSS

AE33

VSS

AE6

VSS

AD30

VSS

AD29

VSS

AD12

VSS

AD11

VSS

AD10

VSS

AD9

VSS

AD8

VSS

AD7

VSS

AD6

VSS

AC38

VSS

AC37

VSS

AC12

VSS

AC6

VSS

AC5

VSS

AC4

VSS

AC3

VSS

AC2

VSS

AC1

VSS

AB34

VSS

AB33

VSS

AB6

VSS

AA30

VSS

AA29

VSS

AA12

VSS

A30

VSS

A28

VSS

A26

VSS

A24

VSS

A22

VSS

A20

VSS

A18

VSS

A16

VSS

A14

VSS

A12

VSS

A10

VSS

A9

VSS

A6

VSS

B37

B3

A34

A4

A3

?

?12 OF 14

A A

LENOVO.CRDN

LENOVO.CRDN

1

LENOVO.CRDN

99

99

99

of

of

Rev

Rev

Rev

V0.3

V0.3

V0.3

9Wednesday, January 27, 2016

9Wednesday, January 27, 2016

9Wednesday, January 27, 2016

Title

Title

Title

PROCESSOR-VSS

PROCESSOR-VSS

PROCESSOR-VSS

Size Document Number

Size Document Number

Size

Document Number

C

C

C

Skylake-H

Skylake-H

Skylake-H

Date: Sheet

Date: Sheet

Date: Sheet of

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

5

4

3

2

5

D D

C C

+1.2V_CPU_VDDQ 4X0603(22UF) 10X0402(10UF)

BRD Note:

Placed backside

+1.2V_CPU_VDDQ +1.2V_CPU_VDDQ

1

1

1

1

C916

22U

_0603_6.3V6M

C917

22U

2

_0603_6.3V6M

1

C918

22U

2

_0603_6.3V6M

C915

22U

2

2

B B

_0603_6.3V6M

1

C919

10U

2

_0402_6.3V6M

C920

10U

2

_0402_6.3V6M

1

C921

10U

2

_0402_6.3V6M

1

C922

10U

2

_0402_6.3V6M

4

1

C923

10U_0402_6.3V6M

2

1

C924

10U

2

_0402_6.3V6M

1

C925

10U

2

_0402_6.3V6M

1

C926

10U

2

_0402_6.3V6M

1

C927

10U

2

_0402_6.3V6M

1

C928

10U

2

_0402_6.3V6M

3

+VCCSA

BOTTOM:1X0805(47UF), 8X0402(10UF), 3X0201(1UF);

TOP:2XBULK(220UF),1X0805(22UF)

BRD Note:

Placed backside

+VCCSA +VCCSA +VCCSA +VCCSA

1

C931

10U

2

_0402_6.3V6M

1

C932

10U

2

_0402_6.3V6M

C933

10U

_0402_6.3V6M

1

1

C929

47U

1 2

_0805_6.3V6-M

C930

10U

2

_0402_6.3V6M

2

1

C934

10U

2

_0402_6.3V6M

2

1

C935

10U

2

_0402_6.3V6M

1

C936

10U

2

_0402_6.3V6M

1

C937

10U

2

_0402_6.3V6M

2

C938

1u_0201_10V6M

1

2

C939

1u_0201_10V6M

1

2

C940

1u_0201_10V6M

1

1

BRD Note:

Placed TOP BGA EDGE

1

1

C942

C941

+

+

@

330U_B2_2.5VM_R9M

330U

_B2_2.5VM_R9M

2

C312

47U