Lenovo S530-13 Schematic

A

1 1

B

C

D

E

Compal Confidential

2 2

S530 (ELZ02)

DIS M/B Schematics Document

Intel Whiskey Lake U Processor with LPDDR3

N17S-LG (Geforce MX150) (23x23mm)

3 3

2018-5-21

LA-G651P

R E V

:

:

::

0 . 2

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Compal For Lenovo

A

B

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2018/2/5 2019/2/5

2018/2/5 2019/2/5

2018/2/5 2019/2/5

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet

Date : Sheet of

D

Date : Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

LA-G651P

LA-G651P

LA-G651P

0.2

0.2

0.2

o f

1 52Friday, May 18, 2018

1 52Friday, May 18, 2018

1 52Friday, May 18, 2018

E

5

4

3

2

1

D D

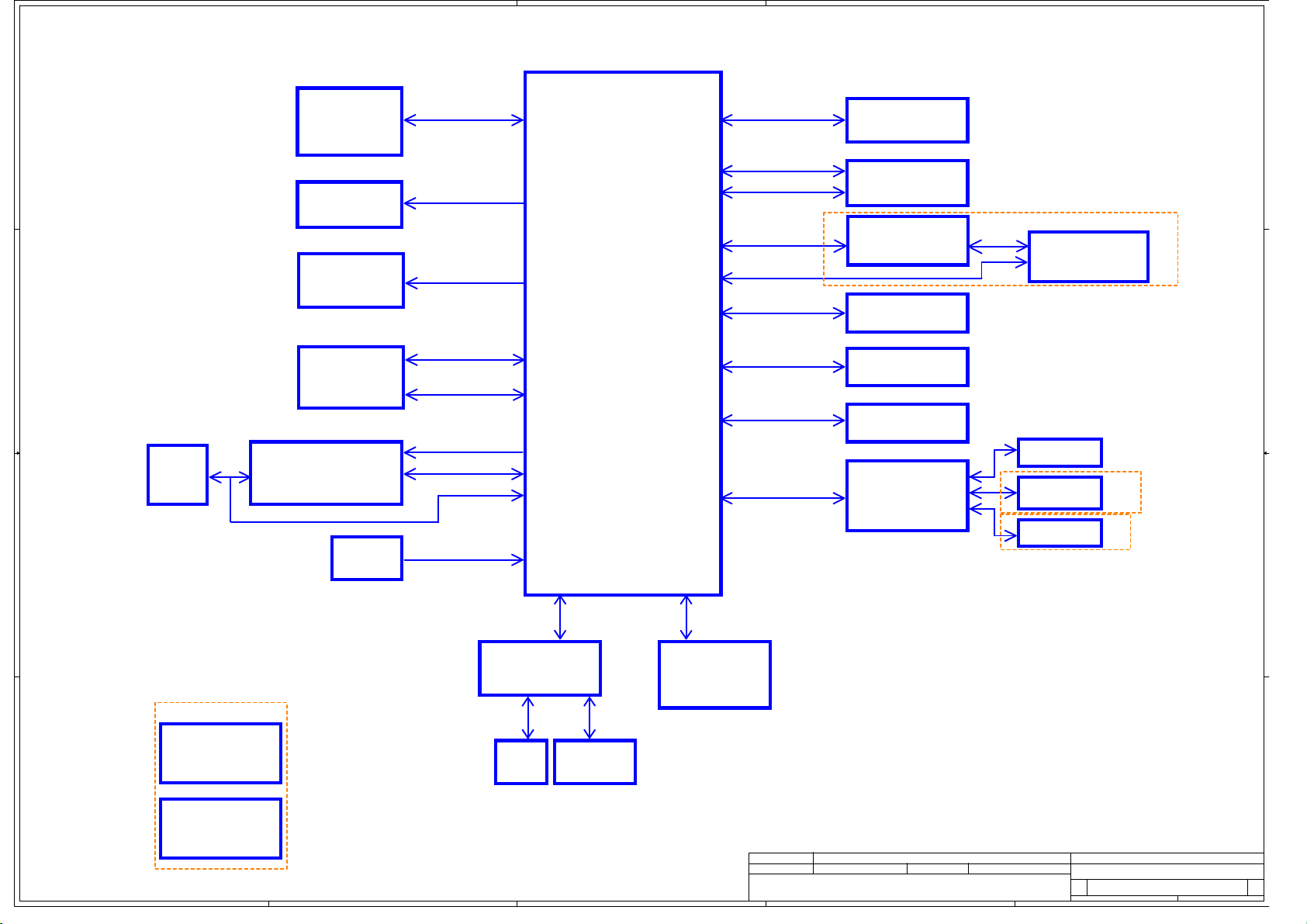

N17S-LG (MX150)

VRAM(GDDR5)*2

PCIe x4

2 Lanes

2GB

eDP Panel

FHD LCD

HDMI CONN

eDP x1

2 Lanes

DDI x1

Channel A/B

(1866 MT/s)

USB3.0

USB2.0

USB3.0

USB2.0

USB2.0

On board X 4

LPDDR3

USB3.0 Connector

(USB charger port)

USB3.0 redriver

TI

SN65 LVPE50 2A

Camera

USB3.0 Connector

IO/B

Intel WHL-U_15W

C C

Wireless LAN

WIFI /BT combo

NGFF

Type-C DP/USB3 Switch

Type-C

Conn

B B

Realtek RTS5455

Touch Pad

PCIE x1

GEN1 : 2.5G

USB2.0 x1

DDI x1

USB 3.0

USB 2.0

I2C

4+2

1528 pin BGA

USB2.0

PCIE x4

HDA

Finger print

SSD CONN

NGFF

Audio Codec

Realtek ALC3240

Int. Speaker

Int. Array Mic x2

MIC B

Combo Jack

IO/B

EC

ENE

KB9022

LPC

SPI

SPI ROM

16 MB

Sub-Board

IO/B

USB3.0 *1

Combo Jack *1

A A

Int. KBD

Hall Sensor x1

MIC B

Int. Array Mic x2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Compal For Lenovo

5

4

3

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

2018/2/5 2019/2/5

2018/2/5 2019/2/5

2018/2/5 2019/2/5

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

Custom

Custom

Custom

Date : Sheet

Date : Sheet of

Date : Sheet of

LA-G651P

LA-G651P

LA-G651P

1

2 52Friday, May 18, 2018

2 52Friday, May 18, 2018

2 52Friday, May 18, 2018

0.2

0.2

0.2

of

1

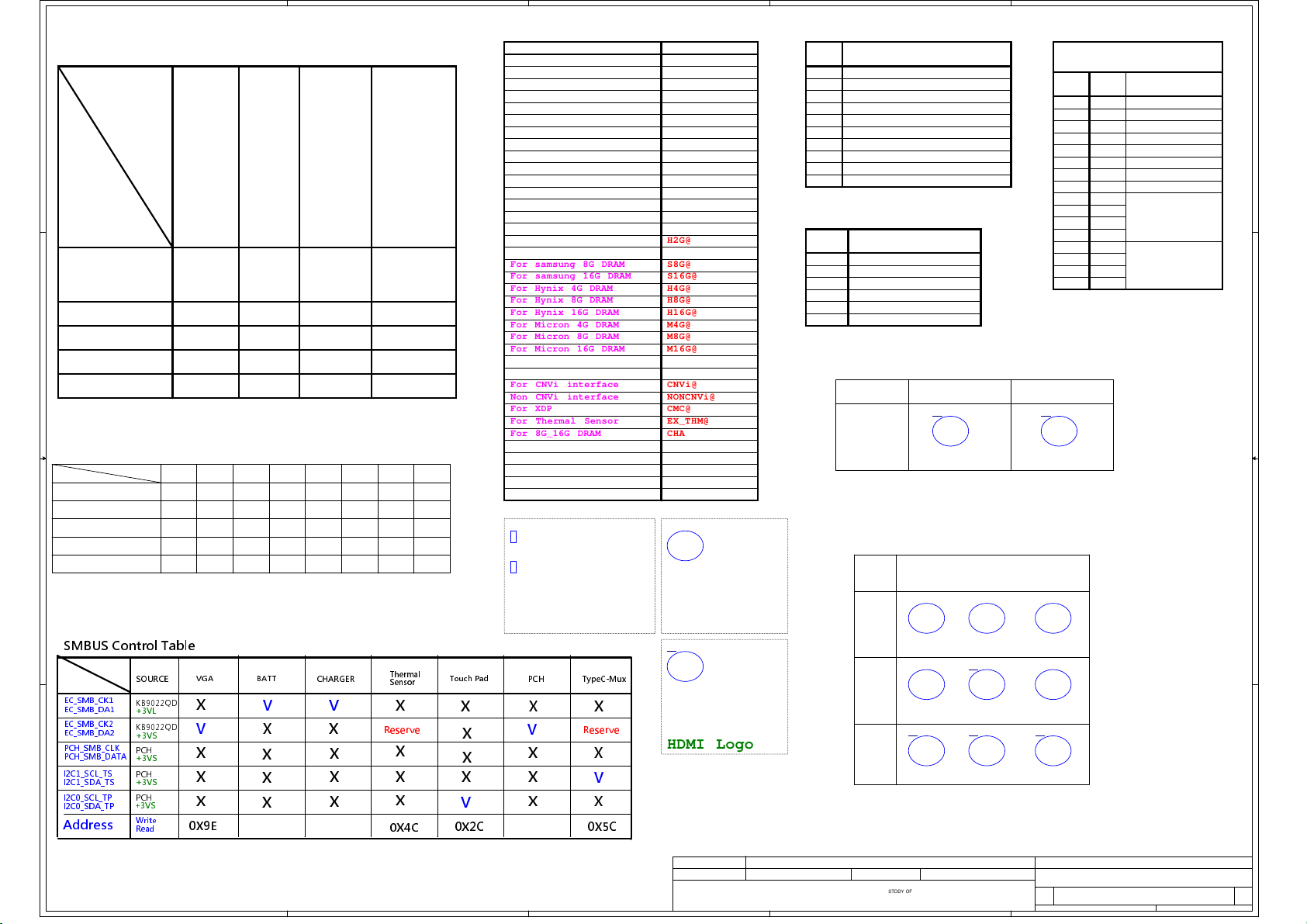

Voltage Rails

State

S0

S3

S5 S4/AC

power

plane

SIGNAL

B+

O

O

O

O

X

SLP_S1#

LOW

HIGH HIGH HIGH

LOW

LOW

LOW LOW LOW

LOWLOW

+5VALW

+3VALW

+1.8VALW

+1.05VAL W

O

O

+1.2V

+2.5V

O O

O

O

X

SLP_S4#SLP_S3# +V+VALWSLP_S5# Clock+VS

HIGHHIGHHIGH

HIGH

HIGH

HIGH

HIGH

LOWLOW

X

ONONON

ON

ON

ON

ON

ON

OFF

OFF

A A

B B

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

C C

SMBUS Control Table

SOURCE

EC_SMB_CK1

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

PCH_SMB_CLK

PCH_SMB_DATA

I2C1_SCL_TS

I2C1_SDA_TS

I2C0_SCL_TP

D D

I2C0_SDA_TP

Address

KB9022QD

+3VL

KB9022QD

+3VS

PCH

+3VS

PCH

+3VS

PCH

+3VS

Write

Read

VGA

X

V

X

X

X

0X9E

BATT

V X

X

X

X

X

CHARGER

V

X

X

X

X

2

+5VS

+3VS

+VCCPLL_ OC

+VCCCORE

+VCCGT

+1.05V_V CCST

+1.05VS_V CCIO

+1.8VS

+1.8V_ME M

X

XX

X

XXX

ONON

ON

LOW

OFF

OFF

OFF

OFF

OFF

OFF

Thermal

Sensor

Reserve

X

X

X

0X4C

Touch Pad

X

X

X

X

V

0X2C

3

BOM Structure Table

Ite m

For DIS DIS@

For UMA UMA@

For GPU GC6

No GPU GC6

For Ke yboard backlight KBL @

No Keyboa rd backlight NOKB L@

For RF RF@

No RF @RF @

For EMI

For ESD

No ESD

For Samsung VRAM

For Micron VRAM

For Hynix VRAM

For samsung 4G DRAM S4G @

For samsung 8G DRAM S8G @

For samsu ng 16G DRAM S16 G@

For Hynix 4G DRAM H4G @

For Hynix 8G DRAM

For Micron 4G DRAM

For Micron 8G DRAM

X4E for UMA X4E_ UMA

X4E for DIS X4E_ DIS

For CNVi interface CNV i@

Non CNVi interface NONC NVi @

For XDP CMC@

For Thermal Sensor EX_T HM@

For 8G_16G DRAM CHA @

UC1

SA0000C1510

S IC FJ8068403999819 QQAT W0 1.8G C38

I7@

UC1

SA0000C1610

S IC FJ8068404000016 QQAU W0 1.6G C38

I5@

BOM Structure

GC6 @

NOGC 6@

EMI @

@EM I@No EMI

ESD @

@ES D@

ME@Conne ct or

S2G @

M2G @

H2G @

H8G @

H16 G@For Hynix 16G DRAM

M4G @

M8G @

M16 G@For Micron 16G DRAM

ZZZ

DA8001FP000

PCB 2D5 LA-G651P REV0 M/B 2

CPU MB

ZZZ

PCH

X

V

X

X

X

TypeC-Mux

X

Reserve

X

V

X

0X5C

HDMI Logo

RO0000003HM

HDMI Logo

4

5

USB 2.0 Port Table

Por t

1

USB2/3 (re-driver) ( I/O BD)

2

USB2/3 (Charger)

3

Type-C

4

5

Camera

6

FP

7

8

9

10

NGFF WLAN+BT(CNVi)

USB 3.0 Port Table

Por t

1

USB2/3 (re-driver) (I/O SB)

2

USB2/3 (for charger)

3

Type-C

4

5

6

PCIE Port Table

Por t

Lan e

1

2

3

4

5

6

7

8

0

9

3

10

2

11

1

12

0

13

0

14

1

15

2

16

3

NGFF WLAN+BT

SSD

GPU

UMA DiscreteEMC/ESD

ZZZ

X4E_UMA@

X4E_UMA

X4EADO38L02

ZZZ

X4E_DIS@

X4E_DIS

X4EADO38L01

LPDDR3 Onboard RAM

ZZZ

ZZZ

X76@ ZZZ

4G

LPDDR3_S4G

8G

X7679138L01

ZZZ

X76@

LPDDR3_S8G

X7679138L04

ZZZ

X76@

LPDDR3_S16G

X7679138L07

45@

16G

X76@

LPDDR3_H4G

X7679138L02

X76@

LPDDR3_H8G

X7679138L05

ZZZ

X76@

LPDDR3_H16G

X7679138L08

X76@

LPDDR3_M4G

X7679138L03

ZZZ

X76@ZZZ

LPDDR3_M8G

X7679138L06

ZZZ

X76@

LPDDR3_M16G

X7679138L09

Security Classification

Security Classification

Compal For Lenovo

1

2

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2018/2/5 2019/2/5

2018/2/5 2019/2/5

2018/2/5 2019/2/5

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

4

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Notes List

Notes List

Notes List

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

LA-G651P

LA-G651P

LA-G651P

5

3 52Friday, May 18, 2018

3 52Friday, May 18, 2018

3 52Friday, May 18, 2018

0.2

0.2

0.2

of

of

of

5

D D

C C

4

3

2

1

B B

A A

Security Classification

Security Classification

Compal For Lenovo

5

4

3

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Compal Secret Data

Compal Secret Data

Compal Secret Data

2018/2/5 2019/2/5

2018/2/5 2019/2/5

2018/2/5 2019/2/5

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Elect ronics, Inc.

Compal Elect ronics, Inc.

Compal Elect ronics, Inc.

Title

Title

Title

Power MAP

Power MAP

Power MAP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date : Sheet o f

Date : Sheet o f

Date : Sheet o f

1

4 52Friday, May 18, 201 8

4 52Friday, May 18, 201 8

4 52Friday, May 18, 201 8

0.2

0.2

0.2

5

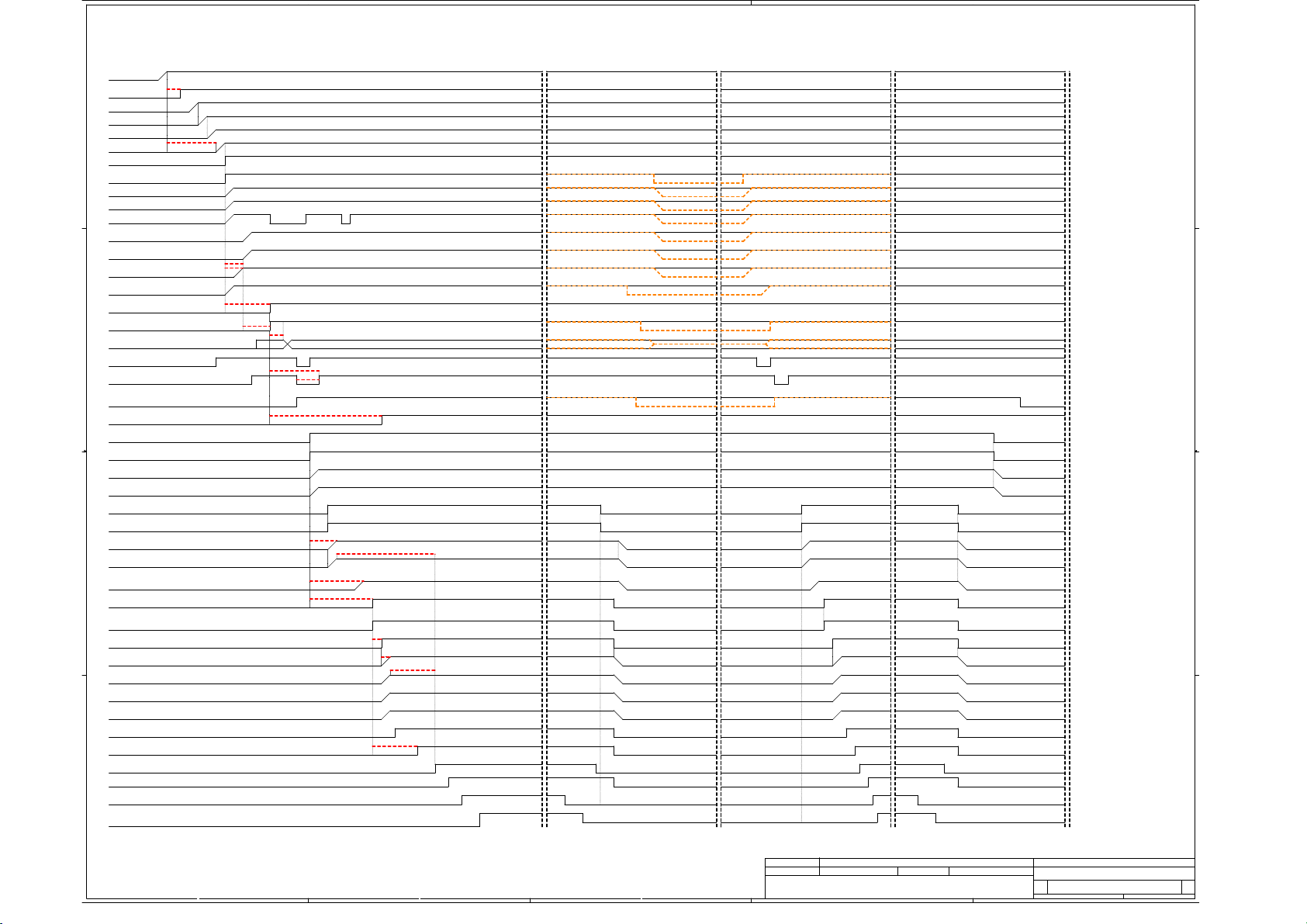

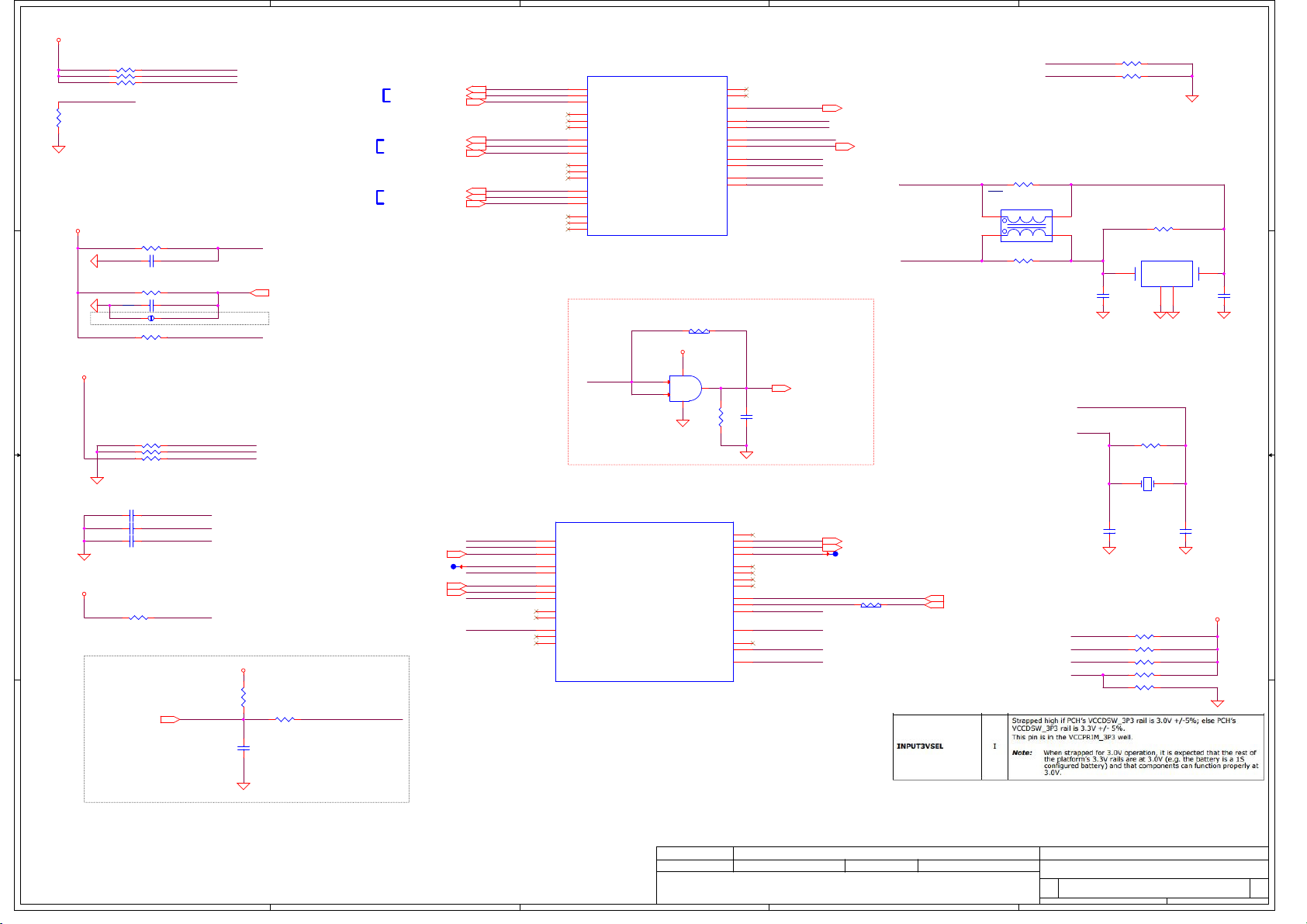

[ELZ02-PWR Sequence]

4

3

2

1

G3->S0 S0->S3 ->S0

+3VL_RTC

SOC_RTCRST#

B+

D D

+3VLP/+5V LP

EC_ON

+5VALW/+3VALW/+3VALW _DSW

PM_BATLOW#

PCH_PWR_EN (SLP_SUS#)

+3V_PRIM

+1.8V_PRIM

EXT_PWR_GATE#

+1.05V_MPHYPLL

+1.05V_PRIM_CORE

+1.05V_PRIM

SUSACK#

PCH_DPWROK

EC_RSMRST#

C C

AC_PRESENT

ON/OFF

PBTN_OUT#

PM_SLP_S5#

ESPI_RST#

PM_SLP_S4#

SYSON

VCCST

+1.2V_VDDQ/+1.2V_VCCSFR_OC

PM_SLP_S3#

SUSP#

VCCSTG

VCCIO

B B

+5VS/+3VS/+1.5VS /+1.05VS

EC_VCCST_PG

VR_ON

DDR_VTT_PG_CT RL

+0.6VS

+VCC_SA

+VCC_CORE

+VCC_GT

VR_PWRGD

PCH_PWROK

H_CPUPWRGD

SYS_PWROK

A A

SUS_STAT#

SOC_PLTRST#

tPCH01_Min : 9 ms

tPCH06_Min : 200 us

tPCH04_Min : 9 ms

Pull-up to DSW well if not implemented.

If EXT_PWR_GATE# Toffmin is too small, Pwr

gate may choose to completely ignore it

tPCH34_Max : 20 ms

tPCH02_Min : 10 ms

tPCH03_Min : 10 ms

tPLT02_Min : 0 ms Max : 90 ms

tPCH43_Min : 95 ms

Minimum duration of PWRBTN# assertion = 16mS. PWRBTN# can assert before or after RSMRST#

tPCH18_Min : 90 us

tCPU04 Min : 100 ns

tCPU10 Min : 1 ms

T <=10msec

T = 10msec

tCPU19 Max : 100 ns

tCPU18 Max : 35 us

tCPU09 Min : 1 ms

tCPU16 Min : 0 ns

/DS3 DS3S0/

S0->S5

+3VL_RTC

SOC_RTCRST#

B+

+3VLP/+5V LP

EC_ON

+5VALW/+3VALW/+3VALW _DSW

PM_BATLOW#

PCH_PWR_EN (SLP_SUS#)

+3V_PRIM

+1.8V_PRIM

EXT_PWR_GATE#

+1.05V_MPHYPLL

+1.05V_PRIM_CORE

+1.05V_PRIM

SUSACK#

PCH_DPWROK

EC_RSMRST#

AC_PRESENT

ON/OFF

PBTN_OUT#

PM_SLP_S5#

ESPI_RST#

PM_SLP_S4#

SYSON

VCCST

+1.2V_VDDQ/+1.2V_VCCSFR_OC

PM_SLP_S3#

SUSP#

VCCSTG

VCCIO

+5VS/+3VS/+1.5VS /+1.05VS

EC_VCCST_PG

VR_ON

DDR_VTT_PG_CT RL

+0.6VS

+VCC_SA

+VCC_CORE

+VCC_GT

VR_PWRGD

PCH_PWROK

H_CPUPWRGD

SYS_PWROK

SUS_STAT#

SOC_PLTRST#

Security Classification Compal Secret Data

Security Classification Compal Secret Data

Security Classification Compal Secret Data

Issued Date

Issued Date

Compal For Lenovo

5

4

3

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED T O ANY T HIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED T O ANY T HIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED T O ANY T HIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2018/2/5 2019/2/5

2018/2/5 2019/2/5

2018/2/5 2019/2/5

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Power Sequence

Power Sequence

Power Sequence

1

5 52Friday, May 1 8, 2018

5 52Friday, May 1 8, 2018

5 52Friday, May 1 8, 2018

0.2

0.2

0.2

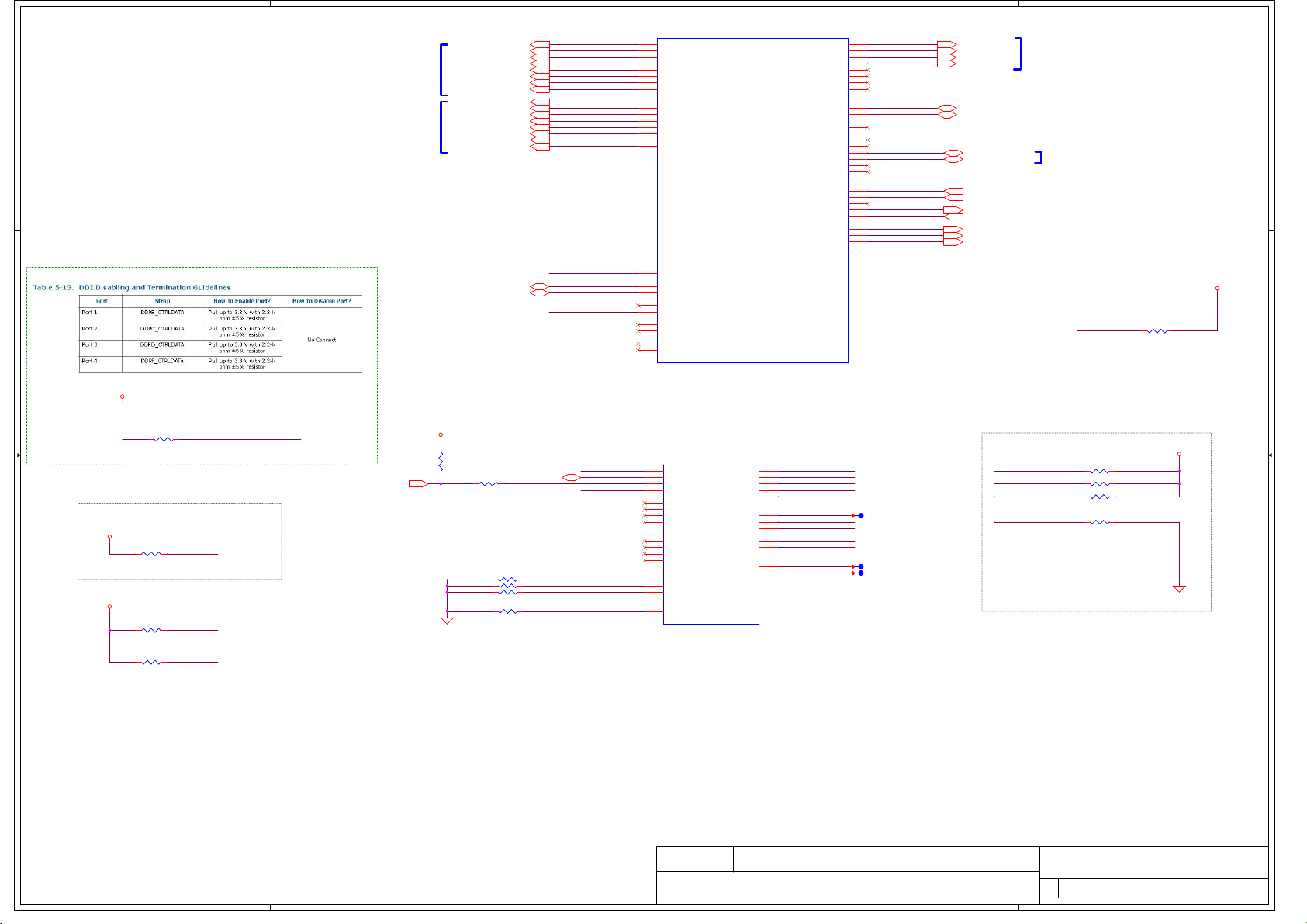

A

1 1

2 2

+3VS

B

HDMI

MUX

For HDMI 1.4

C

UC1A

CPU_DP1_N 0<29>

CPU_DP1_P0<29>

CPU_DP1_N 1<29>

CPU_DP1_P1<29>

CPU_DP1_N 2<29>

CPU_DP1_P2<29>

CPU_DP1_N 3<29>

CPU_DP1_P3<29>

CPU_DP2_N 0<30>

CPU_DP2_P0<30>

CPU_DP2_N 1<30>

CPU_DP2_P1<30>

CPU_DP2_N 2<30>

CPU_DP2_P2<30>

CPU_DP2_N 3<30>

CPU_DP2_P3<30>

EDP_COMP

CPU_DP1_C TRL_CLK<29>

CPU_DP1_C TRL_DATA<29>

CPU_DDPC_ CTRL_DATA

AL5

DDI1_TXN_0

AL6

DDI1_TXP_0

AJ5

DDI1_TXN_1

AJ6

DDI1_TXP_1

AF6

DDI1_TXN_2

AF5

DDI1_TXP_2

AE5

DDI1_TXN_3

AE6

DDI1_TXP_3

AC4

DDI2_TXN_0

AC3

DDI2_TXP_0

AC1

DDI2_TXN_1

AC2

DDI2_TXP_1

AE4

DDI2_TXN_2

AE3

DDI2_TXP_2

AE1

DDI2_TXN_3

AE2

DDI2_TXP_3

AM6

DISP_RCOMP

CC8

GPP_E18/DPPB_CTRLCLK/CNV_BT_HOST_WAKE#

CC9

GPP_E19/DPPB_CTRLDATA

CH4

GPP_E20/DPPC_CTRLCLK

CH3

GPP_E21/DPPC_CTRLDATA

CP4

GPP_E22/DPPD_CTRLCLK

CN4

GPP_E23/DPPD_CTRLDATA

CR26

GPP_H16/DDPF_CTRLCLK

CP26

GPP_H17/DDPF_CTRLDATA

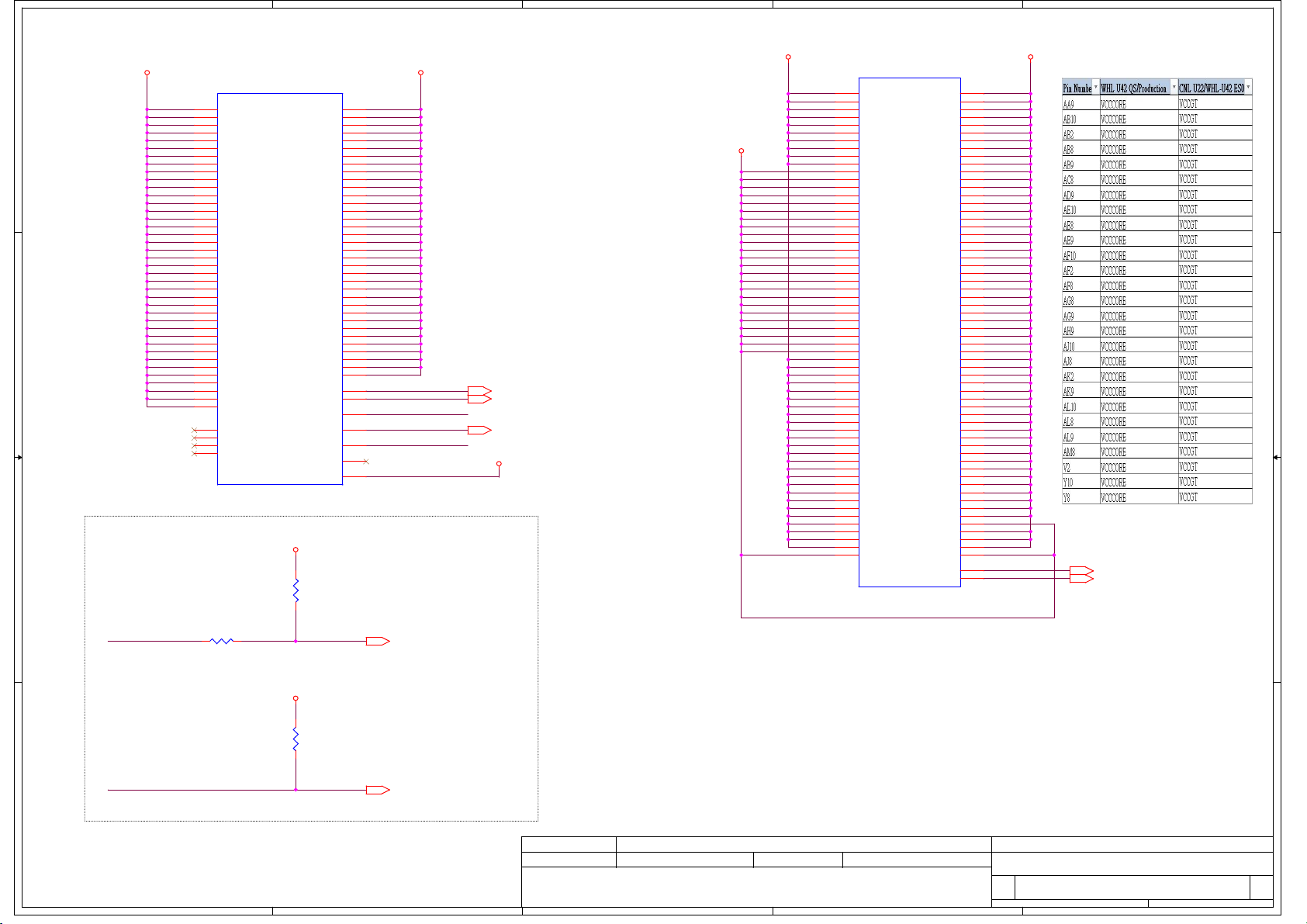

WHL-U42 _BGA1528

1 of 20

EDP_TXN_0

EDP_TXP_0

EDP_TXN_1

EDP_TXP_1

EDP_TXN_2

EDP_TXP_2

EDP_TXN_3

EDP_TXP_3

EDP_AUX_N

EDP_AUX_P

DISP_UTILS

DDI1_AUX_N

DDI1_AUX_P

DDI2_AUX_N

DDI2_AUX_P

DDI3_AUX_N

DDI3_AUX_P

GPP_E13/DDPB_HPD0/DISP_MISC0

GPP_E14/DDPC_HPD1/DISP_MISC1

GPP_E15/DPPD_HPD2/DISP_MISC2

GPP_E16/DPPE_HPD3/DISP_MISC3

GPP_E17/EDP_HPD/DISP_MISC4

EDP_BKLTEN

EDP_VDDEN

EDP_BKLTCTL

AG4

AG3

AG2

AG1

AJ4

AJ3

AJ2

AJ1

AH4

AH3

AM7

AC7

AC6

AD4

AD3

AG7

AG6

CN6

CM6

CP7

CP6

CM7

CK11

CG11

CH11

D

EDP_TXN0 <28>

EDP_TXP0 <28>

EC_SCI#

EDP_TXN1 <28>

EDP_TXP1 <28>

EDP_AUXN <28>

EDP_AUXP <2 8>

CPU_DP2_AUXN <30>

CPU_DP2_AUXP <30>

CPU_DP1_H PD <29>

CPU_DP2_H PD <30>

EC_SCI# <34>

EDP_HPD <28>

ENBKL <28,34>

PCH_ENVDD <28>

INVPWM <28>

eDP

From eDP

MUX

From HDMI

From MUX

EC_SCI#

E

1 2

RC480 10K_04 02_5%

+3VS

B

+1.05VS_VCCSTG

12

RC4

1K_0402_5%

RC6 499_0402_ 1%

If routed MS, PECI requires 18 mils spacing to other signals

CATERR#

H_PECI

H_PECI<34>

1 2

RC7 49.9_0402 _1%

RC8 49.9_0402 _1%

RC9 49.9_0402_1%@

RC10 49.9_0402_ 1%@

12

12

12

12

H_PROCHOT# _R

H_THERMT RIP#

CPU_POPIRCOMP

PCH_OPIRCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

UC1D

AA4

CATERR#

AR1

PECI

Y4

PROCHOT#

BJ1

THRMTRIP#

U1

BPM#_0

U2

BPM#_1

U3

BPM#_2

U4

BPM#_3

CE9

GPP_E3/CPU_GP0

CN3

GPP_E7/CPU_GP1

CB34

GPP_B3/CPU_GP2

CC35

GPP_B4/CPU_GP3

BP27

PROC_POPIRCOMP

BW25

PCH_OPIRCOMP

L5

OPCE_RCOMP

N5

OPC_RCOMP

WHL-U42 _BGA1528

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

4 of 20

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

PCH_TRST#

PCH_JTAGX

PROC_PREQ#

PROC_PRDY#

CPU_XDP_TCK 0

T6

SOC_XDP_TDI

U6

SOC_XDP_TDO

Y5

SOC_XDP_TMS

T5

SOC_XDP_TRST #

AB6

W6

SOC_XDP_TDI

U5

SOC_XDP_TDO

W5

SOC_XDP_TMS

P5

SOC_XDP_TRST #

Y6

CPU_XDP_TCK 0

P6

W2

W1

2017/5/3 2017/6/2

2017/5/3 2017/6/2

2017/5/3 2017/6/2

DCI

T2402TP@

DCI

T2403TP@

T2404TP@

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

< PU/PD for CMC Debug >

SOC_XDP_TMS

SOC_XDP_TDI

SOC_XDP_TDO

CPU_XDP_TCK 0

1 2

RC11 51_0402_5 %CMC@

1 2

RC12 51_0402_5 %CMC@

1 2

RC13 51_0402_5 %

1 2

RC14 51_0402_5 %

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size D ocument Number R ev

Size D ocument Number R ev

Size D ocument Number R ev

Date : Sheet of

Date : Sheet of

Date : Sheet of

Compal Electronics, Inc.

WHL-U(1/12)DDI,EDP,MISC,CMC

WHL-U(1/12)DDI,EDP,MISC,CMC

WHL-U(1/12)DDI,EDP,MISC,CMC

Custom

Custom

Custom

+1.05VS_VCCSTG

LA-G651P

LA-G651P

LA-G651P

E

0.2

0.2

6 52Friday, May 18, 2018

6 52Friday, May 18, 2018

6 52Friday, May 18, 2018

0.2

RC436 2.2K_02 01_5%

12

CPU_DDPC_ CTRL_DATA

H_PROCHOT#<34>

< Compensation PU For eDP >

+1.05VS_VCCIO

EDP_COMP

1 2

RC3

3 3

4 4

Trace width=20 mils, Spacing=25mil, Max length=600mils

+1.05V_VCCST

RC5 1K_0402_5%

RC19 4 9.9_0402_1%

1 2

@

24.9_0201_1 %

H_THERMT RIP#

12

CATERR#

Compal For Lenovo

A

5

4

3

2

1

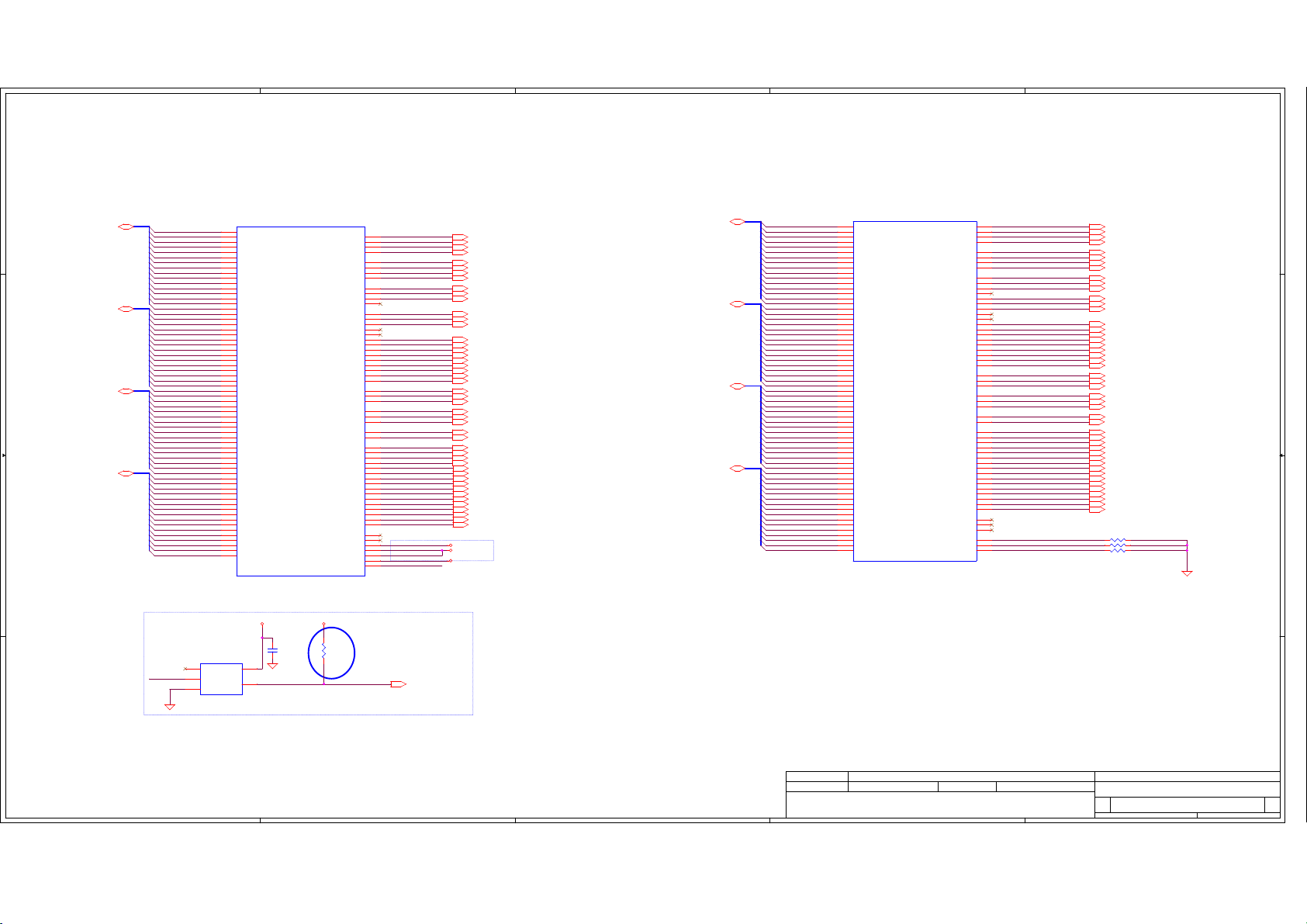

Non- Interleaved Memory

D D

DDR_A_D[16..31]<19>

DDR_A_D[48..63]<19>

DDR_B_D[16..31]<20>

DDR_B_D[48..63]<20>

AN35

AN34

AR35

AR34

AN37

AN36

AR36

AR37

AU35

AU34

AW35

AW34

AU37

AU36

AW36

AW37

BA35

BA34

BC35

BC34

BA37

BA36

BC36

BC37

BE35

BE34

BG35

BG34

BE37

BE36

BG36

BG37

NC1VCC

A

GND

SA00005U600

UC1B

A26

DDR0_DQ_0/DDR0_DQ_0

D26

DDR0_DQ_1/DDR0_DQ_1

D28

DDR0_DQ_2/DDR0_DQ_2

C28

DDR0_DQ_3/DDR0_DQ_3

B26

DDR0_DQ_4/DDR0_DQ_4

C26

DDR0_DQ_5/DDR0_DQ_5

B28

DDR0_DQ_6/DDR0_DQ_6

A28

DDR0_DQ_7/DDR0_DQ_7

B30

DDR0_DQ_8/DDR0_DQ_8

D30

DDR0_DQ_9/DDR0_DQ_9

B33

DDR0_DQ_10/DDR0_DQ_10

D32

DDR0_DQ_11/DDR0_DQ_11

A30

DDR0_DQ_12/DDR0_DQ_12

C30

DDR0_DQ_13/DDR0_DQ_13

B32

DDR0_DQ_14/DDR0_DQ_14

C32

DDR0_DQ_15/DDR0_DQ_15

H37

DDR0_DQ_16/DDR0_DQ_32

H34

DDR0_DQ_17/DDR0_DQ_33

K34

DDR0_DQ_18/DDR0_DQ_34

K35

DDR0_DQ_19/DDR0_DQ_35

H36

DDR0_DQ_20/DDR0_DQ_36

H35

DDR0_DQ_21/DDR0_DQ_37

K36

DDR0_DQ_22/DDR0_DQ_38

K37

DDR0_DQ_23/DDR0_DQ_39

N36

DDR0_DQ_24/DDR0_DQ_40

N34

DDR0_DQ_25/DDR0_DQ_41

R37

DDR0_DQ_26/DDR0_DQ_42

R34

DDR0_DQ_27/DDR0_DQ_43

N37

DDR0_DQ_28/DDR0_DQ_44

N35

DDR0_DQ_29/DDR0_DQ_45

R36

DDR0_DQ_30/DDR0_DQ_46

R35

DDR0_DQ_31/DDR0_DQ_47

DDR0_DQ_32/DDR1_DQ_0

DDR0_DQ_33/DDR1_DQ_1

DDR0_DQ_34/DDR1_DQ_2

DDR0_DQ_35/DDR1_DQ_3

DDR0_DQ_36/DDR1_DQ_4

DDR0_DQ_37/DDR1_DQ_5

DDR0_DQ_38/DDR1_DQ_6

DDR0_DQ_39/DDR1_DQ_7

DDR0_DQ_40/DDR1_DQ_8

DDR0_DQ_41/DDR1_DQ_9

DDR0_DQ_42/DDR1_DQ_10

DDR0_DQ_43/DDR1_DQ_11

DDR0_DQ_44/DDR1_DQ_12

DDR0_DQ_45/DDR1_DQ_13

DDR0_DQ_46/DDR1_DQ_14

DDR0_DQ_47/DDR1_DQ_15

DDR0_DQ_48/DDR1_DQ_32

DDR0_DQ_49/DDR1_DQ_33

DDR0_DQ_50/DDR1_DQ_34

DDR0_DQ_51/DDR1_DQ_35

DDR0_DQ_52/DDR1_DQ_36

DDR0_DQ_53/DDR1_DQ_37

DDR0_DQ_54/DDR1_DQ_38

DDR0_DQ_55/DDR1_DQ_39

DDR0_DQ_56/DDR1_DQ_40

DDR0_DQ_57/DDR1_DQ_41

DDR0_DQ_58/DDR1_DQ_42

DDR0_DQ_59/DDR1_DQ_43

DDR0_DQ_60/DDR1_DQ_44

DDR0_DQ_61/DDR1_DQ_45

DDR0_DQ_62/DDR1_DQ_46

DDR0_DQ_63/DDR1_DQ_47

WHL-U42_BGA1528

UC2

5

4

Y

DDR0_CKN_0/DDR0_CKN_0

DDR0_CKP_0/DDR0_CKP_0

DDR0_CKN_1/DDR0_CKN_1

DDR0_CKP_1/DDR0_CKP_1

DDR0_CKE_0/DDR0_CKE_0

DDR0_CKE_1/DDR0_CKE_1

DDR0_CS#_0/DDR0_CS#_0

DDR0_CS#_1/DDR0_CS#_1

DDR0_ODT_0/DDR0_ODT_0

DDR0_CAB_9/DDR0_MA_0

DDR0_CAB_8/DDR0_MA_1

DDR0_CAB_5/DDR0_MA_2

DDR0_CAA_0/DDR0_MA_5

DDR0_CAA_2/DDR0_MA_6

DDR0_CAA_4/DDR0_MA_7

DDR0_CAA_3/DDR0_MA_8

DDR0_CAA_1/DDR0_MA_9

DDR0_CAB_7/DDR0_MA_10

DDR0_CAA_7/DDR0_MA_11

DDR0_CAA_6/DDR0_MA_12

DDR0_CAB_0/DDR0_MA_13

DDR0_CAB_2/DDR0_MA_14

DDR0_CAB_1/DDR0_MA_15

DDR0_CAB_3/DDR0_MA_16

DDR0_CAB_4/DDR0_BA_0

DDR0_CAB_6/DDR0_BA_1

DDR0_CAA_5/DDR0_BG_0

DDR0_CAA_8/DDR0_ACT#

DDR0_CAA_9/DDR0_BG_1

DDR0_DQSN_0/DDR0_DQSN_0

DDR0_DQSP_0/DDR0_DQSP_0

DDR0_DQSN_1/DDR0_DQSN_1

DDR0_DQSP_1/DDR0_DQSP_1

DDR0_DQSN_2/DDR0_DQSN_4

DDR0_DQSP_2/DDR0_DQSP_4

DDR0_DQSN_3/DDR0_DQSN_5

DDR0_DQSP_3/DDR0_DQSP_5

DDR0_DQSN_4/DDR1_DQSN_0

DDR0_DQSP_4/DDR1_DQSP_0

DDR0_DQSN_5/DDR1_DQSN_1

DDR0_DQSP_5/DDR1_DQSP_1

DDR0_DQSN_6/DDR1_DQSN_4

DDR0_DQSP_6/DDR1_DQSP_4

DDR0_DQSN_7/DDR1_DQSN_5

DDR0_DQSP_7/DDR1_DQSP_5

2 of 20

1

CC1

0.1U_0201_10V6K

@

2

DDR0_CKE_2/NC

DDR0_CKE_3/NC

NC/DDR0_ODT_1

NC/DDR0_MA_3

NC/DDR0_MA_4

NC/DDR0_ALERT#

NC/DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ_0

DDR0_VREF_DQ_1

DDR1_VREF_DQ

DDR_VTT_CNTL

+3VS+1.2V

12

RC132

100K_0402_5%

V32

V31

T32

T31

U36

U37

U34

U35

AE32

AF32

AE31

AF31

AC37

AC36

AC34

AC35

AA35

AB35

AA37

AA36

AB34

W36

Y31

W34

AA34

AC32

AC31

AB32

Y32

W32

AB31

V34

V35

W35

C27

D27

D31

C31

J35

J34

P34

P35

AP35

AP34

AV34

AV35

BB35

BB34

BF34

BF35

W37

W31

F36

D35

D37

E36

C35

follow CRB

DDR_A_CLK#0

DDR_A_CLK0

DDR_A_CLK#1

DDR_A_CLK1

DDR_A_CKE0

DDR_A_CKE1

DDR_A_CKE2

DDR_A_CKE3

DDR_A_CS#0

DDR_A_CS#1

DDR_A_ODT0

DDR_A_CAB9

DDR_A_CAB8

DDR_A_CAB5

DDR_A_CAA0

DDR_A_CAA2

DDR_A_CAA4

DDR_A_CAA3

DDR_A_CAA1

DDR_A_CAB7

DDR_A_CAA7

DDR_A_CAA6

DDR_A_CAB0

DDR_A_CAB2

DDR_A_CAB1

DDR_A_CAB3

DDR_A_CAB4

DDR_A_CAB6

DDR_A_CAA5

DDR_A_CAA8

DDR_A_CAA9

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_DQS#5

DDR_A_DQS5

DDR_B_DQS#0

DDR_B_DQS0

DDR_B_DQS#1

DDR_B_DQS1

DDR_B_DQS#4

DDR_B_DQS4

DDR_B_DQS#5

DDR_B_DQS5

+VREF_CA_C

+V_DDR_REFA_C

+V_DDR_REFB_C

DDR_PG_CTRL

DDR_VTT_PG_CTRL <43>

DDR_A_CLK#0 <19>

DDR_A_CLK0 <19>

DDR_A_CLK#1 <19>

DDR_A_CLK1 <19>

DDR_A_CKE0 <19>

DDR_A_CKE1 <19>

DDR_A_CKE2 <19>

DDR_A_CKE3 <19>

DDR_A_CS#0 <19>

DDR_A_CS#1 <19>

DDR_A_ODT0 <19>

DDR_A_CAB9 <19>

DDR_A_CAB8 <19>

DDR_A_CAB5 <19>

DDR_A_CAA0 <19>

DDR_A_CAA2 <19>

DDR_A_CAA4 <19>

DDR_A_CAA3 <19>

DDR_A_CAA1 <19>

DDR_A_CAB7 <19>

DDR_A_CAA7 <19>

DDR_A_CAA6 <19>

DDR_A_CAB0 <19>

DDR_A_CAB2 <19>

DDR_A_CAB1 <19>

DDR_A_CAB3 <19>

DDR_A_CAB4 <19>

DDR_A_CAB6 <19>

DDR_A_CAA5 <19>

DDR_A_CAA8 <19>

DDR_A_CAA9 <19>

DDR_A_DQS#0 <19>

DDR_A_DQS0 <19>

DDR_A_DQS#1 <19>

DDR_A_DQS1 <19>

DDR_A_DQS#4 <19>

DDR_A_DQS4 <19>

DDR_A_DQS#5 <19>

DDR_A_DQS5 <19>

DDR_B_DQS#0 <20>

DDR_B_DQS0 <20>

DDR_B_DQS#1 <20>

DDR_B_DQS1 <20>

DDR_B_DQS#4 <20>

DDR_B_DQS4 <20>

DDR_B_DQS#5 <20>

DDR_B_DQS5 <20>

+VREF_CA_C

+V_DDR_REFA_C

+V_DDR_REFB_C

Trace width/Spacing >= 20mils

DDR_A_D[0..15]<19>

DDR_A_D[32..47]<19>

C C

DDR_B_D[0..15]<20>

DDR_B_D[32..47]<20>

B B

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

< For ODT & VTT Power Control >

DDR_VTT_CNTL to DDR

VTT supplied ramped

<35u S

(tCPU 18)

DDR_PG_CTRL

2

3

74AUP1G07GW_TSSOP5

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

UC1C

J22

DDR1_DQ_0/DDR0_DQ_16

H25

DDR1_DQ_1/DDR0_DQ_17

G22

DDR1_DQ_2/DDR0_DQ_18

H22

DDR1_DQ_3/DDR0_DQ_19

F25

DDR1_DQ_4/DDR0_DQ_20

J25

DDR1_DQ_5/DDR0_DQ_21

G25

DDR1_DQ_6/DDR0_DQ_22

F22

DDR1_DQ_7/DDR0_DQ_23

D22

DDR1_DQ_8/DDR0_DQ_24

C22

DDR1_DQ_9/DDR0_DQ_25

C24

DDR1_DQ_10/DDR0_DQ_26

D24

DDR1_DQ_11/DDR0_DQ_27

A22

DDR1_DQ_12/DDR0_DQ_28

B22

DDR1_DQ_13/DDR0_DQ_29

A24

DDR1_DQ_14/DDR0_DQ_30

B24

DDR1_DQ_15/DDR0_DQ_31

G31

DDR1_DQ_16/DDR0_DQ_48

G32

DDR1_DQ_17/DDR0_DQ_49

H29

DDR1_DQ_18/DDR0_DQ_50

H28

DDR1_DQ_19/DDR0_DQ_51

G28

DDR1_DQ_20/DDR0_DQ_52

G29

DDR1_DQ_21/DDR0_DQ_53

H31

DDR1_DQ_22/DDR0_DQ_54

H32

DDR1_DQ_23/DDR0_DQ_55

L31

DDR1_DQ_24/DDR0_DQ_56

L32

DDR1_DQ_25/DDR0_DQ_57

N29

DDR1_DQ_26/DDR0_DQ_58

N28

DDR1_DQ_27/DDR0_DQ_59

L28

DDR1_DQ_28/DDR0_DQ_60

L29

DDR1_DQ_29/DDR0_DQ_61

N31

DDR1_DQ_30/DDR0_DQ_62

N32

DDR1_DQ_31/DDR0_DQ_63

AJ29

DDR1_DQ_32/DDR1_DQ_16

AJ30

DDR1_DQ_33/DDR1_DQ_17

AM32

DDR1_DQ_34/DDR1_DQ_18

AM31

DDR1_DQ_35/DDR1_DQ_19

AM30

DDR1_DQ_36/DDR1_DQ_20

AM29

DDR1_DQ_37/DDR1_DQ_21

AJ31

DDR1_DQ_38/DDR1_DQ_22

AJ32

DDR1_DQ_39/DDR1_DQ_23

AR31

DDR1_DQ_40/DDR1_DQ_24

AR32

DDR1_DQ_41/DDR1_DQ_25

AV30

DDR1_DQ_42/DDR1_DQ_26

AV29

DDR1_DQ_43/DDR1_DQ_27

AR30

DDR1_DQ_44/DDR1_DQ_28

AR29

DDR1_DQ_45/DDR1_DQ_29

AV32

DDR1_DQ_46/DDR1_DQ_30

AV31

DDR1_DQ_47/DDR1_DQ_31

BA32

DDR1_DQ_48/DDR1_DQ_48

BA31

DDR1_DQ_49/DDR1_DQ_49

BD31

DDR1_DQ_50/DDR1_DQ_50

BD32

DDR1_DQ_51/DDR1_DQ_51

BA30

DDR1_DQ_52/DDR1_DQ_52

BA29

DDR1_DQ_53/DDR1_DQ_53

BD29

DDR1_DQ_54/DDR1_DQ_54

BD30

DDR1_DQ_55/DDR1_DQ_55

BG31

DDR1_DQ_56/DDR1_DQ_56

BG32

DDR1_DQ_57/DDR1_DQ_57

BK32

DDR1_DQ_58/DDR1_DQ_58

BK31

DDR1_DQ_59/DDR1_DQ_59

BG29

DDR1_DQ_60/DDR1_DQ_60

BG30

DDR1_DQ_61/DDR1_DQ_61

BK30

DDR1_DQ_62/DDR1_DQ_62

BK29

DDR1_DQ_63/DDR1_DQ_63

WHL-U42_BGA1528

DDR1_CKN_0/DDR1_CKN_0

DDR1_CKP_0/DDR1_CKP_0

DDR1_CKN_1/DDR1_CKN_1

DDR1_CKP_1/DDR1_CKP_1

DDR1_CKE_0/DDR1_CKE_0

DDR1_CKE_1/DDR1_CKE_1

DDR1_CKE_2/NC

DDR1_CKE_3/NC

DDR1_CS#_0/DDR1_CS#_0

DDR1_CS#_1/DDR1_CS#_1

DDR1_ODT_0/DDR1_ODT_0

NC/DDR1_ODT_1

DDR1_CAB_9/DDR1_MA_0

DDR1_CAB_8/DDR1_MA_1

DDR1_CAB_5/DDR1_MA_2

NC/DDR1_MA_3

NC/DDR1_MA_4

DDR1_CAA_0/DDR1_MA_5

DDR1_CAA_2/DDR1_MA_6

DDR1_CAA_4/DDR1_MA_7

DDR1_CAA_3/DDR1_MA_8

DDR1_CAA_1/DDR1_MA_9

DDR1_CAB_7/DDR1_MA_10

DDR1_CAA_7/DDR1_MA_11

DDR1_CAA_6/DDR1_MA_12

DDR1_CAB_0/DDR1_MA_13

DDR1_CAB_2/DDR1_MA_14

DDR1_CAB_1/DDR1_MA_15

DDR1_CAB_3/DDR1_MA_16

DDR1_CAB_4/DDR1_BA_0

DDR1_CAB_6/DDR1_BA_1

DDR1_CAA_5/DDR1_BG_0

DDR1_CAA_9/DDR1_BG_1

DDR1_CAA_8/DDR1_ACT#

DDR1_DQSN_0/DDR0_DQSN_2

DDR1_DQSP_0/DDR0_DQSP_2

DDR1_DQSN_1/DDR0_DQSN_3

DDR1_DQSP_1/DDR0_DQSP_3

DDR1_DQSN_2/DDR0_DQSN_6

DDR1_DQSP_2/DDR0_DQSP_6

DDR1_DQSN_3/DDR0_DQSN_7

DDR1_DQSP_3/DDR0_DQSP_7

DDR1_DQSN_4/DDR1_DQSN_2

DDR1_DQSP_4/DDR1_DQSP_2

DDR1_DQSN_5/DDR1_DQSN_3

DDR1_DQSP_5/DDR1_DQSP_3

DDR1_DQSN_6/DDR1_DQSN_6

DDR1_DQSP_6/DDR1_DQSP_6

DDR1_DQSN_7/DDR1_DQSN_7

DDR1_DQSP_7/DDR1_DQSP_7

NC/DDR1_ALERT#

NC/DDR1_PAR

DRAM_RESET#

DDR_COMP_0

DDR_COMP_1

DDR_COMP_2

3 of 20

AF28

AF29

AE28

AE29

T28

T29

V28

V29

AL37

AL35

AL36

AL34

AG36

AG35

AF34

AG37

AE35

AF35

AE37

AC29

AE36

AB29

AG34

AC28

AB28

AK35

AJ35

AK34

AJ34

AJ37

AJ36

W29

Y28

W28

H24

G24

C23

D23

G30

H30

L30

N30

AL31

AL30

AU31

AU30

BC31

BC30

BH31

BH30

Y29

AE34

BU31

BN28

BN27

BN29

DDR_B_CLK#0

DDR_B_CLK0

DDR_B_CLK#1

DDR_B_CLK1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CKE2

DDR_B_CKE3

DDR_B_CS#0

DDR_B_CS#1

DDR_B_ODT0

DDR_B_CAB9

DDR_B_CAB8

DDR_B_CAB5

DDR_B_CAA0

DDR_B_CAA2

DDR_B_CAA4

DDR_B_CAA3

DDR_B_CAA1

DDR_B_CAB7

DDR_B_CAA7

DDR_B_CAA6

DDR_B_CAB0

DDR_B_CAB2

DDR_B_CAB1

DDR_B_CAB3

DDR_B_CAB4

DDR_B_CAB6

DDR_B_CAA5

DDR_B_CAA9

DDR_B_CAA8

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_DQS#3

DDR_A_DQS3

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_DQS#7

DDR_A_DQS7

DDR_B_DQS#2

DDR_B_DQS2

DDR_B_DQS#3

DDR_B_DQS3

DDR_B_DQS#6

DDR_B_DQS6

DDR_B_DQS#7

DDR_B_DQS7

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

DDR_B_CLK#0 <20>

DDR_B_CLK0 <20>

DDR_B_CLK#1 <20>

DDR_B_CLK1 <20>

DDR_B_CKE0 <20>

DDR_B_CKE1 <20>

DDR_B_CKE2 <20>

DDR_B_CKE3 <20>

DDR_B_CS#0 <20>

DDR_B_CS#1 <20>

DDR_B_ODT0 <20>

DDR_B_CAB9 <20>

DDR_B_CAB8 <20>

DDR_B_CAB5 <20>

DDR_B_CAA0 <20>

DDR_B_CAA2 <20>

DDR_B_CAA4 <20>

DDR_B_CAA3 <20>

DDR_B_CAA1 <20>

DDR_B_CAB7 <20>

DDR_B_CAA7 <20>

DDR_B_CAA6 <20>

DDR_B_CAB0 <20>

DDR_B_CAB2 <20>

DDR_B_CAB1 <20>

DDR_B_CAB3 <20>

DDR_B_CAB4 <20>

DDR_B_CAB6 <20>

DDR_B_CAA5 <20>

DDR_B_CAA9 <20>

DDR_B_CAA8 <20>

DDR_A_DQS#2 <19>

DDR_A_DQS2 <19>

DDR_A_DQS#3 <19>

DDR_A_DQS3 <19>

DDR_A_DQS#6 <19>

DDR_A_DQS6 <19>

DDR_A_DQS#7 <19>

DDR_A_DQS7 <19>

DDR_B_DQS#2 <20>

DDR_B_DQS2 <20>

DDR_B_DQS#3 <20>

DDR_B_DQS3 <20>

DDR_B_DQS#6 <20>

DDR_B_DQS6 <20>

DDR_B_DQS#7 <20>

DDR_B_DQS7 <20>

1 2

RC246 200_0402_1%

RC247 80.6_0201_1%

1 2

1 2

RC40 162_0402_1%

Trace width=12~15 mil, Spacing=20 mils

Max trace length= 500 mil

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2018/02/06 202 0/5/17

2018/02/06 202 0/5/17

2018/02/06 202 0/5/17

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

WHL-U(2/12)LPDDR3

WHL-U(2/12)LPDDR3

WHL-U(2/12)LPDDR3

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Friday, May 18, 2018

Friday, May 18, 2018

Friday, May 18, 2018

LA-G651P

LA-G651P

LA-G651P

1

52

52

52

7

7

7

0.2

0.2

0.2

Compal For Lenovo

5

4

3

2

1

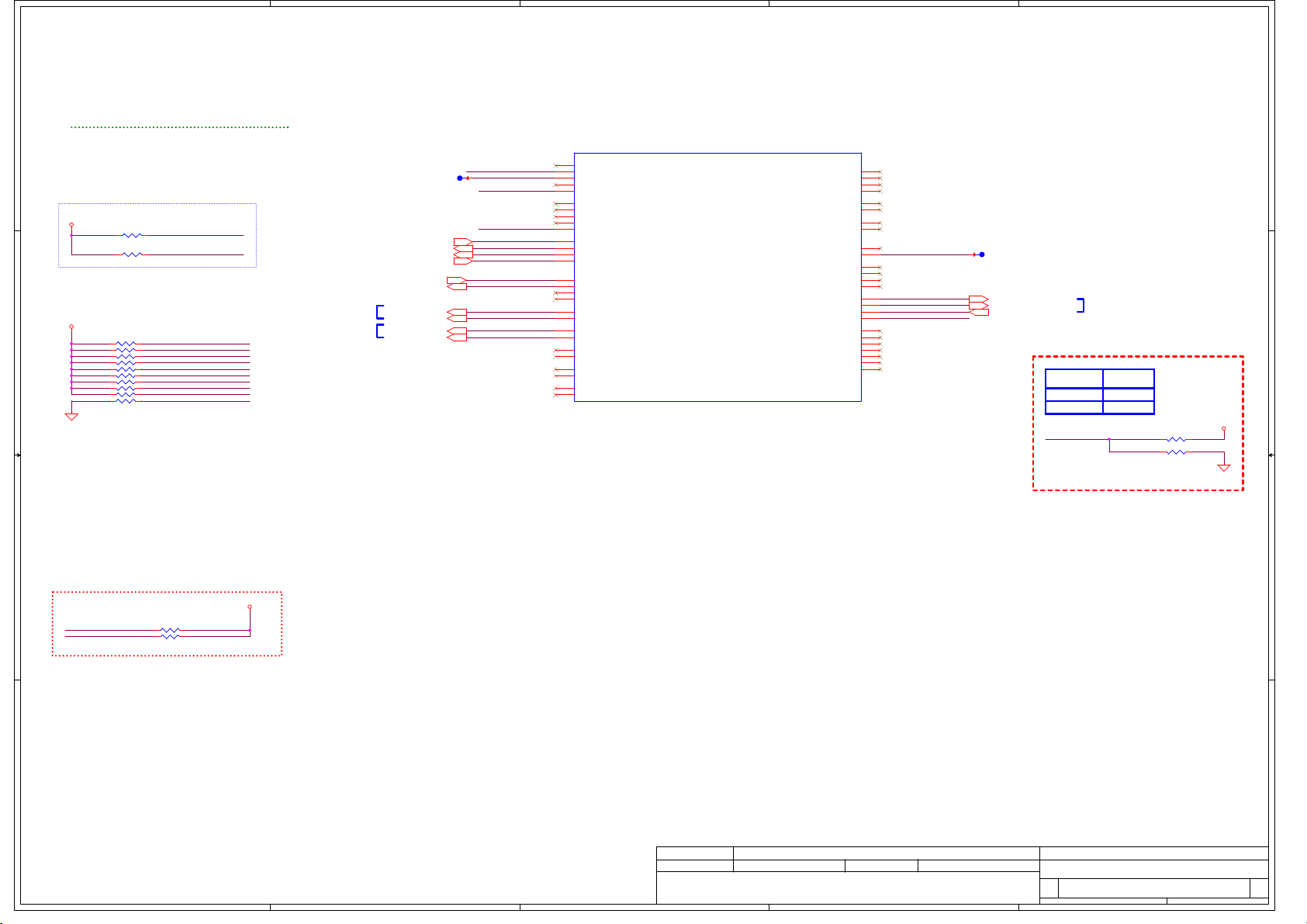

+3VALW

1 2

RC437 100K_02 01_5%

1 2

RC438 100K_02 01_5%

1 2

RC439 100K_02 01_5%

SOC_SPI_0 _SI

SOC_SPI_0 _IO2

SOC_SPI_0 _IO3

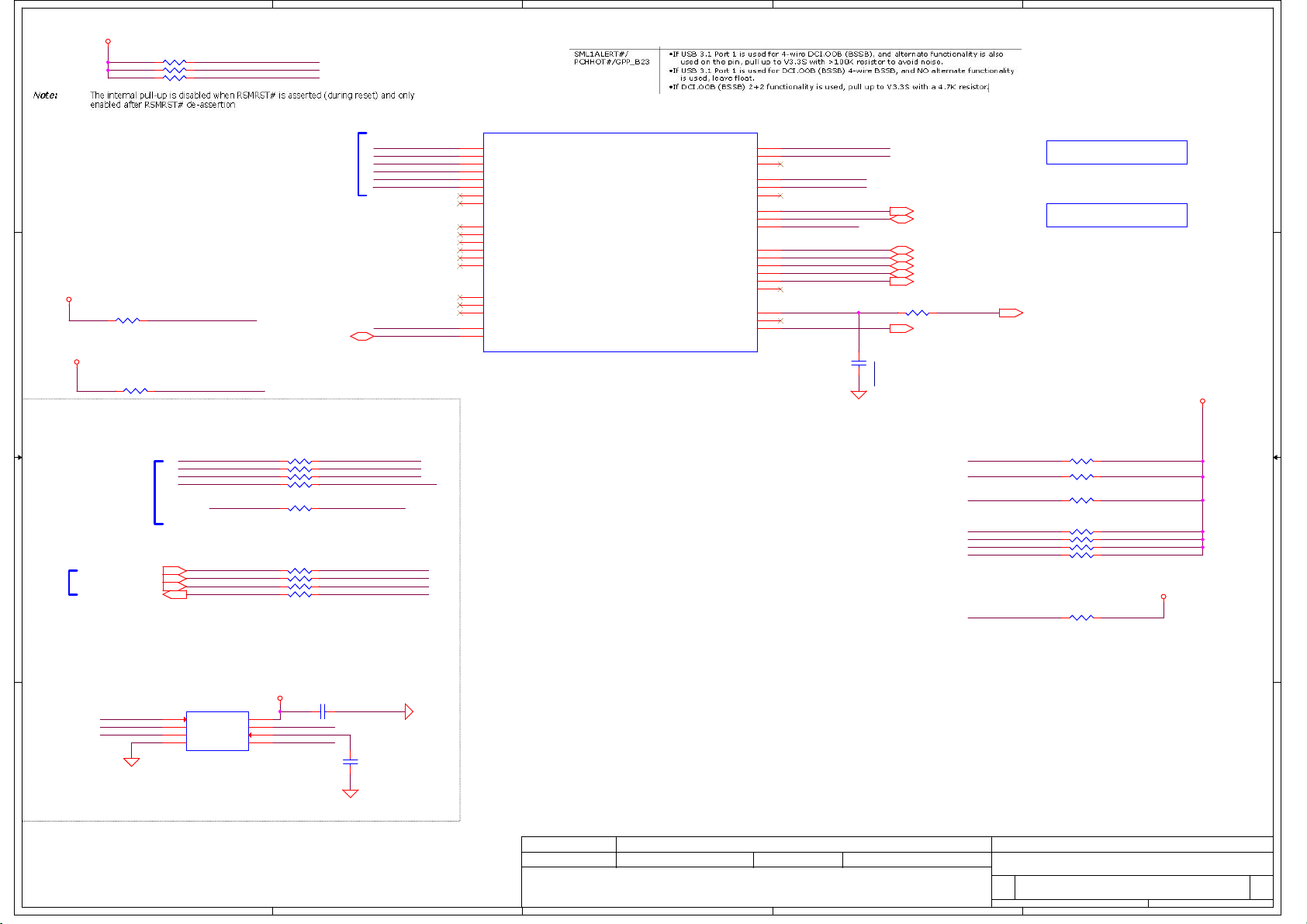

SML0ALERT# (Internal Pull Down):

eSPI or LPC

0 = LPC is selected for EC ==> Default

1 = eSPI is selected for EC

D D

SOC_SPI_0 _CLK

SOC_SPI_0 _SO

SOC_SPI_0 _SI

SPI ROM

+3VS

1 2

RC25 8.2K_040 2_5%

C C

+3VS

1 2

RC112 10K_040 2_5%

SERIRQ

SERIRQ<34>

KB_RST#

SOC_SPI_0 _IO2

SOC_SPI_0 _IO3

SOC_SPI_0 _CS#0

SERIRQ

RPC1, RPC3 an d RC30 are clo se to UC3

SOC_SPI_0 _SO

SOC_SPI_0 _CLK SOC_SPI_0_CLK_R

SOC_SPI_0 _SI

From SOC

B B

From EC

EC_SPI_CL K<34>

EC_SPI_MO SI<34>

EC_SPI_CS 0#<34>

EC_SPI_MISO<34>

SOC_SPI_0 _IO3

SOC_SPI_0 _IO2

EC_SPI_CL K

EC_SPI_MO SI SOC_SPI_0 _SI_R

EC_SPI_CS 0#

EC_SPI_MISO

1 2

RC469 33_0402 _5%

1 2

RC470 33_0402 _5%EMI@

1 2

RC471 33_0402 _5%

1 2

RC472 33_0402 _5%

1 2

RC30 33_0402 _5%

1 2

RC473 33_0402 _5%EMI@

1 2

RC474 33_0402 _5%

1 2

RC475 33_0402 _5%

1 2

RC476 33_0402 _5%

SOC_SPI_0 _IO2_R

SOC_SPI_0 _SO_R

SOC_SPI_0 _SI_R

SOC_SPI_0 _IO3_R

SOC_SPI_0 _CLK_R

SOC_SPI_0 _CS#0

SOC_SPI_0 _SO_R

UC1E

CH37

SPI0_CLK

CF37

SPI0_MISO

CF36

SPI0_MOSI

CF34

SPI0_IO2

CG34

SPI0_IO3

CG36

SPI0_CS0#

CG35

SPI0_CS1#

CH34

SPI0_CS2#

CF20

GPP_D1/SPI1_CLK/BK1/SBK1

CG22

GPP_D2/SPI1_MISO_IO1/BK2/SBK2

CF22

GPP_D3/SPI1_MOSI_IO0/BK3/SBK3

CG23

GPP_D21/SPI1_IO2

CH23

GPP_D22/SPI1_IO3

CG20

GPP_D0/SPI1_CS0#/BK0/SBK0

CH7

CL_CLK

CH8

CL_DATA

CH9

CL_RST#

BV29

GPP_A0/RCIN#/TIME_SYNC1

BV28

GPP_A6/SERIRQ

WHL -U42_BGA1528

GPP_C5/SML0ALERT#

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

5 of 20

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_A8/CLKRUN#

CK14

CH15

CJ15

CH14

CF15

CG15

CN15

CM15

CC34

CA29

BY29

BY27

BV27

CA28

CA27

BV32

BV30

BY30

PCH_SMB _CLK

PCH_SMB _DATA

SOC_SML 0CLK

SOC_SML 0DATA

EC_SMB_ CK2

EC_SMB_ DA2

SOC_SML 1ALERT#

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRA ME#

LPC_CLK 0

PM_CLKR UN#KB_RST#

1 2

RC26 22_0402 _5%EMI@

1

2

Close to RC26

CC3865

33P_0402_50V8J

@RF@

EC_SMB_ CK2 <24,30,34 ,36>

EC_SMB_ DA2 <24,30,34 ,36>

LPC_AD0 <34>

LPC_AD1 <34>

LPC_AD2 <34>

LPC_AD3 <34>

LPC_FRA ME# <34>

PM_CLKR UN# <3 4>

EC_SMB_ CK2

EC_SMB_ DA2

SOC_SML 1ALERT#

PCH_SMB _CLK

PCH_SMB _DATA

SOC_SML 0CLK

SOC_SML 0DATA

PM_CLKR UN#

SMB

(Link to DDR)

SML1

(Link to EC,DGPU,Thermal IC)

CLK_LPC _EC <3 4>

1 2

RC28 1K_0402 _5%

1 2

RC29 1K_0402 _5%

1 2

@

RC113 150K_04 02_5%

1 2

12

12

12

12

RC465 1K_0402 _5%

RC466 1K_0402 _5%

RC467 1K_0402 _5%

RC468 1K_0402 _5%

RC31 8.2K_0402_5%

+3VS

+3VS

< SPI ROM - 16M >

SOC_SPI_0 _CS#0

SOC_SPI_0 _IO2_R

A A

UC3

1

CS#

2

DO(IO1)

3

IO2

4

GND

XM25QH1 28AHIG SOP 8P

Compal For Lenovo

5

VCC

CLK

DI(IO0)

IO

8

7

6

5

+3VALW

@

1 2

CC2 0.1U_0201 _10V6K

SOC_SPI_0 _IO3_RSOC_SPI_0 _SO_R

SOC_SPI_0 _CLK_R

SOC_SPI_0 _SI_R

1

CC3

10P_040 2_50V8J

2

@EMI@

Security Classification

Security Classification

Security Classification

2017/5/3 2017/6/2

2017/5/3 2017/6/2

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

2017/5/3 2017/6/2

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet o f

Date : Sheet o f

2

Date : Sheet o f

Compal Electronics, Inc.

WHL-U(3/12)SPI,SMB,LPC,ESPI

WHL-U(3/12)SPI,SMB,LPC,ESPI

WHL-U(3/12)SPI,SMB,LPC,ESPI

LA-G651P

LA-G651P

LA-G651P

8 52Friday, May 18, 2018

8 52Friday, May 18, 2018

8 52Friday, May 18, 2018

1

0.2

0.2

0.2

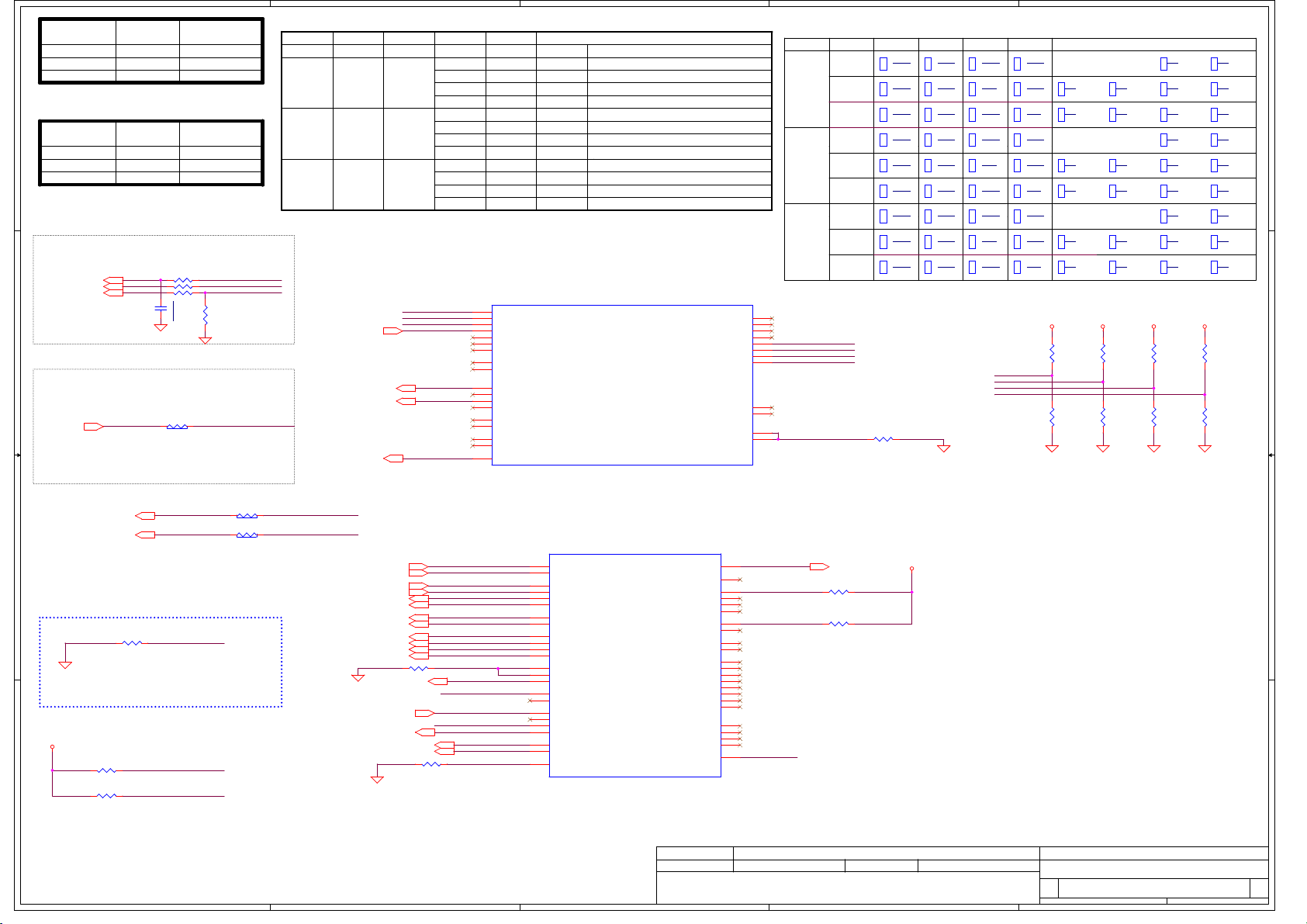

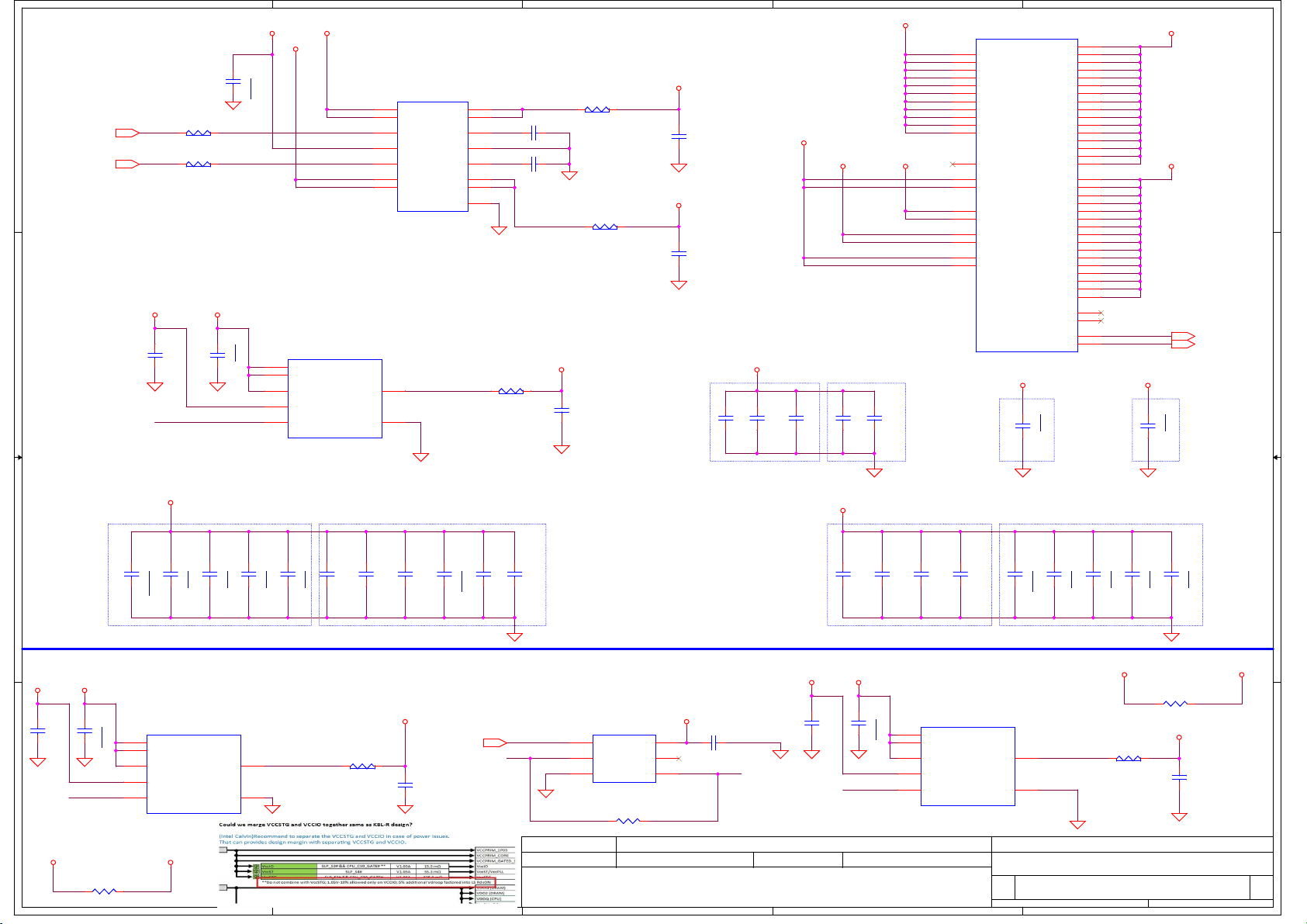

5

Vender ID

Samsung

Hynix

Micron

D D

DRAM Capacity

4GB

8GB

16GB

< HD AUDIO >

HDA_BIT_CLK_R<33>

HDA_SYNC_R<33>

HDA_SDOUT_R<33>

C C

CPU_GPP_G7 CPU_GPP_G6

SDRAM_ID4 SDRAM_ID3

0 0

0

1

CPU_GPP_G5 CPU_GPP_G4

SDRAM_ID2 SDRAM_ID1

1

0

0 0

0

1

HDA_SDOUT reserve 500 ohm PD for Audio

lost issue

1 2

RC477 33_040 2_5%EMI@

1 2

RC478 33_040 2_5%

1 2

RC479 33_040 2_5%

1

Close to RC477

2

1

0

HDA_BIT_CLK

HDA_SYNC

HDA_SDOUT

12

RC3945

@

499_0402_ 1%

CC3866

33P_0402_50V8J

@RF@

CPU Memory down vender control table

CPU_GPP_G7

0 0

1 0 0 1

HDA_SDIN0<33>

< To Enable ME Override >

CNV_RF_RESET #<3 2>

CLKREQ_CNV#<32>

ME_EN< 34>

DGPU

B B

RC116 0_0402 _5%

GC6_FB_EN<24,25>

GPU_EVENT#<24>

1 2

12

GC6_FB_EN GC6_FB_EN1V8

GPU_EVENT# SOC_GPP_C10

CNV_RF_RESET #

RC390775K_0 402_5% CNVi@

HDA_SDOUT

RC463 0_0402 _5%

RC464 0_0402 _5%

12

1 2

HDA_SPKR<33 >

CLK_CNV_CRX_D TX_N<32>

CLK_CNV_CRX_D TX_P<32>

CLK_CNV_CT X_DRX_N<32>

CLK_CNV_CT X_DRX_P<32>

Follow Jefferson Peak schematic check list.

+3VS

1 2

RC487 10K_0402_5%@

1 2

A A

RC33 2.2K_0402 _5%@

WLBT_OFF#

HDA_SPKR

4

CPU_GPP_G4CPU_GPP_G5CPU_GPP_G6

SDRAM_ID2SDRAM_ID3SDRAM_ID4

Vende r

Samsung K4E6E304EC-EG CG

0

Hynix

Micron

HDA_SYNC

HDA_BIT_CLK

HDA_SDOUT

CNV_RF_RESET #

CLKREQ_CNV#

HDA_SPKR

1 2

COEX3<32>

1 2

10K_0402_5 %

CNV_CRX_DTX_N0

CNV_CRX_DTX_P0

CNV_CRX_DTX_N1

CNV_CRX_DTX_P1

CNV_CTX_DRX_N0

CNV_CTX_DRX_P0

CNV_CTX_DRX_N1

CNV_CTX_DRX_P1

CLK_CNV_CRX_D TX_N

CLK_CNV_CRX_D TX_P

CLK_CNV_CT X_DRX_N

CLK_CNV_CT X_DRX_P

RC443150_040 2_1% C NVi@

SOC_GPP_C10

WLBT_OFF#

CNV_CRX_DTX_N0<32>

CNV_CRX_DTX_P0<32>

CNV_CRX_DTX_N1<32>

CNV_CRX_DTX_P1<32>

CNV_CTX_DRX_N0<32>

CNV_CTX_DRX_P0<32>

CNV_CTX_DRX_N1<32>

CNV_CTX_DRX_P1<32>

TP_INT#<35>

WLBT_OFF#<32>

COEX1<32>

COEX2<32>

RC444

SDRAM_ID1

0

1

1 1

0 0

010

1

1 1

0 0

MD size

0

1

0

8GB

16GB

4GB

4GB

1

0

8GB

16GB

4GB

4GB

8GB

01

1 1

UC1G

BN34

HDA_SYNC/I2S0_SFRM

BN37

HDA_BCLK/I2S0_SCLK

BN36

HDA_SDO/I2S0_TXD

BN35

HDA_SDI0/I2S0_RXD

BL36

HDA_SDI1/I2S1_RXD/SNDW1_DATA

BL35

HDA_RST#/I2S1_SCLK/SNDW1_CLK

CK23

GPP_D23/I2S_MCLK

BL37

I2S1_SFRM/SNDW2_CLK

BL34

I2S1_TXD/SNDW2_DATA

CJ32

GPP_H1/I2S2_SFRM/CNV_BT_I2S_BCLK/CNV_RF_RESET#

CH32

GPP_H0/I2S2_SCLK/CNV_BT_I2S_SCLK

CH29

GPP_H2/I2S2_TXD/CNV_BT_I2S_SDI/MODEM_CLKREQ

CH30

GPP_H3/I2S2_RXD/CNV_BT_I2S_SDO

CP24

GPP_D19/DMIC_CLK0/SNDW4_CLK

CN24

GPP_D20/DMIC_DATA0/SNDW4_DATA

CK25

GPP_D17/DMIC_CLK1/SNDW3_CLK

CJ25

GPP_D18/DMIC_DATA1/SNDW3_DATA

CF35

GPP_B14/SPKR

WHL-U42 _BGA1528

CNV_WT_R COMP

COEX3

GC6_FB_EN1V8

COEX1

COEX2

SOC_A4WP_PR ESENT

16GB

4GB

UC1I

CR30

CNV_WR_D0N

CP30

CNV_WR_D0P

CM30

CNV_WR_D1N

CN30

CNV_WR_D1P

CN32

CNV_WT_D0N

CM32

CNV_WT_D0P

CP33

CNV_WT_D1N

CN33

CNV_WT_D1P

CN31

CNV_WR_CLKN

CP31

CNV_WR_CLKP

CP34

CNV_WT_CLKN

CN34

CNV_WT_CLKP

CP32

CNV_WT_RCOMP_0

CR32

CNV_WT_RCOMP_1

CP20

GPP_F0/CNV_PA_BLANKING

CK19

GPP_F1

CG17

GPP_F2

CR14

GPP_C8/UART0_RXD

CP14

GPP_C9/UART0_TXD

CN14

GPP_C10/UART0_RTS#

CM14

GPP_C11/UART0_CTS#

CJ17

GPP_F8/CNV_MFUART2_RXD

CH17

GPP_F9/CNV_MFUART2_TXD

CF17

GPP_F23/A4WP_PRESENT

WHL-U42 _BGA1528

3

Vender desciption

K4E8E324EB-EGC G4GB

K4EBE304EC -EGCG

K4E6E304EC -EGCG(CH B-ONLY)

H9CCNNN8GTALAR-NV D

H9CCNNNBJTALAR-NVD

H9CCNNNCLGALAR-NVD

H9CCNNNBJ TALAR-NVD(C HB-ONLY)

MT52L256M32D1PF-093WT:B

MT52L512M32D2PF-093WT:B

MT52L1G32D4PG-093WT:B

MT52L512M32D2PF-093WT:B(CHB-ONLY)

GPP_G0/SD_CMD

GPP_G1/SD3_DATA0

GPP_G2/SD3_DATA1

GPP_G3/SD3_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A17/SD_VDD1_PWR_EN#/ISH_GP7

7 of 20

GPP_D4/IMGCLKOUT0/BK4/SBK4

9 of 20

GPP_A16/SD_1P8_SEL

SD_1P8_RCOMP

SD_3P3_RCOMP

GPP_H18/CPU_C10_GATE#

GPP_H19/TIMESYNC_0

GPP_H21

GPP_H22

GPP_H23

GPP_F10

GPD7

GPP_F3

GPP_H20/IMGCLKOUT_1

GPP_F12/EMMC_DATA0

GPP_F13/EMMC_DATA1

GPP_F14/EMMC_DATA2

GPP_F15/EMMC_DATA3

GPP_F16/EMMC_DATA4

GPP_F17/EMMC_DATA5

GPP_F18/EMMC_DATA6

GPP_F19/EMMC_DATA7

GPP_F20/EMMC_RCLK

GPP_F21/EMMC_CLK

GPP_F11/EMMC_CMD

GPP_F22/EMMC_RESET#

EMMC_RCOMP

GPP_H21 XTAL frequency selected.

0: 38.4/19.2Mhz

1: 24MHz XTAL selected

SOC_C10_GATE#

CN27

CM27

SOC_GPP_H21

CF25

CN26

CM26

CK17

SOC_GPD7

BV35

CN20

XTAL INPUT MODE (HVM ONLY)

CG25

LOW: XTAL INPUT IS SINGLE ENDED

CH25

HIGH: XTAL IS ATTACHED

CR20

CM20

CN19

CM19

CN18

CR18

CP18

CM18

CM16

CP16

CR16

CN16

SOC_SD_RCOM P

CK15

BOM Conf i g

Vende r

Samsung

Hynix

Micron

CH36

CL35

CL36

CM35

SDRAM_ID1

CN35

SDRAM_ID2

CH35

SDRAM_ID3

CK36

SDRAM_ID4

CK34

BW36

BY31

CK33

SOC_SD_RCOM P

CM34

RC441 4.7K_0402_5 %

RC442 100K_0 201_5%

SDRAM_ID4 SDRAM_ID3 SDRAM_ID2 SDRAM_ID1

MD size

4GB

8GB

16GB

4GB

8GB

16GB

4GB

8GB

16GB

1 2

RC440 200_040 2_1%

SOC_C10_GATE# <13>

1 2

1 2

2

RC435

RC433

S4G@

RC435

S8G@

RC435

S16G@

RC435

H4G@

RC435

H8G@

RC435

H16G@

RC434

M4G@

RC434

M8G@

RC434

M16G@

S4G@

RC433

S8G@

RC433

S16G@

RC432

H4G@

RC432

H8G@

RC432

H16G@

RC433

M4G@

RC433

M8G@

RC433

M16G@

RC248

RC249

S4G@

S4G@

RC89

S8G@

RC248

S16G@

RC248

H4G@

RC89

H8G@

RC248

H16G@

RC248

M4G@

RC89

M8G@

RC248

M16G@

RC249

S8G@

RC88

S16G@

RC249

H4G@

RC249

H8G@

RC88

H16G@

RC249

M4G@

RC249

M8G@

RC88

M16G@

UD1 S8G@

SA0000AZT20

UD1 S16G@

SA00008VV20

UD1 H8G@

SA0000ALP00

UD1 H16G@

SA00009ZL00

UD1 M8G@

SA0000AM400

UD1 M16G@

SA00009ZN00

LPDDR3

UD2 S8G@

SA0000AZT20

UD2 S16G@

SA00008VV20

UD2 H8G@

SA0000ALP00

UD2 H16G@

SA00009ZL00

UD2 M8G@

SA0000AM400

UD2 M16G@

SA00009ZN00

1

UD3 S4G@

SA0000AZT20

UD3 S8G@

SA0000AZT20

UD3 S16G@

SA00008VV20

UD3 H4G@

SA0000ALP00

UD3 H8G@

SA0000ALP00

UD3 H16G@

SA00009ZL00

UD3 M4G@

SA0000AM400

UD3 M8G@

SA0000AM400

UD3 M16G@

SA00009ZN00

UD4 S4G@

SA0000AZT20

UD4 S8G@

SA0000AZT20

UD4 S16G@

SA00008VV20

UD4 H4G@

SA0000ALP00

UD4 H8G@

SA0000ALP00

UD4 H16G@

SA00009ZL00

UD4 M4G@

SA0000AM400

UD4 M8G@

SA0000AM400

UD4 M16G@

SA00009ZN00

Memory Strap Resistors

+3VS +3VS +3VS + 3VS

+3VALW

SDRAM_ID1

SDRAM_ID2

SDRAM_ID3

SDRAM_ID4

12

12

RC249

10K_0201_5 %

@

RC88

10K_0201_5 %

@

12

12

RC248

10K_0201_5 %

@

RC89

10K_0201_5 %

@

12

RC432

10K_0201_5 %

12

RC433

10K_0201_5 %

12

RC434

@

@

10K_0201_5 %

12

RC435

10K_0201_5 %

@

@

SPKR ( Internal Pull Down):

TOP Swap Override

0 = Disable TOP Swap mode. ==> Default

1 = Enable TOP Swap Mode.

Compal For Lenovo

5

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2017/5/3 2017/6/2

2017/5/3 2017/6/2

2017/5/3 2017/6/2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size D ocument Number R ev

Size D ocument Number R ev

Size D ocument Number R ev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

Compal Electronics, Inc.

WHL-U(4/12)HDA,EMMC,SDIO,CSI2

WHL-U(4/12)HDA,EMMC,SDIO,CSI2

WHL-U(4/12)HDA,EMMC,SDIO,CSI2

LA-G651P

LA-G651P

Friday, May 18, 2018

Friday, May 18, 2018

Friday, May 18, 2018

LA-G651P

1

52

52

52

9

9

9

0.2

0.2

0.2

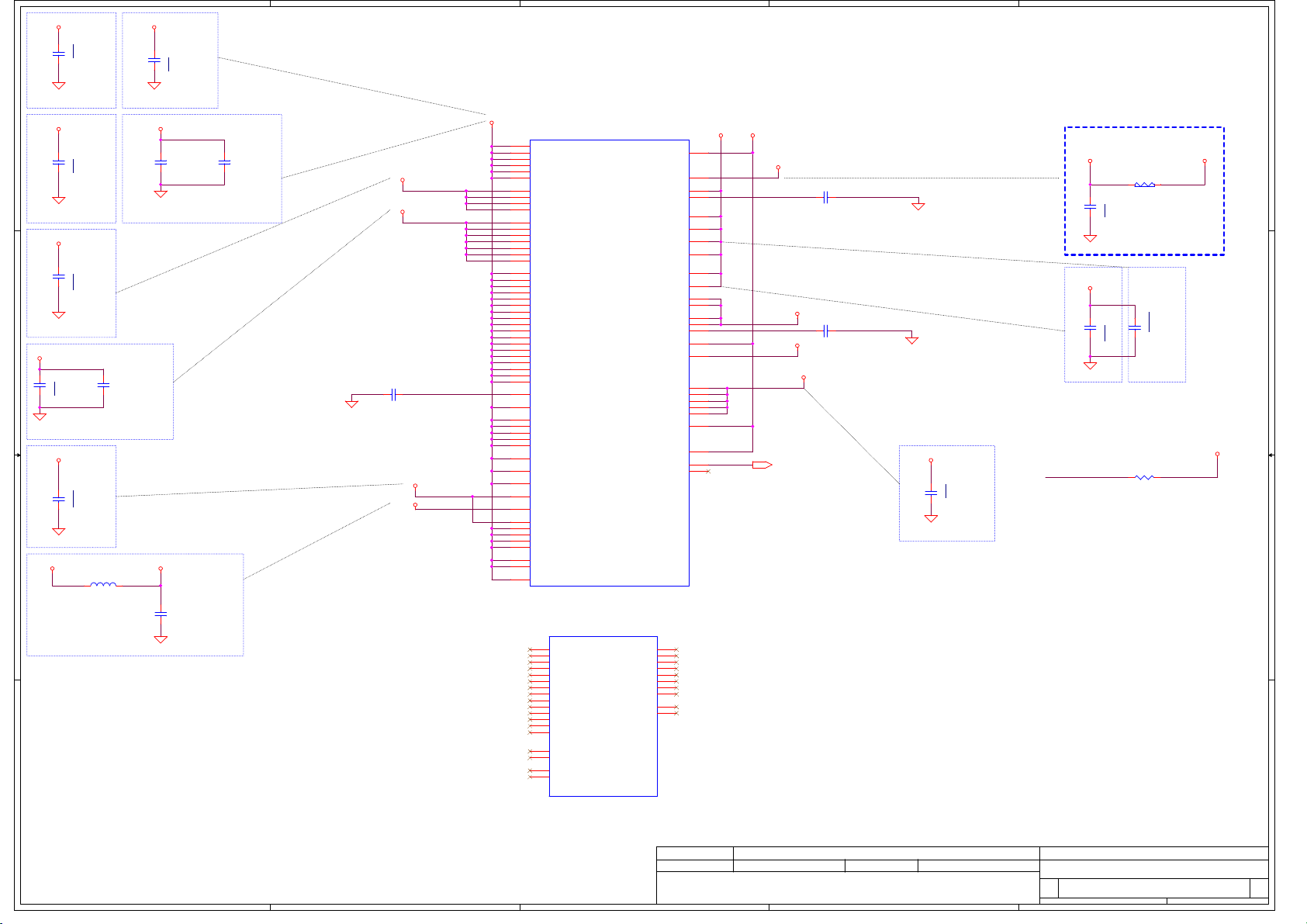

5

< PCH PLTRST Buf f er >

+3VS

1 2

RC481 10K_04 02_5%

1 2

RC482 10K_04 02_5%

1 2

RC483 10K_04 02_5%

CLKREQ_PCIE#0

12

RC140

@

D D

10K_0402_5 %

CLKREQ_PCIE#0

CLKREQ_PCIE#2

CLKREQ_PCIE#4

DGPU

NGFF WL+BT(KEY E)

SSD

+3VL_RTC

WAKE#

SOC_SRTCRS T#

CLR CMOS

SM_INTRUDER#

PCH_PWR OK

EC_RSMRST#

SYS_RESET#

+1.05V_VCCST

12

RC52

1K_0402_5%

RC53 60.4_0402_ 1%

CC126

100P_0402_50V8J

1

ESD@

2

EC_CLEAR_CMO S# <34>

1 2

1 2

RC36 20K_0402_ 5%

12

CC6 1U_0201_6 .3V6M

1 2

RC37 20K_0402_ 5%

12

CC7 1U_0201_6 .3V6M

1 2

CLRP2 SHORT PADS

1 2

C C

B B

RC39 1M_0402_5 %

+3VALW

RC484 10K_04 02_5%

RC485 10K_04 02_5%

RC486 10K_04 02_5%

1 2

ESD@

CC97 100P_0402_ 50V8J

1 2

ESD@

CC94 100P_0402_ 50V8J

1 2

ESD@

CC95 100P_0402_ 50V8J

+3VALW

1 2

1 2

1 2

1 2

RC54

1K_0402_5%

SYS_RESET#

EC_RSMRST#

SYS_PWROK

From EC (Open-Drain)

VCCST_PWR GD<34>

EC_VCCST_PG

4

UC1J

CLK_PCIE_N0< 21>

CLK_PCIE_P0<21>

CLKREQ_PCIE#0<2 1>

CLK_PCIE_N2< 32>

CLK_PCIE_P2<32>

CLKREQ_PCIE#2<3 2>

CLK_PCIE_N4< 32>

CLK_PCIE_P4<32>

CLKREQ_PCIE#4<3 2>

EC_RSMRST#<34>

T31 T P@

SYS_PWROK<34>

PCH_PWR OK<34>

CLKREQ_PCIE#0

CLKREQ_PCIE#2

CLKREQ_PCIE#4

SOC_PLTRST #

SYS_RESET#

EC_RSMRST#

EC_VCCST_PG

SYS_PWROK

PCH_PWR OK

EC_RSMRST#

WAKE#

AW2

CLKOUT_PCIE_N_0

AY3

CLKOUT_PCIE_P_0

CF32

GPP_B5/SRCCLKREQ0#

BC1

CLKOUT_PCIE_N_1

BC2

CLKOUT_PCIE_P_1

CE32

GPP_B6/SRCCLKREQ1#

BD3

CLKOUT_PCIE_N_2

BC3

CLKOUT_PCIE_P_2

CF30

GPP_B7/SRCCLKREQ2#

BH3

CLKOUT_PCIE_N_3

BH4

CLKOUT_PCIE_P_3

CE31

GPP_B8/SRCCLKREQ3#

BA1

CLKOUT_PCIE_N_4

BA2

CLKOUT_PCIE_P_4

CE30

GPP_B9/SRCCLKREQ4#

BE1

CLKOUT_PCIE_N_5

BE2

CLKOUT_PCIE_P_5

CF31

GPP_B10/SRCCLKREQ5#

WHL-U42 _BGA1528

SOC_PLTRST #

UC1K

BJ35

GPP_B13/PLTRST#

CN10

SYS_RESET#

BR36

RSMRST#

AR2

PROCPWRGD

BJ2

VCCST_PWRGOOD

CR10

SYS_PWROK

BP31

PCH_PWROK

BP30

DSW_PWROK

BV34

GPP_A13/SUSWARN#/SUSPWRDACK

BY32

GPP_A15/SUSACK#

BU30

WAKE#

BU32

GPD2/LAN_WAKE#

BU34

GPD11/LANPHYPC

WHL-U42 _BGA1528

3

10 of 20

TC7SH08FU F_SSOP5

GPP_B11/EXT_PWR_GATE#

11 of 20

XTAL_IN

XTAL_OUT

CLK_BIASREF

CLKIN_XTAL

RTCX1

RTCX2

SRTCRST#

RTCRST#

UC4

P

4

Y

G

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD6/SLP_A#

GPD0/BATLOW#

INTRUDER#

INPUT3VSEL

AU1

AU2

BT32

CK3

CK2

CJ1

CM3

BN31

BN32

BR37

BR34

12

RC44

100K_0402_5%

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SUSCLK

1 2

RC55 0_0402_5%

+3VS

5

1

B

2

A

3

@

GPP_B12/SLP_S0#

GPD9/SLP_WLAN#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPP_B2/VRALERT#

SUSCLK

33E_SOC_XTAL24 _IN_R

33E_SOC_XTAL24 _OUT_R

XCLK_BIASREF

CLKIN_XTAL

SOC_RTCX1

SOC_RTCX2

SOC_SRTCRS T#

EC_CLEAR_CMO S#

12

CC8

100P_0402_ 50V8J

ESD@

BJ37

PM_SLP_S3#

BU36

PM_SLP_S4#

BU27

PM_SLP_S5#

BT29

BU29

BT31

BT30

BU37

PBTN_OUT#

BU28

AC_PRESENT_R

BU35

PM_BATLOW#

BV36

SM_INTRUDER#

BR35

CC37

SOC_VRALERT#

CC36

SOC_INPUT3VSEL

BT27

PCI_RST# <21,32,34>

RC103 0_0402 _5%

SUSCLK <32>

CLKIN_XTAL < 32>

PM_SLP_S3# <34 >

PM_SLP_S4# <34 ,41>

T131TP@

1 2

2

33E_SOC_XTAL24 _IN_R

33E_SOC_XTAL24 _OUT_R

RC58 47_0201_5 %

LC99

1

1

4

4

DLM0NSN90 0HY2D_4P

RC63 47_0201_5 %EMI@

PBTN_OUT# < 34>

AC_PRESENT <24,34 >

1 2

EMI@

@EMI@

1 2

XCLK_BIASREF

RC110 60.4_04 02_1%

CLKIN_XTAL

RC245 10K_04 02_5%

33E_SOC_XTAL24 _IN

2

2

3

3

33E_SOC_XTAL24 _OUT

SOC_RTCX2

SOC_RTCX1

PM_BATLOW#

AC_PRESENT_R

SOC_VRALERT#

SOC_INPUT3VSEL

1

1 2

1 2

1 2

RC38 200K_0402 _1%

YC3

SJ10000UJ00

24MHZ_18PF_XRC GB24M000F2P51R0

3

3

CC19

27P_0402_50V8J

1

2

RC41 10M_0402_ 5%

32.768KHZ_9P F_X1A000141000200

1

CC9

6.8P_0402_5 0V8C

2

RC46 8.2K_0402_ 5%

RC48 10K_0402_ 5%

RC50 10K_0402_ 5%

RC445 4.7K_0402 _5%

RC446 4.7K_0402 _5%

1 2

YC2

1 2

1 2

1 2

@

1 2

@

1 2

@

1 2

NC

NC

2

4

1

1

1

CC10

6.8P_0402_5 0V8C

2

+3VALW

CC20

27P_0402_50V8J

1

2

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Compal For Lenovo

5

4

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2017/5/3 2017/6/2

2017/5/3 2017/6/2

2017/5/3 2017/6/2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

WHL-U(5/12)CLK,PM,GPIO

WHL-U(5/12)CLK,PM,GPIO

WHL-U(5/12)CLK,PM,GPIO

Size D ocument Number R ev

Size D ocument Number R ev

Size D ocument Number R ev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

2

Date : Sheet of

LA-G651P

LA-G651P

LA-G651P

1

10 52Friday, May 18, 2018

10 52Friday, May 18, 2018

10 52Friday, May 18, 2018

0.2

0.2

0.2

5

4

3

2

1

GSPI0_MOSI (Internal Pu ll Down):

No Reboot

0 = Disable No Reboot mode. ==> Default

1 = Enable No Reboot Mode. (PCH will disable the TCO

Timer system reboot feature). This funct i on is usef ul

when running ITP/XDP.

D D

GSPI1_MOSI (Internal Pu ll Down):

Boot BIOS Strap Bit

0 = SPI Mode ==> Default

1 = LPC Mode

+3VS

+3VS

C C

1 2

RC59 4.7K_0402 _5%@

1 2

RC60 150K_040 2_5%@

1 2

RC83 49.9K_040 2_1%

1 2

RC84 49.9K_040 2_1%

1 2

RC3941 2.2K_040 2_5%

1 2

RC3942 2.2K_040 2_5%

1 2

RC488 10K_04 02_5%DIS@

1 2

RC489 10K_04 02_5%

1 2

RC42 2.2K_0402 _5%

1 2

RC43 2.2K_0402 _5%

1 2

RC447 10K_04 02_5%@

1 2

RC448 10K_04 02_5%DIS@

GSPI0_MOSI

GSPI1_MOSI

UART0_RX

UART0_TX

I2C_1_SDA

I2C_1_SCL

DGPU_PWR _EN

SOC_GPP_A7

I2C_0_SDA

I2C_0_SCL

DGPU_HOLD_R ST#

DGPU_HOLD_R ST#

Touch Pad

UCM

CNV_BRI_CRX_DTX<32>

CNV_RGI_CTX_DRX<32>

CNV_BRI_CTX_DRX<32>

CNV_RGI_CRX_DTX<32>

I2C_0_SDA<35>

I2C_0_SCL<35>

I2C_1_SDA<30>

I2C_1_SCL<30>

T2406

SOC_GPP_A7

GPP_B16

GSPI0_MOSI

TP@

GSPI1_MOSI

CNV_BRI_CRX_DTX

CNV_RGI_CTX_DRX

CNV_BRI_CTX_DRX

CNV_RGI_CRX_DTX

UART0_RX<32,35 >

UART0_TX<32,35>

UC1F

CC27

GPP_B15/GSPI0_CS0#

CC32

GPP_A7/PIRQA#/GSPI0_CS1#

CE28

GPP_B16/GSPI0_CLK

CE27

GPP_B17/GSPI0_MISO

CE29

GPP_B18/GSPI0_MOSI

CA31

GPP_B19/GSPI1_CS0#

CA32

GPP_A11/PME#/GSPI1_CS1#/SD_VDD2_PWR_EN#

CC29

GPP_B20/GSPI1_CLK

CC30

GPP_B21/GSPI1_MISO

CA30

GPP_B22/GSPI1_MOSI

CK20

GPP_F5/CNV_BRI_RSP

CG19

GPP_F6/CNV_RGI_DT

CJ20

GPP_F4/CNV_BRI_DT

CH19

GPP_F7/CNV_RGI_RSP

CR12

GPP_C20/UART2_RXD

CP12

GPP_C21/UART2_TXD

CN12

GPP_C22/UART2_RTS#

CM12

GPP_C23/UART2_CTS#

CM11

GPP_C16/I2C0_SDA

CN11

GPP_C17/I2C0_SCL

CK12

GPP_C18/I2C1_SDA

CJ12

GPP_C19/I2C1_SCL

CF27

GPP_H4/I2C2_SDA

CF29

GPP_H5/I2C2_SCL

CH27

GPP_H6/I2C3_SDA

CH28

GPP_H7/I2C3_SCL

CJ30

GPP_H8/I2C4_SDA

CJ31

GPP_H9/I2C4_SCL

WHL-U42 _BGA1528

GPP_D9/ISH_SPI_CS#/GSPI2_CS0#

GPP_D10/ISH_SPI_CLK/GSPI2_CLK

GPP_D11/ISH_SPI_MISO/GSPI2_MISO

GPP_D12/ISH_SPI_MOSI/GSPI2_MOSI

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_H10/I2C5_SDA/ISH_I2C2_SDA

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_A12/ISH_GP6/BM_BUSY#/SX_EXIT_HOLDOFF#

6 of 20

GPP_H11/I2C5_SCL/ISH_I2C2_SCL

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

GPP_D15/ISH_UART0_RTS#/GSPI2_CS1#

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

CN22

CR22

CM22

CP22

CK22

CH20

CH22

CJ22

CJ27

CJ29

CM24

CN23

CM23

CR24

CG12

CH12

CF12

CG14

BW35

BW34

CA37

CA36

CA35

CA34

BW37

GPP_H11

DGPU_PWR _EN

DGPU_HOLD_R ST#

GPU_ALL_PGOOD

DGPU_PRSNT #

T2405TP@

DGPU_PWR _EN <24,26,34>

DGPU_HOLD_R ST# <21>

GPU_ALL_PGOOD < 21>

Funct i on

DIS

UMA Only

DGPU_PRSNT #

DGPU

DGPU_PRSNT#

(GPP_C1 5)

0

1

+3VS

12

R7310K_0402_5 % UMA@

12

R7410K_0402_5 % DIS@

B B

Place close to PCH

+1.8VALW

CNV_RGI_CRX_DTX

CNV_BRI_CRX_DTX

A A

1 2

RC3939 20K_020 1_5%@

1 2

RC3938 20K_020 1_5%@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Compal For Lenovo

5

4

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL