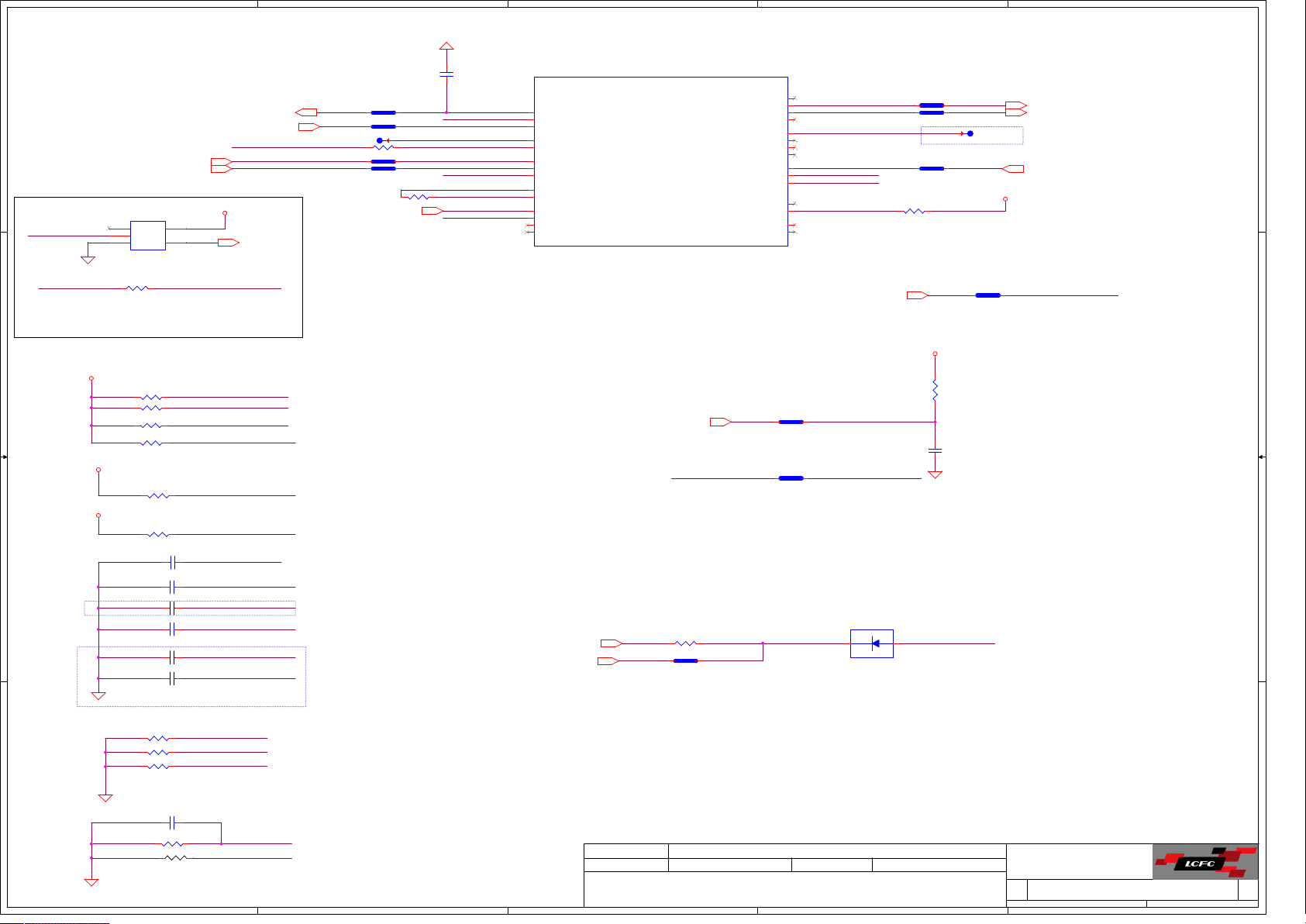

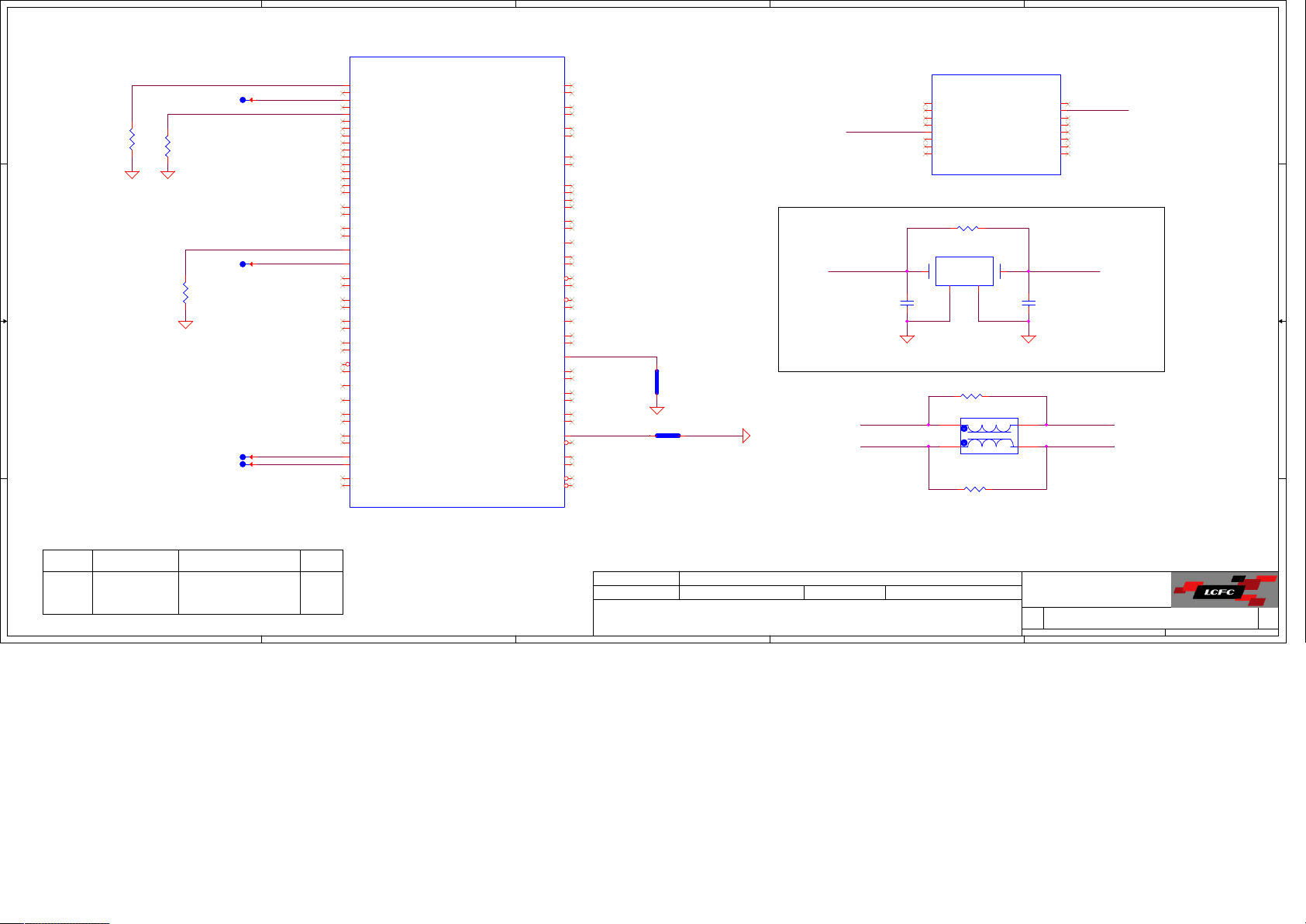

Lenovo IdeaPad S145-15IK Schematic

5

https://vinafix.com

D D

C C

4

3

2

1

B B

A A

5

4

3

2

1

5

https://vinafix.com

D D

C C

4

3

2

1

B B

A A

5

4

3

2

1

A

https://vinafix.com

1 1

B

C

D

E

LCFC Confidential

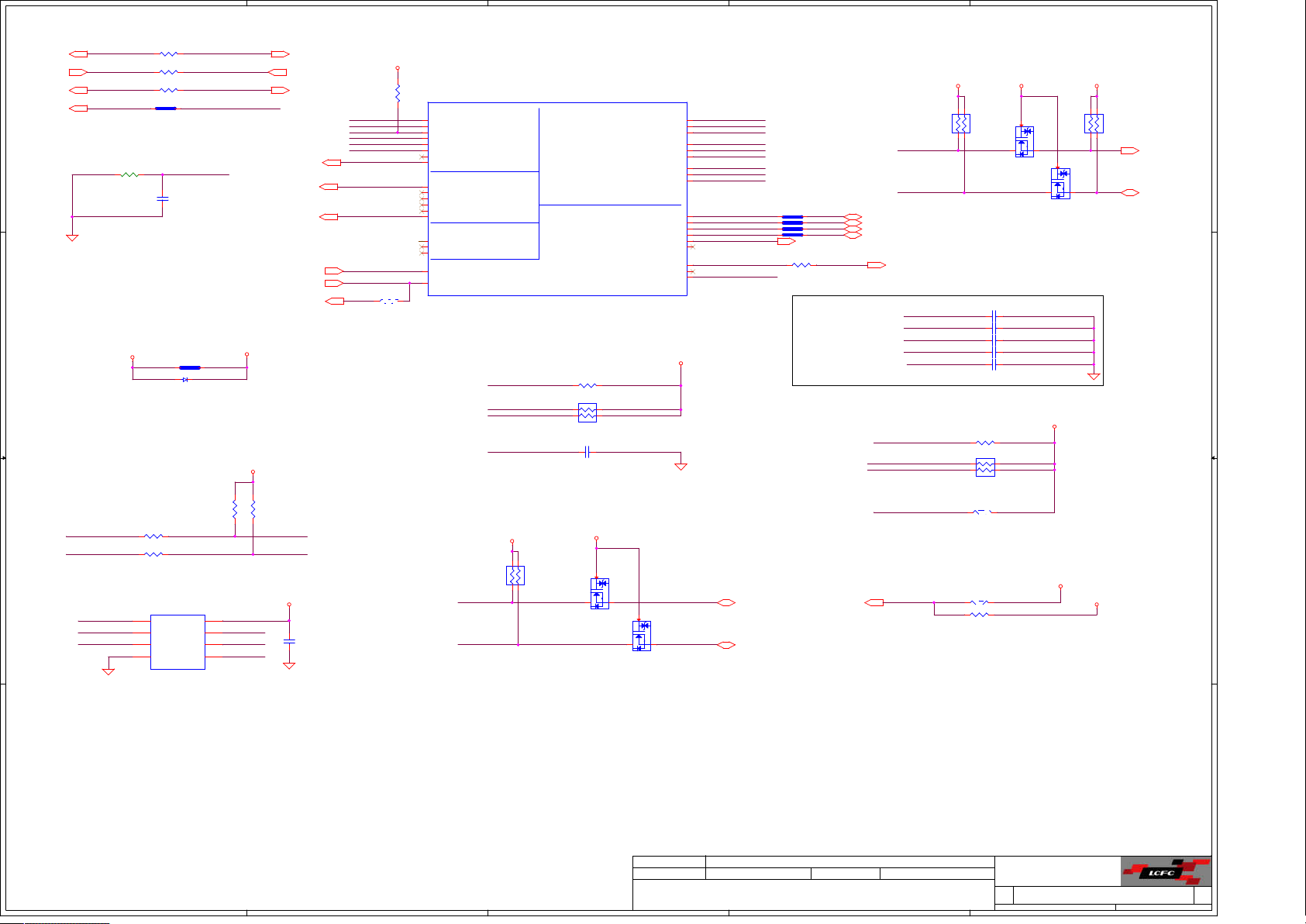

GS44B/GS54B/GS44C/GS54C MB Schematics Document

2 2

KBL-U22/U42 with DDR4 + Nvidia N16S-GTR/N17S-G1

2019-02

REV:0.1

3 3

4 4

Title

Title

Title

Cover Page

Cover Page

Cover Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wednesday, May 29, 2019

Wednesday, May 29, 2019

Wednesday, May 29, 2019

GS44B/GS54B

GS44B/GS54B

GS44B/GS54B

E

1 60

1 60

1 60

1.0

1.0

1.0

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

C

2015/08/20

2015/08/20

2015/08/20

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

2016/08/20

2016/08/20

2016/08/20

LCFC confidential

https://vinafix.com

5

4

3

2

1

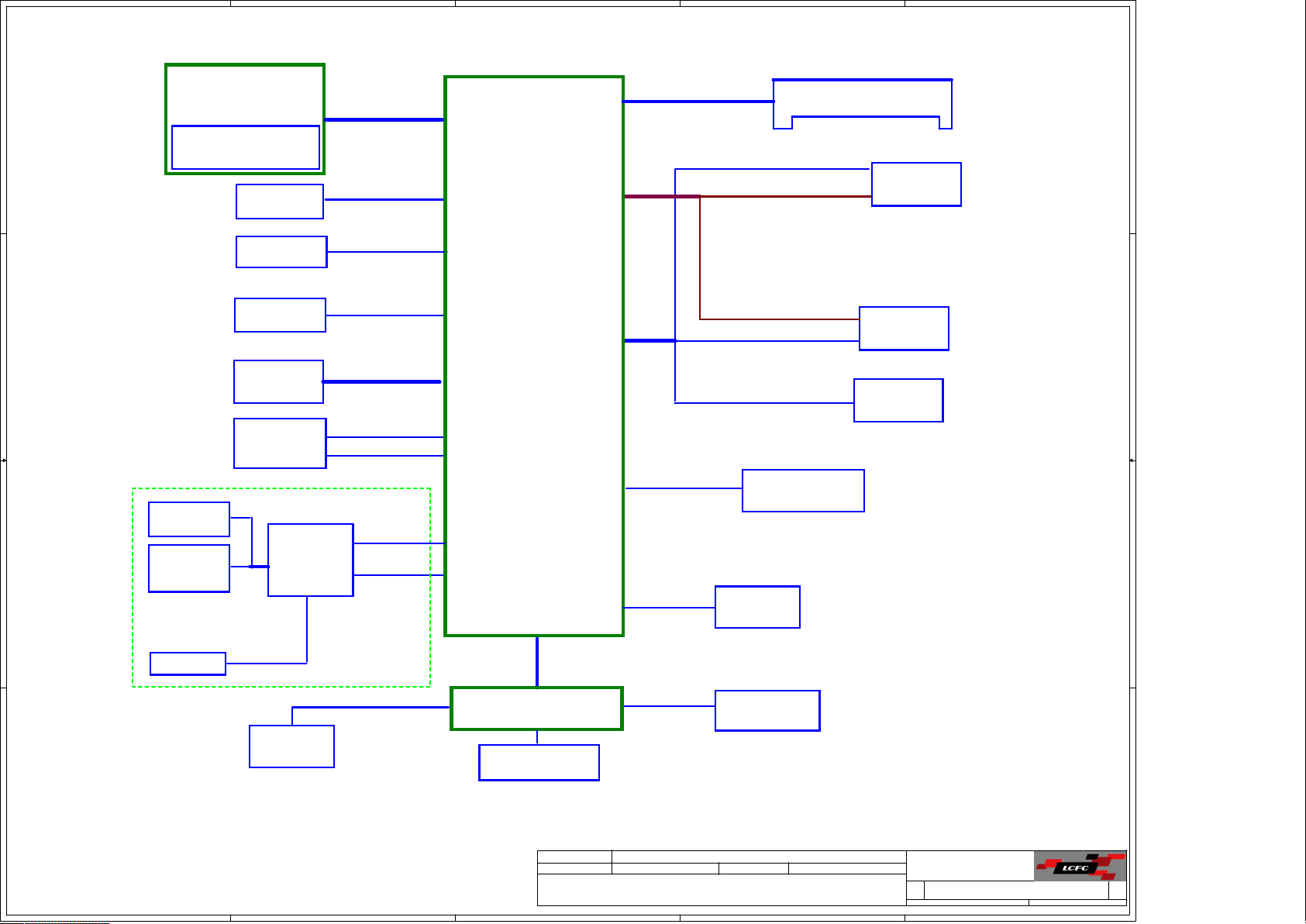

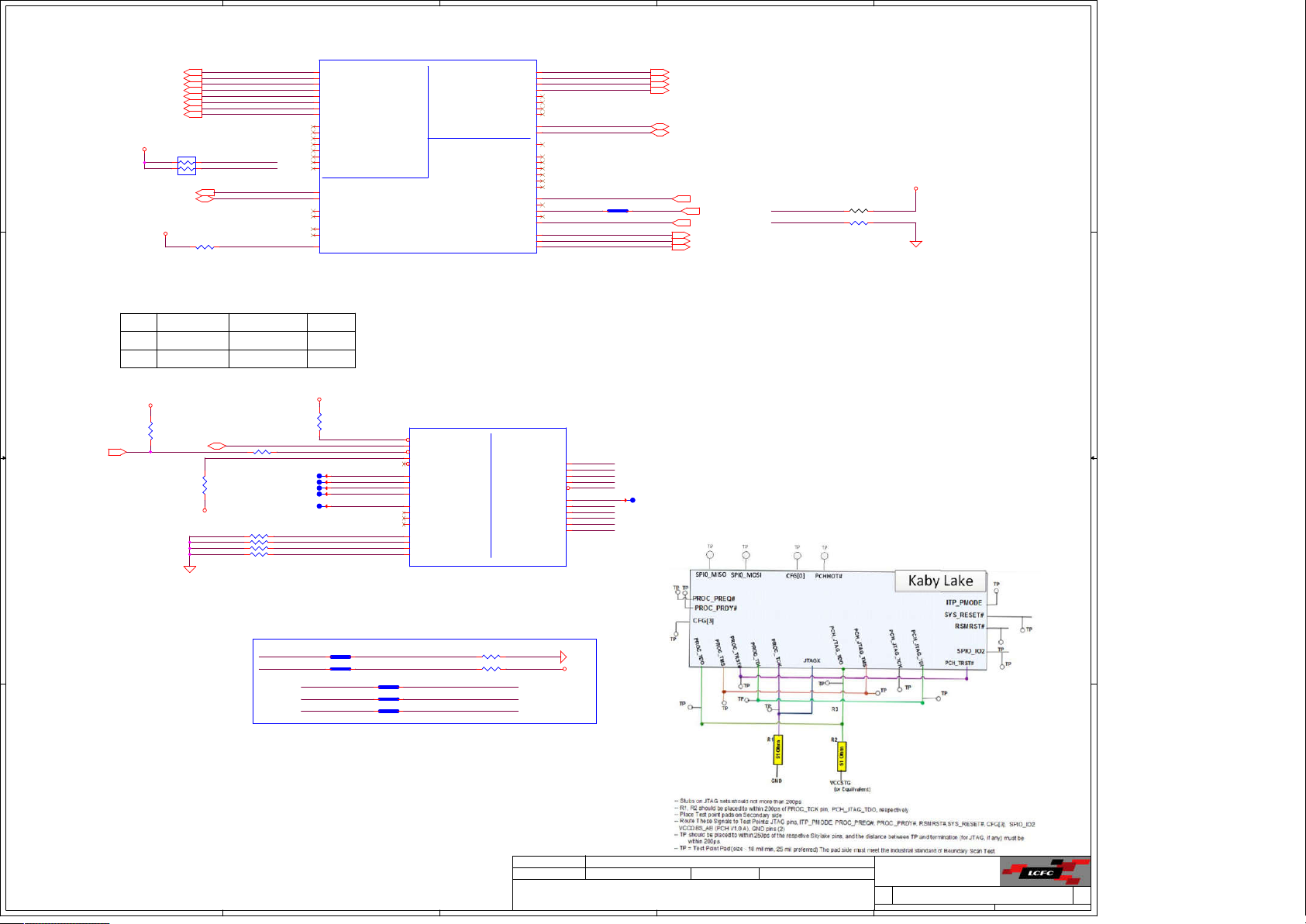

NV N16x/N17x

Package: FCBGA595

D D

PCI-Express

4x Gen3

Memory Bus

1.2V DDR4

DDR4 SO-DIMM+MDx4

Page 17/18

VRAM: 256*32

GDDR5*2: 2GB

HDMI Conn.

eDP Conn

HDMI (DDI 1)

eDP x2

USB3.0

x1

x1

USB3.0 Conn

x1

Intel MCP

SATA HDD

C C

SATA x1

KBL-R-U22 /U42 15W

USB2.0

NGFF PCI-Express

SSD

4x Gen3

BGA-1356

42mm*24mm

I2C

Page 3~16

Page 43

PCIe x1

USB2.0 x1

HD Audio

USB2.0

x1

x1

NGFF

WLAN&BT

SPK Conn.

Page 30

Realtek

HP&Mic

B B

Combo Conn.

Page 30

RTS5199

SPI

x1

x1

Touch Pad

SPI ROM (16MB)

W25Q128JVSIQ

Page 45

Page 07

USB3.0 Conn

USB2.0 Conn

EC

LPC

Page 44

GPIO

HALL Sensor

SD Conn.

IO Board

ITE IT8586E-LQFP128

Int.KBD

Page 45

A A

5

4

Thermal Sensor

F75303M

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

Page 39

3

2015/08/20

2015/08/20

2015/08/20

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/08/20

2016/08/20

2016/08/20

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

GS44B/GS54B

GS44B/GS54B

GS44B/GS54B

Wednesday, May 29, 2019

Wednesday, May 29, 2019

Wednesday, May 29, 2019

2 61

2 61

2 61

1

0.1

0.1

0.1

A

Vinafix.com

https://vinafix.com

B

C

D

E

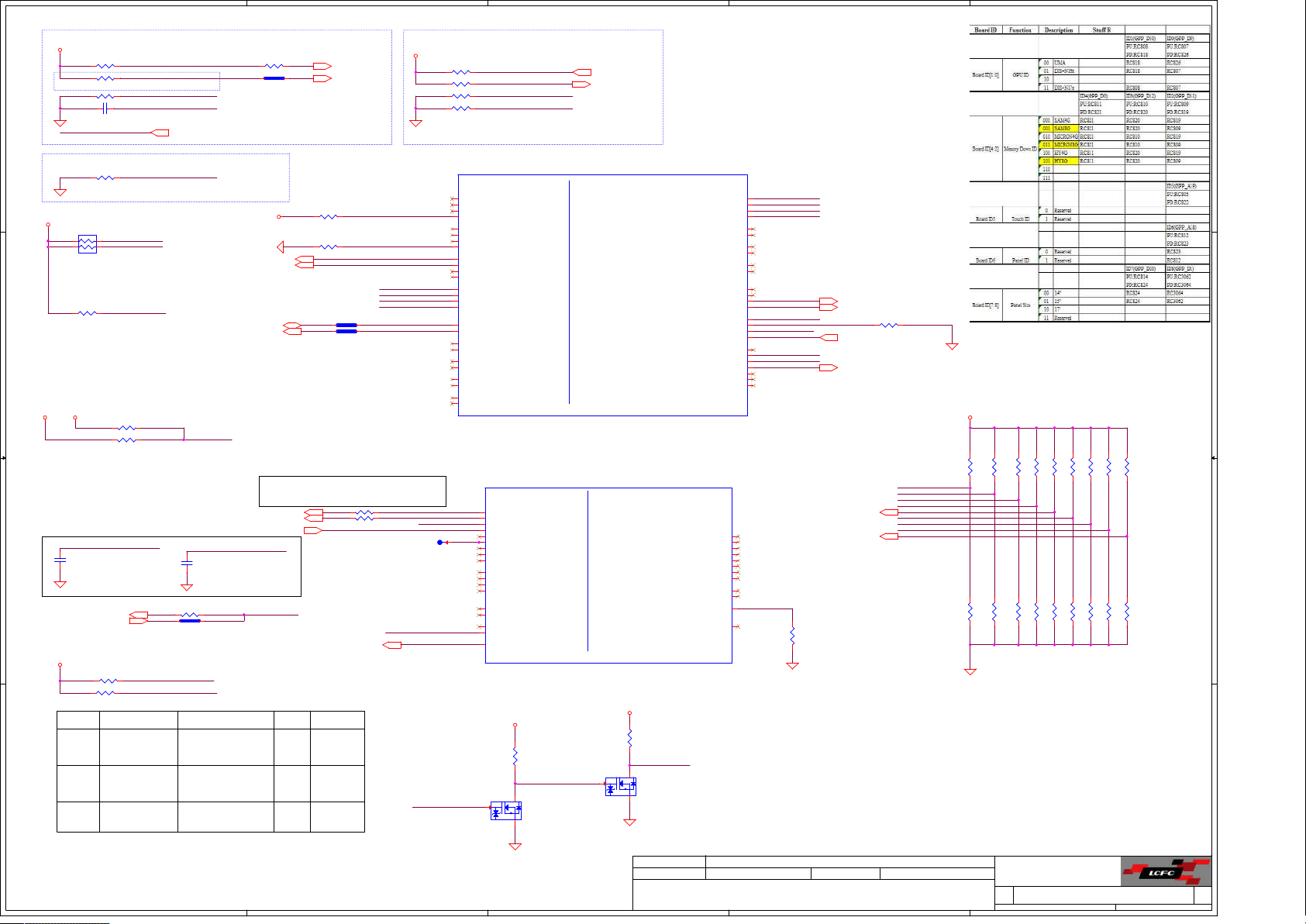

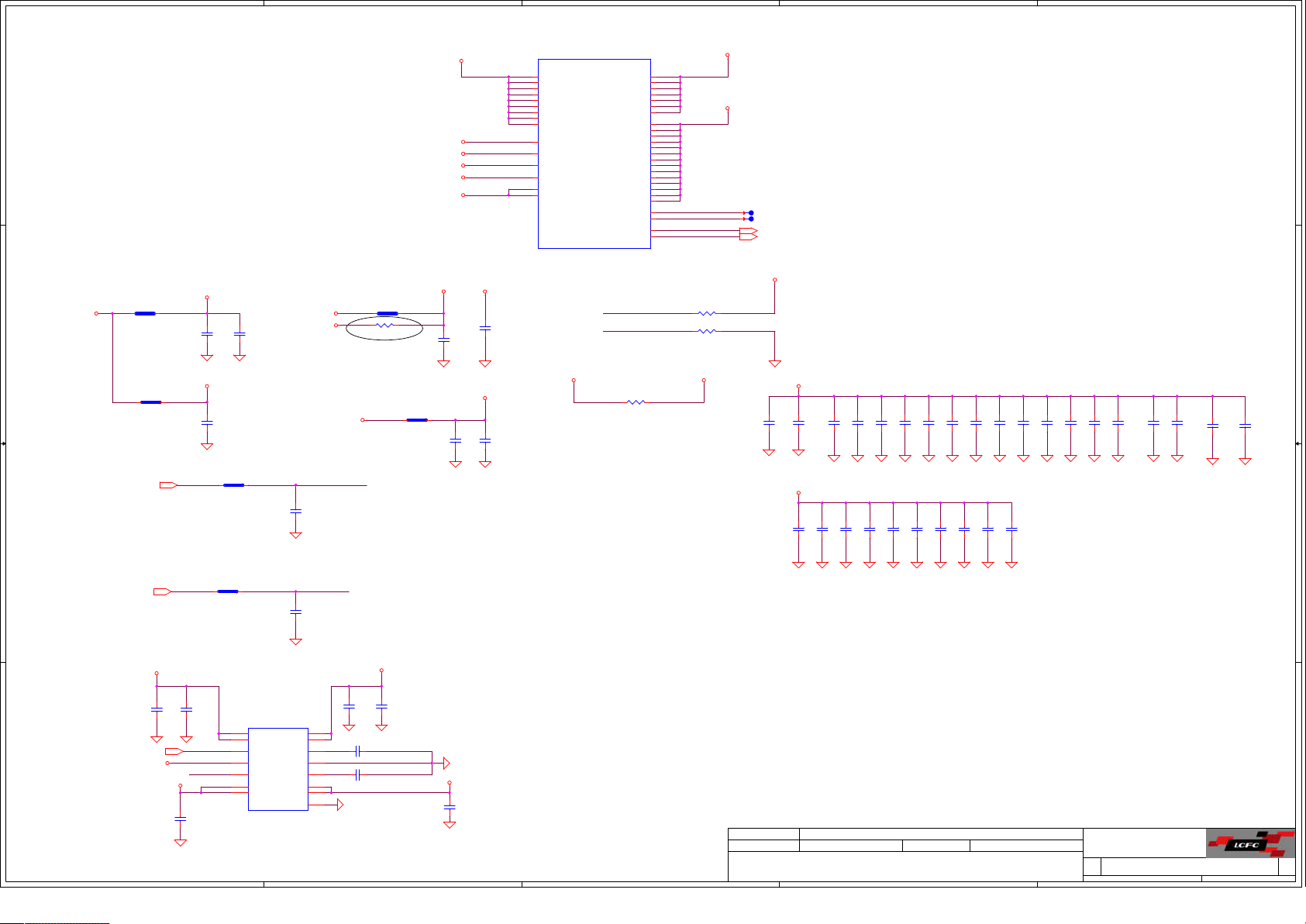

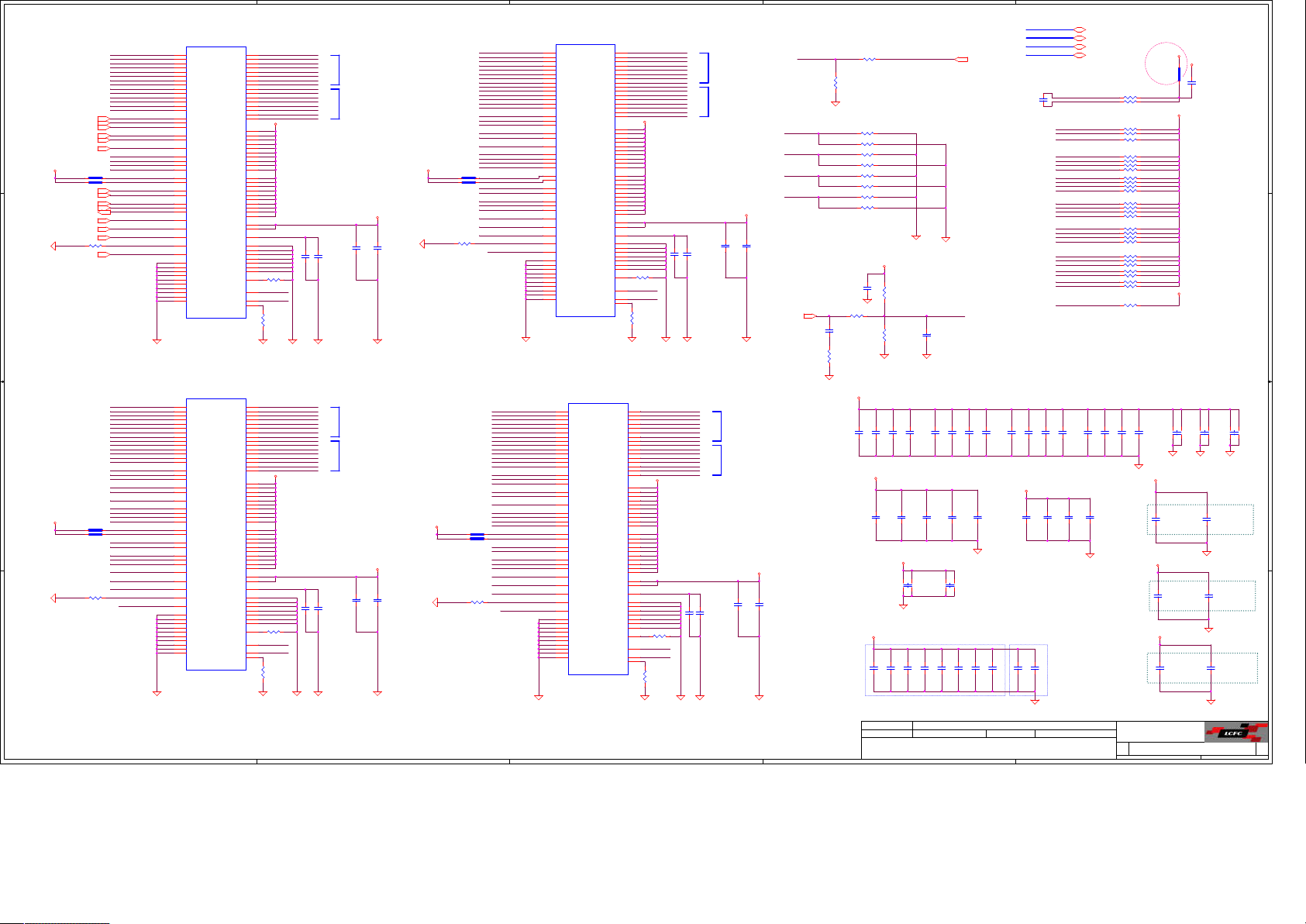

Voltage Rails

Power Plane

1 1

State

S0

S3

2 2

S3

Battery only

S5 S4

AC Only

S5 S4

Battery only

S5 S4

AC & Battery

don't exist

SMBUS Control Table

3 3

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

EC_SMB_CK3

EC_SMB_DA3

( O --> Means ON , X --> Means OFF )

+3VALW

+5VALW

V20B+

+3VALW_PCH

+1.8VALW

+1.05VALW

O

O

O

O X

O

O

O

O

O

X X

X X

SOURCE

IT8586EEC_SMB_CK1

+3VL_EC

IT8586E

IT8586E

+3VL_EC

+3VS

BATT

V

X

ChargerVDGPU

X

X

V

+3VG_AON

IT8586E

+3VL_EC

+3VS

+3VL_EC

+1.2V

+2.5V_DDR

+VCCST

Memory

Down

V

V

V

+5VS

+3VS

+VCCIO

+VCCSTG

+VCCSA

+VCC_GT

+CPU_CORE

+0.6VS

O

O

O

O

X

X

X

X

PCH

X

V

X

PMIC

X

X

X X

+3VALW_PCH

SODIMM

Thermal

Sensor

X

X

X

VX X X X X X X

STATE

Full ON

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

HSIO PORT

1

2

USB3.0

USB2.0

PCIE

WLAN

WiMAX

X

X

V

X

3

4

5

6

1

2

3

4

5

6

7

8

9

10

5~8

X4

9

10

11

12

13~16

X4

X

SIGNAL

Function

USB3.0 Conn

USB3.0 Conn

NC

NC

NC

NC

USB3.0 Conn

NC

USB3.0 Conn

USB2.0 conn

Card reader

Touch Screen

Camera

NC

NC

Bluetooth

DGPU

WLAN

NC

SATA HDD

NC

PCIE/SATA SSD

SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

ON

ON

ON

ON

ON ON ON

ON

OFF

OFF

OFF

OFF

OFFLOW LOW LOW

OFF

OFF

OFF

HIGH HIGH HIGH

LOW

HIGH

HIGH

LOWLOW

LOW

BTO ItemBOM Structure

@

14@

15@

YOGA@

530@

CD@

EMC@

EMC_15@

EMC_NS@

EMC_PX@

EMC_PXNS@

ME@

OPT@

OPTN16@

OPTN17@

TS@

TP@

UMA@

Un-stuff

For 14" part

For 15" part

For YOGA530 part

For 530S part

For C cost down

For EMC part

For EMC 15" part

For EMC un-stuff part

For EMC PX part

For EMC PX nu-stuff part

For ME part

For NV GPU part

For NV N16S-GTR GPU pa rt

For NV N17S-G1 GPU part

For touch screen part

For TOuch Pad Part

For UMA part

PCH_SMB_CLK

PCH_SMB_DATA

EC SMBus1 address

Device

Smart Battery

4 4

Charger

PCH

+3VALW_PCH

need to update

0001 0010 b

X

X

X

X

X X

EC SMBus2 address

Device

Thermal Sensor(NCT7718W)

PCH

DGPU

A

Address

1001_100xb

need to update

need to update

V

+3VALW_PCH

EC SMBus3 address

Device AddressAddress

PMIC

B

V

+3VS

need to update

X

V

+3VS

PCH SM Bus address

Device Address

DDR4 SODIMM

Wlan

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LCFUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LCFUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LCFUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFEREDFROM THE CUSTODY OF THE CO MPETENTDIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFEREDFROM THE CUSTODY OF THE CO MPETENTDIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFEREDFROM THE CUSTODY OF THE CO MPETENTDIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEETNO R THE INFORMATIONIT CO NTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEETNO R THE INFORMATIONIT CO NTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEETNO R THE INFORMATIONIT CO NTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURECENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURECENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURECENTER.

C

need to update

Reserved

2015/08/20

2015/08/20

2015/08/20

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

DecipheredDate

DecipheredDate

DecipheredDate

D

2016/08/20

2016/08/20

2016/08/20

Title

Title

Title

Notes List

Notes List

Notes List

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

GS44B/GS54B

GS44B/GS54B

GS44B/GS54B

Wednesday, May 29, 2019

Wednesday, May 29, 2019

Wednesday, May 29, 2019

3 61

3 61

E

3 61

0.1

0.1

0.1

5

https://vinafix.com

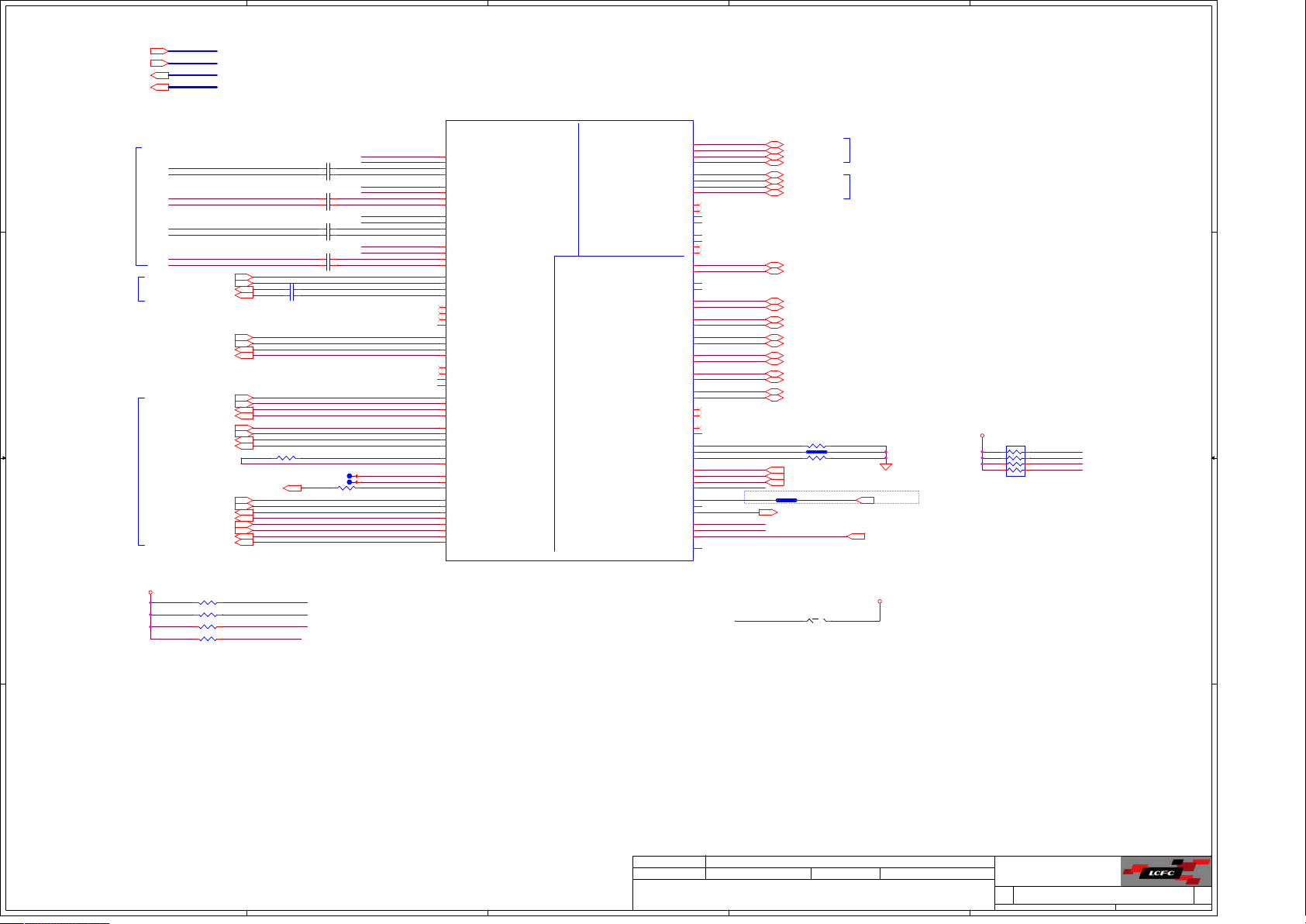

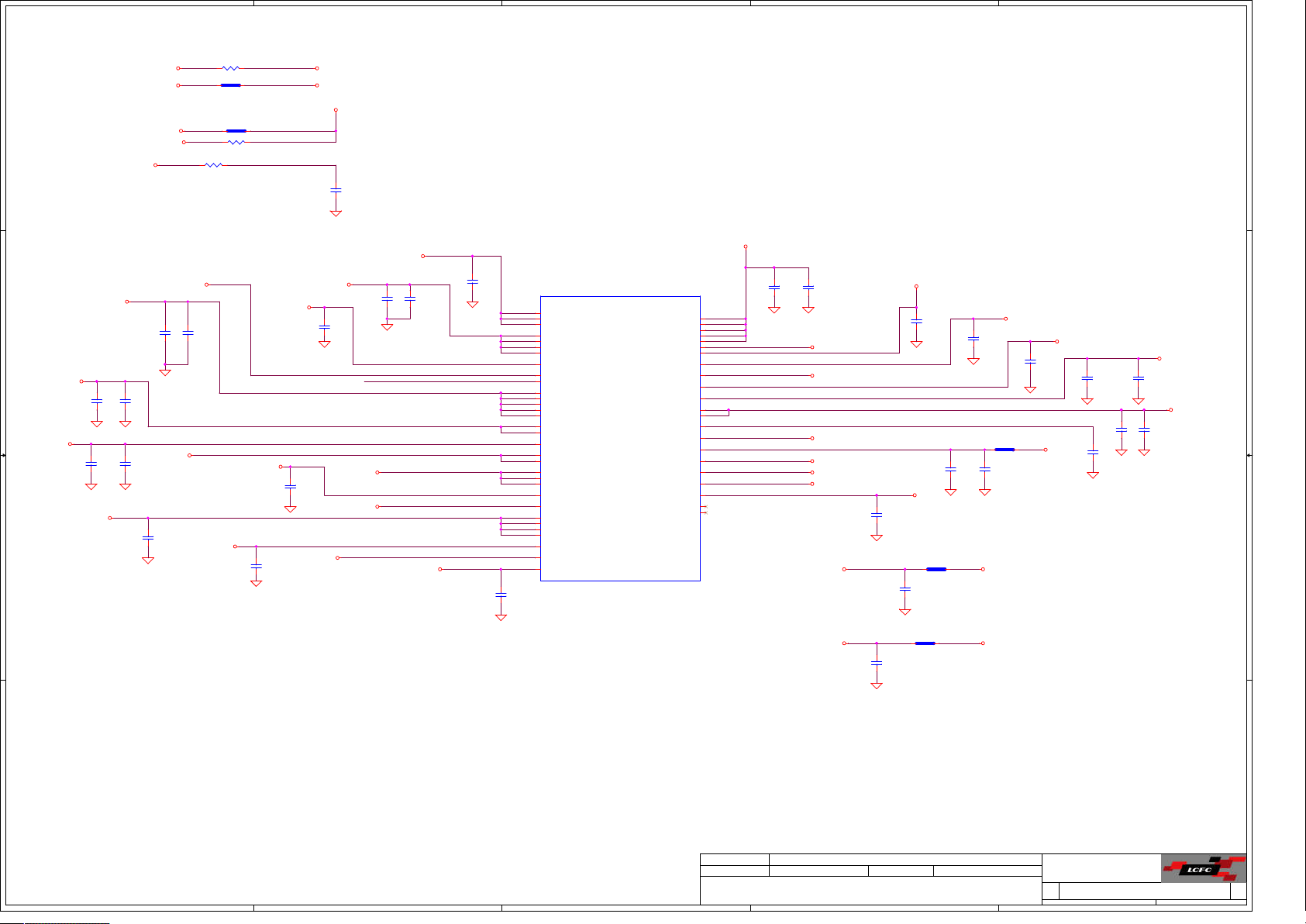

HDMI D2

HDMI D1

HDMI D0

D D

HDMI CLK

CPU_HDMI_TXN234

CPU_HDMI_TXP234

CPU_HDMI_TXN134

CPU_HDMI_TXP134

CPU_HDMI_TXN034

CPU_HDMI_TXP034

CPU_HDMI_CLKN34

CPU_HDMI_CLKP34

PCH_HDMI_DDC_CLK34

PCH_HDMI_DDC_DATA34

+3VS

2.2K_0404_4P2R_5%

+VCCIO

RPC27

1 4

2 3

RC4 24.9_0402_1%

CPU_HDMI_TXN2

CPU_HDMI_TXP2

CPU_HDMI_TXN1

CPU_HDMI_TXP1

CPU_HDMI_TXN0

CPU_HDMI_TXP0

CPU_HDMI_CLKN

CPU_HDMI_CLKP

PCH_HDMI_DDC_CLK

PCH_HDMI_DDC_DATA

PCH_HDMI_DDC_CLK

PCH_HDMI_DDC_DATA

12

+VCCIO&EDP_COMP :

Trace Width: 20mil

Isolation Spacing: 25mil

Max length: 100mil

EDP_COMP PCH_ENVDD

4

UC1A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

SKYLAKE-U_BGA1356

REV = 1

@

SKL_ULT

DDI

DISPLAY SIDEBANDS

3

?

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP

1 OF 20

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

CPU_EDP_TX0-

C47

CPU_EDP_TX0+

C46

CPU_EDP_TX1-

D46

CPU_EDP_TX1+

C45

A45

B45

A47

B47

CPU_EDP_AUX#

E45

CPU_EDP_AUX

F45

B52

G50

F50

E48

F48

G46

F46

CPU_HDMI_HPD

L9

L7

GPP_E15 GPP_E15

L6

N9

CPU_EDP_HPD

L10

PCH_ENBKL

R12

PCH_EDP_PWM

R11

U13

?

@

1 2

RC432 0_0201_5%

CPU_EDP_TX0- 33

CPU_EDP_TX0+ 33

CPU_EDP_TX1- 33

CPU_EDP_TX1+ 33

CPU_EDP_AUX# 33

CPU_EDP_AUX 33

CPU_HDMI_HPD 34

EC_SCI# 44

CPU_EDP_HPD 33

PCH_ENBKL 33,44

PCH_EDP_PWM 33

PCH_ENVDD 33

2

RC1601 10K_0201_5%

CPU_EDP_HPD

RC13 100K_0201_5%

1 2

@

1 2

1

+3VS

DDP*_CTRLDATA strapping sampled on the rising edge of PWROK

Port

Strap Enable Disable

DDPB_CTRLDATA

C C

Port 1

Port 2

DDPC_CTRLDATA

Pull up to 3.3 V

with 2.2Kohm

Pull up to 3.3 V

with 2.2Kohm

NC

NC

+VCCSTG

12

RC19

1K_0402_5%

H_PROCHOT#44,55

B B

A A

H_PECI44

+VCCST_CPU

1 2

RC20 499 +-1% 0402

12

RC143

1K_0201_5%

1 2

RC155 49.9_0402_1%

1 2

RC156 49.9_0402_1%

1 2

RC157 49.9_0402_1%U23E@

1 2

RC170 49.9_0402_1%U23E@

+VCCST_CPU

12

RC1625

49.9_0402_1%

@

CATERR#

H_PECI

H_PROCHOT#_R

H_THRMTRIP#

XDP_BPM0#

1

TC11PAD @

XDP_BPM1#

1

TC12PAD @

XDP_BPM2#

1

TC13PAD @

XDP_BPM3#

1

TC14PAD @

GPP_E3

1

TC162@PAD

PROC_OPI_RCOMP

PCH_OPI_RCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

XDP_TCK

XDP_TDO

@

1 2

RC3097 0_0201_5%

@

1 2

RC3101 0_0201_5%

XDP_TDI PCH_JTAG_TDI

@

1 2

RC3098 0_0201_5%

@

1 2

RC3099 0_0201_5%

@

1 2

RC3100 0_0201_5%

UC1D

D63

CATERR#

A54

PECI

C65

PROCHOT#

C63

THERMTRIP#

A65

SKTOCC#

C55

BPM#[0]

D55

BPM#[1]

B54

BPM#[2]

C56

BPM#[3]

A6

GPP_E3/CPU_GP0

A7

GPP_E7/CPU_GP1

BA5

GPP_B3/CPU_GP2

AY5

GPP_B4/CPU_GP3

AT16

PROC_POPIRCOMP

AU16

PCH_OPIRCOMP

H66

OPCE_RCOMP

H65

OPC_RCOMP

SKYLAKE-U_BGA1356

REV = 1

@

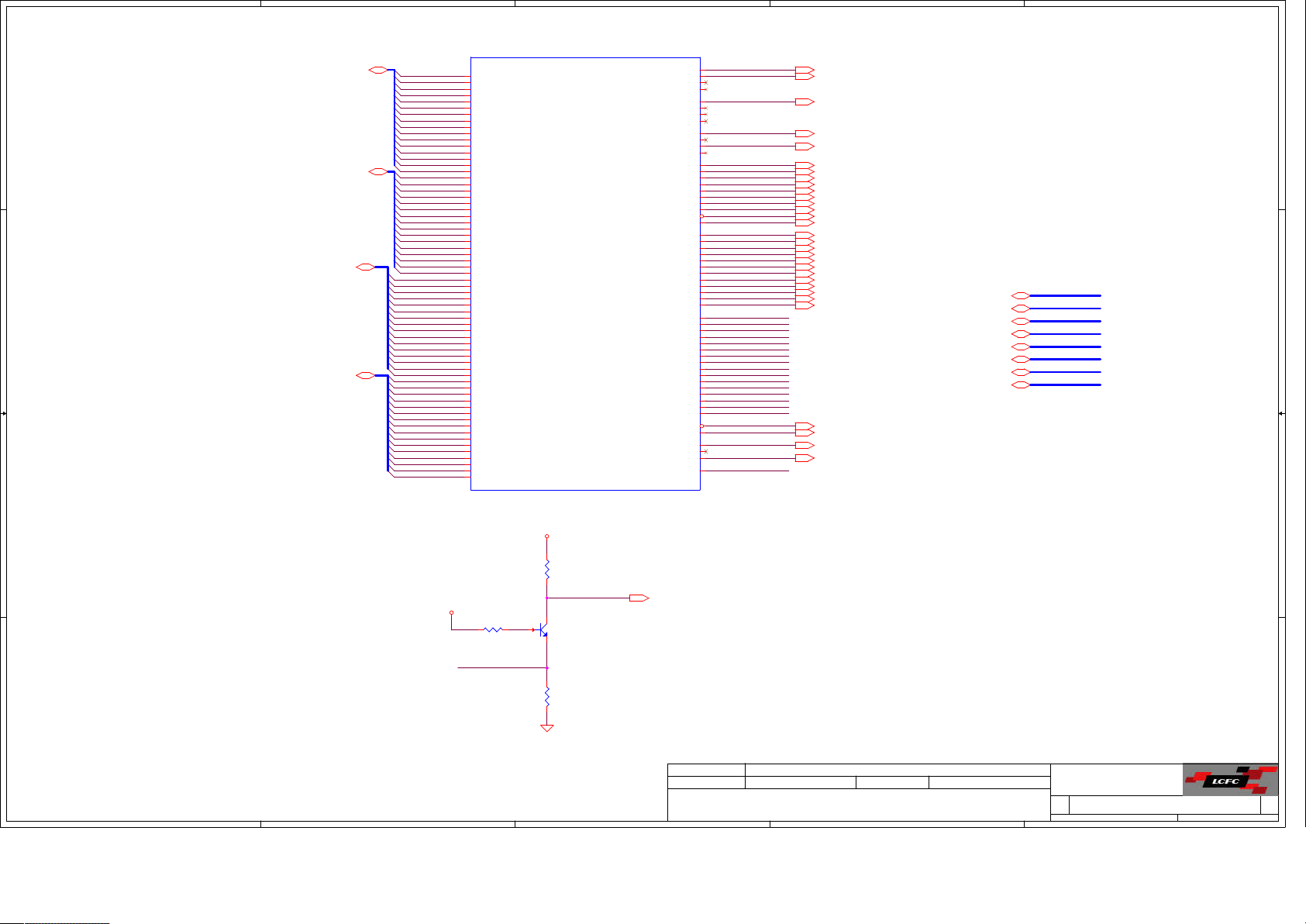

JTAGX

PCH_JTAG_TDO

?

SKL_ULT

JTAG

CPU MISC

PCH_JTAG_TCK

PCH_JTAG_TDO

PCH_JTAG_TMS

1 OF 20

1 2

RC1551 51_0402_5%

1 2

RC1543 51_0402_5%

PCH_JTAG_TMSXDP_TMS

PCH_JTAG_TRST#XDP_TRST#

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TDI

PCH_TRST#

JTAGX

?

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

+VCCSTG

XDP_TCK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

PCH_JTAG_TCK

1

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_JTAG_TRST#

JTAGX

TC29 PAD@

5

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF LC FU TURE CENTER. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF LC FU TURE CENTER. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF LC FU TURE CENTER. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THI S SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THI S SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THI S SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF LC FUTURE CENT ER.

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF LC FUTURE CENT ER.

4

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF LC FUTURE CENT ER.

3

2015/08/20 2016/08/20

2015/08/20 2016/08/20

2015/08/20 2016/08/20

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

MCP (DDI,EDP)

MCP (DDI,EDP)

MCP (DDI,EDP)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

GS44B/GS54B

GS44B/GS54B

GS44B/GS54B

Wednesday, May 29, 2019

Wednesday, May 29, 2019

Wednesday, May 29, 2019

4 60

4 60

4 60

1

1.0

1.0

1.0

5

https://vinafix.com

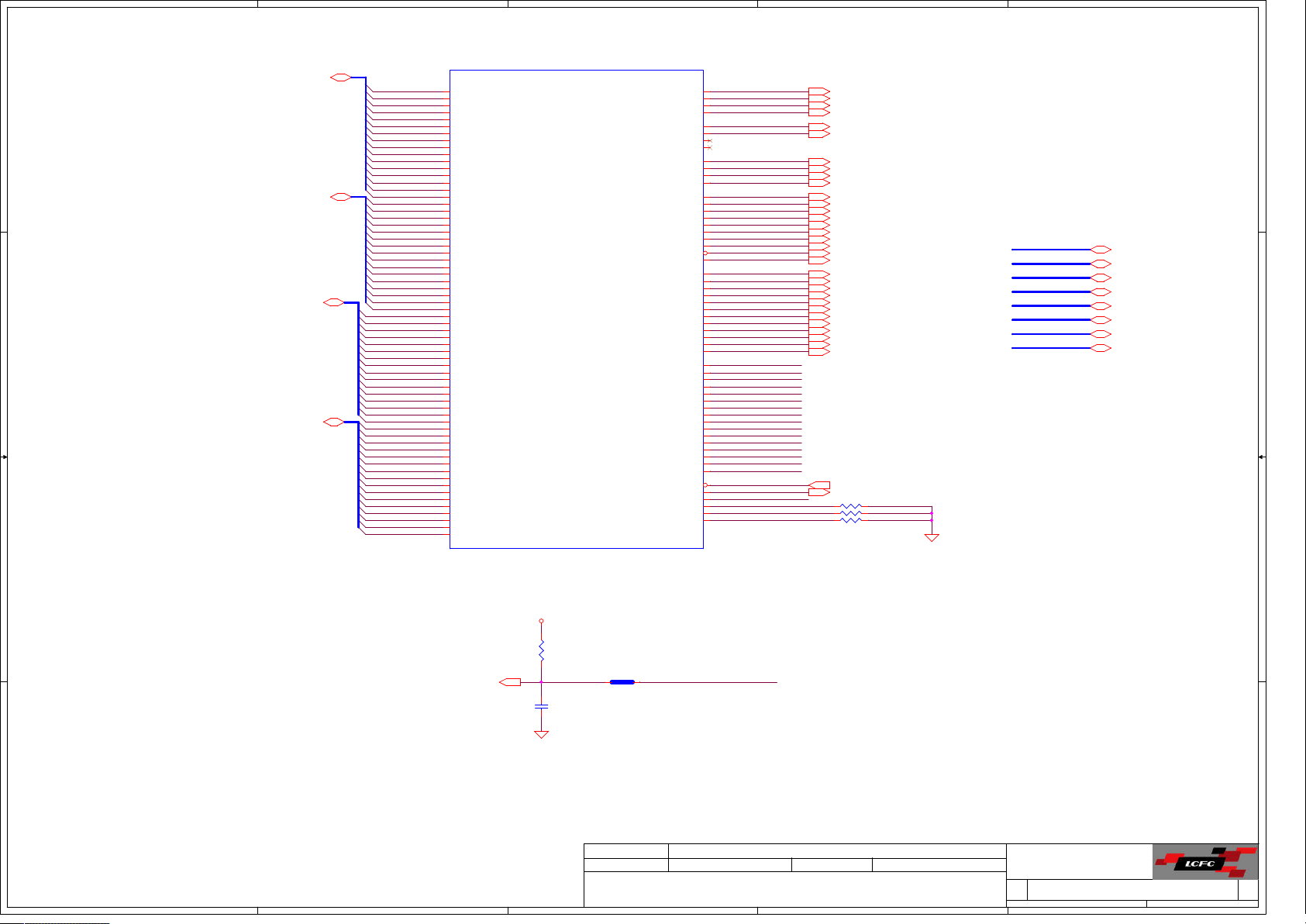

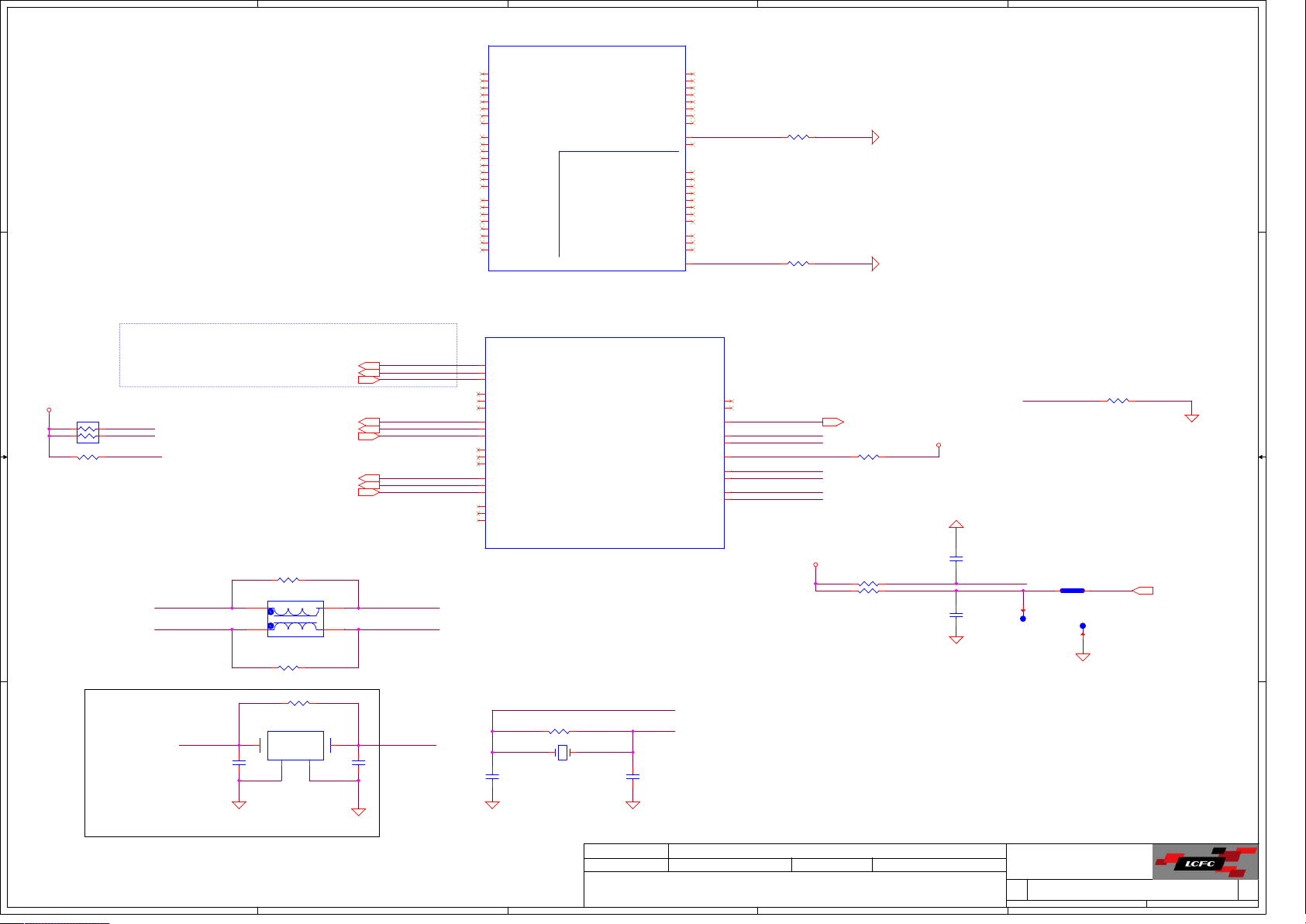

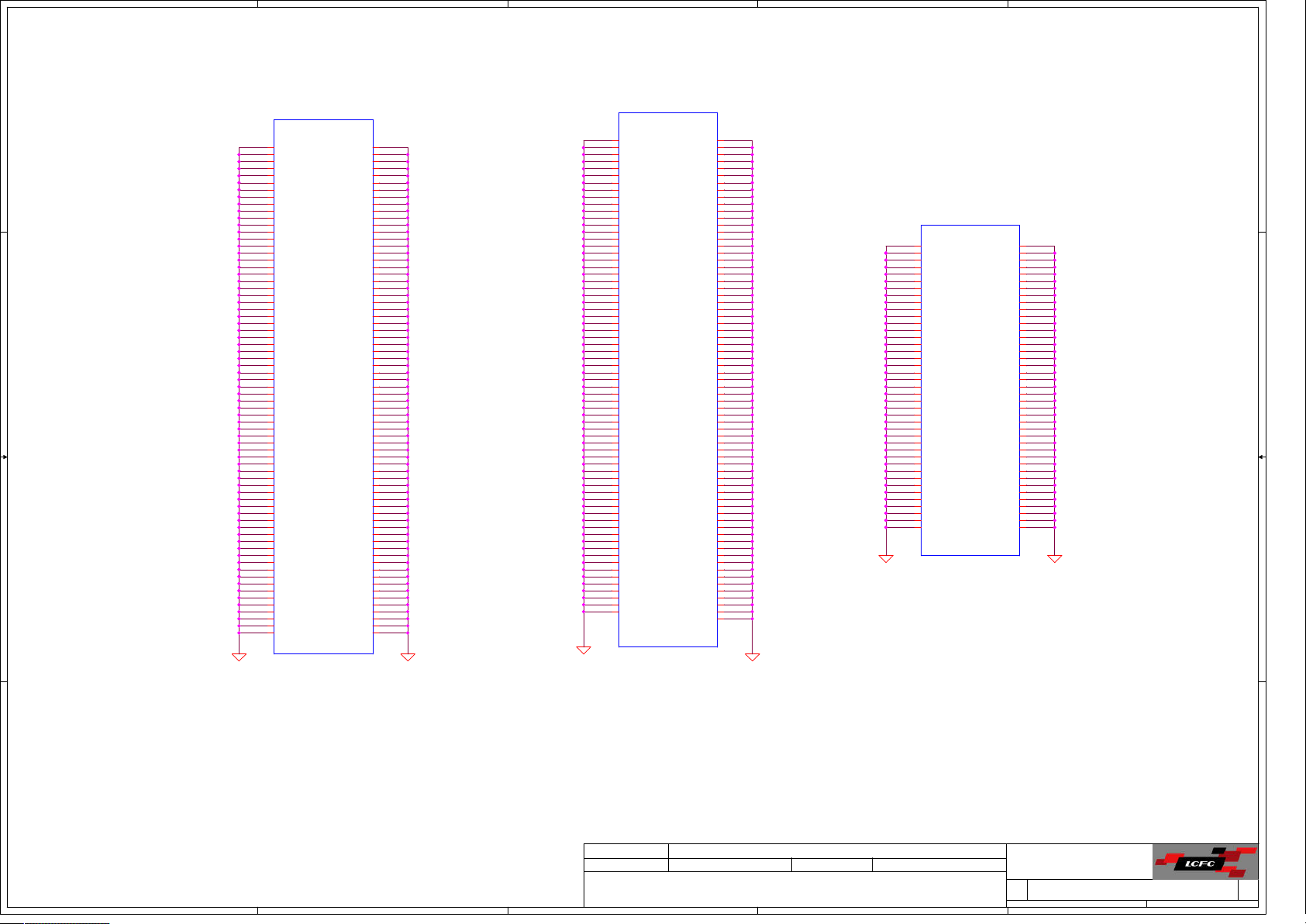

DDRA_DQ[0..15]17

D D

DDRA_DQ[32..47]17

DDRB_DQ[0..15]18

C C

DDRB_DQ[32..47 ]18

B B

4

DDRA_DQ0

DDRA_DQ1

DDRA_DQ2

DDRA_DQ3

DDRA_DQ4

DDRA_DQ5

DDRA_DQ6

DDRA_DQ7

DDRA_DQ8

DDRA_DQ9

DDRA_DQ10

DDRA_DQ11

DDRA_DQ12

DDRA_DQ13

DDRA_DQ14

DDRA_DQ15

DDRA_DQ32

DDRA_DQ33

DDRA_DQ34

DDRA_DQ35

DDRA_DQ36

DDRA_DQ37

DDRA_DQ38

DDRA_DQ39

DDRA_DQ40

DDRA_DQ41

DDRA_DQ42

DDRA_DQ43

DDRA_DQ44

DDRA_DQ45

DDRA_DQ46

DDRA_DQ47

DDRB_DQ0

DDRB_DQ1

DDRB_DQ2

DDRB_DQ3

DDRB_DQ4

DDRB_DQ5

DDRB_DQ6

DDRB_DQ7

DDRB_DQ8

DDRB_DQ9

DDRB_DQ10

DDRB_DQ11

DDRB_DQ12

DDRB_DQ13

DDRB_DQ14

DDRB_DQ15

DDRB_DQ32

DDRB_DQ33

DDRB_DQ34

DDRB_DQ35

DDRB_DQ36

DDRB_DQ37

DDRB_DQ38

DDRB_DQ39

DDRB_DQ40

DDRB_DQ41

DDRB_DQ42

DDRB_DQ43

DDRB_DQ44

DDRB_DQ45

DDRB_DQ46

DDRB_DQ47

UC1B

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

SKYLAKE-U_BGA1356

REV = 1

@

+3VALW

12

?

SKL_ULT

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR CH - A

1 OF 20

RC30

100K_0402_5%

3

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

?

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW50

AT52

AY67

AY68

BA67

AW67

DDRA_DQS#0

DDRA_DQS0

DDRA_DQS#1

DDRA_DQS1

DDRA_DQS#4

DDRA_DQS4

DDRA_DQS#5

DDRA_DQS5

DDRB_DQS#0

DDRB_DQS0

DDRB_DQS#1

DDRB_DQS1

DDRB_DQS#4

DDRB_DQS4

DDRB_DQS#5

DDRB_DQS5

DDR_SB_VREFCA

DDR_VTT_CNTL

DDRA_CLK0# 17

DDRA_CLK0 17

DDRA_CKE0 17

DDRA_CS0# 17

DDRA_ODT0 17

DDRA_MA5 17

DDRA_MA9 17

DDRA_MA6 17

DDRA_MA8 17

DDRA_MA7 17

DDRA_BG0 17

DDRA_MA12 17

DDRA_MA11 17

DDRA_ACT# 17

DDRA_BG1 17

DDRA_MA13 17

DDRA_MA15_CAS# 17

DDRA_MA14_W E# 17

DDRA_MA16_RAS# 17

DDRA_BS0# 17

DDRA_MA2 17

DDRA_BS1# 17

DDRA_MA10 17

DDRA_MA1 17

DDRA_MA0 17

DDRA_MA3 17

DDRA_MA4 17

DDRA_ALERT# 17

DDRA_PAR 17

DDR_SA_VREFCA 17

DDR_SB_VREFCA 18

2

DDRA_DQS#[0..1]17

DDRA_DQS[0..1]17

DDRA_DQS#[4..5]17

DDRA_DQS[4..5]17

DDRB_DQS#[0..1 ]18

DDRB_DQS[0..1]18

DDRB_DQS#[4..5 ]18

DDRB_DQS[4..5]18

SMVREF

WIDTH:20MIL

SPACING: 20MIL

DDRA_DQS#[0..1]

DDRA_DQS[0..1]

DDRA_DQS#[4..5]

DDRA_DQS[4..5]

DDRB_DQS#[0..1 ]

DDRB_DQS[0..1]

DDRB_DQS#[4..5 ]

DDRB_DQS[4..5]

1

+1.2V

RC3

1K_0402_5%

1 2

DDR_VTT_CNTL

A A

5

4

C

2

QC18

B

E

3 1

MMBT3904WH_SOT323-3

RC29

10K_0402_5%

@

1 2

CPU_DRAMPG_CNTL 55

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2015/08/20

2015/08/20

2015/08/20

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/08/20

2016/08/20

2016/08/20

Title

Title

Title

MCP (DDR4)

MCP (DDR4)

MCP (DDR4)

Size D ocument Number Rev

Size D ocument Number Rev

Size D ocument Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

GS44B/GS54B

GS44B/GS54B

GS44B/GS54B

Wednesday, May 29, 2019

Wednesday, May 29, 2019

Wednesday, May 29, 2019

5 60

5 60

1

5 60

1.0

1.0

1.0

5

https://vinafix.com

DDRA_DQ[16..31]17

D D

DDRA_DQ[48..63]17

DDRB_DQ[16..31]18

C C

DDRB_DQ[48..63]18

B B

4

DDRA_DQ16

DDRA_DQ17

DDRA_DQ18

DDRA_DQ19

DDRA_DQ20

DDRA_DQ21

DDRA_DQ22

DDRA_DQ23

DDRA_DQ24

DDRA_DQ25

DDRA_DQ26

DDRA_DQ27

DDRA_DQ28

DDRA_DQ29

DDRA_DQ30

DDRA_DQ31

DDRA_DQ48

DDRA_DQ49

DDRA_DQ50

DDRA_DQ51

DDRA_DQ52

DDRA_DQ53

DDRA_DQ54

DDRA_DQ55

DDRA_DQ56

DDRA_DQ57

DDRA_DQ58

DDRA_DQ59

DDRA_DQ60

DDRA_DQ61

DDRA_DQ62

DDRA_DQ63

DDRB_DQ16

DDRB_DQ17

DDRB_DQ18

DDRB_DQ19

DDRB_DQ20

DDRB_DQ21

DDRB_DQ22

DDRB_DQ23

DDRB_DQ24

DDRB_DQ25

DDRB_DQ26

DDRB_DQ27

DDRB_DQ28

DDRB_DQ29

DDRB_DQ30

DDRB_DQ31

DDRB_DQ48

DDRB_DQ49

DDRB_DQ50

DDRB_DQ51

DDRB_DQ52

DDRB_DQ53

DDRB_DQ54

DDRB_DQ55

DDRB_DQ56

DDRB_DQ57

DDRB_DQ58

DDRB_DQ59

DDRB_DQ60

DDRB_DQ61

DDRB_DQ62

DDRB_DQ63

UC1C

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKYLAKE-U_BGA1356

REV = 1

@

3

?

SKL_ULT

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT #

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_M A[15]

DDR1_WE#/DDR1_C AB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_M A[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR CH - B

1 OF 20

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

DDRA_DQS#2

AH66

DDRA_DQS2

AH65

DDRA_DQS#3

AG69

DDRA_DQS3

AG70

DDRA_DQS#6

AR66

DDRA_DQS6

AR65

DDRA_DQS#7

AR61

DDRA_DQS7

AR60

DDRB_DQS#2

AT38

DDRB_DQS2

AR38

DDRB_DQS#3

AT32

DDRB_DQS3

AR32

DDRB_DQS#6

AR25

DDRB_DQS6

AR27

DDRB_DQS#7

AR22

DDRB_DQS7

AR21

AN43

AP43

DDR1_PAR

CPU_DRAMRST#_R

AT13

SM_RCOMP_0

AR18

SM_RCOMP_1

AT18

SM_RCOMP_2

AU18

according PDG P105: RCOMP[0] value for SDP is 200+/1% ohm, and for DDP is 121+/- 1% ohm

?

RC24 121_0402_1%

RC25 80.6_0402_1%

RC26 100_0402_1%

DDRB_CLK0# 18

DDRB_CLK1# 18

DDRB_CLK0 18

DDRB_CLK1 18

DDRB_CKE0 18

DDRB_CKE1 18

DDRB_CS0# 18

DDRB_CS1# 18

DDRB_ODT0 18

DDRB_ODT1 18

DDRB_MA5 18

DDRB_MA9 18

DDRB_MA6 18

DDRB_MA8 18

DDRB_MA7 18

DDRB_BG0 18

DDRB_MA12 18

DDRB_MA11 18

DDRB_ACT# 18

DDRB_BG1 18

DDRB_MA13 18

DDRB_MA15_CAS# 18

DDRB_MA14_WE# 18

DDRB_MA16_RAS# 18

DDRB_BS0# 18

DDRB_MA2 18

DDRB_BS1# 18

DDRB_MA10 18

DDRB_MA1 18

DDRB_MA0 18

DDRB_MA3 18

DDRB_MA4 18

DDRB_ALERT# 18

DDRB_PAR 18

1 2

1 2

1 2

2

DDRA_DQS#[2..3]

DDRA_DQS[2..3]

DDRA_DQS#[6..7]

DDRA_DQS[6..7]

DDRB_DQS#[2..3]

DDRB_DQS[2..3]

DDRB_DQS#[6..7]

DDRB_DQS[6..7]

1

DDRA_DQS#[2..3] 17

DDRA_DQS[2..3] 17

DDRA_DQS#[6..7] 17

DDRA_DQS[6..7] 17

DDRB_DQS#[2..3] 18

DDRB_DQS[2..3] 18

DDRB_DQS#[6..7] 18

DDRB_DQS[6..7] 18

+1.2V

12

RC22

470_0402_5%

@

Issued Date

Issued Date

Issued Date

12

3

CPU_DRAMRST#17,18

A A

5

4

RC23 0_0402_5%

1

CC1

0.01U_0201_25V6-K

EMC_NS@

2

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

CPU_DRAMRST#_R

2015/08/20

2015/08/20

2015/08/20

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/08/20

2016/08/20

2016/08/20

Title

Title

Title

MCP (DDR4)

MCP (DDR4)

MCP (DDR4)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wednesday, May 29, 2019

Wednesday, May 29, 2019

Wednesday, May 29, 2019

GS44B/GS54B

GS44B/GS54B

GS44B/GS54B

1

6 60

6 60

6 60

1.0

1.0

1.0

5

Vinafix.com

https://vinafix.com

4

3

2

1

SPI_CLK44

SPI_SO44

SPI_SI44

SPI_CS0#44

D D

C C

B B

SPI_CLK SPI_CLK_R

SPI_SO

SPI_SI

SPI_CS0# SPI_CS0#_R

RC1154 100K_0201_5%

+3V_SPI

1. If support DS3, connect to+3VS and don't support EC mirror code;

2. If don't support DS3, connect to +3VALW_PCH and support EC mirror code.

*

SPI_WP#_R

SPI_HOLD#_R

Check with BIOS, SPI is Dual mode or quad mode

SPI_CS0#

SPI_SO

SPI_WP#

1 2

RC703 15_0402_5%

1 2

RC701 15_0402_5%

1 2

RC702 15_0402_5%

1 2

RC704 0_0402_5%@

1 2

@

1

@

CC717

12P_0201_25V8-J

2

+3VALW

RC3102 0_0402_5%@

1 2

D2201 RB520CM-30T2R_VMN2M2

@

1 2

RC54 15_0402_5%

1 2

RC55 15_0402_5%

UC3

1

/CS

2

DO (IO1)

3

IO2

GND4DI (IO0)

W25Q64JVSSIQ_SO8

SPI_CLK_R

12

1K_0402_5%

VCC

IO3

CLK

12

RC61

1K_0402_5%

SPI_CS2#_R32

BOARD_ID88

BOARD_ID48

TPM_SPI_IRQ#32

SPI_WP#

SPI_HOLD#

+3V_SPI

SPI_CLK_R 32

SPI_SO_R 32

SPI_SI_R 32

KBRST#44

SERIRQ44

1

CC8

0.1u_0201_10V6K

2

SPI_SO_R

SPI_SI_R

+3V_SPI

+3V_SPI

12

RC60

8

SPI_HOLD#

7

SPI_CLK

6

SPI_SI

5

SPI_CLK_R

SPI_SO_R

SPI_SI_R

SPI_WP#_R

SPI_HOLD#_R

SPI_CS0#_R

SPI_CS2#_R

KBRST#

SERIRQ

RC3122

+3VALW_PCH

1 2

TPM1@

0_0402_5%

RC3088

100K_0201_5%

@

1 2

AV2

AW3

AV3

AW2

AU4

AU3

AU2

AU1

AW13

AY11

UC1E

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

M2

GPP_D1/SPI1_CLK

M3

GPP_D2/SPI1_MISO

J4

GPP_D3/SPI1_MOSI

V1

GPP_D21/SPI1_IO2

V2

GPP_D22/SPI1_IO3

M1

GPP_D0/SPI1_CS#

G3

CL_CLK

G2

CL_DATA

G1

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

SKYLAKE-U_BGA1356

REV = 1

@

SPI - FLASH

SPI - TOUCH

C LINK

RPC30

2.2K_0404_4P2R_5%

PCH_SML1_CLK

PCH_SML1_DAT

?

SKL_ULT

SMBUS, SMLINK

GPP_C5/SML0ALERT#

GPP_B23/SML1ALERT#/PCHHOT#

LPC

1 OF 20

check CLKRUN# / SUS_STAT# signal if need to connect

PM_CLKRUN#

SERIRQ

KBRST#

KBRST#

+3VALW_PCH

1 4

2 3

1 2

RC11 8.2K_0402_5%

1 4

2 3

1 2

CC1255 1000P_0201_50V7-K

EMC_NS@

QC10A

2N7002KDWH_SOT363-6

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

RP3402

10K_0404_4P2R_5%

+3VS

2

G

6 1

S

D

@

3 4

QC10B

2N7002KDWH_SOT363-6

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_A8/CLKRUN#

5

G

S

D

@

+3VS

+3VALW_PCH +3VS +3VS

PCH_SMB_CLK

R7

PCH_SMB_DATA

R8

SMB_ALERT#

R10

SML0_CLK

R9

SML0_DATA

W2

SML0_ALERT#

W1

PCH_SML1_CLK

W3

PCH_SML1_DAT

V3

SML1_ALERT#

AM7

LPC_AD0

AY13

LPC_AD1

BA13

LPC_AD2

BB13

LPC_AD3

AY12

BA12

BA11

CLK_PCI_EC_R

AW9

AY9

PM_CLKRUN#

AW11

?

DIMM, NGFF

GPU, EC, Thermal Sensor

1 2

RE4418 0_0402_5%@

1 2

RE4424 0_0402_5%@

1 2

RE4419 0_0402_5%@

1 2

RE4420 0_0402_5%@

RC173 22_0402_5%

EC_SMB_CK2 26,39,44

EC_SMB_DA2 26,39,44

LPC_AD0_EC 44

LPC_AD1_EC 44

LPC_AD2_EC 44

LPC_FRAME# 44

12

LPC_AD3_EC 44

LPC R/C close to PCH

SML1_ALERT#44

RPC1

2.2K_0404_4P2R_5%

PCH_SMB_CLK

PCH_SMB_DATA

CLK_PCI_EC 44

SMB_ALERT#

SML0_CLK

SML0_DATA

SML0_ALERT#

This signal has a weak internal pull-down.

0 = LPC Is selected for EC. (Default)

1 = eSPI Is selected for EC.

Notes:

1. The internal pull-down is disabled after RSMRST#

de-asserts.

2. This signal is in the primary wel

Rising edge of RSMRST#

SML1_ALERT#

To enable Direct Connect Interface (DCI), a 150Kpull up resistor will need to be

added to PCHHOT# pin. This pin must be low during ther ising edgeof RSMRST#.

(Refer to WW52_MOW)

1 4

2 3

LPC_AD3_EC

CE4432 27P_0402_50V8J EMC_NS@

LPC_AD2_EC

CE4428 27P_0402_50V8J EMC_NS@

LPC_AD1_EC

CE4429 27P_0402_50V8J EMC_NS@

LPC_AD0_EC

CE4430 27P_0402_50V8J EMC_NS@

CLK_PCI_EC

CE4431 27P_0402_50V8J EMC_NS@

1 4

2 3

2.2K_0404_4P2R_5%

2

RC1564 2.2K_0402_5%@

1 2

RC1569 150K_0402_5%

1 2

RC1655 150K_0402_5%

6 1

QC2A

2N7002KDWH_SOT363-6

1 2

1 2

1 2

1 2

1 2

12

RC15622.2K_0402_5%

RPC29

1

@

2

G

S

D

QC2B

2N7002KDWH_SOT363-6

+3VALW_PCH

+3VALW_PCH

5

3 4

D

RPC24

2.2K_0404_4P2R_5%

1 4

2 3

SMB_CLK_S3 18,40

G

S

SMB_DATA_S3 18,40

+3VS

A A

Title

Title

Title

MCP (MISC,JTAG,SPI,LPC,SM B)

MCP (MISC,JTAG,SPI,LPC,SM B)

MCP (MISC,JTAG,SPI,LPC,SM B)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

GS44B/GS54B

GS44B/GS54B

GS44B/GS54B

Wednesday, May 29, 2019

Wednesday, May 29, 2019

Wednesday, May 29, 2019

7 60

7 60

1

7 60

1.0

1.0

1.0

5

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONT AINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONT AINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONT AINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. TH IS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

AND TRADE SECRET INFORMATION. TH IS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

AND TRADE SECRET INFORMATION. TH IS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUT URE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUT URE CENTER.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUT URE CENTER.

3

2015/08/20

2015/08/20

2015/08/20

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/08/20

2016/08/20

2016/08/20

5

https://vinafix.com

4

3

2

1

+3VS

RC1559 10K_0402_5%OPT@

RC1641 10K_0402_5%

RC1557 10K_0402_5%OPT@

D D

C C

B B

CC1259 0.01U_0201_10V6K

RC1558 10K_0201_5%UMA@

+3VS

1 4

2 3

2.2K_0404_4P2R_5%

+3VALW

+3VS

*

HDA_SDO This signal has a weak internal pull-down.

0 = Enable security measures defined in the Flash Descriptor.

1 = Disable Flash Descriptor Security(override). This strap

should only be asserted high during external pull-up in

manufacturing/debug environments ONLY.

1

10P_0201_50V8F

2

HDA_SDOUT_AUDIO30

ME_FLASH44

+3VS

RC14 2.2K_0402_5%

12

1 2

@

1 2

1 2

OPT@

DGPU_PWROK

@UMA SKU

1 2

RPC28

PCH_I2C_SCL0

PCH_I2C_SDA0

RC1658

PCH_TP_INT#

12

10K_0402_5%

1 2

RC1600 1K_0402_5%

@

1 2

RC47 1K_0402_5%

@

For EMI

HDA_SDIN0

CC7

EMC_NS@

1 2

@

RC3113

12

@

10K_0402_5%

Pin Name Strap Description Configuration

SPKR /

Top Swap

GPP_B14

Override

GSPI0_MOSI

No Reboot

/GPP_B18

A A

GSPI1_MOSI

/GPP_B22

Boot BIOS

Strap Bit

BBS

PXS_PWREN_R

PXS_RST#_R

Reserve for GPU sequence

PXS_RST#_R

PXS_RST#

DGPU_PWROK 23,57

DGPU_PWROK

Touch PAD

HDA_SDOUT

For EMI

1

CC4220

56P_50V_J_NPO_0201

2

EMC@

Close to PCH

RC45 33_0201_5%

1 2

RC3104 0_0402_5%@

PCH_BEEP

PCH_TS_IRQ

Internal PD

0 = Disable “Top Swap”

mode. (Default)

1 = Enable “Top Swap”

mode.

Internal PD

0 = Disable “No Reboot”

mode. (Default)

1 = Enable “No Reboot”

mode

Internal PD

0 = SPI (Default)

1 = LPC

RC804 0_0402_5%@

HDA_BCLK

12

12

RC71K_0201_5% OPT@

1 2

+3VS

UART_RX_DEBUG40

UART_TX_DEBUG40

TP_I2C_SDA045

TP_I2C_SCL045

RC42&RC43&RC45 due to nolink CIS,

cant choose the Component,so choose one instead the location

SD00000LH8J, S RES 1/20W 33 +-5% 0201

changed the VALUE and LCFC PN for BOM

HDA_SYNC_AUDIO30

HDA_BITCLK_AUDIO30

HDA_SDIN030

CC4220 for EMC demand,due to nolink CIS,

cant choose the Component,so choose one instead the location

or change x5r&x7r if suit,sutff

SE00001AF00, S CER CAP 56P 50V J NPO 0201

HDA_SDOUT

Default

Value

0*Rising edge

0

*

0

*

PXS_PWREN 23

PXS_RST# 26

1 2

RC1561 2.2K_0402_5%

@

1 2

RC1563 2.2K_0402_5%

@

1 2

RC831 0_0402_5%@

1 2

RC3103 0_0402_5%@

RC43 33_0201_5%

RC42 33_0201_5%

PCH_BEEP30

When

Sampled

of PCH_PWROK

Rising edge

of PCH_PWROK

Rising edge

of PCH_PWROK

@OPT&GC6 Only for NV GPU SKU

+3VS

GPP_B18

GPP_B22

UART_RX_DEBUG

UART_TX_DEBUG

PXS_PWREN_R

PXS_RST#_R

DGPU_PWROK

FB_GC6_EN_R

12

12

PAD @

PCH_I2C_SDA0

PCH_I2C_SCL0

BOARD_ID7

@

1 2

RC1629 10K_0402_5%

1 2

RC1630 10K_0201_5%GC6@

1 2

RC1637 10K_0402_5%

@

1 2

RC1638 10K_0201_5%

@

UC1F

AN8

GPP_B15/GSPI0_CS#

AP7

GPP_B16/GSPI0_CLK

AP8

GPP_B17/GSPI0_MISO

AR7

GPP_B18/GSPI0_MOSI

AM5

GPP_B19/GSPI1_CS#

AN7

GPP_B20/GSPI1_CLK

AP5

GPP_B21/GSPI1_MISO

AN5

GPP_B22/GSPI1_MOSI

AB1

GPP_C8/UART0_RXD

AB2

GPP_C9/UART0_TXD

W4

GPP_C10/UART0_RTS#

AB3

GPP_C11/UART0_CTS#

AD1

GPP_C20/UART2_RXD

AD2

GPP_C21/UART2_TXD

AD3

GPP_C22/UART2_RTS#

AD4

GPP_C23/UART2_CTS#

U7

GPP_C16/I2C0_SDA

U6

GPP_C17/I2C0_SCL

U8

GPP_C18/I2C1_SDA

U9

GPP_C19/I2C1_SCL

AH9

GPP_F4/I2C2_SDA

AH10

GPP_F5/I2C2_SCL

AH11

GPP_F6/I2C3_SDA

AH12

GPP_F7/I2C3_SCL

AF11

GPP_F8/I2C4_SDA

AF12

GPP_F9/I2C4_SCL

SKYLAKE-U_BGA1356

REV = 1

@

HDA_SYNC

BA22

HDA_BCLK

ME_FLASH

TC808

1

AY22

BB22

BA21

AY21

AW22

J5

AY20

AW20

AK7

AK6

AK9

AK10

H5

D7

D8

C8

AW5

SKYLAKE-U_BGA1356

REV = 1

@

RC3108

10K_0402_5%

2

HDA_SDOUT

HDA_SDIN0

PCH_BEEP

FB_GC6_EN_R

GPU_EVENT#

FB_GC6_EN_R

GPU_EVENT#

LPSS ISH

UC1G

AUDIO

HDA_SYNC/I2S0_SFRM

HDA_BLK/I2S0_SCLK

HDA_SDO/I2S0_TXD

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_RST#/I2S1_SCLK

GPP_D23/I2S_MCLK

I2S1_SFRM

I2S1_TXD

GPP_F1/I2S2_SFRM

GPP_F0/I2S2_SCLK

GPP_F2/I2S2_TXD

GPP_F3/I2S2_RXD

GPP_D19/DMIC_CLK0

GPP_D20/DMIC_DATA0

GPP_D17/DMIC_CLK1

GPP_D18/DMIC_DATA1

GPP_B14/SPKR

+3VALW_PCH

1 2

13

D

Q4610

G

S

SKL_ULT

HDA18@

ME_FLASH#

L2N7002KWT1G_SOT323-3HDA18@

FB_GC6_EN_R 23,26

GPU_EVENT# 26

?

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

GPP_A12/BM_BUSY#/ISH_GP6

1 OF 20

SKL_ULT

?

SDIO/SDXC

GPP_A17/SD_PWR_EN#/ISH_GP7

1 OF 20

+1.8VALW

RC834

HDA18@

4.7K_0402_5%

1 2

HDA_SDOUT

13

D

Q4609

2

G

S

L2N7002KWT1G_SOT323-3HDA18@

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_D15/ISH_UART0_RTS#

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A16/SD_1P8_SEL

SD_RCOMP

GPP_F23

?

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

AF13

?

P2

P3

P4

P1

M4

N3

N1

N2

AD11

AD12

U1

U2

PCH_WLAN_OFF#

U3

PCH_BT_OFF#

U4

PCH_TS_IRQ

AC1

PCH_TS_RST#

AC2

GPU_EVENT#

AC3

PCH_TP_INT#

AB4

AY8

BOARD_ID6

BA8

BOARD_ID5

BB7

AOAC_ON#

BA7

AY7

AW7

AP13

SD_RCOMP

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

12

RC49

200_0402_1%

PCH_WLAN_OFF# 40

PCH_BT_OFF# 40

RC3114

10K_0402_5%

PCH_TP_INT# 45

AOAC_ON# 40

BOARD_ID47

BOARD_ID87

@

12

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

BOARD_ID5

BOARD_ID6

BOARD_ID7

BOARD_ID8

+3VS

@

@

@

OPT@

OPTN17@

RC807

UMA@

RC826

RC809

RC808

1 2

1 2

10K_0201_5%

10K_0201_5%

@

RC818

RC819

1 2

1 2

10K_0201_5% UMAorN16@

10K_0201_5%

@

RC810

RC811

RC805

1 2

1 2

1 2

1 2

10K_0201_5%

10K_0201_5%

10K_0201_5%

10K_0201_5%

@

@

@

RC820

RC822

RC821

1 2

1 2

10K_0201_5%

1 2

1 2

10K_0201_5%

10K_0201_5%

10K_0201_5%

15@

@

17@

RC814

RC812

RC3062

1 2

1 2

1 2

10K_0201_5%

10K_0201_5%

10K_0201_5%

14or15@

14or17@

@

RC824

RC823

RC3064

1 2

1 2

1 2

10K_0201_5%

10K_0201_5%

10K_0201_5%

5

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF LC FU TURE CENTER. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF LC FU TURE CENTER. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF LC FU TURE CENTER. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THI S SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THI S SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THI S SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF LC FUTURE CENT ER.

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF LC FUTURE CENT ER.

4

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF LC FUTURE CENT ER.

3

2015/08/20 2016/08/20

2015/08/20 2016/08/20

2015/08/20 2016/08/20

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

MCP (LPSS,ISH,AUDIO,SDI O)

MCP (LPSS,ISH,AUDIO,SDI O)

MCP (LPSS,ISH,AUDIO,SDI O)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

GS44B/GS54B

GS44B/GS54B

GS44B/GS54B

Wednesday, May 29, 2019

Wednesday, May 29, 2019

Wednesday, May 29, 2019

8 60

8 60

1

8 60

1.0

1.0

1.0

5

Vinafix.com

https://vinafix.com

PCIE_CRX_GTX_N[5..8]20

PCIE_CRX_GTX_P[5..8]20

PCIE_CTX_C_GRX_N[5..8]20

PCIE_CTX_C_GRX_P[5..8]20

D D

PCIE_CTX_C_GRX_N5

PCIE_CTX_C_GRX_P5

PCIE_CTX_C_GRX_N6

DGPU

WLAN

C C

HDD

SSD

B B

PCIE_CTX_C_GRX_P6

PCIE_CTX_C_GRX_N7

PCIE_CTX_C_GRX_P7

PCIE_CTX_C_GRX_N8

PCIE_CTX_C_GRX_P8

PCIE_PRX_DTX_N940

PCIE_PRX_DTX_P940

PCIE_PTX_C_DRX_N940

PCIE_PTX_C_DRX_P940

SATA_PRX_DTX_N038

SATA_PRX_DTX_P038

SATA_PTX_DRX_N038

SATA_PTX_DRX_P038

PCIE_PRX_DTX_N1337

PCIE_PRX_DTX_P1337

PCIE_PTX_DRX_N1337

PCIE_PTX_DRX_P1337

PCIE_PRX_DTX_N1437

PCIE_PRX_DTX_P1437

PCIE_PTX_DRX_N1437

PCIE_PTX_DRX_P1437

PCIE_RCOMPN and PCIE_RCOMPP

Trace Width: 12-15mil

Differential between RCOMPP/RCOMPN

PCIE_PRX_DTX_N1537

PCIE_PRX_DTX_P1537

PCIE_PTX_DRX_N1537

PCIE_PTX_DRX_P1537

PCIE_PRX_DTX_N1637

PCIE_PRX_DTX_P1637

PCIE_PTX_DRX_N1637

PCIE_PTX_DRX_P1637

+3VS

1 2

RC3115 10K_0402_5%

1 2

RC3116 10K_0402_5%

1 2

RC3117 10K_0402_5%

1 2

RC3118 10K_0402_5%@

CC1264 0.1u_0201_10V6K

CC1263 0.1u_0201_10V6K

1 2

RC119 100_0402_1%

TPM_SPI_IRQ#32

SSD_PCIE_DET#

1 2

1 2

PIRQA#

SATA0GP

SSD_1_PCIE_DET#

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

RC1541

TC20PAD @

TC19PAD @

1 2

TPM@

0_0402_5%

CC160.22U_0201_6.3V6-K OPT@

CC140.22U_0201_6.3V6-K OPT@

CC150.22U_0201_6.3V6-K OPT@

CC170.22U_0201_6.3V6-K OPT@

CC180.22U_0201_6.3V6-K OPT@

CC190.22U_0201_6.3V6-K OPT@

CC200.22U_0201_6.3V6-K OPT@

CC210.22U_0201_6.3V6-K OPT@

4

PCIE_CRX_GTX_N5

PCIE_CRX_GTX_P5

PCIE_CTX_GRX_N5

PCIE_CTX_GRX_P5

PCIE_CRX_GTX_N6

PCIE_CRX_GTX_P6

PCIE_CTX_GRX_N6

PCIE_CTX_GRX_P6

PCIE_CRX_GTX_N7

PCIE_CRX_GTX_P7

PCIE_CTX_GRX_N7

PCIE_CTX_GRX_P7

PCIE_CRX_GTX_N8

PCIE_CRX_GTX_P8

PCIE_CTX_GRX_N8

PCIE_CTX_GRX_P8

PCIE_PRX_DTX_N9

PCIE_PRX_DTX_P9

PCIE_PTX_DRX_N9

PCIE_PTX_DRX_P9

SATA_PRX_DTX_N0

SATA_PRX_DTX_P0

SATA_PTX_DRX_N0

SATA_PTX_DRX_P0

PCIE_PRX_DTX_N13

PCIE_PRX_DTX_P13

PCIE_PTX_DRX_N13

PCIE_PTX_DRX_P13

PCIE_PRX_DTX_N14

PCIE_PRX_DTX_P14

PCIE_PTX_DRX_N14

PCIE_PTX_DRX_P14

PCIE_RCOMPN

PCIE_RCOMPP

XDP_PRDY#

1

XDP_PREQ#

1

PIRQA#

PCIE_PRX_DTX_N15

PCIE_PRX_DTX_P15

PCIE_PTX_DRX_N15

PCIE_PTX_DRX_P15

PCIE_PRX_DTX_N16

PCIE_PRX_DTX_P16

PCIE_PTX_DRX_N16

PCIE_PTX_DRX_P16

UC1H

PCIE/USB3/SATA

H13

PCIE1_RXN/USB3_5_RXN

G13

PCIE1_RXP/USB3_5_RXP

B17

PCIE1_TXN/USB3_5_TXN

A17

PCIE1_TXP/USB3_5_TXP

G11

PCIE2_RXN/USB3_6_RXN

F11

PCIE2_RXP/USB3_6_RXP

D16

PCIE2_TXN/USB3_6_TXN

C16

PCIE2_TXP/USB3_6_TXP

H16

PCIE3_RXN

G16

PCIE3_RXP

D17

PCIE3_TXN

C17

PCIE3_TXP

G15

PCIE4_RXN

F15

PCIE4_RXP

B19

PCIE4_TXN

A19

PCIE4_TXP

F16

PCIE5_RXN

E16

PCIE5_RXP

C19

PCIE5_TXN

D19

PCIE5_TXP

G18

PCIE6_RXN

F18

PCIE6_RXP

D20

PCIE6_TXN

C20

PCIE6_TXP

F20

PCIE7_RXN/SATA0_RXN

E20

PCIE7_RXP/SATA0_RXP

B21

PCIE7_TXN/SATA0_TXN

A21

PCIE7_TXP/SATA0_TXP

G21

PCIE8_RXN/SATA1A_RXN

F21

PCIE8_RXP/SATA1A_RXP

D21

PCIE8_TXN/SATA1A_TXN

C21

PCIE8_TXP/SATA1A_TXP

E22

PCIE9_RXN

E23

PCIE9_RXP

B23

PCIE9_TXN

A23

PCIE9_TXP

F25

PCIE10_RXN

E25

PCIE10_RXP

D23

PCIE10_TXN

C23

PCIE10_TXP

F5

PCIE_RCOMPN

E5

PCIE_RCOMPP

D56

PROC_PRDY#

D61

PROC_PREQ#

BB11

GPP_A7/PIRQA#

E28

PCIE11_RXN/SATA1B_RXN

E27

PCIE11_RXP/SATA1B_RXP

D24

PCIE11_TXN/SATA1B_TXN

C24

PCIE11_TXP/SATA1B_TXP

E30

PCIE12_RXN/SATA2_RXN

F30

PCIE12_RXP/SATA2_RXP

A25

PCIE12_TXN/SATA2_TXN

B25

PCIE12_TXP/SATA2_TXP

SKYLAKE-U_BGA1356

REV = 1

@

SKL_ULT

?

USB2

1 OF 20

3

SSIC / USB3

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_3_RXN/SSIC_2_RXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_TXP/SSIC_2_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_COMP

USB2_ID

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E8/SATALED#

?

H8

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

AB10

AD6

AD7

AH3

AJ3

AD9

AD10

AJ1

AJ2

AF6

AF7

AH1

AH2

AF8

AF9

AG1

AG2

AH7

AH8

AB6

AG3

AG4

A9

C9

D9

B9

J1

J2

J3

H2

H3

G4

H1

USB30_RX_N1

USB30_RX_P1

USB30_TX_N1

USB30_TX_P1

USB30_RX_N2

USB30_RX_P2

USB30_TX_N2

USB30_TX_P2

USB20_N1

USB20_P1

USB20_N3

USB20_P3

USB20_N4

USB20_P4

USB20_N5

USB20_P5

USB20_N6

USB20_P6

USB20_N10

USB20_P10

USB20_N7

USB20_P7

USB2_COMP

USB2_ID

USB2_VBUSSENSE

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

GPP_E4

RC1628 0_0201_5%

SATA0GP

SSD_1_PCIE_DET#

SSD_PCIE_DET#

GPP_E4

USB30_RX_N1 43

USB30_RX_P1 43

USB30_TX_N1 43

USB30_TX_P1 43

USB30_RX_N2 41

USB30_RX_P2 41

USB30_TX_N2 41

USB30_TX_P2 41

USB20_N1 41

USB20_P1 41

USB20_N3 43

USB20_P3 43

USB20_N4 43

USB20_P4 43

USB20_N5 30

USB20_P5 30

USB20_N6 33

USB20_P6 33

USB20_N10 40

USB20_P10 40

USB20_N7 33

USB20_P7 33

RC118 113_0402_1%

RC1626 0_0402_5%@

RC1627 1K_0402_5%

USB_OC0# 43

USB_OC1# 41

USB_OC2# 43

@

1 2

PCH_SATA_DEVSLP 37

RC1617 10K_0201_5%

1 2

1 2

2

@

USB3.0

USB3.0

USB2.0

Card reader

Touch Screen

BT

Camera

12

1

2

USB3.0

USB3.0

SSD_PCIE_DET# 37

+3VS

EC_SMI# 44

USBRBIAS

Width 20Mil

Space 15Mil

Length 500Mil

1

+3VALW_PCH

RPC17

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

2016/05/03: Implement as Power Button

function for Windows RedStone support

USB_OC0#

USB_OC1#

USB_OC3#

USB_OC2#

A A

Title

Title

Title

MCP (PCIE,SATA,USB3,USB2)

MCP (PCIE,SATA,USB3,USB2)

MCP (PCIE,SATA,USB3,USB2)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

GS44B/GS54B

GS44B/GS54B

GS44B/GS54B

Wednesday, May 29, 2019

Wednesday, May 29, 2019

Wednesday, May 29, 2019

9 60

9 60

1

9 60

1.0

1.0

1.0

5

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONT AINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONT AINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONT AINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. TH IS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

AND TRADE SECRET INFORMATION. TH IS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

AND TRADE SECRET INFORMATION. TH IS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUT URE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUT URE CENTER.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUT URE CENTER.

3

2015/08/20

2015/08/20

2015/08/20

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/08/20

2016/08/20

2016/08/20

5

https://vinafix.com

D D

C C

+3VS

1 4

2 3

10K_0404_4P2R_5%

1 2

RC3123

10K_0402_5%

B B

A A

@DIS For NV GPU SKU

PCIE CLK0 DGPU

RPC4

GPU_CLKREQ#

SSD_CLKREQ#

WLAN_CLKREQ#

XTAL24_U22_IN_R

XTAL24_U22_OUT_R

15P_50V_J_NPO_0201

5

CC1324

U22_NF@

the R,C Change value and Footprint,and YC3 Must be changed:

RC3030: SD04310048J, S RES 1/20W 1M +-5% 0201,

changed RC3030 LCFC PN for BOM

Changed YC3 CC1324 CC1325 source for BOM according the owner recommodation:

YC3:SJ10000S500&SJ10000TG00 CC1324&CC1325:SE00001AD00

CLK_PCIE_GPU#20

CLK_PCIE_GPU20

GPU_CLKREQ#20

CLK_PCIE_WLAN#40

WLAN

SSD-1

RC3035 0_0402_5%

RC3034 0_0402_5%

note:U22_NF@ represent the i3-7020U 2.3G/2C/3M

1

2

CLK_PCIE_WLAN40

WLAN_CLKREQ#40

CLK_PCIE_SSD#37

CLK_PCIE_SSD37

SSD_CLKREQ#37

U22_NF@

12

L1

U22_EMC_NS@

1

1

4

4

EXC24CH900U_4P

SM070004400

U22_NF@

1 2

RC3030

1M_0201_5%

YC3

24MHZ_8PF_7R24080003

1

1

GND1

GND2

15P_50V_J_NPO_0201

U22_NF@

2

2

3

U22_NF@

12

U22_NF@

4

3

2

3

CC1325

KBL U22 Use

3

4

XTAL24_U22_IN

XTAL24_U22_OUT

XTAL24_U22_IN_RXTAL24_U22_OUT_R

1

2

4

CLK_PCIE_GPU#

CLK_PCIE_GPU

GPU_CLKREQ#

CLK_PCIE_WLAN#

CLK_PCIE_WLAN

WLAN_CLKREQ#

CLK_PCIE_SSD#

CLK_PCIE_SSD

SSD_CLKREQ#

UC1I

CSI-2

A36

CSI2_DN0

B36

CSI2_DP0

C38

CSI2_DN1

D38

CSI2_DP1

C36

CSI2_DN2

D36

CSI2_DP2

A38

CSI2_DN3

B38

CSI2_DP3

C31

CSI2_DN4

D31

CSI2_DP4

C33

CSI2_DN5

D33

CSI2_DP5

A31

CSI2_DN6

B31

CSI2_DP6

A33

CSI2_DN7

B33

CSI2_DP7

A29

CSI2_DN8

B29

CSI2_DP8

C28

CSI2_DN9

D28

CSI2_DP9

A27

CSI2_DN10

B27

CSI2_DP10

C27

CSI2_DN11

D27

CSI2_DP11

SKYLAKE-U_BGA1356

REV = 1

@

UC1J

D42

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

AR10

GPP_B5/SRCCLKREQ0#

B42

CLKOUT_PCIE_N1

A42

CLKOUT_PCIE_P1

AT7

GPP_B6/SRCCLKREQ1#

D41

CLKOUT_PCIE_N2

C41

CLKOUT_PCIE_P2

AT8

GPP_B7/SRCCLKREQ2#

D40

CLKOUT_PCIE_N3

C40

CLKOUT_PCIE_P3

AT10

GPP_B8/SRCCLKREQ3#

B40

CLKOUT_PCIE_N4

A40

CLKOUT_PCIE_P4

AU8

GPP_B9/SRCCLKREQ4#

E40

CLKOUT_PCIE_N5

E38

CLKOUT_PCIE_P5

AU7

GPP_B10/SRCCLKREQ5#

SKYLAKE-U_BGA1356

REV = 1

@

1

2

SKL_ULT

?

1 OF 20

SKL_ULT

CLOCK SIGNALS

RC32 10M_0402_5%

32.768KHZ_9PF_X1A0001410002

CC4

7P_50V_D_NPO_0402

12

YC1

1 2

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

?

1 OF 20

RTC_X1

RTC_X2

1

CC5

7P_50V_D_NPO_0402

2

Issued Date

Issued Date

Issued Date

3

C37

D37

C32

D32

C29

D29

B26

A26

E13

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

?

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

SRTCRST#

RTCRST#

CSI2_COMP

EMMC_RCOMP

RTCX1

RTCX2

?

2015/08/20

2015/08/20

2015/08/20

1 2

RC73 100_0402_1%

1 2

RC50 200_0402_1%

F43

E43

BA17

SUSCLK

XTAL24_U22_IN

E37

XTAL24_U22_OUT

E35

DIFFCLK_BIASREF

E42

RTC_X1

AM18

RTC_X2

AM20

SRTC_RST#

AN18

RTC_RST#

AM16

VCCRTC

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

2

SUSCLK 40

1 2

RC72 2.7K_0402_1%

1 2

RC33 20K_0402_1%

1 2

RC34 20K_0402_1%

Deciphered Date

Deciphered Date

Deciphered Date

2

+VCCCLK5

2016/08/20

2016/08/20

2016/08/20

1

2

1

2

1

SUSCLK

1U_0402_6.3V6K

CC3

SRTC_RST#

CC6

RTC_RST#

1U_0402_6.3V6K

RC1624 0_0402_5%@

1

JCMOS2

@

Place Bottom

Title

Title

Title

MCP (CSI2,EMMC,CLOCK)

MCP (CSI2,EMMC,CLOCK)

MCP (CSI2,EMMC,CLOCK)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

1 2

RC95 1K_0402_5%

@

1 2

JCMOS3

@

1

GS44B/GS54B

GS44B/GS54B

Wednesday, May 29, 2019

Wednesday, May 29, 2019

Wednesday, May 29, 2019

GS44B/GS54B

1

EC_RTC_RST# 44

10 60

10 60

10 60

1.0

1.0

1.0

5

https://vinafix.com

D D

SYS_PWROK44

PCH_PWROK44

U4404

PLT_RST#

PLT_RST# PLT_RST#_B

1

2

SN74LVC1G17DCKR_SC70-5

1 2

NC

VCC

A

GND3Y

@

RC3107