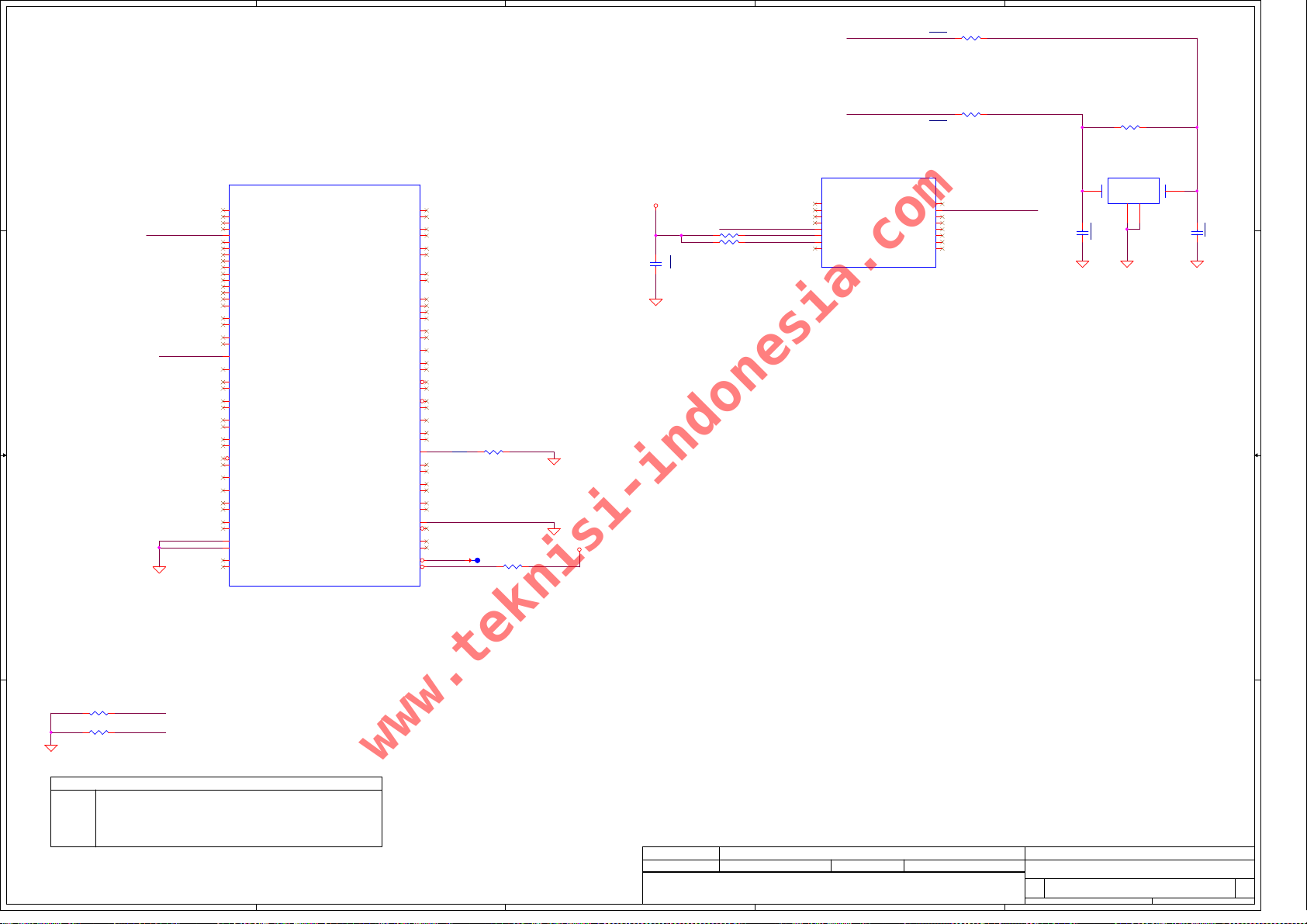

Lenovo IdeaPad 330C-15IKB - Schematic

A

www.teknisi-indonesia.com

1 1

B

C

D

E

Compal Confidential

DULU 330C (DLID4 / DLID5)

2 2

DIS M/B Schematic Document

Intel KabyLake U/KabyLake R Processor with DDR4

MX110 (23x23mm)

2018-03-09

3 3

LA-G201P

R E V: 1.0

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2018/03/09 2019/03/09

2018/03/09 2019/03/09

2018/03/09 2019/03/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

Date: Sheet o f

Date: Sheet o f

D

Date: Sheet o f

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

LA-G201P

LA-G201P

LA-G201P

1.0

1.0

1 55Friday, March 09, 2018

1 55Friday, March 09, 2018

E

1 55Friday, March 09, 2018

1.0

A

www.teknisi-indonesia.com

B

C

D

E

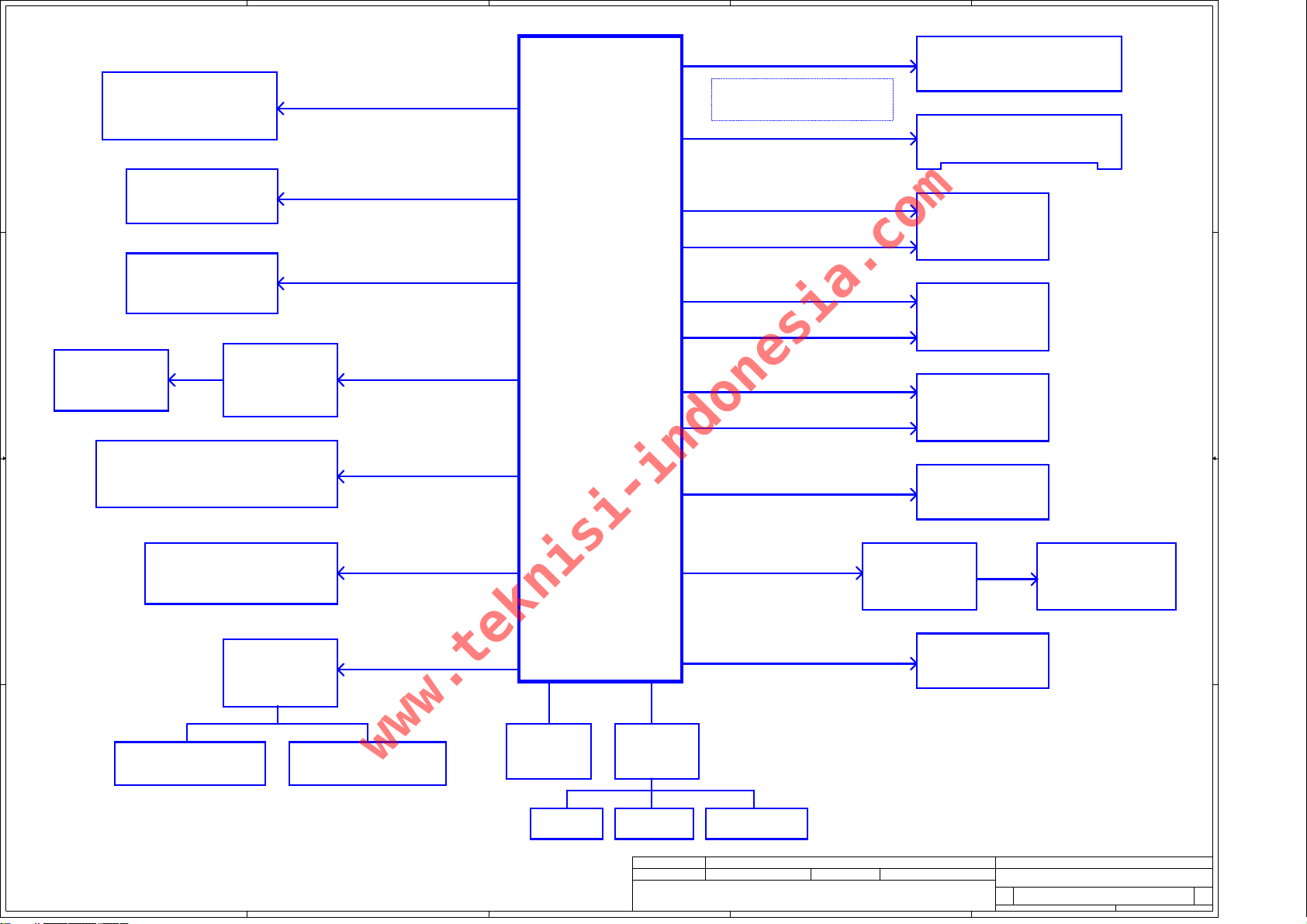

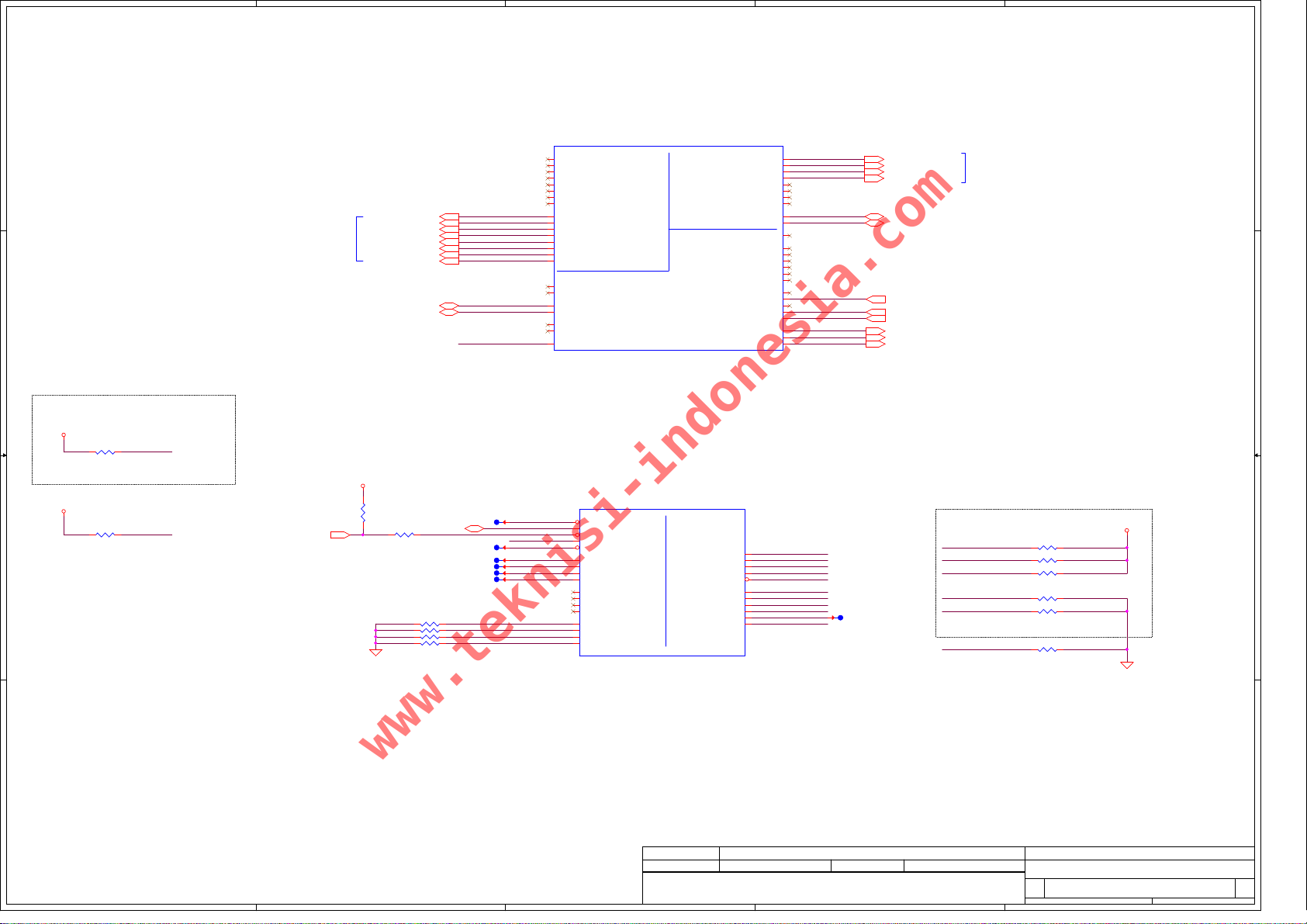

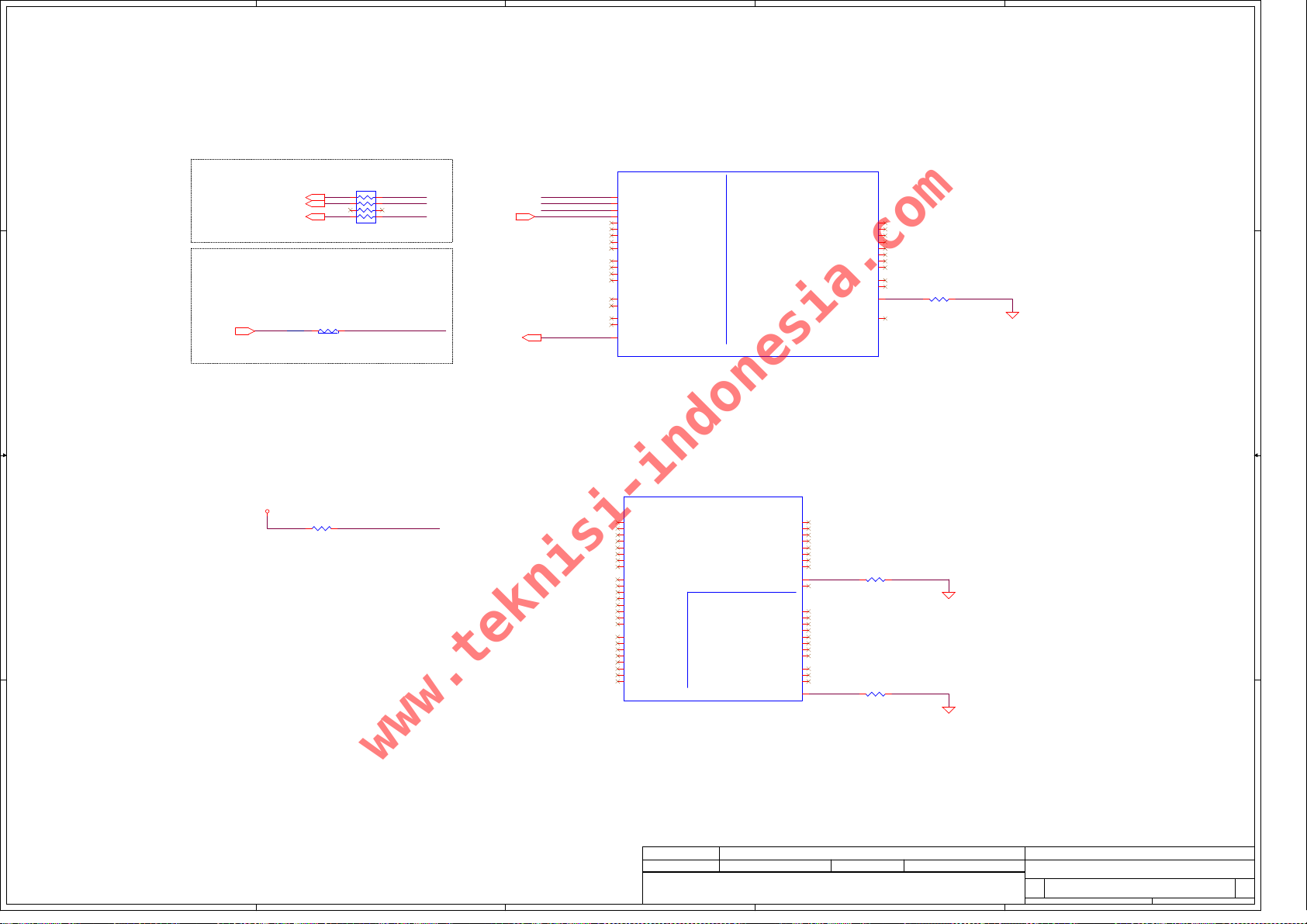

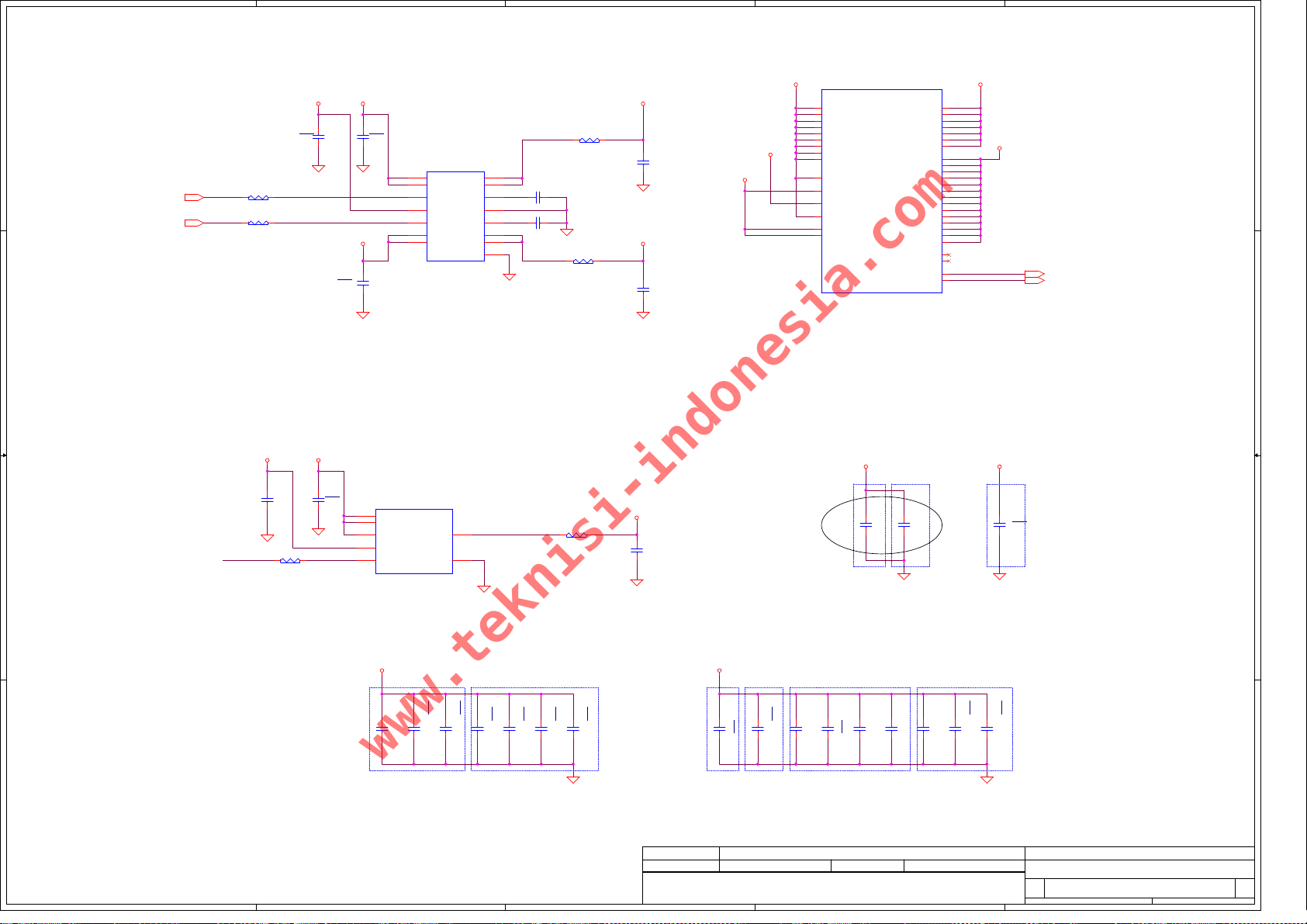

Memory Bus (Channel A)

NVIDIA MX110

1 1

(2GB GDDR5 VRAM)

(256 x 32 x 2 PCS)

PCIe X4 Gen3

*KBL-U: DDR4 (2133MHz, 1.2V)

*KBL-R: DDR4 (2400MHz, 1.2V)

Memory Bus (Channel B)

eDP Conn.

eDP X1 (2 Lanes)

PCIe X1 (1 Lanes)

USB 2.0 X1

HDMI Conn.

DDI X1 (4 Lanes)

Intel KabyLake-U

USB3.0 x1

Intel KabyLake-R

USB2.0 x1

2 2

RJ45 Conn.

LAN

RTL8106E-CG

PCIe X1 (1 Lane)

10/100

ODD Conn.

(14" -> On Mother Board)

SATA X1

(15" -> On Sub/B through FFC)

SOC

1356 Pin BGA

USB3.0 x1

USB2.0 x1

USB2.0 x1

DDR4 (On Board) X4

DDR4 (SO DIMM) X1

WLAN / BT

Left USB3.0 x1

Left USB3.0 x1

Int. Camera

3 3

HDD Conn.

(On Sub/B through FFC)

SATA X1

USB2.0 x1

Card Reader

Realtek

SD Card Conn.

RTS5146-GR

Audio Codec

HDA

I2C x1

Touch Pad

Realtek

ALC3240

Int. Speaker Conn.

4 4

A

Audio Combo Jack

Headphone / Mic

B

SPI LPC

SPI ROM

8MB, 3.3V

LED

EC

ENE

KB9022QD

Int. KBD

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEE T NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEE T NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEE T NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Hall Sensor

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Document Number R e v

Document Number R e v

Document Number R e v

C

C

C

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

Block Diagram

Block Diagram

Block Diagram

LA-G201P

LA-G201P

LA-G201P

E

2 55Friday, March 09, 2018

2 55Friday, March 09, 2018

2 55Friday, March 09, 2018

1.0

1.0

1.0

1

www.teknisi-indonesia.com

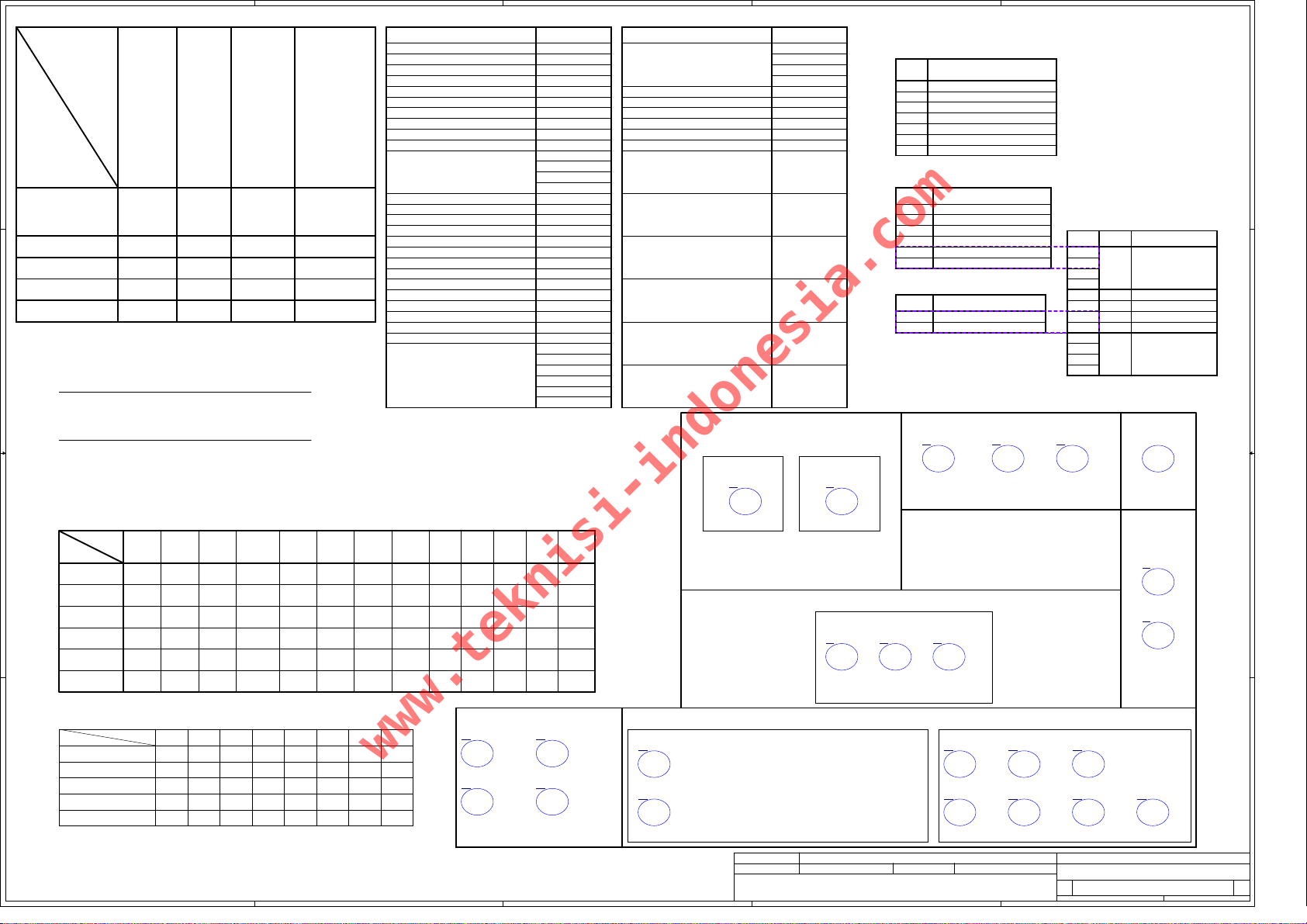

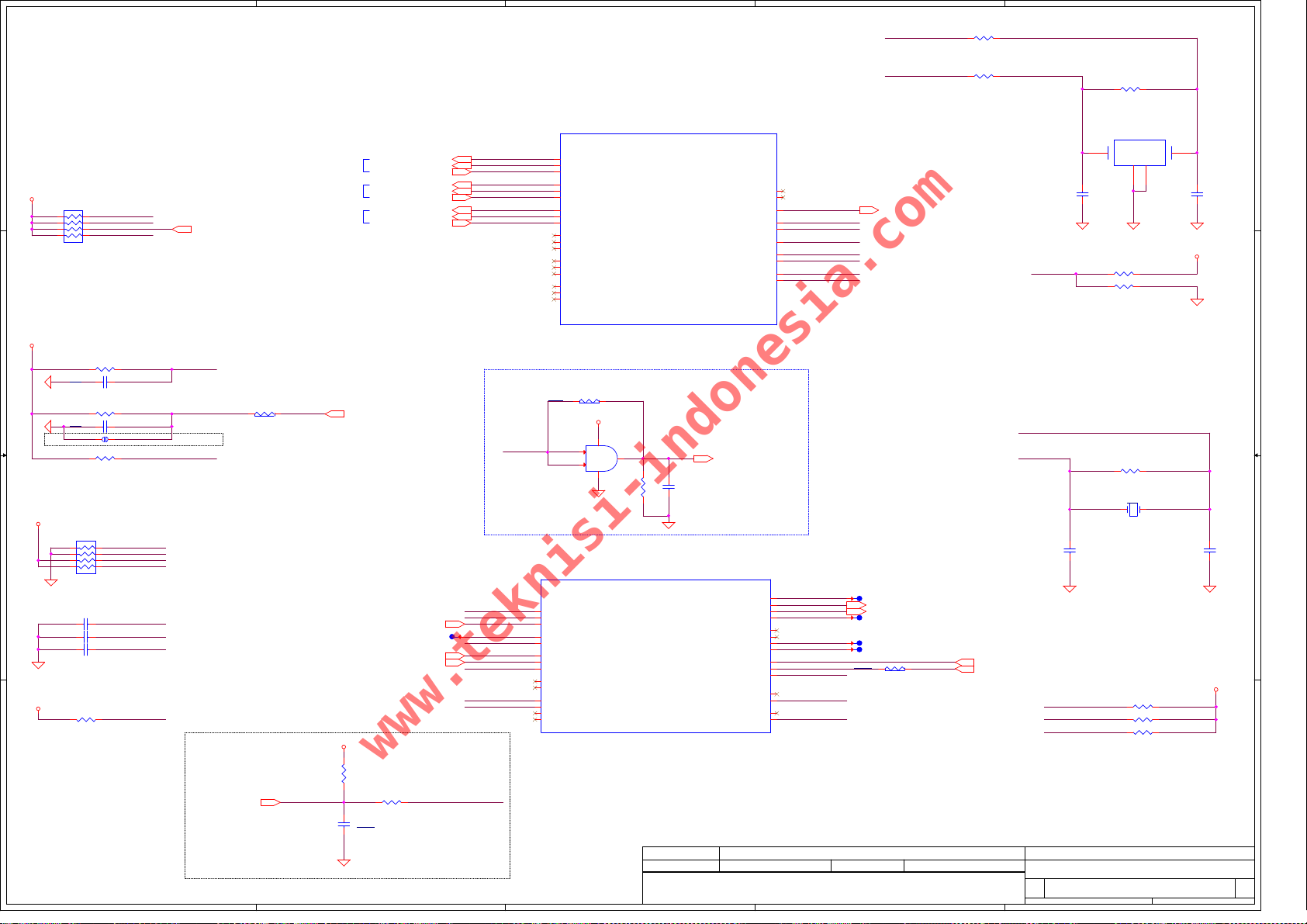

Voltage Rails

+VCC_GFXCORE_AXG

Address

1001 100x 98h

Address

1001 111x 9Eh

+5VS

+3VS

+1.35VS

+VCC_CORE

+VGA_CORE

+1.8VS

+0.6VS

+1.0VALW

X

XX

X

XXX

power

plane

+5VALW

B+

A A

State

S0

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

B B

EC SM Bus1 address

Device

Smart Battery

PCH SM Bus address

Device

DDR_JDIMM1

Touch Pad

Address

0001 011x 16h

Address

1010 000x A0h

+3VALW

O

O

O

O

O

O

O

X

X

EC SM Bus2 address

GPU SM Bus address

+1.2V

Device

NCT7718W

Device

Internal thermal sensor

O O

O

X

2

BOM Structure Table

Item

DIS Only Comp onents DIS@

UMA Only Comp onents UMA@

14" Only Comp onents

15" Only Comp onents

HDMI Logo 45@

GIGA LAN Rese rved Items 8111GLDO@

Memory Down - DDP Package

GPU

ESD Category ESD@

RF Category RF@

ESD Un-Mount Items

RF Un-Mount I tems @RF@

Connectors ME@

Test Point TP@

Intel Debug C omponents @DCI@

Un-Mount Com ponents @

CPU Component s - U22 Only

CPU Component s - U42 Only

EMI U42 Compo nents

CPU

BOM Structure

14@

15@

SDP@Memory Down - SDP Package

DDP@

GC6@GPU GC6 Compo nents

NOGC6@Un-Mount GPU GC6 Componen ts

N16S_R1@

N16S_R3@

N16V_R1@

N16V_R3@

EMI@EMI Category

@EMI@EMI Un- Mount Items

@ESD@

U22@

U42@

U22_EMI@EMI U22 Compo nents

U42_EMI@

i3_7020U_R1@

i5_8250U_R1@

i5_8250U_R3@

i7_8550U_R1@

i7_8550U_R3@

i3_8130U_R1@

3

Item

X4E

On Board RAM (Hynix 4GB)

On Board RAM (Micron 4GB)

On Board RAM (Samsung 4GB )

On Board RAM X76 Resistor s X76RAM@

Realtek Card Reader

Genesys Card Reader

VRAM (Hynix 2 GB)

VRAM (Hynix 4 GB)

VRAM (Micron 2GB)

VRAM (Micron 4GB)

VRAM (Samsung 2GB)

VRAM (Samsung 4GB)

BOM Structure

X4E_U22_14@

X4E_U22_15@

X4E_U42_14@

X4E_U42_15@

H4G_MD@

M4G_MD@

S4G_MD@

RTK_CR@

GNS_CR@

H2G_VRAM@

H2G@

H2G_R1@

H2G_R3@

H4G_VRAM@

H4G@

H4G_R1@

H4G_R3@

M2G_VRAM@

M2G@

M2G_R1@

M2G_R3@

M4G_VRAM@

M4G@

M4G_R1@

M4G_R3@

S2G_VRAM@

S2G@

S2G_R1@

S2G_R3@

S4G_VRAM@

S4G@

S4G_R1@

S4G_R3@

X4E

U42 U22

ZZZ

X4E_U42@

4

5

USB 2.0 Port Table

External USB PortPort

1

2

USB2/3 Port (MB-1)

3

USB2/3 Port (MB-2)

4

5

Camera

6

Card Reader

7

NGFF WLAN+BT

USB 3.0 Port Table

Port

1

2

USB2/3 Port (MB-1)

3

USB2/3 Port (MB-2)

4

5

6

SATA Port Table

Port

0

HDD

1

ODD

ON BOARD RAM * 4

ZZZ

S4G_MD@

X76 SAMSUNG 4GB MD

ZZZ

X4E_U22@

X7677538L13

ZZZ

M4G_MD@

X76 MICRON 4GB MD

X7677538L14

PCIE Port Table

Port

Lane

1

2

1

3

4

5

6

7

8

9

10

11

12

ZZZ

H4G_MD@

X76 HYNIX 4GB MD

X7677538L15

GPU

LAN

NGFF WLAN+BT

HDMI Logo

ZZZ

45@

HDMI Logo

RO0000003HM

X4E U42

SMBUS Control Table

VGA

C C

D D

SMB_EC_CK1

SMB_EC_DA1

SMB_EC_CK2

SMB_EC_DA2

SMB_EC_CK4

SMB_EC_DA4

PCH_SMBCLK

PCH_SMBDATA

SML0CLK

SML0DATA

SML1CLK

SML1DATA

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SOURCE

NECP388

+3VALW

NECP388

+3VS

NECP388

+3VALW

PCH

+3VALW

PCH

+3VALW

PCH

+3VALW

SIGNAL

1

V

+3VGS

X X X X X X X X X

X

X

SLP_S1#

LOW

HIGH HIGH HIGH

LOW

LOW LOW LOW

CHARGER

VX X

+19V_VIN

+3VALW

X

X

V

V X

X

+3VS

X

X

XX

X

SLP_S4#SLP_S3# +V+VALWSLP_S5# Clock+VS

HIGHHIGHHIGH

LOW

HIGH

LOWLOW

X

X

X

X

V

+3VS

ONONON

HIGH

ON

ON

HIGH

ON

HIGH

ON

LOWLOW

SODIMMNECP388BATT

X

V

+3VS

XX

X

ON

OFF

OFF

Thermal

DGPU TP

Sensor

X

X

V

+3VS

X

X

X

X

V

X

+3VS

ONON

ON

LOW

OFF

OFF

OFF

OFF

OFF

OFF

2

X

X

X

X

X

X

X

V

X

+3VS

X

X

GPU

UV1

N16S-GTR-S-A2 BGA 595P

SA00009FP00

UV1

N16S-GTR-S-A2 BGA 595P

SA00009FP30

X

X

V

+3VS

X

X

*N16V - MX110 (Device ID: 0x174E

*N16S - MX130 (Device ID: 0x174D

N16S_R1@

N16S_R3@

G-

PCH

SENSOR

X

X

V

X

+3VS

V

+3VS

X

X

X

X

X

X

UV1

N16V_R1@

N16V-GMR1-S-A2 BGA 595P

SA00009IT00

UV1

N16V_R3@

N16V-GMR1-S-A2 BGA 595P

SA00009IT30

)

CPU

)

KBL U22 (= U22@)

UC1

i3_7020U_R1@

QNZU H0 2.3G

SA0000BLH10

UC1

i3_7020U_U22@

SR3TK H0 2.3G

SA0000BLH50

3

X4EABQ38L01

GDDR5 VRAM * 2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS C ONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS C ONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS C ONFIDENTIAL

AND TRADE SECRET INFOR MATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFOR MATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFOR MATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT A S AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHE ET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT A S AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHE ET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT A S AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHE ET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR D ISCLOSED TO ANY THIRD PAR TY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR D ISCLOSED TO ANY THIRD PAR TY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR D ISCLOSED TO ANY THIRD PAR TY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

X4E U22

X4EABQ38L02

CARD READER

*Main Source - Realtek

*Substitute - Genesys

2GB

ZZZ

H2G_VRAM@

ZZZ

M2G_VRAM@

ZZZ

S2G_VRAM@

X76 HYNIX 2GB

X7677538L06

2018/03/09 2019/03/09

2018/03/09 2019/03/09

2018/03/09 2019/03/09

X76 MICRON 2GB

X7677538L05

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

4

X76 SAMSUNG 2GB

X7677538L04

KBL U42 (= U42@)

UC1

i5_8250U_R1@

SR3LA Y0 1.6G FCBGA

SA0000AWB20

UC1

i5_8250U_R3@

SR3LA Y0 1.6G FCBGA

SA0000AWB50

UC1

i7_8550U_R1@

SR3LC Y0 1.8G FCBGA

SA0000AWC20

UC1

i7_8550U_R3@

SR3LC Y0 1.8G FCBGA

SA0000AWC50

PCB

ZZZ

14_DAZ@

PCB

DAZ29900201

ZZZ

15_DAZ@

PCB

DAZ29A00201

UC1

i3_8130U_R1@

QP8K Y0 2.2G

SA0000BKN20

UC1

i3_8130U_R3@

SR3W0 Y0 2.2G

SA0000BKN30

Title

Title

Title

Notes List

Notes List

Notes List

Size

Size

Size

Document Number R e v

Document Number R e v

Document Number R e v

Custom

Custom

Custom

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

UC1

i3_7020U_U42@

SR3LD Y0 2.3G

SA0000BLD60

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

LA-G201P

LA-G201P

LA-G201P

5

3 55Friday, March 09, 2018

3 55Friday, March 09, 2018

3 55Friday, March 09, 2018

1.0

1.0

1.0

5

www.teknisi-indonesia.com

4

3

2

1

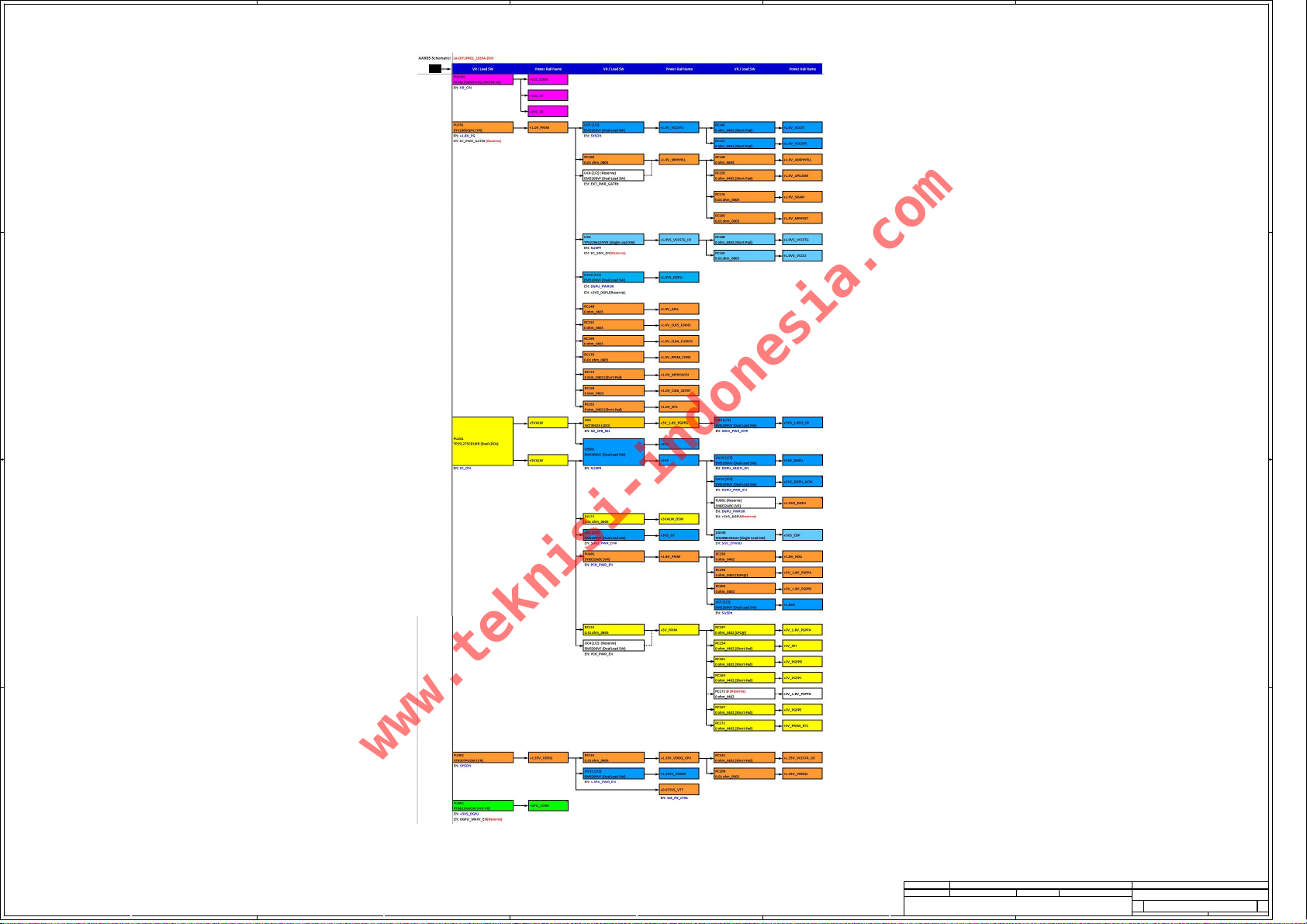

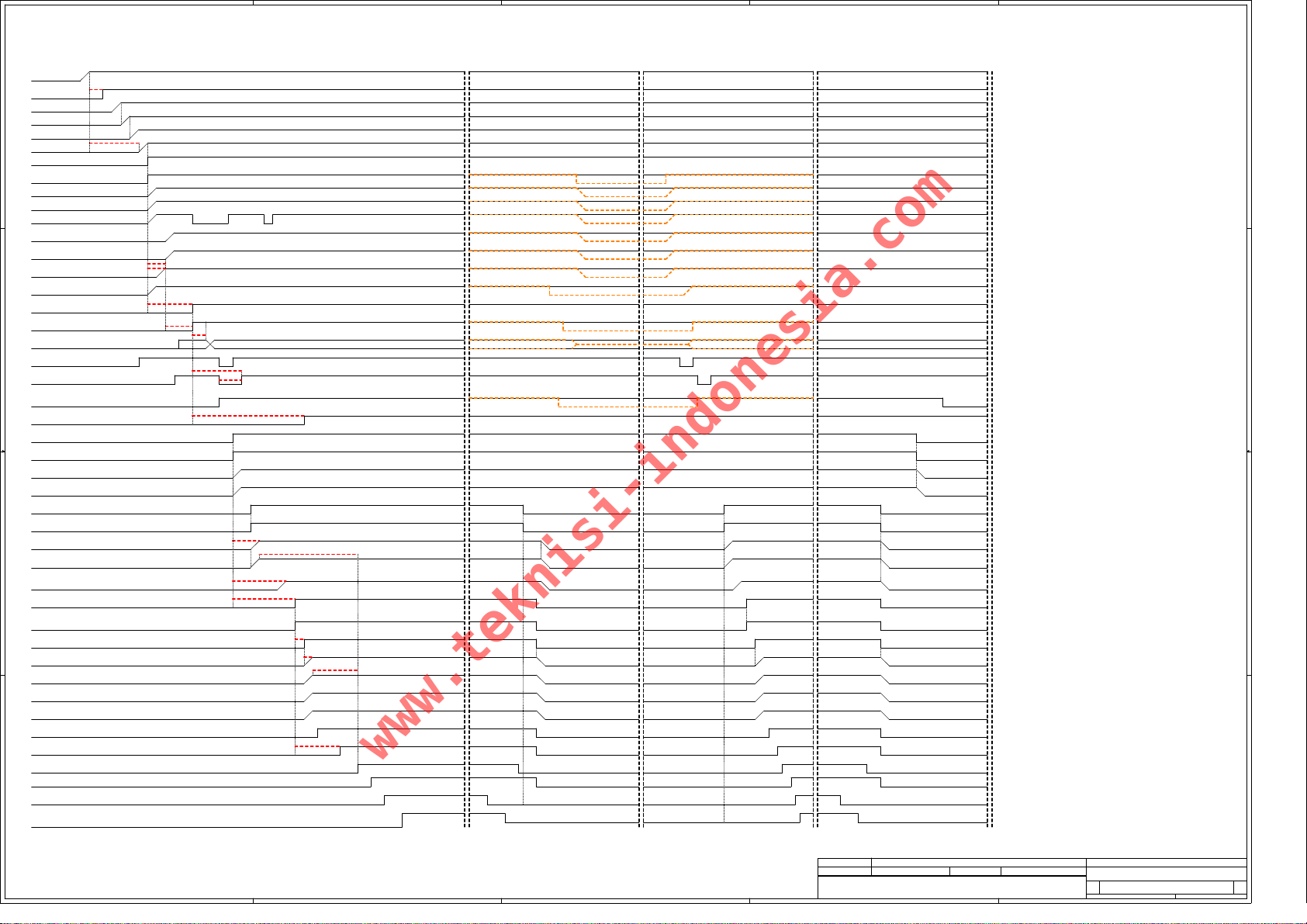

-PowerMap_KBL_DDR4_Volume_NON CS]

B+

D D

C C

B B

A A

Security Classification

Security Classification

5

4

3

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROP RIETARY PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS CONFID ENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROP RIETARY PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS CONFID ENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROP RIETARY PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS CONFID ENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TR ANSFERED FROM THE CU STODY OF THE COMPETE NT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TR ANSFERED FROM THE CU STODY OF THE COMPETE NT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TR ANSFERED FROM THE CU STODY OF THE COMPETE NT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELEC TRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELEC TRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELEC TRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY T HIRD PARTY WITHOUT PR IOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY T HIRD PARTY WITHOUT PR IOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY T HIRD PARTY WITHOUT PR IOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

2018/03/09 2019/03/09

2018/03/09 2019/03/09

2018/03/09 2019/03/09

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

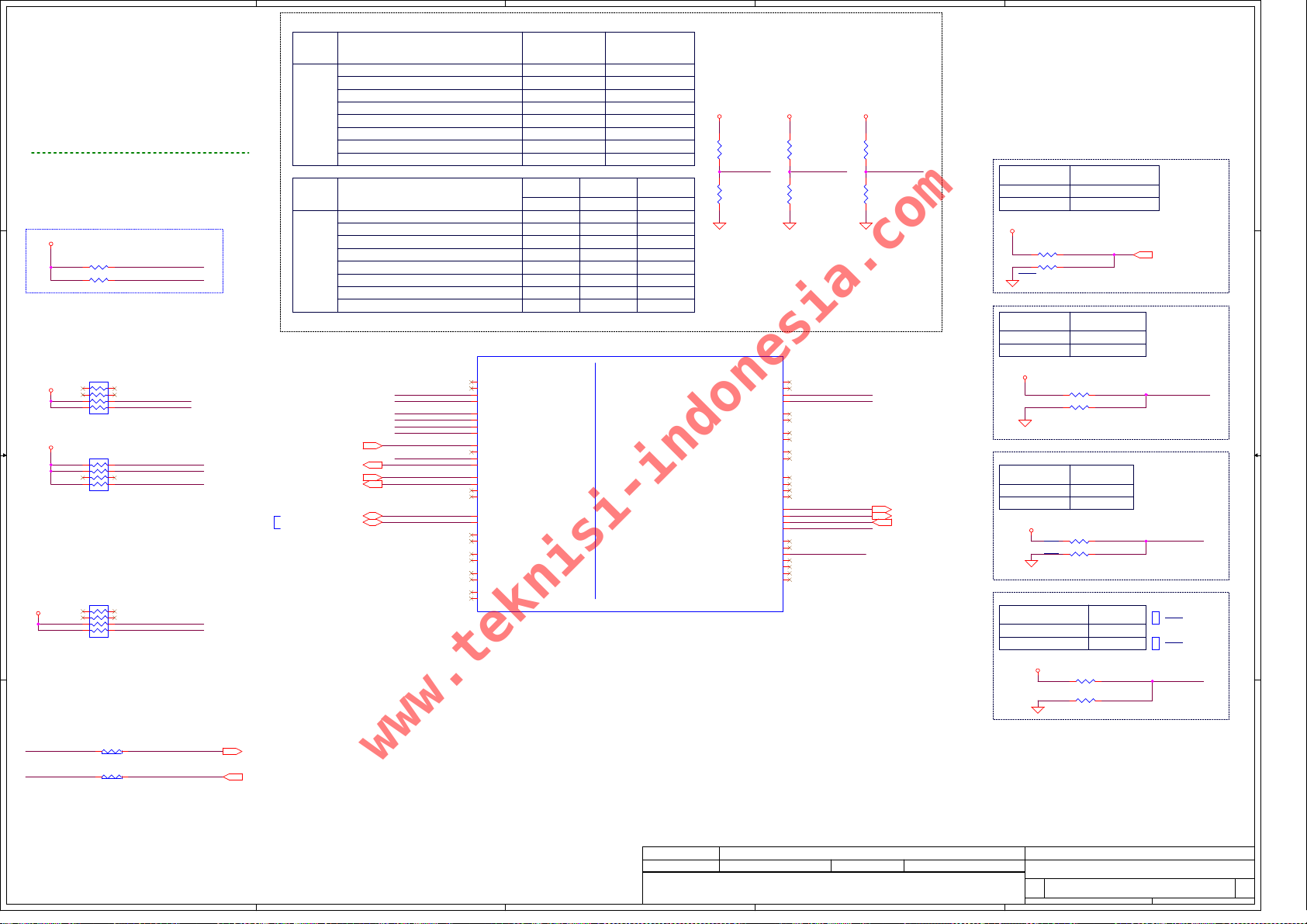

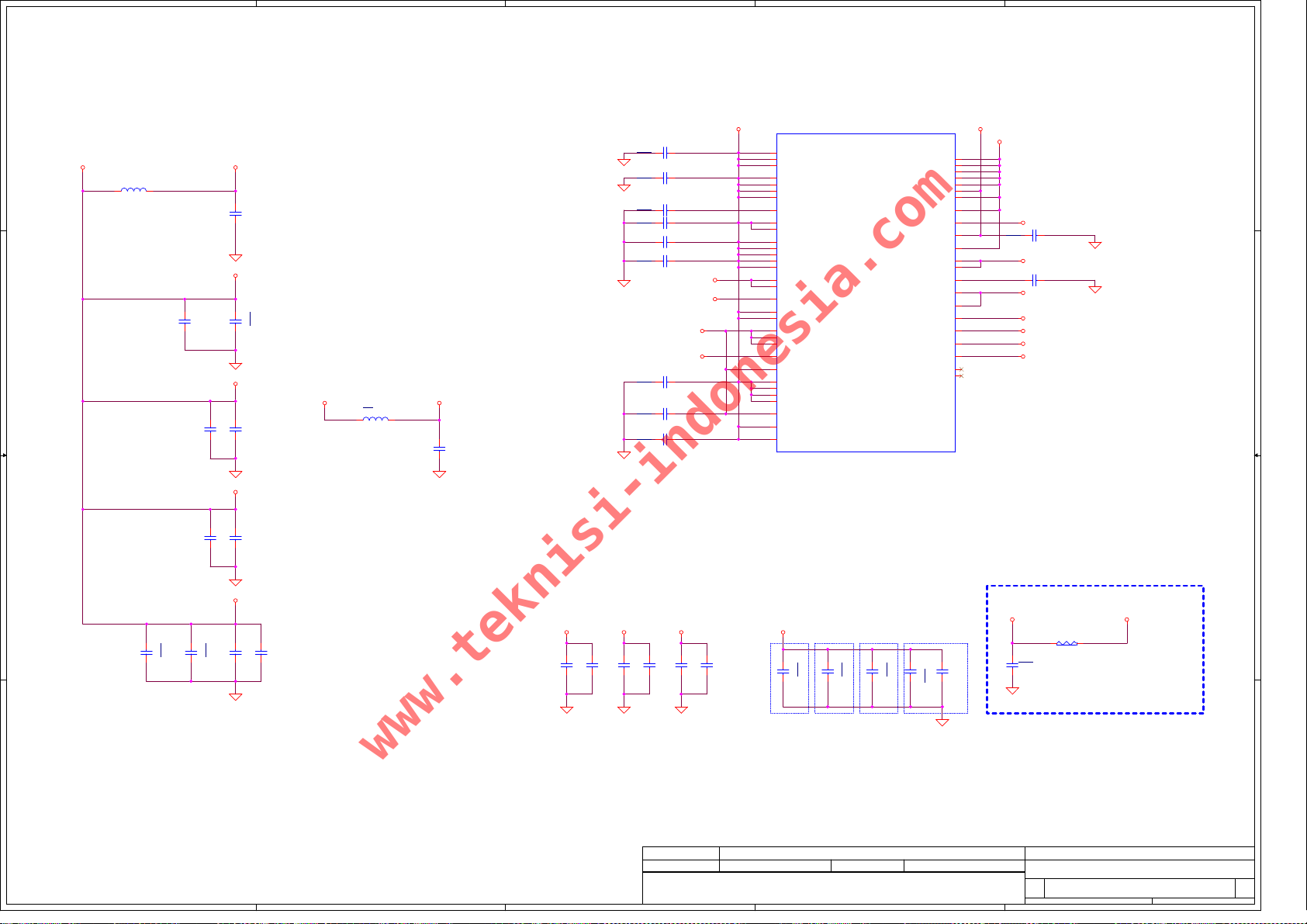

Power MAP

Power MAP

Power MAP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

LA-C071P

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

1

4 55Friday, March 09, 2018

4 55Friday, March 09, 2018

4 55Friday, March 09, 2018

1.0

1.0

1.0

5

www.teknisi-indonesia.com

4

3

2

1

G3->S0 S0->S3 ->S0

+3VL_RTC

SOC_RTCRST#

B+

D D

+3VLP/+5VLP

EC_ON

+5VALW/+3VALW/+3VALW_DSW

PM_BATLOW#

tPCH01_Min : 9 ms

tPCH04_Min : 9 ms

Pull-up to DSW well if not implemented.

/DS3 DS3S0/

PCH_PWR_EN (SLP_SUS#)

+3V_PRIM

+1.8V_PRIM

EXT_PWR_GATE#

+1.0V_MPHYPLL

+1.0V_PRIM_CORE

+1.0V_PRIM

tPCH06_Min : 200 us

SUSACK#

PCH_DPWROK

EC_RSMRST#

C C

AC_PRESENT

tPCH34_Max : 20 ms

tPCH02_Min : 10 ms

tPCH03_Min : 10 ms

tPLT02_Min : 0 ms Max : 90 ms

ON/OFF

PBTN_OUT#

Minimum duration of PWRBTN# assertion = 16m S. PWRBTN# can assert before or after RSMRST#

PM_SLP_S5#

ESPI_RST#

If EXT_PWR_GATE# Toffmin is too small, Pwr

gate may choose to completely ign ore it

tPCH43_Min : 95 ms

tPCH18_Min : 90 us

PM_SLP_S4#

SYSON

+1.0V_VCCST/+1.0V_VCCSFR

+1.35V_VDDQ/+1.35V_VCCSFR_OC

PM_SLP_S3#

SUSP#

+1.0VS_VCCSTG

+1.0VS_VCCIO

B B

+5VS/+3VS/+1.5VS/+1.05VS

EC_VCCST_PG

VR_ON

SM_PG_CTRL

+0.675VS_VTT

+VCC_SA

+VCC_CORE

tCPU04 Min : 100 ns

tCPU10 Min : 1 ms

T <=10msec

T = 10msec

tCPU19 Max : 100 ns

tCPU18 Max : 35 us

tCPU09 Min : 1 ms

+VCC_GT

VR_PWRGD

PCH_PWROK

tCPU16 Min : 0 ns

H_CPUPWRGD

SYS_PWROK

A A

SUS_STAT#

SOC_PLTRST#

S0->S5

+3VL_RTC

SOC_RTCRST#

B+

+3VLP/+5VLP

EC_ON

+5VALW/+3VALW/+3VALW_DSW

PM_BATLOW#

PCH_PWR_EN (SLP_SUS#)

+3V_PRIM

+1.8V_PRIM

EXT_PWR_GATE#

+1.0V_MPHYPLL

+1.0V_PRIM_CORE

+1.0V_PRIM

SUSACK#

PCH_DPWROK

EC_RSMRST#

AC_PRESENT

ON/OFF

PBTN_OUT#

PM_SLP_S5#

ESPI_RST#

PM_SLP_S4#

SYSON

+1.0V_VCCST/+1.0V_VCCSFR

+1.35V_VDDQ/+1.35V_VCCSFR_OC

PM_SLP_S3#

SUSP#

+1.0VS_VCCSTG

+1.0VS_VCCIO

+5VS/+3VS/+1.5VS/+1.05VS

EC_VCCST_PG

VR_ON

SM_PG_CTRL

+0.675VS_VTT

+VCC_SA

+VCC_CORE

+VCC_GT

VR_PWRGD

PCH_PWROK

H_CPUPWRGD

SYS_PWROK

SUS_STAT#

SOC_PLTRST#

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Compal Secret Data

Compal Secret Data

Compal Secret Data

2018/03/09 2019/03/09

2018/03/09 2019/03/09

2018/03/09 2019/03/09

2

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

Power Seque nce

Power Seque nce

Power Seque nce

1

5 55Friday, March 09, 2018

5 55Friday, March 09, 2018

5 55Friday, March 09, 2018

1.0

1.0

1.0

A

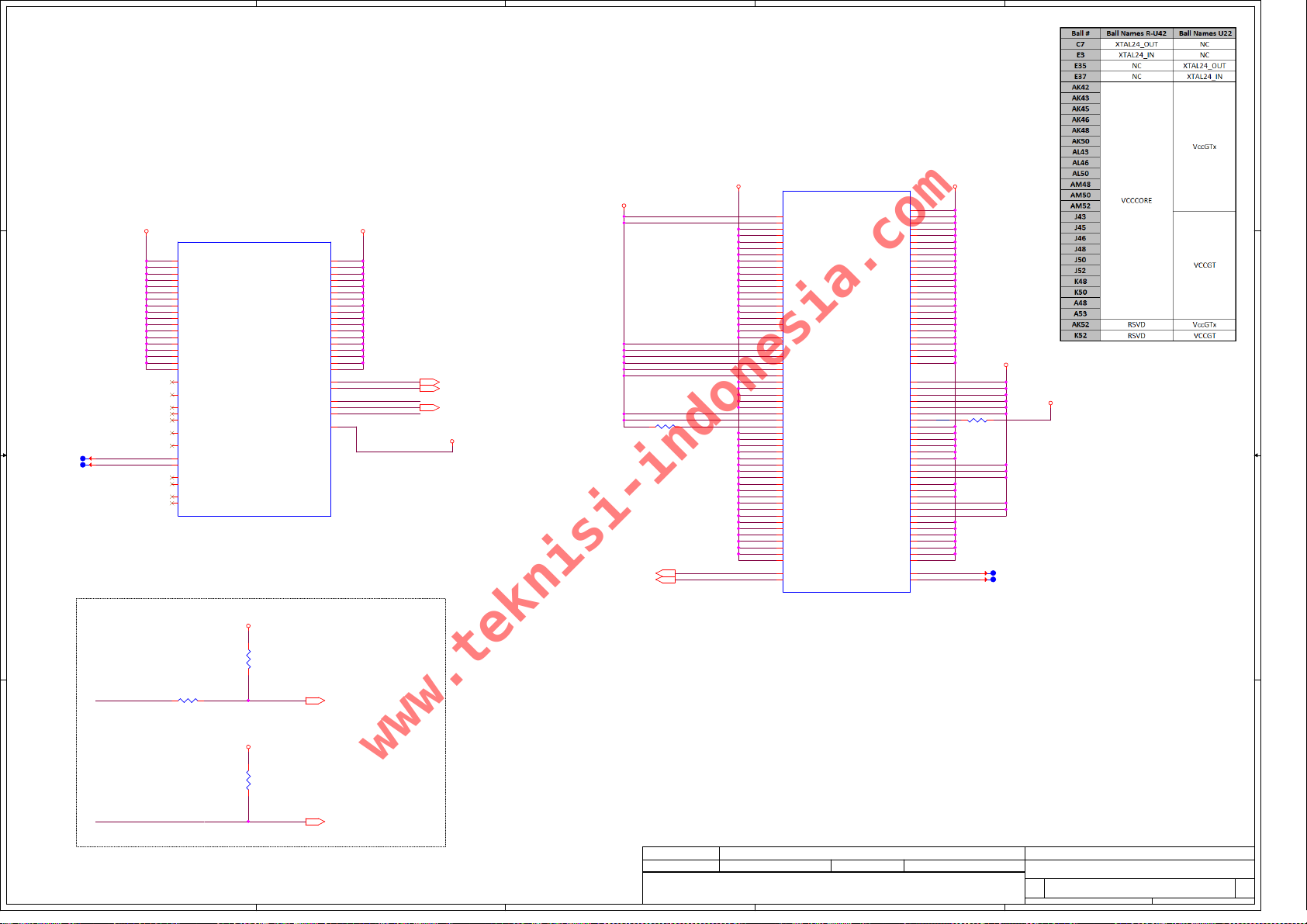

www.teknisi-indonesia.com

1 1

<HDMI>

HDMI DDC (Port C)

2 2

B

UC1A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

HDMI_TX2-_CK<29>

HDMI_TX2+_CK<29>

HDMI_TX1-_CK<29>

HDMI_TX1+_CK<29>

HDMI_TX0-_CK<29>

HDMI_TX0+_CK<29>

HDMI_CLK-_CK<29>

HDMI_CLK+_CK<29>

HDMICLK_NB<29>

HDMIDAT_NB<29>

EDP_COMP

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22

N12

GPP_E23

E52

EDP_RCOMP

SKL-U_BGA1356 @

C

DDI

DISPLAY SIDEBANDS

SKL-U

1 OF 20

EDP

Rev_1.0

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

RSVD

RSVD

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

D

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

EDP_TXN0 <28>

EDP_TXP0 <28>

EDP_TXN1 <28>

EDP_TXP1 <28>

EDP_AUXN <28>

EDP_AUXP <28>

TMDS_B_HPD <29>

EC_SCI# <10,36>

EDP_HPD <28>

ENBKL <36>

INVPWM <28>

PCH_ENVDD <28>

<eDP>

From HDMI

From eDP

E

< Compensation PU For eDP >

+1.0VS_VCCIO

EDP_COMP

1 2

RC3 24.9_0402_1%

Trace width=20 mils, Spacing=25mil, Max length=100mils

+1.0V_VCCST

H_THERMTRIP#

1 2

RC5 1K_0402_5%

3 3

H_PROCHOT#<36>

+1.0VS_VCCIO

12

RC4

1K_0402_5%

1 2

RC6 499_0402_1%

RC7 49.9_0402_1%

RC8 49.9_0402_1%

RC9 49.9_0402_1%@

RC10 49.9_0402_1%@

If routed MS, PECI requires 18 mils spacing to other signals

T99 TP@

H_PECI<36>

T100 TP@

T103 TP@

T105 TP@

T107 TP@

T109 TP@

12

12

12

12

SOC_CATERR#

H_PECI

H_PROCHOT#_R

H_THERMTRIP#

SOC_OCC#

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

CPU_POPIRCOMP

PCH_OPIRCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

UC1D

D63

CATERR#

A54

PECI

C65

PROCHOT#

C63

THERMTRIP#

A65

SKTOCC#

C55

BPM#[0]

D55

BPM#[1]

B54

BPM#[2]

C56

BPM#[3]

A6

GPP_E3/CPU_GP0

A7

GPP_E7/CPU_GP1

BA5

GPP_B3/CPU_GP2

AY5

GPP_B4/CPU_GP3

AT16

PROC_POPIRCOMP

AU16

PCH_OPIRCOMP

H66

OPCE_RCOMP

H65

OPC_RCOMP

SKL-U_BGA1356 @

SKL-U

CPU MISC

4 OF 20

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

Rev_1.0

JTAGX

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

CPU_XDP_TCK0

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

SOC_XDP_TRST#

PCH_JTAG_TCK1

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

SOC_XDP_TRST#

CPU_XDP_TCK0

T116 TP@

< PU/PD for CMC Debug >

SOC_XDP_TMS

SOC_XDP_TDI

SOC_XDP_TDO

CPU_XDP_TCK0

PCH_JTAG_TCK1

SOC_XDP_TRST#

RC11 51_0402_5%@

RC12 51_0402_5%@

RC13 51_0402_5%@DCI@

RC14 51_0402_5%@DCI@

RC15 51_0402_5%@

RC23 51_0402_5%@

+1.0VS_VCCIO

1 2

1 2

1 2

1 2

1 2

1 2

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2018/03/09 2019/03/09

2018/03/09 2019/03/09

2018/03/09 2019/03/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Date: Sheet o f

Date: Sheet o f

D

Date: Sheet o f

Compal Electronics, Inc.

SKL-U(1/12)DDI,EDP,MISC,CMC

SKL-U(1/12)DDI,EDP,MISC,CMC

SKL-U(1/12)DDI,EDP,MISC,CMC

Custom

Custom

Custom

LA-G201P

LA-G201P

LA-G201P

E

1.0

1.0

6 55Friday, March 09, 2018

6 55Friday, March 09, 2018

6 55Friday, March 09, 2018

1.0

5

www.teknisi-indonesia.com

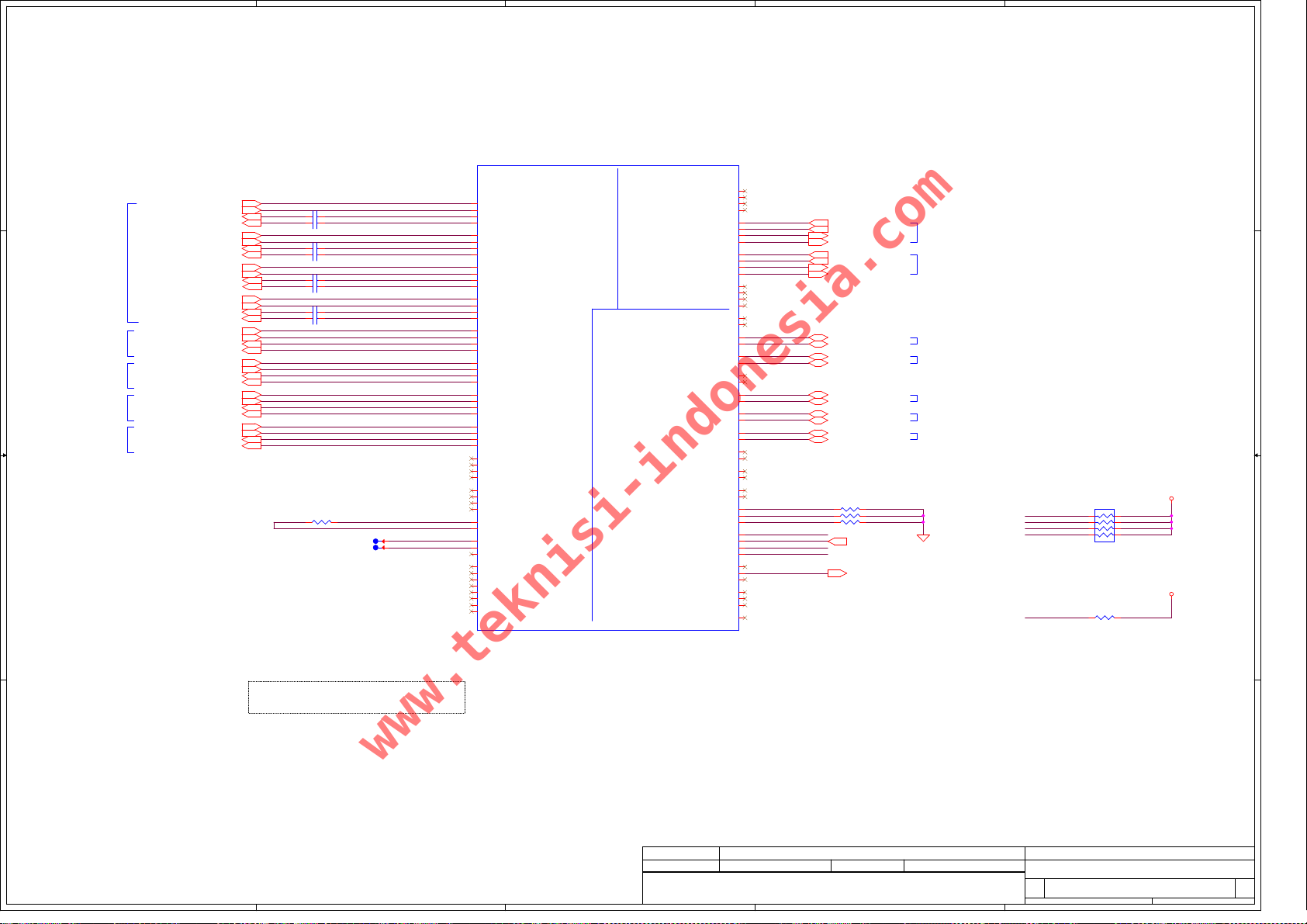

Interleaved Memory

4

3

2

1

D D

DDR_A_D[0..15]<18>

DDR_A_D[16..31]<18>

C C

DDR_A_D[32..47]<18>

DDR_A_D[48..63]<18>

B B

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

UC1B

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

Interleave / Non-Interleaved

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

SKL-U_BGA1356 @

SKL-U

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR3L / LPDDR3 / DDR4

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

Interleave / Non-Interleaved

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR CH - A

2 OF 20

DDR0_ALERT#

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

DDR_A_CLK0 DDR_A_CLK#0

Rev_1.0

DDR_A_CLK#0

AU53

DDR_A_CLK0

AT53

DDR_A_CLK#1

AU55

DDR_A_CLK1

AT55

DDR_A_CKE0

BA56

DDR_A_CKE1

BB56

AW56

AY56

DDR_A_CS#0

AU45

DDR_A_CS#1

AU43

DDR_A_ODT0

AT45

DDR_A_ODT1

AT43

DDR_A_MA5

BA51

DDR_A_MA9

BB54

DDR_A_MA6

BA52

DDR_A_MA8

AY52

DDR_A_MA7

AW52

DDR_A_BG0

AY55

DDR_A_MA12

AW54

DDR_A_MA11

BA54

M_A_ACT#

BA55

DDR_A_BG1

AY54

DDR_A_MA13

AU46

DDR_A_MA15

AU48

DDR_A_MA14

AT46

DDR_A_MA16

AU50

DDR_A_BA0

AU52

DDR_A_MA2

AY51

DDR_A_BA1

AT48

DDR_A_MA10

AT50

DDR_A_MA1

BB50

DDR_A_MA0

AY50

DDR_A_MA3

BA50

DDR_A_MA4

BB52

DDR_A_DQS#0

AM70

DDR_A_DQS0

AM69

DDR_A_DQS#1

AT69

DDR_A_DQS1

AT70

DDR_A_DQS#2

BA64

DDR_A_DQS2

AY64

DDR_A_DQS#3

AY60

DDR_A_DQS3

BA60

DDR_A_DQS#4

BA38

DDR_A_DQS4

AY38

DDR_A_DQS#5

AY34

DDR_A_DQS5

BA34

DDR_A_DQS#6

BA30

DDR_A_DQS6

AY30

DDR_A_DQS#7

AY26

DDR_A_DQS7

BA26

DDR_A_ALERT#

AW50

DDR_A_PARITY

AT52

+0.6V_A_VREFCA

AY67

AY68

+0.6V_B_VREFDQ

BA67

DDR_PG_CTRL

AW67

@

1 2

CC110

3300P_0402_50V7-K

DDR_A_CLK#0 <18>

DDR_A_CLK0 <18>

T186TP@

T189TP@

DDR_A_CKE0 <18,20>

T190TP@

DDR_A_CS#0 <18,20>

T187TP@

DDR_A_ODT0 <18,20>

T188TP@

DDR_A_MA5 <18,20>

DDR_A_MA9 <18,20>

DDR_A_MA6 <18,20>

DDR_A_MA8 <18,20>

DDR_A_MA7 <18,20>

DDR_A_BG0 < 18,20>

DDR_A_MA12 <18,20>

DDR_A_MA11 <18,20>

M_A_ACT# <18,20>

DDR_A_BG1 < 18>

DDR_A_MA13 <18,20>

DDR_A_MA15 <18,20>

DDR_A_MA14 <18,20>

DDR_A_MA16 <18,20>

DDR_A_BA0 < 18,20>

DDR_A_MA2 <18,20>

DDR_A_BA1 < 18,20>

DDR_A_MA10 <18,20>

DDR_A_MA1 <18,20>

DDR_A_MA0 <18,20>

DDR_A_MA3 <18,20>

DDR_A_MA4 <18,20>

DDR_A_DQS#0 <18>

DDR_A_DQS0 <18>

DDR_A_DQS#1 <18>

DDR_A_DQS1 <18>

DDR_A_DQS#2 <18>

DDR_A_DQS2 <18>

DDR_A_DQS#3 <18>

DDR_A_DQS3 <18>

DDR_A_DQS#4 <18>

DDR_A_DQS4 <18>

DDR_A_DQS#5 <18>

DDR_A_DQS5 <18>

DDR_A_DQS#6 <18>

DDR_A_DQS6 <18>

DDR_A_DQS#7 <18>

DDR_A_DQS7 <18>

DDR_A_ALERT# <18>

DDR_A_PARITY <18,20>

+0.6V_A_VREFCA <18>

T25@

+0.6V_B_VREFDQ <19>

DDR_B_D[0..15]<19>

DDR_B_D[16..31]<19>

DDR_B_D[32..47]<19>

DDR_B_D[48..63]<19>

Trace width/Spacing >= 20mils

Place componment near SODIMM

#543016 PDG0.9 P.163 RC place near SODIMM

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

UC1C

Interleave / Non-Interleaved

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKL-U_BGA1356 @

SKL-U

DDR3L / LPDDR3 / DDR4

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

Interleave / Non-Interleaved

DDR1_DQS N[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQS N[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQS N[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQS N[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQS N[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQS N[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR CH - B

3 OF 20

Rev_1.0

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

DDR_B_CLK#0

AN45

DDR_B_CLK#1

AN46

DDR_B_CLK0

AP45

DDR_B_CLK1

AP46

DDR_B_CKE0

AN56

DDR_B_CKE1

AP55

AN55

AP53

DDR_B_CS#0

BB42

DDR_B_CS#1

AY42

DDR_B_ODT0

BA42

DDR_B_ODT1

AW42

DDR_B_MA5

AY48

DDR_B_MA9

AP50

DDR_B_MA6

BA48

DDR_B_MA8

BB48

DDR_B_MA7

AP48

DDR_B_BG0

AP52

DDR_B_MA12

AN50

DDR_B_MA11

AN48

M_B_ACT#

AN53

DDR_B_BG1

AN52

DDR_B_MA13

BA43

DDR_B_MA15

AY43

DDR_B_MA14

AY44

DDR_B_MA16

AW44

DDR_B_BA0

BB44

DDR_B_MA2

AY47

DDR_B_BA1

BA44

DDR_B_MA10

AW46

DDR_B_MA1

AY46

DDR_B_MA0

BA46

DDR_B_MA3

BB46

DDR_B_MA4

BA47

DDR_B_DQS#0

AH66

DDR_B_DQS0

AH65

DDR_B_DQS#1

AG69

DDR_B_DQS1

AG70

DDR_B_DQS#2

AR66

DDR_B_DQS2

AR65

DDR_B_DQS#3

AR61

DDR_B_DQS3

AR60

DDR_B_DQS#4

AT38

DDR_B_DQS4

AR38

DDR_B_DQS#5

AT32

DDR_B_DQS5

AR32

DDR_B_DQS#6

AR25

DDR_B_DQS6

AR27

DDR_B_DQS#7

AR22

DDR_B_DQS7

AR21

DDR_B_ALERT#

AN43

DDR_B_PARITY

AP43

DDR_DRAMRST#

AT13

AR18

AT18

SM_RCOMP0

AU18

SM_RCOMP1

SM_RCOMP2

#543016 PDG0.9 P.117

W=12-15 Space= 20/25 L=500mil

DDR_B_CLK#0 <19>

DDR_B_CLK#1 <19>

DDR_B_CLK0 <19>

DDR_B_CLK1 <19>

DDR_B_CKE0 <19>

DDR_B_CKE1 <19>

DDR_B_CS#0 <19>

DDR_B_CS#1 <19>

DDR_B_ODT0 <19>

DDR_B_ODT1 <19>

DDR_B_MA5 <19>

DDR_B_MA9 <19>

DDR_B_MA6 <19>

DDR_B_MA8 <19>

DDR_B_MA7 <19>

DDR_B_BG0 <19>

DDR_B_MA12 <19>

DDR_B_MA11 <19>

M_B_ACT# <19>

DDR_B_BG1 <19>

DDR_B_MA13 <19>

DDR_B_MA15 <19>

DDR_B_MA14 <19>

DDR_B_MA16 <19>

DDR_B_BA0 <19>

DDR_B_MA2 <19>

DDR_B_BA1 <19>

DDR_B_MA10 <19>

DDR_B_MA1 <19>

DDR_B_MA0 <19>

DDR_B_MA3 <19>

DDR_B_MA4 <19>

DDR_B_DQS#0 <19>

DDR_B_DQS0 <19>

DDR_B_DQS#1 <19>

DDR_B_DQS1 <19>

DDR_B_DQS#2 <19>

DDR_B_DQS2 <19>

DDR_B_DQS#3 <19>

DDR_B_DQS3 <19>

DDR_B_DQS#4 <19>

DDR_B_DQS4 <19>

DDR_B_DQS#5 <19>

DDR_B_DQS5 <19>

DDR_B_DQS#6 <19>

DDR_B_DQS6 <19>

DDR_B_DQS#7 <19>

DDR_B_DQS7 <19>

DDR_B_ALERT# <19>

DDR_B_PARITY <19>

DDR_DRAMRST# <18,19>

1 2

RC16 200_0402_1%SDP@

1 2

RC17 80.6_0402_1%

1 2

RC18 100_0402_1%

< For ODT & VTT Power Control >

DDR_VTT_CNTL to DDR

VTT supplied ramped

<35uS

(tCPU18)

UC2

DDR_PG_CTRL

A A

5

NC1VCC

2

A

3

GND

74AUP1G07SE-7 SOT353 5P LOW PW BUFF

SA00007WE00

1

CC1

0.1U_0201_10V6K

@

2

5

4

Y

+3VS+1.2V

12

RC132

100K_0402_5%

4

DDR_VTT_PG_CTRL <45>

DDR_DRAMRST#

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

+1.2V

12

RC20

470_0402_5%

@

1

CC96

100P_0402_50V8J

ESD@

2

Close to CPU

Compal Secret Data

Compal Secret Data

2018/03/09 2019/03/09

2018/03/09 2019/03/09

2018/03/09 2019/03/09

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Recommended By Intel Max

RC16

SD034121090

121_0402_1%

DDP@

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

SKL-U(2/12)DDR3L

SKL-U(2/12)DDR3L

SKL-U(2/12)DDR3L

LA-G201P

LA-G201P

Friday, March 09, 2018

Friday, March 09, 2018

Friday, March 09, 2018

LA-G201P

1

7

7

7

1.0

1.0

1.0

55

55

55

5

www.teknisi-indonesia.com

4

3

2

1

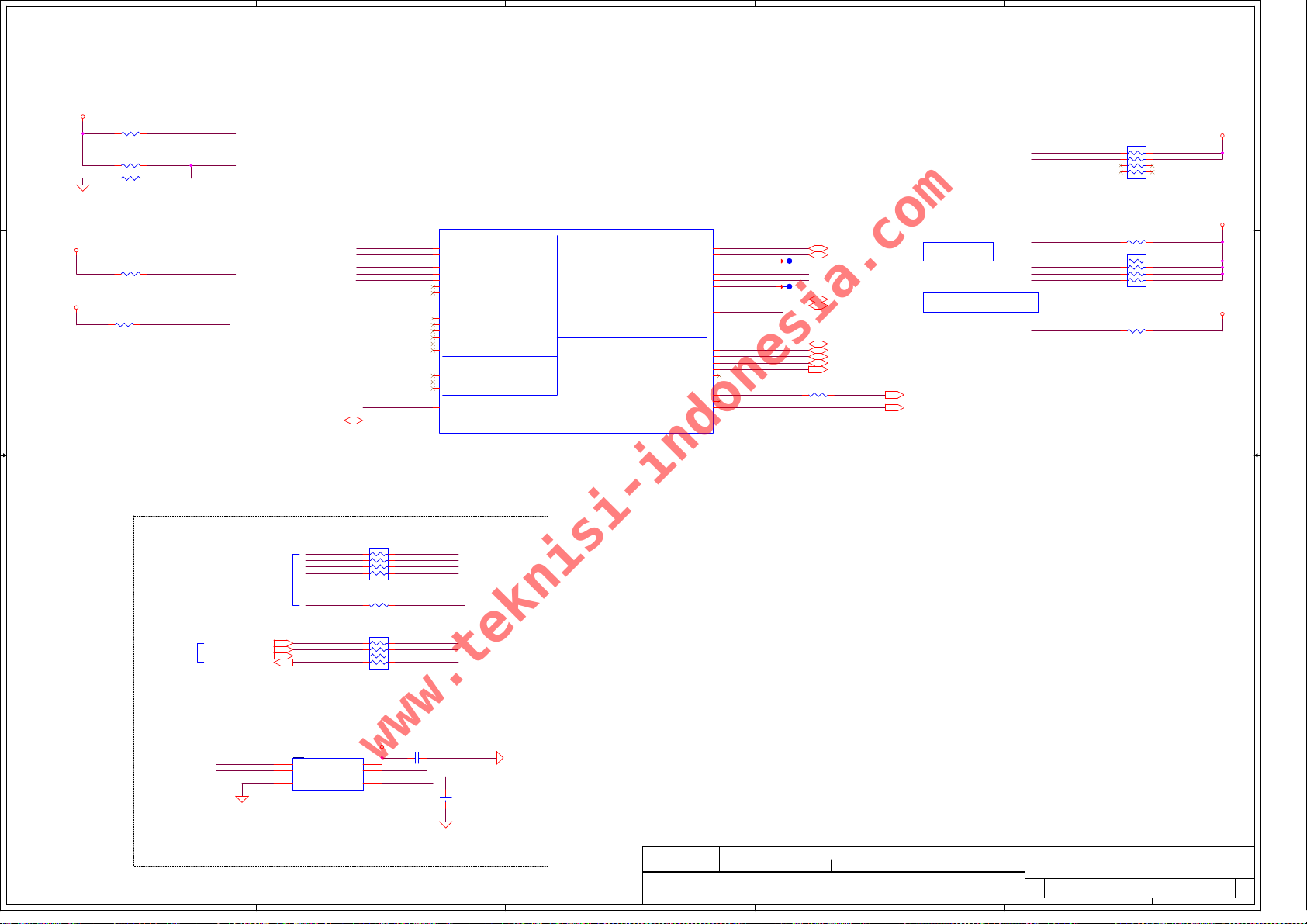

SML0ALERT# (Internal Pull Down):

eSPI or LPC

0 = LPC is selected for EC ==> Default

D D

+3VALW

1 2

RC21 1K_0402_5%@

1 2

RC22 1K_0402_5%@

1 2

RC24 1K_0402_5%@

SOC_SPI_IO2

SOC_SPI_IO3

1 = eSPI is selected for EC

SOC_SML0CLK

SOC_SML0DATA

RPC12

1 8

2 7

3 6

4 5

499_0804_8P4R_1%

+3VS

UC1E

+3VS

1 2

RC112 10K_0402_5%

+3VS

1 2

RC25 8.2K_0402_5%

C C

KB_RST#

SERIRQ

SERIRQ<36>

SOC_SPI_CLK

SOC_SPI_SO

SOC_SPI_SI

SOC_SPI_IO2

SOC_SPI_IO3

SOC_SPI_CS#0

SERIRQ

AW13

AY11

SPI - FLASH

AV2

SPI0_CLK

AW3

SPI0_MISO

AV3

SPI0_MOSI

AW2

SPI0_IO2

AU4

SPI0_IO3

AU3

SPI0_CS0#

AU2

SPI0_CS1#

AU1

SPI0_CS2#

SPI - TOUCH

M2

GPP_D1/SPI1_CLK

M3

GPP_D2/SPI1_MISO

J4

GPP_D3/SPI1_MOSI

V1

GPP_D21/SPI1_IO2

V2

GPP_D22/SPI1_IO3

M1

GPP_D0/SPI1_CS#

C LINK

G3

CL_CLK

G2

CL_DATA

G1

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

SKL-U_BGA1356 @

SKL-U

SMBUS, SMLINK

LPC

GPP_A14/SUS_STAT#/ESPI_RESET#

5 OF 20

Rev_1.0

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

R7

R8

R10

R9

W2

W1

W3

V3

AM7

AY13

BA13

BB13

AY12

BA12

BA11

AW9

AY9

AW11

SOC_SMBCLK

SOC_SMBDATA

SOC_SMBALERT#

SOC_SML0CLK

SOC_SML0DATA

SOC_SML0ALERT#

SOC_SML1ALERT#

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

LPC_CLK0

PM_CLKRUN#KB_RST#

T124TP@

T125TP@

1 2

RC26 22_0402_5%EMI@

SOC_SMBCLK <19>

SOC_SMBDATA <19>

EC_SMB_CK2 <24,36>

EC_SMB_DA2 <24,36>

LPC_AD0 <36>

LPC_AD1 <36>

LPC_AD2 <36>

LPC_AD3 <36>

LPC_FRAME# <36>

SMB

(Link to DDR)

SML1

(Link to EC,DGPU,Thermal Sensor)

CLK_LPC_EC <36>

PM_CLKRUN# <36>

SOC_SML1ALERT#

SOC_SMBCLK

SOC_SMBDATA

EC_SMB_CK2

EC_SMB_DA2

PM_CLKRUN#

RC113 150K_0402_5%@

RC31 8.2K_0402_5%

Follow 543016_SKL_U_Y_PDG_0_9

1 2

RPC2

1 8

2 7

3 6

4 5

1K_0804_8P4R_5%

1 2

+3VS

+3VS

RPC1, RPC3 and RC30 are close to UC3

SOC_SPI_SO

SOC_SPI_CLK SOC_SPI_CLK_0_R

SOC_SPI_SI

B B

From EC

EC_SPI_MISO<36>

EC_SPI_CLK<36>

EC_SPI_MOSI<36>

EC_SPI_CS0#<36>

From SOC

SOC_SPI_IO3

SOC_SPI_IO2

EC_SPI_CLK

EC_SPI_MOSI SOC_SPI_SI_0_R

EC_SPI_CS0#

EC_SPI_MISO

RPC1

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

EMI@

1 2

RC30 33_0402_5%EMI@

RPC3

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

EMI@

SOC_SPI_SO_0_R

SOC_SPI_SI_0_R

SOC_SPI_IO3_0_R

SOC_SPI_IO2_0_R

SOC_SPI_CLK_0_R

SOC_SPI_CS#0

SOC_SPI_SO_0_R

< SPI ROM - 8MB > - Main Source - XMC

+3VALW

@

SOC_SPI_CS#0

SOC_SPI_IO2_0_R

A A

5

UC3

1

/CS

2

DO(IO1)

3

/WP(IO2)

4

GND

S IC FL 64M XM25QH64AHIG SOP 8P

SA0000B8300

/HOLD(IO3)

DI(IO0)

VCC

CLK

1 2

CC2 0.1U_0201_10V K X5R

8

SOC_SPI_IO3_0_RSOC_SPI_SO_0_R

7

SOC_SPI_CLK_0_R

6

SOC_SPI_SI_0_R

5

4

1

CC3

10P_0402_50V8J

2

@EMI@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2018/03/09 2019/03/09

2018/03/09 2019/03/09

2018/03/09 2019/03/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

Compal Electronics, Inc.

SKL-U(3/12)SPI,SMB,LPC,ESPI

SKL-U(3/12)SPI,SMB,LPC,ESPI

SKL-U(3/12)SPI,SMB,LPC,ESPI

LA-G201P

LA-G201P

LA-G201P

1

8 55Friday, March 09, 2018

8 55Friday, March 09, 2018

8 55Friday, March 09, 2018

1.0

1.0

1.0

5

www.teknisi-indonesia.com

D D

4

3

2

1

< HD AUDIO >

HDA_BITCLK_AUDIO<30>

HDA_SYNC_AUDIO<30>

RPC4

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

EMI@

HDA_BIT_CLK

HDA_SYNC

HDA_SDOUT

HDA_SYNC

HDA_BIT_CLK

HDA_SDIN0<30>HDA_SDOUT_AUDIO<30>

HDA_SDOUT

< To Enable ME Override >

1 2

C C

ME_EN<36>

RC116 0_0402_5%

+3VS

1 2

RC33 2.2K_0402_5%@

HDA_SDOUT

HDA_SPKR

HDA_SPKR<30>

HDA_SPKR

SPKR (Internal Pull Down):

B B

TOP Swap Override

0 = Disable TOP Swap mode. ==> Default

1 = Enable TOP Swap Mode.

UC1G

BA22

AY22

BB22

BA21

AY21

AW22

AY20

AW20

AK10

AW5

AK7

AK6

AK9

AUDIO

HDA_SYNC/I2S0_SFRM

HDA_BLK/I2S0_SCLK

HDA_SDO/I2S0_TXD

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_RST#/I2S1_SCLK

J5

GPP_D23/I2S_MCLK

I2S1_SFRM

I2S1_TXD

GPP_F1/I2S2_SFRM

GPP_F0/I2S2_SCLK

GPP_F2/I2S2_TXD

GPP_F3/I2S2_RXD

H5

GPP_D19/DMIC_CLK0

D7

GPP_D20/DMIC_DATA0

D8

GPP_D17/DMIC_CLK1

C8

GPP_D18/DMIC_DATA1

GPP_B14/SPKR

SKL-U_BGA1356 @

UC1I

CSI-2

A36

CSI2_DN0

B36

CSI2_DP0

C38

CSI2_DN1

D38

CSI2_DP1

C36

CSI2_DN2

D36

CSI2_DP2

A38

CSI2_DN3

B38

CSI2_DP3

C31

CSI2_DN4

D31

CSI2_DP4

C33

CSI2_DN5

D33

CSI2_DP5

A31

CSI2_DN6

B31

CSI2_DP6

A33

CSI2_DN7

B33

CSI2_DP7

A29

CSI2_DN8

B29

CSI2_DP8

C28

CSI2_DN9

D28

CSI2_DP9

A27

CSI2_DN10

B27

CSI2_DP10

C27

CSI2_DN11

D27

CSI2_DP11

SKL-U_BGA1356 @

SKL-U

SKL-U

9 OF 20

GPP_A17/SD_PWR_EN#/ISH_GP7

7 OF 20

Rev_1.0

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

SDIO / SDXC

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A16/SD_1P8_SEL

SD_RCOMP

GPP_F23

C37

D37

C32

D32

C29

D29

B26

A26

E13

RC80 100_0402_1%@

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

RC129 200_0402_1%@

Rev_1.0

1 2

1 2

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

AF13

1 2

RC76 200_0402_1%@

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2018/03/09 2019/03/09

2018/03/09 2019/03/09

2018/03/09 2019/03/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Custom

Custom

Custom

Date: Sheet o f

Date: Sheet o f

2

Date: Sheet o f

Compal Electronics, Inc.

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

LA-G201P

LA-G201P

Friday, March 09, 2018

Friday, March 09, 2018

Friday, March 09, 2018

LA-G201P

1

55

55

55

9

9

9

1.0

1.0

1.0

5

www.teknisi-indonesia.com

4

3

2

SOC_XTAL24_IN XTAL24_IN

U22_EMI@

1 2

RC154 33_0402_1%

1

SOC_XTAL24_OUT XTAL24_OUT

D D

DGPU

+3VS

RPC6

VGA_CLKREQ#

18

WLANCLK_REQ#

27

36

LANCLK_REQ#

45

10K_0804_8P4R_5%

+3VL_RTC

C C

1 2

RC36 20K_0402_5%

1 2

CC6 1U_0201_6.3V6M

RC37 20K_0402_5%

CC7 1U_0201_6.3V6M

CLRP2 SHORT PADS

RC39 1M_0402_5%

+3VALW

B B

10K_0804_8P4R_5%

ESD@

CC97 100P_0402_50V8J

ESD@

CC94 100P_0402_50V8J

ESD@

CC95 100P_0402_50V8J

+3VALW

1 2

RC47 1K_0402_5%

RPC7

1 2

1 2

1 2

1 2

1 2

1 2

1 2

18

27

36

45

SE00000UC00

SE00000UC00

PCH_PWROK

EC_RSMRST#

LAN_WAKE#

SYS_RESET#

SYS_RESET#

EC_RSMRST#

SYS_PWROK

WAKE#

EC_SCI# <6,36>

SOC_SRTCRST#

SOC_RTCRST#

CLR CMOS

SM_INTRUDER#

1 2

RC38 0_0402_5%

Only For Power Sequence Debug

From EC (Open-Drain)

A A

5

VCCST_PWRGD<36>

LAN

NGFF WL+BT

+1.0V_VCCST

EC_CLEAR_CMOS# <36>

12

RC52

1K_0402_5%

1

2

CLK_PEG_VGA#<21>

CLK_PEG_VGA<21>

VGA_CLKREQ#<21>

CLK_PCIE_LAN#<31>

CLK_PCIE_LAN<31>

LANCLK_REQ#<31>

CLK_PCIE_WLAN#<33>

CLK_PCIE_WLAN<33>

WLANCLK_REQ#<33>

EC_RSMRST#<36>

T132 TP @

SYS_PWROK<36>

PCH_PWROK<36>

1 2

RC53 60.4_0402_1%

CC117

100P_0402_50V8J

ESD@

4

VGA_CLKREQ#

LANCLK_REQ#

WLANCLK_REQ#

< PCH PLTRST Buffer >

SOC_PLTRST#

SOC_PLTRST#

SYS_RESET#

EC_RSMRST#

H_CPUPWRGD

EC_VCCST_PG

SYS_PWROK

PCH_PWROK

EC_RSMRST#

WAKE#

LAN_WAKE#

EC_VCCST_PG

UC1J

D42

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

AR10

GPP_B5/SRCCLKREQ0#

B42

CLKOUT_PCIE_N1

A42

CLKOUT_PCIE_P1

AT7

GPP_B6/SRCCLKREQ1#

D41

CLKOUT_PCIE_N2

C41

CLKOUT_PCIE_P2

AT8

GPP_B7/SRCCLKREQ2#

D40

CLKOUT_PCIE_N3

C40

CLKOUT_PCIE_P3

AT10

GPP_B8/SRCCLKREQ3#

B40

CLKOUT_PCIE_N4

A40

CLKOUT_PCIE_P4

AU8

GPP_B9/SRCCLKREQ4#

E40

CLKOUT_PCIE_N5

E38

CLKOUT_PCIE_P5

AU7

GPP_B10/SRCCLKREQ5#

SKL-U_BGA1356 @

1 2

RC42 0_0402_5%@

+3VS

5

UC4

1

P

B

2

A

TC7SH08FUF_SSOP5

SA007080100

UC1K

AN10

GPP_B13/PLTRST#

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PWROK

AR13

GPP_A13/SUSWARN#/SUSPWRDNACK

AP11

GPP_A15/SUSACK#

BB15

WAKE#

AM15

GPD2/LAN_WAKE#

AW17

GPD11/LANPHYPC

AT15

GPD7/RSVD

SKL-U_BGA1356 @

G

3

SYSTEM POWER MANAGEMENT

SKL-U

CLOCK SIGNALS

10 OF 20

@

4

Y

3

1

1

0

0

0

0

12

K

P

_

_

R

12

0

0

C

ESD@

4

4

C

4

0

0

C

4

2

2

8

_

_

5

5

0

%

V

8

J

SKL-U

GPP_B11/EXT_PWR_GATE#

11 OF 20

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

GPP_B2/VRALERT#

Rev_1.0

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SUSCLK

XCLK_BIASREF

PCI_RST# <21,31,33,36>

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

GPD9/SLP_WLAN#

GPD6/SLP_A#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

GPP_A11/PME#

INTRUDER#

F43

E43

BA17

SUSCLK

SOC_XTAL24_IN

E37

XTAL24_IN

XTAL24_OUT

RTCX1

RTCX2

SRTCRST#

RTCRST#

Rev_1.0

SLP_SUS#

SLP_LAN#

2018/03/09 2019/03/09

2018/03/09 2019/03/09

2018/03/09 2019/03/09

AT11

AP15

BA16

AY16

AN15

AW15

BB17

AN16

BA15

AY15

AU13

AU11

AP16

AM10

AM11

E35

E42

AM18

AM20

AN18

AM16

SOC_XTAL24_OUT

XCLK_BIASREF

SOC_RTCX1

SOC_RTCX2

SOC_SRTCRST#

SOC_RTCRST#

PM_SLP_S0#

PM_SLP_S3#

PM_SLP_S4#

PM_SLP_S5#

SLP_WLAN#

PM_SLP_A#

PBTN_OUT#

AC_PRESENT_R

PM_BATLOW#

SM_INTRUDER#

SOC_VRALERT#

Compal Secret Data

Compal Secret Data

Compal Secret Data

T130TP@

PM_SLP_S3# <36>

PM_SLP_S4# <36,43,46>

T131TP@

T133TP@

T134TP@

1 2

RC103 0_0402_5%@

Deciphered Date

Deciphered Date

Deciphered Date

2

SUSCLK <33>

U22_EMI@

1 2

RC155 33_0402_1%

SOC_RTCX2

SOC_RTCX1

PBTN_OUT# <36>

AC_PRESENT <24,36>

Custom

Custom

Custom

U22@

1 2

RC34 1M_0402_5%

YC1

U22@

24MHZ_18PF_XRCGB24M000F2P51R0

XCLK_BIASREF

SJ10000UJ00

1

1

U22@

2

7

P

1

_

0

C

4

C

0

4

2

_

5

2

0

V

8

J

1 2

RC35 2.7K_0402_1%

1 2

RC110 60.4_0402_1%@

3

3

NC

NC

2

4

U22@

2

7

P

1

_

0

C

4

C

0

5

2

_

5

2

0

V

8

J

+1.0V_CLK5_F24NS

Follow 546765_2014WW48_Skylake_MOW_Rev_1_0

Stuff 2.7k ohm (RC35) PU for SkyLake-U

Stuff 60.4 ohm (RC110) PD for CannonLake-U

1 2

RC41 10M_0402_5%

YC2

1 2

S CRYSTAL 32.768KHZ 9PF X1A000141000200

SJ10000PW00

6

.

8

1

P

_

C

0

C

4

0

9

2

_

5

2

0

V

8

C

PM_BATLOW#

AC_PRESENT

SOC_VRALERT#

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SKL-U(5/12)CLK,PM,GPIO

SKL-U(5/12)CLK,PM,GPIO

SKL-U(5/12)CLK,PM,GPIO

Size Document Number R ev

Size Document Number R ev

Size Document Number R ev

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

1 2

RC46 8.2K_0402_5%

1 2

RC48 10K_0402_5%@

1 2

RC50 10K_0402_5%@

LA-G201P

LA-G201P

LA-G201P

1

6

.

8

1

P

_

C

0

C

4

0

1

2

0

_

5

2

0

V

8

C

+3VALW

10 55Friday, March 09, 2018

10 55Friday, March 09, 2018

10 55Friday, March 09, 2018

1.0

1.0

1.0

5

www.teknisi-indonesia.com

4

3

2

1

GSPI0_MOSI (Internal Pull Down):

Capacity

No Reboot

0 = Disable No Reboot mode. ==> Default

1 = Enable No Reboot Mode. (PCH will disable the TCO

Timer system reboot feature). This funct i on i s usef ul

D D

when running ITP/XDP.

4GB

GSPI1_MOSI (Internal Pull Down):

Boot BIOS Strap Bit

0 = SPI Mode ==> Default

Capacity

1 = LPC Mode

+3VS

1 2

RC59 4.7K_0402_5%@

RC60 150K_0402_5%@

1 2

C C

+3VS

RPC10

1 8

2 7

3 6

4 5

49.9K_0804_8P4R_1%

RPC8

18

27

36

45

10K_0804_8P4R_5%

+3VS

GSPI0_MOSI

GSPI1_MOSI

UART0_RX

UART0_TX

DGPU_PWR_EN

DGPU_HOLD_RST#

WLBT_OFF#

4GB

Touch PAD

B B

+3VS

RPC11

18

27

36

45

2.2K_0804_8P4R_5%

I2C0_SCL_TP

I2C0_SDA_TP

Description

WITHOUT ON-BOARD RAM

SAMSUNG 2666MHz K4A8G165WC-BCTD)

HYNIX 2666MHz H5AN8G6NCJ R-VKC)

MICRON 2666MHz MT40A512M16LY-075:E)

(

(

(

N/A

N/A

N/A

N/A

Description

WITHOUT ON-BOARD RAM

SAMSUNG 2666MHz K4A8G165WC-BCTD)

HYNIX 2666MHz H5AN8G6NCJ R-VKC)

MICRON 2666MHz MT40A512M16LY-075:E)

(

(

(

N/A

N/A

N/A

N/A

SOC_GPIOB17

GSPI0_MOSI

OBRAM_ID0

OBRAM_ID1

OBRAM_ID2

GSPI1_MOSI

TP_INT#<38>

WLBT_OFF#< 33>

UART0_RX<33>

UART0_TX< 33>

I2C0_SDA_TP<38>

I2C0_SCL_TP<38>

SOC_GPIOC10

X76

N/A

X7677538L13

X7677538L15

X7677538L14

N/A

N/A

N/A

N/A

GPP__B19

OBRAM__ID0 OBRAM__ID1 OBRAM__ID2

0

PART NUMBER (R3)

SA0000B6F10

SA0000BMN10

SA0000ARD30

GPP__B20

0 0

N/A

N/A

N/A

N/A

N/A

GPP__B21

12

RC135

10K_0402_5%

@

12

RC214

10K_0402_5%

X76RAM@

0 0 1

0 1 0

0 1 1

1

0 0

1 0 1

1 1 0

1 1 1

UC1F

LPSS ISH

GPP_B15/GSPI0_CS#

GPP_B16/GSPI0_CLK

GPP_B17/GSPI0_MISO

GPP_B18/GSPI0_MOSI

GPP_B19/GSPI1_CS#

GPP_B20/GSPI1_CLK

GPP_B21/GSPI1_MISO

GPP_B22/GSPI1_MOSI

GPP_C8/UART0_RXD

GPP_C9/UART0_TXD

GPP_C10/UART0_RTS#

GPP_C11/UART0_CTS#

GPP_C20/UART2_RXD

GPP_C21/UART2_TXD

GPP_C22/UART2_RTS#

GPP_C23/UART2_CTS#

GPP_C16/I2C0_SDA

GPP_C17/I2C0_SCL

GPP_C18/I2C1_SDA

GPP_C19/I2C1_SCL

GPP_F4/I2C2_SDA

GPP_F5/I2C2_SCL

GPP_F6/I2C3_SDA

GPP_F7/I2C3_SCL

GPP_F8/I2C4_SDA

GPP_F9/I2C4_SCL

SKL-U_BGA1356 @

AH10

AH11

AH12

AF11

AF12

AN8

AP7

AP8

AR7

AM5

AN7

AP5

AN5

AB1

AB2

W4

AB3

AD1

AD2

AD3

AD4

U7

U6

U8

U9

AH9

SKL-U

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

Sx_EXIT_HOLDOFF# / GPP_A12 / BM_BUSY# / ISH_GP6

6 OF 20

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_D15/ISH_UART0_RTS#

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

+3VS+3VS +3VS

12

RC133

10K_0402_5%

Rev_1.0

GPP_D9

GPP_D10

GPP_D11

GPP_D12

X76RAM@

12

RC134

10K_0402_5%

X76RAM@

P2

P3

HDD_ODD_DETECT

P4

MODEL_SETTING

P1

M4

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

DGPU_PWR_EN

AC1

DGPU_HOLD_RST#

AC2

GPU_ALL_PGOOD

AC3

DGPU_PRSNT

AB4

AY8

BA8

DGPU_SEL

BB7

BA7

AY7

AW7

AP13

OBRAM_ID0 OBRAM_ID1 OBRAM_ID2

12

RC215

10K_0402_5%

X76RAM@

12

RC138

10K_0402_5%

X76RAM@

DGPU_PWR_EN <26,36>

DGPU_HOLD_RST# <21>

GPU_ALL_PGOOD <26>

Function

Mount ODD

Mount 2nd HDD

+3VS

HDD_ODD_DETECT

1 2

RC208 10K_0402_5%

1 2

@

RC207 10K_0402_5%

Function

15"

14"

+3VS

1 2

RC206 10K_0402_5%14@

1 2

RC205 10K_0402_5%15@

Function

DIS 0

UMA Only

+3VS

1 2

RC61 10K_0402_5%UMA@

1 2

RC62 10K_0402_5%DIS@

Function

N16V-GMR1 MX110)

(

N16S-GTR MX130)

(

+3VS

1 2

RC210 10K_0402_5%

1 2

RC209 10K_0402_5%

HDD__ DD__DETECT

O

GPP__D11)

(

0

1

MODEL__SETTING

GPP__ D12)

(

0

1

DGPU__PRSNT

GPP__C15)

(

1

DGPU__SEL

GPP__A20)

(

0

1

N16S_R1@

N16V_R1@

HDD_ODD_DETECT <35>

MODEL_SETTING

DGPU_PRSNT

RC210 N16S_R3@

10K_0402_5%

RC209 N16V_R3@

10K_0402_5%

DGPU_SEL

*N16V - MX110 (Device ID: 0x174E

*N16S - MX130 (Device ID: 0x174D

)

)

SOC_GPIOC10 GP U_EVENT#

SOC_GPIOB17 GC6_FB_EN

A A

1 2

RC204 0_0402_5%

1 2

RC195 0_0402_5%

5

GPU_EVENT# <24>

GC6_FB_EN <24,25>

TO DGPU

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL