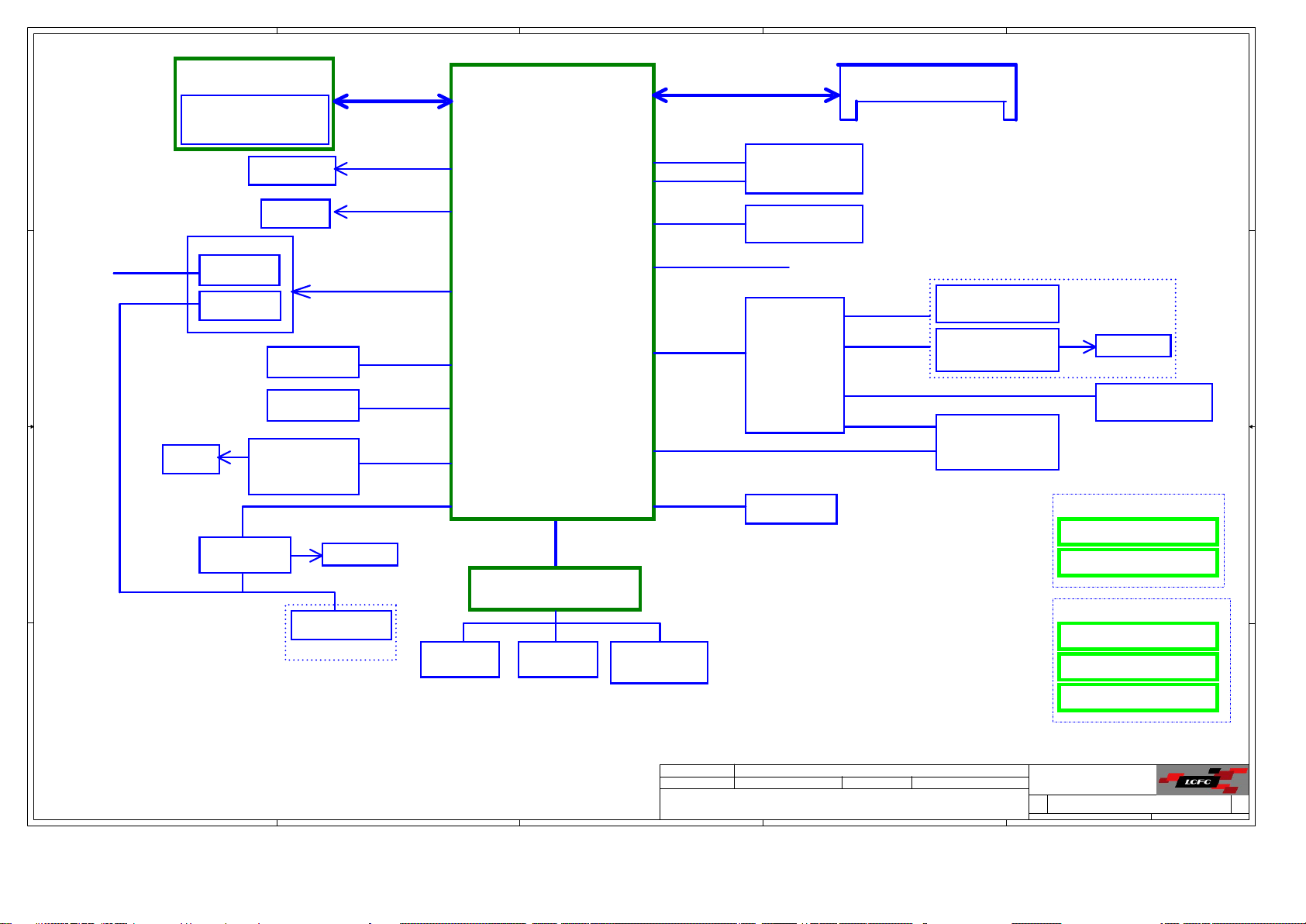

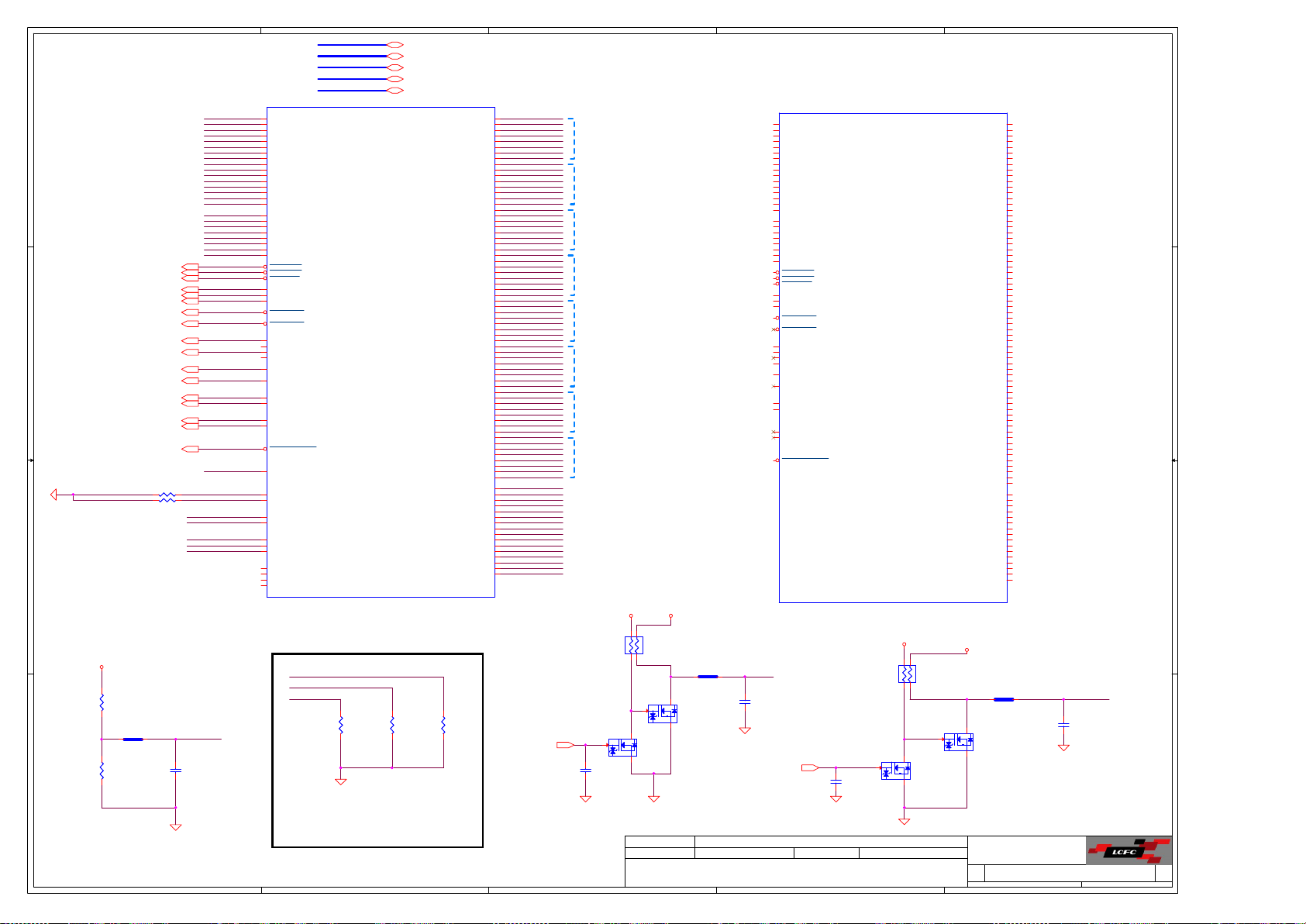

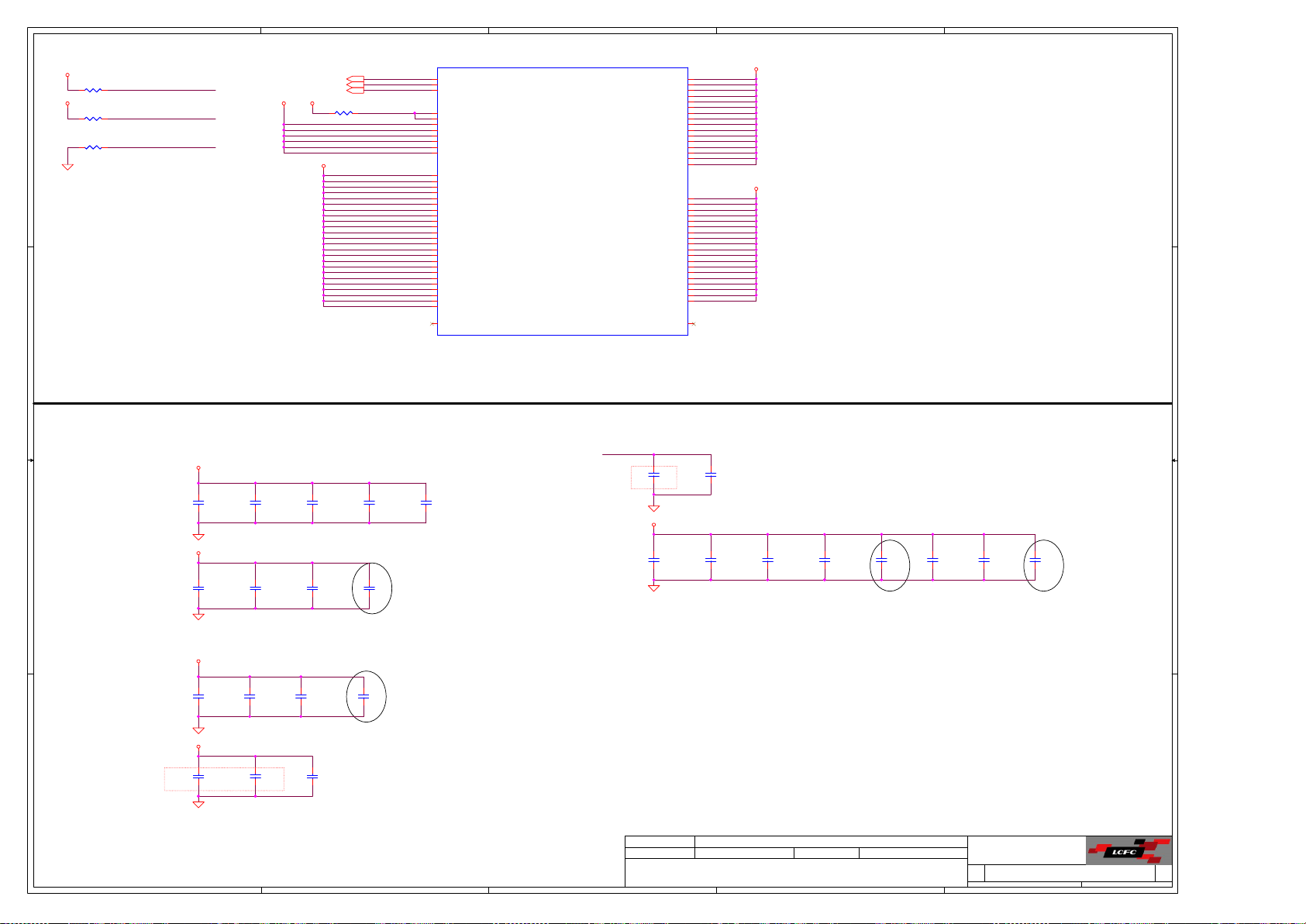

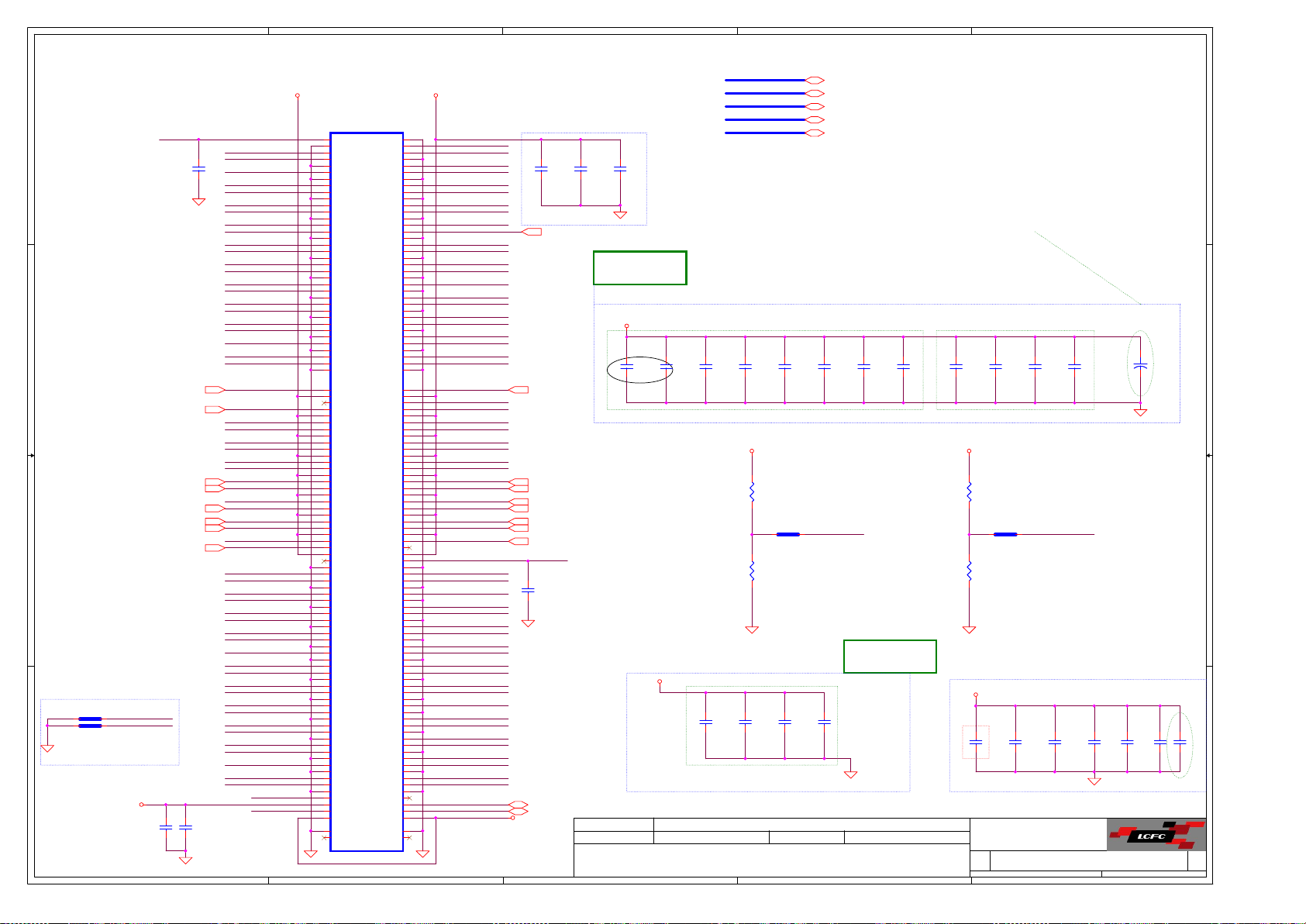

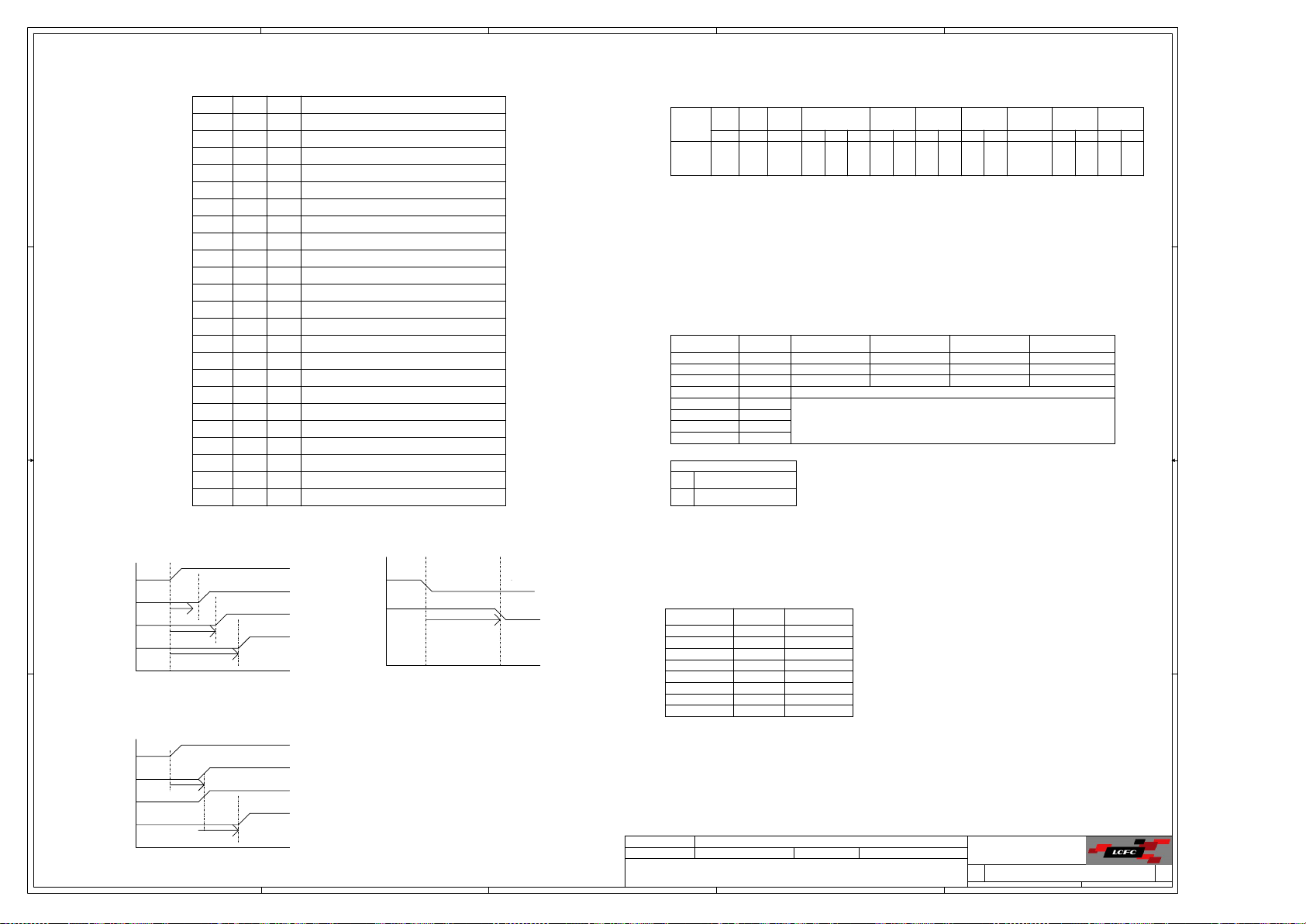

Compal NM-A311 ACLU9, G40-30, G50-30 Schematic

A

1 1

B

C

D

E

L

AC

2 2

3 3

Intel BayTrail M-Processor with DDRIIIL + NV (N15V-GM/N15S-GT) GPU

CFC Confidential

LU9 M/B Schematics Document

013-12-22

2

REV:0.2

4 4

itle

itle

itle

T

T

ecurity Classification

ecurity Classification

ecurity Classification

S

S

S

I

I

I

ssued Date

ssued Date

ssued Date

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

T

T

T

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

C

2

2

2

013/08/08

013/08/08

013/08/08

C Future Center Secret Data

C Future Center Secret Data

C Future Center Secret Data

L

L

L

D

D

D

eciphered Date

eciphered Date

eciphered Date

2013/08/05

2013/08/05

2013/08/05

D

T

C

C

C

over Page

over Page

over Page

ize Document Number Rev

ize Document Number Rev

ize Document Number Rev

S

S

S

C

C

C

ustom

ustom

ustom

M

M

M

onday, December 23, 2013

onday, December 23, 2013

Date: Sheet

Date: Sheet

Date: Sheet

onday, December 23, 2013

ACLU9

ACLU9

ACLU9

E

o

o

o

f

1 59

f

1 59

f

1 59

0

0

0

.2

.2

.2

A

CIe Port5

P

ACLU9

LCFC confid

ential

N

G

P

File Name :

V (N15V-GM/N15S-GT)

B2B-64 Package

age 18~28

VRAM 256/128*16

DR3L*8 4GB/2GB/1GB

1 1

to USB Port

2 2

3 3

D

Page 19~28

J45 Conn.

R

Page 38

eDP Conn

Page 33

DMI Conn.

H

age 34

P

V

Page 36

nt. Camera

I

SB2.0 Port2

U

Int. MIC Conn.

RTL8111GUL (1G)

RTL8106EUL (10M/100M)

Page 37

dec

Co

Conexant CX20752

Page 43

GA Conn.

Page 42

Page 42

AN Realtek

L

ATA Port0

S

ATA Port1

S

PCIe Port1

SP

K Conn.

Page 43

B

P

CI-Express

x Gen2

2

H

DMI

RT

C

DP x2 Lane

e

SATA Gen2SATA HDD

SATA Gen1SATA ODD

PCIe 1x

HD Audio

Page 4~12

Ba

ytrail M (4.5W)

BGA-1170

25mm*27mm

C

M

emory BUS (DDR3L)

Dual Channel

1

.35V DDR3L 1333 MT/s

SB 3.0 1x

U

SB 2.0 1x

U

SB 2.0 1x

U

USB 2.0 1x

SB 2.0 1x

U

PCIe 1x

S

PI BUS

SB Left 3.0 Conn

U

SB 3.0 Port0

U

SB 2.0 Port0

U

U

SB Left 2.0 Conn

U

SB 2.0 Port3

to Camera

SB Hub

U

SB 2.0 Port1

U

PI ROM

S

MB

8

Page 07

P

D

DR3L-SO-DIMM

D

Page 41

age 41

P

USB2.0 1x

U

SB2.0 1x

U

SB2.0 1x

USB2.0 1x

age 16

UP TO 8G

U

Ca

RTS5170

NGFF Card

WLAN&BT

Page 40

ge 14

Pa

SB Right

USB2.0 Hub Port1

rdreader Realtek

U

SB2.0 Hub Port3

PCIe Port0

USB2.0 Hub Port4

E

/MMC Conn.

SD

USB Board

ouch Screen

T

reserved

USB 2.0 Port2

b-board ( for 14")

Su

POWER BOARD

USB Board

Page 33

EC

ITE IT8586E-LQFP

Page 44

HP&Mic Combo Conn.

Su

b-board ( for 15")

POWER BOARD

SB Board

U

4 4

Touch Pad Int.KBD

Page 45 Page 45

Thermal Sensor

NCT7718W

Page 39

SB Board

U

OD

D Board

itle

itle

itle

T

T

ecurity Classification

ecurity Classification

ecurity Classification

S

S

S

ssued Date

ssued Date

ssued Date

I

I

I

TH

TH

TH

IS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

IS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

IS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

C

2

2

2

013/08/08

013/08/08

013/08/08

L

L

L

C Future Center Secret Data

C Future Center Secret Data

C Future Center Secret Data

D

D

D

eciphered Date

eciphered Date

eciphered Date

D

2013/08/05

2013/08/05

2013/08/05

T

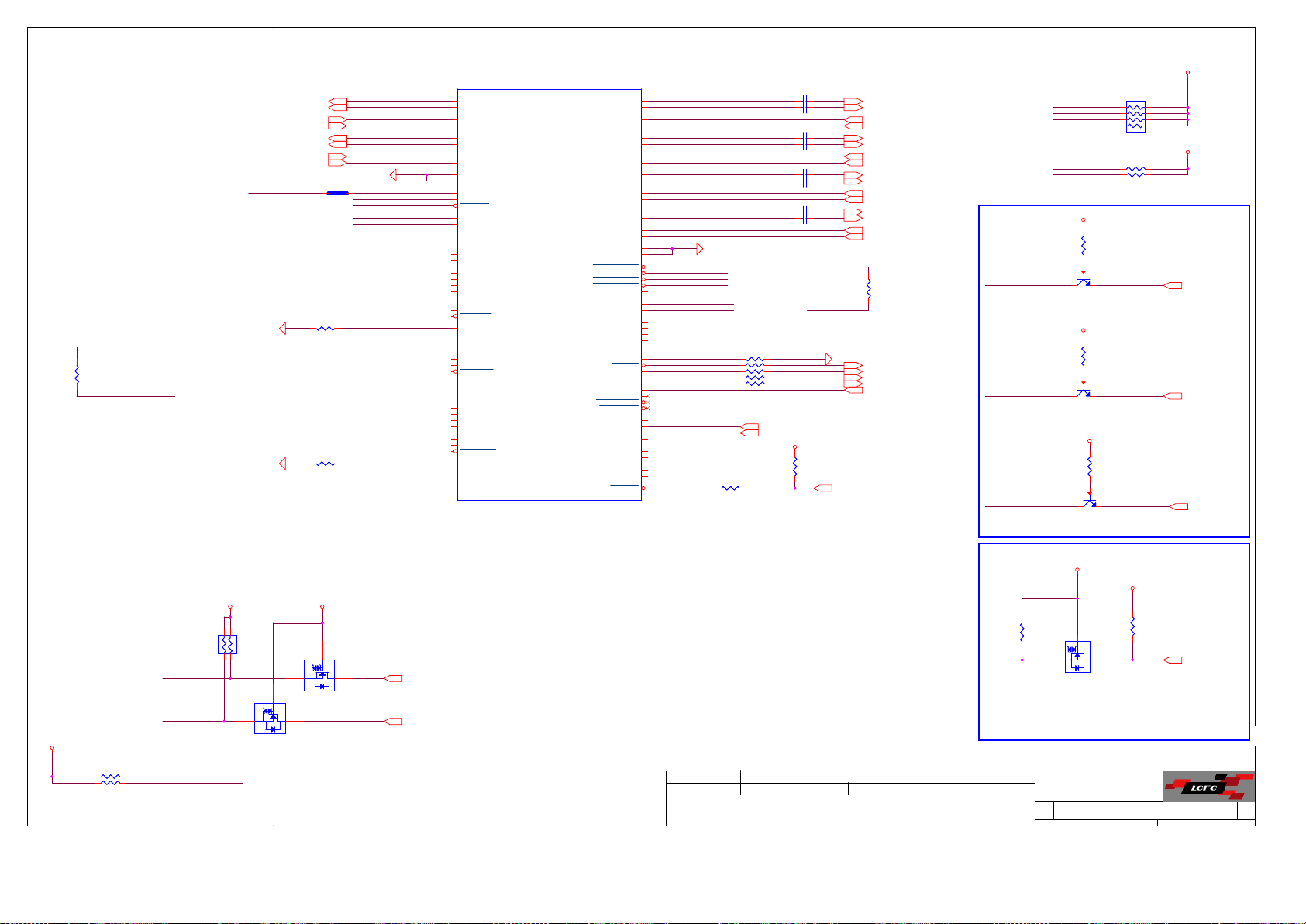

lock Diagram

lock Diagram

lock Diagram

B

B

B

S

S

S

ize Document Number Rev

ize Document Number Rev

ize Document Number Rev

C

C

C

ustom

ustom

ustom

onday, December 23, 2013

onday, December 23, 2013

onday, December 23, 2013

M

M

M

Date: Sheet

Date: Sheet

Date: Sheet

ACLU9

ACLU9

ACLU9

E

o

o

o

f

2 59

f

2 59

f

2 59

0

0

0

.2

.2

.2

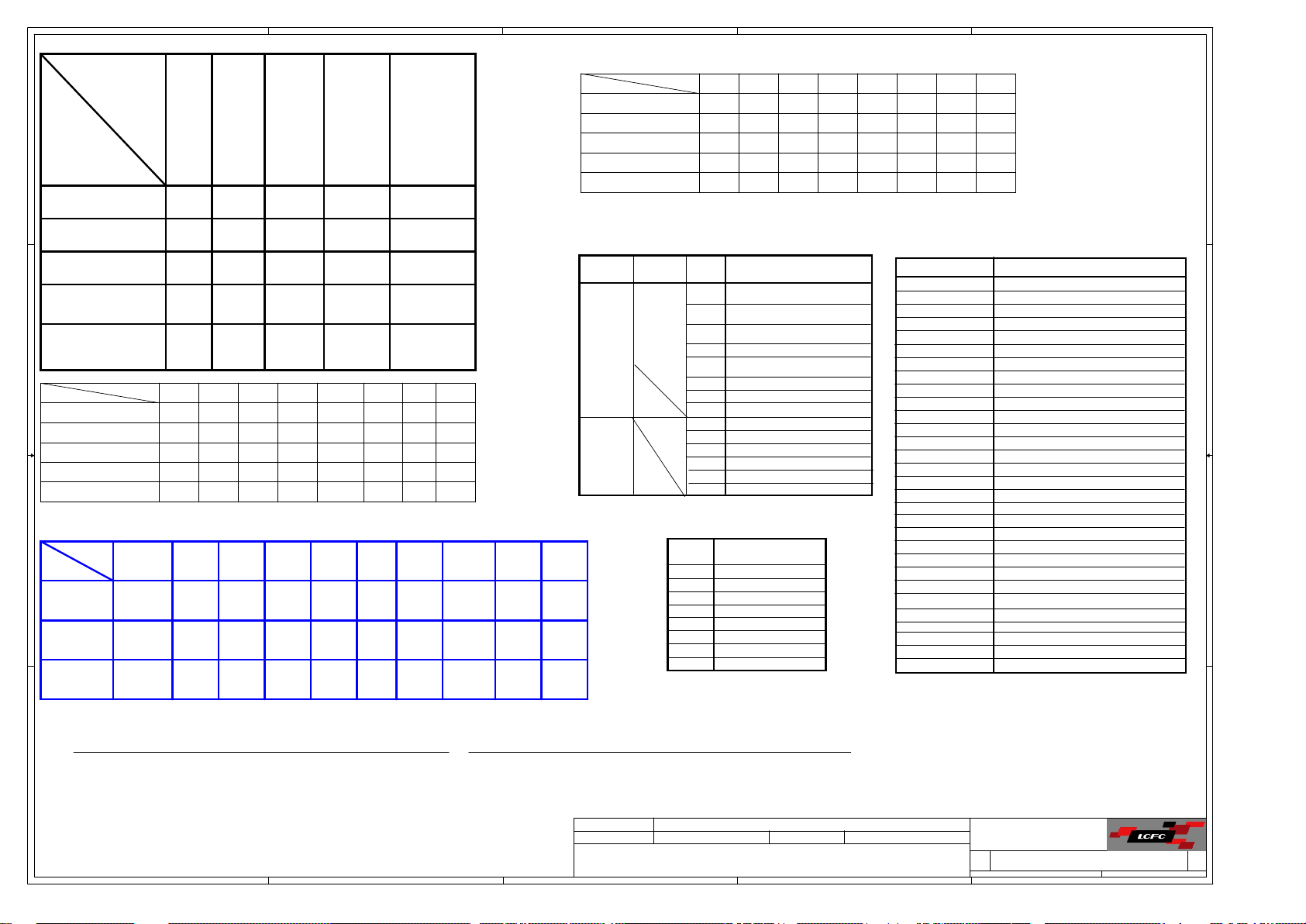

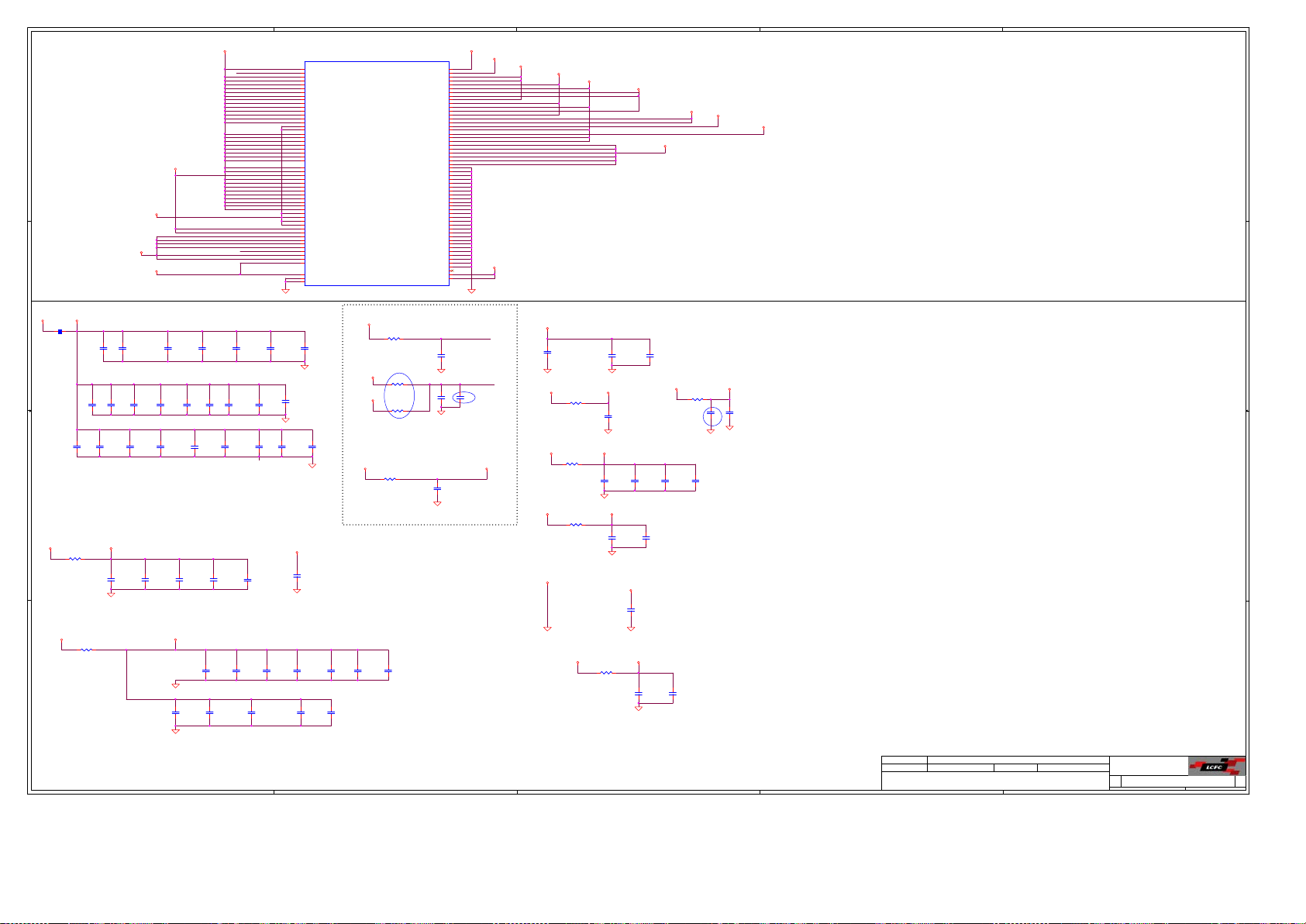

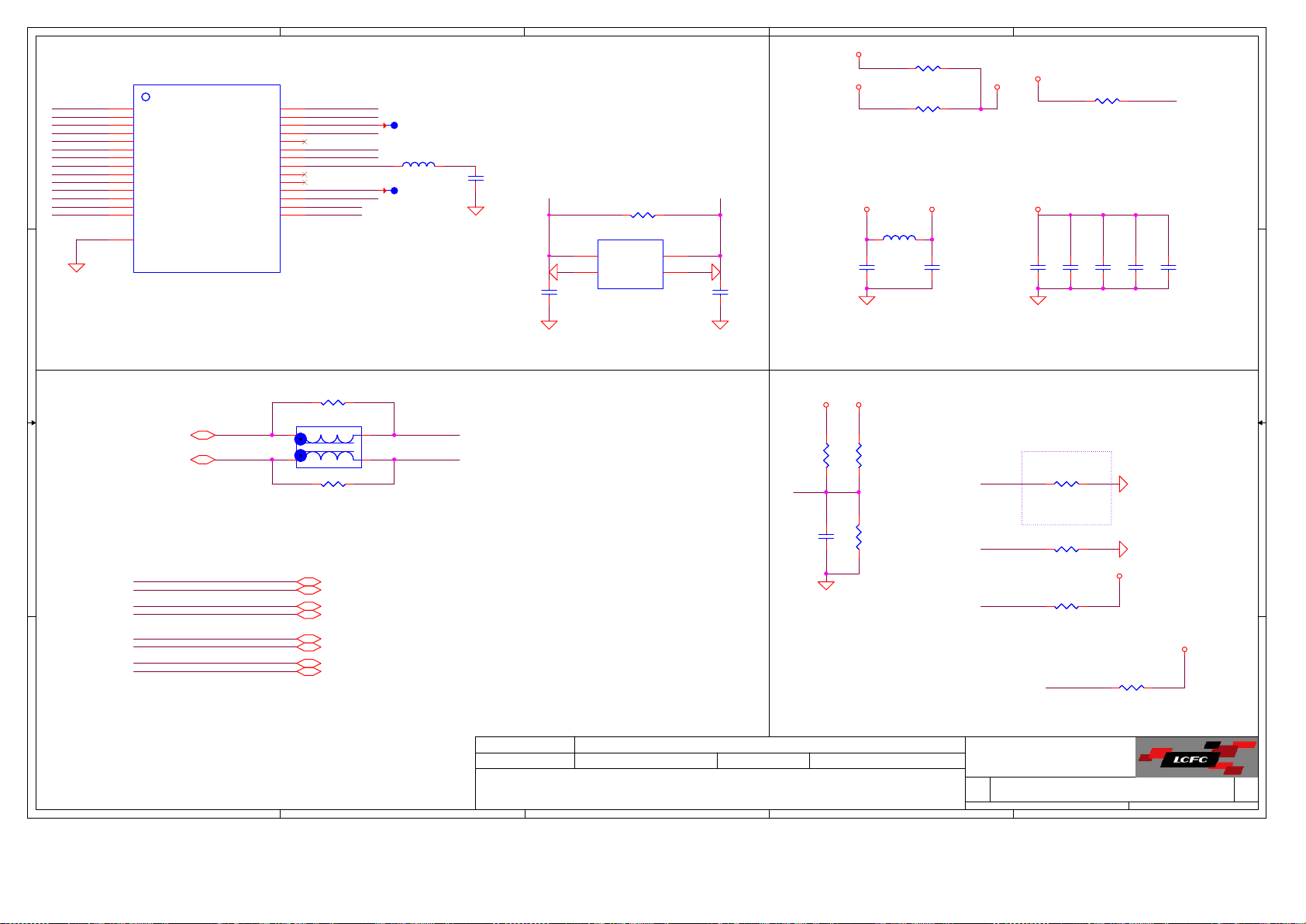

oltage Rails

V

A

,

X --> Means OFF )( O --> Means ON

B

C

D

E

+5VS

P

ower Plane

3VALW_SOC

B

+

+3VALW

3VL

+

1 1

S

tate

0

S

3

S

5 S4/AC Only

S

S5 S4

+5VALW

O

O

O

+

1.0VALW

+

+1.8VALW

O O O

O X X

+

1.35V

O

O

OO O X

O

X

XX

+3VS

+1.5VS

+1.05VS

+0.68VS

CPU_CORE

GFX_CORE

X

TATE

S

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

U

SB Port Table

Battery only

S5 S4

AC & Battery

2 2

XX

X

X

X

EHCI1

don't exist

STATE SLP_S3#SLP_S1#

Full ON

1(Power On Suspend)

S

S3 (Suspend to RAM)

S4 (Suspend to Disk) ON

S5 (Soft OFF)

SIGNAL

SLP_S4# +VS+V

HIGHHIGHHIGH

LOW

HIGH HIGH

LOW

LOW HIGH

LOW

LOW LOW

LOW LOW

LOW OFF

+

VALW

ON

ON

ON

ON

ON

VALW_PCH

+

O

NONON

ONONON

ON

OFF

lock

C

ONON

ON

LOW

OFF OFF

OFF

OFF

OFF

OFF

USB HUB

SIGNAL

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

USB 3.0USB 2.0 Port

XHCI

1

HIGH HIGH HIGH HIGH

HIGH

LOWLOWLOW

HIGHHIGHHIGH

HIGH

HIGH

LOW

LOW

LOW

LOW LOW LOW LOW

3 External

USB Port

0

1

2

3

1

2

3

4

SB Port (Left Side)

U

U

SB Port (Right Side)

U

SB Port (Left Side)

U

SB HUB

amera

C

Cardreader

B

T(WLAN)

TOUCH PANEL

ONONON ON

ON

ON

ON

ON

OFF

ON

ON

OFF

OM Structure Table

B

AOAC@

OPT@

UMA@

14@

15@

100M@

N15SGT@

N15VGM@

GIGA@

GC6@

TS@

RANKA@

RANKB@

ME@

CD@

@

ON

OFF

OFF

OFF

re

LOW

OFF

OFF

OFF

BTO ItemBOM Structu

AOAC support part

PU Part

G

U

MA SKU ID part

For 14" part

F

or 15" part

00M LAN part

1

N

15SGT Part

15GSM Part

N

GIGA LAN Part

PU GC6 Part

G

Touch Screen part

PU VRAM RANKA PART

G

PU VRAM RANKB PART

G

C

onnector

OST DOWN

C

ot stuff

N

S

MBUS Control Table

WLAN

GA BATT SODIMM

0

001 011X b

eed to update

n

A

V

+

3VGS

X

V

X

3 3

EC_SMB_DA1

E

C_SMB_CK2

EC_SMB_DA2

P

CH_SMB_CLK

PCH_SMB_DATA

E

4 4

SOURCE

IT8586EEC_SMB_CK1

+

3VALW

IT8586E

+3VS

PCH

3VALW_PCH

+

C SM Bus1 address

D

evice

mart Battery

S

C

harger

IT8586E

V

+

3VALW

V

X

+3VS

X X X

C SM Bus2 address

E

hermal Sensor EMC1403-2

T

X

V V

+3VS +3VS

D

evice

V

GA

CH

P

WiMAX

X

X

V

A

ddress

1

001_100xb

x9E

0

0

x96

B

Thermal

Sensor

X XV

V

+3VS

+

3VALW_PCH

PCH

TP

harger

c

Module

XX

V

X

X

CH SM Bus address

P

D

evice Address

DR DIMMA

D

lan

W

TP

X

X

X

1

001 000Xb

svd

R

need to update

ecurity Classification

ecurity Classification

ecurity Classification

S

S

S

ssued Date

ssued Date

ssued Date

I

I

I

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

T

T

T

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

C

CIE PORT LIST

P

Port Device

1

D

iscrete GPU

2

D

iscrete GPU

3

4

5

LAN

W

AN

L

6

7

8

L

L

013/08/08

013/08/08

013/08/08

2

2

2

L

C Future Center Secret Data

C Future Center Secret Data

C Future Center Secret Data

eciphered Date

eciphered Date

eciphered Date

D

D

D

D

2013/08/05

2013/08/05

2013/08/05

H4T@

M4T@

S4T@@

H

ynix VRAM Part

Micron VRAM Part

Samsung VRAM Part

itle

itle

itle

T

T

T

N

N

N

otes List

otes List

otes List

ize Document Number Rev

ize Document Number Rev

ize Document Number Rev

S

S

S

C

C

C

ustom

ustom

ustom

M

M

M

onday, December 23, 2013

onday, December 23, 2013

Date: Sheet

Date: Sheet

Date: Sheet

onday, December 23, 2013

ACLU9

ACLU9

ACLU9

E

o

o

o

f

3 59

f

3 59

f

3 59

0

0

0

.2

.2

.2

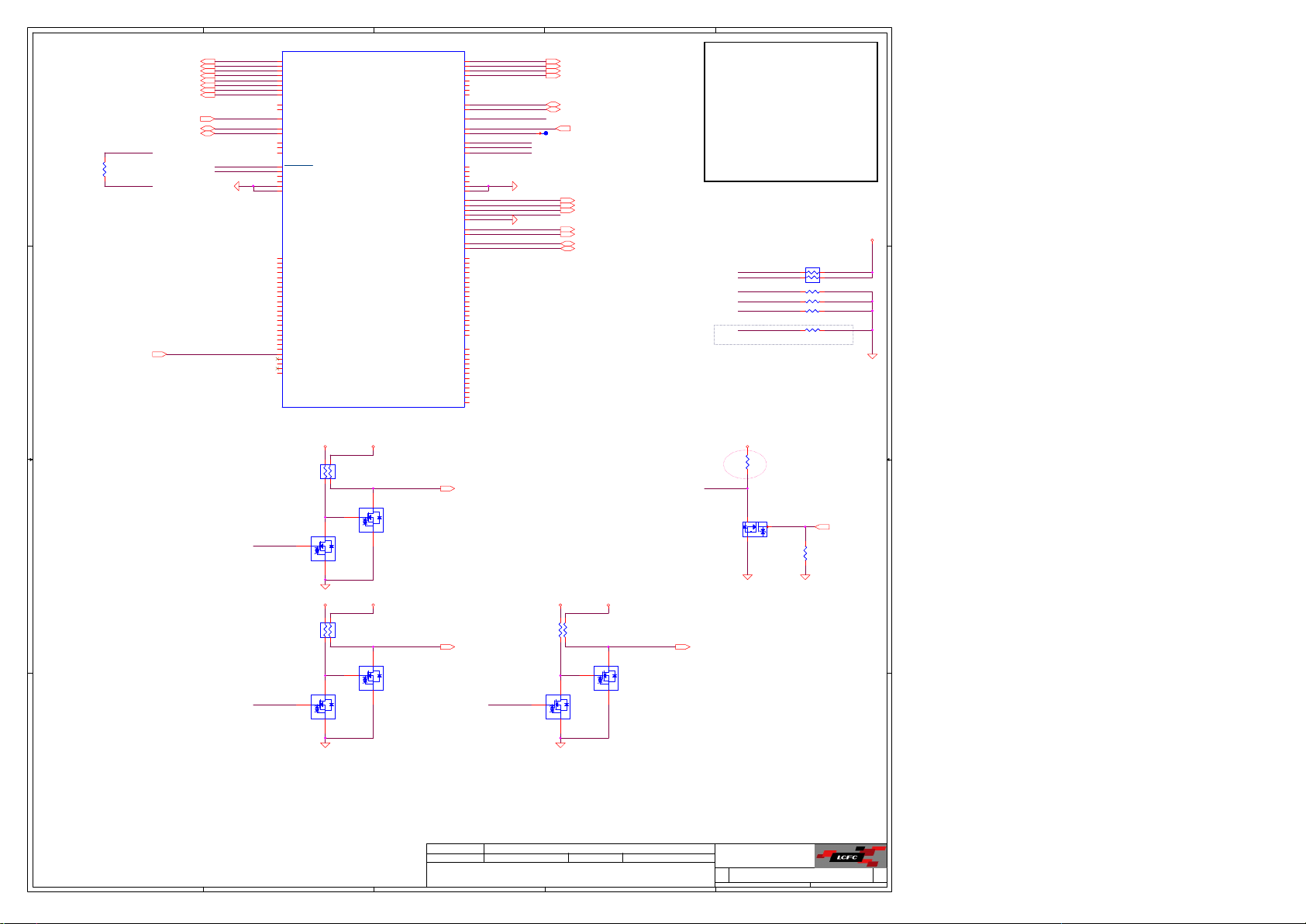

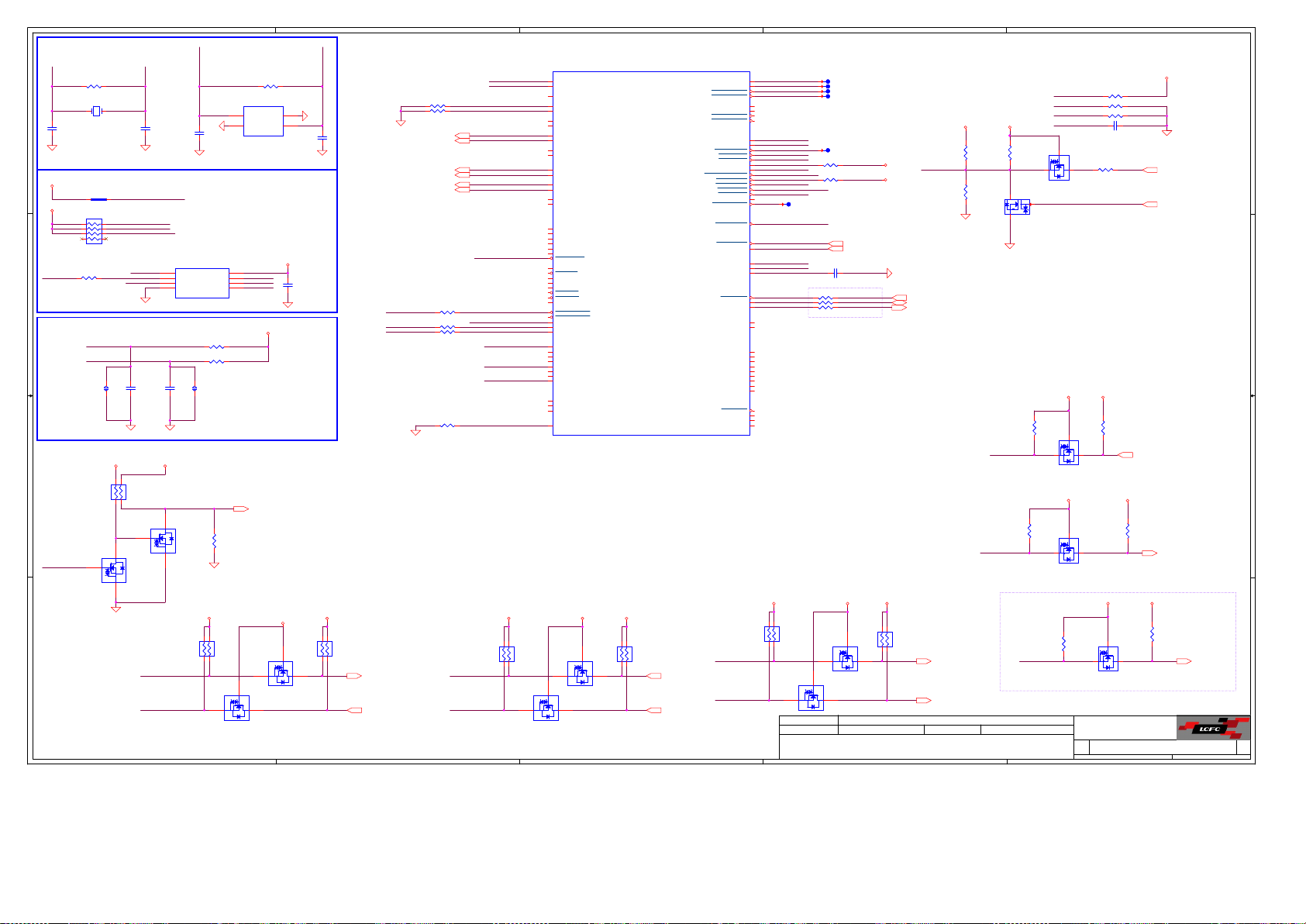

5

DI0_RCOMP_N

D

DI0_RCOMP_P

D

G

H

H

H

H

H

H

H

H

PIO_NC13

DMI_TX2+{34}

H

DMI_TX2-{34}

HDMI D2

HDMI D1

HDMI D0

DMI CLK

H

D D

C C

c

hange dual mos to one mos

B B

D

12

C1

C1

R

R

402_0402_1%

402_0402_1%

D

DI0_RCOMP_N

DI0_RCOMP_P

PIO_NC13{12}

G

H

DMI_TX1+{34}

H

DMI_TX1-{34}

H

DMI_TX0+{34}

H

DMI_TX0-{34}

H

DMI_CLK+{34}

H

DMI_CLK-{34}

H

DMI_HPD{34}

H

DPB_DATA{34}

D

DPB_CLK{34}

D

DMI_TX2+

DMI_TX2DMI_TX1+

DMI_TX1DMI_TX0+

DMI_TX0-

DMI_CLK+

DMI_CLK-

CH_LCD_VDDEN_ Q

P

CH_BKLT_EN_Q

P

4

UC1C

UC1C

AV3

DI0_TXP_0

D

V1P0Sx

AV2

DI0_TXN_0

D

AT2

V1P0Sx

DI0_TXP_1

D

V1P0Sx

AT3

DI0_TXN_1

D

V1P0Sx

AR3

DI0_TXP_2

D

V1P0Sx

AR1

DI0_TXN_2

D

V1P0Sx

AP3

DI0_TXP_3

D

AP2

V1P0Sx

DI0_TXN_3

D

V1P0Sx

AL3

DI0_AUXP

D

V1P0Sx

AL1

DI0_AUXN

D

V1P0Sx

D27

DI0_HPD

D

V1P8S V1P8S

C26

DI0_DDCDATA

D

C28

B28

C27

B26

K13

A

AK12

AM14

AM13

AM3

AM2

T2

T3

AB3

AB2

Y3

Y2

W3

W1

V2

V3

R3

R1

AD6

AD4

AB9

AB7

Y4

Y6

V4

V6

A29

C29

AB14

B30

C30

V1P8S

DI0_DDCCLK

D

V1P8S

DI0_VDDEN

D

V1P8S V1P8S

DI0_BKLTEN

D

V1P8S

DI0_BKLTCTL

D

V1P8S

DI0_RCOMP

D

V1P0Sx

DI0_RCOMP_P

D

V1P0Sx

ESERVED_AM14

R

ESERVED_AM13

R

SS_AM3

V

SS_AM2

V

ESERVED_T2

R

ESERVED_T3

R

ESERVED_AB3

R

ESERVED_AB2

R

ESERVED_Y3

R

ESERVED_Y2

R

ESERVED_W3

R

ESERVED_W1

R

ESERVED_V2

R

ESERVED_V3

R

ESERVED_R3

R

ESERVED_R1

R

ESERVED_AD6

R

ESERVED_AD4

R

ESERVED_AB9

R

ESERVED_AB7

R

ESERVED_Y4

R

ESERVED_Y6

R

ESERVED_V4

R

ESERVED_V6

R

PIO_S0_NC13

G

PIO_S0_NC14_C29

G

ESERVED_AB14

R

PIO_S0_NC12

G

ESERVED_C30

R

BAY-TRAIL-M-SOC_FCBGA1170

BAY-TRAIL-M-SOC_FCBGA1170

@

@

RESERVED_VS

RESERVED_VSS1

2

G

1

2

G

1

3VALW

+

1.8VALW

+

1 4

2 3

1 6

D

11

S

1 4

2 3

1 6

D

11

S

S0

RESERVED_A2

RESERVED_C29

V1P8S

R

R

10K_0404_4P2R_5%

10K_0404_4P2R_5%

Q

Q

PJT138K_SOT363-6

PJT138K_SOT363-6

R

R

10K_0404_4P2R_5%

10K_0404_4P2R_5%

Q

Q

PJT138K_SOT363-6

PJT138K_SOT363-6

V1P8S

V1P8S

V1P8S

V1P8S

RESERVED_VSS2

RESERVED_VSS3

VVGA_GPIO

VVGA_GPIO

VVGA_GPIO

VVGA_GPIO

3VS

+

2 3

D

2

S

4

3VS

+

2 3

D

2

S

4

V1P8S

RESERVED_D32

RESERVED_N32

RESERVED_J34

RESERVED_K28

RESERVED_F28

RESERVED_F32

RESERVED_D34

RESERVED_J28

RESERVED_D28

RESERVED_M32

RESERVED_F34

C1B

C1B

Q

Q

PJT138K_SOT363-6

PJT138K_SOT363-6

C2B

C2B

Q

Q

PJT138K_SOT363-6

PJT138K_SOT363-6

9

OF 13 REV = 1.15 ?

OF 13 REV = 1.15 ?

3

3

PC24

PC24

25

G

C1A

C1A

PC25

PC25

25

G

C2A

C2A

V1P0Sx

V1P0Sx

V1P0Sx

V1P0Sx

V1P0Sx

V1P0Sx

V1P0Sx

V1P0Sx

V1P0Sx

V1P0Sx

DI1_DDCDATA

D

DI1_DDCCLK

D

D

D

DI1_BKLTCTL

D

ESERVED_AH14

R

ESERVED_AH13

R

ESERVED_AF14

R

ESERVED_AF13

R

V

GA_DDCDATA

V

ESERVED_T7

R

ESERVED_T9

R

ESERVED_AB13

R

ESERVED_AB12

R

ESERVED_Y12

R

ESERVED_Y13

R

ESERVED_V10

R

ESERVED_V9

R

ESERVED_T12

R

ESERVED_T10

R

ESERVED_V14

R

ESERVED_V13

R

ESERVED_T14

R

ESERVED_T13

R

ESERVED_T6

R

ESERVED_T4

R

ESERVED_P14

R

ESERVED_K34

R

PIO_S0_NC26

G

PIO_S0_NC25

G

PIO_S0_NC24

G

PIO_S0_NC23

G

PIO_S0_NC22

G

PIO_S0_NC21

G

PIO_S0_NC20

G

PIO_S0_NC18

G

PIO_S0_NC17

G

PIO_S0_NC16

G

PIO_S0_NC15

G

DI1_TXP_0

D

DI1_TXN_0

D

DI1_TXP_1

D

DI1_TXN_1

D

DI1_TXP_2

D

DI1_TXN_2

D

DI1_TXP_3

D

DI1_TXN_3

D

DI1_AUXP

D

DI1_AUXN

D

DI1_HPD

D

DI1_VDDEN

DI1_BKLTEN

SS_AH3

V

SS_AH2

V

GA_RED

V

GA_BLUE

V

GA_GREEN

V

GA_IREF

V

GA_IRTN

V

GA_HSYNC

V

GA_VSYNC

V

GA_DDCCLK

3

AG3

AG1

AF3

AF2

AD3

AD2

AC3

AC1

AK3

AK2

K30

P30

G30

N30

J30

M30

AH14

AH13

AF14

AF13

AH3

AH2

BA3

AY2

BA1

AW1

AY3

BD2

BF2

BC1

BC2

T7

T9

AB13

AB12

Y12

Y13

V10

V9

T12

T10

V14

V13

T14

T13

T6

T4

P14

K34

D32

N32

J34

K28

F28

F32

D34

J28

D28

M32

F34

CH_ENVDD {33}

P

CH_ENBKL {33}

P

PU_EDP_TX0+

C

PU_EDP_TX0-

C

PU_EDP_TX1+

C

PU_EDP_TX1-

C

PU_EDP_AUX

C

PU_EDP_AUX#

C

DP_HPD

E

DI1_DDCDATA

D

CH_LCD_VDDEN_ Q

P

CH_BKLT_EN_Q

P

CH_BKLT_CTRL_Q

P

RT_R

C

RT_B

C

RT_G

C

RT_IREF

C

GA_HS

V

GA_VS

V

GA_DDC_CLK

V

GA_DDC_DAT

V

XDP

CH_BKLT_CTRL_Q

P

1

R

R

10K_0402_5%

10K_0402_5%

2

P11@TP11@

T

+

C972

C972

G

1

PU_EDP_TX0+ {33}

C

PU_EDP_TX0- {33}

C

PU_EDP_TX1+ {33}

C

PU_EDP_TX1- {33}

C

PU_EDP_AUX {33}

C

PU_EDP_AUX# {33}

C

DI1_DDCDATA {12}

D

V

V

3VALW

12

12

R

R

C973

C973

10K_0402_5%

10K_0402_5%

1 6

Q

Q

C198A

C198A

D

PJT138K_SOT363-6

PJT138K_SOT363-6

11

S

RT_R {36}

C

RT_B {36}

C

RT_G {36}

C

GA_HS {36}

V

GA_VS {36}

V

GA_DDC_CLK {36}

GA_DDC_DAT {3 6}

3VS

+

2 3

D

25

G

2

S

4

2

E

DP

C198B

C198B

Q

Q

PJT138K_SOT363-6

PJT138K_SOT363-6

Port

DDI PROCESSOR Pin Names

Port 0

DDI0_TXP_0

DDI0_TXN_0

DDI0_TXP_1

DDI0_TXN_1

DDI0_TXP_2

DDI0_TXN_2

DDI0_TXP_3

DDI0_TXP_3

DDI0_HPD

DDI0_DDCDATA

DDI0_DDCCLK

Port

DDI PROCESSOR Pin Names

Port 1

DDI1_TXP_0

DDI1_TXN_0

DDI1_TXP_1

DDI1_TXN_1

DDI1_AUXP

DDI1_AUXN

DDI1_HPD

GA_DDC_CLK

V

GA_DDC_DAT

V

RT_R

C

C

C

C

n

4602 change from 10K to 1K,

R

as Vienna

+

DP_HPD

E

C3

C3

Q

Q

604

0

R

R

RT_B

R

R

RT_G

R

R

RT_IREF

R

R

eed to change 357 1%

1.8VS

4602

4602

R

R

1K_0402_1%

1K_0402_1%

1 2

13

D

D

2

G

G

S

S

2N7002KW_SOT32 3-3

2N7002KW_SOT32 3-3

EDP_HPD

CH_EDP_PWM {33 }

P

1

HDMI* Mapping

HDMI_TX2+

HDMI_TX2HDMI_TX1+

HDMI_TX1HDMI_TX0+

HDMI_TX0HDMI_CLK+

HDMI_CLKHDMI_HPD

DDPB_DAT

DDPB_CLK

EDP* Mapping

CPU_EDP_TX0+

CPU_EDP_TX0CPU_EDP_TX1+

CPU_EDP_TX1CPU_EDP_AUX

CPU_EDP_AUX#

EDP_HPD

PC16

PC16

R

R

23

14

2.2K_0404_4P2R_5%

2.2K_0404_4P2R_5%

12

C5 150_0402_1%

C5 150_0402_1%

12

C6 150_0402_1%

C6 150_0402_1%

12

C7 150_0402_1%

C7 150_0402_1%

1 2

C4 357_0402_1%

C4 357_0402_1%

PU_EDP_HPD {33}

C

12

4603

4603

R

R

100K_0402_5%

100K_0402_5%

3VS

+

A A

itle

itle

itle

T

T

S

S

S

ecurity Classification

ecurity Classification

ecurity Classification

I

I

I

ssued Date

ssued Date

ssued Date

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

T

T

T

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2

2

2

013/03/2 6

013/03/2 6

013/03/2 6

C Future Center Secret Data

C Future Center Secret Data

C Future Center Secret Data

L

L

L

eciphered Date

eciphered Date

eciphered Date

D

D

D

2013/02/01

2013/02/01

2013/02/01

2

T

OC (DDI,EDP)

OC (DDI,EDP)

OC (DDI,EDP)

S

S

S

Size Document Number R ev

ize Document Number R ev

ize Document Number R ev

S

S

C

C

C

ustom

ustom

ustom

Date: Sheetof

Date: Sheetof

Date: Sheetof

ACLU9

ACLU9

ACLU9

onday, December 23, 2013

onday, December 23, 2013

onday, December 23, 2013

M

M

M

4 59

4 59

4 59

1

0

0

0

.2

.2

.2

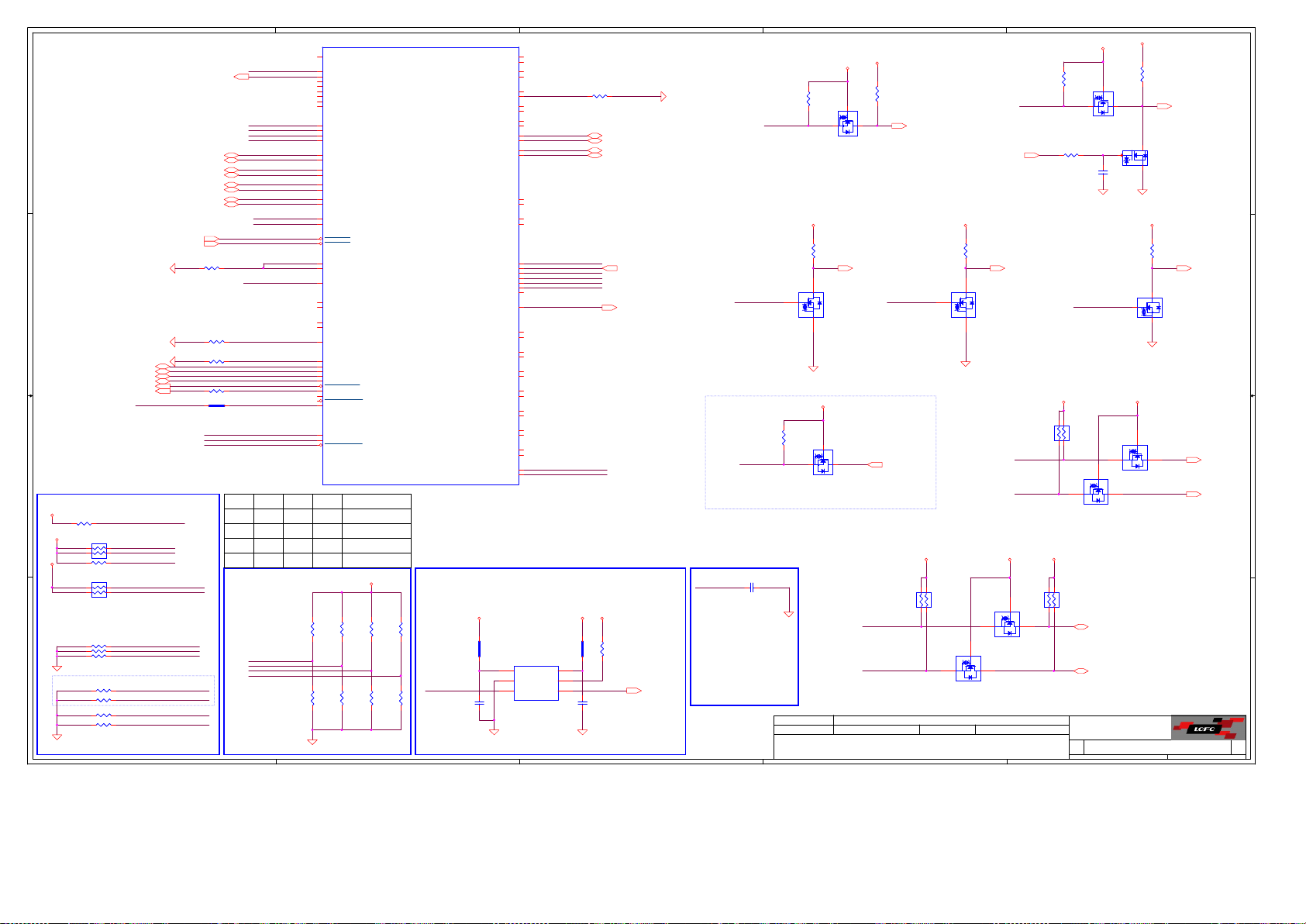

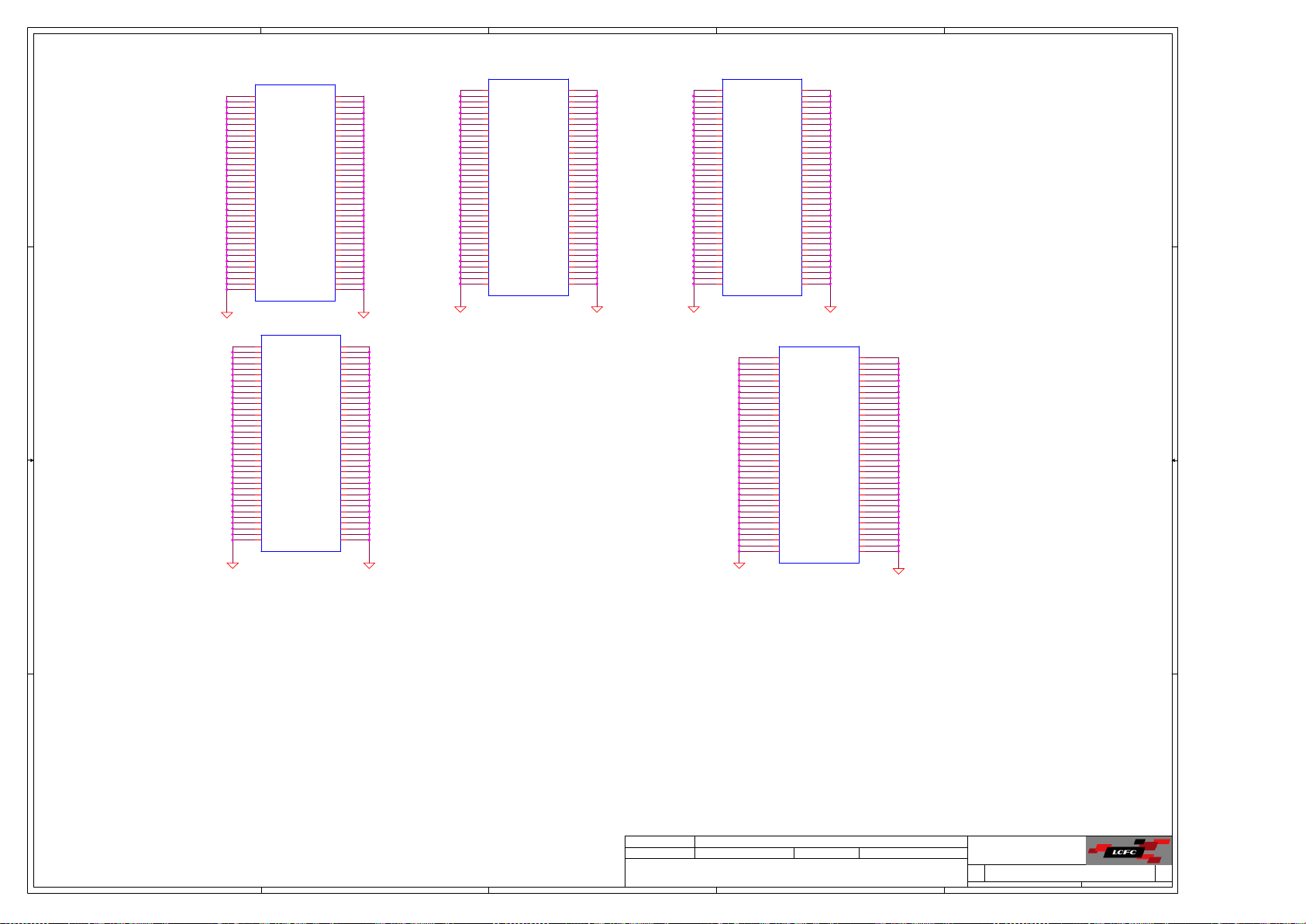

5

UC1A

UC1A

K45

D

DRA_MA0

DRA_MA1

D

DDRA_MA2

D

DRA_MA3

DRA_MA4

12

CLK_DRAM_TERMN_0ICLK_DRAM_TERMN_0

I

12

I

CLK_DRAM_TERMN_1ICLK_DRAM_TERMN_1

DR_PWROK

D

DR_CORE_PWROK

D

S

M_RCOMP_0

S

M_RCOMP_1

S

M_RCOMP_2

D

DRA_MA5

D

D

DRA_MA6

DRA_MA7

D

DDRA_MA8

D

DRA_MA9

DRA_MA10

D

DRA_MA11

D

D

DRA_MA12

D

DRA_MA13

D

DRA_MA14

D

DRA_MA15

DDRA_DM0

D

DRA_DM1

DRA_DM3

D

DRA_DM2

D

D

DRA_DM4

DRA_DM6

D

DDRA_DM7

D

DRA_DM5

DRAM_VREF

D D

Swap Group 2 to Group 3

Swap Group to 6\7\5

DDRA_RAS#{14}

D

DRA_CAS#{14}

D

DRA_WE#{14}

DDRA_BS0#{14}

D

DRA_BS1#{14}

DDRA_BS2#{14}

DRA_CS0#{14}

D

D

DRA_CS1#{14}

D

DRA_CKE0{14}

C C

B B

DDRA_CKE1{14}

DRA_ODT0{14}

D

D

DRA_ODT1{14}

DRA_CLK0{14}

D

DRA_CLK0#{14}

D

DRA_CLK1{14}

D

DRA_CLK1#{14}

D

DRA_DRAMRST#{14}

D

R

C19100K_0402_1%RC19100K_0402_1%

R

C20100K_0402_1%RC20100K_0402_1%

RAM0_MA_00

D

H47

RAM0_MA_11

D

L41

RAM0_MA_22

D

H44

RAM0_MA_33

D

H50

RAM0_MA_44

D

G53

RAM0_MA_55

D

H49

RAM0_MA_66

D

D50

RAM0_MA_77

D

G52

RAM0_MA_88

D

E52

RAM0_MA_99

D

K48

RAM0_MA_1010

D

E51

RAM0_MA_1111

D

F47

RAM0_MA_1212

D

J51

RAM0_MA_1313

D

B49

RAM0_MA_1414

D

B50

RAM0_MA_1515

D

G36

RAM0_DM_0 0

D

B36

RAM0_DM_1 1

D

F38

RAM0_DM_2 2

D

B42

RAM0_DM_3 3

D

P51

RAM0_DM_4 4

D

V42

RAM0_DM_5 5

D

Y50

RAM0_DM_6 6

D

Y52

RAM0_DM_7 7

D

45

M

RAM0_RAS

D

44

M

RAM0_CAS

D

51

H

RAM0_WE

D

K47

RAM0_BS_ 00

D

K44

RAM0_BS_ 11

D

D52

RAM0_BS_ 22

D

44

P

RAM0_CS_0

D

45

P

RAM0_CS_2

D

C47

RAM0_CKE_00

D

D48

ESERVED_ D48

R

F44

RAM0_CKE_22

D

E46

ESERVED_ E46

R

T41

RAM0_ODT_0

D

P42

RAM0_ODT_2

D

M50

RAM0_CKP_0

D

M48

D

RAM0_CKN_ 0

P50

RAM0_CKP_2

D

P48

D

RAM0_CKN_ 2

41

P

D

RAM0_DRAMRST

AF44

D

RAM_VREF

AH42

I

CLK_DRAM_ TERMN

AF42

CLK_DRAM_ TERMN_AF42

I

AD42

D

RAM_VDD_S 4_PWROK

AB42

RAM_CORE_ PWROK

D

AD44

RAM_RCOMP_ 00

D

AF45

RAM_RCOMP_ 11

D

AD45

RAM_RCOMP_ 22

D

AF40

ESERVED_ AF40

R

AF41

ESERVED_ AF41

R

AD40

ESERVED_ AD40

R

AD41

R

ESERVED_ AD41

BAY-TRAIL-M-SOC_FCBGA1170

BAY-TRAIL-M-SOC_FCBGA1170

@

@

ICLK_DRAM_T

ERM_1

EV = 1.15

EV = 1.15

4

1 OF 13

1 OF 13

DDRA_DQ[63:0] {14}

DRA_MA[15:0] {14}

D

D

DRA_DQS[7:0] {14}

DRA_DQS#[7:0] {14}

D

DRA_DM[7:0] {14}

D

?R

?R

RAM0_DQ_00

D

RAM0_DQ_11

D

RAM0_DQ_22

D

RAM0_DQ_33

D

RAM0_DQ_44

D

RAM0_DQ_55

D

RAM0_DQ_66

D

RAM0_DQ_77

D

RAM0_DQ_88

D

RAM0_DQ09_C32

D

RAM0_DQ_1010

D

RAM0_DQ_1111

D

RAM0_DQ_1212

D

RAM0_DQ_1313

D

RAM0_DQ_1414

D

RAM0_DQ_1515

D

RAM0_DQ_1616

D

RAM0_DQ_1717

D

RAM0_DQ_1818

D

RAM0_DQ_1919

D

RAM0_DQ_2020

D

RAM0_DQ_2121

D

RAM0_DQ_2222

D

RAM0_DQ_2323

D

RAM0_DQ_2424

D

RAM0_DQ_2525

D

RAM0_DQ_2626

D

RAM0_DQ_2727

D

RAM0_DQ_2828

D

RAM0_DQ_2929

D

RAM0_DQ_3030

D

RAM0_DQ_3131

D

RAM0_DQ_3232

D

RAM0_DQ_3333

D

RAM0_DQ_3434

D

RAM0_DQ_3535

D

RAM0_DQ_3636

D

RAM0_DQ_3737

D

RAM0_DQ_3838

D

RAM0_DQ_3939

D

RAM0_DQ_4040

D

RAM0_DQ_4141

D

RAM0_DQ_4242

D

RAM0_DQ_4343

D

RAM0_DQ_4444

D

RAM0_DQ_4545

D

RAM0_DQ_4646

D

RAM0_DQ_4747

D

RAM0_DQ_4848

D

RAM0_DQ_4949

D

D

RAM0_DQ_5050

D

RAM0_DQ_5151

RAM0_DQ_5252

D

RAM0_DQ_5353

D

D

RAM0_DQ_5454

RAM0_DQ_5555

D

RAM0_DQ_5656

D

RAM0_DQ_5757

D

D

RAM0_DQ_5858

RAM0_DQ_5959

D

RAM0_DQ_6060

D

RAM0_DQ_6161

D

D

RAM0_DQ_6262

RAM0_DQ_6363

D

RAM0_DQSP_00

D

D

RAM0_DQSN_00

RAM0_DQSP_11

D

RAM0_DQSN_11

D

D

RAM0_DQSP_22

D

RAM0_DQSN_22

RAM0_DQSP_33

D

RAM0_DQSN_33

D

RAM0_DQSP_44

D

RAM0_DQSN_44

D

RAM0_DQSP_55

D

RAM0_DQSN_55

D

D

RAM0_DQSP_66

D

RAM0_DQSN_66

RAM0_DQSP_77

D

RAM0_DQSN_77

D

M36

J36

P40

M40

P36

N36

K40

K42

B32

C32

C36

A37

C33

A33

C37

B38

F36

G38

F42

J42

G40

C38

G44

D42

A41

C41

A45

B46

C40

B40

B48

B47

K52

K51

T52

T51

L51

L53

R51

R53

T47

T45

Y40

V41

T48

T50

Y42

AB40

V45

V47

AD48

AD50

V48

V50

AB44

Y45

V52

W51

AC53

AC51

W53

Y51

AD52

AD51

J38

K38

C35

B34

D40

F40

B44

C43

N53

M52

T42

T44

Y47

Y48

AB52

AA51

D

DRA_DQ0

DRA_DQ1

D

DDRA_DQ2

D

DRA_DQ3

DRA_DQ4

D

DRA_DQ5

D

D

DRA_DQ6

DRA_DQ7

D

DDRA_DQ8

D

DRA_DQ9

DRA_DQ10

D

DRA_DQ11

D

D

DRA_DQ12

D

DRA_DQ13

D

DRA_DQ14

D

DRA_DQ15

DRA_DQ24

D

DDRA_DQ25

D

DRA_DQ26

DRA_DQ27

D

DRA_DQ28

D

D

DRA_DQ29

DRA_DQ30

D

DDRA_DQ31

D

DRA_DQ16

DRA_DQ17

D

DRA_DQ18

D

D

DRA_DQ19

D

DRA_DQ20

D

DRA_DQ21

D

DRA_DQ22

DRA_DQ23

D

DDRA_DQ32

D

DRA_DQ33

DRA_DQ34

D

DRA_DQ35

D

D

DRA_DQ36

DRA_DQ37

D

DDRA_DQ38

D

DRA_DQ39

DRA_DQ48

D

DRA_DQ49

D

D

DRA_DQ50

D

DRA_DQ51

D

DRA_DQ52

D

DRA_DQ53

DRA_DQ54

D

DDRA_DQ55

D

DRA_DQ56

DRA_DQ57

D

DRA_DQ58

D

D

DRA_DQ59

DRA_DQ60

D

DDRA_DQ61

D

DRA_DQ62

DRA_DQ63

D

DRA_DQ40

D

DRA_DQ41

D

DRA_DQ42

D

D

DRA_DQ43

D

DRA_DQ44

D

DRA_DQ45

DDRA_DQ46

DRA_DQ47

D

DRA_DQS0

D

DRA_DQS#0

D

D

DRA_DQS1

D

DRA_DQS#1

D

DRA_DQS3

DRA_DQS#3

D

DRA_DQS2

D

DRA_DQS#2

D

DRA_DQS4

D

D

DRA_DQS#4

D

DRA_DQS6

D

DRA_DQS#6

DDRA_DQS7

DRA_DQS#7

D

DRA_DQS5

D

DRA_DQS#5

D

3

Group 0

Group 1

Group 3

Swap Group 2 to Group 3

Group 2

Group 4

Group 6

S

wap Group to 6\7\5

Group 7

Group 5

Swap Group 2 to Group 3

Swap Group to 6\7\5

3VALW+1.35V

+

UC1B

UC1B

AY45

RAM1_MA_00

D

BB47

RAM1_MA_11

D

AW41

RAM1_MA_22

D

BB44

RAM1_MA_33

D

BB50

RAM1_MA_44

D

BC53

RAM1_MA_55

D

BB49

RAM1_MA_66

D

BF50

RAM1_MA_77

D

BC52

RAM1_MA_88

D

BE52

RAM1_MA_99

D

AY48

RAM1_MA_1010

D

BE51

RAM1_MA_1111

D

BD47

RAM1_MA_1212

D

BA51

RAM1_MA_1313

D

BH49

RAM1_MA_1414

D

BH50

RAM1_MA_1515

D

BD38

RAM1_DM_0 0

D

BH36

RAM1_DM_1 1

D

BC36

RAM1_DM_2 2

D

BH42

RAM1_DM_3 3

D

AT51

RAM1_DM_4 4

D

AM42

RAM1_DM_5 5

D

AK50

RAM1_DM_6 6

D

AK52

RAM1_DM_7 7

D

V45

A

RAM1_RAS

D

V44

A

RAM1_CAS

D

B51

B

RAM1_WE

D

AY47

RAM1_BS_ 00

D

AY44

RAM1_BS_ 11

D

BF52

RAM1_BS_ 22

D

T44

A

RAM1_CS_0

D

T45

A

RAM1_CS_2

D

BG47

RAM1_CKE_00

D

BE46

ESERVED_ BE46

R

BD44

RAM1_CKE_22

D

BF48

ESERVED_ BF48

R

AP41

RAM1_ODT_0

D

AT42

RAM1_ODT_2

D

AV50

D

RAM1_CKP_0

AV48

D

RAM1_CKN_ 0

AT50

RAM1_CKP_2

D

AT48

RAM1_CKN_ 2

D

T41

A

RAM1_DRAMRST

D

BAY-TRAIL-M-SOC_FCBGA1170

BAY-TRAIL-M-SOC_FCBGA1170

@

@

2

BG38

RAM1_DQ_00

D

BC40

RAM1_DQ_11

D

BA42

RAM1_DQ_22

D

BD42

RAM1_DQ_33

D

BC38

RAM1_DQ_44

D

BD36

RAM1_DQ_55

D

BF42

RAM1_DQ_66

D

BC44

RAM1_DQ_77

D

BH32

RAM1_DQ_88

D

BG32

RAM1_DQ_99

D

BG36

BJ37

BG33

BJ33

BG37

BH38

AU36

AT36

AV40

AT40

BA36

AV36

AY42

AY40

BJ41

BG41

BJ45

BH46

BG40

BH40

BH48

BH47

AY52

AY51

AP52

AP51

AW51

AW53

AR51

AR53

AP47

AP45

AK40

AM41

AP48

AP50

AK42

AH40

AM45

AM47

AF48

AF50

AM48

AM50

AH44

AK45

AM52

AL51

AG53

AG51

AL53

AK51

AF52

AF51

BF40

BD40

BG35

BH34

BA38

AY38

BH44

BG43

AU53

AV52

AP42

AP44

AK47

AK48

AH52

AJ51

EV = 1.15

EV = 1.15

2 OF 13

2 OF 13

RAM1_DQ_1010

D

RAM1_DQ_1111

D

RAM1_DQ_1212

D

RAM1_DQ_1313

D

RAM1_DQ_1414

D

RAM1_DQ_1515

D

RAM1_DQ_1616

D

RAM1_DQ_1717

D

RAM1_DQ_1818

D

RAM1_DQ_1919

D

RAM1_DQ_2020

D

RAM1_DQ_2121

D

RAM1_DQ_2222

D

RAM1_DQ_2323

D

RAM1_DQ_2424

D

RAM1_DQ_2525

D

RAM1_DQ_2626

D

RAM1_DQ_2727

D

RAM1_DQ_2828

D

RAM1_DQ_2929

D

RAM1_DQ_3030

D

RAM1_DQ_3131

D

RAM1_DQ_3232

D

RAM1_DQ_3333

D

RAM1_DQ_3434

D

RAM1_DQ_3535

D

RAM1_DQ_3636

D

RAM1_DQ_3737

D

RAM1_DQ_3838

D

RAM1_DQ_3939

D

RAM1_DQ_4040

D

RAM1_DQ_4141

D

RAM1_DQ_4242

D

RAM1_DQ_4343

D

RAM1_DQ_4444

D

RAM1_DQ_4545

D

RAM1_DQ_4646

D

RAM1_DQ_4747

D

RAM1_DQ_4848

D

D

RAM1_DQ_4949

D

RAM1_DQ_5050

RAM1_DQ_5151

D

RAM1_DQ_5252

D

D

RAM1_DQ_5353

RAM1_DQ_5454

D

RAM1_DQ_5555

D

RAM1_DQ_5656

D

D

RAM1_DQ_5757

RAM1_DQ_5858

D

RAM1_DQ_5959

D

RAM1_DQ_6060

D

D

RAM1_DQ_6161

RAM1_DQ_6262

D

RAM1_DQ_6363

D

D

RAM1_DQSP_00

RAM1_DQSN_00

D

RAM1_DQSP_11

D

D

RAM1_DQSN_11

D

RAM1_DQSP_22

RAM1_DQSN_22

D

RAM1_DQSP_33

D

RAM1_DQSN_33

D

RAM1_DQSP_44

D

RAM1_DQSN_44

D

RAM1_DQSP_55

D

D

RAM1_DQSN_55

D

RAM1_DQSP_66

RAM1_DQSN_66

D

RAM1_DQSP_77

D

RAM1_DQSN_77

D

?R

?R

1

Q

Q

C16A

C16A

2

G

G

3VALW

+

1 4

61

D

D

S

S

2013/02/01

2013/02/01

2013/02/01

2 3

R

R

PC14

PC14

10K_0404_4P2R_5%

10K_0404_4P2R_5%

C16B

C16B

Q

Q

5

G

G

2N7002KDWH_SOT363-6

2N7002KDWH_SOT363-6

1.35V

+

C103

C103

R

R

1 2

0_0402_5%

0_0402_5%

34

D

D

2N7002KDWH_SOT363-6

2N7002KDWH_SOT363-6

S

S

T

T

T

itle

itle

itle

S

S

S

OC (DDR3L)

OC (DDR3L)

OC (DDR3L)

ize Document Number Rev

ize Document Number Rev

ize Document Number Rev

S

S

S

C

C

C

M

M

M

Date: Sheet

Date: Sheet

Date: Sheet

DR_CORE_PWROK

D

ACLU9

ACLU9

ACLU9

onday, December 23, 2013

onday, December 23, 2013

onday, December 23, 2013

1

1

C18

C18

C

C

.1U_0402_10V6-K

.1U_0402_10V6-K

2

5 5

5 5

5 5

o

o

o

f

f

f

.2

.2

.2

0

0

0

9

9

9

PC13

PC13

R

R

10K_0404_4P2R_5%

10K_0404_4P2R_5%

1 4

+

1.35V

12

C24

C24

R

R

4.7K_0402_1%

4.7K_0402_1%

C28

C28

R

R

1 2

12

RC29

RC29

4.7K_0402_1%

A A

4.7K_0402_1%

0_0402_5%

0_0402_5%

5

RAM_VREF

D

1

C2

C2

C

C

.1U_0402_10V6-K

.1U_0402_10V6-K

2

S

M_RCOMP_2

M_RCOMP_1

S

M_RCOMP_0

S

R

R

C25

C25

23.2_0402_1%

23.2_0402_1%

1 2

D

DR3 Compensation Signal

WIDTH:20MIL

SPACING: 25MIL

Length: 500Mil

R

1 2

R

C27

C27

162_0402_1%

162_0402_1%

V

DDQ_PGOOD{44,55}

1

2

R

R

C26

C26

29.4_0402_1%

29.4_0402_1%

1 2

4

2 3

C5B

C5B

Q

Q

5

G

G

61

C5A

C5A

Q

Q

D

D

2

G

G

2N7002KDWH_SOT363-6

2N7002KDWH_SOT363-6

S

S

C3

C3

C

C

.1U_0402_10V6-K

.1U_0402_10V6-K

ecurity Classification

ecurity Classification

ecurity Classification

S

S

S

ssued Date

ssued Date

ssued Date

I

I

I

HIS SHEET OF ENGINEERING DRAWIN G IS THE PROPRIETARY PROPERTY OF LC F UTURE CENTER. AND CONTAI NS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWIN G IS THE PROPRIETARY PROPERTY OF LC F UTURE CENTER. AND CONTAI NS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWIN G IS THE PROPRIETARY PROPERTY OF LC F UTURE CENTER. AND CONTAI NS CONFIDENTIAL

T

T

T

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER T HIS SHEET NOR THE INFORMATI ON IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER T HIS SHEET NOR THE INFORMATI ON IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER T HIS SHEET NOR THE INFORMATI ON IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WR ITTEN CONSENT OF LC FUTU RE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WR ITTEN CONSENT OF LC FUTU RE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WR ITTEN CONSENT OF LC FUTU RE CENTER.

3

R

R

C23

C23

1 2

0_0402_5%

0_0402_5%

34

D

D

2N7002KDWH_SOT363-6

2N7002KDWH_SOT363-6

S

S

D

DR_PWROK

013/03/26

013/03/26

013/03/26

2

2

2

1

C1

C1

C

C

.1U_0402_10V6-K

.1U_0402_10V6-K

2

YS_PWROK{7,44}

S

C Future Center Secret Data

C Future Center Secret Data

C Future Center Secret Data

L

L

L

eciphered Date

eciphered Date

eciphered Date

D

D

D

1

2

2

C19

C19

C

C

.1U_0402_10V6-K

.1U_0402_10V6-K

5

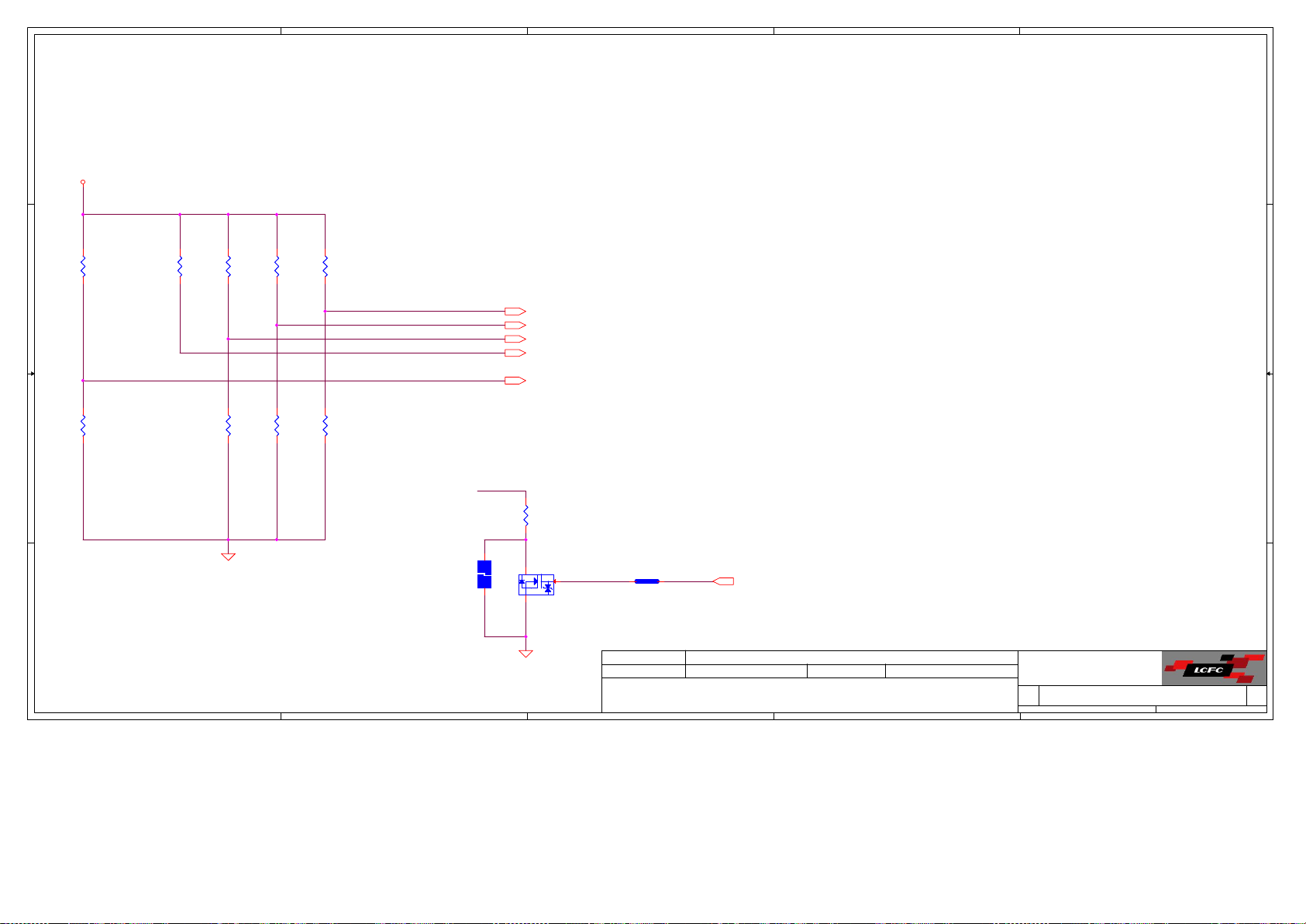

SATA_PTX_DRX_P0{42}

S

ATA_PTX_DRX_N0{42}

DD

H

S

ATA_PRX_DTX_P0{42}

ATA_PRX_DTX_N0{42}

S

S

D D

RB USE SATA_GP0

C

need check with BIOS

nly GPIO_S0_SC[0..7] can make SCI

o

C C

12

R

R

C30

C30

402_0402_1%

402_0402_1%

ATA_RCOMP_DP

S

SATA_RCOMP_DN

ATA_PTX_DRX_P1{42}

SATA_PTX_DRX_N1{42}

DD

O

ATA_PRX_DTX_P1{42}

S

S

ATA_PRX_DTX_N1{42}

S

OC_SCI#

1 2

R

R

C32 0_0402_5%

C32 0_0402_5%

1 2

C35 49.9_0402_1%

C35 49.9_0402_1%

R

R

1 2

R

R

C43 49.9_0402_1%

C43 49.9_0402_1%

B B

+

1.8VS

R

R

PC9

PC9

2.2K_0404_4P2R_5%

2.2K_0404_4P2R_5%

1 4

2 3

O

DD_DA#_SOC

DD_DETECT#_SOC

O

A A

+

3VS

@

@

1 2

C957 10K_0402_5%

C957 10K_0402_5%

R

R

1 2

C965 10K_0402_5%

C965 10K_0402_5%

R

R

@

@

O

DD_DETECT#

O

DD_DA#

S

11

C17A

C17A

Q

Q

PJT138K_SOT363-6

PJT138K_SOT363-6

2

G1

D

1 6

@

@

+

1.8VS

2 5

G

2 3

D

4

S

2

C17B

C17B

Q

Q

PJT138K_SOT363-6

PJT138K_SOT363-6

@

@

5

4

S

ATA_PTX_DRX_P0

ATA_PTX_DRX_N0

S

S

ATA_PRX_DTX_P0

ATA_PRX_DTX_N0

S

ATA_PTX_DRX_P1

S

SATA_PTX_DRX_N1

ATA_PRX_DTX_P1

S

S

ATA_PRX_DTX_N1

DD_DETECT#_SOC

O

O

DD_DA#_SOC

SATA_RCOMP_DP

S

ATA_RCOMP_DN

S

DMMC1_RCOMP

DMMC3_RCOMP

S

4

AU16

AV16

BD10

BF10

AY16

BA16

BB10

BC10

BA12

AY14

A

AU18

AT18

AT22

AV20

AU22

AV22

AT20

AY24

AU26

AT26

AU20

AV26

B

AY18

BA18

AY20

BD20

BA20

B

BC18

AY26

AT28

BD26

AU28

BA26

BC24

AV28

BF22

B

BF26

DD_DA# {42}

O

DD_DETECT# {42}

O

UC1D

UC1D

BF6

ATA_TXP_0

S

BG7

ATA_TXN_0

S

ATA_RXP_0

S

ATA_RXN_0

S

ATA_TXP1

S

ATA_TXN_1

S

ATA_RXP_1

S

ATA_RXN_1

S

CLK_SATA_TERMP

I

CLK_SATA_TERMN

I

ATA_GP0

S

ATA_GP1

S

Y12

ATA_LED

S

ATA_RCOMP_P_AU18

S

ATA_RCOMP_N_AT18

S

MC1_CLK

M

MC1_D0

M

MC1_D1

M

MC1_D2

M

MC1_D3

M

MC1_D4

M

MC1_D5

M

MC1_D6

M

MC1_D7

M

MC1_CMD

M

A24

MC1_RST

M

MC1_RCOMP

M

D2_CLK

S

D2_D0

S

D2_D1

S

S

D2_D2

D18

S

D2_D3_CD

S

D2_CMD

S

D3_CLK

S

D3_D0

S

D3_D1

S

D3_D2

S

D3_D3

S

D3_CD#

S

D3_CMD

S

D3_1P8EN

D22

S

D3_PWREN

S

D3_RCOMP

BAY-TRAIL-M-SOC_FCBGA1170

BAY-TRAIL-M-SOC_FCBGA1170

@

@

V1P8S

V1P8S

V1P8S

RESERVED_VS

RESERVED_VSS5

?

?

VLV_M_D

VLV_M_D

S4

RESERVED_VSS7

RESERVED_VSS6

P

V1P8S

P

V1P8S

P

V1P8S

P

V1P8S

CIE_RCOMP_P_AP14_AP14

P

CIE_RCOMP_N_AP13_AP13

P

R

R

R

R

DA_LPE_RCOMP

H

VAUD

VAUD

VAUD

VAUD

VAUD

VAUD

VAUD

GPIO_S0_SC_14

GPIO_S0_SC_15

L

PE_I2S2_DATAOUT

L

PE_I2S2_DATAIN

R

R

R

R

V1P0_S3

OF 13 REV = 1.15

OF 13 REV = 1.15

4

4

CIE_TXP_0

P

CIE_TXN_0

P

CIE_RXP_0

P

CIE_RXN_0

P

CIE_TXP_1

P

CIE_TXN_1

P

CIE_RXP_1

P

CIE_RXN_1

P

CIE_TXP_2

P

CIE_TXN_2

P

CIE_RXP_2

P

CIE_RXN_2

P

CIE_TXP_3

P

CIE_TXN_3

P

CIE_RXP_3

P

CIE_RXN_3

P

SS_BB7

V

SS_BB5

V

CIE_CLKREQ_0

CIE_CLKREQ_1

CIE_CLKREQ_2

CIE_CLKREQ_3

D3_WP_BD5

S

ESERVED_BB4

ESERVED_BB3

ESERVED_AV10

ESERVED_AV9

H

DA_RST

H

DA_SYNC

H

DA_CLK

H

DA_SDO

H

DA_SDI0

H

DA_SDI1

H

DA_DOCKRST

H

DA_DOCKEN

L

PE_I2S2_CLK

L

PE_I2S2_FRM

ESERVED_P34

ESERVED_N34

ESERVED_AK9

ESERVED_AK7

P

ROCHOT

?

?

3

et name changed to same as ACLU1

N

AY7

P

CIE_CTX_GRX_P0

AY6

CIE_CTX_GRX_N0

P

AT14

P

CIE_CRX_GTX_P0

AT13

CIE_CRX_GTX_N0

P

AV6

CIE_CTX_GRX_P1

P

AV4

PCIE_CTX_GRX_N1

AT10

CIE_CRX_GTX_P1

P

AT9

P

CIE_CRX_GTX_N1

AT7

P

CIE_PTX_DRX_P4

AT6

CIE_PTX_DRX_N4

P

AP12

P

CIE_PRX_DTX_P4

AP10

CIE_PRX_DTX_N4

P

AP6

CIE_PTX_DRX_P3

P

AP4

PCIE_PTX_DRX_N3

AP9

CIE_PRX_DTX_P3

P

AP7

P

CIE_PRX_DTX_N3

BB7

BB5

G3

B

G

PU_CLKREQ#_Q

D7

B

CIE_CLKREQ_2#

P

G5

B

W

LAN_CLKREQ#_Q

E3

B

AN_CLKREQ#_Q

L

BD5

AP14

CIE_RCOMP_DP

P

AP13

P

CIE_RCOMP_DN

BB4

BB3

AV10

AV9

BF20

DA_RCOMP

H

G22

B

HDA_RST_AUDIO#_R

BH20

H

DA_SYNC_AUDIO_R

BJ21

DA_BITCLK_AUDIO_R

H

BG20

H

DA_SDOUT_AUDIO_R

BG19

BG21

H18

B

G18

B

BF28

BA30

I

2S_2_FS

BC30

I

2S_2_TXD

BD28

P34

N34

AK9

AK7

24

C

C

PU_PROCHOT#_R

ecurity Classification

ecurity Classification

ecurity Classification

S

S

S

ssued Date

ssued Date

ssued Date

I

I

I

TH

TH

TH

IS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

IS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

IS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

1 2

1 2

1 2

1 2

1 2

1 2

C44 0_0402_5%

C44 0_0402_5%

R

R

C36 49.9_0402_1%

C36 49.9_0402_1%

R

R

RC37 33_0402_5%RC37 33_0402_5%

R

R

C38 33_0402_5%

C38 33_0402_5%

C39 33_0402_5%

C39 33_0402_5%

R

R

R

R

C40 33_0402_5%

C40 33_0402_5%

2S_2_FS {12}

I

2S_2_TXD {12}

I

+

013/03/26

013/03/26

013/03/26

2

2

2

OPT@

OPT@

12

C

C

C4.1U_0402_10V6-K

C4.1U_0402_10V6-K

12

C5.1U_0402_10V6-K

C5.1U_0402_10V6-K

C

C

OPT@

OPT@

OPT@

OPT@

12

C6.1U_0402_10V6-K

C6.1U_0402_10V6-K

C

C

12

C

C

C7.1U_0402_10V6-K

C7.1U_0402_10V6-K

OPT@

OPT@

12

C

C

C104.1U_0402_10V6-K

C104.1U_0402_10V6-K

12

C103.1U_0402_10V6-K

C103.1U_0402_10V6-K

C

C

12

C105.1U_0402_10V6-K

C105.1U_0402_10V6-K

C

C

12

C

C

C106.1U_0402_10V6-K

C106.1U_0402_10V6-K

P

CIE_RCOMP_DP

P

CIE_RCOMP_DN

1.0VS

R

R

C42

C42

73.2_0402_1%

73.2_0402_1%

@

@

1 2

H

C Future Center Secret Data

C Future Center Secret Data

C Future Center Secret Data

L

L

L

_PROCHOT# {44,51,52}

3

2

PCIE_CTX_C_GRX_P0 {19}

P

CIE_CTX_C_GRX_N0 {19}

CIE_CRX_GTX_P0 {19}

P

P

CIE_CRX_GTX_N0 {19}

P

CIE_CTX_C_GRX_P1 {19}

PCIE_CTX_C_GRX_N1 {19}

P

CIE_CRX_GTX_P1 {19}

CIE_CRX_GTX_N1 {19}

P

PCIE_PTX_C_DRX_P4 {40}

P

CIE_PTX_C_DRX_N4 {40}

CIE_PRX_DTX_P4 {40}

P

P

CIE_PRX_DTX_N4 {40}

P

CIE_PTX_C_DRX_P3 {37}

CIE_PTX_C_DRX_N3 {37}

P

P

CIE_PRX_DTX_P3 {37}

CIE_PRX_DTX_N3 {37}

P

C31

C31

R

R

402_0402_1%

402_0402_1%

1 2

DA_RST_AUDIO# {43}

H

H

DA_SYNC_AUDIO {43}

DA_BITCLK_AUDIO {43}

H

H

DA_SDOUT_AUDIO {43}

H

DA_SDIN0 {43}

eciphered Date

eciphered Date

eciphered Date

D

D

D

2

0607

GPU

d

W

LAN

LAN

2013/02/01

2013/02/01

2013/02/01

AN_CLKREQ#_Q

L

MMBT3904WH_SOT323-3

MMBT3904WH_SOT323-3

WLAN_CLKREQ#_Q

MMBT3904WH_SOT323-3

MMBT3904WH_SOT323-3

G

PU_CLKREQ#_Q

12

OC_SCI#

S

1

+

1.8VS

PC1

PC1

R

R

AN_CLKREQ#_Q

L

GPU_CLKREQ#_Q

P

CIE_CLKREQ_2#

LAN_CLKREQ#_Q

W

AN_CLKREQ#

L

W

LAN_CLKREQ#

+

+

MMBT3904WH_SOT323-3

MMBT3904WH_SOT323-3

+

R

R

C967

C967

2.2K_0402_5%

2.2K_0402_5%

G

G

3

S

S

Q

Q

C13

C13

PJA138K_SOT23-3

PJA138K_SOT23-3

itle

itle

itle

T

T

T

S

S

S

OC (PCIE&HDA&SATA&STRAPS)

OC (PCIE&HDA&SATA&STRAPS)

OC (PCIE&HDA&SATA&STRAPS)

S

S

Size Document Number Rev

ize Document Number Rev

ize Document Number Rev

C

C

C

ustom

ustom

ustom

Date: Sheet

Date: Sheet

Date: Sheet

1 8

2 7

3 6

4 5

C968 10K_0402_5%

C968 10K_0402_5%

R

R

R

R

C969 10K_0402_5%

C969 10K_0402_5%

1.8VS

12

C958

C958

R

R

2.2K_0402_5%

2.2K_0402_5%

2

B

B

E

E

31

C

C

Q

Q

C6

C6

1.8VS

12

R

R

C959

C959

2.2K_0402_5%

2.2K_0402_5%

2

B

B

E

E

31

C

C

C7

C7

Q

Q

+1.8VS

12

R

R

C960

C960

2.2K_0402_5%

2.2K_0402_5%

OPT@

OPT@

2

B

B

E

E

31

C

C

OPT@

OPT@

Q

Q

C199

C199

c

1.8VS

2

1

D

D

ACLU9

ACLU9

ACLU9

M

M

M

onday, December 23, 2013

onday, December 23, 2013

onday, December 23, 2013

10K_0804_8P4R_5%

10K_0804_8P4R_5%

12

12

3VS

+

LAN_CLKREQ# {37}

W

LAN_CLKREQ# {40}

G

PU_CLKREQ# {19}

hange mos to 3904

3VALW_R

+

R

R

C95

C95

10K_0402_5%

10K_0402_5%

@

@

1 2

E

C_SCI# {44}

o

o

o

f

6 59

f

6 59

f

6 59

1

0

0

0

.2

.2

.2

5

TAL25_IN

C12

C12

C

C

18P_0402_50V8J

18P_0402_50V8J

1

2

3

4

C

C

1

C10

C10

2

X

1

C13

C13

C

C

10P_0402_50V8-J

10P_0402_50V8-J

2

C2

C2

U

U

S#

C

SO(IO1)

HOLD#(IO3)

W

S

P#(IO2)

V

S

SS

I(IO0)

GD25LQ64CVIGR_TSOP8

GD25LQ64CVIGR_TSOP8

0605

C89 2 0K_0402_1%

C89 2 0K_0402_1%

R

R

1 2

C90 2 0K_0402_1%

C90 2 0K_0402_1%

R

R

1 2

1U_0402_6.3V6K

1U_0402_6.3V6K

12

CMOS1

CMOS1

J

J

SHORT PADS

SHORT PADS

@

@

JCMOS/JCMOS1

Place under Bo ttom

RTCRST#

S

pace 15Mil

C93 1M_0402 _5%

C93 1M_0402 _5%

R

R

C2

C2

Y

Y

1

O

SC1

2

ND1

G

25MHZ_10PF_7V25000 014

25MHZ_10PF_7V25000 014

8

CC

V

7

PI_HOLD#

S

6

CH_SPI_CLK

P

CLK

5

CH_SPI_SI

P

1 2

0mA

5

V

G

O

CCRTC

ND2

SC2

TC_X1

R

1 2

C92 1 0M_0402_5%

C92 1 0M_0402_5%

R

R

1 2

C1

C1

Y

Y

32.768KHZ_12.5PF_2004 58-PG14

32.768KHZ_12.5PF_2004 58-PG14

2

C11

C11

C

C

D D

18P_0402_50V8J

18P_0402_50V8J

1

1,Space 15MIL

2,No trace und er crystal

RYSTAL

C

1.8VALW_SPI

+

P

C C

SPI ROM

3,place on opp sosit side of MCP for temp i nfluence

1.8VALW

+

C82 0_0402_ 5%

C82 0_0402_ 5%

R

R

1 2

PC15

PC15

R

R

1 8

2 7

3 6

4 5

2.2K_0804_8P4R_5%

2.2K_0804_8P4R_5%

hange 3.3K to 2.2K 4R8P

c

C85

C85

R

R

1 2

CH_SPI_SO_R

22_0402_5%

22_0402_5%

RTC_RST#

S

TC_RST#

R

ME1

ME1

J

J

SHORT PADS

SHORT PADS

@

@

TC_X2

R

2

1

1.8VALW_SPI

+

PI_WP#

S

PI_HOLD#

S

CH_SPI_CS0#

P

CH_SPI_CS0#

P

CH_SPI_SO

P

PI_WP#

S

1U_0402_6.3V6K

1U_0402_6.3V6K

1

12

C

C

C9

C9

2

4

3

C14

C14

C

C

10P_0402_50V8-J

10P_0402_50V8-J

1.8VALW_SPI

+

1

C8

C8

C

C

.1U_0402_10V6-K

.1U_0402_10V6-K

2

TAL25_OUT

X

1

2

RTC RST#

PC17

PC17

R

R

10K_0404_4P2R_5%

10K_0404_4P2R_5%

1 4

C15A

C15A

Q

Q

PJT138K_SOT363-6

PJT138K_SOT363-6

3VS

+

2 3

D

25

G

2

S

4

0603

OC_SMI#

S

OC_LID_OUT#

S

5

C15B

C15B

Q

Q

PJT138K_SOT363-6

PJT138K_SOT363-6

+

0605

2 3

C104

C104

R

R

100K_0402_5%

100K_0402_5%

1 2

1.8VALW

PC6

PC6

R

R

2.2K_0404_4P2R_5%

2.2K_0404_4P2R_5%

1 4

4

S

Q

Q

PJT138K_SOT363-6

PJT138K_SOT363-6

2

C14B

C14B

P

LT_RST# {19,37,40,44}

2 5

G

2 3

D

1.8VALW

+

2

1

G

1 6S11

D

C14A

C14A

Q

Q

PJT138K_SOT363-6

PJT138K_SOT363-6

3VALW_R

+

2 3

1 4

PC7

PC7

R

R

10K_0404_4P2R_5%

10K_0404_4P2R_5%

3VALW

+

B B

2 3

1 6

D

1

G

MC_PLTRST#

P

A A

2

11

S

_SERIRQ need change to level shift

0801 EC_INT

P

P

P

E

C_SMI# {44}

E

C_LID_OUT# {44}

4

UC1E

UC1E

AH12

TAL25_IN

X

TAL25_OUT

X

1 2

C70 4 .02K_0402_1%

C70 4 .02K_0402_1%

R

R

1 2

C62 47.5_040 2_1%

C62 47.5_040 2_1%

R

R

LK_PCIE_GPU#{19}

C

LK_PCIE_GPU{19}

C

LK_PCIE_WLAN#{40}

C

LK_PCIE_WLAN{40}

C

LK_PCIE_LAN#{37}

C

LK_PCIE_LAN{37}

C

CLK_ICOMP

I

CLK_RCOMP

I

LK_PCIE_GPU#

C

LK_PCIE_GPU

C

C

C

C

C

LK_PCIE_WLAN#

LK_PCIE_WLAN

LK_PCIE_LAN#

LK_PCIE_LAN

RTC_RST#

S

XDP

C81 2 2_0402_5%

C81 2 2_0402_5%

R

R

1 2

CH_SPI_CS0#

1 2

CH_SPI_SI

C84 2 2_0402_5%

C84 2 2_0402_5%

R

R

1 2

CH_SPI_CLK

C88 2 2_0402_5%

C88 2 2_0402_5%

R

R

1 2

C91 4 9.9_0402_1%

C91 4 9.9_0402_1%

R

R

T

he ALT_GPIO_SMI.CORE_GPIO_SMI_STS [31:24] & ALT_GPIO_SMI.CORE_GPIO_SMI _EN[15:8] register bits correspond

to GPIO_S0_SC[7:0]. ALT_GPIO_SMI.SUS_GPIO_SMI_STS[23:16] & ALT_GPIO_SMI.SUS_GPIO_SMI_EN[7:0] correspond

to GPIO_S5[7:0].

4

OC_KBRST#

S

MC_PWRBTN#

P

CH_SPI_CS0#_R

P

CH_SPI_SO_R

P

CH_SPI_SI_R

P

CH_SPI_CLK_R

P

OC_KBRST#

S

OC_LID_OUT#

S

OC_SMI#

S

PIO_RCOMP18

G

1.8VALW

+

1 4

2 3

AH10

AD9

AD14

AD13

AD10

AD12

AF6

AF4

AF9

AF7

AK4

AK6

AM4

AM6

AM10

AM9

BH7

BH5

BH4

BH8

BH6

BJ9

C12

D14

G

12

F14

F12

G16

D

18

F

16

AT34

C23

C

21

B22

A21

C22

B18

B16

C18

A17

C17

C16

B14

C15

C13

A13

C19

N26

PC4

PC4

R

R

10K_0404_4P2R_5%

10K_0404_4P2R_5%

4

2

S

C12B

C12B

Q

Q

PJT138K_SOT363-6

PJT138K_SOT363-6

ICLK_OSCIN

I

CLK_OSCOUT

ESERVED_AD9

R

ICLK_ICOMP

I

CLK_RCOMP

ESERVED_AD10

R

ESERVED_AD12

R

P

CIE_CLKN_00

P

CIE_CLKP_00

CIE_CLKN_11

P

PCIE_CLKP_11

CIE_CLKN_22

P

CIE_CLKP_22

P

P

CIE_CLKN_33

P

CIE_CLKP_33

ESERVED_AM10

R

RESERVED_AM9

PMC_PLT_CLK_00

P

MC_PLT_CLK_11

P

MC_PLT_CLK_22

MC_PLT_CLK_33

P

MC_PLT_CLK_44

P

PMC_PLT_CLK_55

I

LB_RTC_RST

AP_TCK

T

AP_TRST

T

TAP_TMS

T

AP_TDI

T

AP_TDO

AP_PRDY

T

AP_PREQ

T

RESERVED

P

CU_SPI_CS_00

CU_SPI_CS_11

P

CU_SPI_MISO

P

PCU_SPI_MOSI

P

CU_SPI_CLK

PIO_S5_0

G

GPIO_S5_1

G

PIO_S5_2

G

PIO_S5_3

PIO_S5_4

G

PIO_S5_5

G

GPIO_S5_6

G

PIO_S5_7

GPIO_S5_8

G

PIO_S5_9

G

PIO_S5_10

GPIO_RCOMP

BAY-TRAIL-M-SOC_FCBGA1170

BAY-TRAIL-M-SOC_FCBGA1170

@

@

1.8VALW

+

2

1

G

1 6S11

D

C12A

C12A

Q

Q

PJT138K_SOT363-6

PJT138K_SOT363-6

2 5

G

2 3

D

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

5 OF 13 ?REV = 1.15

5 OF 13 ?REV = 1.15

3VALW_R

+

R

R

10K_0404_4P2R_5%

10K_0404_4P2R_5%

1 4

2 3

3

PC5

PC5

3

?

?

LV_M_D

LV_M_D

V

V

GPIO_S5_14

Internal 20

GPIO_S5_17

K

P

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8S

K(H)

V1P8A

V1P8A

V1P8A

VRTC

VRTC

BRST# {44}

BTN_OUT# {44}

SIO_UART1_RXD

S

IO_UART1_TXD

S

IO_UART1_RTS

IO_UART1_CTS

S

SIO_UART2_RXD

S

IO_UART2_TXD

S

IO_UART2_RTS

IO_UART2_CTS

S

P

MC_SUSPWRDNACK

MC_SUSCLK0_G24

P

MC_SLP_S0IX

P

PMC_SLP_S4

P

G

PIO_S514_J20

MC_ACPRESENT

P

MC_WAKE_PCIE_0

P

PMC_BATLOW

P

MC_PWRBTN

P

P

PIO_S517_J24

G

PMC_SUS_STAT

LB_RTC_TEST

I

MC_RSMRST

P

MC_CORE_PWROK

P

LB_RTC_EXTPAD

I

V1P0S

V1P0S

V1P0S

S

SIO_PWM_11

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8A

V1P8S

IO_SPI_MISO

S

V1P8S

IO_SPI_MOSI

S

V1P8S

SIO_SPI_CLK

V1P8S

MC_SLP_S3

MC_RSTBTN

MC_PLTRST

I

LB_RTC_X1

LB_RTC_X2

I

VID_ALERT

S

SVID_DATA

S

VID_CLK

IO_PWM_00

GPIO_S5_22

G

PIO_S5_23

G

PIO_S5_24

PIO_S5_25

G

PIO_S5_26

G

GPIO_S5_27

G

PIO_S5_28

G

PIO_S5_29

PIO_S5_30

G

S

IO_SPI_CS

P

MC_SLP_S3#

P

MC_SLP_S4#

AU34

AV34

BA34

A

Y34

BF34

BD34

BD32

B

F32

D26

G24

F

18

22

F

D22

J20

D20

F

26

26

K

J26

BG9

F

20

J24

18

G

C

11

B

10

B7

C9

A9

B8

B

24

A25

C25

AU32

AT32

K24

N24

M20

J18

M18

K18

K20

M22

M24

AV32

BA28

AY28

AY30

USPWRDNACK

S

MC_SUSCLK

P

MC_SLP_S0IX#

P

MC_SLP_S4#

P

MC_SLP_S3#

P

PIO_S514_J20

G

MC_ACIN

P

MC_PCIE_WAKE#

P

MC_BATLOW#

P

MC_PWRBTN#

P

MC_RSTBTN#

P

MC_PLTRST#

P

1

TC_RST#

R

C_RSMRST#

E

YS_PWROK

S

TC_X1

R

TC_X2

R

VCCRTC_EXTPAD

B

PU_SVID_ALRT#_R

C

PU_SVID_DAT_R

C

PU_SVID_CLK_R

C

1.8VALW

+

1 4

2 3

2

1

P9@TP9@

T

1

P10@TP10@

T

P1@TP1@

T

1

1

P3@TP3@

T

1.8VALW

3VALW_R

+

+

604

0

P4

1

@

@

R

R

1 2

1 2

R

R

P5@TP5@

T

C17 .1U_0402_10V6-K

C17 .1U_0402_10V6-K

C

C

C78 20_0402_1%

C78 20_0402_1%

1 2

R

R

1 2

C79 16.9_0402_1%

C79 16.9_0402_1%

R

R

1 2

C80 0_0402_5%

C80 0_0402_5%

R

R

P4

T

T

C71 10K_0402_5%

C71 10K_0402_5%

C72 10K_0402_5%

C72 10K_0402_5%

C_RSMRST# {44}

E

YS_PWROK {5,44 }

S

1 2

1.8VALW

+

1.8VALW

+

PU_SVID_ALERT# {59}

C

PU_SVID_DAT {5 9}

C

PU_SVID_CLK {59}

C

MC_ACIN

P

C60

C60

R

R

10K_0402_5%

10K_0402_5%

1 2

C63

C63

R

R

10K_0402_5%

10K_0402_5%

1 2

C61

C61

R

R

2.2K_0402_5%

2.2K_0402_5%

@

@

1 2

3

S

S

Q

Q

PJA138K_SOT23-3

PJA138K_SOT23-3

13

D

D

C9

@

@

C9

Q

Q

S

S

2N7002KW_SOT32 3-3

2N7002KW_SOT32 3-3

2

G

G

need check pow er part if RES is staffed

C927

C927

R

R

10K_0402_5%

10K_0402_5%

1 2

MC_PCIE_WAKE#

P

R

R

C75

C75

10K_0402_5%

10K_0402_5%

1 2

USPWRDNACK

S

+

1.8VALW

3VALW_R

+

R

R

PC2

PC2

10K_0404_4P2R_5%

10K_0404_4P2R_5%

@

@

4

S

S

S

S

ecurity Classification

ecurity Classification

ecurity Classification

I

I

I

ssued Date

ssued Date

ssued Date

T

T

T

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

2

PJT138K_SOT363-6

PJT138K_SOT363-6

2 5

G

Q

Q

D

2 3

PJT138K_SOT363-6

PJT138K_SOT363-6

2

C11B

C11B

PC3

PC3

R

R

10K_0404_4P2R_5%

10K_0404_4P2R_5%

C11A

C11A

Q

Q

1

1 4

2 3

G

D

1 6S11

013/03/26

013/03/26

013/03/26

2

2

2

2

M_SLP_S3# {44}

P

M_SLP_S4# {44}

P

C Future Center Secret Data

C Future Center Secret Data

C Future Center Secret Data

L

L

L

eciphered Date

eciphered Date

eciphered Date

D

D

D

P

MC_SUSCLK

B

ay trail plaform susclk is 1.8VSA level, NGFF card need 3.3V

2013/02/01

2013/02/01

2013/02/01

1

1.8VS

+

1 2

MC_RSTBTN#

P

MC_SUSCLK

P

C_RSMRST#

E

C_RSMRST#

E

2

G

G

D

D

C203

C203

0605

+

G

G

3

S

S

C168

C168

Q

Q

PJA138K_SOT23-3

PJA138K_SOT23-3

G

G

3

S

S

C10

C10

Q

Q

PJA138K_SOT23-3

PJA138K_SOT23-3

12

@

@

C73 10K_0402_5%

C73 10K_0402_5%

R

R

1 2

C83 10K_0402_5%@RC83 10K_0402_5%@

R

C930 100K_0402_5%

C930 100K_0402_5%

R

R

12

C113 0.01U_0402_25V7 K

C113 0.01U_0402_25V7 K

1 2

C

C

@

@

f

or ACINneed ch eck with power team

1

1 2

C69

@RC69

@

R

0_0402_5%

0_0402_5%

@

@

1.8VALW

3VALW

+

12

C793

C793

R

R

10K_0402_5%

10K_0402_5%

2

1

D

D

+

1.8VALW

2

1

D

D

@

@

+

1.8VALW

C932

C932

R

R

2

2.2K_0402_5%

2.2K_0402_5%

G

G

3

D

S

D

S

C200

C200

Q

Q

PJA138K_SOT23-3

PJA138K_SOT23-3

T

T

T

itle

itle

itle

S

S

S

OC (RTC&SPI&PM)