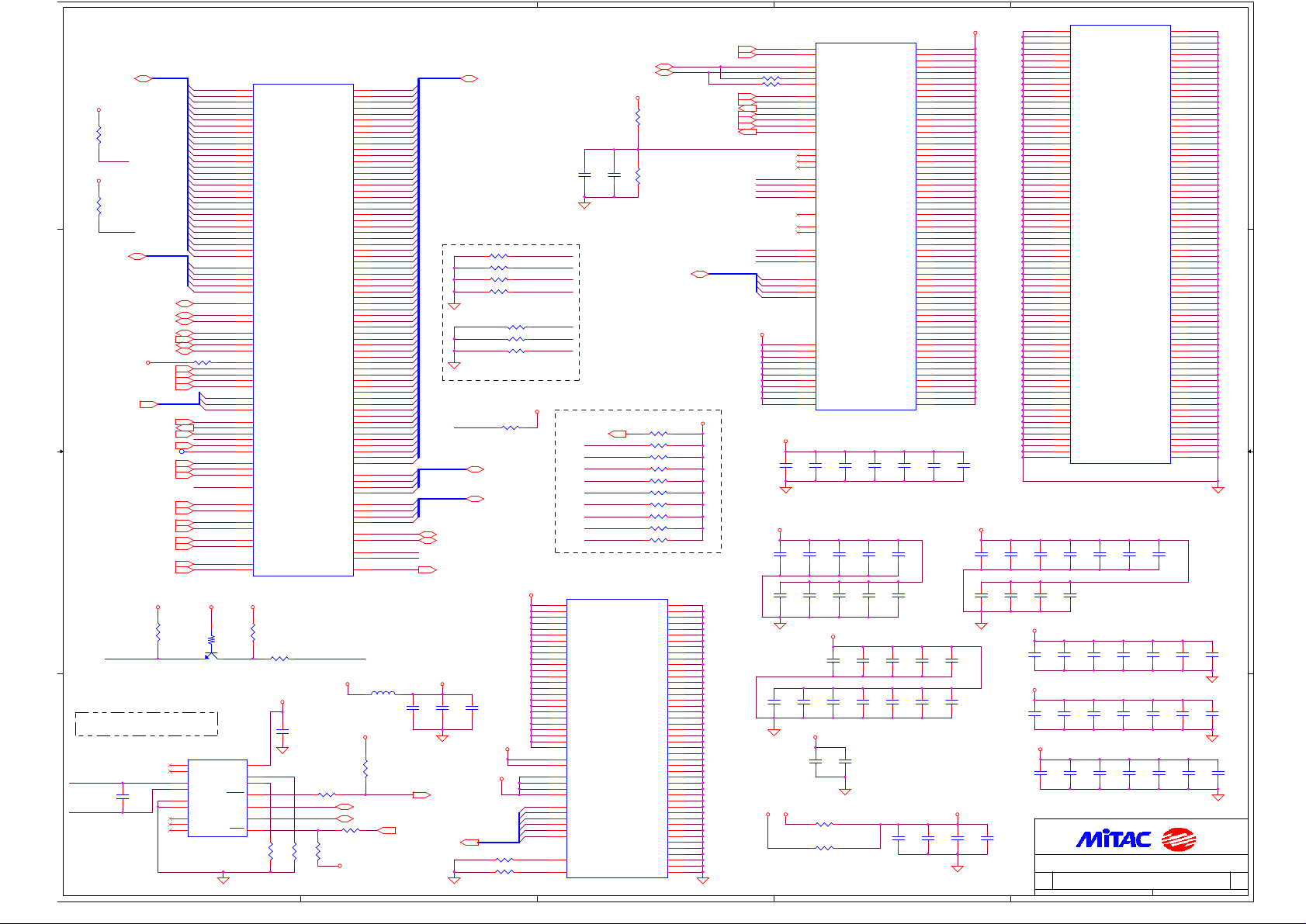

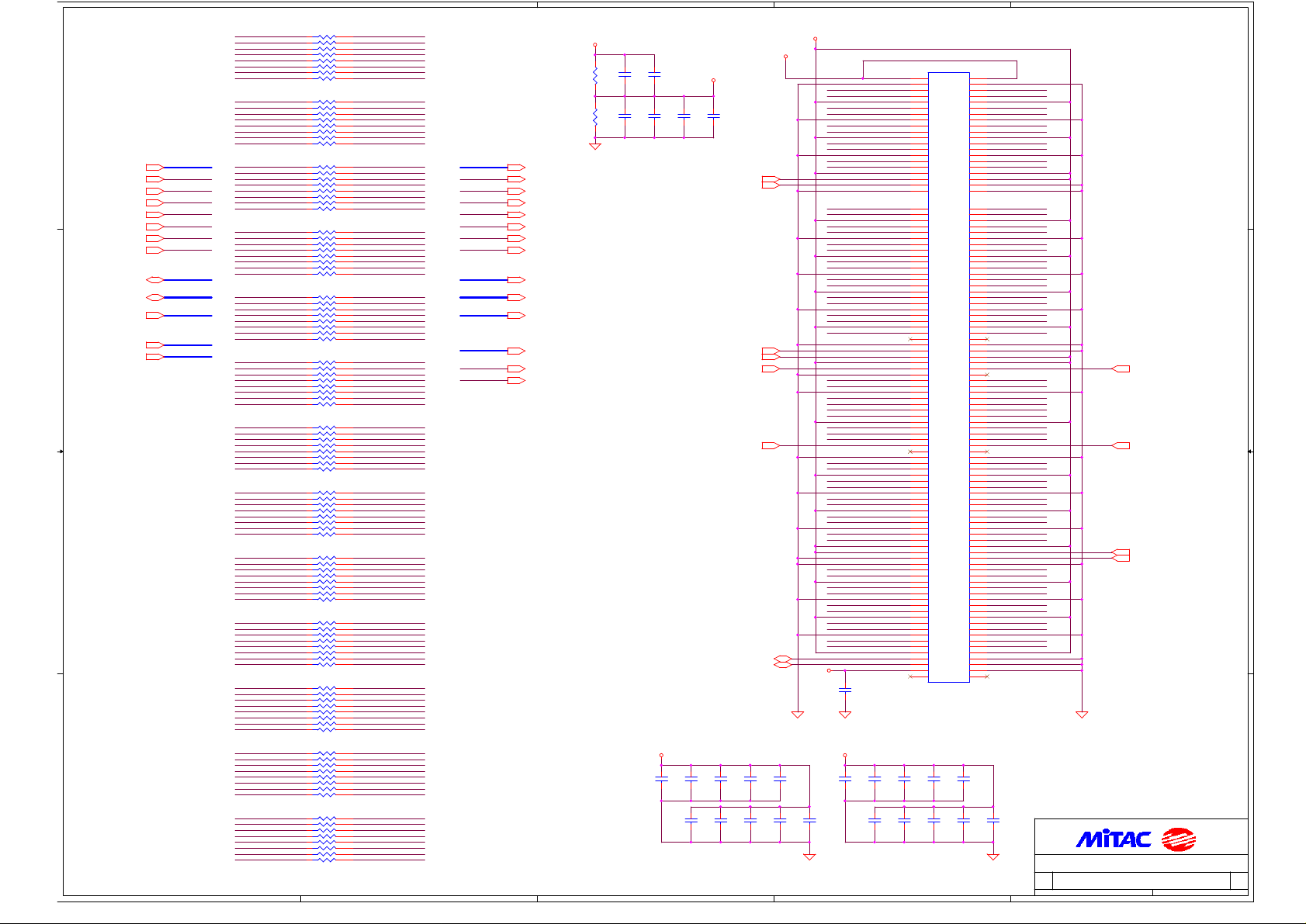

Lenovo E255 Schematics

5

4

3

2

1

8081 MB R01

Project Code : G072

Product Code : 6785

D D

PAG

E01

Block Dia

PAG

E02

PAG

E03

PAG

E04

PAG

E05

PAG

E06

PAG

E07

PAG

E08

PAG

E09

PAG

E10

PAG

E11

PAG

E12

PAG

E13

PAG

E14

PAG

E15

PAG

E16

PAG

E17

PAG

PAG

PAG

PAG

PAG

PAG

PAG

PAG

PAG

PAG

PAG

E18

E19

E20

E21

E22

E23

E24

E25

E26

E27

E28

C C

B B

gram

Mou

nting Hole

Banais

Clock Generat

Montara_

Montara_

SO-D

On Board DDR

DDR Termi

ICH4-M

ICH4-M

HDD & CD_ROM

Audio Co

OP AMP(APA2020)

LCD & CRT connector

LAN(VT6105LOM

Mini

CardBus &

Super IO(

Micro Cont

USB to IDE(U

BIOS & Inverter & LED

Power On Control L

1.2V & 1.5V(SC33

1.25V

2.5V & 1.0

3V & 5V(L

CPU_CORE(MA

GM(1)

GM(2)

IMM

nation

(1)

(2)

dec(CMI9738S)

PCI

1394(R5C551)

PC87393)

roller(H8_3437)

(LP2996)

5V(LTC3728L)

TC3728L)

or

) & MDC

PD720130)

ogic

8) & 1.8V

XIM1907)

Mini PCI Slot

1394 * 1

* 1

Clock Generat

ICS950810

CardBus & 1394

R5C551

R5C485(OPT

ION)

PCMCIA Slot * 1

or

Power

Switch

G571

RJ-45

RJ-11

Audio Amp

APA2020ARI

H8

SMB

CRT Connec

TFT Flat Pa

Trans

former

MDC

Daughtor Boar

AC'97 Codec

CMI9738S

Thermal

ADM1021A

tor

nel

Sensor

RGB

LVDS

PCI Bus

LAN Contro

VT6105LOM

d

llor

AC Link

CPU

Intel

Banias

Micro-FCPGA

FSB

400

Monta

ra-GM

GMCH

732 pin

Micro-FCBGA

Hub Interface

ICH

4-M

421 pin BGA

LPC Bus

Super I/O

PC87393

266-

S-IDE

USB2.0*4

PI

O

MHz

SO-DIMM

P-IDE

CD-ROM

USB

Connect

DEBUG LED

* 1

HDD

or

On Boar

Cells

256MB

IDE to USB

NEC

uPD720130

(OPTION

d

)

USB * 1(

OPTION)

ISA Bu

Mic-in

Connecto

Internal

Speaker

+5V/+3V

+2.5V/+1.05V

D/D Power

+1.25V

+1.2V/+1.5V

A A

1.8V

+CPU_CORE

5

AC-Adapter

BATT-Adapter

Charger

Headphon

e

Connect

or

4

3

r

Syste

BIO

S

s

m

Keyboard BIOS

Hitachi

H8/3437S

PS/2

KEY MA

TRIX

2

Touch P

Tit

Siz

Date:

ad

le

C

e

Document

Number

Inte

rnal

Keyboard

Wednesday, June 11, 2003

Blo

ck Diagram

411678500006

1

Sheet

Rev

1

01

28

of

5

+3

V

12

EC1

0.1U

0603

50V

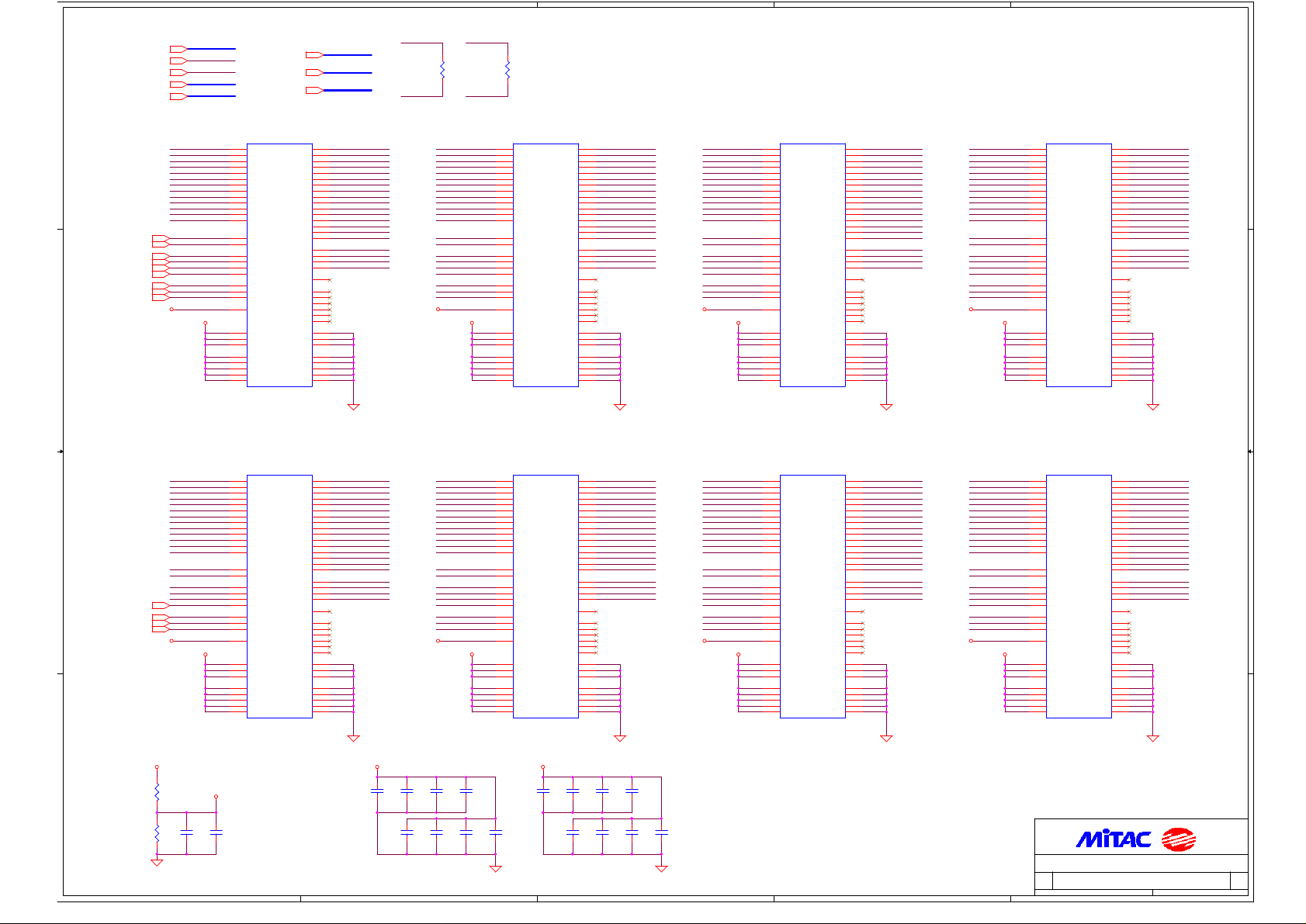

D D

VT6105LOM(LA

IDSEL: AD1

PCI REQ1

PCI GNT1

PCI INTE

Mini PC

IDSEL: AD1

PCI REQ3

PCI GNT3

PCI INTD# INT

R5C551

IDSEL: AD2

PCI REQ2

PCI GNT2

PCI INTB# INT

C C

N)

8

#

#

#

I

7

#

#

0

#

#

+3V

12

EC10

0.1U

0603

50V

F#

+VCCP

G#

12

EC15

0.1U

0603

50V

12

12

+VCC_CORE

EC17

0.1U

0603

50V

12

EC4

0.1U

0603

50V

12

EC6

EC7

0.1U

0.1U

0603

0603

50V

50V

+VCC_CORE

12

EC12

0.1U

0603

50V

12

12

EC18

EC19

0.1U

0.1U

0603

0603

50V

50V

MT

G503

AM20-45

1

12

EC2

0.1U

0603

50V

12

EC11

0.1U

0603

50V

12

EC16

0.1U

0603

50V

4

+2.5V_DDR

12

EC9

+5V

0.1U

0603

50V

+VCCP

12

+VCCP

EC13

0.1U

0603

50V

+1.5V

+3V

12

EC14

0.1U

0603

50V

12

12

12

EC21

EC20

0.1U

0.1U

0603

0603

50V

50V

EC22

0.1U

0603

50V

12

12

EC27

0.1U

0603

50V

+1.5V

+3V

EC28

0.1U

0603

50V

+1.2V

+2.5V_DDR

+1.2V

12

12

EC25

0.1U

0603

50V

12

12

EC23

0.1U

0603

50V

EC26

0.1U

0603

50V

EC24

0.1U

0603

50V

3

+1.5V

+3V

REV

R00

Initail release (base on PUMA)

R01

1.

Change PR4 ,PR29 and PR45 to 470 ohm for SUSB# signal quality.

2.LAN signal add fuse to protect LAN transformer.

3.

Modify U533 control signal(SUSC# and 2 * 2N7002) for leakage

current.

4

.Remove R98 for leakage current and change pull high to +3V.

5.Change R202 and R217(M/B ID) pull high to +VDD3.

6.Change Q24 pin2 pull high to +EXT3V.

7.Change R777 and R778 to 6.8K for CD ROM audio noise.

8.Inverter input voltage add VMAIN option for future use.

9.Change Q517 to 2N7002 and rename Q33 for LED flash issue.

1

0.Change U522 power to +AVDDAD, C753 to AGND, R736 to AGND.

11.Change J10(MIC) pin6 to CAGND.

12.Reserve band pass tuning capacitor.(Page 13)

13.Add a resistor on CD LED# signal to prevent signal O.D.

14.Delete M/B to charger BD connector USB signal reserver

resistors and connector origanl pin to GND.

15.Add a resistor(1M) and change R505 to 47K ohm and rename

R507 for divided DVMAIN to tuen on LCDVCC MOS.(Reserved)

16.Reserve a regulator for audio +5V input.

17.Modify back light circuit.

18.Re-assign M/B to Charger BD pin.

19.Change R766 pull high to +VA.

20.Add R505 between CLK_DDR3/CLK_DDR3# and R686 between

CLK_DDR4/CLK_DDR4#

Change detail

2

DATE

1

ECR No.

2003/05/02

2003/05/26

GND

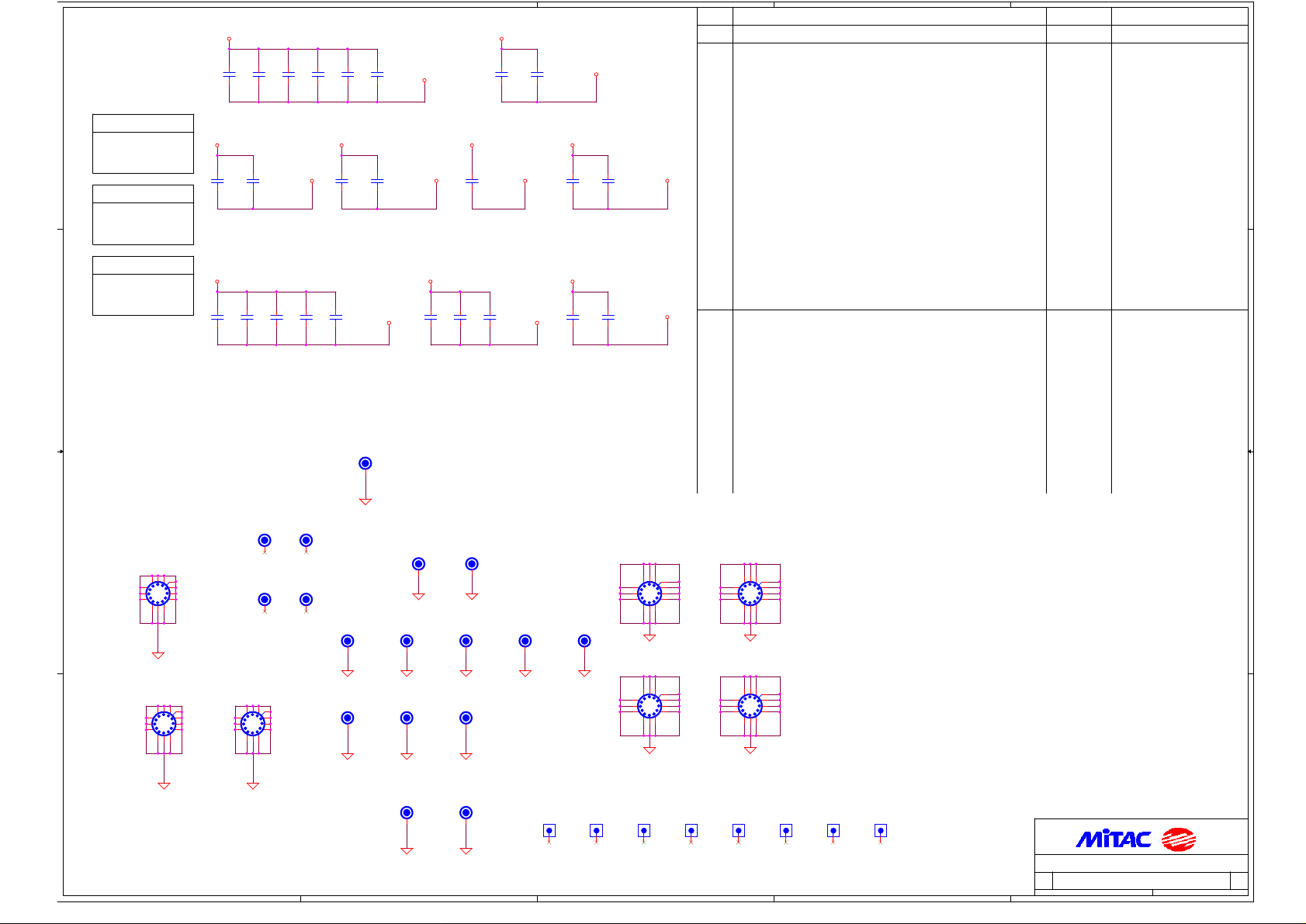

MTG21

MT

1

1

MTG

7

ID3.0/OD7.0/SLD9.0

123

13

12

11

10

9

GND

G22

ID2.2/OD4.5

1

MT

G24

ID2.2/OD4.5

1

MTG

1

ID3.0/OD7.0/SLD9

1

AGND

MTG

8

ID3.0/OD7.0/SLD9

1

GND

ID2.2/OD4.5

B B

A A

4

5

6

4

5

6

PCM_GND

MTG

ID3.0/OD7.0/SLD9.0

123

7

9

8

123

7

9

8

GND

3

13

12

11

10

MTG

6

ID3.0/OD7.0/SLD9.0

13

12

11

10

5

MTG23

ID2.2/OD4.5

4

5

6

7

8

MTG

501

AM20-30

1

MTG

2

ID3.0/OD7.0/SLD9

1

CAGND

MTG

9

ID3.0/OD7.0/SLD9

1

GND_45

MTG17

ID1.5/OD3

1

GND_45

4

For MDC Onl

y

MT

G502

AM20-3

0

1

GNDGND

MTG

4

ID3.0/OD7.0/SLD9

1

MTG11

ID3.0/OD7.0/SLD9

CD-ROM

1

GND

MTG18

ID1.5/OD3

1

GND

MTG

5

ID3.0/OD7.0/SLD9

1

GND

FD4

FIDUCIAL-MARK

1

MTG10

ID3.0/OD7.0/SLD9

1

GNDGND

FD2

FIDUCIAL-MARK

1

123

4

5

6

7

9

8

GND

123

4

5

6

7

9

8

GND

FD3

FIDUCIAL-MARK

1

3

MTG12

ID4.5/OD9.0

13

12

11

10

MTG14

ID4.5/OD9.0

13

12

11

10

CPU

FD1

FIDUCIAL-MARK

1

123

4

5

6

7

9

8

GND

123

4

5

6

7

9

8

GND

FD501

FIDUCIAL-MARK

1

MT

G13

ID4.5/OD9.0

13

12

11

10

MT

G15

ID4.5/OD9.0

13

12

11

10

FD504

FIDUCIAL-MARK

FD502

FIDUCIAL-MARK

1

FD503

FIDUCIAL-MARK

1

1

2

Tit

Siz

Date:

le

C

e

Document

Number

Mo

unting Hole

41167*******

Wednesday, June 11, 2003

1

Sheet

Rev

2

01

28

of

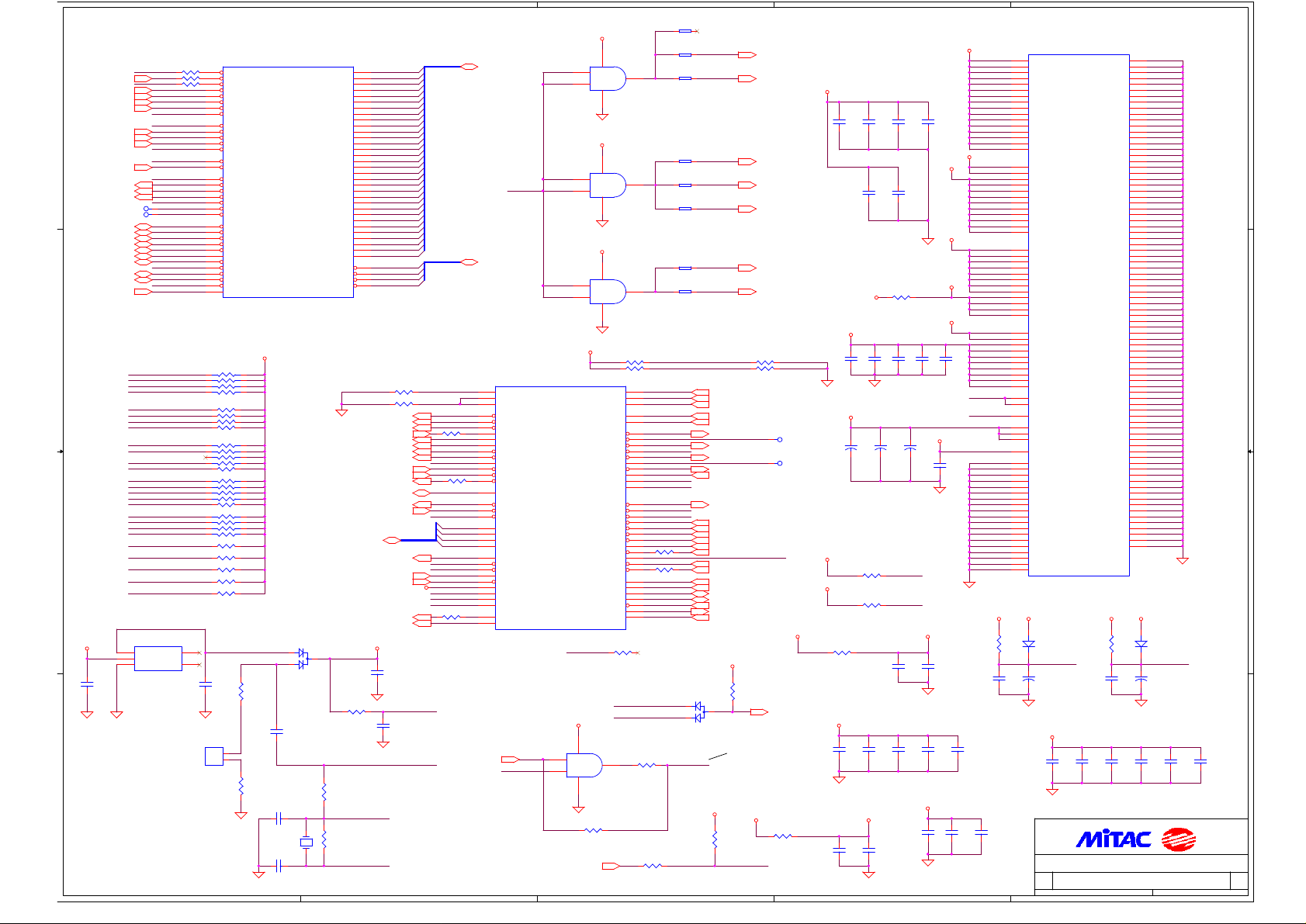

VCC : PROCESSOR CORE POWER SUPPLY.

VCCA : ISOLATE POWER FOR INTERNAL PLL.

VCCP : PROCESSOR I/O POWER SUPPLY.

VCCQ : QUIET POWER SUPPLY FOR ON DIE COMP CKT.

HA#[3..31]

5

+VCC_CORE

12

D D

C C

B B

A A

R54

51

0603

HBR0#

+VCCP

12

R105

300

0603

HPWRGD

HREQ#[0..4]

5

5

5

5

5

5

5

5

+VCCP

5

5

5

5

HRS#[0..2]

5

10

11

5

10

10

10

10

10

5,10

10

10

10

4,5

CLK_ITP_CPU

4

CLK_ITP_CPU#

4

HPROCHOT#

Place thermal sensor as close to

VGA as possible for the critical

of VGA chip thermal issue.

CPU_THERMDA

CPU_THERMDC

12

C573

2200P

0603

5

HA#[3..31]

HREQ#[0..4]

HADS#

HADSTB#0

HADSTB#1

HBR0#

HBPRI#

HBNR#

HLOCK#

HHIT#

HHITM#

HDEFER#

HTRDY#

HA20M#

HFERR#

HDPWR#

HSLP#

HIGNNE#

HSMI#

HPWRGD

HSTPCLK#

HDPSLP#

HINTR

HNMI

HINIT#

HCPURST#

+VCCP

12

Slave Address 0011000

R577

HRS#[0..2]

TP

5

R61

56

0603

16

13

1 2

1

U505

1

TEST

TEST1

3

D+

4

D-

7

GND1

8

GND2

5

NC1

9

NC2

NC3

ADM1021A

5

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HBR0#

HRS#0

HRS#1

HRS#2

HA20M#

HDBR#

HSLP#

HPSI#

HIGNNE#

HSMI#

HPWRGD

HPROCHOT#

HSTPCLK#

HDPSLP#

HINTR

HNMI

HINIT#

+VCCP

2

R1

1 3

Q8

DTC144TKA/NA

56

0603

VDD

ADD0

ADD1

ALERT

SDATA

SCLK

STBY

QSOP16

U504A

P4

A3#

U4

A4#

V3

A5#

R3

A6#

V2

A7#

W1

A8#

T4

A9#

W2

A10#

Y4

A11#

Y1

A12#

U1

A13#

AA3

A14#

Y3

A15#

AA2

A16#

AF4

A17#

AC4

A18#

AC7

A19#

AC3

A20#

AD3

A21#

AE4

A22#

AD2

A23#

AB4

A24#

AC6

A25#

AD5

A26#

AE2

A27#

AD6

A28#

AF3

A29#

AE1

A30#

AF1

A31#

R2

REQ0#

P3

REQ1#

T2

REQ2#

P1

REQ3#

T1

REQ4#

N2

ADS#

U3

ADSTB0#

AE5

ADSTB1#

N4

BR0#

J3

BPRI#

L1

BNR#

J2

LOCK#

A4

IERR#

K3

HIT#

K4

HITM#

L4

DEFER#

M3

TRDY#

H1

RS0#

K1

RS1#

L2

RS2#

C2

A20M#

D3

FERR#

C19

DPWR#

A7

DBR#

A6

SLP#

E1

PSI#

A3

IGNNE#

B4

SMI#

E4

PWRGOOD

B17

PROCHOT#

C6

STPCLK#

B7

DPSLP#

D1

LINT0

D4

LINT1

B5

INIT#

B11

RESET#

A16

ITP_CLK0

A15

ITP_CLK1

BANIAS

BGA479_S

KT3

+3V

12

R64

10K/NA

0603

R63

1 2

0/NA

0603

+3V_P

12

C574

0.1U

0603

50V

GND

2

10

6

11

12

14

15

B

1 2

12

12

R583

R568

0

0

0603

0603

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

DBSY#

DRDY#

THERMDA

THERMDC

THERMTRIP#

TEMP_AL

+VCCP

R581

0

0603

1 2

R582

12

R569

10K/NA

0603

A19

D0#

A25

D1#

A22

D2#

B21

D3#

A24

D4#

B26

D5#

A21

D6#

B20

D7#

C20

D8#

B24

D9#

D24

E24

C26

B23

E23

C25

H23

G25

L23

M26

H24

F25

G24

J23

M23

J25

L26

N24

M25

H26

N25

K25

Y26

AA24

T25

U23

V23

R24

R26

R23

AA23

U26

V24

U25

V26

Y23

AA26

Y25

AB25

AC23

AB24

AC20

AC22

AC25

AD23

AE22

AF23

AD24

AF20

AE21

AD21

AF25

AF22

AF26

C23

K24

W25

AE24

C22

L24

W24

AE25

M2

H2

B18

A18

C17

ERT#

L14

1 2

120Z/100M

2012

+3V_P

12

TEMP_A

H8_THRM_DATA20,21

H8_THRM_CLK

0

+3V_P

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

CPU_THERMDA

CPU_THERMDC

R580

10K

0603

LERT#

20,21

SUSB#

4

HD#[0..63]

HCOMP0 & HCOMP2 should be

route with 18 mil width

27.4

54.9

1%

27.4

54.9

1%

GND

0603

0603

0603

GND

Close to CPU as possible.

HDBR#

HDSTBN#[0..3]

HDSTBP#[0..3]

HDBSY#

5

HDRDY#

5

CPU_THRMTRIP_OUT#

+VCCQ

12

12

GND

TEMP_A

VID[0..5]

12

C72

0.1U

0603

50V

LERT#

11

1%

1%

GNDGND

C46

10U

1206

10V

4,10,18,21,22,23,24,25,26,28

28

4

HD#[0..63]

1 2

1 2

1 2

1 2

R59

1K

5%

R62

1K

5%

R60

1K

5%

10K/NA

0603

HDSTBN#[0..3]

HDSTBP#[0..3]

(1.05V

C43

0.1U

0603

50V

+VCCA

VID[0..5]

1 2

1 2

5

1 2

1 2

1 2

R575

1 2

11

+VCCQ

HBPM#0

4

HBPM#1

4

+VCCP

12

Close to CPU as possible.

12

GND

HCOMP0

R552

0603

HCOMP1

R553

0603

HCOMP2

R50

0603

HCOMP3

R52

0603

CPU_TE

ST1

CPU_TE

ST2

CPU_TE

ST3

+3V

CPUPERF#

10

HA20M#

HIGNNE#

HINTR

HNMI

HSMI#

HSTPCLK#

HDPSLP#

HSLP#

HINIT#

PLACEMENT MAX. 3" FROM CPU.

Don't overlay by CHOKE or vibrating signals.

U504D

D10

VCCP_0

D12

VCCP_1

D14

VCCP_2

D16

VCCP_3

E11

VCCP_4

E13

VCCP_5

E15

VCCP_6

F10

VCCP_7

F12

VCCP_8

F14

VCCP_9

F16

VCCP_10

K6

VCCP_11

L5

VCCP_12

L21

VCCP_13

M6

VCCP_14

M22

VCCP_15

N5

VCCP_16

N21

VCCP_17

P6

VCCP_18

P22

VCCP_19

R5

VCCP_20

R21

VCCP_21

T6

VCCP_22

T22

VCCP_23

U21

VCCP_24

P23

VCCQ0

W4

VCCQ1

F26

VCCA0

B1

VCCA1

N1

VCCA2

AC26

VCCA3

E2

VID0

F2

VID1

F3

VID2

G3

VID3

G4

VID4

H4

VID5

AE7

VCCSENSE

AF6

VSSENSE

BANIAS

BGA479_S

+VCCP

)

R534

54.90603

R535

54.90603

5

5

VID0

VID1

VID2

VID3

VID4

VID5

12

12

C47

C44

220P

1U

0603

0603

10%

HCOMP1 & HCOMP3 should be

route with 5 mil width

5

1 2

200 0603

1 2

200/NA

1 2

200/NA

1 2

200/NA

1 2

200/NA

1 2

200/NA

1 2

200/NA

1 2

200/NA

1 2

200/NA

1 2

200/NA

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

KT3

3

R38

953

0603

1%

R41

2K

0603

1%

HDINV#[0..3]

3

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE3

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF2

AF5

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF24

HBPM#0

HBPM#1

R637

R118

0603

R578

0603

R119

0603

R58

0603

R566

0603

R564

0603

R563

0603

R576

0603

R565

0603

4

4

4

4

4

4

4

+VCCP

GND

HCLK_CPU

HCLK_CPU#

HTCLK

HTDI

HTD

O4

HTM

S4

HTRS

HPREQ#

HPRDY#

HDINV#[0..3]

U504B

B15

BCLK0

B14

BCLK1

C8

BPM0#

B8

BPM1#

0

0

T#

0603

0603

+VCC_CORE

R574

HTCLK

HTDI

HTDO

HTM

S

HTRS

T#

HPREQ#

HPRDY#

HCOMP0

HCOMP1

HCOMP2

HCOMP3

CPU_TES

CPU_TES

CPU_TES

HDINV#0

HDINV#1

HDINV#2

HDINV#3

+VCCP

GND

+VCC_CORE

12

12

GND

12

1206

GND

+1.8V

C24

10U

10V

+1.5V

R562

T1

T2

T3

12

C17

10U

1206

10V

C14

10U

1206

10V

R57

R48

A9

C9

A13

C12

A12

C11

B13

B10

A10

AD26

E26

G1

AC1

P25

P26

AB2

AB1

AF7

C14

C3

C5

F23

C16

D25

J26

T24

AD20

AE11

AE13

AE15

AE17

AE19

AF8

AF10

AF12

AF14

AF16

AF18

1.05V, 2.4A

C92

10U

1206

10V

12

12

12

C77

10U

1206

10V

+VCCP

1 2

0/NA

1 2

0

BPM2#

BPM3#

TCK

TDI

TDO

TMS

TRST#

PREQ#

PRDY#

GTLREF0

GTLREF1

GTLREF2

GTLREF3

COMP0

COMP1

COMP2

COMP3

RSVD_0

RSVD_2

RSVD_3

TEST1

TEST2

TEST3

DINV0#

DINV1#

DINV2#

DINV3#

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

BANIAS

BGA479_S

12

C91

10U

1206

10V

C15

10U

1206

10V

C13

10U

1206

10V

+VCC_CORE

12

12

12

C93

10U

1206

10V

0805

0805

1 2

1 2

1.8V, 0.6A, 10uF and 10nF each VCCA pin.

1.5V for future support.

2

+VCCP

12

12

Tit

Siz

Date:

12

12

12

le

C

C85

0603

C106

0603

e

0.1U

50V

0.1U

50V

C52

10U

1206

10V

C84

10U

1206

10V

C109

0.1U

0603

50V

A11

A14

A17

A20

A23

A26

B12

B16

B19

B22

B25

C10

C13

C15

C18

C21

C24

D11

D13

D15

D17

D19

D21

D23

D26

E10

E12

E14

E16

E18

E20

E22

E25

F11

F13

F15

F17

F19

F21

F24

G22

G23

G26

H21

H25

Document

Number

U504C

A2

VSS_0

A5

VSS_1

A8

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

B3

VSS_9

B6

VSS_10

B9

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

C1

VSS_17

C4

VSS_18

C7

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

D2

VSS_26

D5

VSS_27

D7

VSS_28

D9

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

E3

VSS_38

E6

VSS_39

E8

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

F1

VSS_49

F4

VSS_50

F5

VSS_51

F7

VSS_52

F9

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

G2

VSS_61

G6

VSS_62

VSS_63

VSS_64

VSS_65

H3

VSS_66

H5

VSS_67

VSS_68

VSS_69

J1

VSS_70

J4

VSS_71

J6

VSS_72

BANIAS

BGA479_S

12

C55

10U

1206

10V

12

C49

10U

1206

10V

12

C64

0.1U

0603

50V

12

C107

0.1U

0603

50V

12

C98

0.1U

0603

50V

Wednesday, June 11, 2003

+VCC_CORE

D6

VCC_0

D8

VCC_1

D18

VCC_2

D20

VCC_3

D22

VCC_4

E5

VCC_5

E7

VCC_6

E9

VCC_7

E17

VCC_8

E19

VCC_9

E21

VCC_10

F6

VCC_11

F8

VCC_12

F18

VCC_13

F20

VCC_14

F22

VCC_15

G5

VCC_16

G21

VCC_17

H6

VCC_18

H22

VCC_19

J5

VCC_20

J21

VCC_21

K22

VCC_22

U5

VCC_23

V6

VCC_24

V22

VCC_25

W5

VCC_26

W21

VCC_27

Y6

VCC_28

Y22

VCC_29

AA5

VCC_30

AA7

VCC_31

AA9

VCC_32

AA11

VCC_33

AA13

VCC_34

AA15

VCC_35

AA17

VCC_36

AA19

VCC_37

AA21

VCC_38

AB6

VCC_39

AB8

VCC_40

AB10

VCC_41

AB12

VCC_42

AB14

VCC_43

AB16

VCC_44

AB18

VCC_45

AB20

VCC_46

AB22

VCC_47

AC9

VCC_48

AC11

VCC_49

AC13

VCC_50

AC15

VCC_51

AC17

VCC_52

AC19

VCC_53

AD8

VCC_54

AD10

VCC_55

AD12

VCC_56

AD14

VCC_57

AD16

VCC_58

AD18

VCC_59

AE9

VCC_60

KT3

12

12

C97

C94

10U

10U

1206

1206

10V

10V

12

12

C524

C76

10U

10U

1206

1206

10V

10V

12

12

C25

C26

10U

10U

1206

1206

10V

10V

12

C56

C53

10U

10U

1206

1206

10V

10V

12

C19

C18

10U

10U

1206

1206

10V

10V

12

C96

10U

1206

10V

GND

12

12

C95

10U

1206

10V

12

C16

10U

1206

10V

12

C525

10U

1206

10V

12

C54

10U

1206

10V

12

C20

10U

1206

10V

12

C88

2.2U

1206

16V

2

12

C90

C89

10U

10U

1206

1206

10V

10V

12

12

GND

C62

0.1U

0603

50V

0.844V ~ 1.356V, 32A

12

C50

C51

10U

10U

1206

1206

10V

10V

12

C83

C82

10U

10U

1206

1206

10V

10V

+VCC_CORE

+VCC_CORE

12

C99

0.1U

0603

50V

+VCC_CORE

12

12

C78

C23

10U

10U

1206

1206

10V

10V

12

12

C22

C21

10U

10U

1206

1206

10V

10V

+VCCA

12

12

C105

0.1U

0603

50V

GND

1

J22

VSS_73

J24

VSS_74

K2

VSS_75

K5

VSS_76

K21

VSS_77

K23

VSS_78

K26

VSS_79

L3

VSS_80

L6

VSS_81

L22

VSS_82

L25

VSS_83

M1

VSS_84

M4

VSS_85

M5

VSS_86

M21

VSS_87

M24

VSS_88

N3

VSS_89

N6

VSS_90

N22

VSS_91

N23

VSS_92

N26

VSS_93

P2

VSS_94

P5

VSS_95

P21

VSS_96

P24

VSS_97

R1

VSS_98

R4

VSS_99

R6

VSS_100

R22

VSS_101

R25

VSS_102

T3

VSS_103

T5

VSS_104

T21

VSS_105

T23

VSS_106

T26

VSS_107

U2

VSS_108

U6

VSS_109

U22

VSS_110

U24

VSS_111

V1

VSS_112

V4

VSS_113

V5

VSS_114

V21

VSS_115

V25

VSS_116

W3

VSS_117

W6

VSS_118

W22

VSS_119

W23

VSS_120

W26

VSS_121

Y2

VSS_122

Y5

VSS_123

Y21

VSS_124

Y24

VSS_125

AA1

VSS_126

AA4

VSS_127

AA6

VSS_128

AA8

VSS_129

AA10

VSS_130

AA12

VSS_131

AA14

VSS_132

AA16

VSS_133

AA18

VSS_134

AA20

VSS_135

AA22

VSS_136

AA25

VSS_137

AB3

VSS_138

AB5

VSS_139

AB7

VSS_140

AB9

VSS_141

AB11

VSS_142

AB13

VSS_143

AB15

VSS_144

AB17

VSS_145

KT3

GND

12

12

C80

10U

1206

10V

12

C111

0.1U

0603

50V

12

C527

0.1U

0603

50V

12

C100

0.1U

0603

50V

Bana

41167*******

1

12

12

is

Sheet

12

C81

10U

1206

10V

12

12

C102

0.1U

0603

50V

C11

0.1U

0603

50V

12

C104

0.1U

0603

50V

C59

C103

0.1U

0.1U

0603

0603

50V

50V

GND

12

12

C27

C529

0.1U

0.1U

0603

0603

50V

50V

GND

12

12

C108

C110

0.1U

0.1U

0603

0603

50V

50V

GND

Rev

3

01

28

of

C79

10U

1206

10V

12

C28

0.1U

0603

50V

12

C528

0.1U

0603

50V

12

C112

0.1U

0603

50V

5

VID

5

4

0

0

0

0

0

0

0

D D

C C

B B

A A

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0 1

0

1

0

0

1

1

0

1

0

0

1

0

1

0

1

0

1

1

0

0

1

0

1

1

0

0

1

0

1

0

1

0

1

CORE_CLKEN#

28

+3V

L523

1 2

120Z/100M

12

2012

C603

0.1U

0603

50V

GND

+3V

L521

1 2

120Z/100M

12

2012

C591

0.1U

0603

50V

GND

0

2

VCC-Core

1

0

0

1.708

0

1

1.692

0

0

1

0

0

1.676

0

1

1.660

1

1.644

0

1

0

0

1

1

1.628

1

0

1

1.612

1

1

1

1.596

0

0

1.580

0

0

0

1.564

1

0

1.548

1 0

0

1.532

1

1

00

1.516

0

0

1

0

1

1

1.500

1

1.484

0

1

1

1

1.468

1

0

1.452

0

1.436

1

0

0

0

0

1

1.420

1

0

1.404

1

0

1

1.388

0

1

0

1.372

1

1

1.356

1

0

1

1

1

1.340

0

1.324

0

0

1.308

0

0

1

1

0

1.292

0

0

1

1

1.276

0

1 0

1.260

1

0

1

1.244

1

1.228

1

0

1

1

1.212

1

0

0603

STOP_CPU#

STOP_PCI#

12

12

C596

0.1U

0603

50V

5

1 2

0603

1 2

0603

12

C607

C605

0.1U

0.1U

0603

0603

50V

50V

+3VCLK66

12

12

C613

0.1U

0603

50V

GND

10,28

3

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

10

1 2

12

C594

0.1U

0603

50V

C598

2.2U

0805

+80-20

5

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

R634

R594

0/NA

R602

0/NA

+3VCLKANA

12

+80-2

GND

%

4

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

+3V

CLK_CPU_STOP#

CLK_PCI_STOP#

C606

2.2U

0805

0%

VID

3

2

0

0

0

0

0

0

0

0

1

0

1

0

1

0

1

1

0

0

1

1

0

1

1

1

1

1

1

1

1

0

00

0

0

0

0

0

0

0

1

0

1

1

0

0

1

0

1

0

1

1

0

1

0

1 0

1

1

1

1

1

1

1

12

R633

10K

0603

1%

VTT_P

1

0

0

110

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

01

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

WRGD#

VCC-Core

1.196

1.180

1.164

1.148

1.132

1.116

1.100

1.084

1.068

1.052

1.036

1.020

1.004

0.988

0.972

0.956

0.940

0.924

0.908

0.892

0.876

0.860

0.844

0.828

0.812

0.796

0.780

0.764

0.748

0.732

0.716

0.700

+3V

12

GND

+3V

12

GND

C575

0603

C621

0603

0.1U

50V

0.1U

50V

L515

1 2

120Z/100M

2012

L526

1 2

120Z/100M

2012

4

Layout note: Place crystal within

500 mils of CLK Gen.

SMBDAT

A

7,11

SMBCLK

7,11

+3V

+3VCLKCPU

12

12

C593

0.1U

0603

50V

12

C611

0.1U

0603

50V

4

12

C588

0.1U

0603

50V

GND

3,10,18,21,22,23,24,25,26,28

+3VCLKPCI

12

12

C612

0.1U

0603

50V

GND

R631

R612

R603

+80-2

+80-2

C585

2.2U

0805

C618

2.2U

0805

1 3

14.318MHZ

12

C610

1 2

1 2

1 2

0%

0%

3

+VCC_CORE

12

12

12

R573

R561

51

0603

HPREQ#

3

HPRDY#

3

HBPM#1

3

HBPM#0

3

HTDO

3

HTM

S3

HTDI

3

HCPURST#

3,5

HTRS

T#

3

HTCLK

3

GND

R67

51

51

0603

0603

12

12

R570

R558

680

27.4

0603

0603

GND

+VCCP

12

R559

51/NA

0603

R560

39

0603

12

R571

150

0603

12

12

R68

51

0603

Place close to CPU socket within 2".

X5

01

2

4

12

33P

0603

50V

5%

C622

33P

0603

50V

5%

GND

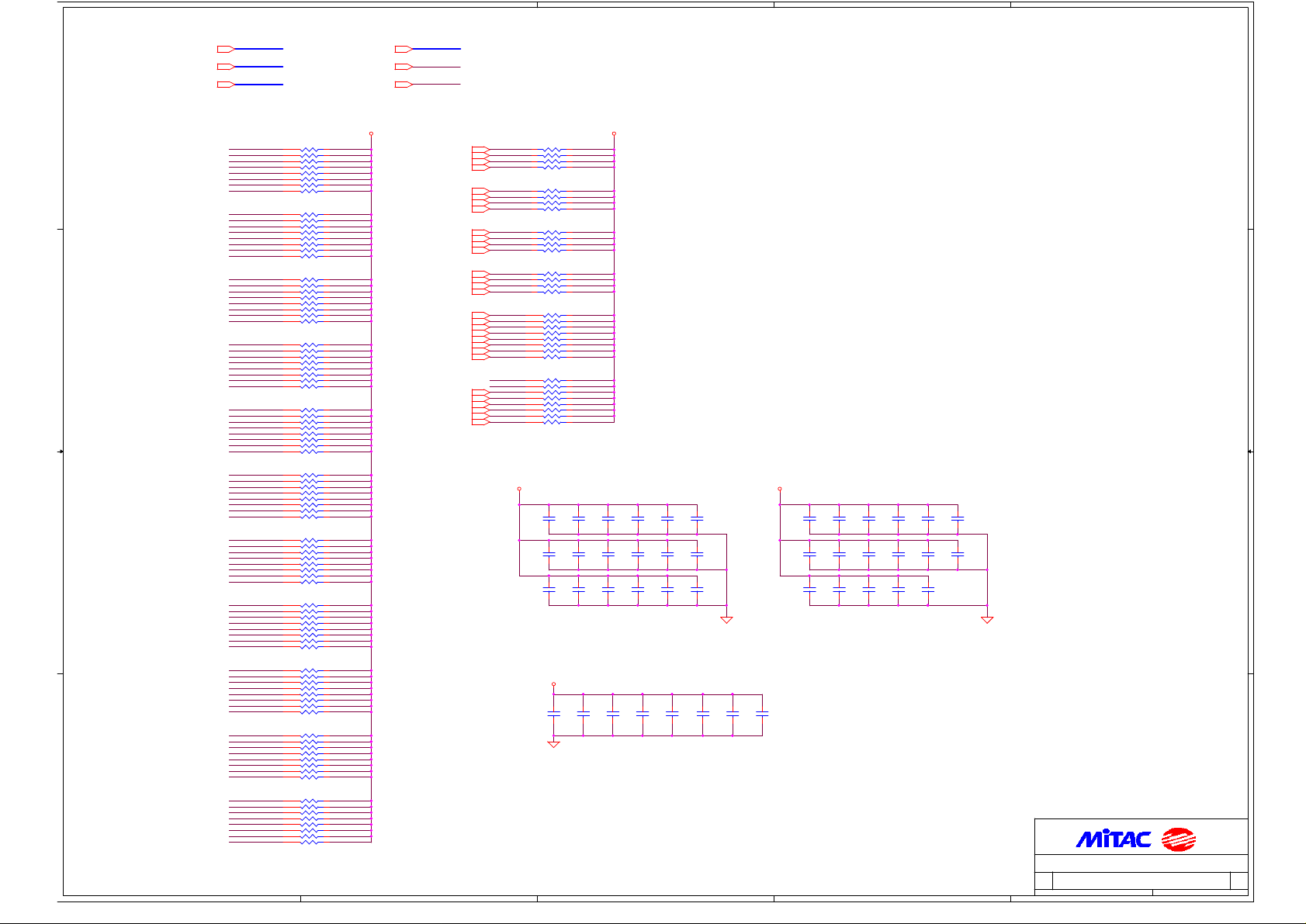

FS0

FS1

CLK_PCI_STOP#

CLK_CPU_STOP#

1 2

+3VCLKANA

+3VCLK66

+3VCLKCPU

+3VCLKPCI

FS2

R588

VTT_PW

VCH_CLK

1 2

R585

SMBDAT

SMBCLK

8.2K

0603D

8.2K

0603D

8.2K

0603D

8.2K

+3

V

SUSB#

U512

2

X1

3

X2

29

SDATA

30

SCLK

54

FS0

55

FS1

40

FS2

25

*PD#

34

PCI_STOP#

53

CPU_STOP#*

43

MULTSEL0*

RGD#

28

VTT_PWRGD#

1

VDDREF

37

VDD48

26

VDDA

19

VDD3V66_0

32

VDD3V66_1

46

VDDCPU0

50

VDDCPU1

8

VDDPCI0

14

VDDPCI1

4

GND0

9

GND1

15

GND2

20

GND3

27

GND4

31

GND5

36

GND6

41

GND7

47

GND8

ICS950810

TSSOP

GND

U506

1

CLKIN

8

*PD#

0/NA

A

6

SDATA

7

SCLK

ICS91718/NA

SO8

3

66MHZ_OUT0/3V66_2

66MHZ_OUT1/3V66_3

66MHZ_OUT2/3V66_4

56

**CLKOUT/FS_IN0

*REF_OUT/FS_IN1

48MHZ_USB

48MHZ_DOT

3V66_1/VCH_CLK

CPUCLKT0

CPUCLKT1

CPUCLKT2

CPUCLKC0

CPUCLKC1

CPUCLKC2

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

PCICLK6

PCICLK_F0

PCICLK_F1

PCICLK_F2

3V66_0

66MHZ_IN/3V66_5

VDD

GND

R592

33

0603

1 2

39

38

35

56

REF

33/NA

52

33 0603

49

33 0603

45

33/NA

51

33 0603

48

33 0603

44

10

11

12

13

16

17

18

5

6

7

21

22

23

33

24

42

IREF

12

GND

R587

1 2

4

5

1 2

R584

2

3

12

R586

10K/NA

0603

GND

1 2

1 2

330603

1 2

330603

0603

0603

R589

475

0603

1%

VCH_CLK

33/NA

10K/NA

R601

22

0603

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

330603

1 2

330603

1 2

330603

1 2

330603

1 2

330603

1 2

330603

1 2

330603

12

R610

33

0603

R611

R615

R593

0

0603

+3V

12

R604

R606

R608

R605

R607

R609

R628

R87

R86

R85

R627

R629

R630

R572

51/NA

0603

2

1 2

66M_DEFSSCLK

2

R614

330603

R591

R590

12

R595

R597

R599

R596

R598

R600

C620

10P/NA

0603

10%

5

001

0603

10%

0603

10%

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

12

C617

10P/NA

0603

10%

12

GND

1 2

1 2

C619

10P/NA

0603

10%

0603D

0603D

12

FS0

FS1

FS2

10P/NA

C601

10P/NA

49.9/NA

49.9

49.9

49.9/NA

49.9

49.9

C143

10P/NA

0603

10%

12

C590

C616

10P/NA

0603

10%

1

+3V

12

R616

4.7K/NA

0603

R613

4.7K

0603

0

1

1

00

0

1

1

C144

10P/NA

0603

10%

Document

Number

R625

4.7K/NA

0603

12

R621

4.7K

0603

GND

FS0

0

10

0

1

0

1

0

1

12

C586

10P/NA

0603

10%

12

R626

4.7K

0603

12

R622

4.7K/NA

0603

CPU

166.66

100.00

200.00

133.33

Tristate

TCLK/2

Reserved

Reserved

VCH_CLK

12

C587

10P/NA

0603

10%

GND

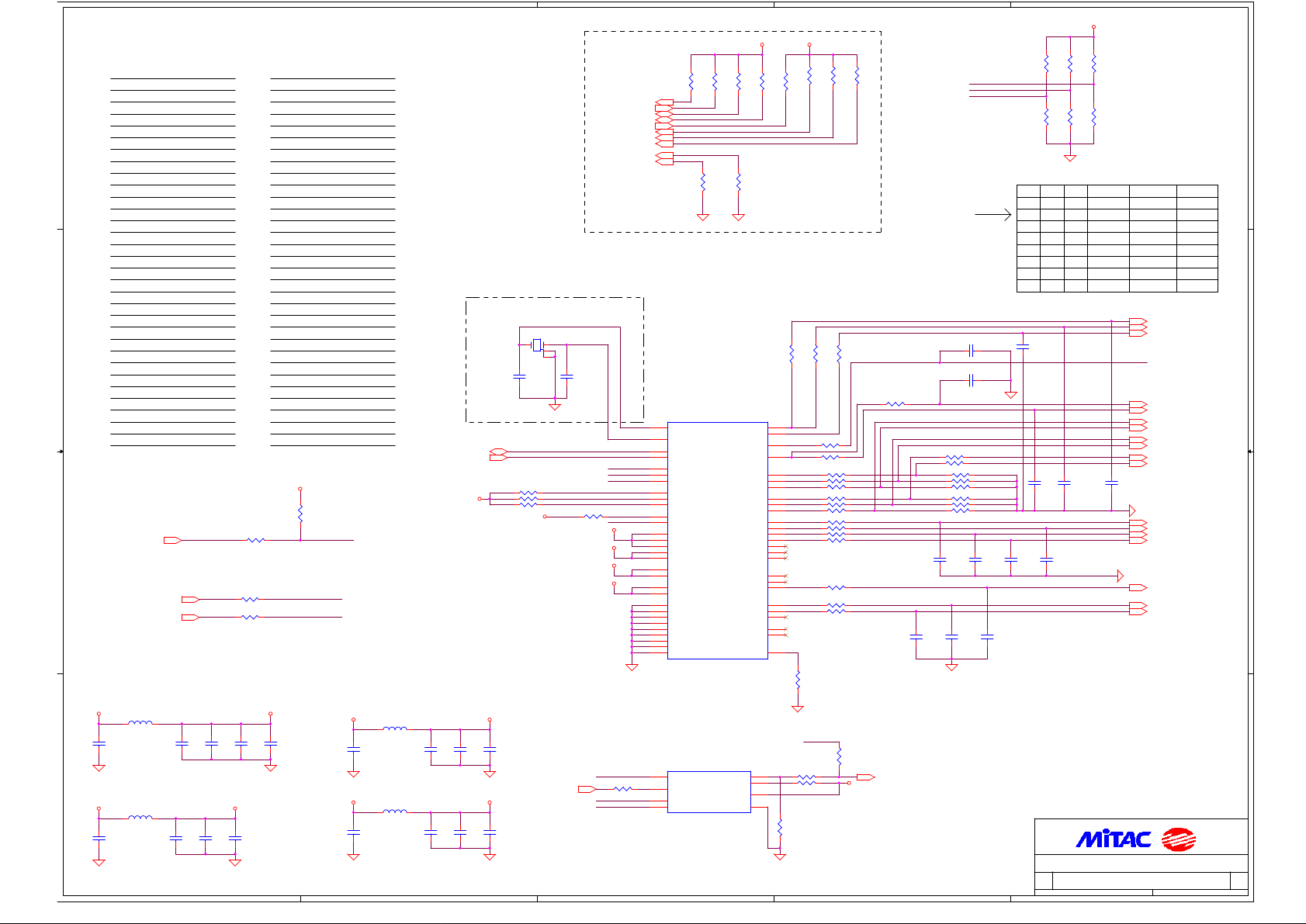

Clo

ck Generator

41167*******

Wednesday, June 11, 2003

1

3V66[5:0]

66.66

66.66

66.66

66.66

Tristate

TCLK/2

Reserved

Reserved

48M_DREFCLK

USBCLK_ICH

48M_SUPERIO

14M_CODEC

14M_ICH

HCLK_CPU#

HCLK_CPU

HCLK_MCH#

HCLK_MCH

CLK_ITP_CPU#

CLK_ITP_CPU

GND

PCICLK_LPC

PCICLK_MINIPCI

PCICLK_CARD

PCICLK_LAN

PCICLK_ICH

66M_MCH

66M_ICH

Sheet

PCI*

33.33

33.33

33.33

33.33

Tristate

TCLK/2

Reserved

Reserved

UNIT: MHz

5

11

19

13

10

3

3

5

5

3

3

19

17

18

16

10

5

11

4

Rev

01

28

of

12

12

FS1

FS2

X

X

X1

X

Mid

Mid

Mid

Mid

0:0V

1:3.3V

12

C589

10P/NA

0603

10%

GND

0/NA

0/NA

12

C602

10P/NA

0603

10%

12

12

C142

10P/NA

0603

10%

Tit

le

Siz

e

C

Date:

5

4

3

2

1

R27

R33

R28

R30

R531

R529

R23

R21

R22

R24

R528

R530

R31

R29

R34

R26

HUB_HI[0..10]

+1.2V

12

R546

243

0603

12

R547

100

0603

GND

+1.2V

ADD ID : 0x7Fh

1 2

8.2K/NA

1 2

8.2K/NA

1 2

8.2K/NA

1 2

8.2K/NA

1 2

8.2K/NA

1 2

8.2K/NA

1 2

8.2K/NA

1 2

8.2K/NA

1 2

330/NA

1 2

330/NA

1 2

330/NA

1 2

330/NA

1 2

330/NA

1 2

330/NA

1 2

330/NA

1 2

330/NA

10

HCLK_MCH

4

HCLK_MCH#

4

HDPSLP#

3,10

3

48M_DREFCLK

4

15

15

15

15

15

15

15

15

66M_MCH

4

11

11

MCH_PCIRST#

10

15

15

15

15

15

CRT_HSYNC

15

CRT_VSYNC

15

66M_DEFSSCLK

4

1%

12

1%

R542

1 2

27.4

0603

AGPBUSY#

HDPWR#

TXOUT

TXOUT

TXOUT

TXOU

T0+

TXOU

T1+

TXOU

T2+

TXC

LKOUT0-

TXC

LKOUT0+

HUB_HI[0..10]

HUB_STB

HUB_STB#

CRT_DDDA

CRT_DDCK

CRT_R

CRT_G

CRT_B

C540

0.1U

0603

50V

012-

+3V

+3V

12

HUB_RCOMP

AGPBUSY#

PM_SUSCLK

R19

1 2

HUB_MCH_VREF

HUB_RCOMP

1 2

R518

1 2

R524

GND

1 2

R522

HUB_MCH_VREF

C538

0.01U

0603

10K

DVOVREF

HUB_HI0

HUB_HI1

HUB_HI2

HUB_HI3

HUB_HI4

HUB_HI5

HUB_HI6

HUB_HI7

HUB_HI8

HUB_HI9

HUB_HI10

REFSET

10K

10K

0

AE29

AD29

AA22

AD28

E5

F5

E3

E2

G5

F4

G6

F6

F7

D5

Y23

B7

G14

E15

C15

C13

F14

E14

C14

B13

H12

E12

C12

G11

G12

E11

C11

G10

D14

E13

E10

F10

D6

Y3

F1

U7

U4

U3

V3

W2

W6

V6

W7

T3

V5

V4

W3

V2

W1

T2

E8

G9

B6

B4

C5

A7

A8

C8

D8

C9

D9

H10

J9

B17

U502A

ADDID[0]

ADDID[1]

ADDID[2]

ADDID[3]

ADDID[4]

ADDID[5]

ADDID[6]

ADDID[7]

AGPBUSY#

BCLK

BCLK#

DPMS

DPSLP#

DPWR#

DREFCLK

IYAM[0]

IYAM[1]

IYAM[2]

IYAM[3]

IYAP[0]

IYAP[1]

IYAP[2]

IYAP[3]

IYBM[0]

IYBM[1]

IYBM[2]

IYBM[3]

IYBP[0]

IYBP[1]

IYBP[2]

IYBP[3]

ICLKAM

ICLKAP

ICLKBM

ICLKBP

EXTTS_0

GCLKIN

GVREF

HL[0]

HL[1]

HL[2]

HL[3]

HL[4]

HL[5]

HL[6]

HL[7]

HL[8]

HL[9]

HL[10]

HLSTB

HLSTB#

HLVREF

HLRCOMP

RSTIN#

REFSET

DDCADATE

DDCACLK

DDCPCLK

DDCPDATA

RED

RED#

GEEN

GREEN#

BLUE

BLUE#

HSYNC

VSYNC

DEFSSCLK

MONTARA

BGA707_25

MCH_PSWING

2

+3V

P3

P4

R3

R5

R6

R4

P6

P5

N5

P2

N2

N3

M1

M5

M3

G2

M2

L2

T6

T5

J3

J2

K5

K1

K3

K2

J6

J5

H2

H1

H3

H4

H6

G3

L7

D1

H5

L3

K6

L5

H9

C6

A10

P7

T7

N7

M6

K7

N6

G8

F8

A5

U2

AC16

AC15

AJ29

AH29

B29

A29

AJ28

A28

AA9

AJ4

AJ2

A2

AH1

B1

GND

MCH_PSWING

RCVENIN#

RCVENOUT#

R544

49.9

0603

1%

R545

100

0603

1%

R17

1 2

10K

0603

DVOBCCLKINT

DVOBCINTR#

1 2

R543

10K

0603

1 2

R37

33

1 2

R527

40.2

1 2

R539

0/NA

R15

10K/NA

1 2

1 2

R14

10K/NA

R521

1 2

1 2

R44

10K

1 2

R46

10K

1 2

R42

10K

1 2

R40

10K

R25

0/NA

1 2

Tit

Siz

Date:

1.5K

le

e

C

1 2

R53

REFSET

Document

Number

GND

GND

DVOCFLDSTL

+3

V

GND

+1.5V

+1.5V

BLADJ

21,22

ENBL

22

FPVCC

15

0/NA

1 2

Wednesday, June 11, 2003

DVOBCCLKINT

12

GND

R18

137

0603

1%

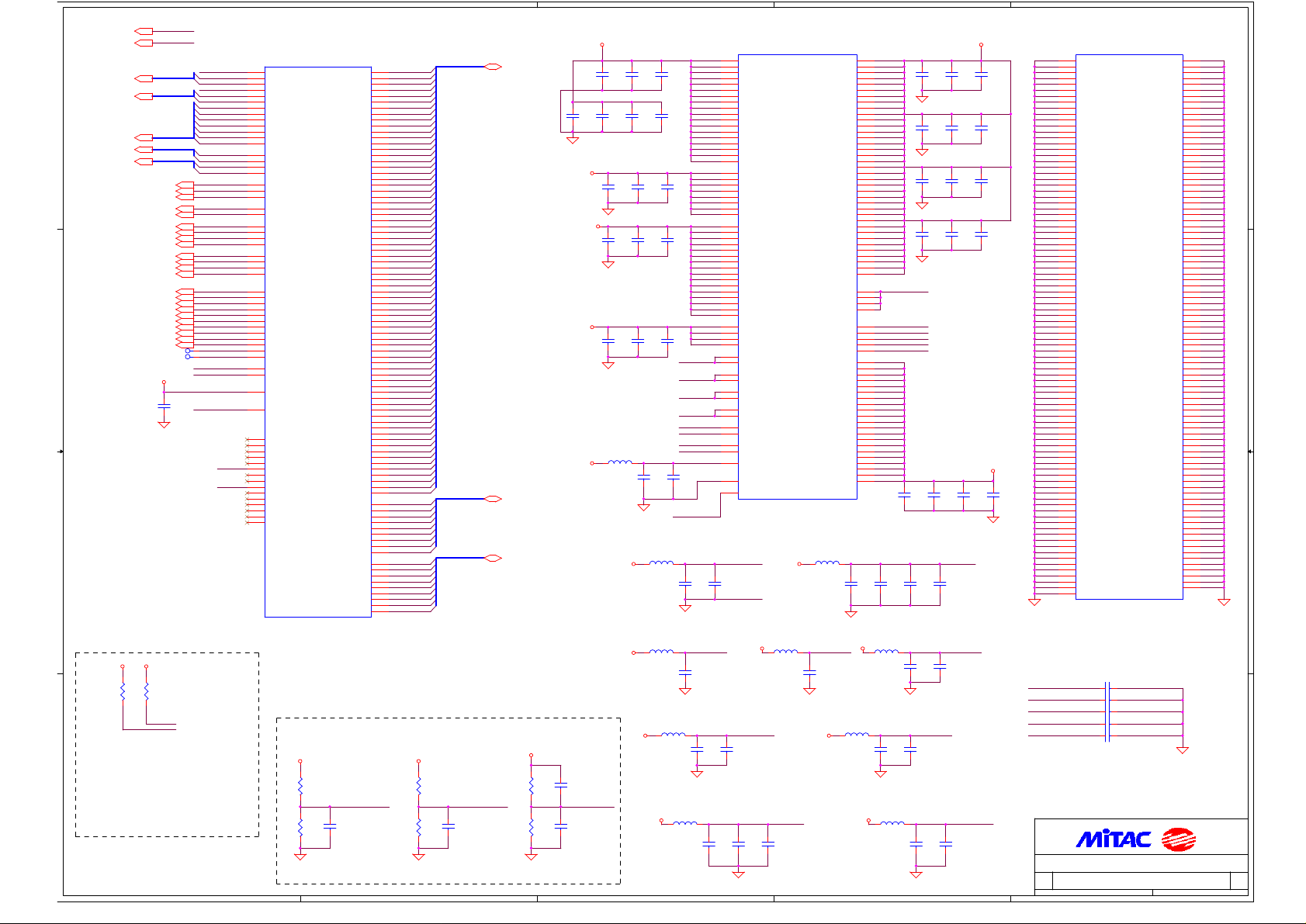

Montara_GM(

41167*******

1

GND

Sheet

GND

R32

10K

0603

12

R540

10K

0603

DVOBCINTR#

1)

5

+1.5V

12

R537

10K

0603

Rev

01

28

of

AGPBUSY#

DVOBCLK

DVOBCLK#

DVOBD[0]

DVOBD[1]

DVOBD[2]

DVOBD[3]

DVOBD[4]

DVOBD[5]

DVOBD[6]

DVOBD[7]

DVOBD[8]

DVOBD[9]

DVOBD[10]

DVOBD[11]

DVOBCCLKINT

DVOBCINTR#

DVOBFLDSTL

DVOBBLANK#

DVOBHSYNC

DVOBVSYNC

DVOCCLK

DVOCCLK#

DVOCD[0]

DVOCD[1]

DVOCD[2]

DVOCD[3]

DVOCD[4]

DVOCD[5]

DVOCD[6]

DVOCD[7]

DVOCD[8]

DVOCD[9]

DVOCD[10]

DVOCD[11]

DVODETECT

DVORCOMP

DVOCFLDSTL

DVOCBLANK#

DVOCHSYNC

DVOCVSYNC

LCLKCTLA

LCLKCTLB

LIBG

MDDCCLK

MDDCDATA

MDVICLK

MDVIDATA

MI2CCLK

MI2CDATA

PANELBKLTCTL

PANELBKLTEN

PANELVDDEN

PSWING

RCVENIN#

RCVENOUT#

NC_0

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

NC_10

-GM

NC_11

+1.2V

12

C533

0.1U

0603

50V

12

12

C534

1U

0603

12

+1.5V

D D

HA#[3..31]

3

HXRCOMP & HYRCOMP should be

route with 18 mil width

Less than 0.5"

HXRCOMP

1 2

R523

27.4

HYRCOMP

1 2

R533

27.4

GND

HREQ#[0..4]

3

C C

HDSTBP#[0..3]

3

HDSTBN#[0..3]

3

HDINV#[0..3]

3

B B

A A

HRS#[0..2]

3

Maximum length less than 0.5" from pin to

voltage divider.

HAVREF

12

C63

0.1U

0603

50V

10,21

3

3

3

3

3

3

3

3

3

3

3

3

3

HADSTB#0

HADSTB#1

3,4

PWROK

HA#[3..31]

HREQ#[0..4]

HDSTBP#[0..3]

HDSTBN#[0..3]

HDINV#[0..3]

HADS#

HTRDY#

HDRDY#

HDEFER#

HHITM#

HHIT#

HLOCK#

HBR0#

HBNR#

HBPRI#

HDBSY#

HRS#[0..2]

HCPURST#

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HXRCOMP

HXSWING

HYRCOMP

HYSWING

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HRS#0

HRS#1

HRS#2

1 2

R36

0

AA27

AA28

AB27

AB28

AA26

W25

W24

W23

W27

W28

P23

T25

T28

R27

U23

U24

R24

U28

V28

U27

T27

V27

U25

V26

Y24

V25

V23

Y25

Y27

Y26

R28

P25

R23

R25

T23

T26

B20

B18

H28

K28

K27

D26

E21

E18

J28

C27

E22

D18

J25

E25

B25

G19

L28

M25

N24

M28

N28

N27

P27

M23

N25

P28

M26

N23

P26

M27

F15

J11

U502B

HA[3]#

HA[4]#

HA[5]#

HA[6]#

HA[7]#

HA[8]#

HA[9]#

HA[10]#

HA[11]#

HA[12]#

HA[13]#

HA[14]#

HA[15]#

HA[16]#

HA[17]#

HA[18]#

HA[19]#

HA[20]#

HA[21]#

HA[22]#

HA[23]#

HA[24]#

HA[25]#

HA[26]#

HA[27]#

HA[28]#

HA[29]#

HA[30]#

HA[31]#

HREQ[0]#

HREQ[1]#

HREQ[2]#

HREQ[3]#

HREQ[4]#

HADSTB[0]#

HADSTB[1]#

HXRCOMP

HXSWING

HYRCOMP

HYSWING

HDSTBP[0]#

HDSTBP[1]#

HDSTBP[2]#

HDSTBP[3]#

HDSTBN[0]#

HDSTBN[1]#

HDSTBN[2]#

HDSTBN[3]#

DINV[0]#

DINV[1]#

DINV[2]#

DINV[3]#

ADS#

HTRDY#

DRDY#

DEFER#

HITM#

HIT#

HLOCK#

BREQ0#

BNR#

BPRI#

DBSY#

RS[0]#

RS[1]#

RS[2]#

CPURST#

PWROK

MONTARA

BGA707_25

HD[0]#

HD[1]#

HD[2]#

HD[3]#

HD[4]#

HD[5]#

HD[6]#

HD[7]#

HD[8]#

HD[9]#

HD[10]#

HD[11]#

HD[12]#

HD[13]#

HD[14]#

HD[15]#

HD[16]#

HD[17]#

HD18]#

HD[19]#

HD[20]#

HD[21]#

HD[22]#

HD[23]#

HD24]#

HD[25]#

HD[26]#

HD[27]#

HD[28]#

HD[29]#

HD[30]#

HD[31]#

HD[32]#

HD[33]#

HD[34]#

HD[35]#

HD[36]#

HD[37]#

HD[38]#

HD[39]#

HD[40]#

HD[41]#

HD[42]#

HD[43]#

HD[44]#

HD[45]#

HD[46]#

HD[47]#

HD[48]#

HD[49]#

HD[50]#

HD[51]#

HD[52]#

HD[53]#

HD[54]#

HD[55]#

HD[56]#

HD[57]#

HD[58]#

HD[59]#

HD[60]#

HD[61]#

HD[62]#

HD[63]#

HDVREF[0]

HDVREF[1]

HDVREF[2]

HAVREF

HCCVREF

-GM

HD#1

H27

HD#2

K25

HD#3

L24

HD#4

J27

HD#5

G28

HD#6

L27

HD#7

L23

HD#8

L25

HD#9

J24

HD#10

H25

HD#11

K23

HD#12

G27

HD#13

K26

HD#14

J23

HD#15

H26

HD#16

F25

HD#17

F26

HD#18

B27

HD#19

H23

HD#20

E27

HD#21

G25

HD#22

F28

HD#23

D27

HD#24

G24

HD#25

C28

HD#26

B26

HD#27

G22

HD#28

C26

HD#29

E26

HD#30

G23

HD#31

B28

HD#32

B21

HD#33

G21

HD#34

C24

HD#35

C23

HD#36

D22

HD#37

C25

HD#38

E24

HD#39

D24

HD#40

G20

HD#41

E23

HD#42

B22

HD#43

B23

HD#44

F23

HD#45

F21

HD#46

C20

HD#47

C21

HD#48

G18

HD#49

E19

HD#50

E20

HD#51

G17

HD#52

D20

HD#53

F19

HD#54

C19

HD#55

C17

HD#56

F17

HD#57

B19

HD#58

G16

HD#59

E16

HD#60

C16

HD#61

E17

HD#62

D16

HD#63

C18

K21

J21

J17

HAVREF

Y22

HCCVREF

Y28

HD#0

K22

12

HD#[0..63]

C32

0.1U

0603

50V

HD#[0..63]

3

+1.5V

12

R16

1K

0603

PM_SUSCLK

DS

DSQ6

12

R536

1K

0603

1%

12

R532

1K

0603

1%

GND

+VCCP

12

C38

1U

0603

G

GND

1 2

R20

Place near to GMCH.

12

C526

0.1U

0603

50V

GND

12

R35

Maximum length less than

49.9

0.5" from pin to voltage

0603

divider.

1%

12

R39

100

0603

1%

GND

2N7002

0/NA

DVOVREF

SUSCLK

10

+1.5V

12

C33

0.1U

0603

50V

GND

11

Non SSC

W/ SSC

Less than 0.5"

+VCCP

(1.05V)

12

R49

49.9

0603

1%

HCCVREF

12

12

R51

C65

100

1U

0603

0603

1%

GND

5

+VCCP

12

R549

49.9

0603

1%

C541

0.1U

0603

50V

12

12

R548

C542

100

1U

0603

0603

1%

GND

12

HXSWING HYSWING

4

+VCCP +VCCP

12

R516

301

0603

12

12

R515

C522

150

0.1U

0603

0603

50V

GND

12

R538

301

0603

12

12

R541

C531

150

0.1U

0603

0603

50V

GND

3

5

NB_MA0

7

NB_MA3

7

SMA[1..2]

7,9

SMA[4..5]

7,9

D D

NB_MA[6..12]

7

SMAB[1..2]

8,9

SMAB[4..5]

8,9

C C

B B

+1.5V +1.5V

Clock config bit GST[1,0]

PSB/Sys Mem Core/GFX Core(CL/CH)

A A

00(def): 400/266/200(133/200)

01 : 400/200/200(100/200)

10 : 400/200/133(100/133)

NB_MA0

NB_MA3

GST0

GST1

U502C

AC18

SMA[0]

AD14

SMA[1]

AD13

SMA[2]

AD17

SMA[3]

AD11

SMA[4]

AC13

SMA[5]

AD8

SMA[6]

AD7

SMA[7]

AC6

SMA[8]

AC5

SMA[9]

AC19

SMA[10]

AD5

SMA[11]

AB5

SMA[12]

AD16

SMAB[1]

AC12

SMAB[2]

AF11

SMAB[4]

AD10

SMAB[5]

AD25

SWE#

AC24

SCAS#

AC21

SRAS#

AD22

SBA[0]

AD20

SBA[1]

AD23

SCS[0]#

AD26

SCS[1]#

AC22

SCS[2]#

AC25

SCS[3]#

AC7

SCKE[0]

AB7

SCKE[1]

AC9

SCKE[2]

AC10

SCKE[3]

AB2

SCK[0]

AA2

SCK[0]#

AC26

SCK[1]

AB25

SCK[1]#

AC3

SCK[2]

AD4

SCK[2]#

AC2

SCK[3]

AD2

SCK[3]#

AB23

SCK[4]

AB24

SCK[4]#

AA3

SCK[5]

AB4

SCK[5]#

AJ19

SMVSWINGH

AJ22

SMVSWINGL

AJ24

SMVREF_0

AB1

SMRCOMP

F12

RSVD_0

D12

RSVD_1

B12

RSVD_2

AA5

RSVD_3

L4

RSVD_4

C4

RSVD_5

F3

RSVD_6

D3

RSVD_7

C3

RSVD_8

B3

RSVD_9

F2

RSVD_10

D2

RSVD_11

C2

RSVD_12

B2

RSVD_13

D7

RSVD_14

MONTARA

-GM

BGA707_25

+2.5V_DDR +2.5V_DDR

12

R557

604

0603

1%

MCH_SMVSWINGL

12

12

R556

C554

150

0.1U

0603

0603

50V

SDQ[0]

SDQ[1]

SDQ[2]

SDQ[3]

SDQ[4]

SDQ[5]

SDQ[6]

SDQ[7]

SDQ[8]

SDQ[9]

SDQ[10]

SDQ[11]

SDQ[12]

SDQ[13]

SDQ[14]

SDQ[15]

SDQ[16]

SDQ[17]

SDQ[18]

SDQ[19]

SDQ[20]

SDQ[21]

SDQ[22]

SDQ[23]

SDQ[24]

SDQ[25]

SDQ[26]

SDQ[27]

SDQ[28]

SDQ[29]

SDQ[30]

SDQ[31]

SDQ[32]

SDQ[33]

SDQ[34]

SDQ[35]

SDQ[36]

SDQ[37]

SDQ[38]

SDQ[39]

SDQ[40]

SDQ[41]

SDQ[42]

SDQ[43]

SDQ[44]

SDQ[45]

SDQ[46]

SDQ[47]

SDQ[48]

SDQ[49]

SDQ[50]

SDQ[51]

SDQ[52]

SDQ[53]

SDQ[54]

SDQ[55]

SDQ[56]

SDQ[57]

SDQ[58]

SDQ[59]

SDQ[60]

SDQ[61]

SDQ[62]

SDQ[63]

SDQ[64]

SDQ[65]

SDQ[66]

SDQ[67]

SDQ[68]

SDQ[69]

SDQ[70]

SDQ[71]

SDQS[0]

SDQS[1]

SDQS[2]

SDQS[3]

SDQS[4]

SDQS[5]

SDQS[6]

SDQS[7]

SDQS[8]

SDM[0]

SDM[1]

SDM[2]

SDM[3]

SDM[4]

SDM[5]

SDM[6]

SDM[7]

SDM[8]

TP

1

TP

3

12

C557

0.1U

0603

50V

GND

1

1

MCH_SMVSWINGH

MCH_SMVSWINGL

MCH_SMRCOMP

5

NB_MA0

SMA1

SMA2

NB_MA3

SMA4

SMA5

NB_MA6

NB_MA7

NB_MA8

NB_MA9

NB_MA10

NB_MA11

NB_MA12

SMAB1

SMAB2

SMAB4

SMAB5

SMA[1..2]

SMA[4..5]

NB_MA[6..12]

SMAB[1..2]

SMAB[4..5]

NB_WE#

7

NB_CAS#

7

NB_RAS#

7

NB_BA0

7

NB_BA1

7

CS#0

7,9

CS#1

7,9

CS#2

8,9

CS#3

8,9

CKE0

7,9

CKE1

7,9

CKE2

8,9

CKE3

8,9

CLK_DDR0

7

CLK_DDR0#

7

CLK_DDR1

7

CLK_DDR1#

7

CLK_DDR2

7

CLK_DDR2#

7

CLK_DDR3

8

CLK_DDR3#

8

CLK_DDR4

8

CLK_DDR4#

8

+1.25V_DDR

12

12

R525

R526

1K/NA

1K/NA

0603

0603

GST0

GST1

4

AF2

AE3

AF4

AH2

AD3

AE2

AG4

AH3

AD6

AG5

AG7

AE8

AF5

AH4

AF7

AH6

AF8

AG8

AH9

AG10

AH7

AD9

AF10

AE11

AH10

AH11

AG13

AF14

AG11

AD12

AF13

AH13

AH16

AG17

AF19

AE20

AD18

AE18

AH18

AG19

AH20

AG20

AF22

AH22

AF20

AH19

AH21

AG22

AE23

AH23

AE24

AH25

AG23

AF23

AF25

AG25

AH26

AE26

AG28

AF28

AG26

AF26

AE27

AD27

AG14

AE14

AE17

AG16

AH14

AE15

AF16

AF17

AG2

AH5

AH8

AE12

AH17

AE21

AH24

AH27

AD15

AE5

AE6

AE9

AH12

AD19

AD21

AD24

AH28

AH15

NB_MD0

NB_MD1

NB_MD2

NB_MD3

NB_MD4

NB_MD5

NB_MD6

NB_MD7

NB_MD8

NB_MD9

NB_MD10

NB_MD11

NB_MD12

NB_MD13

NB_MD14

NB_MD15

NB_MD16

NB_MD17

NB_MD18

NB_MD19

NB_MD20

NB_MD21

NB_MD22

NB_MD23

NB_MD24

NB_MD25

NB_MD26

NB_MD27

NB_MD28

NB_MD29

NB_MD30

NB_MD31

NB_MD32

NB_MD33

NB_MD34

NB_MD35

NB_MD36

NB_MD37

NB_MD38

NB_MD39

NB_MD40

NB_MD41

NB_MD42

NB_MD43

NB_MD44

NB_MD45

NB_MD46

NB_MD47

NB_MD48

NB_MD49

NB_MD50

NB_MD51

NB_MD52

NB_MD53

NB_MD54

NB_MD55

NB_MD56

NB_MD57

NB_MD58

NB_MD59

NB_MD60

NB_MD61

NB_MD62

NB_MD63

NB_MD64

NB_MD65

NB_MD66

NB_MD67

NB_MD68

NB_MD69

NB_MD70

NB_MD71

NB_DQS0

NB_DQS1

NB_DQS2

NB_DQS3

NB_DQS4

NB_DQS5

NB_DQS6

NB_DQS7

NB_DQS8

NB_DM0

NB_DM1

NB_DM2

NB_DM3

NB_DM4

NB_DM5

NB_DM6

NB_DM7

NB_DM8

NB_MD[0..71]

NB_DQS[0..8]

NB_DM[0..8]

Place within 0.5" with 15-mil wide.

12

R554

150

0603

MCH_SMVSWINGH

12

12

R555

C553

604

0.1U

0603

0603

50V

1%

GNDGND

4

NB_MD[0..71]

NB_DQS[0..8]

NB_DM[0..8]

+2.5V_DDR

3

+1.2V

12

12

C67

C68

0.1U

0.1U

0603

0603

50V

50V

12

12

C57

C30

0.1U

0.1U

0603

0603

50V

50V

12

12

C60

C41

10U

1206

10V

C42

10U

1206

10V

GND

C48

10U

1206

10V

GND

+1.5V

+1.2V

+1.2V +1.2V

0.1U

0603

50V

12

C35

0.1U

0603

50V

12

C31

0.1U

0603

50V

12

C515

0.1U

0603

50V

GND

1 2

L506

120Z/100M

1 2

L511

120Z/100M

1 2

+2.5V_DDR

3

C58

0.1U

0603

50V

12

C39

0.1U

0603

50V

12

C36

0.1U

0603

50V

VCCADAC

VCCASM

VCCGPIO

VCCQSM

VCCADPLLA

VCCADPLLB

VCCAGPLL

VCCAHPLL

VCCALVDS

12

C520

0.01U

0603

VSSADAC

12

C508

0.1U

0603

50V

GND

VCCAHPLL

12

C523

0.1U

0603

50V

GND GND

L510

120Z/100M

1 2

L13

120Z/100M

12

C69

0.1U

0603

50V

GND

+1.2V

+1.5V

+1.5V

+1.5V

12

C544

0.1U

0603

50V

MCH_SMRCOMP

12

C545

0.1U/NA

0603

50V

12

C61

10U

1206

10V

12

C66

0.1U

0603

50V

12

GND

12

12

1 2

L508

120Z/100M

7

7

7

12

R551

60.4

0603

1%

12

R550

60.4

0603

1%

GND

U502D

W21

VCC_0

AA19

VCC_1

AA17

VCC_2

T17

VCC_3

P17

VCC_4

U16

VCC_5

R16

VCC_6

N16

VCC_7

AA15

VCC_8

T15

VCC_9

P15

VCC_10

J15

VCC_11

U14

VCC_12

R14

VCC_13

N14

VCC_14

H14

VCC_15

T13

VCC_16

P13

VCC_17

V9

VCCHL_0

W8

VCCHL_1

U8

VCCHL_2

V7

VCCHL_3

U6

VCCHL_4

W5

VCCHL_5

Y1

VCCHL_6

V1

VCCHL_7

P9

VCCDVO_0

M9

VCCDVO_1

K9

VCCDVO_2

R8

VCCDVO_3

N8

VCCDVO_4

M8

VCCDVO_5

L8

VCCDVO_6

J8

VCCDVO_7

H7

VCCDVO_8

E6

VCCDVO_9

M4

VCCDVO_10

J4

VCCDVO_11

E4

VCCDVO_12

N1

VCCDVO_13

J1

VCCDVO_14

E1

VCCDVO_15

B15

VCCDLVDS_0

B14

VCCDLVDS_1

J13

VCCDLVDS_2

G13

VCCDLVDS_3

B9

VCCADAC_0

A9

VCCADAC_1

AF1

VCCASM_0

AD1

VCCASM_1

A4

VCCGPIO_0

A3

VCCGPIO_1

AJ8

VCCQSM_0

AJ6

VCCQSM_1

A6

VCCADPLLA

B16

VCCADPLLB

Y2

VCCAGPLL

D29

VCCAHPLL

A11

VCCALVDS

B11

VSSALVDS

B8

VSSADAC

MONTARA

-GM

BGA707_25

VCCADAC

12

C513

0.01U

0603

VSSADAC

VCCADPLLA

12

12

C519

C512

22U

1206

10V

GND

12

C10

22U

1206

10V

0.01U

0603

+1.2V

+1.2V

1 2

L512

120Z/100M

VCCTXLVD

12

12

C12

C9

10U

0.01U

1206

0603

10V

GND

VCCTXLVDS_0

VCCTXLVDS_1

VCCTXLVDS_2

VCCTXLVDS_3

1 2

L513

120Z/100M

VCCAGPLL

12

C543

0.1U

0603

50V

S

VCCSM_0

VCCSM_1

VCCSM_2

VCCSM_3

VCCSM_4

VCCSM_5

VCCSM_6

VCCSM_7

VCCSM_8

VCCSM_9

VCCSM_10

VCCSM_11

VCCSM_12

VCCSM_13

VCCSM_14

VCCSM_15

VCCSM_16

VCCSM_17

VCCSM_18

VCCSM_19

VCCSM_20

VCCSM_21

VCCSM_22

VCCSM_23

VCCSM_24

VCCSM_25

VCCSM_26

VCCSM_27

VCCSM_28

VCCSM_29

VCCSM_30

VCCSM_31

VCCSM_32

VCCSM_33

VCCSM_34

VCCSM_35

VCCSM_36

VTTHF_0

VTTHF_1

VTTHF_2

VTTHF_3

VTTHF_4

VTTLF_0

VTTLF_1

VTTLF_2

VTTLF_3

VTTLF_4

VTTLF_5

VTTLF_6

VTTLF_7

VTTLF_8

VTTLF_9

VTTLF_10

VTTLF_11

VTTLF_12

VTTLF_13

VTTLF_14

VTTLF_15

VTTLF_16

VTTLF_17

VTTLF_18

VTTLF_19

VTTLF_20

1 2

L507

120Z/100M

12

C546

22U

1206

10V

GND

+3

AG29

AF29

AC29

AF27

AJ25

AF24

AB22

AJ21

AF21

AB20

AF18

AB18

AJ17

AB16

AF15

AB14

AJ13

AA13

AF12

AB12

AA11

AB10

AJ9

AF9

Y9

AB8

AA8

Y7

AF6

AB6

AA6

AJ5

Y4

AF3

AB3

AG1

AC1

A12

D10

B10

F9

V29

M29

H29

A24

A22

AB29

Y29

K29

F29

A26

V22

T22

P22

M22

H22

U21

R21

N21

L21

H20

A20

J19

H18

A18

H16

G15

12

V

1 2

L509

120Z/100M

12

+2.5V_DDR

1 2

L514

120Z/100M

2

VCCTXLVD

VTTH

VTTH

VTTH

VTTH

VTTH

C549

22U

1206

10V

C514

22U

1206

10V

GND

2

F_0

F_1

F_2

F_3

F_4

12

12

12

12

12

GND

12

GND

12

GND

12

GND

S

C37

0.1U

0603

50V

C551

10U

1206

10V

C511

10U

1206

10V

GND

VCCADPLLB

C521

0.01U

0603

12

C558

4.7U

0805

+80-20

GND

C555

0.1U

0603

50V

C87

0.1U

0603

50V

C86

0.1U

0603

50V

C29

0.1U

0603

50V

1

+2.5V_DDR

(1.9A)

12

12

C556

C70

0.1U

10U

0603

1206

50V

10V

12

12

C74

C548

10U

0.1U

1206

0603

10V

50V

12

12

C75

C550

10U

0.1U

1206

0603

10V

50V

12

12

C73

C71

10U

0.1U

1206

0603

10V

50V

+VCCP

12

C40

0.1U

0603

50V

VCCASM

12

12

12

%

C547

0.01U

0603

VCCGPIO

C518

0.01U

0603

VCCQSM

C552

0.01U

0603

12

12

C45

C34

22U

22U

1206

1206

10V

10V

GND

U502E

AA29

VSS_0

W29

VSS_1

U29

VSS_2

N29

VSS_3

L29

VSS_4

J29

VSS_5

G29

VSS_6

E29

VSS_7

C29

VSS_8

AE28

VSS_9

AC28

VSS_10

E28

VSS_11

D28

VSS_12

AJ27

VSS_13

AG27

VSS_14

AC27

VSS_15

F27

VSS_16

A27

VSS_17

AJ26

VSS_18

AB26

VSS_19

W26

VSS_20

R26

VSS_21

N26

VSS_22

L26

VSS_23

J26

VSS_24

G26

VSS_25

AE25

VSS_26

AA25

VSS_27

D25

VSS_28

A25

VSS_29

AG24

VSS_30

AA24

VSS_31

V24

VSS_32

T24

VSS_33

P24

VSS_34

M24

VSS_35

K24

VSS_36

H24

VSS_37

F24

VSS_38

B24

VSS_39

AJ23

VSS_40

AC23

VSS_41

AA23

VSS_42

D23

VSS_43

A23

VSS_44

AE22

VSS_45

W22

VSS_46

U22

VSS_47

R22

VSS_48

N22

VSS_49

L22

VSS_50

J22

VSS_51

F22

VSS_52

C22

VSS_53

AG21

VSS_54

AB21

VSS_55

AA21

VSS_56

Y21

VSS_57

V21

VSS_58

T21

VSS_59

P21

VSS_60

M21

VSS_61

H21

VSS_62

D21

VSS_63

A21

VSS_64

AJ20

VSS_65

AC20

VSS_66

AA20

VSS_67

J20

VSS_68

F20

VSS_69

AE19

VSS_70

AB19

VSS_71

H19

VSS_72

D19

VSS_73

A19

VSS_74

AJ18

VSS_75

AG18

VSS_76

AA18

VSS_77

J18

VSS_78

F18

VSS_79

AC17

VSS_80

AB17

VSS_81

U17

VSS_82

R17

VSS_83

N17

VSS_84

H17

VSS_85

D17

VSS_86

A17

VSS_87

AE16

VSS_88

AA16

VSS_89

T16

VSS_90

MONTARA-

GND GND

VTTH

F_0

VTTH

F_1

VTTH

F_2

VTTH

F_3

VTTH

F_4

Tit

le

Siz

e

Document

C

Number

Date:

GM

BGA707_25

C536

0.1U