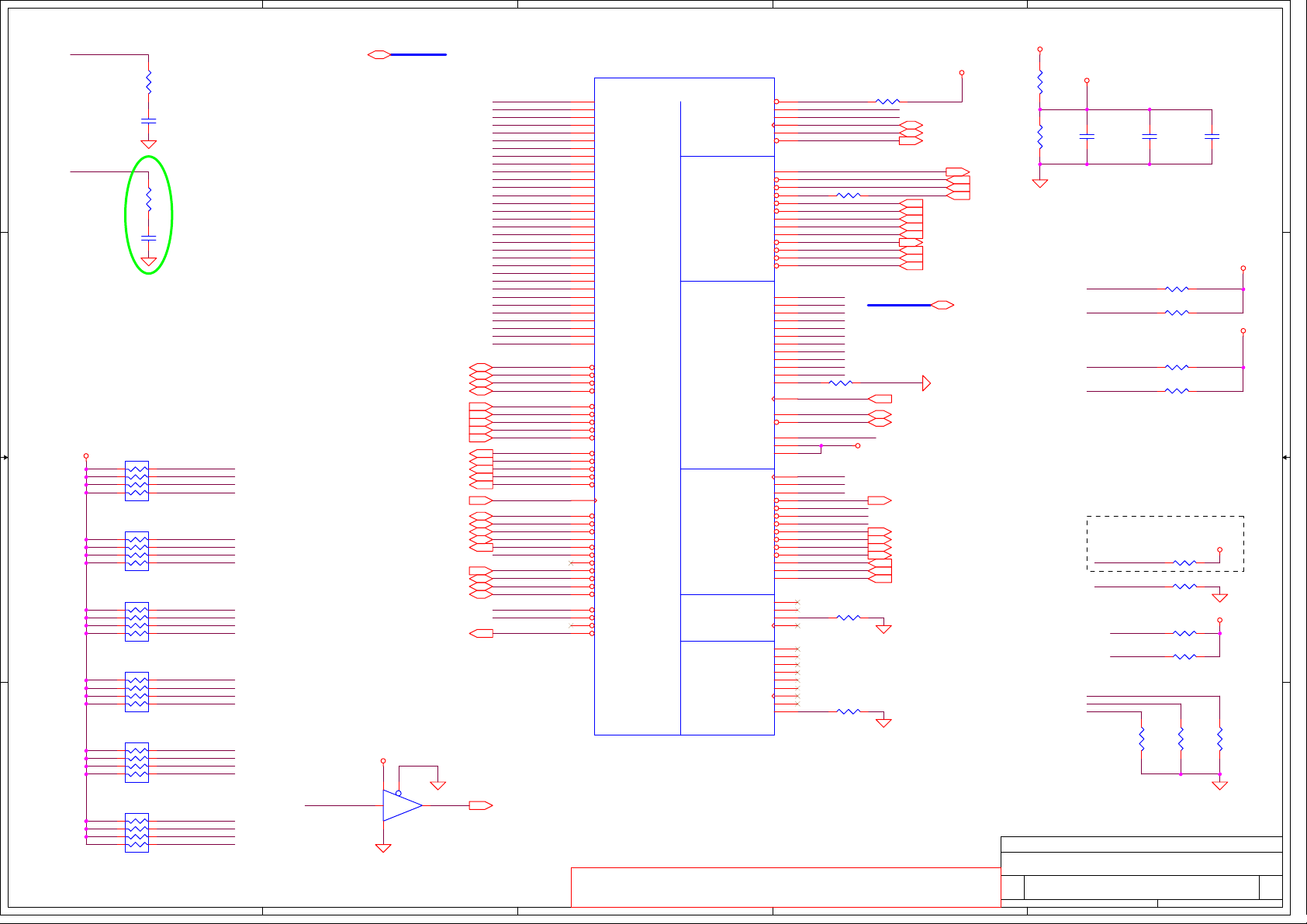

Lenovo A500G E600 Schematics

A

1 1

B

C

D

E

2 2

Compal Confidential

DAT20 Schematics Document

Banias uFCPGA Package with 855PM(Odem) + ICH4-M

3 3

2003-09-25

REV: 0.3

4 4

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SE CRET INFO RMATI ON. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Cover Sheet

Size Document Number Rev

Custom

DAT20 LA-1971

Date: Sheet

142Friday, September 26, 2003

E

of

0.3

A

B

C

D

E

Compal confidential

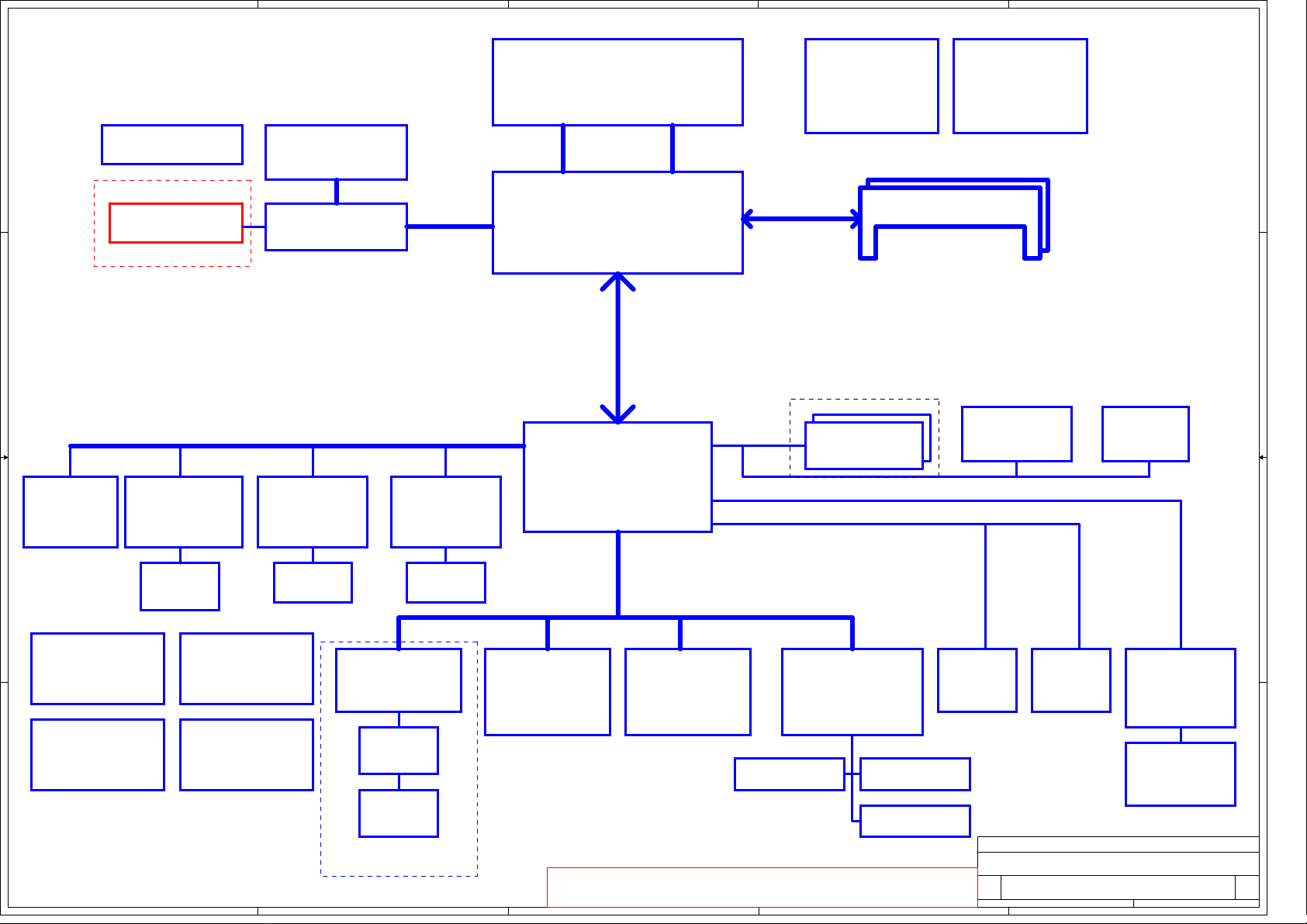

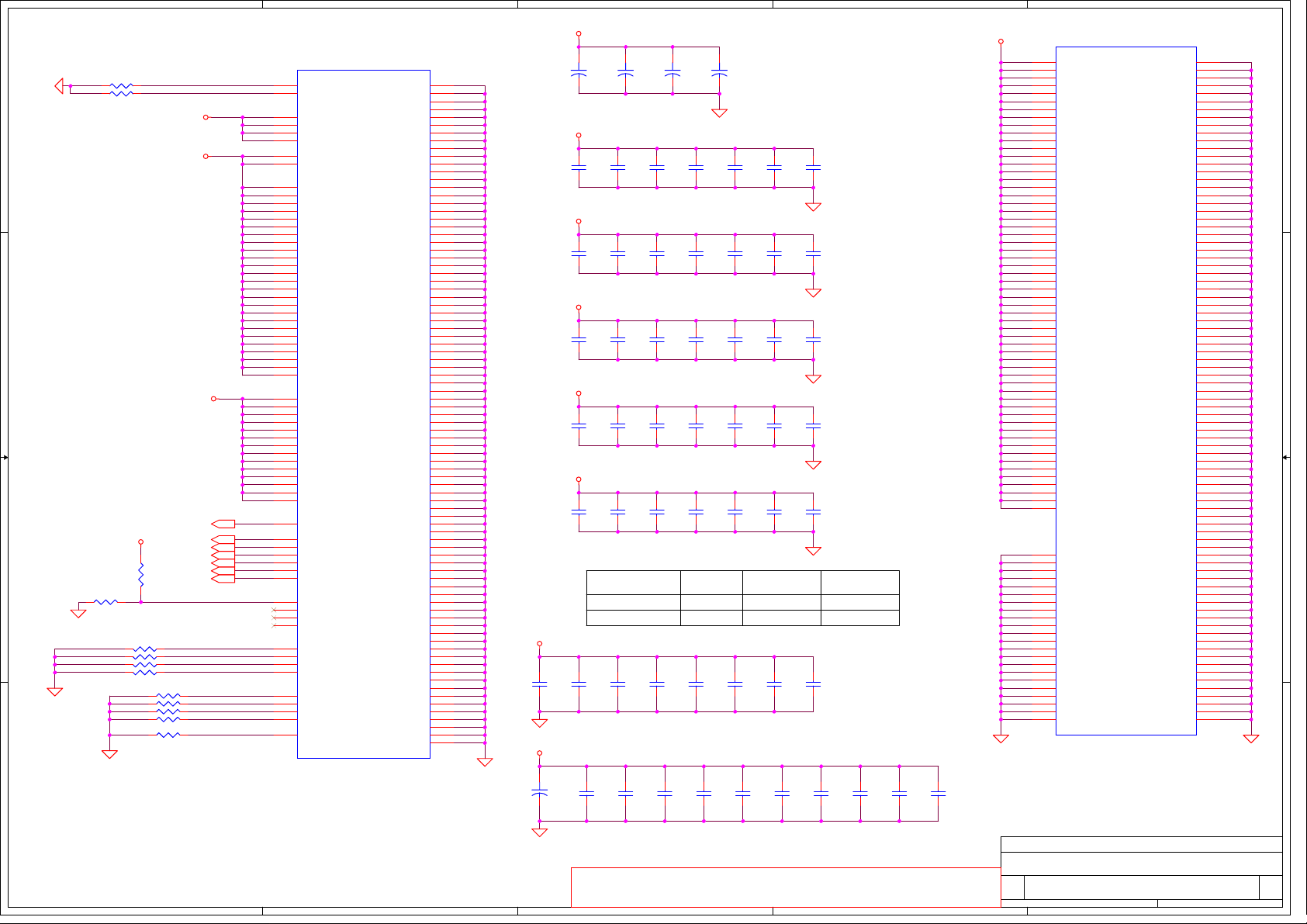

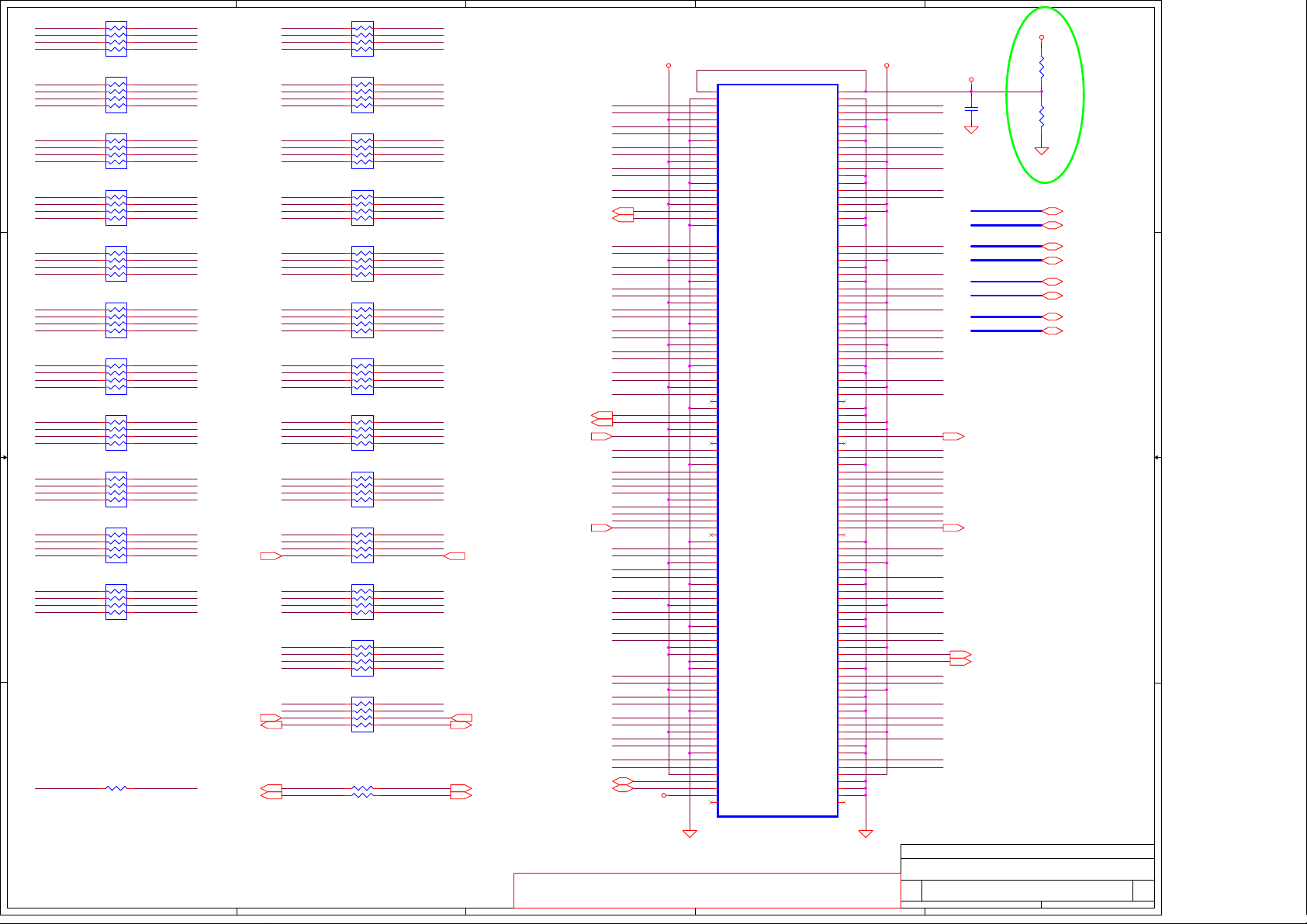

Block Diagram

Model Name : DAT20

File Name : LA-1971 Rev:0.3

Part Number : DA8AT20L000

1 1

Fan Control

page 29

VGA

Board

2 2

IDSEL: AD18

PIRQG#, PIRQH#

GNT#1, REQ#1

GNT#4, REQ#4

IDSEL: AD16

PIRQE#

GNT#0, REQ#0

CRT

TV-OUT CONN.

AGP Conn

IDSEL: AD17

PIRQF#

GNT#3, REQ#3

page 18

page 17

PCI BUS

PIRQA#

AGP4X(1.5V)

IDSEL: AD20

PIRQA#

GNT#2, REQ#2

SERIRQ

3.3V 33MHz

Mobile Banias

uFCPGA CPU

478pin

System Bus

400MHz

Odem-B

uFCBGA-593 pin

HUB-LINK

ICH4-M

page 4,5

HD#(0..63)HA#(3..31)

page 6,7,8

Memory

BUS(DDR)

2.5V 200/266/333MHz

3.3V 48MHz

Thermal Se nsor

ADM1032ARM

DDR-SO-DIMM X2

BANK 0, 1, 2, 3

USB port 0, 2

USB conn

page 24

page 4

USBx2

Clock Generator

ICS950810CG

page 12

page 9,10,11

USB port 4

BlueTooth I/F

page 26

USB port 5

I-Stick

page 24

MINI

PCI I/F

3 3

DC/DC Interface

1394 Controller

TI TSB43AB21A

page 22page 23

1394

Connector

page 22

LED INDICATOR

Suspend

page 33

Power Circuit

DC/DC

page

34,35,36,37,38,39,40

4 4

page 17

Power On/Off

Reset & RTC

LAN

RTL 8101L

page 21

RJ45

page 21

page 29

page 29

CardBus

ENE CB1410

Slot 0

page 20

SIO LPC47N217

Base I/O Address 2Eh

page 25

PARALLEL

page 26

page 19

TPM

SLD9630TT

Base I/O Address 4Eh Base I/O Address 4Eh

BGA-421

page 24

page 13,14,15

LPC BUS

3.3V 33MHz

MS/SD/MMC

W83L518D

page 32

3.3V 24.576MHz

3.3V ATA100

ENE KB910

BIOS

page 28

LPC to X-BUS

& KBC

FIR

page 24

Legacy I/O Option

A

B

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SE CRET INFO RMATI ON. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

AC-LINK

page 27

Touch Pad

Int.KBD

page 17

page 17

D

HDD

page 16

CDROM

page 16

AC97

Codec

ALC250

page 30

AMP& Phone

Jack

page 31

Compal Electronics, Inc.

Title

Block Diagram

Size Document Number Rev

Custom

DAT20 LA-1971

Date: Sheet

242Friday, September 26, 2003

E

0.3

of

A

B

C

D

E

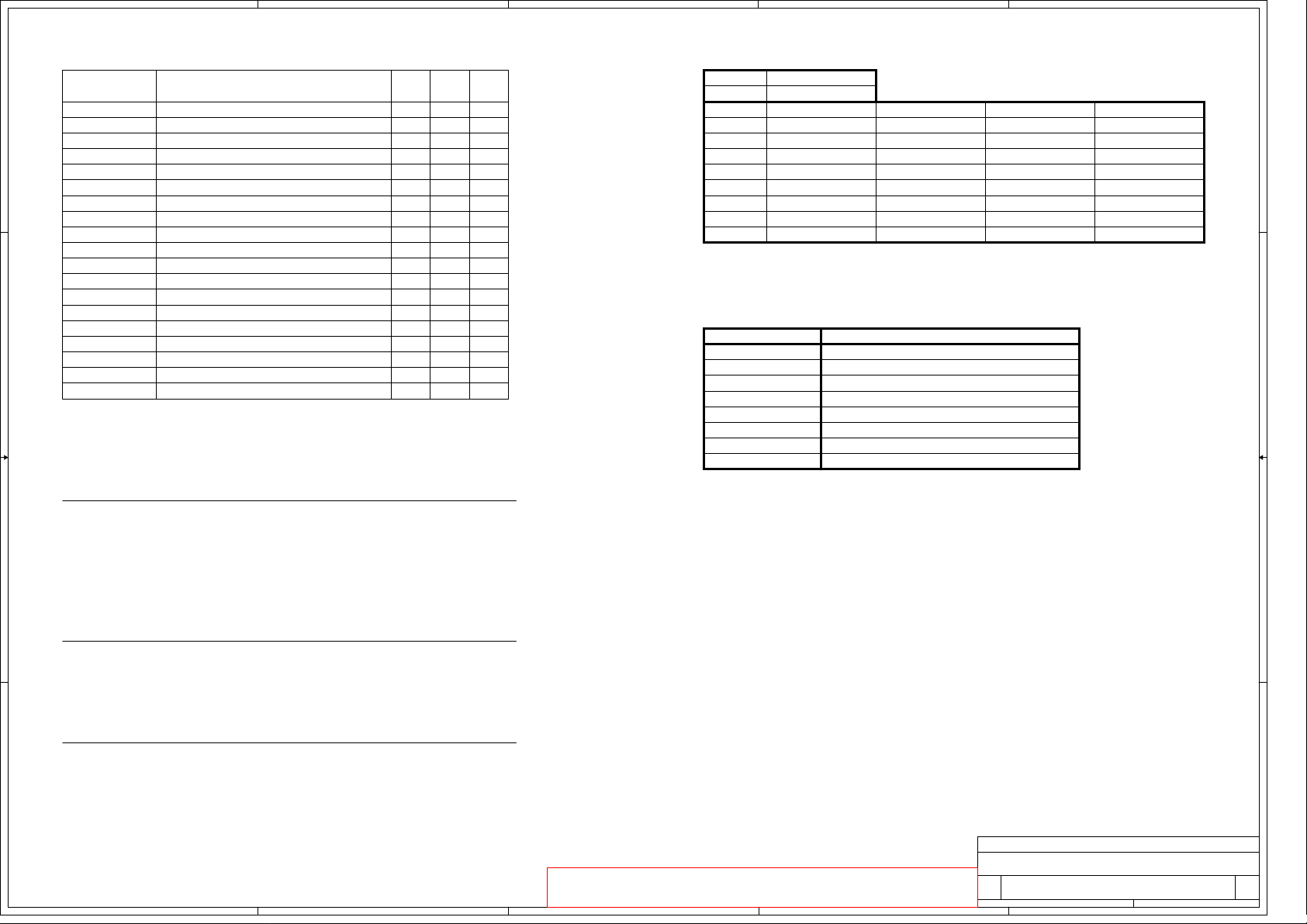

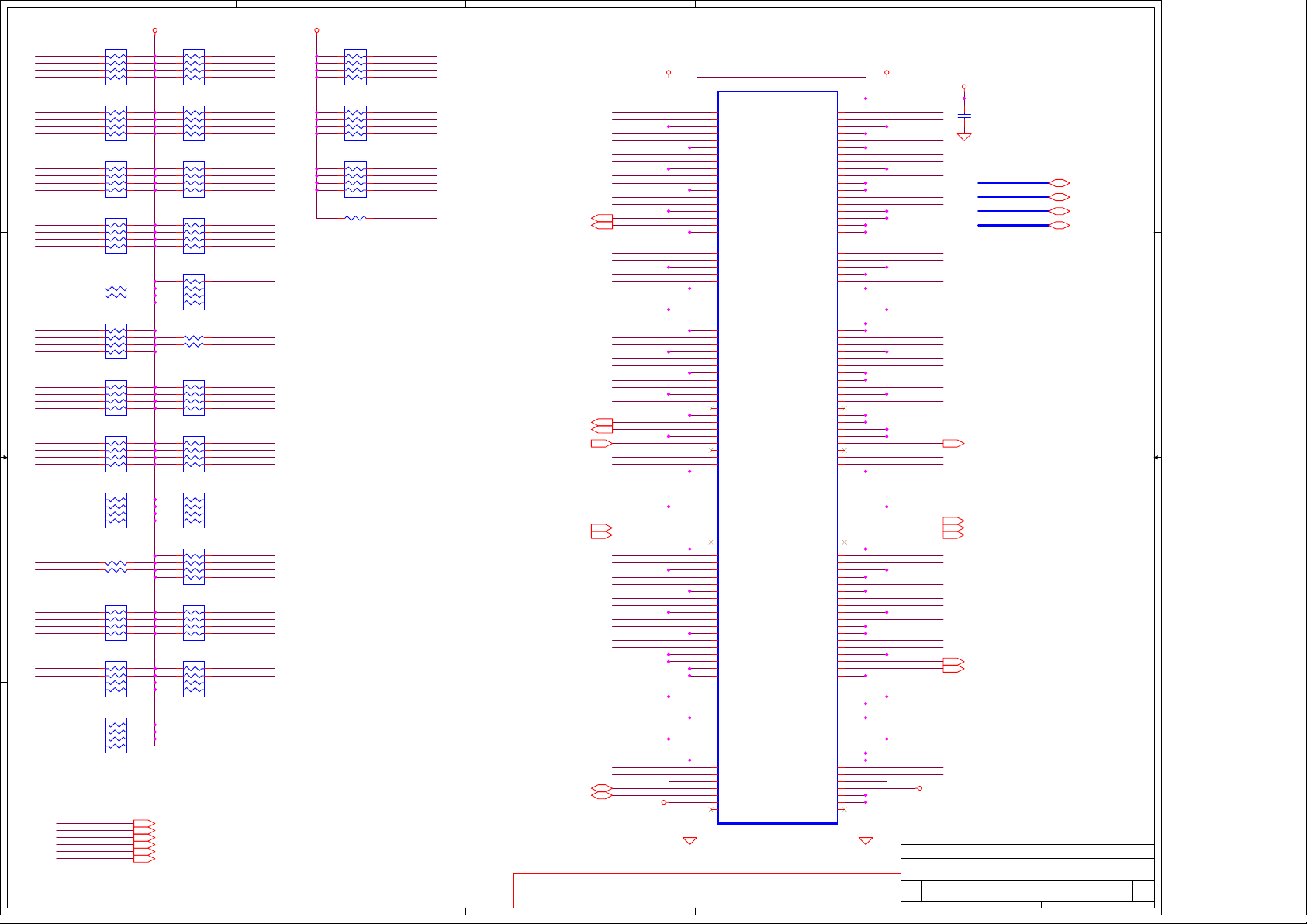

Voltage Rails

Power Plane Description

1 1

2 2

VIN

B+

+CPU_CORE

+VCCP ON OF F OFF1.05V rail for Processor I/O

+1.2VS

+1.25VS 1.25V switched power rail

+1.5VALW 1.5V power rail O N ON ON

+1.8VS

+2.5V

+2.5VS 2.5V switched power rail

+3VALW

+3V

+3VS

+5VALW

+5V

+5VS

+RTCVCC

Adapter power supply (19V)

AC or batte ry power rail for power circuit.

Core voltage for CPU

1.2VS switched power rail for MCH

AGP 4X ON OF F O F F+1.5VS

1.8V switched power rail

2.5V power rail

3.3V always on power rail

3.3V power rail

3.3V switched power rail

5V always on power rail

5V power rail

5V switched power rail

12V always on power rail

RTC power

S0-S1 S3 S5

N/A N/A N/A

ON OFF

ON OFF

ON OFF OFF

OFF

ON

ON

ON

OFF

ON

ON

ON ON*

ON

ON

OFF

ON

ON

ON

ON ON

OFF

ON

ON

ON+12VALW

ON

ON

N/AN/AN/A

OFF

OFF

OFF

OFF

OFF

OFF

OFF

ON*

OFF

OFF

ON*

ON

Board ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 NC

Board ID

*

100K +/- 5%Ra

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

0

1

2

3

Rb V min

0

AD_BID

0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

PCB Revision

0.1

0.2

0.3

0.4

Vtyp

AD_BID

V

AD_BID

0 V 0 V

0.503 V

0.819 V

0.538 V

0.875 V

1.185 V 1.264 V

2.200 V

3.300 V

2.341 V

3.300 V

max

4

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

5

6

7

External PCI Devices

Device IDSEL # REQ # / GNT # Interrupts

VGA

CardBus

LAN

3 3

Mini-PCI

1394

AD20

AD17

AD18,AD22

AD16 0

2

3PIRQF

1/4

PIRQA

PIRQA

PIRQG/PIRQH

PIRQE

EC SM Bus1 address

Device

Smart Battery

EEPROM(24C16/02)

(24C04)

Address Address

0001 011X b

1010 000X b

1011 000Xb

EC SM Bus2 address

Device

ADM1032

1001 110X b

ICH4-M SM Bus address

Device

Clock Generator (

ICS950810CG)

4 4

DDR DIMM0

DDR DIMM1

A

Address

1101 001Xb

1010 000Xb

1010 001Xb

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SE CRET INFO RMATI ON. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Notes

Size Document Number Rev

Custom

DAT20 LA-1971

Date: Sheet

342Friday, September 26, 2003

E

of

0.3

A

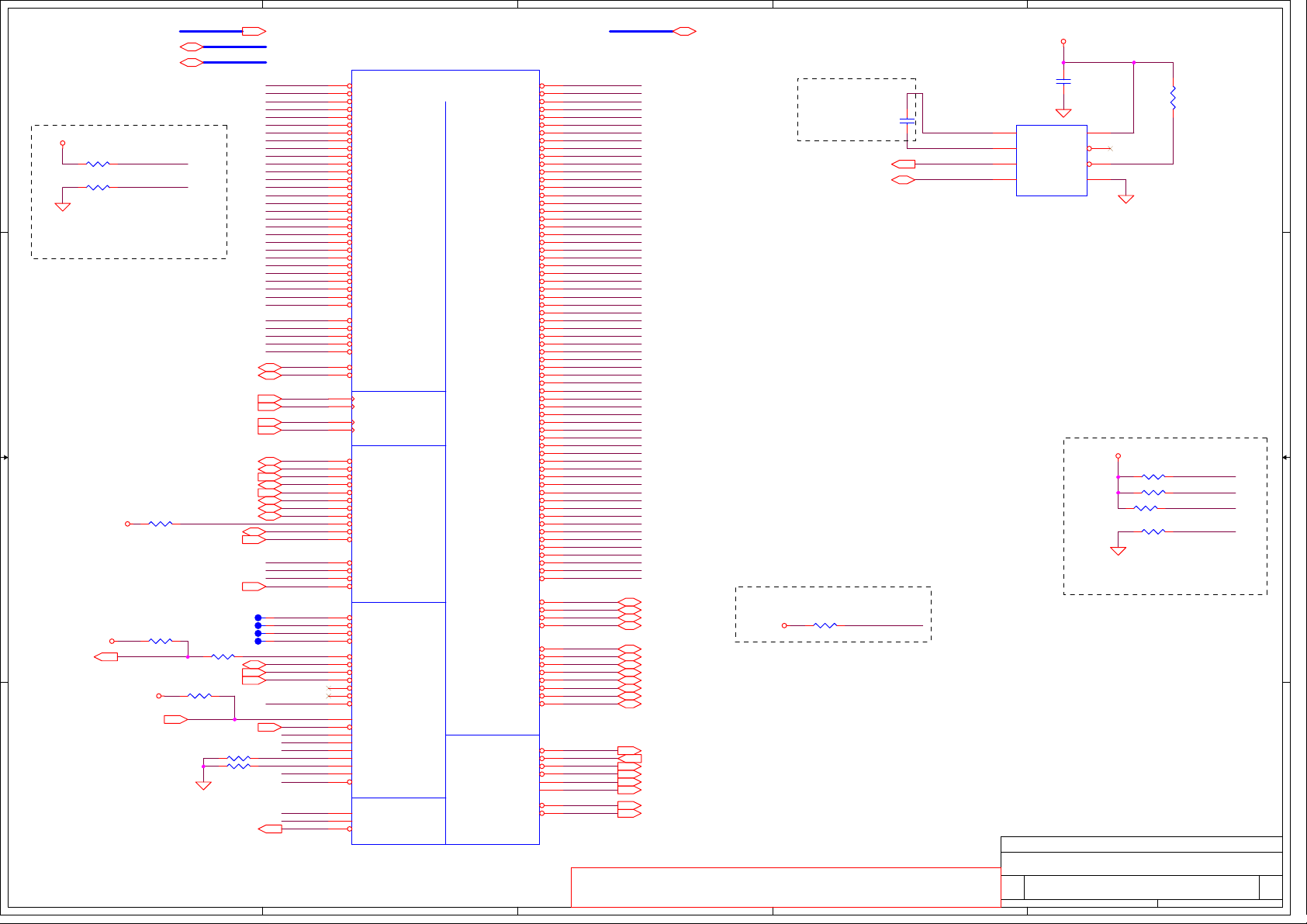

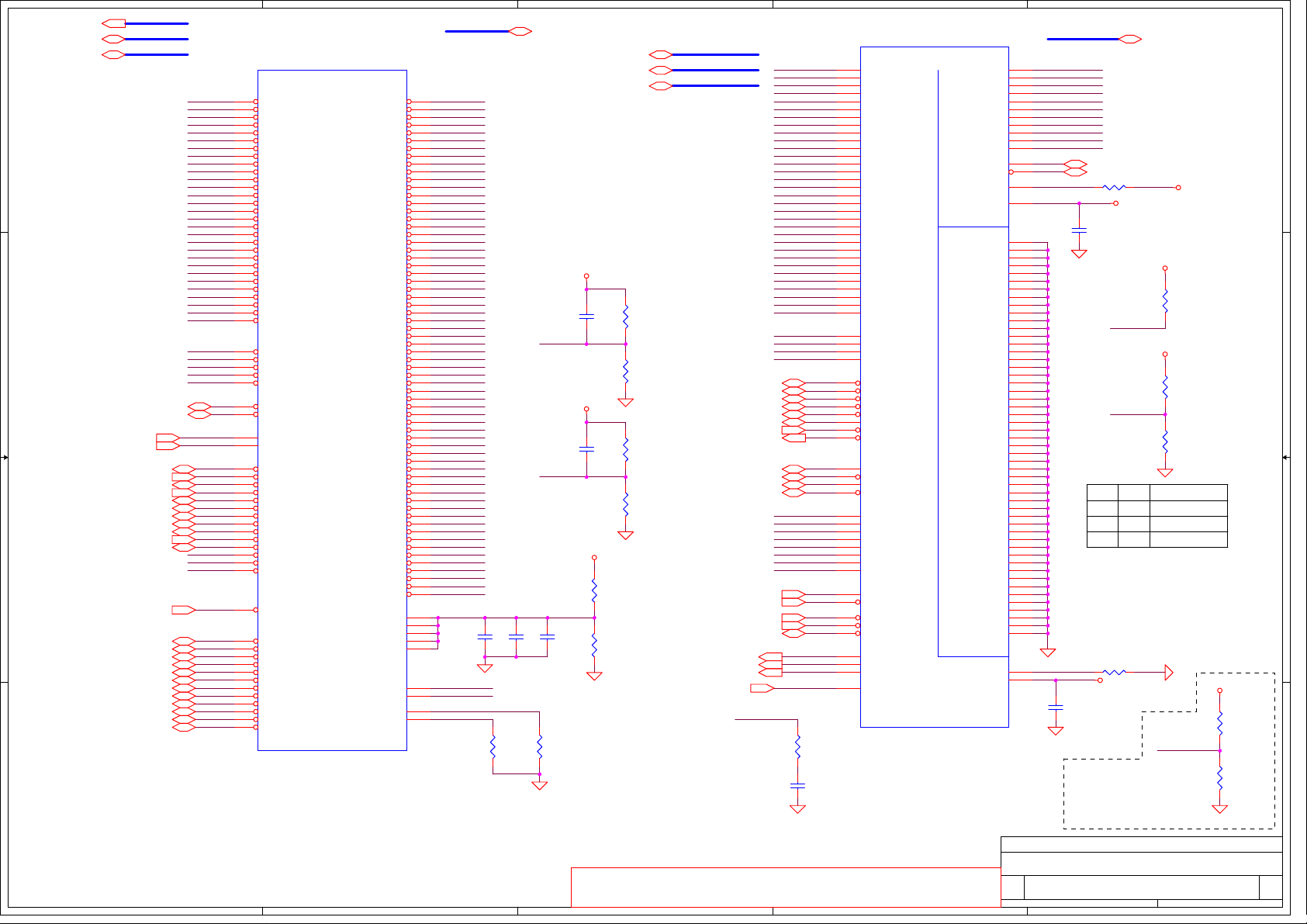

H_RS#[0..2] HD#[0..63]

CLK_CPU_ITP12

CLK_CPU_ITP#12

CLK_CPU_BCLK12

CLK_CPU_BCLK#12

H_LOCK#6

H_CPURST#6

H_TRDY#6

R223

0_0402_5%

1 2

H_DBSY#6

H_DPSLP#7,13

H_DPWR#7

1 2

R227

330_0402_5%

H_THERMTRIP#14

HA#[3..31]

H_REQ#[0..4]

H_ADSTB#06

H_ADSTB#16

H_BPRI#6

H_DEFER#6

H_CPUSLP#13

R226

@1K_0402_5%

1 2

1 2

R208

@1K_0402_5%

HA#[3..31]6

H_REQ#[0..4]6

1 1

2 2

3 3

4 4

+VCCP

ITP_TDI

R216

1 2

150_0402_5%

ITP_TRST#

R214

1 2

680_0402_5%

Note:

Placement near to CPU Conn

1 2

+VCCP

+3VALW

ITP_DBRESET#14

R228

56_0402_5%

R224

150_0402_5%

1 2

ITP_DBRESET#

+VCCP

H_PWRGD13

A

H_ADS#6

H_BNR#6

H_BR0#6

H_DRDY#6

H_HIT#6

H_HITM#6

T1 @PAD

T2 @PAD

T3 @PAD

T4 @PAD

H_RS#[0..2] 6

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

H_REQ#0

H_REQ#1

H_REQ#2 HD#32

H_REQ#3

H_REQ#4

H_IERR#

H_CPURST#

H_RS#0

H_RS#1

H_RS#2

H_PROCHOT#

ITP_TCK

ITP_TDI

ITP_TDO

TEST1

TEST2

ITP_TMS

ITP_TRST#

THERMDA

THERMDC

BPM0#

BPM1#

BPM2#

BPM3#

AA3

AA2

AF4

AC4

AC7

AC3

AD3

AE4

AD2

AB4

AC6

AD5

AE2

AD6

AF3

AE1

AF1

AE5

A16

A15

B15

B14

B11

C19

A10

B10

B17

A13

C12

A12

F23

C11

B13

B18

A18

C17

P4

U4

V3

R3

V2

W1

T4

W2

Y4

Y1

U1

Y3

R2

P3

T2

P1

T1

U3

N2

L1

J3

N4

L4

H2

K3

K4

A4

J2

H1

K1

L2

M3

C8

B8

A9

C9

A7

M2

B7

E4

A6

C5

B

JP11A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

ADDR GROUP

A25#

A26#

A27#

A28#

A29#

A30#

A31#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

ADSTB0#

ADSTB1#

ITP_CLK0

ITP_CLK1

BCLK0

HOST CLK

BCLK1

ADS#

BNR#

BPRI#

BR0#

DEFER#

DRDY#

HIT#

CONTROL GROUP

HITM#

IERR#

LOCK#

RESET#

RS0#

RS1#

RS2#

TRDY#

BPM0#

BPM1#

BPM2#

BPM3#

DBR#

DBSY#

DPSLP#

DPWR#

PRDY#

PREQ#

PROCHOT#

PWRGOOD

SLP#

TCK

TDI

TDO

TEST1

TEST2

TMS

TRST#

THERMDA

THERMDC

THERMTRIP#

AMP_1473129-1

B

Banias

MISC

THERMAL

DIODE

DATA GROUP

LEGACY CPU

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

A20M#

FERR#

IGNNE#

INIT#

LINT0

LINT1

STPCLK#

SMI#

C

HD#[0..63] 6

HD#0

A19

HD#1

A25

HD#2

A22

HD#3

B21

HD#4

A24

HD#5

B26

HD#6

A21

HD#7

B20

HD#8

C20

HD#9

B24

HD#10

D24

HD#11

E24

HD#12

C26

HD#13

B23

HD#14

E23

HD#15

C25

HD#16

H23

HD#17

G25

HD#18

L23

HD#19

M26

HD#20

H24

HD#21

F25

HD#22

G24

HD#23

J23

HD#24

M23

HD#25

J25

HD#26

L26

HD#27

N24

HD#28

M25

HD#29

H26

HD#30

N25

HD#31

K25

Y26

HD#33

AA24

HD#34

T25

HD#35

U23

HD#36

V23

HD#37

R24

HD#38

R26

HD#39

R23

HD#40

AA23

HD#41

U26

HD#42

V24

HD#43

U25

HD#44

V26

HD#45

Y23

HD#46

AA26

HD#47

Y25

HD#48

AB25

HD#49

AC23

HD#50

AB24

HD#51

AC20

HD#52

AC22

HD#53

AC25

HD#54

AD23

HD#55

AE22

HD#56

AF23

HD#57

AD24

HD#58

AF20

HD#59

AE21

HD#60

AD21

HD#61

AF25

HD#62

AF22

HD#63

AF26

D25

J26

T24

AD20

C23

K24

W25

AE24

C22

L24

W24

AE25

C2

D3

A3

B5

D1

D4

C6

B4

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

H_DINV#0 6

H_DINV#1 6

H_DINV#2 6

H_DINV#3 6

H_DSTBN#0 6

H_DSTBN#1 6

H_DSTBN#2 6

H_DSTBN#3 6

H_DSTBP#0 6

H_DSTBP#1 6

H_DSTBP#2 6

H_DSTBP#3 6

H_A20M# 13

H_FERR# 13

H_IGNNE# 13

H_INIT# 13

H_INTR 13

H_NMI 13

H_STPCLK# 13

H_SMI# 13

C

Place closed to CPU pin B17

+VCCP

Place closed to

CPU related Pin

A18 / B18

EC_SMC227

EC_SMD227

1 2

R209 56_0402_5%

D

H_PROCHOT#

D

C49

1

2200P_0402_50V7K

THERMDA

2

THERMDC

E

+3VS

1

C50

0.1U_0402_16V4Z

2

U9

2

D+

3

D-

8

SCLK

7

SDATA

ADM1032ARM_RM8

Compal Electronics, Inc.

Title

Banias Processor in mFCPGA479 (1/2)

Size Document Number Rev

Custom

DAT20 LA-1971

Date: Sheet

1

VDD1

6

ALERT#

THERM#

GND

1032_THERM#

4

5

+VCCP

R217 @54.9_0402_1%

R219 @54.9_0402_1%

1 2

R220 39.2_0603_1%

R215 27.4_0402_1%

Note:

Placement near to ITP Conn

1 2

1 2

1 2

E

12

R27

@10K_0402_5%

ITP_TDO

H_CPURST#

ITP_TMS

ITP_TCK

442Friday, September 26, 2003

of

0.3

A

JP11B

R222 @54.9_0402_1%

1 2

R225 @54.9_0402_1%

1 2

1 1

2 2

R26

3 3

4 4

1K_0402_1%

(+0.7V)

1 2

R25

2K_0402_1%

R207 27.4_0402_1%

Ra

R206 54.9_0402_1%

Rb

R232 27.4_0402_1%

Rc

R231 54.9_0402_1%

Rd

R230 @1K_0402_5%

R221 @1K_0402_5%

R212 @1K_0402_5%

R229 @1K_0402_5%

R210 @1K_0402_5%

Ra, Rb, Rc, Rd placed close to related pin within 0.5".

COMP0/1/2/3 Trace should 25mil away from any other toggling signal.

+1.8VS

+VCCP

+CPU_CORE

PSI#40

+VCCP

CPU_VID040

CPU_VID140

CPU_VID240

12

CPU_VID340

CPU_VID440

CPU_VID540

Placed closed to Pin AD26

within 0. 5".

12

12

12

12

1 2

1 2

1 2

1 2

1 2

A

VCCSENSE

VSSSENSE

GTL_REF0

COMP0

COMP1

COMP2

COMP3

AE7

AF6

F26

AC26

P23

D10

D12

D14

D16

E11

E13

E15

F10

F12

F14

F16

M22

N21

P22

R21

T22

U21

D18

D20

D22

E17

E19

E21

F18

AD26

E26

AC1

P25

P26

AB2

AB1

AF7

C14

C16

B1

N1

W4

K6

L5

L21

M6

N5

P6

R5

T6

D6

D8

E5

E7

E9

F6

F8

E1

E2

F2

F3

G3

G4

H4

G1

B2

C3

VCCSENSE

VSSSENSE

VCCA0

VCCA1

VCCA2

VCCA3

VCCQ0

VCCQ1

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

PSI#

VID0

VID1

VID2

VID3

VID4

VID5

GTLREF0

RSVD

RSVD

RSVD

COMP0

COMP1

COMP2

COMP3

RSVD

RSVD

RSVD

RSVD

TEST3

AMP_1473129-1

B

+CPU_CORE

A2

VSS

A5

VSS

A8

VSS

A11

VSS

A14

VSS

A17

VSS

A20

VSS

A23

VSS

A26

VSS

B3

VSS

B6

VSS

B9

VSS

B12

Banias

POWER, GROUNG, RESERVED SIGNALS AND NC

VSS

B16

VSS

B19

VSS

B22

VSS

B25

VSS

C1

VSS

C4

VSS

C7

VSS

C10

VSS

C13

VSS

C15

VSS

C18

VSS

C21

VSS

C24

VSS

D2

VSS

D5

VSS

D7

VSS

D9

VSS

D11

VSS

D13

VSS

D15

VSS

D17

VSS

D19

VSS

D21

VSS

D23

VSS

D26

VSS

E3

VSS

E6

VSS

E8

VSS

E10

VSS

E12

VSS

E14

VSS

E16

VSS

E18

VSS

E20

VSS

E22

VSS

E25

VSS

F1

VSS

F4

VSS

F5

VSS

F7

VSS

F9

VSS

F11

VSS

F13

VSS

F15

VSS

F17

VSS

F19

VSS

F21

VSS

F24

VSS

G2

VSS

G6

VSS

G22

VSS

G23

VSS

G26

VSS

H3

VSS

H5

VSS

H21

VSS

H25

VSS

J1

VSS

J4

VSS

J6

VSS

J22

VSS

J24

VSS

K2

VSS

K5

VSS

K21

VSS

K23

VSS

K26

VSS

L3

VSS

L6

VSS

L22

VSS

L25

VSS

M1

VSS

B

+CPU_CORE

+CPU_CORE

+CPU_CORE

+CPU_CORE

+CPU_CORE

+1.8VS

1

C48

2

0.01U_0402_16V7K

+VCCP

1

+

C382

2

150U_D2_6.3VM

C

1

+

C341

2

220U_D2_4VM_R12

1

1

C340

2

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

1

C333

2

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

1

C367

2

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

1

C354

2

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

1

C352

2

2

10U_0805_6.3V6M

10U_0805_6.3V6M

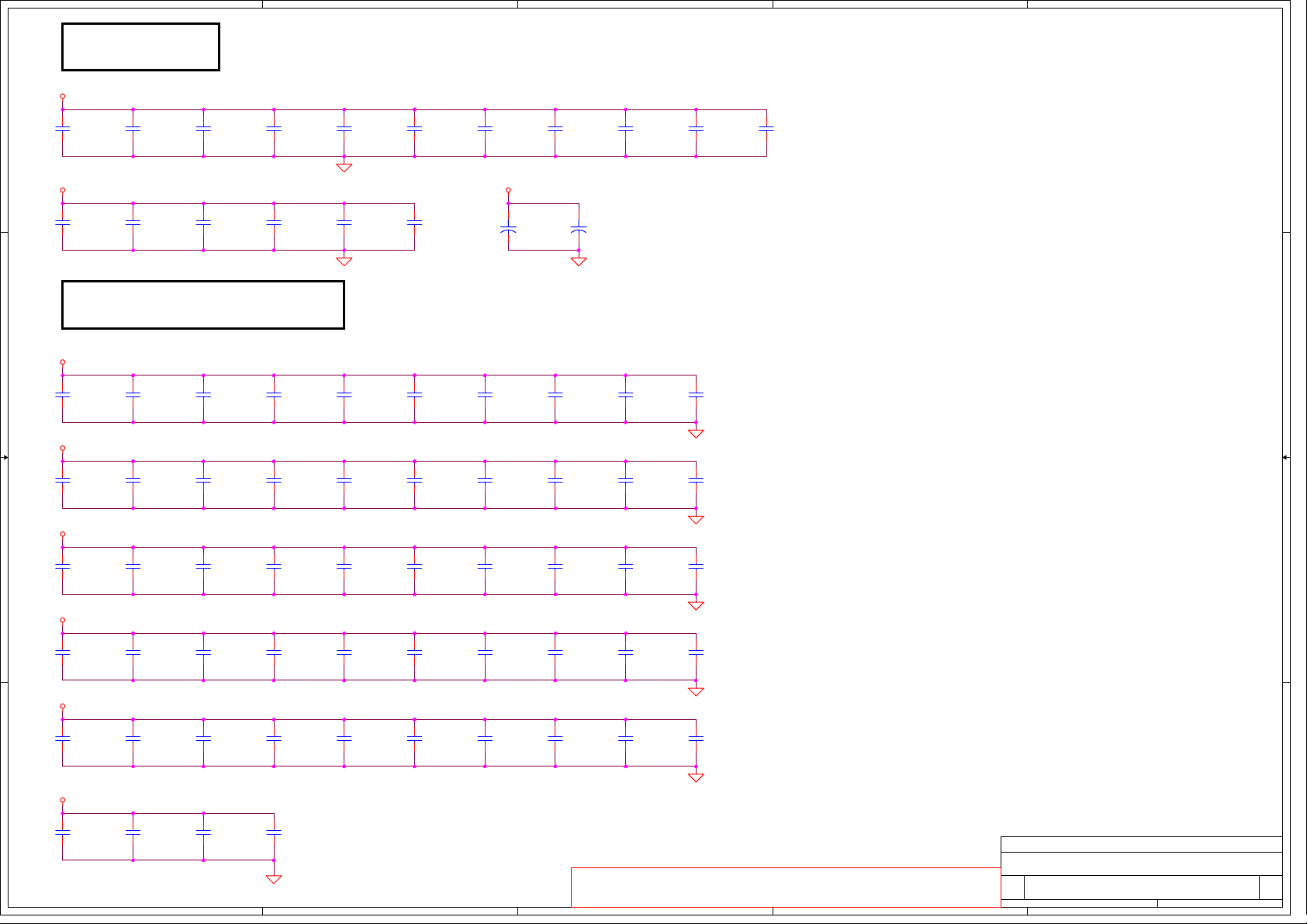

Vcc-core

Decoupling

1

1

+

C347

2

2

220U_D2_4VM_R12

220U_D2_4VM_R12

1

C338

C339

2

10U_0805_6.3V6M

1

C344

C349

2

10U_0805_6.3V6M

1

C368

C369

2

10U_0805_6.3V6M

1

C345

C350

2

10U_0805_6.3V6M

1

C358

C362

2

10U_0805_6.3V6M

SPCAP,Polymer

MLCC 0805 X5R

1

1

C324

2

0.01U_0402_16V7K

1

C375

2

0.1U_0402_16V4Z

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

C378

2

0.01U_0402_16V7K

C379

2

0.01U_0402_16V7K

1

1

C376

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

C

1

+

+

C357

2

220U_D2_4VM_R12

1

C337

2

10U_0805_6.3V6M

1

C353

2

10U_0805_6.3V6M

1

C370

2

10U_0805_6.3V6M

1

C332

2

10U_0805_6.3V6M

1

C372

2

10U_0805_6.3V6M

C363

1

1

C336

2

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

1

C359

2

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

1

C371

2

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

1

C342

2

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

1

C331

2

2

10U_0805_6.3V6M

10U_0805_6.3V6M

C335

C365

C364

C343

C374

1

C334

2

10U_0805_6.3V6M

1

C366

2

10U_0805_6.3V6M

1

C360

2

10U_0805_6.3V6M

1

C348

2

10U_0805_6.3V6M

1

C373

2

10U_0805_6.3V6M

C,uF ESR, mohm ESL,nH

4X220uF 12m ohm/4 3.5nH/4

35X10uF 5m ohm/35 0.6nH/35

1

2

10U_0805_10V4Z

1

C356

2

0.1U_0402_16V4Z

C47

C351

1

C319

2

10U_0805_10V4Z

1

C346

2

0.1U_0402_16V4Z

1

1

C380

2

2

10U_0805_10V4Z

10U_0805_10V4Z

1

C330

2

0.1U_0402_16V4Z

C381

1

C328

2

0.1U_0402_16V4Z

D

1

1

C329

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

D

C377

1

C327

2

0.1U_0402_16V4Z

E

+CPU_CORE

Title

Size Document Number Rev

Custom

Date: Sheet

JP11C

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

T26

U2

U6

U22

U24

V1

V4

V5

V21

V25

W3

W6

W22

W23

W26

Y2

Y5

Y21

Y24

AA1

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE3

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF2

AF5

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF24

G21

H22

W21

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC9

AC11

AC13

AC15

AC17

AC19

AD8

AD10

AD12

AD14

AD16

AD18

AE9

AE11

AE13

AE15

AE17

AE19

AF8

AF10

AF12

AF14

AF16

AF18

M21

M24

N22

N23

N26

R22

R25

F20

F22

K22

V22

Y22

P21

P24

T21

T23

G5

H6

J5

J21

U5

V6

W5

Y6

M4

M5

N3

N6

P2

P5

R1

R4

R6

T3

T5

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

POWER, GROUND

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AMP_1473129-1

Banias

Compal Electronics, Inc.

Banias Processor in mFCPGA479 (2/2)

DAT20 LA-1971

542Friday, September 26, 2003

E

0.3

of

A

H_RS#[0..2]4

HA#[3..31]4

H_REQ#[0..4]4

1 1

2 2

3 3

4 4

H_RS#[0..2]

HA#[3..31]

H_REQ#[0..4]

U8A

HA#3

U6

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#04

H_ADSTB#14

CLK_MCH_BCLK#12

CLK_MCH_BCLK12

H_ADS#4

H_TRDY#4

H_DRDY#4

H_DEFER#4

H_HITM#4

H_HIT#4

H_LOCK#4

H_BR0#4

H_BNR#4

H_BPRI#4

H_DBSY#4

H_CPURST#4

H_DSTBN#04

H_DSTBN#14

H_DSTBN#24

H_DSTBN#34

H_DSTBP#04

H_DSTBP#14

H_DSTBP#24

H_DSTBP#34

H_DINV#04

H_DINV#14

H_DINV#24

H_DINV#34

H_RS#0

H_RS#1

H_RS#2

HA#3

T5

HA#4

R2

HA#5

U3

HA#6

R3

HA#7

P7

HA#8

T3

HA#9

P4

HA#10

P3

HA#11

P5

HA#12

R6

HA#13

N2

HA#14

N5

HA#15

N3

HA#16

J3

HA#17

M3

HA#18

M4

HA#19

M5

HA#20

L5

HA#21

K3

HA#22

J2

HA#23

N6

HA#24

L6

HA#25

L2

HA#26

K5

HA#27

L3

HA#28

L7

HA#29

K4

HA#30

J5

HA#31

U2

HREQ#0

T7

HREQ#1

R7

HREQ#2

U5

HREQ#3

T4

HREQ#4

R5

HADSTB#0

N7

HADSTB#1

K8

BCLK#

J8

BCLK

U7

ADS#

V4

HTRDY#

W2

DRDY#

Y4

DEFER#

Y3

HITM#

Y5

HIT#

W3

HLOCK#

V7

BR0#

V3

BNR#

Y7

BPRI#

V5

DBSY#

W7

RS#0

W5

RS#1

W6

RS#2

AE17

CPURST#

AD4

HDSTBN#0

AF6

HDSTBN#1

AD11

HDSTBN#2

AC15

HDSTBN#3

AD3

HDSTBP#0

AG6

HDSTBP#1

AE11

HDSTBP#2

AC16

HDSTBP#3

AD5

DBI#0

AG5

DBI#1

AH9

DBI#2

AD15

DBI#3

RG82P4300M_FCBGA593

Odem

HOST

B

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HVREF0

HVREF1

HVREF2

HVREF3

HVREF4

HSWNG1

HSWNG0

HRCOMP1

HRCOMP0

AA2

AB5

AA5

AB3

AB4

AC5

AA3

AA6

AE3

AB7

AE5

AF3

AC6

AC3

AF4

AE2

AG4

AG2

AE7

AE8

AH2

AC7

AG3

AD7

AH7

AE6

AC8

AG8

AG7

AH3

AF8

AH5

AC11

AC12

AE9

AC10

AE10

AD9

AG9

AC9

AE12

AF10

AG11

AG10

AH11

AG12

AE13

AF12

AG13

AH13

AC14

AF14

AG14

AE14

AG15

AG16

AG17

AH15

AC17

AF16

AE15

AH17

AD17

AE16

M7

P8

AA9

AB12

AB16

AD13

AA7

AC13

AC2

HD#[0..63]

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

H_SWNG1

H_SWNG0

H_RCOMP1

H_RCOMP0

27.4_0402_1%

1

C273

2

220P_0402_50V7K

R187

1 2

HD#[0..63] 4

C268

0.01U_0402_16V7K

H_SWNG1

C274

0.01U_0402_16V7K

H_SWNG0

MGH_GTLREF

1

1

C290

C276

2

2

1U_0603_10V4Z

220P_0402_50V7K

R189

27.4_0402_1%

1 2

+VCCP

+VCCP

+VCCP

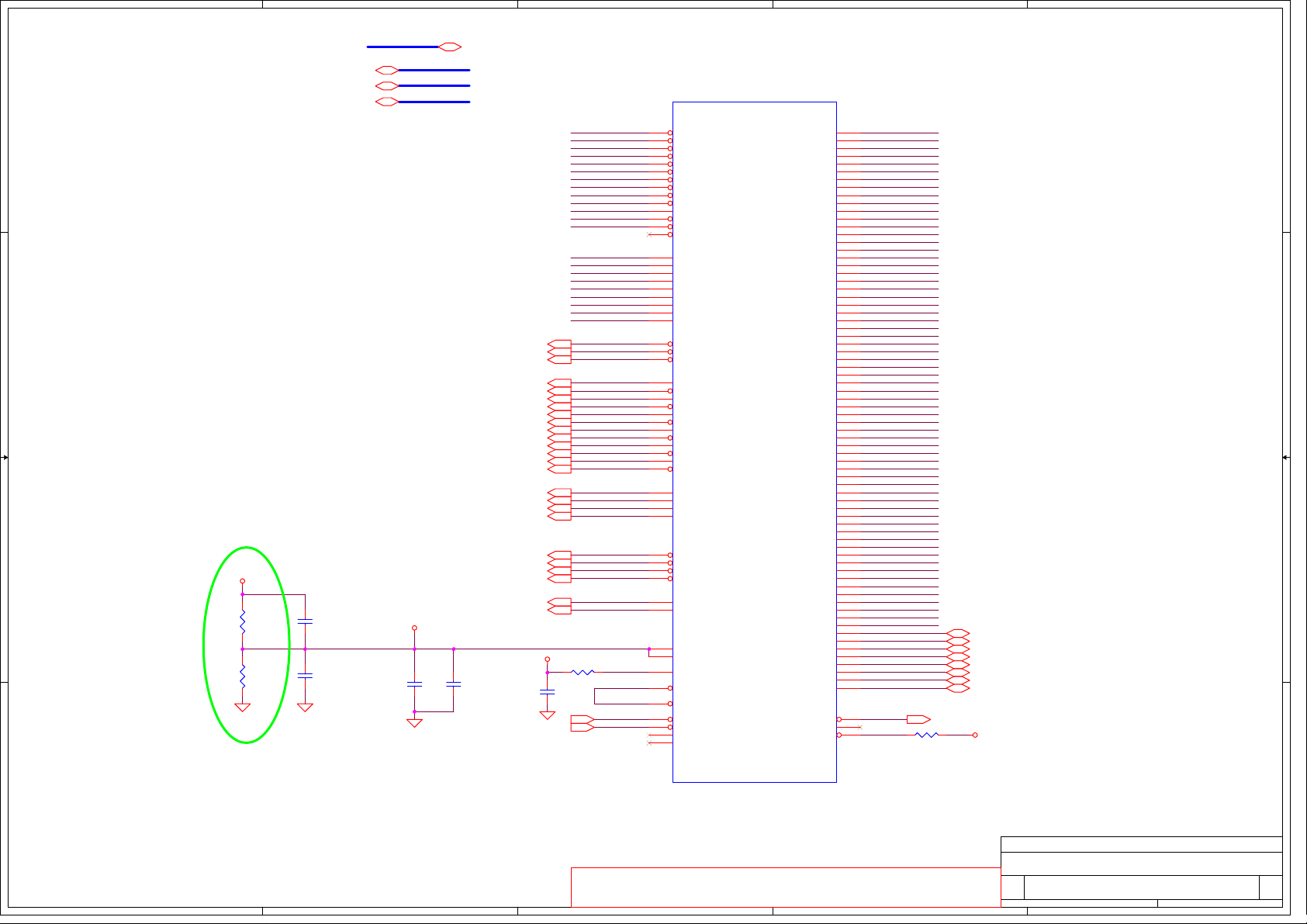

AGP_AD[0..31]17

AGP_C/BE#[0..3]17

AGP_SBA[0..7]17

1

2

1

2

12

12

12

R193

301_0402_1%

12

R192

150_0402_1%

12

R191

301_0402_1%

12

R188

150_0402_1%

R196

49.9_0402_1%

R199

100_0402_1%

C

AGP_AD[0..31]

AGP_C/BE#[0..3]

AGP_SBA[0..7]

AGP_FRAME#17

AGP_DEVSEL#17

AGP_IRDY#17

AGP_TRDY#17

AGP_STOP#17

AGP_PAR17

AGP_ADSTB017

AGP_ADSTB0#17

AGP_ADSTB117

AGP_ADSTB1#17

AGP_SBSTB17

AGP_SBSTB#17

AGP_RBF#17

AGP_WBF#17

AGP_ST017

AGP_ST117

AGP_ST217

CLK_MCH_66M12

AGP_REQ#17

AGP_GNT#17

AGP_PIPE#17

CLK_MCH_66M

D

U8B

AGP_AD0 HUB_PD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

AGP_C/BE#0

AGP_C/BE#1

AGP_C/BE#2

AGP_C/BE#3

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

CLK_MCH_66M

AGP_ST1

AGP_ST2

12

R197

@22_0402_5%

1

C294

@10P_0402_50V8K

2

R27

GAD0

R28

GAD1

T25

GAD2

R25

GAD3

T26

GAD4

T27

GAD5

U27

GAD6

U28

GAD7

V26

GAD8

V27

GAD9

T23

GAD10

U23

GAD11

T24

GAD12

U24

GAD13

U25

GAD14

V24

GAD15

Y27

GAD16

Y26

GAD17

AA28

GAD18

AB25

GAD19

AB27

GAD20

AA27

GAD21

AB26

GAD22

Y23

GAD23

AB23

GAD24

AA24

GAD25

AA25

GAD26

AB24

GAD27

AC25

GAD28

AC24

GAD29

AC22

GAD30

AD24

GAD31

V25

GCBE#0

V23

GCBE#1

Y25

GCBE#2

AA23

GCBE#3

Y24

GFRAME#

W28

GDEVSEL#

W27

GIRDY#

W24

GTRDY#

W23

GSTOP#

W25

GPAR

AG24

GREQ#

AH25

GGNT#

R24

AD_STB0

R23

AD_STB#0

AC27

AD_STB1

AC28

AD_STB#1

AH28

SBA0

AH27

SBA1

AG28

SBA2

AG27

SBA3

AE28

SBA4

AE27

SBA5

AE24

SBA6

AE25

SBA7

AF27

SB_STB

AF26

SB_STB#

AE22

RBF#

AE23

WBF#

AF22

PIPE#

AG25

ST0

AF24

ST1

AG26

ST2

P22

66IN

RG82P4300M_FCBGA593

Odem

AGP

HUB

GND

HI_0

HI_1

HI_2

HI_3

HI_4

HI_5

HI_6

HI_7

HI_8

HI_9

HI_10

HI_STB

HI_STB#

HLRCOMP

HI_REF

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

GRCOMP

AGPREF

P25

P24

N27

P23

M26

M25

L28

L27

M27

N28

M24

N25

N24

P27

P26

AB9

AD10

AF9

AJ9

A7

F8

J7

L8

N8

R8

U8

W8

AA8

AD8

AF7

AJ7

D5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

AF5

AJ5

A3

J4

L4

N4

R4

U4

W4

AA4

AC4

AE4

AJ3

E1

J1

L1

N1

R1

U1

W1

AA1

AC1

AE1

AG1

AD25

AA21

HUB_PD1

HUB_PD2

HUB_PD3

HUB_PD4

HUB_PD5

HUB_PD6AGP_AD6

HUB_PD7AGP_AD7

HUB_PD8

HUB_PD9

HUB_PD10

HUB_RCOMP

AGP_RCOMP

+AGP_VREF

E

HUB_PD[0..10]

HUB_PSTRB 13

HUB_PSTRB# 13

1 2

1

C291

0.01U_0402_16V7K

2

ST1 ST2

1 2

1

C275

0.1U_0402_16V4Z

2

36.5_0402_1%

+HUB_VREF

AGP_ST2

AGP_ST1

X

11DDR

X

0

X

R190

40.2_0402_1%

+AGP_VREF

HUB_PD[0:10] 13

R198

+1.5VS

+1.5VS

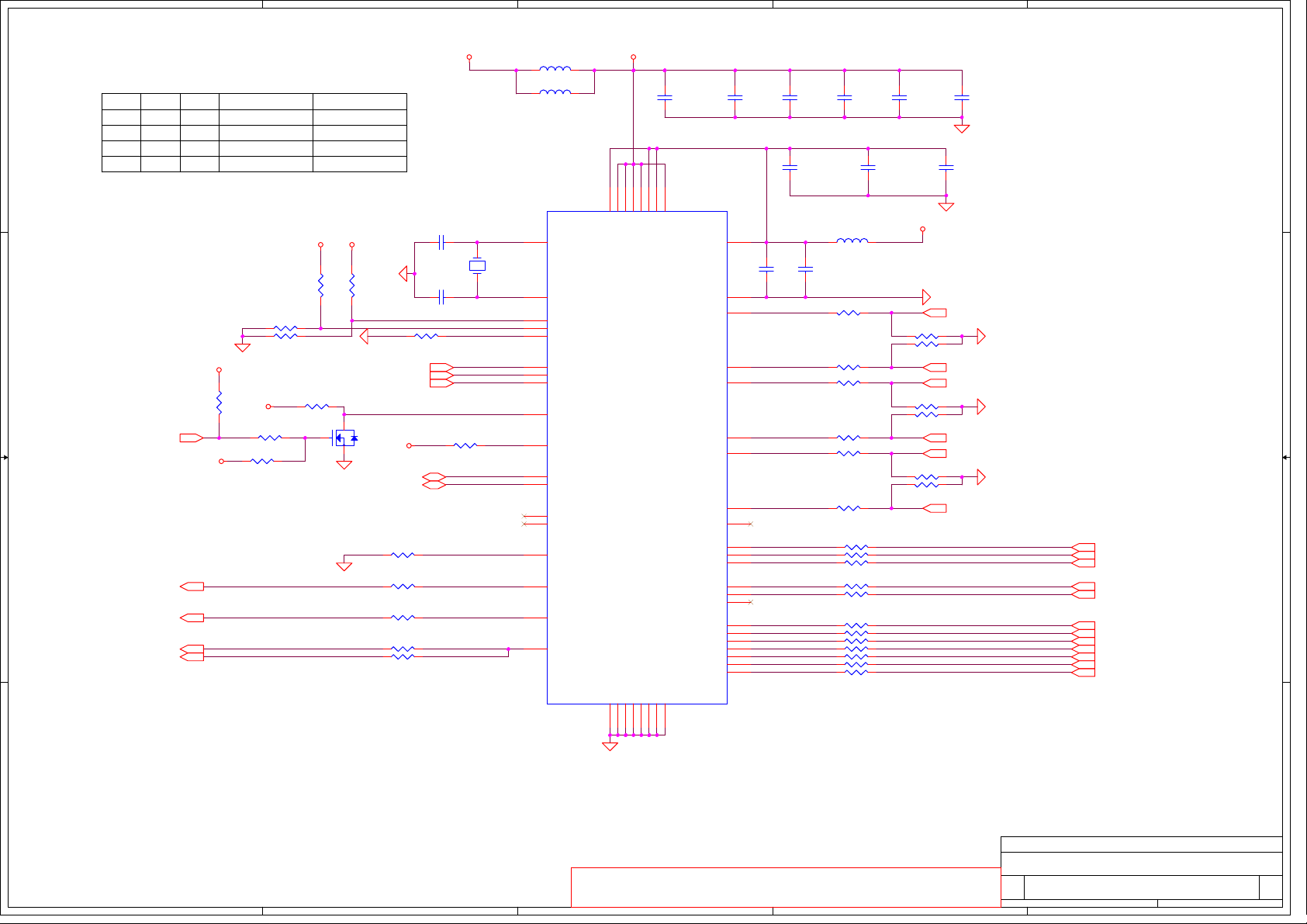

MCH STRAP

TEST MODE

400 Mhz PSB

Note:

Ra & Rb placed at

center of MCH and AGP

+1.8VS

12

R183

@1K_0402_5%

12

R184

@1K_0402_5%

12

R185

@1K_0402_5%

+AGP_VREF

+1.5VS

12

R195

1K_0402_1%

12

R194

1K_0402_1%

Ra

Rb

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Odem (1/3)

Size Document Number Rev

Custom

DAT20 LA-1971

Date: Sheet

642Friday, September 26, 2003

E

of

0.3

A

B

C

D

E

DDR_SMA[0..12]

DDR_SDQ[0..63]9

DDR_SDQS[0..8]9

DDR_CB[0..7]9

1 1

2 2

3 3

+2.5V

12

R201

75_0603_1%

12

R200

75_0603_1%

1

C308

0.1U_0402_16V4Z

2

1

C305

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

DDR_SDQ[0..63]

DDR_SDQS[0..8]

DDR_CB[0..7]

+1.25VS_SMVREF

(Closed to Pin J9)

1

C307

2

DDR_SMA[0..12] 9

DDR_SWE#9

DDR_SRAS#9

DDR_SCAS#9

DDR_CLK09

DDR_CLK0#9

DDR_CLK19

DDR_CLK1#9

DDR_CLK29

DDR_CLK2#9

DDR_CLK310

DDR_CLK3#10

DDR_CLK410

DDR_CLK4#10

DDR_CLK510

DDR_CLK5#10

DDR_CKE09,10

DDR_CKE19,10

DDR_CKE210

DDR_CKE310

DDR_SCS#09,10

DDR_SCS#19,10

DDR_SCS#210

DDR_SCS#310

DDR_SBS09

DDR_SBS19

1

C304

0.1U_0402_16V4Z

2

(Closed to Pi n J21)

+1.25VS

1

C316

2

0.1U_0402_16V4Z

H_DPSLP#4,13

H_DPWR#4

1 2

R203

30.1_0603_1%

DDR_SMA0

DDR_SMA1

DDR_SMA2

DDR_SMA3

DDR_SMA4

DDR_SMA5

DDR_SMA6

DDR_SMA7

DDR_SMA8

DDR_SMA9

DDR_SMA10

DDR_SMA11

DDR_SMA12

DDR_SDQS0

DDR_SDQS1

DDR_SDQS2

DDR_SDQS3

DDR_SDQS4

DDR_SDQS5

DDR_SDQS6

DDR_SDQS7

DDR_SDQS8

DDR_RCOMP

M_RCV#

E12

F17

E16

G17

G18

E18

F19

G20

G19

F21

F13

E20

G21

G22

F26

C26

C23

B19

D12

E15

G11

F11

K25

G24

E24

G25

K23

G23

E22

H23

F23

G12

G13

G15

G14

AD26

AD27

C8

C5

E3

G8

J25

G5

F5

J24

G6

G7

J23

E9

F7

F9

E7

J9

J21

J28

V8

Y8

U8C

SMA0

SMA1

SMA2

SMA3

SMA4

SMA5

SMA6

SMA7

SMA8

SMA9

SMA10

SMA11

SMA12

RSVD2

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDQS8

SWE#

SRAS#

SCAS#

SCK0

SCK#0

SCK1

SCK#1

SCK2

SCK#2

SCK3

SCK#3

SCK4

SCK#4

SCK5

SCK#5

SCKE0

SCKE1

SCKE2

SCKE3

SCS#0

SCS#1

SCS#2

SCS#3

SBS0

SBS1

SMVREF0

SMVREF1

SMRCOMP

RCVENIN#

RCVENOUT#

DPSLP#

DPWR#

NC0

NC1

Odem

MEMORY

SDQ0

SDQ1

SDQ2

SDQ3

SDQ4

SDQ5

SDQ6

SDQ7

SDQ8

SDQ9

SDQ10

SDQ11

SDQ12

SDQ13

SDQ14

SDQ15

SDQ16

SDQ17

SDQ18

SDQ19

SDQ20

SDQ21

SDQ22

SDQ23

SDQ24

SDQ25

SDQ26

SDQ27

SDQ28

SDQ29

SDQ30

SDQ31

SDQ32

SDQ33

SDQ34

SDQ35

SDQ36

SDQ37

SDQ38

SDQ39

SDQ40

SDQ41

SDQ42

SDQ43

SDQ44

SDQ45

SDQ46

SDQ47

SDQ48

SDQ49

SDQ50

SDQ51

SDQ52

SDQ53

SDQ54

SDQ55

SDQ56

SDQ57

SDQ58

SDQ59

SDQ60

SDQ61

SDQ62

SDQ63

SDQ64

SDQ65

SDQ66

SDQ67

SDQ68

SDQ69

SDQ70

SDQ71

RSTIN#

RSVD1

TESTIN#

G28

F27

C28

E28

H25

G27

F25

B28

E27

C27

B25

C25

B27

D27

D26

E25

D24

E23

C22

E21

C24

B23

D22

B21

C21

D20

C19

D18

C20

E19

C18

E17

E13

C12

B11

C10

B13

C13

C11

D10

E10

C9

D8

E8

E11

B9

B7

C7

C6

D6

D4

B3

E6

B5

C4

E4

C3

D3

F4

F3

B2

C2

E2

G4

C16

D16

B15

C14

B17

C17

C15

D14

J27

H27

H26

DDR_SDQ0

DDR_SDQ1

DDR_SDQ2

DDR_SDQ3

DDR_SDQ4

DDR_SDQ5

DDR_SDQ6

DDR_SDQ7

DDR_SDQ8

DDR_SDQ9

DDR_SDQ10

DDR_SDQ11

DDR_SDQ12

DDR_SDQ13

DDR_SDQ14

DDR_SDQ15

DDR_SDQ16

DDR_SDQ17

DDR_SDQ18

DDR_SDQ19

DDR_SDQ20

DDR_SDQ21

DDR_SDQ22

DDR_SDQ23

DDR_SDQ24

DDR_SDQ25

DDR_SDQ26

DDR_SDQ27

DDR_SDQ28

DDR_SDQ29

DDR_SDQ30

DDR_SDQ31

DDR_SDQ32

DDR_SDQ33

DDR_SDQ34

DDR_SDQ35

DDR_SDQ36

DDR_SDQ37

DDR_SDQ38

DDR_SDQ39

DDR_SDQ40

DDR_SDQ41

DDR_SDQ42

DDR_SDQ43

DDR_SDQ44

DDR_SDQ45

DDR_SDQ46

DDR_SDQ47

DDR_SDQ48

DDR_SDQ49

DDR_SDQ50

DDR_SDQ51

DDR_SDQ52

DDR_SDQ53

DDR_SDQ54

DDR_SDQ55

DDR_SDQ56

DDR_SDQ57

DDR_SDQ58

DDR_SDQ59

DDR_SDQ60

DDR_SDQ61

DDR_SDQ62

DDR_SDQ63

MCH_TEST#

DDR_CB0

DDR_CB1

DDR_CB2

DDR_CB3

DDR_CB4

DDR_CB5

DDR_CB6

DDR_CB7

PCIRST# 13,19, 20,21,23,24,25

1 2

R205

@4.7K_0402_5%

DDR_CB0 9

DDR_CB1 9

DDR_CB2 9

DDR_CB3 9

DDR_CB4 9

DDR_CB5 9

DDR_CB6 9

DDR_CB7 9

+1.5VS

4 4

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

RG82P4300M_FCBGA593

C

Compal Electronics, Inc.

Title

Odem (2/3)

Size Document Number Rev

Custom

DAT20 LA-1971

D

Date: Sheet

742Friday, September 26, 2003

E

0.3

of

A

U8D

+1.5VS_ODEM

1 1

+1.2VS

+1.8VS

2 2

3 3

4 4

C297

0.1U_0402_16V4Z

A

+1.8VS

1

2

+VCCP

+2.5V

1

2

R29

W29

AC29

AG29

U26

AA26

AE26

AJ25

AD23

AF23

R22

U22

W22

AA22

AB21

AD21

P17

N16

P15

R16

T15

U16

N14

P13

R14

U14

N26

N23

M22

AG23

AJ23

AE21

AG21

AJ21

AB20

AC19

AD20

AE19

AF20

AG19

AJ19

AB18

AD18

AF18

AB14

AB10

AB8

C29

G29

A25

D25

K26

D23

H24

K24

A21

F22

H22

K22

D19

H20

A17

F18

H18

D15

F16

H16

A13

F14

H14

D11

H12

F10

H10

T17

T13

C280

10U_0805_10V4Z

VCCAGP0

VCCAGP1

VCCAGP2

VCCAGP3

VCCAGP4

VCCAGP5

VCCAGP6

VCCAGP7

VCCAGP8

VCCAGP9

VCCAGP10

VCCAGP11

VCCAGP12

VCCAGP13

VCCAGP14

VCCAGP15

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

L29

VCCHL0

L25

VCCHL1

VCCHL2

VCCHL3

VCCHL4

POWER GND

VCCP0

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

M8

VCCP17

T8

VCCP18

VCCP19

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

L23

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

A9

VCCSM26

VCCSM27

VCCSM28

D7

VCCSM29

H8

VCCSM30

K7

VCCSM31

A5

VCCSM32

E5

VCCSM33

H5

VCCSM34

J6

VCCSM35

C1

VCCSM36

G1

VCCSM37

VCCGA

VCCHA

RG82P4300M_FCBGA593

B

Odem

B

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

ETS#

E29

J29

N29

U29

AA29

AE29

A27

K27

AJ27

E26

G26

J26

L26

R26

W26

AC26

AF25

A23

F24

L24

M23

AC23

AH23

D21

H21

J22

L22

N22

T22

V22

Y22

AB22

AC21

AD22

AF21

AG22

AH21

A19

F20

H19

AB19

AC20

AD19

AE20

AF19

AG20

AH19

D17

H17

N17

R17

U17

AB17

AC18

AE18

AF17

AG18

AJ17

A15

F15

H15

N15

P16

R15

T16

U15

AB15

AD16

AF15

AJ15

D13

E14

H13

N13

P14

R13

T14

U13

AB13

AD14

AF13

AJ13

A11

F12

H11

AB11

AD12

AF11

AJ11

D9

H9

G16

G10

G9

H7

G2

G3

H3

H4

1 2

12

R202

@1K_0402_5%

C

+2.5V

1

C326

2

22U_1206_16V4Z

0.1U_0402_16V4Z

1

C313

C312

2

1

C296

2

0.1U_0402_16V4Z

1

C286

2

1

C281

2

2.2U_0805_16V4Z

1

C266

2

0.1U_0402_16V4Z

22U_1206_16V4Z

1

C325

2

1

C311

2

0.1U_0402_16V4Z

1

C282

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

1

C279

2

0.22U_0603_10V7K

1

C288

2

0.1U_0402_16V4Z

1

C270

2

150U_D2_6.3VM

1

1

+

+

C322

2

0.1U_0402_16V4Z

1

C314

C315

2

0.1U_0402_16V4Z

1

C298

2

10U_0805_10V4Z

1

C37

2

150U_D2_6.3VM

150U_D2_6.3VM

1

+

C277

2

0.1U_0402_16V4Z

1

C259

2

C321

C295

C260

C265

C299

1

2

0.1U_0402_16V4Z

10U_0805_10V4Z

2

150U_D2_6.3VM

+2.5V

1

2

0.1U_0402_16V4Z

+1.8VS

1

2

10U_0805_10V4Z

+1.5VS_ODEM

1

+

2

+1.2VS

1

+

2

150U_D2_6.3VM

+VCCP

1

+

2

150U_D2_6.3VM

+2.5V

R204

10K_0402_5%

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CON SENT O F COMPAL ELECTRONICS, INC.

C

0.1U_0402_16V4Z

1

1

C300

C302

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

1

C310

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

1

C285

C278

2

2

0.1U_0402_16V4Z

0.01U_0402_16V7K

1

1

C292

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

1

C269

C261

2

2

0.1U_0402_16V4Z

D

D

1

C303

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C317

2

1

C264

2

0.1U_0402_16V4Z

1

C287

C283

2

0.22U_0603_10V7K

1

C262

2

0.1U_0402_16V4Z

1

C323

0.1U_0402_16V4Z

2

1

C318

C301

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C267

2

1

C293

0.047U_0603_16V7K

2

0.1U_0402_16V4Z

1

C263

2

E

0.1U_0402_16V4Z

1

C306

2

1

C271

0.1U_0402_16V4Z

2

1

C272

0.1U_0402_16V4Z

2

Compal Electronics, Inc.

Title

Odem (3/3)

Size Document Number Rev

Custom

Date: Sheet

1

1

C320

C309

0.1U_0402_16V4Z

2

2

0.1U_0402_16V4Z

DAT20 LA-1971

of

842Friday, September 26, 2003

E

0.3

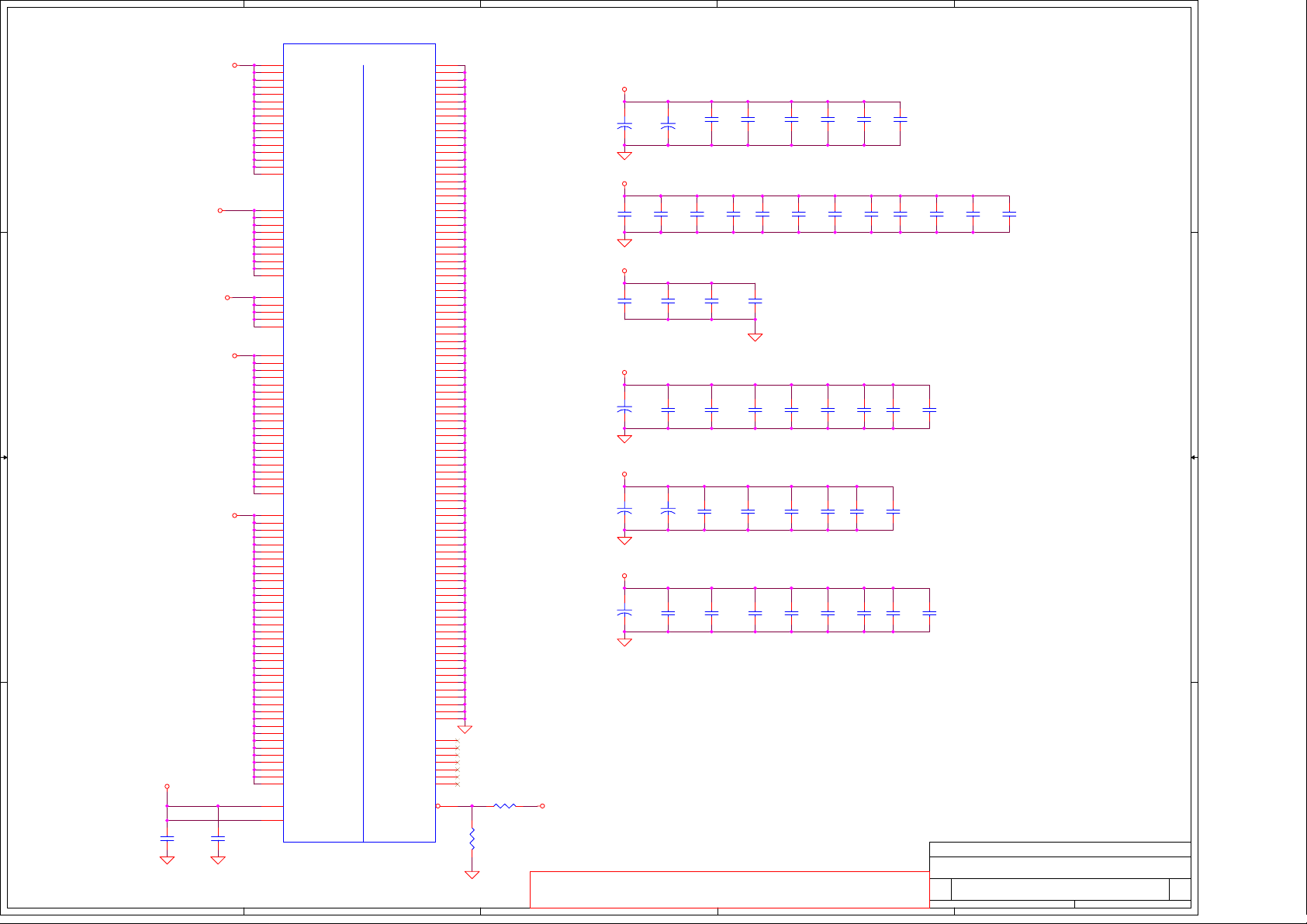

A

DDR_SDQ0

DDR_SDQ3

DDR_SDQS0

DDR_SDQ2

RP5

DDR_DQ0

18

DDR_DQ3

27

DDR_DQS0

36

DDR_DQ2

45

DDR_SDQ32

DDR_SDQ37

DDR_SDQS4

DDR_SDQ36

10_0804_8P4R_5%

RP18

RP6

DDR_DQ5

18

DDR_DQ1

27

DDR_DQ4DDR_SDQ4

36

45

18

DDR_DQ8

27

DDR_DQ13

36

45

DDR_SDQ5

DDR_SDQ1

DDR_SDQ6 DDR_DQ6

1 1

DDR_SDQ7 DDR_DQ7

DDR_SDQ8

DDR_SDQ13

DDR_SDQS1 DDR_DQS1

10_0804_8P4R_5%

DDR_SDQ33

DDR_SDQ38

DDR_SDQ34

DDR_SDQ39

DDR_SDQ35

DDR_SDQ44

DDR_SDQ40

DDR_SDQ41

10_0804_8P4R_5%

DDR_SDQ9

DDR_SDQ12

DDR_SDQ14

DDR_SDQ15

RP22

DDR_DQ9

18

DDR_DQ12

27

DDR_DQ14

36

DDR_DQ15

45

DDR_SDQ45

DDR_SDQS5

DDR_SDQ43

DDR_SDQ42 DDR_DQ42

10_0804_8P4R_5%

DDR_SDQ11

DDR_SDQ16

DDR_SDQ20

RP7

DDR_DQ11

18

DDR_DQ10DDR_SDQ10

27

DDR_DQ16

36

DDR_DQ20

45

DDR_SDQ47

DDR_SDQ46

DDR_SDQ52 DDR_DQ52

DDR_SDQ49

10_0804_8P4R_5%

DDR_SDQ17

RP19

DDR_SDQ21 DDR_DQ21

2 2

DDR_SDQ18

DDR_SDQ19

DDR_SDQ23 DDR_DQ23

DDR_SDQ24

10_0804_8P4R_5%

RP9

DDR_DQ17

18

DDR_DQS2DDR_SDQS2

27

36

DDR_DQ22DDR_SDQ22

45

DDR_DQ18

18

DDR_DQ19

27

36

DDR_DQ24

45

DDR_SDQ48

DDR_SDQS6

DDR_SDQ53

DDR_SDQ55

DDR_SDQ50

DDR_SDQ54

DDR_SDQ51

DDR_SDQ63

10_0804_8P4R_5%

DDR_SDQ25

DDR_SDQ28

DDR_SDQS3

RP17

DDR_DQ25

18

DDR_DQ28

27

DDR_DQS3

36

DDR_DQ29DDR_SDQ29

45

DDR_SDQ58

DDR_SDQS7

DDR_SDQ59

DDR_SDQ57

10_0804_8P4R_5%

DDR_SDQ26 DDR_DQ26

DDR_SDQ27 DDR_DQ27

RP10

18

27

DDR_DQ30DDR_SDQ30

36

DDR_DQ31DDR_SDQ31

45

DDR_SDQ56 DDR_SMA5

DDR_SDQ62

DDR_SDQ61

DDR_SDQ60

10_0804_8P4R_5%

DDR_CB4

DDR_CB5

DDR_CB0

DDR_CB1

3 3

DDR_CB2

DDR_CB6

DDR_CB3

DDR_CB7

RP20

18

27

36

45

10_0804_8P4R_5%

RP8

18

27

36

45

DDR_F_CB4

DDR_F_CB5

DDR_F_CB0

DDR_F_CB1

DDR_F_CB2

DDR_F_CB6

DDR_F_CB3

DDR_F_CB7

DDR_SMA3

DDR_SMA1

DDR_SMA10

DDR_SBS0

DDR_SMA12

DDR_SMA9

DDR_SMA7

DDR_SMA5

10_0804_8P4R_5%

DDR_SMA11

DDR_SMA8

DDR_SMA6

DDR_SMA4

DDR_SMA2

DDR_SMA0

DDR_SBS17

DDR_SRAS#7

DDR_SDQS8 DDR_DQS8 DDR_SCAS# DDR_F_ SCAS#

4 4

1 2

R30

10_0402_5%

DDR_SCAS#7

DDR_SWE#7

DDR_SBS1

DDR_SRAS#

DDR_SWE# DDR_F_SWE#

B

RP11

18

27

36

45

10_0804_8P4R_5%

RP16

18

27

36

45

10_0804_8P4R_5%

RP12

18

27

36

45

10_0804_8P4R_5%

RP21

18

27

36

45

10_0804_8P4R_5%

RP15

18

27

36

45

10_0804_8P4R_5%

RP23

18

27

36

45

10_0804_8P4R_5%

RP13

18

27

36

45

10_0804_8P4R_5%

RP14

18

27

36

45

10_0804_8P4R_5%

RP24

18

27

36

45

10_0804_8P4R_5%

RP26

18

27

36

45

10_0804_8P4R_5%

RP25

18

27

36

45

10_0804_8P4R_5%

RP27

18

27

36

45

10_0804_8P4R_5%

RP28

18

27

36

45

10_0804_8P4R_5%

R32

10_0402_5%

1 2

1 2

R31

10_0402_5%

DDR_DQ32

DDR_DQ37

DDR_DQS4

DDR_DQ36

DDR_DQ33

DDR_DQ38

DDR_DQ34

DDR_DQ39

DDR_DQ35

DDR_DQ44

DDR_DQ40

DDR_DQ41

DDR_DQ45

DDR_DQS5

DDR_DQ43

DDR_DQ47

DDR_DQ46

DDR_DQ49

DDR_DQ48

DDR_DQS6

DDR_DQ53

DDR_DQ55

DDR_DQ50

DDR_DQ54

DDR_DQ51

DDR_DQ63

DDR_DQ58

DDR_DQS7

DDR_DQ59

DDR_DQ57

DDR_DQ56

DDR_DQ62

DDR_DQ61

DDR_DQ60

DDR_F_SMA3

DDR_F_SMA1

DDR_F_SMA10

DDR_F_SBS0

DDR_F_SMA12

DDR_F_SMA9

DDR_F_SMA7

DDR_F_SMA5

DDR_F_SMA11

DDR_F_SMA8

DDR_F_SMA6

DDR_F_SMA4

DDR_F_SMA2

DDR_F_SMA0

DDR_F_SBS1

DDR_F_SRAS#

DDR_F_SBS0 10DDR_SBS07

DDR_F_SBS1 10

DDR_F_SRAS# 10

DDR_F_SCAS# 10

DDR_F_SWE# 10

C

D

E

+2.5V

+2.5V

JP25

1

VREF

3

DDR_DQ0

DDR_DQ3

DDR_DQS0

DDR_DQ2

DDR_DQ7

DDR_DQ8

DDR_DQ13

DDR_DQS1

DDR_DQ9

DDR_DQ12

DDR_CLK07

DDR_CLK0#7

DDR_DQ16

DDR_DQ20

DDR_DQS2

DDR_DQ19

DDR_DQ24

DDR_DQS3

DDR_DQ27

DDR_F_CB0

DDR_F_CB1

DDR_DQS8

DDR_F_CB2

DDR_F_CB3

DDR_CLK27

DDR_CLK2#7

DDR_CKE17,10

DDR_CKE1

DDR_SMA12

DDR_SMA9

DDR_SMA7

DDR_SMA3

DDR_SMA1

DDR_SMA10

DDR_SBS0

DDR_SWE#

DDR_SCS#07,10

DDR_SCS#0

DDR_DQ32

DDR_DQ37

DDR_DQS4

DDR_DQ36

DDR_DQ35

DDR_DQ44

DDR_DQS5

DDR_DQ43

DDR_DQ42

DDR_DQ52

DDR_DQ49

DDR_DQS6

DDR_DQ53

DDR_DQ55

DDR_DQ63

DDR_DQ58

DDR_DQS7

DDR_DQ59

DDR_DQ57

SMB_DATA10,12,13

SMB_CLK10,12,13

+3VS

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

197

VDD_SPD

199

VDD_ID

VREF

DQ12

DQ13

DQ14

DQ15

DQ20

DQ21

DQ22

DQ23

DQ28

DQ29

DQ30

DQ31

DU/RESET#

CKE0

DU/BA2

RAS#

CAS#

DQ36

DQ37

DQ38

DQ39

DQ44

DQ45

DQ46

DQ47

CK1#

DQ52

DQ53

DQ54

DQ55

DQ60

DQ61

DQ62

DQ63

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

VDD

DM1

VSS

VDD

VDD

VSS

VSS

VDD

DM2

VSS

VDD

DM3

VSS

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

VSS

VSS

VDD

VDD

VSS

VDD

BA1

VSS

VDD

DM4

VSS

VDD

DM5

VSS

VDD

CK1

VSS

VDD

DM6

VSS

VDD

DM7

VSS

VDD

SA0

SA1

SA2

A11

A8

A6

A4

A2

A0

S1#

DU

DU

+2.5V

+1.25VS_SDREF_R

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DDR_DQ5

DDR_DQ1

DDR_DQ4

DDR_DQ6

DDR_DQ14

DDR_DQ15

DDR_DQ11

DDR_DQ10

DDR_DQ17

DDR_DQ21

DDR_DQ22DDR_DQ18

DDR_DQ23

DDR_DQ28

DDR_DQ29DDR_DQ25

DDR_DQ30DDR_DQ26

DDR_DQ31

DDR_F_CB4

DDR_F_CB5

DDR_F_CB6

DDR_F_CB7

DDR_CKE0

DDR_SMA11

DDR_SMA8

DDR_SMA6

DDR_SMA4

DDR_SMA2

DDR_SMA0

DDR_SBS1

DDR_SRAS#

DDR_SCAS#

DDR_SCS#1

DDR_DQ33

DDR_DQ38

DDR_DQ34

DDR_DQ39

DDR_DQ40

DDR_DQ41DDR_DQ45

DDR_DQ47

DDR_DQ46

DDR_DQ48

DDR_DQ50

DDR_DQ54

DDR_DQ51

DDR_DQ56

DDR_DQ62

DDR_DQ61

DDR_DQ60

1

C56

2

0.1U_0402_16V4Z

DDR_SDQ[0..63]

DDR_DQ[0..63]

DDR_DQS[0..8]

DDR_SDQS[0..8]

DDR_CB[0..7]

DDR_F_CB[0..7]

DDR_F_SMA[0..12]

DDR_SMA[0..12]

DDR_CKE0 7,10

DDR_SCS#1 7,10

DDR_CLK1# 7

DDR_CLK1 7

12

R33

75_0603_1%

12

R34

75_0603_1%

DDR_SDQ[0..63] 7

DDR_DQ[0..63] 10

DDR_DQS[0..8] 10

DDR_SDQS[0..8] 7

DDR_CB[0..7] 7

DDR_F_CB[0..7] 10

DDR_F_SMA[0..12] 10

DDR_SMA[0..12] 7

AMP1376409_REVERSE

DIMM0

Compal Electronics, Inc.

Title

THIS SHEET OF EN GINEE RING D RAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

DDR-SODIMM SLOT0

Size Document Number Rev

Custom

DAT20 LA-1971

Date: Sheet

E

of

942Friday, Septe m ber 26, 2003

0.3

A

+1.25VS

DDR_DQ0

DDR_DQ3

DDR_DQS0

DDR_DQ2

RP30

18

27

36

45

56_0804_8P4R_5%

DDR_DQ6

1 1

DDR_DQ4

DDR_DQ1

DDR_DQ5

RP45

18

27

36

45

56_0804_8P4R_5%

DDR_DQ7

DDR_DQ8

DDR_DQS1

DDR_DQ13

RP31

18

27

36

45

56_0804_8P4R_5%

DDR_DQ10

DDR_DQ11

DDR_DQ15

DDR_DQ14

RP46

18

27

36

45

56_0804_8P4R_5%

R66

56_0402_5%

DDR_DQ9

DDR_DQ12

DDR_DQ16

DDR_DQ20

2 2

DDR_DQS2

DDR_DQ18

R65

56_0402_5%

RP32

12

12

18

27

36

45

56_0804_8P4R_5%

DDR_DQ23

DDR_DQ22

DDR_DQ21

DDR_DQ17

RP47

18

27

36

45

56_0804_8P4R_5%

DDR_DQ19

DDR_DQ24

DDR_DQ25

DDR_DQS3

RP33

18

27

36

45

56_0804_8P4R_5%

DDR_DQ31

DDR_DQ30

DDR_DQ29

DDR_DQ28

RP48

18

27

36

45

56_0804_8P4R_5%

R67

56_0402_5%

DDR_DQ26

3 3

DDR_DQ27

DDR_F_CB4

DDR_F_CB5

DDR_F_CB0

DDR_F_CB1

R68

56_0402_5%

RP34

12

12

18

27

36

45

56_0804_8P4R_5%

DDR_F_CB2

DDR_F_CB3 DDR_SCS#0

DDR_F_CB6

DDR_F_CB7

RP35

18

27

36

45

56_0804_8P4R_5%

DDR_CKE2

DDR_CKE3

DDR_CKE0

DDR_CKE1

RP36

18

27

36

45

RP37

1 8

2 7

3 6

4 5

56_0804_8P4R_5%

RP49

1 8

2 7

3 6

4 5

56_0804_8P4R_5%

RP38

1 8

2 7

3 6

4 5

56_0804_8P4R_5%

RP50

1 8

2 7

3 6

4 5

56_0804_8P4R_5%

RP39

1 8

2 7

3 6

4 5

56_0804_8P4R_5%

R86

56_0402_5%

1 2

1 2

R85

56_0402_5%

RP51

1 8

2 7

3 6

4 5

56_0804_8P4R_5%

RP41

1 8

2 7

3 6

4 5

56_0804_8P4R_5%

RP52

1 8

2 7

3 6

4 5

56_0804_8P4R_5%

RP42

1 8

2 7

3 6

4 5

56_0804_8P4R_5%

RP53

1 8

2 7

3 6

4 5

56_0804_8P4R_5%

RP40

1 8

2 7

3 6

4 5

56_0804_8P4R_5%

DDR_F_SMA12

DDR_F_SMA9

DDR_F_SMA7

DDR_F_SMA5

DDR_F_SMA4

DDR_F_SMA6

DDR_F_SMA8

DDR_F_SMA11

DDR_F_SMA3

DDR_F_SMA1

DDR_F_SMA10

DDR_F_SBS0

DDR_F_SRAS#

DDR_F_SBS1

DDR_F_SMA0

DDR_F_SMA2

DDR_F_SWE#

DDR_SCS#2

DDR_DQ32

DDR_DQ37

DDR_SCS#3

DDR_F_SCAS#

DDR_DQ39

DDR_DQ34

DDR_DQ38

DDR_DQ33

DDR_DQ35

DDR_DQ44

DDR_DQ45

DDR_DQS5

DDR_DQ46

DDR_DQ47

DDR_DQ41

DDR_DQ40

DDR_DQ43

DDR_DQ42

DDR_DQ52

DDR_DQ49

DDR_DQ51

DDR_DQ54

DDR_DQ50

DDR_DQ48

DDR_SCS#1

DDR_DQ36

DDR_DQS4

56_0804_8P4R_5%

4 4

DDR_F_SBS0

DDR_F_SBS1

DDR_SCS#0

DDR_SCS#1

DDR_CKE0

DDR_CKE1

A

DDR_F_SBS0 9

DDR_F_SBS1 9

DDR_SCS#0 7,9

DDR_SCS#1 7,9

DDR_CKE0 7,9

DDR_CKE1 7,9

+1.25VS

B

RP43

1 8

2 7

3 6

4 5

56_0804_8P4R_5%

RP54

1 8

2 7

3 6

4 5

56_0804_8P4R_5%

RP44

1 8

2 7

3 6

4 5

56_0804_8P4R_5%

1 2

R64

56_0402_5%

B

DDR_DQS6

DDR_DQ53

DDR_DQ55

DDR_DQ63

DDR_DQ60

DDR_DQ61

DDR_DQ62

DDR_DQ56

DDR_DQ58

DDR_DQS7

DDR_DQ59

DDR_DQ57

DDR_DQS8

C

D

+2.5V +2.5V

JP26

1

VREF

3

DDR_DQ0

DDR_DQ3

DDR_DQS0

DDR_DQ2

DDR_DQ7

DDR_DQ8

DDR_DQ13

DDR_DQS1

DDR_DQ9

DDR_DQ12

DDR_CLK37

DDR_CLK3#7

DDR_DQ16

DDR_DQ20

DDR_DQS2

DDR_DQ18

DDR_DQ19

DDR_DQ24

DDR_DQ25

DDR_DQS3

DDR_DQ26

DDR_DQ27

DDR_F_CB0

DDR_F_CB1

DDR_DQS8

DDR_F_CB2

DDR_F_CB3

DDR_CLK57

DDR_CLK5#7

DDR_F_SWE#9

SMB_DATA9,12,13

SMB_CLK9,12,13

DDR_CKE3 DDR_CKE2

DDR_F_SMA12

DDR_F_SMA9

DDR_F_SMA7

DDR_F_SMA5

DDR_F_SMA3

DDR_F_SMA1

DDR_F_SMA10

DDR_F_SBS0

DDR_F_SWE#

DDR_SCS#2 DDR_SCS#3

DDR_DQ32

DDR_DQ37

DDR_DQS4

DDR_DQ36

DDR_DQ35

DDR_DQ44

DDR_DQ45

DDR_DQS5

DDR_DQ43

DDR_DQ42

DDR_DQ52

DDR_DQ49

DDR_DQS6

DDR_DQ53

DDR_DQ55

DDR_DQ63

DDR_DQ58

DDR_DQS7

DDR_DQ59

DDR_DQ57

+3VS

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

197

VDD_SPD

199

VDD_ID

VREF

DQ12

DQ13

DQ14

DQ15

DQ20

DQ21

DQ22

DQ23

DQ28

DQ29

DQ30

DQ31

DU/RESET#

CKE0

DU/BA2

RAS#

CAS#

DQ36

DQ37

DQ38

DQ39

DQ44

DQ45

DQ46

DQ47

CK1#

DQ52

DQ53

DQ54

DQ55

DQ60

DQ61

DQ62

DQ63

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

VDD

DM1

VSS

VDD

VDD

VSS

VSS

VDD

DM2

VSS

VDD

DM3

VSS

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

VSS

VSS

VDD

VDD

VSS

VDD

BA1

VSS

VDD

DM4

VSS

VDD

DM5

VSS

VDD

CK1

VSS

VDD

DM6

VSS

VDD

DM7

VSS

VDD

SA0

SA1

SA2

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

A11

102

A8

104

106

A6

108

A4

110

A2

112

A0

114

116

118

120

122

S1#

124

DU

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DU

AMP1376408_STANDARD

DIMM1

THIS SHEET OF EN GINEE RING D RAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

E

+1.25VS_SDREF_R

DDR_DQ5

DDR_DQ1

DDR_DQ4

DDR_DQ6

DDR_DQ14

DDR_DQ15

DDR_DQ11

DDR_DQ10

DDR_DQ17

DDR_DQ21

1

C69

2

0.1U_0402_16V4Z

DDR_F_SMA[0..12]

DDR_DQ[0..63]

DDR_DQS[0..8]

DDR_F_CB[0..7]