Page 1

DSTni-EX User Guide

Section Five

Part Number 900-335

Revision A 3/04

Page 2

Page 3

Copyright & Trademark

© 2003 Lantronix, Inc. All rights reserved.

Lantronix and the Lantronix logo, and combinations thereof are registered trademarks of

Lantronix, Inc. DSTni is a registered trademark of Lantronix, Inc. Ethernet is a registered

trademark of Xerox Corporation. All other product names, company names, logos or other

designations mentioned herein are trademarks of their respective owners.

Am186 is a trademark of Advanced Micro Devices, Inc.

Ethernet is a registered trademark of Xerox Corporation.

SPI is a trademark of Motorola, Inc.

No part of this guide may be reproduced or transmitted in any form for any purpose other than

the purchaser's personal use, without the express written permission of Lantronix, Inc.

Lantronix

15353 Barranca Parkway

Irvine, CA 92618, USA

Phone: 949-453-3990

Fax: 949-453-3995

Technical Support

Phone: 630-245-1445

Fax: 630-245-1717

Master Distributor

Grid Connect

1841 Centre Point Circle, Suite 143

Naperville, IL 60563

Phone: 630-245-1445

www.gridconnect.com

Am186 is a trademark of Advanced Micro Devices, Inc.

Ethernet is a registered trademark of Xerox Corporation.

SPI is a trademark of Motorola, Inc.

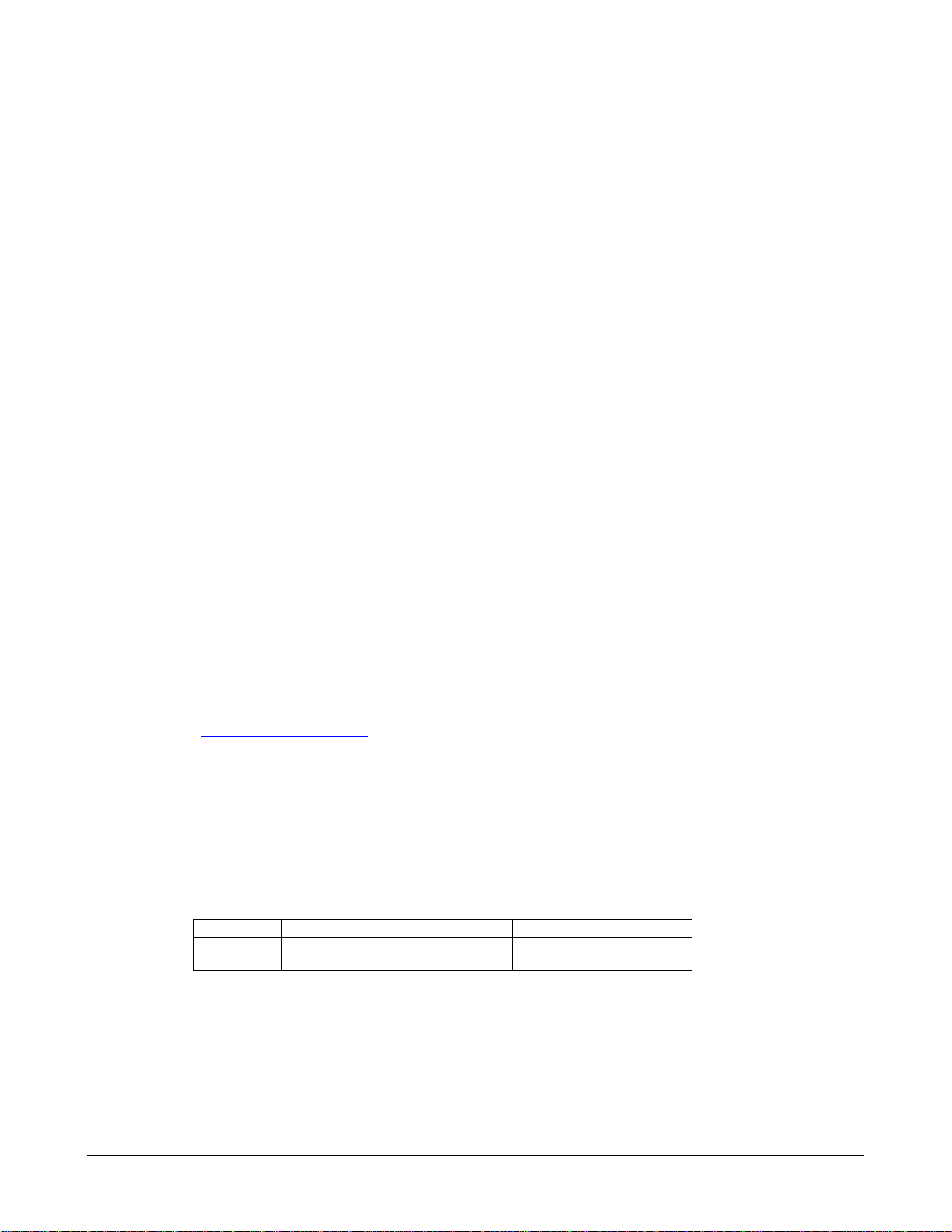

REV Changes Released Date

A Reformat. Add changes from Design

Spec. 1.1

3-24-04

i

Page 4

Warranty

Lantronix warrants each Lantronix product to be free from defects in material and workmanship

for a period specified on the product warranty registration card after the date of shipment.

During this period, if a customer is unable to resolve a product problem with Lantronix Technical

Support, a Return Material Authorization (RMA) will be issued. Following receipt of an RMA

number, the customer shall return the product to Lantronix, freight prepaid. Upon verification of

warranty, Lantronix will -- at its option -- repair or replace the product and return it to the

customer freight prepaid. If the product is not under warranty, the customer may have Lantronix

repair the unit on a fee basis or return it. No services are handled at the customer's site under

this warranty. This warranty is voided if the customer uses the product in an unauthorized or

improper way, or in an environment for which it was not designed.

Lantronix warrants the media containing its software product to be free from defects and

warrants that the software will operate substantially according to Lantronix specifications for a

period of 60 DAYS after the date of shipment. The customer will ship defective media to

Lantronix. Lantronix will ship the replacement media to the customer.

* * * *

In no event will Lantronix be responsible to the user in contract, in tort (including negligence),

strict liability or otherwise for any special, indirect, incidental or consequential damage or loss of

equipment, plant or power system, cost of capital, loss of profits or revenues, cost of

replacement power, additional expenses in the use of existing software, hardware, equipment or

facilities, or claims against the user by its employees or customers resulting from the use of the

information, recommendations, descriptions and safety notations supplied by Lantronix.

Lantronix liability is limited (at its election) to:

refund of buyer's purchase price for such affected products (without interest)

repair or replacement of such products, provided that the buyer follows the above procedures.

There are no understandings, agreements, representations or warranties, express or implied,

including warranties of merchantability or fitness for a particular purpose, other than those

specifically set out above or by any existing contract between the parties. Any such contract

states the entire obligation of Lantronix. The contents of this document shall not become part of

or modify any prior or existing agreement, commitment or relationship.

For details on the Lantronix warranty replacement policy, go to our web site at

http://www.lantronix.com/support/warranty/index.html

ii

Page 5

Contents

Copyright & Trademark ________________________________________________________i

Warranty___________________________________________________________________ ii

Contents___________________________________________________________________ iii

List of Tables _______________________________________________________________iv

List of Figures_______________________________________________________________ vi

1: About This User Guide_________________________________________ 1

Intended Audience ___________________________________________________________ 2

Conventions ________________________________________________________________ 2

Navigating Online____________________________________________________________ 2

Organization________________________________________________________________ 3

2: SPI Controller ________________________________________________ 4

Theory of Operation __________________________________________________________ 4

SPI Background___________________________________________________________ 4

DSTni SPI Controller _______________________________________________________ 4

SPI Controller Register Summary _______________________________________________ 5

SPI Controller Register Definitions ______________________________________________ 6

SPI_DATA Register ________________________________________________________ 6

CTL Register _____________________________________________________________ 7

SPI_STAT Register ________________________________________________________ 8

SPI_SSEL Register ________________________________________________________ 9

DVD_CNTR_LO Register __________________________________________________ 10

DVD_CNTR_HI __________________________________________________________ 10

3: I2C Controller________________________________________________ 11

Features __________________________________________________________________ 11

Block Diagram _____________________________________________________________ 12

Theory of Operation _________________________________________________________ 12

2

I

C Background __________________________________________________________ 12

2

I

C Controller ____________________________________________________________ 13

Operating Modes _________________________________________________________ 13

Bus Clock Considerations __________________________________________________ 21

Programmer’s Reference _____________________________________________________ 22

2

I

C Controller Register Summary_______________________________________________ 22

2

I

C Controller Register Definitions ______________________________________________ 23

Slave Address Register ____________________________________________________ 23

Data Register____________________________________________________________ 24

Control Register__________________________________________________________ 25

Status Register __________________________________________________________ 26

Clock Control Register_____________________________________________________ 28

Extended Slave Address Register ____________________________________________ 29

Software Reset Register ___________________________________________________ 29

4: USB Controller ______________________________________________ 30

Features __________________________________________________________________ 30

Theory of Operation _________________________________________________________ 31

USB Background _________________________________________________________ 31

USB Interrupt ____________________________________________________________ 31

USB Core_______________________________________________________________ 31

USB Hardware/Software Interface ___________________________________________ 32

USB Transaction _________________________________________________________ 37

USB Register Summary ______________________________________________________ 38

USB Register Definitions _____________________________________________________ 39

Interrupt Status Register ___________________________________________________ 39

Error Register ___________________________________________________________ 41

Status Register __________________________________________________________ 43

Address Register _________________________________________________________ 45

Frame Number Registers __________________________________________________ 46

Token Register __________________________________________________________ 47

Endpoint Control Registers _________________________________________________ 49

iii

Page 6

Host Mode Operation________________________________________________________ 50

Sample Host Mode Operations ________________________________________________ 51

USB Pull-up/Pull-down Resistors_______________________________________________ 53

USB Interface Signals _______________________________________________________ 54

5: CAN Controllers _____________________________________________ 55

CANBUS Background _______________________________________________________ 56

Data Exchanges and Communication _________________________________________ 56

Arbitration and Error Checking ______________________________________________ 56

CANBUS Speed and Length ________________________________________________ 57

Features __________________________________________________________________ 57

Theory of Operation _________________________________________________________ 58

CAN Register Summaries ____________________________________________________ 58

Register Summary ________________________________________________________ 58

Detailed CAN Register Map_________________________________________________ 60

CAN Register Definitions _____________________________________________________ 63

TX Message Registers ____________________________________________________ 63

Tx Message Registers _____________________________________________________ 64

RX Message Registers ____________________________________________________ 66

Rx Message Registers_____________________________________________________ 67

Error Count and Status Registers ____________________________________________ 70

Interrupt Flags ___________________________________________________________ 72

Interrupt Enable Registers __________________________________________________ 73

CAN Operating Mode _____________________________________________________ 74

CAN Configuration Registers _______________________________________________ 75

Acceptance Filter and Acceptance Code Mask__________________________________ 78

CANbus Analysis _________________________________________________________ 81

CAN Bus Interface __________________________________________________________ 84

Interface Connections _____________________________________________________ 84

List of Tables

Table 2-1. SPI Controller Register Summary .............................................................................. 5

Table 2-2. SPI_DATA Register ...................................................................................................6

Table 2-3. SPI_DATA Register Definitions.................................................................................. 6

Table 2-4. CTL Register.............................................................................................................. 7

Table 2-5. CTL Register Definitions ............................................................................................ 7

Table 2-6. SPI_STAT Register....................................................................................................8

Table 2-7. SPI_STAT Register Definitions .................................................................................. 8

Table 2-8. SPI_SSEL Register....................................................................................................9

Table 2-9. SPI_SSEL Register Definitions .................................................................................. 9

Table 2-10. BCNT Bit Settings ....................................................................................................9

Table 2-11. DVD_CNTR_LO Register ...................................................................................... 10

Table 2-12. DVD_CNTR_LO Register Definitions..................................................................... 10

Table 2-13. DVD_CNTR_HI Register........................................................................................ 10

Table 2-14. DVD_CNTR_HI Register Definitions ...................................................................... 10

Table 3-1. Master Transmit Status Codes................................................................................. 14

Table 3-2. Codes After Servicing Interrupts (Master Transmit) ................................................. 15

Table 3-3. Status Codes After Each Data Byte Transmits ........................................................16

Table 3-4. Master Receive Status Codes.................................................................................. 17

Table 3-5. Codes After Servicing Interrupt (Master Receive) .................................................... 18

Table 3-6. Codes After Receiving Each Data Byte.................................................................... 19

Table 3-7. I

Table 3-8. Slave Address Register............................................................................................ 23

Table 3-9. Address Register Definitions.................................................................................... 23

Table 3-10. Data Register .........................................................................................................24

Table 3-11. Data Register Definitions ....................................................................................... 24

Table 3-12. Control Register ..................................................................................................... 25

Table 3-13. Control Register Definitions ................................................................................... 25

Table 3-14. Status Register ...................................................................................................... 26

Table 3-15. Status Register Definitions..................................................................................... 27

Table 3-16. Status Codes ......................................................................................................... 27

2

C Controller Register Summary ............................................................................. 22

iv

Page 7

Table 3-17. Clock Control Register ........................................................................................... 28

Table 3-18. Clock Control Register Definitions.......................................................................... 28

Table 3-19. Extended Slave Address Register ......................................................................... 29

Table 3-20. Extended Slave Address Register Definitions........................................................ 29

Table 3-21. Software Reset Register ........................................................................................ 29

Table 3-22. Software Reset Register Definitions....................................................................... 29

Table 4-1. USB Data Direction.................................................................................................. 34

Table 4-2. 16-Bit USB Address ................................................................................................. 34

Table 4-3. 16-Bit USB Address Definitions ............................................................................... 34

Table 4-4. BDT Data Used by USB Controller and Microprocessor .......................................... 35

Table 4-5. USB Buffer Descriptor Format ................................................................................. 35

Table 4-6. USB Buffer Descriptor Format Definitions................................................................ 36

Table 4-7. USB Register Summary ........................................................................................... 38

Table 4-8. Interrupt Status Register .......................................................................................... 39

Table 4-9. 16- Interrupt Status Register Definitions ..................................................................39

Table 4-10. Error Interrupt Status Register ...............................................................................41

Table 4-11. 16- Error Interrupt Status Register Definitions ....................................................... 41

Table 4-12. Status Register ...................................................................................................... 43

Table 4-13. Status Register Definitions..................................................................................... 43

Table 4-14. Address Register ................................................................................................... 45

Table 4-15. 16- Address Register Definitions............................................................................ 45

Table 4-16. Frame Number Register......................................................................................... 46

Table 4-17. Frame Number Register Definitions ....................................................................... 46

Table 4-18. Token Register....................................................................................................... 48

Table 4-19. Token Register Definitions ..................................................................................... 48

Table 4-20. Valid PID Tokens ...................................................................................................48

Table 4-21. Endpoint Control Registers ....................................................................................49

Table 4-22. Endpoint Control Register Definitions ....................................................................49

Table 4-23. Endpoint Control Register Definitions ....................................................................50

Table 5-1. Bit Rates for Different Cable Lengths....................................................................... 57

Table 5-2. CAN I/O Address ..................................................................................................... 58

Table 5-3. CAN Channel Register Summary ............................................................................ 58

Table 5-4. Detailed CAN Register Map ..................................................................................... 60

Table 5-5. TxMessage_0:ID28.................................................................................................. 64

Table 5-6. TxMessage_0:ID12.................................................................................................. 64

Table 5-7. TxMessage_0:Data 55 ............................................................................................. 64

Table 5-8. TxMessage_0:Data 39 ............................................................................................. 64

Table 5-9. TxMessage_0:Data 23 ............................................................................................. 64

Table 5-10. TxMessage_0:Data 7 ............................................................................................. 64

Table 5-11. TxMessage_0:RTR ................................................................................................ 64

Table 5-12. TxMessage_0:Ctrl Flags ........................................................................................65

Table 5-13. TxMessage_0 Register Definitions......................................................................... 65

Table 5-14. RxMessage:ID28 ................................................................................................... 67

Table 5-15. Rx Message: ID28 Register Definitions.................................................................. 67

Table 5-16. RxMessage:ID12 ................................................................................................... 67

Table 5-17. Rx Message: ID12 Register Definitions.................................................................. 67

Table 5-18. Rx Message: Data 55............................................................................................. 67

Table 5-19. Rx Message: Data 55 Register Definitions............................................................. 67

Table 5-20. Rx Message: Data 39............................................................................................. 68

Table 5-21. Rx Message: Data 39 Register Definitions............................................................. 68

Table 5-22. Rx Message: Data 23............................................................................................. 68

Table 5-23. Rx Message: Data 23 Register Definitions............................................................. 68

Table 5-24. Rx Message: Data 7............................................................................................... 68

Table 5-25. Rx Message: Data 7 Register Definitions............................................................... 68

Table 5-26. RxMessage: RTR................................................................................................... 69

Table 5-27. Rx Message: RTR Register Definitions.................................................................. 69

Table 5-28. Rx Message: Msg Flags......................................................................................... 69

Table 5-29. Rx Message: Msg Flags Register Definitions......................................................... 69

Table 5-30. Tx/Rx Error Count ..................................................................................................70

Table 5-31. Tx\Rx Error Count Register Definitions .................................................................. 70

Table 5-32. Error Status............................................................................................................ 70

Table 5-33. Error Status Register Definitions............................................................................ 70

v

Page 8

Table 5-34. Tx/Rx Message Level Register ..............................................................................71

Table 5-35. Tx/Rx Message Level Register Definitions............................................................. 71

Table 5-36. Interrupt Flags........................................................................................................ 72

Table 5-37. Interrupt Flag Definitions ........................................................................................ 72

Table 5-38. Interrupt Enable Registers ..................................................................................... 73

Table 5-39. Interrupt Enable Register Definitions...................................................................... 73

Table 5-40. Interrupt Enable Registers ..................................................................................... 74

Table 5-41. Interrupt Enable Register Definitions...................................................................... 74

Table 5-42. Bit Rate Divisor Register ........................................................................................ 75

Table 5-43. Bit Rate Divisor Register Definitions ......................................................................75

Table 5-44. Configuration Register ........................................................................................... 76

Table 5-45. Configuration Register Definitions.......................................................................... 76

Table 5-46. Acceptance Filter Enable Register ......................................................................... 78

Table 5-47. Acceptance Filter Enable Register Definitions .......................................................78

Table 5-48. Acceptance Mask 0 Register ................................................................................. 78

Table 5-49. Acceptance Mask 0 Register Definitions................................................................ 78

Table 5-50. Acceptance Mask Register: ID 12.......................................................................... 79

Table 5-51. Acceptance Mask Register: ID12 Definitions .........................................................79

Table 5-52. Acceptance Mask Register: Data 55 ...................................................................... 79

Table 5-53. Acceptance Mask Register: Data 55 Definitions ....................................................79

Table 5-54. Acceptance Code Register .................................................................................... 80

Table 5-55. Acceptance Code Register Definitions................................................................... 80

Table 5-56. Acceptance Mask Register: ID12 ........................................................................... 80

Table 5-57. Acceptance Mask Register: ID12 Definitions .........................................................80

Table 5-58. Acceptance Mask Register: Data 55 ...................................................................... 80

Table 5-59. Acceptance Mask Register: Data 55 Definitions ....................................................80

Table 5-60. Arbitration Lost Capture Register ........................................................................... 81

Table 5-61. Arbitration Lost Capture Register Definitions .........................................................81

Table 5-62. Error Capture Register ........................................................................................... 82

Table 5-63. Error Capture Register Definitions .........................................................................82

Table 5-64. Frame Reference Register..................................................................................... 83

Table 5-65. Error Capture Register Definitions .........................................................................83

List of Figures

Figure 3-1. DSTni I

Figure 4-1. Buffer Descriptor Table ........................................................................................... 33

Figure 4-2. USB Token Transaction.......................................................................................... 37

Figure 3. Enable Host Mode and Configure a Target Device.................................................... 51

Figure 4. Full-Speed Bulk Data Transfers to a Target Device................................................... 52

Figure 4-5. Pull-up/Pull-down USB............................................................................................ 53

Figure 5-1. TX Message Routing ..............................................................................................63

Figure 5-2. RX Message Routing .............................................................................................. 66

Figure 5-3. CAN Operating Mode.............................................................................................. 75

Figure 5-4. Bit Time, Time Quanta, and Sample Point Relationships .......................................77

Figure 5-5. CAN Bus Interface ..................................................................................................84

Figure 5-6. CAN Connector.......................................................................................................84

Figure 5-7. Power for CAN........................................................................................................ 85

Figure 5-8. CAN Transceiver and Isolation Circuits .................................................................. 86

2

C Controller Block Diagram ....................................................................... 12

vi

Page 9

11:: AAbboouutt TThhiiss UUsseerr GGuuiiddee

This User Guide describes the technical features and programming interfaces of the Lantronix

DSTni-EX chip (hereafter referred to as “DSTni”).

DSTni is an Application Specific Integrated Circuit (ASIC)-based single-chip solution (SCS) that

integrates the leading-edge functionalities needed to develop low-cost, high-performance device

server products. On a single chip, the DSTni integrates an x186 microprocessor, 16K-byte

ROM, 256K-byte SRAM, programmable input/output (I/O), and serial, Ethernet, and Universal

Serial Bus (USB) connectivity — key ingredients for device- server solutions. Although DSTni

embeds multiple functions onto a single chip, it can be easily customized, based on the

comprehensive feature set designed into the chip.

Providing a complete device server solution on a single chip enables system designers to build

affordable, full-function solutions that provide the highest level of performance in both

processing power and peripheral systems, while reducing the number of total system

components. The advantages gained from this synergy include:

Simplifying system design and increased reliability.

Minimizing marketing and administration costs by eliminating the need to source

products from multiple vendors.

Eliminating the compatibility and reliability problems that occur when combining

separate subsystems.

Dramatically reducing implementation costs.

Increasing performance and functionality, while maintaining quality and cost

effectiveness.

Streamlining development by reducing programming effort and debugging time.

Enabling solution providers to bring their products to market faster.

These advantages make DSTni the ideal solution for designs requiring x86 compatibility;

increased performance; serial, programmable I/O, Ethernet, and USB communications; and a

glueless bus interface.

1

Page 10

Intended Audience

This User Guide is intended for use by hardware and software engineers, programmers, and

designers who understand the basic operating principles of microprocessors and their systems

and are considering designing systems that utilize DSTni.

Conventions

This User Guide uses the following conventions to alert you to information of special interest.

The symbols # and n are used throughout this Guide to denote active LOW signals.

Notes: Notes are information requiring attention.

Navigating Online

The electronic Portable Document Format (PDF) version of this User Guide contains hyperlinks.

Clicking one of these hyper links moves you to that location in this User Guide. The PDF file

was created with Bookmarks and active links for the Table of Contents, Tables, Figures and

cross-references.

2

Page 11

Organization

This User Guide contains information essential for system architects and design engineers. The

information in this User Guide is organized into the following chapters and appendixes.

Section 1: Introduction

Describes the DSTni architecture, design benefits, theory of operations, ball

assignments, packaging, and electrical specifications. This chapter includes a

DSTni block diagram.

Section 2: Microprocessor

Describes the DSTni microprocessor and its control registers.

Section 2: SDRAM

Describes the DSTni SDRAM and the registers associated with it.

Section 3: Serial Ports

Describes the DSTni serial ports and the registers associated with them.

Section 3: Programmable Input/Output

Describes DSTni’s Programmable Input/ Output (PIO) functions and the

registers associated with them.

Section 3: Timers

Describes the DSTni timers.

Section 4: Ethernet Controllers

Describes the DSTni Ethernet controllers.

Section 4: Ethernet PHY

Describes the DSTni Ethernet physical layer core.

Section 5: SPI Controller

Describes the DSTni Serial Peripheral Interface (SPI) controller.

Section 5: I2C Controller

Describes the DSTni I

Section 5: USB Controller

Describes the DSTni USB controller.

Section 5: CAN Controllers

Describes the DSTni Controller Area Network (CAN) bus controllers.

Section 6: Interrupt Controller

Describes the DSTni interrupt controller.

Section 6: Miscellaneous Registers

Describes DSTni registers not covered in other chapters of this Guide.

Section 6: Debugging In-circuit Emulator (Delce)

Section 6: Packaging and Electrical

Describes DSTni’s packaging and electrical characteristics.

Section 6: Applications

Describes DSTni’s packaging and electrical characteristics.

Section 6: Instruction Clocks

Describes the DSTni instruction clocks.

Section 6: DSTni Sample Code

Section 6: Baud Rate Calculations

Provides baud rate calculation tables.

2

C controller.

3

Page 12

22:: SSPPII CCoonnttrroolllleerr

This chapter describes the DSTni Serial Peripheral Interface (SPI) controller. Topics include:

Theory of Operation on page 4

SPI Controller Register Summary on page 5

SPI Controller Register Definitions on page 6

Theory of Operation

SPI Background

SPI is a high-speed synchronous serial input/output (I/O) port that allows a serial bit stream of

programmed length (one to eight bits) to be shifted into and out of the device at a

programmable bit-transfer rate.

SPI is an industry-standard communications interface that does not have specifications or a

standards organizing group. As a result, there are no licensing requirements. Because of its

simplicity, SPI is commonly used in embedded systems. Many semiconductor manufacturers

sell a variety of sensor, conversion, and control devices that use SPI.

DSTni SPI Controller

The DSTni SPI controller is located at base I/O address B800h. It shares an interrupt with the

2

I

C controller and connects to interrupt 2. The SPI controller is enabled using the DSTni

Configuration register. If set to 1, the SPI controller is enabled on serial port 3. This bit can

reset to 1 with an external pull-up resistor. Normally it resets to 0 on reset or power-up.

The SPI bus is a 3-wire bus serial bus that links a serial shift register between a master device

and a slave device. This design supports both master and slave operations. Typically, master

and slave devices have an 8-bit shift register, for a combined register of 16 bits. During an SPI

transfer, the master and slave shift registers by eight bits and exchange their 8-bit register

values, starting with the most-significant bit.

The SPI interface is software configurable. The clock polarity, clock phase, SLVSEL polarity,

clock frequency in master mode, and number of bits to be transferred are all software

programmable. SPI supports multiple slaves on a single 3-wire bus by using separate Slave

Select signals to enable the desired slave. Multiple masters are also fully supported and some

support is provided for detecting collisions when multiple masters attempt to transfer at the

same time.

A Wired-OR mode is provided which allows multiple masters to collide on the bus without risk of

damage. In this mode, an external pull-up resistor is required on the Master Out Slave In

(MOSI) ) and Master In Slave Out (MISO) pins. The wired-OR mode also allows the SPI bus to

operate as a 2-wire bus by connecting the MOSI and MISO pins to form a single bi-directional

data pin. Generally, pull-ups are recommended on all of the external SPI signals to ensure they

are held in a valid state, even when the SPI interface is disabled. For some device connections,

the ALT mode bit will swap the TX and RX pins.

The SPI controller has an enhanced mode called AUTODRV. This mode is valid in master

mode. In this mode, the SLVSEL pin is driven active when data is written to the data register.

After the last bit of data is shifted out, the SLVSEL goes inactive and an interrupt is generated.

The INVCS bit can generate either a positive or negative true SLVSEL pin.

4

Page 13

When operating as a slave, the SPI clock signal (SCLK) must be slower than 1/8th of the CPU

clock (1/16th is recommended).

Note: The SPI is fully synchronous to the CLK signal. As a result, SCLK is sampled and then

operated on. This results in a delay of 3 to 4 clocks, which may violate the SPI specification if

SCLK is faster than 1/8th of the CPU clock. In master mode, the SPI operates exactly on the

proper edges, since the SPI controller is generating SCLK.

The SPI controller uses a 16-bit counter that is continually reloaded from DVD_CNTR_HI and

DVD_CNTR_LO. The counter divides the CPU clock by this divider and uses the result to

generate SCLK.

The SPI interface includes the internal interrupt connection, SPI interrupt.

In SPI master mode, an SPI interrupt occurs when the Transmit Holding register is

empty.

In SPI slave mode, an SPI interrupt occurs when the SLVSEL pin transitions from active

to inactive.

A familiar Interrupt Control register is provided for the SPI interrupt. The interrupt has a two

CPU clock delay from SLVSEL in slave mode because of synchronization registers.

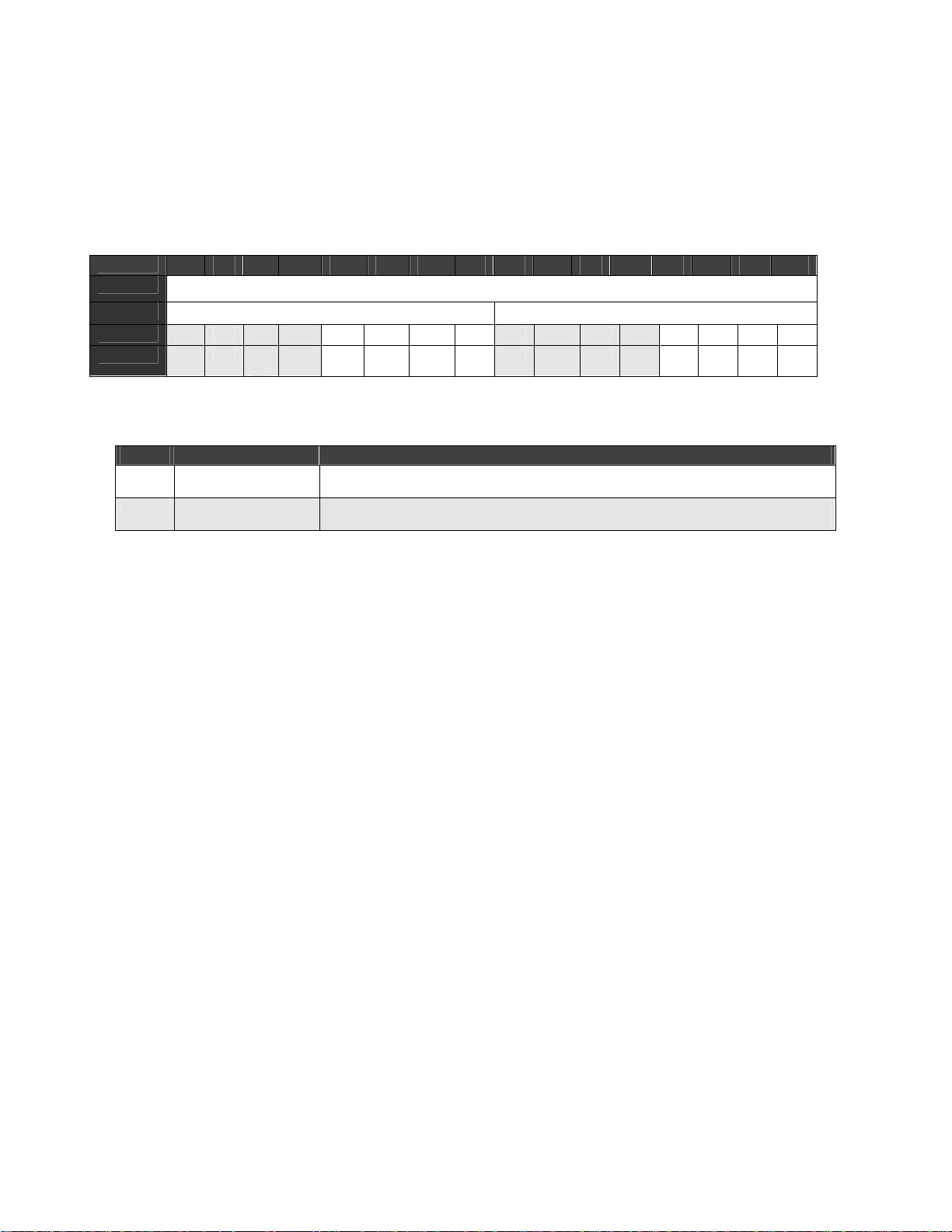

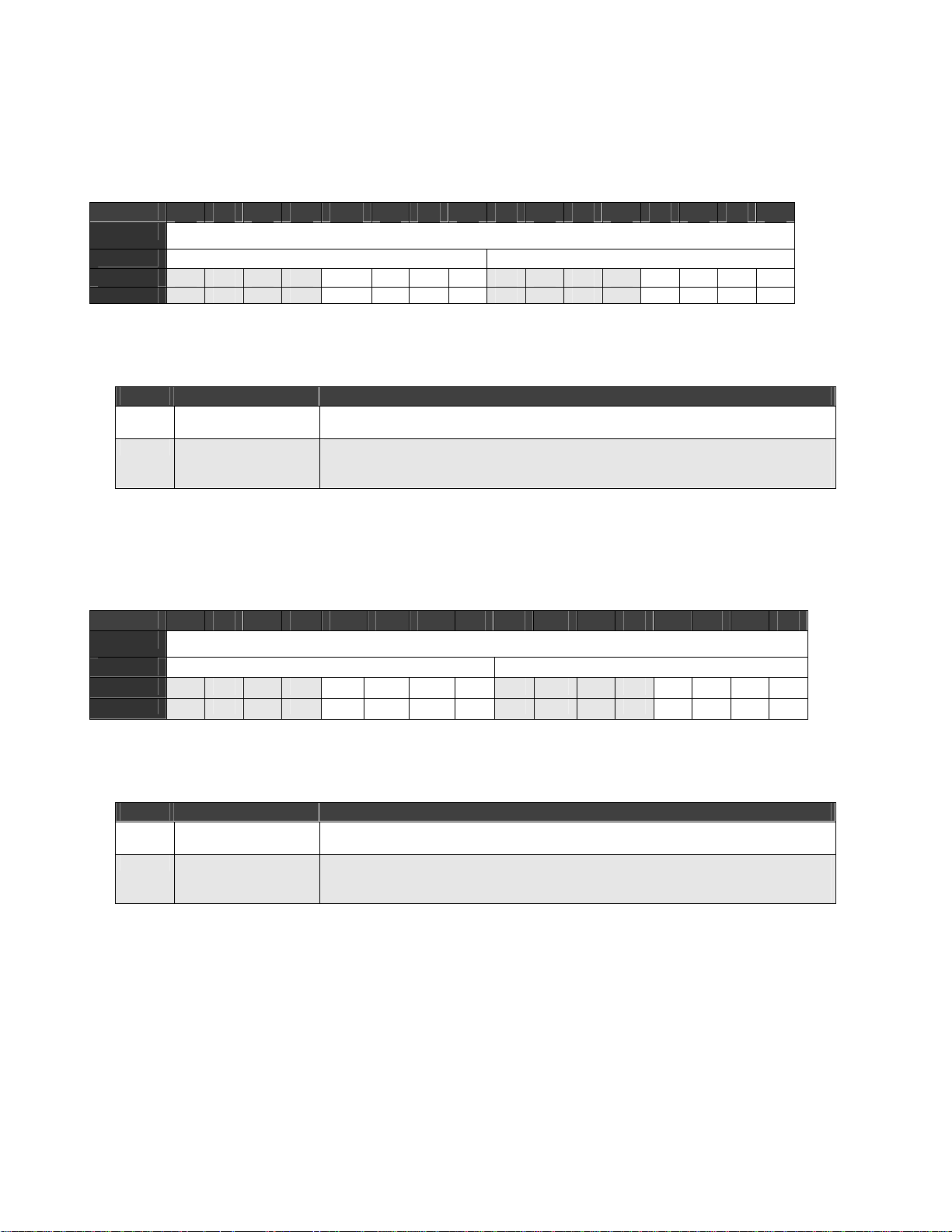

SPI Controller Register Summary

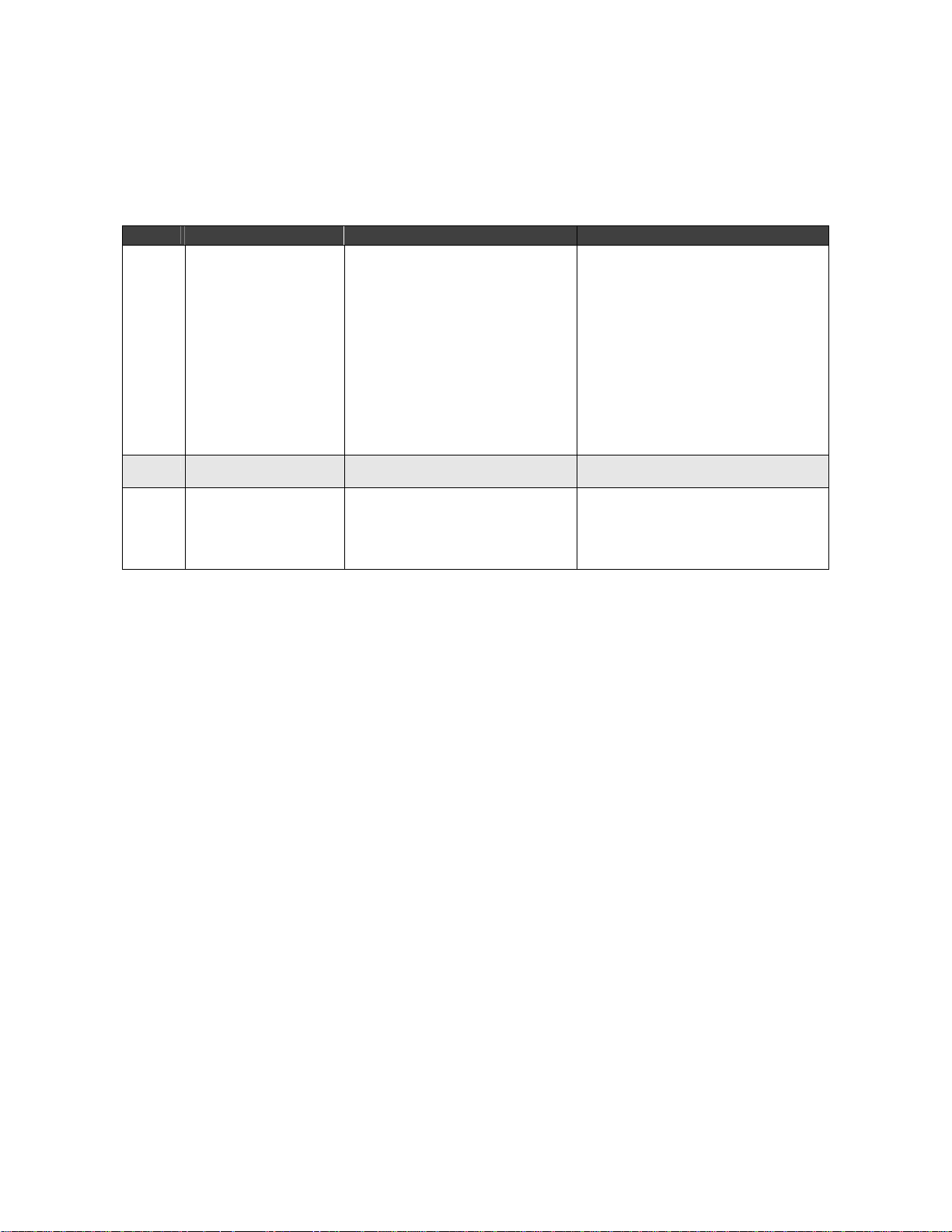

Table 2-1. SPI Controller Register Summary

Hex Address Mnemonic Register Description Page

B800 SPI_DATA Data register

B802 CTL Control register

B804 SPI_STAT Status register

B806 SPI_SSEL Slave Select Bit Count register

B808 DVD_CNTR_LO DVD Counter Low Byte register

B80A DVD_CNTR_HI DVD Counter High Byte register

6

7

8

9

10

10

5

Page 14

SPI Controller Register Definitions

SPI_DATA Register

SPI_DATA is the SPI Controller Data register.

Table 2-2. SPI_DATA Register

BIT

OFFSET

FIELD

RESET

RW

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

/// DATA[7:0]

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

Table 2-3. SPI_DATA Register Definitions

Bits Field Name Description

15:8 ///

7:0 DATA[7:0]

Reserved

Always returns zero.

Data

The location where the CPU reads data from or writes data for the SPI interface.

B800

6

Page 15

CTL Register

CTL is the SPI Controller Control register.

Table 2-4. CTL Register

BIT

OFFSET

FIELD

RESET

RW RW RW RW RW R

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

///

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

W

Table 2-5. CTL Register Definitions

Bits Field Name Description

15:8 ///

7 IRQENB

6

AUTODRV

5

INVCS

4 PHASE

3 CKPOL

2 WOR

1 MSTN

0 ALT

Reserved

Always returns zero.

Interrupt Request Enable

1 = enable the SPI to generate interrupts.

0 = disable the SPI from generating interrupts (default).

Autodrv

1 = enabled. Autodrv generates the sequence of selecting the serial device (CS)

and transferring data to it and then deselecting the device with no CPU

interaction. The transfer is started by writing to the data register.

0 = disabled (default).

Invert Chip Select

1 = inverted CS.

0 = normal (default).

Phase Select

Selects the operating mode for the SPI interface. The two modes select where

the opposite edge D-Flip-Flop is placed.

1 = the negative edge flop is inserted into the shift_out path to hold the data for an

extra ½ clock.

0 = a negative edge flop is inserted into the shift_in path (default).

Clock Polarity

Controls the polarity of the SCLK (SPI clock).

1 = SCLK idles HIGH.

0 = SCLK idles LOW (default).

Wire-O

HIGH = WOR bit configures the SPI bus to operate as an Open-Drain. This

prevents SPI bus conflicts when there are multiple bus masters.

LOW = WOR bit does not configure the SPI bus to operate as an Open-Drain.

Master Enable

Selects master or slave mode for the SPI interface.

1 = master mode.

0 = slave mode (default).

Alternate I/O Pinouts

Enable alternate I/O pinouts.

1 = alternate I/O.

0 = normal (default).

B802

IRQENB

AUTODRV

INVCS

PHASE

CKPOL

WOR

MSTN

ALT

RW RW RW RW RW RW RW RW RW RW RW

7

Page 16

SPI_STAT Register

To clear a bit in the SPI_STAT register, write a 1 to that bit.

Table 2-6. SPI_STAT Register

BIT

OFFSET

FIELD

RESET

RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW R R

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

B804

///

IRQ

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

OVERRUN

COL

///

TXRUN

SLVSEL

Table 2-7. SPI_STAT Register Definitions

Bits Field Name Description

15:8 ///

7 IRQ

6 OVERRUN

5 COL

4:2 ///

1 TXRUN

0 SLVSEL

Reserved

Always returns zero.

Interrupt Request

1 = indicates the end of a master mode transfer, or that SLVSEL_N input has

gone HIGH on a slave transfer.

0 = indicates no end of a master mode transfer, or that SLVSEL_N input has not

gone HIGH on a slave transfer (default).

It takes two CPU clocks after SLVSEL_n changes to see the interrupt.

Overrun

1 = SPIDAT register is written to while an SPI transfer is in progress or

SLVSEL_N goes active in master mode.

0 = SPIDAT register has not been written to or SLVSEL_N has not gone active in

master mode (default).

Collision

1 = a master mode collision has occurred between multiple SPI masters (SLVSEL

is active while MSTEN=1).

0 = a master mode collision has not occurred (default).

Reserved

Transmitter Running

1 = master mode operation underway.

0 = idle (default).

SLVSEL Pin

Corresponds to the SLVSEL (MSCS*) pin on SPI core (pin is normally inverted at

the I/O pin).

8

Page 17

SPI_SSEL Register

SPI_SSEL is the Slave Select Bit Count register.

Table 2-8. SPI_SSEL Register

BIT

OFFSET

FIELD

RESET

RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

Bits Field Name Description

15:8 ///

7:6 BCNT[2:0]

5:1 ///

0 SELECTO

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

B806

/// BCNT[2:0] ///

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Table 2-9. SPI_SSEL Register Definitions

Reserved

Always returns zero.

Bit Shift Count

Controls the number of bits shifted between the master and slave device during a

transfer, when this device is the master. See Table 2-10.

Reserved

Always returns zero.

SelectO Signal

This bit is the select output for master mode.

1 = this bit drives the SLVSEL pin active.

0 = this bit inactivates SLVSEL (default).

This bit is not used with Autodrv. If using Autodrv, leave this bit set to 0. The

INVCS is used to invert the SLVSEL for active LOW devices.

SELECTO

Table 2-10. BCNT Bit Settings

BCNT[2:0]

Bit [2] Bit [1] Bit [0]

0 0 0 8 (default)

0 0 1 1

0 1 0 2

0 1 1 3

1 0 0 4

1 0 1 5

1 1 0 6

1 1 1 7

Number of Bits Shifted

9

Page 18

DVD_CNTR_LO Register

DVD_CNTR_LO is the DVD Counter Low Byte register.

Table 2-11. DVD_CNTR_LO Register

BIT

OFFSET

FIELD

RESET

RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

B808

/// DVDCNT[7:0]

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Table 2-12. DVD_CNTR_LO Register Definitions

Bits Field Name Description

15:8 ///

7:0 DVDCNT[7:0]

Reserved

Always returns zero.

Divisor Select

Selects the SPI clock rate during master mode. DVD_CNTR_HI and this byte

generate a 16-bit divisor that generates the SPI clock.

DVD_CNTR_HI

DVD_CNTR_HI is the DVD Counter High Byte register.

Table 2-13. DVD_CNTR_HI Register

BIT

OFFSET

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

B80A

FIELD

RESET

RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

/// DVDCNT[15:8]

Table 2-14. DVD_CNTR_HI Register Definitions

Bits Field Name Description

15:8 ///

7:0 DVDCNT[15:8]

Reserved

Always returns zero.

Divisor Select

Selects the SPI clock rate during master mode. DVD_CNTR_LO and this byte

generate a 16-bit divisor that generates the SPI clock.

10

Page 19

2

2

I

33:: I

CC CCoonnttrroolllleerr

Features

This chapter describes the DSTni I2C controller. Topics include:

Features on page 11

Block Diagram on page 12

Theory of Operation on page 12

Programmer’s Reference on page 22

2

I

C Controller Register Summary on page 22

2

I

C Controller Register Definitions on page 23

Master or slave operation

Multmaster operation

Software selectable acknowledge bit

Arbitration-lost interrupt with automatic mode switching from master to slave

Calling address identification interrupt with automatic mode switching from master to

slave

START and STOP signal generation/detection

Repeated START signal generation

Acknowledge bit generation/detection

Bus busy detection

100 KHz to 400 KHz operation

11

Page 20

Block Diagram

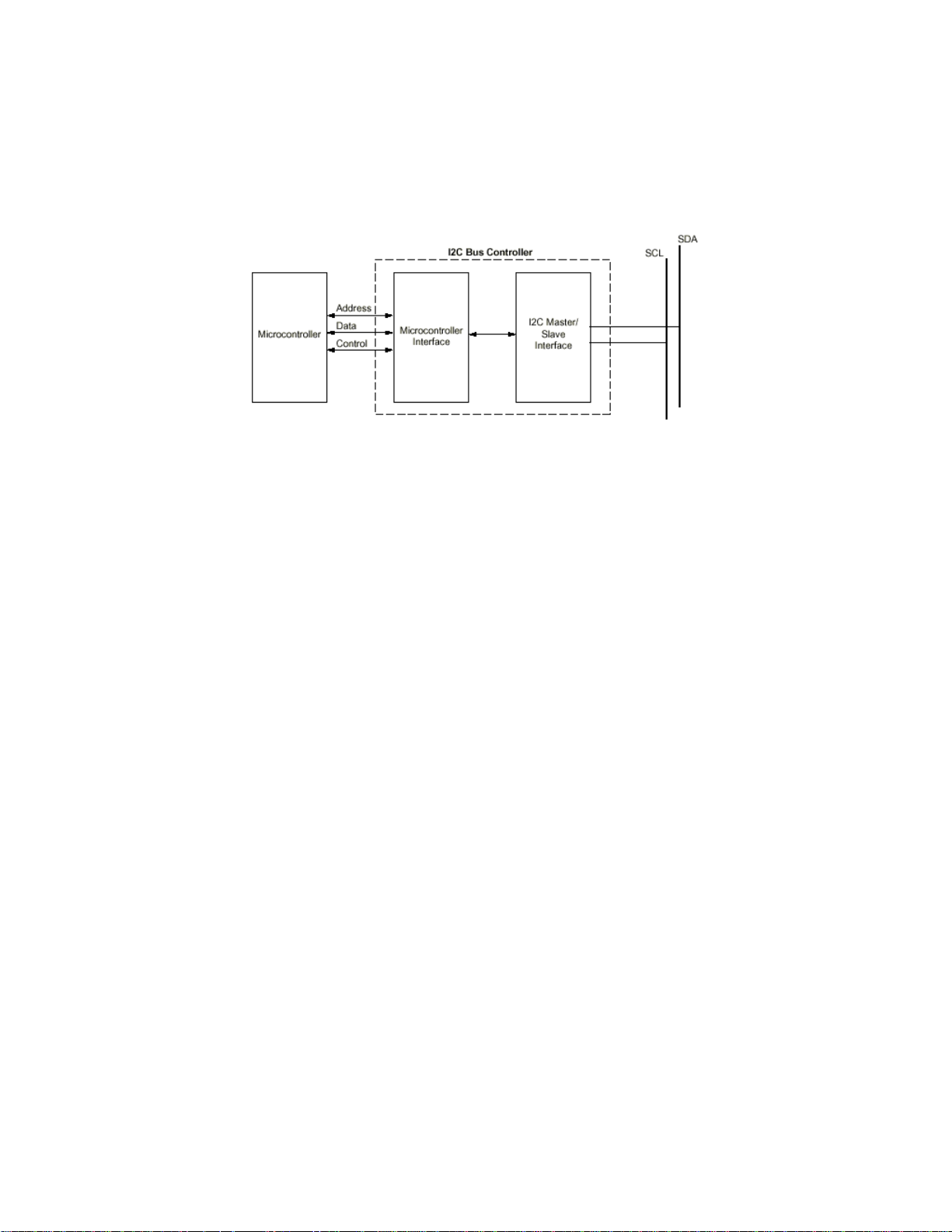

Figure 3-1 shows a block diagram of the DSTni I2C controller.

Theory of Operation

I2C Background

The I2C bus is a popular serial, two-wire interface used in many systems because of its low

overhead. Capable of 100 KHz operation, each device connected to the bus is software

addressable by a unique address, with a simple master/slave protocol.

2

The I

C bus consists of two wires, serial data (SDA), and a serial clock (SCL), which carry

information between the devices connected to the bus. This two-wire interface minimizes

interconnections, so integrated circuits have fewer pins, and the number of traces required on

printed circuit boards is reduced.

Figure 3-1. DSTni I

2

C Controller Block Diagram

The number of devices connected to the same bus is limited only by a maximum bus

capacitance of 400 pF. Both the SDA and SCL lines are bidirectional, connected to a positive

supply voltage via a pull-up resistor. When the bus is free, both lines are HIGH. The output

stages of devices connected to the bus must have an open-drain or open-collector to perform

the wired-AND function.

Each device on the bus has a unique address and can operate as either a transmitter or

receiver. In addition, devices can also be configured as masters or slaves.

A master is the device that initiates a data transfer on the bus and generates the clock

signals to permit that transfer.

Any other device that is being addressed is considered a slave.

2

The I

C protocol defines an arbitration procedure to ensure that if more than one master

simultaneously tries to control the bus, only one is allowed to do so and the message is not

corrupted. The arbitration and clock synchronization procedures defined in the I

are supported by the DSTni I

2

C controller.

2

C specification

12

Page 21

I2C Controller

The I2C controller base address is D000h and shares INT2 with the SPI controller. The I2C bus

interface requires two bi-directional buffers with open collector (or open drain) outputs and

Schmitt inputs.

Operating Modes

The following sections describe the possible I2C operating modes:

Master Transmit Mode, page 13

Master Receive Mode, page 16

Slave Transmit Mode, page 19

Slave Receive Mode, page 20

Master Transmit Mode

In master transmit mode, the I

2

C controller transmits a number of bytes to a slave receiver.

To enter the master transmit mode, set the STA bit to one. The following actions occur:

1. The DATA register loads either a 7-bit slave address or the first part of a 10-bit slave

address, with the least-significant bits cleared to zero, to specify transmit mode.

2. The M I

2

C tests the I2C bus and sends a START condition when the bus is free.

3. The IFLG bit is set and the status code in the Status register becomes 08h.

4. The IFLG bit clears to zero to prompt the transfer to continue.

5. After the 7-bit slave address (or the first part of a 10-bit address) and the write bit are sent,

the IFLG is set again.

During this sequence, a number of status codes are possible in the Status register (see Table

3-1).

Note: In 10-bit addressing, after the first part of a 10-bit address and the write bit transmit

successfully, the status code is 18h or 20h.

13

Page 22

Table 3-1. Master Transmit Status Codes

Code I2C State Microprocessor Response Next I2C Action

18h Addr + W transmitted,

ACK received

20h Addr + W transmitted,

ACK not received

38h Arbitration lost Clear IFLG

68h Arbitration lost,

SLA + W received,

ACK transmitted

78h Arbitration lost,

general call addr

received, ACK

transmitted

B0h Arbitration lost, SLA + R

received, ACK

transmitted

7-bit address:

Write byte to DATA, clear IFLG

OR

Set STA, clear IFLG

OR

Set STP, clear IFLG

OR

Set STA & STP, clear IFLG

10-bit address:

Write extended address byte to

DATA, clear IFLG

Same as code 18h Same as code 18h

OR

Set STA, clearIFLG

Clear IFLG, AAK=0

OR

Clear IFLG, AAK=1

Same as code 68h Same as code 68h

Write byte to DATA, clear IFLG,

AAK=0

OR

Write byte to DATA, clear IFLG,

AAK=1

Transmit data byte, receive

ACK

Transmit repeated START

Transmit STOP

Transmit STOP, then START

Transmit extended address byte

Return to idle

Transmit START when bus is free

Receive data byte, transmit not ACK

Receive data byte, transmit ACK

Transmit last byte, receive ACK

Transmit data byte, receive ACK

14

Page 23

Servicing the Interrupt

After servicing this interrupt, and transmitting the second part of the address, the Status register

contains one of the codes in Table 3-2.

Note: If a repeated START condition transmits, the status code is 10h instead of 08h.

Table 3-2. Codes After Servicing Interrupts (Master Transmit)

Code I2C State Microprocessor Response Next I2C Action

38h Arbitration lost Clear IFLG

OR

Set STA, clear IFLG

68h Arbitration lost,

SLA + W received,

ACK transmitted

B0h Arbitration lost,

SLA + R received,

ACK transmitted

D0h Second Address byte +

W, transmitted ACK

received

D8h Second Address byte +

W, transmitted ACK

received

Clear IFLG, AAK=0

OR

Clear IFLG, AAK=1

Write byte to DATA, Clear IFLG,

AAK=0

OR

Write byte to DATA, Clear IFLG,

AAK=1

Write byte to DATA, clear IFLG

OR

Set STA, clear IFLG

OR

Set STP, clear IFLG

OR

Set STA & STP, clear IFLG

Same as code D0h Same as code D0h

Return to idle

Transmit START when bus free

Receive data byte, transmit not ACK

Receive data byte, transmit ACK

Transmit data byte, receive ACK

Transmit data byte, receive ACK

Transmit data byte, receive ACK

Transmit repeated START

Transmit STOP

Transmit STOP, then START

15

Page 24

Transmitting Each Data Byte

After each data byte transmits, the IFLG is set, and one of the three status codes in Table 3-3 is

in the Status register.

Table 3-3. Status Codes After Each Data Byte Transmits

Code I2C State Microprocessor Response Next I2C Action

28h Data byte transmitted,

ACK received

30h Data byte transmitted,

ACK not received

38h Arbitration lost Clear IFLG

Write byte to DAT, clear IFLG

OR

Set STA, clear IFLG

OR

Set STP, clear IFLG

OR

Set STA and STP, clear IFLG

Same as code 28h Same as code 28h

OR

Set STA, clear IFLG

Transmit data byte, receive ACK

Transmit repeated START

Transmit STOP

Transmit START then STOP

Return to idle

Transmit START when bus free

All Bytes Transmit Completely

When all bytes transmit completely, set the STP bit by writing a 1 to this bit in the Control

register. The I

Transmits a STOP condition

Clears the STP bit

Returns to the idle state

2

C controller:

Master Receive Mode

In master receive mode, the I

2

C controller receives a number of bytes from a slave transmitter.

After the START condition transmits:

1. The IFLG bit is set and status code 08h is in the Status register.

2. The Data register has the slave address (or the first part of a 10-bit slave address), with the

least-significant bits set to 1 to signify a read.

3. The IFLG bit is 0 and prompts the transfer to continue.

4. When the 7-bit slave address (or the first part of a 10-bit address) and the read bit transmit,

the IFLG bit is set again.

A number of status codes are possible in the Status register, as shown in Table 3-4.

Note: In 10-bit addressing, after the first part of a 10-bit address and the read bit successfully

transmit, the status code is 40h or 48h. If a repeated START condition transmits, the status

code is 10h instead of 08h.

16

Page 25

Table 3-4. Master Receive Status Codes

Code I2C State Microprocessor Response Next I2C Action

40h Addr + W transmitted,

ACK received

48h Addr + W transmitted,

ACK not received

38h Arbitration lost Clear IFLG

68h Arbitration lost,

SLA + W received,

ACK transmitted

78h Arbitration lost,

general call addr

received, ACK

transmitted

B0h Arbitration lost, SLA + R

received, ACK

transmitted

7-bit address:

Clear IFLG, AAK=0

OR

Clear IFLG, AAK=1

10-bit address:

Write extended address byte to

DATA, clear IFLG

7-bit address:

Set STA, clear IFLG

OR

Set STP, clear IFLG

OR

Set STA & STP, clear IFLG

10-bit address:

Write extended address byte to

DATA, clear IFLG

OR

Set STA, clearIFLG

Clear IFLG, AAK=0

OR

Clear IFLG, AAK=1

Same as code 68h Same as code 68h

Write byte to DATA, clear IFLG,

AAK=0

OR

Write byte to DATA, clear IFLG,

AAK=1

Transmit data byte, receive not ACK

Receive data byte, transmit ACK

Transmit extended address byte

Transmit repeated START

Transmit STOP

Transmit STOP and START

Transmit extended address byte

Return to idle

Transmit START when bus is free

Receive data byte, transmit not ACK

Receive data byte, transmit ACK

Transmit last byte, receive ACK

Transmit data byte, receive ACK

17

Page 26

Servicing the Interrupt

After servicing this interrupt and transmitting the second part of the address, the Status register

contains one of the codes in Table 3-5.

Table 3-5. Codes After Servicing Interrupt (Master Receive)

Code I2C State Microprocessor Response Next I2C Action

38h Arbitration lost Clear IFLG

OR

Set STA, clear IFLG

68h Arbitration lost,

SLA + W received,

ACK transmitted

78h Arbitration lost,

SLA + R received,

ACK transmitted

B0h Arbitration lost Clear IFLG

E0h Second Address byte +

R transmitted, ACK

received

E8h Second Address byte +

R transmitted, ACK not

received

Clear IFLG, AAK=0

OR

Clear IFLG, AAK=1

Write byte to DATA, Clear IFLG,

AAK=0

OR

Write byte to DATA, Clear IFLG,

AAK=1

OR

Set STA, clear IFLG

Clear IFLG, AAK=0

OR

Clear IFLG, AAK=1

Clear IFLG, AAK=0

OR

Clear IFLG, AAK=1

Return to idle

Transmit START when bus free

Receive data byte, transmit not ACK

Receive data byte, transmit ACK

Transmit data byte, receive ACK

Transmit data byte, receive ACK

Return to idle

Transmit START when bus free

Receive data byte, transmit not ACK

Receive data byte, transmit ACK

Receive data byte, transmit not ACK

Receive data byte, transmit ACK

18

Page 27

Receiving Each Data Byte

After receiving each data byte, the IFLG is set and one of three status codes in Table 3-6 is in

the Status register.

When all bytes are received, set the STP bit by writing a 1 to it in the Control register. The I

controller:

Transmits a STOP condition

Clears the STP bit

Returns to the idle state

Table 3-6. Codes After Receiving Each Data Byte

Code I2C State Microprocessor Response Next I2C Action

50h Data byte received,

ACK transmitted

58h Data byte received, Not

ACK transmitted

38h Arbitration lost in not

ACK bit

Read DATA, clear IFLG, AAK=0

OR

Read DATA, clear IFLG, AAK=1

Read DATA, set STA, clear IFLG

OR

Read DATA, set STP, clear IFLG

OR

Read DATA, set STA & STP, clear

IFLG

Clear IFLG

OR

Set STA, clear IFLG

Receive data byte, transmit not ACK

Receive data byte, transmit ACK

Transmit repeated START

Transmit STOP

Transmit STOP then START

Return to idle

Transmit START when bus free

2

C

Slave Transmit Mode

In the slave transmit mode, a number of bytes are transmitted to a master receiver.

2

The I

C controller enters slave transmit mode when it receives its own slave address and a read

bit after a START condition. The I

2

C controller then transmits an acknowledge bit and sets the

IFLG bit in the Control register. The Status register contains the status code A8h.

Note: If the I

2

C controller has an extended slave address (signified by F0h - F7h in the Slave

Address register), it transmits an acknowledge after receiving the first address byte, but does

not generate an interrupt; the IFLG is not set and the status does not change. Only after

receiving the second address byte does The I

2

C controller generate an interrupt and set the

IFLG bit and status code as described above.

2

The I

C controller can also enter slave transmit mode directly from a master mode if arbitration

is lost in master mode during address transmission, and both the slave address and read bit are

received. The status code in the Status register is B0h.

After the I

1. The Data register loads the data byte to be transmitted, then IFLG clears.

2. The I

3. The I

2

C controller enters slave transmit mode:

2

C controller transmits the byte.

2

C controller receives or does not receive an acknowledge.

2

If the I

C controller receives an acknowledge:

19

Page 28

− The IFLG is set and the Status register contains B8h.

− After the last transmission byte loads in the Data register, clear

AAK when IFLG clears.

− After the last byte is transmitted, the IFLG is set and the Status

register contains C8h.

− The I

2

C controller returns to the idle state and the AAK bit must be

set to 1 before slave mode can be entered again.

2

If the I

C controller does not receive an acknowledge:

− The IFLG is set.

− The Status register contains C0h.

− The I

2

C controller returns to the idle state.

4. If the I2C detects a STOP condition after an acknowledge bit, it returns to the idle state.

Slave Receive Mode

In slave receive mode, a number of data bytes are received from a master transmitter.

2

The I

C controller enters slave receive mode when it receives its own slave address and write

bit (least-significant bit = 0) after a START condition. The I

acknowledge bit and sets the IFLG bit in the Control register. The Status register status code is

60h.

2

The I

C controller also enters slave receive mode when it receives the general call address 00h

(if the GCE bit in the Slave Address register is set). The status code is 70h.

Note: If the I

2

C controller has an extended slave address (signified by F0h - F7h in the Slave

Address register), it transmits an acknowledge after receiving the first address byte, but does

not generate an interrupt; the IFLG is not set and the status does not change. Only after

receiving the second address byte does the I

2

C controller generate an interrupt and set the

IFLG bit and the status code as described above.

2

The I

C controller also enters slave transmit mode directly from a master mode if arbitration is

lost during address transmission, and both the slave address and write bit (or general call

address if bit GCE in the Slave Address register is set to one) are received. The status code in

the Status register is 68h if the slave address is received or 78h if the general call address is

received. The IFLG bit must clear to 0 to allow the data transfer to continue.

2

C controller then transmits an

If the AAK bit in the Control register is set to 1:

1. Receiving each byte transmits an acknowledge bit (LOW level on SDA) and sets the IFLG

bit.

2. The Status register contains status code 80h (or 90h if slave receive mode was entered

with the general call address).

3. The received data byte can be read from the Data register and the IFLG bit must clear to

allow the transfer to continue.

4. When the STOP condition or repeated START condition is detected after the acknowledge

bit, the IFLG bit is set and the Status register contains status code A0h.

If the AAK bit clears to zero during a transfer, the I

2

C controller transfers a not acknowledge bit

(high level on SDA) after the next byte is received and sets the IFLG bit. The Status register

contains status code 88h (or 98h if slave receive mode was entered with the general call

address). When the IFLG bit clears to zero, the I

2

C controller returns to the idle state.

20

Page 29

Bus Clock Considerations

Bus Clock Speed

2

The I

C bus can be defined for bus clock speeds up to 100 Kb/s and up to 400 Kb/s in fast

mode.

To detect START and STOP conditions on the bus, the M I

10 times faster than the fastest master bus clock on the bus. The sampling frequency must be

at least 1 MHz (4 MHz in fast-mode) to guarantee correct operation with other bus masters.

The CLK input clock frequency and the value in CCR bits 2 - 0 determine the I

frequency. When the I

CLK input and the values in bits [2:0] and [6:3] of the Clock Control register (see Clock Control

Register on page 28).

2

C controller is in the master mode, it determines the frequency of the

2

C must sample the I2C bus at least

2

C sampling

Clock Synchronization

If another device on the I

2

the I

C controller synchronizes its clock to the I2C bus clock.

The device that generates the shortest high clock period determines the high period of

2

C bus drives the clock line when the I2C controller is in master mode,

the clock.

The device that generates the longest LOW clock period determines the LOW period of

the clock.

When the I

can stretch each bit period by holding the SCL line LOW until it is ready for the next bit. When

the I

2

C controller is in master mode and is communicating with a slow slave, the slave

2

C controller is in slave mode, it holds the SCL line LOW after each byte transfers until the

IFLG clears in the Control register.

Bus Arbitration

In master mode, the I

2

C controller checks that each logical 1 transmitted appears on the I2C bus

as a logical 1. If another device on the bus overrules and pulls the SDA line LOW, arbitration is

lost.

If arbitration is lost:

While a data byte or Not-Acknowledge bit is being transmitted, the I

2

C controller returns

to the idle state.

During the transmission of an address, the I

2

C controller switches to slave mode so that

it can recognize its own slave address or the general call address.

21

Page 30

Resetting the I

2

C Controller

There are two ways to reset the I

Using the RSTIN# pin

Writing to the Software Reset register

Using the RSTIN# pin reset method:

Clears the Address, Extended Slave Address, Data, and Control registers to 00h.

Sets the Status register to F8h.

Sets the Clock Control register to 00h.

Writing any value to the Software Reset register:

Sets the I

Sets the STP, STA, and IFLG bits of the Control register to 0.

2

C controller back to idle.

Programmer’s Reference

The DSTni I2C controller base address is D000h. The controller shares interrupt 2 with the SPI

controller. The I

drain) outputs and Schmitt inputs.

2

C bus interface requires two bidirectional buffers, with open collector (or open

2

C controller.

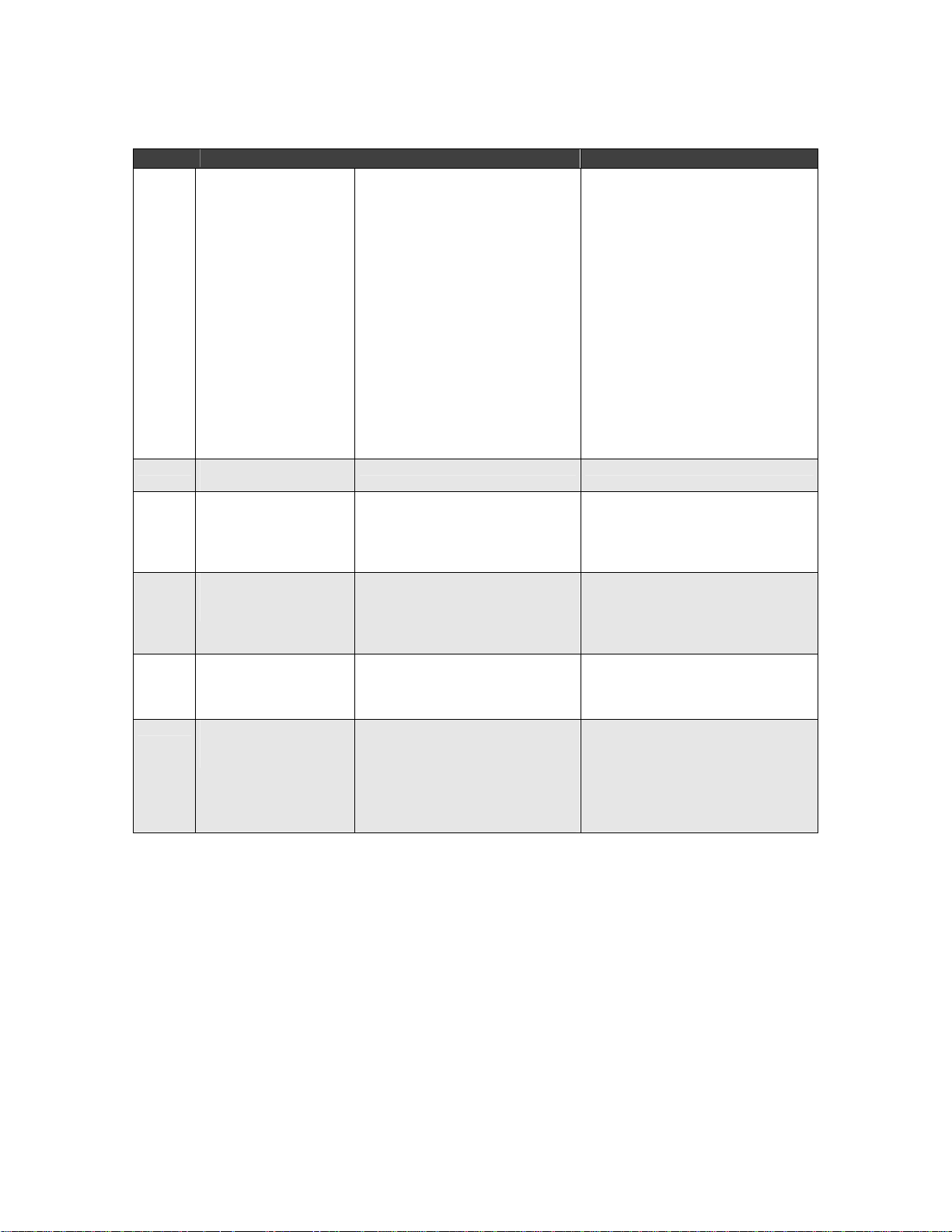

I2C Controller Register Summary

The A[2:0] address lines of the microprocessor interface provide access to the 8-bit registers in

Table 3-7.

On a hardware reset:

Address, Extended Slave Address, Data, and Control register clear to 00h.

The Status register is set to F8h.

The Clock Control register is set to 00h.

On a software reset, the STP, STA and IFLG bits of the Control register are set to zero.

2

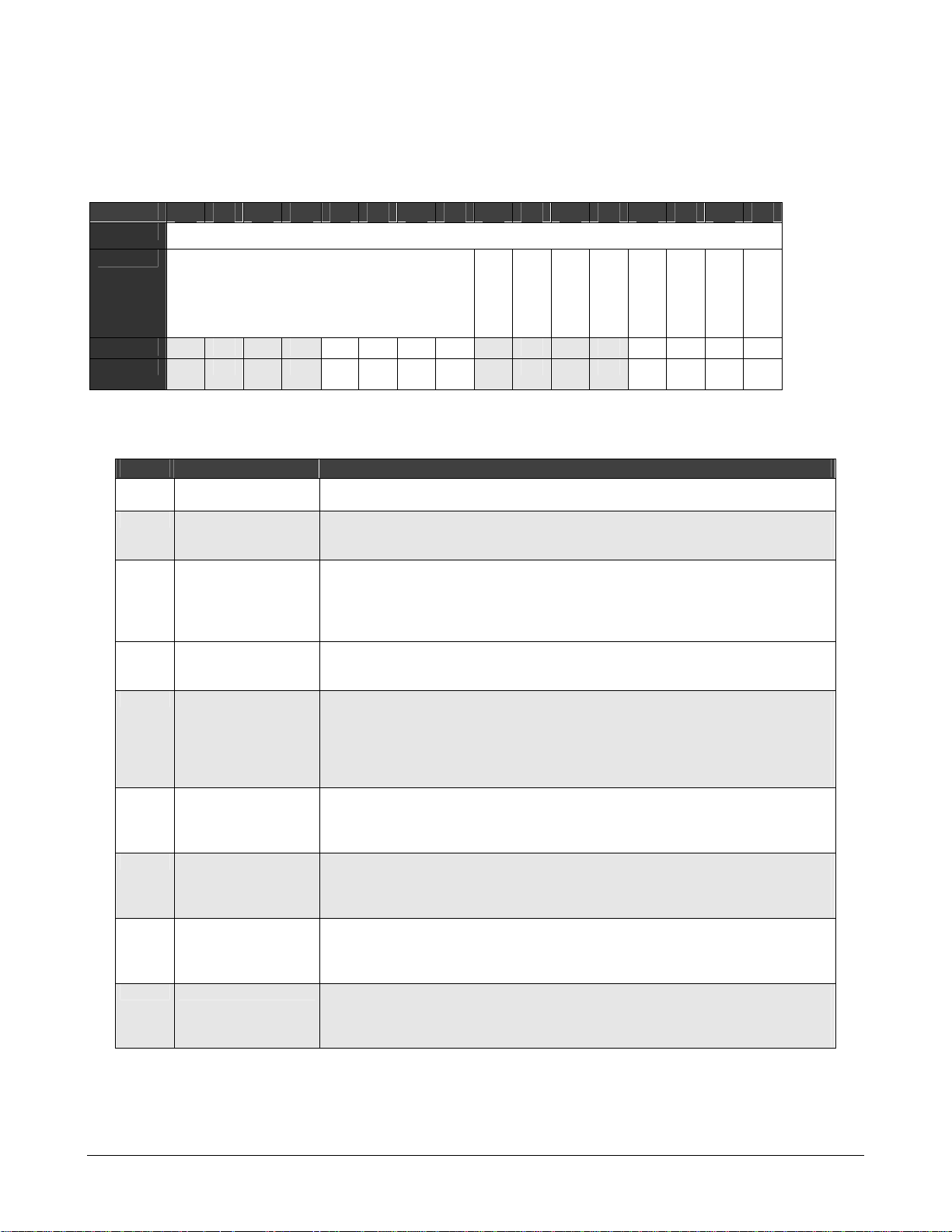

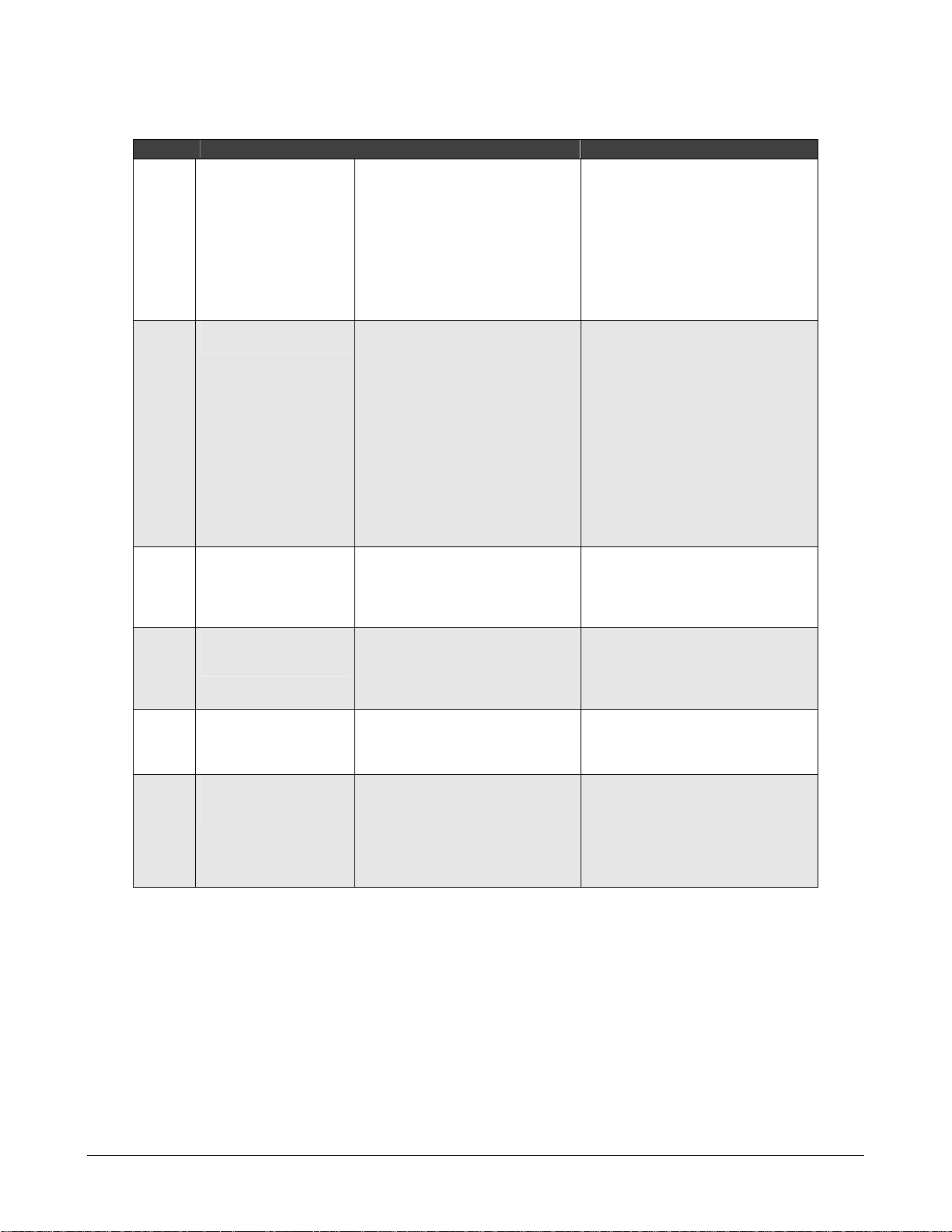

Table 3-7. I

A[2:0] Bits Page

A2 A1 A0

0 0 0 D000 ADDR Slave Address register

0 0 1 D002 DATA Data register

0 1 0 D004 CNTR Control register

0 1 1 D006 STAT Status register

0 1 1 D007 CCR Clock Control register

1 0 0 D008 XADDR Extended Slave Address register

1 1 1 D00E SRST Software Reset register

Hex

Offset

C Controller Register Summary

Mnemonic Register Description

23

24

25

26

28

29

29

22

Page 31

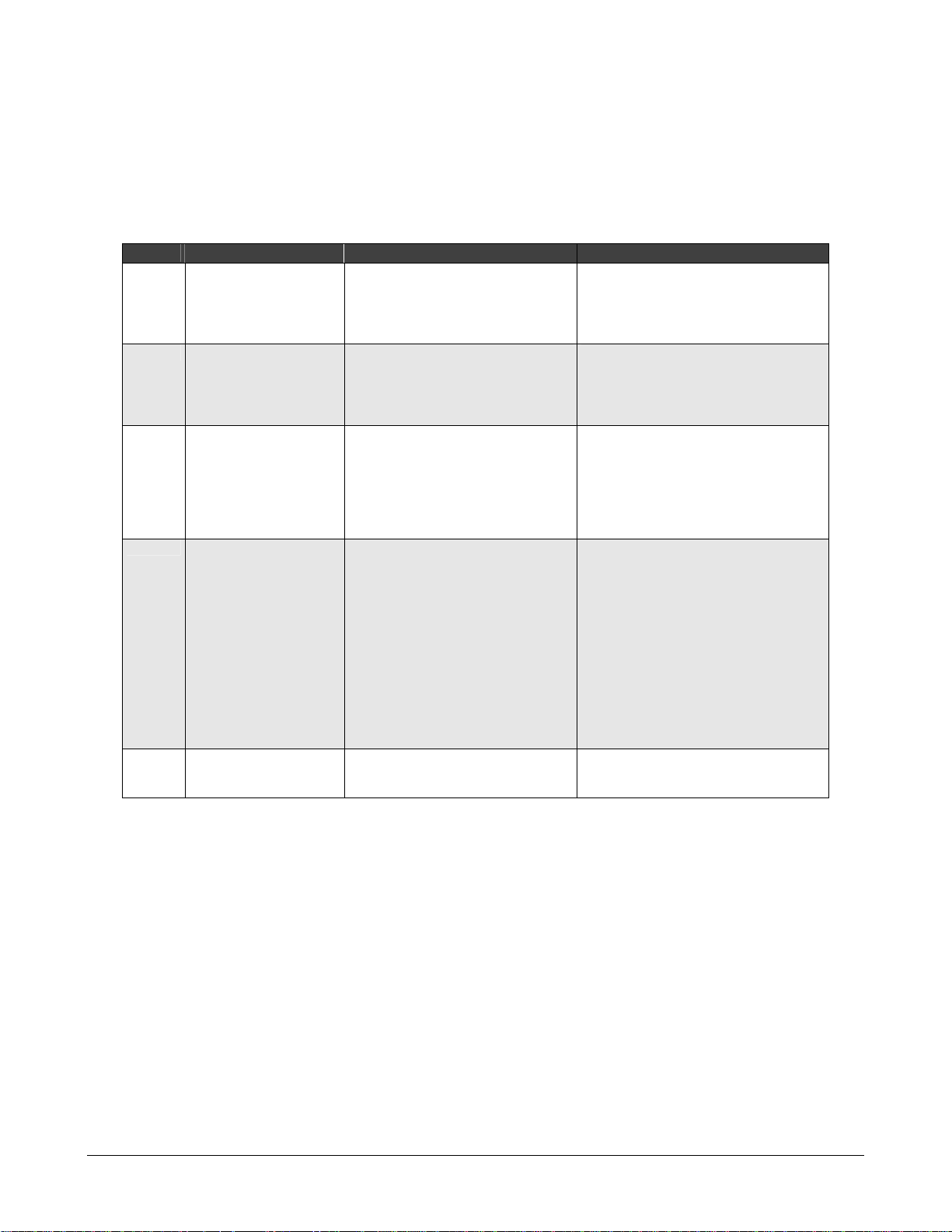

I2C Controller Register Definitions

Slave Address Register

Table 3-8. Slave Address Register

BIT

OFFSET

EXTENDED

ADDRESS

FIELD

7 6 5 4 3 2 1 0

D000

1 1 1 1 0 SLAX9 SLAX8

SLA6 SLA5 SLA4 SLA3 SLA2 SLA1 SLA0 GCE

General Call Address Enable

RESET

RW

0 0 0 0 0 0 0 0

RW RW RW RW RW RW RW RW

Table 3-9. Address Register Definitions

Bits Field Name Description

7:1 SLA6 – SLA0

0 GCE

Slave Address

For 7-bit addressing, these bits are the 7-bit address of the I

mode. When the I

generates an interrupt and enters slave mode. (SLA6 corresponds to the first bit

received from the I2C bus.)

For 10-bit addressing, when the address received starts with F0h-F7h, the I2C

controller recognizes the correspondence to SLAX9 and SLAX8 of an extended

address, and sends an ACK. (The device does not generate an interrupt at this

point.) After receiving the next address byte, the I

interrupt and enters slave mode.

General Call Address Enable

1 = I2C controller recognizes the general-call address at 00h (7-bit addressing).

0 = I2C controller does not recognize the general-call address at 00h (7-bit

addressing).

2

2

C controller receives this address after a START condition, it

2

C controller generates an

C controller in slave

23

Page 32

Data Register

The Data register contains the transmission data/slave address or the receipt data byte.

In transmit mode, the byte is sent most-significant bits first.

In receive mode, the first bit received is placed in the register’s most-significant bits.

After each byte transmits, the Data register contains the byte present on the bus; therefore, if

arbitration is lost, the Data register has the correct receive byte.

Table 3-10. Data Register

BIT 7 6 5 4 3 2 1 0

OFFSET

D002

FIELD

RESET

RW

0 0 0 0 0 0 0 0

RW RW RW RW RW RW RW RW

Transmission Data/Slave Address or Receipt Data Byte

Table 3-11. Data Register Definitions

Bits Field Name Description

7:0 SLA6 – SLA0

Transmission Data/Slave Address or Receipt Data Byte

24

Page 33

Control Register

Table 3-12. Control Register

BIT 7 6 5 4 3 2 1 0

OFFSET

D004

FIELD

RESET

RW

IEN ENAB STA STP IFLG AAK /// ///

0 0 0 0 0 0 0 0

RW RW RW RW RW RW RW RW

Table 3-13. Control Register Definitions

Bits Field Name Description

7 IEN

6 ENAB

5 STA

4 STP

3 IFLG

Extended Slave Address

l = interrupt line (INTR) goes HIGH when the IFLG bit is set.

0 = interrupt line remains LOW (default).

Extended Slave Address

1 = I2C Controller responds to calls to its slave address and to the general call

address if the GCE bit in the ADDR register is set.

0 = I2C bus inputs ISDA/ISCL are ignored and the I2C controller will not respond

to any address on the bus (default).

Start Condition

1 = I2C controller enters master mode and transmits a START condition on the

bus when the bus is free. If the I2C controller is already in master mode and one

or more bytes have been transmitted, a repeated START condition is sent. If the

I2C controller is being accessed in slave mode, the I2C controller completes the

data transfer in slave mode and enters master mode when the bus is released.

The STA bit is cleared automatically after a START condition has been sent.

0 = no effect.

Stop Condition

1 and I2C controller is in slave mode in master mode = a stop condition is

transmitted on the I2C bus.

0 and I2C controller is in slave mode = I2C controller behaves as if a STOP

condition has been received, but no STOP condition will be transmitted on the I2C

bus. If both STA and STP bits are set, the I2C controller transmits the STOP

condition (if in master mode), then transmits the START condition.

0 = no effect.

The STP bit is cleared automatically.

I2C State

1 = an I2C state has been entered. The only state that does not set IFLG is state

F8h. See the Status register.

1 and IEN bit is set = interrupt line goes HIGH. When IFLG is set by the I2C

controller, the low period of the I2C bus clock line (SCL) is stretched and the data

transfer is suspended.

0 = interrupt line goes LOW and the I2C clock line is released.

25

Page 34

Bits Field Name Description

2 AAK

1:0 ///

Acknowledge

1 = send Acknowledge (LOW level on SDA) during acknowledge clock pulse on

the I2C bus if:

−The entire 7-bit slave address or the first or second bytes of a 10-bit slave

address are received.

− The general call address is received and the GCE bit in the ADDR register is

set to one.

− A data byte is received in master or slave mode.

0 in slave transmitter mode = send Not Acknowledge (HIGH level on SDA) when

a data byte is received in master or slave mode. After this byte transmits, the I2C

controller enters state C8h and returns to idle state. The I2C controller does not

respond as a slave unless AAK is set.

Reserved

Status Register

The Status register is a Read Only register that contains a 5-bit status code in the five mostsignificant bits. The three least-significant bits are always zero. This register can contain any of

the 31 status codes in Table 3-16. When this register contains the status code F8h:

No relevant status information is available.

No interrupt is generated.

The IFLG bit in the Control register is not set.

All other status codes correspond to a defined state of the I

3-16.

2

C controller, as described in Table

When entering each of these states, the corresponding status code appears in this register and

the IFLG bit in the Control register is set. When the IFLG bit clears, the status code returns to

F8h

If an illegal condition occurs on the I

To recover from this state, set the STP bit in the Control register and clear the IFLG bit. The I

controller then returns to the idle state. No STOP condition transmits on the I

Note: The STP and STA bits can be set to 1 at the same time to recover from the bus error,

causing the I

2

C controller to send a START.

2

C bus, the bus enters the bus error state (status code 00h).

2

C bus.

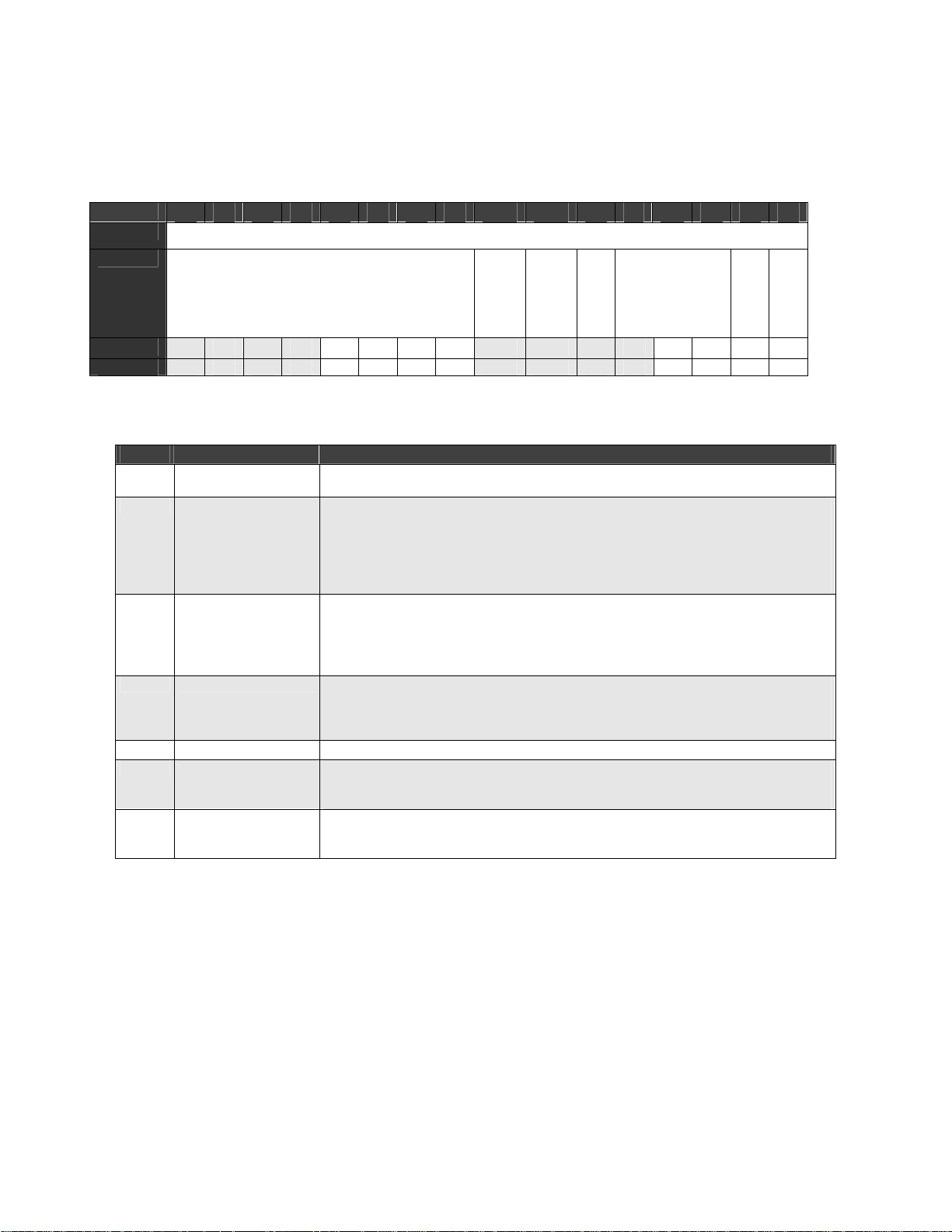

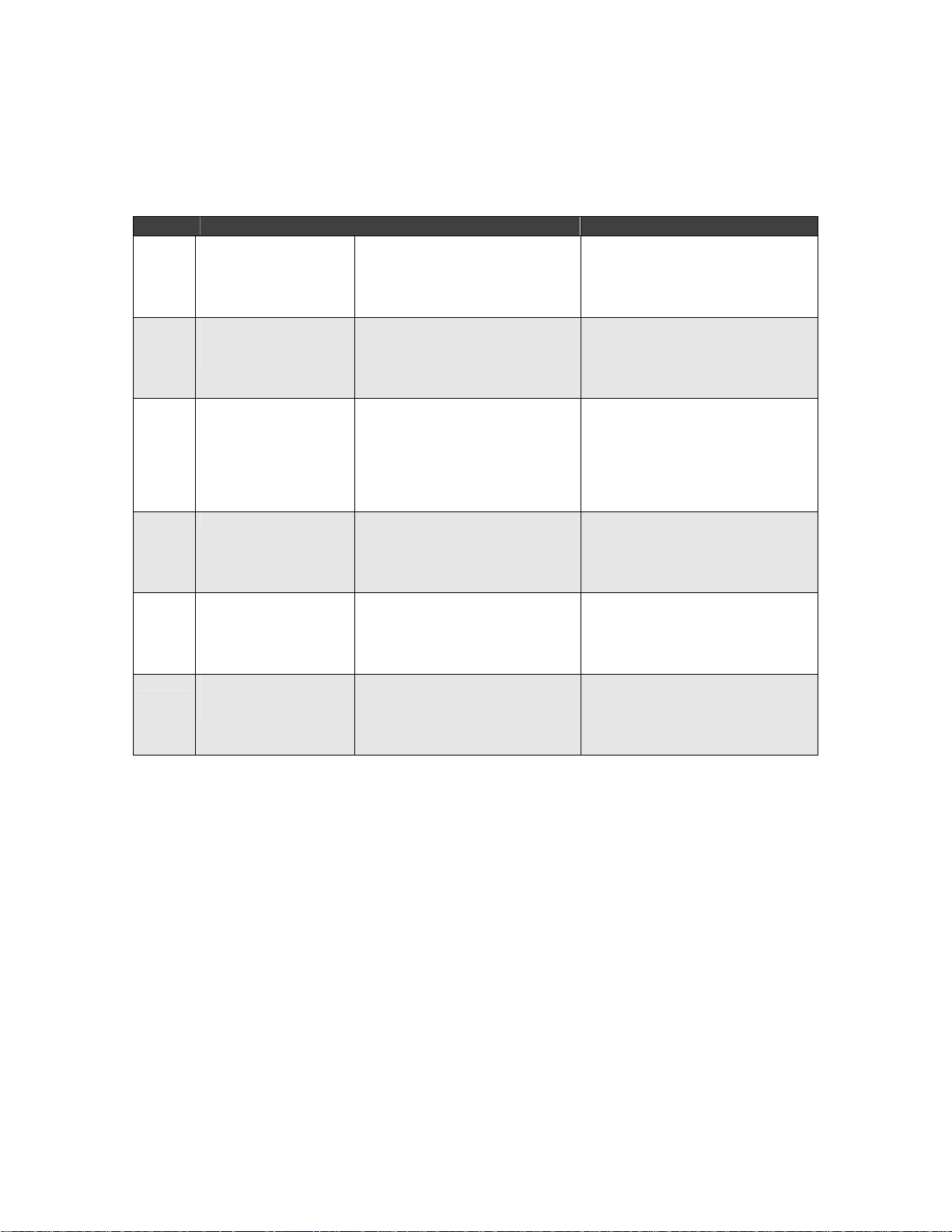

Table 3-14. Status Register

BIT 7 6 5 4 3 2 1 0

OFFSET

FIELD

RESET

RW

STATUS CODE /// /// ///

0 0 0 0 0 0 0 0

R R R R R R R R

D006

2

C

26

Page 35

Table 3-15. Status Register Definitions

Bits Field Name Description

7:3 STATUS CODE

2:0 ///

Status Code

Five-bit status code. See Table 3-16.

Reserved

Table 3-16. Status Codes

Code Description

00h Bus error

08h START condition sent

10h Repeated START condition sent

18h Address + write bit sent, ACK received

20h Address + write bit sent ACK not received

28h Data byte sent in master mode, ACK received

30h Data byte sent in master mode, ACK not received

38h Arbitration lost in address or data byte

40h Address + read bit sent, ACK received

48h Address + read bit sent, ACK not received

50h Data byte received in master mode, ACK sent

58h Data byte received in master mode, no ACK sent

60h Slave address + write bit received, ACK sent

68h Arbitration lost in address as master, slave address + write bit received, ACK sent

70h General Call address received, ACK sent

78h Arbitration lost in address as master, General Call address received, ACK sent

80h Data byte received after slave address received, ACK sent

88h Data byte received after slave address received, no ACK sent

90h Data byte received after General Call received, ACK sent

98h Data byte received after General Call received, ACK not sent

A0h STOP or repeated START condition received in slave mode

A8h Slave address + read bit received, ACK sent

B0h Arbitration lost in address as master, slave address + read bit received, ACK sent

B8h Data byte sent in slave mode, ACK received

C0h Data byte sent in slave mode, ACK not received

C8h Last byte sent in slave mode, ACK received

D0h Second Address byte + write bit sent, ACK received

D8h Second Address byte + write bit sent, ACK not received

E0h Second address byte + read bit transmitted, ACK received

E8h Second Address byte + read bit sent, ACK not received

F8h No relevant status information IFLG=0

27

Page 36

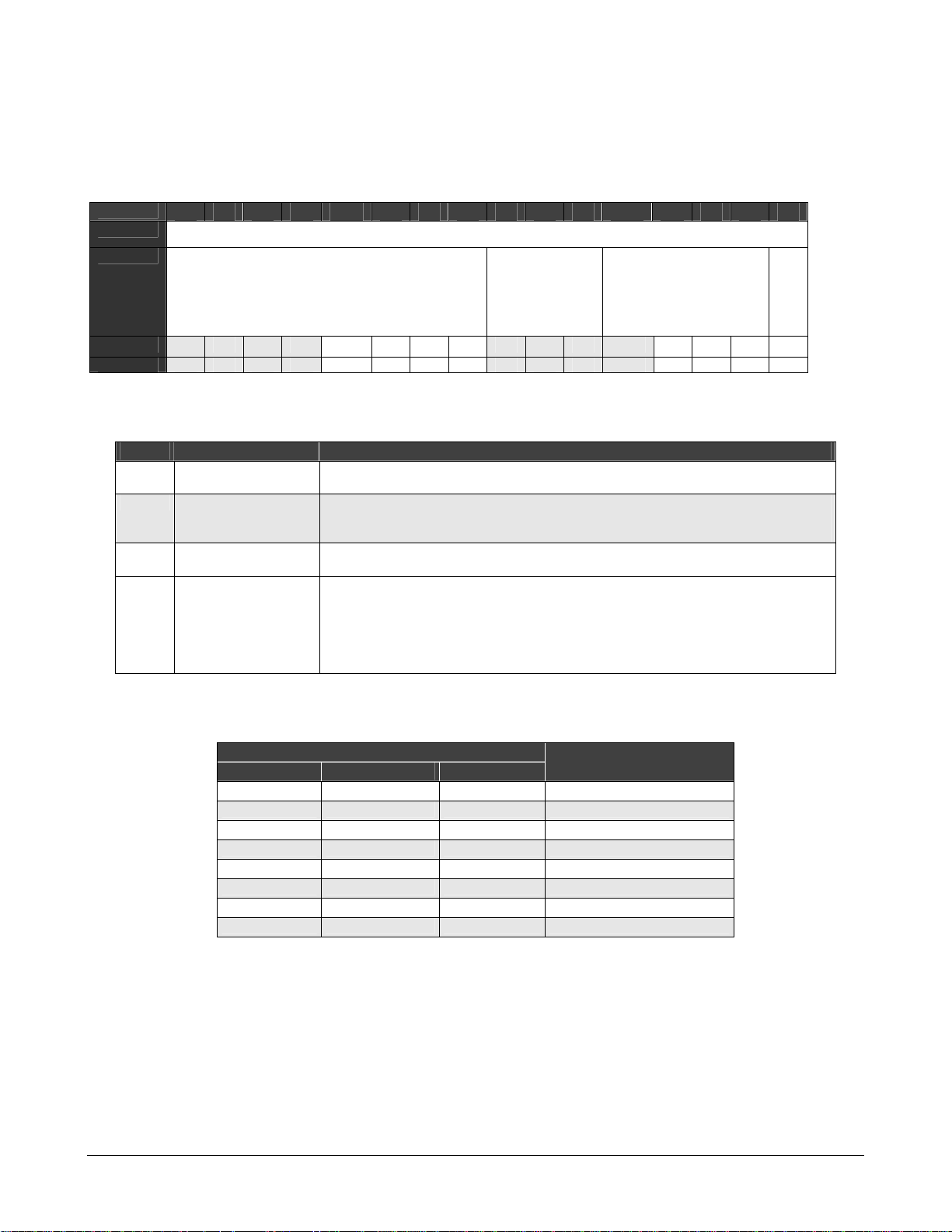

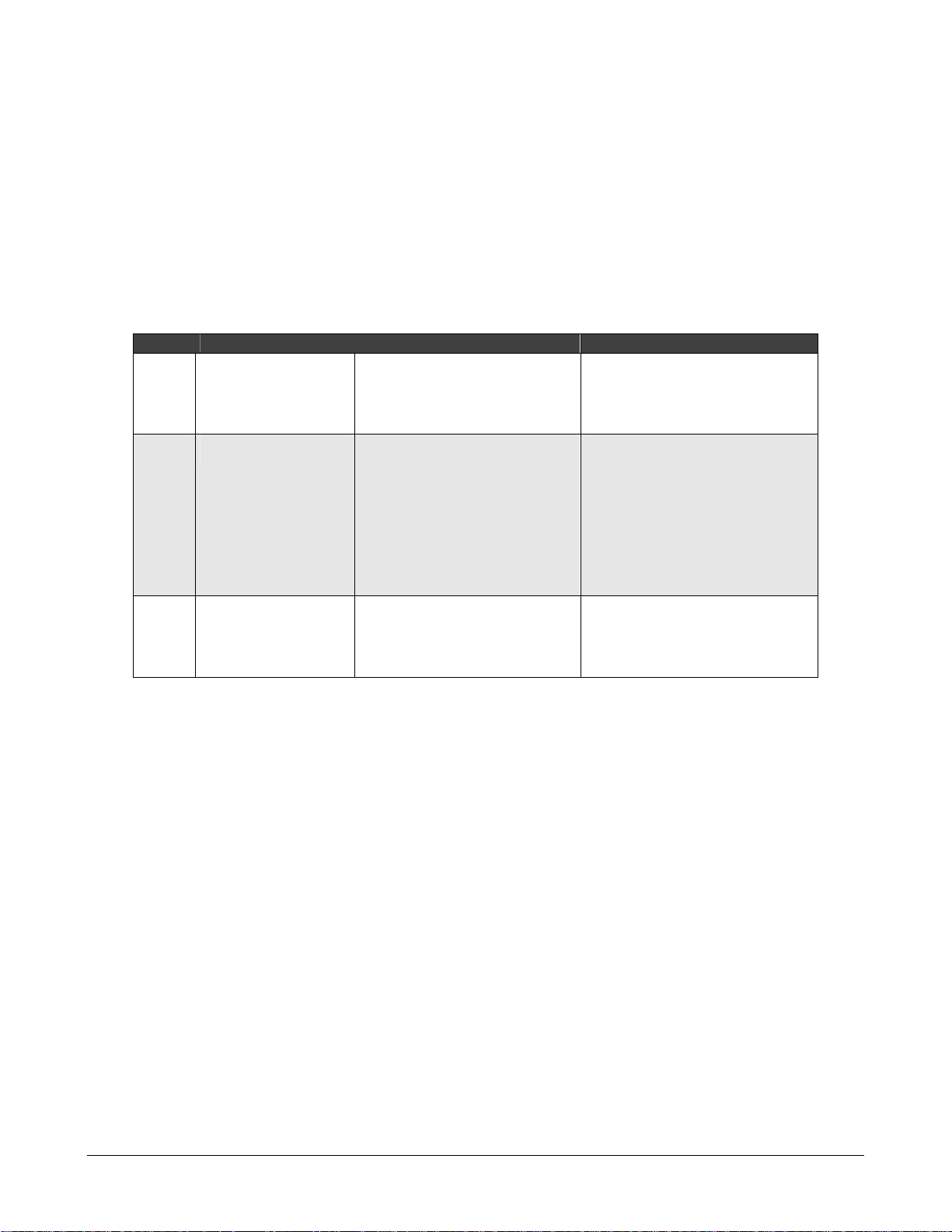

Clock Control Register

The Clock Control register is a Write Only register that contains seven least-significant bits.

These least-significant bits control the frequency:

At which the I

Of the I

The CPU clock frequency (of CLK) is first divided by a factor of 2