Page 1

Embedded &

Industrial Computing

Hardware Platforms for Embedded and Industrial Computing

LEC-7105

Version 1.0

>>

User's Manual

Publication date:2012-01-03

Page 2

About

About

Overview

Icon Descriptions

The icons are used in the manual to serve as an indication

of interest topics or important messages. Below is a

description of these icons:

NOTE: This check mark indicates that

there is a note of interest and is something

that you should pay special attention to

while using the product.

Online Resources

The listed websites are links to the on-line product

information and technical support.

Resource Website

Lanner http://www.lannerinc.com

Product Resources http://assist.lannerinc.com

WARNING: This exclamation point

indicates that there is a caution or

warning and it is something that could

damage your property or product.

Acknowledgement

Intel, Pentium and Celeron are registered trademarks of

Intel Corp.

Microsoft Windows and MS-DOS are registered trademarks

of Microsoft Corp.

All other product names or trademarks are properties of

their respective owners.

Compliances and Certification

CE Certication

This product has passed the CE test for environmental

specifications. Test conditions for passing included the

equipment being operated within an industrial enclosure.

In order to protect the product from being damaged by

ESD (Electrostatic Discharge) and EMI leakage, we strongly

recommend the use of CE-compliant industrial enclosure

products.

FCC Class A Certication

This equipment has been tested and found to comply

with the limits for a Class A digital device, pursuant to Part

15 of the FCC Rules. These limits are designed to provide

reasonable protection against harmful interference when

the equipment is operated in a commercial environment.

This equipment generates, uses and can radiate radio

frequency energy and, if not installed and used in

accordance with the instruction manual, may cause

harmful interference to radio communications. Operation

of this equipment in a residential area is likely to cause

harmful interference in which case the user will be required

to correct the interference at his own expense.

RMA http://eRMA.lannerinc.com

Copyright and Trademarks

This document is copyrighted, © 2011. All rights are

reserved. The original manufacturer reserves the right to

make improvements to the products described in this

manual at any time without notice.

No part of this manual may be reproduced, copied,

translated or transmitted in any form or by any means

without the prior written permission of the original

manufacturer. Information provided in this manual is

intended to be accurate and reliable. However, the original

manufacturer assumes no responsibility for its use, nor for

any infringements upon the rights of third parties that

may result from such use.

Embedded and Industrial Computing

2

Page 3

TTaTTable of Contentsbeable of Contents

Chapter 1: Introduction 4

System Specication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Package Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Chapter 2: System Components 6

System Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Front Components. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Rear Components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Chapter 3: Board Layout 10

External Connectors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Internal Connectors and Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Connectors and Jumpers List. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Jumper Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Chapter 4: Hardware Setup 18

Preparing the Hardware Installation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

Installing the System Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

Installing the Hard Disk . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

Installing a CompactFlash Card. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

3G SIM Card Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Wireless 3G module Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Wall Mounting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Appendix A: Programming Watchdog Timer 21

Appendix B: Digital Input/Output Control on the GPIO port 30

Appendix C: Terms and Conditions 36

Warranty Policy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

RMA Service . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

3

Page 4

Chapter 1

Introduction

Chapter 1: Introduction

Thank you for choosing the LEC-7105. The LEC-7105 is

Lanner’s flagship IPC. It features the Dual Core Intel®

Atom™ D525 processor that has 1.8GHz of processing

power.

The LEC-7105 is an ideal solution for digital signage and

public infortainment. All electronics are protected in a

compact sealed aluminum case as a stand-alone unit and

can be easily situated in a place where space is limited and

the weather condition is diverse.

A solid sealed Aluminum extrusion framing provides

vibration and dust resistance while providing a passive

cooling solution. It also provides great protection from

EMI and shock.

Here is the list of the key features:

Intel integrated Graphics Media Accelerator 3150 •

which supports VGA (up to 2048x1536) and DVI-D

(1920 x1080)

Dual 10/100/1000 Mbps LAN (support WOL (Wake-on- •

LAN) and Remote-wake-up)

Two • Mini-PCIe expansion slots (One Mini-PCIe comes

with a SIM card reader that can support 3G Internet

and the other Mini-PCIe can support Wi-Fi or Bluetooth

connection)

One power eSATA (5V external SATA) which also •

supports USB connectivity. The Power eSATA solution

incorporates the eSATA connector with power source

together, allowing you to use external SATA devices

without the need of additional power source. It

provides storage for photos, videos and other multimedia contents.

USB x 4, COM x 2 (COM1 is RS-232 and COM2 is RS- •

232/422/485 selectable, and Digital Input/Output

(through 2 x 5-pin terminal block)

Audio output for L/R channels with RCA connectors ( •

Realtek ALC888S codec)

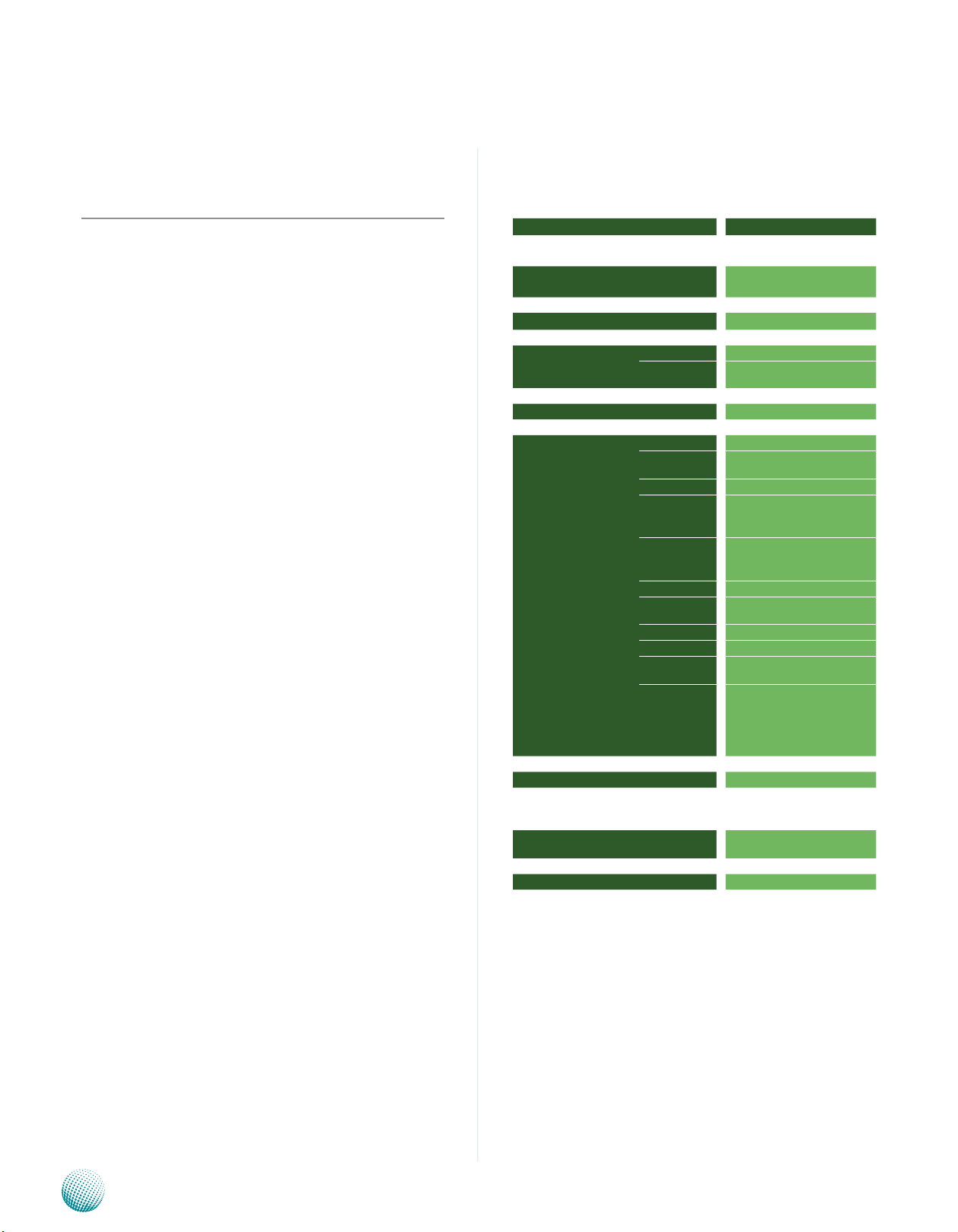

System Specification

LEC 7 Series

Dimension (WxHxD)

Processor

Chipset

System

Memory

Storage

Ethernet Controller

Graphic Controller

Audio Controller

IO

Power Input

AC Adapter

Hardware Monitor

OS Support

Certications

Compliance

Operating Temperature Range

with

Commercial Components

Technology DDR3 SODIMM x1

Max. Capacity Up to 4GB

IDE CF socket Type I/II x1

SATA 2.5” HDD/SSD drive bay x1

LAN GbE RJ45 x2

Display

Video Grabber No

Audio

Serial I/O

GPS No

Digital I/O

USB 2.0 Type A x4; Internal x2

Power Input DC jack with lock

Expansion

Others

LEC-7105

268x44x174mm

(10.55”x1.73”x6.85”)

Intel Atom D525 1.8GHz

Intel ICH8M

Realtek RTL8111 x2

Intel GMA3150

Realtek ALC888S

DB15 x1 for VGA, DVI-D

( up to1920x1080)

RCA x2 for right/left Line-out

channels, Internal pin header for

Line-out, Line-in and Mic-in

DB9 x2 for RS232 x1;

RS232/422/485 x1

2 x 5-pin terminal block for DI x4

and DO x4 (5V TTL)

Mini-PCIe x2 (one with SIM card

reader)

External: Power-on button,

Power-on switch, 3x SMA

antenna hole, reset.

Internal: PS/2 keyboard and

mouse, +5Vdc output

+12Vdc +/- 5%, ATX mode

60W +12V @ 5A

Winbond W83627UHG integrated watchdog timer 1~255

level

Linux , XPE/WES2009, XP PRO

FES, WS7E, WS7P, WIN 7 PRO-E

CE, FCC Class A

No

-5~45°C/23~113°F

Embedded and Industrial Computing

4

Page 5

Chapter 1

Package Contents

Your package contains the following items:

LEC-7105 Embedded System •

DC+12V 60W Power Adapter (080W240318306, US •

type)

Serial-ATA/Power Cable (P/N: 080W1N2201001) •

Wall-Mounting Kit (P/N: SE • 9ESA900R100)

Drivers and User’s Manual CD •

Introduction

Embedded and Industrial Computing

5

Page 6

Chapter 2

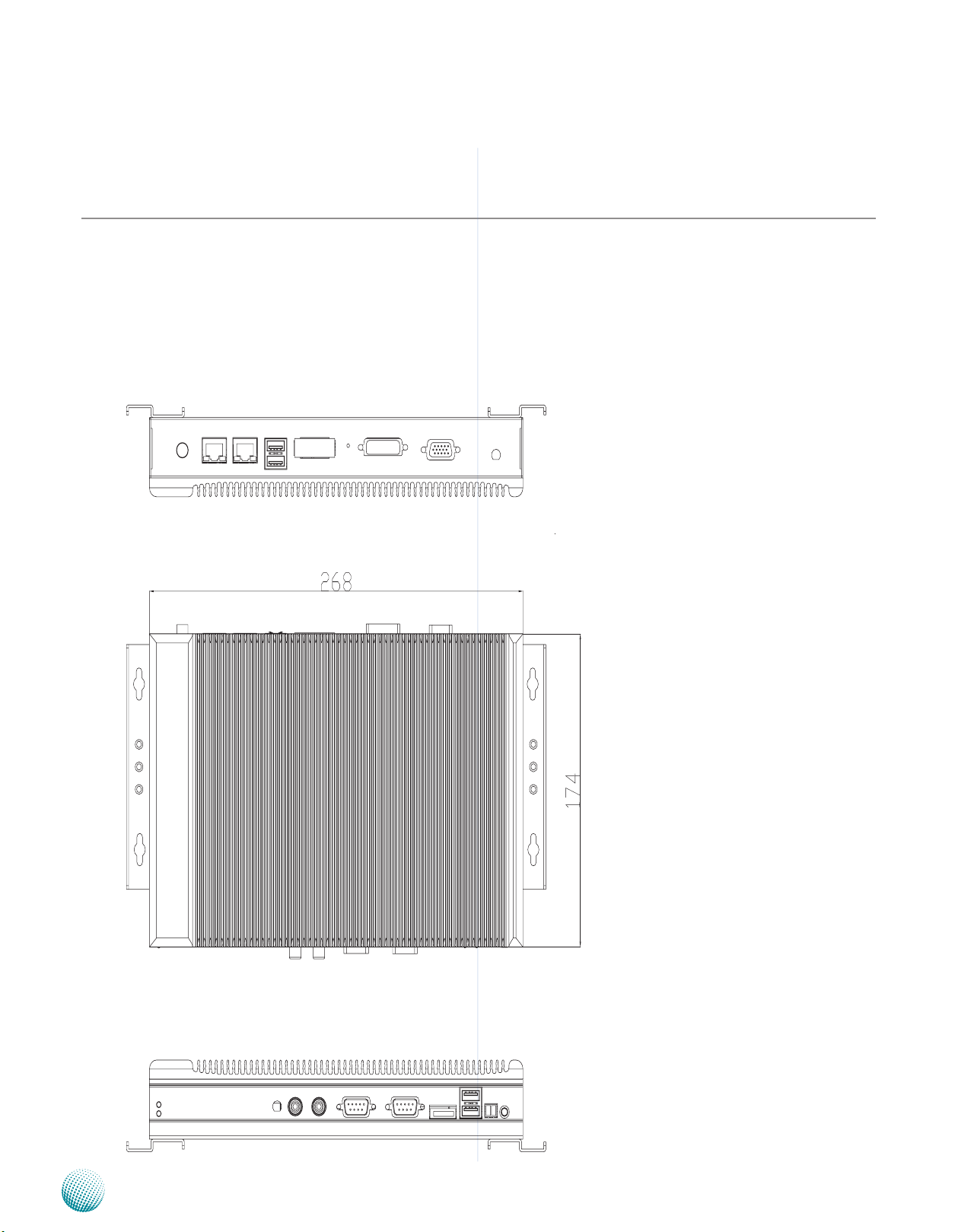

Chapter 2: System Components

System Drawing

Mechanical dimensions of the LEC-7105

Unit: mm

System Components

Embedded and Industrial Computing

6

Page 7

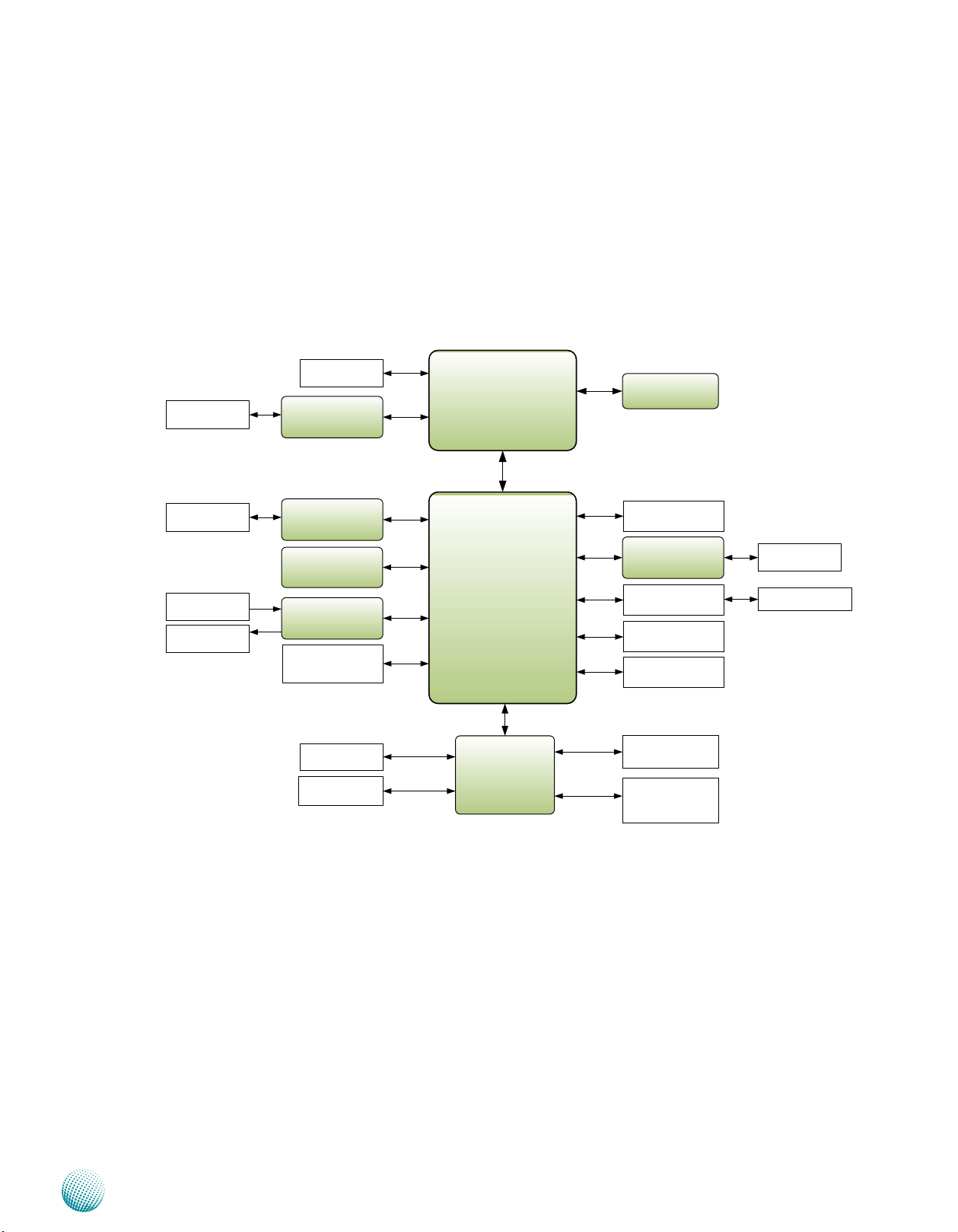

Chapter 2

Intel

ICH8M

Processor

ATOM D525

Winbond

W83627UHG

H/W Monitor

WDT

Digital IO

Terminal Block

PS/2 KB/MS

Pin Header

SATA

VGA

GbE LAN

2x RTL8111

2x PCIe

IDE

DDR3

SO-DIMM

Mini PCI Express

Socket

PCIe

USB

SIM Card Reader

Serial Port

RS232

RS232/422/485

2x DB-9

2x RJ-45

SATA-II

2x Connector

Compact Flash

Socket

LPC

BIOS Flash

SPI

VGA

DMI

USB

USB 2.0 Ports

4x Type A

1x Pin Header

LVDS to DVI

Encoder

CH7036

LVDS

DVI

PCIe to SATA

Controller

JMB362

PCIe

USB

Power

eSATA

Mini PCI Express

Socket (Support mSATA)

PCIe

SATA

HD Audio

Reaktek ALC888S

HD

MIC/Line In

Aduio/Line Out

Block Diagram

The block diagram depicts the relationships among the

interfaces and modules on the motherboard..

System Components

Embedded and Industrial Computing

7

Page 8

Chapter 2

Front Components

System Components

F1

Component Description Pin Definition Reference

F1 HDD (Yellow) and

Power LED (Green)

F2 Antenna Hole Reserved for antenna

F3 Line_Out_R

Line_Out_L

F4 Serial Ports 1 and 2 Serial ports through the DB-9

F5 Power eSATA An external SATA connector with

F6 Dual USB Stack Connector An USB type A connector; in addition to

F7 Power-on Switch A power-on switch through the

F8 Power Button with dual LED ATX Power-on button with LEDs:

F2

HDD

Power

RCA Jack for audio output left and

right

connector; COM1 supports RS-232

and COM2 supports RS-232/422/485

with switch selection among RS232/422/485.

5V power supply and support hot

plugging. It also supports USB 2.0

connection.

this connector, an internal pin header is

provided.

Phoenix contact for distant power-on/

off control

Standby mode in Red; Power-on mode

in Green

F3

Blinking: data access activities•

Off: no data access activities•

On: The computer is on.•

Off: The computer is off .•

F4

F5

F6

CN1, CN2 on page 17

COM1, COM2 on page 14

EUSB1 on page 14

Dual USB Port Connectors

(USB1, USB2) on Page16

J12 on page 16

F7

F8

Embedded and Industrial Computing

8

Page 9

Chapter 2

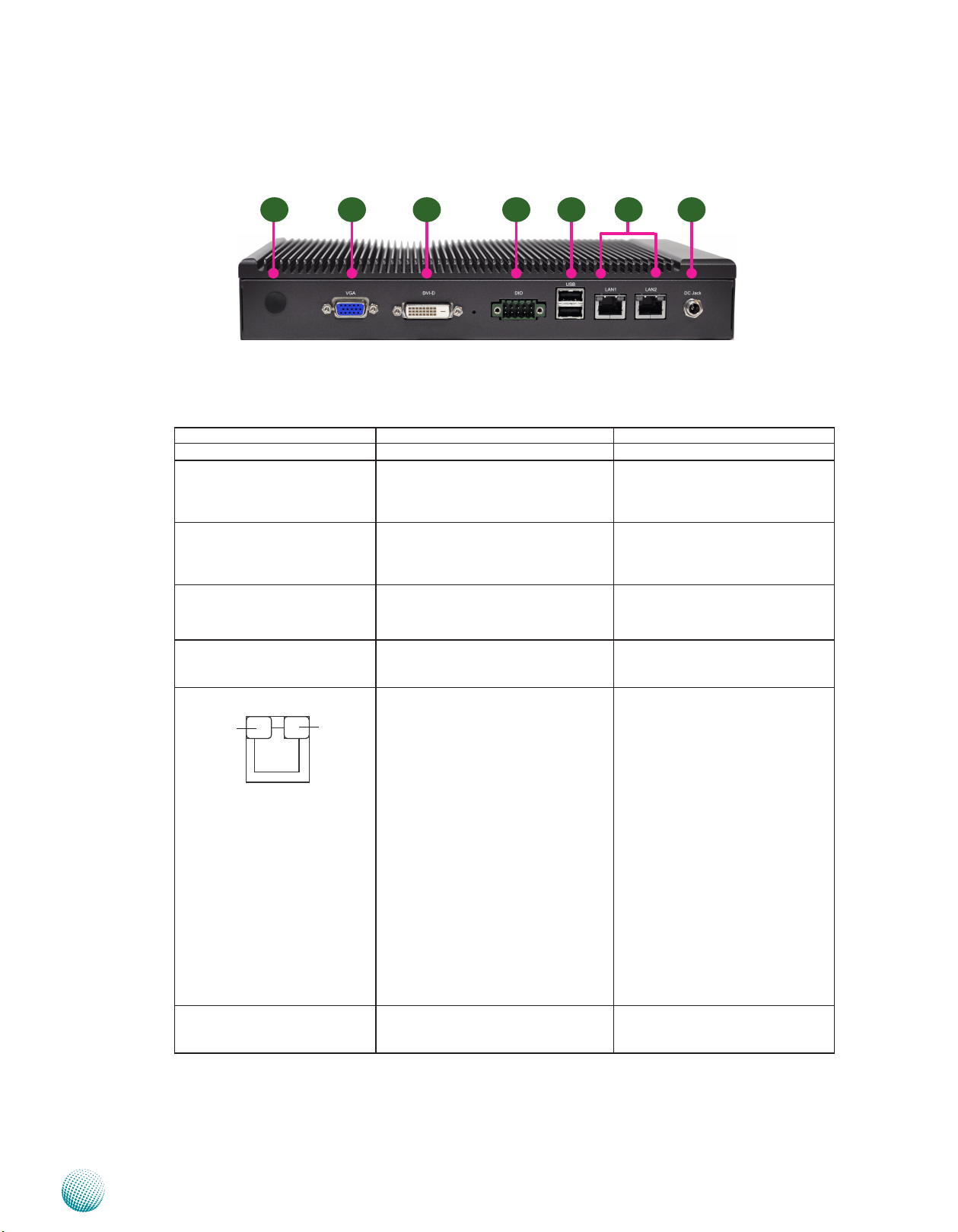

Rear Components

R1 Antenna Hole Reserved for antenna

R2 VGA Port DB-15 Female Connector for VGA

System Components

R1 R2 R3 R4 R5 R6 R7

Component Description Pin Definition Reference

VGA1 on page 17

connection (up to 2048x1536)

R3 DVI-D DVI-D port (single link) is provided

by Intel GMA 3150 through the

Chrontel’s CH7036 LVDS to DVI

converter.

R4 DIO Port 4 digital input and 4 output ports

to support input and output

operations.

R5 Dual USB Stack Connector An USB type A connector; in

addition to this connector, an

internal pin header is provided.

R6 Dual 10/100/1000 LAN

Ports

LINK/ACT

R7 DC Jack DC-in 12V power socket with

SPEED

Two RJ-45 (network) jacks with LED

indicators as described below. The

LAN ports are provided by Realtek

RTL8111. They both support WOL

(Wake-on-LAN) and Remote-wakeup.

LINK/ACT (Yellow)

On/Flashing: The port is linking •

and active in data transmission.

Off: The port is not linking.•

SPEED (Green/Amber)

Amber: The connection speed is •

1000Mbps.

Green: The connection speed is •

100Mbps

Off: .The connection speed is •

10Mbps.

Lock. Only use the power adapter

supplied with the LEC-7105 System.

DVI1 Connector on page 17

DIO1 on page 15

Dual USB Port Connectors (USB1,

USB2) on Page 16

LAN Ports (LAN1/LAN2) on page

15

Embedded and Industrial Computing

9

Page 10

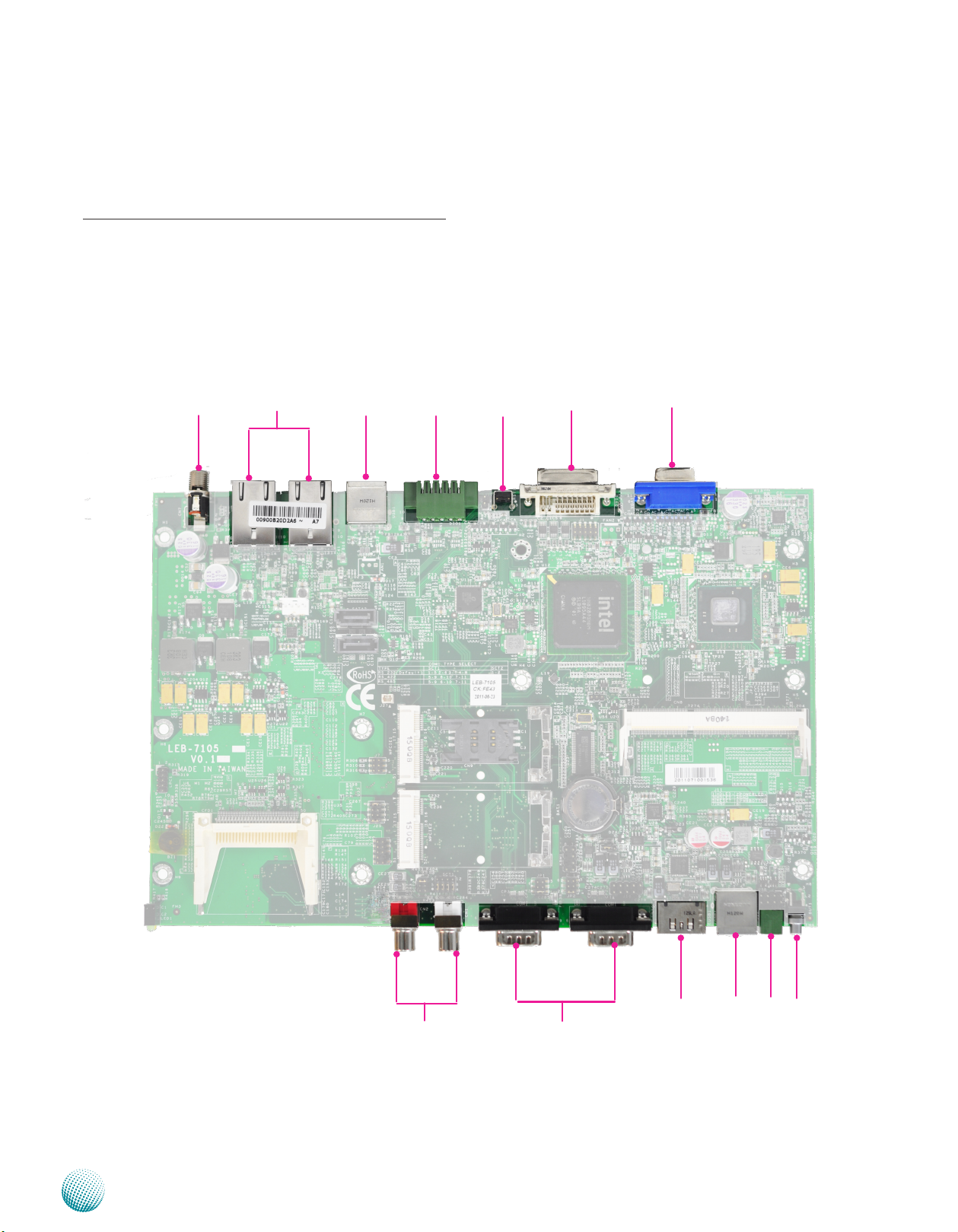

Chapter 3

Chapter 3: Board Layout

External Connectors

The following picture highlights the location of system

input/output connectors. Refer to the table 3.1 Connector

List for more details.

Board Layout

CN7

LAN1/LAN2

USB1

DIO1

RST1

DVI1

VGA1

Embedded and Industrial Computing

CN2/CN1

COM2/COM1

EUSB1

USB2

J12

BUT1

10

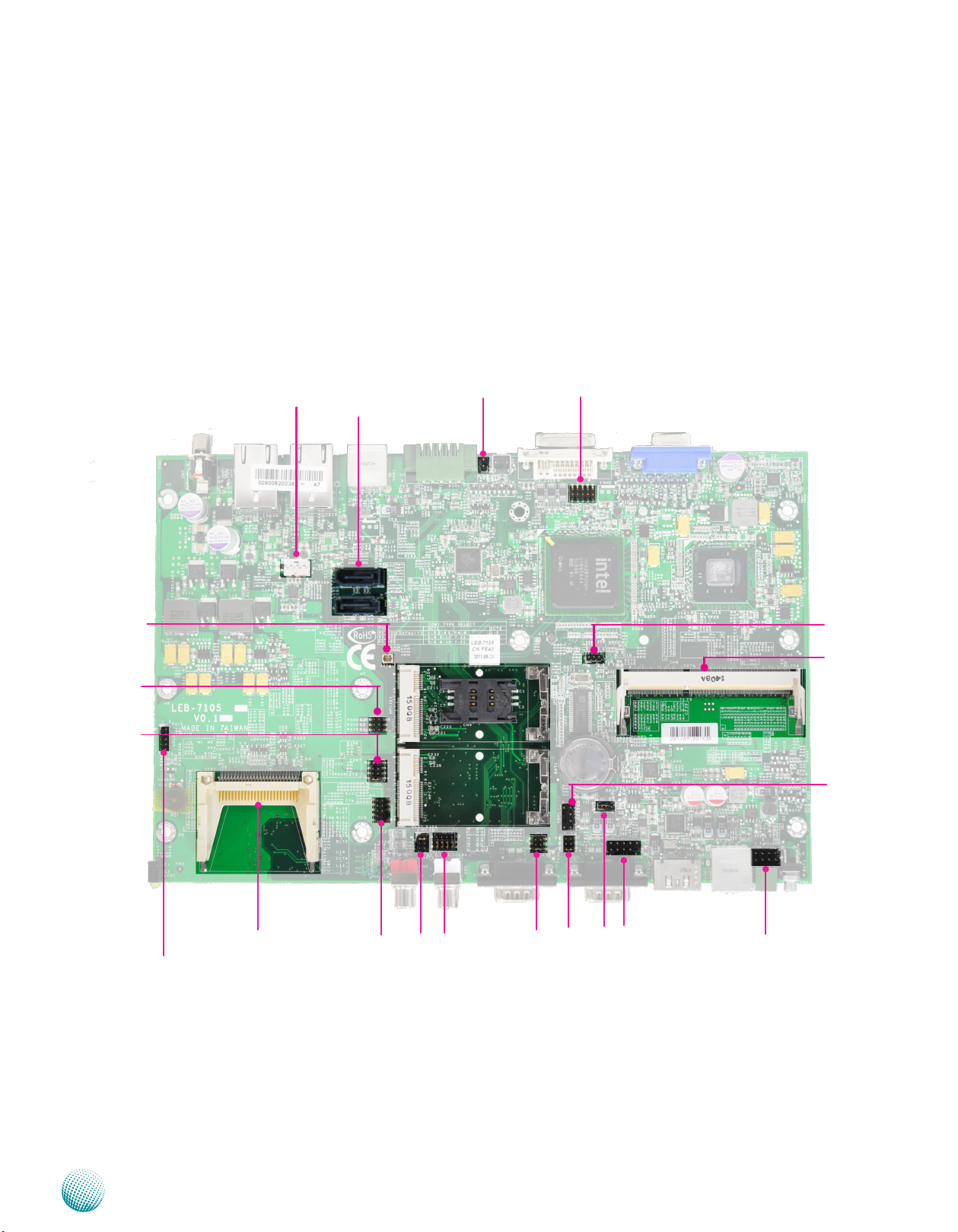

Page 11

Chapter 3

Internal Connectors and Jumpers

The following picture highlights the location of internal

connectors and jumpers. Refer to the table 3.1 Connector

List for more details.

Board Layout

J27

J7

J25

J3

SATA2

SATA1

J13

J1

J6

CN8

KBM1

CFD1

LPC1

Embedded and Industrial Computing

JP3

JP2

SCT1

SCT2

J2

JP1

J10

J11

LEB-7105

11

Page 12

Chapter 3

Board Layout

Connectors and Jumpers List

The tables below list the function of each of the board

jumpers and connectors by labels shown in the above

section. The next section in this chapter gives pin

definitions and instructions on setting jumpers.

Table 3.1 Connector List for LEB-7105

Labels Function Pin Denition Reference

Page

CFD1 CompactFlash P15

CN1 & CN2 Lineout Left/Right P17

COM1 RS-232 Port P14

COM2 RS-232/422/485 Port P14

DIO1 Digital Input/Output P15

DVI1 DVI-D Connector P17

EUSB1 Power eSATA Port P14

J1 SPI ROM Header Reserved for Factory

J10 USB Pin Header P16

J11 Miscellaneous Front Panel Pins P16

J12 External Power Switch P16

J13 SYSTEM Thermal Sensor P17

J2 Line In/Out and MIC Pin Header P17

J25 Mini-PCIe Power Voltage Selection P17

J27 Power for Passive Antenna P18

J3 SATA Power P14

J6 ICH8M Chipset SMB Signals Reserved for Factory

J7 LAN and WLAN LED (Only on MPCIE1) P17

JP1 & JP2 Select COM1/COM2 Pin9 Function Jumper Settings P14

JP3 Clean CMOS P15

KBM1 PS/2 Keyboard and Mouse P17

LAN1/LAN2 Ports LAN1, LAN2 ports P15

LPC1 Low Pin Count Bus for Debug Purpose Reserved for Factory

MPCIE1 Mini-PCIe Slot (with SIM Card Reader) P16

MPCIE2 Mini-PCIe Slot P16

SATA1 Serial-ATA Connector 1 P14

SATA2 Serial-ATA Connector 2 P14

SCT1/SCT2 Seclect COM2 Protocol Jumper settings P14

USB1 Dual USB Port P16

USB2 Dual USB Port P16

VGA DB-15 VGA Port P17

Embedded and Industrial Computing

12

Page 13

Chapter 3

Board Layout

Jumper Settings

LEB-7105

Serial-ATA Connector (SATA1, SATA2): It is for connecting

a 2.5’’ harddisk to be served as your system’s storage. It

can support SATA II which features Data transfer rates up

to 3.0 Gb/s (300 MB/s).

Pin No. Function

1 2 3 4 5 6 7

4-pin Serial-ATA Power Connector (J3): It is for

connecting the SATA power cord.

4 3 2 1

Power eSATA Port (5V, EUSB1): A Power external SATA

port supports hot plugging of SATA II disc. It was provided

by the PCIe to SATA controller: JMB362 which connects

to the ICH8M through the PCIe interface. It can support

USB2.0 as well as eSATA transmission.

Pin No. Function Pin No. Function

S7 S6 S5 S4 S3 S2 S1

1 GND

2 TX0_+

3 TX0_4 GND

5 RX0_6 RX0_+

7 GND

Pin No. Function

1 +5V

2 GND

3 GND

4 +12V

1 GND 1 +5V

2 TX1_+ 2 USB8+

3 TX1_- 3 USB84 GND 4 GND

5 RX1_6 RX1_+

7 VCC5

RS-232/422/485 Serial Port(COM2): It is a RS-232/422/485

port through the D-SUB9 connector.

Pin No. Pin Name

1 DCD TxD- Data2 RXD TxD+ Data+

3 TXD RxD4 DTR RxD+

5 GND

6 DSR

7 RTS

8 CTS

9 RI

RS-232 RS-422 RS-485

SCT1, SCT2: Select COM2 Protocol Setting

SCT2

1

3

5

2

4

6

SCT1

9

5

1

12

8

4

RS-232

RS-422

RS-485

RS-232 Serial Port (COM1): It is a RS-232 port through

the D-SUB9 connector.

12345

6789

Pin No. Pin Name Pin No. Pin Name

1 DCD 6 DSR

2 RXD 7 RTS

3 TXD 8 CTS

4 DTR 9 RIA

5 GND

Embedded and Industrial Computing

COM1 TYPE SCT2 SCT1

RS-232 (Default) 1-2 1-5, 2-6, 3-7, 4-8

RS-422 3-4 5-9, 6-10, 7-11, 8-12

RS-485 5-6 5-9,6-10,7-11,8-12

JP1, JP2: Select COM1 and COM2 power : The Pin No.

9 of RS-232 can be altered to supply power. JP1 and JP2

are used to select the power voltage for COM1 and COM2

respectively.

RS-232 Pin 9 Function JP1, JP2

6

4

2

+5V 1-2

+12V 3-4

RI (Default) 5-6

5

3

1

13

Page 14

Chapter 3

25 1

50 26

Board Layout

CompactFlash Connector (CFD1): It is for connecting a

Compact Flash card to be served as your system’s storage.

Pin No. Function Pin No. Function

Pin Signal Pin Signal

1 GND 26 CD1#

2 PDD3 27 PDD11

3 PDD4 28 PDD12

4 PDD5 29 PDD13

5 PDD6 30 PDD14

6 PDD7 31 PDD15

7 PDCS1_N 32 PDCS3_N

8 GND 33 N/A

9 GND 34 PDIOR_N

10 GND 35 PDIOW_N

11 GND 36 WE#

12 1GND 37 IRQ14

13 VCC5 38 VCC5

14 GND 39 CSEL#

15 GND 40 N/A

16 GND 41 PRST

17 GND 42 PDIORDY

18 PDA2 43 PDDREQ

19 PDA1 44 PDDACK

20 PDA0 45 PDACTIVE

21 PDD0 46 PATADET

22 PDD1 47 PDD8

23 PDD2 48 PDD9

24 IOCS16# 49 PDD10

25 CD2# 50 GND

Clear CMOS jumper (JP3): It is for clearing the CMOS

memory.

1

2

3

Pin No. Pin Name

1-2 Normal (Default)

2-3 Clear CMOS

Digital I/O (DIO1)

Digital IN/OUT(DIO1) Connector: The 8 pins of digital

Input/Output (GPIO) support input and output operations

through the 2x5-pin terminal block.

TTL Level is +5V; Maximum input/output current for

each port is 20mA

Input/Output Voltage Logic Register

0~2V Low 0

2~5V High 1

The output default value is 0

DIO Address LDN8

Address Description

0x2e SUPERIO_INDEX

0x2f SUPERIO_DATA

0x07 BANK_REG

0xE6 (Bit 3) GPO63

0: Low 1: High

0xE6 (Bit 2) GPO62

0: Low 1: High

0xE6 (Bit 1) GPO61

0: Low 1: High

0xE6 (Bit 0) GPO60

0: Low 1: High

LAN1/LAN2 Ports (LAN1/LAN2): The LAN ports are

provided by Realtek RTL8111E Ethernet Controllers. The

following lists its main features:

Pin No. Description

1 TX+ BI_DA+

2 TX- BI_DA3 RX+ BI_DB+

4 -- BI_DC+

5 -- BI_DC6 RX- BI_DB7 -- BI_DD+

8 -- BI_DD-

Wake-on-LAN and remote wake-up support•

Microsoft NDIS5, NDIS6 Checksum Offload (IPv4, IPv6, •

TCP, UDP) and Segmentation Task-offload (Large send

v1 and Large send v2) support

Supports IEEE 802.1P Layer 2 Priority Encoding•

Supports IEEE 802.1Q VLAN tagging•

Fast Ethernet Gigabit Ethernet

Embedded and Industrial Computing

DIO Address LDN9

Address Description

0x2e SUPERIO_INDEX

0x2f SUPERIO_DATA

0x07 BANK_REG

0xE6 (Bit 3) GPI24

0: Low 1: High

0xE6 (Bit 2) GPI25

0: Low 1: High

0xE6 (Bit 1) GPI26

0: Low 1: High

0xE6 (Bit 0) GPI27

0: Low 1:High

1 3 5 7 9

2 4 6 8 10

Pin No. Pin Name

1 Input0

3 Input1

5 Input2

7 Input3

9 GND

Pin No. Pin Name

2 Output0

4 Output1

6 Output2

8 Output3

10 GND

14

Page 15

Chapter 3

Board Layout

Dual USB Port Connector #0 and #1 (USB1):

Dual USB Port Connector #2 and #3 (USB2)

Pin No. Pin Name

1 +5V

5 6 7 8

1 2 3 4

2 USBD13 USBD1+

4 GND

5 +5V

6 USBD07 USBD0+

8 GND

USB 2.0 Pin Header (J10, USB#4 and #5):

2 4 6 8 10

1 3 5 7 9

Pin No. Pin Name

1 +5V

3 USBD45 USBD4+

7 Ground

Pin No. Pin Name

2 +5V

4 USBD56 USBD5+

8 Ground

10 NC

External Power Button (J12): The external power button

is provided for distant power-on control.

Mini PCI Express Connector 1(MPCIE1):

PIN Pin Name PIN Pin Name

1 WAKE# 2 VCC3.3

3 N/A 4 GND

5 N/A 6 VCC1.5

7 CLKREQ# 8 VREG_USIM

9 GND 10 UIM_DATA

11 CLK_PCIE_MINI_N1 12 UIM_CLK

13 CLK_PCIE_MINI_P1 14 UIM_RESET

15 GND 16 UIM_VPP

17 RSV 18 GND

19 RSV 20 RF_KILL_N1

21 GND 22 PLTRST

23 PCIE_RX_N2 24 PCIE1_P24

25 PCIE_RX_P2 26 GND

27 GND 28 VCC1.5

29 GND 30 SMBCLK

31 PCIE_TX_N2 32 SMBDATA

33 PCIE_TX_P2 34 GND

35 GND 36 USB_N6

37 GND 38 USB_P6

39 VCC3.3 40 GND

41 VCC3.3 42 LED1_WWAN

43 GND 44 LED1_WLAN

45 RSV 46 LED1_WPAN

47 RSV 48 VCC1.5

49 RSV 50 GND

51 RSV 52 VCC3.3

PIN NO. DESCRIPTION

1 2

1 PWR_BTN_N

2 GND

Front Panel Function Pin Header (J11): It provides

redundant LED signal and button function on the front

panel.

7 5 3 1

8 6 4 2

Pin No. Pin Name Function Pin No. Pin Name Function

1 POWER_LED HDD LED 2 PWR_LED+ Power LED

3 HD_LED 4 GND

5 Reset System Reset

7 GND 8 GND

Button

6 POWER_BTN- Power On/Off

Push Button

Mini PCI Express Connector 2 (MPCIE2)

PIN Pin Name PIN Pin Name

1 WAKE# 2 VCC3.3

3 N/A 4 GND

5 N/A 6 VCC1.5

7 CLKREQ# 8 N/A

9 GND 10 N/A

11 CLK_PCIE_MINI_N2 12 N/A

13 CLK_PCIE_MINI_P2 14 N/A

15 GND 16 N/A

17 RSV 18 GND

19 RSV 20 RF_KILL_N2

21 GND 22 PLTRST

23 PCIE_RX_N4 24 PCIE2_P24

25 PCIE_RX_P4 26 GND

27 GND 28 VCC1.5

29 GND 30 SMBCLK

31 PCIE_TX_N4 32 SMBDATA

33 PCIE_TX_P4 34 GND

35 GND 36 USB_N7

37 GND 38 USB_P7

39 VCC3.3 40 GND

41 VCC3.3 42 N/A

43 GND 44 N/A

45 RSV 46 N/A

47 RSV 48 VCC1.5

49 RSV 50 GND

51 RSV 52 VCC3.3

Embedded and Industrial Computing

15

Page 16

Chapter 3

Board Layout

Mini PCI Express (MPCIE1/MPCIE2) Power Setting in

Pin 24 (J25):

7

8

5

6

3

4

1

2

Connector Description J25

MPCIE1 +3.3V Standby (miniPCIe 1.2) 1-2

MPCIE1 +3.3V Default (miniPCIe 1.0) 5-6

MPCIE2 +3.3V Standby (miniPCIe 1.2) 3-4

MPCIE2 +3.3V Default (miniPCIe 1.0) 7-8

Line Out Left/Right (CN1/CN2)

Pin No. Description Pin No. Description

1 GND 1 GND

2 FRONT_OUT_L 2 FRONT_OUT_R

CN1 CN2

Line In/Out and MIC Pin Header (J2)

2

1

4

3

6

5

8

7

10

9

Pin No. Description Pin No. Description

1 LINE_OUT2_R 2 LINE_PUT2_L

3 GND 4 GND

5 MIC_R 6 MIC_L

7 LINE_IN_R 8 N/A

9 LINE_IN_L 10 GND

SYSTEM Thermal Sensor ( J13)

2

1

Pin No. Description

1 SYS_TIN

2 GND

DVI-D Connector (DVI1): A single link DVI-D connector

Pin No. Description Pin No. Description

1 TXD_2- 9 TXD_12 TXD_2+ 10 TXD_1+

3 GND 11 GND

4 N/A 12 N/A

5 N/A 13 N/A

6 DDC_CLK 14 VCC5

7 DDC_DATA 15 GND

8 16 HPD

Pin No. Description Pin No. Description

17 TXD_0- C1

18 TXD_0+ C2

19 GND C3

20 NC C4

21 NC C5 GND

22 GND C6 GND

23 TXD_CLK_P

24 TXD_CLK_N

DB-15 VGA Connector (VGA1)

5

10

15

Pin No. Description Pin No. Description

1 RED 6 CRT DET

2 GREEN 7 GND

3 BLUE 8 GND

4 N/A 9 VCC5

5 GND 10 GND

Pin No. Description

11 N/A

12 DDC DAT

13 HSYNC

14 VSYNC

15 DDC CLK

1

6

11

PS/2 Keyboard and Mouse (KBM1)

7

8

5

6

3

4

1

2

Pin No. Description Pin No. Description

1 +5V 2 MCLK

3 MDATA 4 NC

5 KDATA 6 NC

7 GND 8 KCLK

Embedded and Industrial Computing

LAN and WLAN LED (Only on MPCIE1, J7)

5

6

3

4

1

2

Pin No. Description Pin No. Description

1 LED1_WWAN 2 +3.3V

3 LED1_WLAN 4 +3.3V

5 LED1_WPAN 6 +3.3V

16

Page 17

Chapter 3

Power for Passive Antenna (J27)

1 2

Pin No. Description

1 +3.3V

2 GND

Board Layout

Embedded and Industrial Computing

17

Page 18

Chapter 4

Introduction

Chapter 4: Hardware Setup

Preparing the Hardware Installation

To access some components and perform certain service

procedures, you must perform the following procedures

first.

WARNING: To reduce the risk of personal injury,

electric shock, or damage to the equipment,

remove the power cord to remove power from the

server. The front panel Power On/Standby button

does not completely shut off system power.

Portions of the power supply and some internal

circuitry remain active until AC power is removed.

Unpower the LEC-7105 and remove the power cord.1.

Unscrew the 3 threaded screws on both sides of the 2.

top cover of the LEC-7105 System.

Slide the cover backwards and open the cover 3.

Note:

The motherboards can support up to 4 GB 1.

memory capacity in maximum.

Installing the Hard Disk

The system can accomdate two Serial-ATA disks. Follow

these steps to install a hard disk into the LEC-7105:

Unsrew the 4 screws on the hard disk tray to take out 1.

the hard disk tray from the system.

Place hard disk on the hard disk tray and align the holes 2.

of the hard disk with the mounting holes on the tray.

Secure the hard disk with 4 mounting screws on the 3.

hard disk tray.

Connect the Serial-ATA power and datacables to the 4.

hard disk’s connectors respectively.

Plug the Serial-ATA cable to the Serial-ATA Connector 5.

on the main board.

Put the hard disk tray with the installed hard disk back 6.

to the system and secure it with the mounting screws.

upwards.

Installing the System Memory

The motherboard supports DDR3 memory. It comes with

one Double Data Rate (DDR3) Small Outline Dual Inline

Memory Modules (SO-DIMM) sockets.

Open the SO-DIMM slot latches.1.

Install the SO-DIMM.2.

1

2

Embedded and Industrial Computing

18

Page 19

Chapter 4

Introduction

Installing a CompactFlash Card

LEC-7105 provides one CompactFlash slot. To install the

CF card, Follow these procedures bellow for installing a

CompactFlash card.

In order to insert the CF card, you will have to take off 1.

the front panel first. To take off the front panel, unscrew

the 2 screws on the front panel and the hex-shaped

screws of the COM ports.

Align CompactFlash card and the card slot with the 2.

arrow pointing toward the connector.

Push the card to insert into the connector.3.

1

3G SIM Card Installation

Open the SIM tray and flip it diagnolly.1.

Align the cut corner of the SIM card with the SIM card 2.

socket. Make sure the ICs is in contact with the reader.

Insert the 3. SIM card into the tray diagonally. Close and

lock the tray.

Wireless 3G module Installation

Align the wireless module’s cutout with the Mini-PCIe 1.

slot notch.

Insert the wireless module into the connector 2.

diagnoally.

Push the other end of the wireless module to be 3.

tightened with the latch.

3

3G module

1

3

2

2

2

SIM Card

Note:

To remove the module from the system, release 1.

the latch first by slightly bending it inward.

To remove the SIM card, unlock the tray first by 2.

sliding it outward.

lock

Embedded and Industrial Computing

Unlock

19

Page 20

Chapter 4

Wall Mounting

The product ships with wall mounting kit. To mount your

product on the wall, follow the instructions below:

First make a hole for the anchor in the surface on the 1.

wall.

Then press the anchor into the hole until it is flush with 2.

the surface. You may need a hammer to tap the wall

anchor.

Use a screwdriver to screw the threaded screw into the 3.

plastic anchor.

Attach the wall mounting bracket to the back of the 4.

device, securing it in place with four of the flat-head

screws provided.

Hang the device on the wall.5.

Introduction

Unit: mm

Embedded and Industrial Computing

20

Page 21

Appendix A

Programming Watchdog Timer

Appendix A: Programming Watchdog Timer

A watchdog timer is a piece of hardware that can be used

to automatically detect system anomalies and reset the

system (or one pair of network ports in bypassed state;

However, only one function can be activated at a time.)

in case there are any problems. Generally speaking, a

watchdog timer is based on a counter that counts down

from an initial value to zero. The software selects the

counter’s initial value and periodically restarts it. Should

the counter reach zero before the software restarts it,

the software is presumed to be malfunctioning and the

processor’s reset signal is asserted. Thus, the processor

will be restarted as if a human operator had cycled the

power.

For sample watchdog code, see wd_bp folder under Driver

and Utility on the Driver and Manual CD

Set the access mode with these two parameters 2.

by editing the Makefile.linux directly: DIRECT_IO_

ACCESS= [0|1] (enter either 1 or 0) and LANNER_

DRIVER= [0|1] (enter either 1 or 0). 1 is for direct access

and no driver is needed. You will only need to execute

the program directly. However, when it equaled to 0,

driver installation is needed. Refer to the following

Install section for more details.

Type make to build source code:3.

make Makefile (Note: omit the file extensions)

After compiled, the executable program (bpwd_tst) and

the driver (bpwd_drv.ko) will be in the bin subdirectory.

Install

The installation procedures depend on the access mode

that you have set by using the above mentioned method.

If you have set DIRECT_IO_ACCESS=1, driver installation is

not necessary. Proceed to the next section on executing

If you have set DIRECT_IO_ACCESS=0, Lanner bypass

driver needs to be installed. Install the driver and create

a node in the /dev directory as shown in the following

example:

Executing the commands through the Command Line:

1. wd_tst --swtsr (Set Watchdog Timeout State to Reset)

2. wd_tst --swt xxx (Set Watchdog Timer 1-255 seconds)

3. wd_tst[*] --start (Start Watchdog Timer)

4. wd_tst --stop (Stop Watchdog Timer)

The following procedures are required for running the

watchdog program on DOS, Linux and FreeBSD.

Note:

For DOS environment, use DJGPP as compiler 1.

and the makefile: Makefile.dos.

For Linux, support kernel versions are 2.4.x and 2.

2.6.x. Use the makefile:Makefile.linux.

For FreeBSD, support version is FreeBSD 8.0. 3.

Use the makefile: Makefile.

Build

To build program source code on Linux platform, use the

following steps as a guideline:

For Linux:

Insert module and create node in /dev as below

example:

#insmod wd_drv.[k]o

#mknod /dev/wd_drv c 241 0

For FreeBSD:

Insert module as below example:

#kldload -v ./wd_drv.ko

Execute

# wd_tst --swtsb (Set Watchdog Timeout State to Bypass

function)

# wd_tst --swtsr (Set Watchdog Timeout State to Reset

function)

# wd_tst --swt xxx (Set Watchdog Timer 1-255 seconds)

# wd_tst[*] --start (Start Watchdog Timer)

# wd_tst --stop (Stop Watchdog Timer)

Copy the proper makefile from the Driver and Manual 1.

CD to your system

Embedded and Industrial Computing

Note:

wd_tst --start will not be available if 1.

21

Page 22

Appendix A

Programming Watchdog Timer

DIRECT_IO_ACCESS=1, use the command: “./

wd_tst --swt xxx” to start the watchdog timer

instead .

Watchdog timer can support two functions, 2.

- system rest or LAN bypass. However, only

one function can be activated at a time. You

should modify the code or switch it to the

desired state/function accordingly.

For more details, refer to the README file 3.

contained within the program.

A sample Watchdog program in C:

*********************************************************

**********************/

#include “../include/config.h”

#ifdef DJGPP

/* standard include file */

#include <stdio.h>

#include <stdlib.h>

#include <unistd.h>

/* For DOS DJGPP */

#include <dos.h>

#if defined(FreeBSD_ENV)

#include <machine/cpufunc.h>

#endif

#include <time.h>

#include <stdint.h>

#include <fcntl.h>

#include <errno.h>

#include <string.h>

#define delay(x) usleep(x)

#endif

#ifdef MODULE

#include <linux/kernel.h>

#include <linux/module.h>

#include <linux/kernel.h>

#include <linux/fs.h>

#include <asm/io.h>

#include <linux/delay.h>

#include <inlines/pc.h>

#else //DJGPP

/* For Linux */

#ifdef DIRECT_IO_ACCESS

/* For Linux direct io access code */

/* standard include file */

#include <stdio.h>

#include <stdlib.h>

#include <unistd.h>

#if defined(LINUX_ENV)

#include <sys/io.h>

#endif

Embedded and Industrial Computing

#undef delay

#define delay(x) mdelay(x)

#undef fprintf

#define fprintf(S, A) printk(A)

#endif //MODULE

#ifdef KLD_MODULE

#include <sys/types.h>

#include <sys/param.h>

#include <sys/systm.h>

#include <sys/malloc.h>

#include <sys/kernel.h>

#include <sys/bus.h>

22

Page 23

Appendix A

Programming Watchdog Timer

#include <sys/errno.h>

#include <machine/bus.h>

#include <machine/resource.h>

#endif

#endif

/* local include file */

#include “../include/ioaccess.h”

#if (defined(MODULE) || defined(DIRECT_IO_ACCESS) ||

defined(KLD_MODULE))

/*

* Platform Depend GPIOs Interface for Watchdog and Lan

bypass

*/

/*

*---------------------------------------------------------------------------

---

* LEB-7105 Version V1.0

*

* LEB-7105 embedded with HW Watchdog timer functions.

* Set Lan bypass Enable/Disable while System-off:

* ======================================

=========

* It is able to set Lan bypass enable/disable in system off

mode by SW program.

* The IO interface for off-mode bypass is connected to

Winbond SIO 83627UHG

* GPO22,GPO23(Pair1), GPO30,GPO31(Pair2),

* Refer to Winbond 83527 datasheet for details.

*

* The truth table of function is defined as below:

*

* Pair Bypass function GPIO Pin

* ---------------------------------------------------

* 1 Enable G P O 2 2 = 1

GPO23=0

* 1 Disable G P O 2 2 = 0

GPO23=1

* 2 Enable G P O 3 0 = 1

GPO31=0

* 2 Disable G P O 3 0 = 0

GPO31=1

*

* Runtime:

* ========

* It is able to set Lan bypass enable/disable alone, or design

hybrid with

* watchdog timeout(WDTO#).

* The IO interface for this function is conjunction with

Winbond 83627

* GPO24 (Pair1), GPO60(Pair2) and WDTO#.

* Refer to Winbond 83627 datasheet for details.

* The truth table is defined as below:

*

* Below setting is to determine system behavior while

watchdog timer expired.

*

* GPO27 System behavior

* ------------------------------------------------

* 0 Lan-bypass while watchdog timeout

* 1 System Reset while watchdog timeout

*

* Below setting is to determine lan bypass in runtime mode

*

* Pair Bypass function GPIO Pin

* -----------------------------------------------------------

* 1 Enable GPO24 =1

* 1 Disable GPO24 =0

* 2 Enable GPO60 =1

* 2 Disable GPO60 =0

*

* Note: To sete runtime bypass mode, user need to set

off-mode bypass

* enabled in order to let function activity.

*

Embedded and Industrial Computing

23

Page 24

Appendix A

Programming Watchdog Timer

*---------------------------------------------------------------------------

---

*---------------------------------------------------------------------------

---

*/

/*

* Device Depend Definition : Winbond 83627UHG

*/

#define INDEX_PORT 0x2E

#define DATA_PORT 0x2F

#define SIO_GPIO_22_BIT 0x04

#define SIO_GPIO_23_BIT 0x08

#define SIO_GPIO_24_BIT 0x10

#define SIO_GPIO_27_BIT 0x80

#define SIO_GPIO_30_BIT 0x01

#define SIO_GPIO_31_BIT 0x02

#define SIO_GPIO_60_BIT 0x01

{

unsigned char tmp = 0;

enter_w83627_config();

outportb(INDEX_PORT, 0x07); // LDN Register

outportb(DATA_PORT, LDN); // Select LDNx

outportb(INDEX_PORT, reg); // Select Register

tmp = inportb( DATA_PORT ); // Read Register

exit_w83627_config();

return tmp;

}

void write_w83627_reg(int LDN, int reg, int value)

{

enter_w83627_config();

outportb(INDEX_PORT, 0x07); // LDN Register

outportb(DATA_PORT, LDN); // Select LDNx

outportb(INDEX_PORT, reg); // Select Register

outportb(DATA_PORT, value); // Write Register

exit_w83627_config();

void enter_w83627_config(void)

{

outportb(INDEX_PORT, 0x87); // Must Do It Twice

outportb(INDEX_PORT, 0x87);

return;

}

void exit_w83627_config(void)

{

outportb(INDEX_PORT, 0xAA);

return;

}

unsigned char read_w83627_reg(int LDN, int reg)

return;

}

/*Runtime bypass definitions */

#define RUNTIME_BYPASS_PAIR1_LDN (9)

#define RUNTIME_BYPASS_PAIR1_REG (0xe5)

#define RUNTIME_BYPASS_PAIR1_BIT ( S I O _

GPIO_24_BIT)

#define RUNTIME_BYPASS_PAIR1_ENABLE (0)

#define RUNTIME_BYPASS_PAIR1_DISABLE ( S I O _

GPIO_24_BIT)

#define RUNTIME_BYPASS_PAIR2_LDN (8)

#define RUNTIME_BYPASS_PAIR2_REG (0xe5)

#define RUNTIME_BYPASS_PAIR2_BIT ( S I O _

GPIO_60_BIT)

Embedded and Industrial Computing

24

Page 25

Appendix A

Programming Watchdog Timer

#define RUNTIME_BYPASS_PAIR2_ENABLE (0)

#define RUNTIME_BYPASS_PAIR2_DISABLE ( S I O _

GPIO_60_BIT)

/*Offmode bypass definitions */

#define OFFMODE_BYPASS_PAIR1_LDN (9)

#define OFFMODE_BYPASS_PAIR1_REG (0xe5)

#define OFFMODE_BYPASS_PAIR1_BIT ( S I O _

GPIO_22_BIT | SIO_GPIO_23_BIT)

#define OFFMODE_BYPASS_PAIR1_ENABLE S I O _

GPIO_22_BIT

#define OFFMODE_BYPASS_PAIR1_DISABLE S I O _

GPIO_23_BIT

#define OFFMODE_BYPASS_PAIR2_LDN (7)

#define OFFMODE_BYPASS_PAIR2_REG (0xe1)

#define OFFMODE_BYPASS_PAIR2_BIT ( S I O _

GPIO_30_BIT | SIO_GPIO_31_BIT)

#define OFFMODE_BYPASS_PAIR2_ENABLE S I O _

GPIO_30_BIT

#define OFFMODE_BYPASS_PAIR2_DISABLE S I O _

GPIO_31_BIT

/* set WDT Reset Event */

tmp=read_w83627_reg(0x08, 0xF7);

tmp = (0x00);

write_w83627_reg(0x08, 0xF7, tmp);

/* Set function enable */

write_w83627_reg(0x08, 0x30, 1);

/* fill in timeout value */

write_w83627_reg(0x08, 0xf6, watchdog_time);

return;

}

void stop_watchdog_timer(void)

{

/* stop timer */

write_w83627_reg(0x08, 0xf6, 0);

}

void start_watchdog_timer(int watchdog_time)

{

unsigned char tmp;

/* clear timeout value */

write_w83627_reg(0x08, 0xf6, 0x00);

/* set to count with second */

tmp=read_w83627_reg(0x08, 0xF5);

tmp &= ~(0x08);

write_w83627_reg(0x08, 0xF5, tmp);

/* clear status bit */

tmp=read_w83627_reg(0x08, 0xf7);

tmp &= ~(0x10);

write_w83627_reg(0x08, 0xf7, tmp);

Embedded and Industrial Computing

int wd_gpio_init(void)

{

unsigned char tmp;

int ret=0;

/* Set W83627 multiplex pin to WDTO function */

tmp=read_w83627_reg(0x00, 0x2b);

tmp &= ~(0x0c);

tmp |= 0x04;

write_w83627_reg(0x00, 0x2b, tmp);

/* clear timeout value */

write_w83627_reg(0x08, 0xf6, 0x00);

/* Enable LDN8 watchdog function */

tmp=read_w83627_reg(0x08, 0x30);

tmp |= 1;

25

Page 26

Appendix A

write_w83627_reg(0x08, 0x30, tmp);

Programming Watchdog Timer

int reg_no, ldn_no;

/* active GPIO2 group */

tmp=read_w83627_reg(0x09, 0x30);

tmp |= 2;

write_w83627_reg(0x09, 0x30, tmp);

/* Set GPIO22, 23, 24 and 27 to output mode */

tmp=read_w83627_reg(0x09, 0xe4);

tmp &= ~(SIO_GPIO_22_BIT+SIO_GPIO_23_

BIT+SIO_GPIO_24_BIT+SIO_GPIO_27_BIT) ;

write_w83627_reg(0x09, 0xe4, tmp);

/* active GPIO3 group */

tmp=read_w83627_reg(0x07, 0x30);

tmp |= 1;

write_w83627_reg(0x07, 0x30, tmp);

/* Set GPIO30 and 31 to output mode */

tmp=read_w83627_reg(0x07, 0xe0);

tmp &= ~(SIO_GPIO_30_BIT + SIO_GPIO_31_BIT) ;

write_w83627_reg(0x07, 0xe0, tmp);

/* active GPIO6 group */

tmp=read_w83627_reg(0x08, 0x30);

tmp |= 0x4;

write_w83627_reg(0x08, 0x30, tmp);

unsigned char bit_mask;

unsigned char en_data;

unsigned char tmp;

reg_no=ldn_no=bit_mask=en_data=tmp=0;

switch(pair_no) {

case BYPASS_PAIR_1:

ldn_no = OFFMODE_BYPASS_

PAIR1_LDN;

reg_no = OFFMODE_BYPASS_

PAIR1_REG;

bit_mask = OFFMODE_BYPASS_

PAIR1_BIT;

en_data = OFFMODE_BYPASS_

PAIR1_ENABLE;

break;

case BYPASS_PAIR_2:

ldn_no = OFFMODE_BYPASS_

PAIR2_LDN;

reg_no = OFFMODE_BYPASS_

PAIR2_REG;

bit_mask = OFFMODE_BYPASS_

PAIR2_BIT;

en_data = OFFMODE_BYPASS_

PAIR2_ENABLE;

break;

default:

/*un-support pair no, return */

/* Set GPIO60 to output mode */

tmp=read_w83627_reg(0x08, 0xe4);

tmp &= ~(SIO_GPIO_60_BIT) ;

write_w83627_reg(0x08, 0xe4, tmp);

return ret;

}

void set_bypass_enable_when_system_off(unsigned long

pair_no)

{

Embedded and Industrial Computing

return;

}

tmp=read_w83627_reg(ldn_no, reg_no);

tmp &= ~(bit_mask) ;

tmp |= en_data;

write_w83627_reg(ldn_no, reg_no, tmp);

return;

}

26

Page 27

Appendix A

Programming Watchdog Timer

void set_bypass_disable_when_system_off(unsigned long

pair_no)

{

int reg_no, ldn_no;

unsigned char bit_mask;

unsigned char en_data;

unsigned char tmp;

reg_no=ldn_no=bit_mask=en_data=tmp=0;

switch(pair_no) {

case BYPASS_PAIR_1:

ldn_no = OFFMODE_BYPASS_

PAIR1_LDN;

reg_no = OFFMODE_BYPASS_

PAIR1_REG;

bit_mask = OFFMODE_BYPASS_

PAIR1_BIT;

en_data = OFFMODE_BYPASS_

PAIR1_DISABLE;

break;

case BYPASS_PAIR_2:

ldn_no = OFFMODE_BYPASS_

PAIR2_LDN;

reg_no = OFFMODE_BYPASS_

PAIR2_REG;

bit_mask = OFFMODE_BYPASS_

PAIR2_BIT;

en_data = OFFMODE_BYPASS_

PAIR2_DISABLE;

break;

default:

/*un-support pair no, return */

return;

}

tmp=read_w83627_reg(ldn_no, reg_no);

}

void set_runtime_bypass_enable(unsigned long pair_no)

{

int reg_no, ldn_no;

unsigned char tmp, bit_mask, en_data;

reg_no=ldn_no=bit_mask=en_data=tmp=0;

/* Note: To sete runtime bypass mode, user need to set offmode bypass

* enabled in order to let function activity.

*/

set_bypass_enable_when_system_off(pair_no);

switch(pair_no) {

case BYPASS_PAIR_1:

ldn_no = RUNTIME_BYPASS_

PAIR1_LDN;

reg_no = RUNTIME_BYPASS_

PAIR1_REG;

bit_mask = RUNTIME_BYPASS_PAIR1_BIT;

en_data = RUNTIME_BYPASS_PAIR1_ENABLE;

break;

case BYPASS_PAIR_2:

ldn_no = RUNTIME_BYPASS_

PAIR2_LDN;

reg_no = RUNTIME_BYPASS_

PAIR2_REG;

bit_mask = RUNTIME_BYPASS_PAIR2_BIT;

en_data = RUNTIME_BYPASS_PAIR2_ENABLE;

break;

default:

/*un-support pair no, return */

return;

tmp &= ~(bit_mask) ;

tmp |= en_data;

write_w83627_reg(ldn_no, reg_no, tmp);

return;

Embedded and Industrial Computing

}

tmp=read_w83627_reg(ldn_no, reg_no);

tmp &= ~(bit_mask) ;

tmp |= en_data;

write_w83627_reg(ldn_no, reg_no, tmp);

27

Page 28

Appendix A

Programming Watchdog Timer

return;

}

void set_runtime_bypass_disable(unsigned long pair_no)

{

int reg_no, ldn_no;

unsigned char tmp, bit_mask, en_data;

reg_no=ldn_no=tmp=bit_mask=en_data=0;

switch(pair_no) {

case BYPASS_PAIR_1:

ldn_no = RUNTIME_BYPASS_PAIR1_LDN;

reg_no = RUNTIME_BYPASS_PAIR1_REG;

bit_mask = RUNTIME_BYPASS_PAIR1_BIT;

en_data = RUNTIME_BYPASS_PAIR1_

DISABLE;

break;

case BYPASS_PAIR_2:

/* set GPIO27=1 for reset mode */

tmp=read_w83627_reg(0x9, 0xe5);

tmp |= SIO_GPIO_27_BIT;

write_w83627_reg(0x9, 0xe5, tmp);

return;

}

void set_wdto_state_system_bypass(void)

{

unsigned char tmp;

/* set GPIO27=0 for bypass mode */

tmp=read_w83627_reg(0x9, 0xe5);

tmp &= ~SIO_GPIO_27_BIT;

write_w83627_reg(0x9, 0xe5, tmp);

return;

}

ldn_no = RUNTIME_BYPASS_PAIR2_LDN;

reg_no = RUNTIME_BYPASS_PAIR2_REG;

bit_mask = RUNTIME_BYPASS_PAIR2_BIT;

en_data = RUNTIME_BYPASS_PAIR2_

DISABLE;

break;

}

tmp=read_w83627_reg(ldn_no, reg_no);

tmp &= ~(bit_mask) ;

tmp |= en_data;

write_w83627_reg(ldn_no, reg_no, tmp);

return;

}

void set_wdto_state_system_reset(void)

{

#endif

int main (int argc, char* argv[])

{

try

{

int num = sizeof (id2fun) / sizeof (id2fun[0])

; //Total function number

//No parameter. Print the help message

if (argc < 2)

RETMSG (-1, PARAMETER_HELP) ;

//Find and call the coresponding function

for (int i = 0 ; i < num ; i++)

if (stricmp (argv[1], id2fun[i].szID)

== 0)

unsigned char tmp;

Embedded and Industrial Computing

return id2fun[i].function

28

Page 29

Appendix A

(argc, argv) ;

RETMSG (-1, “Unknown function name\n”)

;

}

catch (char *str)

{

printf (“\n%s\n”, str) ;

}

catch (...)

{

printf (“\nUnknown Exception\n”) ;

}

return -1 ;

Programming Watchdog Timer

}

Embedded and Industrial Computing

29

Page 30

Appendix B

Digital Input/Output Control

Appendix B: Digital Input/Output Control on the GPIO port

The Digital I/O port (DIO) is designed to provide the input

and output operations for the system. For sample DIO

code, see DIO folder under Driver and Utility on the Driver

and Manual CD.

Executing the commands through the Command Line:

# dio_tst

The program will drive output pin with specific value and

read status of input pin. If you have external loopback

which connects input to output pins directly, the input

value should be identical with the output value.

Note:

For DOS environment, use DJGPP as compiler 1.

and the makefile: Makefile.dos.

For Linux, support kernel versions are 2.4.x and 2.

2.6.x. Use the makefile:Makefile.linux.

For FreeBSD, support version is FreeBSD 8.0. 3.

use the makefile: Makefile.

Build

To build program source code on Linux platform, use the

following steps as a guideline:

Copy the proper makefile from the Driver and Manual 1.

CD to your system

Set the access mode with these two parameters 2.

by editing the Makefile.linux directly: DIRECT_IO_

ACCESS= [0|1] (enter either 1 or 0) and LANNER_

DRIVER= [0|1] (enter either 1 or 0). 1 is for direct access

and no driver is needed. You will only need to execute

the program directly. However, when it equaled to 0,

driver installation is needed. Refer to the following

Install section for more details.

Type make to build source code:3.

make Makefile (Note: omit the file extensions)

After compiled, the executable program (bpwd_tst) and

the driver (bpwd_drv.ko) will be in the bin subdirecto

Install

The installation procedures depend on the access mode

that you have set by using the above mentioned method.

If you have set DIRECT_IO_ACCESS=1, driver installation is

not necessary. Proceed to the next section on executing

If you have set DIRECT_IO_ACCESS=0, Lanner bypass

driver needs to be installed. Install the driver and create

a node in the /dev directory as shown in the following

example:

For Linux:

Insert module and create node in /dev as below

example:

#insmod dio_drv.[k]o

#mknod /dev/dio_drv c 240 0

For FreeBSD:

Insert module as below example:

#kldload -v ./dio_drv.ko

I/O Address

DIO Address LDN8

Address Description

0x2e SUPERIO_INDEX

0x2f SUPERIO_DATA

0x07 BANK_REG

0xE6 (Bit 3) GPO63

0: Low 1: High

0xE6 (Bit 2) GPO62

0: Low 1: High

0xE6 (Bit 1) GPO61

0: Low 1: High

0xE6 (Bit 0) GPO60

0: Low 1: High

DIO Address LDN9

Address Description

0x2e SUPERIO_INDEX

0x2f SUPERIO_DATA

0x07 BANK_REG

0xE6 (Bit 3) GPI24

0: Low 1: High

0xE6 (Bit 2) GPI25

0: Low 1: High

0xE6 (Bit 1) GPI26

0: Low 1: High

0xE6 (Bit 0) GPI27

0: Low 1:High

Embedded and Industrial Computing

30

Page 31

Appendix B

For example

Setting GPO 60-63 all low.1.

outportb(0x2e, 0x07); LDN8

outportb(0x2f, 0x08);

outportb(0x2e, 0x30); Setting GPIO6.

outportb(0x2f, 0x04);

outportb(0x2e, 0xE4); GP0 60-63

outportb(0x2f, 0x?0); ?:GP0 64-67 Unuse.

outportb(0x2e, 0xE6); GP0 60-63 Uninvert

outportb(0x2f, 0x?0); ?:GP0 64-67 Unuse.

Digital Input/Output Control

Execute

Once build completed, application (and driver) is available

in bin sub-directory.

Just run “dio_tst” for Digital IO test. This program will drive

output pin with specific value and read status of input

pin. If you have external loopback which connects input

to output pins directly, the input value should be identical

with output value.

screen capture of the execution result:

outportb(0x2e, 0xE5); GP0 60-63 1:high

outportb(0x2f, 0x?0); 0:low

Setting GPI 24-27. 2.

outportb(0x2e, 0x07); LDN9

outportb(0x2f, 0x09);

outportb(0x2e, 0x30); Setting GPIO6.

outportb(0x2f, 0x04);

outportb(0x2e, 0xE4); GPI 24-27

outportb(0x2f, 0x?F); ?:GPI 20-23 Unuse.

outportb(0x2e, 0xE6); GPI 24-27 Uninvert

outportb(0x2f, 0x?0); ?:GPI 20-23 Unuse.

Note: For more details, refer to the README file

contained within the program

Embedded and Industrial Computing

31

Page 32

Appendix B

Digital Input/Output Control

A sample DIO program in C:

/********************************************************

***********************

ioaccess.c: IO access code for Lanner Platfomr Digital IO

program

Lanner Platform Miscellaneous Utility

Copyright(c) 2010- 2011 Lanner Electronics Inc.

All rights reserved.

*******/

#include “../include/config.h”

#ifdef DJGPP

#endif

#if defined(FreeBSD_ENV)

#include <machine/cpufunc.h>

#endif

#include <time.h>

#include <stdint.h>

#include <fcntl.h>

#include <errno.h>

#include <string.h>

#define delay(x) usleep(x)

#endif

#ifdef MODULE

/* standard include file */

#include <stdio.h>

#include <stdlib.h>

#include <unistd.h>

/* For DOS DJGPP */

#include <dos.h>

#include <inlines/pc.h>

#else //DJGPP

/* For Linux */

#ifdef DIRECT_IO_ACCESS

/* For Linux direct io access code */

/* standard include file */

#include <stdio.h>

#include <stdlib.h>

#include <linux/kernel.h>

#include <linux/module.h>

#include <linux/kernel.h>

#include <linux/fs.h>

#include <asm/io.h>

#include <linux/delay.h>

#undef delay

#define delay(x) mdelay(x)

#undef fprintf

#define fprintf(S, A) printk(A)

#endif //MODULE

#ifdef KLD_MODULE

#include <unistd.h>

#if defined(LINUX_ENV)

#include <sys/io.h>

Embedded and Industrial Computing

#include <sys/types.h>

#include <sys/param.h>

#include <sys/systm.h>

32

Page 33

Appendix B

Digital Input/Output Control

#include <sys/malloc.h>

#include <sys/kernel.h>

#include <sys/bus.h>

#include <sys/errno.h>

#include <machine/bus.h>

#include <machine/resource.h>

#endif

#endif

/* local include file */

#include “../include/ioaccess.h”

#if (defined(MODULE) || defined(DIRECT_IO_ACCESS) ||

defined(KLD_MODULE))

/*

* Device Depend Definition : Winbond 83627 SIO

*/

#define INDEX_PORT 0x2E

#define DATA_PORT 0x2F

#define GPIO2X 2

#define GPIO24_BIT (1 << 4)

#define GPIO25_BIT (1 << 5)

#define GPIO26_BIT (1 << 6)

#define GPIO27_BIT (1 << 7)

#define GPIO_GPIO24_GPIO27_MASK (GPIO24_BIT |

GPIO25_BIT | GPIO26_BIT | GPIO27_BIT)

#define GPIO6X 4

#define GPIO60_BIT (1 << 0)

#define GPIO61_BIT (1 << 1)

/*

*---------------------------------------------------------------------------

---

* LEB-7105 Version V1.0

*

* The IO interface for Digital DIO is connected to Winbond

SIO 83627.

* Platform provide 4 digital input and 4 digital output.

* GPIO24-27 as input function, GPIO60-63 as output

function

* Refer to Winbond 83627 datasheet for details.

* The truth table is defined as below:

* DIO GPIO pins as follows:

* IN OUT

* DIO GP24 GP60

* DIO GP25 GP61

* DIO GP26 GP62

* DIO GP27 GP63

#define GPIO62_BIT (1 << 2)

#define GPIO63_BIT (1 << 3)

#define GPIO_GPIO60_GPIO63_MASK (GPIO60_BIT |

GPIO61_BIT | GPIO62_BIT | GPIO63_BIT)

void enter_w83627_config(void)

{

outportb(INDEX_PORT, 0x87); // Must Do It Twice

outportb(INDEX_PORT, 0x87);

return;

}

void exit_w83627_config(void)

{

outportb(INDEX_PORT, 0xAA);

return;

}

*---------------------------------------------------------------------------

--------

*/

Embedded and Industrial Computing

unsigned char read_w83627_reg(int LDN, int reg)

{

unsigned char tmp = 0;

33

Page 34

Appendix B

Digital Input/Output Control

write_w83627_reg(0x08, 0xE6, tmp);

enter_w83627_config();

outportb(INDEX_PORT, 0x07); // LDN Register

outportb(DATA_PORT, LDN); // Select LDNx

outportb(INDEX_PORT, reg); // Select Register

tmp = inportb( DATA_PORT); // Read Register

exit_w83627_config();

return tmp;

}

void write_w83627_reg(int LDN, int reg, int value)

{

enter_w83627_config();

outportb(INDEX_PORT, 0x07); // LDN Register

outportb(DATA_PORT, LDN); // Select LDNx

outportb(INDEX_PORT, reg); // Select Register

outportb(DATA_PORT, value); // Write Register

/* set GPIO60~63 generate high signal */

tmp=read_w83627_reg(0x08, 0xE5);

tmp |= GPIO_GPIO60_GPIO63_MASK;

write_w83627_reg(0x08, 0xE5, tmp);

/* Enable GPIO 2x function */

tmp=read_w83627_reg(0x09, 0x30);

tmp |= GPIO2X;

write_w83627_reg(0x09, 0x30, tmp);

/* set GPIO24~27 as Input function */

tmp=read_w83627_reg(0x09, 0xE4);

tmp |= GPIO_GPIO24_GPIO27_MASK;

write_w83627_reg(0x09, 0xE4, tmp);

/* set GPIO24~27 as uninvert */

exit_w83627_config();

return;

}

void dio_gpio_init(void)

{

unsigned char tmp;

/* Enable GPIO 6x function */

tmp=read_w83627_reg(0x08, 0x30);

tmp |= GPIO6X;

write_w83627_reg(0x08, 0x30, tmp);

/* set GPIO60~63 as Output function */

tmp=read_w83627_reg(0x08, 0xE4);

tmp &= ~(GPIO_GPIO60_GPIO63_MASK);

write_w83627_reg(0x08, 0xE4, tmp);

tmp=read_w83627_reg(0x09, 0xE6);

tmp &= ~(GPIO_GPIO24_GPIO27_MASK);

write_w83627_reg(0x09, 0xE6, tmp);

return;

}

void dio_set_output(unsigned char out_value)

{

unsigned char tmp;

tmp = read_w83627_reg(0x08,0xE5);

tmp &= ~GPIO_GPIO60_GPIO63_MASK;

tmp |= out_value;

write_w83627_reg(0x08, 0xE5, tmp);

delay(333);

return;

}

/* set GPIO60~63 as uninvert */

tmp=read_w83627_reg(0x08, 0xE6);

tmp &= ~(GPIO_GPIO60_GPIO63_MASK);

Embedded and Industrial Computing

unsigned char dio_get_input(void)

{

34

Page 35

Appendix B

unsigned char tmp;

tmp=read_w83627_reg(0x09, 0xE5);

tmp &= GPIO_GPIO24_GPIO27_MASK;

return tmp;

}

#endif

Digital Input/Output Control

Embedded and Industrial Computing

35

Page 36

Appendix C

Terms and Conditions

Appendix C: Terms and Conditions

Warranty Policy

All products are under warranty against defects in 1.

materials and workmanship for a period of one year

from the date of purchase.

The buyer will bear the return freight charges for 2.

goods returned for repair within the warranty period;

whereas the manufacturer will bear the after service

freight charges for goods returned to the user.

The buyer will pay for repair (for replaced components 3.

plus service time) and transportation charges (both

ways) for items after the expiration of the warranty

period.

If the RMA Service Request Form does not meet the 4.

stated requirement as listed on “RMA Service,” RMA

goods will be returned at customer’s expense.

The following conditions are excluded from this 5.

warranty:

RMA Service

Requesting a RMA#

To obtain a RMA number, simply fill out and fax the 6.

“RMA Request Form” to your supplier.

The customer is required to fill out the problem code 7.

as listed. If your problem is not among the codes listed,

please write the symptom description in the remarks

box.

Ship the defective unit(s) on freight prepaid terms. 8.

Use the original packing materials when possible.

Mark the RMA# clearly on the box. 9.

Note: Customer is responsible for shipping

damage(s) resulting from inadequate/loose

packing of the defective unit(s). All RMA# are valid

for 30 days only; RMA goods received after the

effective RMA# period will be rejected.

Improper or inadequate maintenance by the customer

Unauthorized modification, misuse, or reversed

engineering of the product Operation outside of the

environmental specifications for the product.

Embedded and Industrial Computing

36

Page 37

Appendix C

RMA Service Request Form

When requesting RMA service, please fill out the following form. Without

this form enclosed, your RMA cannot be processed.

RMA No:

Reasons to Return: Ŀ Repair(Please include failure details)

Ŀ Testing Purpose

Company: Contact Person:

Phone No. Purchased Date:

Fax No.: Applied Date:

Return Shipping Address:

Shipping by: Ŀ Air Freight Ŀ Sea Ŀ Express ___

Ŀ Others:________________

Item Model Name Serial Number Configuration

Item Problem Code Failure Status

*Problem Code:

01:D.O.A.

02: Second Time

R.M.A.

03: CMOS Data Lost

04: FDC Fail

05: HDC Fail

06: Bad Slot

07: BIOS Problem

08: Keyboard Controller Fail

09: Cache RMA Problem

10: Memory Socket Bad

11: Hang Up Software

12: Out Look Damage

13: SCSI

14: LPT Port

15: PS2

16: LAN

17: COM Port

18: Watchdog Timer

19: DIO

20: Buzzer

21: Shut Down

22: Panel Fail

23: CRT Fail

24: Others (Pls specify)

Request Party

Confirmed By Supplier

Authorized Signature / Date Authorized Signature / Date

Terms and Conditions

Embedded and Industrial Computing

37

Loading...

Loading...