Page 1

www.kontron.com

If it's embedded, it's Kontron.

» Kontron User's Guide «

AT8404

Document Revision 1.6

Document ID: AT8404

Issue Date: 16 March, 2010

Page 2

www.kontron.com

Revision History

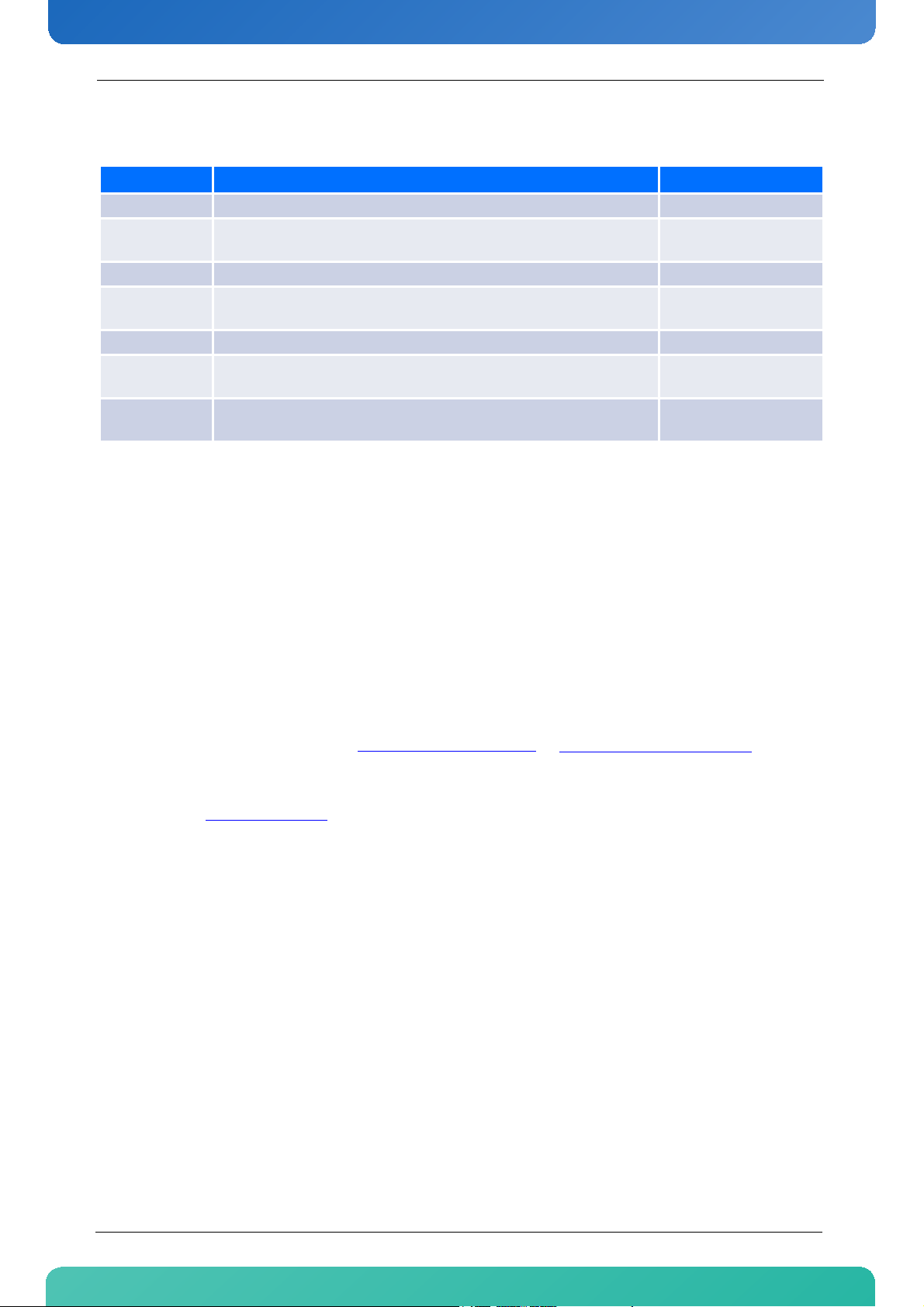

Rev. Index Brief Description of Changes Date of Issue

1.0 Initial Issue 9 January, 2008

1.1

1.2 Added Note in chapter 3.2 2 December, 2008

1.3

1.4 Pre-Release with major Rework in chapter 4 25 September, 2009

1.5

1.6

Rework on chapter 4 ( Software description) and chapter 1.3 (Software

support), add chapter 3.2 (RTM8030)

Rework covering SW update for FASTPATH 5.2 and WindRiver PNE

2.0

New Kontron outfit, chapter 4.5 and 4.6 added, chapter 5 added,

major rework in chapter 4.2 and 4.3

Add chapter for OEM sensors, rework sensor list, rework PLD

update chapter

29 February, 2008

15 May, 2009

03 November, 2009

16 March, 2010

Customer Service

Contact Information: Kontron Canada, Inc.

4555 Ambroise-Lafortune

Boisbriand, Québec, Canada

J7H 0A4

Tel: (450) 437-5682

(800) 354-4223

Fax: (450) 437-8053

E-mail: support@ca.kontron.com

Visit our site at:www.kontron.com

© 2010 Kontron, an International Corporation. All rights reserved.

The information in this user's guide is provided for reference only. Kontron does not assume any liability

arising out of the application or use of the information or products described herein. This user's guide may

contain or reference information and products protected by copyrights or patents and does not convey any

license under the patent rights of Kontron, nor the rights of others.

Kontron is a registered trademark of Kontron. All trademarks, registered trademarks, and trade names used

in this user's guide are the property of their respective owners. All rights reserved. Printed in Canada. This

user's guide contains information proprietary to Kontron. Customers may reprint and use this user's guide

in other publications. Customers may alter this user's guide and publish it only after they remove the Kontron name, cover, and logo.

Kontron Modular Computer GmbH

Sudetenstrasse 7

87600 Kaufbeuren

Germany

+49 (0) 8341 803 333

+49 (0) 8341 803 339

support-kom@kontron.com

Kontron reserves the right to make changes without notice in product or component design as warranted by

evolution in user needs or progress in engineering or manufacturing technology. Changes that affect the

operation of the unit will be documented in the next revision of this user's guide.

ii AT8404 User Guide

Page 3

www.kontron.com

Table of Contents

Revision History .................................................................................................................. ii

Customer Service ................................................................................................................ ii

Proprietary Note ...............................................................................................................viii

Trademarks .................................................................................................................... viii

Environmental Protection Statement ..................................................................................... viii

Explanation of Symbols ........................................................................................................ix

For Your Safety ................................................................................................................... x

General Instructions on Usage ..............................................................................................xii

Two Year Warranty .............................................................................................................xiii

1. Introduction ...................................................................................................2

1.1 Product Overview ................................................................................................... 2

1.1.1 AT8404 Features ............................................................................................. 2

1.1.2 General compliances ........................................................................................ 4

1.1.3 Optional Accessories ........................................................................................ 5

1.1.4 Hot Swap Capability ......................................................................................... 5

1.1.5 Board Options ................................................................................................. 5

1.2 Technical Specification ............................................................................................ 6

1.3 Software Support ................................................................................................... 9

2. Installation .................................................................................................. 12

2.1 Safety Requirements ............................................................................................. 12

2.2 AT8404 Initial Installation Procedures ...................................................................... 13

2.3 Standard Removal Procedures ................................................................................. 14

2.4 AMC Installation .................................................................................................. 14

2.5 Software Installation ............................................................................................ 14

2.6 Quick Start ......................................................................................................... 15

2.6.1 In-Band CLI Access ......................................................................................... 15

2.6.2 Out-of-band CLI Access ................................................................................... 15

2.6.3 Storage Configuration .................................................................................... 17

3. Hardware Description .....................................................................................19

3.1 Base Board ......................................................................................................... 19

3.1.1 Ethernet Switch ............................................................................................. 20

3.1.2 Unit Computer and Memory .............................................................................. 21

3.1.3 Fat Pipe Interconnect ..................................................................................... 23

3.1.4 Storage Interconnect ...................................................................................... 23

3.1.5 Synchronous Clock Distribution ......................................................................... 24

3.1.6 AMC Bays ..................................................................................................... 24

3.1.7 IPMI ........................................................................................................... 28

3.1.8 RTM Interface ............................................................................................... 29

3.1.9 Power Supply ................................................................................................ 32

3.1.10 Jumpers ...................................................................................................... 34

3.1.11 Front Panel Elements ...................................................................................... 36

iii AT8404 User Guide

Page 4

www.kontron.com

3.2 RTM8030 ........................................................................................................... 38

3.2.1 Hot Swap ..................................................................................................... 39

3.2.2 Unit Computer RS232 Management Interface ....................................................... 39

3.2.3 Unit Computer Fast Ethernet Management Interface .............................................. 40

3.2.4 GbE Port ...................................................................................................... 41

3.2.5 SAS Channels ................................................................................................ 42

3.2.6 SAS Hard Drive Option ..................................................................................... 42

3.2.7 Display Elements ........................................................................................... 43

4. Software Description ......................................................................................45

4.1 Supported RFCs, Standards and MIBs ........................................................................ 45

4.1.1 Fastpath Switching ........................................................................................ 45

4.1.2 Fastpath Quality of Service .............................................................................. 47

4.1.3 Fastpath Management .................................................................................... 48

4.2 Bootloader ......................................................................................................... 50

4.2.1 Power on self Test .......................................................................................... 50

4.2.2 Bootloader shell options ................................................................................. 52

4.3 IPMI Firmware ..................................................................................................... 54

4.3.1 Sensor Data Record (SDR) ............................................................................... 54

4.3.2 OEM Commands ............................................................................................ 68

4.3.3 Field Replaceable Unit (FRU) Information ........................................................... 82

4.3.4 E-Keying ...................................................................................................... 82

4.3.5 IPMC Firmware Code ....................................................................................... 83

4.3.6 LEDs ........................................................................................................... 83

4.3.7 Hot Swap Process ........................................................................................... 84

4.4 Firmware Administration ....................................................................................... 85

4.4.1 Updating the Firmware ................................................................................... 86

4.4.2 Updating IPMI FW .......................................................................................... 87

4.4.3 Updating PLD ............................................................................................... 88

4.5 Carrier Clocking ................................................................................................... 90

4.5.1 Clock source to AMC ........................................................................................ 90

4.5.2 Clock source to backplane from any AMCs TCLK-B/D ................................................ 92

4.5.3 Examples ..................................................................................................... 93

4.6 Carrier Configuration ............................................................................................ 95

4.6.1 Switch default settings ................................................................................... 95

4.6.2 Using SNMP .................................................................................................. 99

4.6.3 Using the “current-settings” file ......................................................................102

5. Thermal Considerations ................................................................................. 107

5.1 Thermal Monitoring .............................................................................................107

5.2 Thermal Regulation .............................................................................................108

5.3 Airflow .............................................................................................................109

A Getting Help .................................................................................................A-2

A.1 Returning Defective Merchandise........................................................................... A1- 2

A.2 When Returning a Unit ........................................................................................ A2- 3

B. Glossary ...................................................................................................... B-2

iv AT8404 User Guide

Page 5

www.kontron.com

List of Tables

Table 1-1: AMC Slot Options ................................................................................................. 5

Table 1-2: AT8404 Main Specifications ................................................................................... 6

Table 1-3: AT8404 Software Specifications .............................................................................. 9

Table 3-1: GbE Switch Port Assignment ..................................................................................20

Table 3-2: Fast Ethernet Pins on RTM Connector .......................................................................21

Table 3-3: Serial Port (J11) Pin Assignment ............................................................................22

Table 3-4: RS232 Pins on RTM Connector ................................................................................22

Table 3-5: Fat Pipe Interconnect ..........................................................................................23

Table 3-6: AMC Storage Interconnect .....................................................................................23

Table 3-7: AMC Slot Types ...................................................................................................24

Table 3-8: AMC B1 Port Assignment .......................................................................................24

Table 3-9: AMC B2 Port Assignment .......................................................................................25

Table 3-10: AMC B3 Port Assignment .......................................................................................26

Table 3-11: AMC B4 Port Assignment .......................................................................................27

Table 3-12: Temperature Sensors ...........................................................................................28

Table 3-13: J30 Assignment .................................................................................................30

Table 3-14: J31 Assignment .................................................................................................31

Table 3-15: J32 Assignment .................................................................................................32

Table 3-16: Power Connector (P10) ........................................................................................33

Table 3-17: Power Transients ................................................................................................34

Table 3-18: Jumper Settings ( • Default Setting) ......................................................................35

Table 3-20: ATCA LEDs Signification ........................................................................................37

Table 3-19: Symbols Chart ....................................................................................................37

Table 3-21: Serial Port (RJ45) Pin Assignment ..........................................................................39

Table 3-22: Serial console terminal cable interface: RJ45 Female to DB9 Female ...............................40

Table 3-23: FE Port (RJ45) Pin Assignment ..............................................................................40

Table 3-24: Fast Ethernet Management (RJ45) LEDs Signification .................................................41

Table 3-25: SFP Connectors Pin Assignment ..............................................................................41

Table 4-1: POST routines and error codes ................................................................................50

Table 4-2: POST Boot Steps .................................................................................................51

Table 4-3: Bootloader environment variables ..........................................................................52

Table 4-4: AT8404 sensors ..................................................................................................55

Table 4-5: Kontron FRU info agent sensor ...............................................................................62

Table 4-6: Kontron IPMB-L Link sensor ...................................................................................63

Table 4-7: Kontron POST code value sensor .............................................................................64

Table 4-8: Kontron Switch management status sensor ...............................................................64

Table 4-9: Kontron diagnostic status sensor ............................................................................64

Table 4-10: Kontron external comp. firmw. Upgrd. Status sensor ...................................................64

v AT8404 User Guide

Page 6

www.kontron.com

Table 4-11: Kontron FRU over current sensor .............................................................................65

Table 4-12: Kontron FRU Power Denied sensor ...........................................................................65

Table 4-13: Kontron reset sensor ........................................................................................... 65

Table 4-14: Kontron clock input status sensor ...........................................................................66

Table 4-15: Kontron PLL status ..............................................................................................66

Table 4-16: Current Sensor Thresholds .....................................................................................66

Table 4-17: Voltage Sensor Thresholds ....................................................................................67

Table 4-18: Temperature Sensor Thresholds ..............................................................................67

Table 4-19: Board-specific OEM Command Overview ....................................................................68

Table 4-20: LED state ..........................................................................................................83

Table 4-21: OOS LED state ....................................................................................................83

Table 4-22: Health LED state .................................................................................................84

Table 4-23: FLASH Partition Scheme (128MB) ...........................................................................85

Table 5-1: Temperatur sensor thresholds .............................................................................. 108

vi AT8404 User Guide

Page 7

www.kontron.com

List of Figures

Figure 3-1: Functional Block Diagram Base Board......................................................................... 19

Figure 3-2: Front Panel of AT8404............................................................................................. 36

Figure 3-3: SAS Port Mapping................................................................................................... 42

Figure 3-4: Front Panel of the RTM8030...................................................................................... 43

Figure 4-1: AMC TCLKA sourced by PLL ........................................................................................ 90

Figure 4-2: AMC TCLKA sourced by AMC TCLKB ............................................................................... 91

Figure 4-3: AMC TCLKA sourced by backplane ............................................................................... 91

Figure 4-4: Clock source from AMC to backplane ........................................................................... 92

Figure 4-5: Clock ekeying ........................................................................................................93

Figure 5-1: Temperature Sensor Locations (AT8404 Top View) ........................................................107

Figure 5-2: Configuration A - Airflow Measurement.......................................................................109

Figure 5-3: Configuration B - Airflow Measurement ......................................................................110

vii AT8404 User Guide

Page 8

Preface

www.kontron.com

Proprietary Note

This document contains information proprietary to Kontron AG. It may not be copied or transmitted by any

means, disclosed to others, or stored in any retrieval system or media without the prior written consent of

Kontron AG or one of its authorized agents.

The information contained in this document is, to the best of our knowledge, entirely correct. However, Kontron AG cannot accept liability for any inaccuracies or the consequences thereof, or for any liability arising

from the use or application of any circuit, product, or example shown in this document.

Kontron AG reserves the right to change, modify, or improve this document or the product described herein,

as seen fit by Kontron AG without further notice.

Trademarks

Kontron AG and the Kontron logo are trade marks owned by Kontron AG, Germany. In addition, this document may include names, company logos and trademarks, which are registered trademarks and, therefore,

proprietary to their respective owners.

Environmental Protection Statement

This product has been manufactured to satisfy environmental protection requirements where possible. Many

of the components used (structural parts, printed circuit boards, connectors, batteries, etc.) are capable of

being recycled.

Final disposition of this product after its service life must be accomplished in accordance with applicable

country, state, or local laws or regulations.

viii AT8404 User Guide

Page 9

www.kontron.com

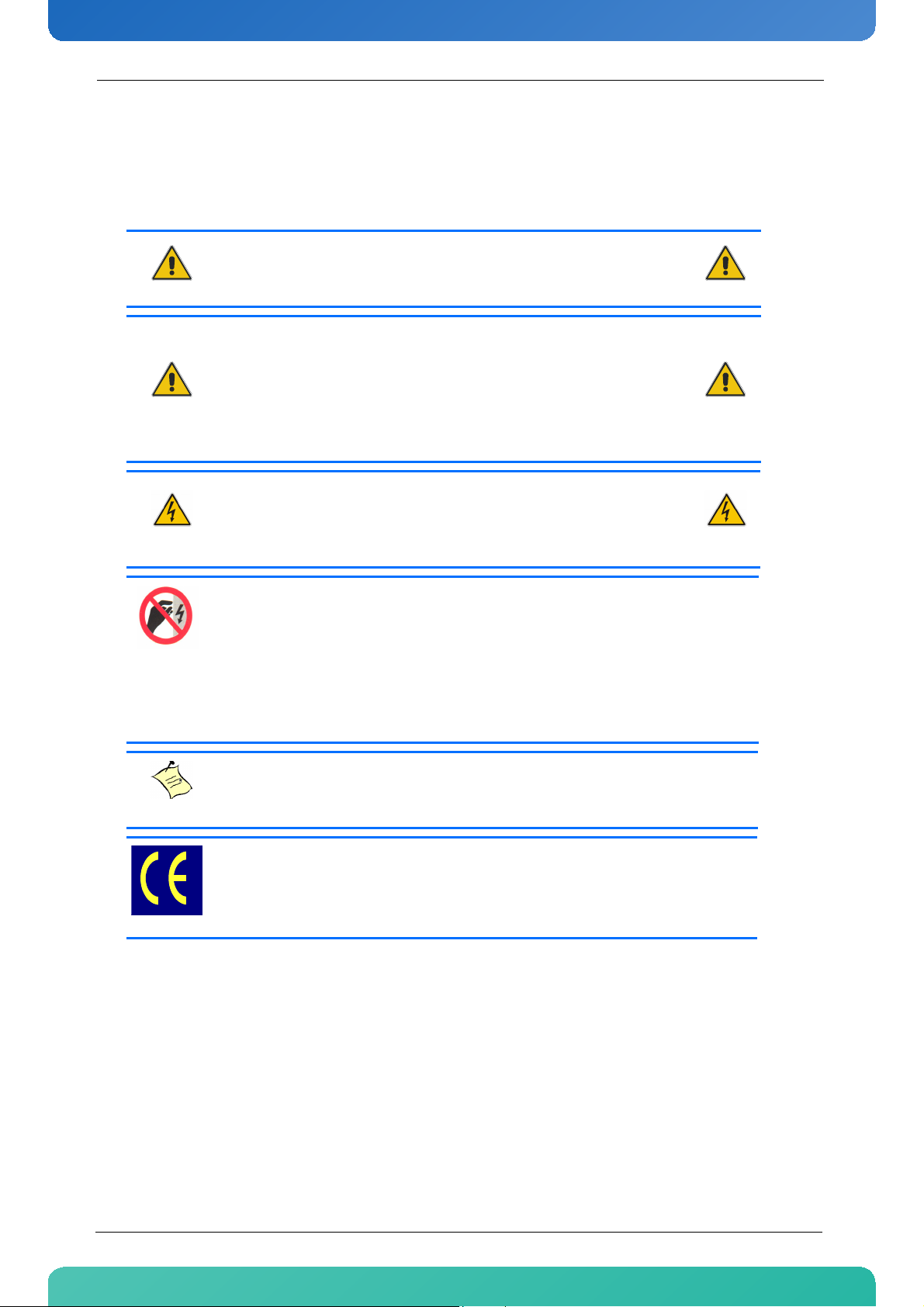

Explanation of Symbols

CAUTION

This symbol and title indicate potential damage to hardware and tells

you how to avoid the problem.

CAUTION

Electric Shock

This symbol and title warn of hazards due to electrical shocks (> 60V)

when touching products or parts of them. Failure to observe the precautions indicated and/or prescribed by the law may endanger your

life/health and/or result in damage to your material.

WARNING

This symbol and title emphasize points which, if not fully understood

and taken into consideration by the reader, may endanger your

health and/or result in damage to your material.

Preface

ESD Sensitive Device

This symbol and title inform that electronic boards and their components are sensitive to static electricity. Therefore, care must be taken

during all handling operations and inspections of this product, in

order to ensure product integrity at all times.

Please read also the section “Special Handling and Unpacking

Instructions”.

Note...

This symbol and title emphasize aspects the reader should read through carefully for his or her own advantage.

CE Conformity

This symbol indicates that the product described in this manual is in

compliance with all applied CE standards. Please refer also to the section “Regulatory Compliance Statements” in this manual.

ix AT8404 User Guide

Page 10

Preface

www.kontron.com

For Your Safety

Your new Kontron product was developed and tested carefully to provide all features necessary to ensure its

compliance with electrical safety requirements. It was also designed for a long fault-free life. However, the

life expectancy of your product can be drastically reduced by improper treatment during unpacking and

installation. Therefore, in the interest of your own safety and of the correct operation of your new Kontron

product, you are requested to conform with the following guidelines.

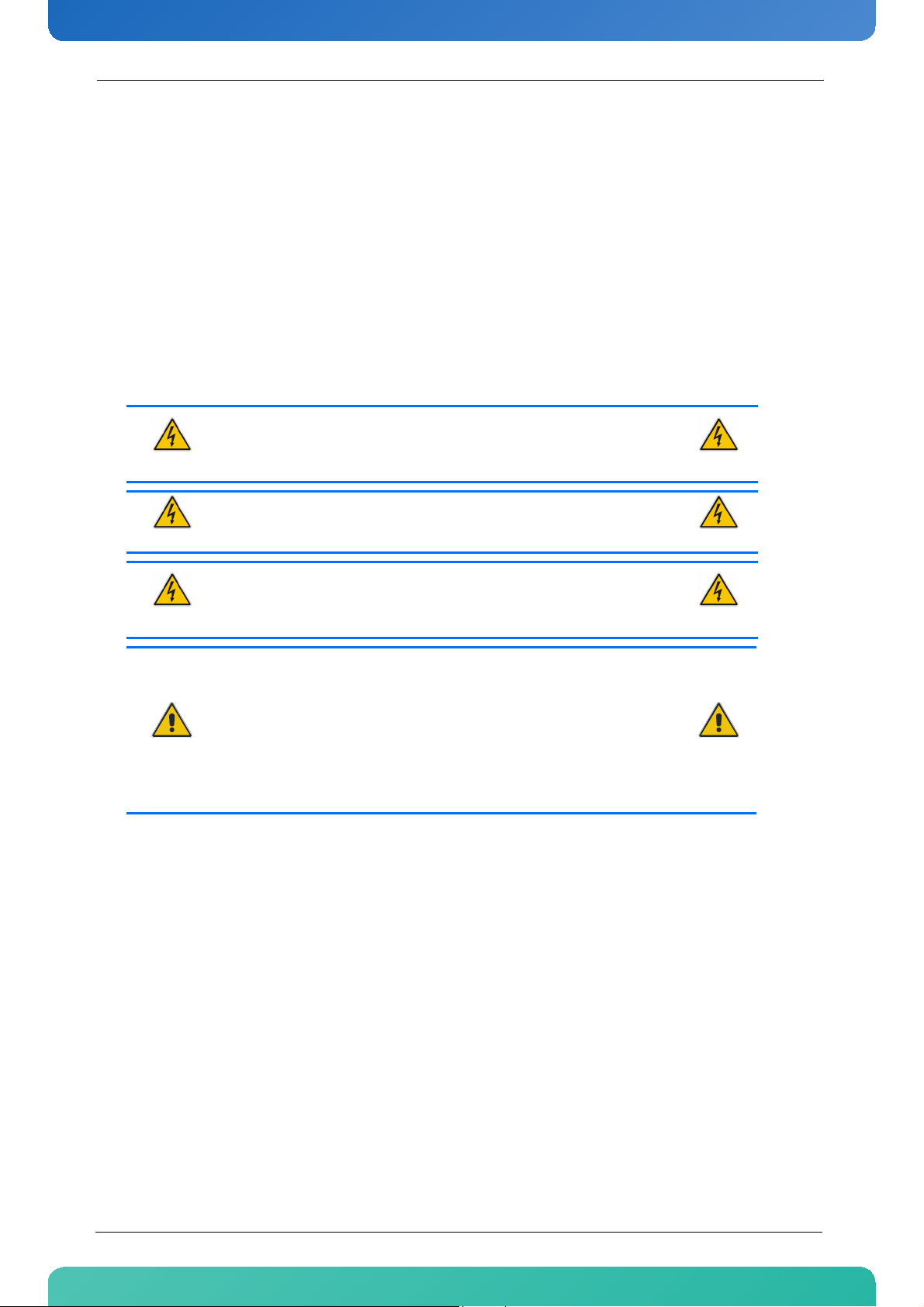

Safety Instructions

WARNING

All operations on this device must be carried out by sufficiently

skilled personnel only.

WARNING

Do not connect a switch port to a telephone line.

WARNING

For installation in a Hot-Plug system, observe the safety instructions specific to the system. Read the relevant documentation.

CAUTION

Electric Shock

High voltages are present inside the chassis when the unit’s power

cord is plugged into an electrical outlet. Turn off system power, turn

off the power supply, and then disconnect the power cord from its

source before removing the chassis cover. Turning off the system

power switch does not remove power to components.

x AT8404 User Guide

Page 11

Preface

www.kontron.com

Special Handling and Unpacking Instructions

ESD Sensitive Device

This symbol and title inform that electronic boards and their components

are sensitive to static electricity. Therefore, care must be taken during

all handling operations and inspections of this product, in order to

ensure product integrity at all times.

Do not handle this product out of its protective enclosure while it is not used for operational purposes unless

it is otherwise protected.

Whenever possible, unpack or pack this product only at EOS/ESD safe work stations. Where a safe work station is not guaranteed, it is important for the user to be electrically discharged before touching the product

with his/her hands or tools. This is most easily done by touching a metal part of your system housing.

It is particularly important to observe standard anti-static precautions when changing mezzanines, ROM

devices, jumper settings etc. If the product contains batteries for RTC or memory back-up, ensure that the

board is not placed on conductive surfaces, including anti-static plastics or sponges. They can cause short

circuits and damage the batteries or conductive circuits on the board.

xi AT8404 User Guide

Page 12

Preface

www.kontron.com

General Instructions on Usage

In order to maintain Kontron’s product warranty, this product must not be altered or modified in any way.

Changes or modifications to the device, which are not explicitly approved by Kontron AG and described in

this manual or received from Kontron’s Technical Support as a special handling instruction, will void your

warranty.

This device should only be installed in or connected to systems that fulfill all necessary technical and specific environmental requirements. This applies also to the operational temperature range of the specific

board version, which must not be exceeded. If batteries are present their temperature restrictions must be

taken into account.

In performing all necessary installation and application operations, please follow only the instructions supplied by the present manual.

Keep all the original packaging material for future storage or warranty shipments. If it is necessary to store

or ship the board please re-pack it as nearly as possible in the manner in which it was delivered.

Special care is necessary when handling or unpacking the product. Please, consult the special handling and

unpacking instruction on the previous page of this manual.

xii AT8404 User Guide

Page 13

Preface

www.kontron.com

Two Year Warranty

Kontron AG grants the original purchaser of Kontron’s products a TWO YEAR LIMITED HARDWARE WARRANTY as

described in the following. However, no other warranties that may be granted or implied by anyone on behalf

of Kontron are valid unless the consumer has the express written consent of Kontron AG.

Kontron AG warrants their own products, excluding software, to be free from manufacturing and material

defects for a period of 24 consecutive months from the date of purchase. This warranty is not transferable

nor extendible to cover any other users or long-term storage of the product. It does not cover products

which have been modified, altered or repaired by any other party than Kontron Modular Computers GmbH or

their authorized agents. Furthermore, any product which has been, or is suspected of being damaged as a

result of negligence, improper use, incorrect handling, servicing or maintenance, or which has been damaged as a result of excessive current/voltage or temperature, or which has had its serial number(s), any

other markings or parts thereof altered, defaced or removed will also be excluded from this warranty.

If the customer’s eligibility for warranty has not been voided, in the event of any claim, he may return the

product at the earliest possible convenience to the original place of purchase, together with a copy of the

original document of purchase, a full description of the application the product is used on and a description

of the defect. Pack the product in such a way as to ensure safe transportation (see our safety instructions).

Kontron provides for repair or replacement of any part, assembly or sub-assembly at their own discretion, or

to refund the original cost of purchase, if appropriate. In the event of repair, refunding or replacement of

any part, the ownership of the removed or replaced parts reverts to Kontron Modular Computers GmbH, and

the remaining part of the original guarantee, or any new guarantee to cover the repaired or replaced items,

will be transferred to cover the new or repaired items. Any extensions to the original guarantee are considered gestures of goodwill, and will be defined in the “Repair Report” issued by Kontron with the repaired or

replaced item.

Kontron Modular Computers GmbH will not accept liability for any further claims resulting directly or indirectly from any warranty claim, other than the above specified repair, replacement or refunding. In particular, all claims for damage to any system or process in which the product was employed, or any loss incurred as

a result of the product not functioning at any given time, are excluded. The extent of Kontron Modular Computers GmbH liability to the customer shall not exceed the original purchase price of the item for which the

claim exists.

Kontron Modular Computers GmbH issues no warranty or representation, either explicit or implicit, with

respect to its products’ reliability, fitness, quality, marketability or ability to fulfil any particular application

or purpose. As a result, the products are sold “as is,” and the responsibility to ensure their suitability for any

given task remains that of the purchaser. In no event will Kontron be liable for direct, indirect or consequential damages resulting from the use of our hardware or software products, or documentation, even if Kontron

were advised of the possibility of such claims prior to the purchase of the product or during any period since

the date of its purchase.

Please remember that no Kontron Modular Computers GmbH employee, dealer or agent is authorized to make

any modification or addition to the above specified terms, either verbally or in any other form, written or

electronically transmitted, without the company’s consent.

xiii AT8404 User Guide

Page 14

Chapter 1

Introduction

www.kontron.com

1KTC5520/EATX

Page 15

Introduction

www.kontron.com

1. Introduction

The Board described in this manual is designed for the Advanced Telecom Computing Architecture

(AdvancedTCA® or ATCA) defined by the PCI Industrial Computer Manufacturers Group (PICMG). The main

advantages of AdvancedTCA include high throughput, multi-protocol support, high-power capability, hot

swappability, high scalability and integrated system management. For further information regarding the

AdvancedTCA standards and their use, please consult the complete AdvancedTCA specification or visit the

PICMG web site.

1.1 Product Overview

The Kontron AT8404 is a PICMG 3.0 and 3.1 Option 9 compliant Carrier Board for Advanced TCA shelves,

designed according to the RoHS directive. It is a PICMG AMC.0 compliant Conventional Carrier providing four

mid-size AMC slots. A Gigabit Ethernet Switch provides connection to the base interface (BI) and fabric

interface (FI).

1.1.1 AT8404 Features

The main features of the AT8404 are:

• Gigabit Ethernet Switch

• Fat Pipe Interconnect

• Storage Interconnect

• Unit Computer and Memory

• Synchronous Clock Distribution

• Up to four mid-size AMC bays

• APS (Automatic Protection Switching) for AMCs

• RTM Connector (Zone 3)

•IPMI

• Power Supply Mezzanine incl. Hold Over Circuit

1.1.1.1 Ethernet Switch

• Broadcom BCM56502: 24 Port Gigabit Layer-2/3 Switch with 2 x 10GbE Uplinks

• PCI 32b/66MHz Management IF

• Line rate switching for all packet sizes and conditions

• Supports 2 Base channels 10/100/1000Base-T

• Supports 2 Fabric channels with 10GbE XAUI

2 AT8404 User Guide

Page 16

Introduction

www.kontron.com

• Supports 5 AMC GbE interfaces per AMC slot

• Supports a 10/100/1000Base-T interfaces to the RTM

• Supports a GbE connection to the unit computer for fast packet transfer

1.1.1.2 Fat Pipe Interconnect

• AMC bays B1 and B2 as well as B3 and B4 are directly (copper) interconnected via AMC Fat Pipe ports 4-7

1.1.1.3 Storage Interconnect

• AMC storage ports are connected between pairs of AMC bays

• SAS/SATA HDD on RTM is supported for two AMC bays

• Flexible routing supports different configurations

1.1.1.4 Unit Computer and System Memory

• Socketless PowerPC IBM PPC405GPr-400 MHz

• Used for switch provisioning and diagnostics

• 256 MBytes of SDRAM memory, 133 MHz

• 128 MBytes of Flash memory

1.1.1.5 Synchronous Clock and PCI Express Clock Distribution

• PICMG AMC.0 Revision 2.0 compliant

• Configurable routing of Telecom clock lines between backplane and AMC bays

• PCI Express compliant clock source with optional Spread Spectrum Clock

• Switchable PCI Express clock source to all AMCs

1.1.1.6 IPMI

• PICMG 3.0 / IPMI 1.5 compliant

• Serial EEPROM for FRU storage (serial ID)

• Current, voltage and temperature sensors

• Base Board, AMC bays and RTM hot swap and power control

• Firmware update handling for field upgrades, rollbacks and watchdog functions

1.1.1.7 AMC Bays

• Up to four PICMG AMC.0 Revision 2.0 compatible mid-size AMC bays (see section 1.1.5)

• AMC B+ connectors

• 5 x 1 GbE connections (Common Option and Fat Pipe Regions)

• Full Telecom clocks and PCI Express clock support

• 7 Extended Options Region RTM links

• Update Channel (APS) link per AMC bay running at up to 2.5Gbps

3 AT8404 User Guide

Page 17

www.kontron.com

1.1.1.8 RTM Connector

• Support for 7 RTM lanes from each AMC

• FE and RS232 (RJ45) management ports

• 2x Storage connections

•1x GbE

• 12V and 3V3 sus Supply Voltage connections

• I²C support

• JTAG and production I/O support

1.1.1.9 Power Supply Mezzanine

• Isolated 48V to 12V Standard Quarterbrick intermediate bus converter

• Hot swap support

• Hold Over Circuit using high voltage capacitor and charge pump

• Isolated management power supply

• 48V power Supply 'ORing' circuit

Introduction

• Supplies point of load regulators for secondary supply voltages (derived from 12V intermediate rail) on

base board

1.1.2 General compliances

The AT8404 is conform to the following specifications:

• PICMG 3.0 AdvancedTCA Base Specification, Revision 2.0

• PICMG 3.1 Ethernet/Fibre Channel for AdvancedTCA Systems

• AMC.0 Advance Mezzanine Card Base Specification, Revision 2.0

• AMC.1 PCI Express and Advanced Switching

• AMC.2 AMC Gigabit Ethernet

•AMC.3 AMC Storage

• IPMI v1.5 Intelligent Platform Management Interface Specification

4 AT8404 User Guide

Page 18

Introduction

www.kontron.com

1.1.3 Optional Accessories

1.1.3.1 AMC

Up to four mid-size single width or up to two mid-size double width AMC bays for standard or custom AMCs

are implemented.

AMC slots can be equipped with a:

• Processor-AMC

• HDD-AMC as mass storage device for the Processor-AMC

• Interface AMC, e.g. Quad GbE

1.1.3.2 RTM

The Kontron RTM8030 provides an additional GbE switch port and out-of-band management access via Fast

Ethernet or RS232. Two storage lines from the AMC bays are routed to a connector on the RTM’s face plate for

interconnecting two carriers. They may also connect to a SATA HDD located on the RTM. For more information

on the RTM8030, refer to chapter 3.2.

1.1.4 Hot Swap Capability

The board supports Full Hot Swap capability as required by PICMG 3.0 R1.0. It can be removed or installed

without powering-down the system. Please refer to the PICMG 3.0 R1.0 specification for additional details.

1.1.5 Board Options

The Kontron AT8404 is available with different AMC slot configurations.

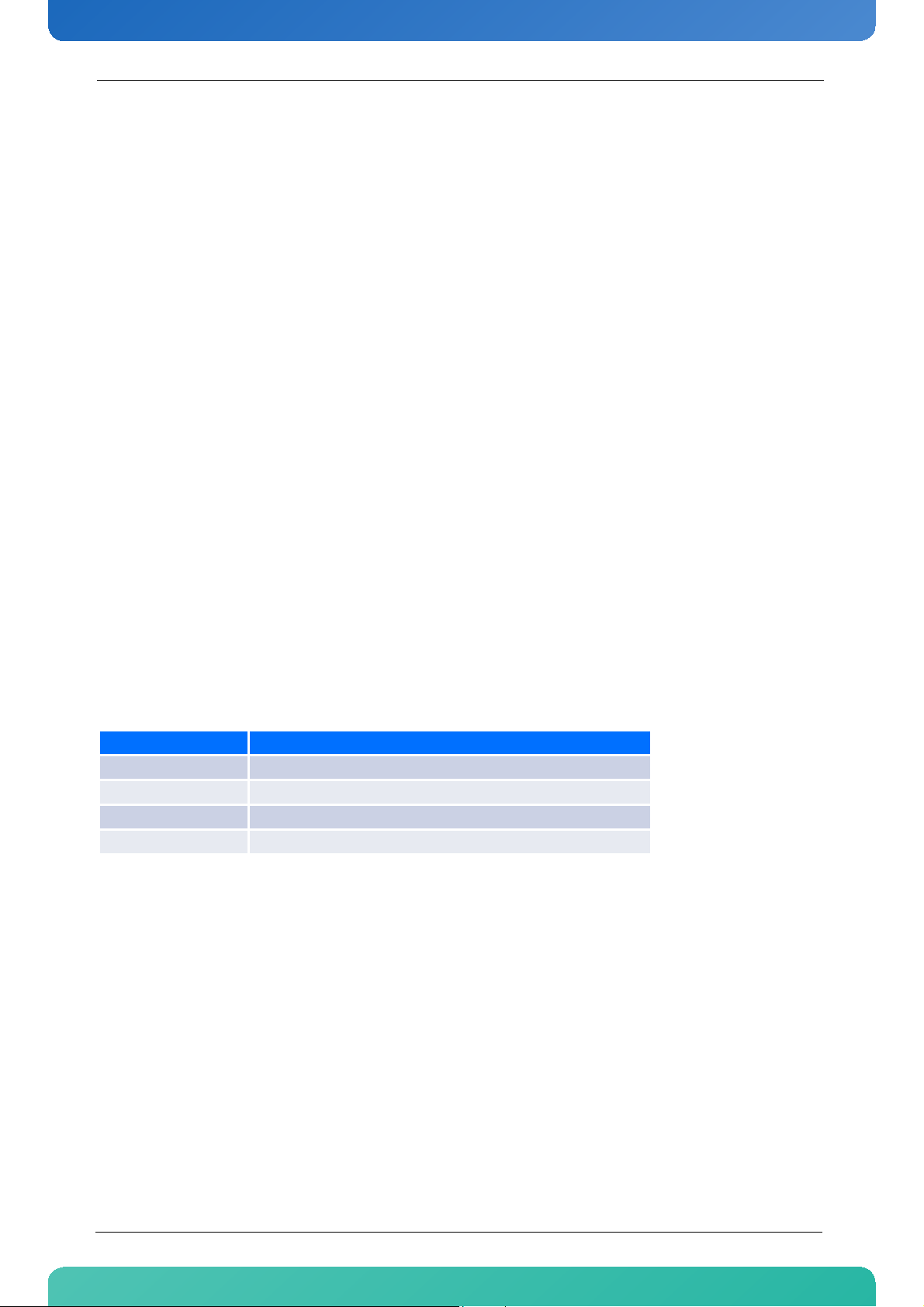

Table 1-1: AMC Slot Options

Option AMC Slot Configuration

A 4 x single width slots

B 2 x double width slots

C 2 x single width slots and 1 x double width slot on B1/B2

D 2 x single width slots and 1 x double width slot on B3/B4

5 AT8404 User Guide

Page 19

www.kontron.com

1.2 Technical Specification

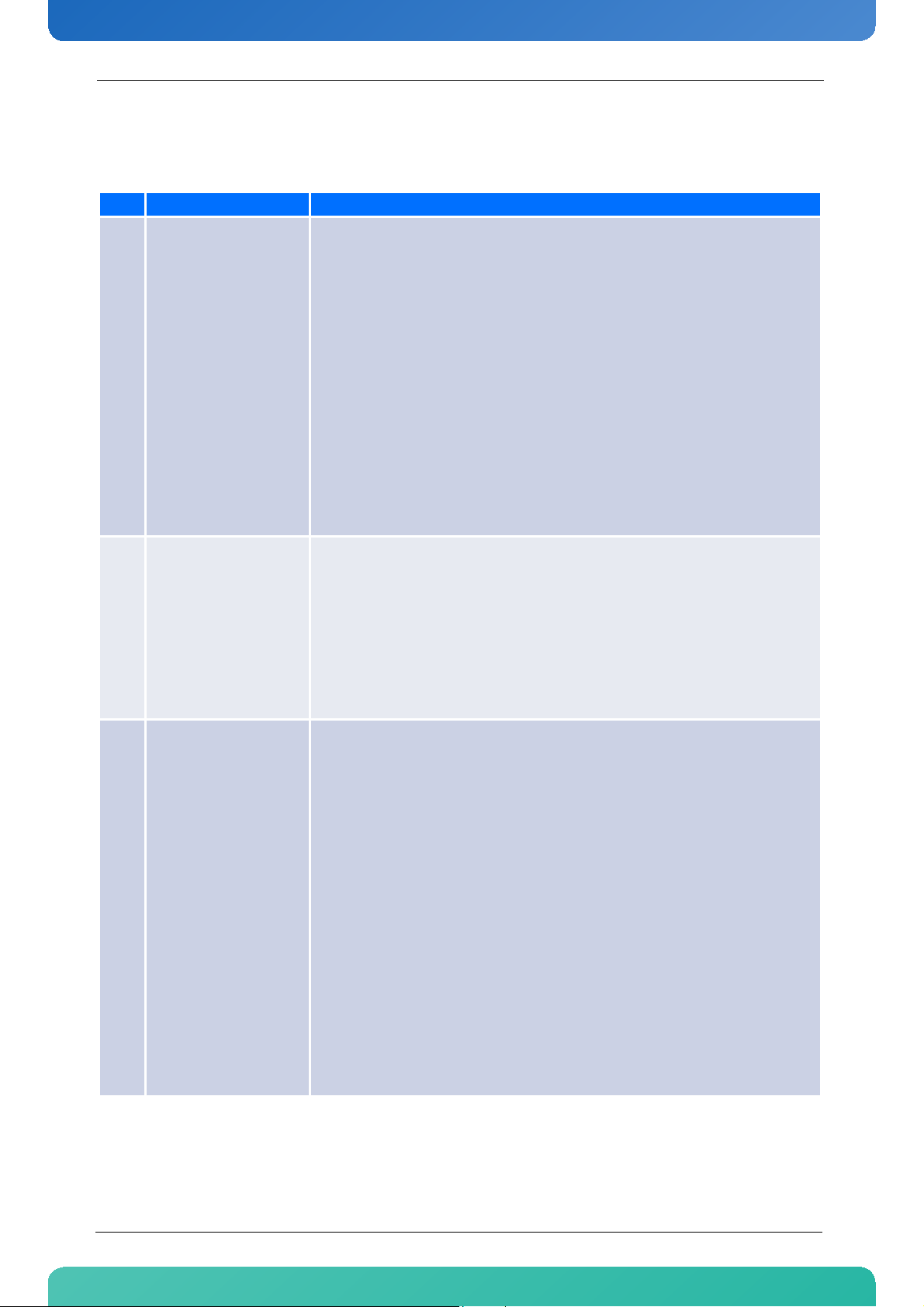

Table 1-2: AT8404 Main Specifications

AT8404 SPECIFICATIONS

•

IBM PowerPC® 405 32-bit RISC processor core operating up to 400MHz with 16KB Iand D-caches

•

PC-133 synchronus DRAM (SDRAM) interface

•

40-bit interface serves 32 bits of data plus 8 check bits for ECC applications

•

4KB on-chip memory (OCM)

•

DMA support for external peripherals, internal UART and memory

PowerPC IBM PPC 405

GPr-400MHz

Unit Computer and Memory

•

Scatter-gather chaining supported

•

Four channels

•

PCI Revision 2.2 compliant interface (32-bit, up to 66MHz)

•

Ethernet 10/100Mbps (full-duplex) support with media independent interface (MII)

•

Two serial ports (16550 compatible UART)

•

Internal processor local Bus (PLB) runs at SDRAM interface frequency

Introduction

Broadcom 5466R

Ethernet

Broadcom 56502

Ethernet

•

IEEE 1149.1 (JTAG) boundary scan

•

Advanced power management Line-side and MAC-side loopback

•

Ethernet@WireSpeed

•

Cable plant diagnostics that detects cable plant impairments

•

Automatic detection and correction of wiring pair swaps, pair skew, and pair polarity

•

Robust CESD tolerance and low EMI emissions

•

Support for jumbo packets up to 10 KB in size

•

IEEE 1149.1 (JTAG) boundary scan

• 24 10/100/1000 Mbps Ethernet ports

•

2 10GbE ports

•

Fifth generation of StrataSwitch and StrataXGS product line

•

Line-rate switching for all packet sizes and conditions

•

On-chip data packet memory and table memory

•

Advanced Fast Filter Processor (FFP) Content Aware classification

•

Advanced security features in hardware

•

Port-trunking and mirroring supported across stack

•

Advanced packet flow control:

•

Head-of-line-blocking prevention

•

Back pressure support

•

QoS queues per port with hierarchical minimum/maximum shaping per class of Service (CoS) per queue per port

•

Standard compliant 802.1ad provider bridging

•

IEEE 1149.1 (JTAG) boundary scan

6 AT8404 User Guide

Page 20

www.kontron.com

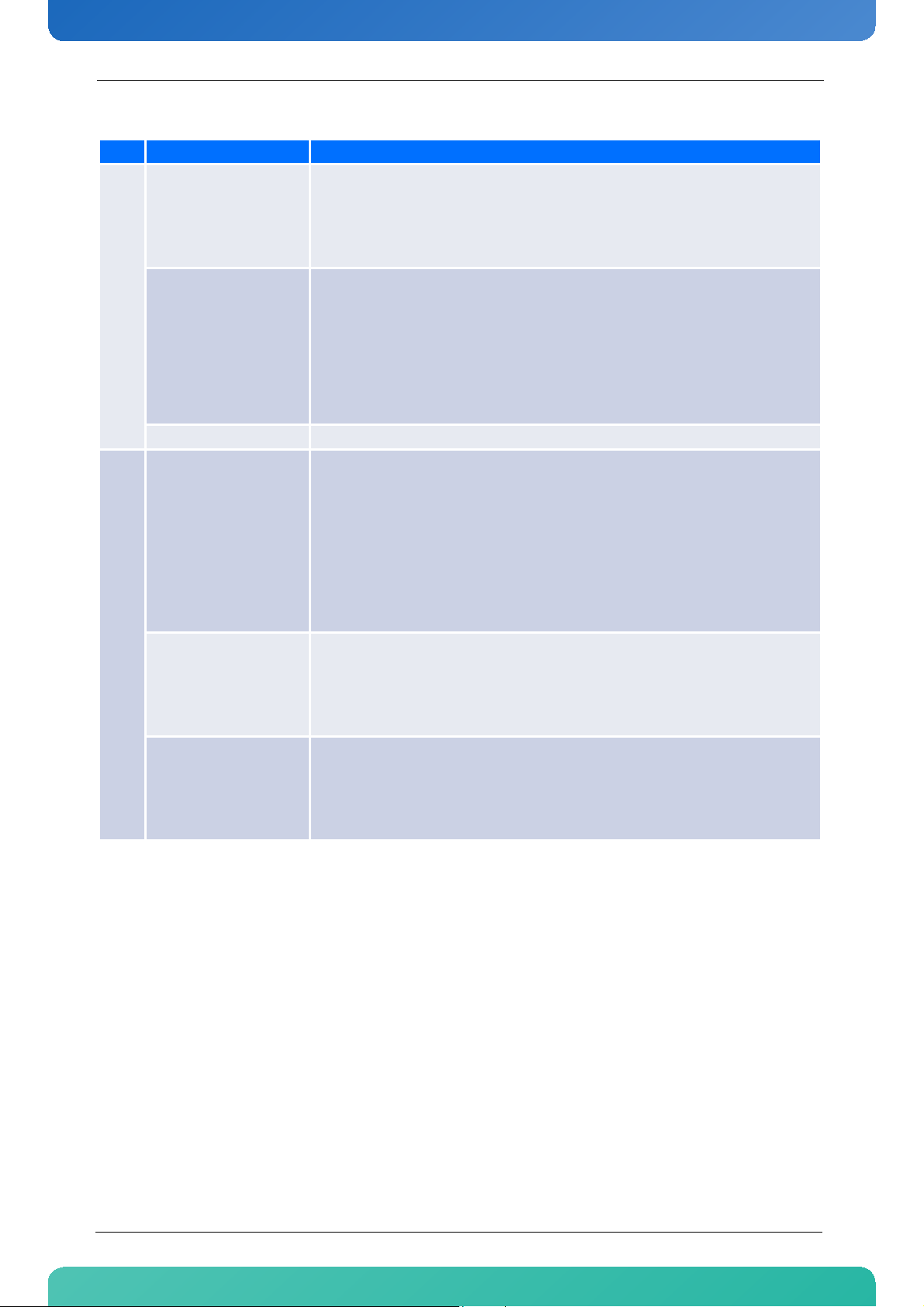

Table 1-2: AT8404 Main Specifications

AT8404 SPECIFICATIONS

•

Base channels 1 and 2: 1 x GbE (1000BASE-T)

•

Backplane (Zone 2)

Fabric channels 1 and 2: 1 x 10 GbE (XAUI)

•

Synchronization Clock: 2 x CLK 1/2/3 (A/B)

•

Update channels 0-3: APS Path

• 7 generic RTM channels from each AMC Slot

• 2 SAS/SATA/FC interfaces for mass storage

•

Interfaces

RTM (Zone 3)

1 GbE interface to front board switch

• Serial port for Unit Computer management

•

Fast Ethernet for Unit Computer management

• I2C IPMI connection

Front Panel •

Serial port for Unit Computer management

•

8U form factor mechanically compliant to PICMG 3.0 and AMC.0

•

Single slot (6HP)

Introduction

Mechanical

General

Power Requirements

Temperature

•

Up to four mid-size/single width AMC slots

•

or up to two mid-size/double width AMC slots

• 280 mm x 322 mm (11.024“ x 12.677“)

•

150 mm cut away in AMC area

• Weight: 1.825 kg

•

Typical: 40W

•

Maximum (4 AMCs and RTM): 210W

•

AMCs may consume up to 140W

•

Operating Voltage: -38 to -72 VDC

Designed to meet or exceed the following (Characteristics without AMCs):

•

Air Flow: 30 CFM min

•

Operating:

• Non-operating: -40°C to +70°C

0°C to +55°C (32°F to 131°F)

(-40°F to 158°F)

7 AT8404 User Guide

Page 21

www.kontron.com

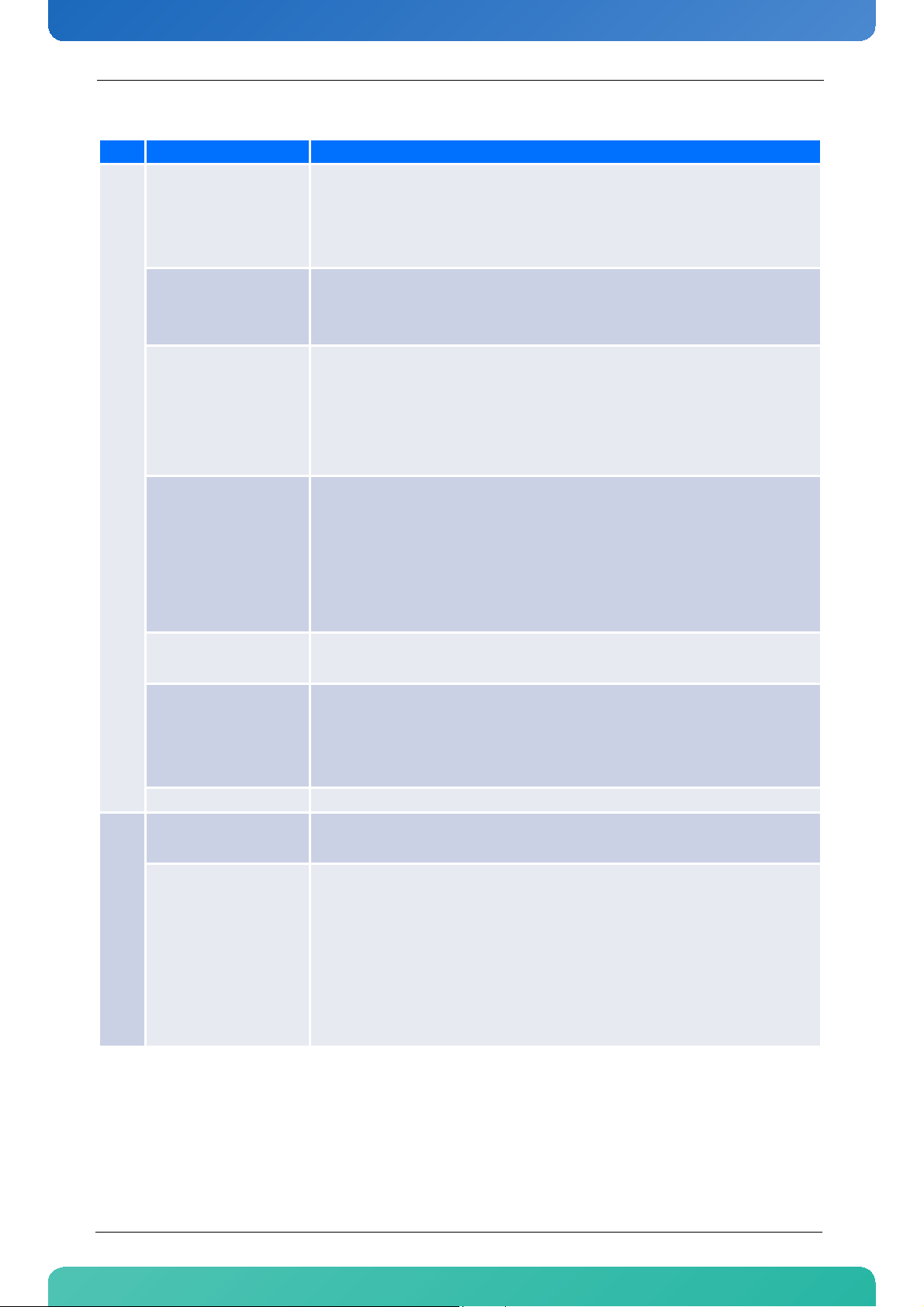

Table 1-2: AT8404 Main Specifications

AT8404 SPECIFICATIONS

Designed to meet or exceed the following:

•

Humidity

Altitude

Vibration

General

Shock

Bellcore GR-63, Section 4.1

•

Operating: 15%-90% (non-condensing) at 55°C (131°F)

•

Non-Operating: 5%-95% (non-condensing) at 40°C (104°F)

Designed to meet or exceed the following:

•

Operating: 4000 m (13123 ft)

•

Non-operating: 15000 m (49212 ft)

Designed to meet or exceed the following:

•

Bellcore GR-63, Section 4.4

•

ETSI EN 300 019-2-3

•

Operating: Sinusoidal 1.0G (5-100Hz), 0.2G (100-200Hz), each axis

•

Packaged: Random 0.89Grms (5-200Hz), each axis

Designed to meet or exceed the following:

•

DIN/IEC 60068-2-27

•

Bellcore GR-63, Section 4.3

•

ETSI EN 300 019-2-3

Introduction

Safety

EMC

Reliability •

LEDs

Board Management

HW Monitoring

•

Operating: 3G, half-sine 11ms, each axis

•

Packaged: 18G, half-sine 6ms, each axis

Designed to meet or exceed the following:

•

CB report to IEC 60950-1, complies with EN/CSA/ UL 60950-1

Designed to meet or exceed the following:

•

FCC 47 CFR Part 15, Subpart B

•

EN55022, EN55024

•

EN 300 386

MTBF: > 384,000 hours @ 40°C/104°F (Telcordia SR-332, Issue 1)

ATCA LEDs:

•

4 LEDs ("Ready for Hot Swap", "Out of Service", "Healthy", "Activity")

•

based on IPMI 1.5

•

FRU Management

•

Sensors (Voltage, Current, Temperature, Fuse)

•

Status and Alerting

•

Hot Swap Management for Base Board and AMC

•

Electronic Keying of Base and Fabric Interfaces and AMC ports

•

Local SEL

8 AT8404 User Guide

Page 22

www.kontron.com

1.3 Software Support

The following table contains information related to software supported by the AT8404.

Table 1-3: AT8404 Software Specifications

AT8404 SPECIFICATIONS

•

Reliable field upgrades for all software components

•

Dual boot images with roll-back capability

•

General

Management via SNMP and Command Line Interface

•

System access via TELNET, SSH and serial line

•

Hot-Swap support (IPMI)

•

Hot-Plug support for AMC modules (IPMI)

•

Static link aggregation (IEEE 802.3ad) on any port combination

•

Classic and rapid spanning tree algorithms supported (IEEE 802.1D, IEEE 802.1w)

•

Quality Of Service on all ports (IEEE 802.1p)

•

Full Duplex operation and flow control on all ports (IEEE 802.3x)

•

Static MAC filtering

Introduction

Ethernet/Bridging

Applications

•

Port Authentication (IEEE 802.1X)

•

Auto negotiation of speeds and operational mode on all external GE interfaces

as well as on all base fabric interfaces

•

Layer 2 multicast services using GARP/GMRP (IEEE 802.1p)

•

VLAN support including VLAN tagging (IEEE 802.3ac), dynamic VLAN registration with

GARP/GVRP (IEEE 802.1Q) and Protocol based VLANs (IEEE 802.1v)

•

Double VLAN tagging

•

Port Mirroring

• NTP client for retrieving accurate time and date information

• DHCP server

• Onboard event management

• Test and trace facilities

• POST (power on self tests) diagnostics

• Standards based SNMP implementation supporting SNMP v1, v2 and v3

for monitoring and management purposes

• IPMI based management of the onboard AMC slots (AMC.*)

• Persistent storage of configuration across restarts

• Support for retrieving and installing multiple configurations

•

CoS (Class of Service )

QoS

•

DifffServ (Differentiated Services)

•

ACL (Access Control List)

9 AT8404 User Guide

Page 23

www.kontron.com

Table 1-3: AT8404 Software Specifications

AT8404 SPECIFICATIONS

• Switching Package MIBs

• RFC 1213 - MIB-II

• RFC 1493 - Bridge MIB

• RFC 1643 - Ethernet-like -MIB

• RFC 2233 - The Interfaces Group MIB using SMI v2

• RFC 2618 - RADIUS Authentication Client MIB

• RFC 2674 - VLAN & Ethernet Priority MIB

• RFC 2819 - RMON Groups 1,2,3 & 9

Supported MIBS

• RFC 3291 - Textual Conventions for Internet Network Addresses

• IANA-ifType-MIB

• IEEE 802.1X MIB (IEEE8021-PAE-MIB)

• IEEE 802.3AD MIB (IEEE8021-AD-MIB)

• QoS Package MIB

• RFC 3289 - DIFFSERV-MIB & DIFFSERV-DCSP-TC MIBs

• FASTPATH Enterpr ise MIB

• Support for all managed objects not contained in standards based

MIBs.

u-boot Version 1.2.0

•

POST

Introduction

•

Bootloader

•

•

•

•

Operating System •

loadable bootimage via network (bootp/tftp)

reliable field upgradable

H/W protected

KCS interface to IPMC

serial console support

Wind River Linux PNE 2.0

10 AT8404 User Guide

Page 24

Chapter 2

Installation

www.kontron.com

11KTC5520/EATX

Page 25

Installation

www.kontron.com

2. Installation

The AT8404 has been designed for easy installation. However, the following standard precautions, installation procedures, and general information must be observed to ensure proper installation and to preclude

damage to the board, other system components, or injury to personnel.

2.1 Safety Requirements

The following safety precautions must be observed when installing or operating the AT8404. Kontron

assumes no responsibility for any damage resulting from failure to comply with these requirements.

WARNING

Due care should be exercised when handling the board due to the fact

that the heat sink can get very hot. Do not touch the heat sink when

installing or removing the board.

In addition, the board should not be placed on any surface or in any form

of storage container until such time as the board and heat sink have

cooled down to room temperature.

ESD sensitive equipment

This ATCA board contains electrostatically sensitive devices. Please observe the necessary precautions to avoid damage to your board:

• Discharge your clothing before touching the assembly. Tools must be discharged

before use.

• When unpacking a static-sensitive component from its shipping carton, do not re-

move the component's antistatic packing material until you are ready to install

the component in a computer. Just before unwrapping the antistatic packaging,

be sure you are at an ESD workstation or grounded. This will discharge any static

electricity that may have built up in your body.

• When transporting a sensitive component, first place it in an antistatic container

or packaging.

• Handle all sensitive components at an ESD workstation. If possible, use antistatic

floor pads and workbench pads.

• Handle components and boards with care. Do not touch the components or con-

tacts on a board. Hold a board by its edges or by its metal mounting bracket.

• Do not handle or store system boards near strong electrostatic, electromagnetic,

magnetic, or radioactive fields.

12 AT8404 User Guide

Page 26

Installation

www.kontron.com

2.2 AT8404 Initial Installation Procedures

The following procedures are applicable only for the initial installation of the AT8404 in a system. Procedures for standard removal and hot swap operations are found in their respective chapters.

To perform an initial installation of the AT8404 in a system proceed as follows:

1. Ensure that the safety requirements indicated in section 2.1. are observed.

WARNING

Failure to comply with the instruction below may cause damage to the

board or result in improper system operation.

2. Ensure that the board is properly configured for operation in accordance with application requirements

before installing. For information regarding the configuration of the AT8404 refer to Chapter 4.

WARNING

Care must be taken when applying the procedures below to ensure that

neither the AT8404 nor other system boards are physically damaged by

the application of these procedures.

3. To install the AT8404 perform the following:

1. Carefully insert the board into the slot designated by the application requirements for the board un-

til it makes contact with the backplane connectors.

WARNING

DO NOT push the board into the backplane connectors. Use the ejector

handles to seat the board into the backplane connectors.

2. Using the ejector handle, engage the board with the backplane. When the ejector handle is locked,

the board is engaged.

3. Fasten the front panel retaining screws.

4. Connect all external interfacing cables to the board as required.

5. Ensure that the board and all required interfacing cables are properly secured.

4. The AT8404 is now ready for operation.

13 AT8404 User Guide

Page 27

Installation

www.kontron.com

2.3 Standard Removal Procedures

To remove the board proceed as follows:

1. Ensure that the safety requirements indicated in section 2.1. are observed.

WARNING

Care must be taken when applying the procedures below to ensure

that neither the AT8404 nor system boards are physically damaged by

the application of these procedures.

2. Unscrew the front panel retaining screws.

3. Lift the notch of the lower handle and pull the handle with the notch away from the faceplate until you

feel a resistance. The blue LED starts blinking.

4. Wait until the blue LED is fully ON, this mean that the hot swap sequence is ready for board removal.

5. Disengage the board from the backplane by using both board ejection handles.

6. After disengaging the board from the backplane, pull the board out of the slot.

2.4 AMC Installation

To install an AMC proceed as follows:

1. Remove the AMC filler panel.

2. Carefully engage the AMC into the card guide. Push the AMC until it fully mates with its connector. Secure the AMC handle to the locking position.

3. In normal condition, the blue LED shall turn ON as soon as the AMC is fully inserted. It will turn OFF at

the end of the hot swap sequence.

2.5 Software Installation

The AT8404 comes as a pre-installed system with all necessary OS, Filesystem, drivers and applications factory-installed with default configurations.

Updating the Software with new Operating System or applications or new versions is provided by a dedicated

update mechanism, which is described in Chapter 4.

14 AT8404 User Guide

Page 28

Installation

www.kontron.com

2.6 Quick Start

This section gives instructions for (initially) accessing the CLI (Command Line Interface) of the AT8404 using

either in-band access via the BI or the out-of-band management interfaces (serial port or Fast Ethernet)

accessible from the front plate serial connector or via an appropriate RTM. The CLI is required for configuring

the GbE switch, as well as the storage interconnect.

2.6.1 In-Band CLI Access

The GbE switch on the AT8404 is pre-configured with a management VLAN. This VLAN is accessible over the

BI. Telnet accesses to port 23 of this VLAN connect to the CLI. The VLAN is configured for DHCP and retrieves

its IP address automatically when a DHCP server is found in the network. The procedure to obtain the issued

IP from the DHCP server is beyond the scope of this document.

The management VLAN is configured with VLAN ID 1. The following Ethernet ports are members of the management VLAN ID 1 by default:

• Interface 0/23 connected to base interface switch in ATCA logical slot 1

• Interface 0/5, 0/10, 0/15, 0/20 connected to AMC bay B4, B3, B2, B1 on port 0

Thus connectivity to the management VLAN ID 1 is by default possible through the base interface switch in

ATCA chassis logical slot 1.

For more information on the management VLAN and how to assign a fixed IP address, refer to the AT8404 CLI

Reference Manual.

2.6.2 Out-of-band CLI Access

The CLI can also be accessed via serial port (using the front plate connector and provided cable or an appropriate RTM like the RTM8030) or Fast Ethernet (only via RTM). The serial port is ready to use offhand without

further configuration.

To connect to the CLI via the Fast Ethernet serviceport on the RTM, a telnet session must be established to

the IP address of this interface, port 23.

Using the default configuration, it is necessary to assign an IP address statically to the serviceport. Because

the required configuration steps are done in the CLI, an initial access using the serial port or in-band connectivity via the BI is required. The procedure for assigning an IP address to the serviceport is described in

the following. User input is printed in bold letters.

1. Connect to serial port on the front plate (using the Kontron DB9 adapter cable) or RTM (using a RJ45

straight cable).

Port settings are:

• 115200 bps (serial speed might be different for customized board variants)

• 8 bit, no parity, 1 stop bit (8N1)

• no flow control

2. Ensure that the board is powered up.

15 AT8404 User Guide

Page 29

Installation

www.kontron.com

3. Wait for boot process to complete, i.e. until the console selection menu appears.

b - connect Base Fabric console

c - connect Custom Application console

! - shell escape

r - reset system

4. Type ’b’ to connect to the Base Fabric console.

Connected to Base Fabric console

Press ^X or ^V to get to menu again

Base Fabric switching application release GA 2.00 starting

(Unit 1)>

User:

5. Log in as admin and enter privileged mode by typing ’enable’ (no passwords required by default).

User:admin

Password:

(Ethernet Fabric) >enable

Password:

(Ethernet Fabric) #

6. Set IP address and netmask. (see below for an example IP address setting)

(Ethernet Fabric) #serviceport ip 192.168.50.107 255.255.255.0

The FE management interface is available from now on.

7. Save configuration by copying it to the flash, confirm by typing ’y’

(Ethernet Fabric) #copy system:running-config nvram:startup-config

This operation may take a few minutes.

Management interfaces will not be available during this time.

Are you sure you want to save? (y/n) y

Configuration Saved!

(Ethernet Fabric) #

To access the CLI via Fast Ethernet management port, open a telnet connection to the configured IP address,

port 23.

For additional information on the system configuration, refer to the AT8404 CLI Reference Manual.

16 AT8404 User Guide

Page 30

Installation

www.kontron.com

2.6.3 Storage Configuration

The storage connection on Port 2 of AMC B4 is linked to AMC B2 (port 2) by default. To establish a storage

connection between AMC bays 1 (port 3) and 4 (port 2), use the following command in privileged mode:

(Ethernet Fabric) #set board storage connect amcb4 amcb1

To reset the configuration to the default settings, use the following command:

(Ethernet Fabric) #set board storage connect amcb4 amcb2

For an overview of the current configuration, use the CLI boardinfo command:

(Ethernet Fabric) #show boardinfo storage

The AMC B4 (port 2) is connected to AMC B2 (port 2)

17 AT8404 User Guide

Page 31

Chapter 3

Hardware Description

www.kontron.com

18KTC5520/EATX

Page 32

Hardware Description

www.kontron.com

Base IF

Zone 2

Fabric IF

Zone 2

Zone 1

Telco

Clk

4

Switch

Controller

Gigabit

Ethernet

Switch

RTM IF

Zone 3

4

4

4

AMC B2

AMC Connector

AMC B3

AMC Connector

AMC B4

1

PCI

2x 10GbE

To all

AMC

slots

Telco Clk

4x7

RS232

FE

AMC Connector

AMC B1

AMC Connector

Power

Mezzanine

Update

IF

IPMI

To all AMC slots

5

5

5

5

RS232

To all

AMC

slots

APS

2

1

Gigabit Ethernet

Storage Interconnect

AMC Fabric P2P Interconnect

AMC/RTM Extension Ports

3. Hardware Description

This chapter describes the board specific items of the AdvancedTCA AMC Carrier Board AT8404 consisting of

the main assembly with the Power Mezzanine Module. Also described is the RTM8030 used for management

access and I/O extension.

3.1 Base Board

The base board is a PICMG 3.0 and 3.1 Option 9 compliant Carrier Board for AdvancedTCA shelves offering up

to four mid-size AMC bays.

Figure 3-1: Functional Block Diagram Base Board

19 AT8404 User Guide

Page 33

Hardware Description

www.kontron.com

The main building blocks of the base board are:

• Ethernet Switch

• Unit Computer and Memory

• Fat Pipe Interconnect

• Storage Interconnect

• Synchronous Clock Distribution

• AMC Bays with APS (Automatic Protection Switching)

•IPMI

• RTM Interface

•Power Supply

3.1.1 Ethernet Switch

The main parts of the Ethernet Switch building block is a Broadcom BCM56502 24 port Gigabit Layer-2/3

Switch and a Broadcom BCM5466R QUAD 10/100/1000BASE-T PHY for the base and extension fabric inter face,

AMC and RTM Uplink connectivity. The BCM56502 is managed via the 32bit/33MHz PCI interface.

A BCM 5466R performs PHY functions for the 10/100/1000BASE-T ports of the Unit Computer and the two base

interface links.

The ports of the BCM56502 are assigned as follows:

Table 3-1: GbE Switch Port Assignment

CLI ID Speed Type Connection

0/1 1 GbE Serdes AMC B1, Port 8

0/2 1 GbE Serdes AMC B1, Port 9

0/3 1 GbE Serdes AMC B1, Port 10

0/4 1 GbE Serdes AMC B1, Port 11

0/5 1 GbE Serdes AMC B1, Port 0

0/6 1 GbE Serdes AMC B2, Port 8

0/7 1 GbE Serdes AMC B2, Port 9

0/8 1 GbE Serdes AMC B2, Port 10

0/9 1 GbE Serdes AMC B2, Port 11

0/10 1 GbE Serdes AMC B2, Port 0

0/11 1 GbE Serdes AMC B3, Port 8

0/12 1 GbE Serdes AMC B3, Port 9

0/13 1 GbE Serdes AMC B3, Port 10

0/14 1 GbE Serdes AMC B3, Port 11

0/15 1 GbE Serdes AMC B3, Port 0

0/16 1 GbE Serdes AMC B4, Port 8

0/17 1 GbE Serdes AMC B4, Port 9

0/18 1 GbE Serdes AMC B4, Port 10

0/19 1 GbE Serdes AMC B4, Port 11

0/20 1 GbE Serdes AMC B4, Port 0

20 AT8404 User Guide

Page 34

Hardware Description

www.kontron.com

Table 3-1: GbE Switch Port Assignment (Continued)

CLI ID Speed Type Connection

0/21 1 GbE 100BaseTX Unit Computer

0/22 1 GbE Serdes RTM SFP

0/23 1 GbE 1000BaseT Base Channel 1

0/24 1 GbE 1000BaseT Base Channel 2

0/25 10 GbE XAUI Fabric Channel 1

0/26 10 GbE XAUI Fabric Channel 2

3.1.2 Unit Computer and Memory

A PowerPC PPC405GPr-400MHz 32 bit RISC processor with 16KB D-cache, 256MB SDRAM and 128MB Flash

memory manages the Ethernet switch via 32bit / 66MHZ PCI local bus. The CPU is accessible via serial port or

10/100BASE-T Ethernet from the RTM or in-band via the GbE switch.

Besides the direct PCI connection to the management interface of the switch, a PCI Ethernet controller links

the Unit Computer to a switch port which is configured as 10/100BaseTX.

3.1.2.1 Fast Ethernet Management Interface

The 10/100BaseTX Ethernet management interface connects the Unit Computer to the RTM. It uses the following pins of the ATCA Zone 3 connector:

Table 3-2: Fast Ethernet Pins on RTM Connector

J30 Pin Function

B8 MNG_LAN_DA-

A8 MNG_LAN_DA+

D8 MNG_LAN_DB-

C8 MNG_LAN_DB+

3.1.2.2 RS232 Management Interface

One RS232 interface of the Unit Computer is the serial port which is routed to a miniature connector on the

front plate. An adapter cable is available from Kontron to establish a connection with a terminal with a standard DB9 serial port. Additionally, the Unit Computer’s serial port is routed to the Zone 3 connector so that a

connection can also be established by using an appropriate RTM like the RTM8030. If both ports are connected

to a terminal, the front plate connection takes precedence over the RTM connection.

21 AT8404 User Guide

Page 35

www.kontron.com

The front plate connector has the following pinning:

10

1

Table 3-3: Serial Port (J11) Pin Assignment

Hardware Description

Pin Num-

ber

1 N.C.

2 RXD

3 TXD

4 DTR

5 GND

6 DSR

7 RTS

8 CTS

9 N.C.

10 N.C.

Signal

The RS232 Management Interface uses the following pins of the ATCA Zone 3 connector:

Table 3-4: RS232 Pins on RTM Connector

J30 Pin Function

B3 RXD

A3 TXD

3.1.2.3 SDRAM

Five 512 Mbit devices, soldered directly onto the PCB, provide 256 MByte of SDRAM plus 64 MByte for ECC. The

SDRAM interface of the Unit Computer is 32 bit wide and operated at 133 MHz.

3.1.2.4 Flash ROM

The CPU uses a 128 Mbyte Flash Memory device. The sector containing the boot initialization code is write protected.

22 AT8404 User Guide

Page 36

Hardware Description

www.kontron.com

3.1.3 Fat Pipe Interconnect

AMC bays B1 and B2 as well as B3 and B4 are directly (copper) interconnected via AMC Fat Pipe ports 4-7, see

following table.

Table 3-5: Fat Pipe Interconnect

AMC Port Connects to

B1 port 4 B2 port 4

B1 port 5 B2 port 5

B1 port 6 B2 port 6

B1 port 7 B2 port 7

B2 port 4 B1 port 4

B2 port 5 B1 port 5

B2 port 6 B1 port 6

B2 port 7 B1 port 7

B3 port 4 B4 port 4

B3 port 5 B4 port 5

B3 port 6 B4 port 6

B3 port 7 B4 port 7

B4 port 4 B3 port 4

B4 port 5 B3 port 5

B4 port 6 B3 port 6

B4 port 7 B3 port 7

3.1.4 Storage Interconnect

A port selector is used to conf igure either a storage connection between the AMC B2 and B4 or B1 and B4. The

port selector is controlled by the IPMC.

Depending on the configuration, the SAS/SATA ports of the four mid-size AMC bays are interconnected as follows:

Table 3-6: AMC Storage Interconnect

AMC Port Connects to

B1 port 2 B3 port 2

B1 port 3 B4 port 2 via port selector

B2 port 2 B4 port 2 via port selector

B2 port 3 RTM port SAS_0

B3 port 2 B1 port 2

B3 port 3 -

B4 port 2 B1 port 3 or B2 port 2 via port selector

B4 port 3 RTM port SAS_1

For more information on how to configure the AMC Storage connections, refer to the AT8404 CLI Reference

Manual.

23 AT8404 User Guide

Page 37

Hardware Description

www.kontron.com

3.1.5 Synchronous Clock Distribution

An FPGA is the global clock distribution device on the carrier board. In conjunction with the Telecom Clock

protection switch, the FPGA distributes all necessary Telecom Clocks to or from the AMCs and the backplane.

TCLKA and TCLKC of any AMC can be driven by any backplane clock (CLK1A/B, CLK2A/B or CLK3A/B). TCLKB and

TCLKD of any AMC can drive any backplane clock. Any ATCA backplane clock can be used as the reference clock

input.

For more information on how to configure the clock distribution, refer to the AT8404 CLI Reference Manual.

3.1.6 AMC Bays

Up to four mid-size and single width or up to two mid-size and double width AMC bays for standard or custom

AMCs are implemented with B+ AMC connectors, depending on the board option.

Table 3-7: AMC Slot Types

Board option B1 B2 B3 B4

A Single width Single width Single width Single width

B - Double width - Double width

C - Double width Single width Single width

D Single width Single width - Double width

Because of the AMC slot storage interconnects (see section 3.1.2. Storage Interconnect) and for thermal reasons, the preferred Processor AMC slots are B1 and B2 and the preferred HDD-AMC slots are B3 and B4.

Table 3-8: AMC B1 Port Assignment

Port Region Connection

0 GbE GbE Switch 0/5

1 GbE -

2 Storage AMC B3 Port 2

3 Storage AMC B4 Port 2 / -*

4 Fabric AMC B2 Port 4

5 Fabric AMC B2 Port 5

6 Fabric AMC B2 Port 6

7 Fabric AMC B2 Port 7

8 Fabric GbE Switch 0/1

9 Fabric GbE Switch 0/2

10 Fabric GbE Switch 0/3

11 Fabric GbE Switch 0/4

12 Extended Update, APS Channel

13 Extended RTM, AMC_B1_P13

14 Extended RTM, AMC_B1_P14

15 Extended RTM, AMC_B1_P15

17 Extended RTM, AMC_B1_P17

18 Extended RTM, AMC_B1_P18

19 Extended RTM, AMC_B1_P19

24 AT8404 User Guide

Page 38

www.kontron.com

Table 3-8: AMC B1 Port Assignment (Continued)

Port Region Connection

20 Extended RTM, AMC_B1_P20

TCLKA Clock From Backplane

TCLKB Clock To Backplane

TCLKC Clock From Backplane

TCLKD Clock To Backplane

FCLKA Clock Fabric Reference Clock

* Depends on configuration

Table 3-9: AMC B2 Port Assignment

Port Region Connection

0 GbE GbE Switch 0/10

1 GbE -

2 Storage AMC B4 Port 2 / -*

3 Storage RTM SAS_0

4 Fabric AMC B1 Port 4

5 Fabric AMC B1 Port 5

6 Fabric AMC B1 Port 6

7 Fabric AMC B1 Port 7

8 Fabric GbE Switch 0/6

9 Fabric GbE Switch 0/7

10 Fabric GbE Switch 0/8

11 Fabric GbE Switch 0/9

12 Extended Update, APS Channel

13 Extended RTM, AMC_B2_P13

14 Extended RTM, AMC_B2_P14

15 Extended RTM, AMC_B2_P15

17 Extended RTM, AMC_B2_P17

18 Extended RTM, AMC_B2_P18

19 Extended RTM, AMC_B2_P19

20 Extended RTM, AMC_B2_P20

TCLKA Clock From Backplane

TCLKB Clock To Backplane

TCLKC Clock From Backplane

TCLKD Clock To Backplane

FCLKA Clock Fabric Reference Clock

* Depends on configuration

Hardware Description

25 AT8404 User Guide

Page 39

www.kontron.com

Table 3-10: AMC B3 Port Assignment

Port Region Connection

0 GbE GbE Switch 0/15

1 GbE -

2 Storage AMC B1 Port 2

3 Storage -

4 Fabric AMC B4 Port 4

5 Fabric AMC B4 Port 5

6 Fabric AMC B4 Port 6

7 Fabric AMC B4 Port 7

8 Fabric GbE Switch 0/11

9 Fabric GbE Switch 0/12

10 Fabric GbE Switch 0/13

11 Fabric GbE Switch 0/14

12 Extended Update, APS Channel

13 Extended RTM, AMC_B3_P13

14 Extended RTM, AMC_B3_P14

15 Extended RTM, AMC_B3_P15

17 Extended RTM, AMC_B3_P17

18 Extended RTM, AMC_B3_P18

19 Extended RTM, AMC_B3_P19

20 Extended RTM, AMC_B3_P20

TCLKA Clock From Backplane

TCLKB Clock To Backplane

TCLKC Clock From Backplane

TCLKD Clock To Backplane

FCLKA Clock Fabric Reference Clock

Hardware Description

26 AT8404 User Guide

Page 40

www.kontron.com

Table 3-11: AMC B4 Port Assignment

Port Region Connection

0 GbE GbE Switch 0/20

1 GbE -

2 Storage AMC B1 Port 3 / AMC B2 Port 2*

3 Storage RTM SAS_1

4 Fabric AMC B3 Port 4

5 Fabric AMC B3 Port 5

6 Fabric AMC B3 Port 6

7 Fabric AMC B3 Port 7

8 Fabric GbE Switch 0/16

9 Fabric GbE Switch 0/17

10 Fabric GbE Switch 0/18

11 Fabric GbE Switch 0/19

12 Extended Update, APS Channel

13 Extended RTM, AMC_B4_P13

14 Extended RTM, AMC_B4_P14

15 Extended RTM, AMC_B4_P15

17 Extended RTM, AMC_B4_P17

18 Extended RTM, AMC_B4_P18

19 Extended RTM, AMC_B4_P19

20 Extended RTM, AMC_B4_P20

TCLKA Clock From Backplane

TCLKB Clock To Backplane

TCLKC Clock From Backplane

TCLKD Clock To Backplane

FCLKA Clock Fabric Reference Clock

* Depends on configuration

Hardware Description

27 AT8404 User Guide

Page 41

Hardware Description

www.kontron.com

Gigabit Ethernet

Port 0 and ports 8 to 11 of each AMC are connected to the Ethernet switch. The Ethernet switch supports

1000BASE-BX Gigabit Ethernet.

Storage

Ports 2 and 3 of the AMC slots are reserved for storage connections to other AMC bays or the RTM (see section

3.1.2. Storage Interconnect).

PCI Express

Bays B1 and B3 and bays B2 and B4 implement a x4 direct connection on ports 4 to 7.

Automatic Protection Switching

Port 12 on each AMC bay is used as a 2.5 Gbps direct interconnect to the neighbouring Carrier Board via the

update channel for line card applications.

Interconnects to RTM

Each AMC Bay has seven generic interconnects to the RTM Zone 3 (ports 13 to 20).

3.1.7 IPMI

The AT8404 supports an intelligent hardware management system based on the Intelligent Platform Management Interface (IPMI) Specification 1.5. It provides the ability to manage the power, cooling and interconnect needs of intelligent devices, to monitor events and to log events to a central repository.

The main building blocks of the IPMI architecture of the AT8404 are:

• IPMC Intelligent Platform Management Controller

• FPGA (Field Programmable Gate Array)

3.1.7.1 IPMC

The IPMC controls all hotswap and E-Keying processes required by ATCA. It activates the board power supply

and enables communication with the AMC card and the RTM. The IPMC manages the Ethernet switch E-Keying

and the baseboard ATCA feature. The controller is connected to the ATCA shelf manager via IPMB bus on the

backplane.

All voltages and currents on the base board are monitored by the IPMC, including the management and AMC

supply. Six temperature sensors on the board make sure that thermal conditions are met. Following is a list

of the temperature sensors and their positions. For information on how to obtain sensor values and thresholds, refer to the AT8404 CLI Reference Manual.

Table 3-12: Temperature Sensors

Temperature Sensor Position

Temp PPC Inlet Lower board edge, rear third, near Unit Computer

Temp PPC Outlet Near Unit Computer

Temp AMC Inlet Lower board edge, middle of AMC area

Temp AMC Outlet Upper board edge, middle of AMC area

Temp PCB Outlet Upper board edge, rear third

Temp BCM Outlet Near GbE switch

28 AT8404 User Guide

Page 42

Hardware Description

www.kontron.com

The internal Flash memory of the IPMC is divided into two distinct parts, the IPMI firmware and the boot block.

This allows maintaining a permanent boot block and only erasing the IPMI firmware for upgrade procedure.

This is the key feature to achieve a fail-safe upgrade procedure.

The IPMC executes normally the IPMI firmware located in its internal Flash memory. During an update, the

IPMC transfers the new IPMI firmware to one of the two external menory banks. Then, it programs its internal

Flash memory with the new contents of the external memory and restarts. The restart does not affect board

operation in any way. In case of a failure, the IPMC memory is restored from the second external bank. A twostage (internal and external) watchdog mechanism enables a reliable fault detection.

3.1.7.2 FPGA

The Field Programmable Gate Array (FPGA) is the central device for all glue logic resources. It is configured

after the management voltages are stable by an external serial Flash device. The FPGA implements the Synchronous Clock Distribution (see section 3.1.5) and is part of the board management. It connects the Unit

Computer to the IPMC and handles the serial interfaces of Unit Computer, IPMC, RTM and the RS232 connector

on the front panel. The FPGA controls the LEDs for the whole board, handles the signals to control and to monitor the AMCs, the RTM and all payload devices connected to the FPGA and it is responsible for the power and

reset sequencing.

The FPGA provides a MultiBoot feature that allows to load one of two FPGA images, either the factory image

or the user image. In combination with a watchdog and fallback mechanism, this allows fail-safe in-field upgrades of the FPGA code.

3.1.8 RTM Interface

Management and I/O interfaces from the base board are routed to Zone 3 where a connector mates with the

RTM. This allows base boards to be quickly and reliably serviced without the issues associated with disconnecting and reconnecting multiple cable assemblies. The RTM connection is compliant to the PICMG 3.0 standard.

For the connection between the AT8404 and the RTM, three connectors with 40 differential pairs are used

(J30, J31 and J32).

Each AMC Bay has seven generic interconnects to the RTM Zone 3. Two SAS/SATA interfaces for mass storage

are implemented. There is a JTAG connection for FPGA update or Boundary Scan-Test. An I²C IPMI interface is

implemented for board management. The Unit Computer’s management interfaces (Fast Ethernet and RS232)

are also connected to the RTM. A GbE port allows connection to the GbE switch.

29 AT8404 User Guide

Page 43

Hardware Description

www.kontron.com

The Zone 3 connectors have the following pin assignments.

Table 3-13: J30 Assignment

J30 ROW A AB ROW B ROW C CD ROW D

1 12V GND 12V 12V GND 3V3_SUS

2 12V GND 12V 12V GND JTAG_AMC_EN#

3 SPA_RX# GND SPA_TX# JTAG_TDI GND JTAG_TDO

4 N.C. GND N.C. N.C. GND N.C.

5 RS232_TX1 GND N.C. RS232_TX2 GND N.C.

6 AMC_B2_P15_TX+ GND AMC_B2_P15_TX- AMC_B3_P15_TX+ GND AMC_B3_P15_TX-

7 AMC_B2_P15_RX+ GND AMC_B2_P15_RX- AMC_B3_P15_RX+ GND AMC_B3_P15_RX-

8 MNG_LAN_TXD+ GND MNG_LAN_TXD- MNG_LAN_RXD+ GND MNG_LAN_RXD-

9 SAS_1_TX+ GND SAS_1_TX- SAS_1_RX+ GND SAS_1_RX-

10 N.C. GND N.C. N.C. GND N.C.

J30 ROW E EF ROW F ROW G GH ROW H

1 N.C. GND RTM_PRNT# N.C. GND RTM_EN#

2 IPMB_SCL GND IPMB_SDA N.C. GND N.C.

3 JTAG_TMS GND JTAG_TCK JTAG_TRST GND TEST_ON#

4 RTML_TX GND RTML_RX RTML_CLK GND RST_PROG

5 AMC_B4_P15_RX+ GND AMC_B4_P15_RX- AMC_B1_P15_TX+ GND AMC_B1_P15_TX-

6 AMC_B4_P15_TX+ GND AMC_B4_P15_TX- SFP_SCL GND SFP_SDA

7 PPC_RST# GND N.C. AMC_B1_P15_RX+ GND AMC_B1_P15_RX-

8 MNG_LAN_CT GND JTAG_EN# FLASH_WE GND FLASH_WP

9 SAS_0_TX+ GND SAS_0_TX- SAS_0_RX+ GND SAS_0_RX-

10 GE22_TX+ GND GE22_TX- GE22_RX+ GND GE22_RX-

30 AT8404 User Guide

Page 44