Page 1

Sample Application Programs Guide Book

Agilent 4155C Semiconductor Parameter Analyzer

Agilent 4156C Precision Semiconductor Parameter Analyzer

Agilent Part No. 04156-90070

Printed in Japan January 2001

Edition 1

Page 2

Legal Notice

The information contained in this document is subject to change without notice.

Copyright © 2001 Agilent Technologies

This document contains information which is protected by copyright. All rights are

reserved. Reproduction, adaptation, or translation without prior written permission is

prohibited, except as allowed under the copyright laws.

• Product Warranty

Agilent Technologies warrant Agilent Technologies hardware, accessories and supplies

against defects in materials and workmanship for the period of one year from the

warranty start date specified below. If Agilent Technologies receive notice of such

defects during the warranty period, Agilent Technologies will, at its option, either

repair or replace products which prove to be defective. Replacement products may be

either new or like-new.

Warranty service of this product will be performed at Agilent Technologies. Buyer

shall prepay shipping charges to Agilent Technologies and Agilent Technologies shall

pay shipping charges to return the product to Buyer. However, Buyer shall pay all

shipping charges, duties, and taxes for products returned to Agilent Technologies from

another country.

Agilent Technologies do not warrant that the operation of Agilent Technologies

products will be uninterrupted or error free. If Agilent is unable, within a reasonable

time, to repair or replace any product to a condition as warranted, customer will be

entitled to a refund of the purchase price upon prompt return of the product.

The Agilent Technologies products may contain remanufactured parts equivalent to

new in performance or may have been subject to incidental use.

The warranty period begins on the date of delivery or on the date of installation if

installed by Agilent Technologies. If customer schedules or delays Agilent

Technologies installation more than 30 days after delivery, warranty begins on the 31st

day from delivery.

Warranty does not apply to defects resulting from (a) improper or inadequate

maintenance or calibration, (b) software, interfacing, parts or supplies not supplied by

Agilent Technologies, (c) unauthorized modification or misuse, (d) operation outside of

the published environmental specifications for the product, or (e) improper site

preparation or maintenance.

To the extent allowed by local law, the above warranties are exclusive and no other

warranty or condition, whether written or oral, is expressed or implied and Agilent

Technologies specifically disclaim any implied warranties or conditions of

merchantability, satisfactory quality, and fitness for a particular purpose.

Agilent Technologies will be liable for damage to tangible property per incident up to

the greater of $300,000 or the actual amount paid for the product that is the subject of

the claim, and for damages for bodily injury or death, to the extent that all such

damages are determined by a court of competent jurisdiction to have been directly

caused by a defective Agilent Technologies product.

2 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 3

To the extent allowed by local law, the remedies in this warranty statement are

customer’s sole and exclusive remedies. Expect as indicated above, in no event will

Agilent Technologies or its suppliers be liable for loss of date or for direct, special,

incidental, consequential (including lost profit or date), or other damage, whether based

in contract, tort, or otherwise.

For consumer transactions in Australia and New Zealand: the warranty terms contained

in this statement, except to the extent lawfully permitted, do not exclude, restrict or

modify and are in addition to the mandatory statutory rights applicable to the sale of

this product to you.

• Assistance

Product maintenance agreements and other customer assistance agreements are

available for Agilent Technologies products.

For any assistance, contact your nearest Agilent Technologies Sales Office.

• Certification

Agilent Technologies Inc. certifies that this product met its published specifications at

the time of shipment from the factory. Agilent further certifies that its calibration

measurements are traceable to the National Institute of Standards and Technology

(NIST), to the extent allowed by the Institute’s calibration facility, and to the

calibration facilities of other International Standards Organization members.

Printing History

Edition 1: January 2001

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 3

Page 4

In This Manual

This manual describes some sample application programs and setup files, which will be

helpful for creating your own applications using Agilent 4155C/4156C.

All programs and setup files described in this manual are stored on the Sample Application

Program Disk (DOS formatted, 3.5-inch diskette) that is furnished with your

4155C/4156C. All programs are written in the Instrument BASIC, and ready to run in the

4155C/4156C’s built-in Instrument BASIC environment.

This manual covers the following applications:

• V- RA M P

• J-RAMP

• SWEAT

• GO/NO-GO Test

• HCI Degradation Test

• Charge Pumping

• Flash EEPROM Test

• TDDB

• Electromigration

CAUTION These programs are only examples, so you may need to modify these programs and setup

files for your own application before executing. If these example programs damage your

devices, Agilent Technologies is NOT LIABLE for the damage.

NOTE You should copy all files in the Sample Application Program Disk to a diskette that you

will use as your working diskette, and keep the original diskette as backup.

4 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 5

Contents

1. V-RAMP

Theory of V-Ramp Test Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

V-Ramp Test Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

Initial Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Post Stress Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Ramp Stress Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Failure Categorization and Data Recording . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

Basic Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

Methodology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

Required Equipment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-16

Files on the Diskette . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-16

Executing the VRAMP Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-17

Flowchart of Sample VRAMP Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-18

Customization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-20

Using an External Computer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-20

Specifying Setup File to Load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-21

File for Saving Measurement Results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-21

Setting up Input Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-22

Searching for 10 ¥ Iexpect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-23

Measurement Setups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-24

Setups for Initial and Post Stress Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-24

Setups for Ramped Stress Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-24

2. J-RAMP

Theory of J-Ramp Test Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

J-Ramp Test Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Initial Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

J-Ramp Stress Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

Post Stress Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

Failure Categorization and Data Recording . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

Basic Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

Methodology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

Required Equipment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-20

Program Files Required . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-20

Executing the JRAMP Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-20

Flowchart of Sample JRAMP Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

Customization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24

Using an External Computer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24

Specifying Setup File to Load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-25

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 Contents - 1

Page 6

Contents

File for Saving Measurement Results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-25

Setting up Input Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26

When SMU Lacks Power to Break Oxide . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-27

Measurement Setups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-28

Setups for Initial and Post Stress Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-28

Setups for Ramped Stress Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-28

Proof of Equations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-36

Step Increase Factor (F). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-36

Step Time (Step_time) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-36

Current Stop Value (Istop) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-36

3. SWEAT

SWEAT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

Input Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

Initial Resistance (Rinit) Measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

CTTF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

Rfail . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

Exit Condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

Output Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

Basic Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

Methodology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

Required Equipment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

Files on the Diskette . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

Sample SWEAT Program Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

Customization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

Using External Computer or Built-in Controller . . . . . . . . . . . . . . . . . . . . . . 3-13

Specifying Setup File to Load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

File for Saving Measurement Results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

Setting up Input Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15

Setting up Input Parameters Related to CTTF Calculation . . . . . . . . . . . . . . . 3-15

How to Reduce the Settling Time of CTTF . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

Defining JSTART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-18

Current Adjustment Routine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-18

Setup files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19

Setup File for Initial Resistance Measurement . . . . . . . . . . . . . . . . . . . . . . . . 3-19

Setup File for Stress/Resistance Measurement . . . . . . . . . . . . . . . . . . . . . . . . 3-19

Contents - 2 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 7

Contents

4. Go/NO-GO

GONOGO Sample Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

Basic Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

Required Equipment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

Files on the Diskette . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

Sample Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

Viewing All Curves while Measurement is in Progress . . . . . . . . . . . . . . . . . 4-10

Viewing Only Results while Measurement is in Progress . . . . . . . . . . . . . . . . 4-11

Viewing a Particular Measurement Curve . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

Changing Limits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-13

Displaying Statistical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-13

Exporting Data to Spreadsheet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-14

Customization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

Hints to Use with Handler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-21

5. HCI Degradation Test

Hot-Carrier-Induced (HCI) Degradation Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

Determining Stress Bias Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Selecting Test Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Initial Characterization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Parameter Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

Stress Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

Interim Characterization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

Stress Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

Technical Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

HCI Degradation Test Data Analysis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

Basic Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

Methodology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

Input Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

HCI Degradation Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

HCI Degradation Data Analysis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-16

Required Equipment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-17

Files on the Diskette . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-18

Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-19

Sample HCI Degradation Test Program (DCDAHC) Overview . . . . . . . . . . . 5-27

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 Contents - 3

Page 8

Contents

Sample HCI Degradation Test Data Analysis Program (ANALYSIS) Overview 5-30

Customization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-32

Using External Computer or Built-in Controller . . . . . . . . . . . . . . . . . . . . . . 5-32

Modifying and Specifying Setup File to Load . . . . . . . . . . . . . . . . . . . . . . . . 5-33

Changing File for Saving Measurement Results . . . . . . . . . . . . . . . . . . . . . . . 5-34

Changing Input Parameters for HCI Degradation Test . . . . . . . . . . . . . . . . . . 5-35

To Change Pin Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-37

To Change Number of Test Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-37

Changing the Cumulative Stress Times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-38

Skipping Determination of Gate Stress Bias Condition . . . . . . . . . . . . . . . . . 5-38

Reducing the Interval between Stress and Interim Measurement . . . . . . . . . . 5-39

Selecting Parameter Shift Graphs to Draw . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-39

If You Don't Use Switching Matrix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-40

Using Another Switching Matrix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-40

Performing HCI Degradation Test with AC Stress . . . . . . . . . . . . . . . . . . . . . 5-41

Performing Reverse Mode Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-42

Changing Input Parameters for Test Data Analysis . . . . . . . . . . . . . . . . . . . . 5-43

Not to Pause Program after each Tdc Extraction . . . . . . . . . . . . . . . . . . . . . . 5-43

Changing File Name to save Calculated Average Tdc . . . . . . . . . . . . . . . . . . 5-43

Setup Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-44

Setup File for Id-Vd Measurement to Determine Drain Stress Voltage . . . . . 5-44

Setup File for Ib-Vg Measurement to Determine Gate Stress Voltage . . . . . . 5-46

Setup File for Gate Leakage Current Measurement . . . . . . . . . . . . . . . . . . . . 5-49

Setup File for Initial/Interim Characterization . . . . . . . . . . . . . . . . . . . . . . . . 5-52

Setup File for DC Stress . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-55

Setup File for AC Stress . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-56

6. Charge Pumping

Charge Pumping Methods . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

Square Pulse Method . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

Triangular Pulse Method . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

Trapezoidal Pulse Method . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

Equipment Required . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

Square Pulse Method . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

To Extract Interface-state Density . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

Program Files Required . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

Sample Setup File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

To Execute the Sample Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-10

Square Pulse Method without Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

Requirement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

Contents - 4 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 9

Contents

Sample Setup File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

To Execute the Measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-16

Triangular Pulse Method . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-17

To Extract Interface-state Density . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-18

To Extract Capture Cross Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-19

Program Files Required . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-20

Sample Setup File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-20

To Execute the Sample Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-24

Trapezoidal Pulse Method . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-27

To Extract Interface-state Density . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-28

Program Files Required . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-30

Sample Setup File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-30

To Execute the Sample Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-33

Program Modification Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-36

To Change the Initial Value of Input Parameters . . . . . . . . . . . . . . . . . . . . . . . 6-36

To Change the Measurement Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-42

To Change the Destination of the File Operation . . . . . . . . . . . . . . . . . . . . . . 6-45

7. Flash EEPROM Test

Program Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

Device Connection for NOR type flash EEPROM . . . . . . . . . . . . . . . . . . . . . . 7-3

Device Connection for NAND type flash EEPROM . . . . . . . . . . . . . . . . . . . . . 7-4

Main Program. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

Stress_loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

Vth_meas . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-8

Program Customization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

Subprogram “Test_setting” . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

Measurement setup file for Vth measurement (for NOR type) . . . . . . . . . . . . 7-10

Stress setup file for write pulse of NOR type. . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

Stress setup file for erase pulse of NOR type. . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

Stress setup file for write pulse of NAND type . . . . . . . . . . . . . . . . . . . . . . . . 7-12

Stress setup file for erase pulse of NAND type . . . . . . . . . . . . . . . . . . . . . . . . 7-12

Program Listing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-13

8. Time Dependent Dielectric Breakdown (TDDB)

Application Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

Customization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-4

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 Contents - 5

Page 10

Contents

9. Electromigration

Application Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-3

Customization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-4

Contents - 6 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 11

1V-RAMP

Page 12

V-RAMP

Voltage-Ramped (V-Ramp) test is one of the Wafer Level Reliability (WLR) tests, which is

used to evaluate device reliability on a wafer. This test can provide quick evaluation data

for estimating the overall reliability of thin oxides, and this data can be used to improve the

thin oxide manufacturing process.

With the thickness of oxide shrinking along with device geometries, creating a reliable thin

oxide has become an important issue. The integrity of the thin oxide in a MOS device is a

dominant factor in determining the overall reliability of a micro-circuit. The V-Ramp test

can promptly give useful feedback to the manufacturing process about oxide reliability.

This operation manual covers a sample V-Ramp program running on Agilent 4155/4156,

and how to use and customize the program. The program is written in the Instrument

BASIC (IBASIC), and is ready to run on the built-in IBASIC controller of the 4155/4156.

“Theory of V-Ramp Test Procedure” describes basic theory, procedure, and terminology of

the V-Ramp test.

“Basic Operation” describes the V-Ramp sample program. Included are V-Ramp

methodology using the 4155/4156, how to execute the sample program, and program

overview.

“Customization” describes how to customize the sample program. This is very helpful

because you probably need to modify the sample program to suit your test device.

“Measurement Setups” shows the 4155/4156 page settings that are stored in the setup files.

1-2 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 13

V-RAMP

Theory of V-Ramp Test Procedure

Theory of V-Ramp Test Procedure

This section describes the Voltage-Ramped (V-Ramp) Test procedure. Included are basic

theory, procedure, and terminology of V-Ramp test. The V-Ramp test procedure is based on

JEDEC standard No.35.

V-Ramp Test Overview

V-Ramp test measures the breakdown voltage (Vbd) and breakdown charge (Qbd) of thin

oxide capacitors, which you designed as test structures on the wafer. These results are used

to evaluate the oxide integrity. The higher the Vbd and Qbd measured by this test, the better

the integrity of the oxide on wafer.

You extract these two parameters from a large amount of test structures and extracted

parameters are used for standard process control to quickly evaluate oxide integrity.

In the V-Ramp test, an increasing voltage is forced to the oxide capacitor until the oxide

layer is broken. Breakdown voltage (Vbd) is defined as the voltage at which breakdown

occurs. And breakdown charge (Qbd) is the total charge forced through the oxide until the

breakdown occurs.

Figure 1-1 shows a simplified flowchart of V-Ramp test.

Figure 1-1 Simplified Flow Diagram of V-Ramp Test

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 1-3

Page 14

V-RAMP

Theory of V-Ramp Test Procedure

The V-Ramp test consists of three tests: initial test, ramp stress test, and post stress test.

In the initial test, normal operating voltage is applied to the oxide capacitor, then leakage

current through the capacitor is measured to check for initial failure.

In the ramp stress test, linear ramped voltage is applied to the capacitor, and the current is

measured.

The post stress test is for confirming that failure occurred during the ramp stress test. The

normal operating voltage is applied to the oxide capacitor again, and leakage current is

measured under the same conditions as the initial test.

After the tests, the test results must be analyzed and saved (data recording).

Before performing the V-Ramp test, test conditions must satisfy the following:

• Gate bias polarity is in accumulated direction. That is, negative (minus) voltage is

applied to gate conductor for P-type bulk, and positive (plus) voltage is applied for

N-type bulk.

• Diffusions and wells (if any) must be connected to substrate.

• Temperature is in 25 ± 5 °C range.

Initial Test

Initial test is to confirm that the oxide capacitor is initially good. If leakage current of that

capacitor exceeds 1 mA, it is categorized as initial failure.

For example, when you test a TTL-level oxide capacitor, constant voltage of -5 V is

applied to that capacitor, and leakage current is measured. If the leakage current is more

than 1 mA, that capacitor is an initial failure.

Post Stress Test

The post stress test checks the oxide status after the ramp stress test. If the oxide is broken,

proper ramp stress was applied to the oxide capacitor. If not, maybe the ramp stress was not

applied correctly.

To check the oxide status, the normal operating voltage is applied to the oxide capacitor

(same as initial test), then leakage current is measured. The leakage current (I

indicates the following:

• If I

• If I

> 1 mA:

leak

The oxide was broken by the applied ramped voltage.

< 1 mA:

leak

The oxide was not broken by the applied ramped voltage.

If the applied ramped voltage reached the maximum electric field, the testing was

probably faulty: for example, the ramped voltage was not applied to the oxide due to an

open circuit.

leak

) value

For example, if you test a TTL level oxide capacitor, constant voltage of -5 V is applied to

that capacitor, then leakage current is measured. If the leakage current is more than 1 mA,

the capacitor was properly broken.

1-4 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 15

V-RAMP

Theory of V-Ramp Test Procedure

Ramp Stress Test

A linear ramped voltage or a linear stepped voltage, which is approximately ramped

voltage, is applied to the oxide capacitor. While the ramped voltage is forced, the current

through the oxide is measured.

The ramped voltage is stopped when one of the following conditions occurs:

• Current through the oxide exceeds ten times the expected current. The expected current

is calculated from the applied voltage and structure of oxide capacitor. For example, the

expected current density J for a 200 angstrom oxide capacitor is calculated from the

equation for Fowler-Nordheim current as follows:

2 B

æö

JAE

Where, A and B are constants in terms of effective mass and barrier height.E is electric

field.

exp×=

---

–

èø

E

• Current through the oxide exceeds the current compliance determined by the current

density compliance limit of 20 A/cm

2

.

• Electric field generated by the applied voltage exceeds 15 MV/cm. This typically

indicates faulty testing.

Figure 1-2 shows the concept of Vbd and Qbd. In the graph, left vertical axis shows current

through the oxide, right vertical axis shows voltage applied to the oxide capacitor, and

horizontal axis shows time.

When the current through the oxide reaches 10 times the expected current, the ramped

voltage is stopped, and the applied voltage at this point is the breakdown voltage (Vbd).

Breakdown charge (Qbd) is calculated by integrating the current through the oxide:

Tbd

=

Qbd Imeas t() td

ò

Tstart

Figure 1-2 Concept of Breakdown Voltage and Charge

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 1-5

Page 16

V-RAMP

Theory of V-Ramp Test Procedure

Figure 1-3 shows the two ways to apply the voltage: linear ramped voltage or linear

stepped voltage.

Note that the applied ramped voltage must satisfy the following conditions:

• Ramp rate is in range from 0.1 MV/cm×s to 1.0 MV/cm×s.

• Current measurement interval is 0.1 s or less.

• Ramped voltage starts at normal operating voltage or lower.

• Ramped voltage stops if electric field reaches 15 MV/cm.

If you use the linear stepped voltage, the following conditions must be satisfied also:

• Step value of ramped voltage is 0.1 MV/cm or less.

• Current measurement must be performed at least once for every step.

Figure 1-3 Linear Ramped and Linear Stepped Voltage

1-6 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 17

Failure Categorization and Data Recording

According to the measurement results, the oxide status is categorized as follows and

recorded:

Initial Failure: Failed the initial test. Indicates initially defective oxide

Catastrophic Failure: Failed ramped and post stress tests. Indicates that oxide

Masked Catastrophic Failure: Did not fail ramped stress test, but failed post stress test.

Non-catastrophic Failure: Failed ramped stress test, but not post stress test.

Other Did not fail ramped stress test or post stress test.

The failure category is recorded for each test device. If the catastrophic failure is observed,

breakdown voltage (Vbd) and breakdown charge density (q

recorded.

Table 1-1 shows the oxide failure categories.

Table 1-1 Oxide Failure Categories

V-RAMP

Theory of V-Ramp Test Procedure

capacitor. Other tests should not be performed.

capacitor was properly broken by the ramped stress test.

= Qbd/Area) are also

bd

Failure Category Initial Test

Ramp Stress

Test

Post Stress Test

Initial Fail n.a. n.a.

Catastrophic

a

Pass Fail Fail

Masked Catastrophic Pass Pass Fail

Non-catastrophic Pass Fail Pass

Other Pass Pass Pass

a. Vbd and qbd are also recorded.

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 1-7

Page 18

V-RAMP

Basic Operation

Basic Operation

This section covers the following for using an 4155/4156 to perform V-Ramp Test:

required equipment, required files, methodology, how to execute the sample program, and

sample program overview.

Methodology

The entire V-Ramp Test procedure can be performed by executing the VRAMP sample

program on the built-in IBASIC controller of the 4155/4156.

As explained in “Theory of V-Ramp Test Procedure”, the V-Ramp test consists of three

measurement parts and an analysis part. Each measurement part executes three steps as

follows:

1. Loads the measurement setup file into the 4155/4156 execution environment.

2. Changes some of the measurement or analysis parameters on the setup pages.

3. Executes the measurement.

The VRAMP program executes the above three steps for each test: initial test, ramp stress

test, and post stress test. Using the measurement setups (step 1 above) loaded from a file

reduces the length and complexity of the program. For details, see Programmer's Guide.

Measurement setups, which are loaded into the 4155/4156 execution environment, were

previously developed and saved to measurement setup files on the diskette. You can easily

modify the measurement setup information in fill-in-the-blank manner in the 4155/4156

execution environment. The VRAMP sample program is also saved to the diskette. You

can easily modify the sample program by using the editor in the built-in IBASIC

environment.

The VRAMP sample program assumes that the built-in IBASIC controller of the

4155/4156 is used, but you can also use another controller, such as HP BASIC running on

an external computer. To do so, you must modify the sample program for your

environment. See “Customization” on how to modify the program to run on an external

controller.

Initial Test

The initial test makes sure the oxide capacitor is initially good by applying the normal

operating voltage (Vuse), then measuring the leakage current (I

I

exceeds 1 mA, the oxide capacitor is categorized as "initial failure".

leak

The sample program assumes that SMU1 and SMU4 are connected to the oxide capacitor

as shown in Figure 1-4.

) through the oxide. If

leak

1-8 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 19

V-RAMP

Basic Operation

For the initial test, the sample program does as follows:

1. Sets up the 4155/4156 according to the VRSPOT.MES setup file, which the sample

program previously loaded from the diskette into internal memory MEM1.

2. Sets up SMU1 to constant voltage Vuse for PMOS device, or -Vuse for NMOS

device. Vuse value is specified previously in the sample program, and reset on the

MEASURE: SAMPLING SETUP page by OUTPUT statement (line 2550 of the

sample program).

3. Forces voltage from SMU1, then measures current after the HOLD TIME, which was

setup by VRSPOT.MES setup file described next.

4. Checks if current through the oxide Ig exceeds 1 mA. If so, the sample program aborts

further testing.

The following are main points about the setup by the VRSPOT.MES setup file:

• On CHANNELS: CHANNEL DEFINITION page (see Figure 1-13)

• MEASUREMENT MODE is set to SAMPLING.

• SMU1 and SMU4 are set to be constant voltage sources.

• Ig is defined as name of current measured by SMU1.

• On MEASURE: SAMPLING SETUP page (see Figure 1-5)

• NO. OF SAMPLES is set to 1 to execute the measurement once.

• HOLD TIME is set to 2.00 s to allow the output voltage to stabilize.

• SMU4 is set to force a constant 0 V.

• STOP CONDITION is enabled, NAME is set to Ig, THRESHOLD is set to 1 mA,

and EVENT is set to Val > Th.

So, the measurement will stop if the current through the oxide (Ig) exceeds 1 mA.

If so, the sample program will abort further testing.

Figure 1-4 Simplified Measurement Circuit and Output Voltage of Initial Test

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 1-9

Page 20

V-RAMP

Basic Operation

Figure 1-5 MEASURE: SAMPLING SETUP Page for Initial Test

Ramp Stress Test

After the initial test, the sample program executes the ramp stress test. Linear stepped

voltage is applied to the oxide.

The measurement setup for the ramp stress test is stored in the VRSWEP.MES setup file on

the diskette. At the beginning of the sample program, this setup is loaded into internal

memory (MEM2). Then, at the beginning of the ramp stress test, the sample program loads

this setup into the 4155/4156.

To force proper stepped voltage, the sample program and VRSWEP.MES set the following:

• SMU channel definition (see Figure 1-6):

SMU4 is set to force a constant 0 V, and SMU1 is set to voltage sweep mode.

• Constant step interval time (see Figure 1-8):

Step interval time of output sweep voltage must be constant.

• Measurement stop mode:

If the current through the oxide reaches the specified compliance, the voltage sweep

and measurement stops.

• Auto-analysis and user functions:

After the measurement, the 4155/4156 executes analysis automatically to search for

Vbd, and to calculate Qbd.

1-10 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 21

SMU Channel Definition.

The sample program assumes the connection between the SMUs and the oxide capacitor as

shown in Figure 1-6. SMU4 is set to force a constant 0 V, and SMU1 is set to voltage

sweep mode by the VRSWEP.MES setup as shown in Figure 1-7.

Figure 1-6 Simplified Measurement Circuit of Ramp Stress Test

V-RAMP

Basic Operation

Figure 1-7 CHANNELS: CHANNEL DEFINITION Page for Ramp Stress Test

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 1-11

Page 22

V-RAMP

Basic Operation

Constant step interval time.

To keep a constant step interval time for the voltage sweep and measurement, triggering

and measurement ranging techniques are used. VRSWEP.MES sets the measurement

ranging mode to FIXED, so the time between measurements does not vary due to range

changing.

VRSWEP.MES enables the TRIG OUT function, and the sample program calculates and

sets values so that the step interval time becomes constant as shown in Figure 1-8. The step

interval time (Step_time) is the delay time (Step_delay_t) plus step delay time

(Step_keep_t). Strictly speaking, the sample program calculates these as follows:

Step_time=Vstep/(Ramp_rate*Tox)-1.2ms+0.1ms

Step_delay_t=Step_time/2

Step_keep_t=Step_time-Step_delay_t

Where,

• 1.2 ms is overhead time associated with the delay time for voltage sweep measurement,

when the WAIT TIME field is set to 0 (zero). So, do not set another value in this field.

• 0.1 ms is overhead time associated with the TRIG OUT function.

• Ramp rate (Ramp_rate), oxide thickness (Tox), and step voltage (Vstep) are

specified in lines 1800 to 1840 of the sample program.

The start voltage (Vstart), stop voltage (Vstop), and step voltage (Vstep) are

specified in sample program in lines 1830 to 1850. For NMOS devices, the ramp stress test

subprogram actually sets the opposite polarity for these values by using the Tp variable.

Measurement stop mode.

NOTE The JEDEC standard says that the ramp stress test should abort when the current through

the oxide reaches 10 times the expected current (Iexpect). But this sample program

aborts when the current reaches current compliance (Igcomp). The Iexpect and

Igcomp values are specified in lines 1860 and 1870 of the sample program, and must

meet the following condition: Igcomp ³ Iexpect ´ 10.

VRSWEP.MES file sets the sweep stop condition to SWEEP STOP AT COMPLIANCE as

shown in the Figure 1-10.

Figure 1-8 Output Sweep Voltage for Ramp Stress Test

1-12 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 23

V-RAMP

Basic Operation

Figure 1-9 MEASURE: MEASURE SETUP and OUTPUT SEQUENCE Pages for Ramp Stress

Test

Figure 1-10 MEASURE: SWEEP SETUP Page for Ramp Stress Test

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 1-13

Page 24

V-RAMP

Basic Operation

Auto-analysis and user functions.

The sample program does the following:

1. Sets up the maximum and minimum values for graph axes: X, Y1, and Y2. Lines 2940

to 2980.

2. Performs the measurement. Line 3020.

3. Moves marker to maximum Ig, and saves value to Igmax. Lines 3100 to 3170.

4. Moves marker to position where Ig = Iexpect*10. Line 3200.

5. If compliance was reached or if Igmax ³ Iexpect*10, the sample program reads

the value of Vbd and Qbd at present marker position. Lines 3250 to 3320. Where Vdb

and Qbd are specified as described below.

The VRSWEP.MES setup file defines user functions on the CHANNELS: USER

FUNCTION DEFINITION page (see Figure 1-20) as follows:

Table 1-2 User Functions for Ramp Stress Test

Name Units Definition

Time (sec)

@INDEX * 1

a

Vbd (V) @MY2

Qbd (Q) INTEG(Ig,Time)

a. This is a temporary value. Value of Time is redefined by line 2810 of the

sample program.

The above user function calculates Qbd as follows:

Tbd

Qbd Imeas t() td

==

ò

Tstart

N

1

-- - Imeas

å

2

i 2=

Imeas

+()TiT

i

i 1–

–()´

i 1–

Where, N is step number when the breakdown occurs.

1-14 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 25

Post Stress Test

Post stress test checks the oxide status after the ramp stress test.

The methodology of the post stress test is the same as for initial test. The normal operating

voltage (Vuse) is applied to the oxide, then the leakage current (I

For the measurement circuit, connections, and measurement setups, see “Initial Test”.

Failure Categorization

Table 1-3 shows the oxide failure categories that are determined by the sample program.

The failure category is displayed for each device, and Vbd, Qbd, and qbd are also

displayed.

The measured data and measurement settings are saved in a file.

Table 1-3 Oxide Failure Categories

Basic Operation

) is measured.

leak

V-RAMP

Category Initial Test Ramp Stress Test

Initial I

Catastrophic I

> 1 mA n.a. n.a.

meas

£ 1 mAI

meas

meas

³ I

expect

I compliance reached.

Masked Catastrophic I

£ 1 mAI

meas

meas

< I

expect

I compliance not reached.

Non-catastrophic I

£ 1 mAI

meas

meas

³ I

expect

I compliance reached.

Other I

£ 1 mAI

meas

meas

< I

expect

I compliance not reached.

´ 10, or

´ 10, and

´ 10, or

´ 10, and

Post Stress

Test

I

> 1 mA

meas

I

> 1 mA

meas

I

£ 1 mA

meas

I

£ 1 mA

meas

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 1-15

Page 26

V-RAMP

Basic Operation

Required Equipment

The following equipment is required to use the V-Ramp sample program:

• Agilent 4155 or Agilent 4156 Semiconductor Parameter Analyzer

• Two triaxial cables

• Probe station

• This operation manual

• Diskette that contains sample program file and two setup files

Files on the Diskette

The following files are stored in the sample diskette:

VRAMP V-Ramp sample program. This is an IBASIC program file saved in

ASCII format.

VRSPOT.MES Measurement setup file for initial and post stress test.

VRSWEP.MES Measurement setup file for ramp stress test.

1-16 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 27

V-RAMP

V

Basic Operation

Executing the VRAMP Program

Before executing the program, you may need to customize the program to suit your test

device. See “Customization”.

To execute the sample program, use the following procedure:

1. Connect your 4155/4156 to your test device. See Figure 1-4.

2. Turn on your 4155/4156.

3. Insert the diskette containing the VRAMP program into the built-in 3.5 inch flexible

disk drive.

4. Press

Display key in the IBASIC area of the front panel until All IBASIC screen is

displayed.

5. Load the VRAMP program. Type: GET "VRAMP" and press

6. Press

RUN key in the IBASIC area of the front panel to start the program.

Measurement results similar to Figure 1-11 will be displayed on the GRAPHICS page of

the 4155/4156.

Figure 1-11 An Example of Measurement Results

GRAPH/ LI ST: GRAPHI CS SHORT 9 4OCT 23 1 0: 5 3A M

ol t ag e Ramp Sweep Meas ur emen t

MARKER( 28. 1250 000 sec - 50. 0048mA - 27. 450 V )

( A) Qbd - 13. 059987500mQ ( V)

-1.00 -40. 0

Ig Vg

decade ------

/div /div

Vbd - 27. 4 50000000 V

Enter key.

Vs ub

0. 00 V

100. mA

VSU1

0. 00 V

o

VSU2

0. 00 V

*

- 1. 00p -5. 00

0. 00 Ti me ( sec) 5. 00 / di v 43. *

STATUS:008000(8------- -)

AXI S

Y1

MA R K E R/

CURSOR

L I NE SCAL I NG DI SPL AY

SETUP

SWEEP

SETUP

TI MI NG

SET UP

B

CONST

SETUP

Note that this example is obtained when the maximum electric field is set to 50 MV/cm.

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 1-17

Page 28

V-RAMP

Basic Operation

Flowchart of Sample VRAMP Program

Figure 1-12 shows flowchart of sample VRAMP program and corresponding subprogram

names.

Figure 1-12 Flowchart of Sample VRAMP Program

1-18 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 29

V-RAMP

Basic Operation

The following provides a brief description for each subprogram.

Test_setting Specifies and checks the parameter values. These are values that the

program will set directly instead of some of the setup file values.

Get_file Loads measurement setup files from the diskette into internal memory:

spot measurement setup into MEM1, and sweep measurement setup

into MEM2. Having the measurement setups in internal memory

reduces the measurement time.

Init_fin_test Executes the spot measurement for initial test or for post stress test.

First parameter specifies the test: Init is for initial test, and Fin is

for post stress test. The measurement results are returned to the second

parameter.

Judge Categorizes failure according to measurement results of initial, ramped

stress, and post stress tests. If the failure is initial failure, this

subprogram aborts the program.

Sweep_test Executes sweep measurement for ramped stress test, then returns the

result flag, Vbd, and Qbd to the three parameters. The measurement

result data is temporarily stored in internal memory (MEM3).

Save_data Saves measurement result data (that is in MEM3) to a file on the

diskette.

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 1-19

Page 30

V-RAMP

Customization

Customization

This section describes how to customize the sample program to suit your test device.

Using an External Computer

This sample program (VRAMP) is assumed to run on the Instrument BASIC that is built

into the 4155/4156. The 4155/4156 is used as both the measurement instrument and the

controller running IBASIC, so VRAMP sets device selector 800. On the following three

lines, the 4155/4156 is assigned and interrupt from it is enabled as follows:

1470 ASSIGN @Hp4155 TO 800

:

1540 ON INTR 8 CALL Err_check

1550 ENABLE INTR 8;2

If you use an external controller (that can run HP BASIC environment) to control the

4155/4156, you need to modify a few lines of the sample program. For example, if you use

HP BASIC/WS on an HP 9000 Series 300 computer, you only need to modify lines the

above three lines as follows:

In this case, the 4155/4156 has GPIB address 17 and is not used as the system controller,

and is connected to the built-in GPIB of the HP 9000 series 300 controller with an GPIB

cable. Use the following procedure to set the GPIB address and system mode:

1. Turn on your 4155/4156.

2. Press

3. Select MISCELLANEOUS softkey.

4. Move the field pointer to the "415x is " field, then select the NOT CONTROLLER

5. Move the field pointer to the "415x" field in the GPIB ADDRESS area, then enter: 17.

1-20 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

System key.

softkey.

Page 31

V-RAMP

Customization

System Mode

GPIB Address

SYSTEM: MI SCELL ANEOUS 99 DEC10 0 4 : 42 PM

* 41 56 B i s * POWER L I NE FREQUENCY

NOT S YS T EM CONT ROL L E R 50 H z

* GPI B ADDRESS *414156B NETWORK SETUP

4156B 17 HOST NAME

HARD COPY 1 I P A DDRES S 0 . 0. 0. 0

* REMOT E CONT ROL GROU P I D 1 0 0

COMMAND SET 4155/ 56

*CLOCK TEXT OUT -h

YMDHM GRAPHOUT-h-l

19 99 1 2 10 16 4 2 SERVER T YPE BSD

*SYSTEM SETUP *NETWORK DRI VE SETUP

BEEP ON LABEL

SCREEN SAVE 30 mi n I P ADDRESS 0. 0. 0. 0

LP TI MEOUT 300 s ec DI RECTORY /

NOT SYSTEM CONTROLLER

Sel ect Syst em Cont r ol Mode wi t h sof t key or r ot ar y knob.

FI LER MI SCEL-

LANEOUS

CONFI G CAL I B/

USER I D 200

* NETWORK PRI NTER SETUP

PRI NTER

IP ADDRESS 0.0.0.0

DI AG

PRI NT

SETUP

COLOR

SETUP

Specifying Setup File to Load

CON-

TROLLER

NOT

CON-

TROLLER

Two setup files are used to set up the 4155/4156 for the V-Ramp test: one is used for initial

and post stress tests, and the other is for ramp stress test.

Filenames of these setups are defined on the following lines:

1730 Init_file$="VRSPOT.MES" !Spot Measurement Setup File Name

1740 Sweep_file$="VRSWEP.MES" !Sweep Measurement Setup File Name

If you want to use other setup files, store the setup files on the diskette, then modify the

filenames on the lines above.

File for Saving Measurement Results

The following lines specify the filename for the measurement results file. The filename

starts with "D", then HHMMS, then ends with ".DAT". Where HH is hour, MM is minute,

and S is second (tens digit only).

1750 Save_file$=TIME$(TIMEDATE) !File Name for saving measurement

results

1760 Save_file$="D"&Save_file$[1,2]&Save_file$[4,5]&Save_file$[7,7]&".D

AT"

The following line commands the 4155/4156 to create the specified file on the diskette,

then stores the result data in the file.

3860 OUTPUT @Hp4155;":MMEM:STOR:TRAC DEF,'"&Save_file$&"','DISK'"

For example, "D09344.DAT" file that contains measurement data is created on the

diskette. This filename means the "data file created at 9:34 4x seconds."

To change to your desired filename, you only need to edit line 1760.

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 1-21

Page 32

V-RAMP

Customization

Setting up Input Parameters

Input parameter values are specified on the following lines. These are values that the

sample program will set directly instead of using some of the setup file values. You can

easily modify the values by editing these program lines.

1780 Type$="NMOS" ! Type NMOS -- Pbulk, PMOS -- Nbulk

1790 Vuse=5 ! Vuse (V)

1800 Ramp_rate=.5*1.E+6 ! Ramp rate (MV/cm*s)

1810 Tox=160*1.E-8 ! Oxide Thickness (cm)

1820 Area=.001 ! Gate Area (cm^2)

1830 Vstart=5 ! Start voltage (V)

1840 Vstop=24 ! Stop voltage (V)

1850 Vstep=.05 ! Step voltage (V)

1860 Iexpect=.003 ! Expected breakdown current (A)

1870 Igcomp=.05 ! Ig compliance (A)

Parameter Default Description

Type$

NMOS

a

Bulk type: NMOS is for P bulk and PMOS is for

N bulk

Vuse 5 (V) Normal operating voltage for the device

Ramp_rate

Tox

Area

5

5.0´10

(MV/cm×s)

1.60´10

0.001 (cm

-6

(cm)

2

)

Ramp rate of stepped voltage

Thickness of oxide

Area of target oxide

Vstart 5 (V) Start voltage

Vstop 24 (V) Stop voltage

Vstep 50 (mV) Step voltage

Iexpect 3 (mA) Expected current through the oxide

Igcomp 50 (mA) Current compliance through the oxide

a. If type is NMOS, opposite polarity values for the voltages are actually used

later in the program by using the tp parameter, which is set to -1 in line 1880.

1-22 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 33

V-RAMP

Customization

Searching for 10 ´ Iexpect

In the VRAMP program, Iexpect is set to 0.003 A in line 1860 of the program.

However, this is a very simple method and might not give accurate results.

Iexpect is the expected current through the oxide, and is a function of the electric field E.

So, the actual Iexpect depends on the applied voltage.

To get more accurate results, you can plot a graph of Iexpect versus Vg by using the

Fowler-Nordheim equation:

2 B

æö

JAE

Where: A and B are constants in terms of effective mass and barrier height. E is electric

field.

The oxide capacitor of MOS can be considered to be a parallel plate capacitance, so the

oxide thickness (To x) and its area (Area) results in the

following:

Iexpect Area J× Area A

Where: V is applied voltage.

To draw the curve for the above equation, you can use a user function. For example, when

a=100 and b=-415, you set the following user function on the CHANNELS: USER

FUNCTION page:

exp×=

---

–

èø

E

2

V

æö

---------

èø

Tox

BTox×

æö

----------------- -

–

exp××

èø

V

Area A×

------------------ --2

Tox

2

BTox×

æö

V

----------------- -

–

exp×× aV

èø

V

2

b

æö

---

exp××== = =

èø

V

NAME UNIT DESCRIPTION

Iexp A 100*Vg^2*EXP(-415/Vg)

So, after the measurement finishes, you set up Vg for the X-Axis, Ig for the Y1 axis, and

Iexp for the Y2 axis on the DISPLAY: DISPLAY SETUP page.

Also, set up analysis so that the marker will move automatically to the point on the curve

where Ig is equal to 10*Iexp. In the DISPLAY: ANALYSIS SETUP page, you would

set as follows:

*MARKER: At a point where

[Ig ] = [10*Iexp ]

[]

This method allows you to find more accurately the Vbd, which it the value of Vg where

Ig is equal to 10*Iexp.

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 1-23

Page 34

V-RAMP

Measurement Setups

Measurement Setups

This section covers the measurement setups that are stored in the VRSPOT.MES and

VRSWEP.MES files.

Setups for Initial and Post Stress Tests

The measurement setups stored in VRSPOT.MES are used for the initial and post stress

tests. The setups of each page are shown in Figure 1-13 to Figure 1-18.

Setups for Ramped Stress Test

The measurement setups that are stored in VRSWEP.MES are used for the ramped stress

test. The setups of each page are shown in Figure 1-19 to Figure 1-25.

Figure 1-13 CHANNELS: CHANNEL DEFINITION Page for Initial/Post Stress

CHANNE L S: CHANNE L D EF I NI T I ON 9 5 F EB 0 2 08 : 1 7 A M

Vol t age Ramp I ni t i al / Post Spot Measur ement

* MEAS UREMENT MODE

SAMPLI NG

* CHA NNEL S

UNI T V NAME I NA ME MODE F CT N RESI S TA NCE

SMU1 : HR Vg I g V CONST 0 o h m

SMU2 : HR 0 o h m

SMU3 : HR

SMU4 : HR Vs u b I s u b V CONST

VSU1 -------

VSU2 -------

VMU1 ------- ----- ----

VMU2 ------- ----- ----

SAMPLI NG

Sel ect Measur ement Mode wi t h sof t key or r ot ar y kn ob.

CHANNE L

DEF

USER

FCTN

MEASURE STBY SERI ES

USER

VAR

SWEEP

SAM-

PL I NG

DEF AU L T

ME A S UR E

SETUP

ME M1 M

B- Tr

VCE- I C

ME M2 M

FET

VDS- I D

ME M3 M

FET

VGS- I D

ME M4 M

DI ODE

VF- I F

NEX T

PAGE

1-24 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 35

Figure 1-14 MEASURE: SAMPLING SETUP Page for Initial/Post Stress

V-RAMP

Measurement Setups

MEASURE: SAMPLI NG SETUP 95FEB02 08: 19AM

Vol t age Ramp I ni t i al / Post Spot Measu r ement

* SAMPLI NG PARAMET ER * STOP CONDI T I ON

MODE L I NEAR ENABL E/ DI SABL E ENABL E

I NI TI AL I NTERVAL 1. 00000 s ENABLE DELAY 0. 0000000 s

NO. OF SAMP LES 1 NAME I g

TOTAL SAMP. TI ME AUTO THRESHOL D 1. 0 000 000 uA

HOLD TI ME 2. 0000 s EVENT NO. 1

FI L TER ON

* CONSTANT

UNI T S MU1 : HR SMU4 : HR

NAME Vg Vs u b

MOD E V V

SOURCE 5.000 V 0. 0000 V --------- ---------

COMPLIANCE 10.00uA 100.00uA --------- ---------

LI NEAR

Sel ect Sampl i ng Mode wi t h sof t key or r ot ar y k nob.

SAMPL NG

SETUP

MEASURE

SETUP

OUT PU T

SEQ

EVENT Va l > T h

PREV

PAGE

LI NEAR

L OG1 0

L OG2 5

L OG5 0

THI NNED

OUT

NEXT

PAGE

Figure 1-15 MEASURE: MEASURE SETUP Page for Initial/Post Stress

MEASURE: MEASURE SETUP 9 5FEB0 2 0 8: 2 0AM

Vol t age Ramp I ni t i al / Post Spot Measur ement

* MEAS UREMENT RANGE

UNI T NA ME RA NGE ZE RO CANCE L OF F

SMU1: HR I g LI MI TED 1nA OFF [ 10pA]

SMU4: HR I sub FI XED 100uA OFF [ 10pA]

*I NTEG TI ME

SHORT 640us 0. 032

ME D @ 2 0 . 0 ms 1

LONG 320. ms 16

*WAI T TI ME

LI MI TED

Sel ect Range Mode wi t h sof t key or rot ar y kn ob.

SAMPL NG

SETUP

TI ME NPLC

1 * ( DEFAULT WAI T T I ME)

MEASURE

SETUP

OUT PU T

SEQ

( *: Ol d dat a i s used. )

PREV

PAGE

AUTO

FI XED

LI MI TED

AUTO

NEXT

PAGE

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 1-25

Page 36

V-RAMP

Measurement Setups

Figure 1-16 MEASURE: OUTPUT SEQUENCE Page for Initial/Post Stress

MEASURE: OUTPUT SEQUENCE 9 5F EB02 0 8 : 2 0AM

Vol t age Ramp I ni t i al / Post Spot Measur ement

* OUTP UT SE QUENCE * TRI GGER SET UP

UNIT NAME MODE ENABLE/DISABLE DISABLE

1 SMU2: HR FUNCTI ON TRI G OUT

2 SMU3: HR STEP DELAY 0. 000 s

3 S MU4 : HR V s u b V P OL A R I T Y P OS I T I V E

4SMU1:HRVg V

5VSU1

6VSU2

* OUTP UT SE QUENCE MODE

OF S A MP L I NG

SEQUENTI AL

SMU2: HR

Sel ect Out put Sequence wi t h sof t key or rot ar y knob.

SAMPL NG

SETUP

MEASURE

SETUP

OUT PU T

SEQ

PREV

PAGE

SMU1 : HR

SMU2 : HR

SMU3 : HR

SMU4 : HR

VSU1

VSU2

NEXT

PAGE

Figure 1-17 DISPLAY: DISPLAY SETUP Page for Initial/Post Stress

DI SPL AY: DI SPLAY SETUP 9 5FEB0 2 0 8: 2 1AM

Vol t age Ramp I ni t i al / Post Spot Measu r ement

*DISPLAY MODE

GRA P HI C S

*GRAPHI CS

NAME @T I ME I g

SCALE LI NEAR L I NEAR

MI N 0. 000000000 s - 2. 000000000uA

MAX 2. 00000 s 2. 000000000uA

* GRI D * L I NE PARAMETER

ON ON

* DATA VARI ABL ES

Vg

GRA P HI CS

Sel ect Di spl ay Mode wi t h sof t key or r ot ar y knob.

DI SPL AY

SETUP

Xaxi s Y1axi s Y2axi s

ANLYSI S

SETUP

PREV

PAGE

GRA P H-

ICS

LI ST

NEXT

PAGE

1-26 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 37

Figure 1-18 DISPLAY: ANALYSIS SETUP Page for Initial/Post Stress

V-RAMP

Measurement Setups

DI SPL AY: ANAL YSI S SETUP 9 5F EB02 08 : 2 1AM

Vol t age Ramp I ni t i al / Post Spot Measur ement

*LI NE1:[ ]

*LI NE2:[ ]

* MARKER: At a p o i n t whe r e

[@INDEX] = [1 ]

[]

*I nt er pol at e: [ OFF]

Sel ect Li ne Mode wi t h sof t key or r ot ar y knob.

DI SPL AY

SETUP

ANLYSI S

SETUP

PREV

PAGE

NORMA L

GRA D

TANGENT

REGRES -

SI ON

DI SABL E

NEXT

PAGE

Figure 1-19 CHANNELS: CHANNEL DEFINITION Page for Ramped Stress

CHANNELS: CHANNEL DEFI NI TI ON 95FEB02 08: 35AM

Vol t age Ramp I ni t i al / Post Spot Measu r ement

* MEASUREMENT MODE

SWEEP

* CHA NNEL S

UNI T V NAME I NA ME MODE F CT N RES I ST ANCE

SMU1: HR Vg I g V VAR1 0 o hm

SMU2: HR 0 o h m

SMU3: HR

SMU4: HR Vsub I sub V CONST

VSU1 -------

VSU2 -------

VMU1 ------- ----- ----

VMU2 ------- ----- ----

SWEEP

Sel ect Measur ement Mode wi t h sof t key or r ot ar y knob.

CHANNE L

DEF

USER

FCTN

MEASURE STBY SERI ES

USER

VAR

SWEEP

SAM-

PL I NG

DEF A UL T

MEASURE

SETUP

ME M1 M

B- Tr

VCE- I C

ME M2 M

FET

VDS- I D

ME M3 M

FET

VGS- I D

ME M4 M

DI ODE

VF- I F

B

NEXT

PAGE

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 1-27

Page 38

V-RAMP

Measurement Setups

Figure 1-20 CHANNELS: USER FUNCTION DEFINITION Page for Ramped Stress

CHANNELS: USER FUNCTI ON DEFI NI TI ON 95FEB02 08: 37AM

Vol t age Ramp I ni t i al / Post Spot Measur ement

* USER FUNCTI ON

NAME UNI T DEF I NI TI ON

Ti me s e c @I NDEX* . 06 14

Vbd V @MY2

Qbd C INTEG(Ig,Ti me)

Ti me

Ent er User Funct i on Name. ( max 6 chars. )

CHANNE L

DEF

USER

FCTN

USER

VAR

PREV

PAGE

DEL E T E

ROW

NEXT

PAGE

Figure 1-21 MEASURE: SWEEP SETUP Page for Ramped Stress

MEASURE: SWEEP SETUP 95FEB02 08: 38AM

Vol t age Ramp I ni t i al / Post Spot Measur ement

* VARI ABL E VAR1 VAR2

UNIT SMU1:HR

NAME Vg

SWEEP MODE SI NGL E

LI N/ LOG LI NEAR

START - 5. 0 0 0 V

STOP - 24. 000 V

STEP - 50. 0mV

NO OF STEP 3 81

COMPLI ANCE 50. 00mA

POWER COMP OFF

*TIMING

HOLD TI ME 0. 0000 s

DELAY TI ME 30. 7ms * SWEEP STOP AT COMPLI ANCE St at us

* CONSTANT

UNIT SMU4:HR

NAME Vs u b

MOD E V

SOURCE 0 . 0 0 0 0 V --------- --------- ---------

COMPLIANCE 100.00mA --------- --------- ---------

SI NGLE

Sel ect Sweep Mode wi t h sof t key or r ot ar y knob.

SWEEP

SETUP

MEAS URE

SETUP

OUT PU T

SEQ

PREV

PAGE

SI NGLE

DOUBL E

NEXT

PAGE

1-28 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 39

Figure 1-22 MEASURE: MEASURE SETUP Page for Ramped Stress

V-RAMP

Measurement Setups

MEASURE: MEASURE SETUP 9 5FEB0 2 0 8: 3 8AM

Vol t age Ramp I ni t i al / Post Spot Measur ement

* MEAS UREMENT RANGE

UNI T NA ME RA NGE ZE RO CANCE L OF F

SMU1: HR I g FI XED 100uA OFF [ 10pA]

SMU4: HR I sub FI XED 100uA OFF [ 10pA]

*I NTEG TI ME

SHORT@ 64 0u s 0 . 0 32

MED 20. 0ms 1

LONG 320. ms 16

*WAI T TI ME

FI XED

Sel ect Range Mode wi t h sof t key or rot ar y kn ob.

SWEEP

SETUP

TI ME NPLC

0 * ( DEFAULT WAI T T I ME)

MEASURE

SETUP

OUT PU T

SEQ

( *: Ol d dat a i s used. )

PREV

PAGE

AUTO

FI XED

LI MI TED

AUTO

NEXT

PAGE

Figure 1-23 MEASURE: OUTPUT SEQUENCE Page for Ramped Stress

MEASURE: OUTPUT SEQUENCE 9 5F EB02 0 8 : 3 9AM

Vol t age Ramp I ni t i al / Post Spot Measur ement

* OUTP UT SE QUENCE * TRI GGER SET UP

UNI T NAME MODE ENABL E/ DI SABL E ENABL E

1 S MU4 : HR Vs u b V F UNCT I ON TRI G OUT

2 SMU1: HR Vg V ST EP DEL AY 3 0 . 7 ms

3 SMU2: HR POLARI T Y POSI TI VE

4SMU3:HR

5VSU1

6VSU2

SMU4: HR

Sel ect Out put Sequence wi t h sof t key or rot ar y knob.

SWEEP

SETUP

MEASURE

SETUP

OUT PU T

SEQ

PREV

PAGE

SMU1 : HR

SMU2 : HR

SMU3 : HR

SMU4 : HR

VSU1

VSU2

NEXT

PAGE

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 1-29

Page 40

V-RAMP

Measurement Setups

Figure 1-24 DISPLAY: DISPLAY SETUP Page for Ramped Stress

DI SPL AY: DI SPLAY SETUP 9 5FEB0 2 0 8: 3 9AM

Vol t age Ramp I ni t i al / Post Spot Measu r ement

*DISPLAY MODE

GRA P HI C S

*GRAPHI CS

NAME Ti me I g Vg

SCALE LI NEAR L OG LI NEAR

MI N 0. 0000000 sec - 1. 00pA - 5. 000000 V

MAX 40. 000000 sec - 1. 000000000 A - 30. 000000 V

* GRI D * L I NE PARAMETER

ON ON

* DATA VARI ABL ES

Vb d

Qb d

GRA P HI CS

Sel ect Di spl ay Mode wi t h sof t key or r ot ar y knob.

DI SPL AY

SETUP

Xaxi s Y1axi s Y2axi s

ANLYSI S

SETUP

PREV

PAGE

GRA P H-

ICS

LI ST

NEXT

PAGE

Figure 1-25 DISPLAY: ANALYSIS SETUP Page for Ramped Stress

DI SPL AY: ANAL YSI S SETUP 9 5F EB02 08 : 4 0AM

Vol t age Ramp I ni t i al / Post Spot Measur ement

*LI NE1:[ ]

*LI NE2:[ ]

* MARKER: At a p o i n t whe r e

[Ig ] = [-.03 ]

[]

*I nt er pol at e: [ OFF]

Sel ect Li ne Mode wi t h sof t key or r ot ar y knob.

DI SPL AY

SETUP

ANLYSI S

SETUP

PREV

PAGE

NORMA L

GRA D

TANGENT

REGRES -

SI ON

DI SABL E

NEXT

PAGE

1-30 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 41

2 J-RAMP

Page 42

J-RAMP

Current-Ramped (J-Ramp) test is one of the Wafer Level Reliability (WLR) tests, which is

used to evaluate device reliability on a wafer. This test can provide quick evaluation data

for estimating the overall reliability of thin oxides, and this data can be used to improve the

thin oxide manufacturing process.

With the thickness of oxide shrinking along with device geometries, creating a reliable thin

oxide has become an important issue. The integrity of the thin oxide in a MOS device is a

dominant factor in determining the overall reliability of a micro-circuit. The J-Ramp test

can promptly give useful feedback to the manufacturing process about oxide reliability.

This operation manual covers a sample J-Ramp program running on the 4155/4156, and

how to use and customize the program. The program is written in the Instrument BASIC

(IBASIC), and is ready to run on the built-in IBASIC controller of the 4155/4156.

“Theory of J-Ramp Test Procedure” describes basic theory, procedure, and terminology of

the J-Ramp test.

“Basic Operation” describes the J-Ramp sample program. Included are J-Ramp

methodology using the 4155/4156, how to execute the sample program, and program

overview.

“Customization” describes how to customize the sample program. This is very helpful

because you probably need to modify the sample program to suit your test device.

“Measurement Setups” shows the 4155/4156 page settings that are stored in the setup files.

“Proof of Equations” shows how to solve equations described in “Basic Operation”.

2-2 Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1

Page 43

J-RAMP

Theory of J-Ramp Test Procedure

Theory of J-Ramp Test Procedure

This section covers Current Ramped (J-Ramp) Test procedure. Included are basic theory,

procedure, and terminology of J-Ramp test.

The J-Ramp test procedure is based on the JEDEC standard No.35.

J-Ramp Test Overview

J-Ramp test searches for the breakdown voltage (Vbd), then calculates the breakdown

charge (Qbd) of thin oxide capacitors, which you designed as test structures on the wafer.

These results are used to evaluate the oxide integrity. The higher the Vbd and Qbd

measured by this test, the better the integrity of the oxide on wafer.

You extract these two parameters from a large amount of test structures and usually plot the

cumulative breakdown/breakdown charge distribution on a probability chart. The

manufacturing process should be driven so that this distribution becomes closer to the ideal

shape.

In the J-Ramp test, an increasing current is forced to the oxide capacitor. This charges up

the capacitor so the voltage across the capacitor increases. When the oxide layer is broken

by the high electric field in the oxide, the current can flow through, so the voltage across

the oxide capacitor decreases (breakdown). Breakdown voltage (Vbd) is defined as the

voltage at which breakdown occurs. And breakdown charge (Qbd) is the total charge

forced through the oxide until breakdown occurs.

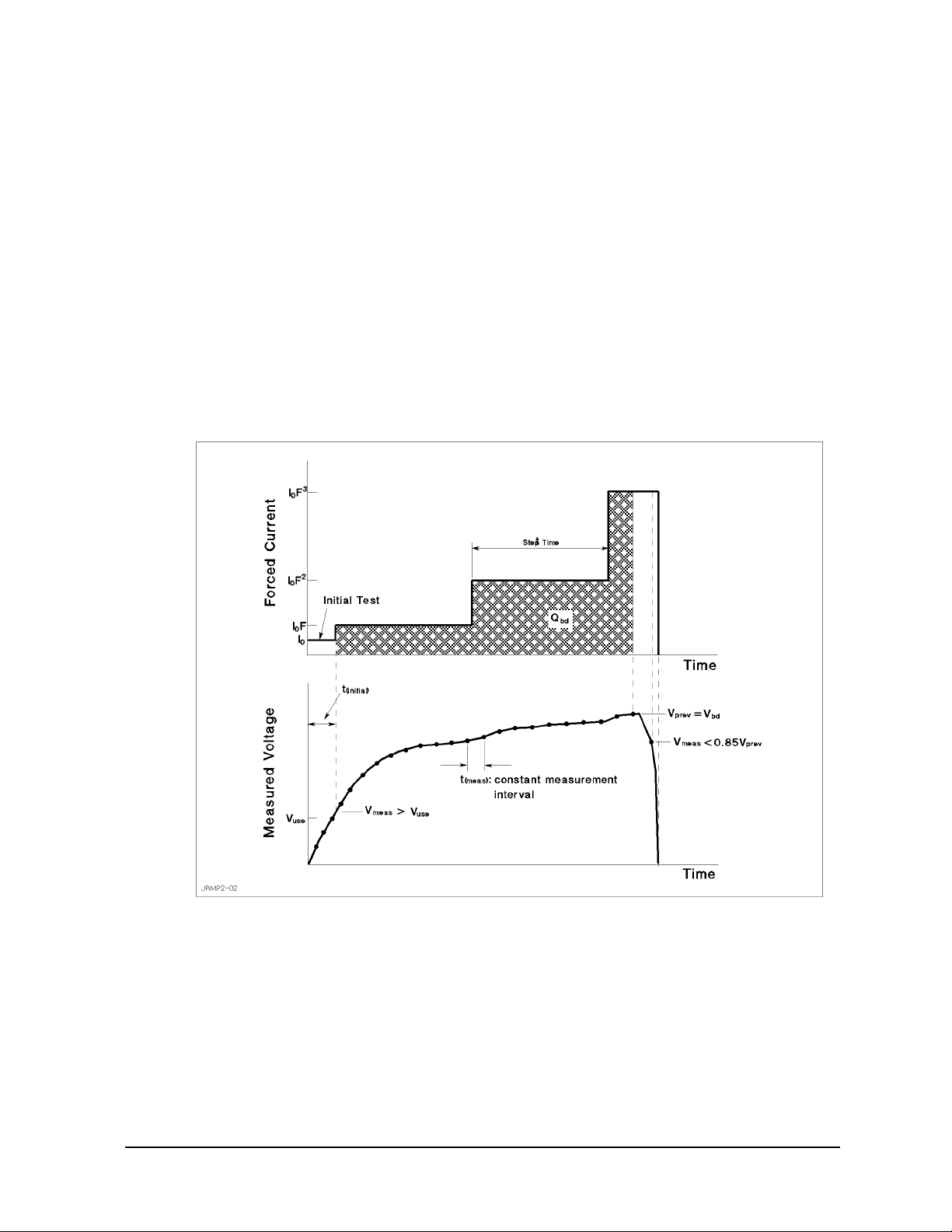

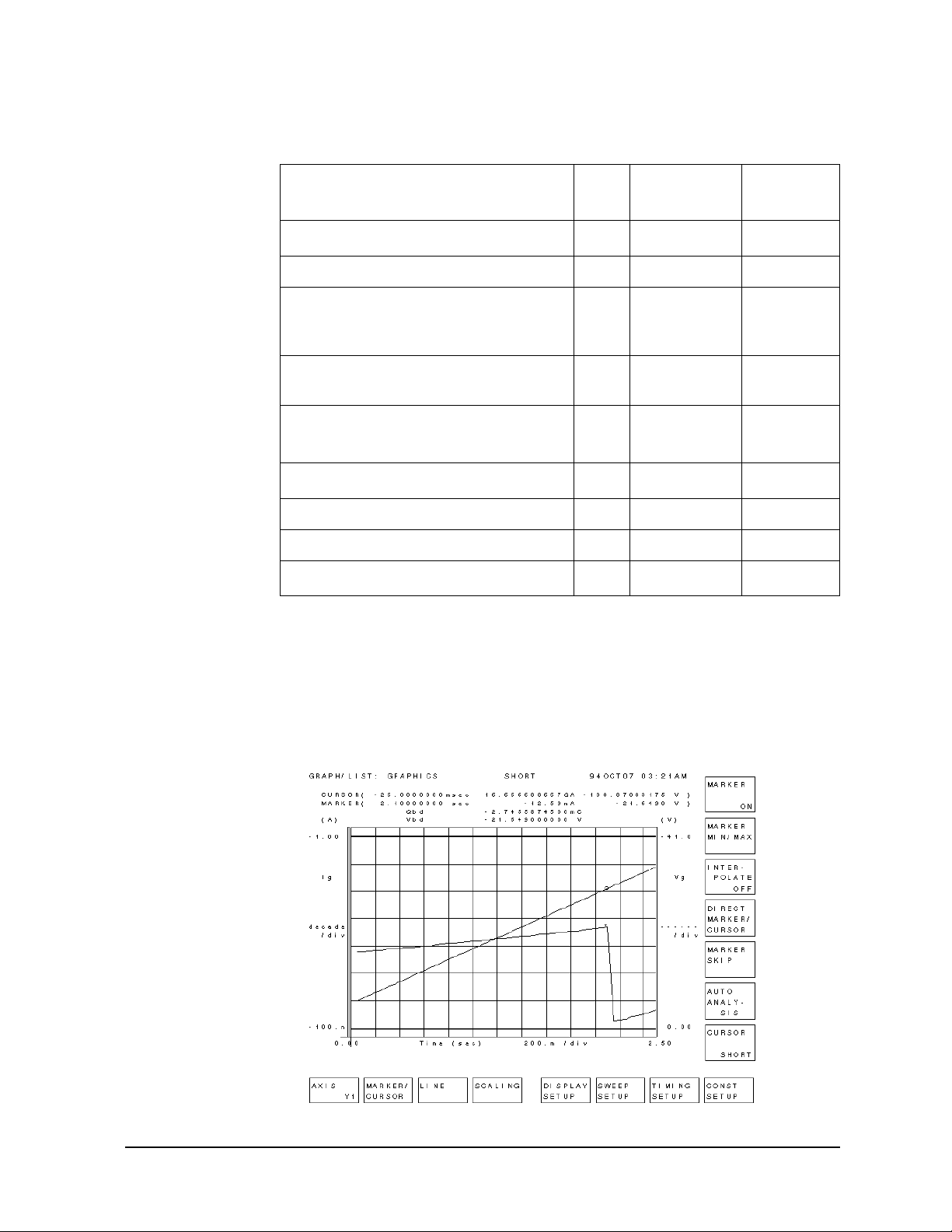

Figure 2-1 shows a simplified flowchart of J-Ramp test.

The J-Ramp test consists of three tests: initial test, ramp stress test, and post stress test.

In the initial test, an initial current I

then voltage across the oxide is measured to check for initial failure.

In the ramp stress test, a stepped current is applied, and the voltage across the oxide is

continuously measured.

The post stress test is for confirming that failure occurred during the ramp stress test. The

initial current is forced again, then the voltage across the oxide is measured.

After the tests, the test results must be analyzed and saved (data recording).

Before performing the J-Ramp test, test conditions must satisfy the following:

• Gate bias polarity is in accumulated direction. That is, negative (minus) current is

applied to gate conductor for P-type bulk, and positive (plus) current is applied for

N-type bulk.

• Diffusions and wells (if any) must be connected to substrate.

• Temperature is in 25 ± 5 °C range.

(typical value is 1 mA) is forced to the oxide capacitor,

0

Agilent 4155C/4156C Sample Application Programs Guide Book, Edition 1 2-3

Page 44

J-RAMP

Theory of J-Ramp Test Procedure

Figure 2-1 Simplified Flow Diagram of J-Ramp Test

Initial Test

Initial test is to confirm that the oxide capacitor is initially good. To do so, an initial current

I

(typical value is 1 mA), which is low enough not to break the oxide, is forced to the oxide

0

capacitor, and the voltage across the oxide is measured after a certain time t

measured voltage does not reach the normal operating voltage, it is categorized as initial

failure.

If an oxide capacitor is categorized as initial failure, test should not continue for the

capacitor. If the capacitor passes the initial test, the J-ramp stress test may begin

immediately.

The value of t

Initial current I

time t

, but must be small enough not to break the oxide.

initial