Kenwood FGZ-201-ELF-2, FGZ-201-ERF-2 Service manual

7 inch MULTIDISPLAY

FGZ201ELF2/ERF2

SERVICE MANUAL

© 2003-8 CREATED IN JAPAN

B53-0084-00 (N) 0

SUBARU GENUINE

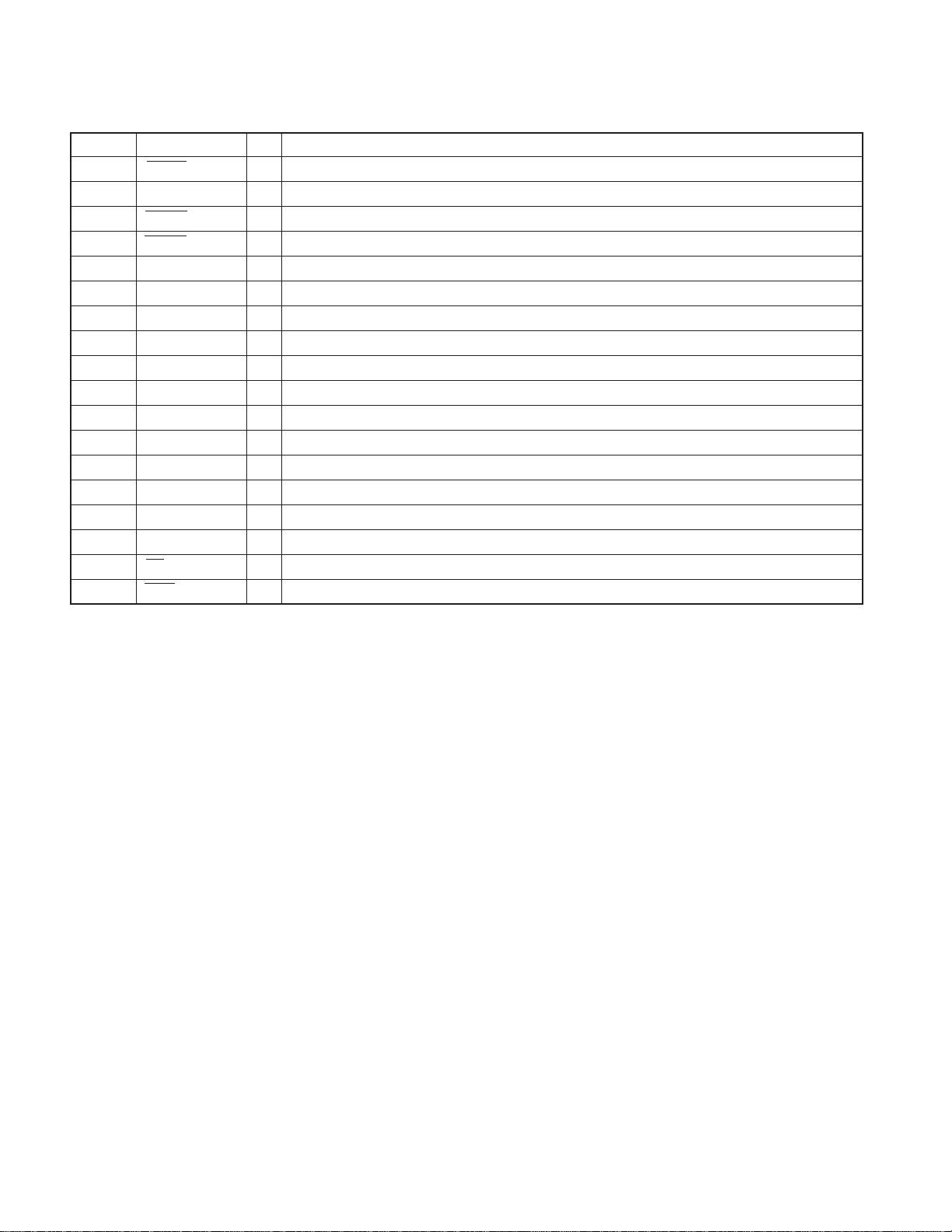

MODEL PARTS No.

FGZ201ELF2 86281AG030

FGZ201ERF2 86281AG010

Panel

(A64-2772-21)

Liquid crystal

(B38-1100-05)

Knob (image adj.)

K24-3974-24 (ERF2)

K24-4009-24 (ELF2)

Knob (navi)

K24-3973-24 (ERF2)

K24-4008-24 (ELF2)

Knob (menu)

K24-3971-24 (ERF2)

K24-4011-24 (ELF2)

Knob (clock)

K24-3975-24 (ERF2)

K24-4010-24 (ELF2)

Knob (info.)

K24-3972-24 (ERF2)

K24-4012-24 (ELF2)

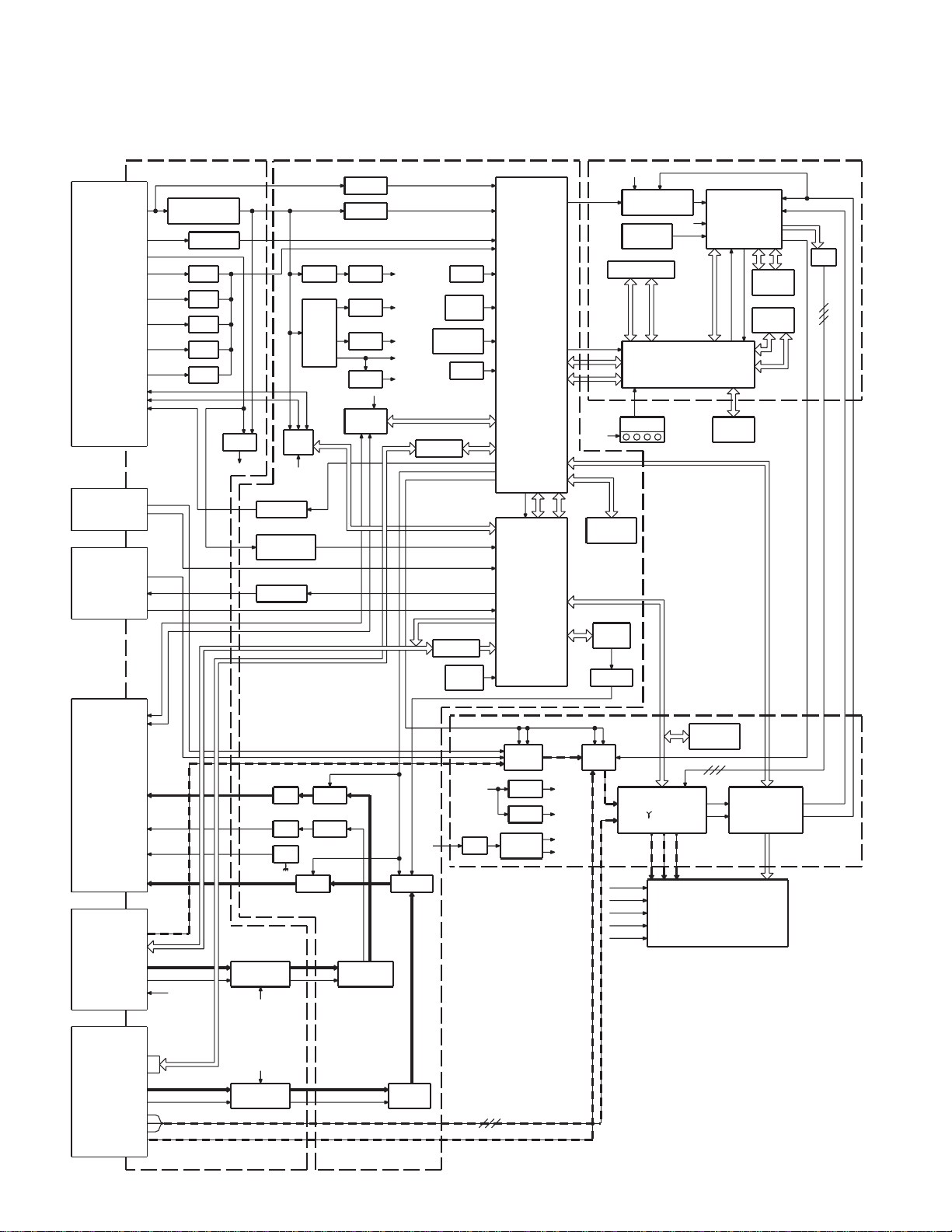

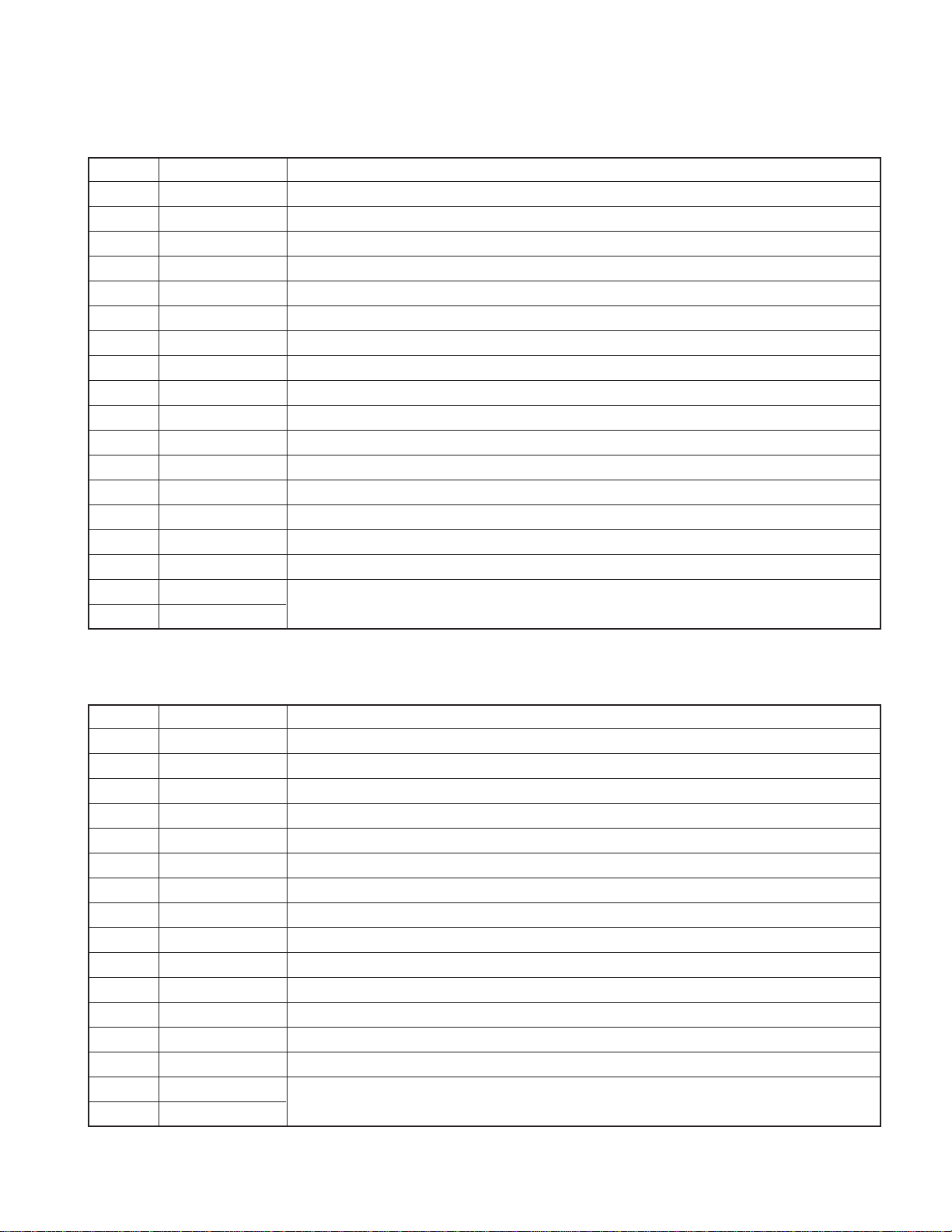

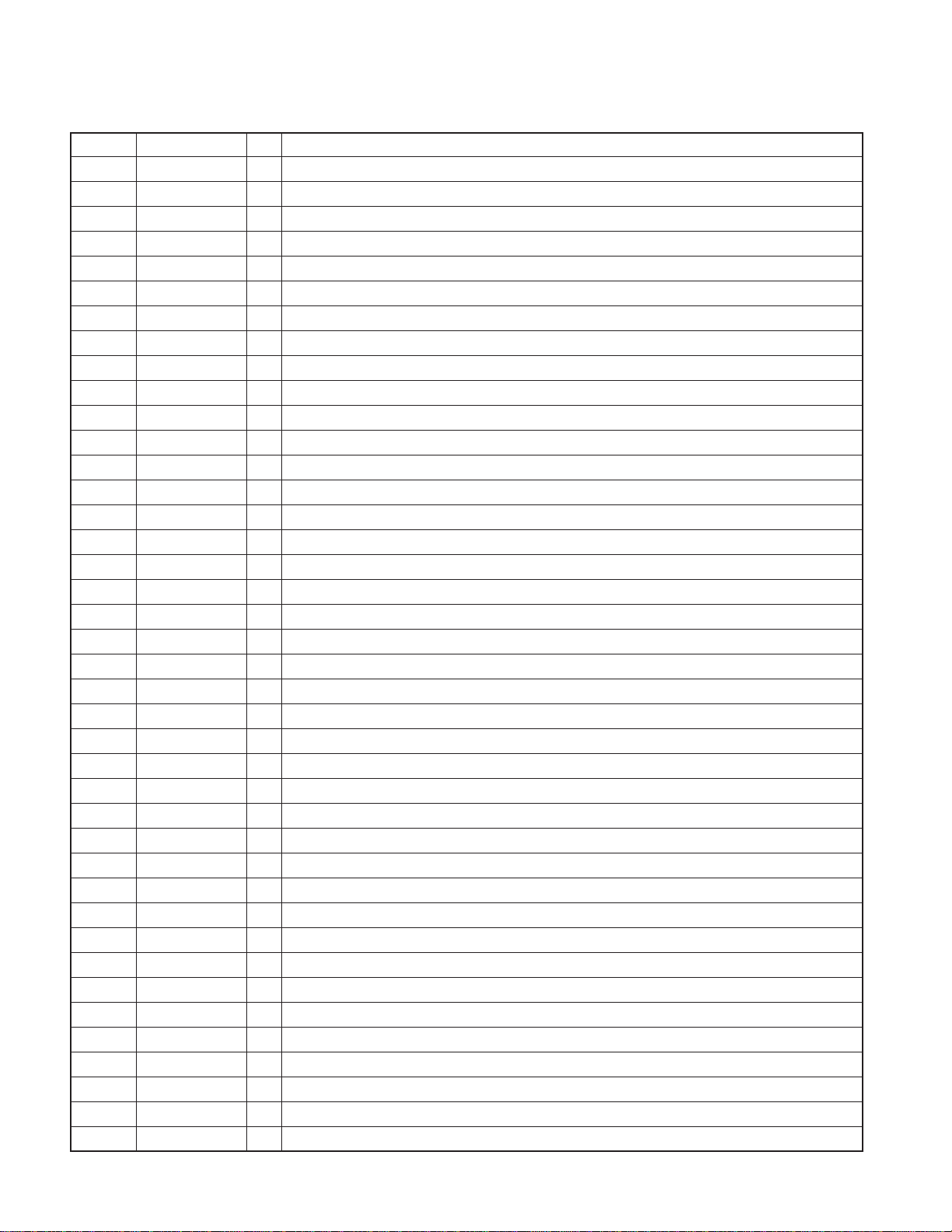

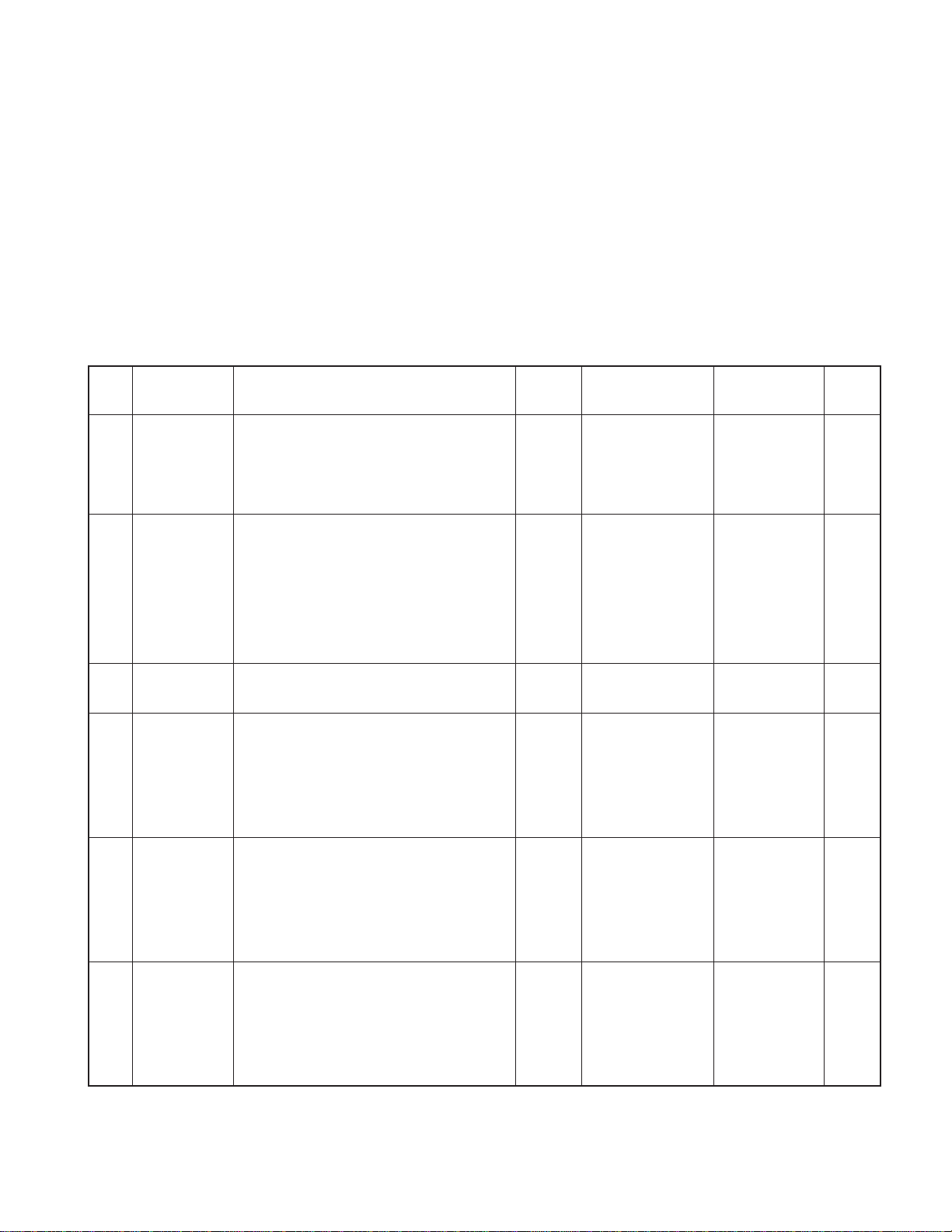

FGZ201ELF2/ERF2

BLOCK DIAGRAM

J803 (B/3)

1-16PIN

CAR

INTERFACE

2. +BATT

4. ACC

12. ILL(PWM)

4. SPD

7. PARKING

10. REVERSE

11. ILL(SMALL)

6. CAN-H

5. CAN-L

16. PTT

1. GND

3. GND

15. GND

J800 (C/3)

RCA

1. AUX-V-IN2

2. AUX-DET

3. GND

J806 (C/3)

REAR

CAMERA

1. REAR-V-IN3

2. GND

3. GUIDE

4. REAR-DET

J803 (C/3)

17-36PIN

AUDIO BUS

20. F-BUS+

22. F-BUS-

19. GND

21. GND

23. RESET

24. AUDIO-MUTE

26. BUS ON

17. BUS OFF

34. A-OUT(L)

32. A-OUT(R)

33. A-GND

35. NAVI-GND

36. NAVI-AUDIO

J802 (C/3)

TV TUNER

UNIT

8. TV -V -IN

10-15. TU 5L

18. TV -A UDIO-L

20. TV -A UDIO-R

19. TV -A-GND

1.2. TU+B

3-8. GND

J805 (B/3)

NAVIGATION

UNIT

10. NAVI-RX

11. NAVI-TX

8. NAVI-A-R

12. NAVI-A-L

7. NAVI-A-GND

1. NAVI-R

5. NAVI-G

9. NAVI-B

13. C-SYNC

2.6. GND

SYNTHESIZER UNIT SYNTHESIZER UNIT

(X14- ) (B/3)(C/3)

PROTECTION

CIRCUIT

Q803

Q801

Q804

8. IGN

Q800

Q805

Q806

18. +B

MONO

L/R

AUDIO-GND

+B

L/R

AUDIO-GND

ACC DET

DET

DET

DET

DET

DET

Q806,

810

ILL-V

ILL-V

Q43

Q5

Q62

Q45,

52

IC801

ISOLATION

AMP

P7.5V

P7.5V

IC800

ISOLATION

AMP

(X14- ) (A/3)

CAN

TX

PTT-DET

ILL

PWM DET.

REAR-SW

Q65

SW

Q60

SW

SW

+B

IC20 Q49

DC/D

Q42 Q47

SW

IC19

IC18

P5V

Q22

MUTE

Q21

MUTE

Q17

MUTE

L

R

+B DET

REG.

Q31

REG.

REG. P7.5V

IC17

IE BUS

TX

IC14

TV-AUDIO

BUFFER

L

R

SW

Q26,28

IC18

Q27,30

P5V

P-15.5V

32.768k

P18.5V

SUB CLK

P8.5V

BU5V

CONTROL/DATA

IC16

BUFFER

IC15

BUFFER

+B B/L INV

IC13

SW-OP

IC10

MIX

IC5

BU5V

IC1

RST

15MHz

MAIN

TH

IC3

10MHz

CLK

V SYNC SW

IC200 IC201

SW

CPU1

SYSTEM

MICROPROCESSOR

RST

CPU2

CAN

MICROPROCESSOR

VIDEO

SW

ELECTRIC UNIT

(X25- )

DATA

RST

ILL-V

I2C BUS

IC7

EEPROM

8kB

I2C BUS

IC4

AUDIO

MIX

IC6

E-VOL

SYNC

SW

P5VREG.P7.5V

P3VREG.

VFL H

VFL L

V-SYNC

P8.5V

SYNC

GENERATOR

SUB CLK

7.99MHz

FLASH ROM

DATA

ADDRESS

GRAPHIC

MICROPROCESSOR

SWTCH UNIT

IC203

CHROMA

DECODER &

RGB

COMPENSATION

R

G

P18.5V

P-15.5V

P5V

VFL H

VFL L

P5V

IC12

(X16- )

VIDEO UNIT

(X35- )

EEPROM

1kB

RGB

B

TFT LCD ASSY

IC4

GRAPHIC

CONTROLLER

SDRAM

(8MB)

INT

RST

IC11

CONTROL

SDRAM

(8MB)

TOUCH

PANEL

IC102

HD

TIMING

VD

CONTROLLER

IC5

VD

HD

IC6

D/A

RGB

C-SYNC

2

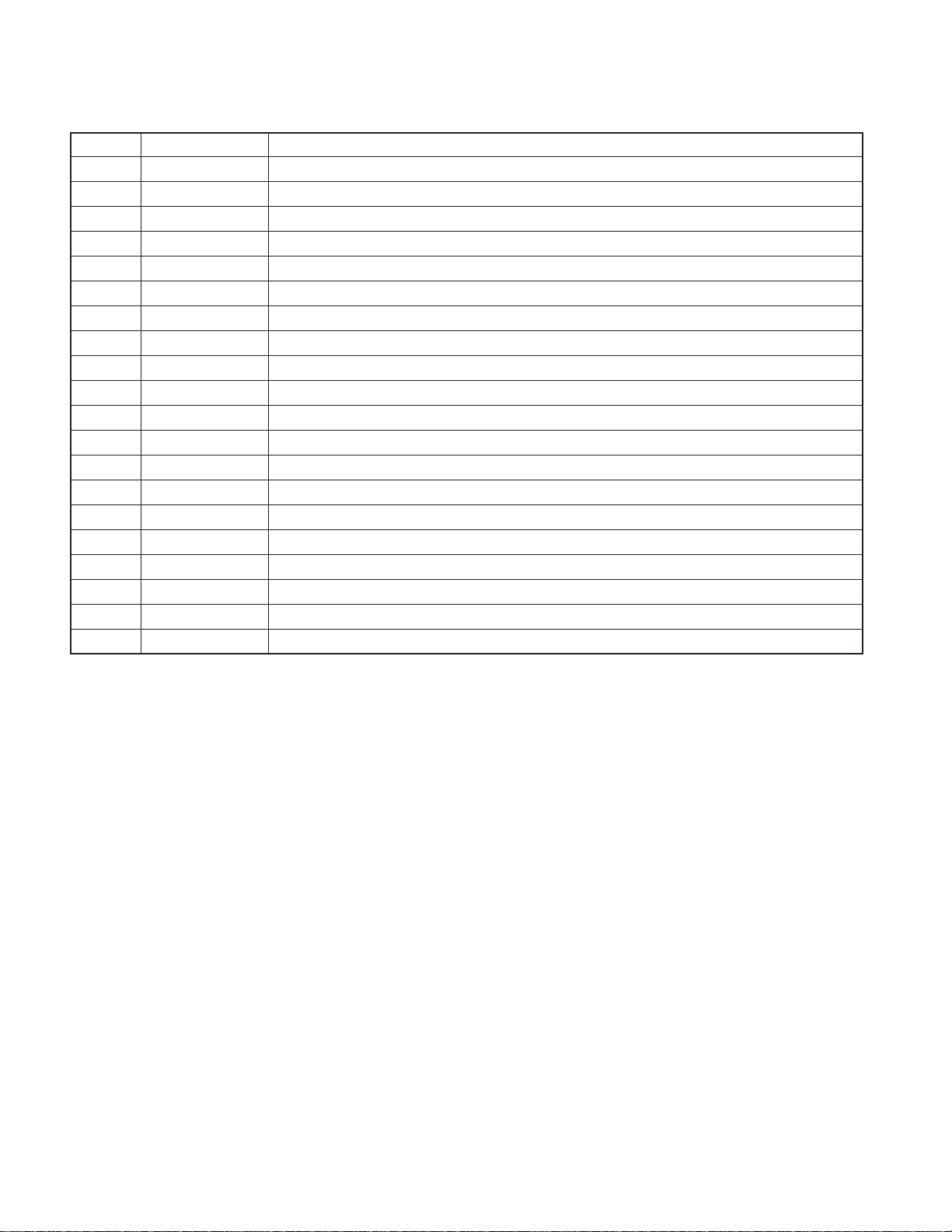

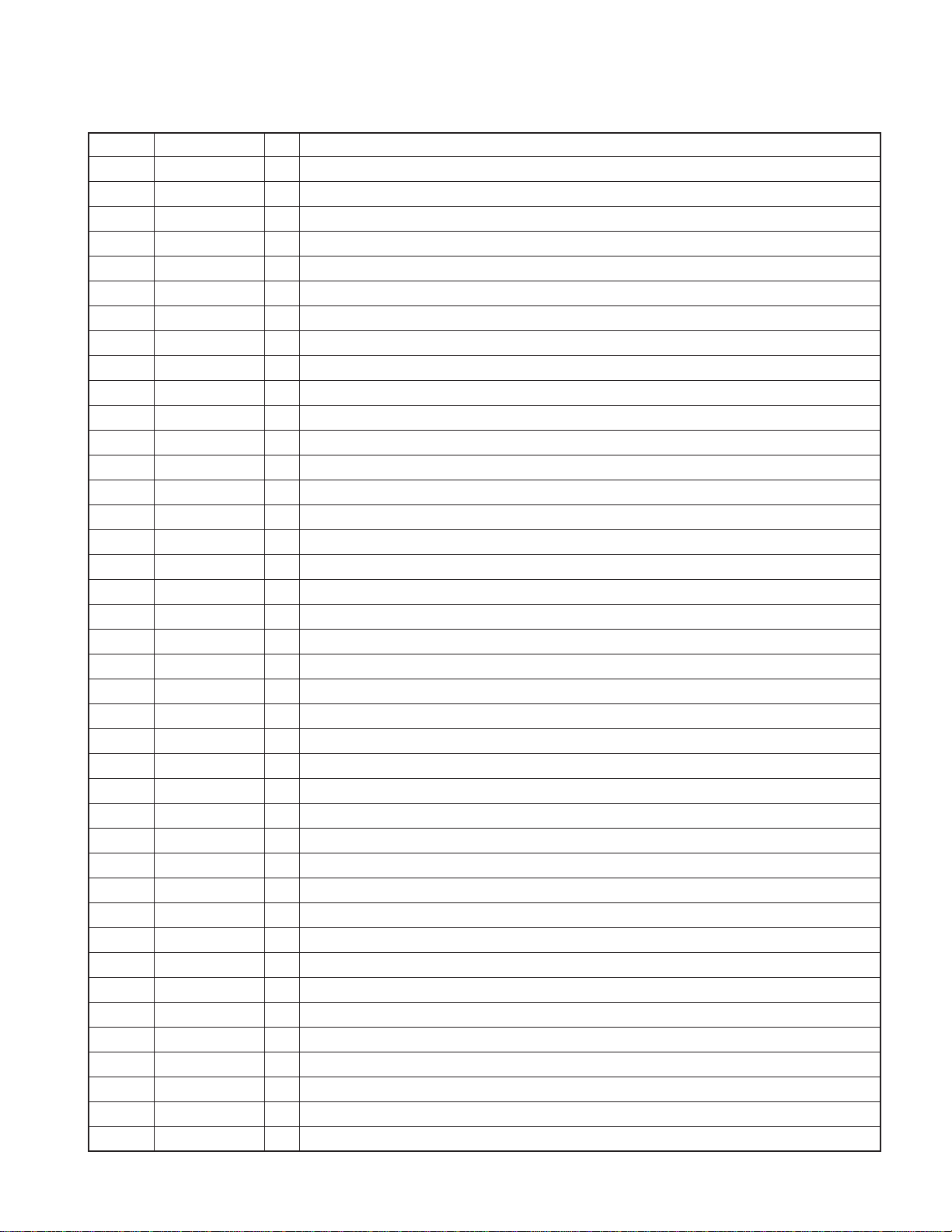

FGZ201ELF2/ERF2

COMPONENTS DESCRIPTION

● Synthesizer unit (X14-9122-71)

Ref. No. Component Name Application / Function / Operation / Condition

IC1 S-80943CNMC Reset IC (when resets at the time of backup power supply is OFF)

IC2 TC7WHU04FU Inverter IC (audio unit control and microprocessor program writing)

IC3 M306NBFCTFP5Q0

IC5 M30624FGAFP9P3

IC7 S-24CS08AFJ-TB EEP-ROM (memory of a receiving TV station name and touch-panel compensation data for memory)

IC8 TJA1054 CAN transceiver (communication with a car unit)

IC9 S-80943CNMC Reset IC (detection of the 5V power supply )

IC10 NJM4565MD OP AMP IC (LR sound MIX of NAVI audio and bias of power supply an internal audio circuit)

IC12 TC4066BFT(N) Analog SW (port SW at the time of microprocessor program writing)

IC13 NJM2120M OP AMP with SW (change of a NAVI sound and an ADA sound)

IC16 TC7WH126FU Buffer IC (the microprocessor is protected from a communication line with a NAVI unit)

IC17 HA12187FP BUS transceiver (communication with an audio unit)

IC18 S-816A50AMC-T2 Regulator IC (5V power supply of a system microprocessor)

IC19 BA00ASFP Regulator IC (analog system 7.5V power supply)

IC20 BA9743AFV DC/DC controller IC (power supply of without system microprocessor and key illumination circuit)

IC21 S-80925CNMC Reset IC (it resets at the time of the abnormal of function for system microprocessor)

IC800 TDA8579T-T Isolation AMP (noise removal of a NAVI audio sound)

Q1 DTA124EUA Audio MUTE SW

Q2 DTA124EUA

Q32,37 2SC4081

Q34 2SA1576A

Q35,53 DTC144EUA

Q36,39,41

Q46 2SB1188(Q,R)

Q4 DTC144EUA

Q5 DTC124EUA Key illumination tone light detection (it turns on at the time of a illumination PWM input)

Q6 DTA124EUA Temperature detection SW (at the time of ACC → ON is ON : temperature detection mode start)

Q7~11,

Q55,56,58

Q12,16 DTC144EUA Audio control SW (at the time of the audio communication is ON : Q16 is ON, at the time of OFF : Q15 is

Q15,18 DTA144EUA ON)

Q17 2SD2114K

Q50 DTA124EUA

DTA144EUA

DTC124EUA Video setup SW (it is ON/OFF by screen mode and adjustment)

CAN microprocessor (control of a setup and ADA voice synthesis of the connection existence distinction

quality of image of a communication rear camera and an AUX terminal with a car unit and TV tuner)

System microprocessor (surveillance of communication internal electrical power source control and a

power supply with the setting audio unit and NAVI unit of the control video sauce, the screen zoom, and

the brightness of the control and the graphic microprocessor of a CAN microprocessor, and the abnormalities in temperature)

DC/DC controller power supply

Microprocessor reset SW (at the time of power-supply ON/OFF is ON : CAN microprocessor is reset mode)

Audio MUTE (at the time of power supply ON/OFF MUTE is ON)

3

FGZ201ELF2/ERF2

COMPONENTS DESCRIPTION

Ref. No. Component Name Application / Function / Operation / Condition

Q19 2SB1188(Q,R)

Q25 DTC124EUA

Q20 2SC4081 Audio SW (at the time of ADA audio out is ON)

Q24 2SC4081

Q26 DTC124EUA

Q28 2SA1576A

Q29 2SC4081

Q30 2SB1203-FA Constant voltage power supply (backup 5V power regulator)

Q64 2SA1576A

Q31 FMY6

Q57 2SA1576A Constant voltage power supply (at the time of Q61 is ON : +18.5V output)

Q61 DTC144EUA

Q33 2SA1576A Over-current detection (at the time of 18.5V over-current detection the controller power supply is OFF)

Q38 IMT1A Over-current detection (at the time of 8.5V over-current detection the controller power supply is OFF)

Q40 FMY6

Q42 2SJ327Z

Q43 FMY6

Q49 2SJ327Z

Q44 2SC4081 Over-current detection (at the time of -15.5V over-current detection the controller power supply is OFF)

Q47 FMY6 Constant voltage power supply (-15.5V constant voltage power supply)

Q48 IMT1A Over-current detection (at the time of 5V over-current detection the controller power supply is OFF)

Q66,67 DTA144EUA

Q68,69 DTC144EUA

Q700,701 2SC4081

Q702 DTA124EUA

Q800 DTA124EUA PARKING detection (at the time of car PARKING is ON)

Q801 DTA124EUA Speed detection (at the time of a speed pulse input is ON)

Q802 DTC124EUA Reset input (at the time of Q802 ON when system microprocessor is reset mode)

Q803 2SC4081 ACC detection (at the time of car ACC → ON : ON)

Q804 2SC4081 IGN detection (at the time of car Ignition → ON : ON)

Q805 2SC4081 Reverse detection (at the time of car reverse : ON)

Q806 2SC4081 SMALL detection (at the time of car SMALL → ON : ON)

Q807,809 DTA124EUA

Q808,811 2SC4081

Q810 2SB1203-FA

Microprocessor power supply SW (at the time of CAN microprocessor program writing is OFF)

Power supply voltage dropout detection (when turns off at the time of backup power supply voltage dropout)

Voltage detection (at the time of Q26 : ON backup power supply voltage detection)

DC/DC switching (primary side switching of a transformer)

DC/DC switching (switching of 5V power supply)

Timer (at the time of a system microprocessor reckless run Q67 is OFF)

Audio connection detection (at the time of audio connection Q700 is ON)

Key illumination tone light power supply regulator (it is illumination VCC (7V) with the duty cycle according

to PWM output)

4

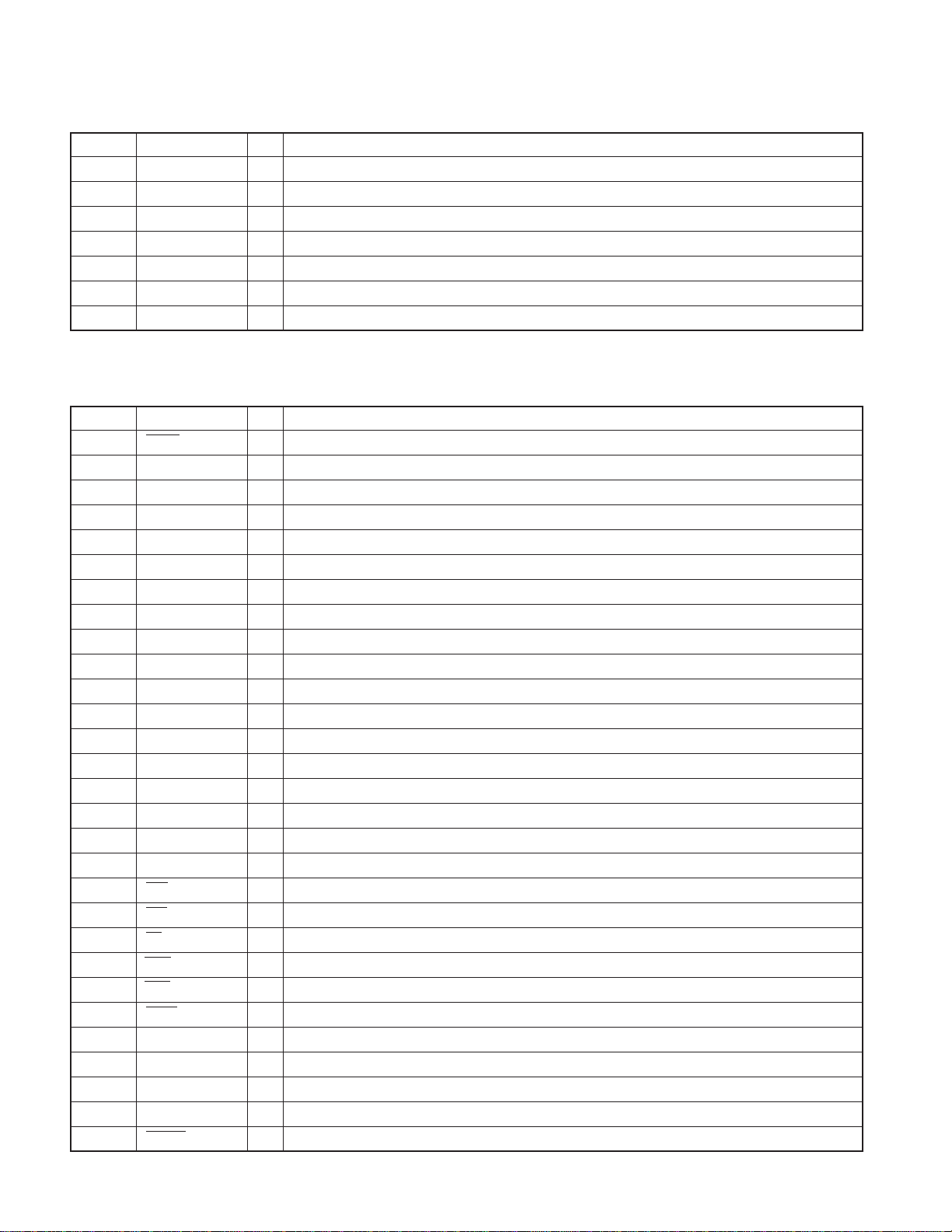

FGZ201ELF2/ERF2

COMPONENTS DESCRIPTION

● Electric unit (X25-9412-71)

Ref. No. Component Name Application / Function / Operation / Condition

IC2 TC9246F PLL Oscillator IC

IC3 TC7SHU04F Inverter (DOT CLOCK)

IC4 HD64412FI Graphic control IC

IC5 MSM5118165FP60 The memory for graphic control IC

IC6 BU3616K Video D/A converter

IC7 TC7SHU04F Inverter (DACK SIGNAL)

IC10 TC7SH32FU OR gate IC

IC11 MSM5118165FP60 The memory for graphic microprocessors

IC12 HD6437041AG57E Graphic microprocessor

IC19 MBM29F160TE9P6 Graphic bitmap data & program data memory

IC20 TC7SHU04F Inverter (SYNC. SIGNAL)

IC22 TC7SHU04F Inverter

IC23 TC7SET08FU AND gate

IC24 MSM5258MS-K Synchronized signal generator

IC26 TA78DS05F 5V AVR

IC27,28 TC7SHU04F Inverter (SYNC. SIGNAL)

Q2,3 DTC124EUA

Q4,5 DTA124EUA

The transistor for touch-panel detection

● Video unit (X35-4250-00)

Ref. No. Component Name Application / Function / Operation / Condition

IC31 TL5001ID Switching regulator (for back light 7.5V power supply)

IC101 NJM2107F Operational amplifier (oscillating circuit : low path output)

IC102 TC160G11AF1146 Timing controller (LCD driver IC)

IC200,201 NJM2535V Video switch (input video signal change)

IC202 NJW1303V Synchronous separation

IC203 AN2546FH-A Chrome decoder, gamma correction (an input video signal conversion to LCD drive signal)

IC205 S-24C01B EEP-ROM (I2C memory backup)

IC207 NJM4580V Operational amplifier (V-COM buffer)

IC209 TC7W34FU Buffer containing 3 circuits (synchronized signal output buffer)

IC211 NJU7222U30 3V Regulator

IC212 NJU7223DL1-50 5V Regulator

IC217 TC7S14F Inverter (for side black reverse signal )

Q1 2SC4081 ACC ON/OFF SW (for back light power supply)

Q2 2SB1203-FA +B SW (for back light power supply)

Q3 DTA124EUA

Q4 DTC124EUA

ACC ON/OFF SW (for back light power supply)

5

FGZ201ELF2/ERF2

COMPONENTS DESCRIPTION

Ref. No. Component Name Application / Function / Operation / Condition

Q31 2SC4081 SW REG Output (FET drive)

Q32 2SA1576A SW REG Output (FET drive)

Q33 2SJ327Z DC/DC converter SW (for back light power supply)

Q35,36 2SD1803 Inverter oscillation change SW

Q37 2SD1803 Back light tone light (for PWM pules drive)

Q38 DTA124EUA Back light tone light (for PWM pules drive)

Q39 DTC124EUA Back light tone light (for PWM pules drive)

Q40 2SA1576A Transistor for over-current protection (back light power supply)

Q41 2SC4081 An over-current for over voltage protection (back light power supply)

Q42 2SJ327Z FET for the back light lighting SW

Q43 DTC124EUA The transistor for the back light lighting SW

Q101 2SC2411K Transistor for oscillating circuits (a timing controller for a standard oscillation)

Q102 DTC124EUA LCD reverse signal control (LCD up-and-down side reverse control transistor)

Q203 2SC4097 V-COM buffer

Q204 2SA1577 V-COM buffer

Q205 2SC4081 Video signal buffer

Q206 2SA1576A Video signal buffer

Q209,210 DTC124EUA Synchronized signal muting (timing controller : at the time of adjustment muting)

X200 L78-0549-05 Synchronous separation reference oscillator (15.734kHz)

X201 L77-2818-05 Color reference oscillator (3.58MHz)

6

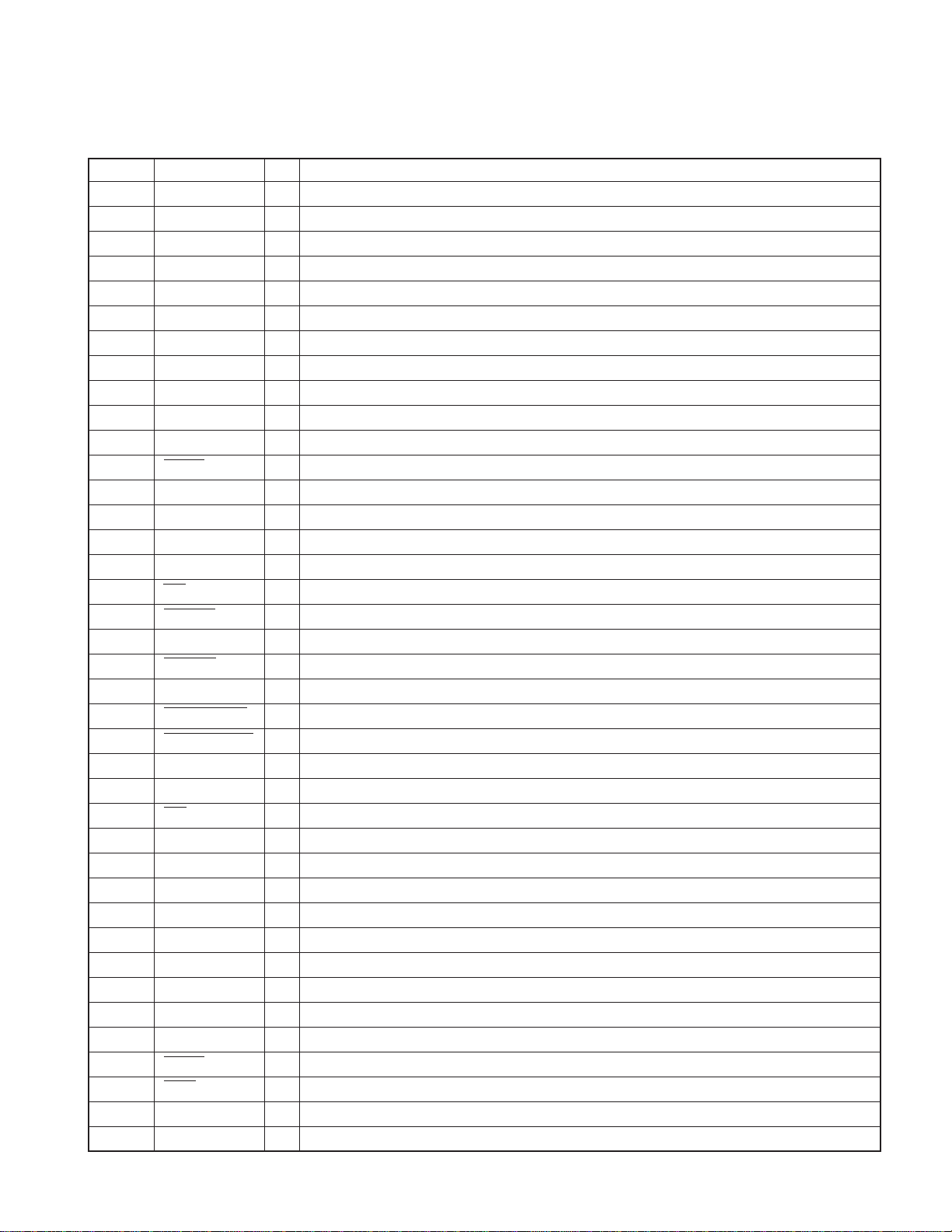

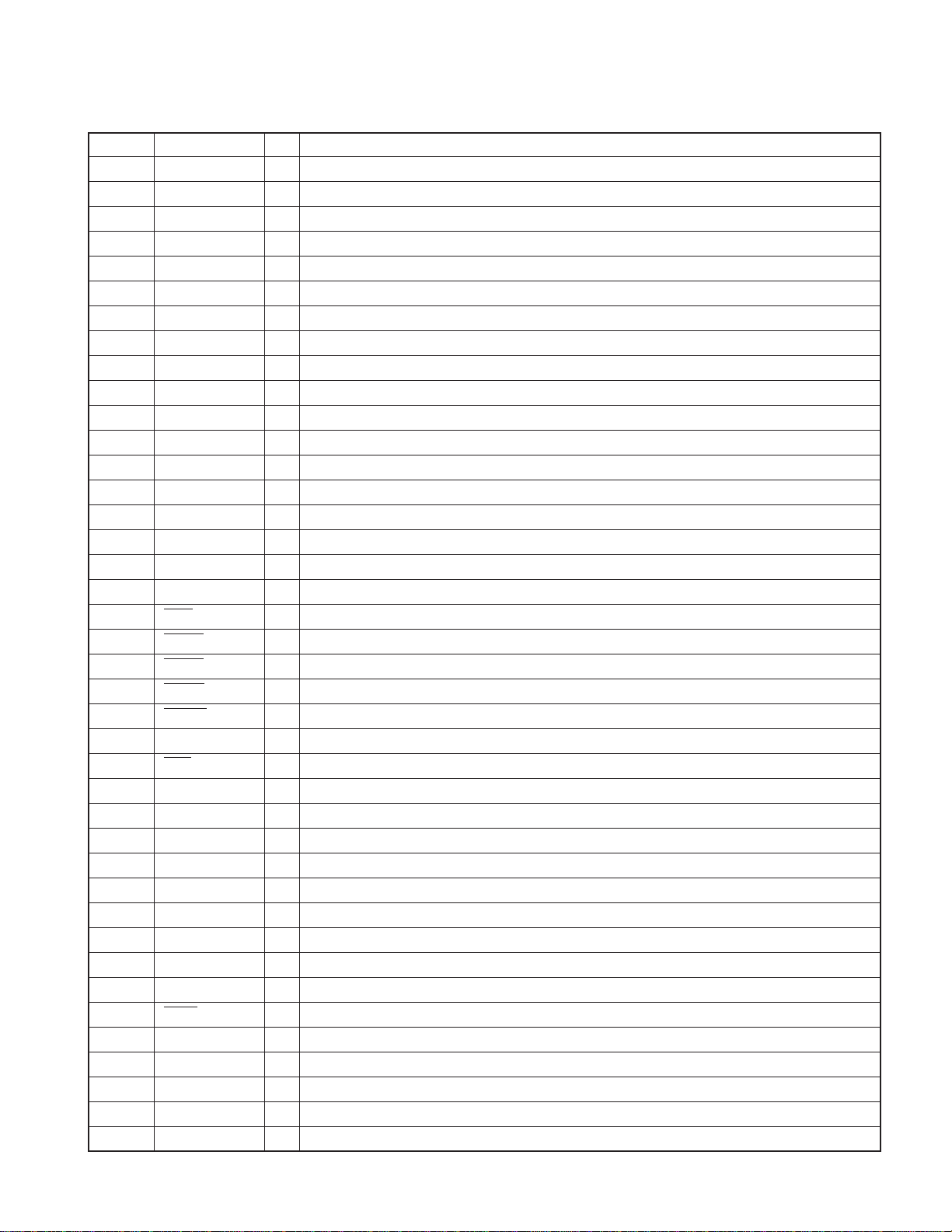

FGZ201ELF2/ERF2

MICROCOMPUTER’S TERMINAL DESCRIPTION

● System microprocessor : M30624FGAFP9P3 (X14-9122-71 : IC5)

Pin No. Pin Name I/O Purpose / Description / Processing / Operation

1 C-SYSDATA O System microprocessor data output

2 CANCLK O System microprocessor clock output

3 SPD I Speed pulse input

4 PON2 O PON7.5V control output

5 PON3 O PON18.5V control output

6 WDP O Watch dog pulse output

7 PTT O The PTT output for a telephone

8 BYTE - Un-connecting

9 CNVSS - It is high at the time of rewriting

10 XCIN I Sub clock input

11 XCOUT O Sub clock output

12 RESET I Reset input

13 XOUT O Clock output

14 VSS - Ground

15 XIN I Clock input

16 VCC - Power supply

17 NMI I Interruption input

18 CANREQ I System microprocessor Request-to-Send input

19 NC - Un-connecting

20 CANCON O CAN microprocessor control output

21 AUDIO-BUS+ I AUDIO BUS communication end detection input

22 BUS_ON_REQ I AUDIO BUS ON detection input

23 BUS_OFF_REQ I AUDIO BUS OFF detection input

24 BRIGHT O BRIGHT control output

25~27 NC - Un-connecting

28 STB O AUDIO BUS communication standby output

29 SI I AUDIO BUS communication data reception input

30 SO O AUDIO BUS communication data transmitting output

31 NAVI-TXD O Usually, a NAVI communication transmitting data output

32 NAVI-RXD I It is NAVI communication receiving data input at the time of usual

33 BUS_SYS_ON O It is an AUDIO BUS system-on output at the time of usual

34 BUS_SYS_OFF O AUDIO BUS system-off output

35 SYSDATA O System microprocessor data output

36 SHDATA I System microprocessor data input

37 SHCLK O System microprocessor clock output

38 SHRST O Graphic microprocessor reset output

39 SHINI O Graphic microprocessor initial output

40 SHRDY I The notice input of a state which can be graphic communicated

41 EPM I Flash write-in EPM input

7

FGZ201ELF2/ERF2

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. Pin Name I/O Purpose / Description / Processing / Operation

42 SHCON O Graphic microprocessor standby control output

43 SHSTBY I The completion input of graphic microprocessor standby shift

44 SYSCS O System microprocessor Request-to-Send output

45 SH_VMUTE I Graphic microprocessor image muting demand input

46 CE I Flash write-in CE input

47 TOUCH_EN O Graphic microprocessor touch key analysis permission output

48 TOUCH I Notice input of graphic microprocessor touch key-on

49 PLLCE O The clock generating IC mode output for Q2i

50 PLLSDA O The clock generating IC data output for Q2i

51 PLLSCK O The clock generating IC clock output for Q2i

52 BL-ON O Back light switch output

53 VIDEO Swa O TV/REAR changeover switch output

54 NC - Un-connecting

55 VIDEO SWb O DVD changeover switch output

56 SYNC Swa O VIDEO/NAVI SYUn-connecting changeover switch output

57 SYNC SWb O GRAPHICS SYUn-connecting changeover switch output

58 VIDEO SWc O DVD-CH/NAVI-AUX changeover switch output

59 VIDEO SWd O AUX changeover switch output

60 HPOSI1 O Level position adjusted power

61 HPOSI2 O Level position adjusted power

62 VCC - Power supply

63 SCAN1 O Screen mode changeover switch output

64 VSS - Ground

65 SCAN2 O Screen mode changeover switch output

66 NTSC/PAL O NTSC/PAL changeover switch output

67 VMUTE O Video muting control output

68 +BDET SW O +B voltage detector circuit control output

69 REV I Reverse detection input

70 PARKING I Parking detection input

71 P-ON O Power supply control output

72 FAULT O FAULT display output

73 ACC I ACC voltage detection input

74 BUDET I +B voltage variation detection input

75 SHCS I Graphic microprocessor Request-to-Send input

76 IGN I Ignition voltage detection input

77 ADA-INT O NAVI voice changeover switch output

78 AUDIO-MUTE O AUDIO muting signal output

79 TV O TV voice muting output

80 MUTE1 O MUTE1 signal output

81 TYPE0 I It forces and is a setting input

8

FGZ201ELF2/ERF2

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. Pin Name I/O Purpose / Description / Processing / Operation

82 TYPE1 I It forces and is a setting input

83 MUTE2 O MUTE2 signal output

84 E2PSCL O IIC clock output

85 E2PSDA O IIC data input and output

86 INH - Un-connecting.

87 HPOSI3 O Level position adjusted power

88 HPOSI4 O Level position adjusted power

89 AUDIODET I Audio voltage detection input

90 TEMPDET I High temperature temperature detection input

91 BLDET2 I Back light voltage detection input

92 BLDET I Back light voltage detection input

93 +BDET I +B voltage detection input

94 DC/DC DET I PON5V voltage detection input

95 CANRESET O CAN microprocessor reset output

96 AVSS I Analog grand input

97 C-SYSREQ O System microprocessor Request-to-Send output

98 VREF - Reference voltage

99 AVCC - Analog power supply

100 CANDATA I System microprocessor data input

● Graphic microprocessor : HD6437041AG57E (X25-9412-71 : IC12)

Pin No. Pin Name I/O Purpose / Description / Processing / Operation

1~5 NC - Un-connecting

6 VSS - Ground

7~11 A0~A4 O Address bus output

12 VCC - Power supply

13 A5 O Address bus output

14 VSS - Ground

15~25 A6~A16 O Address bus output

26 VCC - Power supply

27 A17 O Address bus output

28 VSS - Ground

29, 30 NC - Un-connecting

31 RAS O DRAM row address Strobe output

32 CASL O DRAM low rank side column address Strobe output

33 NC - Un-connecting

34 CASH O DRAM higher rank side column address Strobe output

35 VSS - Ground

36 RDWR O DRAM write-in Strobe output

9

FGZ201ELF2/ERF2

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. Pin Name I/O Purpose / Description / Processing / Operation

37~39 A18~A20 O Address bus output

40 VCC - Power supply

41 A21 O Address bus output

42 VSS - Ground

43 RD O External device read-out Strobe output

44 NC - Un-connecting

45 SH_VMUTE O Graphic microprocessor video mute request output

46 NC - Un-connecting

47 WRH O An external device higher rank side write-in output

48 WRL O An external device low rank side write-in output

49 CS1 O Chip selection output (inside register of Q2i)

50 CS0 O Chip selection output (flash ROM)

51~53 NC - Un-connecting

54 CS2 O Chip selection output (Q2iUGM)

55 VSS - Ground

56 ROM_RESET O Flash ROM reset output

57 ROM_RY/BY I Flash ROM lady busy input

58 NC - Un-connecting.

59 DACK O Q2iDMA transmission Strobe output

60 NC - Un-connecting.

61 VSS - Grand input

62 DREQ I Q2iDMA transmission demand input

63 VCC - Power supply

64~68 NC - Un-connecting.

69 SYSCS I Graphic microprocessor Request-to-Send input

70 IRL I Q2i interrupt request input

71 VSS - Ground

72 SHCON I Graphic microprocessor standby control input

73~76 D12~D15 I/O Data bus input and output

77 VCC - Power supply

78 D11 I/O Data bus input and output

79 VSS - Ground

80~84 D6~D10 I/O Data bus input and output

85 VCC - Power supply

86 D5 I/O Data bus input and output

87 VSS - Ground

88~92 D0~D4 I/O Data bus input and output

93 VSS - Ground

94 XTAL I Crystal oscillator input

95 MD3 I Mode setting input of operation

10

FGZ201ELF2/ERF2

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. Pin Name I/O Purpose / Description / Processing / Operation

96 EXTAL I Crystal oscillator input

97 MD2 I Mode setting input of operation

98 NMI I Non maskable interrupt input

99 VCC - Power supply

100 NC - Un-connecting

101 WAIT I Q2i wait cycle insertion input

102 MD1 I Mode setting input of operation

103 MD0 I Mode setting input of operation

104 PLLVCC I The power supply input for built-in PLL

105 PLLCAP I The capacity input for built-in PLL

106 PLLVSS I The grand input for built-in PLL

107 NC - Un-connecting

108 SHRST I Reset input

109~111 NC - Un-connecting

112 VCC - Power supply

113 Y- O The switching output for a touch-panel input

114 X- O The switching output for a touch-panel input

115 Y+ O The switching output for a touch-panel input

116 X+ O The switching output for a touch-panel input

117 VSS - Ground

118 KEYDATA1 I Touch-panel data input (Y)

119 KEYDATA2 I Touch-panel data input (X)

120 NC - Un-connecting.

121 KEY5 I Key switch input

122 KEY4 I Key switch input

123 KEY3 I Key switch input

124 AVSS - Analog ground

125 KEY2 I Key switch input

126 KEY1 I Key switch input

127 VREF - Reference voltage

128 AVCC - Analog power supply

129 VSS - Ground

130 SYSDATA I Graphic microprocessor data input

131 SHDATA O Graphic microprocessor data output

132 SYSCLK I Graphic microprocessor clock input

133 ROM_RXD I Flash ROM write-in data input

134 ROM_TXD O Flash ROM write-in data output

135 VCC - Power supply

136 SHSTBY O The completion output of graphic microprocessor standby shift

137 TOUCH O Notice output of graphic microprocessor touch key-on

11

FGZ201ELF2/ERF2

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. Pin Name I/O Purpose / Description / Processing / Operation

138 SHCS O System microprocessor Request-to-Send output

139 NC - Un-connecting

140 SHRDY O The notice output of a state which can be graphic microprocessor communicated

141 VSS I Grand input

142 NC - Un-connecting

143 TOUTH_EN I Graphic microprocessor touch key analysis permission input

144 SHINI I Graphic microprocessor initial input

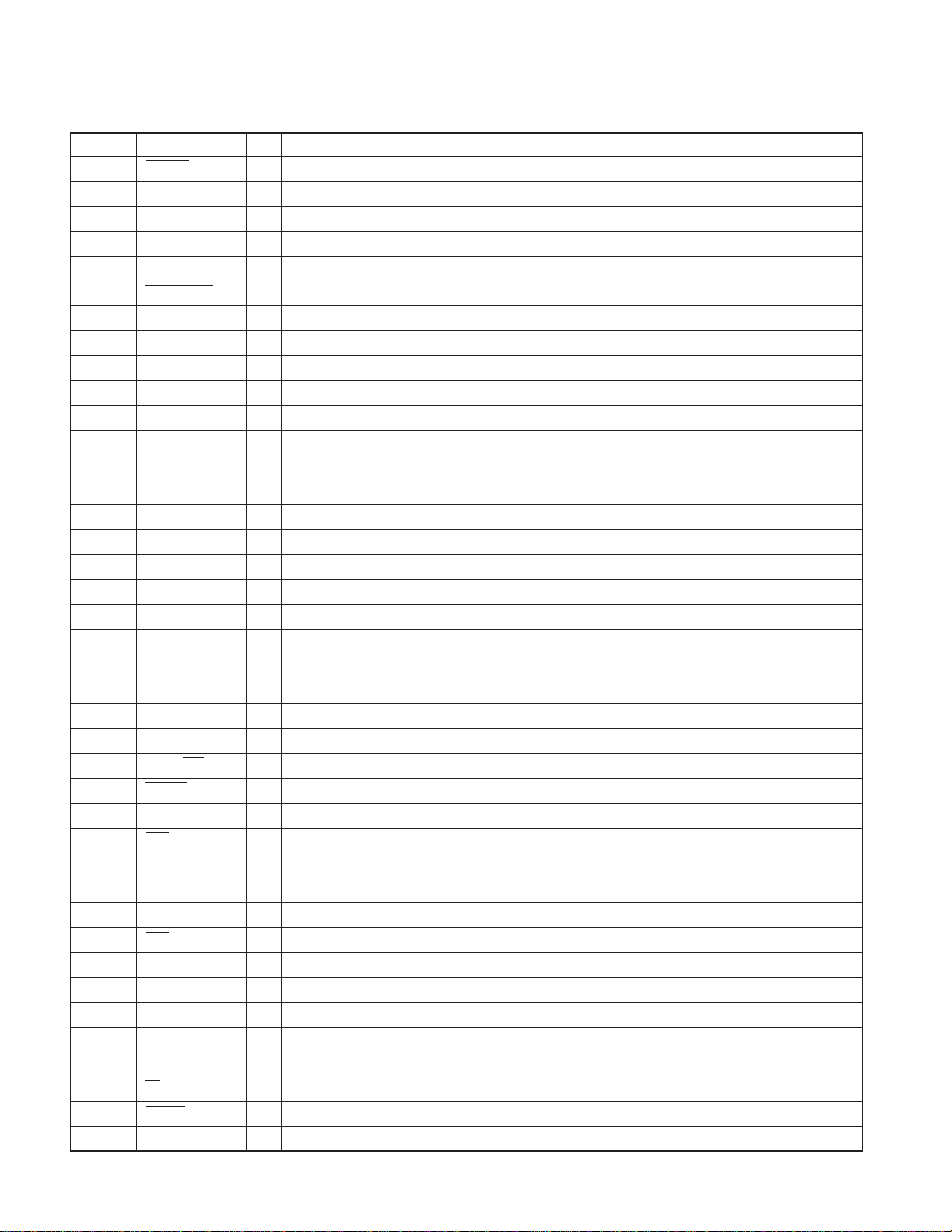

● Graphic control IC : HD64412FI (X25-9412-71 : IC4)

Pin No. Pin Name I/O Purpose / Description / Processing / Operation

1 DREQ DMA request

2D0OCPU data input and output

3D1OCPU data input and output

4 CVCC1 - Power supply

5D2 I/O CPU data input and output

6 CGND1 - Ground

7~11 D3~D7 O CPU data input and output

12 CGND2 Grand input

13 D8 CPU data input and output

14 D9 CPU data input and output

15 D10 CPU data input and output

16 CVCC2 - Power supply

17, 18 D11, D12 I/O CPU data input and output

19 CGND3 - Ground

20~22 D13~D15 I/O CPU data input and output

23 PGND - Ground

24 CAP0 - The external capacity terminal for multiplication circuit

25 PVCC - Power supply

26 CS0 I/O Chip selection 0 (UGM)

27 CS1 I/O Chip selection 1 (internal register)

28 RD Lead Strobe

29 WE0 The write-in pulse 0 (low rank side)

30 WE1 The write-in pulse 1 (higher rank side)

31 DACK DMA acknowledge

32 MODE0 I Mode terminal 0 of operation

33 MODE1 I Mode terminal 1 of operation

34 MODE2 I Mode terminal 2 of operation

35 TEST I Test terminal

36 RESET I Reset

12

FGZ201ELF2/ERF2

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. Pin Name I/O Purpose / Description / Processing / Operation

37 CLK0 Q2i operation clock

38 GND1 - Grand input

39, 40 A1, A2 I CPU address input

41 VCC1 - Power supply input

42~49 A3~A10 I CPU address input

50 GND2 - Ground

51~60 A11~A20 I CPU address input

61, 62 A21, A22 - Un-connecting

63 GND3 - Ground

64~68 MD0~MD4 I/O Memory data input and output

69 GND4 - Ground

70 MD5 I/O Memory data input and output

71 VCC2 - Power supply

72~78 MD6~MD12 I/O Memory data input and output

79 GND5 - Ground

80, 81 MD13, MD14 I/O Memory data input and output

82 VCC3 - Power supply

83 MD15 I/O Memory data input and output

84 MWE A memory write-in pulse

85 MRAS0 A low selection signal

86 MRAS1 A low selection signal

87 MLCAS Low rank side column selection signal

88 MUCAS Higher rank side column selection signal

89 GND6 - Ground

90 MOE Memory read-out pulse

91~93 MA0~MA2 O Memory address output

94 VCC4 - Power supply

95~98 MA3~MA6 O Memory address output

99 GND7 - Grand input

100~104 MA7~MA11 O Memory address output

105 GND8 - Ground

106 CLK1 The dot clock for a display

107 VCC5 - Power supply

108 FCLK 1/2 display dot clock

109 ODDF The pulse which shows the odd number field

110 GND9 - Ground

111 DCLK O Display clock output

112 CDE Color detection

113 VCC6 - Power supply

114 DISP Display period pulse

13

FGZ201ELF2/ERF2

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. Pin Name I/O Purpose / Description / Processing / Operation

115 CSYNC O Composite synchronize signal output

116 GND10 - Ground

117 HSYNC O Horizontal synchronize signal output

118 VSYNC O Vertical synchronize signal output

119~121 DD0~DD2 O Display data output

122 GND11 - Ground

123~125 DD3~DD5 O Display data output

126 VCC7 - Power supply

127, 128 DD6, DD7 Display data output

129 GND12 - Ground

130~134 DD8~DD12 O Display data output

135 GND13 - Ground

136 DD13 O Display data output

137 VCC8 - Power supply

138~141 DD14~DD17 O Display data output

142 CGND4 - Ground

143 IRL Interrupt request

144 WAIT CPU weight

14

FGZ201ELF2/ERF2

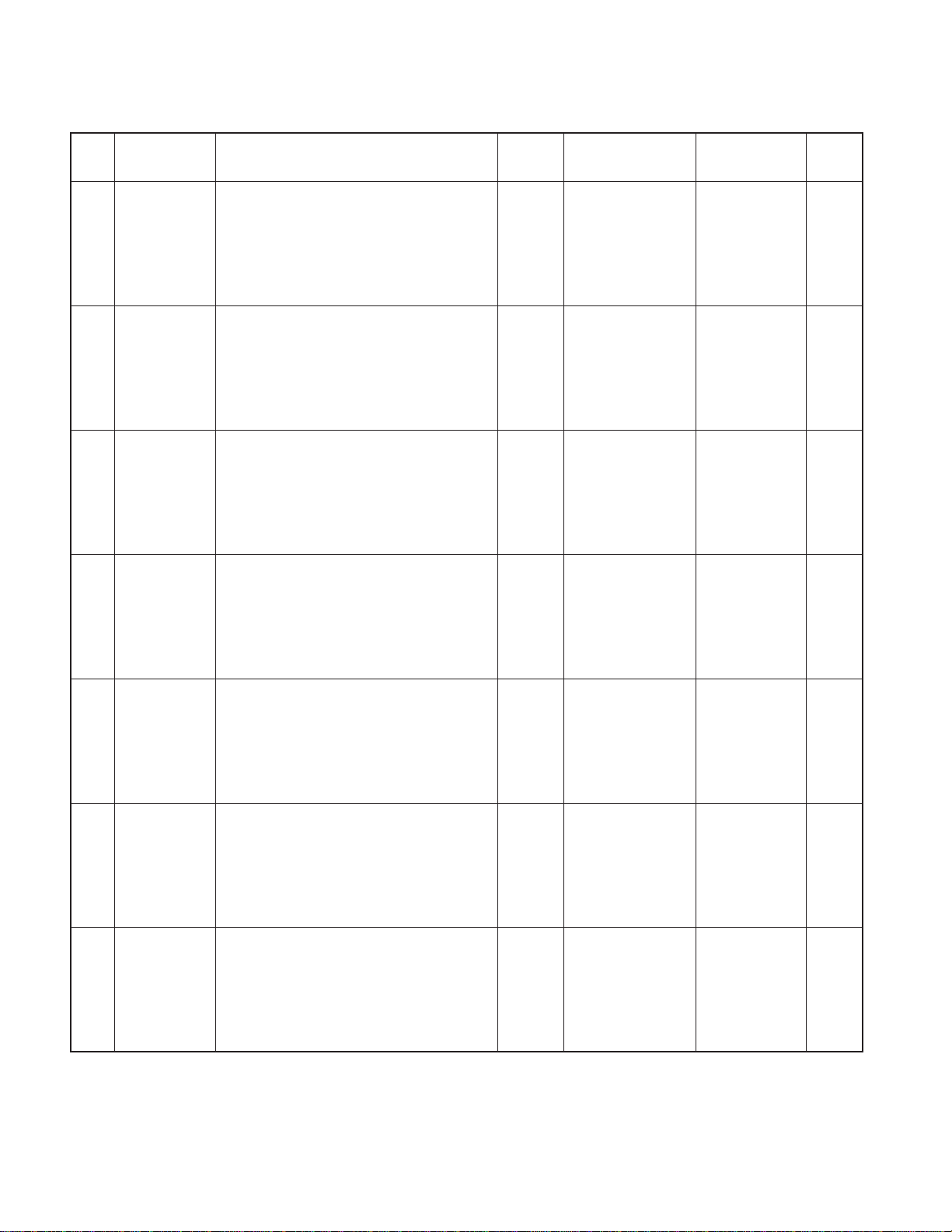

ADJUSTMENT

● Video unit (X35-4250-00)

• Start a set in test mode at the time of video board adjustment.

•How to enter to test mode : Pushing operation of 2 keys right (clock)-and-left (image adj.) both ends side and a touch panel. And

supply to power is ON.

• After starting : perform substrate adjustment for a video board by a design mode → VIDEO ADJ key with reference to the

following item.

• Adjust a picture position by After starting : (AUX) Manufacture mode → POSI (NAVI)

• VIDEO ADJ mode : it is the rectangle color frog of middle at the time of adjustment item selection. It is considered as an

adjustment end by choosing a rectangle again after adjustment.

No.

Adjustment item

1Inverter power It is considered as Bright : DUTY 100% after VR30 7.5±0.1V - TP577

regulation VIDEO ADJ - key selection.

The voltage of TP577 at this time is adjusted to

7.5±0.1V.

2 Timing f Consider it as microcomputer : SYNC (9 pin : VR101 15.734±0.01kHz Input selector : TP138

controller TP138 of IC102) MUTE → H after Adj key AUX input

free-run selection. non-signal

frequency VR101 (H-FREE) is turned and the frequency

of the NDSH output at this time is adjusted to

15.734±0.01kHz.

3 Chrome IC It is made the chroma IC adjustment mode of - - Input selector : -

adjustment a static test mode. AUX or RGB

3-A Chrome VCO 1 of IC202, 4, and 5 pin are dropped on GND, CH16 15.734±0.01kHz An input TP320

adjustment and a touch panel adjusts TP320 in f shop non-signal

counter.

- Carry out the monitor of TP138 of IC102, and

adjust VR101 in f shop counter.

3-B Black limiter Carry out the monitor of the waveform of TP527 CH5 3.5V±0.1V Incoming signal : TP527

with an oscilloscope. 10 STEP (NTSC)

Adjst the amplitude value so that the waveform /RGB

between the pedestal to the negative pedestal

is 3.5V±0.1V.

3-C White limiter Carry out the monitor of the waveform of TP527 CH10 3.5V±0.1V Incoming signal : TP527

with an oscilloscope. 10 STEP (NTSC)

Adjst the amplitude value so that the waveform /RGB

between the 8 step signal to the negative 8 step

signal is 3.5V±0.1V.

The adjustment method

Adjustment

part

Adjustment value Conditions

Test point

15

FGZ201ELF2/ERF2

ADJUSTMENT

No.

Adjustment item

3-D Bright Carry out the monitor of the waveform of TP527 CH6 2.5V±0.1V Incoming signal : TP527

adjustment with an oscilloscope. 10 STEP (NTSC)

Adjst the amplitude value so that the waveform /RGB

between the 2 step signal to the negative 2 step

signal is 2.5V±0.1V.

3-E Contrast Carry out the monitor of the waveform of TP527 CH13 3.0V±0.1V Incoming signal : TP527

with an oscilloscope. 10 STEP (NTSC)

Adjst the amplitude value so that the waveform /RGB

between the 9 step signal to the negative 9 step

signal is 3.0V±0.1V.

3-F Gamma 1 Carry out the monitor of the waveform of TP527 CH11 1.2V±0.1V Incoming signal : TP527

with an oscilloscope. 10 STEP (NTSC)

Adjst the amplitude value so that the waveform /RGB

between the pedestal to the 3 step signal is

1.2V±0.1V.

3-G Gamma 2 Carry out the monitor of the waveform of TP527 CH12 2.9V±0.1V Incoming signal : TP527

with an oscilloscope. 10 STEP (NTSC)

Adjst the amplitude value so that the waveform /RGB

between the pedestal to the 10 step signal is

2.9V±0.1V.

3-H Y gain Carry out the monitor of the waveform of TP527 CH2 2.3V±0.1V Incoming signal : TP527

with an oscilloscope. 10 STEP (NTSC)

Adjst the amplitude value so that the waveform /AUX

between the pedestal to the 9 step signal is

2.3V±0.1V.

3-I R sub bright Carry out the monitor of the waveform of TP528 CH8 2.1V±0.1V Incoming signal : TP528

with an oscilloscope. 10 STEP (NTSC)

Adjst the amplitude value so that the waveform /RGB

between the 2 step signal to the negative 2 step

signal is 2.1V±0.1V.

3-J B sub bright Carry out the monitor of the waveform of TP526 CH9 2.1V±0.1V Incoming signal : TP526

with an oscilloscope. 10 STEP (NTSC)

Adjst the amplitude value so that the waveform /RGB

between the 2 step signal to the negative 2 step

signal is 2.1V±0.1V.

The adjustment method

Adjustment

part

Adjustment value Conditions

Test point

16

Loading...

Loading...