Page 1

SERVICE MANUAL

DVD DIGITAL THEATER SYSTEM

TH-A10R

SP-PWA10

TH-A10

RM-STHA10R

TH-A10R/TH-A10TH-A10R/TH-A10

TH-A10R

TH-A10

SP-XSA10 SP-XSA10

SP-XCA10

XV-THA10R

Area Suffix

TH-A10R

B

EN

EE

XV-THA10R (DVD player)/XV-TH-A10

SP-THA10

(Speaker section)

Northern Europe

U.K.

Russia

SP-PWA10 (Powered subwoofer)

SP-XCA10 (Center speaker)

SP-XSA10 (Satellite speaker) x 4

E Continental Europe

RM-STHA10EC

Area Suffix

TH-A10

Contents

Safety Precautions

Important for laser products

Preventing static electricity

Disassembly method

Adjustment method

COPYRIGHT 2000 VICTOR COMPANY OF JAPAN, LTD.

1-2

1-3

1-4

1-5

1-21

Flow of functional operation

until TOC read

Maintenance of laser pickup

Replacement of laser pickup

Description of major ICs

1-24

1-25

1-25

1-26

No.20872

Sep. 2000

Page 2

TH-A10R/TH-A10

Safety precautions

1. This design of this product contains special hardware and many circuits and components specially

for safety purposes. For continued protection, no changes should be made to the original design

unless authorized in writing by the manufacturer. Replacement parts must be identical to those

used in the original circuits. Services should be performed by qualified personnel only.

2. Alterations of the design or circuitry of the product should not be made. Any design alterations of

the product should not be made. Any design alterations or additions will void the manufacturer`s

warranty and will further relieve the manufacture of responsibility for personal injury or property

damage resulting therefrom.

3. Many electrical and mechanical parts in the products have special safety-related characteristics.

These characteristics are often not evident from visual inspection nor can the protection afforded

by them necessarily be obtained by using replacement components rated for higher voltage,

wattage, etc. Replacement parts which have these special safety characteristics are identified in

the Parts List of Service Manual. Electrical components having such features are identified by

shading on the schematics and by ( ) on the Parts List in the Service Manual. The use of a

substitute replacement which does not have the same safety characteristics as the recommended

replacement parts shown in the Parts List of Service Manual may create shock, fire, or other

hazards.

4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the

like to be separated from live parts, high temperature parts, moving parts and/or sharp edges

for the prevention of electric shock and fire hazard. When service is required, the original lead

routing and dress should be observed, and it should be confirmed that they have been returned

to normal, after re-assembling.

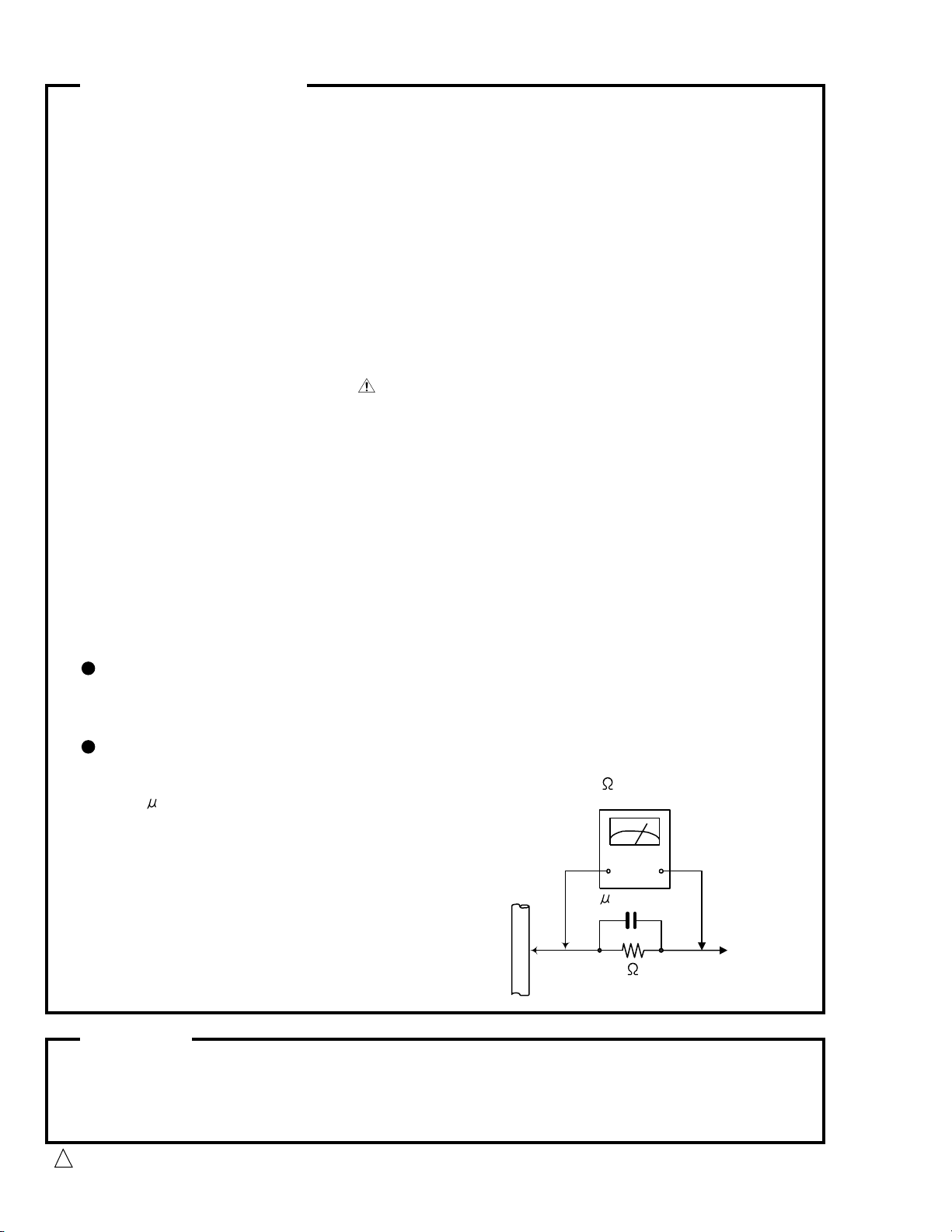

5. Leakage currnet check (Electrical shock hazard testing)

After re-assembling the product, always perform an isolation check on the exposed metal parts

of the product (antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control

shafts, etc.) to be sure the product is safe to operate without danger of electrical shock.

Do not use a line isolation transformer during this check.

Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure

the leakage current from each exposed metal parts of the cabinet , particularly any exposed

metal part having a return path to the chassis, to a known good earth ground. Any leakage

current must not exceed 0.5mA AC (r.m.s.)

Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms

per volt or more sensitivity in the following manner. Connect a 1,500 10W resistor paralleled by

a 0.15 F AC-type capacitor between an exposed

metal part and a known good earth ground.

Measure the AC voltage across the resistor with the

AC voltmeter.

Move the resistor connection to eachexposed metal

part, particularly any exposed metal part having a

return path to the chassis, and meausre the AC

voltage across the resistor. Now, reverse the plug in

the AC outlet and repeat each measurement. voltage

measured Any must not exceed 0.75 V AC (r.m.s.).

This corresponds to 0.5 mA AC (r.m.s.).

0.15 F AC TYPE

1500 10W

Good earth ground

AC VOLTMETER

(Having 1000

ohms/volts,

or more sensitivity)

Place this

probe on

each exposed

metal part.

Warning

1. This equipment has been designed and manufactured to meet international safety standards.

2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

3. Repairs must be made in accordance with the relevant safety standards.

4. It is essential that safety critical components are replaced by approved parts.

5. If mains voltage selector is provided, check setting for local voltage.

Burrs formed during molding may be left over on some parts of the chassis. Therefore,

pay attention to such burrs in the case of preforming repair of this system.

1-2

CAUTION

!

Page 3

TH-A10R/TH-A10

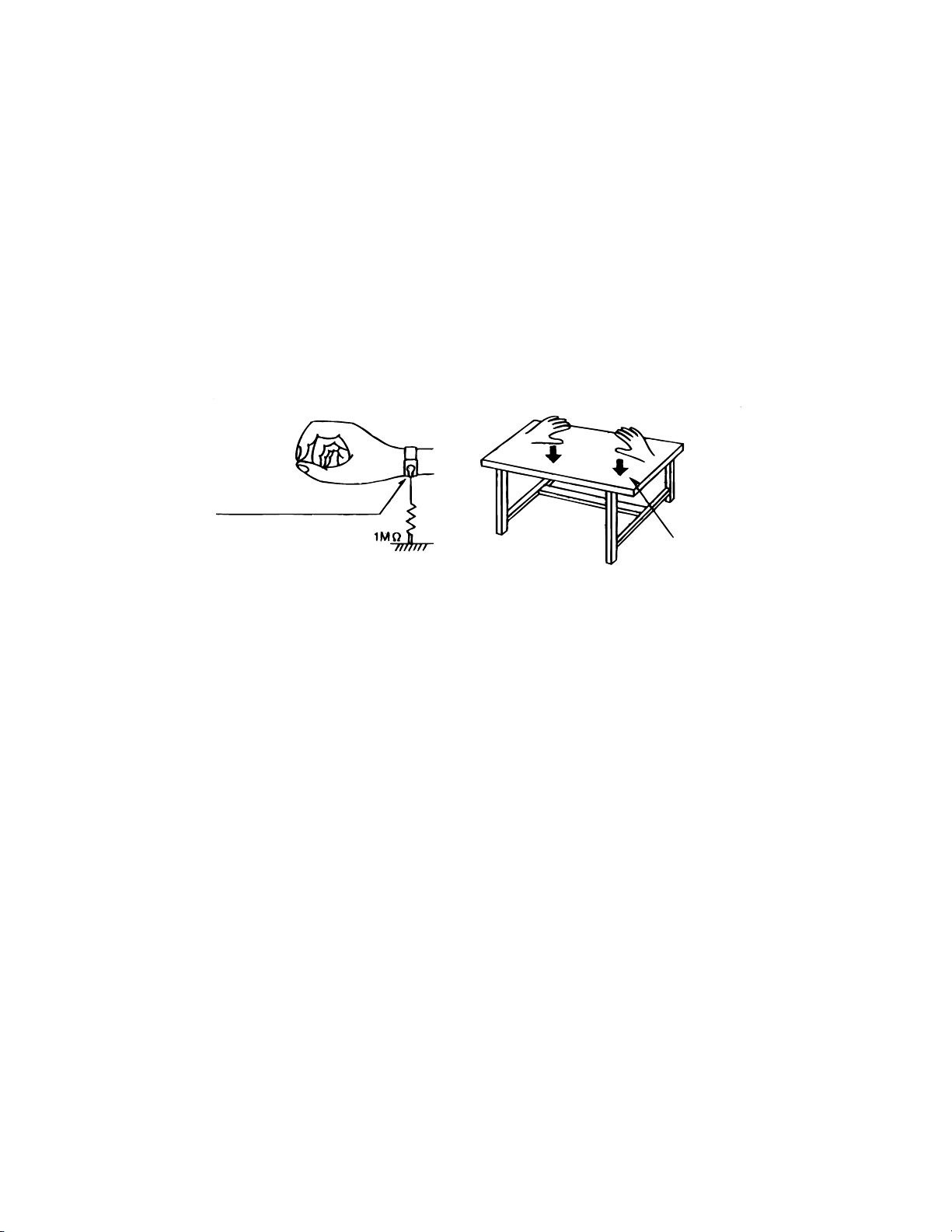

Preventing static electricity

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged,

can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs.

1.1. Grounding to prevent damage by static electricity

Static electricity in the work area can destroy the optical pickup (laser diode) in devices such as DVD players.

Be careful to use proper grounding in the area where repairs are being performed.

1.1.1. Ground the workbench

1. Ground the workbench by laying conductive material (such as a conductive sheet) or an iron plate over

it before placing the traverse unit (optical pickup) on it.

1.1.2. Ground yourself

1. Use an anti-static wrist strap to release any static electricity built up in your body.

(caption)

Anti-static wrist strap

Conductive material

(conductive sheet) or iron plate

1.1.3. Handling the optical pickup

1. In order to maintain quality during transport and before installation, both sides of the laser diode on the

replacement optical pickup are shorted. After replacement, return the shorted parts to their original condition.

(Refer to the text.)

2. Do not use a tester to check the condition of the laser diode in the optical pickup. The tester's internal power

source can easily destroy the laser diode.

1.2. Handling the traverse unit (optical pickup)

1. Do not subject the traverse unit (optical pickup) to strong shocks, as it is a sensitive, complex unit.

2. Cut off the shorted part of the flexible cable using nippers, etc. after replacing the optical pickup. For specific

details, refer to the replacement procedure in the text. Remove the anti-static pin when replacing the traverse

unit. Be careful not to take too long a time when attaching it to the connector.

3. Handle the flexible cable carefully as it may break when subjected to strong force.

4. It is not possible to adjust the semi-fixed resistor that adjusts the laser power. Do not turn it

1-3

Page 4

TH-A10R/TH-A10

Dismantling and assembling the traverse unit

1. Notice regarding replacement of optical pickup

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged,

can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing

repairs to the optical pickup or connected devices.

(Refer to the section regarding anti-static measures.)

1. Do not touch the area around the laser diode and actuator.

2. Do not check the laser diode using a tester, as the diode may easily be destroyed.

3. It is recommended that you use a grounded soldering iron when shorting or removing the laser diode.

Recommended soldering iron: HAKKO ESD-compatible product

4. Solder the land on the optical pickup's flexible cable.

Note : Short the land after shorting the terminal on the flexible cable using a clip, etc., when using an

ungrounded soldering iron.

Note : After shorting the laser diode according to the procedure above, remove the solder according

to the text explanation.

Short circuit land

Laser pick-up unit

Flexible cable

Shorting

Shot with the rclip

1-4

Page 5

TH-A10R/TH-A10

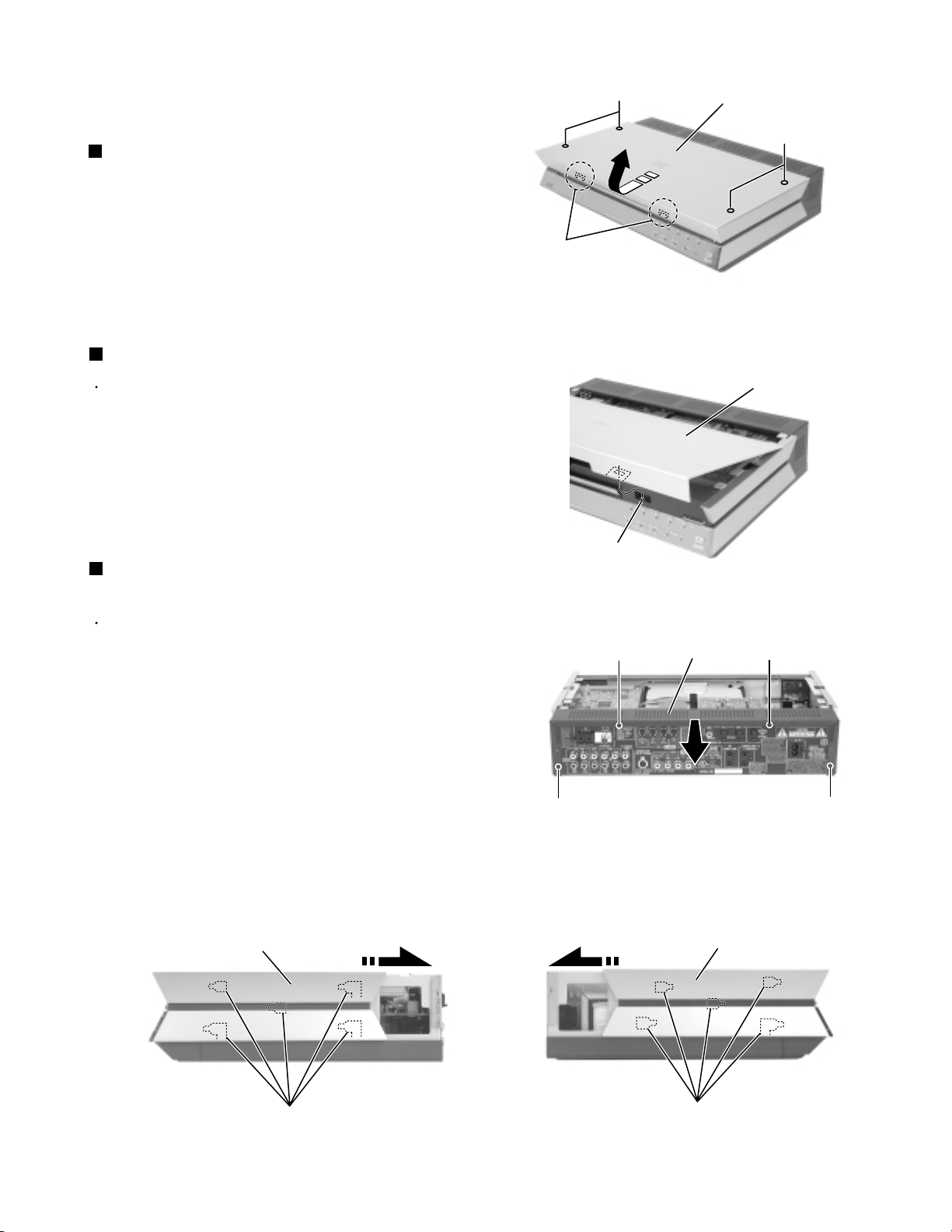

Disassembly method

<Main body>

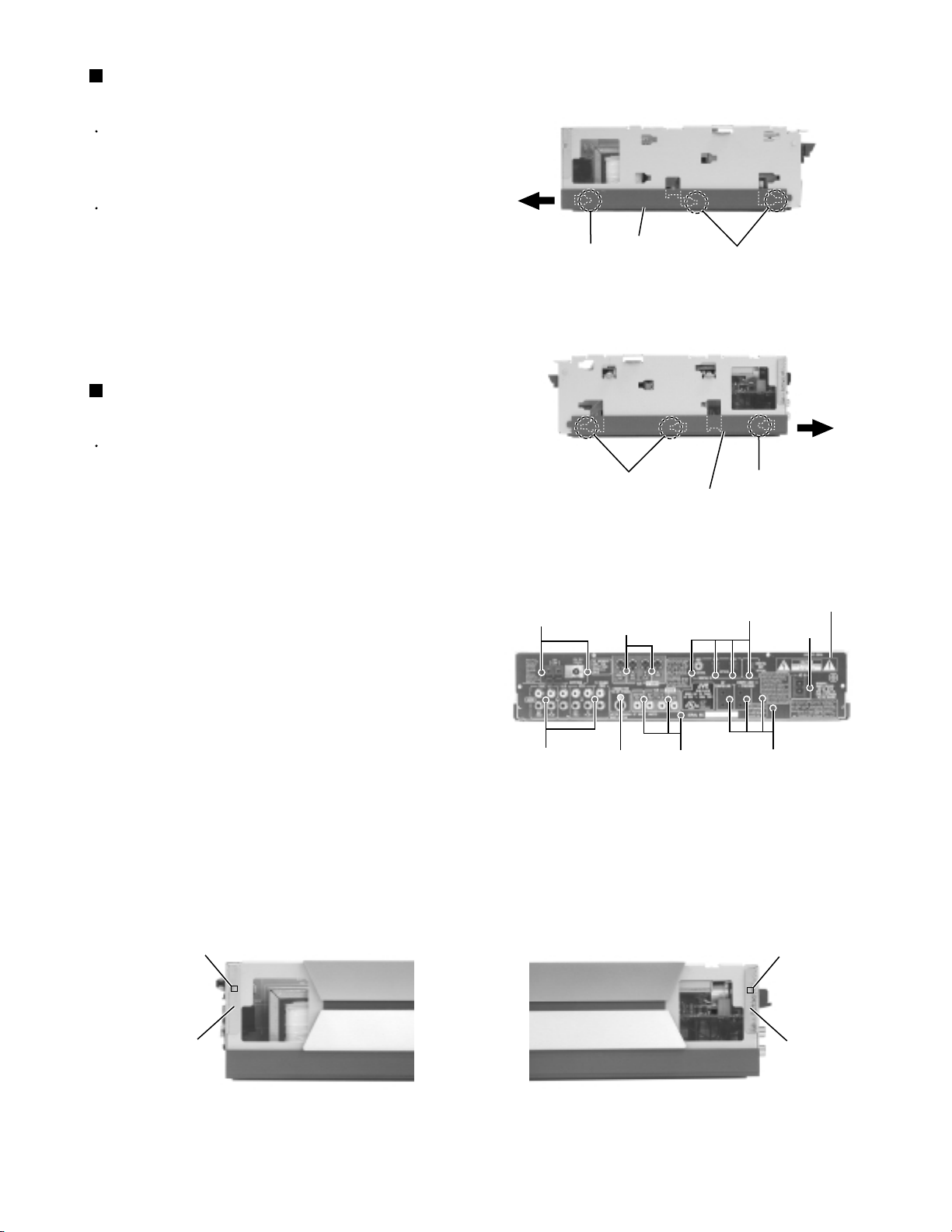

Removing the top cover

(See Fig.1 and 2)

1.

Remove the four screws A attaching the top cover

(Use an Allen wrench).

2.

Lift up the front part of the top cover to release the

two joints a and remove the top cover toward the

front.

Removing the rear cover (See Fig. 3)

Prior to performing the following procedure, remove

the top cover.

1.

Remove the four screws B attaching the rear cover

on the back of the body. Pull out the rear cover

backward.

Joints a

A

Top cover

A

Fig.1

Top cover

Removing the right and left side covers

(See Fig. 4 and 5)

Prior to performing the following procedure, remove

the top cover and the rear cover.

1.

Move the left side cover backward to release the five

joint hooks b and remove the left side cover outward.

2.

Remove the right side cover in the same way.

Right side cover

B

Joint a

B

Fig.2

Rear cover

Fig.3

Left side cover

B

B

Joints b

Joints b

Fig.4Fig.5

1-5

Page 6

TH-A10R/TH-A10

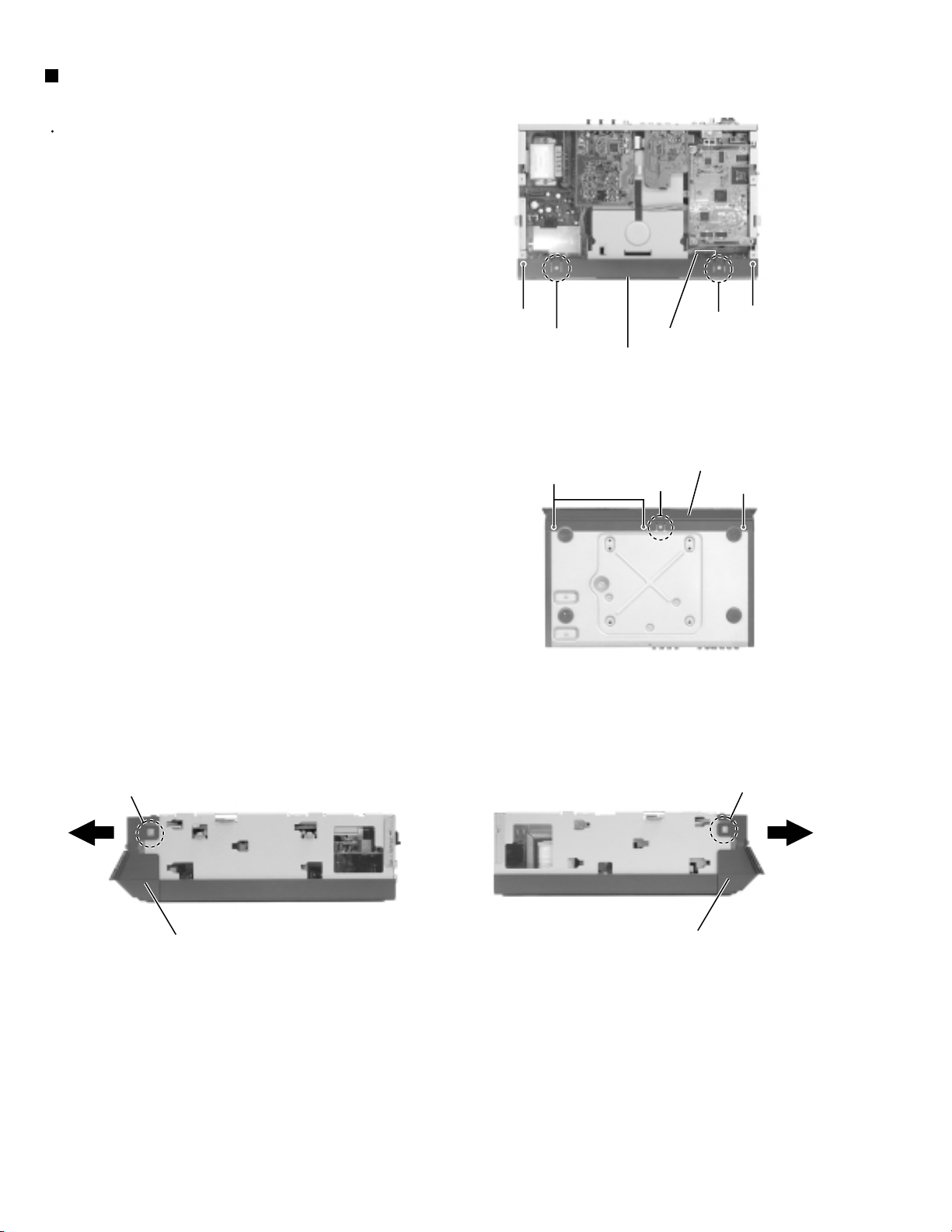

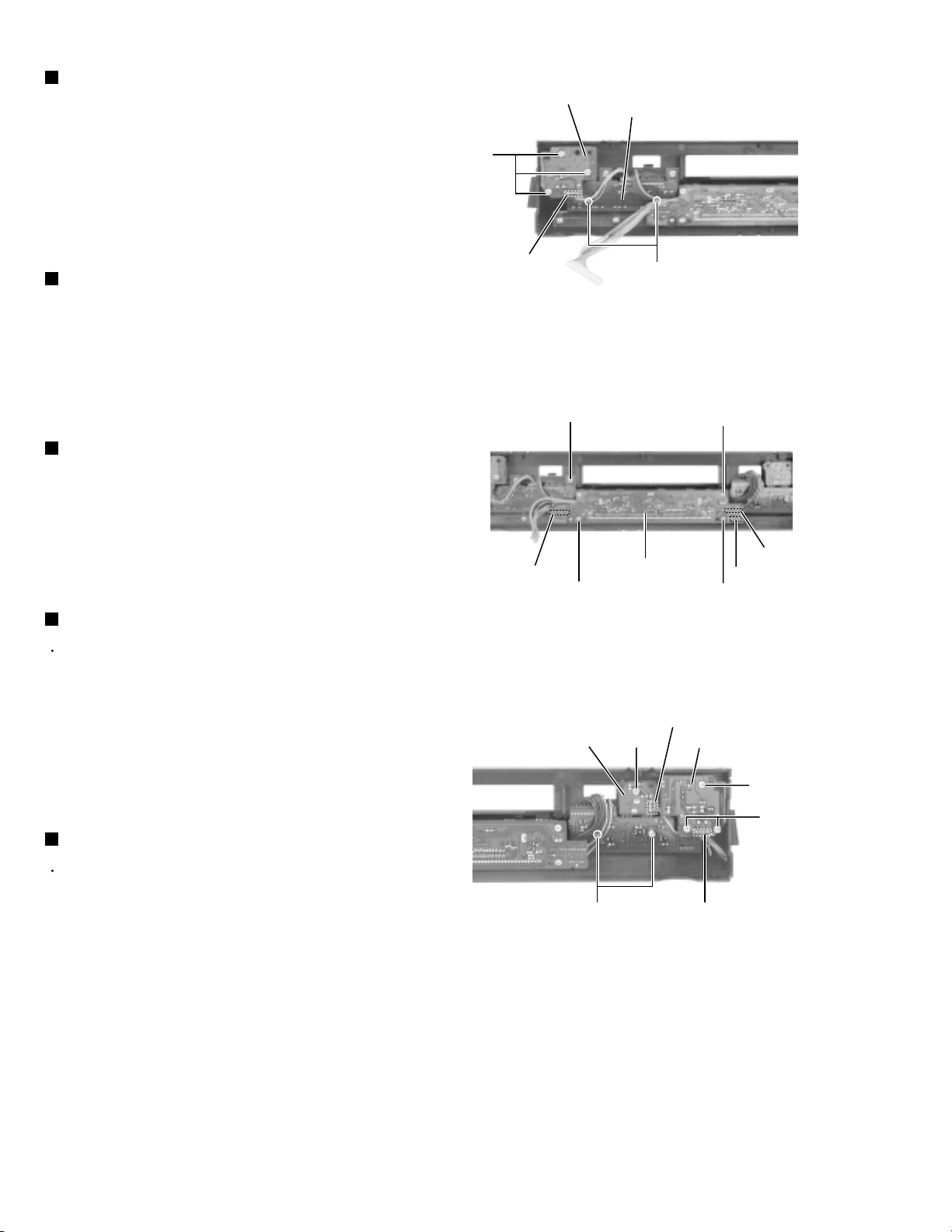

Removing the front panel assembly

(See Fig. 6 to 9)

Prior to performing the following procedure, remove

the top cover, the rear cover and the side covers.

1.

Disconnect the harness from connector CN802 on

the main board on the upper side of the body.

2.

Remove the two screws C on the upper side of the

body.

3.

Remove the three screws D on the bottom of the

body.

4.

Release the five joints c and detach the front panel

assembly toward the front.

C

Joint c

Joint c

CN802

Front panel assembly

Fig.6

C

Joint c

D

Front panel assembly

Joint c

Fig.7

D

Joint c

1-6

Front panel assembly

Front panel assembly

Fig.8Fig.9

Page 7

Removing the right and left corner

covers (See Fig.10 and 11)

Prior to performing the following procedure, remove

the top cover, the rear cover, the side covers and the

front panel assembly.

It is not necessary to remove the front panel

assembly.

1.

Move the left corner cover backward to release the

three joint hooks d.

2.

Remove the right corner cover in the same way.

Removing the rear panel

(See Fig.12 to 14)

Prior to performing the following procedure, remove

the top cover and the rear cover.

1.

Remove the eighteen screws E and the one screw F

attaching the rear panel.

Left corner cover

Joint d

Joints d

TH-A10R/TH-A10

Joints d

Fig.10

Joint d

Right corner cover

Fig.11

2.

Release the two joints e on both sides of the body.

Joint e

E

E

F

E

E

Fig.12

E

Rear panel

E

E

Joint e

Rear panel

Rear panel

Fig.12Fig.12

1-7

Page 8

TH-A10R/TH-A10

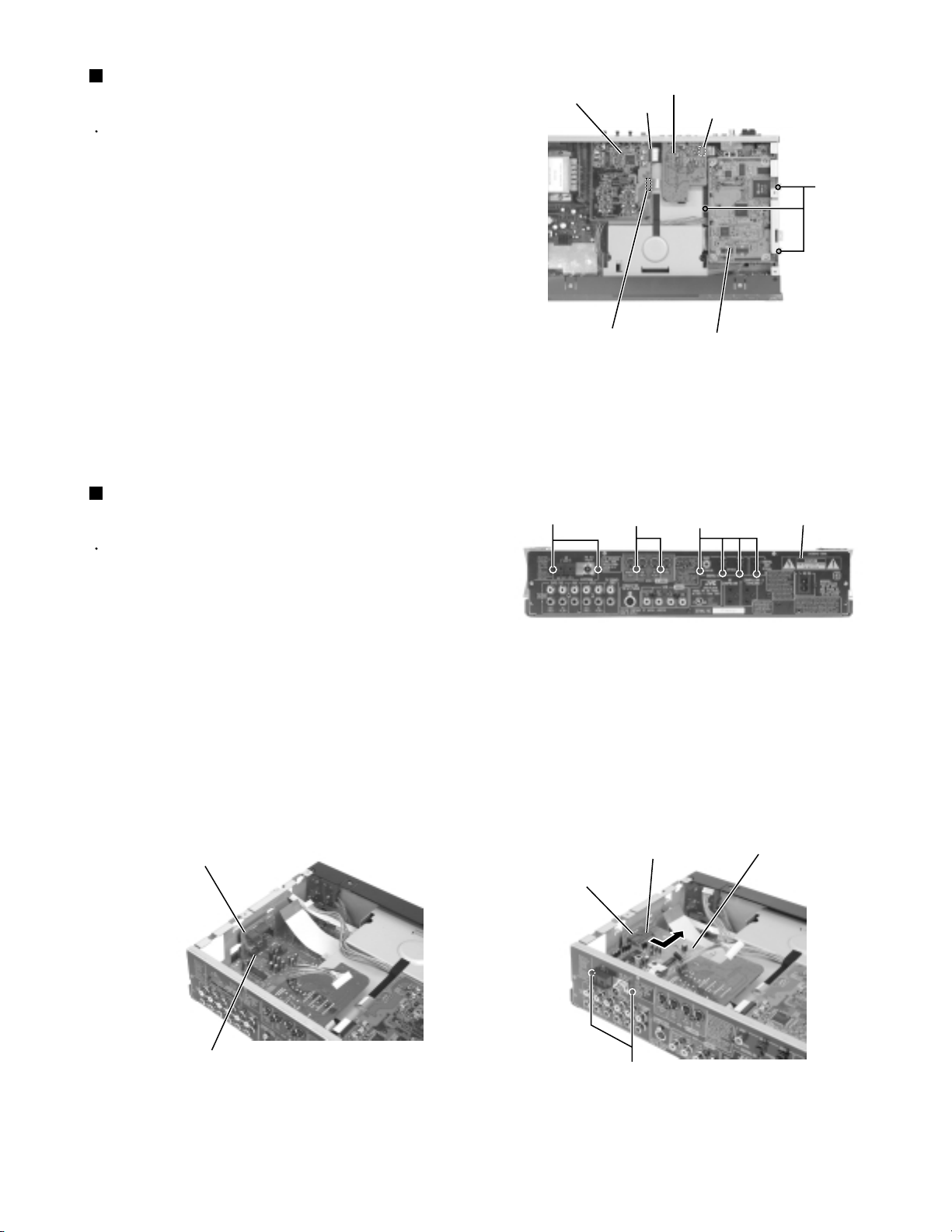

Removing the DVD servo control board

(See Fig.15 to 17)

Prior to performing the following procedure,

remcover and the right side cover.ove the top cover,

the rear

1.

Remove the three screws G and pull the DVD servo

control board case upward.

2.

Disconnect the harness from connector CN501 and

CN503, and the card wire from CN101, CN103 and

CN502 of the DVD servo control board on the

underside of the DVD servo control board case.

3.

Remove the four screws H attaching the DVD servo

control board.

Digital I / O board

CN687

CN501

Analog I / O board

CN681

CN201

DVD servo control board (case)

Fig.15

CN503

CN502

G

DVD servo control board case

DVD servo control board

H

DVD servo control board case

CN103

Fig.16

H

Fig.17

CN101

H

H

1-8

Page 9

TH-A10R/TH-A10

Removing the analog I / O board / the

digital I / O board (See Fig.18 and 19)

Prior to performing the following procedure, remove

the top cover and the rear cover.

1.

Remove the two screws E attaching the analog I / O

board on the back of the body.

2.

Disconnect the card wire from connector CN201 on

the analog I / O board.

3.

Remove the four screws E attaching the digital I / O

board on the back of the body.

4.

Disconnect the card wire from connector CN681 and

CN687 on the digital I / O board.

Removing the tuner board / the sub

board (See Fig.20 and 21)

Digital I / O board

CN687

E

Analog I / O board

CN681

E

CN201

DVD servo control board (case)

Fig.18

E

G

Rear panel

Prior to performing the following procedure, remove

the top cover, the rear cover and the DVD servo

control board case.

1.

Remove the two screws E attaching the tuner board

on the back of the body.

2.

Disconnect connector CN111 on the tuner board

from the sub board.

3.

Disconnect connector CN131 on the sub board from

the main board.

Sub board

Sub board

CN111

Fig.19

Tuner board

CN131

E

Fig.20Fig.21

1-9

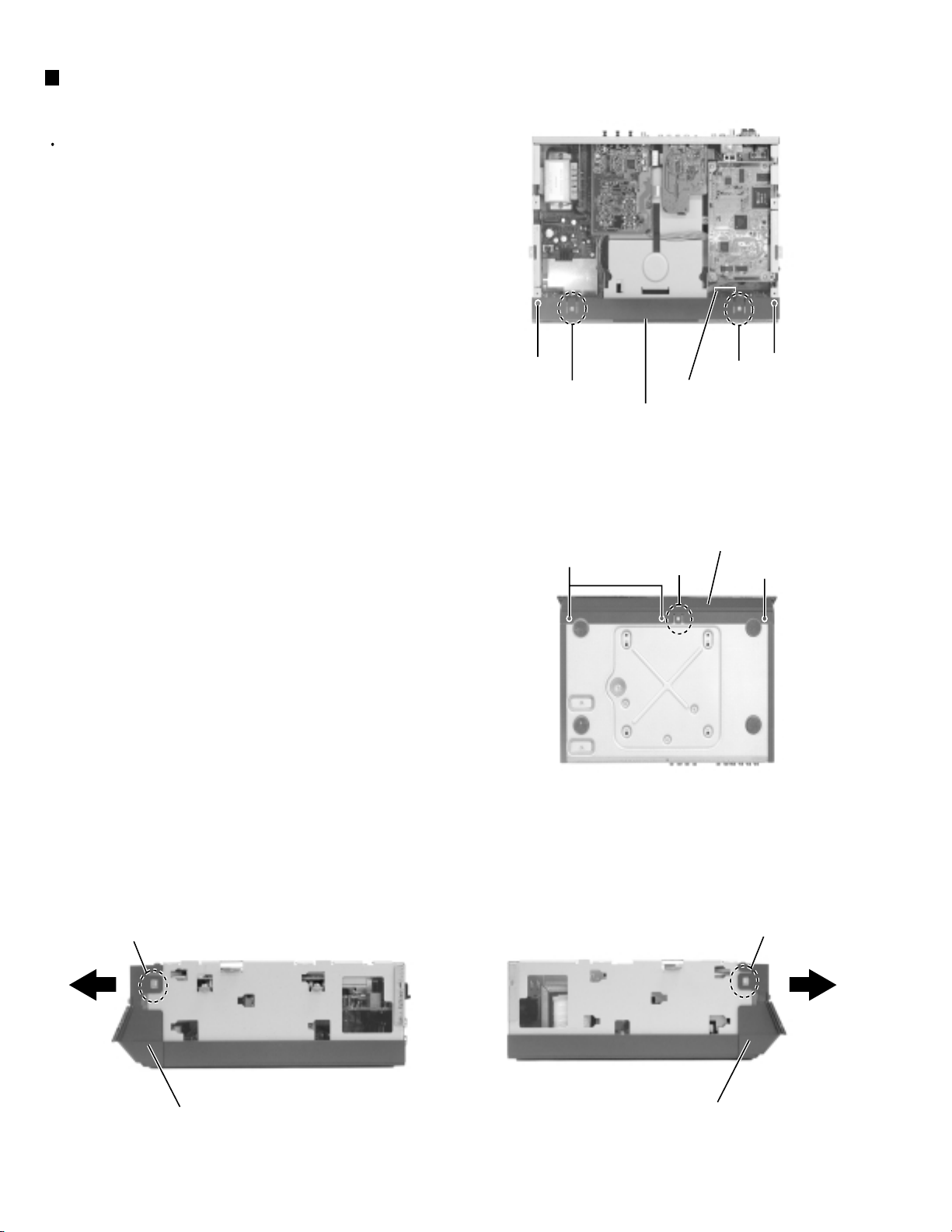

Page 10

TH-A10R/TH-A10

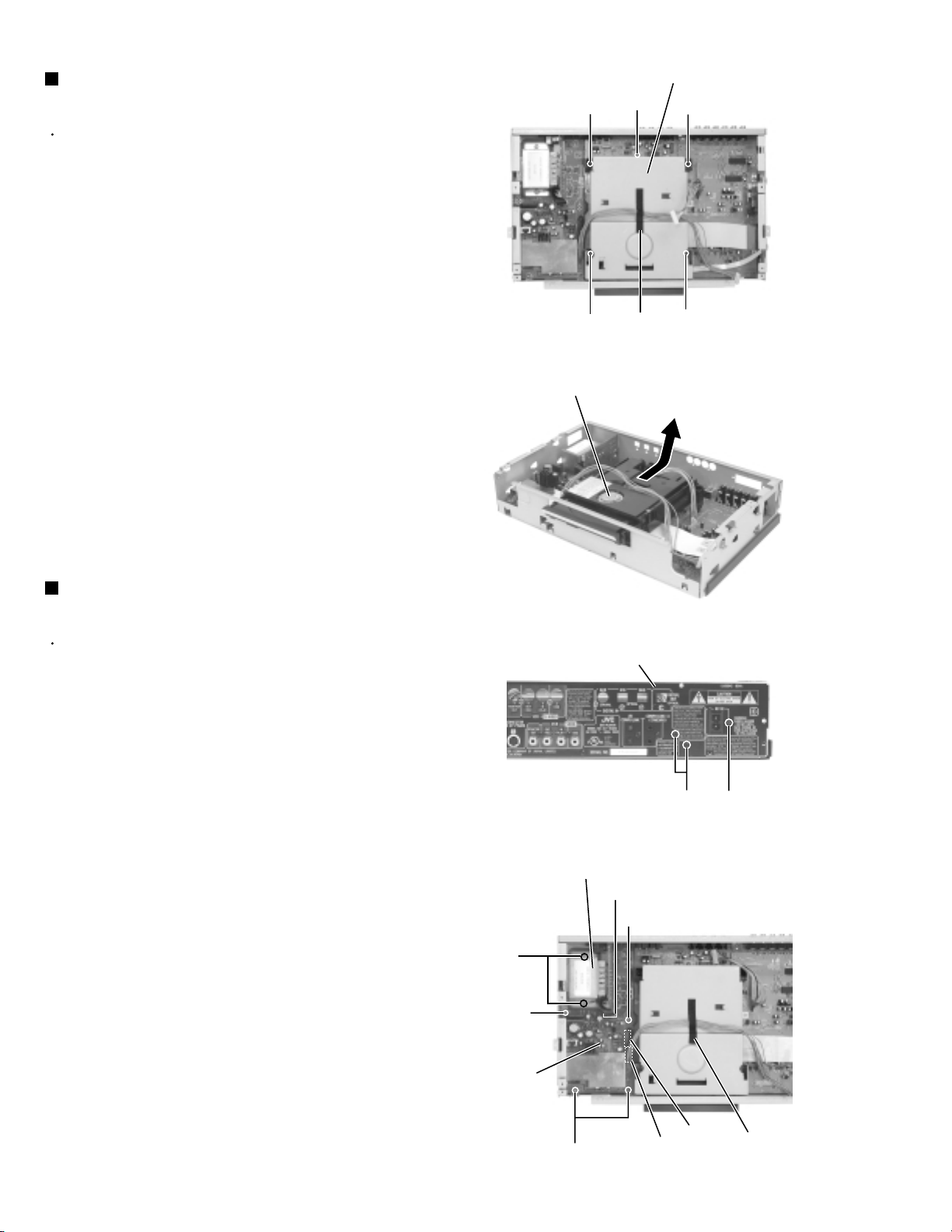

Removing the DVD mechanism assembly

(See Fig.22 and 23)

Prior to performing the following procedure, remove

the top cover, the rear cover, the front panel

assembly, the DVD servo control board case, the

analog I / O board, the digital I / O board and the

tuner board.

1.

Disconnect the harnesses from the spacer on the

upper side of the DVD mechanism cover.

2.

Remove the two screws I and the one screw J

attaching the DVD mechanism cover.

3.

Remove the two screws K attaching the DVD

mechanism assembly.

4.

Remove the DVD mechanism assembly upward

while pulling it backward.

K

I

DVD mechanism assembly

DVD mechanism cover

J

Spacer

Fig.22

K

I

Removing the power board

(See Fig.24 and 25)

Prior to performing the following procedure, remove

the top cover, the rear cover, the front panel

assembly, the DVD servo control board case and the

digital I / O board.

1.

Disconnect the harness from the spacer on the

upper side of the DVD mechanism cover.

2.

Remove the two screws E attaching the power

board on the back of the body.

3.

Disconnect the harness from connector CN911 and

CN912 on the power board.

4.

Remove the four screws L attaching the power

board.

5.

Disconnect connector CN913 and CN914 of the

power board from the main board by pulling out them

respectively.

Fig.23

Rear panel

Fig.24

Power transformer assembly

CN911,CN912

L

M

L

E

E

1-10

Power board

CN914

CN913

Spacer

L

Fig.25

Page 11

TH-A10R/TH-A10

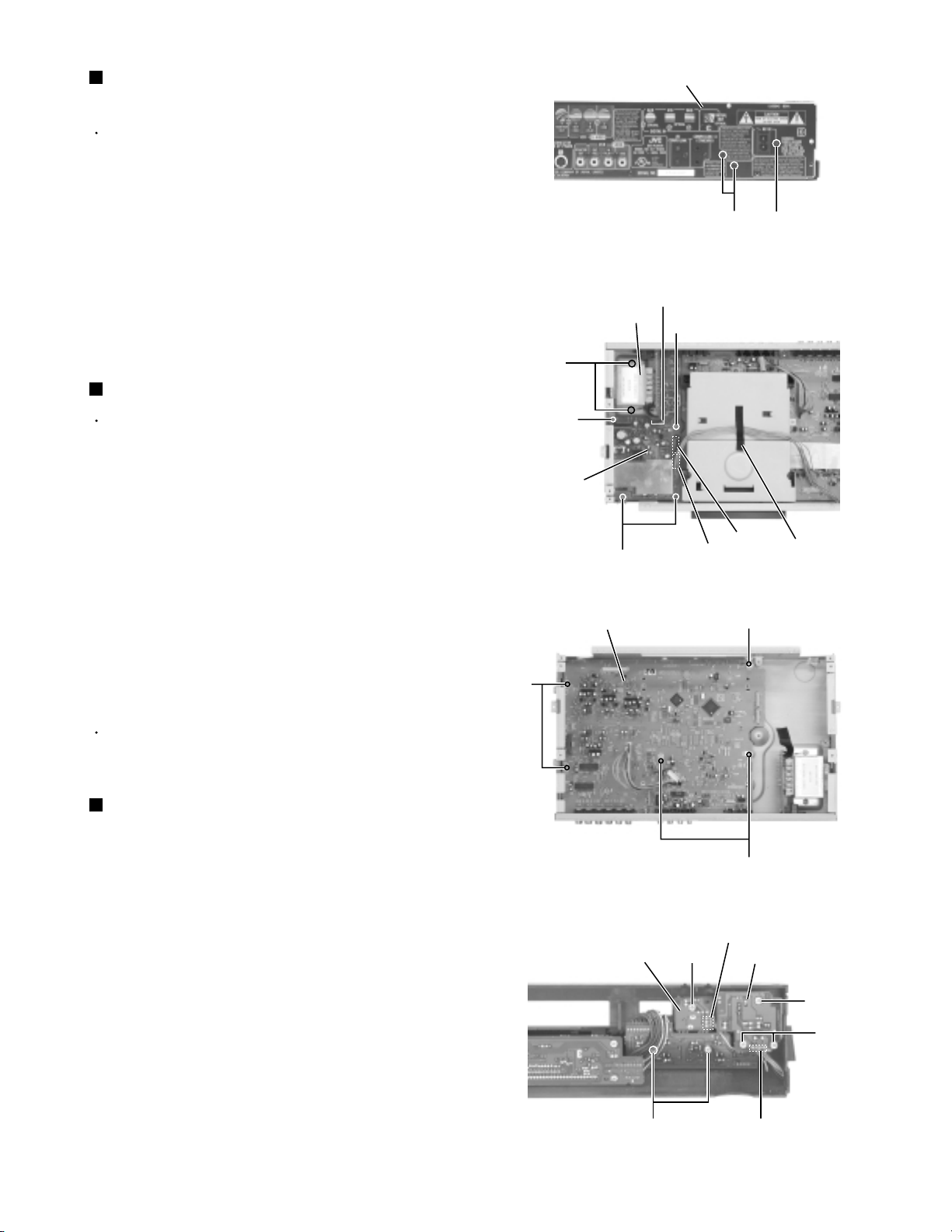

Removing the power transformer assembly

(See Fig.24 and 25)

Prior to performing the following procedures, remove

the top cover and the rear cover.

1.

Disconnect the harnesses from connector CN911

and CN912 on the power board.

2.

Remove the two screws M attaching the power

transformer assembly.

3.

Remove the screw E attaching the power

transformer assembly on the back of the body.

Removing the main board (See Fig.26)

Prior to performing the following procedure, remove

the top cover, the rear cover, the front panel

assembly, the rear panel, the DVD mechanism

assembly, the power board and the sub board.

1.

Remove the four DVD spacers on the upper side of

the main board.

2.

Remove the five screws N attaching the main board.

M

L

Power board

Rear panel

Fig.24

CN911,CN912

L

Fig.25

L

CN914

E

CN913

E

Spacer

<Front panel assembly>

Prior to performing the following procedure, remove

the top cover, the rear cover, the side covers and the

front panel assembly.

Removing the power switch board

(See Fig.27)

1.

Dithe harness from connector CN705 on the power

switch board.sconnect

2.

Remove the three screws O attaching the power

switch board.

N

Mainboard

IC board

Fig.26

R

N

N

CN706

Power switch board

O

O

S

Fig.27

LED board

1-11

Page 12

TH-A10R/TH-A10

Removing the eject board (See Fig.28)

1.

Disconnect the harness from connector CN702 on

the eject board.

Eject board

Switch board

2.

Remove the three screws P attaching the eject

board.

Removing the LCD board (See Fig.29)

1.

Remove the four screws Q attaching the LCD board.

2.

Unsolder WA701, WA703 and WA704 on the LCD

board.

Removing the IC board (See Fig.27)

1.

Remove the screw R attaching the IC board.

2.

Disconnect the harness from connector CN706 on

the IC board.

Removing the LED board (See Fig.27)

P

CN702

WA701

Q

Q

T

Fig.28

LCD board

Fig.29

Q

WA704

WA703

Q

Prior to performing the following procedure, remove

the LCD board and the IC board.

1.

Disconnect the harness from connector CN705 on

the power switch board.

2.

Remove the two screws S attaching the LED board.

Removing the switch board (See Fig.28)

Prior to performing the following procedure, remove

the LCD board.

1.

Disconnect the harness from connector CN702 on

the eject board.

2.

Remove the two screws T attaching the switch

board.

IC board

S

R

Fig.27

CN706

Power switch board

O

O

LED board

1-12

Page 13

TH-A10R/TH-A10

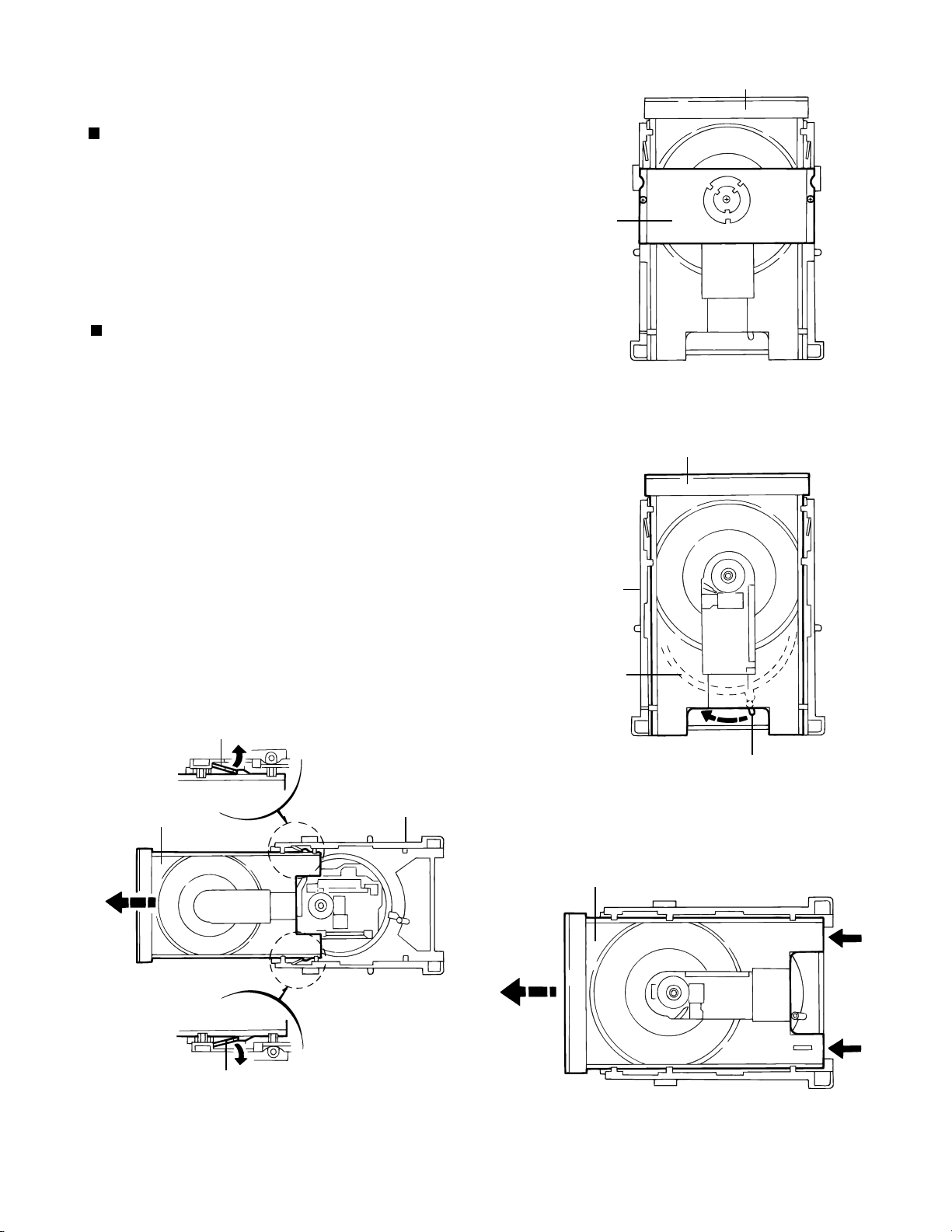

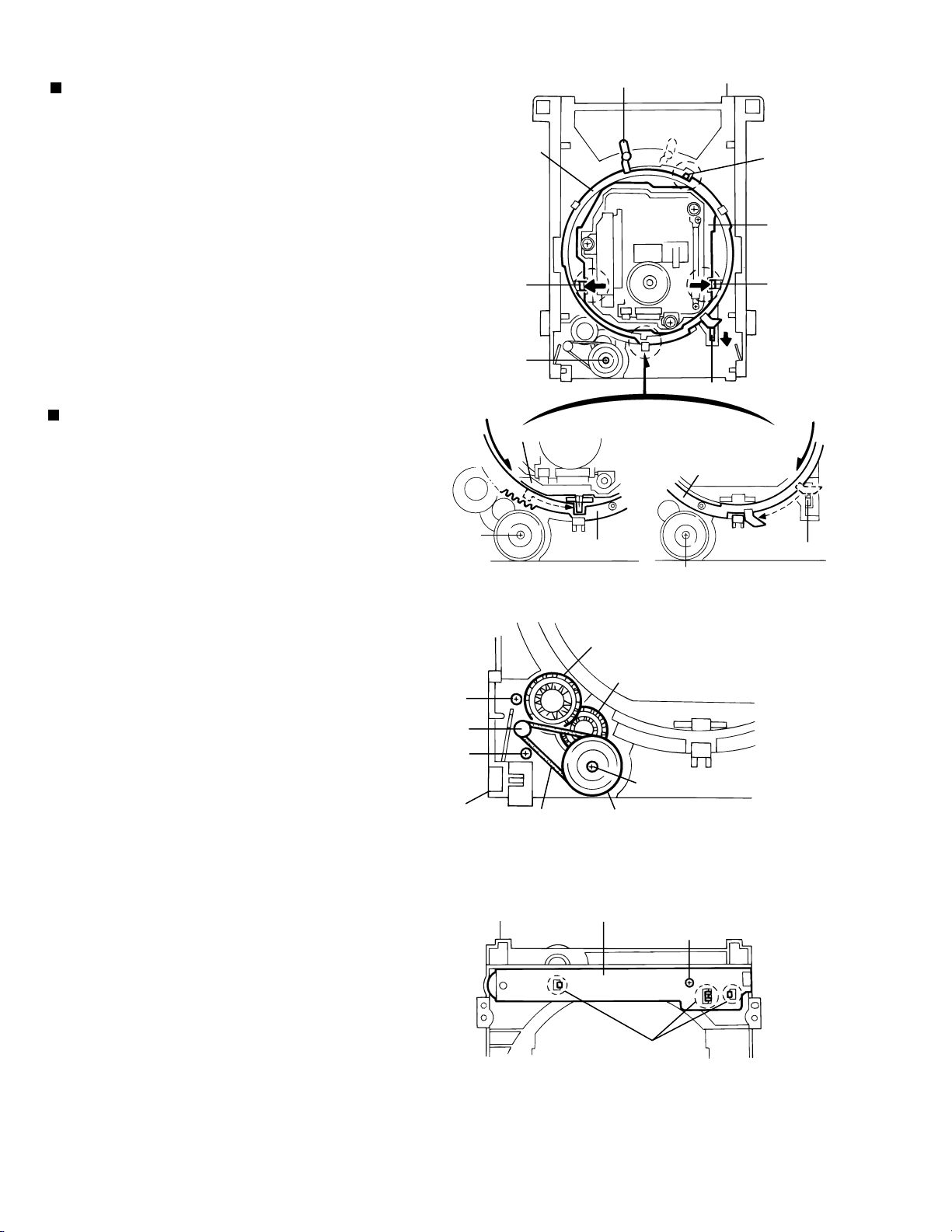

<Removing DVD mechanism unit>

Removing the clamper base (refer to Figure 1)

o Remove the top cover.

o Remove the DVD mechanism unit.

1. Remove the two screws at A fixing the clamper base.

Removing the loading tray (refer to Figures 2 - 4)

o Remove the clamper base.

1. Turn the up-down cam lever clockwise (in the direction

of the arrow in Figure 2) to lower the position of the mechanism.

2. Manually set the loading tray to the fully-open position.

3. Stretch the tray stoppers on both sides of the loading

base outward and pull out the tray.

Loading tray

Clamper base

Figure 1

Loading tray (front side)

Tray stopper

Loading tray

Loading base

Loading base

Up-down cam

Lever

Figure 2

Loading tray

Push

Push

Tray stopper

Figure 4

Figure 3

1-13

Page 14

TH-A10R/TH-A10

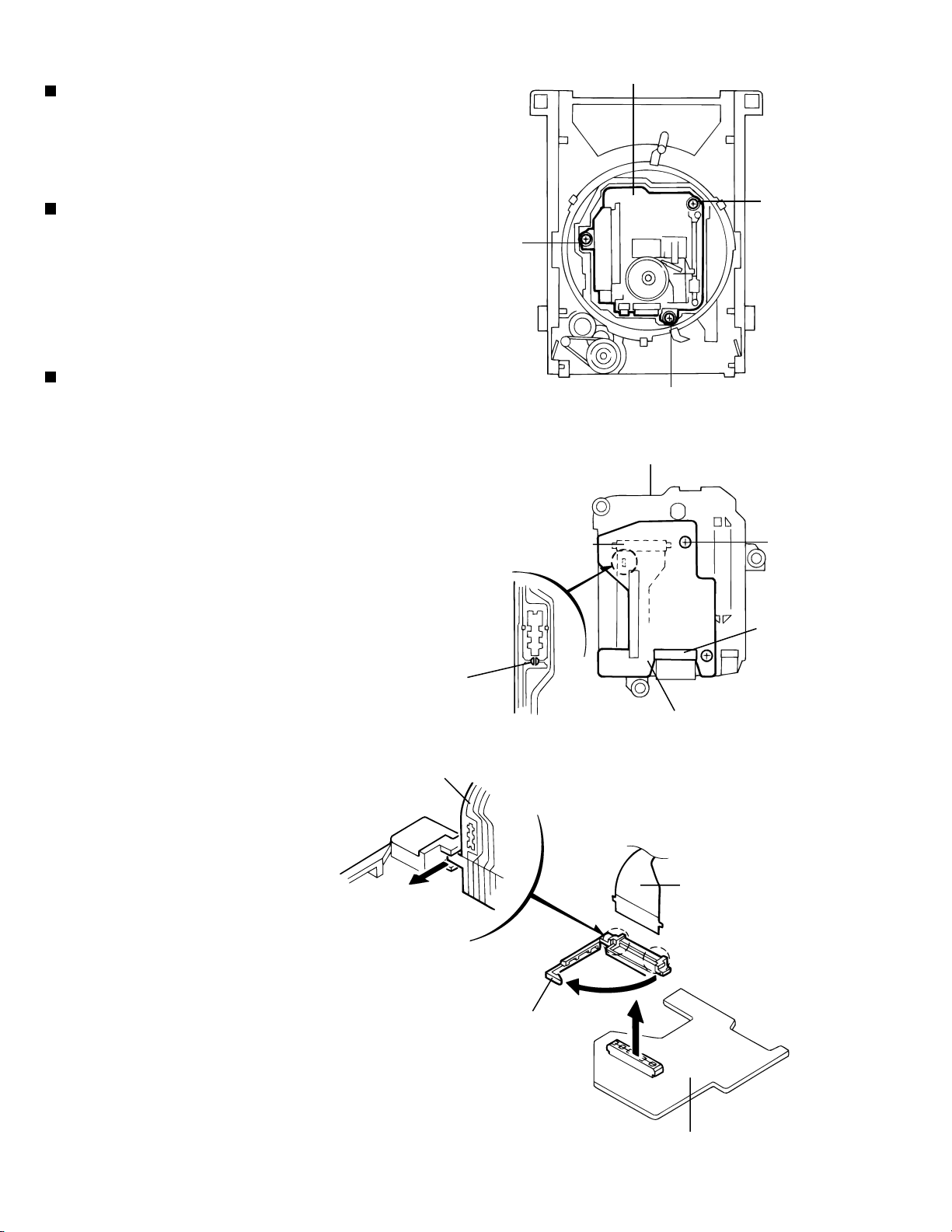

Removing the traverse mechanism unit (refer to Figure 5)

o Remove the loading tray.

1. Remove the three screws at B fixing the traverse

mechanism unit.

Traverse mechanism unit

Protecting the optical pickup

o Solder the flexible ground point on the optical pickup

when replacing the pickup or before detaching the

mechanism control board. When assembling the unit,

remove the solder last.

Removing the mechanism control board

(refer to Figures 6 - 7)

o Remove the traverse unit. (Can be detached without

detaching the T-mechanism unit.)

1. Remove the two screws at C fixing the mechanism

control base from the bottom of the traverse unit.

2. Pull out the CN12 connector and detach the

mechanism control board.

3. Remove the card wire from the CN13 connector

on the mechanism control board.

4. Pull out the FPC holder from the CN12 connector

on the reverse side of the mechanism control board

and remove the flexible harness, referring to Figure 7.

B

Enlargement

Figure 5

Traverse mechanism unit

CN12

B

B

C

CN13

Connection area

(Solder the flexible

ground point)

Flexible harness

3

Enlargement

FPC holder

Figure 7

Mechanism control board

Figure 6

Flexible harness

2

1

CN12

Mechanism control board

1-14

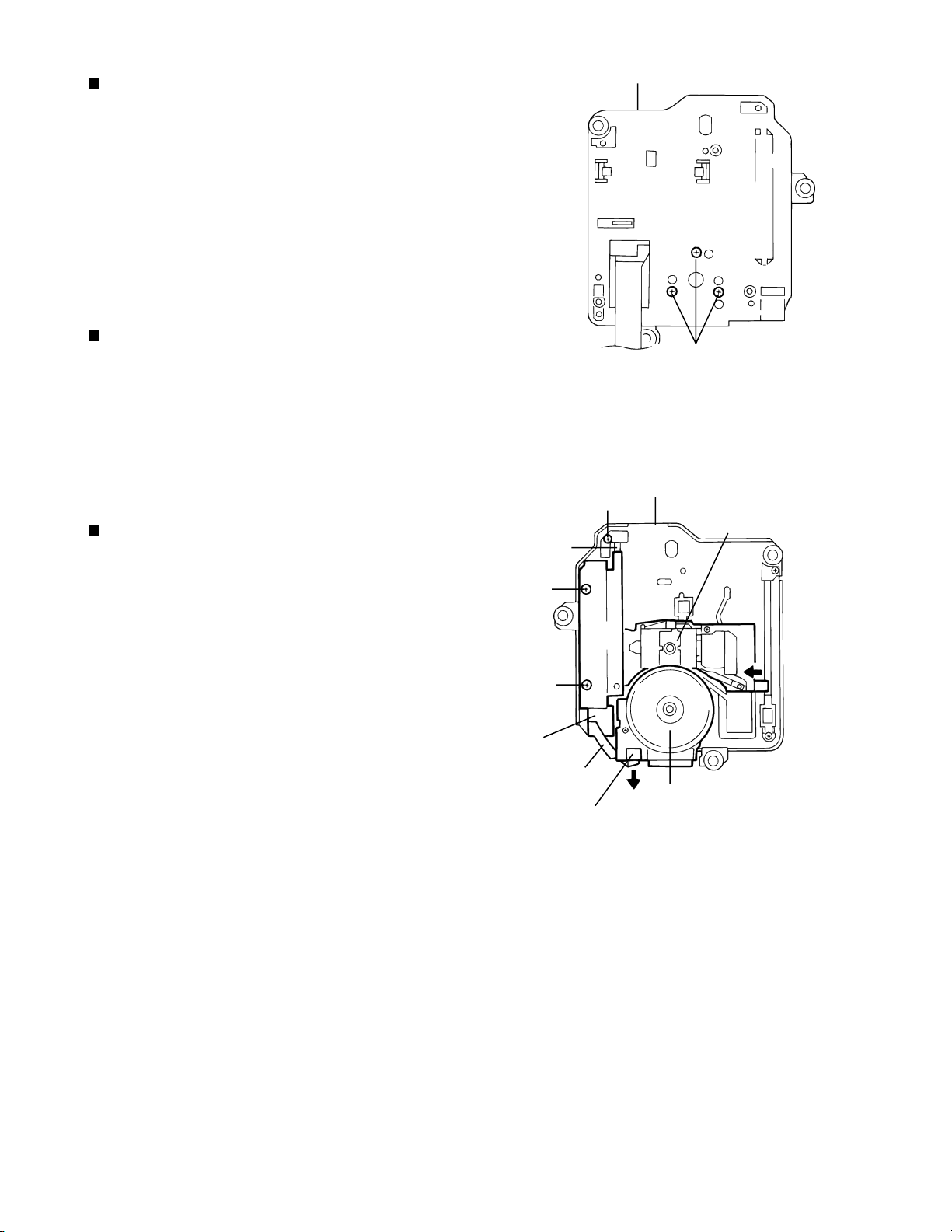

Page 15

TH-A10R/TH-A10

Removeing the turntable and spindle motor assemby

(refer to Figures 8 - 9)

o Remove the traverse mechanism unit.

o Solder the flexible ground point on the optical pickup.

(Figure 6)

o Remove the mechanism control board.

1. Remove the flexible harness from the feed motor

connector on the spindle motor board assembly.

2. Remove the three screws at D fixing the spindle motor

from the bottom of the traverse chassis.

Removing the feed motor unit (refer to Figure 9)

o Remove the traverse mechanism unit.

o Remove the mechanism control board.

1. Remove the FPC from the feed motor connector

on the turntable spindle motor board.

2. Remove the two screws at E fixing the feed motor unit.

Removing the optical pickup unit (refer to Figure 9)

o Remove the traverse mechanism unit.

Guide shaft B

o Remove the mechanism control board.

o Remove the feed motor unit.

1. Remove the screw at F fixing the guide shaft holder at B,

then simultaneously remove the guide shaft at B and the

optical pickup unit. While doing so, slide the unit

horizontally away from the guide shaft at A.

Traverse chassis

D

Figure 8

Traverse mechanism unit

F

Pick-up assembly

E

Guide shaft A

E

Feed motor assembly

Flexible harness

Feed motor connector

Turn table spindle motor unit

Figure 9

1-15

Page 16

TH-A10R/TH-A10

Removeing the loading mechanism parts

(refer to Figures 10 - 11)

o Remove the clamper base.

o Remove the disk tray.

1. Turn the lever counterclockwise until it stops (position 1),

while pushing the switch lever in the direction of the

arrow and pushing up the pawl at A using a screwdriver.

2. Stretch the two pawls at B outward using a screwdriver

and remove the chassis.

3. Turn the lever clockwise (position 2) to remove the

up-down cam.

4. Remove the pulley gear and the pulley gear belt after

removing the screw at G fixing the pulley gear.

5. Pull out drive gear 2 then drive gear 1.

(1)When detaching

Removing the loading motor board

the chassis.

(refer to Figures 11 - 12)

o Remove the clamper base.

o Remove the disk tray.

1. Remove the loading belt.

2. Remove the two screws at H fixing the loading motor.

3. Remove the screw at I and the three pawls at C fixing

the loading motor base from the reverse side of the

loading base.

Up-down cam

Pawl B

G

chassis.

G

Lever

1

Up-down cam

Figure 10

Loading base

2

Pawl A

Chassis

Pawl B

Switch lever

(2)When detaching

the up-down cam.

Up-down cam

Switch lever

G

H

Loading motor unit

Loading base

H

Loading belt

Loading base

Drive gear 1

Drive gear 2

G

Pulley gear

Figure 11

Loading motor board

I

Pawl C

1-16

Figure 12

Page 17

TH-A10R/TH-A10

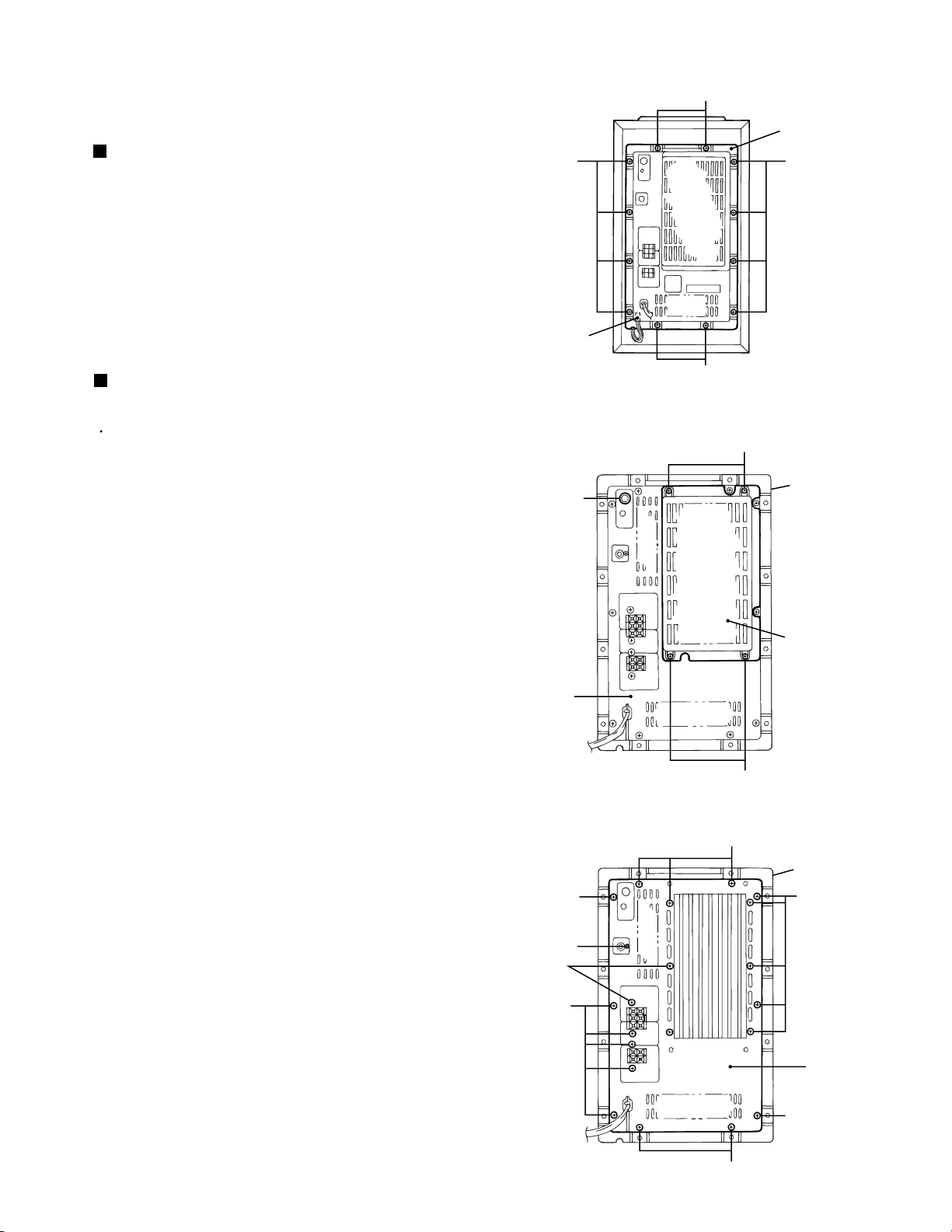

Disassembly method

<Speaker>

Removing the amplifier assembly

(See Fig.1)

1.

Remove the twelve screws A attaching the amplifier

assembly on the back of the body.

2.

Move the amplifier assembly backward and

disconnect the harness from connector CN109 in the

lower part of the amplifier assembly.

Removing the heat sink cover and the

amplifier cover (See Fig.2 and 3)

Prior to performing the following procedure, remove

the amplifier assembly.

1.

Pull out the volume knob.

2.

Remove the four screws B attaching the heat sink

cover.

AA

CN109

Volume knob

A

Amplifier

assembly

A

Fig.1

B

Amplifier

assembly

3.

Remove the twenty screws C and the one screw D

attaching the amplifier cover.

Amplifier

cover

D

C

C

Fig.2

Heat sink

cover

B

C

Amplifier

assembly

CC

Fig.3

Amplifier

cover

C

C

1-17

Page 18

TH-A10R/TH-A10

Removing the front panel assembly

(See Fig. 6 to 9)

Prior to performing the following procedure, remove

the top cover, the rear cover and the side covers.

1.

Disconnect the harness from connector CN802 on

the main board on the upper side of the body.

2.

Remove the two screws C on the upper side of the

body.

3.

Remove the three screws D on the bottom of the

body.

4.

Release the five joints c and detach the front panel

assembly toward the front.

C

Joint c

Joint c

CN802

Front panel assembly

Fig.6

C

Joint c

D

Front panel assembly

Joint c

Fig.7

D

Joint c

1-18

Front panel assembly

Front panel assembly

Fig.8Fig.9

Page 19

Removing the right and left corner

covers (See Fig.10 and 11)

Prior to performing the following procedure, remove

the top cover, the rear cover, the side covers and the

front panel assembly.

It is not necessary to remove the front panel

assembly.

1.

Move the left corner cover backward to release the

three joint hooks d.

2.

Remove the right corner cover in the same way.

Removing the rear panel

(See Fig.12 to 14)

Prior to performing the following procedure, remove

the top cover and the rear cover.

1.

Remove the eighteen screws E and the one screw F

attaching the rear panel.

Left corner cover

Joint d

Joints d

TH-A10R/TH-A10

Joints d

Fig.10

Joint d

Right corner cover

Fig.11

2.

Release the two joints e on both sides of the body.

Joint e

E

E

F

E

E

Fig.12

E

Rear panel

E

E

Joint e

Rear panel

Rear panel

Fig.12Fig.12

1-19

Page 20

TH-A10R/TH-A10

Removing the DVD servo control board

(See Fig.15 to 17)

Prior to performing the following procedure,

remcover and the right side cover.ove the top cover,

the rear

1.

Remove the three screws G and pull the DVD servo

control board case upward.

2.

Disconnect the harness from connector CN501 and

CN503, and the card wire from CN101, CN103 and

CN502 of the DVD servo control board on the

underside of the DVD servo control board case.

3.

Remove the four screws H attaching the DVD servo

control board.

Digital I / O board

CN687

CN501

Analog I / O board

CN681

CN201

DVD servo control board (case)

Fig.15

CN503

CN502

G

1-20

DVD servo control board case

CN103

Fig.16

DVD servo control board

H

DVD servo control board case

Fig.17

CN101

H

H

H

Page 21

Main Adjustment

Adjustment and confirmation matter

(1) Auto adjustment method

If microprocessor (IC401, IC402, IC714, IC716) or DVD Prek-up is replaced, initialize

the DVD player in the following matter:

1. Initialize the DVD player in the following matter:

1) Make sure that no disc is on the tray.

2) Insert the power pulag to the outret while pressing "PLAY" and "OPEN/CLOSE" button at the

same time.

FL Display indicate ; Region cord.

3) Press Enter button. And EEPROM initialize start.

4) When indicate "96kHz EEPROM" on the display , initialize finished.

Note : During the EEPROM initialization the keys may not be operated.

Press the "POWER" key to initiate the STAND-BY mode and the test mode will then

be cancelled.

TH-A10R/TH-A10

(2) Confirmation of DVD RF level

1.The oscilloscope is connected between "1"(RFOP) of

CN104 and "2"(GND).

2.Reproduction of the test disc (VT-501)

made by JVC.

3.It is confirmed that RF LEVEL is 350mVp-p 150mVp-p.

4.When there is disorder in the waveform road cuts etc,

test disk is exchanged and measured.

(3) Confirmation of CD jitter level and RF level

1. The CD jitter meter is connected between "11"(GND)

of CN104 and "12"(FLTOUT).

The RF level is observed at the same time.

2.The first test disk(CTS-1000) made of JVC is reproduced.

3.It is confirmed that RF LEVEL is 360 100mVp-p.

5. When there is disorder in the waveform road cuts

etc, test disk is exchanged and measured.

P12

and

GND

DVD SERVO CONTROL PWB

P1

and

GND

FRONT SIDE

1-21

Page 22

TH-A10R/TH-A10

(4) Flap adjustment of the Pick-up guide shaft

1) Make sure that there is no disc on the tray.

2) Press both the "PLAY" and "OPEN/CLOSE" keys of the main unit to activate the primary

power and ∗ ∗ ( ∗ ∗ ; Version3, ; Region cord) will be displayed on the FL indicator.

Note: If the FL indicator display stops and remains at "TEST 0", unplug the power

cord from the outlet and after waiting at least 1 second, plug it in again. After

the tray open/close procedure has completed, unplug it again and then

perform the initialization procedure again.

3) Press the "OPEN/CLOSE" key of the main unit to draw the tray out.

*Place the test disk (VT-501) on the tray and then press the "OPEN/CLOSE" key.

(Note: Pushing the tray to close it is not possible.)

4) Press the "PLAY" key of the main unit.

5) The "JIT 0000" is displayed on the FL indicator.

Set the FL indicator figure value to its minimum by adjusting the pickup guide shaft flap.

* The test mode is cancelled when the power is turned off.

Measurement

Measurement machine

No need

General tool : Hex-head wrench (1.27 mm)

Adjustment point

Refer to Fig.2

connections

Refer to Fig.1

Mode

Reproduction

part

Extension cord No.

QUQ110-3740AM

Disc

VT-501

"Flap adjustment" of the Pick-up guide shaft adjusts

"Tangential adjustment machine screw" A and

"Tilt adjustment machine screw" B from the

DVD Mechanism A'ssy bottom.

1. The part at the center on the DVD test disc is

reproduced.

2.The flap adjustment screws is turned alternately

and adjusted like clearly seeing the waveform of

CN104"1" to the way.

Note

1.The tangential adjustment is done finish and,

then, tilt is adjusted.

2.The repeat the adjustment 2-3 times,for best

result.

3.The final adjustment should be tilt adjustment.

Extension Cord

DVD Mechanism A'ssy

CN11 of

Stand

Connection PWB

CN101 of DVD Servo Control PWB

DVD player

Stand

200mm

Fig.1

1-22

Page 23

TH-A10R/TH-A10

Confirmation after adjustment.

Confirm to reproduce video CD and CD after

the DVD test disc is adjusted and to find abnormality.

B

Fig.2

A

A

(5) About keeping the disc

As for the DVD test disc, plane accuracy is demanded.Please note the keeping place on the disc.

1. Please do not put the disc directly on the work desk etc. after uses .

2. To keep the planarity of the disc, politely handle ,and please put in a special case and keep

the disc vertically after uses .

Please keep keeping the disc in a cool place where direct sunshine and the air-conditioning

wind do not drive.

3. When the disc curves,an accurate adjustment cannot be done.

Please exchange for a new test disc and adjust optics.

4. Other discs might not be able to be reproduced when adjusting on a curved disc.

Point of adjustment

* Please execute the static electricity protection measures before starting the adjustment.

* When the following parts are exchanged,optical adjustment "Adjust the flap of the disc motor"

is necessary.

1.The disc motor was exchanged.

2.The laser pick up was exchanged.

3.The traverse motor unit was exchanged.

Note

Additionally, please adjust the flap of the disc motor when the picture quality

deterioration is seen .The basic adjustment though, is unnecessary for part exchange

in the traverse.

An optical adjustment in the laser pick up cannot be done.

Please adjust the flap of the disc motor after exchanging the laser pick up.

* When the traverse unit is exchanged, the adjustment is basically unnecessary.

1-23

Page 24

TH-A10R/TH-A10

Precautions for Service

Handling of Traverse Unit and Laser Pickup

1. Do not touch any peripheral element of the pickup or the actuator.

2. The traverse unit and the pickup are precision devices and therefore must not be subjected to

strong shock.

3. Do not use a tester to examine the laser diode. (The diode can easily be destroyed by the

internal power supply of the tester.)

4. To replace the traverse unit, pull out the metal short pin for protection from charging.

5. When replacing the pickup, after mounting a new pickup, remove the solder on the short land

which is provided at the center of the flexible wire to open the circuit.

6. Half-fixed resistors for laser power adjustment are adjusted in pairs at shipment to match the

characteristics of the optical block.

Do not change the setting of these half-fixed resistors for laser power adjustment.

Destruction of Traverse Unit and Laser Pickup by Static Electricity

Laser diodes are easily destroyed by static electricity charged on clothing

or the human body. Before repairing peripheral elements of the traverse

unit or pickup, be sure to take the following electrostatic protection:

1. Wear an antistatic wrist wrap.

2. With a conductive sheet or a steel plate on the workbench on which

the traverse unit or the pick up is to be repaired, ground the sheet

or the plate.

3. After removing the flexible wire from the connector (CN101),

short-circuit the flexible wire by the metal clip.

4. Short-circuit the laser diode by soldering the land which is provided

at the center of the flexible wire for the pickup.

After completing the repair, remove the solder

to open the circuit.

Short-circuit

1-24

Page 25

Discription of major IC's

AL4527 (IC601): A/D, D/A Converters

1. Terminal layout

CDTO

CDTI

CCLKCSPIS

TH-A10R/TH-A10

XTO

XTI

AVSS

AVDD

VREFH

VCOM

2. Block diagram

LIN+

LIN-

SDOS

OCKS

MIS

BCLK

LRCK

SDTI1

SDTI2

SDTI3

SDTO

DAUX

DFS

4443424140393837363534

1

2

3

4

5

6

7

8

9

10

11

1213141516171819202122

DEM1

DEM0

MCKO

DVDD

ADC

DVSSPDXTS

HPF

ICKS1

ICKS0

CAD1

Audio

I/F

33

32

31

30

29

28

27

26

25

24

23

CAD0

VREFL

RIN+

RINLIN+

LINROUT1

LOUT1

ROUT2

LOUT2

ROUT3

LOUT3

RIN+

RIN-

LOUT1

ROUT1

LOUT2

ROUT2

LOUT3

ROUT3

LPF

LPF

LPF

LPF

LPF

LPF

ADC

DAC

DAC

DAC

DAC

DAC

DAC

HPF

DATT

DATT

DATT

DATT

DATT

DATT

LRCK

BICK

MCLK

SDOUT

SDIN1

SDIN2

SDIN3

DAUX

Format

Converter

SDOS

SDTO

SDTI1

SDTI2

SDTI3

1-25

Page 26

TH-A10R/TH-A10

3. Pin function

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

SDOS

OCKS

MIS

BCLK

LRCK

SDTI1

SDTI2

SDTI3

SDTO

DAUX

DFS

DEM1

DEM0

MCKO

DVDD

DVSS

PD

XTS

ICKS1

ICKS0

CAD1

CAD0

LOUT3

ROUT3

LOUT2

ROUT2

LOUT1

ROUT1

LINLIN+

RINRIN+

VREF

VCOM

VREFH

AVDD

AVSS

XTI

XTO

PIS

CS

CCLK

CDTI

CDTO

Symbol

I/O

SDTO source select terminal L: Internal ADC output H: DAUX input

I

Serial control mode select terminal L: 3-wire serial H: IC bus

I

Soft mute terminal H: Starting Soft mute L: Cancel

I

Audio serial data clock terminal

I

Input channel clock terminal

I/O

DAC1 audio serial data input terminal

I

DAC2 audio serial data input terminal

I

DAC3 audio serial data input terminal

I

Audio serial data output terminal

O

Auxiliary audio serial data input terminal

I

2x sampling mode terminal L: Ordinal speed H: 2x speed

I

De-emphasize 1 terminal

I

De-emphasize 2 terminal

I

Power terminal for output buffer 2.7 5.5 V

Digital power supply terminal 4.5 5.5 V

Digital ground terminal 0 V

Power down & reset terminal L: Power is down and register is initialized.

I

Input clock selection 2 terminals

I

Input clock selection 1 terminals

I

Input clock selection 0 terminals

I

Chip address 1 terminal

I

Chip address 0 terminal

I

DAC3 L channel analog output terminal

O

DAC3 R channel analog output terminal

O

DAC2 L channel analog output terminal

O

DAC2 R channel analog output terminal

O

DAC1 L channel analog output terminal

O

DAC1 R channel analog output terminal

O

L channel analog reverse input terminal

I

L channel analog non-reverse input terminal

I

R channel analog reverse input terminal

I

R channel analog non-reverse input terminal

I

Zero input detection terminal L: P/S = H

O

COMMON voltage output terminal

O

Reference voltage input terminal

Analog power supply terminal 4.5 5.5 V

Analog ground terminal 0 V

Zero input detection terminal L: P/S = H

O

Master clock input terminal

I

Parallel/serial select terminal

I

L: Serial control mode H: Parallel control mode

Audio data interface format 0 terminal (with parallel control mode)

I

Chip select terminal (with 3-wire serial control mode)

I

Audio data interface format 0 terminal (with parallel control mode)

I

Control data clock terminal (with serial control mode)

I

Loopback mode 0 terminal (with parallel control mode)

I

Control data input terminal (with serial control mode)

I/O

Loopback mode 1 terminal

I

Functions

1-26

Page 27

AK93C65AF-X (IC403) : EEPROM

1.Terminal layout

TH-A10R/TH-A10

PE

VCC

CS

SK

2.Block diagram

DI

CS

INSTRUCTION

1

2

3

4

8 PIN SOP

REGISTER

8

7

6

5

INSTRUCTION

GENERATION

NC

GND

DO

DI

DECODE,

CONTROL

AND

CLOCK

DATA

REGISTER

ADD.

BUFFERS

16

R/W AMPS

AND

AUTO ERASE

DECODER

DO

16

EEPROM

4096bit

256 x 16

SK

PE

3.Pin function

Pin no. Symbol

1 PE

2 VCC

3 CS

4 SK

5 DI

6 DO

7 GND

8 NC

Function

Program enable (With built-in pull-up resistor)

Power supply

Chip selection

Cereal clock input

Cereal data input

Cereal data output

Ground

No connection

NOTE : The pull-up resistor of the PE pin is about 2.5M (VCC=5V)

VREF

VPP SW

VPP

GENERATOR

1-27

Page 28

TH-A10R/TH-A10

AN8706FHQ (IC101) : Front end processor

1.Pin layout

CBDOSL

CSAG

DCAGC

AGCG

PEAK

BOTTOM

RFENVFCBOOST

OFTR

BDO

JITOUT

75747372717069686766656463626160595857565554535251

RBCA

RFINP

RFINN

VCC2

GND2

VREF2

RFON

RFOP

TS

DCRF

FS

VIN6

VIN5

VCC1

VIN1

VIN2

VIN3

VIN4

VREF4

DIFP

DIFN

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

AN8706FHQ

CBDOFS

TESTSG

COFTFS

COFTSL

GND3

FUPDN

ITDLI

VCOIN

PLFLT

PLFLT2

FCPO

PCPO

VCC3

CAPA

DTRD

IDGT

VCC5

50

RDCKP

49

RDCKN

48

RDTP

47

RDTN

46

GND5

45

GND4

44

VCC4

43

DTMONN

42

DTMONP

41

DSLFLT

40

DSLO

39

FLTOUT

38

DCFLT

37

VREF3

36

VPWBDO

35

VPWOFT

34

IDDLY

33

DBAL

32

GND1

31

VREF1

30

TKCNT

29

TKCFLT

28

TEOUT

27

TEI

26

RSCL

2.Block diagram

Head Amp.

SSD Signal

Head Amp.

DPD Signal

12345678910111213141516171819202122232425

TG

LPCOA

LDONB

LDONA

LPC1

VHARF

RFOUT

FS/TS

PTH

POFLT

TGBAL

TBAL

FBAL

FGCTL

FEN

VREFL

FEOUT

PULIN

VREFC

VREFH

TGTETKCNTTBALFBALFE

SEN

SCK

STDI

FC/Boost

AGC Cont

TKCNT

FE(SSD)

FE BAL

AGC EQ

MU

TE(DPD)

TE BAL

STNBY

XTRON

RFIN

MTRON

ROMRAM

RF ENV

DSL

BDO Det

OFTR Det

DFLTOP/NRFENV

PLL

JITTER Det

SYNC

JITOUT

CLK

DATA

DSLOUT

BDO

OFTR

1-28

TG(DPD)

LPC(Amp)

OPTICAL HEAD

(650nm)

INTERFACE

VREF reg

TGBAL CPU STNBY MTRON

SERVO PROCESSOR

Head Amp.

Page 29

TH-A10R/TH-A10

3.Pin function

Pin No. Symbol I/O

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

LDONB

LDONA

LPCOA

LPC1

VHARF

TGBAL

POFLT

PTH

TBAL

TG

FGCTL

FBAL

FEOUT

FEN

VREFL

VREFC

VREFH

PULIN

SEN

SCK

STDI

STNBY

XTRON

MTRON

ROMRAM

RSCL

TEI

TEOUT

TKCFLT

TKCNT

VREF1

GND1

DBAL

IDDLY

VPWOFT

VPWBDO

VREF3

DCFLT

FLTOUT

DSLO

DSLFLT

DTMONP

DTMONN

VCC4

GND4

GND5

RDTN

RDTP

RDCKN

RDCKP

Functions

I

Laser ON (CD Head) terminal

I

Laser ON (DVD Head) terminal

O

Laser drive output terminal

I

Laser PIN input terminal

O

VHALF voltage output terminal

I

Tangential phase balance control terminal

O

Track detection Threshold value level terminal

I

Track detection Threshold value level terminal

I

Tracking balance control terminal

O

Tangential phase error signal output terminal

I

Focus amplifier Gain control terminal

I

Focus balance control terminal

O

Focus error signal output terminal

I

Focus error output amplifier reversing input terminal

O

VREFL voltage output terminal

O

VREFC voltage output terminal

O

VREFH voltage output terminal

I

DSL,PLL drawing mode switch terminal

I

SEN(Cereal data input terminal)

I

SCK(Cereal data input terminal)

I

STDI(Cereal data input terminal)

I

Standby mode control terminal

I

Tracking OFF holding input terminal

I

Monitor output ON/OFF switch terminal

I

ROM . RAM switch terminal

O

Standard current source terminal

I

Tracking error output Amp reversing input terminal

O

Tracking error signal output terminal

O

Track count detection filter terminal

O

Track count output terminal

O

VREF1 voltage output terminal

O

Earth terminal 1

I

Data slice offset adjustment terminal

I

Data slice delay adjustment terminal

I

OFTR detection level setting terminal

I

BDO detection level setting terminal

O

VREF3 voltage output terminal

O

Capacity connection terminal for data slice input filter

O

Filter amplifier output terminal

O

Data slice single data output terminal

O

Constant filter terminal when data is sliceddelly

O

PLL differential motion 2 making to value edge signal moniter output (+)

O

PLL differential motion 2 making to value edge signal moniter output (-)

I

Power terminal 4 (5V)

O

Earth terminal 4

O

Earth terminal 5

O

PLL differential motion making to synchronization RF signal reversing output

O

PLL differential motion making to synchronization RF signal rotation output

O

PLL differential motion making synchronization clock reversing output

O

PLL differential motion making synchronization clock rotation output

AN8706FHQ (1/2)

1-29

Page 30

TH-A10R/TH-A10

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

VCC5

IDGT

DTRD

CAPA

VCC3

PCPO

FCPO

PLFLT2

PLFLT

VCOIN

ITDLI

FUPDN

GND3

JITOUT

BDO

OFTR

BOOST

FC

RFENV

BOTTOM

PEAK

AGCG

DCAGC

CSAG

CBDOSL

CBDOFS

RBCA

TESTSG

RFINP

RFINN

VCC2

GND2

VREF2

COFTFS

COFTFL

RFON

RFOP

TS

DCRF

FS

VIN6

VIN5

VCC1

VIN1

VIN2

VIN3

VIN4

VREF4

DIFP

DIFN

I/OPin No. Symbol Functions

Power terminal 5 (3.3V)

I

Data slice part address part gate signal input terminal (For RAM)

I

Data slice data read signal input terminal(For RAM)

I

Data slice CAPA(Address)signal input terminal (For RAM)

I

Power terminal 3 (5V)

I

PLL phase gain set terminal

O

PLL frequency gain set terminal

O

PLL low region filter terminal

O

PLL high region filter terminal

O

PLL VCO input terminal

I

PLL jitter free current ripple removal filter terminal

O

PLL frequency control input terminal

I

Earth terminal 3

O

Detection signal output of jitter

O

BDO output terminal

O

OFTR output terminal

O

Booth control terminal for filter

I

FC control terminal for filter

I

RF enve output terminal

O

Bottom enve detection filter terminal

O

Peak enve detection filter terminal

O

AGC amplifier gain control terminal

O

AGC amp filter terminal

O

Sag cancellation circuit filter terminal

O

BDO detection capacitor terminal

O

BDO detection capacitor terminal

O

BCA detection level setting terminal

O

TEST signal input terminal

I

RF signal positive moving input terminal

I

RF signal reversing input terminal

I

Power terminal 2 (5V)

I

Earth terminal 2

O

VREF2 voltage output terminal

O

OFTR detection capacitor terminal

O

OFTR detection capacitor terminal

O

RF signal output terminal P

O

RF signal output terminal N

O

All addition amplifier (DVD) output terminal

O

All addition amplifier capacitor terminal

O

All addition amplifier (CD) output terminal

O

Focus input of external division into two terminal

I

Focus input of external division into two terminal

I

Power terminal 1 (5V)

I

External division into four (DVD/CD) RF input terminal 1

I

External division into four (DVD/CD) RF input terminal 2

I

External division into four (DVD/CD) RF input terminal 3

I

External division into four (DVD/CD) RF input terminal 4

I

VREF4 voltage output terminal

O

RF signal (RAM) output terminal P

O

RF signal (RAM) output terminal N

O

AN8706FHQ(2/2)

1-30

Page 31

BA5983FM (IC271) : 4CH DRIVER

1.Block Diagram

TH-A10R/TH-A10

28

Vcc

27

1

2

25

26

10k

10k

3

20k

10k

4

24

5

23 22

10k

10k

6

20k

10k

7

2.Pin Function

Pin No. Pin No.

Symbol Symbol

1

BLAS IN

2

OPIN1(+)

3

OPIN1(-)

4

OPOUT1

5

OPIN2(+)

6

OPIN2(-)

7

OPOUT2

8

9

10

11

12

13

14

GND

STBY1

PowVcc1

VO2(-)

VO2(+)

VO1(-)

VO1(+)

I/O I/O

Input for Bias-amplifier

I

Non inverting input for CH1 OP-AMP

I

Inverting input for CH1 OP-AMP

I

Output for CH1 OP-AMP

O

Non inverting input for CH2 OP-AMP

I

Inverting input for CH2 OP-AMP

I

Output for CH2 OP-AMP

O

Substrate ground

-

Input for CH1/2/3 stand by control

I

Vcc for CH1/2 power block

-

Inverted output of CH2

O

Non inverted outpur of CH2

O

Inverted output of CH1

O

Non inverted outpur of CH1

O

Function

15

16

17

18

19

20

21

22

23

24

25

26

27

28

21

20

Vcc

STAND BY

CH4

STAND BY

CH1/2/3

89

VO4(+)

VO4(-)

VO3(+)

VO3(-)

PowVcc2

STBY2

GND

OPOUT3

OPIN3(-)

OPIN3(+)

OPOUT4

OPIN4(-)

OPIN4(+)

PreVcc

17 16

18

19

10k

10k

10k

10k

Level Shift

Level Shift

10k

10k

10k

10k

12

13

Vcc

10

10k

10k

Level Shift

Level Shift

10k

10k

11

Function

O

Non inverted output of CH4

O

Inverted output of CH4

O

Non inverted output of CH3

O

Inverted output of CH3

-

Vcc for CH3/4 power block

I

Input for Ch4 stand by control

-

Substrate ground

O

Output for CH3 OP-AMP

I

Inverting input for CH3 OP-AMP

I

Non inverting input for CH3 OP-AMP

O

Output for CH4 OP-AMP

I

Inverting input for CH4 OP-AMP

I

Non inverting input for CH4 OP-AMP

-

Vcc for pre block

15

10k

10k

10k

10k

14

1-31

Page 32

TH-A10R/TH-A10

JCE8011(IC551):GRAPHIC CONTROLLER

Pin No. Symbol

1~8

9

10

11

12

13

14

15

16~23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39~46

47

48

49

50

51

52

53

54~61

62

63~70

71

72

73~82

83

84~93

94

95

96

97

98

99

100

VD0~7

VCLKI

HSYNCI

VSYNCI

VCC

VCLKD

HSYNCO

VSYNCO

DOUT0~7

TEST

RESETB

GND

NTB

DTSF0

DTSFI

VIDEG

DOSF0

DOSF1

XVRST

F1

HBL

VBL

VOEDG

VCC

FRD7~0

GND

FRCK

FWCK

FREB

FWEB

FRRSTB

FWRSTB

FWD7~0

VCC

CHD7~0

GND

CHOEB

CHA19~10

VCC

CHA9~0

GND

ACK

CS1B

CS2B

SCK

RXD

TXD

I/O

I

I

I

I

O

O

O

O

-

I

-

I

I

I

I

I

I

O

O

O

O

I

-

I

O

O

O

O

O

O

O

-

I

O

O

O

O

I

I

I

I

O

Function

DVD Image signal input (Multi plex data Y,Cr,Cb)

Dot clock signal input (27MHz)

The horizontal synchronous signal input

Vertical synchronous signal input

Power supply

Dot clock signal output (27MHz)

'H' blanking output

'V' blanking output

Digital data output

Test terminal (Uses as GND usually)

System reset signal

Connect to GND

Mode switching NTSC(low) / PAL(high)

Taking timing shift of VD input

Taking timing shift of VD input

Taking edge specification of VD input (0:up , 1:down)

Timing shift input of output data

Timing shift input of output data

Non connect

Field Identification signal output

'H' blanking output

'V' blanking output

Output timing setting of DOUT (0:up , 1:down)

Power supply

Field memory read data input

Connect to GND

Field memory read clock

Field memory write clock

Field memory read enable

Field memory write enable

Field memory read address reset

Field memory write address reset

Field memory write data output

Power supply

Character ROM data

Connect to GND

Character ROM output enable

Character ROM address output

Power supply

Character ROM address output

Connect to GND

Serial data chip select for graphic control

Serial data chip select for encoder control

Serial clock input

Serial input data

Serial output data

1-32

Page 33

MC44724AVFU(IC554):VIDEO ENCODER

TH-A10R/TH-A10

1.Terminal Layout 2.Block Diagrams

64 ~ 49

1

~

16

17 ~ 32

48

~

33

ChipA

DVdd

DVdd

DVss

DVss

DVIN[7:0]

TP[8:1]

TVIN

TP[0]IN

Clock

Reset

PAL/NTSC

3.Pin function

No. Symbol

1

CVBS/Cb/B1

2

CVBS/Cb/B1

3

CVBS/Cb/B1Vdd

4

Y/G1

5

Y/G1

6

Y/G1/Vdd

7

C/Cr/R1

8

C/Cr/R1

9

C/Cr/R1Vdd

10

DAVss

11

TBIAS1

12

Vref1

13

DAVdd

14

Vref2

15

TBIAS2

16

NC

17

CVBS/Cb/B2

18

CVBS/Cb/B2

19

CVBS/Cb/B2Vdd

20

Y/G2

21

Y/G2

22

Y/GVdd

23

C/Cr/R2

24

C/Cr/R2

25

C/Cr/R2Vdd

26

ChipA

27

TEST

28

DVdd

29

CLOCK

30

DVss

31

Reset

32

PAL/NTSC

I/O

Analog composite drive signal (+)

O

Analog composite drive signal (-)

O

Power supply for CVBS/Cb/B DAC1

-

Analog brightness signal/G drive signal (+)

O

Analog brightness signal/G drive signal (-)

O

Power supply for Y/G DAC

-

Analog chroma signal (+)

O

Analog chroma signal (-)

O

Power supply for C/Cr/RDAC

-

Connect to ground for DAC

-

Standard BIAS for DAC1

O

Standard voltage for DAC1

-

Power supply for DAC

-

Standard voltage for DAC2

-

Standard BIAS for DAC2

O

Non connect

-

Analog composite drive signal (+)

O

Analog composite drive signal (-)

O

Power supply for CVBS/Cb/B DAC2

-

Analog brightness signal/G drive signal (+)

O

Analog brightness signal/G drive signal (-)

O

Power supply for Y/G DAC

-

Analog chroma signal (+)

O

Analog chroma signal (-)

O

Power supply for C/Cr/RDAC2

-

Chip address selection

-

Connect to test pin

I

Digital ground

-

Clock signal input (27MHz)

I

Power supply for digital circuit

-

Reset signal input L:ON

I

Selection NTSC/PAL NTSC:L PAL:H

I

Function

H.V

DEMAX

Y

cb

cr

12C / SPI

SO

SDA/SI

EXT

Sync_ generator

CGMS,

wss gen

0

off_set

0

0

sub carrier

SEL

SCL/SCK

Hsync

F/Vsync

CCwss gen

+

Modulator

gen

RGB

matrix

TEST

No. Symbol

SO

33

SDA/SI

34

SCL/SCK

35

SEL

36

DVdd

37

DVss

38

DVIN7

39

DVIN6

40

DVIN5

41

DVIN4

42

DVIN3

43

DVIN2

44

DVIN1

45

DVIN0

46

TVIN

47

EXT

48

F/Vsyac

49

Chsyac

50

DATST

51

TP-8

52

TP7

53

TP6

54

TP5

55

DVss

56

DVdd

57

TP4

58

TP3

59

TP2

60

TP1

61

TP0

62

DLVdd

63

DLVss

64

+

TEST

Y/G2Vdd

C/Cr/R2Vdd

CVBS/Cb/B2Vdd

DLVdd

DAC BIAS DAC DAC DAC

DAC

DAC

BIAS

DLVss

Y/G1Vdd

CVBS/Cb/B1Vdd

C/Cr/R1Vdd

Y/G1

Y/G1

CVBS/Cb/B1

CVBS/Cb/B1

C/Cr/R1

C/Cr/R1

Vref1

iBIAS1

Y/G2

Y/G2

CVBS/Cb/B2

CVBS/Cb/B2

C/Cr/R2

C/Cr/R2

Vref2

Ibias

DAVdd

DAVss

Function

Copy,

protection

bus

0

0

0

0

0

0

Output Selector

I/O

Non connect

-

SPI Mode : Serial data input

I

Serial clock input

I

Power supply for serial data,chip select,digital

I

Power supply for digital circuit

--

Digital ground

--

Y data input / test data I/O

I/O

Y data input / test data I/O

I/O

Y data input / test data I/O

I/O

Y data input / test data I/O

I/O

Y data input / test data I/O

I/O

Y data input / test data I/O

I/O

Y data input / test data I/O

I/O

Y data input / test data I/O

I/O

VIDEO mote on Reset(0:nomal, 1:mute)

I

Frame output / VBI information input

I/O

Frame / Vertical, synchronous I/O

I/O

The horizontal, synchronous I/O

I/O

Data input

I

Multiplex data input

I/O

Multiplex data input

I/O

Multiplex data input

I/O

Multiplex data input

I/O

Ground for digital circuit

-

Power supply for digital circuit

-

Data input / Test data I/O

I/O

Data input / Test data I/O

I/O

Data input / Test data I/O

I/O

Data input / Test data I/O

I/O

Data input / Test data I/O

I/O

Power supply for D/A converter

-

Ground for D/A converter

-

1-33

Page 34

TH-A10R/TH-A10

MN101C12G (IC701): System micom

1.Terminal layout

100 ~ 76

25

2.Pin function

Pin No. Symbol I/O Function

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

1

~

GND

CS0

CS1

CS2

NTSEL

POWER SW

SHUT1

KEY1-5

KEY6-10

VREF

VDD

OSC2

OSC1

VSS

-

MMOD

OSDCS3

RSTE

OSDDO

S2UDT

U2SDT

SCLK

BUSY

CPURST

REQ

REMO

CS3

TEST

TEST

TEST

NC

RESET

NC

NC

VDD

OSDCK

NT

26 ~ 50

75

~

51

GND

A set bit0 (It is effective in the U.E version)

I

A set bit1 (It is effective in the U.E version)

I

A set bit2 (It is effective in the U.E version)

I

NTSC/PAL switch SW input

I

Power key input

I

JOG shuttle inout (AD)

I

10 Key input (1~5)

I

10 Key input (6~10, +10)

I

+B (Apply 5V)

+B (Apply 5V)

-

O

O

O

O

O

O

O

O

O

O

O

O

O

10MHz OSC

10MHz OSC

I

GND

Unused, Connects with GND

I

Unused

Connects with GND

I

VENCODER chip selection

V.ENCOSER reset

V.ENCODER communication DATA

Communication between unit microcomputers DATA OUT

Communication between unit microcomputers DATA IN

I

Communication between unit microcomputers CLK

Communication between unit microcomputers BUSY

Unit microcomputer reset

Communication between unit microcomputers REQ

I

Remote control interruption

I

Set password change judgment bit(H:Change, L:Usual)

I

I

H:Checkers mode, L:Normal mode

I

H:Running mode, L:Normal mode

I

Un used

I

Reset input

I

Un uesd

Un used

Un used

V.ENCODER communication CK

1-34

Page 35

Pin No. Symbol I/O Function

TH-A10R/TH-A10

MN101C12G (2/2)

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66~76

77

78

79

80

81~85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

FS2

CHREQ

CHST

CHDATAIO

NC

CHCK

FLDATAO

FLDATAI

FLCK

FLCS

FLRST

EEDO

EEDI

EECK

EECS

VS1

VS3

DMUT1

DMUT2

PDB2

PDB2

DEMP2

DEMP1

DENA

KARAOKE

POWERON

VS2

NC

AVCI

AVCO

NC

STANBYIND

NC

CS4

MA

MB

M1M3

MD

MC

GAIN2

GAIN1

HPMUT

DAVSS

LMUTE

CMUTE

SMUTE

MUTE

DAVDD

O

I

O

O

48kHz, 96kHz switch

Changer communication REQUEST

Changer communication STROBE

Changer communication DATAI/O

O

O

I

O

O

O

O

I

O

O

O

O

-

-

-

-

-

-

O

O

O

O

I

O

O

O

O

O

O

O

O

O

O

-

-

O

O

O

O

O

-

Changer communication CLOCK

FL driver communication DATAO

FL driver communication DATAI

FL driver communication CLOCK

FL driver communication CS

FL reset output

EEPROM communication DATAO

EEPROM communication DATAI

EEPROM communication CLOCK

EEPROM communication CS

S1 control

S3 control(STBY:H, P.ON:L)

Un used

Un used

Un used

Un used

Un used

Un used

Un used

KARAOKE gain control(At KARAOKE : H)

Power ON output

S2 control

Un used

AV COMPULINK input

AV COMPULINK output

Un used

Standby LED output

Un used

Un used

DAC control MA

DAC control MB

DAC control M1M3

DAC control MD

DAC control MC

Un used

Un used

Un used

Un used

Un used

Un used

Un used

Front mute output

Apply 5V

1-35

Page 36

TH-A10R/TH-A10

MN101C15FDD (IC401) : System controler

1. Terminal layout

80~61

1

60

20

21~40

2. Pin function

Pin

No

Symbol SymbolFunction Function

1

2

3

DVD-S/C

VCR-S/C

4

5

6

7

8

PROTECTOR IN

9

10

11

12

13

14

VREF+

VDD

OSC 2

OSC 1

VSS

15

16

17

MMOD

18

19

20

DSP-COMMAND

21

DSP-STATUS

22

23

DSP-CLK

24

25

26

27

RESET-IN

TUNER-CE

TUNER-CLK

28

TUNER-DATA

29

30

31

32

33

34

35

RDS SCL

TUNER-IN

STEREO-IN

RDS-ST

M-BUSY

RDSCLOCKIN

36

37

38

39

40

VIDEO1

VIDEO2

X1

X0

41

Ground connection

DVD S/C selection terminal

VCR S/C selection terminal

Ground connection

Ground connection

Ground connection

Ground connection

Ground connection

Protector input

Ground connection

Power supply terminal

Quartz oscillation terminal (8 MHz)

Quartz oscillation terminal (8 MHz)

Ground connection

Ground connection

Terminal (unused)

Ground connection

Terminal (unused)

Ground connection

Ground connection

DSP control signal terminal

DSP control signal terminal

DSP control signal terminal

Ground connection

Reset signal input terminal

Tuner chip enable

Tuner clock signal input

Ground connection

Tuner control terminal

Clock signal (RDS)

Tuner signal input terminal

Stereo signal input terminal

Terminal (unused)

Busy signal from IC400 input

Ground connection

Terminal (unused)

Terminal (unused)

Terminal (unused)

VIDEO 1 signal

VIDEO 2 signal

Pin

No

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

S-MUTE

T-MUTE

RDS-DATA

INHIBIT IN

DSP-READY

DSP-RESET

M/CS

M-RESET

M-STATUS

M-COMMAND

M-CLK

S W- D ATA

SW-CLK

VOL-STB

VOL-DATA

VOL-CLK

SW-STB

SWF MUTE

SURR

FR-RELAY

CNTR-RELAY

SUR-RELAY

LED

D.AUT LED

SURR LED

System mute

Terminal (unused)

Tuner mute

Terminal (unused)

Terminal (unused)

Terminal (unused)

RDS control signal terminal

Terminal (unused)

Inhibit signal input

DSP control signal

DSP reset signal

Control signal from IC400

Reset signal from IC400

Status signal from IC400

Command signal from IC400

Clock signal from IC400

Terminal (unused)

Terminal (unused)

Terminal (unused)

Terminal (unused)

Data signal for source selector

Clock signal for source selector

Strop signal for controlling volume

Data signal for controlling volume

Clock signal for controlling volume

Strop signal for source selector

Terminal (unused)

Sub woofer mute

Terminal (unused)

Front speaker relay control

Center speaker relay control

Rear speaker relay control

Terminal (unused)

Ground connection

Ground connection

Ground connection

Ground connection

Terminal (unused)

Indicate control (DIGITAL AUTO)

Indicate control (SURROUND)

1-36

Page 37

MN102L25GCY(IC401):UNIT CPU

TH-A10R/TH-A10

Pin No. Pin No.

Symbol Symbol

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

WAIT

RE

MUTE

WEM

CS0

CS1

CS2

CS3

FGCONT

/SPKICK

LSIRST

WORD

A0

A1

A2

A3

VDD

SYSCLK

VSS

XI

XO

VDD

OSCI

OSCO

MODE

A4

A5

A6

A7

A8

A9

A10

A11

VDD

A12

A13

A14

A15

A16

A17

A18

A19

VSS

A20

TXSEL

TMPSN

-

ADPD

-

TRVSW

I/O I/O

Micon wait signal input

I

Read enable

O

Driver mute

O

Write enable

O

Non connect

O

Chip select for ODC

O

Chip select for ZIVA

O

Chip select for outer ROM

O

Photo control

O

Spin kick

O

LSI reset

O

Bus selection input

O

Address bus 0 for CPU

O

Address bus 1 for CPU

O

Address bus 2 for CPU

O

Address bus 3 for CPU

O

Power supply

System clock signal output

O

Power supply

Non connect

Non connect

Power supply

Clock signal input(13.5MHz)

I

Non connect

CPU Mode selection input

I

Address bus 4 for CPU

O

Address bus 5 for CPU

O

Address bus 6 for CPU

O

Address bus 7 for CPU

O

Address bus 8 for CPU

O

Address bus 9 for CPU

O

Address bus 10 for CPU

O

Address bus 11 for CPU

O

Power supply

Address bus 12 for CPU

O

Address bus 13 for CPU

O

Address bus 14 for CPU

O

Address bus 15 for CPU

O

Address bus 16 for CPU

O

Address bus 17 for CPU

O

Address bus 18 for CPU

O

Address bus 19 for CPU

O

Power supply

Address bus 20 for CPU

O

TX Select

O

Non connect

O

Non connect

AD Power down

O

Non connect

Detection switch of traverse

I

inside

Function

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

FGIN

-

ADSCEN

VDD

FEPEN

SLEEP

BUSY

REQ

CIRCEN

HSSEEK

VSS

EPCS

EPSK

DPDI

EPDO

VDD

SCLK0

S2UDT

U2SDT

CPSCK

SDIN

SDOUT

-

-

NMI

ADSCIRQ

ODCIRQ

DECIRQ

WAKEUP

ODCIRQ2

ADSEP

RST

VDD

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

TEST7

TEST8

VSS

D0

D1

D2

D3

D4

D5

D6

D7

Function

Photo input

I

Non connect

Serial enable signal for ADSC

O

Non connect

Serial enable signal for FEP

O

Standby signal for FEP

O

Communication busy

I

Communication Request

O

CIRC command select

O

Seek select

O

Power supply

EEPROM chip select

O

EEPROM clock

O

EEPROM data input

I

EEPROM data output

O

Power supply

Communication clock

I

Communication input data

I

Communication output data

O

Clock for ADSC serial

O

ADSC serial data input

I

ADSC serial data output

O

Non connect

Non connect

Non connect

Interrupt input of ADSC

I

Interrupt input of ODC

I