Page 1

SCHEMATIC DIAGRAMS

COMPACT VHS CAMCORDER

GR-AXM18US, GR-SXM38US

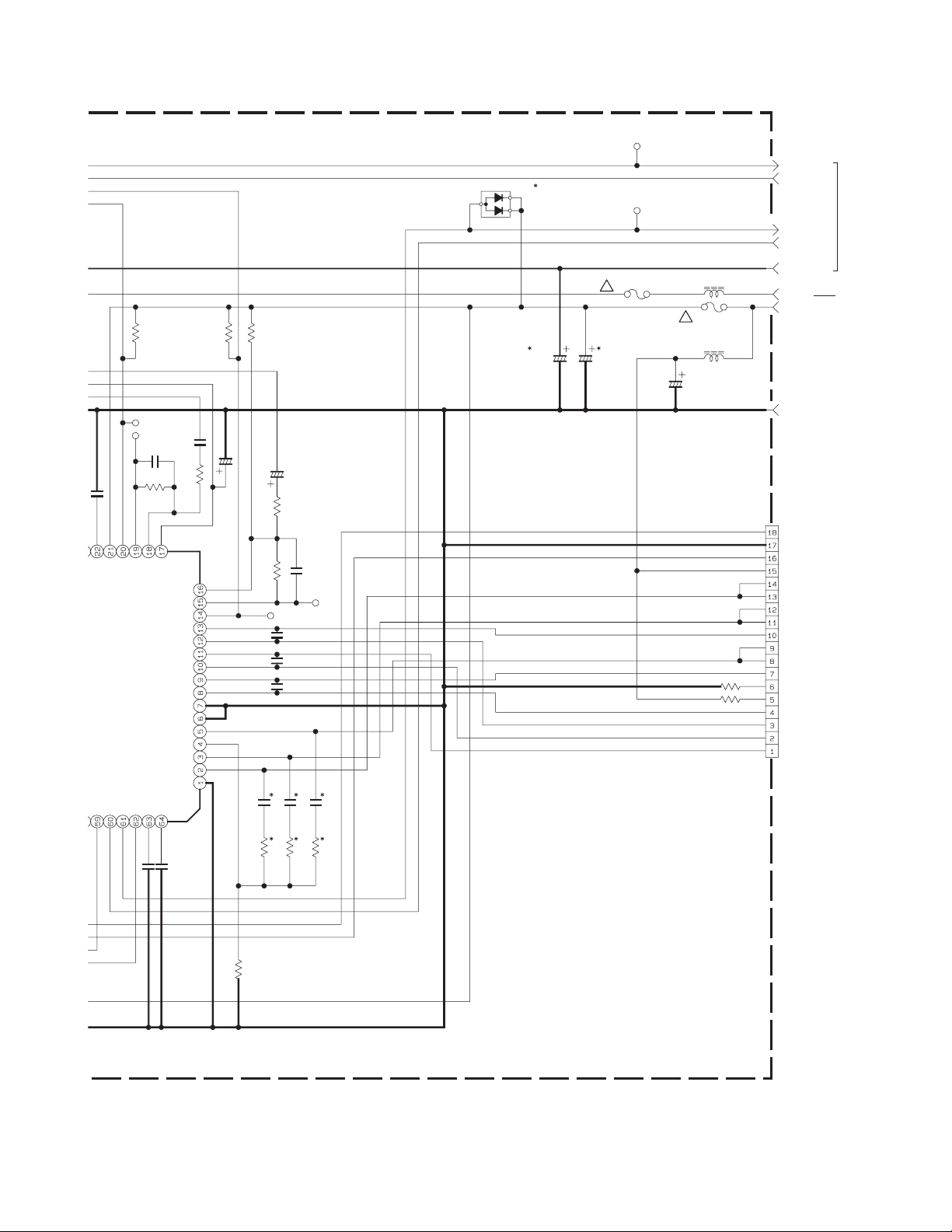

CD-ROM No.SML200602

GR-AXM18USM[M6A622],

GR-SXM38USM[M6C623]

For disassembling and assembling of MECHANISM ASSEMBLY, refer to the SERVICE MANUAL No.86700(MECHANISM ASSEMBLY).

Lead free solder used in the board (material : Sn-Ag-Cu, melting point : 219 Centigrade).

COPYRIGHT © 2006 Victor Company of Japan, Limited

No.YF126SCH

2006/2

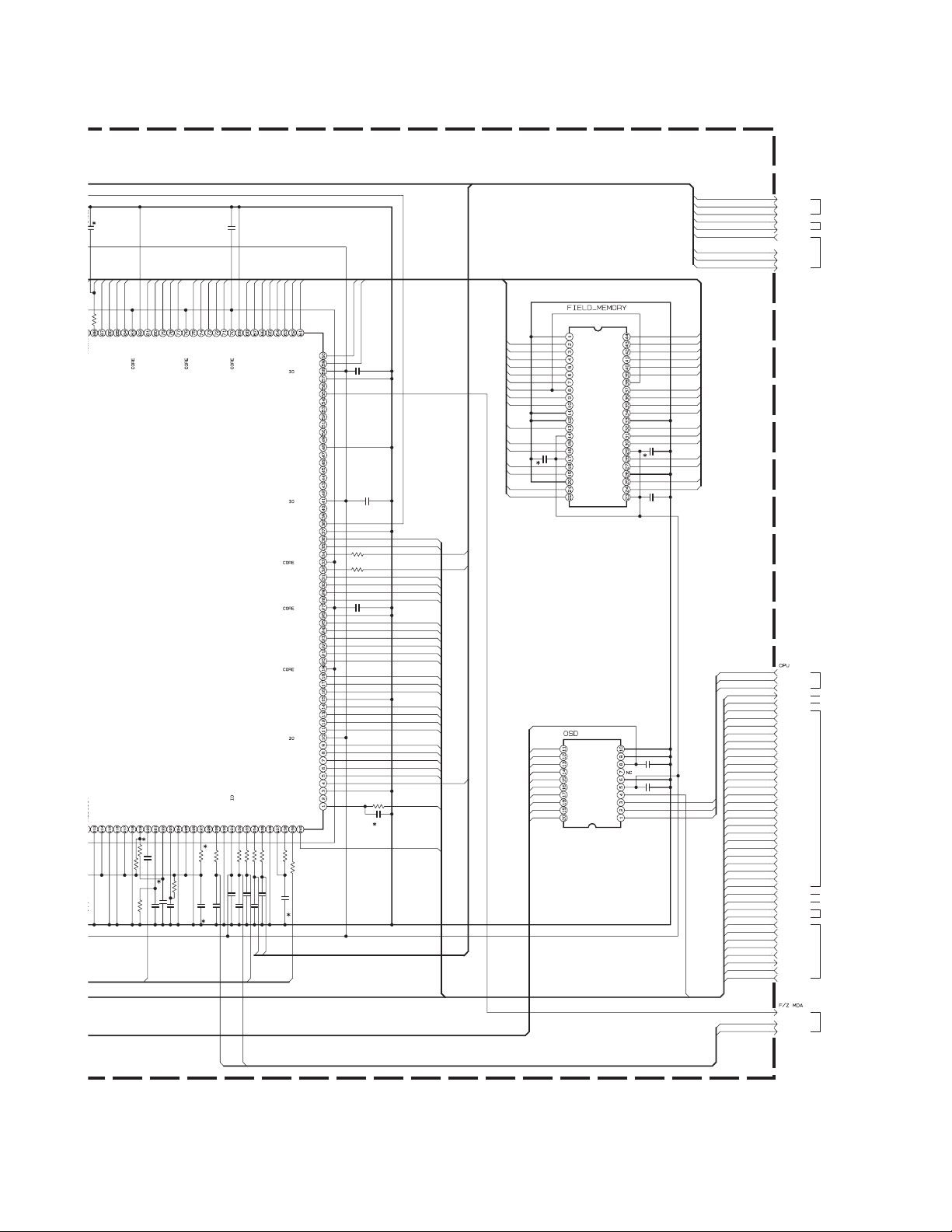

Page 2

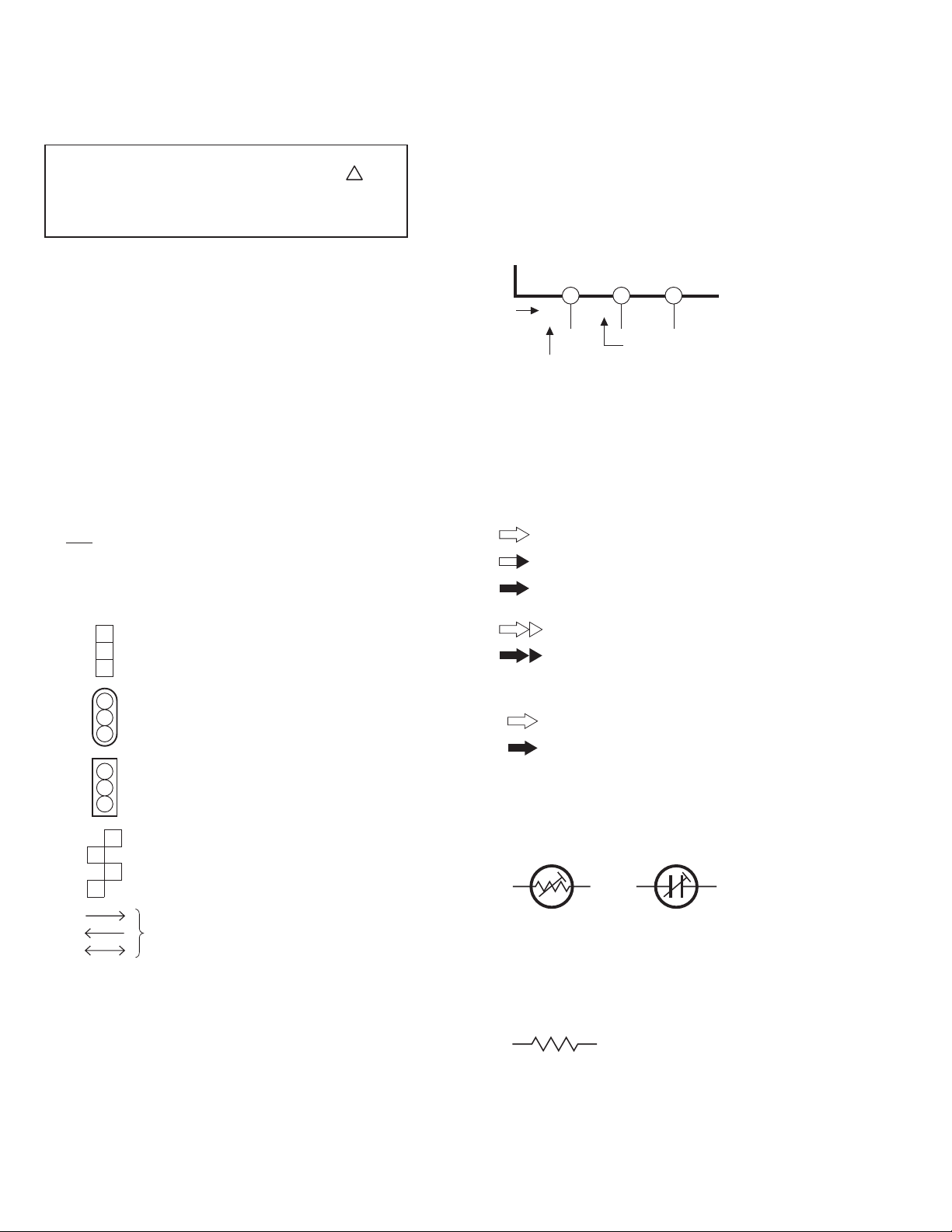

CHARTS AND DIAGRAMS

NOTES OF SCHEMATIC DIAGRAM

Safety precautions

The Components indentified by the symbol are

critical for safety. For continued safety, replace safety

critical components only with manufacturer's recommended parts.

1. Units of components on the schematic diagram

Unless otherwise specified.

1) All resistance values are in ohm. 1/6 W, 1/8 W (refer to

parts list).

Chip resistors are 1/16 W.

K: KΩ(1000Ω), M: MΩ (1000KΩ)

2) All capacitance values are in µF, (P: PF).

3) All inductance values are in µH, (m: mH).

4) All diodes are 1SS133, MA165 or 1N4148M (refer to parts

list).

Note: The Parts Number, value and rated voltage etc. in

the Schematic Diagram are for references only.

When replacing the parts, refer to the Parts List.

2. Indications of control voltage

AUX : Active at high.

AUX or AUX(L) : Active at low.

!

4. Voltage measurement

1) Regulator (DC/DC CONV) circuits

REC : Colour bar signal.

PB : Alignment tape (Colour bar).

— : Unmeasurable or unnecessary to measure.

2) Indication on schematic diagram

Voltage indications for REC and PB mode on the schematic diagram are as shown below.

REC mode

12 3

2.5

(5.0)

PB mode

1.8

PB and REC modes

(Voltage of PB and REC modes

are the same)

Note: If the voltages are not indicated on the schematic

diagram, refer to the voltage charts.

5. Signal path Symbols

The arrows indicate the signal path as follows.

NOTE : The arrow is DVC unique object.

Playback signal path

Playback and recording signal path

3. Interpreting Connector indications

1

2

Removable connector

3

1

2

Wire soldered directly on board

3

1

Non-removable Board connector

2

3

1

2

4

Board to Board

3

Connected pattern on board

The arrows indicate signal path

Note: For the destination of each signal and further line

connections that are cut off from the diagram,

refer to "BOARD INTERCONNECTIONS"

Recording signal path

(including E-E signal path)

Capstan servo path

Drum servo path

(Example)

R-Y

Playback R-Y signal path

Y

Recording Y signal path

6. Indication of the parts for adjustments

The parts for the adjustments are surrounded with the circle

as shown below.

7. Indication of the parts not mounted on the circuit board

“OPEN” is indicated by the parts not mounted on the circuit

board.

R216

2-1(No.YF126)

OPEN

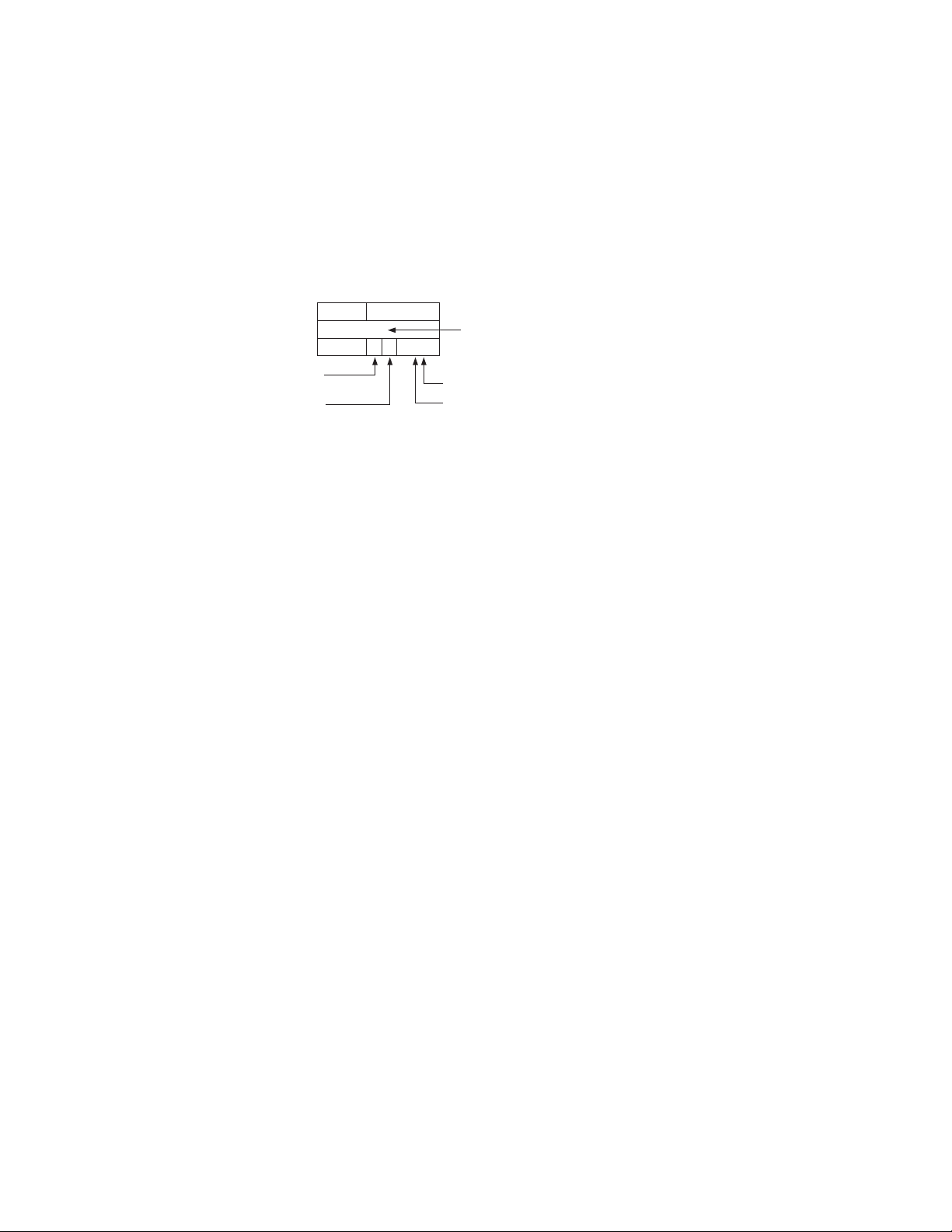

Page 3

CIRCUIT BOARD NOTES

1. Foil and Component sides

1) Foil side (B side) :

Parts on the foil side seen from foil face (pattern face)

are indicated.

2) Component side (A side) :

Parts on the component side seen from component face

(parts face) indicated.

rts location are indicated by guide scale on the circuit board.

2. Parts location guides

Parts location are indicated by guide scale on the circuit board.

LOCATION

IC

Category : IC

Horizontal “A” zone

Vertical “6” zone

(A : Component side)

D : Discrete component)

B : Foil side

C : Chip component

REF No.

IC101 B C 6 A

Note: For general information in service manual, please

refer to the Service Manual of GENERAL INFORMATION Edition 4 No. 82054D (January 1994).

(No.YF126)2-2

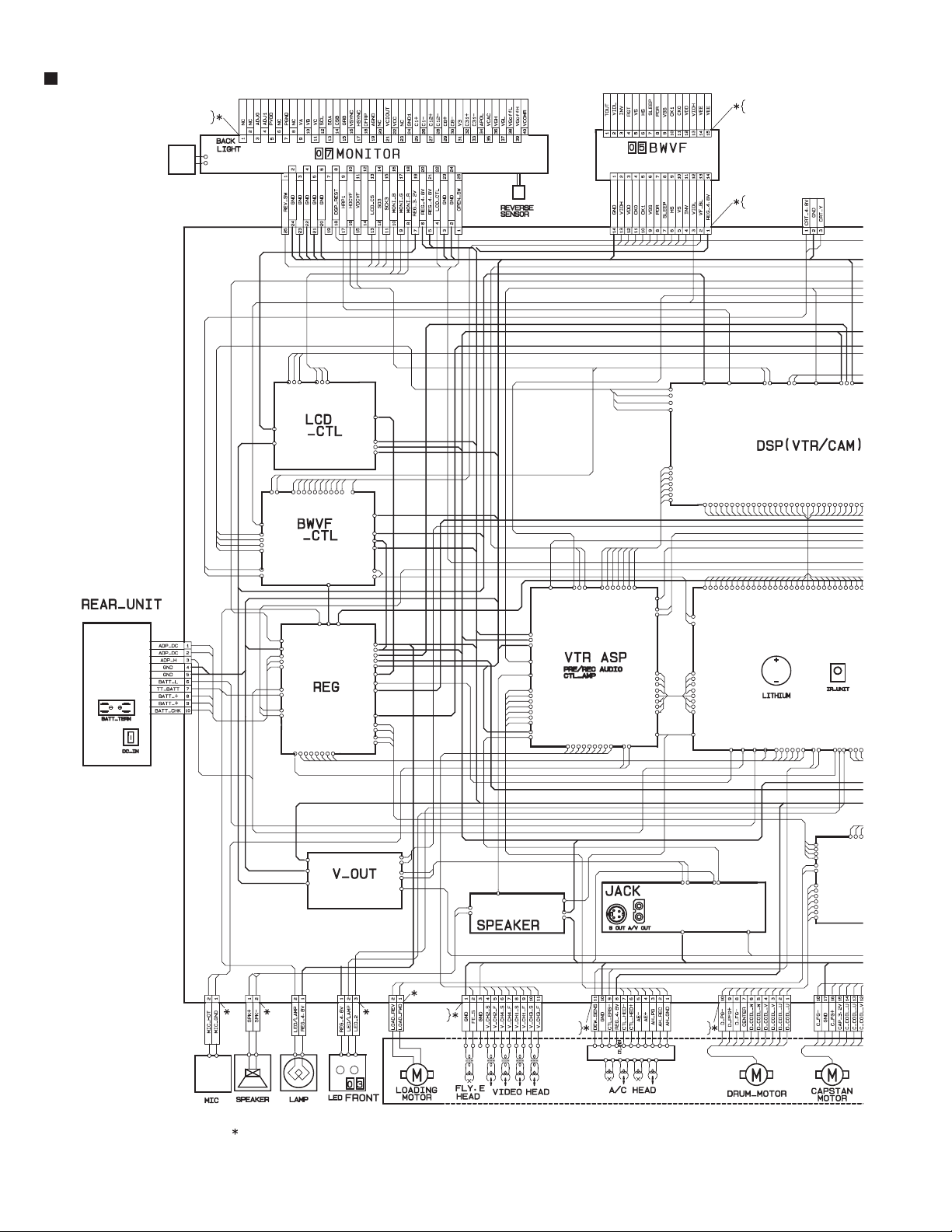

Page 4

CFM

C FRB

CFM

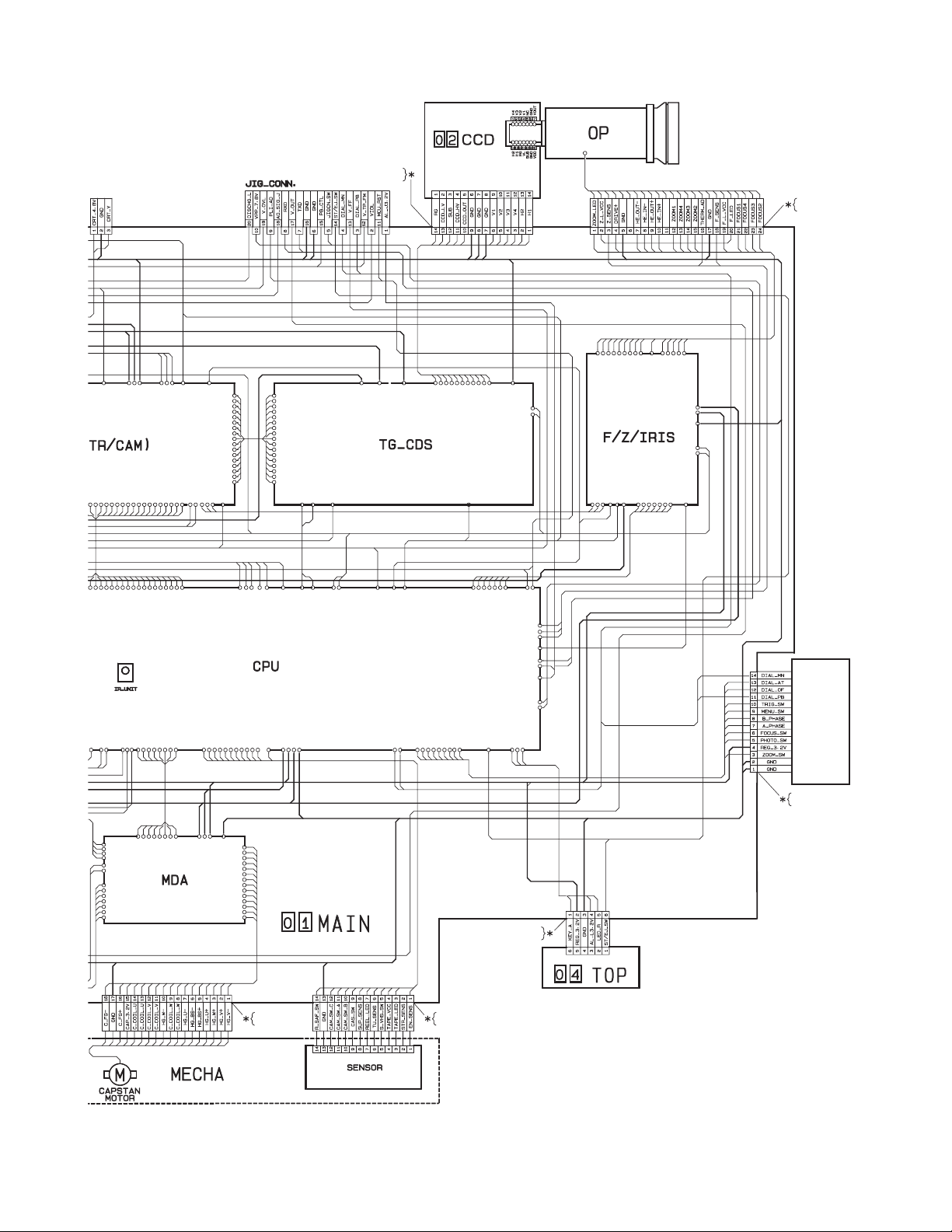

BOARD INTERCONNECTION

YTU94105-40

YTU94077-40

BL_GND

HV

CN7601

(Page2-29)

LCD MODULE

CN16

CN7602

BWVF MODULE

CN7402

(Page2-28)

CN7401

CN7301

YTU94074-15

YTU94077-15

YTU94074-14

YTU94077-14

(OPEN)

CN12

CN28

REG_3.2V

DAC_3.2V

VDCVF

HDCVF

VIDL

VF_EXCLK

BWYOUT

BWGAMMA

BWYGAIN

CRT_Y

CRT_4.8V

BOUT

ROUT

GOUT

(Page2-23)

CK0

CK1

VSS

VDD

VIDH

(Page2-21)

DISCHG_L

GND

BATT_CHK

BATT_+

ADP_DC

ADP_H

TT_BATT

(Page2-19)

MCU_RST

PLI_AD

AD_REF

T_BATT

AL_3.2V

LAMP_ON

MONI_R

MONI_G

PDR

SLEEP

LED/LAMP

REG_CS

AREG_SO

MONI_B

VS

HS

INV

REG_-5V

ZF_4.8V

REG_-5V

DRUM_PWR

DRUM_ERR

AREG_CLK

V_BATT

REG_-15V

REG_4.8V

REG_3.2V

VF_BL

DAC_3.2V

REG_3.2V

REG_4.8V

PB_VF

VF_CTL

REG_4.8V

REG_3.2V

REG_2V

UNREG

REG_-15V

C_GAIN

REG_15V

REG-8-5V

CAP_PWR

CAP_ERR

BWYGAIN

BWYOUT

BWGAMMA

VF_EXCLK

GND

GND

2FSC

V_PB_F

PB_CTL

V_TP_FM

V_CH4_S

V_CH2_F

V_CH1_S

V_CH4_F

V_REC_C

V_CH3_S

V_CH1_F

V_REC_F

V_CH3_F

S_DET+

MIC_HOT

V_PB_C

AO_SIG_J

REG_4.8V

REG_3.2V

GND

GND

V_OVL

PA_SIG

AH_GND

AH_REC

AH_PB

AE+

AECTL_HED+

CTL_HED-

AO_GND

AO_SIG

(Page2-9)

FE_S

V_CH2_S

SH_SIG

SPK_VOL

FEH_ON

V_ENV

CTL_OUT

REC_CTL

A_BIAS

A_MUTE

MIC_GND

V_FF

SCK3

A_PB

V_PB_F

V_REC_C

V_REC_F

2FSC

S_DET+

SPK_VOL

SH_SIG

SO3

DAC_3.2V

S_DET_L

S_DET_L

PB_VF

VF_CTL

FEH_ON

V_ENV

V_ASP_CSV_ASP_CS

CTL_OUT

REC_CTL

A_BIAS

A_PB

APB_EP_HAPB_EP_H

A_MUTE

SDET_CTLSDET_CTL

CLKCPU

V_DSP_CSV_DSP_CS

CLKCPU

HRP1

V_OVL_B

V_OVL_A

V_OVL_A

V_OVL_B

C_GAIN

VD_H

VD_H

V_PULSE

ASTB

ASTB

V_PULSE

ADP_H

AD0

AD1

AD0

AD1

BATT_L

HDCVF

AD2

AD2

T_BATT

SO3

SCK3

VDCVF

(Page2-11)

AD3

AD4

AD5

AD6

AD7

AD8

AD3

AD4

AD5

AD6

AD7

AD8

AL_3.2V

REG_CS

AREG_SO

AREG_CLK

V_BATT

AD9

AD10

AD9

AD10

AD_REF

V_OVL

AD11

AD12

AD13

AD11

AD12

AD13

CTL_ERS-

DEW_SENS

AD14

AD15

AD14

AD15

LAMP_ON

GND

REG_2V

REG_3.2V

R/W_L

V_PLS_ON

OMT

OMT

R/W_L

V_PLS_ON

DRUM_REF

LED/LAMP

LED_2

FI

FI

CAP_REF

C FRB

REG_4.8V

GND

DAC_3.2V

(Page2-15)

CN8

CN27

YUJ40095A-2

YUJ40095A-2

CN9

CN6

CAM_Y

CAM_C

SC_OUT

SY_OUT

V_OUT

CN4

YUJ40095A-3

(Page2-27)

NOTE: The number of patch cords () are indicated by interconnected.

2-3(No.YF126)

YUJ40095A-2

YTU94074-11

YTU94077-11

SPK+

PA_SIG

SPK-

(Page2-24)

A_MUTE

REG_3.2V

GND

CN5

YTU94074-11

YTU94077-11

SC_OUT

(Page2-25)

GND

CN7

YTU94074-10

YTU94077-10

SY_OUT

AO_SIG

AO_GND

V_OUT

CAP_PWR

CAP_ERR

DRUM_PWR

DRUM_ERR

CAP_REF

DRUM_REF

LOAD_FWD

LOAD_REV

D_PGD_PFG+

D_FGCENTER

D_COIL_W

D_COIL_V

D_COIL_U

CN1

CN3

Page 5

PEN)

e2-11)

AD9

AD10

AD11

V_OVL

AD12

YTU94074-14

(Page2-26)

YTU94077-14

GND

BOUT

ROUT

REG_2V

REG_3.2V

AD15

V_PLS_ON

R/W_L

HD_H

OMT

FI

CFM

WAIT_L

DSTB_L

AD13

AD14

GOUT

OSD_CLK

OSD_DATA

DSP_REST

AD_0

AD_1

VDVHS

AD_2

AD_3

AD_4

AD_5

AD_6

AD_7

AD_8

AD_9

TG_CLK

CDS_CLK

PBLK

ID

HDTG

VDTG VDTG

LHFO LHFO

CAM_Y

CAM_C

VDDSC

V_FF

H_GAIN

H_OFFSET

AD_0

AD_1

AD_2

AD_3

AD_4

AD_5

AD_6

AD_7

AD_8

AD_9

TG_CLK

CDS_CLK

PBLK

ID

HDTG

V_PB_L

CDS_CS

V_PB_C

REG_15V

REG-8-5V

(Page2-17)

CN25

REG_3.2V

CN5301

SUB

CCD_LV

CCD_HV

CCD_OUT

V1

DSP_REST

YTU94074-24

YTU94077-24

CN22

CN15

HE_IN-

FOCUS3

OP_VCC

LENS_CLK

LENS_CS

DRIVE+

IRIS_O/C

HALL_A/D

HE_OUT+

REG_4.8V

REG_3.2V

IR_FLICK

IRIS_PWM

LENS_LED

HE_IN+

HE_OUT-

GND

SCK3

ZOOM_LED

SO3

IR_DC

ZOOM1

ZOOM3

ZOOM4

ZOOM2

FOCUS2

FOCUS4

V4V3V2

H1RGH2

GND

SCK3

SO3

FOCUS1

(Page2-13)

ZF_4.8V

H_GAIN

H_OFFSET

VDDSC

DSP_REST

VDVHS

AD9

AD10

AD_REF

CN3

AD11

AD12

CTL_ERS-

DEW_SENS

CAP_PWR

CAP_ERR

DRUM_PWR

DRUM_ERR

LOAD_FWD

LOAD_REV

D_PGD_PFG+

D_FGCENTER

D_COIL_W

D_COIL_V

D_COIL_U

FI

CFM

OMT

AD13

AD14

AD15

HD_H

R/W_L

WAIT_L

DSTB_L

OSD_CS OSD_CS

OSD_CLK

V_PLS_ON

LED/LAMP

LAMP_ON

DRUM_REF

LED_2

DRUM_REF

CAP_REF

C_FRB

C_FRB

CAP_REF

DRUM_FG

CAP_FG

DRUM_PG

CAP_FG

DRUM_FG

DRUM_PG

OSD_DATA

L_FRB

MDA_PS

L_FRB

MDA_PS

(Page2-7)

R_SAF_SW

TAPE_VCC

UNREG

REG_3.2V

REG_4.8V

CAM_SW_C

CAM_SW_B

CAM_SW_A

C_FG-

GND

CAP_3.2V

C_FG+

C_COIL_U

C_COIL_V

HG_W-

C_COIL_W

HG_U-

HG_BS-

HG_BS+

HG_U+

HG_W+

HG_V+

HG_V-

SO3

SCK3

LCD_CS

(Page2-5)

SUP_SENS

REEL_LED

S_VHS_SW

TU_SENS

CAS_SW

REV_SW

LCD_CTL

EN_SENS

TAPE_LED

OPEN_SW

REG_4.8V

REG_3.2V

UNREG

V_PB_L

GND

CDS_CS

SCK3

SO3

V_FF

VDVHS

DIAL_MN

DIAL_PB

DSP_REST

FOCUS_SW

PHOTO_SW

ZOOM_SW

TRIG_SW

MENU_SW

A_PHASE

B_PHASE

DIAL_AT

DIAL_OF

LENS_CS

LENS_CLK

IRIS_O/C

HALL_A/D

ST/EJ_SW

IR_FLICK

IRIS_PWM

LENS_LED

THERM_AD

YTU94074-6

YTU94077-6

Z_SENS

F_SENS

IR_DC

AL_J3.2V

JIGCN_SW

VPP_7.8V

KEY_A

LED_R

PLI_AD

RXD

TXD

AL_L3.2V

MCU_RST

CN18

CN401

yf126_y10488001a_rev0.1

CN13

ZOOM

UNIT

(Page2-30)

YTU94074-14

YTU94077-14

(Page2-27)

YTU94074-18

YTU94077-18

CN2

YTU94074-14

YTU94077-14

(Page2-30)

(No.YF126)2-4

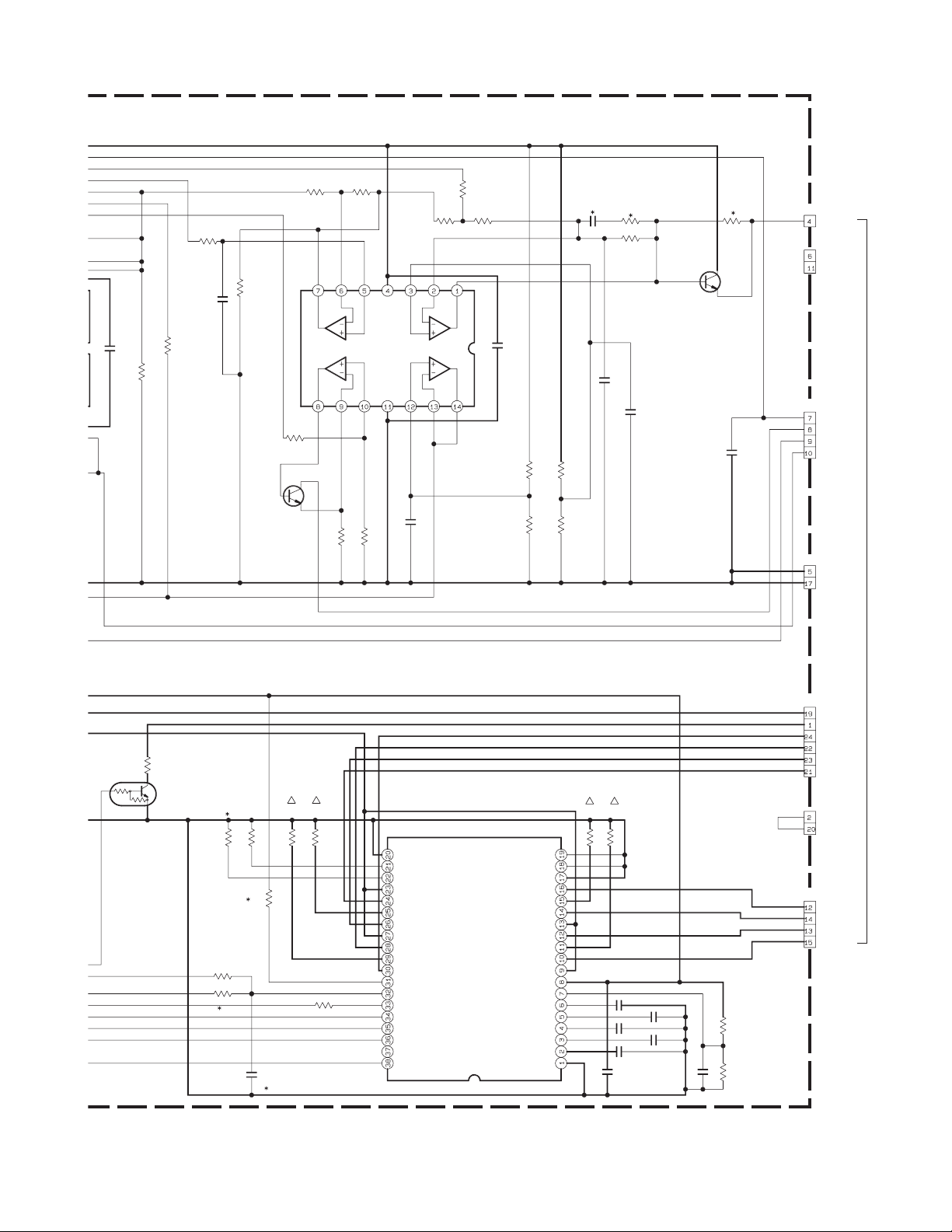

Page 6

5

5

3

P163/PWM3P56/AD14

µ

0

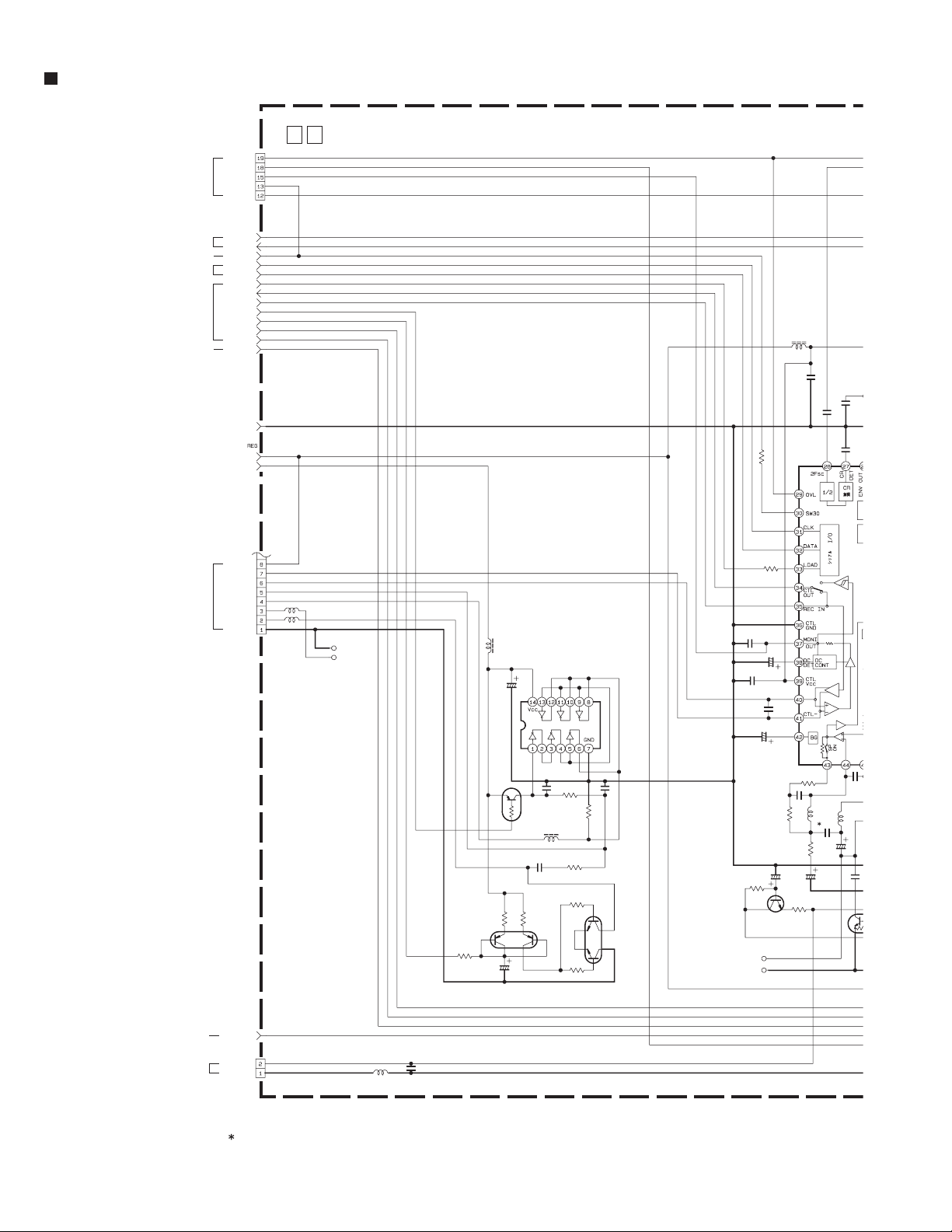

MAIN(CPU) SCHEMATIC DIAGRAM

MAIN(CPU)

CN25

CN25

CN2

CN13

CN13

CN25

CN25

CN13

CN18

CN18

CN2

CN2

CN2

CN25

CN13

REC_CTL

FEH_ON

V_OVL_A

V_OVL_B

V_PULSE

V_PLS_ON

SDET_CTL

CN2

CN13

CN13

CN18

CN25

CN2

CN2

CN2

TL105

CN13

CN7

CN15

CN15

CN2

CN18

CN15

TL106

CN13

CN13

CN2

C112

A_BIAS

L_FRB

10

R104

VOUTNCNC

IC104

BD4827FVE-W

VDDGND

C103

C104

L101

22µ

T

10µ

0.01µ

/10V

R117

1K

1SS355-X

C146

/6V

22µ

V_FF

D106

WAIT_L

ASTB

DSTB_L

CLKCPU

R/W_L

AD15

AD14

AD13

AD12

AD11

AD10

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

R119

R118

10K

10K

D103

D104

1SS355-X

C147

0.01

R120

R121

27K

27K

R196

R197

D105

C135

C136

R101

100K

R177

470K

330K

R171

R179

470K

R126

15K

18K

R167

5.6K

R168

0.4µ

C138

27K

C139

C141

R125

C143

2SA1774/RS/-X

Q101

R107 R108

R105

10K

C105

0.22

470K

470K

R153

R152

RA105

C101

15K 24K

D102

R109

R106

2.2K

Q102

DTC144EE-X

0.01µ

R170

C113

R131

47K

82K

100K

RA112

R128

18K

T

C108

2.2µ

/10V

UDZS7.5B-X

MA8075/M/-X

RD7.5M/B1/-X

RPM7138-S

IC1801

#

GND

VCC

OUT

39K

R122

#

0.01µ1M0.01µ

75K

R169

R140

C114

C116

R132

2.2K

RA101

2.2K

R133

2.2K

C118

0.1µ

2.2K

RA102

R178

R134

330

2.2K

220

R127

C102

470K

RA111

82K

330K

R129

R141

33K

R135

R130

RA103

2.2K

RA104

2.2K

33K

470K

C106

C140

0.01

R137

R138

R136

C137

C145

C144

0.01µ

R157

#

1K

10K

T

R110

V_PLS_ON

P155/RTP15

V_PLS_ON

P156/RTP16

TAPE_LED

P157/RTP17

C_GAIN

P00/NMI

ADP_SW

P01/INTP0

REC_SAFE_SW

P02/INTP1

EJECT_SW

P03/INTP2

RXD

P04/INTP3

BATT_SW

P05/INTP4/ADTRG

VD

P06/INTP5/RTPTRG0

NC

P07/INTP6

OMT

VDD

SYS_3V

VSS

GND

P130/INTCP80

REMOTE_IN

P131/INTCP81

A_PHASE

P132/INTCP82

FI

P133/INTCP83

FRP

P134/TI8

B_PHASE

P135/TCLR8

CAM_SW_A

P136/TO80

CAM_SW_B

P137/TO81

CAM_SW_C

P140/INTCP90

DRUM_FG

P141/INTCP91

VDVHS

P142/INTCP92

CAP_FG

P143/INTCP93

PB_CTL

P144/TI9

DRUM_PG

P145/RTPTRG1

MENU_SW

P146

PHOTO_SW

P147

D_PWR_ON

P70/ANI0

V_ENV

P71/ANI1

START_SENS

P72/ANI2

EN_SENS

P73/ANI3

BATT

P74/ANI4

IR_DC

P75/ANI5

DEW_SENS

P76/ANI6

FOCUS_SENS

P77/ANI7

ZOOM_SENS

P80/ANI8

HOLE

P81/ANI9

KEY_A

P82/ANI10

THERM_AD

P83/ANI11

KEY_C

P84/ANI12

PLI_AD

P85/ANI13

ZOOM_SW

P86/ANI14

T_BATT

P87/ANI15

V_BATT

AVREF

AD_REF

C115

0.1

27K

R111

C109

10

/10V

P154/RTP14

AVSS

2SC4617/QR/-X

Q103

A_BIAS

FEH_ON

R153/RTP13

P152/RTP12

FEH_ON

A_BIAS_L

CTL_ERASE

SYS_3V

SYS_3v

GND

VDD

AVDD

L_FRB

R192

P151/RTP11

LOAD_F

GND

VSS

R112

330

C110

100p

TL102

10K

R193

V_PULSE

V_OVL_A

R191

10K

P107/RTP07

P106/RTP06

SYS_3V

LOAD_R

DSTB_L

R/W_L

P94/ASTB

P93/DSTB/RD

R/W_L

DSTB_L

SDET_CTL

P105/RTP05

V_PULSE

SDET_CTL

S_VHS_SW

ASTB

P95/HLDAK

ASTB

R176

P104/RTP04

P103/RTP03

TBC_VD

FOCUS_SW

AD0

LCD_CTL

P40/AD0

P96/HLDRQ

AD0

V_OVL_B

2.2K

P102/RTP02

P101/RTP01

V_OVL_BCD

AD1

P42/AD2

P41/AD1

AD1

REC_CTL

C121 C122

0.1µ 0.1µ

0R0

VSS

VDD

GND

P150/RTP10

REC_CTL

HBEN

LBEN

P92/RW/WRH

P91/UBEN

P90/LBEN/WRL

C134

0.1µ

C123 C124

10p

V_FF

NAX0571-001

VSS

V_FF

P100/RTP00

V_OVL_A

AD3

AD2

P44/AD4

P43/AD3

AD3

AD2

2SC4617/RS/-X

R114

3.3K

X101

R144

R143

1M

X1

X2

X1

GND

AD5

AD4

P46/AD6

P45/AD5

AD5

AD4

12p

X2

AD6

10K

220

VDD

P47/AD7

AD6

R113

SYS_3V

AD7

AD7

Q105

10K

R142

1M

R173

R145

XT2

XT1

RESET

XT2

XT1

IC101

#

UPD703039-064-A

GND

SYS_3V

P50/AD8

BVSS

BVDD

C133

0.1µ

TO REG

TO REG

TO TOP

TO MDA

TO REG

TO REG

TO REG

TO MDA

TO MDA

TO MDA

TO OP

TO TOP

TO OP

TO REG

TO REG

TO REG

UNREG

AL_3.2V

MCU_RST

MCU_RST

REG_3.2V

REG_4.8V

VPP_7.8V

REG_3.2V

REG_3.2V

REEL_LED

TU_SENS

SUP_SENS

JIGCN_SW

TL104

FOCUS_SW

REC_CTL

A_BIAS

FEH_ON

L_FRB

V_OVL_A

V_OVL_B

V_PULSE

V_PLS_ON

SDET_CTL

ADP_H

R_SAF_SW

B_PHASE

A_PHASE

ST/EJ_SW

BATT_L

C_GAIN

ST/EJ_SW

DRUM_FG

CAM_SW_A

CAM_SW_B

CAM_SW_C

VDVHS

CAP_FG

CTL_OUT

DRUM_PG

MENU_SW

V_ENV

HALL_A/D

IR_DC

DEW_SENS

F_SENS

Z_SENS

EN_SENS

KEY_A

THERM_AD

PLI_AD

ZOOM_SW

PHOTO_SW

S_VHS_SW

AD_REF

WAIT_L

DSTB_L

CLKCPU

R/W_L

T_BATT

V_BATT

LCD_CTL

GND

GND

GND

GND

GND

GND

GND

V_FF

VD_H

OMT

FI

CFM

ASTB

AD15

AD14

AD13

AD12

AD11

AD10

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

TO MDA, REG

TO JIG_CONN

TO SENSOR

TO CN13

TO JIG_CONN

TO JIG_CONN

TO SENSOR

TO JIG_CONN

TO CN13

TO VTR ASP

TO VTR ASP

TO DSP(VTR/CAM)

TO SENSOR

TO CN13

TO TOP,JIG_CONN

TO DSP(VTR/CAM)

TO DSP(VTR/CAM)

TO JIG_CONN

TO DSP(VTR/CAM)

TO SENSOR

TO DSP(VTR/CAM),F/Z/IRIS

TO VTR ASP

TO CN13

TO VTR ASP

TO F/Z/IRIS

TO A/C HEAD

TO SENSOR

TO CN13

TO SENSOR

TO DSP(VTR/CAM)

TO LCD_CTL

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

2.2K

NC/VPP

VPP7.8V

RESET( L)

AD9

AD8

P51/AD9

AD9

AD8

0.033

0.47µ

C128C129

0.033µ

C120

0.01µ

C119

330

2.2K

R124

R174

P165/VSOUT

P167/HSOUT1

P166/HSOUT0

PMIRROR

LIGHT_SW

AD11

AD10

P54/AD12

P53/AD11

P52/AD10

AD11

AD10

470K

R123

C127

0.

R166

P164/CSYNCIN

REFRESH

JIGCN_SW

AD13

AD12

P55/AD13

AD13

AD12

R1

R1

R1

2-5(No.YF126)

Page 7

R113

1

7/RS/-X

XT2

BVDD

AD7

R172

Q105

100

CN2

TAPE_VCC

TO MECHA

(SENSOR)

TAPE_LED

CN2

NC

CN7

CTL_ERS-

TO A/C HEAD

GND

TL103

470K

0.01µ

2.2K

R166

P163/PWM3

P164/CSYNCIN

REFRESH

PLI_PWM

JIGCN_SW

P56/AD14

P55/AD13

AD14

AD13

AD12

AD14

AD13

AD12

470K

R158

470K

R159

100K

R139

R147

P162/PWM2

P161/PWM1

IRIS_PWM

DRUM_REF

P60/A16

P57/AD15

VF_CTL

AD15

AD15

TL101

R149

2.2K4.7K

R148

2.2K

P177/KR7

P160/PWM0

CAP_REF

RTC_INTR

P62/A18

P61/A17

PLED_SIS

PDATE_SW

R150

P176/KR6

P175/KR5

TBC_CTL

P64/A20

P63/A19

A_PB

2.2K

R151

P174/KR4

SUPSENS

TUPSENS

P65/A21

NC

A_MUTE

CLKCPU

2.2K

P173/KR3

CLKOUT

R190

P172/KR2

DIAL_MN

WAIT

CLKOUT

470K

RA109

RA108

P171/KR1

DIAL_AT

P110

WAIT_L

WAIT_L

2.2K

P170/KR0

DIAL_OF

DIAL_PB

P111

P0LUX_SW

PLED_ECT

470K

RA110

P197

P196

P195

REV_SW

OPEN_SW

LENS_MDA_CS

EEPROM_CS

LENS_MDA_CLK

P10/SI0/SDA0

P113

P112

S_DET_L

NC

RA107

2.2K

P194

CAS_SW

P193

APB_EP_H

TRIG_SW

P192

V_PB_L

P191

LCD_CS

P190

GND

SYS_3V

P187

CAP_STOP

P186

CAP_FR

P185

NC

P184

CDS_CS

P183

V_DSP_CS

P182

V_ASP_CS

P181

P180

OSD_CS

P127/TI11/TO11

REG_CS

P126/TI10/TO10

NC

P125/TI7/TO7

RTC_CS

P124/TI6/TO6

MDA_PS

P123/CLO

P122/SCK4

OSD_CLK

P121/SO4

OSD_DATA

P120/SI4

RS232C

P37/TI5/TO5

NC

P36/TI4/TO4

PB_VF

P35/TO1

LAMP_ON

P34/TO0

P33/TIO11

LED_R

P32/TIO10

LENS_LED

P31/TIO01

IRIS_O/C

P30/TIO00

HD

GND

SYS_3V

P27/TI3/TO3

IR_FLICK

P26/TI2/TO2

TO2

P25/SCK3/ASCK1

SCK3

P24/SO3/TXD1

SO3

P23/SI3/RXD1

NC

P22/SCK2/SCL1

SCK2

P21/SO2

SO2

P20/SI2/SDA1

SI2

P15/SCK1/ASCK0

DSP_RST

P14/SO1/TXD0

TXD

P13/SI1/RXD0

RXD

P12/SCK0/SCL0

AL_CLK

P11/SO0

AL_SO

AL_SI

!

J101

DRUM_REF

TO MDA

CAP_REF

IRIS_PWM

TO F/Z/IRIS

CN25

DIAL_MN

C117

R165

C130

VSS

VDD

VSS

VDD

C131

0.1µ

TL115

C132

0.1µ

R163

10K

330

R103

330

R102

R180

0R0

R154

2.2K

R175

4.7K

IC103

RS5C314-X

CE

SCLK

SIO

Vss

R116

OSCIN

OSCOUT

C125

R160

10K

0R0

R115

10K

#

#

R203

10k

#

R162

4.7K

#

Q118

2SC4617/QRS/-X

R202

1.5k

#

R199

560

R200

#

27

#

R161

4.7K

R146

!

1K

R156

D101

RB715F-X

!

VDD

X102

INTR

NAX0267-001X

C126

C142

10p

0.01

3p

C107

0.01µ

IC102

25LC160-I/SN-X

100K

R155

Vcc

CS

HOLD

SO

SCK

WP

SI

Vss

CN25

CN13

CN13

CN13

CN13

CN13

CN2

#

CN9

#

Q119

UMX1N

R201

#

27

CN18

R164

220

Q114

DTC114EE

CN25

R198

0

CN25

CN25

DIAL_PB

DIAL_MN

DIAL_AT

DIAL_OF

DIAL_PB

OPEN_SW

REV_SW

TRIG_SW

CAS_SW

LCD_CS

APB_EP_H

V_PB_L

LENS_CS

C_FRB

CDS_CS

V_DSP_CS

V_ASP_CS

OSD_CS

REG_CS

MDA_PS

OSD_CLK

OSD_DATA

LAMP_ON

PB_VF

REG_4.8V

LED/LAMP

LED_2

LED/LAMP

LENS_LED

IRIS_O/C

HD_H

IR_FLICK

SCK3

SO3

DSP_REST

AL_L3.2V

LED_R

AL_J3.2V

TXD

RXD

AREG_CLK

AREG_SO

S_DET_L

A_MUTE

A_PB

VF_CTL

TO JIG CONN

OPEN

TO LCD_CTL

TO CN13

TO SPEAKER

TO LCD_CTL

TO VTR ASP

TO TG_CDS

TO F/Z/IRIS

TO MDA

TO TG_CDS

TO DSP(VTR/CAM)

TO VTR ASP

TO DSP(VTR/CAM)

TO REG

TO MDA

TO DSP(VTR/CAM)

TO REG

TO BWVF_CTL

TO LED

TO REG

TO F/Z/IRIS

TO DSP(VTR/CAM)

TO F/Z/IRIS

TO DSP(VTR/CAM),F/Z/IRIS,

VTR ASP,LCD_CTL,TG_CDS

TO DSP(VTR/CAM),F/Z/IRIS,

LCD_CTL,TG_CDS

TO TOP

TO JIG CONN

TO JIG CONN

TO REG

TO DSP(VTR/CAM)

TO VTR ASP

TO BWVF_CTL

R123

C127

0.033µ

0.47µ

C128C129

0.033µ

10K

R142

C120

0.01µ

C119

1M

R173

2.2K

330

2.2K

R145

R124

R174

XT1

RESET

XT2

XT1

NC/VPP

P165/VSOUT

P167/HSOUT1

P166/HSOUT0

VPP7.8V

PMIRROR

RESET( L)

LIGHT_SW

#

IC101

UPD703039-064-A

P54/AD12

P53/AD11

P52/AD10

P51/AD9

P50/AD8

BVSS

AD11

AD10

AD9

AD8

GND

SYS_3V

AD9

AD8

AD11

AD10

C133

0.1µ

ONS".

yf126_y10489001a_rev1.1

(No.YF126)2-6

Page 8

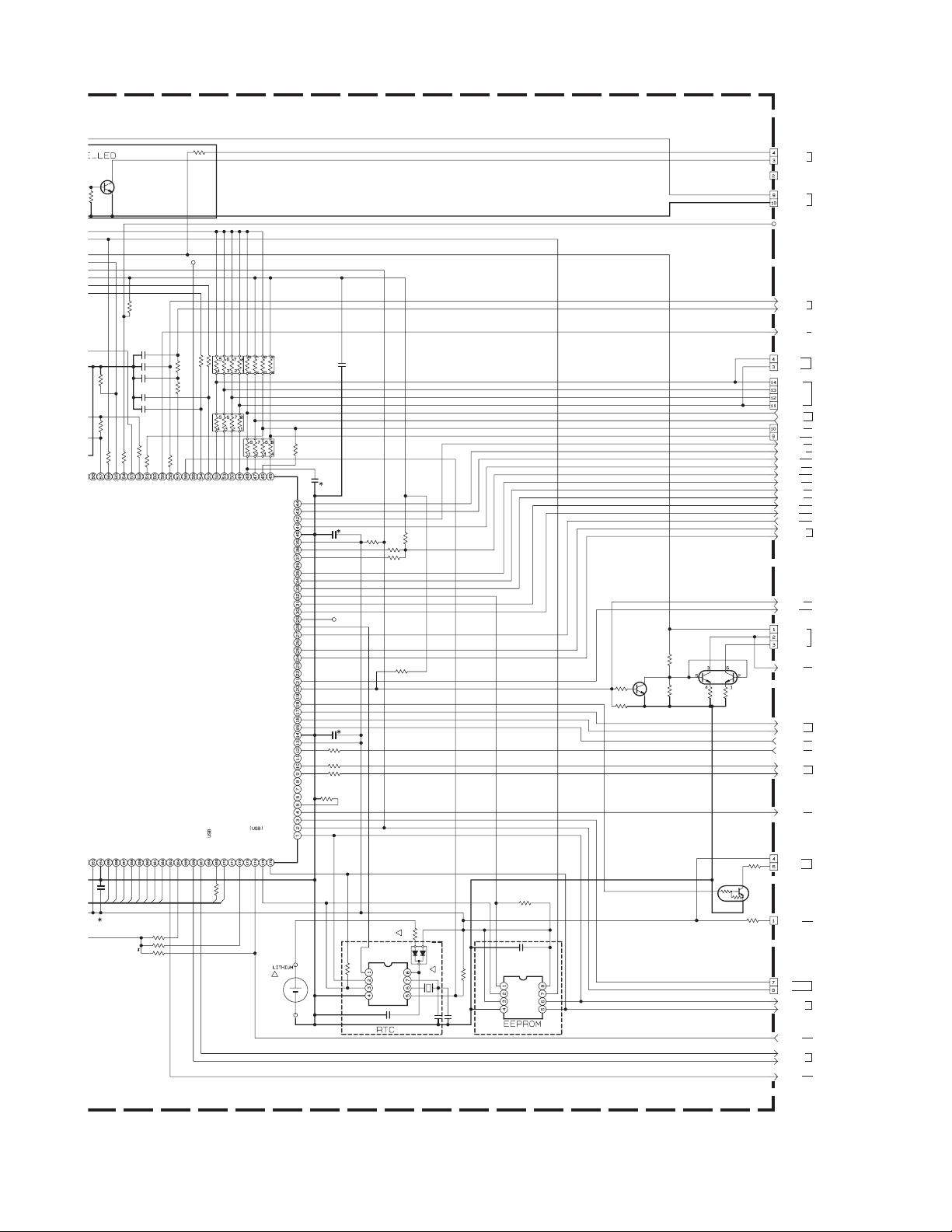

P

P

C1618

D.FGIN

C.PCI

3

0

0 068

MAIN(MDA) SCHEMATIC DIAGRAM

MAIN(MDA)

10

DRUM_PG

DRUM_FG

CAP_FG

DRUM_REF

TO CPU

CAP_REF

C_FRB

L_FRB

MDA_PS

100p

C1613

0.01

C1612

0.0068

C1611

0.0068

22k

C1610

R1610

0.33

C1609

68k

R1609

T

T

C1

0.

R1

3

TO MECHA

(LOADING MOTOR)

LOAD_FWD

LOAD_REV

TO MECHA

(DRUM_ MOTOR)

D_PG-

D_PFG+

D_FG-

CENTER

D_COIL_W

D_COIL_W

D_COIL_V

D_COIL_V

D_COIL_U

D_COIL_U

CN4

CN1

C1614

0.01

D1602

DAP222-X

680

R1611

C1622

C1623

C1624

R1612

R1613

R1602

68k

18k

R1614

150k

1k

R1615

0.1

C1615

0.33

TP1603

TP1606

D.PCV

D.COM

D.U

D.V

D.RNF

D.W

NC

L.FRB

L.REF

L.FWD

NC

L.GND

L.REV

L.VM

C.FGIN+

C.FGIN-

C.FGAMP

C.FGSMT

R1616

68k

D.PCI

NC

0.22

C1616

D.EC

VG

D.VS

CP1

0.22

C1617

D.VM

CP2

NC

NC

0.22

C1629

UNREG

IC1601

BD6637KV

GND

D.SL1

D.SL2

D.ISET

!

GDXPSC.RCC

6.8k

R1617

VCC

D.FGSMT

D.DETECT

C.FRB

C.VM

C.VS

-

D.FGAMP

C.EC

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

2-7(No.YF126)

Page 9

R1617

R1610

6

8k

22k

68k

68k

680k

D1601

DAP222-X

TP1607

TP1608

NMFZ007-R20X-K

R20

F1601

!

NOL365K-470X

L1604

!

F1602

NMFZ007-R50X-K

47

R50

DRUM_ERR

DRUM_PWR

CAP_ERR

CAP_PWR

REG_4.8V

UNREG

REG_3.2V

TO REG

TO CPU,

REG

.

0.33

C1609

D.DETECTC.FRB

VCC

C.VM

R1609

TP1604

TP1601

C1608

0.0015

R1608

330k

D.FGSMT

D.FGAMP

C.VS

C.EC

D.PFGIN+

D.FGIN-

D.PGIN-

D.PGAMP

D.PGSMT

C.HW-

C.HW+

C.HV-

C.HV+

C.HU-

C.HU+

C.W

C.RNF

C.PCI

C.PCV

0.068

0.01

C1618

C1619

C.V

C.U

NC

NC

NC

0.47

C1607

1k

R1607

R1606

/6.3

10µ

C1606

R1603

220k

C1603

C1602

C1601

R1605

T

C1604

10

R1604

470

TP1605

C1625

R1620

0.022

0.022

0.022

/6.3

C1605

680p

TP1602

C1626

R1621

C1627

R1622

C1621

C1620

T

T

C1628

10

/6.3

T

L1603

NQL315K-470X

R1619

R1618

47

GND

TO MECHA

(CAPSTAN MOTOR)

CN3

C_FG-

GND

C_FG+

CAP_3.2V

C_COIL_U

C_COIL_U

C_COIL_V

C_COIL_V

HG_W-

C_COIL_W

C_COIL_W

HG_U-

HG_BS-

470

HG_BS+

470

HG_U+

HG_W+

HG_V+

HG_V-

ONS".

R1601

0.33

yf126_y20346001a_rev0.1

(No.YF126)2-8

Page 10

R

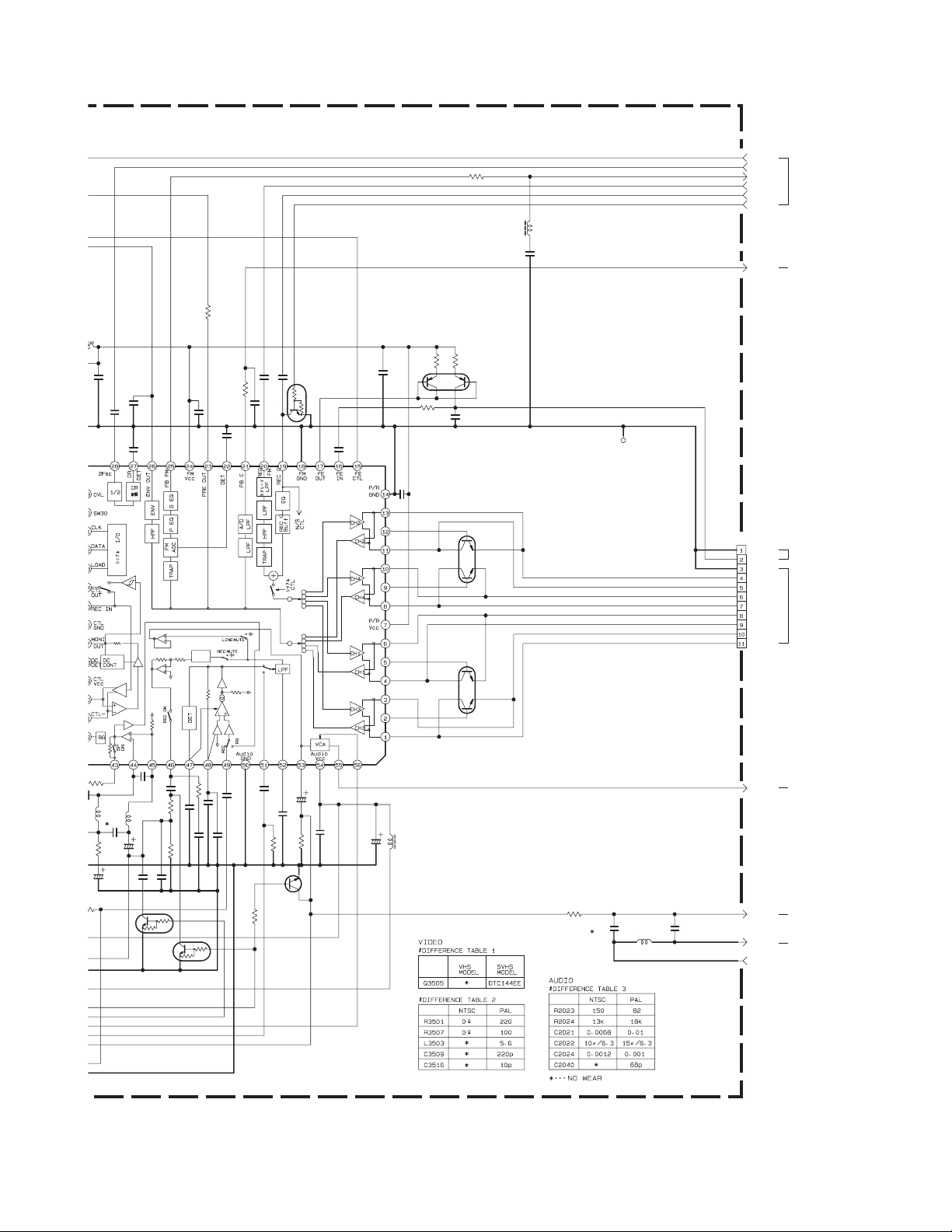

MAIN(VTR ASP) SCHEMATIC DIAGRAM

MAIN(VTR ASP)

10

TO JIG_CONN

V_OVL

AO_SIG_J

PB_CTL

V_TP_FM

CN25

V_FF

TO CPU,DSP(VTR/CAM)

TO CPU,DSP(VTR/CAM),

F/Z/IRIS,LCD_CTL,TG_CDS

TO CPU

TO DSP(VTR/CAM)

TO A/C HEAD

TO CPU

FEH_ON

V_ENV

V_ASP_CS

CTL_OUT

REC_CTL

A_BIAS

A_MUTE

APB_EP_H

SPK_VOL

REG_4.8V

REG_3.2V

REG_4.8V

CTL_HED-

CTL_HED+

AH_PB

AH_REC

AH_GND

V_FF

SCK3

SO3

A_PB

GND

CN7

AE-

L2004

AE+

L2005

0Ω

0Ω

JP2001

JP2002

R2005

2.7k

Q2008

PUMT1

L2001

47µ

C2001

10

/6.3

T

MC74AC04DT-X

IC2001

C2003

330p

DTA114TE

Q2001

L2003

47µ

C2005

1.0

R2002

R2004

6803.3k

C2004

/6.3

22

R2001

C2002

TF

100k

R2003

R2011

R2012

0.018

1k

R2006

1k

100

Q2007

PUMX1

100

JP2004

JP2003

C1206

10

R2071

47k

C1201

C1205

C1202

10

/16

/6.3

2SC4617/QR/

R3508

R3506

T

1000p

15k

1k

C1204

C2021

#

R2022

330k

Q2071

NQR0006-001X

0.015

T

C2071

10

R2023

#

/6.3

R2072

10k

L3502

R2021

10k

C3512

L2022

0Ω

T

C3513

0.022

10

C3515

0.01

C3514

1.0

C2040

#

L2023

C2039

0Ω

C2023

1.0

T

/16

C2022

#

C2026

0.0022

TO DSP(VTR/CAM)

TO MIC(CN8)

SH_SIG

MIC_HOT

MIC_GND

L2072

C2072

0.0022

0Ω

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

2-9(No.YF126)

Page 11

0

V_OVL

#

R3507

#

L3503

#

C3516

R3502

1k

2

-001X

R3901R3902

R3903

1.8k

Q3502

10100

C3901

OPEN

Q3901

JP3501

C3902

C3507

C3508

0.01

0.01

#

Q3505

#

C3509

C3903

3p

C3513

0.022

C3512

10

0.01

C3515

C3514

1.0

C3511

OPEN

#

R3501

IC3501

C3510

0.1

HA118224F

0.01

C3506

0.01

2FSC

V_PB_F

TO DSP

V_REC_F

(VTR/CAM)

V_REC_C

S_DET+

V_PB_C

TO TG_CDS

CN5

GND

TO FLY. E HEAD

FE_S

GND

V_CH2_S

V_CH2_F

V_CH4_S

V_CH4_F

V_CH1_S

V_CH1_F

V_CH3_S

V_CH3_F

(CN5)

TO VIDEO HEAD

(CN5)

2021

0k

L2022

0Ω

C2039

C2023

3

C2022

#

T

2

ONS".

Q3501

1.0

#

C2025

C2040

R2024

L2023

0Ω

1.0

T

/16

0.0022

C2026

C2024

#

R2025

R2030

100k

#

82k

Q2021

DTC144EE

Q2022

DTC144EE

C2027

1.0

C2029

1.0

C2028

0.47

1.0

C2036

0.47

C2038

C2031

0.1

R2031

3.3k

C2032

1k 0.0047

R2027

Q2023

2SC4617/QR/

C2033

/6.3

4.7

T

0.1

1k

R2028

C2034

C2035

22

L2021

NQR0006-001X

T

/6.3

R2051

1k

C2052 C2051

L2052

0.01

0Ω

PA_SIG

AO_SIG

AO_GND

GND

TO SPEAKER

(CN27)

TO JACK

TO JACK

yf126_y20348001a_rev0.1

(No.YF126)2-10

Page 12

C4033

0.1

TMY 6

MAIN(DSP) SCHEMATIC DIAGRAM

MAIN(DSP)

10

CAM_Y

CAM_C

SPK_VOL

SH_SIG

S_DET+

V_REC_C

V_REC_F

2FSC

V_PB_F

CDS_CLK

AD_9

AD_8

AD_7

AD_6

AD_5

AD_4

AD_3

AD_2

AD_1

AD_0

LHFO

HDTG

VDTG

TG_CLK

ID

R4034

3.3k

R4035

3.3k

C4047

0.1

S_DET+

TO TG_CDS

TO V_OUT

TO VTR ASP

TO BWVF_CTL

TO V_OUT

LCD_CTL

BWVF_CTL

CDS_CLK

LHFO

HDTG

VDTG

TG_CLK

PBLK

CAM_Y

CAM_C

SPK_VOL

SH_SIG

S_DET+

V_REC_C

V_REC_F

2FSC

V_PB_F

V_OVL

VF_EXCLK

DAC_3.2V

REG_2V

REG_3.2V

AD_9

AD_8

AD_7

AD_6

AD_5

AD_4

AD_3

AD_2

AD_1

AD_0

ID

GND

SH_SIG

D4001

#

Q4001

#

V_PLS_ON

V_OVL_A

V_OVL_B

SDET_CTL

V_PULSE

SCK3

V_DSP_CS

SO3

V_FF

CLKCPU

S_DET_L

DSP_REST

BWYOUT

BOUT

R4041

2.2k 6.8k

CAM_Y

CAM_C

ROUT

GOUT

L4001

NQR0006-001X

CDS_CLK

R4042

1.2k

R4045

0

C4053

1000p

C4054

#

C4026

10

L4002 C4049

NQR0006-001X

C4009

10p

C4010

10p

C4011

C4052

#

C4019

#

C4024

#

C4025

#

C4031

1

R4009

2.7k

R4010

10

R4004

C4015

0.1

C4018

0.1

C4013

0.1

C4021

0.1

1000p

C4017

0.1

X4001

CHCH

CH

R4003

56k

R4014

#

R4047

100

CH

0.1

C4007

FMRE

AVDD

R4043

VDD10

NC

C4029

R4044

1.2k

IE

WAD

IE

GND9

IC4001

JCY0184

NC

VREFFMY

2.7k

R4019

2.2k

C4030

0.1

FMWR

RAD

RAD

WAD

FMOUT

IRSETFMY

R4020

V_REC_C

V_REC_F

C4006

FCLK

TMC_3

#

R4036

MCLK

FMWR

RECCOUT

1000p

C4055

220

R4021

100

TMC[3]

AVDDNCAVSS

TMC_2

TMC[2]

NC

TMC_1

TMC[1]

NC

TMC_0

TMC[0]

R4024

TMY_7

VDD9

GND8

TMY[7]

AVDD

VIN

AVSS

R4023

0

C4032

1.5k

R4022

V_PB_F

C4048

0.1

AD_9

AD_8

AD_7

AD_6

AD_5

AD_4

AD_3

AD_2

AD_1

HDMASK

CLKOSD

VC_1

CLKOSD

SDPRD

VC1

VDTG

VC_2

R4037

VDTG

VC2

HDTG

VR

HDTG

VR

AD_0

GND10

TDI

ADIN[6]

TDO

R4018

ADIN[7]

GND15

C4028

ADIN[8]

VDD18

0.1

LHFO

ADIN[9]

VPD

R4015

#

WAE

WAE

LHFO

TVSELO

GND16

RAE

R4016

#

FMWE

RAE

VDD19

FMRE

FMWE

AVSS

ID

1k

ID

VDD11

ADIN[5]

ADIN[4]

ADIN[3]

ADIN[2]

ADIN[1]

ADIN[0]

VDD17

0.1

VGVBBLK1

BLK_1VBVG

BLK_2

TCK

BLK2

VBLK

R4017

VBLK

GND14

C4027

TG_CLK

R4040

120

#

R4002

1M

C4008

0.1

C4012

0.1

C4014

C4016

C4020

C4023

0.1

R4013

#

XIN

XOUT

VDD12

SDCK

SLD

STD

GND12

VDD13

SW30

DOCK

DCKI

CLKI

VDD14

CLKCPU

SCLEARI

GND13

AD1_CK

CAMADCK

SVHSOUT

CLR

TMS

ASEL

TVTR1

AVDD

AVSS

BWYO

BYOUT

IRSETBWY

VREFBWY

NC

NC

AVDD

AVSS

NC

AVDD

AVBB

NC

VREFC

IRSETC

YOUT

COUT

AVSS

AVDD

NC

NC

AVDD

AVSS

RYOUT

Y2OUT

IRSETRY

VREFRY

NC

NC

AVDD

AVSS

GND

VDD16

KOUT

CSYNC

AD2_CK

GND11B

SCBLKO

10k

R4046

GND11TRST

CAMCK

VDOSD

VDOSD

ADDV

HDOSD

HDOSD

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

2-11(No.YF126)

Page 13

C4006

C4055

FMWRRECCOUT

220

1000

p

CH

FCLK

R4036

R4021

MCLK

TMC_3

#

100

TMC[3]

AVDDNCAVSS

TMC_2

TMC[2]

NC

TMC_1

TMC[1]

NC

TMC_0

TMC[0]

R4024

BWGAIN

BWGAMMA

BWYOUT

C4005

0.1

FMY_1

R4039

470

R4038

470

FMY_0

C4004

0.1

C4002

0.1

1k

C4003

0.1

R4001

C4001

WAIT_L

VD_H

HD_H

R/W_L

DSTB_L

VDVHS

MSM548331TA

#

IC4002

DIN6

C4050

CLKOSD

BLK_1

VC_1

BLK_2

VC_2

VBLK

VR

VG

VB

VDOSD

HDOSD

VSS

DIN5

DIN4

DIN3

DIN2

DIN1

DIN0

RCLK

RXAD

WADE/RX

RADE/RX

RR

RXINC

RE

OE

DO0

DO1

VCC

DO2

DO3

VSS

DO4

DO5 VCC

BLK1

VC1

BLK2

OSCIN

VC2

OSOUT

VBLK

CKOUT

VR

VG

VB

VSYNC

HSYNC

IC4003

UPD6467GR-567-X

WR/TR

WXINC

GND

TEST

DATA

DIN10

DIN11

WCLK

WXAD

DO11

DO10

VDD

PCL

CLK

DIN7

DIN8

DIN9

WE

IE

C4051

VCC

DO9

DO8

VSS

DO7

DO6

C4044

C4046

CH

220p

C4045

CS

TMY_5

TMY_4

TMY_3

TMY_2

TMY_1

TMY_0

FCLK

RAD

RAE

FMRE

FMY_0

FMY_1

FMY_2

FMY_3

FMY_4

FMY_5

OMT

VDCVF

HDCVF

CFM

FI

AD15

AD14

AD13

AD12

AD11

AD10

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

ASTB

HRP1

VDD7

VDD20

C4038

GND7

PWMOUT2

100k

R4028

0.1

C4039

0.1

FMC_1

FMC[1]

PWMOUT3

#

R4029

C4040

0.1

SPK_VOL

FMC_0

FMY_7

FMC[0]

PWMOUT4

1K

1K

R4031

R4030

C4042

1

C4041

FMY_5

FMY_6

FMY[6]

FMY[7]

PWMOUT5

GND18

1

BWGAMMA

BWGAIN

FMY_4

FMY[5]

DICK

R4032

C4043

FMY[4]

DCKO

CH

FMY_3

FMY[3]

FSC2OUT

0

R4033

2FSC

FMY_2

FMY[2]

FMY[1]

FMY[0]

VDD6

GND6

HDDSC

VDDSC

FLDDSC

CLKDSC

DSC[3]

DSC[2]

DSC[1]

DSC[0]

GND5

DSY[7]

DSY[6]

DSY[5]

DSY[4]

DSY[3]

DSY[2]

VDD5

DSY[1]

DSY[0]

PBLK

GND4

BUSY

VDCVF

VDD4

HDCVF

FLDCPU

VDCPU

HDCPU

VDD3

GND3

BUS[15]

BUS[14]

BUS[13]

BUS[12]

BUS[11]

BUS[10]

VDD2

BUS[9]

BUS[8]

BUS[7]

GND2

BUS[6]

BUS[5]

BUS[4]

BUS[3]

VDD1

BUS[2]

BUS[1]

BUS[0]

ASTB

HRP1

GND1

HRP2

DSTB

VREFO

3.9k

OMT

FRP

RW

TMY_7

TMY_6

TMY_5

TMY_4

TMY_3

TMY_2

TMY_1

TMY_0

FMC_3

FMC_2

GND8

AVDD

TMY[7]

VIN

R4023

C4032

0.1

1.5k

V_PB_F

TMY[6]

REFBOTI

C4033

VDD8

TMY[0]

TMY[1]

TMY[2]

TMY[3]

TMY[4]

TMY[5]

REFTOPI

AVSS

C4034

C4035

0.1

0.1

R4025

AVDD

1.5k

STB

PDNCPWMOUT1

TVTR2

R4026

C4036

C4037

FMC[3]

100k

R4027

0.1

FMC[2]

GND17

VDD9

AVSS

0

R4022

HDCVF

VDCVF

HRP1

GOUT

ROUT

BOUT

TMY_6

TMY_7

TMC_0

TMC_1

TMC_2

TMC_3

WAD

WAE

FMWR

FMWE

IE

FMC_3

FMC_2

FMC_1

FMC_0

FMY_7

FMY_6

#

OSD_CLK

OSD_CS

OSD_DATA

VDVHS

V_FF

DSTB_L

R/W_L

ASTB

AD0

AD1

AD2

AD3

AD4

AD5

AD6

OSD_DATA

OSD_CS

OSD_CLK

DSP_REST

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

OMT

CFM

HD_H

VD_H

FI

DSP_REST

WAIT_L

SCK3

SO3

V_DSP_CS

V_PULSE

V_PLS_ON

V_OVL_A

V_OVL_B

S_DET_L

SDET_CTL

CLKCPU

H_OFFSET

H_GAIN

1

BWGAIN

BWGAMMA

BWYOUT

HDCVF

VDCVF

HRP1

GOUT

ROUT

BOUT

OSD_CLK

OSD_CS

OSD_DATA

VDVHS

V_FF

DSTB_L

R/W_L

ASTB

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

OMT

CFM

HD_H

VD_H

FI

DSP_REST

WAIT_L

SCK3

SO3

V_DSP_CS

V_PULSE

V_PLS_ON

V_OVL_A

V_OVL_B

S_DET_L

SDET_CTL

CLKCPU

VDDSC

H_OFFSET

H_GAIN

TO BWVF_CTL

TO LCD_CTL,

BWVF_CTL

TO LCD_CTL

TO CPU

TO CPU,F/Z/IRIS

TO CPU,VTR ASP

TO CPU

TO CPU,F/Z/IRIS,

LCD_CTL,TG_CDS

TO CPU

TO CPU,F/Z/IRIS,

VTR ASP,LCD_CTL,

TG_CDS

TO CPU

TO CPU

ONS".

H_OFFSET

H_GAIN

yf126_y10490001a_rev0.1

(No.YF126)2-12

Page 14

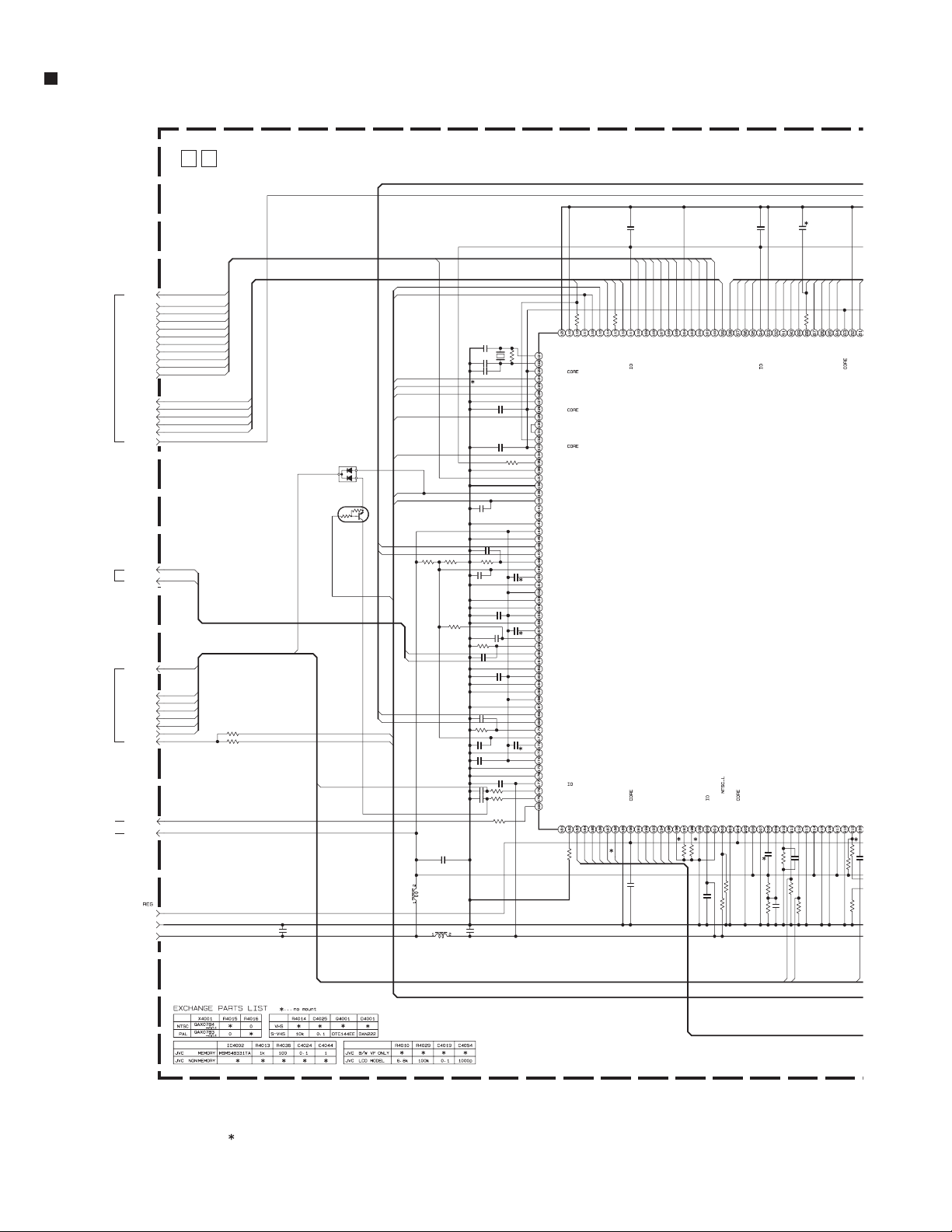

MAIN(F/Z/IRIS) SCHEMATIC DIAGRAM

MAIN(F/Z/IRIS)

10

TO CPU

TO DSP(VTR/CAM)

TO CPU

IRIS_O/C

IRIS_PWM

HALL_A/D

H_OFFSET

H_GAIN

IR_DC

IR_FLICK

REG_4.8V

GND

L4201

NQR0006-001X

C4201

2.2/50

C4202

0.1

R4262

R4258

Q4251

R4259

C4256

R4257

C4253

C4254

R4252

R4251

R4256

R4254

R4253

R4255

C4251

R4210

1M

IC4201

BA10324AF-XE

10k

R4201

R4205

C4205

C4203

0.1

1M

0.1

C4252

R4214

4.7k

TO REG

TO CPU

TO CPU,

DSP(VTR/CAM)

TO DSP(VTR/CAM)

TO CPU

TO CPU,DSP(VTR/CAM),

VTR ASP,LCD_CTL,TG_CDS

TO TG_CDS

TO CPU,

DSP(VTR/CAM),

LCD_CTL,TG_CDS

ZF_4.8V

REG_3.2V

LENS_LED

VDVHS

VDDSC

LENS_CS

SO3

SCK3

LENS_CLK

DSP_REST

R4524

0R0

L4501

NQR0006-001X

C4512

0.1

L4502

22

C4509

10

/10

C4510

0.1

T

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

2-13(No.YF126)

N

(

Page 15

0

R4207R4206

.

100k10k

5

100k

R4209

R4208

C4206

0.1

R4211

24k

C4252

R4214

4.7k

3

4.7k

0.1

IC4202

BA10324AF-XE

0R0

R4202

R4215

68k

R4216

10k

R4217

C4209

Q4202

2SC4617/QR/-X

R4225

C4207

0.01

CN15

CN15

DRIVE+

CN15

HE_OUT-

HE_IN-

HE_OUT+

HE_IN+

TO OP

C4208

R4219

C4211

0.1

R4218

33k

C4212

1

1k

0.1

R4223

33k

R4221

330k

Q4201

2SC4617/QR/-X

330

R4204

R4516

510

1

270

Q4501

DTC114EE-X

R4505

R4506

!!

C4501

33p

R4503R4504

6R86R8

R4507

10K

R4527R4528

0R0

R4513

10K

22k

R4203

1

P_GND

EXP3

EXTa

Vm1

A1

FBa

A2

Vm2

B1

FBb

B2

EXTb

VD

LATCH

SDATA

SCLK

OSCin

OSCout

RESET

C4210

IC4501

UPD16835AGS-X

EXP2

EXP1

EXP0

Vm4

Vm3

FILd

FILc

FILb

FILa

Cosc

GND

22k

R4224

C1

FBc

C2

D1

FBd

D2

Vdd

Vref

R4222

150K

R4502 R4501

6R8 6R8

!!

C4508

0.1

C4506

10000p

C4504

33000p

C4502

33p

C4505

10000p

C4503

33000p

0.1

C4507

R4508

22k

R4509

1.8k

CN15

CN15

CN15

CN15

CN15

GND

GND

OP_VCC

ZOOM_LED

FOCUS2

FOCUS4

FOCUS3

FOCUS1

Z_L_VCC

F_LED

ZOOM1

ZOOM3

ZOOM4

ZOOM2

ONS".

yf126_y20347001a_rev0.1

(No.YF126)2-14

Page 16

MAIN(V_OUT) SCHEMATIC DIAGRAM

MAIN(V_OUT)

10

REG_4.8V

TO DSP, LCD_CTL,

BWVF_CTL

DAC_3.2V

#

R4715

0Ω

#

R4704

1.2k

IC4701

#

NJM2562F1-X

TO DSP

(VTR/CAM)

CAM_Y

GND

TO DSP

(VTR/CAM)

CAM_C

#

R4714

0Ω

#

R4701

C4701

#

R4707

240

#

R4703

680

#

R4709

680

#

#

C4716

27p

#

C4703

5p

#

C4717

5p

#

Q4701

2SA1774

#

R4710

1.2K

#

Q4702

2SA1774

C4704C4702

127p

#

C4705

0.01

IC4702

#

BA7665FS-X

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

2-15(No.YF126)

Page 17

IC4701

M2562F1-X

IC4702

7665FS-X

L4701

NQR0006-001X

C4708

0.1

T

C4709

10

/6.3V

C4706

100

#

C4707

/6.3

22

#

C4714

#

C4713

CN25

V_OUT

TO JIG_CONN

(CN25)

#

R4706

/4

75

#

R4712

V_OUT

D4701

TO JACK

SY_OUT

D4702

ONS".

#

C4715

#

R4713

D4703

SC_OUT

D4704

yf126_y30299001a_rev0.1

(No.YF126)2-16

Page 18

MAIN(TG_CDS) SCHEMATIC DIAGRAM

MAIN(TG_CDS)

10

TO CCD

(CN5301)

CN22

H1

H2

V4

V3

V2

V1

GND

GND

GND

CCD_OUT

CCD_HV

SUB

CCD_LV

RG

1SS355-X

D5201

C5222

0.1

100k

R5212

0.1

C5225

C5231

0.1

IC5202

MN31121SAS-X

IV4

CH2

IV3

NC

VH

OV3

OV4

VM24

VHH

C5224

/25

1µ

ISUBNC

CH1

VDC

OV1

VM13

OV2

OSUB

IV2

IV1

XV2

XV3AVdd

XV4

CH1

R5203

C5211

C5212

C5213

1M

1M

1M

1M

0.1

0.1

0.1

R5204

R5205

R5206

R5208

33k

C5226

0.1

VL

C5223

0.1

CH2

CH3

CH4

XSUB

SUB_SW/ADC

SUB_UP_PD

STROB/Vgate

DVss3

AVss

ADC_in

BIAS

VRB

VRT

VRM

C5214

0.1

C5215

1000p

C5216

1µ

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

2-17(No.YF126)

BLKC

Page 19

R5221

C5204

/25

1

R5220

T

C5203

10

R5218

/16

R5201

0Ω

L5203

L5204

NQR0006-001X

NQR0006-001X

T

L5201

C5201

10µ

/6.3

22µ

REG_15V

REG-8-5V

REG_3.2V

XV2

XV3AVdd

CH1

CH2

CH3

CH4

XSUB

SUB_SW/ADCLK_IN

SUB_UP_PD

STROB/Vgate

DVss3

AVss

ADC_in

BIAS

VRB

VRT

VRM

BLKC

C5214

0.1

C5215

1000p

0.1

C5209

XV1

DVdd3

CDS_IN

AVdd

C5217

DVdd4

BLKFB

C5218

1µ

H2A

1/6CLK

IC5201

HD49335F

BLKSH

AVss

R5219

DVss4

TEST2

2.2K

DVss4

TEST1

C5219

1/3CLK

DLL_C

100p

CH

H1A

DVdd1

C5220

0.1

C5207

DVdd4

MONI

0.1

RG

Reset

DVdd3

DVss1,2

41_CONTCSSdata

TL5204

C5206

R5202

VD

CLK_in

DVss3

DVdd2

Sck

R5214

120Ω

HDXV4

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

ID

LENS_CLK

TG_CLK

LHFO

VDTG

HDTG

AD_9

AD_8

AD_7

AD_6

AD_5

AD_4

AD_3

AD_2

AD_1

AD_0

ID

PBLK

CDS_CLK

TO CPU,DSP(VTR/CAM),

F/Z/IRIS,LCD_CTL

DSP_REST

SCK3

SO3

CDS_CS

V_PB_L

GND

TO F/Z/IRIS

TO DSP

(VTR/CAM)

TO CPU,DSP(VTR/CAM),

F/Z/IRIS,VTR ASP,

LCD_CTL

TO CPU

C5216

1µ

ONS".

C5221

100p

yf126_y30298001a_rev0.1

V_PB_C

TO VTR ASP

(No.YF126)2-18

Page 20

MAIN(REG) SCHEMATIC DIAGRAM

MAIN(REG)

15k680

R6027R6028

10

F6001

2A

!

NMFZ007-2R0X-K

TO

REAR UNIT

(CN28)

1

C6026

1

C6025

1

C6024

1

C6023

C6002

L6001

10µ

L6002

10

C6003

10µ

C6004

R6043

0.1

C6022

C6021

0.1

RA6001

1k

100k

R6007

9.1k

R6029

R6032

C6028

R6031

C6030

0.001

C6031

0.001

4.7k

C6032

0.001

R6033

C6029

0.001

R6045

R6046

R6034

R6030

C6027

0.0047

5.6k

15k

12k

R6047

C6033

0.01

15k

33k

IC6001

FA3698F

15k

C6034

0.1

R6035

180k

180k

R6036

0.1

C6035

C6036

100p

5.6K

R6037

0.1

C6037

0.01

C6038

0.22

C6039

C6040

0.047

C6041

0.047

C6042

0.047

C6043

0.068

R6008

100k

C6046

560p

C6045

C6044

0.01

1

R6038

R6039

1k

o

R6044

220k

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

2-19(No.YF126)

Page 21

ADP_H

UNREG

TO CPU

R6708

C6101

R6709

1

0

33

C6701

2.2

C6301

Q6701

1

Q6101

Q6301

RS0035P03

QS6U24

A

S

GCaD

FDC6506P

G1

S2

G2 D2

1

C6401

NC

D1

S1

Q6401

L6701

10µ

RB160M-30

D6701

QS6U24

A

S

GCaD

1

C6703

L6101

33µ

C6103

NC

D6702

10

D6301

F6301

1.6A

0.5W

RB160M-30

!

R6701

0.2

C6104

R6110

L6301

22µ

C6303

L6401

10

47µ

C6403

100p

1.8k

C6704

1

10k 22k

R6103 R6102

C6304

R6310

C6404

R6702

R6703

R6104

100p

1.8k

R6403

BATT_L

V_BATT

120

120

120

R6711

R6712

0.001

1.2k

12k 10k

R6203 R6202

R6713

Q6702

C4097

R6807

R6808

10k

2.2k

0.01

C6804

82k33k

R6706R6707

15k

Q6201

1

C6201

QS6U24

A

S

GCaD

NC

0.01

C6705

L6201

C6203

R6710

2.2k

47µ

C6204

R6204

10

!

#

R6306

0.47

D

G

R6305

75k

0.068

R6406

#

100k

#

C6305

10

QS6U24

Q6501

A

S

GCaD

1

39k

C6501

L6501

47µ

R6507

150k

NC

C6503

1

C6504

5.6k

R6503

47k

R6502

C6505

R6505

56k

27k

R6506

1

5.6k

4.7k 1.8k

R6303 R6302

R6402

Q6302

S

2SK3577

#

47k

R6405

C6405

F6302

0.4A

CN25

TO JIG_CONN

PLI_AD

MCU_RST

AREG_SO

AREG_CLK

REG_CS

REG_3.2V

REG_2V

T_BATT

GND

REG_4.8V

ZF_4.8V

CN6

LED/LAMP

LAMP_ON

DRUM_PWR

DRUM_ERR

CAP_PWR

C_GAIN

CAP_ERR

TO CPU

TO CPU

TO CPU

TO F/Z/IRIS

TO LAMP

TO LAMP

TO CPU

TO MDA

TO CPU

TO MDA

ONS".

R6044

220k

F6801

0.25A

C6610

REG_15V

REG_-5V

REG-8-5V

REG_-15V

AL_3.2V

AD_REF

TO CPU

R6619

0

220µ

L6601

!

Q6801

47k

R6802

R6803

1k

Q6802

B1121

R6804

1.8k

C6602

C6606

100p

C6801

D6601

1

1SS355

1

D6602

1SS355

C6603

D6603

1SS355

D6604

105

1SS355

100k120k

R6805R6806

150k

R6811

1

C6802

C6604

105

C6607

R6605

68k

R6604

R6602

270k

R6603

3.9k

Q6803

DTA144EU

1

C6803

C6609

Q6604

DTC144EE

7.5B

D6605

1k

R6620

100k

R6612

82k

R6613

D6606

1.8k

R6621

5.1B

yf126_y10491001a_rev0.1

(No.YF126)2-20

Page 22

MAIN(BWVF_CTL) SCHEMATIC DIAGRAM

MAIN(BWVF_CTL)

10

TO JIG_CONN

TO CPU

TO DSP(VTR/CAM),

TO DSP(VTR/CAM),

LCD_CTL

V_OUT, LCD_CTL

TO CN12

TO DSP

(VTR/CAM)

BWGAIN

BWGAMMA

REG_3.2V

REG_-5V

VIDL

VF_CTL

REG_4.8V

BWYOUT

DAC_3.2V

CRT_4.8V

GND

CRT_Y

GND

CN25

R7334

R7333

NBE20JM-106X

L7302

NQL315K-220X

R7301

1.0k

C7201

T

R7305

R7304

C7312

L7201

C7313

0.1µ

F7201

R7338

0W

0.1µ

C7311

CLK_QP3

V33IN

NC

NC

NC

ENB_QP3

VBAT

CLKB

CLKA

NC

C7310

FB_REF

VSSA3

ISINK

PDR

R7329

D7301

R7330

VID0

VID0

KCD-A300-QB

VGAIN

IC7301

R7327

47k

R7328

VID1

VGAMMA

33k

TO CPU

TO DSP(VTR/CAM),

LCD_CTL

PB_VF

HDCVF

R7342

R7339

R7340

R7341

Q7303

Q7304

R7303

120

820

R7302

C7301

FB5V PRE_QP3

REFO

C7303

0.1µ

Q7301

2SA1774/QR/-X

OSD_IN

EXTWT

R7306

R7307

BKLVL

0.1

C7304

VIN

510k

R7308

VBG

WT_SEL

C7306

0.1µ

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

VSSA1 VID1

2-21(No.YF126)

Page 23

VGAMMA

0

1

301

00-QB

33k

R7327

47k

R7328

VID1

VID1

VSSA2

CK1

CK1

VS

CK0

VS

CK0

HS

INV

EXTCLK

V1X_SEL

INV1

INV0

Test_mode0

PAL_MODE

SKIPLIN

FD1

FD0

HS

INV

R7335

R7336

R7325

#

R7317

#

R7313

R7345

0Ω

R7323

R7321

R7319

R7315

0

R7324

#

R7318

R7316

#

R7314

#

R7312

R7322

R7320

0Ω

R7337

R7309

3.3k

Q7302

PUMX1-W

R7331

0

R7311

R7326

560

VID1

CK0

CK1

HS

VS

INV

VID0

C7307

IC7302

R7332

47Ω

0.33µ

C7308

L7301

NQR0006-001X

0.33µ

C7309

C7302

SN74AHC1G08K-X

0.1µ

TO BWVF

(CN7401)

CN7301

TO DSP

(VTR/CAM)

VF_EXCLK

VDCVF

GND

VIDH

VDD

CK0

CK1

VSS

PDR

SLEEP

HS

VS

INV

VIDL

VF_BL

REG_4.8V

WT_SEL

VSSA1

VBBA

PDB

Test_mode1

VSSD

NC

R7344

0

µ

.

R7343

R7310

yf126_y30301001a_rev0.1

ONS".

(No.YF126)2-22

Page 24

MAIN(LCD_CTL) SCHEMATIC DIAGRAM

TO MONITOR (CN7601)

OPEN_SW

GND

GND

LCD_CTL

REG_4.8V

REG_4.8V

REG_3.2V

MONI_R

MONI_G

MONI_B

CN16

MAIN

10

(LCD_CTL)

LCD_CTL

OPEN_SW

SCK3

SCK3

SO3

S03

LCD_CSNCVDCVF

LCD_CS

VDCVF

HDCVF

HDCVF

HRP1

HRP1

DSP_RESTNCGND

DSP_REST

GND

GND

GND

GND

REV_SW

REV_SW

R7016 R7017

33K

33K

R7014

33K

R7012

C7011

15

33p

R7020

R7009

2.4k

C7010

15

33p

R7019

R7006

2.4k

Q7001 Q7002 Q7003

PUMX1-W PUMX1-W PUMX1-W

L7002

22µ

C7009

33p

R7003

2.4k

R7001

12k

15

R7018

C7006

1

C7007

1

R7015

R7013

1

C7008

R7011

R7010

R7008

R7007

R7005

R7004

R7002

C7002

C7001

C7005

0.01

C7004

0.1

C7003

10/16

33K

33K

33K

22K

8.2k

22K

8.2k

22K

8.2k

10k

0.1

4.7/25

L7001

22µ

OPEN_SW

LCD_CTL

REV_SW

SCK3

SO3

LCD_CS

SO3

SCK3

LCD_CS

TO CPU

LCD_CTL

OPEN_SW

TO CPU

TO CPU,DSP(VTR/CAM),

F/Z/ARIS,VTR ASP,TG_CDS

DSP_REST

REV_SW

TO CPU,DSP(VTR/CAM),

HDCVF

HRP1

VDCVF

HRP1

VDCVF

DSP_REST

HDCVF

TO DSP

(VTR/CAM)

BWVF_CTL

F/Z/ARIS,TG_CDS

TO DSP(VTR/CAM),

ROUT

TO DSP

GOUT

BOUT

(VTR/CAM)

GND

DAC_3.2V

REG_4.8V

REG_3.2V

REG_-15V

TO DSP(VTR/CAM),

V_OUT, BWVF_CTL

yf126_y30290001a_rev0.1

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

2-23(No.YF126)

Page 25

MAIN(SPEAKER) SCHEMATIC DIAGRAM

MAIN(SPEAKER)

10

TO VTR ASP

PA_SIG

TO SPEAKER

CN27

SPK-

SPK+

TO REG

REG_3.2V

L2401

NQR0006-001X

C2401

47

/4

C2404

0.1

R2403

10k

R2401

3.9k

R2402

3.3k

IC2401

NJM2149V-X

C2402

1.0

C2403

0.1

TO CPU

A_MUTE

GND

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

Q2401

DTC144EE

yf126_y40141001a_rev0.1

(No.YF126)2-24

Page 26

MAIN(JACK) SCHEMATIC DIAGRAM

MAIN(JACK)

10

J504

LY30041-001A

QNN0679-001A

AO_GND

AO_SIG

V_OUT

J505#

SC_OUT

SY_OUT

GND

TO VTR ASP

TO V_OUT

yf126_y30300001a_rev0.1

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

2-25(No.YF126)

Page 27

CCD SCHEMATIC DIAGRAM

CCD

20

R5304

0.1

C5304

#

IC5301

2200p

C5303

1MΩ

R5301

VO

H1

TO CN22

V4V3V2

H2

V1

GND

GND

GND

CCD_OUT

SUB

CCD_HV

C5302

C5307

C5301

RG

CCD_LV

2SC3931/CD/-X

Q5301

2.2µ

0.1

CN5301

QGF0505F1-14X

C5305

5.6k

R5302

C5306

/16v

yf126_y40142001a_rev0.1

NOTES :1. For the destination of each signal and further line connectionsthat are cut off from this diagram,

refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

3. IC5301 is incorporated in the CCD base assembly .

When IC5301 needs replacement, replace the CCD base assembly in whole because it cannot be replaced alone.

(No.YF126)2-26

Page 28

FRONT AND TOP SCHEMATIC DIAGRAMS

< with LED LIGHT MODEL >

FRONT

30

TO CN18

CN401

QGF0503F3-06X

KEY_A

REG_3.2V

GND

AL_L3.2V

LED_R

ST/EJ_SW

TO CN9

REG_4.8V

LED/LAMP

LED_2

40

TOP

R404

10k

NSPW500BS/CRS/

DI301

R401 R402 R403

1.5k 1.8k 2.7k

S401

NSW0198-001X

DI302

NSPW500BS/CRS/

S402

NSW0198-001X

yf126_y40145001a_rev0.1

S403

NSW0198-001X

DI401

SML-010LT-X

S404

NSW0198-001X

yf126_y40144001a_rev0.1

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

2-27(No.YF126)

Page 29

BWVF SCHEMATIC DIAGRAM

BWVF

50

TO MAIN

CN7401

TO BWVF

MODULE

CN7402

VEE

GND

VIDH

VDD

CK0

CK1

VSS

PDR

SLEEP

HS

VS

INV

VIDL

VF_BL

REG_4.8V

D7401

E1S35AW0C501-X

C7401

0.1µ

VEE

VIDH

VDD

CK0

CK1

VSS

PDR

SLEEP

HS

VS

RGT

INV

VIDL

TOUT

yf126_y40143001a_rev0.1

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

(No.YF126)2-28

Page 30

MONITOR SCHEMATIC DIAGRAM

MONITOR

70

TO CN16

BL_GND

BL_GND

LCD_CTL

REG_4.8V

REG_4.8V

VCC

MON_R

MON_G

MON_B

SCK3

SO3

LCD_CS

VDCVF

HDCVF

HRP1

DSP_REST

GND

GND

GND

GND

GND

RVS_SW

CN7601

NC

NC

NC

NMFZ007-R40X-K

!

F7501

C7620

NQL03BK-100X

L7502

C7504

NCB10JK-106X

R7602

C7601

Q7504

DTC144EE-X

R7601

L7603

10µ

Q7503

DTA144EE-X

R7501

1k

C7503

0.01µ

C7621 C7622

0.1µ

J7603

J7602

J7601

NQLZ010-680X

L7501

R7502

1k

R7503

1k

L7601

10µ

NBE20JM-106X

T

IC7604

DN8797MS-X

Q7502

0.1µ

NCB21EK-273X

C7502

Q7501

2SD1664/QR/-W2SD1664/QR/-W

C7605C7604

T

NBE20JM-106X

L7602

T7501

NQS0056-001X

R7603

C7614

10µ

R7604

NCZ1016-120X

C7501

J7501

J7502

C7602

C7603

R7605

1µ

C7606

C7607

T

C7609

C7612

10µ

T

0

C7608

R7606

C7610

C7611

C7613

C7615

C7616

C7617

C7618

C7619

1µ

1µ

1µ

TO

LCD_MODULE

CN7602

22µ

1µ

1µ

1µ

1µ

NC

NC

ADJ0

ADJ1

PVDD

NC

PGND

NC

VA

VB

VC

SCL

SDA

CSB

GRB

VSYNC

HSYNC

DFRP

AGND

NC

VCIOUT

VCC

NC

GND1

C1+

C1-

C12+

C12-

C8+

C8-

V3

C31+

C31-

APOL

VCAC

VGH

VGL

VGoffL

VGoffH

VCOMR

yf126_y30289001a_rev0.1

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

2-29(No.YF126)

Page 31

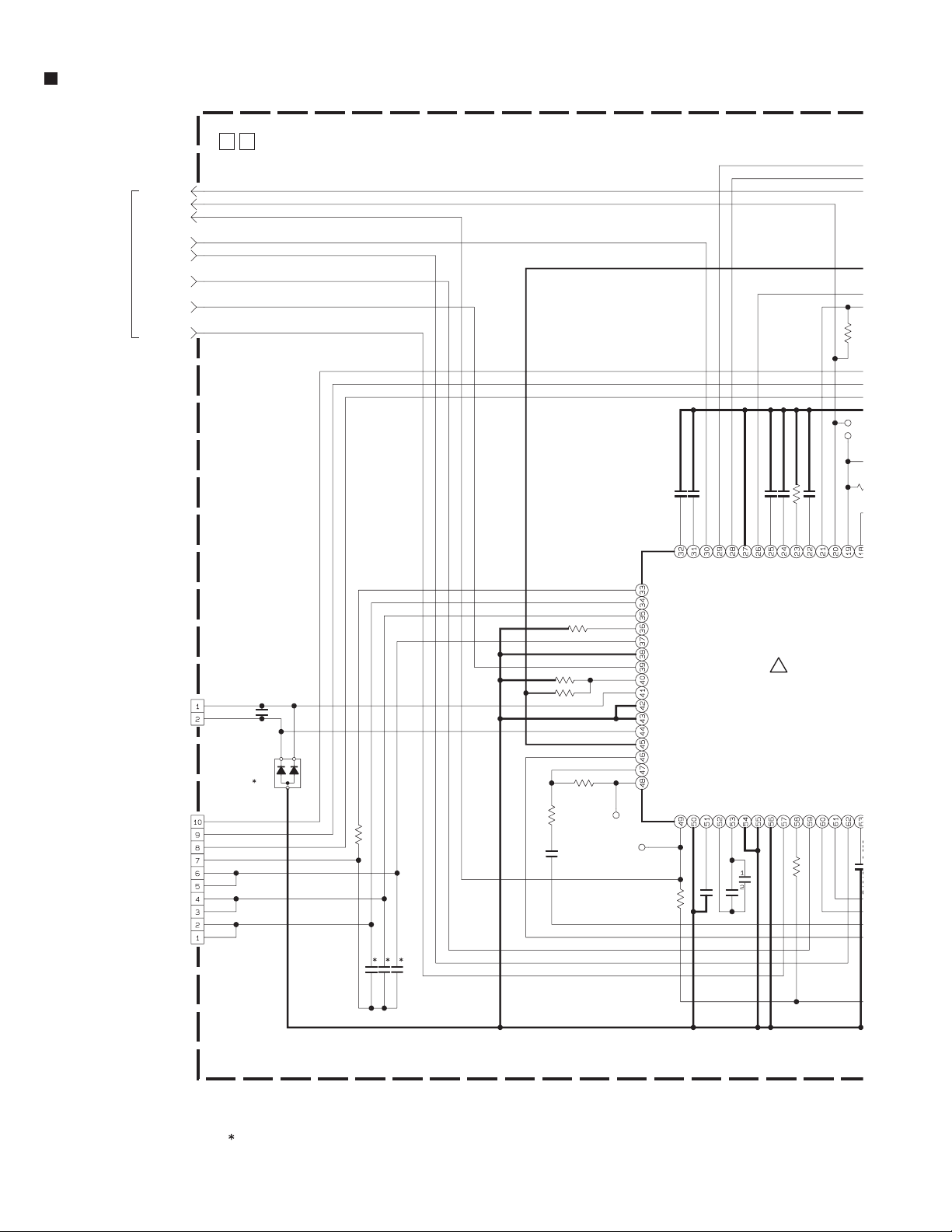

ZOOM UNIT AND SENSOR SCHEMATIC DIAGRAMS

-

ZOOM UNIT

DIAL MN

DIAL AT

DIAL OFF

DIAL PB

MENU SW

B_PHASE

A_PHASE

TRIG SW

FOCUS SW

PHOTO SW

GND

GND

ZOOM SW

REG 3.2V

ZOOM UNIT

-

14

13

12

11

9

8

7

10

6

5

1

2

3

4

DIAL SW

PHOTO

CCW CW

ON

B_PHASE

OFF

ON

A_PHASE

OFF

MULTI FUNCTION SW

FOCUS

<MULTI FUNCTION SW>

ENCODER OUTPUT

360270180900

TO CPU,

REG

- SENSOR -

EN_SENS

STR_SENS

GND

TAPE_LED

S_VHS_SW

TU_SENS

REEL_LED

SUP_SENS

CAS_SW

CAM_SW_B

CAM_SW_A

CAM_SW_C

GND

R_SAF_SW

1

2

3

4

5

6

7

8

9

10

11

12

13

14

SENSOR

FPC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

N.C

TAPE LED

N.C

.

N.C.

SW

CAM

SW

CAM

SW

CAM

GND

REC SAFE SW

FOR SVHS MODEL

S VHS SW

B

A

C

ROTARY ENCODER

yf126_ly10393002e_rev0.1

END SENSOR

CASS

TU SENSOR

2

1

3

4

SW

SUP

SENSOR

23

14

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram,

yf126_qsw1006001,2_rev0.1

refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

3. The schematic diagram is only for reference. Avoid replacing individual parts. Replace the entire unit only.

(No.YF126)2-30

Page 32

6

Q

MAIN CIRCUIT BOARD

<01>MAIN

LYB10022-001C FOIL SIDE(B)

C5211

C5212

C5213

L4501

R4513

C4512 R4524

IC1801

Q4251

C5209

33

R5203

R5204

R5206

R5205

R5208

48

C5217

C5201

C5215

L5201

R4507

38

1

C4502

C4503

C4504

C4505 C4506

R4508

C4507

R4509

C5214

R4504

R4214

32

49

R4205

C4205

IC4501

R4501

C4508

C5218

C4510

14

1

R4211

R4210

R5219

IC5201

R4503

R4502

L4201

C5219

C5207

R4506

20

19

IC4201

C4252

17

ZP-QFNIC5201

R5201

64

C4501

R4528

R4527

R7339

L4502

R4256

R4259

C4253

R4257

C4509

Q7303

8

7

16

1

R7341

R7340

R7342

Q7304

R167

R4252

R4251

R4254

R4255

R4253

F6302

C4254

R163

C7301

C4009

C4010

R4042

C4013

L2004

X4001

C4052

R4004

L4001

C4021

R5214

R7303

R4045

R4041

C4019

C4020

C4024

C2005

L2005

R4002

R7302

R4037

C4011

C4014

C4053

C4054

C4023

L2003

Q2007

R4003

C4031

C4015

C4016R4013

C4017

R4009

R4010

121

180

R2004

R2012

R2011

R4040

R4047

R2003

R2002

120

GLUE3-IC4001

GLUE4-IC4001

181

R4046

C2002

C2004

C2003

R2001

Q2001

L2001

R4036

23

C4051

IC4002

44

C4005

GLUE2-IC4001

GLUE1-IC4001

R4026

R4015

R2005

R4016

14

C2001

R2006

8

C4007

IC4001

1

IC2001

7

Q2008

R4017

22

C4050

C4044

C4006

1

61

TL

60

C4004

C4003

C4002

C4001

1

R4001

240

R7013

R7015

C7003

C7004

L1604

2-31(No.YF126)

R7017

F1601

C1621

F1602

C1620

L7002

C1615

C1629

R1614R1615

C1625

C1617

R1620

R1617

R1601

C1612

C1613

R1606

R1616

R1613

D1601

R1612

R1622

R1609

R1605

C1624

C1627

R1621

R1604

C1623

C1626

C1622

R1607

R1611

C1604

C1607

C1606

L2021

C2028

C2027

C2038

Q2021

Q2022

Q2023

R2031

C2022

R2024

C2025

C2026

R2025

C2035

C2024

C2036

R2028

C2033

C2071

R2023

L2022

R2030

C2023

R2027

R2022

C2039

C2032

C2021

L2023

C2034

R2071

C2031

R2021

C2040

Q2071

C1204

42

43

IC3501

56

1

C3506

Q3501

29

14

Q3502

R3508

C135

28

L3503

R3507

R3502

C351

C3507

C3508

Q3505

15

Page 33

S

IDE(B)

CAUTION :

FOR CONTINUED PROTECTION AGAINST FIRE HAZARD, REPLACE ONLY WITH SAME TYPE AND RATED FUSE(S).

ATTENTION :

POUR UNE PROTECTION PERMANENTE CONTRE LES RISQUE D'INCENDE,

!

REMPLACER LES FUSIBLES PAR UNAAUTRE DE MEME TYPE ET DE MEME TENSION.

R146

C132

C118