JRC NJG1707PG1 Datasheet

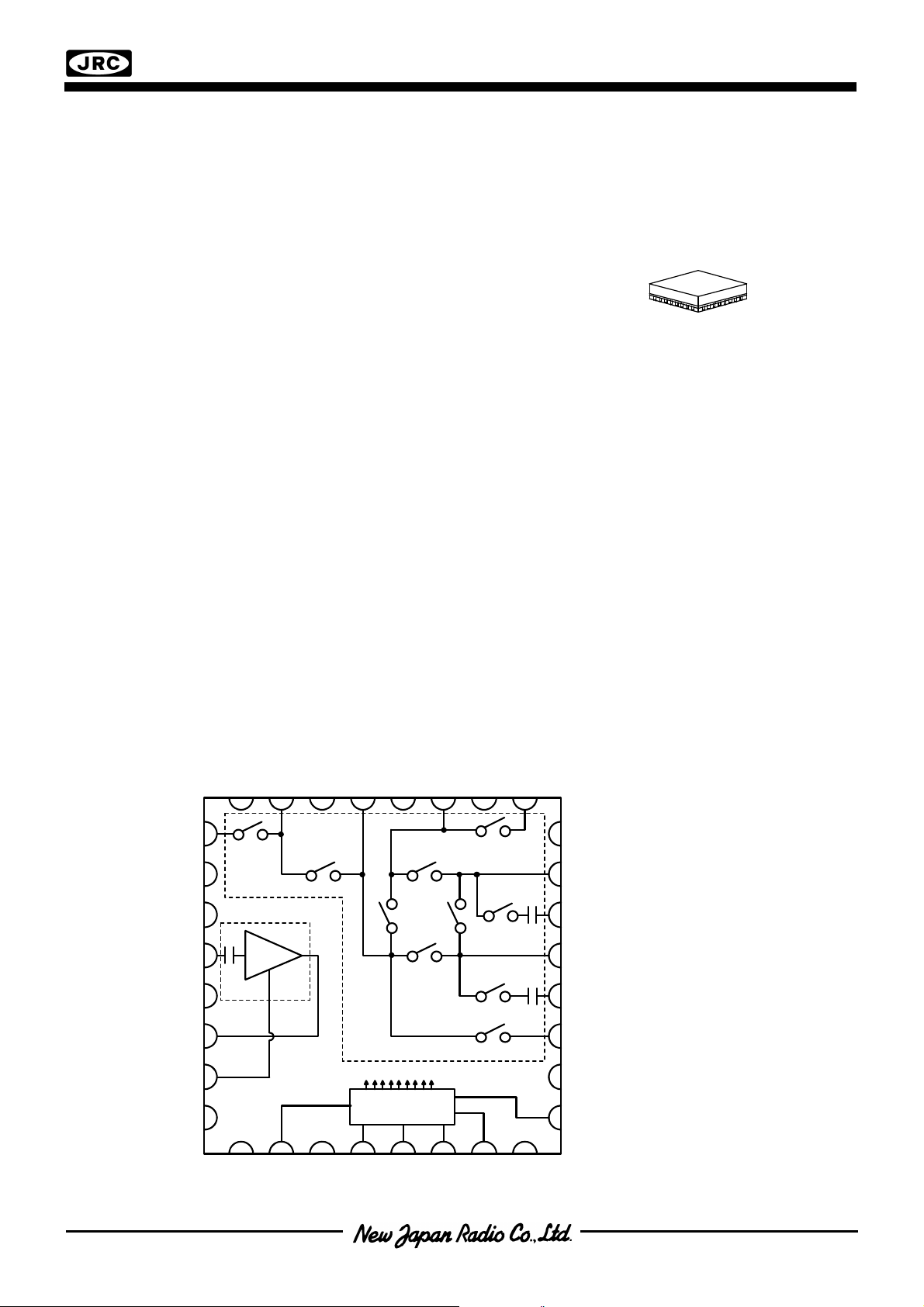

NJG1707PG1

800MHz TDMA FRONT-END GaAs MMIC

n

GENERAL DESCRIPTION

NJG1707PG1 is a front-end IC for a digital cellular phone of

800MHz band. A 2x6 antenna switches and a low noise

amplifier are included.

The parallel control signals of three bits logic connect T/R

circuits to internal two antennas or external two antennas. The

termination ports with external matching circuits make low

interference between diversity antennas.

The ultra small & thin FFP32-G1 package is adopted.

nFEATURES

•Ultra small & thin package FFP32-G1 (Mount Size: 4.5x4.5x0.85mm)

•Antenna Switch

lLow voltage operation -2.5V (Tx only) and +3.5V

lLow current consumption 10uA typ. (Tx Mode, P

=30dBm), 2uA typ. (Rx Mode, Pin=10dBm)

in

lLow insertion loss 0.5dB typ. @(Tx-ANT1, Tx-EXT1) f

lLow Adjacent Channel -63dBc typ. @ VDD=+3.5V, VSS=-2.5V, fin=960MHz, Pin=30dBm

Leakage Power

•Low Noise Amplifier

lLow voltage operation +2.7V typ.

lLow current consumption +2.7mA typ.

lSmall signal gain 17.5dB typ. @f=820MHz

lLow noise figure 1.4dB typ. @ f=820MHz

lHigh input IP3 IIP3=-4.5dBm typ. OIP3=+13dBm typ. @f=820MHz+820.1MHz

n

PACKAGE OUTLINE

NJG1707PG1

=960MHz, Pin=30dBm

in

n

PIN CONFIGURATION

TER1

25

GND(LNA)

GND(LNA)

LNAIN

LNAOUT

EXTCAP

GND

GND

26

27

28

29

30

31

32

FFP32 Type

(Top View)

GND

ANT2

2324

22

SW5

SW1

1

2 3 4 5 6 7

RX

GND

21

ANT-SW CONTROL VOLTAGE

ANT-SW

DECORDER

GND

SW4-1

SW3 SW7

SW4-2

ANT1

GND

SW 6

SW8

SW 9

SW 2

TER2

17181920

16

GND

TX

15

14

GND

13

EXT1

12

GND

11

EXT2

10

GND

9

VDD

8

GND

GND

GND

CTL1

CTL2

VSS

CTL3

GND

NJG1707PG1

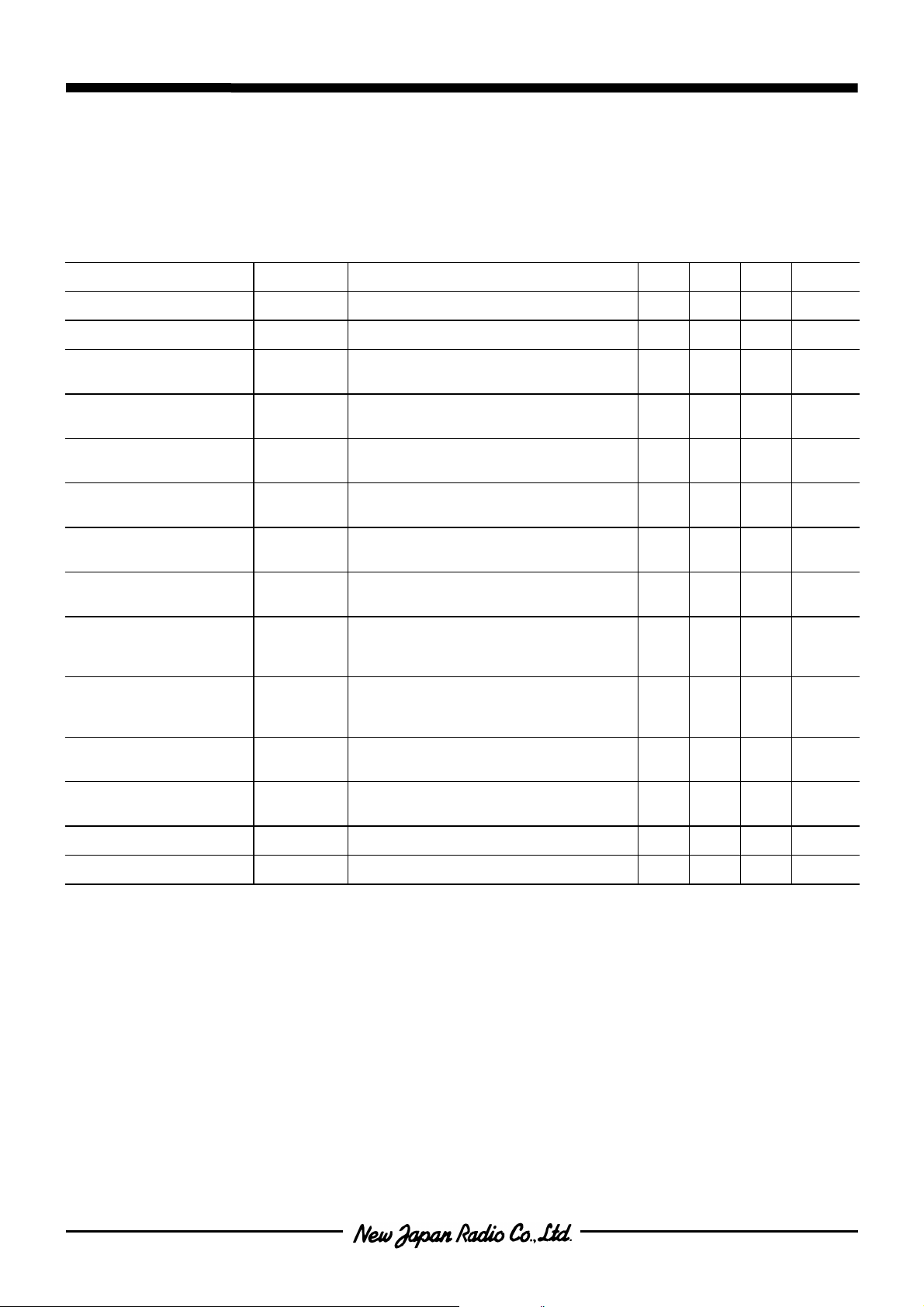

nABSOLUTE MAXIMUM RATINGS

Ta=25°C, VDD=3.5V, VSS=-2.5V

(Ta=25°C)

PARAMETER SYMBOL CONDTIONS RATINGS UNITS

Supply Voltage 1 V

Supply Voltage 2 V

Supply Voltage 3 V

Control Voltage V

DD1

DD2

SS

CTL

VDD Terminal 6.0 V

LNAOUT Terminal 5.0 V

VSS Terminal -4.0~+0.3 V

CTL1, CTL2, CTL3 Terminals 6.0 V

TX, ANT1, EXT1 Terminals 37 dBm

in

RX, ANT2, EXT2 Terminals 28 dBmInput Power P

LNAIN Terminal 10 dBm

Power Dissipation P

Operating

Temperature

Storage

Temperature

n

ELECTRICAL CHARACTERISTICS 1 [ANTENNA SWITCH DC CHARACTERISTICS]

D

T

opr

T

stg

600 mW

-40~+85 °C

-55~+125 °C

General Conditions:

TX, RX, ANT1, ANT2, EXT1, EXT2: terminated (50Ω)

TER1, TER2 : grounded by 10pF capacitor

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Positive Supply Voltage V

Negative Supply Voltage V

Current Consumption 1 I

Current Consumption 2 I

Current Consumption 3 I

Current Consumption 4 I

Control Voltage (H) V

Control Voltage (L) V

Control Current I

Control terminal Input

Impedance

* The voltage of this terminal should be supplied before or same time with other DC supplying

terminals. (CTL1~3, VSS).

DD

SS

DD1

SS1

DD2

SS2

CTL(H)

CTL(L)

CTL

R

in

VDD Terminal 2.7 3.5 5.0 V

VSS Terminal -3.5 -2.5 -2.0 V

VDD Terminal

Rx Mode, No RF Signal

VSS Terminal

Rx Mode, No RF Signal

VDD Terminal, fin=0.1~2GHz

Tx Mode, Pin=30dBm

VSS Terminal, fin=0.1~2GHz

Tx Mode, Pin=30dBm

- 2.0 5.0

-0.1 - 0 uA

- 10 30 uA

-30 -10 - uA

CTL1, CTL2, CTL3 Terminals 2.0 3.0 V

CTL1, CTL2, CTL3 Terminals 0 0 0.6 V

CTL1, CTL2, CTL3=V

or CTL1, CTL2, CTL3=0V

DD

-1.3 - 1.3 uA

CTL1, CTL2, CTL3 Terminals 4 - -

DD

µA

V

MΩ

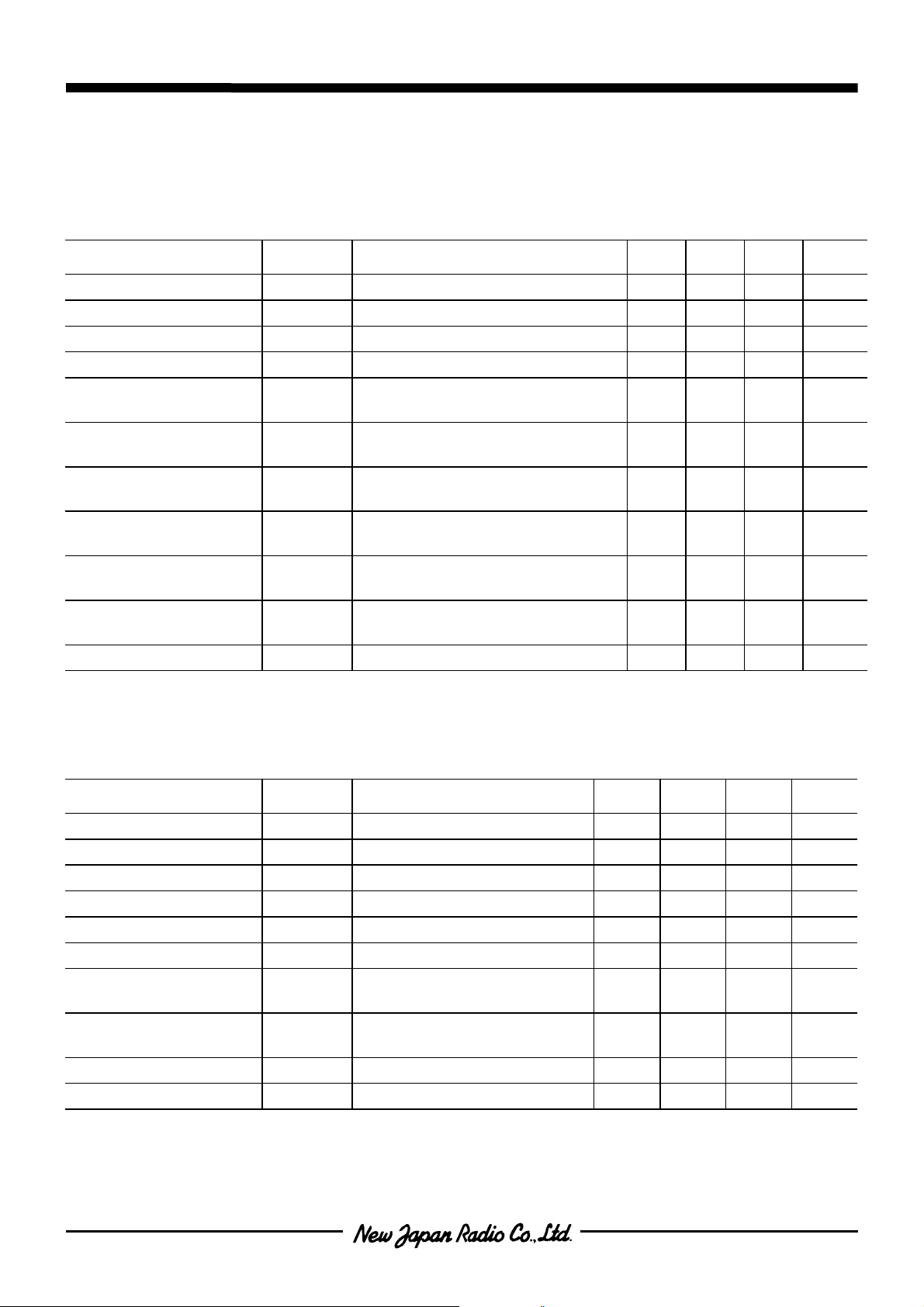

NJG1707PG1

n

Ta=25°C,VDD=3.5V,VSS=-2.5V, fin=885~940MHz

ELECTRICAL CHARACTRISTICS 2 [Tx Mode]

General Conditions:

Tested on PCB circuit as shown below.

Insertion loss of each connectors, striplines, and capacitors are excluded.

TX, RX, ANT1, ANT2, EXT1, EXT2: terminated (50Ω)

TER1, TER2: grounded by 10pF capacitor.

PARAMETER SYMBOL CONDITION MIN TYP MAX UNITS

Tx-ANT1 Insertion Loss LOSS1 Pin=30dBm - 0.50 0.65 dB

Tx-EXT1 Insertion Loss LOSS2 Pin=30dBm - 0.50 0.65 dB

Tx-Rx Isolation ISL1

Tx-ANT1 Isolation ISL2

Tx-ANT2 Isolation ISL3

Tx-EXT1 Isolation ISL4

Tx-EXT2 Isolation ISL5

Input Power at

0.5dB Compression 1

Adjacent Channel

Leakage Power 1

Adjacent Channel

Leakage Power 2

P

-0.5dB

ACP1

ACP2

2nd Harmonics 1 2f0(1)

3rd Harmonics 1 3f0(1)

Pin=30dBm

Tx-ANT1, Tx-EXT1 passing

Pin=30dBm

Tx-EXT1 passing

Pin=30dBm

Tx-ANT1, Tx-EXT1 passing

Pin=30dBm

Tx-ANT1 passing

Pin=30dBm

Tx-ANT1,Tx-EXT1 passing

(1) Tx-ANT1,Tx-EXT1 passing 33 35 - dBm

24 27 - dB

22 25 - dB

33 38 - dB

21 24 - dB

32 37 - dB

PDC Standard, ±50kHz offset

Pin=30dBm

- -63 -60 dBc

Input Signal ACP=-64dBc @ 30dBm

PDC Standard, ±100kHz offset

Pin=30dBm

- -74 -70 dBc

Input Signal ACP=-76dBc @ 30dBm

Pin=30dBm

Input Signal 2nd Harmonics=-70dBc

Pin=30dBm

Input Signal 3rd Harmonics=-100dBc

- -65 -63 dBc

- -64 -62 dBc

VSWR 1 VSWR1 Tx-ANT1, Tx-EXT1 passing - 1.2 1.5

Switching Time 1 TD1 CTL1~3 - 120 500 nsec

NJG1707PG1

n

Ta=25°C, VDD=3.5V, VSS=0V, fin=810~885MHz

Ta=25°C, VDD=3.5V, VSS=0V, fin=820MHz

ELECTRICAL CHARACTRISTICS 3 [Rx Mode]

General Conditions:

Tested on PCB circuit as shown below.

Insertion loss of each connectors, striplines, and capacitors are excluded.

TX, RX, ANT1, ANT2, EXT1, EXT2: terminated (50Ω)

TER1, TER2: grounded by 10pF capacitor.

PARAMETER SYMBOL CONDITION MIN TYP MAX UNITS

Rx-ANT1 Insertion Loss LOSS3 Pin=10dBm - 0.65 0.80 dB

Rx-ANT2 Insertion Loss LOSS4 Pin=10dBm - 0.60 0.75 dB

Rx-EXT1 Insertion Loss LOSS5 Pin=10dBm - 0.70 0.85 dB

Rx-EXT2 Insertion Loss LOSS6 Pin=10dBm - 0.65 0.80 dB

Rx-ANT1 Isolation ISL6

Rx-ANT2 Isolation ISL7

Rx-EXT1 Isolation ISL8

Rx-EXT2 Isolation ISL9

Input Power at 1dB

Compression 1

P

-1dB

VSWR 2 VSWR2

Pin=10dBm

Rx-ANT2, Rx-EXT1, Rx-EXT2 passing

Pin=10dBm

Rx-ANT1, Rx-EXT1, Rx-EXT2 passing

Pin=10dBm

Rx-ANT1, Rx-ANT2, Rx-EXT2 passing

Pin=10dBm

Rx-ANT1, Rx-ANT2, Rx-EXT1 passing

Rx-ANT1, Rx-ANT2, Rx-EXT1, Rx-

(1)

EXT2 passing

RX-ANT1, RX-ANT2, RX-EXT1, RX-

EXT2 passing

22 26 - dB

24 30 - dB

22 26 - dB

22 26 - dB

21 26 - dBm

- 1.2 1.6

Switching Time 2 TD2 CTL1~3 - 120 500 nsec

n

ELECTRICAL CHARACTRISTICS 4 [LNA]

General Conditions:

Tested on PCB circuit as shown below.

PARAMETER SYMBOL CONDITION MIN TYP MAX UNITS

Operation Frequency f

RF

810 - 885 MHz

Drain Voltage VDD3 2.5 2.7 4.5 V

Current Consumption IDD3 No RF input - 2.7 3.6 mA

Small Signal Gain Gain 16.0 17.5 18.5 dB

Gain Flatness G

flat

fRF=810~885MHz - 0.5 1.0 dB

Noise Figure NF - 1.4 1.6 dB

Pout at 1dB Gain

Compression Point

Input 3rd order

Intercept Point

LNAIN Port VSWR VSWR

LNAOUT Port VSWR VSWR

P

(2) -3.0 +1.0 - dBm

-1dB

IIP3 -8.0 -4.5 - dBm

i

o

- 1.5 2.5

- 1.5 2.5

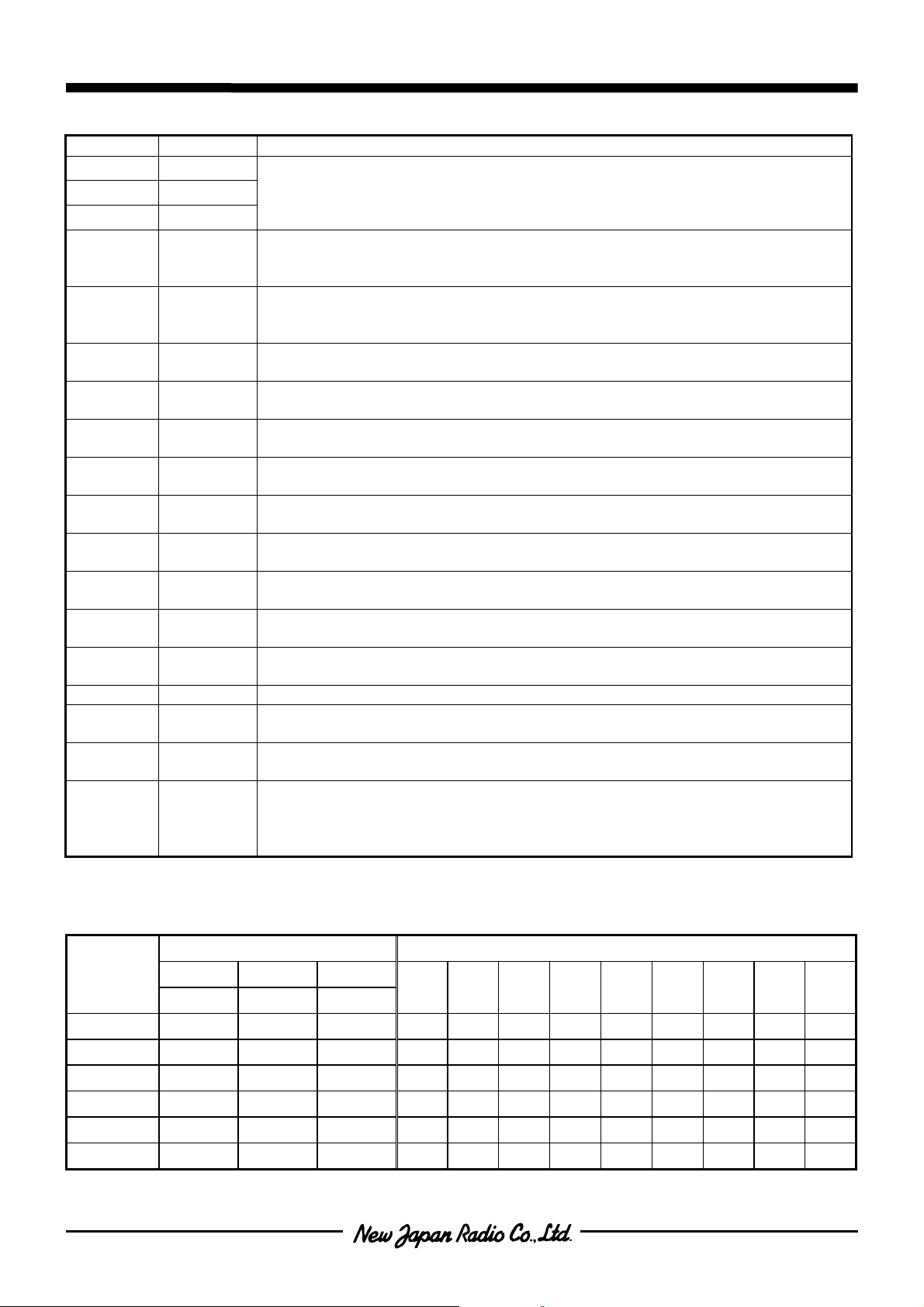

NJG1707PG1

n

DD

DD

DD

DD

TERMINAL INFORMATION

PIN NO. SYMBOL DESCRIPTIONS

4 CTL1

5 CTL2

6 CTL3

7 V

9 V

11 EXT2

13 EXT1

15 TX

17 TER2

19 ANT1

21 RX

23 ANT2

25 TER1

26,27 GND(LNA)

28 LNAIN LNA input terminal. An external matching circuit is required.

30 LNAOUT

31 EXTCAP

1,2,3,8,10,

12,14,16,1

8,20,22,24,

29,32

SS

DD

GND

Control signal input terminal of high impedance C-MOS logic. Logic level: High; more

than +2V, Low; 0~+0.6V. Please connect to GND or VDD with 100kΩ if potential is

open or uncertain.

Negative supply terminal. Negative voltage of -3.5~-2.0V must be supplied on Tx

mode. This terminal is isolated on Rx mode, so open or –2.5~0V condition can be

used. Please connect bypass capacitor with GND to keep RF performance.

Positive supply terminal. The voltage of this terminal should be supplied before or

same time with other DC supplying terminals (CTL1~3, VSS). The bias voltage should

be +2.7~+5.0V. Please connect bypass capacitor with GND to keep RF performance.

RF port for Rx signal. A DC cut capacitor (56pF~100pF) is required to block V

voltage.

RF port for Tx/Rx signal. A DC cut capacitor (56pF~100pF) is required to block V

voltage.

Tx power input terminal. A DC cut capacitor is required to block VDD voltage, and also

an external matching circuit is required to improve VSWR(See Application circuit).

A termination terminal for ANT1 in case ANT2 is in use. The influence of ANT1

against ANT2 is reduced. A DC cut capacitor (10pF) is required to block VDD voltage.

RF port for Tx/Rx signal. A DC cut capacitor (56pF~100pF) is required to block V

voltage.

Rx output terminal. A DC cut capacitor is required to block VDD voltage, and also an

external matching circuit is required to improve VSWR(See Application circuit).

RF port for Rx signal. A DC cut capacitor (56pF~100pF) is required to block V

voltage.

A termination terminal for ANT2 in case ANT1 is in use. The influence of ANT2

against ANT1 is reduced. A DC cut capacitor (10pF) is required to block VDD voltage.

Ground terminal of LNA. Please place ground plane close to this pin for good RF

performance.

LNA output terminal. An external matching circuit with LNA biasing element L3, L4 as

in application circuit is required.

Bypass capacitor terminal of LNA. Please place C9 as in application circuit close to

this terminal.

Ground terminal. Please connect to ground plane as close as possible for good RF

performance.

n

TRUTH TABLE

”H”=VCTL (H), ”L”=VCTL (L), ”X”=H or L

CONTROL INPUT CONTROL OUTPUT

Tx/Rx Diversity IN/OUTROUTE

SW1 SW2 SW3 SW4 SW5 SW6 SW7 SW8 SW9

CTL1 CTL2 CTL3

Tx-ANT1 H X H OFF OFF OFF ON ON OFF OFF OFF ON

Tx-EXT1 H X L OFF OFF ON OFF ON ON ON OFF OFF

Rx-ANT1 L L H OFF OFF ON OFF ON OFF ON ON ON

Rx-ANT2 L H H ON OFF OFF OFF OFF ON ON ON ON

Rx-EXT1 L L L OFF OFF OFF ON ON ON OFF ON OFF

Rx-EXT2 L H L OFF ON OFF OFF ON ON ON ON ON

NJG1707PG1

n

TYPICAL CHARACTERISTICS (ANTENNA SWITCH)

Measured on the PCB evaluation circuit, losses of circuits are eliminated.

ANT SW Loss,V.S.W.R vs. Frequency

0

-0.5

-1

Insertion Loss (dB)

-1.5

-2

500 600 700 800 900 1000

(Thru:TX-ANT1,VDD=3.5V,VSS=-2.5V)

Loss

V.S.W.R

Frequency (MHz)

ANT SW Loss,V.S.W.R vs. Frequency

0

-0.5

(Thru:RX-ANT1,VDD=3.5V,VSS=0V)

Loss

1.8

1.6

1.4

1.2

1

1.8

1.6

0

-0.5

-1

V.S.W.R

Insertion Loss (dB)

-1.5

-2

0

-0.5

ANT SW Loss,V.S.W.R vs. Frequency

(Thru:TX-EXT1,VDD=3.5V,VSS=-2.5V)

Loss

V.S.W.R

500 600 700 800 900 1000

Frequency (MHz)

ANT SW Loss,V.S.W.R vs. Frequency

(Thru:RX-ANT2,VDD=3.5V,VSS=0V)

Loss

1.8

1.6

1.4

V.S.W.R

1.2

1

1.8

1.6

-1

Insertion Loss (dB)

-1.5

-2

500 600 700 800 900 1000

V.S.W.R

Frequency (MHz)

ANT SW Loss,V.S.W.R vs. Frequency

0

-0.5

-1

Insertion Loss (dB)

-1.5

(Thru:RX-EXT1,VDD=3.5V,VSS=0V)

Loss

V.S.W.R

1.4

1.2

1

1.8

1.6

1.4

1.2

-1

V.S.W.R

Insertion Loss (dB)

-1.5

-2

0

-0.5

-1

V.S.W.R

Insertion Loss (dB)

-1.5

V.S.W.R

500 600 700 800 900 1000

Frequency (MHz)

ANT SW Loss,V.S.W.R vs. Frequency

(Thru:RX-EXT2,VDD=3.5V,VSS=0V)

Loss

V.S.W.R

1.4

V.S.W.R

1.2

1

1.8

1.6

1.4

V.S.W.R

1.2

-2

500 600 700 800 900 1000

Frequency (MHz)

1

-2

500 600 700 800 900 1000

Frequency (MHz)

1

Loading...

Loading...