INTERSIL ISL6225 Datasheet

®

N

R

O

F

D

E

D

N

E

M

T

O

N

R

M

M

O

C

E

L

S

I

D

E

Data Sheet December 28, 2004 FN9049.7

D

N

E

O

7

2

2

6

M

O

C

E

R

A

L

P

E

R

R

5

6

L

S

I

E

D

W

E

E

M

E

C

9

3

S

N

G

I

S

:

T

N

ISL6225

Dual Mobile-Friendly PWM Controller with

DDR Memory Option

The ISL6225 dual PWM controller delivers high efficiency and

tight regulation from two voltage regulating synchronous buck

DC/DC converters. The ISL6225 PWM power supply controller

was designed especially for DDR DRAM, SDRAM, and graphic

chipset applications in high performance desknote PCs,

notebook PCs, sub-notebook PCs, and PDAs.

Automatic mode selection of constant-frequency synchronous

rectification at heavy load, and hysteretic diode-emulation at

light load, assure high efficiency over a wide range of

conditions. The hysteretic mode of operation can be disabled

separately on each PWM converter if constant-frequency

continuous-conduction operation is desired for all load levels.

Efficiency is further enhanced by using the lower MOSFET

r

as the current sense element.

DS(ON)

Voltage-feed-forward ramp modulation, average current mode

control, and internal feedback compensation provide fast

response to input voltage and output load transients. Input

current ripple is minimized by channel to channel PWM

phase shift of 0°, 90°, or 180° determined by input voltage

and status of the DDR pin.

The ISL6225 can control two independent output voltages

adjustable from 0.9V to 5.5V or, by activating the DDR pin,

transform into a complete DDR memory power supply

solution. In DDR mode, CH2 output voltage VTT tracks CH1

output voltage VDDQ. CH2 output can both source and sink

current, an essential power supply feature for DDR memory

systems. The reference voltage VREF required by DDR

memory is generated as well.

Features

• Provides regulated output voltage in the range of 0.9V-5.5V

- High efficiency over wide load range

- Synchronous buck converter with hysteretic operation at

light load

- Inhibit Hysteretic mode on one, or both channels

• Complete DDR memory power solution

- VTT tracks VDDQ/2

- VDDQ/2 buffered reference output

• No current-sense resistor required

- Uses MOSFET r

- Optional current-sense resistor for precision overcurrent

• Under-voltage lock-out on V

• Dual input voltage mode operation

- Operates directly from battery 5V to 24V input

- Operates from 3.3V or 5V system rail

- VCC from 5V only

• Excellent dynamic response

- Combined voltage feed-forward and average current

mode control

• Power-good signal for each channel

• 300kHz switching frequency

- 180° channel to channel phase operation for reduced input

ripple when not in DDR mode

- 0° channel to channel phase operation in DDR mode for

reduced channel interference

- 90° channel to channel phase operation for reduced input

ripple in DDR mode when VIN is at GND.

• Pb-Free Available (RoHS Compliant)

DS(ON)

CC

pin

In dual power supply applications the ISL6225 monitors the

output voltage of both CH1 and CH2. An independent

PGOOD (power good) signal is asserted for each channel

after the soft-start sequence has completed, and the output

voltage is within ±10% of the set point. In DDR mode CH1

generates the only PGOOD signal.

Built-in overvoltage protection prevents the output from

going above 115% of the set point by holding the lower

MOSFET on and the upper MOSFET off. When the output

voltage decays below the overvoltage threshold, normal

operation automatically resumes. Once the soft-start

sequence has completed, under-voltage protection may

latch the ISL6225 off if either output drops below 75% of its

set point value.

Adjustable overcurrent protection (OCP) monitors the

voltage drop across the r

more precise current-sensing is required, an external current

sense resistor may be used.

of the lower MOSFET. If

DS(ON)

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

Applications

•

Mobile PCs

•PDAs

• Hand-held portable instruments

Ordering Information

PKG.

PART NUMBER TEMP. (°C) PACKAGE

ISL6225CA -10 to 85 28 Ld SSOP M28.15

ISL6225CAZ (Note 1) -10 to 85 28 Ld SSOP (Pb-free) M28.15

ISL6225CAZA (Note 1) -10 to 85 28 Ld SSOP (Pb-free) M28.15

NOTES:

1. Intersil Pb-free products employ special Pb-free material sets; molding

compounds/die attach materials and 100% matte tin plate termination

finish, which are RoHS compliant and compatible with both SnPb and

Pb-free soldering operations. Intersil Pb-free products are MSL

classified at Pb-free peak reflow temperatures that meet or exceed

the Pb-free requirements of IPC/JEDEC J STD-020.

2. Add “-T” for Tape and Reel.

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright © Intersil Americas Inc. 2002-2004. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

DWG. #

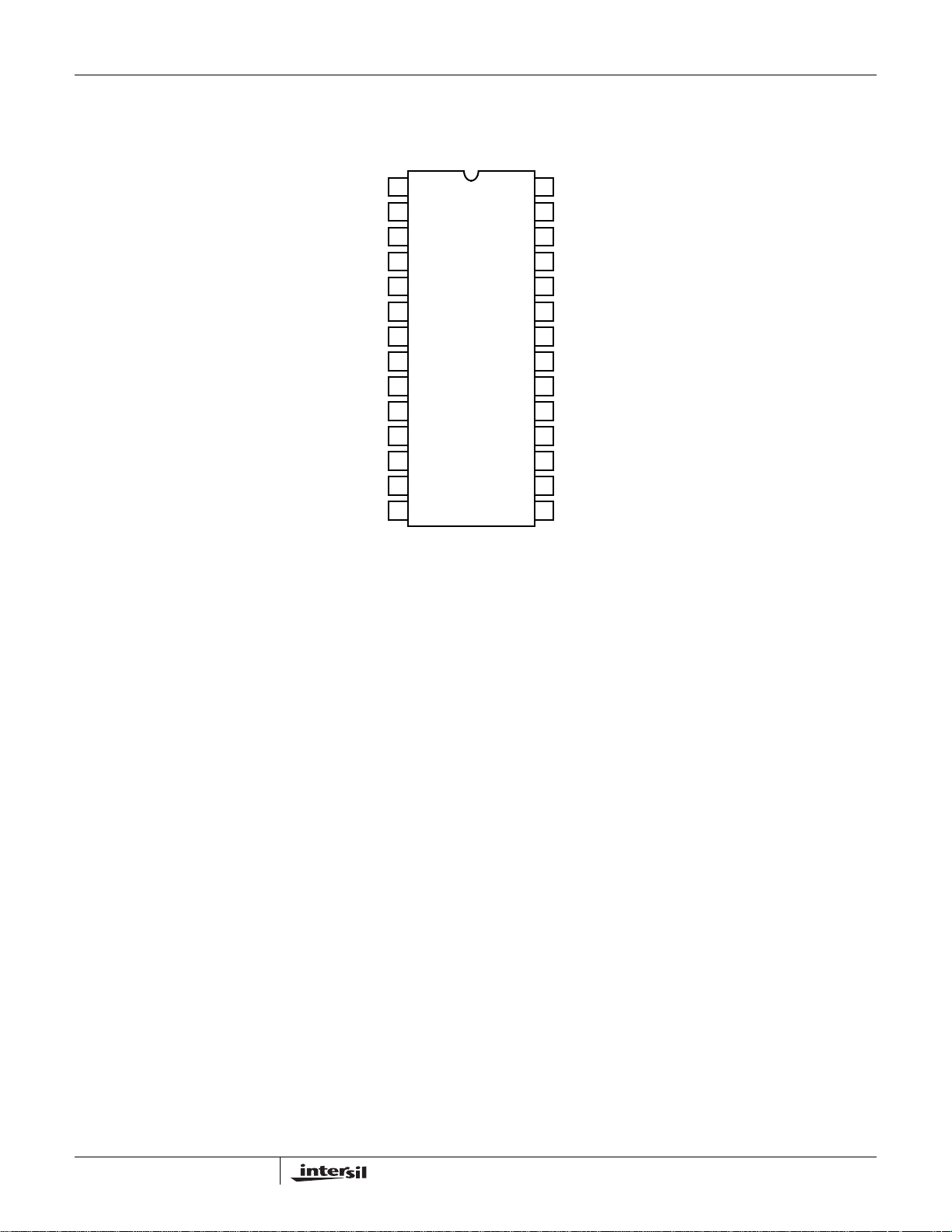

ISL6225

Pinout

GND

LGATE1

PGND1

PHASE1

UGATE1

BOOT1

ISEN1

EN1

VOUT1

VSEN1

OCSET1

SOFT1

DDR

VIN

ISL6225

SSOP-28

TOP VIEW

VCC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

LGATE2

PGND2

PHASE2

UGATE2

BOOT2

ISEN2

EN2

VOUT2

VSEN2

OCSET2

SOFT2

PG2/REF

PG1

2

FN9049.7

December 28, 2004

ISL6225

Absolute Maximum Ratings Thermal Information

Bias Voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+ 6.5V

Input Voltage, V

PHASE, UGATE Voltage . . . . . . . . . . . . . . GND-5V (Note 3) to 33V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +27.0V

IN

BOOT, ISEN Voltage . . . . . . . . . . . . . . . . . . . . GND-0.3V to +33.0V

BOOT with respect to PHASE . . . . . . . . . . . . . . . . . . . . . . . . .+ 6.5V

All Other Pins. . . . . . . . . . . . . . . . . . . . . . GND -0.3V to V

CC

+ 0.3V

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Class 2

Recommended Operating Conditions

Bias Voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +5.0V ±5%

Input Voltage, V

Ambient Temperature Range. . . . . . . . . . . . . . . . . . . . -10°C to 85°C

. . . . . . . . . . . . . . . . . . . . . . . . . . . +5.0V to +24.0V

IN

Junction Temperature Range. . . . . . . . . . . . . . . . . . . -10°C to 125°C

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

3. 200ns transient.

is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

4. θ

JA

Electrical Specifications Recommended Operating Conditions, Unless Otherwise Noted.

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

V

SUPPLY

CC

Bias Current I

Shut-down Current I

UVLO

V

CC

Rising V

Falling V

V

IN

Threshold V

CC

Threshold V

CC

Input Voltage Pin Current (Sink) I

Input Voltage Pin Current (Source) I

Shut-down Current I

CC

CCSN

CCU

CCD

VIN

VINO

VINS

OSCILLATOR

PWM1 Oscillator Frequency F

Ramp Amplitude, pk-pk V

Ramp Amplitude, pk-pk V

Ramp Offset V

Ramp/V

Ramp/V

Gain G

IN

Gain G

IN

ROFF

RB1

RB2

REFERENCE AND SOFT-START

Internal Reference Voltage V

REF

Reference Voltage Accuracy -1.0 - +1.0 %

Soft-Start Current During Start-up I

SOFT

Soft-Start Complete Threshold V

LGATEx, UGATEx Open, VSENx forced above

regulation point, DDR = 0, VIN > 5V

C

V

R1

R2

= 16V, by design - 2 - V

IN

V

= 5V, by design - 1.25 - V

IN

By design - 0.5 - V

V

≥ 3V, by design - 125 - mV/V

IN

1 ≤ V

IN

By design - 1.5 - V

ST

Thermal Resistance (Typical, Note 4)

θ

JA

(°C/W)

SSOP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Maximum Junction Temperature (Plastic Package) . . . . . . . . 150°C

Maximum Storage Temperature Range. . . . . . . . . . . -65°C to 150°C

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300°C

(SSOP - Lead Tips Only)

-2.23.2mA

--30µA

4.3 4.65 4.75 V

4.1 4.35 4.45 V

10 - 30 µA

--15-30 µA

--1µA

255 300 345 kHz

≤ 3V, by design - 250 - mV/V

-0.9- V

--5- µA

3

FN9049.7

December 28, 2004

ISL6225

Electrical Specifications Recommended Operating Conditions, Unless Otherwise Noted. (Continued)

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

PWM CONVERTERS

Load Regulation 0.0mA < I

VSEN pin bias current I

V

pin input impedance I

OUT

Undervoltage Shut-Down Level V

Overvoltage Shut-Down V

VSEN

VOUT

UVL

OVP1

By design 50 80 120 nA

V

= 5V 40 55 65 kΩ

OUT

Fraction of the set point; ~2µs noise filter 70 - 85 %

Fraction of the set point; ~2µs noise filter 110 - 130 %

GATE DRIVERS

Upper Drive Pull-Up Resistance R

Upper Drive Pull-Down Resistance R

Lower Drive Pull-Up Resistance R

Lower Drive Pull-Down Resistance R

2UGPUPVCC

2UGPDNVCC

2LGPUPVCC

2LGPDNVCC

= 4.5V - 8 15 Ω

= 4.5V - 3.2 5 Ω

= 4.5V - 8 15 Ω

= 4.5V - 1.8 3 Ω

POWER GOOD AND CONTROL FUNCTIONS

Power Good Lower Threshold V

Power Good Higher Threshold V

PGOODx Leakage Current I

PGOODx Voltage Low V

PG-

PG+

PGLKG

PGOODIPGOOD

Fraction of the set point; ~3µs noise filter -13 - -7 %

Fraction of the set point; ~3µs noise filter.

Guaranteed by design.

V

PULLUP

EN - Low (Off) --0.8V

EN - High (On) 2.5 - - V

CCM Enforced (Hysteretic Operation

VOUTX pulled low - - 0.1 V

Inhibited)

Automatic CCM/Hysteretic Operation Enabled VOUTX connected to the output 0.9 - - V

DDR - Low (Off) --0.8V

DDR - High (On) 2.5 - - V

DDR REF Output Voltage V

DDR REF Output Current I

DDREF

DDREF

DDR = 1, I

DDR = 1. Guaranteed by design. - 10 16 mA

< 5.0A; 5.0V < V

VOUT1

< 24.0V -2.0 - +2.0 %

BATT

12 - 16 %

= 5.5V - - 1 µA

= -4mA - 0.5 0.85 V

= 0...10mA 0.99*

REF

V

OC2

V

1.01*

OC2

V

OC2

V

4

FN9049.7

December 28, 2004

ISL6225

Functional Pin Description

GND (Pin 1)

Signal ground for the IC.

LGATE1, LGATE2 (Pin 2, 27)

These are outputs of the lower MOSFET drivers.

PGND1, PGND2 (Pin 3, 26)

These pins provide the return connection for lower gate

drivers. These pins are connected to sources of the lower

MOSFETs of their respective converters.

PHASE1, PHASE2 (Pin 4, 25)

The PHASE1 and PHASE2 points are the junction points of

the upper MOSFET sources, output filter inductors, and

lower MOSFET drains. Connect these pins to the respective

converter’s upper MOSFET source.

UGATE1, UGATE2 (Pin 5, 24)

These pins provide the gate drive for the upper MOSFETs.

BOOT1, BOOT2 (Pin 6, 23)

These pins power the upper MOSFET drivers of the PWM

converter. Connect this pin to the junction of the bootstrap

capacitor with the cathode of the bootstrap diode. Anode of

the bootstrap diode is connected to the VCC pin.

ISEN1, ISEN2 (Pin 7, 22)

These pins are used to monitor the voltage drop across the

lower MOSFET for current feedback and overcurrent

protection. For precise current detection these inputs can be

connected to the optional current sense resistors placed in

series with the source of the lower MOSFETs.

EN1, EN2 (Pin 8, 21)

These pins enable operation of the respective converter

when high. When both pins are low, the chip is disabled and

only low leakage current <1µA is taken from V

These pins are to be connected together and switched at the

same time.

VOUT1, VOUT2 (Pin 9, 20)

These pins when connected to the converters’ respective

outputs provide the output voltage inside the chip to reduce

output voltage excursion during HYS/PWM transition. When

connected to ground, these pins command forced

converters operate in continuous conduction mode at all

load levels.

VSEN1, VSEN2 (Pin 10, 19)

These pins are connected to the resistive dividers that set

the desired output voltage. The PGOOD, UVP, and OVP

circuits use this signal to report output voltage status.

and VIN.

CC

SOFT1, SOFT2 (Pin 12, 17)

These pins provide soft-start function for their respective

controllers. When the chip is enabled, the regulated 5µA

pull-up current source charges the capacitor connected from

the pin to ground. The output voltage of the converter follows

the ramping voltage on the SOFT pin.

DDR (Pin 13)

This pin, when high, transforms dual channel chip into

complete DDR memory solution. The OCSET2 pin becomes

an input to provide the required tracking function. The

channel synchronization is changed from out-of-phase to inphase. The PG2/REF pin becomes the output of the VDDQ/

2 buffered voltage that is used as a reference voltage by the

second channel.

VIN (Pin 14)

Provides battery voltage to the oscillator for feed-forward

rejection of the input voltage variation.

When connected to ground via 100kΩ resistor while the

DDR pin is high, this pin commands the out-of-phase 90

channels synchronization for reduced inter-channel

interference.

o

PG1 (Pin 15)

PGOOD1 is an open drain output used to indicate the status

of the output voltage. This pin is pulled low when the first

channel output is not within

±10% of the set value.

PG2/REF (Pin 16)

This pin has a double function depending on the mode the

chip is operating. When the chip is used as a dual channel

PWM controller (DDR = 0), the pin provides a PGOOD2

function for the second channel. The pin is pulled low when

the second channel output is not within

In DDR mode (DDR = 1), this pin serves as an output of the

buffer amplifier that provides VDDQ/2 reference voltage

applied to the OCSET2 pin.

±10% of the set value.

OCSET2 (Pin 18)

In a dual channel application (DDR = 0), a resistor from this

pin to ground sets the overcurrent threshold for the second

controller.

In the DDR application (DDR = 1), this pin sets the output

voltage of the buffer amplifier and the second controller and

should be connected to the center point of a divider from the

VDDQ output.

VCC (Pin 28)

This pin powers the controller.

OCSET1 (Pin 11)

A resistor from this pin to ground sets the overcurrent

threshold for the first controller.

5

FN9049.7

December 28, 2004

Generic Application Circuits

ISL6225

+V

+3.3V TO +24V

+V

IN

+3.3V TO +24V

ENABLE

IN

+5V

OCSET1

EN1

EN2

VCC

DDR

OCSET2

PWM1

PWM2

Q1

Q2

L1

C1

V

OUT1

+

Q3

Q4

L2

C2

+1.80V

V

OUT2

+1.20V

+

FIGURE 1. ISL6225 APPLICATION CIRCUIT FOR TWO CHANNEL POWER SUPPLY

ENABLE

+5V

OCSET1

EN1

EN2

VCC

DDR

PG2/VREF

PWM1

PWM2

Q1

Q2

OCSET2

L1

C1

VDDQ

+

Q3

Q4

L2

C2

+2.50V

VTT

+1.25V

+

VREF

+1.25V

FIGURE 2. ISL6225 APPLICATION CIRCUIT FOR COMPLETE DDR MEMORY POWER SUPPLY

6

FN9049.7

December 28, 2004

Loading...

Loading...