Page 1

Intel® Server Board SDS2

Technical Product Specification

Order Number: A85874-002

Revision 1.2

December 2, 2002

Enterprise Platforms and Services Marketing

Page 2

Revision History Intel® Server Board SDS2

Revision History

Date Revision

Number

9/20/2001 1.0 Initial release.

5/15/2002 1.1 Added Section 13: Errata. Corrected miscellaneous document errors.

Added Table 6.2.5.4: Baseboard Management Controller (BMC) Beep Code

Generation.

12/2/02 1.2 Added Errata 19-37 that are corrected with FAB5. Updated Table 6.2.5.4.

Added Table 25.

Modifications

Revision 1.2

ii

Order Number: A85874-002

Page 3

Intel® Server Board SDS2 Disclaimers

Disclaimers

Information in this document is provided in connection with Intel® products. No license, express

or implied, by estoppel or otherwise, to any intellectual property rights is granted by this

document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel

assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to

sale and/or use of Intel products including liability or warranties relating to fitness for a particular

purpose, merchantability, or infringement of any patent, copyright or other intellectual property

right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions

marked "reserved" or "undefined." Intel reserves these for future definition and shall have no

responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

This document contains information on products in the design phase of development. Do not

finalize a design with this information. Revised information will be published when the product is

available. Verify with your local sales office that you have the latest datasheet before finalizing a

design.

The Intel® Server Board SDS2 may contain design defects or errors known as errata which may

cause the product to deviate from published specifications. Current characterized errata are

available on request.

This document and the software described in it are furnished under license and may only be

used or copied in accordance with the terms of the license. The information in this manual is

furnished for informational use only, is subject to change without notice, and should not be

construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or

liability for any errors or inaccu racies that may appear in this document or any software that may

be provided in association with this document.

Except as permitted by such license, no part of this document may be reproduced, stored in a

retrieval system, or transmitted in any form or by any means without the express written consent

of Intel Corporation.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation.

*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2002.

Revision 1.2

Order Number: A85874-002

iii

Page 4

Table of Contents Intel® Server Board SDS2

iv

Table of Contents

1. Introduction .............................................................................................................................1

2. Architecture.............................................................................................................................2

3. Processor and Chipset..........................................................................................................4

3.1 Processors.........................................................................................................................4

3.1.1 Processor Voltage Regulator Module (VRM)................................................................6

3.2 Memory Subsystem............................................................................................................6

3.2.1 Memory Configuration...................................................................................................6

3.2.2 I2C Bus..........................................................................................................................8

3.3 Chipset................................................................................................................................8

3.3.1 CNB20HE-SL Champion North Bridge.........................................................................9

3.3.2 CIOB20 Champion I/O Bridge....................................................................................10

3.3.3 CSB5 South Bridge.....................................................................................................10

4. I/O Subsystem........................................................................................................................11

4.1 PCI Subsystem.................................................................................................................11

4.1.1 32-bit, 33-MHz PCI Subsystem ..................................................................................11

4.1.2 64-bit, 66-MHz PCI Subsystem ..................................................................................12

4.2 Ultra160 SCSI...................................................................................................................14

4.3 Video Controller................................................................................................................14

4.3.1 Video Modes................................................................................................................14

4.4 Network I nterface Controller (NIC)....................................................................................15

4.4.1 NIC Connector and Status LEDs................................................................................16

4.5 CSB5 South Bridge (PCI -to-LPC Bridge, IDE, USB).......................................................16

4.5.1 PCI Bus Interface........................................................................................................16

4.5.2 PCI Bus Master IDE Interface.....................................................................................16

4.5.3 USB Interface..............................................................................................................17

4.5.4 Compatibility Interrupt Control.....................................................................................17

4.5.5 APIC............................................................................................................................17

4.5.6 Power Management....................................................................................................17

4.5.7 General Purpose Input and Output Pins.....................................................................17

4.6 Chipset Support Components..........................................................................................18

4.6.1 Super I/O.....................................................................................................................18

Revision 1.2

Order Number: A85874-002

Page 5

Intel® Server Board SDS2 Table of Contents

v

4.6.2 BIOS Flash ..................................................................................................................20

4.7 Interrupt Routing...............................................................................................................20

4.7.1 Legacy Interrupt Routing.............................................................................................20

4.7.2 APIC Interrupt Routing................................................................................................21

4.7.3 Serialized IRQ Support...............................................................................................21

4.7.4 IRQ Scan for PCIIRQ..................................................................................................21

5. Server Management.............................................................................................................25

5.1 Sahalee Baseboard Management Controller...................................................................27

5.1.1 Fault Resilient Booting................................................................................................29

5.2 System Reset Control......................................................................................................30

5.2.1 Power-up Reset..........................................................................................................30

5.2.2 Hard Reset..................................................................................................................30

5.2.3 Soft Reset...................................................................................................................30

5.3 Intelligent Platform Management Buses...........................................................................30

5.4 Error Reporting.................................................................................................................32

5.4.1 Error Sources and Types ...........................................................................................32

5.4.2 PCI Bus Errors............................................................................................................32

5.4.3 Intel® Pentium® III Processor Bus Errors..................................................................32

5.4.4 Memory Bus Errors.....................................................................................................33

5.4.5 ID LED.........................................................................................................................33

5.5 ACPI..................................................................................................................................33

5.6 AC Link Mode....................................................................................................................33

6. BIOS........................................................................................................................................35

6.1 System BIOS....................................................................................................................35

6.2 BIOS Error Handling.........................................................................................................36

6.2.1 Error Sources and Types ...........................................................................................36

6.2.2 Handling and Logging System Errors.........................................................................36

6.2.3 SMI Handler.................................................................................................................38

6.2.4 Firmware (BMC).........................................................................................................39

6.2.5 Error Messages and Error Codes ..............................................................................45

6.3 Setup Utility.......................................................................................................................52

6.3.1 Configuration Utilities Overview..................................................................................52

6.3.2 Setup Utility Operation................................................................................................52

6.3.3 CMOS Memory Definition...........................................................................................67

Revision 1.2

Order Number: A85874-002

Page 6

Table of Contents Intel® Server Board SDS2

vi

6.3.4 Clearing CMOS...........................................................................................................67

6.4 Flash Update Utility...........................................................................................................67

6.4.1 Loading the System BIOS..........................................................................................67

6.4.2 User Binary Area.........................................................................................................68

6.4.3 Language Area............................................................................................................68

6.4.4 OEM Logo Screen......................................................................................................68

6.4.5 Recovery Mode...........................................................................................................68

7. Clock/Voltage Generation and Distribution ......................................................................70

7.1 Clock.................................................................................................................................70

7.2 Voltage..............................................................................................................................72

8. Connections ..........................................................................................................................74

8.1 Power Distribution Board Connector................................................................................74

8.2 Memory Module Connector...............................................................................................75

8.3 System Management Headers.........................................................................................76

8.3.1 ICMB Connector..........................................................................................................76

8.3.2 OEM IPMB Connector.................................................................................................76

8.3.3 SCSI HSBP (IPMB) Connector...................................................................................76

8.4 Front Panel Header...........................................................................................................77

8.5 PCI Slot Connector...........................................................................................................78

8.6 I/O Connectors.................................................................................................................80

8.6.1 VGA Connector...........................................................................................................80

8.6.2 SCSI Connector..........................................................................................................80

8.6.3 NIC Connectors..........................................................................................................81

8.6.4 IDE Connector............................................................................................................82

8.6.5 Universal Serial Bus (USB) Connectors.....................................................................82

8.6.6 Floppy Connector........................................................................................................83

8.6.7 Serial Port Connector.................................................................................................84

8.6.8 Parallel Port.................................................................................................................85

8.6.9 Keyboard and Mouse Connector................................................................................85

8.7 Miscellaneous Headers....................................................................................................86

8.7.1 Fan Headers...............................................................................................................86

8.7.2 Chassis Intrusion........................................................................................................86

8.7.3 External SCSI Activity LED Input Signal Connector...................................................86

8.8 Rear I/O Panel..................................................................................................................87

Revision 1.2

Order Number: A85874-002

Page 7

Intel® Server Board SDS2 Table of Contents

vii

8.9 Connector Manufacturers and Part Numbers..................................................................87

9. Jumpers..................................................................................................................................88

9.1 System Configuration Jumpers........................................................................................88

9.2 Performing CMOS Clear, BIOS Recovery, and BMC Force Update...............................92

9.2.1 Performing CMOS Clear.............................................................................................92

9.2.2 Performing BIOS Recovery Boot................................................................................92

9.2.3 Performing BMC Force Update..................................................................................93

10. Electrical and Thermal Specifications ...............................................................................94

10.1 Absolute Maximum Ratings...........................................................................................94

10.2 Power Consumption......................................................................................................94

10.3 Power Supply Specification...........................................................................................95

10.3.1 Power Timing............................................................................................................95

10.3.2 Voltage Recovery Timing Specifications...................................................................98

10.4 Estimateded Server Board MTBF...............................................................................100

11. Mechanical Specifications.................................................................................................101

12. Regulatory and Integration Information...........................................................................102

12.1 Regulatory Compliance...............................................................................................102

12.2 Installation Instructions................................................................................................103

12.2.1 Ensure EMC ............................................................................................................103

12.2.2 Ensure Host Computer and Accessory Module Certifications ...............................104

12.2.3 Prevent Power Supply Overload.............................................................................104

12.2.4 Place Battery Marking on Computer.......................................................................104

12.2.5 Use Only for Intended Applications .........................................................................105

12.2.6 Installation Precautions ...........................................................................................105

12.2.7 External ICMB Cable Information............................................................................105

13. Errata Listing.......................................................................................................................106

13.1 Summary Errata Table................................................................................................106

13.2 Errata...........................................................................................................................108

1. Intel® RAID controller SRCMR not yet supported with Intel® Server Board SDS2.......108

2. Intel® Server Board SDS2 BIOS update utility does not allow updates from a PXE

Server or from network drives ..................................................................................................108

3. Intel® Server Board SDS2 FRU/SDR update fails with console redirection enabled in

BIOS Setup...............................................................................................................................108

4. First characters and arrow keys not echoed with console redirection..........................109

Revision 1.2

Order Number: A85874-002

Page 8

Table of Contents Intel® Server Board SDS2

viii

5. Intel® & ICP Vortex* RAID Controllers will cause the Intel® Server Board SDS2 to halt

during POST when the BIOS Logo screen is enabled.............................................................109

6. Intel® Server Board SDS2 CD-ROM issues..................................................................110

7. NIC driver set 5.12 v.2.3.15 for UnixWare* 7.1.1 drops DPC LAN connection..............111

8. NIC driver set 5.12 v.5.41.27 for Microsoft* Windows* 2000 prevents a DPC LAN

connection when the operating system is loaded....................................................................111

9. Extended RAM Step disable option in BIOS Setup has no effect..................................112

10. High resolution video modes do not work correctly........................................................112

11. Lower performance with CAS Latency 2 memory.........................................................113

12. SDS2 reboots during POST with 4GB or more of total system memory installed........113

13. Novell NetWare* v. 6.0 does not install on SDS2...........................................................114

14. Adaptec* 2100S RAID controller causes system lockup and video blanking................114

15. SDS2 Build Your Own (BYO) Platform Confidence Test (PCT) v. 1.00 fails on the first

run 115

16. SDS2 0B71: System Temperature out of the range POST message...........................115

17. SDS2 0B75: System Voltage out of the range POST message....................................116

18. Miscellaneous numeric keys entered during POST enable PXE boot...........................116

19. SDS2 board level operating temperature and power supply voltage tolerance

modification...............................................................................................................................117

20. Recommendation for SDS2 rubber bumper installation................................................117

21. Keyboard and Mouse do not function under Microsoft* Windows* 2000 when legacy

USB is enabled in BIOS setup..................................................................................................119

22. Data miscompares when using Seagate* ATA III model ST310215A hard drives ........120

23. Boot to service partition via modem fails........................................................................120

24. Secondary IDE References Added To Documentation for FAB 5.................................120

25. Potential Mylex AcceleRAID 352 Adaptor Card Mechanical Interference at PCI Slot 6.120

26. Bootable CD will not boot if inserted during OPTION ROM scan..................................121

27. Swapping bootable for non-bootable CDROM during POST causes hang at boot.......121

28. OB P100 NICs do not show at POST but attempt PXE boot and appear in Boot Menu122

29. Dodson: Adaptec 39160 in slots 5 & 6 causes Expansion ROM error..........................122

30. Can Not Change BIOS SETUP IDE Options Using <Enter> Key..................................123

31. Minimum Wait Time Between Power Off and Power On via Front Panel Power Button Is

One Second..............................................................................................................................123

32. Unable to boot Netware 6.0 (NW6) From CD ROM With Adaptec Adaptor 2100S in Slot

6. 123

33. 3COM* 3C980C-TX NIC causes Microsoft* Windows* 2000 blue screen when greater

than 4GB of system memory is installed..................................................................................124

Revision 1.2

Order Number: A85874-002

Page 9

Intel® Server Board SDS2 Table of Contents

34. Peer-to-peer PCI transactions are not supported between the CIOB-controlled 64-bit

PCI bus and the legacy 32-bit PCI bus controlled by the HE-SL north bridge.........................125

35. SDS2 PCI slot current levels supported by the 5V rail...................................................125

36. OB P100 NICs do not show at POST but attempt PXE boot and appear in Boot Menu125

Glossary...........................................................................................................................................I

Reference Documents.................................................................................................................III

Index.............................................................................................................................................. IV

Revision 1.2

Order Number: A85874-002

ix

Page 10

List of Figures Intel® Server Board SDS2

List of Figures

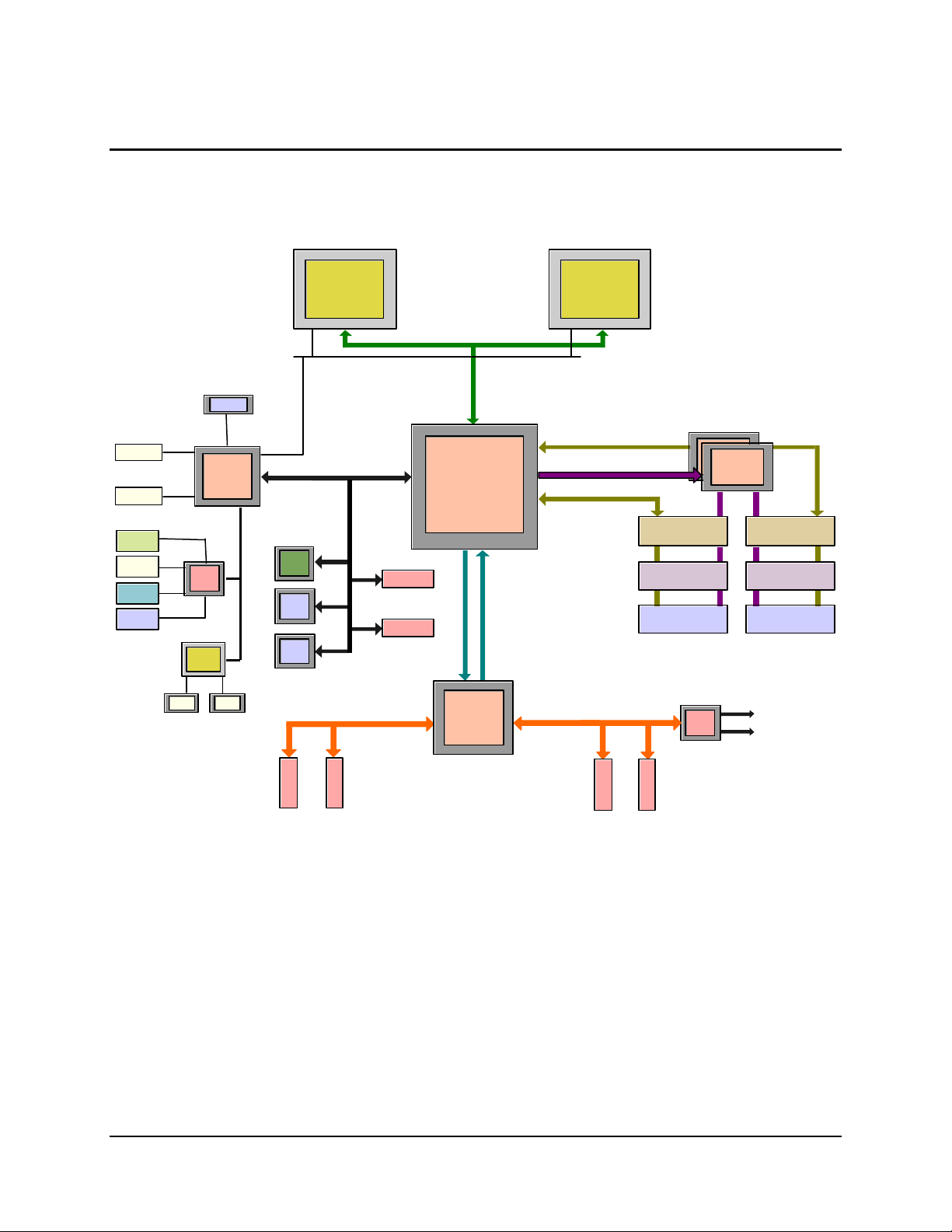

Figure 1. SDS2 Server Board Block Diagram.................................................................................1

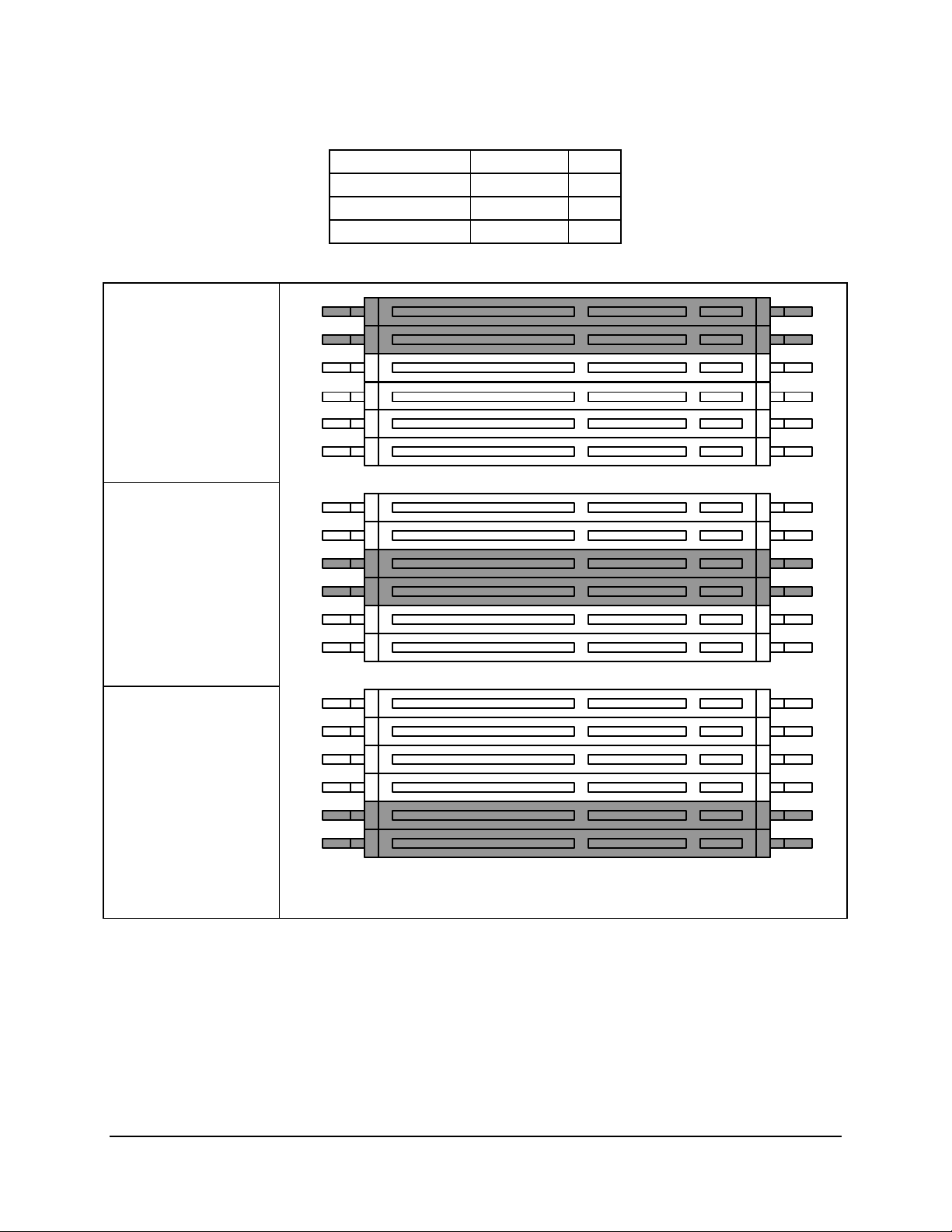

Figure 2. SDS2 Memory Bank Layout..............................................................................................7

Figure 3. SDS2 Interrupt Routing Diagram (CSB5 Internal)..........................................................22

Figure 4. SDS2 Interrupt Routing Diagram....................................................................................23

Figure 5. SDS2 PCI Interrupt Mapping Diagram............................................................................24

Figure 6. SDS2 Sahalee BMC Block Diagram (View as Reference Only)....................................26

Figure 7. SDS2 Locations of ADM1026 and Sahalee....................................................................29

Figure 8. SDS2 Server Board Clock Generation/Distribution Diagram.........................................71

Figure 9. SDS2 Server Board Voltage Generation/Distribution Diagram......................................73

Figure 10. SDS2 Server Board Rear I/O Panel.............................................................................87

Figure 11. SDS2 Configuration Jumpers.......................................................................................89

Figure 12. SDS2 Configuration Jumper Locations........................................................................90

Figure 13. Output Voltage Timing..................................................................................................97

Figure 14. Turn On/Off Timing.......................................................................................................98

Figure 15. SDS2 Server Board Mechanical Drawing..................................................................101

Revision 1.2

x

Order Number: A85874-002

Page 11

Intel® Server Board SDS2 List of Tables

List of Tables

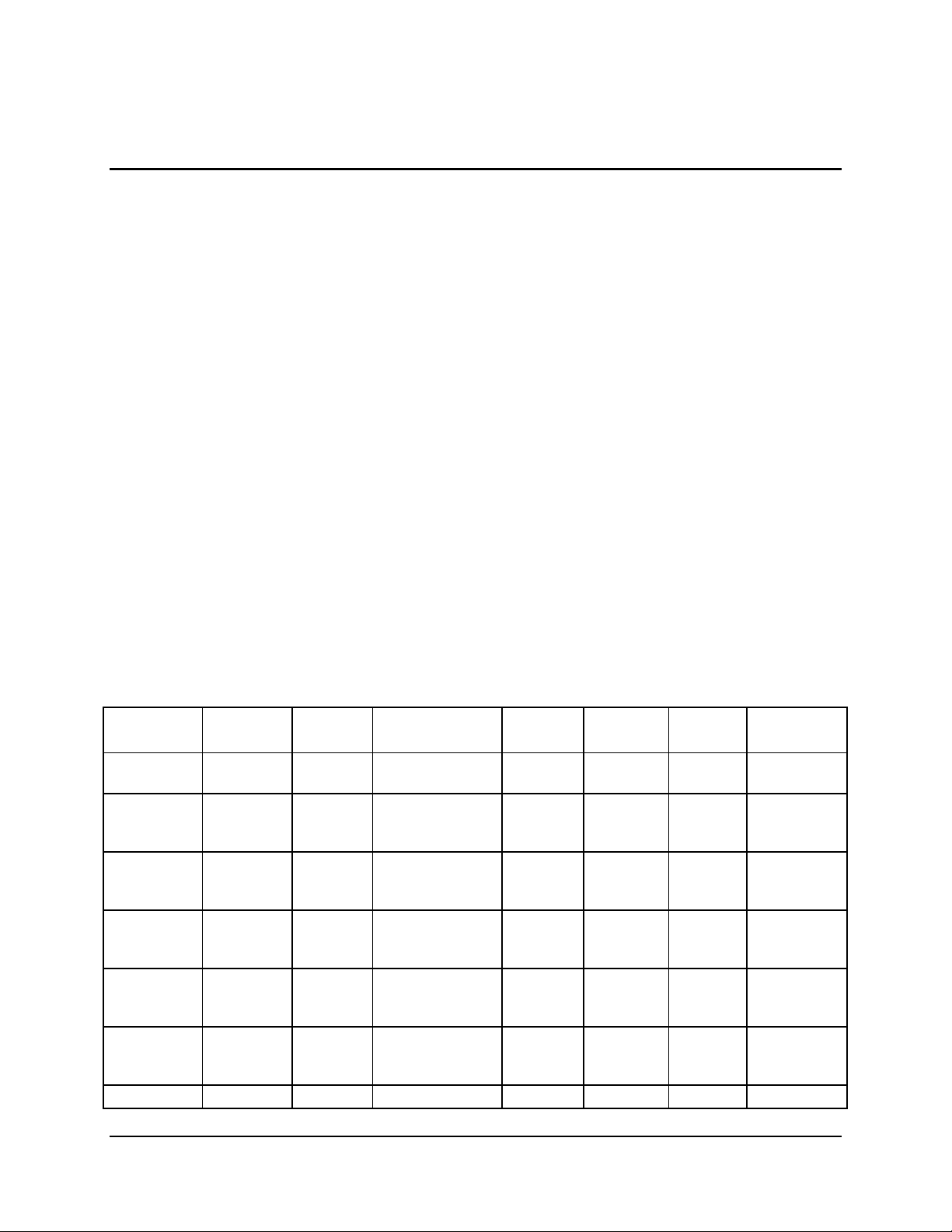

Table 1. SDS2 Intel® Pentium® III Processor Support Matrix.........................................................4

Table 2. Memory DIMM Pairs...........................................................................................................7

Table 3. I2C Addresses for DIMM Slots............................................................................................8

Table 4. PCI Bus Segment Characteristics...................................................................................11

Table 5. P32-A Configuration IDs...................................................................................................12

Table 6. P32-A Arbitration Connections.........................................................................................12

Table 7. P64-B Arbitration Connections.........................................................................................13

Table 8. P64-B Arbitration Connections.........................................................................................13

Table 9. Video Modes.....................................................................................................................15

Table 10. CSB5 GPIO Usage Table..............................................................................................17

Table 11. Super I/O GPIO Usage Table.........................................................................................18

Table 12. PCI Interrupt Routing/Sharing........................................................................................20

Table 13. Interrupt Definitions ........................................................................................................20

Table 14. ADM1026 Input Definition...............................................................................................27

Table 15. Temperature Sensors....................................................................................................28

Table 16. Sahalee Input Definition..................................................................................................28

Table 17. IPMB Bus Device s.........................................................................................................31

Table 18. Private I2C Bus 1 Devices..............................................................................................31

Table 19. Private I2C Bus 2 Devices..............................................................................................31

Table 20. Private I2C Bus 3 Devices..............................................................................................31

Table 21. Private I2C Bus 4 Devices..............................................................................................32

Table 22. BIOS Generated SEL Errors..........................................................................................37

Table 23: Event Request Message Event Data Field Contents ....................................................38

Table 24 Platform SEL Log Sensors for SDS2.............................................................................39

Table 25. Event Request Message Event Data Field Contents ....................................................45

Table 26. Port-80h Code Definition................................................................................................45

Table 27. Standard BIOS POST Codes........................................................................................46

Table 28. Recovery BIOS POST Codes .......................................................................................49

Table 29. POST Error Messages and Codes................................................................................50

Table 30. BMC Beep Codes ..........................................................................................................51

Table 31. Setup Utility Screen........................................................................................................52

Revision 1.2

Order Number: A85874-002

xi

Page 12

List of Tables Intel® Server Board SDS2

Table 32. Main Menu Selections ....................................................................................................55

Table 33. Primary Master and Slave IDE Submenu Selections....................................................56

Table 34. Processor Settings Submenu Selections......................................................................57

Table 35. Advanced Menu Selections............................................................................................58

Table 36. Memory Configuration Menu Selections ........................................................................58

Table 37. PCI Configuration Menu Selections ...............................................................................59

Table 38. On-board SCSI and LAN Submenu Selections.............................................................59

Table 39. On-board VGA Submenu Selections.............................................................................59

Table 40. PCI slot Submenu Selections........................................................................................59

Table 41. I/O Device/Peripheral Configuration Submenu Selections............................................61

Table 42. Advanced Chipset Controller Submenu Selections.......................................................62

Table 43. PCI Device Submenu Selections...................................................................................62

Table 44. Security Menu Selections...............................................................................................62

Table 45. Server Menu Selections.................................................................................................63

Table 46. System Management Submenu Selections ..................................................................64

Table 47. Console Redirection Submenu Selections....................................................................65

Table 48. Boot Device Priority Selections......................................................................................65

Table 49. Hard Drive Selections ....................................................................................................66

Table 50. Removable Drive Selections..........................................................................................66

Table 51. Exit Menu Selections......................................................................................................66

Table 52. 24-Pin Main Power Connector Pin-out...........................................................................74

Table 53. 8-Pin +12 V Power Connector Pin-out...........................................................................74

Table 54. Aux Signal Connector Pin-out........................................................................................74

Table 55. DIMM Connector Pin-out................................................................................................75

Table 56. ICMB Connector Pin-out................................................................................................76

Table 57. IPMB Connector Pin-out.................................................................................................76

Table 58. HSBP-A Connector Pin-out............................................................................................76

Table 59. HSBP-B Connector Pin-out...........................................................................................77

Table 60. Front Panel 34-Pin Header Pin-out................................................................................77

Table 61. 32-bit 5 V PCI Slot Pin-out..............................................................................................78

Table 62: 64-bit 3.3V PCI Slot Pin-out............................................................................................78

Table 63. VGA Connector Pin-out..................................................................................................80

Table 64. 68-pin SCSI Connector Pin-out......................................................................................80

Table 65. RJ -45 Connector Pin-out...............................................................................................81

Revision 1.2

xii

Order Number: A85874-002

Page 13

Intel® Server Board SDS2 List of Tables

Table 66. IDE 40-pin Connector Pin-out........................................................................................82

Table 67. Stacked Three-port USB Connector Pin-out.................................................................82

Table 68. 10-pin USB Connection Header (2 x 5) Pin-out.............................................................83

Table 69. 34-pin Floppy Connector Pin-out...................................................................................84

Table 70. DB9 Serial Port Pin-out..................................................................................................84

Table 71. 10-pin Header Serial Port Pin-out..................................................................................84

Table 72. DB25 Parallel Port Pin-out.............................................................................................85

Table 73. Keyboard and Mouse PS/2 Connector Pin-out..............................................................85

Table 74. Fan Header Pin-out........................................................................................................86

Table 75. Chassis Intrusion Header Pin-out..................................................................................86

Table 76. External Drive Activity Header Pin-out...........................................................................87

Table 77. Server Board Connector Manufacturer Part Numbers..................................................87

Table 78. System Configuration Jumper Options..........................................................................91

Table 79. CPU Frequency Select Jumper Options .......................................................................91

Table 80. List of Assembled Jumpers in Production.....................................................................92

Table 81. Absolute Maximum Ratings ...........................................................................................94

Table 82. SDS2 Server Board Power Consumption.....................................................................95

Table 83: SDS2 Power Supply Specification.................................................................................95

Table 84: Voltage Timing Parameters...........................................................................................95

Table 85: Turn On/Off Timing........................................................................................................97

Table 86. Transient Load Requirements .......................................................................................99

Table 87. Estimated SDS2 Server Board MTBF.........................................................................100

Table 88. Safety Regulations.......................................................................................................102

Table 89. EMC Regulations .........................................................................................................102

Table 90. ICMB External Cable Connectors................................................................................105

Table 91. Errata Summary ...........................................................................................................106

Revision 1.2

Order Number: A85874-002

xiii

Page 14

List of Tables Intel® Server Board SDS2

v

< This page intentionally left blank. >

Revision 1.2

xi

Order Number: A85874-002

Page 15

Intel® Server Board SDS2 Introduction

PCI

Slot

Slot

PCI

Slot

Slot

1. Introduction

This chapter provides an architectural overview of the Intel® SDS2 Server Board. It provides a

view of the functional blocks and their electrical relationships. The figure below shows the

functional blocks of the Server Board and the plug-in modules that it supports.

CPU 1

Front Side Bus (133MHz)

APIC Bus

FLASH

CPU 2

IDE Pri

USB x 4

Floppy

Keyboard

Mouse

COM1

COM2

Parallel

Port

CSB5

LPC

Bus

SIO

BMC

FLASH SRAM

DATA Bus (133MHz)

PCI 32-bit Bus (33MH z, 5V)

VIDEO

NIC 1

NIC 2

PCI 64 -bit Bus (66MHz, 3.3V)

PCI

1

2

PCI Slot 3

PCI Slot 4

HE-SL

(2 x

133MHz)

IMBus

CIOB

ADD/CTRL Bus (133MHz)

DATA Bus (133MHz)

PCI 64-bit Bus (66MHz, 3.3V)

Figure 1. SDS2 Server Board Block Diagram

BANK 1

BANK 2

BANK 3

PCI

5

Registers

Registers

DIMM

DIMM

DIMM

SCSI

6

DIMM

DIMM

DIMM

Channel A

Channel B

Revision 1.2

1

Order Number: A85874-002

Page 16

Architecture Intel® Server Board SDS2

2. Architecture

The SDS2 Server Board is a monolithic printed circuit board that can accept two Intel® Pentium®

III processors using the Socket 370 FCPGA2 package. The SDS2 Server Board complies with

the Entry SSI version 1.0 and ATX version 2.03 (12 inch x 13 inch) form-factor. It is designed

around the Server Works* ServerSet* III HE-SL chipset.

The chipset contains three components:

• The HE-SL CNB20 North Bridge provides an integrated memory controller

• The CIOB20 I/O Bridge provides the interface for two peer 64-bit, 66 MHz PCI busses

• The CSB5 South Bridge provides the LPC bus for legacy support.

The Server Board also contains other embedded devices such as:

• 2D/3D graphics accelerator

• Two 10/100 Network Interface Controller

• Dual channel Ultra160 SCSI

• Standard I/O

• Server management

The SDS2 Server Board provides six DIMM sockets for a maximum memory capacity of 6 GB.

Only registered PC-133 compliant Registered SDRAM memory modules are supported. The

current tested memory listing is posted on the Intel technical support web site:

http://support.intel.com/support/motherboards/server/SDS2/

The SDS2 Server Board provides the following features:

• Dual Intel

• Server Works ServerSet III HE-SL chipset

®

Pentium® III FCPGA2 processors (Socket370)

- HE-SL North Bridge

- CIOB20 I/O Bridge

- CSB5 South Bridge

• Support for six PC-133 compliant registered ECC SDRAM memory modules

• 32-bit, 33-MHz 5 V Full-length PCI segment A (P32-A) with three embedded devices

- 2D/3D Graphics Controller: ATI* RAGE* XL Video Controller with 4MB of SDRAM

- Two Network Interface Controller: Intel 82550 Fast Ethernet Controller

- Two 32-bit Slots: PCI Slots 3 and 4

• 64-bit, 66-MHz 3.3 V full-length PCI segment B (P64-B)

- Two 64-bit Slots: PCI slots 1 and 2

Revision 1.2

2

Order Number: A85874-002

Page 17

Intel® Server Board SDS2 Architecture

• 64-bit, 66-MHz 3.3 V full-length PCI segment C (P64-C) with one embedded device

- Dual Channel Wide Ultra160 SCSI controller: Adaptec* AIC-7899W

- Two 64-bit 3.3 V Slots: PCI slots 5 and 6

• LPC (Low Pin Count) bus segment with two embedded devices

- Baseboard Management Controller (BMC) providing monitoring, alerting, and logging

of critical system information obtained from embedded sensors on the Server Board

- Super I/O controller chip providing all PC-compatible I/O (floppy, serial, keyboard,

mouse)

• X-Bus segment from CSB5 with one embedded device

- Flash ROM device for system BIOS: Fairchild* 29LV008B 8Mbit Flash ROM

• Two IDE connectors, supporting up to two ATA -100 compatible devices each. Note: Fab

4 board PBA A58285-402 and –403 supported only one IDE connector. Fab 5 PBA

A58285-502 (and later revisions) supports two IDE connectors.

• Four Universal Serial Bus (USB) ports: Three on the rear I/O and one on the Server

Board as a 10-pin header

• Two serial ports: One out to rear I/O and one through a 10-pin header on the Server

Board

• One floppy connector

• Four multi speed system fan connectors and two single speed CPU fan connectors.

• 34-pin SSI compliant front panel connector

Revision 1.2

Order Number: A85874-002

3

Page 18

Processor and Chipset Intel® Server Board SDS2

3. Processor and Chipset

The Server Works* ServerSet III HE-SL chipset provides the 36-bit address, 72-bit data (64-bit

data + 8-bit ECC) processor host bus interface , operating at 133 MHz in the AGTL signaling

environment. The HE-SL North Bridge provides an integrated memory controller, the interface to

32-bit, 33-MHz Rev 2.2 compliant PCI bus, and two Inter-Module Bus interfaces. The InterModule Bus (IMB) provides the interface to two 64-bit, 66-MHz Rev 2.2 compliant PCI buses via

the CIOB20.

The SDS2 DP Server Board direct ly supports up to 6 GB of ECC memory, using six PC-133compliant registered SDRAM DIMMs. The ECC implementation in the HE-SL can detect and

correct single-bit errors, and it can detect multiple-bit errors.

3.1 Processors

The SDS2 Server Board supports two Intel® Pentium® III processors in the Socket 370 FCPGA2

package. If two processors are installed, both processors must be of identical revisions with the

same core voltage and speed for the bus and core. If one processor is installed, an AGTL

terminator module must be installed in the other socket. The support circuitry on the Server

Board consists of the following:

• Dual Socket 370 FCPGA2 processor sockets supporting 133-MHz FSB (if using one

processor, an AGTL terminator module goes in the empty socket)

• Processor host bus AGTL support circuitry, including termination power supply

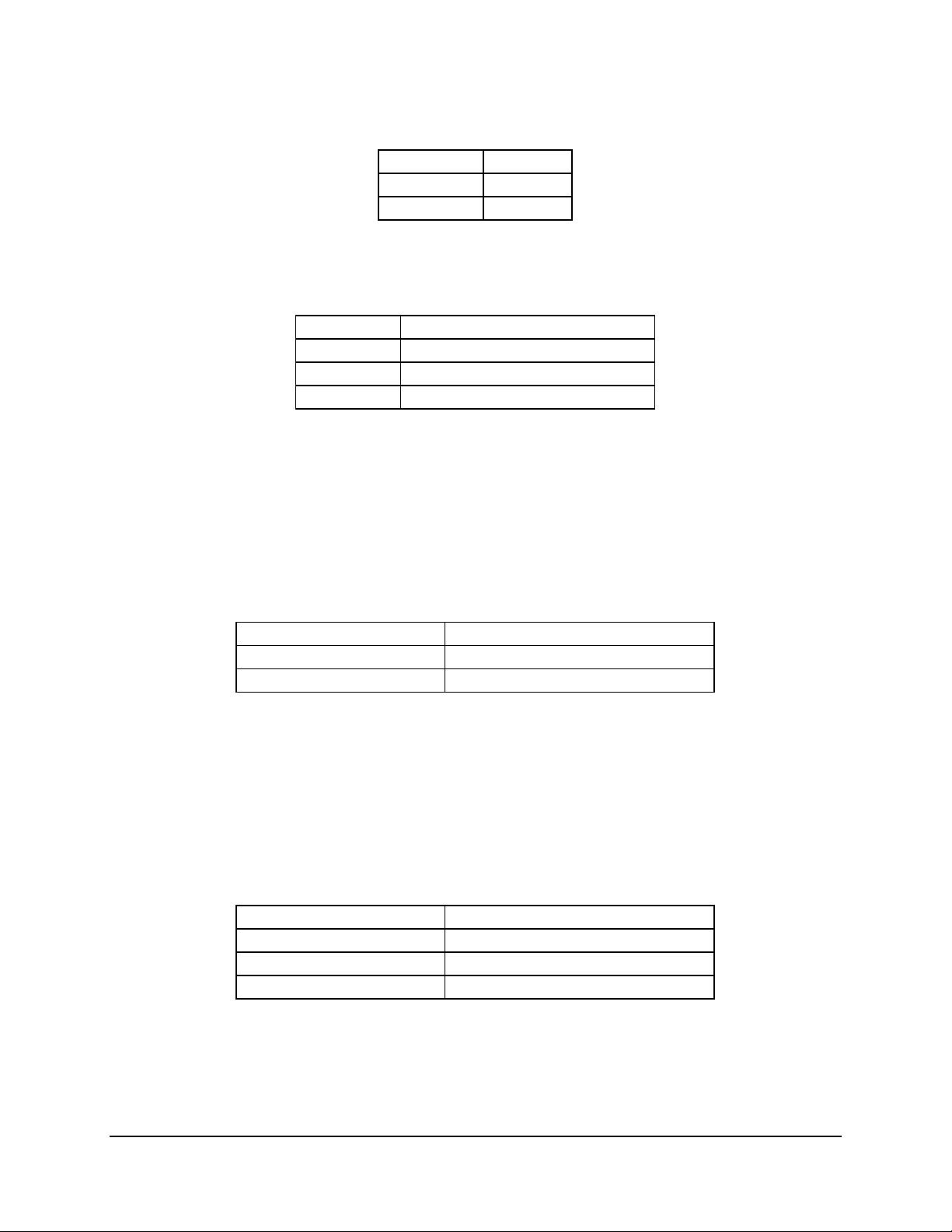

Table 1. SDS2 Intel® Pentium® III Processor Support Matrix

Processor

Family

Intel

Pentium III

Intel

Pentium III –

Tray

Intel

Pentium III –

Tray

Intel

Pentium III –

Boxed

Intel

Pentium III –

Tray

Intel

Pentium III –

Boxed

Intel FCPGA2 838253 1.4GHZ/133MHz 512KB tA1 06B1h Yes

Package

Type

FCPGA 800MHz – 1.0GHz 256KB N/A N/A No

FCPGA2 836606 1.BGHz/133MHz 256KB cD0 068Ah

FCPGA2 836716 1.13GHZ/133MHz 512KB tA1 06B1h

FCPGA2 836384 1.13GHZ/133MHz 512KB tA1 06B1h

FCPGA2 836721 1.26GHZ/133MHz 512KB tA1 06B1h

FCPGA2 836583 1.26GHZ/133MHz 512KB tA1 06B1h

MM## Speed

Core/Bus

Cache

Size

Core

Stepping

CPUID

S-Spec

SL5QJ

SL5PU

SL5LV

SL5QL

SL5LW

Supported

Yes

Yes

Yes

Yes

Yes

Revision 1.2

4

Order Number: A85874-002

Page 19

Intel® Server Board SDS2 Processor and Chipset

Pentium III –

Tray

Intel

Pentium III –

Boxed

FCPGA2 843849 1.4GHZ/133MHz 512KB tA 1 06B1h

SL5XL

Yes

SL5XL

Notes:

• All processor sockets must be populated with either a processor or a terminator module.

The BMC will not allow DC power to be applied to the system unless both processor

sockets contain a properly seated processor or terminator module.

• Processors should be populated in the sequential order. In other words, processor

socket #1 should be populated before processor socket #2.

• BIO 50 (released on FAB 5) supports the tB1 stepping, CPUID 06B4. These processors

are being evaluated for addition to supported processor list. The current Intel support

web site has the latest supported processor list for SDS2:

http://support.intel.com/support/motherboards/server/SDS2/.

Revision 1.2

Order Number: A85874-002

5

Page 20

Processor and Chipset Intel® Server Board SDS2

3.1.1 Processor Voltage Regulator Module (VRM)

The SDS2 Server Board has dual, on board, RM circuitry to support the two processors. The

circuit is compliant with the VRM8.5 specification and provides a maximum of 60A, which will

support the currently available processors and future releases of the Pentium III processors.

The board hardware and the BMC read the processor VID (Voltage Identification) bits for each

processor before turning on the power to the processors (VRMs). If the VIDs of the two

processors are not identical, then the BMC will not turn on the VRMs and a beep code is

generated. Table 30. BMC Beep Codes lists all of the error codes.

3.2 Memory Subsystem

The SDS2 Server Board supports up to six DIMM sockets for a maximum memory capacity of 6

GB using 1 GB DIMMs. The DIMM organization is x72, which includes 8 ECC check bits. ECC

from the DIMMs is passed through to the processor front side bus.

The SDRAM interface runs at the same frequency as the processor bus. The memory controller

supports 2-way interleaved SDRAM, memory scrubbing, single-bit error correction, and multiplebit error detection. Memory can be implemented with either single-sided (one row) or doublesided (two row) DIMMs.

• Only registered PC-133 compliant memory is supported

• Support is 2-way interleaved SDRAM and requires two DIMMs to be installed per bank.

• ECC si ngle-bit error correction and multiple-bit error detection

• Maximum memory capacity of 6 GB

• Minimum memory capacity of 128 MB

Note: Memo ry interleaving is a way to increase memory performance by allowing the system to

access multiple memory modules simultaneously, rather than sequentially, in a similar fashion to

Hard Drive striping. Interleaving can only take place between identical memory modules.

3.2.1 Memory Configuration

Memory configuration requirements are as follow:

• PC-133 SDRAM Registered DIMM modules

• DIMM organization: x72 ECC

• Pin count: 168

• SDRAM Supported: 64 M b, 128 Mb, 256 Mb

• DIMM capacity: 64 MB, 128 MB, 256 MB, 512 MB, 1 GB

• Serial PD: JEDEC Rev 2.0

• Voltage Options: 3.3 V (VDD/VDDQ)

• Interface : LVTTL

• DIMMs must be populated in pairs for a x144 wide memory data path

• Any or all memory banks may be populated

Revision 1.2

6

Order Number: A85874-002

Page 21

Intel® Server Board SDS2 Processor and Chipset

Table 2. Memory DIMM Pairs

Memory DIMM DIMM PAIR Row

DIMM1A, DIMM1B 1 1, 2

DIMM2A, DIMM2B 2 3, 4

DIMM3A, DIMM3B 3 5, 6

DIMM Pair 1

DIMM Pair 2

DIMM Pair 3

Figure 2. SDS2 Memory Bank Layout

Revision 1.2

Order Number: A85874-002

7

Page 22

Processor and Chipset Intel® Server Board SDS2

3.2.2 I2C Bus

An I2C* bus is between the BMC and the six DIMM slots. This bus is used by the system BIOS to

retrieve DIMM information needed to program the HE-SL memory registers which are required to

boot the system.

The following table provides the I2C addresses for each DIMM slot.

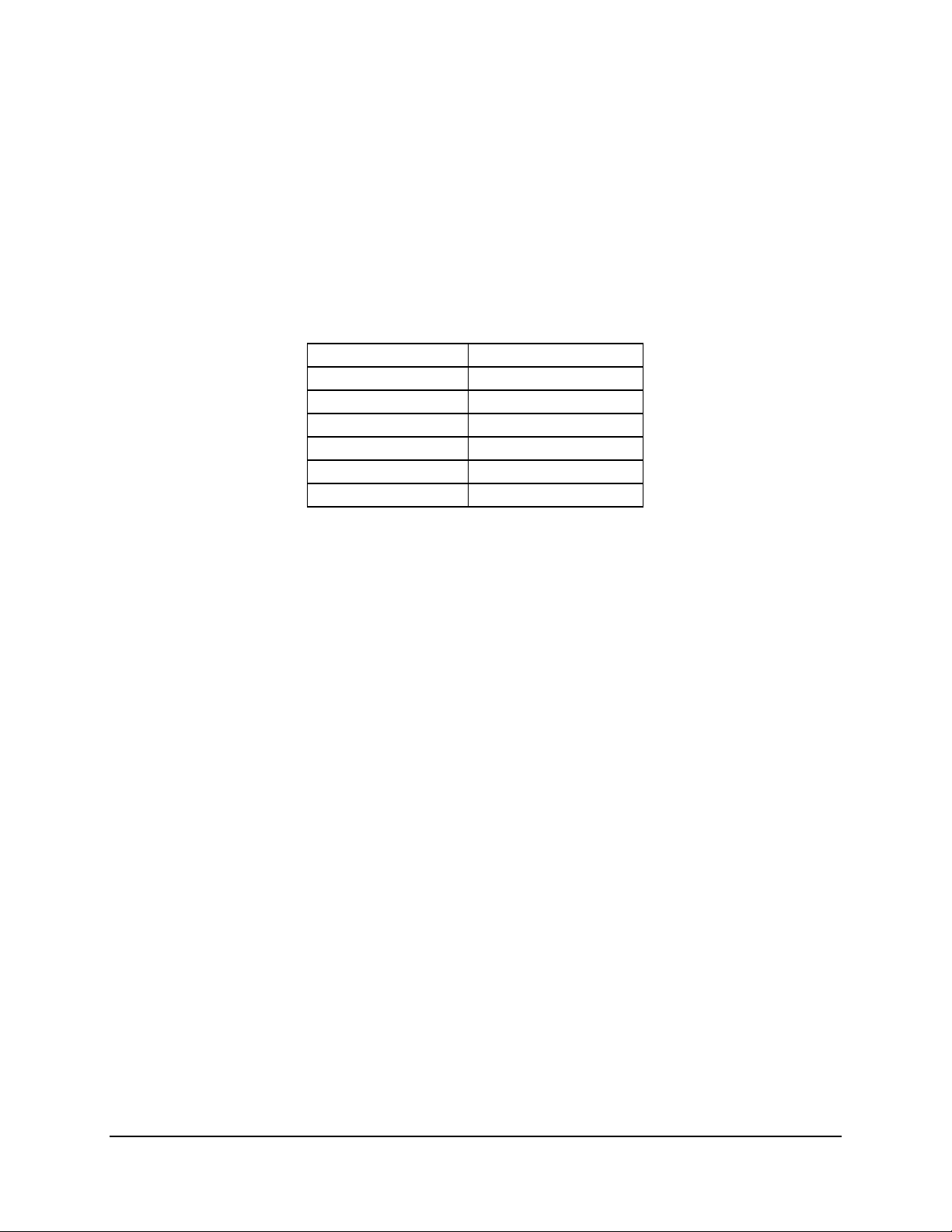

Table 3. I2C Addresses for DIMM Slots

Device Address

DIMM 1A 0xA0

DIMM 1B 0xA2

DIMM 2A 0xA4

DIMM 2B 0xA6

DIMM 3A 0xA8

DIMM 3B 0xAA

3.3 Chipset

The Server Works* ServerSet III HE-SL chipset provides an integrated I/O bridge and memory

controller and a flexible I/O subsystem core (PCI), targeted for multiprocessor systems and

standard high-volume servers. The Server Works* ServerSet III chipset consists of the three

components listed below:

• CNB20HE-SL: Champion North Bridge. The HE-SL North Bridge is responsible for

accepting access requests from the host (processo r) bus and for directing those

accesses to memory or to one of the PCI buses. The HE-SL monitors the host bus,

examining addresses for each request. Accesses may be directed to a memory request

queue, for subsequent forwarding to the memory subsystem, or to an outbound request

queue, for subsequent forwarding to one of the PCI buses. The HE-SL also accepts

inbound requests from the CIOB20 and the legacy PCI bus. The HE-SL is also

responsible for generating the appropriate controls to control data transfer to and from

the memory.

• CIOB20: Champion I/O Bridge. The CIOB20 provides the interface for two 64-bit, 66-

MHz Rev. 2.2 compliant PCI bus. The CIOB is both master and target on both PCI

buses.

• CSB5: South Bridge. The CSB5 controller has several components. It provides the

interface for a 32-bit, 33-MHz Rev. 2.2-compliant PCI bus. The CSB5 can be both a

master and a target on that PCI bus. The CSB5 also includes a USB controller and an

IDE controller. The CSB5 is also responsible for much of the power management

functions, with ACPI control registers built in. The CSB5 also provides a number of GPIO

pins and has the LPC bus to support low-speed legacy I/O.

Revision 1.2

8

Order Number: A85874-002

Page 23

Intel® Server Board SDS2 Processor and Chipset

3.3.1 CNB20HE-SL Champion North Bridge

The Champion North Bridge Rev 2.0 High End Super Lite (CNB20HE-SL) is the third generation

product in the Server Works Champion North Bridge Technology. The HE-SL is a 644-pin ballgrid array (BGA) device and uses the proven components of previous generations like the

Pentium Pro Bus interface unit, the PCI interface unit, and the SDRAM memory interface unit. In

addition, the HE-SL incorporates a proprietary Intra Module Bus (IMBus) Interface. The IMBus

interface enables the HE-SL to directly interface with the CIOB20 through its two unidirectional

16-bit wide data busses with parity support. The HE-SL also increases the main memory

interface bandwidth and maximum memory configuration with a 144-bit wide memory interface.

The HE-SL integrates three main functions:

• An integrated high-performance main memory subsystem

• An IMBus interface that provides a high-performance data flow path between the Pentium

Pro bus and the I/O subsystem

• A PCI interface which provides an interface to the compatibility PCI bus segment and the

CSB5 (South Bridge).

Other features provided by the HE-SL include the following:

• Full support of ECC on the processor bus

• Full support of ECC on the memory interface

• Eight deep in-order queue

• Full support of registered PC-133 ECC SDRAM DIMMs

• Support for 6 GB of 2-way interleaved SDRAM

• Memory scrubbing

3.3.1.1 PCI Bus P32-A I/O Subsystem

The HE-SL provides a legacy 32-bit PCI subsyst em and acts as the central resource on this PCI

interface.

P32-A supports the following embedded devices and connectors:

• CSB5: South Bridge

• Two Intel® 82550PM 10/100 Fast Ethernet PCI network interface controllers

• An ATI RAGE XL Video Controller with 3D/2D graphics accelerator

• Two 32-bit, 33-MHz 5V full length PCI Slots

Revision 1.2

Order Number: A85874-002

9

Page 24

Processor and Chipset Intel® Server Board SDS2

3.3.2 CIOB20 Champion I/O Bridge

The Champion I/O Bridge (CIOB) is a 352-pin ball-grid array device and provides an integrated

I/O bridge that provides a high-performance data flow path between the IMBus and the 64-bit I/O

subsystem. This subsystem supports peer 64-bit PCI segments. Because it has multiple PCI

interfaces, the CIOB can provide large and efficient I/O configurations. The CIOB functions as

the bridge between the IMBus and the multiple 64-bit PCI I/O segments.

The IMBus interface can support 512 MB/s of data bandwidth in both the upstream and

downstream direction simultaneously.

The internal PCI arbiter implements the Least Recently used algorithm to grant access to

requesting masters.

3.3.2.1 PCI Bus P64-B I/O Subsystem

P64-B supports two 64-bit, 66-MHz 3.3V full-length PCI slots.

3.3.2.2 PCI Bus P64-C I/O Subsystem

P64-C supports the following embedded devices and connectors:

• Dual Channel Wide Ultra160 SCSI controller: Adaptec* AIC-7899W

• Two 64-bit, 66-MHz 3.3V full length PCI Slots

3.3.3 CSB5 South Bridge

Please refer to Section 4.5 for information on CSB5.

Revision 1.2

10

Order Number: A85874-002

Page 25

Intel® Server Board SDS2 I/O Subsystem

4. I/O Subsystem

4.1 PCI Subsystem

The primary I/O bus for SDS2 DP Server Board is PCI, with three PCI bus segments. The PCI

buses comply with the PCI Local Bus Specification, Rev 2.2. The P32-A bus segment is directed

through the HE-SL North Bridge while the two 64bit segments, P64-B and P64-C, are directed

through the CIOB20 I/O Bridge. The table below lists the characteristics of the three PCI bus

segments.

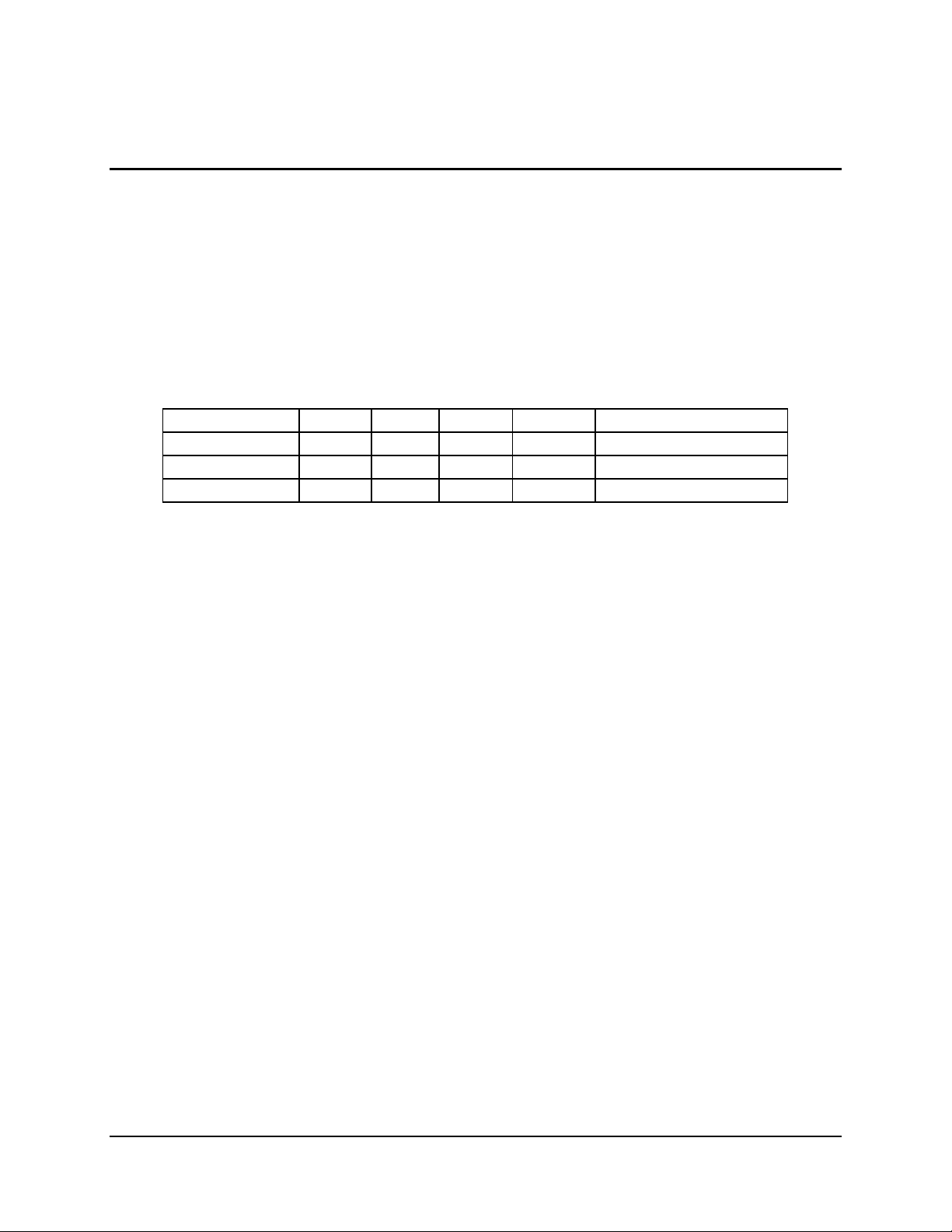

Table 4. PCI Bus Segment Characteristics

PCI Bus Segment Voltage Width Speed Type PCI Slots

P32-A 5 V 32-bits 33-MHz Peer Bus Slots 3 and 4 – Full Length

P64-B 3.3 V 64-bits 66-MHz Peer Bus Slots 1 and 2 – Full Length

P64-C 3.3 V 64-bits 66-MHz Peer Bus Slots 5 and 6 – Full Length

Note: When an add-in 33-MHz PCI card is plugged into a P64 bus segment, such as in the P64C slot 5, this reduces the bus speed for all devices attached to that bus segment, including the

on-board SCSI controller.

4.1.1 32-bit, 33-MHz PCI Subsystem

All 32-bit, 33-MHz PCI I/O for the SDS2 Server Board is directed through the HE-SL North

Bridge. The 32-bit, 33-MHz PCI segment created by the HE-SL is called the P32-A segment. The

P32-A segment supports full-length, full-height PCI cards and contains the following embedded

devices and connectors:

• 2D/3D Graphics Accelerator: ATI RAGE XL Video Controller

• Two Network Interface Controller: Intel 82550 Fast Ethernet Controller

• PCI Slots 3 and 4

• CSB5 South Bridge (PCI -to-LPC bridge)

Each of the embedded devices above, except for the CSB5 South Bridge, is allocated a GPIO to

disable the device.

4.1.1.1 Device IDs (IDSEL)

Each device under the PCI hub bridge has its IDSEL signal connected to one bit of AD [31:16],

which acts as a chip select on the PCI bus segment in configuration cycles. This determines a

unique PCI device ID value for use in configuration cycles. The following table shows the bit to

which each IDSEL signal is attached for P32-A devices, and corresponding device description.

Revision 1.2

Order Number: A85874-002

11

Page 26

I/O Subsystem Intel® Server Board SDS2

Table 5. P32-A Configuration IDs

IDSEL Value Device

18 ATI RAGE XL Video Controller

19 Intel 82550 Fast Ethernet Controller 1

20 Intel 82550 Fast Ethernet Controller 2

24 PCI Slot 3

25 PCI Slot 4

31 CSB5 South Bridge

4.1.1.2 P32-A Arbitration

P32-A supports seven PCI masters (ATA RAGE XL, two Intel 82550s, PCI masters from slots 3

and 4, CSB5, and HE-SL). All PCI masters must arbitrate for PCI access, using resources

supplied by the HE-SL. The following table defines the arbitration connections.

Table 6. P32-A Arbitration Connections

Baseboard Signals Device

REQ_VGA / GNT_VGA ATI* RAGE XL Video Controller

D_PCIREQL1 / D_PCIGNTL1 Intel 82550 Fast Ethernet Controller 1

D_PCIREQL2 / D_PCIGNTL2 Intel 82550 Fast Ethernet Controller 2

D_PCIREQL3 / D_PCIGNTL3 PCI Slot 3

D_PCIREQL4 / D_PCIGNTL4 PCI Slot 4

D_PCIREQL5 / D_PCIGNTL5 CSB5 South Bridge

4.1.2 64-bit, 66-MHz PCI Subsystem

There are two 64-bit, 66-MHz PCI busses directed through the CIOB20 I/O Bridge. Both segments

support full-length, full-height PCI cards. The PCI cards must meet the PCI specification for height,

inclusive of cable connections and memory. The two PCI segments are peer buses.

4.1.2.1 Device IDs (IDSEL)

Each device under the PCI hub bridge has its IDSEL signal connected to one bit of AD [31:16],

which acts as a chip select on the PCI bus segment in configuration cycles. This determines a

unique PCI device ID value for use in configuration cycles. The following tables show the bit to

which each IDSEL signal is attached for P64-B and P64-C devices, and corresponding device

description.

Revision 1.2

12

Order Number: A85874-002

Page 27

Intel® Server Board SDS2 I/O Subsystem

Table 4. P64-B Configuration IDs

IDSEL Value Device

24 PCI Slot 1

25 PCI Slot 2

Table 5. P64-C Configuration IDs

IDSEL Value Device

20 Adaptec AIC-7899W SCSI Controller

24 PCI Slot 5

25 PCI Slot 6

4.1.2.2 P64-B Arbitration

P64-B supports three PCI masters (PCI masters from slots 1 and 2, and CIOB). All PCI

masters must arbitrate for PCI access, using resources supplied by the CIOB. The following

table defines the arbitration connections.

Table 7. P64-B Arbitration Connections

Baseboard Signals Device

FREQL1 / FGNTL1 PCI Slot 1

FREQL2 / FGNTL2 PCI Slot 2

4.1.2.3 P64-C Arbitration

P64-C supports four PCI masters (PCI masters from slots 5 and 6, onboard SCSI, and CIOB).

All PCI masters must arbitrate for PCI access, using resources supplied by the CIOB. The

following table defines the arbitration connections.

Table 8. P64-B Arbitration Connections

Baseboard Signals Device

SCSIREQL0 / SCSIGNTL0 Adaptec AIC-7899W SCSI Controller

P64REQL1 / P64GNTL1 PCI Slot 5

P64REQL2 / P64G NTL2 PCI Slot 6

Revision 1.2

Order Number: A85874-002

13

Page 28

I/O Subsystem Intel® Server Board SDS2

4.1.2.4 Zero Channel RAID (ZCR) Capable PCI Slot 6

The SDS2 Server Board supports zero-channel RAID controller on PCI Slot 6. This add-in card

leverages the on-board SCSI controller along with its own built-in intelligence to provide a

complete RAID controller subsystem on-board. If a specified zero-channel RAID card is

installed, then SCSI interrupts are routed to the RAID card instead of PCI interrupt controller and

the host -based I/O device is effectively hidden from the system. The SDS2 Server Board uses

an implementation commonly referred to as “RAIDI OS” to support this feature.

Note: Zero Channel Raid Cards (ZCR) cards are only supported on PCI slot 6.

Note: Intel zero channel raid cards SRCMR and SRCMRU are not supported on SDS2.

4.2 Ultra160 SCSI

The SDS2 Server Board provides an embedded dual-channel SCSI bus through the use of the

Adaptec*’s AIC-7899W SCSI controller. The AIC-7899W controller contains two independent

SCSI controllers that share a single 64-bit, 66-MHz PCI bus master interface as a multifunction

device, packaged in a 456-pin BGA. Internally, each controller is identical, capable of operations

using either 16-bit SE or LVD SCSI providing 40 MBps (Ultra-wide SE), 80 MBps (Ultra 2), or 160

MBps (Ultra160). Each controller has its own set of PCI configuration registers and SCSI I/O

registers. The SDS2 Server Board supports disabling of the on-board SCSI controller through

the BIOS setup menu.

The SDS2 Server Board provides active terminators, termination voltage, re-settable fuse , and

protection diode for both SCSI channels. The SCSI BIOS setup menu (CNTRL -A) provides the

ability to enable or disable the on-board terminators for both channels A and B.

4.3 Video Controller

The SDS2 Server Board provides an ATI* RAGE XL PCI graphics accelerator, along with video

SDRAM and support circuitry for an embedded SVGA video subsystem. The ATI* RAGE XL chip

contains a SVGA video controller, clock generator, 2D and 3D engine, and RAMDAC in a 272-pin

PBGA. Two 2 MB SDRAM chips provide 4 MB of video memory . The SVGA subsystem supports

a variety of modes, up to 1024 x 768 resolution in 8/16/24/32 bpp modes under 2D and up to 800

x 600 resolution in 8/16/24/32 bpp modes under 3D. It also supports both CRT and LCD

monitors at up to 100 Hz vertical refresh rate. The SDS2 Server Board provides a standard 15pin VGA connector.

4.3.1 Video Modes

The RAGE XL chip supports all standard IBM* VGA modes. The following table shows the 2D/3D

modes supported on the CRT. The table specifies the various display resolution, refresh rates

and color depths supported.

Revision 1.2

14

Order Number: A85874-002

Page 29

Intel® Server Board SDS2 I/O Subsystem

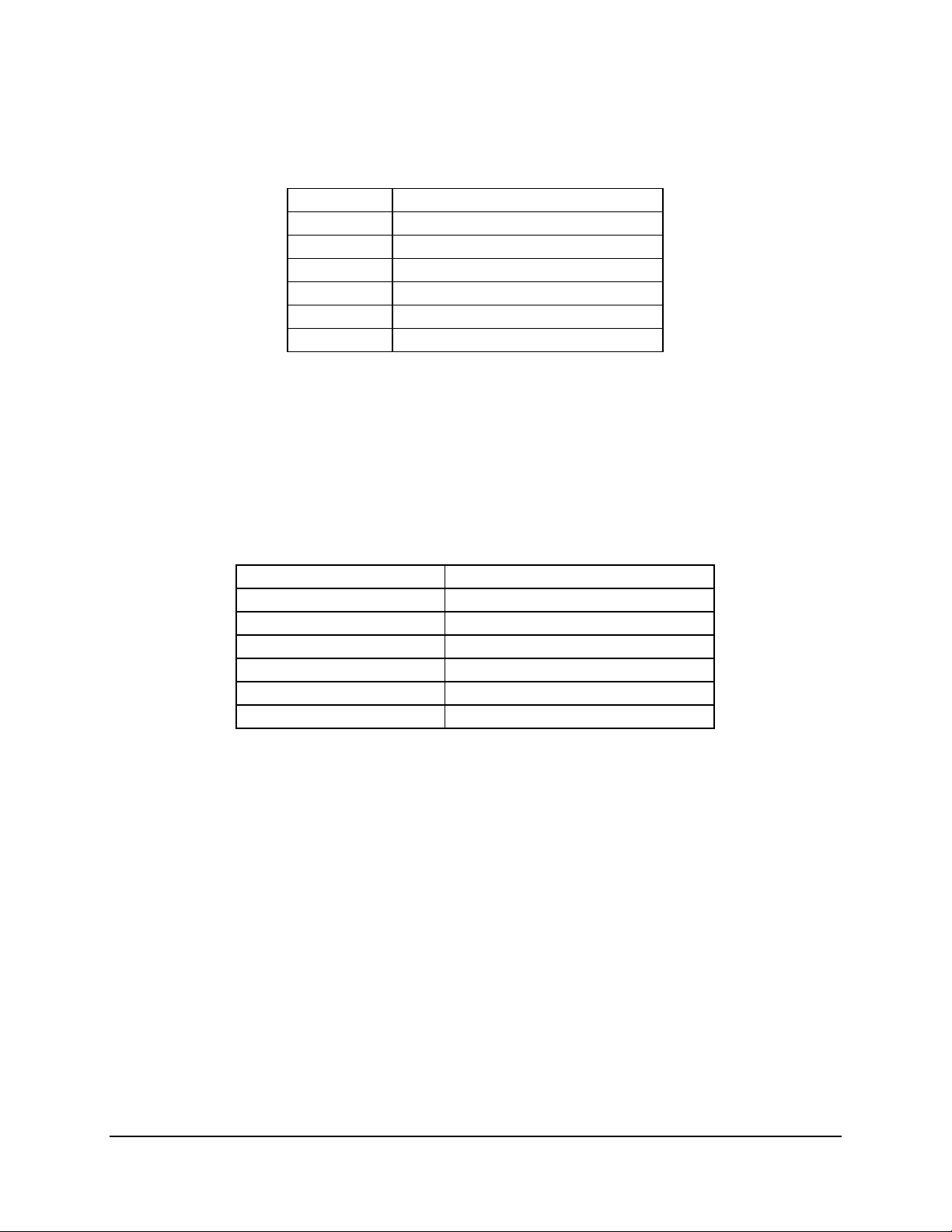

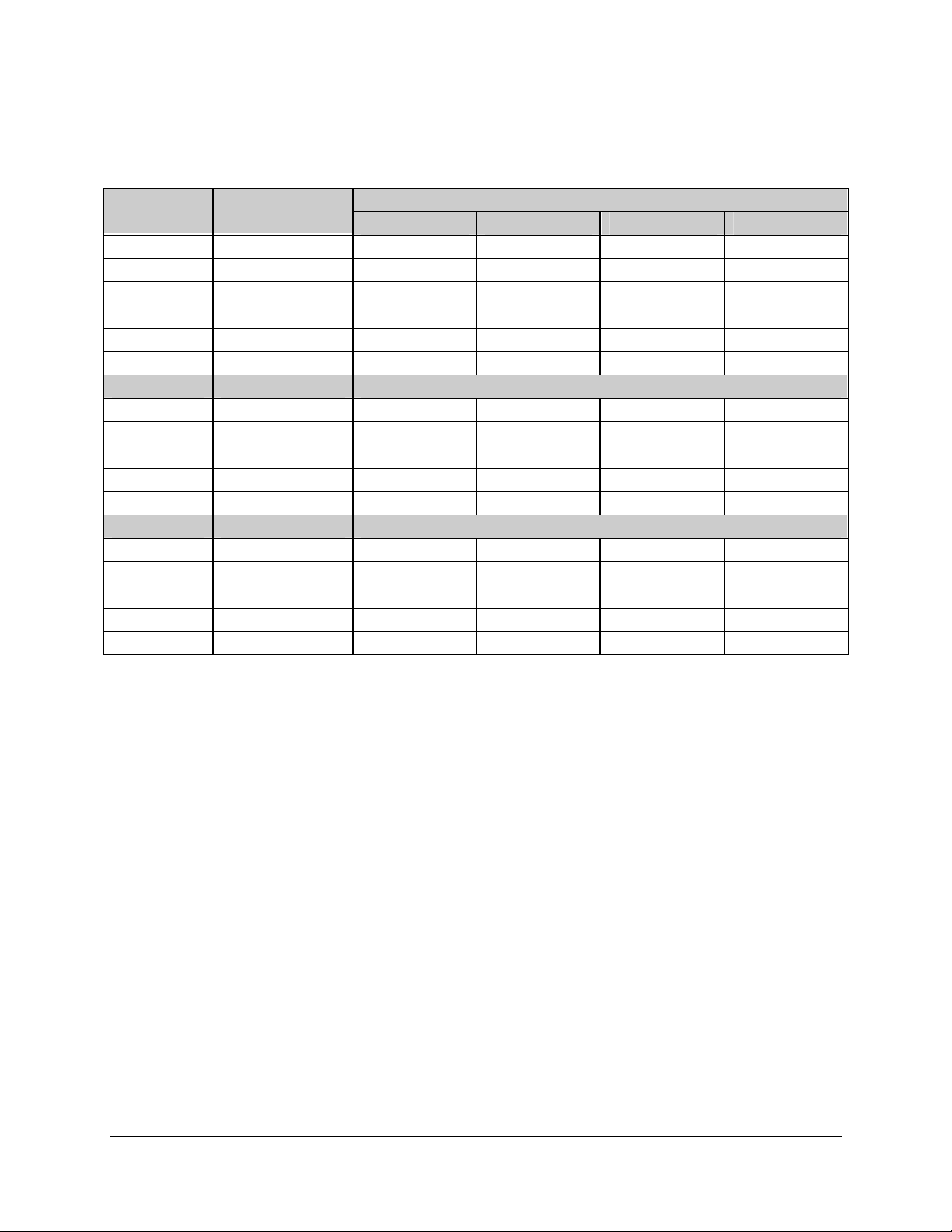

Table 9. Video Modes

SDS2 2D Mode Video Support 2D Mode Refresh Rate (Hz)

8 bpp 16 bpp 24 bpp 32 bpp

640x480 60, 72, 75, 90, 100 Supported Supported Supported Supported

800x600 60, 70, 75, 90, 100 Supported Supported Supported Supported

1024x768 60, 72, 75, 90, 100 Supported Supported Supported Supported

1280x1024 43, 60 Supported Supported Supported –

1280x1024 70, 72 Supported – Supported –

1600x1200 60, 66, 76, 85 Supported Supported – –

3D Mode Refresh Rate (Hz) SDS2 3D Mode Video Support with Z Buffer Enabled

640x480 60, 72, 75, 90, 100 Supported Supported Supported Supported

800x600 60, 70, 75, 90, 100 Supported Supported Supported –

1024x768 60, 72, 75, 90, 100 Supported – – –

1280x1024 43, 60, 70, 72 – – – –

1600x1200 60, 66, 76, 85 – – – –

3D Mode Refresh Rate (Hz) SDS2 3D Mode Video Support with Z Buffer Disabled

640x480 60, 72, 75, 90, 100 Supported Supported Supported Supported

800x600 60, 70, 75, 90, 100 Supported Supported Supported Supported

1024x768 60, 72, 75, 90, 100 Supported Supported – –

1280x1024 43, 60, 70, 72 Supported – – –

1600x1200 60, 66, 76, 85 Supported – – –

4.4 Network Interface Controller (NIC)

The SDS2 Server Board supports two 10Base -T / 100Base-TX network subsystem using the

Intel 82550-PM NIC. The 82550 components are highly integrated PCI LAN controllers in a thin

BGA 15 mm2 package. The controller’s baseline functionality is equivalent to that of the Intel

82559 with the addition of Alert on LAN* functionality.

The SDS2 Server Board supports independent disabling of either of the two NIC controllers

under BIOS setup menu.

The 82550 supports the following features:

• 32-bit PCI/Card Bus master interface

• Integrated IEEE 802.3 10Base -T and 100Base-TX compatible PHY

• IEEE 820.3u auto-negotiation support

• Chained memory structure similar to the 82559, 82558, 82557 and 82596

• Full duplex support at both 10 and 100 Mbps operation

• Low power +3.3 V device

Revision 1.2

Order Number: A85874-002

15

Page 30

I/O Subsystem Intel® Server Board SDS2

4.4.1 NIC Connector and Status LEDs

The 82550 drives LEDs on the network interface connector to indicate link/activity on the LAN and

10-Mbps or 100-Mbps operation.

• The green LED indicates a network connection when lighted solidly and TX/RX activity

when blinking.

• The amber LED indicates 100-Mbps a network connection when lighted solidly and TX/RX

activity when blinking.

4.5 CSB5 South Bridge (PCI -to-LPC Bridge, IDE, USB)

The CSB5 is a multi-function PCI device, housed in a 256-pin BGA device, providing PCI -to-LPC

bridge, PCI IDE interface, PCI USB controller, and power management controller. Each function

within the CSB5 has its own set of configuration registers. Once configured, each appears to the

system as a distinct hardware controller sharing the same PCI bus interface.

In the SDS2 Server Board implementation, the primary role of the CSB5’ is to provide the

gateway to all PC-compatible I/O devices and features. The SDS2 uses the following CSB5

features:

• PCI bus interface

• LPC bus interface

• IDE interface, with Ultra DMA 100 capability

• Universal Serial Bus (USB) interface

• PC-compatible timer/counter and DMA controllers

• APIC and 8259 interrupt controller

• Power management

• General purpose I/O

Following are descriptions of how each supported feature is implemented in SDS2.

4.5.1 PCI Bus Interface

The CSB5 fully implements a 32-bit PCI master/slave interface, in accordance with the PCI

Local Bus Specification, Revision 2.2. On the SDS2 Server Board, the PCI interface operates at

33 MHz, using the 5 V signaling environment.

4.5.2 PCI Bus Master IDE Interface

The CSB5 acts as a PCI -based Fast IDE controller that supports programmed I/O transfers and

bus master IDE transfers. The CSB5 supports two IDE channels, supporting two drives each

(drives 0 and 1). The FAB 5 (PBA A58285-502) SDS2 Server Board supports two IDE channels

through the standard 40-pin (2x20) connector. Note FAB 4 boards (PBA A58285-402 and –403)

supported only one IDE channel.

The SDS2 IDE interface supports the following features:

Revision 1.2

16

Order Number: A85874-002

Page 31

Intel® Server Board SDS2 I/O Subsystem

• The scatter / gather mechanism supports both DMA and PIO IDE drives and ATAPI

devices

• Support for ATA and ATAPI, PIO Mode 0, 1, 2, 3, 4, DMA Mode 0, 1, 2, and Ultra DMA

Mode 0, 1, 2, 3, 4, 5

• The IDE drive transfer rate is capable of up to ATA -100 (100 MB/sec per channel)

4.5.3 USB Interface

The CSB5 contains a USB controller and four USB hubs. The USB controller moves data

between main memory and the four USB connectors.

The SDS2 Server Board provides a three external USB connector interface on the rear I/O. One

additional USB is supported internally through a 10-pin header (2 X 5) that can be cabled to a

front panel board. All four ports function identically and with the same bandwidth. The USB

Specification, Revision 1.1, defines the external connector. Table 68. 10-pin USB Connection

Header (2 x 5) Pin-out.

4.5.4 Compatibility Interrupt Control

The CSB5 provides the functionality of two 82C59 PIC devices for ISA -compatible interrupt

handling.

4.5.5 APIC

The CSB5 integrates a 32-entry I/O APIC that is used to distribute 32 PCI interrupts. It also

includes an additional 16-entry I/O APIC for the distribution of legacy ISA interrupts.

4.5.6 Power Management

One of the embedded functions of CSB5 is a power management controller. The SDS2 Server

Board uses this to implement ACPI -compliant power management features. The SDS2 supports

sleep states S0, S1, S4, and S5.

4.5.7 General Purpose Input and Output Pins

The CSB5 provides a number of general purpose input and output pins. Many of these pins have

alternate functions, and thus all are not available. The following table lists the GPI and GPO pins

used on the SDS2 Server Board and gives a brief description of their function.

Table 10. CSB5 GPIO Usage Table

Pad GPIO Name Description

V3 N_SALERTN Reporting for Fata Errors from HE-SL such as multi-bit ECC errors, Bus

protocol errors, and FSBus parity errors

W2 MIRQL Reporting for Correctable Errors from HE-SL such as single-bit errors on Front

Side Data bus and Memory Data bus

W3 N_CIOBALERTN Reporting for errors from CIOB

Y4 N_CSB5_NMI Generation of NMI from CSB5

Y1 N_BMC_IRQ_SMI_00 Input from BMC of SMI event

Revision 1.2

Order Number: A85874-002

17

Page 32

I/O Subsystem Intel® Server Board SDS2

Pad GPIO Name Description

Y19 N_NVRAMCLR Input from jumper to be in BIOS Recovery mode in case of corruption

V17 N_PASSDIS_00 Input from jumper to clear password assignments

U16 N_CMOSCLR_00 Input from jumper to clear setup info in CMOS

T20 N_F3SETUPEN_00 Input from jumper to to be in special test mode (manufacturing only)

T19 N_BMC_SCIN Input from BMC of SCI event

T18 N_BMCISPMD_00 Input from jumper to to be in special test mode (manufacturing only)

U18 N_FRB3STP_00 Output signal to turn off FRB timer to stop fault conditions (this signal is wire-or

with the 2-pin jumper

Y16 N_SCSI_IDSEL_EN Output signal to disable onboard SCSI controller

V12 N_LAN2_IDSEL_EN Output signal to disable onboard NIC2

U12 N_LAN1_IDSEL_EN Output signal to disable onboard NIC1

V19 CSBPICD0 CSB5 APIC Data Bus 0

W20 CSBPICD1 CSB5 APIC Data Bus 1

Y20 N_ROM_CSN Output signal for BIOS Chip Select

U19 N_VGA_IDSEL_EN Output signal to disable onboard Video

4.6 Chipset Support Components

4.6.1 Super I/O

The National Semiconductor PC87417 Super I/O device contains all of the necessary circuitry to

control two serial ports, one parallel port, floppy disk, and PS/2-compatible keyboard and mouse .

The SDS2 Server Board supports the following features:

• GPIO

• Two serial ports

• Floppy

• Keyboard and mouse through PS/2 connectors

• Parallel port

• Real-time clock

• Wake-up control

4.6.1.1 General Purpose Input and Output - GPIO

The National Semiconductor* PC87417 Super I/O provides number of general-purpose

input/output pins that the SDS2 Server Board utilizes. The following table identifies the pin, the

signal name used in the schematic and a brief description of its usage.

Table 11. Super I/O GPIO Usage Table

Pin #

10 N_BMC_SYSIRQ_00 System Interrupt Controller interrupt from BMC

13 N_SIO_CLK_40M_BMC 40MHz clock output to BMC

Revision 1.2

18

Signal Name Description

Order Number: A85874-002

Page 33

Intel® Server Board SDS2 I/O Subsystem

Pin #

35 N_BMC_SWIN

36 N_BMCPWRN Power LED from BMC

37 N_EXTEN_00 External Event

38 N_SUPERSCI_00 System Control Interrupt used to detect wake-up events

45 N_SIO_CLK_RTC_BMC Real Time Clock output to BMC

49 N_P2_PME Power Management Event from PCI Bus (P64-B segment)

50 N_P3_PME Power Management Event from PCI Bus (P64-C segment)

51 N_FP_PWR_LED+00 Power LED indicator to Front Panel

52 N_LAN_PME Power Management Event from PCI Bus (P32-A segment)

53 N_BMC_SCIN System Management Interrupt from BMC

125 KBCLKL Keyboard Clock

126 KBDATL Keyboard Data

127 MSCLKL Mouse Clock

128 MSDATL Mouse Data

Signal Name Description

4.6.1.2 Serial Ports

Two serial ports are provided on the Server Board, a 9-pin DB9 connector is located on the rear

I/O to supply COM1 and a 10-pin header on the Server Board provides COM2.

4.6.1.3 Floppy

The FDC in the SIO is functionally compatible with floppy disk controllers in the DP8473 and

N844077. All the FDC functions are integrated into the SIO including analog data separator and

16-byte FIFO.

4.6.1.4 Keyboard and Mouse

Two PS/2 ports are provided for keyboard and mouse and are mounted within a single stacked

housing. The mouse connector is stacked over the keyboard connector.

4.6.1.5 Parallel Port

The parallel port is supported on the Server Board through the rear I/O.

4.6.1.6 Real-time Clock

The SIO contains a real-time clock with external battery backup. The device also contains 242

bytes of general purpose battery -backed CMOS RAM.

4.6.1.7 Wake-up Control

The SIO contains functionality that allows various events to control the power-on and power-off

of the system.

Revision 1.2

Order Number: A85874-002

19

Page 34

I/O Subsystem Intel® Server Board SDS2

4.6.2 BIOS Flash

The SDS2 Server Board incorporates a Fairchild* 29LV008B 8Mbit Flash ROM. The flash device

is connected through the X -bus of the CSB5.

4.7 Interrupt Routing

The SDS2 Server Board interrupt architecture implements both PC-compatible PIC mode and

APIC mode interrupts through the use of the integrated I/O APICs in the CSB5.

4.7.1 Legacy Interrupt Routing

For PC-compatible mode, the CSB5 provides two 82C59-compatible interrupt controllers. The

two controllers are cascaded with interrupt levels 8-15 entering on level 2 of the primary interrupt

controller (standard PC configuration). A single interrupt signal is presented to the processors, to

which only one processor will respond for servicing. The CSB5 contains configuration registers

that define which interrupt source logically maps to I/O APIC INTx pins.

Interrupts, both PCI and IRQ types, are handled by the CSB5. The CSB5 then translates these to

the APIC bus. The numbers in the table below indicate the CSB5 PCI interrupt input pin to which

the associated device interrupt (INTA, INTB, INTC, INTD) is connected. The CSB5’s I/O APIC

exists on the I/O APIC bus with the processors.

Table 12. PCI Interrupt Routing/Sharing

Interrupt Device INTA INTB INTC INTD

ATI RAGE XL 4

82550PM #1 2

82550PM #2 3

PCI Slot 1 (P64-B) 5 13 11 12

PCI Slot 2 (P64-B) 6 12 13 11

PCI Slot 3 (P32-A) 7 11 12 13

PCI Slot 4 (P32-A) 8 13 11 12

PCI Slot 5 (P64-C) 9 12 13 11

PCI Slot 6 (P64-C) 10 11 1 0

7899W-SCSI Ch A 0

7899W-SCSI Ch B 1

4.7.1.1 Legacy Interrupt Routing

The table below recommends the logical interrupt mapping of interrupt sources on the SDS2

Server Board. The actual interrupt map is defined using configuration registers in the CSB5.