Page 1

Intel® Quark SoC X1000 Core

Developer’s Manual

October 2013

Order Number: 329679-001US

Page 2

Legal Lines and Disclaimers

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE , E XPRESS OR IMPLIED, BY ESTOPPEL OR

OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS

OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELA TING

TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE,

MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death.

SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND

ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL

CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF , DIRECTL Y OR INDIRECTL Y, ANY CLAIM OF PRODUCT

LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS

SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics

of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever

for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design

with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published

specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-

4725, or go to: http://www.intel.com/design/literature.htm

Any software source code reprinted in this document is furnished for informational purposes only and may only be used or copied and no license, express

or implied, by estoppel or otherwise, to any of the reprinted source code is granted by this document.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different

processor families. Go to: http://www.intel.com/products/processor_number/

Code Names are only for use by Intel to identify products, platforms, programs, services, etc. (“products”) in development by Intel that have not been

made commercially available to the public, i.e., announced, launched or shipped. They are never to be used as “commercial” names for products. Also,

they are not intended to function as trademarks.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries.

*Other names and brands may be claimed as the property of others.

Copyright © 2013, Intel Corporation. All rights reserved.

Intel® Quark SoC X1000 Core

Developer’s Manual October 2013

2 Order Number: 329679-001US

Page 3

Revision History—Intel

®

Quark Core

Revision History

Date Revision Description

September 2013 001 First external release of document.

October 2013 Developer’s Manual

Order Number: 329679-001US 3

Intel® Quark SoC X1000 Core

Page 4

Intel® Quark Core—Contents

Contents

1.0 About this Manual.......................................................................................................17

1.1 Manual Contents............................... .. .. ......................... .. ... ...............................17

1.2 Notation Conventions.........................................................................................18

1.3 Special Terminology.................................... .. ... ........................... .......................19

1.4 Related Documents................................. .. .. .......................... .. .. .........................20

2.0 Intel® Quark SoC X1000 Core Overview.........................................................................21

2.1 Intel

3.0 Architectural Overview.................................................................................................22

3.1 Internal Architecture............................. .. ............................ ........................... ....22

3.2 System Architecture...................................................................... .. .. .................22

3.3 Memory Organization .........................................................................................22

3.4 I/O Space.........................................................................................................25

3.5 Addressing Modes..............................................................................................25

3.6 Data Types .......................................................................................................28

3.7 Interrupts.........................................................................................................33

4.0 System Register Organization.......................................................................................39

4.1 Register Set Overview................... .....................................................................39

4.2 Floating-Point Registers......................................................................................39

4.3 Base Architecture Registers.................................................................. ... .. ..........39

4.4 System-Level Registers ......................................................................................45

®

Quark Core Architecture..................................................... .. .....................21

3.3.1 Address Spaces......................................................................................23

3.3.2 Segment Register Usage..........................................................................24

3.5.1 Addressing Modes Overview.....................................................................25

3.5.2 Register and Immediate Modes.................................... ........................... ..26

3.5.3 32-Bit Memory Addressing Modes .............................................................26

3.5.4 Differences Between 16- and 32-Bit Addresses ...........................................28

3.6.1 Data Types ............................................................................................28

3.6.1.1 Unsigned Data Types.................................................................29

3.6.1.2 Signed Data Types ....................................................................29

3.6.1.3 BCD Data Types.................................. .......................... .. .. ........30

3.6.1.4 Floating-Point Data Types...........................................................30

3.6.1.5 String Data Types ................................................ .. ...................30

3.6.1.6 ASCII Data Types........................ ..............................................31

3.6.1.7 Pointer Data Types....................................................................32

3.6.2 Little Endian vs. Big Endian Data Formats ..................................................33

3.7.1 Interrupts and Exceptions........................................................................33

3.7.2 Interrupt Processing................................................................................34

3.7.3 Maskable Interrupt..................................................................................34

3.7.4 Non-Maskable Interrupt...........................................................................35

3.7.5 Software Interrupts.................................................................................36

3.7.6 Interrupt and Exception Priorities..............................................................36

3.7.7 Instruction Restart..................................................................................37

3.7.8 Double Fault ..........................................................................................38

3.7.9 Floating-Point Interrupt Vectors................................................................38

4.3.1 General Purpose Registers .......................................................................40

4.3.2 Instruction Pointer..................................................................................41

4.3.3 Flags Register ........................................................................................41

4.3.4 Segment Registers..................................................................................44

4.3.5 Segment Descriptor Cache Registers.........................................................44

4.4.1 Control Registers....................................................................................46

®

Quark SoC X1000 Core

Intel

Developer’s Manual October 2013

4 Order Number: 329679-001US

Page 5

Contents—Intel

®

Quark Core

4.4.1.1 Control Register 0 (CR0)............................................................47

4.4.1.2 Control Register 1 (CR1)............................................................51

4.4.1.3 Control Register 2 (CR2)............................................................51

4.4.1.4 Control Register 3 (CR3)............................................................51

4.4.1.5 Control Register 4 (CR4)............................................................51

4.4.2 System Address Registers .......................................................................52

4.5 Floating-Point Registers......................................................................................53

4.5.1 Floating-Point Data Registers...................................................................53

4.5.2 Floating-Point Tag Word..........................................................................54

4.5.3 Floating-Point Status Word......................................................................54

4.5.4 Instruction and Data Pointers...................................................................58

4.5.5 FPU Control Word...................................................................................61

4.6 Debug and Test Registers...................................................................................62

4.6.1 Debug Registers.....................................................................................62

4.6.2 Test Registers........................................................................................62

4.7 Register Accessibility .........................................................................................62

4.7.1 FPU Register Usage ................................................................................63

4.8 Reserved Bits and Software Compatibility.............................................................63

4.9 Intel

®

Quark Core Model Specific Registers (MSRs)................................................64

5.0 Real Mode Architecture................................................................................................65

5.1 Introduction .....................................................................................................65

5.2 Memory Addressing....................................................... ............................ ........66

5.3 Reserved Locations............................................................................................66

5.4 Interrupts ........................................................................................................67

5.5 Shutdown and Halt.............................................. ........................... ...................67

6.0 Protected Mode Architecture ........................................................................................68

6.1 Addressing Mechanism.......................................................................................68

6.2 Segmentation...................................................................................................69

6.2.1 Segmentation Introduction ............................................. .. .. .. .. .................69

6.2.2 Terminology ..........................................................................................70

6.2.3 Descriptor Tables ...................................................................................70

6.2.3.1 Descriptor Tables Introduction....................................................70

6.2.3.2 Global Descriptor Table..................................... .........................71

6.2.3.3 Local Descriptor Table ................................ .. .. ...........................71

6.2.3.4 Interrupt Descriptor Table............................... .. .. .......................71

6.2.4 Descriptors............................................................................................72

6.2.4.1 Descriptor Attribute Bits ............................................................72

6.2.4.2 Intel

®

Quark Core Code, Data Descriptors (S=1) ..........................72

6.2.4.3 System Descriptor Formats ........................................................74

6.2.4.4 LDT Descriptors (S=0, TYPE=2)..................................................75

6.2.4.5 TSS Descriptors (S=0, TYPE=1, 3, 9, B) ......................................75

6.2.4.6 Gate Descriptors (S=0, TYPE=4–7, C, F)......................................75

6.2.4.7 Selector Fields..........................................................................77

6.2.4.8 Segment Descriptor Cache.........................................................77

6.2.4.9 Segment Descriptor Register Settings..........................................77

6.3 Protection ........................................................................................................81

6.3.1 Protection Concepts................................................................................81

6.3.2 Rules of Privilege....................................................................................82

6.3.3 Privilege Levels......................................................................................82

6.3.3.1 Task Privilege...........................................................................82

6.3.3.2 Selector Privilege (RPL) .............................................................82

6.3.3.3 I/O Privilege and I/O Permission Bitmap ......................................83

6.3.3.4 Privilege Validation....................................................................85

6.3.3.5 Descriptor Access .....................................................................85

6.3.4 Privilege Level Transfers..........................................................................86

October 2013 Developer’s Manual

Order Number: 329679-001US 5

Intel® Quark SoC X1000 Core

Page 6

Intel® Quark Core—Contents

6.3.5 Call Gates..............................................................................................87

6.3.6 Task Switching............................ .. ............................ .............................88

6.3.6.1 Floating-Point Task Switching......................................................89

6.3.7 Initialization and Transition to Protected Mode............................................89

6.4 Paging..............................................................................................................91

6.4.1 Paging Concepts.....................................................................................91

6.4.2 Paging Organization................................................................................91

6.4.2.1 Page Mechanism .......................................................................91

6.4.2.2 Page Descriptor Base Register.................................... .. ...............91

6.4.2.3 Page Directory..........................................................................92

6.4.2.4 Page Tables..............................................................................92

6.4.2.5 Page Directory/Table Entries.......................................................92

6.4.2.6 Paging-Mode Modifiers ................................... .. .........................92

6.4.3 PAE Paging ............................................................................................93

6.4.3.1 PDPTE Registers........................................................................93

6.4.3.2 Linear-Address Translation with PAE Paging..................................94

6.4.4 #GP Faults for Intel

®

Quark SoC X1000 Core ..........................................100

6.4.5 Access Rights ......................................................................................100

6.4.5.1 SMEP Details for Intel® Quark SoC X1000 Core...........................101

6.4.6 Page Level Protection (R/W, U/S Bits)......................................................102

6.4.7 Page Cacheability (PWT and PCD Bits).....................................................103

6.4.8 Translation Lookaside Buffer ................................................. .................103

6.4.9 Page-Fault Exceptions ............................ ........................... .. .................104

6.4.10 Paging Operation..................................................................................106

6.4.11 Operating System Responsibilities...........................................................107

6.5 Virtual 8086 Environment ..................................................... .. .... .. .... .. .. ............10 7

6.5.1 Executing Programs..............................................................................107

6.5.2 Virtual 8086 Mode Addressing Mechanism ......... .......................................108

6.5.3 Paging in Virtual Mode...........................................................................108

6.5.4 Protection and I/O Permission Bitmap......................................................109

6.5.5 Interrupt Handling................................................................................110

6.5.6 Entering and Leaving Virtual 8086 Mode ........... .. .. ...................................111

6.5.6.1 Task Switches to and from Virtual 8086 Mode ............................ .112

6.5.6.2 Transitions Through Trap and Interrupt Gates, and IRET...............112

7.0 On-Chip Cache .........................................................................................................114

7.1 Cache Organization..........................................................................................114

7.1.1 Write-Back Enhanced Intel

7.2 Cache Control .................................................................................................116

7.2.1 Write-Back Enhanced Intel

®

Quark SoC X1000 Core Cache ........................115

®

Quark SoC X1000 Core Cache Control and

Operating Modes ..................................................................................116

7.3 Cache Line Fills................................................................................................117

7.4 Cache Line Invalidations...................................................................................118

7.4.1 Write-Back Enhanced Intel

®

Quark SoC X1000 Core Snoop Cycles and

Write-Back Mode Invalidation..................... .. .. .. .. ....................................118

7.5 Cache Replacement..........................................................................................118

7.6 Page Cacheability ............................................................................................119

7.6.1 Write-Back Enhanced Intel

®

Quark SoC X1000 Core and Processor Page

Cacheability.........................................................................................121

7.7 Cache Flushing................................................................................................122

7.7.1 Write-Back Enhanced Intel

7.8 Write-Back Enhanced Intel

®

7.8.1 Write-Back Cache Coherency Protocol......................................................123

7.8.2 Detecting On-Chip Write-Back Cache of the Write-Back Enhanced Intel

®

Quark SoC X1000 Core Cache Flushing............122

Quark SoC X1000 Core Write-Back Cache Architecture .123

®

Quark SoC X1000 Core..........................................................................125

8.0 System Management Mode (SMM) Architectures ...........................................................127

®

Quark SoC X1000 Core

Intel

Developer’s Manual October 2013

6 Order Number: 329679-001US

Page 7

Contents—Intel

®

Quark Core

8.1 SMM Overview................................................................................................ 127

8.2 Terminology ................................................................................................... 127

8.3 System Management Interrupt Processing.......................................................... 128

8.3.1 System Management Interrupt (SMI#).................................................... 129

8.3.2 SMI# Active (SMIACT#)........................................................................ 129

8.3.3 SMRAM............................................................................................... 130

8.3.3.1 SMRAM State Save Map........................................................... 131

8.3.4 Exit From SMM..................................................................................... 133

8.4 System Management Mode Programming Model .................................................. 134

8.4.1 Entering System Management Mode ....................................................... 134

8.4.2 Processor Environment.......................................................................... 135

8.4.2.1 Write-Back Enhanced Intel

®

Quark SoC X1000 Core Environment . 136

8.4.3 Executing System Management Mode Handler.................................. .. .. .... 136

8.4.3.1 Exceptions and Interrupts within System Management Mode ........ 137

8.5 SMM Features................................................................................................. 138

8.5.1 SMM Revision Identifier......................................................................... 138

8.5.2 Auto Halt Restart ................................................................................. 138

8.5.3 I/O Instruction Restart.......................................................................... 139

8.5.4 SMM Base Relocation............................................................................ 140

8.6 SMM System Design Considerations................................................................... 141

8.6.1 SMRAM Interface.................................................................................. 141

8.6.2 Cache Flushes.................................................................................... .. 142

8.6.2.1 Write-Back Enhanced Intel

®

Quark SoC X1000 Core System

Management Mode and Cache Flushing...................................... 144

8.6.2.2 Snoop During SMM.................... .. ............................................ 146

8.6.3 A20M# Pin and SMBASE Relocation ........................................................ 146

8.6.4 Processor Reset During SMM.................................................................. 146

8.6.5 SMM and Second-Level Write Buffers...................................................... 147

8.6.6 Nested SMI#s and I/O Restart ............................................................... 147

8.7 SMM Software Considerations........................................................................... 147

8.7.1 SMM Code Considerations...................................................................... 147

8.7.2 Exception Handling................................. ........................... ................... 148

8.7.3 Halt During SMM.................................................................................. 148

8.7.4 Relocating SMRAM to an Address Above One Megabyte ............................. 148

9.0 Hardware Interface................................................................................................... 149

9.1 Introduction ................................................................................................... 149

9.2 Signal Descriptions.......................................... .. ........................... ................... 150

9.2.1 Clock (CLK)......................................................................................... 150

9.2.2 Address Bus (A[31:2], BE[3:0]#)........................................................... 150

9.2.3 Data Lines (D[31:0]) ............................................................................ 151

9.2.4 Parity ................................................................................................. 151

9.2.4.1 Data Parity Input/Outputs (DP[3:0]) ......................................... 151

9.2.4.2 Parity Status Output (PCHK#) .................................................. 151

9.2.5 Bus Cycle Definition.............................................................................. 152

9.2.5.1 M/IO#, D/C#, W/R# Outputs ................................................... 152

9.2.5.2 Bus Lock Output (LOCK#)........................................................ 152

9.2.5.3 Pseudo-Lock Output (PLOCK#)................................................. 153

9.2.5.4 PLOCK# Floating-Point Considerations ....................................... 153

9.2.6 Bus Control ......................................................................................... 153

9.2.6.1 Address Status Output (ADS#)................................................. 153

9.2.6.2 Non-Burst Ready Input (RDY#).......................... .. .. .. .. ... ............ 153

9.2.7 Burst Control....................................................................................... 154

9.2.7.1 Burst Ready Input (BRDY#) ..................................................... 154

9.2.7.2 Burst Last Output (BLAST#)..................................................... 154

9.2.8 Interrupt Signals.................................................................................. 154

October 2013 Developer’s Manual

Order Number: 329679-001US 7

Intel® Quark SoC X1000 Core

Page 8

Intel® Quark Core—Contents

9.2.8.1 Reset Input (RESET).......................... .. .. .. ............................ ....154

9.2.8.2 Soft Reset Input (SRESET) .......................................................155

9.2.8.3 System Management Interrupt Request Input (SMI#)..................155

9.2.8.4 System Management Mode Active Output (SMIACT#) ..................155

9.2.8.5 Maskable Interrupt Request Input (INTR) ............................... .. ..155

9.2.8.6 Non-maskable Interrupt Request Input (NMI)..............................156

9.2.8.7 Stop Clock Interrupt Request Input (STPCLK#) ...........................156

9.2.9 Bus Arbitration Signals ..........................................................................156

9.2.9.1 Bus Request Output (BREQ).................... .. ... .. ...........................156

9.2.9.2 Bus Hold Request Input (HOLD) ................................................156

9.2.9.3 Bus Hold Acknowledge Output (HLDA)........................................157

9.2.9.4 Backoff Input (BOFF#).............................................................157

9.2.10 Cache Invalidation................................................................................157

9.2.10.1 Address Hold Request Input (AHOLD) ........................................158

9.2.10.2 External Address Valid Input (EADS#)........................................158

9.2.11 Cache Control ......................................................................................158

9.2.11.1 Cache Enable Input (KEN#)....................................... .. ... .. ........158

9.2.11.2 Cache Flush Input (FLUSH#).....................................................158

9.2.12 Page Cacheability (PWT, PCD) ................................................................159

9.2.13 RESERVED#.........................................................................................159

9.2.14 Numeric Error Reporting (FERR#, IGNNE#)..............................................159

9.2.14.1 Floating-Point Error Output (FERR#)..........................................159

9.2.14.2 Ignore Numeric Error Input (IGNNE#)........................................160

9.2.15 Bus Size Control (BS16#, BS8#) ............................................................160

9.2.16 Address Bit 20 Mask (A20M#)................................................................161

9.2.17 Write-Back Enhanced Intel

®

Quark SoC X1000 Core Signals and Other

Enhanced Bus Features .........................................................................161

9.2.17.1 Cacheability (CACHE#) ............................................................161

9.2.17.2 Cache Flush (FLUSH#).................................... .........................162

9.2.17.3 Hit/Miss to a Modified Line (HITM#)...........................................162

9.2.17.4 Soft Reset (SRESET)................................................................163

9.2.17.5 Invalidation Request (INV) ................................ .. .....................163

9.2.17.6 Write-Back/Write-Through (WB/WT#)........................................164

9.2.17.7 Pseudo-Lock Output (PLOCK#)....................... .. .. .. .....................164

9.2.18 Test Signals.........................................................................................164

9.2.18.1 Test Clock (TCK)................................. ....................................164

9.2.18.2 Test Mode Select (TMS) ...........................................................165

9.2.18.3 Test Data Input (TDI) ....................................... .. .. .. .................165

9.2.18.4 Test Data Output (TDO)...........................................................165

9.3 Interrupt and Non-Maskable Interrupt Interface...................................................165

9.3.1 Interrupt Logic .....................................................................................166

9.3.2 NMI Logic............................................................................................166

9.3.3 SMI# Logic..........................................................................................166

9.3.4 STPCLK# Logic.....................................................................................167

9.4 Write Buffers...................................................................................................167

9.4.1 Write Buffers and I/O Cycles ..................................................................169

9.4.2 Write Buffers on Locked Bus Cycles.........................................................169

9.5 Reset and Initialization.....................................................................................169

9.5.1 Floating-Point Register Values ................................................................170

9.5.2 Pin State During Reset ..........................................................................171

9.5.2.1 Controlling the CLK Signal in the Processor during Power On.........173

9.5.2.2 FERR# Pin State During Reset for Intel

®

Quark SoC X1000 Core ...173

9.5.2.3 Power Down Mode (In-circuit Emulator Support)..........................174

9.6 Clock Control ..................................................................................................174

9.6.1 Stop Grant Bus Cycles...........................................................................174

9.6.2 Pin State During Stop Grant...................................................................175

®

Quark SoC X1000 Core

Intel

Developer’s Manual October 2013

8 Order Number: 329679-001US

Page 9

Contents—Intel

®

Quark Core

9.6.3 Write-Back Enhanced Intel® Quark SoC X1000 Core Pin States During Stop

Grant State ......................................................................................... 176

9.6.4 Clock Control State Diagram.................................................................. 177

9.6.4.1 Normal State.......................................................................... 177

9.6.4.2 Stop Grant State .................................................................... 177

9.6.4.3 Stop Clock State..................................................................... 179

9.6.4.4 Auto HALT Power Down State................................................... 179

9.6.4.5 Stop Clock Snoop State (Cache Invalidations)............................. 179

9.6.4.6 Auto Idle Power Down State..................................................... 180

9.6.5 Write-Back Enhanced Intel

®

Quark SoC X1000 Core Clock Control State

Diagram.............................................................................................. 180

9.6.5.1 Normal State.......................................................................... 180

9.6.5.2 Stop Grant State .................................................................... 181

9.6.5.3 Stop Clock State..................................................................... 182

9.6.5.4 Auto HALT Power Down State................................................... 182

9.6.6 Stop Clock Snoop State (Cache Invalidations) .......................................... 183

9.6.6.1 Auto HALT Power Down Flush State (Cache Flush) for the

Write-Back Enhanced Intel

®

Quark SoC X1000 Core.................... 183

10.0 Bus Operation.......................................................................................................... 184

10.1 Data Transfer Mechanism................................................................................. 184

10.1.1 Memory and I/O Spaces......................................... .. .. .. ......................... 184

10.1.1.1 Memory and I/O Space Organization ......................................... 185

10.1.2 Dynamic Data Bus Sizing....................................................................... 186

10.1.3 Interfacing with 8-, 16-, and 32-Bit Memories.......................................... 187

10.1.4 Dynamic Bus Sizing during Cache Line Files............................................. 191

10.1.5 Operand Alignment............................................................................... 192

10.2 Bus Arbitration Logic........................................................................................ 193

10.3 Bus Functional Description................................................................................ 196

10.3.1 Non-Cacheable Non-Burst Single Cycles .................................................. 196

10.3.1.1 No Wait States ....................................................................... 196

10.3.1.2 Inserting Wait States....................... .. ............................ .. ........ 197

10.3.2 Multiple and Burst Cycle Bus Transfers....................... ............................. 198

10.3.2.1 Burst Cycles........................................................................... 198

10.3.2.2 Terminating Multiple and Burst Cycle Transfers........................... 199

10.3.2.3 Non-Cacheable, Non-Burst, Multiple Cycle Transfers.................... 200

10.3.2.4 Non-Cacheable Burst Cycles..................................................... 200

10.3.3 Cacheable Cycles ................................................................................. 201

10.3.3.1 Byte Enables during a Cache Line Fill......................................... 202

10.3.3.2 Non-Burst Cacheable Cycles................................................... .. 202

10.3.3.3 Burst Cacheable Cycles............................................................ 203

10.3.3.4 Effect of Changing KEN# during a Cache Line Fill ........................ 204

10.3.4 Burst Mode Details ............................................................................... 205

10.3.4.1 Adding Wait States to Burst Cycles............................................ 205

10.3.4.2 Burst and Cache Line Fill Order................................................. 206

10.3.4.3 Interrupted Burst Cycles.......................................................... 207

10.3.5 8- and 16-Bit Cycles............................................................................. 209

10.3.6 Locked Cycles.............................................. .. ...................................... 211

10.3.7 Pseudo-Locked Cycles........................................................................... 212

10.3.7.1 Floating-Point Read and Write Cycles......................................... 213

10.3.8 Invalidate Cycles.................................................................................. 213

10.3.8.1 Rate of Invalidate Cycles ......................................................... 215

10.3.8.2 Running Invalidate Cycles Concurrently with Line Fills.................. 215

10.3.9 Bus Hold............................................................................................. 217

10.3.10Interrupt Acknowledge.......................................................................... 219

10.3.11 Special Bus Cycles................................................................................ 220

10.3.11.1HALT Indication Cycle............................ ............................ ...... 220

October 2013 Developer’s Manual

Order Number: 329679-001US 9

Intel® Quark SoC X1000 Core

Page 10

Intel® Quark Core—Contents

10.3.11.2Shutdown Indication Cycle .......................................................221

10.3.11.3Stop Grant Indication Cycle......................................................221

10.3.12Bus Cycle Restart .................................................................................222

10.3.13Bus States ...........................................................................................224

10.3.14Floating-Point Error Handling for the Intel

10.3.14.1Floating-Point Exceptions .........................................................225

®

10.3.15Intel

Quark SoC X1000 Core Floating-Point Error Handling in

AT-Compatible Systems.........................................................................226

10.4 Enhanced Bus Mode Operation for the Write-Back Enhanced Intel

®

Quark SoC X1000 Core.............225

®

Quark SoC X1000

Core .............................................................................................................. 226

10.4.1 Summary of Bus Differences ..................................................................226

10.4.2 Burst Cycles.........................................................................................227

10.4.2.1 Non-Cacheable Burst Operation.................................................227

10.4.2.2 Burst Cycle Signal Protocol.......................................................228

10.4.3 Cache Consistency Cycles ......................................................................228

10.4.3.1 Snoop Collision with a Current Cache Line Operation....................229

10.4.3.2 Snoop under AHOLD................................................................230

10.4.3.3 Snoop During Replacement Write-Back ......................................234

10.4.3.4 Snoop under BOFF# ................................................................235

10.4.3.5 Snoop under HOLD..................................................................237

10.4.3.6 Snoop under HOLD during Replacement Write-Back.....................239

10.4.4 Locked Cycles ......................................................................................239

10.4.4.1 Snoop/Lock Collision................................................................241

10.4.5 Flush Operation....................................................................................241

10.4.6 Pseudo Locked Cycles............................................................................242

10.4.6.1 Snoop under AHOLD during Pseudo-Locked Cycles.......................242

10.4.6.2 Snoop under HOLD during Pseudo-Locked Cycles.........................243

10.4.6.3 Snoop under BOFF# Overlaying a Pseudo-Locked Cycle................244

11.0 Debugging Support...................................................................................................246

11.1 Breakpoint Instruction......................................................................................246

11.2 Single-Step Trap.................. ............................ ........................... .....................246

11.3 Debug Registers......................... .. ......................... .. ......................... .. ... ..........246

11.3.1 Linear Address Breakpoint Registers (DR[3:0]).........................................247

11.3.2 Debug Control Register (DR7) .............................. .. ... .. ...........................247

11.3.3 Debug Status Register (DR6) ........................... .. .. .. ................................250

11.3.4 Use of Resume Flag (RF) in Flag Register.................................................251

12.0 Instruction Set Summary...........................................................................................252

12.1 Instruction Set ................................................................................................252

12.1.1 Floating-Point Instructions .....................................................................253

12.2 Instruction Encoding ........................................................................................253

12.2.1 Overview.............................................................................................253

12.2.2 32-Bit Extensions of the Instruction Set...................................................254

12.2.3 Encoding of Integer Instruction Fields......................................................255

12.2.3.1 Encoding of Operand Length (w) Field........................................255

12.2.3.2 Encoding of the General Register (reg) Field ...............................255

12.2.3.3 Encoding of the Segment Register (sreg) Field ............................256

12.2.3.4 Encoding of Address Mode........................................................257

12.2.3.5 Encoding of Operation Direction (d) Field....................................260

12.2.3.6 Encoding of Sign-Extend (s) Field..............................................261

12.2.3.7 Encoding of Conditional Test (tttn) Field .....................................261

12.2.3.8 Encoding of Control or Debug or Test Register (eee) Field.............261

12.2.4 Encoding of Floating-Point Instruction Fields.............................................262

12.2.5 Intel

®

Quark SoC X1000 Core Instructions...............................................263

12.2.5.1 CMPXCHG8B - Compare and Exchange Bytes..............................263

12.2.5.2 RDMSR ..................................................................................264

®

Quark SoC X1000 Core

Intel

Developer’s Manual October 2013

10 Order Number: 329679-001US

Page 11

Contents—Intel

®

Quark Core

12.2.5.3 RDTSC .................................................................................. 264

12.2.5.4 WRMSR ................................................................................. 264

12.3 Clock Count Summary ..................................................................................... 265

12.3.1 Instruction Clock Count Assumptions ...................................................... 265

A Signal Descriptions.............................. ........................... ........................... ............... 291

B Testability ............................................................................................................... 296

B.1 On-Chip Cache Testing..................................................................................... 296

B.1.1 Cache Testing Registers TR3, TR4 and TR5.............................................. 296

B.1.2 Cache Testability Write ......................................................................... 297

B.1.3 Cache Testability Read.......................................................................... 298

B.1.4 Flush Cache............... ... .. ..................................................................... 299

B.1.5 Additional Cache Testing Features for Write-Back Enhanced Intel® Quark

SoC X1000 Core................................................................................... 299

B.2 Translation Lookaside Buffer (TLB) Testing ......................................................... 300

B.2.1 Translation Lookaside Buffer Organization................................................ 300

B.2.2 TLB Test Registers TR6 and TR7............................................................. 301

B.2.2.1 Command Test Register: TR6........................ ........................... 301

B.2.2.2 Data Test Register: TR7........................................................... 303

B.2.3 TLB Write Test ..................................................................................... 303

B.2.4 TLB Lookup Test .................................................................................. 304

®

B.3 Intel

Quark SoC X1000 Core JTAG................................................................... 304

B.3.1 Test Access Port (TAP) Controller ........................................................... 304

B.3.1.1 Test-Logic-Reset State ............................................................ 305

B.3.1.2 Run-Test/Idle State................................................................. 305

B.3.1.3 Select-DR-Scan State.............................................................. 305

B.3.1.4 Capture-DR State ................................................................... 306

B.3.1.5 Shift-DR State........................................................................ 306

B.3.1.6 Exit1-DR State .................................................. .. ................... 306

B.3.1.7 Pause-DR State...................................................................... 306

B.3.1.8 Exit2-DR State .................................................. .. ................... 306

B.3.1.9 Update-DR State .................................................................... 307

B.3.1.10 Select-IR-Scan State............................................................... 307

B.3.1.11 Capture-IR State .................................................................... 307

B.3.1.12 Shift-IR State......................................................................... 307

B.3.1.13 Exit1-IR State ........................................................................ 307

B.3.1.14 Pause-IR State....................................................................... 307

B.3.1.15 Exit2-IR State ........................................................................ 308

B.3.1.16 Update-IR State ..................................................................... 308

B.3.2 TAP Controller Initialization.................................................................... 308

C Feature Determination .............................................................................................. 309

C.1 CPUID Instruction ........................................................................................... 309

C.2 Intel

®

Quark SoC X1000 Stepping..................................................................... 311

Figures

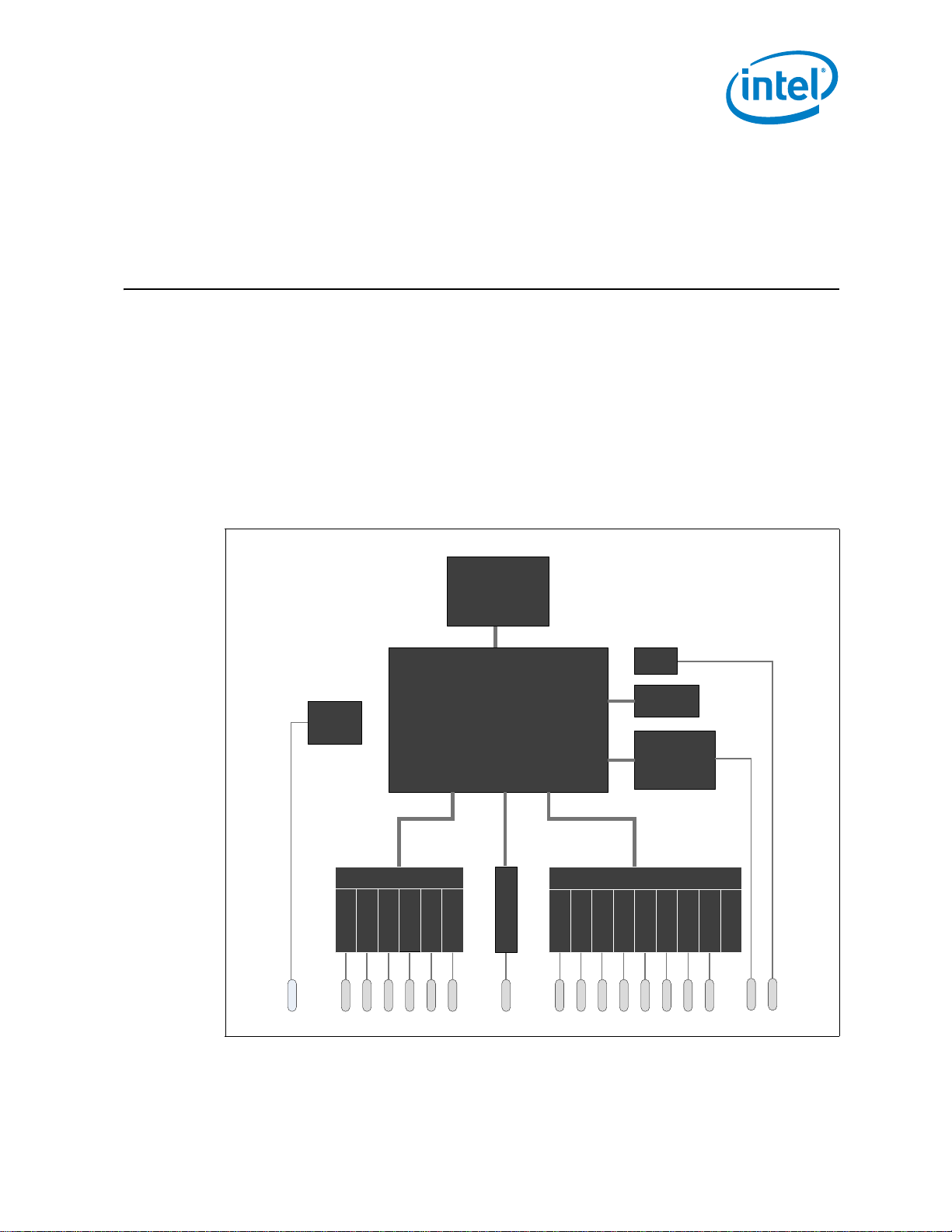

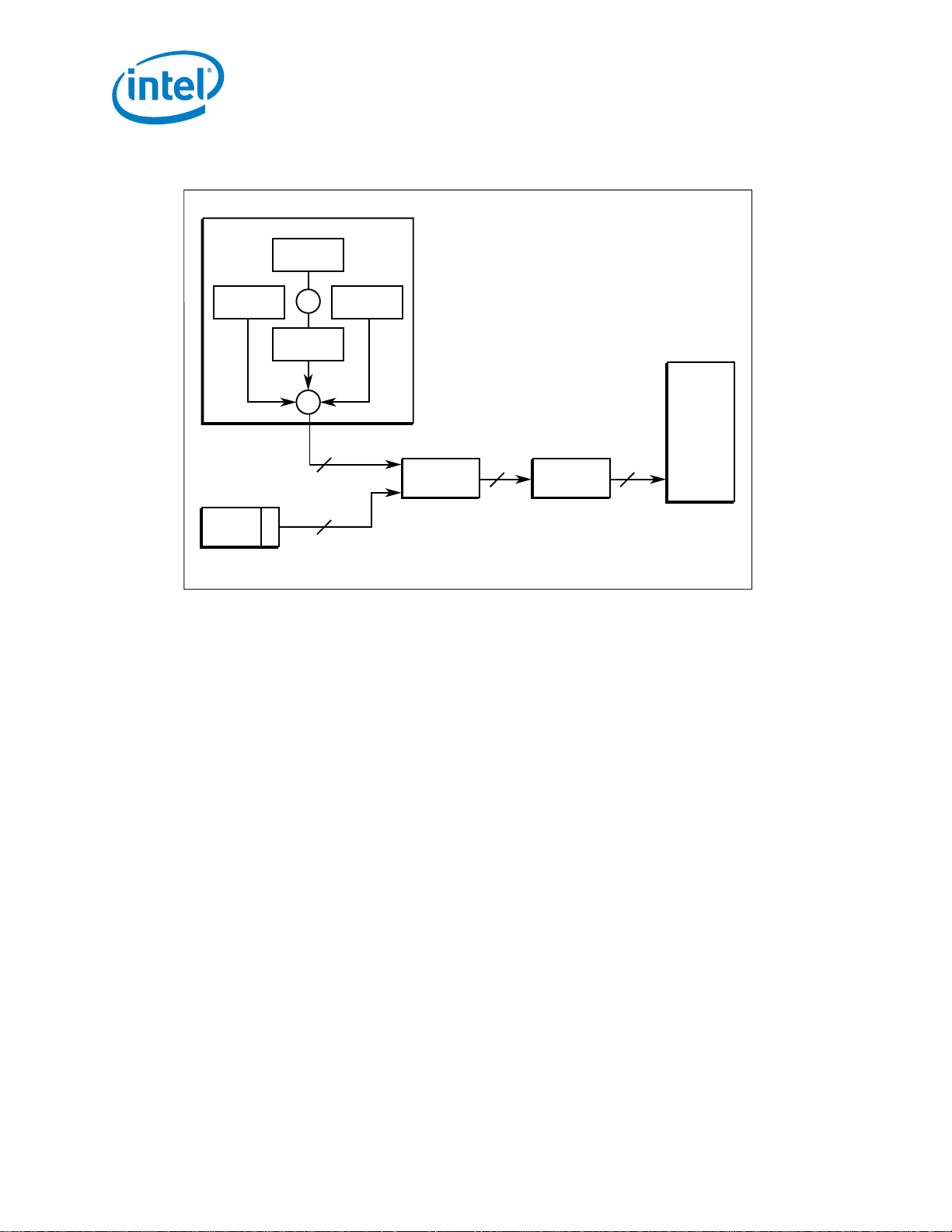

1Intel® Quark SoC X1000 Core used in Intel® Quark SoC X1000 .....................................21

2 Address Translation......................... .. ........................... ........................... .................24

3 Addressing Mode Calculations....................................................................................27

4 Data Types ............................. ................................................... .. .. .........................29

5 Data Types ............................. ................................................... .. .. .........................31

6 String and ASCII Data Types.....................................................................................32

7 Pointer Data Types................................ .. ........................... ............................ ..........32

8 Big vs. Little Endian Memory Format...........................................................................33

October 2013 Developer’s Manual

Order Number: 329679-001US 11

Intel® Quark SoC X1000 Core

Page 12

Intel® Quark Core—Contents

9 Base Architecture Registers .......................................................................................40

10 Flag Registers..........................................................................................................41

11 Intel

®

Quark SoC X1000 Core Segment Registers and Associated Descriptor Cache

Registers.................................................................................................................45

12 System-Level Registers.............................................................................................46

13 Control Registers .....................................................................................................47

14 Intel

®

Quark SoC X1000 Core CR4 Register.................................................................52

15 Floating-Point Registers.............................................................................................53

16 Floating-Point Tag Word............................................................................................54

17 Floating-Point Status Word ........................................................................................55

18 Protected Mode FPU Instructions and Data Pointer Image in Memory (32-Bit Format) ........59

19 Real Mode FPU Instruction and Data Pointer Image in Memory (32-Bit Format).................59

20 Protected Mode FPU Instruction and Data Pointer Image in Memory (16-Bit Format)..........60

21 Real Mode FPU Instruction and Data Pointer Image in Memory (16-Bit Format).................60

22 FPU Control Word.....................................................................................................61

23 Real Address Mode Addressing...................................................................................66

24 Protected Mode Addressing........................................................................................69

25 Paging and Segmentation..........................................................................................69

26 Descriptor Table Registers.........................................................................................71

27 Interrupt Descriptor Table Register Use.......................................................................72

28 Segment Descriptors..................... .. ... ........................... .. ........................... ...............73

29 System Segment Descriptors .....................................................................................75

30 Gate Descriptor Formats............................................................................................76

31 Example Descriptor Selection.................. .. .. .. ........................... ... .. ........................... ..78

32 Segment Descriptor Caches for Real Address Mode (Segment Limit and Attributes Are

Fixed).....................................................................................................................79

33 Segment Descriptor Caches for Protected Mode (Loaded per Descriptor) ..........................80

34 Segment Descriptor Caches for Virtual 8086 Mode within Protected Mode (Segment Limit

and Attributes are Fixed)................................................................ ...........................81

35 Four-Level Hierarchical Protection...............................................................................82

36 Intel

37 Sample I/O Permission Bit Map ..................................................................................85

38 Intel

®

Quark Core TSS and TSS Registers....................................................................84

®

Quark Core TSS .............................................................................................88

39 Simple Protected System........................................... ........................... .. ...................90

40 GDT Descriptors for Simple System.................. ............................ .. .. .. .........................91

41 Linear-Address Translation to a 4-KByte Page using PAE Paging......................................95

42 Linear-Address Translation to a 2-MByte Page using PAE Paging .....................................96

43 Formats of CR3 and Paging-Structure Entries in 32-bit Mode with PAE Paging Disabled ......98

44 Formats of CR3 and Paging-Structure Entries in 32-bit Mode with PAE Paging Enabled.......99

45 Translation Lookaside Buffer ....................................................................................104

46 Page-Fault Error Code.............................................................................................105

47 Page Fault System Information...................... .. .........................................................107

48 Virtual 8086 Environment Memory Management .........................................................108

49 Virtual 8086 Environment Interrupt and Call Handling .................................................111

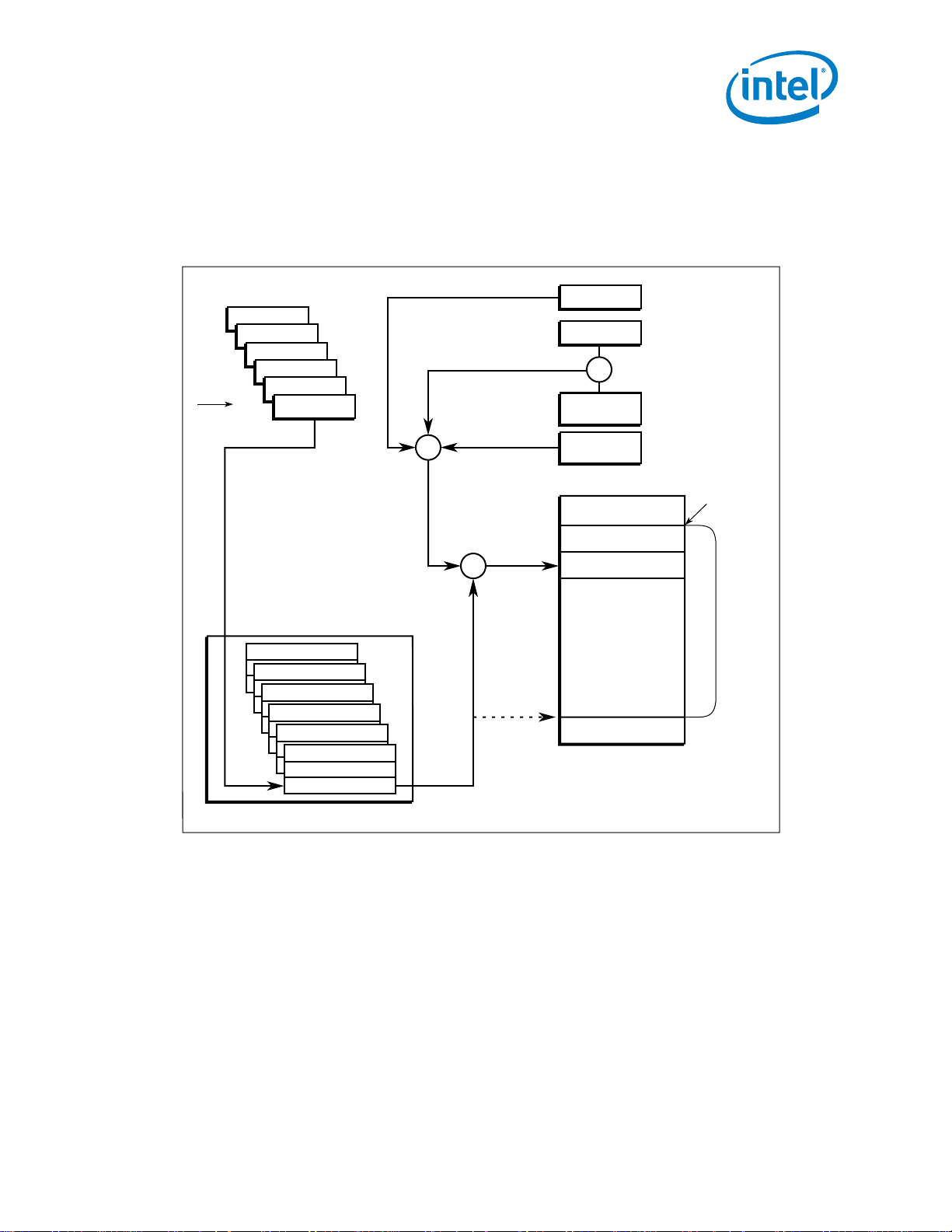

50 On-Chip Cache Physical Organization ........................................................................114

51 On-Chip Cache Replacement Strategy.......................................................................119

52 Page Cacheability ...................................................................................................121

53 Basic SMI# Interrupt Service ...................................................................................128

54 Basic SMI# Hardware Interface................................................................................129

55 SMI# Timing for Servicing an I/O Trap......................................................................130

56 Intel

®

Quark SoC X1000 Core SMIACT# Timing..........................................................130

57 Redirecting System Memory Addresses to SMRAM.......................................................132

58 Transition to and from System Management Mode ......................................................135

59 SMM Revision Identifier...........................................................................................138

60 Auto HALT Restart..................................................................................................139

®

Quark SoC X1000 Core

Intel

Developer’s Manual October 2013

12 Order Number: 329679-001US

Page 13

Contents—Intel

®

Quark Core

61 I/O Instruction Restart............................................................................................ 139

62 SMM Base Location ................................................................................................ 140

63 SMRAM Usage .................................... ......................... .. .. ...................................... 141

64 SMRAM Location ............................. ........................... ........................... ................. 142

65 FLUSH# Mechanism during SMM........................................................... .. .. ............... 143

66 Cached SMM ......................................................................................................... 143

67 Non-Cached SMM................................................................................................... 144

68 Write-Back Enhanced Intel

®

Quark SoC X1000 Core Cache Flushing for Overlaid

SMRAM upon Entry and Exit of Cached SMM.............................................................. 145

69 Functional Signal Groupings .................................................................................... 150

70 Reordering of a Reads with Write Buffers................................................................... 168

71 Reordering of a Reads with Write Buffers................................................................... 168

72 Pin States During RESET......................................................................................... 172

73 Stop Clock Protocol ................................................................................................ 175

74 Intel

75 Recognition of Inputs when Exiting Stop Grant State .................................................. 179

76 Write-Back Enhanced Intel

®

Quark SoC X1000 Core Stop Clock State Machine ............. .. .............................. 178

®

Quark SoC X1000 Core Stop Clock State Machine

(Enhanced

Bus Configuration) ................................................................................................. 181

77 Physical Memory and I/O Spaces.............................................................................. 185

78 Physical Memory and I/O Space Organization............................................................. 186

79 Intel

®

Quark SoC X1000 Core with 32-Bit Memory ..................... .. .... .. .. .... .. ................ 188

80 Addressing 16- and 8-Bit Memories.......................................................................... 188

81 Logic to Generate A1, BHE# and BLE# for 16-Bit Buses .............................................. 190

82 Data Bus Interface to 16- and 8-Bit Memories............................................................ 191

83 Single Master Intel

®

Quark Core System................................................................... 193

84 Single Intel® Quark Core with DMA .......................................................................... 194

85 Single Intel® Quark Core with Multiple Secondary Masters........................................... 195

86 Basic 2-2 Bus Cycle................................................................................................ 197

87 Basic 3-3 Bus Cycle................................................................................................ 198

88 Non-Cacheable, Non-Burst, Multiple-Cycle Transfers................................................... 200

89 Non-Cacheable Burst Cycle...................................................................................... 201

90 Non-Burst, Cacheable Cycles................................................................................... 203

91 Burst Cacheable Cycle ................................... ............................ .. ........................... 204

92 Effect of Changing KEN#......................................................................................... 205

93 Slow Burst Cycle.................................................................................................... 206

94 Burst Cycle Showing Order of Addresses ................................................................... 207

95 Interrupted Burst Cycle........................................................................................... 208

96 Interrupted Burst Cycle with Non-Obvious Order of Addresses...................................... 209

97 8-Bit Bus Size Cycle ............................................................................................... 210

98 Burst Write as a Result of BS8# or BS16#.................................... ........................... .. 211

99 Locked Bus Cycle................................................................................................... 212

100 Pseudo Lock Timing................................................................................................ 213

101 Fast Internal Cache Invalidation Cycle ...................................................................... 214

102 Typical Internal Cache Invalidation Cycle................................................................... 214

103 System with Second-Level Cache............................................................................. 216

104 Cache Invalidation Cycle Concurrent with Line Fill....................................................... 217

105 HOLD/HLDA Cycles................................................................................................. 218

106 HOLD Request Acknowledged during BOFF# .............................................................. 219

107 Interrupt Acknowledge Cycles.................................................................................. 220

108 Stop Grant Bus Cycle.............................................................................................. 221

109 Restarted Read Cycle.............................................................................................. 222

110 Restarted Write Cycle............................................................................................. 223

111 Bus State Diagram................................................................................................. 224

112 Basic Burst Read Cycle ........................................................................................... 227

October 2013 Developer’s Manual

Order Number: 329679-001US 13

Intel® Quark SoC X1000 Core

Page 14

Intel® Quark Core—Contents

113 Snoop Cycle Invalidating a Modified Line ...................................................................231

114 Snoop Cycle Overlaying a Line-Fill Cycle....................................................................232

115 Snoop Cycle Overlaying a Non-Burst Cycle.................................................................233

116 Snoop to the Line that is Being Replaced ...................................................................234

117 Snoop under BOFF# during a Cache Line-Fill Cycle......................................................236

118 Snoop under BOFF# to the Line that is Being Replaced................................................237

119 Snoop under HOLD during Line Fill............................................................................238

120 Snoop using HOLD during a Non-Cacheable, Non-Burstable Code Prefetch .....................239

121 Locked Cycles (Back-to-Back) ............................................ .. .. .. ............................ .. ..240

122 Snoop Cycle Overlaying a Locked Cycle.....................................................................241

123 Flush Cycle.......................................................................... ............................ ......242

124 Snoop under AHOLD Overlaying Pseudo-Locked Cycle .................................................243

125 Snoop under HOLD Overlaying Pseudo-Locked Cycle ...................................................244

126 Snoop under BOFF# Overlaying a Pseudo-Locked Cycle...............................................245

127 Size Breakpoint Fields............................................................................................. 248

128 General Instruction Format .....................................................................................253

129 Intel

130 TR4 Definition for Standard and Enhanced Bus Modes for the Write-Back Enhanced

131 TR5 Definition for Standard and Enhanced Bus Modes for the Write-Back Enhanced

®

Quark SoC X1000 Core Cache Test Registers....................................................296

®

Intel

Quark SoC X1000 Core..................................................................................300

®

Intel

Quark SoC X1000 Core..................................................................................300

132 TLB Organization....................................................................................................301

133 TLB Test Registers..................................................................................................302

134 TAP Controller State Diagram...................................................................................305

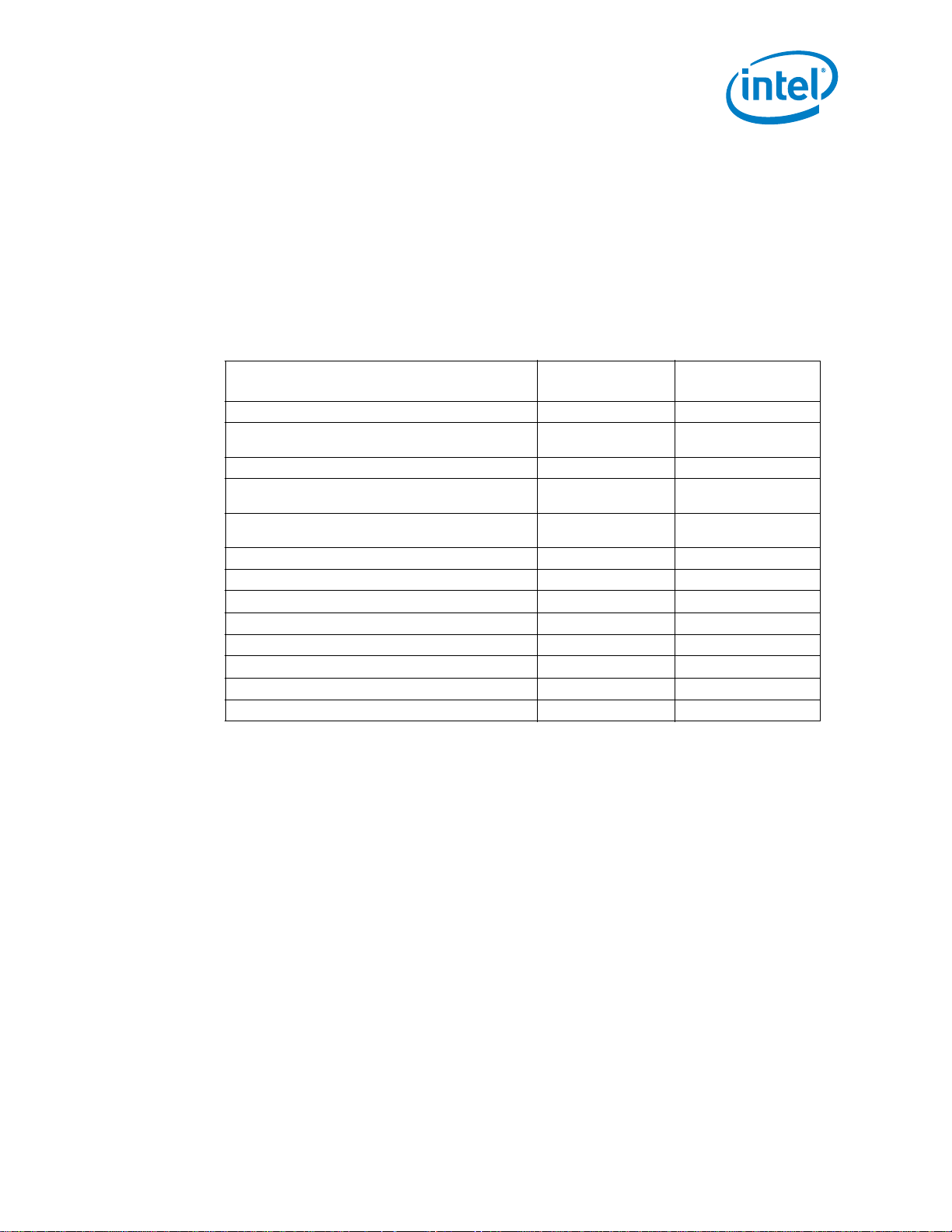

Tables

1 Manual Contents ......................................................................................................17

2 Related Documents...................................................................................................20

3 Segment Register Selection Rules............................... .. .. ........................... .. ... ............25

4 BASE and INDEX Registers for 16- and 32-Bit Addresses ...............................................28

5 Interrupt Vector Assignments.....................................................................................35

6 FPU Interrupt Vector Assignments ..............................................................................35

7 Sequence of Exception Checking.................................................................................37

8 Interrupt Vectors Used by FPU ................................................. ... ........................... ....38

9 Data Type Alignment Requirements ............................................................................42

10 Intel

11 On-Chip Cache Control Modes ............................................ ............................ .. .. ........48

12 Recommended Values of the Floating-Point Related Bits for Intel

13 Interpreting Different Combinations of EM, TS and MP Bits.............................................50

14 Condition Code Interpretation after FPREM and FPREM1 Instructions ...............................56

15 Floating-Point Condition Code Interpretation ................................................................56

16 Condition Code Resulting from Comparison..................................................................57

17 Condition Code Defining Operand Class.......................................................................57

18 FPU Exceptions ........................................................................................................58

19 Debug Registers.......................................................................................................62

20 Test Registers..........................................................................................................62

21 Register Usage.........................................................................................................63

22 FPU Register Usage Differences..................................................................................63

23 MSRs for Intel

24 Instruction Forms in which LOCK Prefix Is Legal............................................................65

25 Exceptions with Different Meanings in Real Mode (see Table 24) .....................................67

26 Access Rights Byte Definition for Code and Data Descriptions.........................................74

27 Pointer Test Instructions............................................................................................85

®

Quark SoC X1000 Core Operating Modes............................................................48

®

Quark SoC X1000

Core.......................................................................................................................50

®

Quark Core 1 ....................................................................................64

®

Quark SoC X1000 Core

Intel

Developer’s Manual October 2013

14 Order Number: 329679-001US

Page 15

Contents—Intel

®

Quark Core

28 Descriptor Types Used for Control Transfer..................................................................86

29 Use of CR3 with PAE Paging.......................................................................................93

30 Format of a PAE Page-Directory-Pointer-Table Entry (PDPTE).........................................94

31 Format of a PAE Page-Directory Entry that Maps a 2-MByte Page....................................96

32 Format of a PAE Page-Directory Entry that References a Page Table................................97

33 Format of a PAE Page-Table Entry that Maps a 4-KByte Page .........................................97

34 Page Level Protection Attributes................................. .. .. ........................... ... .. .. ........ 103

35 Write-Back Enhanced Intel

®

Quark SoC X1000 Core WB/WT# Initialization.................... 115

36 Cache Operating Modes .......................................................................................... 116

37 Write-Back Enhanced Intel® Quark SoC X1000 Core Write-Back Cache Operating

Modes .................................................................................................................. 117

38 Encoding of the Special Cycles for Write-Back Cache ................................................... 119

39 Cache State Transitions for Write-Back Enhanced Intel® Quark SoC X1000

Core-Initiated Unlocked Read Cycles......................................................................... 124

40 Cache State Transitions for Write-Back Enhanced Intel

®

Quark SoC X1000

Core-Initiated Write Cycles...................................................................................... 125

41 Cache State Transitions During Snoop Cycles............................................................. 125

42 SMRAM State Save Map.......................................................................................... 132

43 SMM Initial Processor Core Register Settings ............................................................. 136

44 Bit Values for SMM Revision Identifier....................................................................... 138

45 Bit Values for Auto HALT Restart.............................................................................. 139

46 I/O Instruction Restart Value................................................................................... 140

47 Cache Flushing (Non-Overlaid SMRAM) ..................................................................... 144

48 Cache Flushing (Overlaid SMRAM)............................................................................ 145

49 ADS# Initiated Bus Cycle Definitions ........................................................................ 152

50 Differences between CACHE# and PCD ..................................................................... 161

51 CACHE# vs. Other Intel

52 HITM# vs. Other Intel® Quark Core Signals............................................................... 163

53 INV vs. Other Intel

®

Quark Core Signals ............................................................ 162

®

Quark Core Signals................................................................... 163

54 WB/WT# vs. Other Intel® Quark Core Signals............................................................ 164

55 Register Values after Reset...................................................................................... 170

56 Floating-Point Values after Reset.............................................................................. 170

57 FERR# Pin State after Reset and before FP Instructions............................................... 174

58 Pin State during Stop Grant Bus State ...................................................................... 175

59 Write-Back Enhanced Intel

®

Quark SoC X1000 Core Pin States during Stop Grant Bus

Cycle.................................................................................................................... 176

60 Byte Enables and Associated Data and Operand Bytes................................................. 184

61 Generating A[31:0] from BE[3:0]# and A[31:A2]....................................................... 185

62 Next Byte Enable Values for BSx# Cycles.................................................................. 187

63 Data Pins Read with Different Bus Sizes.................................................................... 187

64 Generating A1, BHE# and BLE# for Addressing 16-Bit Devices..................................... 189

65 Generating A0, A1 and BHE# from the Intel

®

Quark SoC X1000 Core Byte Enables ........ 191

66 Transfer Bus Cycles for Bytes, Words and Dwords ...................................................... 192

67 Burst Order (Both Read and Write Bursts) ................................................................. 206

68 Special Bus Cycle Encoding ..................................................................................... 221

69 Bus State Description ............................................................................................. 224

70 Snoop Cycles under AHOLD, BOFF#, or HOLD............................................................ 228

71 Various Scenarios of a Snoop Write-Back Cycle Colliding with an On-Going Cache Fill or

Replacement Cycle................................................................................................. 230

72 Debug Registers .................................................................................................... 247

73 LENi Encoding........................................................................................................ 248

74 RW Encoding......................................................................................................... 248

75 Fields within Intel

®

Quark Core Instructions .............................................................. 254

76 Encoding of Operand Length (w) Field....................................................................... 255

77 Encoding of reg Field when the (w) Field is Not Present in Instruction............................ 255

October 2013 Developer’s Manual

Order Number: 329679-001US 15

Intel® Quark SoC X1000 Core

Page 16

Intel® Quark Core—Contents

78 Encoding of reg Field when the (w) Field is Present in Instruction..................................256

79 2-Bit sreg2 Field.....................................................................................................256

80 3-Bit sreg3 Field.....................................................................................................257

81 Encoding of 16-Bit Address Mode with “mod r/m” Byte ................................................258