Page 1

Intel® Quark™ Microcontroller D2000

Platform Design Guide

November 2016

Document Number: 333580-002EN

Page 2

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products

described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject

matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product

specifications and roadmaps.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published

specifications. Current characterized errata are available on request.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or by

visiting: http://www.intel.com/design/literature.htm

Intel technologies’ features and benefits depend on system configuration and may require enabled hardware, software or service activation.

Learn more at http://www.intel.com/ or from the OEM or retailer.

No computer system can be absolutely secure.

Intel, Quark and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries.

*Other names and brands may be claimed as the property of others.

Copyright © 2016, Intel Corporation. All rights reserved.

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

2 Document Number: 333580-002EN

Page 3

Contents

1.0 Introduction ................................................................................................................................................. 7

1.1 Overview ................................................................................................................................................................ 7

1.2 Audience and Purpose .................................................................................................................................... 7

1.3 Terminology ......................................................................................................................................................... 8

1.4 Reference Documents ..................................................................................................................................... 8

2.0 System Assumptions ................................................................................................................................. 9

2.1 General Assumptions ....................................................................................................................................... 9

2.1.1 PCB Technology and Stackup ................................................................................................ 11

2.1.2 PCB Technology Considerations .......................................................................................... 11

2.2 Backward and Forward Coupling Coefficient Calculation ............................................................ 14

2.3 Feature Set ........................................................................................................................................................ 15

2.4 CRB Pin Mapping ............................................................................................................................................ 17

3.0 Subsystem Details ....................................................................................................................................18

3.1 Design Recommendations .......................................................................................................................... 18

3.2 General Design Guideline Assumptions ............................................................................................... 19

4.0 I²C Interface ...............................................................................................................................................20

4.1 I²C Interface Signals ...................................................................................................................................... 20

4.2 Interface Routing Guidelines ..................................................................................................................... 21

4.2.1 General Design Considerations ............................................................................................. 22

5.0 Pulse Width Modulation (PWM) ............................................................................................................23

5.1 PWM Signaling ................................................................................................................................................. 24

5.2 Functional Operation .................................................................................................................................... 24

6.0 UART ...........................................................................................................................................................26

6.1 Signal Descriptions ........................................................................................................................................ 27

6.2 Features .............................................................................................................................................................. 28

7.0 SPI ................................................................................................................................................................30

7.1 Features .............................................................................................................................................................. 31

8.0 Clocking ......................................................................................................................................................33

8.1 Features .............................................................................................................................................................. 34

9.0 General Purpose I/O (GPIO) ...................................................................................................................35

9.1 Signal Descriptions ........................................................................................................................................ 35

9.2 Features .............................................................................................................................................................. 36

10.0 JTAG ............................................................................................................................................................38

11.0 Analog-to-Digital Converter (ADC) .......................................................................................................39

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 3

Page 4

11.1 Features .............................................................................................................................................................. 39

12.0 Power Delivery ..........................................................................................................................................41

12.1 DVDD Linear Regulator ................................................................................................................................ 41

12.1.1 Operation of an Active Pull – Down Circuit ...................................................................... 41

12.1.2 Implementation of an Active Pull – Down Circuit .......................................................... 41

Figures

Figure 1. Block Diagram ..................................................................................................................................................... 9

Figure 2. PCB Floor Plan ................................................................................................................................................. 10

Figure 3. System Diagram .............................................................................................................................................. 11

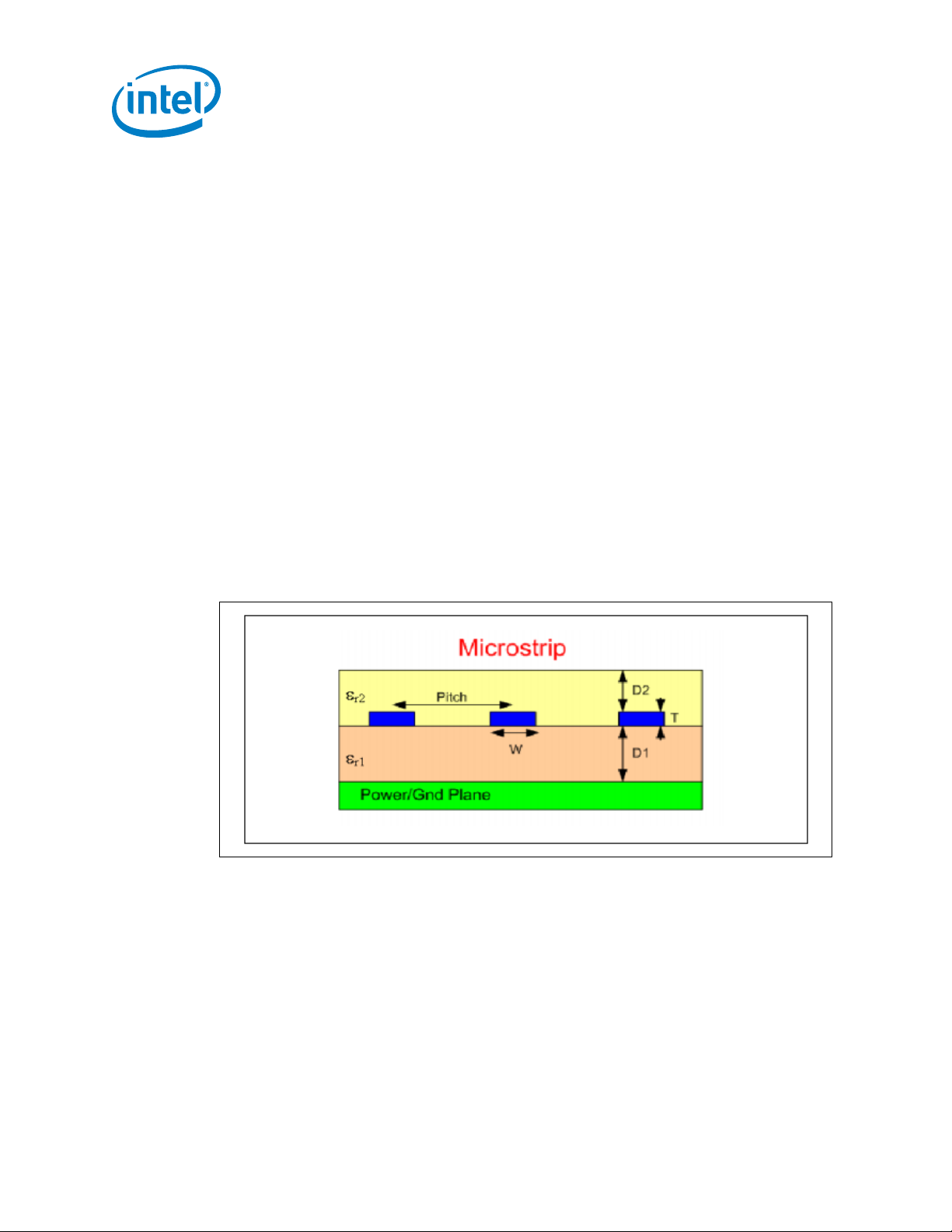

Figure 4. Single-Ended Microstrip Diagram ........................................................................................................... 12

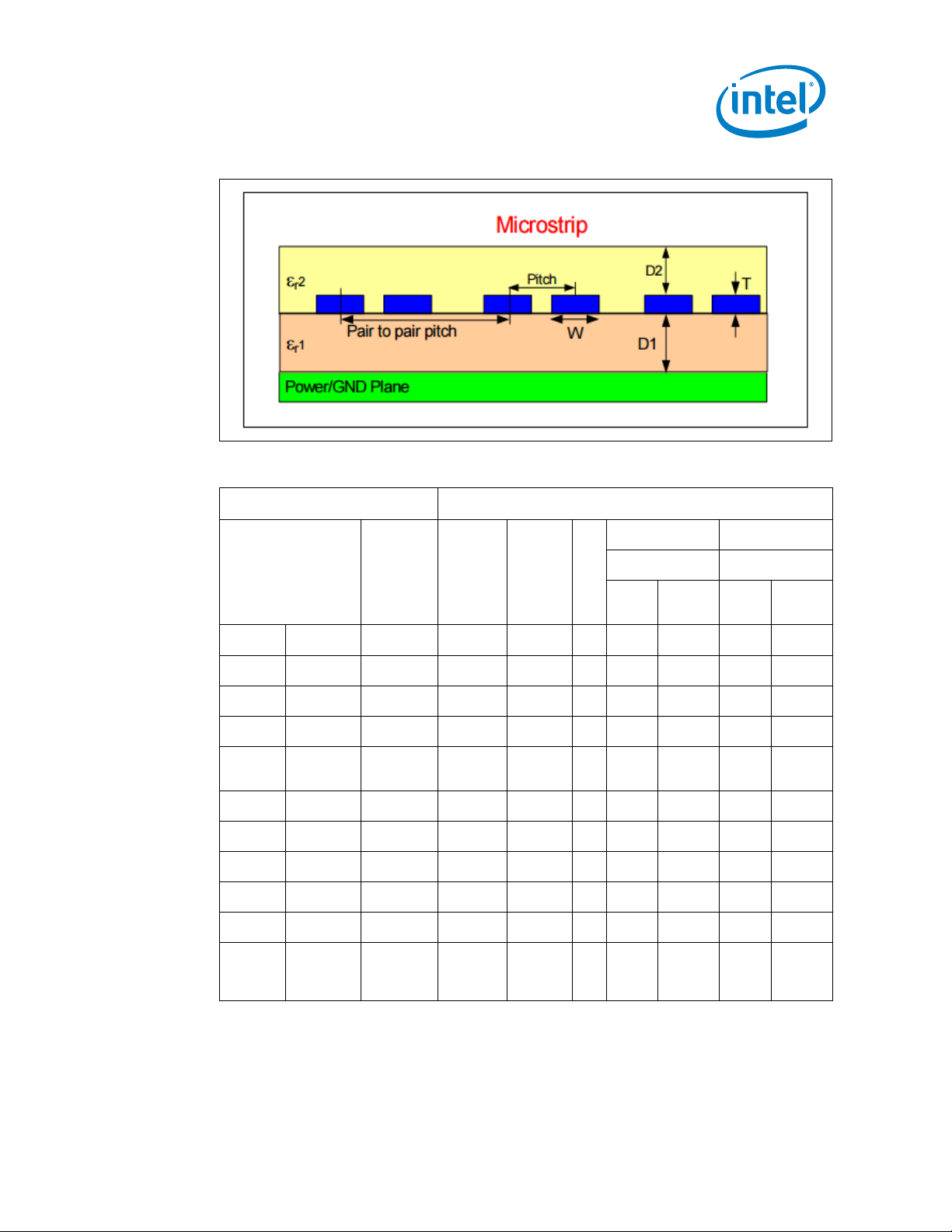

Figure 5. Differential Microstrip Diagram ................................................................................................................ 13

Figure 6. Backward Coupling Coefficient ................................................................................................................ 14

Figure 7. Forward Coupling Coefficient ................................................................................................................... 14

Figure 8. Single-Ended Kb Diagram........................................................................................................................... 15

Figure 9. Differential Kb Diagram ............................................................................................................................... 15

Figure 10. CRB Pin Mapping Diagram .......................................................................................................................... 17

Figure 11. I²C Interface....................................................................................................................................................... 20

Figure 12. I²C Point-to-Point Topology ...................................................................................................................... 21

Figure 13. PWM ..................................................................................................................................................................... 23

Figure 14. Duty Cycle of 20% .......................................................................................................................................... 24

Figure 15. Duty Cycle of 50% .......................................................................................................................................... 24

Figure 16. Duty Cycle of 80% .......................................................................................................................................... 24

Figure 17. UART .................................................................................................................................................................... 26

Figure 18. UART 2-Via Point-to-Point Topology .................................................................................................... 27

Figure 19. SPIO ...................................................................................................................................................................... 30

Figure 20. SPI Point-to-Point Single-Ended Topology ........................................................................................ 31

Figure 21. RTC ........................................................................................................................................................................ 33

Figure 22. RTC Topology ................................................................................................................................................... 34

Figure 23. GPIO ..................................................................................................................................................................... 35

Figure 24. GPIO Pin Routing Topology ....................................................................................................................... 36

Figure 25. JTAG Connectivity .......................................................................................................................................... 38

Figure 26. Analog Shielding Requirements .............................................................................................................. 39

Figure 27. Active Pull – Down circuit implementation ......................................................................................... 41

Tables

Table 1. Terminology ......................................................................................................................................................... 8

Table 2. Reference Documents ..................................................................................................................................... 8

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

4 Document Number: 333580-002EN

Page 5

Table 3. Stackup Details ................................................................................................................................................ 13

Table 4. Good Layout Practices ................................................................................................................................. 19

Table 5. I²C Point-to-Point Platform Routing Guidelines ............................................................................... 21

Table 6. PWM Timing ...................................................................................................................................................... 25

Table 7. Timer Period ..................................................................................................................................................... 25

Table 8. UART Signals .................................................................................................................................................... 27

Table 9. UART Point-to-Point Topology Platform Routing Guidelines .................................................... 28

Table 10. UART Point-to-Point Topology Platform Routing Guidelines .................................................... 28

Table 11. SPI Platform Routing Guidelines ............................................................................................................. 31

Table 12. RTC Signals........................................................................................................................................................ 34

Table 13. GPIO Pin Routing Guidelines ..................................................................................................................... 36

Table 14. Generic Routing Requirements................................................................................................................. 38

Table 15. Active Pull – Down circuit BOM ................................................................................................................ 42

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 5

Page 6

Revision History

Date

Revision

Description

November 2016

002

Memory specification updated. Power Delivery chapter added.

December 2015

001

Initial release.

§

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

6 Document Number: 333580-002EN

Page 7

Introduction

1.0 Introduction

1.1 Overview

This design guide provides motherboard implementation recommendations for the

Intel® Quark™ Microcontroller D2000 platform, based on the Intel® Quark™

Microcontroller D2000 processor. This document includes design guidelines for Intel®

Quark™ Microcontroller D2000 platforms and the hardware integration aspects that

must be considered when designing a platform.

This design guide has been developed to ensure maximum flexibility for board

designers while reducing the risk of board-related issues. Design recommendations are

based on Intel's simulations and lab experience and are strongly recommended, if not

necessary, to meet the timing and signal quality specifications. Design

recommendations are based on the reference platforms designed by Intel. They should

be used as an example but may not be applicable to particular designs.

Note: The guidelines recommended in this document are based on experience, simulation,

and preliminary validation work done at Intel while developing the Intel® Quark™

Microcontroller D2000 processor-based platform. This work is ongoing, and these

recommendations are subject to change.

Caution: If the guidelines listed in this document are not followed, it is very important that

designers perform thorough signal integrity and timing simulations. Even when

following these guidelines, Intel recommends the critical signals to be simulated to

ensure proper signal integrity and flight time. Any deviation from the guidelines should

be simulated.

Metric units are used in some sections in addition to the standard use of U.S. customary

system of units (USCS). If there is a discrepancy between the metric and USCS units,

assume the USCS unit is most accurate. The conversion factor used is 1 inch (1000

mils) = 25.4 mm.

1.2 Audience and Purpose

The Intel® Quark™ Microcontroller D2000 is a highly integrated, ultra-low-power part

designed to enable innovative wearable solutions with long battery life for

fitness/health/wellness monitors, smart watches, and so on.

This document is intended to aid platform hardware designers in system

implementation and reference design reuse by:

Documenting the hardware implementation of a specific form factor wearable

based on the Intel® Quark™ Microcontroller D2000 platform

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 7

Page 8

Providing details such as block diagrams, which illustrate connectivity, system level

Term

Description

ADC

Analog-to-Digital Converter

CRB

Customer Reference Board

GPIO

General Purpose Input/Output

I²C

Inter-Integrated Circuit

I2S

Inter-IC Sound

JTAG

Joint Test Action Group

OSC

Oscillator

PWM

Pulse Width Modulation

RTC

Real-Time Clock

SIO

Serial I/O

SoC

System on Chip

SPI

Serial Peripheral Interface

UART

Universal Asynchronous Receiver Transmitter

XTAL

Crystal

Document

Document No.

Intel® Quark™ Microcontroller D2000 Datasheet

333577

considerations, options, and design guidelines

Describing the theory of operation or principles considered in deriving a design

guideline

1.3 Terminology

Table 1. Terminology

Introduction

1.4 Reference Documents

Table 2. Reference Documents

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

8 Document Number: 333580-002EN

§

Page 9

System Assumptions

2.0 System Assumptions

2.1 General Assumptions

This section covers general Intel® Quark™ Microcontroller D2000 and Intel® Quark™

Microcontroller D2000 Customer Reference Board (CRB) system topology and interface

connectivity assumptions. The Intel® Quark™ Microcontroller D2000 CRB is used as a

baseline reference example for guidelines.

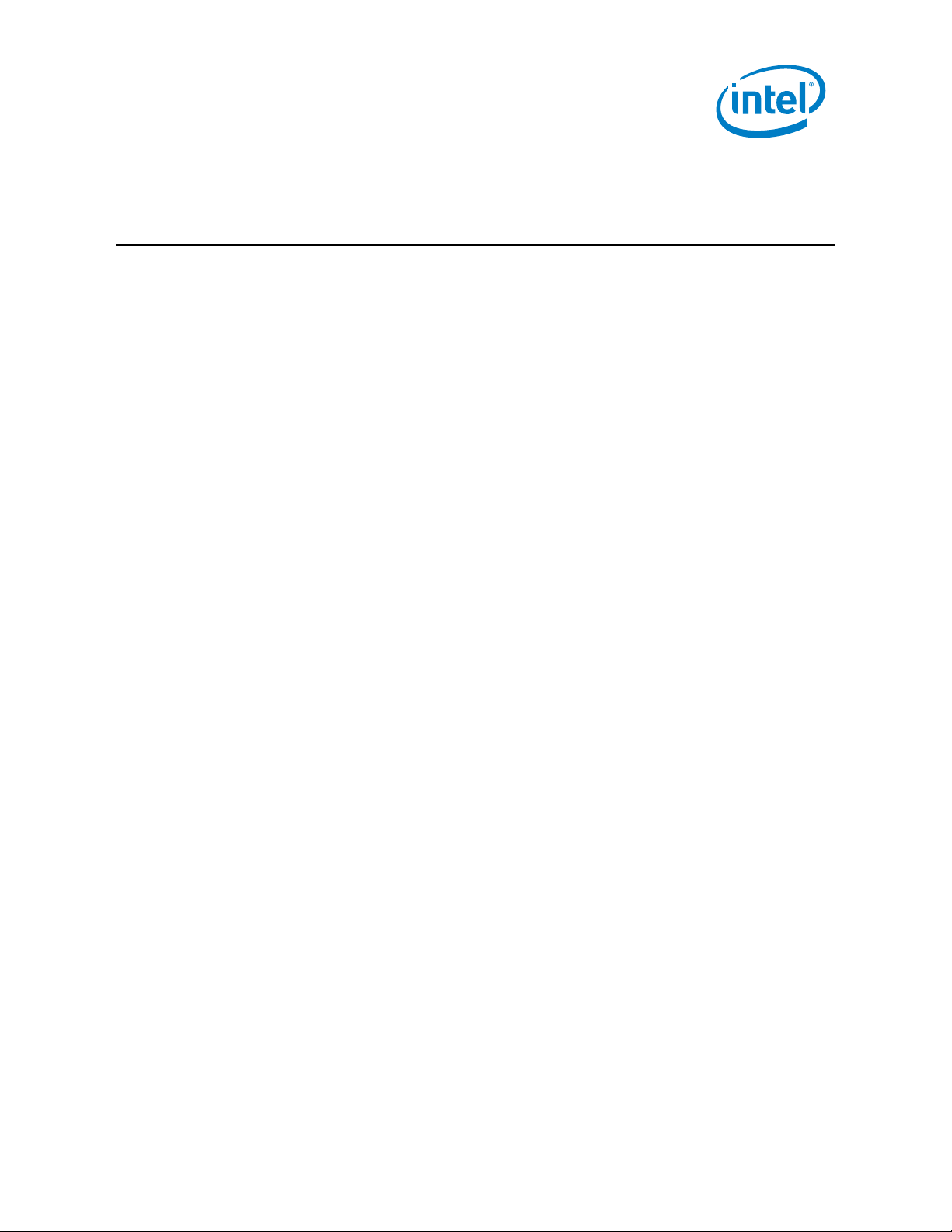

Figure 1. Block Diagram

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 9

Page 10

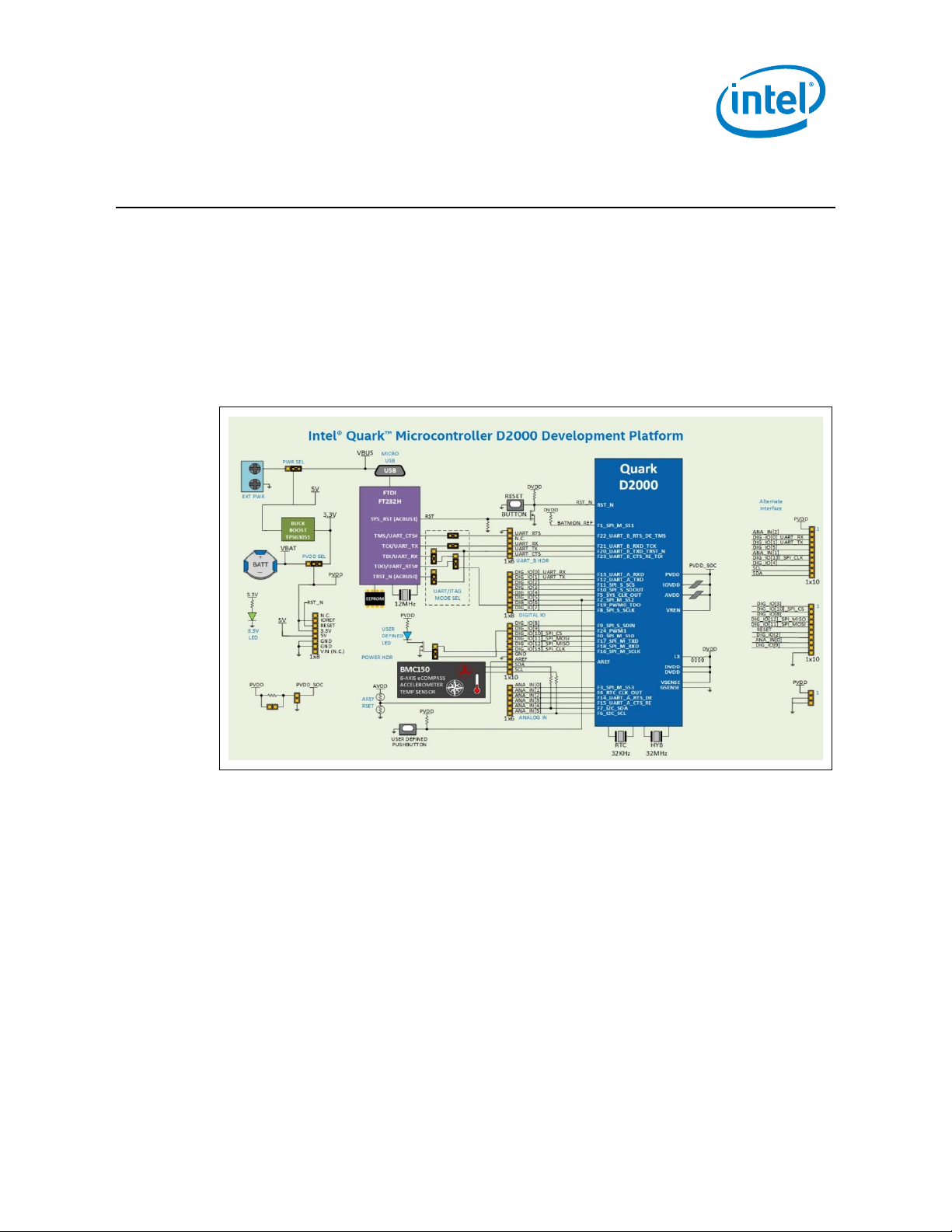

Figure 2. PCB Floor Plan

System Assumptions

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

10 Document Number: 333580-002EN

Page 11

System Assumptions

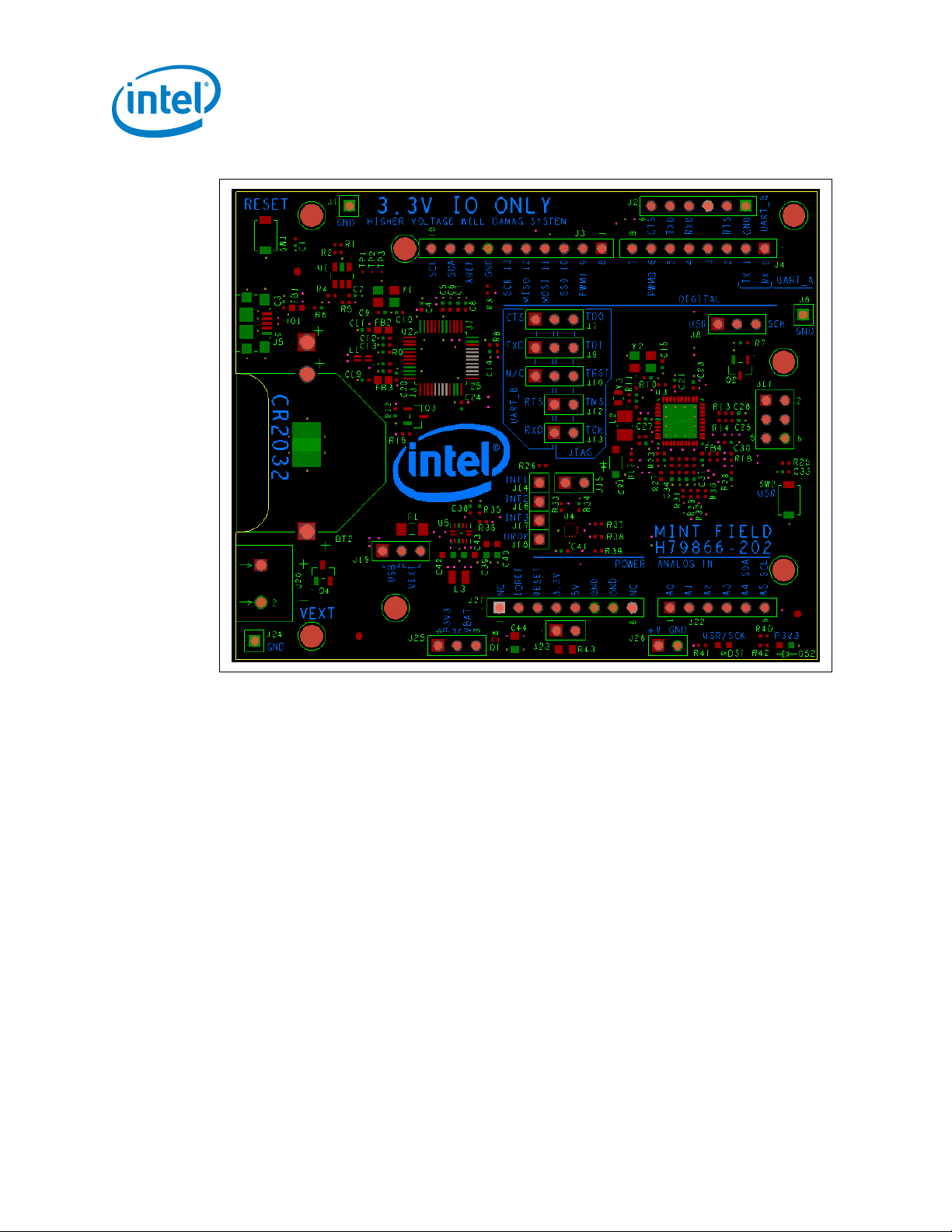

Figure 3. System Diagram

2.1.1 PCB Technology and Stackup

The system uses the PCB technology of a standard interconnect, Type 3, 4-layer board,

no blind or buried vias. It is important to note that variations in the stackup of a

motherboard, such as changes in the dielectric height, trace widths, and spacing, can

impact the impedance, loss, and jitter characteristics of all the interfaces. Such changes

may be intentional, or may be the result of variations in the manufacturing process. In

either case, they must be properly considered when designing interconnects. This

design guide applies the CRB PCB stackup and trace width/spacing that is shown in

Figure 4.

Note: All the routing guidelines in this document are simulated based on the CRB stackup.

2.1.2 PCB Technology Considerations

The typical values, including the design and material tolerances, are centered on a

nominal single line impedance specification of 50𝛺 ± 15% for microstrip. Many

interfaces specify a different nominal single-ended impedance. For more details on the

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 11

Page 12

System Assumptions

nominal trace width to meet those impedance targets, refer to the individual interface

section.

The following general stackup recommendations should be followed:

Microstrip layers are assumed to be built from 1/2oz. foil, plated up nominally

another 1 oz.; however, the trace thickness range defined allows for significant

process variance around this nominal.

Based on the Intel® Quark™ Microcontroller D2000 layout layers, 3/4 dual stripline

is assumed to be built from 1 oz. copper.

All high-speed signals should reference solid planes over the length of their routing

and should not cross plane splits. Ground referencing is preferred.

Reference plane stitching vias must be used in conjunction with high-speed signal

layer transitions that include a reference plane change. Refer to each signal group

section for more specification.

The parameter values for internal and external traces are the final thickness and

width after the motherboard materials are laminated, conductors plated, and

etched. Intel uses these exact values to generate the associated electrical models

for simulation.

Figure 4. Single-Ended Microstrip Diagram

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

12 Document Number: 333580-002EN

Page 13

OPCM Stack-Up Information

Layer

Cu Weight

Proposed

Thickness

(mils)

Structure

Ref

Single End

Differential

50 Ohm ± 10%

90 Ohm ± 10%

Target

LW

Finished

LW

Target

LW/SP

Finished

LW/SP

Soldermask

0.50

L1

Top

Hoz+Plating

1.80 L2 3.94 4.2/8

Prepreg

2.70

1080

L2

GND

1oz

1.20

Core 50

50mil

core

L3

GND

1oz

1.20 Prepreg

2.70

1080

L4

Bottom

Hoz+Plating

1.80 L3 3.94 4.2/8

Soldermask

0.50

Finished

Thickness

(mils)

62.40

System Assumptions

Figure 5. Differential Microstrip Diagram

Table 3. Stackup Details

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 13

Page 14

System Assumptions

2.2 Backward and Forward Coupling Coefficient Calculation

Some designs require a stackup build that is outside of the ranges provided. In this

case, compare the routing electrical characteristics versus the Intel recommendation.

Comparing the single-ended and differential impedances is important. However,

crosstalk level, which is governed by trace spacing, is not implied by the impedance

target. Calculating and comparing the backward coupling coefficient is recommended

to choose proper trace spacing in cases where the selected stackup varies from the

Intel recommendation. The coupling coefficient represents the source voltage

percentage that is coupled to victim lines. As shown in Figure 6, Kb is defined as the

backward coupling coefficient. For backward (near- end) crosstalk, inductive and

capacitive coupling are of the same polarity and the noise magnitude is not a function

of trace length. The backward coupling coefficient (Kb) values can be used to determine

trace spacing. For forward (far-end) crosstalk, Kf inductive and capacitive coupling are

of opposite polarity, and the crosstalk magnitude (Vfe) is proportional to both trace

length and edge rate. Kf is typically a very small value in most practical designs.

Therefore, Intel has not included the Kf values in the design guide. However, if the value

is desired, the equation for calculating Kf is provided in Figure 7.

Figure 6. Backward Coupling Coefficient

Figure 7. Forward Coupling Coefficient

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

14 Document Number: 333580-002EN

Page 15

System Assumptions

Figure 8. Single-Ended Kb Diagram

Figure 9. Differential Kb Diagram

Breakout topologies are mainly decided by package ballout patterns and pitches.

Similar geometries will be used for various stackups. Refer to the interface sections for

the breakout maximum length allowed and signals not listed in Table 3.

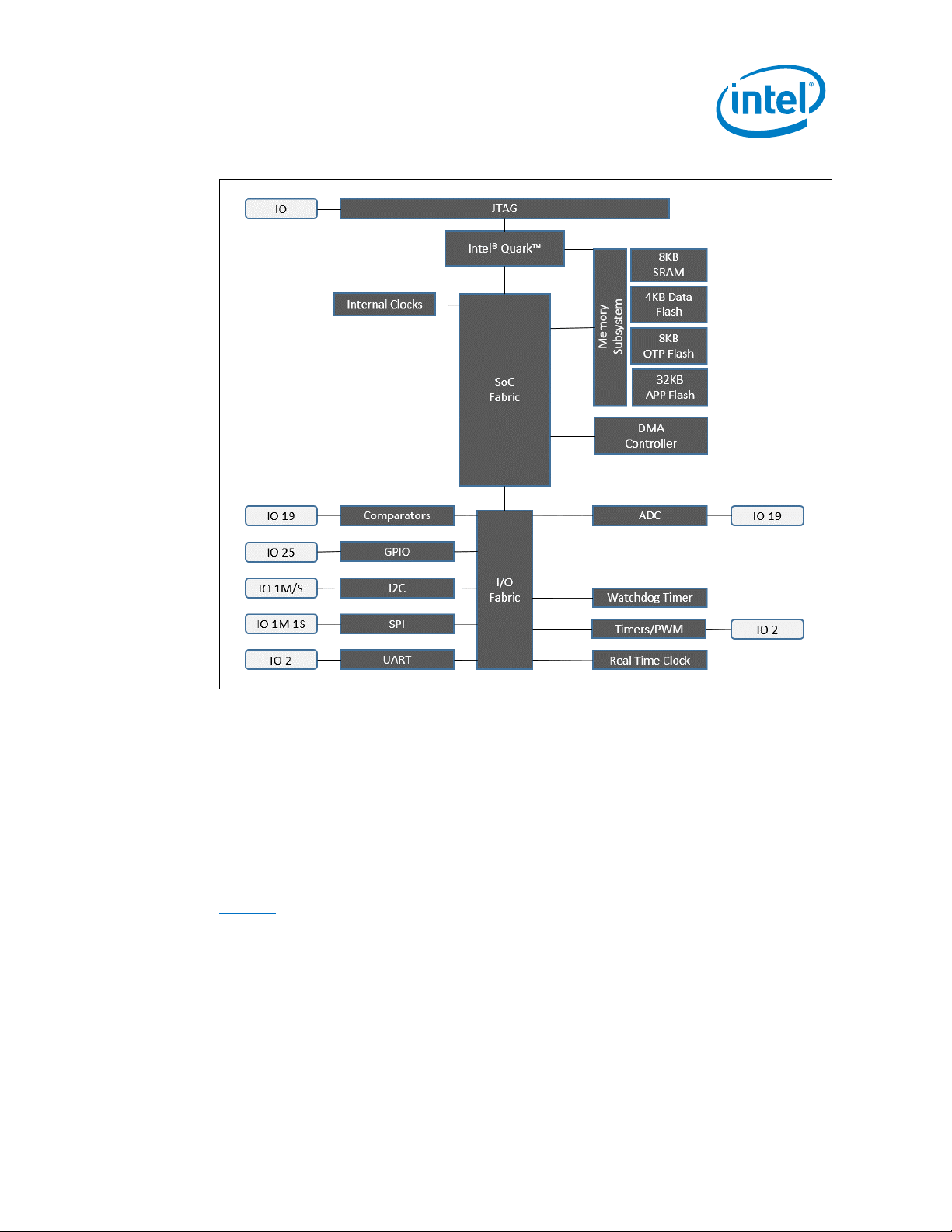

2.3 Feature Set

A wearable can contain any feature set and capabilities supported on Intel® Quark™

Microcontroller D2000. The following is an example feature set of a typical wearable

and used in the Intel® Quark™ Microcontroller D2000 form factor. Refer to the SoC

Datasheet for the latest features supported on the platform.

Intel® Quark™ Microcontroller D2000 features:

Intel® Quark™ Microcontroller D2000 SoC 32 MHz

32 KB flash memory (internal)

8 KB OTP flash (internal)

4 KB Data flash (internal)

8 KB SRAM (internal)

1x I²C (Master/Slave)

1x SPI master supports up to 4 devices

1x SPI slave

2x UART, supports 9-bit addressing mode

19 ADC/Comparator inputs

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 15

Page 16

2x PWM signals

25 GPIOs

Real-time clock

Watchdog timer

Intel® Quark™ Microcontroller D2000 main expansion options:

“Arduino Uno” compatible SIL sockets (3.3V I/O only)

Intel® Quark™ Microcontroller D2000 on-board components:

Accelerometer/Magnetometer sensor

UART/JTAG to USB convert for USB debug port

Other Intel® Quark™ Microcontroller D2000 connectors:

1x USB 2.0 Device Port – micro Type B

On-board coin cell battery holder

System Assumptions

5V input screw terminal/header (external power or Li-ion)

EEMBC power input header

Power sources for this platform:

External 5V DC input

Li-ion battery (external)

USB power (5V) via debug port

Coin cell battery (on-board)

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

16 Document Number: 333580-002EN

Page 17

System Assumptions

2.4 CRB Pin Mapping

Figure 10 shows the CRB interfaces and mapping.

Figure 10. CRB Pin Mapping Diagram

§

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 17

Page 18

3.0 Subsystem Details

This chapter provides design guidelines for the SoC associated interfaces. All of the

routing guidelines (W/S, isolation, length requirement) are based on CRB 4-layer PCB

technology. If a different PCB stackup is implemented, the electrical guidelines

(impedance, Kb, Insertion Loss) provided in this document must be followed to ensure

that the layout can meet simulation recommendations.

3.1 Design Recommendations

The Intel® Quark™ Microcontroller D2000 SoC is an ultra-low-power Intel® architecture

SoC that integrates an Intel® Quark™ Microcontroller D2000 processor core, memory

subsystem with on-die volatile and non-volatile storage and I/O interfaces into a single

system-on-chip solution.

This section presents design recommendations for the subsystems that make up the

Intel® Quark™ Microcontroller D2000 platform. The sections include overview

information, component selection studies, suggested routing guidelines, and additional

filter and signal information for the Intel® Quark™ Microcontroller D2000 platform.

Subsystem Details

The design recommendations are developed to ensure maximum flexibility for board

designers while reducing the risk of board-related issues.

Note: These design recommendations should be carefully followed and any deviations

should be verified through simulations. The component selection recommendations

describe the components that are being considered for the Intel® Quark™

Microcontroller D2000. If and when updated boards become available, this will be

noted in these sections.

The following subsystems are covered in this section:

On-die SRAM

Display interface

SPI

Storage

SPI

I²C

SPI

Integrated Sensor

UART

GPIO

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

18 Document Number: 333580-002EN

Page 19

Stitching Vias

Provide stitching vias for layer transitions

Break-In/Break-Out Regions

1. If desired trace width cannot be maintained in the break regions, maintain a minimum trace

width of 3.5 mil.

2. If desired trace spacing cannot be maintained in the break regions, maximize the trace

spacing.

Over and Around the Voids

1. Avoid routing over the voids and reference plane splits. Consult the SIE if split crossing

cannot be avoided

2. When going around the voids, maintain a minimum spacing of 1xh between signal trace and

void. Desirable spacing is 3xh where "h" is the distance to the nearest reference plane.

Lateral Distance to Reference Plane Edge

1. Keep a signal trace 4xh away from the edge of the reference plane.

Subsystem Details

3.2 General Design Guideline Assumptions

The following assumptions pertain to all the subsystems discussed in this chapter.

Package length compensation is needed. The length values are tested and

measured as package-pin-to-package-pin.

The breakout and breakin minimum spacing ratio is 1:1 for all interfaces.

The trace width/intra-spacing for differential pairs and trace width for single-

ended signals depend on the impedance.

For analog signals, it is important to keep the analog ground return path clean of

digital noise to maintain a high signal-to-noise ratio.

For technical specifications (such as speeds, supported resolutions, and data rates),

refer to the Intel® Quark™ Microcontroller D2000 Datasheet.

Note: 1. Follow the general guidelines in this section, if a specific interface design guide is

not available.

2. All the routing guidelines in this document are simulated based on the CRB

stackup.

Table 4. Good Layout Practices

§

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 19

Page 20

4.0 I²C Interface

I²C is a two-wire serial bus for inter-IC communication. One wire is for data, the other

for clock. There is one I²C controller. The controller owns its own two-wire bus.

4.1 I²C Interface Signals

Signals for the I²C interface are illustrated in the table 6 below.

Figure 11. I²C Interface

I²C Interface

I²C features:

One I²C interface

Support for both master and slave operation

Operational speeds:

Standard mode (0 to 100Kbps)

Fast mode (≤ 400Kbps)

Fast mode plus (≤ 1Mbps)

7-bit or 10-bit addressing

Support for clock stretching by slave devices

Multi-master arbitration

Spike suppression

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

20 Document Number: 333580-002EN

Page 21

Leveraged from Intel®

Quark™ SoC

I²C

I²C (SDA, SCL)

BRK OUT

Main

BRK IN

Transmission Line

Segment

L1

L2

L3

Routing Layer

(Microstrip/Stripline)

MS/SL

MS/SL

MS/SL

Characteristic Impedance

50Ω + 10% (MS)

50Ω + 10% (SL)

50Ω + 10% (MS)

50Ω + 10% (SL)

50Ω + 10% (MS)

50Ω + 10% (SL)

Trace Width (w)

Meet impedance

Meet impedance

Meet impedance

Trace Spacing (S):

Between SPI signals

5 mil minimum

2*w

5 mil minimum

Trace Spacing (S2):

Between SPI signals and

other signals

5 mil minimum

3*w

5 mil minimum

Trace Length

0.5" max

See below

0.5" max

Pull-up Resistor Rpu

See below

I²C Interface

Hardware Handshake Interface to support DMA capability

Interrupt Control

FIFO support with 16B deep RX and TX FIFOs

4.2 Interface Routing Guidelines

I²C clock and data signals require pull-up resistors. The pull-up size is dependent on

the bus capacitive load (this includes all device leakage currents).

Figure 12. I²C Point-to-Point Topology

The following table shows detailed routing requirements for the I²C bus.

Table 5. I²C Point-to-Point Platform Routing Guidelines

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 21

NOTES:

1. Length matching between Data and Clk is 540 mils

2. Load = routing length capacitance + MCP = device pin capacitance

3. MCP + device pin capacitance = 10 µF

Page 22

4. Cap per inch of board (pF) = 3 pF/inch (for the current stackup)

5. If the nominal trace width is not possible in the breakout area, use 4 mils as

minimum trace width. Choose a stackup so that 50 Ohms will be minimum 4 mils.

4.2.1 General Design Considerations

The maximum bus capacitive load for each I²C bus is 400 pF. The pull-up resistor

cannot be made so large that the bus time constant (Resistance X Capacitance) does

not meet the I²C rise and fall time specification.

I²C Interface

§

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

22 Document Number: 333580-002EN

Page 23

Pulse Width Modulation (PWM)

5.0 Pulse Width Modulation (PWM)

The Pulse Width Modulation (PWM) block allows individual control of the frequency

and duty cycle of two output signals. The PWM block also supports use as a Timer

block for the purposes of generating periodic interrupts. A possible usage model

includes connecting PWM to drive a haptic driver. The two PWM pins are also

multiplexed and can be used as a GPIO. Two 32-bit timers running at system clock can

be configured to generate two PWM outputs.

Figure 13. PWM

The following is a list of PWM features:

Two counters capable of operating in PWM Mode or Timer Mode

PWM Mode

Configurable high and low times for each PWM Output

Minimum high and low time of 2 32MHz clock periods (8MHz)

Maximum high and low time of 2^32 32MHz clock periods (< 1Hz)

High and low time granularity of a single 32MHz clock period

Interrupt generation always on both the rising and falling edges of the PWM

Output

Interrupt control per PWM Output:

Interrupt generation only on both edges of the PWM Output

Interrupt mask capability

Timer Mode

32-bit timer operating at 32MHz

Timer periods from 1 32MHz clock period (31.25ns) to 2^32-1

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 23

Page 24

32MHz clock periods (134s)

Interrupt control per timer:

Interrupt generation on timer expiry

Interrupt mask capability

5.1 PWM Signaling

The Timer and PWM block supports the generation of PWM Output signals with

configurable low and high times, which allows both the duty cycle and frequency to be

set.

Example PWM Output signals are shown in the following figures.

Figure 14. Duty Cycle of 20%

Pulse Width Modulation (PWM)

Figure 15. Duty Cycle of 50%

Figure 16. Duty Cycle of 80%

5.2 Functional Operation

Each counter is identical, has an associated PWM Output, and can be individually

configured with the following options:

Enable

PWM Mode or Timer Mode

PWM Duty Cycle and Frequency

Timer Timeout Period

Interrupt Masking

In PWM Mode, the high and low times can be configured as follows. This assumes a

nominal system clock frequency of 32MHz. The values, in nanoseconds, will differ if the

system clock frequency is changed.

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

24 Document Number: 333580-002EN

Page 25

Characteristic

Value (System Clock Cycles)

Value (Time)

Low Time Granularity

1

31.25 ns

Low Time Range

2 to 4294967296 (2^32)

62.5 ns to 134.22 s

High Time Granularity

1

31.25 ns

High Time Range

2 to 4294967296 (2^32)

62.5 ns to 134.22 s

Characteristic

Value (System Clock Cycles)

Value (Time)

Timeout Period

Granularity

1

31.25 ns

Timeout Period Range

0 to 4294967295 (2^32 -1 )

0 to 134.22 s

Pulse Width Modulation (PWM)

Table 6. PWM Timing

PWM Mode supports the following maskable interrupt source:

Both edges of the PWM Output signal

In Timer Mode, the timeout period can be configured as follows. This assumes a

nominal system clock frequency of 32MHz. The values, in nanoseconds, will differ if the

system clock frequency is changed.

Table 7. Timer Period

Timer Mode supports the following maskable interrupt source:

Timer expiry

Interrupts are cleared by reading the Timer N End of Interrupt register.

§

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 25

Page 26

6.0 UART

UART is one of the hardware blocks in the Serial I/O (SIO).

Figure 17. UART

UART

Main features:

Two 16550 compliant UART interfaces

Support for baud rates from 300 to 2M with less than 2% frequency error

Support for hardware and software flow control

FIFO mode support (16B TX and RX FIFOs)

Support for HW DMA with configurable FIFO thresholds

Support for 9-bit operation mode

Support for RS485 and RS232

Support for DTR/DCD/DSR/RI Modem Control Pins through GPIO pins controlled

by software

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

26 Document Number: 333580-002EN

Page 27

Signal Name

Direction/

Type

Description

UART_x_TXD

Logic output

UART A single-ended Transmit data (RS232 or

RS485). In RS485 mode, the differential driver is

outside the SoC.

UART_x_RXD

Logic input

UART A single-ended Receive data (RS232 or

RS485). In RS485 mode, the differential receiver is

outside the SoC.

UART_x_RTS

Logic output

UART A Request to send (RS232)

UART_x_CTS

Logic input

UART A Clear to send (RS232)

UART_x_DE

Logic output

UART A Driver Enable (RS485 mode). Used to

control the differential driver of RS485 in the

platform/board. Polarity is configurable. This is

multiplexed onto the UART_A_RTS pin depending

on RS485 or RS232 mode of operation.

UART_x_RE

Logic output

UART B Receiver Enable (RS485 mode). Used to

control the differential receiver of RS485 in the

platform/board. Polarity is configurable. This is

multiplexed onto the UART_B_CTS pin depending

on RS485 or RS232 mode of operation.

UART

6.1 Signal Descriptions

Table 8. UART Signals

Figure 18. UART 2-Via Point-to-Point Topology

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 27

Page 28

Table 9. UART Point-to-Point Topology Platform Routing Guidelines

UART

TXD, RXD, RTS, CTS

BRK OUT

Main

BRANCH

BRK IN

Transmission Line

Segment

L1

L2

L4

L3

Stackup Layer

(Microstrip/

Stripline/Dual Stripline)

MS/SL

MS/SL

MS/SL

MS/SL

Characteristic Impedance

50Ω SE10%

50Ω SE10%

50Ω SE10%

50Ω SE10%

Trace Width (w)

Meet

impedance

Meet

impedance

Meet

impedance

Meet

impedance

Min Trace Spacing (S1):

Between UART signals

5 mil

2*w

5 mil

5 mil

Min Trace Spacing (S2):

Between UART signals

and other signals

5 mil

3*w

10 mil

5 mil

Trace Segment Length

0.5" max

See Table 11

1" max

0.5" max

Total Trace length and Length Matching Rules

(brd+pkg)

Min

Max

Total trace length

1-5"

No length matching required

Number of vias allowed

Via stub length

Reference Plane

Continuous Ground Reference

• If nominal trace width is not possible in breakout area, use 4 mil as min trace width.

Choose a stack up so 50ohms will be min 4mils

UART

Table 10. UART Point-to-Point Topology Platform Routing Guidelines

Routing can also be extended to10-12" in which case a series Rs of 22 Ω close to the

driver will be necessary to avoid ring back TX - SOC driver, RX - UART driver Max speed

= 2MBaud.

6.2 Features

Both UART instances are configured identically. The following is a list of the UART

controller features:

Operation compliant with the 16550 Standard

Start bit

5 to 9 bits of data

Optional Parity bit (Odd or Even)

1, 1.5 or 2 Stop bits

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

28 Document Number: 333580-002EN

Page 29

UART

Baud rate configurability between 300 baud and 2M baud

Maximum baud rate is limited by system clock frequency divided by 16.

Supported baud rates: 300, 1200, 2400, 4800, 9600, 14400, 19200, 38400,

57600, 76800, 115200; multiples of 38.4 Kbps and multiples of 115.2 Kbps up

to 2M baud

Auto Flow Control mode as specified in the 16750 Standard

Hardware Flow Control

Software Flow Control (when Hardware Flow Control is disabled)

Hardware Handshake Interface to support DMA capability

Interrupt Control

FIFO support with 16B TX and RX FIFOs

Support of RS485

Differential driver/receiver is external to the SoC.

Driver enable (DE) and Receiver enable (RE) outputs are driven from the SoC to

control the differential driver/receiver.

Fractional clock divider that ensures less than 2% frequency error for most

supported baud rates.

Fraction resolution is 4 bits.

Exception: 2.07% error for 1.391 Mbaud, 2.12% for 1.882 Mbaud and 2Mbaud,

2.53% error for 1.684 Mbaud.

9-bit data transfer mode to support a multi-drop system where one master is

connected to multiple slaves in a system.

§

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 29

Page 30

7.0 SPI

The Serial I/O implements one SPI controller that supports master mode and slave

mode. Refer to the Datasheet for additional SPI compatibility requirements and

features. Support for SPI Flash devices is a key platform requirement and needed for all

SoC designs.

Figure 19. SPIO

SPI

Features include:

One SPI master interface with support for SPI clock frequencies up to 16 MHz

One SPI slave interface with support for SPI clock frequencies up to 3.2 MHz

Support for 4-bit up to 32-bit frame size

Up to 4 Slave Select pins per master interface

FIFO mode support (16B TX and RX FIFOs)

Support for HW DMA with configurable FIFO thresholds

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

30 Document Number: 333580-002EN

Page 31

SPI Slave

SPI_S

(SDIN, SDOUT, SCLK, SCS)

BRK OUT

Main

BRK IN

Transmission Line

Segment

L1

L2

L3

Routing Layer

(Microstrip/Stripline)

MS/SL

MS/SL

MS/SL

Characteristic Impedance

50Ω + 10% (MS)

50Ω + 10% (SL)

50Ω + 10% (MS)

50Ω + 10% (SL)

50Ω + 10% (MS)

50Ω + 10% (SL)

Trace Width (w)

Meet impedance

Meet impedance

Meet impedance

Trace Spacing (S): Between

SPI signals

5 mil minimum

2*w

5 mil minimum

Trace Spacing (S2):

Between SPI signals and

other signals

5 mil minimum

3*w

5 mil minimum

Trace Length

0.5" max

7" max

0.5" max

Trace Total Length

Total trace length = 8" max

SPI

Figure 20. SPI Point-to-Point Single-Ended Topology

Table 11. SPI Platform Routing Guidelines

7.1 Features

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 31

The following is a list of the SPI master features:

One SPI master interface

Control of up to 4 Slave Selects

Frame formats:

Motorola* SPI

Texas Instruments* SSP

National Semiconductor Microwire*

Transfer modes:

Transmit & Receive

Page 32

Transmit Only

Receive Only

EEPROM Read

Serial clock frequencies up to 16 MHz

4-bit to 32-bit frame size

Configurable Clock Polarity and Clock Phase

Hardware Handshake Interface to support DMA capability

Interrupt Control

FIFO mode support with 16B deep TX and RX FIFOs

The following is a list of the SPI slave features:

One SPI slave interface

Frame formats:

Motorola* SPI

Texas Instruments* SSP

National Semiconductor Microwire*

SPI

Transfer modes:

Transmit & Receive

Transmit Only

Receive Only

EEPROM Read

Serial clock frequencies up to 3.2 MHz

4-bit to 32-bit frame size

Configurable Clock Polarity and Clock Phase

Hardware Handshake Interface to support DMA capability

Interrupt Control

FIFO mode support with 16B deep TX and RX FIFOs

§

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

32 Document Number: 333580-002EN

Page 33

Clocking

8.0 Clocking

The SoC clocking is controlled by the Clock Control Unit (CCU). There are two primary

clocks: a System clock, and an RTC clock. The CCU uses the primary clocks to generate

secondary clocks to sub modules in the SoC. The secondary clocks are gated and scales

versions of the primary clocks.

The SoC contains a Real-Time Clock (RTC) with 32 bytes of battery-backed SRAM. The

SoC uses the RTC to keep track of time. The RTC operates from 1 Hz to 32.768 kHz. The

RTC supports alarm functionality that allows scheduling an Interrupt/Wake Event for a

future time. The RTC operates in all SoC power states. The RTC is powered from the

same battery supply as the rest of the SoC and does not have its own dedicated supply.

Figure 21. RTC

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 33

Page 34

Figure 22. RTC Topology

Signal Name

Direction/Type

Description

OSC32_IN

I Analog

Crystal Input: This signal is

connected to the 32.768 kHz

Crystal.

OSC32_OUT

O Analog

Crystal Output: This signal is

connected to the 32.768 kHz

Crystal.

Table 12. RTC Signals

Clocking

8.1 Features

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

34 Document Number: 333580-002EN

The following is a list of the RTC features:

Programmable 32-bit binary counter

Counter increments on successive edges of a Counter Clock from 1 Hz to 32.768

kHz (derived from the 32.768 kHz Crystal Oscillator clock)

Comparator for Interrupt/Wake Event generation based on the programmed Match

Value

Support for Interrupt/Wake Event generation when only the Counter Clock is

running (Fabric Clock is off)

§

Page 35

General Purpose I/O (GPIO)

9.0 General Purpose I/O (GPIO)

The SoC contains GPIO pins and the interfaces can be active at different times. To

provide maximum flexibility at the lowest cost point, some GPIO pins are shared/muxed

among various interfaces. BIOS is responsible for enabling proper configuration. The

SoC contains a single instance of the GPIO controller.

Figure 23. GPIO

The GPIO controller provides a total of 26 independently configurable GPIOs.

All GPIOs are interrupt capable supporting level sensitive and edge triggered

modes.

All GPIOs support Debounce logic for interrupt sources.

All 26 GPIOs are Always-on interrupt and wake capable.

9.1 Signal Descriptions

All GPIO pins are described in the SoC Datasheet.

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 35

Page 36

Figure 24. GPIO Pin Routing Topology

GPIO

GPIO (MV to GPIO

Header/Device)

BRK OUT

Main

BRK IN

Transmission Line Segment

L1

L2

L3

Routing Layer

(Microstrip/Stripline)

MS/SL

MS/SL

MS/SL

Characteristic Impedance

50Ω + 10% (MS)

50Ω + 10% (SL)

50Ω + 10% (MS)

50Ω + 10% (SL)

50Ω + 10% (MS)

50Ω + 10% (SL)

Trace Width (w)

Meet impedance

Meet impedance

Meet impedance

Trace Spacing (S): Between

SPI signals

5 mil minimum

2*w

5 mil minimum

Trace Spacing (S2):

Between SPI signals and

other signals

5 mil minimum

3*w

5 mil minimum

Trace Length

0.5" max

9" max

0.5" max

Trace Total Length

Total trace length = 10" max

Table 13. GPIO Pin Routing Guidelines

General Purpose I/O (GPIO)

9.2 Features

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

36 Document Number: 333580-002EN

NOTE:

1. Rs = 22 or 33Ω ideally closer to driver.

2. The modelled GPIO device is 30pF. GPIOs can drive higher loads at reduced lengths.

3. Maximum speed = 8 MHz.

The following is a list of the GPIO controller features:

26 independently configurable GPIOs

Separate data register bit and data direction control bit for each GPIO

Page 37

General Purpose I/O (GPIO)

Metastability registers for GPIO read data

Interrupt mode supported for all GPIOs, configurable as follows:

Active High Level

Active Low Level

Rising Edge

Falling Edge

Both Edge

Debounce logic for interrupt sources

§

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 37

Page 38

10.0 JTAG

This section provides JTAG information.

Figure 25. JTAG Connectivity

JTAG

Table 14. Generic Routing Requirements

§

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

38 Document Number: 333580-002EN

Page 39

Analog-to-Digital Converter (ADC)

11.0 Analog-to-Digital Converter (ADC)

The SoC implements a Successive-Approximation (SAR) Analog-to-Digital Converter

(ADC), which can take 19 single-ended analog inputs for conversion. The ADC is

characterized to operate over the AVDD (1.8 to 3.6V) analog input range.

Analog signal traces in the SoC should be shielded completely to minimize noise

coupling and crosstalk between analog signals.

Figure 26. Analog Shielding Requirements

Example: Analog signal traces A, B and C are shielded “agnd” net with metal

layers/traces adjacent, above and below the signals. An “agnd” trace should be added

on top of signal C if there will be another signal route over it.

11.1 Features

The following is a list of the ADC features:

19:1 multiplexed single-ended analog input channels, 6 high-speed inputs and 13

low-speed inputs.

Selectable resolution among 12-, 10-, 8-, and 6-bit (12-bit at 2.28 MSps and 6- bit

at 4 MSps).

Maximum achievable sampling rate = (adc clock frequency) / (selres + 2).

ADC parameters:

Differential Non-Linearity (DNL) = +/- 1.0 LSB

Integral Non-Linearity (INL) = +/- 2.0 LSB

SINAD = 68 dBFS

Offset Error = +/- 2 LSB (calibration enabled), +/- 64 LSB (calibration disabled)

Latencies:

Power-up time of <= 10 us

1 conversion cycle = (resolution bits + 2) cycles

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 39

Page 40

Analog-to-Digital Converter (ADC)

Full-scale input range is 0 to AVDD.

ADC Reference Voltage (Vrefp) of ADC HIP is connected to AVDD.

Current consumption:

~18 uA at 10 kSPS

~240 uA at 1 MSPS

~1.1 mA at 5 MSPS

~15 uA standby

~2 uA powerdown

§

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

40 Document Number: 333580-002EN

Page 41

Power Delivery

12.0 Power Delivery

This chapter provides the recommendations on how to deliver the power into the Intel®

Quark™ Microcontroller D2000 SoC to assure the system stability and to avoid

unexpected behavior of the system, during power ON sequence especially.

12.1 DVDD Linear Regulator

Providing a load to the DVDD linear regulator at the start of power cycle using active

pull-down circuit it is a very important step which must not be overlooked.

12.1.1 Operation of an Active Pull – Down Circuit

PVDD power rail charges PCB bulk capacitance via on-board VR U5. When PVDD ramps

up/down due to power rail being applied/disconnected, U1 turns on and presents R1

load across DVDD which discharges PCB bulk capacitance. When PVDD reaches steady

state U1 disconnects and removes R1 load across DVDD. PVDD voltage range is from

2.0V to 3.6V.

12.1.2 Implementation of an Active Pull – Down Circuit

Figure 27 illustrates a recommended implementation of an Active Pull – Down Circuit.

The table provides a bill of materials used and recommended.

Figure 27. Active Pull – Down circuit implementation

Intel® Quark™ Microcontroller D2000

November 2016 Platform Design Guide

Document Number: 333580-002EN 41

Page 42

Power Delivery

Symbol

Element

Parameters

Type

C2

MLCC

10uf X7R 0603 6.3Vdc

Farnell 1828828 or 2210949

D2

Schottky Diode

BAT48

Farnell 9801472

R1

Thick Film resistor

316 1% 0603

Any

R2

Thick Film resistor

31K6 1% 0603

Any

U1

P-MOSFET

Vishay SI1013R-T1

Farnell 2335267

Table 15. Active Pull – Down circuit BOM

Note: Not adhering to the recommendations described in this chapter may lead to a faulty

power ON sequence, especially during hard reset. If a faulty power sequence occurs,

the device may enter a high current state and become unresponsive. This high current

state can lead to device heating.

§

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

42 Document Number: 333580-002EN

Loading...

Loading...