Page 1

IQ80960RM/RN Evaluation

Platform

Board Manual

February 1999

Order Number: 273160-004

Page 2

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The IQ80960RM/RN may contain design defects or errors known as errata which may cause the product to deviate from published specifications.

Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-

548-4725 or by visiting Intel’s website at http://www.intel.com.

Copyright © Intel Corporation, 1999

*Third-party brands and names are the property of their respective owners.

IQ80960RM/RN Evaluation Platform Board Manual

Page 3

Contents

1 Introduction............................... ....... ....... ........ ....... ........................................ ....... ...........................1-1

1.1 i960

1.2 Software Development Tools.....................................................................................................1-3

1.3 IxWorks Software Development Toolset....................................................................................1-4

1.4 CTOOLS Software Development Toolset..................................................................................1-5

1.5 About This Manual.....................................................................................................................1-6

1.6 Notational-Conventions .............................................................................................................1-7

1.7 Technical Support......................................................................................................................1-8

2 Getting Star te d....... ....... ............... .............. ..................... .............. ............... .............. .............. ........2-1

2.1 Pre-I ns ta llation Consid e r a tions............................... .............. ..................... .............. ..................2-1

2.2 Software Installation..................................................................................................................2-1

2.3 Hardware Installation........ ..................... .............. ............... .............. .............. .............. .............2-2

2.4 Creating and Downloading Executable Files............................................................................ .2-3

®

RM/RN I/O Processor and IQ80960RM/RN Features.....................................................1-3

1.3.1 IxWorks Real-Time Operating System .........................................................................1-4

1.3.2 TORNADO Build Tools.................................................................................................1-4

1.3.3 TORNA DO Te st and Debug Tools ...............................................................................1-4

1.4.1 CT OOLS and the MON960 Debug Monitor..................................................................1-5

1.4.1.1 MON960 Host Communications...................................................................1-5

1.4.1.2 Terminal Emulation Method.........................................................................1-5

1.4.1.3 Host Debugger Interface (HDI) Method .......................................................1-5

1.7.1 Intel Customer Electronic Mail Support ........................................ ....... ..... ....... ..... ....... .1-8

1.7.2 Intel Customer Support Contacts..................................................................................1-8

1.7.3 Related Inform a tion ................................ ............... .............. .............. .............. .............1-9

2.2.1 Installing Software Development Tools ........................................................................2-1

2.3.1 Battery Backup .............................................................................................................2-2

2.3.2 Installing the IQ80960RM/RN Platforms in the Host System........................... ..... ....... .2-2

2.3.3 Verify IQ809 60RM/RN Platform is Functional ..............................................................2-2

2.4.1 Sam ple Downl oad and Execution Using GDB9 60........................................................2-3

3 Hardware Refere n ce..... ............... .............. .............. ..................... ............... .............. .............. ........3-1

3.1 Power Requirements .................................................................................................................3-1

3.2 SDRAM......................................................................................................................................3-1

3.2.1 SDRAM Performance...................................................................................................3-2

3.2.2 Upgrading SDRAM .......................................................................................................3-3

3.3 Flash ROM.................................................................................................................................3-3

3.3.1 Flash ROM Programming.............................................................................................3-3

3.4 Console Se rial Port.............................. .............. .............. ...................... .............. ......................3-4

3.5 Secondary PCI Bus Expansion Connectors ..............................................................................3-4

3.5.1 PCI Slots Power Availability..........................................................................................3-4

3.5.2 Inte rrupt and IDSEL Routing.........................................................................................3-5

3.6 Battery Backup..........................................................................................................................3-5

3.7 Loss of Fan Detect.....................................................................................................................3-5

3.8 Logic Analyzer Headers................................................. ....... ....... ....... ....... ....... ....... .......... ........3-6

3.9 JTAG Header.................................. .............. ...................... .............. .............. .............. . ............3-7

3.10 User LEDs .................................................................................................................................3-8

3.10.1 User LEDs During Initialization.....................................................................................3-8

IQ80960RM/RN Evaluation Platform Board Manual iii

Page 4

4 i960® RM/RN I/O Processor Overview............................................................................................4-1

4.1 CPU Memory Map........................... ..................... .............. .............. ............... .............. ....... .....4-2

4.2 Local Interrupts ..........................................................................................................................4-3

4.3 CPU Counter/Timers................................ .............. ............... ..................... .............. .................4-5

4.4 Primary PCI Interface................................................................................................................4-5

4.5 Secondary PCI Interface .................................................. ....... ....... ....... ....... ....... ..... ....... ..........4-5

4.6 DMA Channels ..........................................................................................................................4-6

4.7 Application Accelerator Unit ......................................................................................................4-6

4.8 Performance Monitor Unit..........................................................................................................4-7

5 MON960 Support for IQ80960RM/RN.............................................................................................5-1

5.1 Secondary PCI Bus Expansion Connectors........................................................................... ...5-1

5.2 MON960 Components...............................................................................................................5-1

5.2.1 MON 960 Init ialization . .................................................................................................. 5- 1

5.2.2 80960JT Core Initialization........................................... ....... ..... ....... ....... ..... ....... ....... ...5-2

5.2.3 Memory Controller Initialization....................................................................................5-2

5.2.4 SDRAM Initialization.....................................................................................................5-2

5.2.5 Primary PCI Interface Initialization................................................................................5-3

5.2.6 Primary ATU Initialization.............................................................................................5-3

5.2.7 PCI-to-PCI Bridge Initialization.....................................................................................5-4

5.2.8 Secondary ATU Initialization ....................................................................... .. .......... .....5-4

5.3 MON960 Kernel.........................................................................................................................5-5

5.4 MON960 Extensions..................................................................................................................5-5

5.4.1 Secondary PCI Initialization................................................. .......... ....... ......... .......... .....5-5

5.4.2 PCI BIOS Routines .......................................................................................................5-6

5.4.2.1 sysPCIBIOSPresent.....................................................................................5-6

5.4.2.2 sysFindPCIDevice........................................................................................5-7

5.4.2.3 sysFindPCIClassCode.................................................................................5-7

5.4.2.4 sysGenerateSpecialCycle............................................................................5-8

5.4.2.5 sysReadConfigByte......................................................................................5-8

5.4.2.6 sysReadConfigWord....................................................................................5-9

5.4.2.7 sysReadConfigDword ..................................................................................5-9

5.4.2.8 sysWriteConfigByte....................................................................................5-10

5.4.2.9 sysWriteConfigWord..................................................................................5-10

5.4.2.10 sysWriteConfigDword.................................................................................5-11

5.4.2.11 sysGetIrqRoutingOptions...........................................................................5-11

5.4.2.12 sysSetPCIIrq..............................................................................................5-12

5.4.3 Additional MON960 Commands .............................................................................. ...5-12

5.4.3.1 print_pci Utili ty........ ........ ..................... .............. .............. ...................... .....5-12

5.5 Diagnostics / Example Code...................................................................................................5-12

5.5.1 Board Level Diagnostics................................................................ ....... .. ....... .......... .. .5-12

5.5.2 Secondary PCI Diagnostics..................................................................................... ...5-12

A Bill of Materials............................................................................................................... A-1

B Schematics.....................................................................................................................B-1

C PLD Code...... ............................ ............... ............................ .............. ............................C-1

D Recycling the Battery.....................................................................................................D-1

iv IQ80960RM/RN Evaluation Platform Board Manual

Page 5

Figures

1-1 IQ80960RM/IQ80960RN Platform Functional Block Diagram...................................................1-1

1-2 IQ80960RN Platform Physical Diagram ....................................................................................1-2

3-1 LED Register Bitmap .................................................................................................................3-8

4-1 i960

4-2 IQ80960RM/RN Platform Memory Map.....................................................................................4-2

4-3 i960

4-4 i960

4-5 Applicatio n Accelerator Unit.......................................................................................................4-7

®

RM/RN I/O Processor Block Diagram..............................................................................4-1

®

RM/RN I/O Processor Interrupt Controller Connections..................................................4-4

®

RM/RN I/O Processor DMA Con troller ............................................................................4-6

Tables

1-1 Document Information.................................. ............................. .............. .............. ....................1-9

1-2 Cyclone Contacts............................ .............. ............................. ............................ ....................1-9

3-1 IQ80960RN Platform Power Requirements.......................................................................... . ....3-1

3-2 IQ80960RM Platform Power Requirements .............................................................................. 3-1

3-3 SDRAM Perform ance ................................................................................................................3-2

3-4 SDRAM Configura tions..............................................................................................................3-3

3-5 UART Register Addresses.........................................................................................................3-4

3-6 Secondary PCI Bus Interrupt and IDSEL Routing .....................................................................3-5

3-7 Logic Analyzer Header Definitions.............................................................................................3-6

3-8 JTAG Header Pinout.. .............. ............................ ............... ............................ ...........................3-7

3-9 Switch S1 Settings.....................................................................................................................3-7

3-10 Start-up LEDs MON960.............................................................................................................3-8

3-11 IQ80960RM/RN Connectors and LEDs....................................... .. ..... ..... .. ..... .. ....... ..... ..... .. ..... .3-9

5-1 Initialization Modes ........................................................ ......... ....... ............ ............ ....................5-3

A-1 IQ80960RN Bill of Mate rials ..................................................................................................... A-1

A-2 IQ80960RM Bill of Materials .....................................................................................................A-5

B-1 IQ80960RN Schematics List..................................................................................................... B-1

B-2 IQ80960RM Schematics List....................................................................................................B-2

IQ80960RM/RN Evaluation Platform Board Manual v

Page 6

Page 7

Introduction

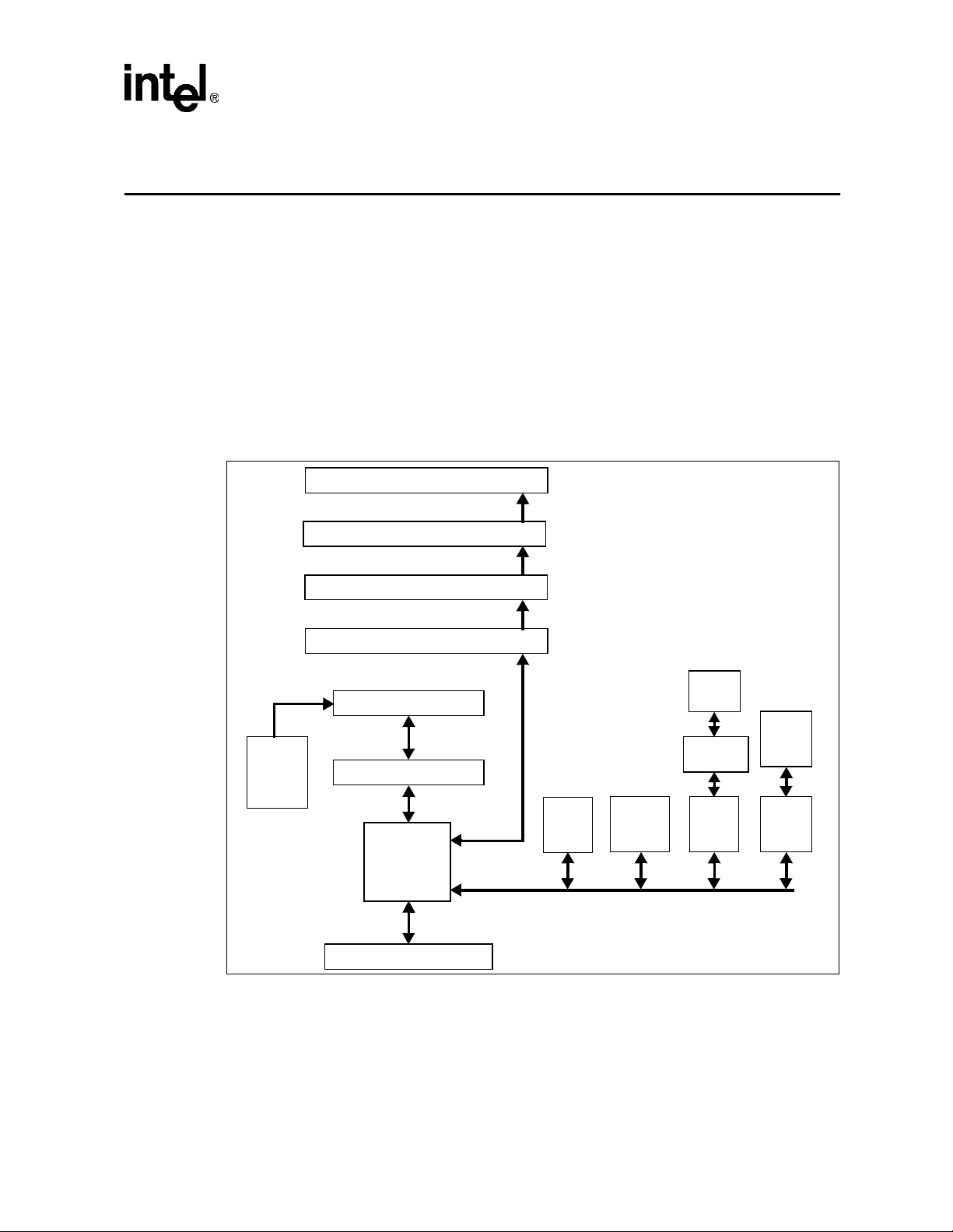

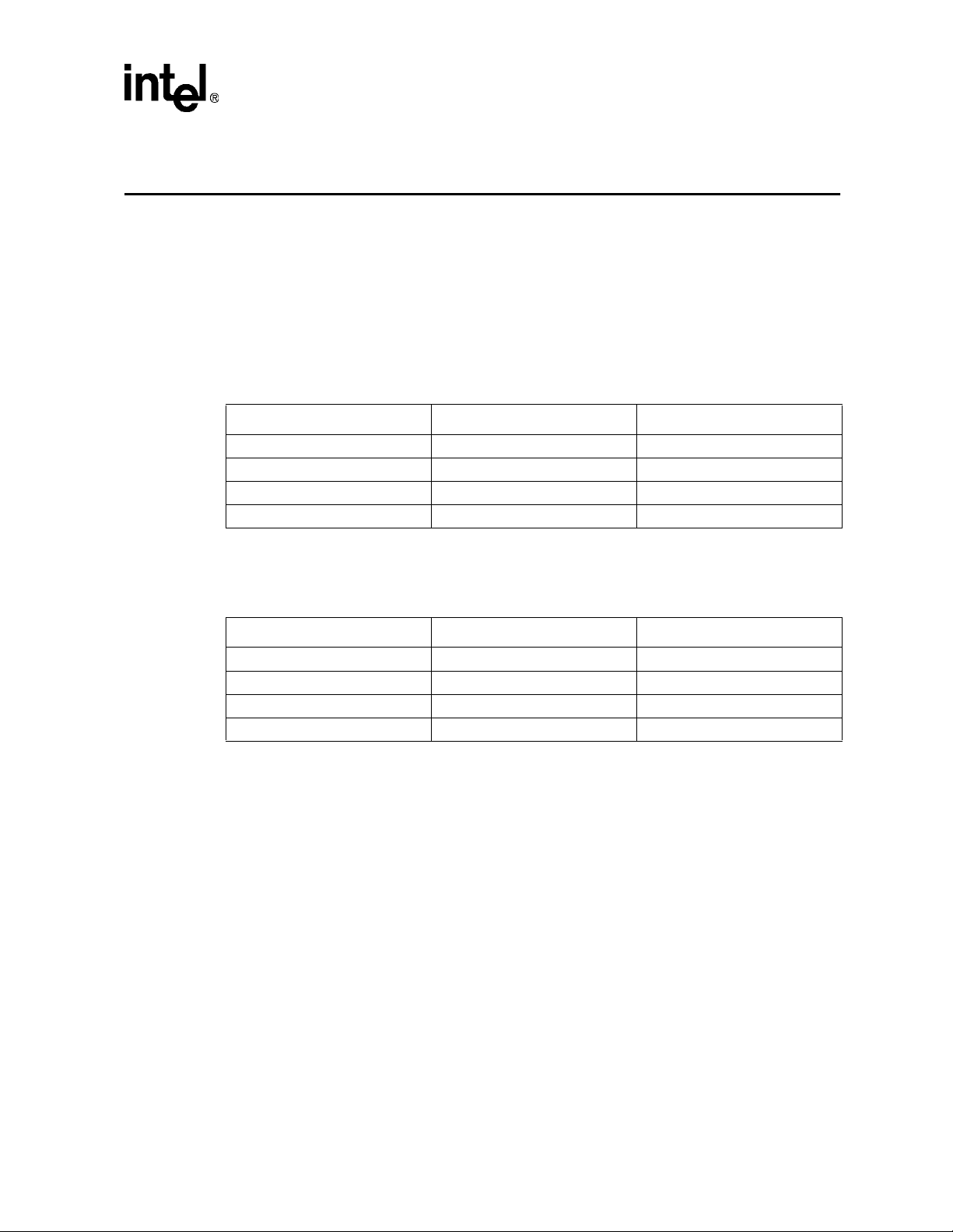

This manual describes the IQ80960RM and IQ80960RN eva luation platforms for Intel’s i960®

RM/RN I/O processor. The i960 RM/RN I/O processors combine an 80960JT core with two PCI

bus interfaces, as well as a memory controller, DMA channels, an interrupt controller interface, and

2

C serial bus. The difference between the two processors is that the 80960RN utilizes 64-bit

an I

primary PCI and secondary P CI bus es while the 80960RM utilizes both a 32-bit primary and

secondary PCI bus . The IQ8096 0RM a nd IQ80960RN pl at forms are full-l ength PCI adapte r boards

and are 8.9” in height to ac commodate four standard PCI connectors on the secondary PCI bus.

The boards can be installed in any PCI host system that complies with the PCI Local Bus

Specificati on Revision 2.1. PCI devices can be connected to the secondary bus to build powerful

intelligent I/O subsystems.

Figure 1-1. IQ80960RM/IQ80960RN Platform Functional Block Diagram

Secondary PCI Slot 4

Secondary PCI Slot 3

Secondary PCI Slot 2

1

Battery

Backup

Support

Secondary PCI Slot 1

SDRAM (x72)

Logic Analyzer Interface

i960® RM/RN

I/O Processor

Primary PCI Bus 32/64-bits

Secondary PCI

Bus 32/64-bits

ROM Bus

Flash

ROM

Logic

Analyzer

Interface

Console

Port

RS-232

Serial Port

UART

User

LED

LED

Registe r

IQ80960RM/RN Evaluation Board Ma nual 1-1

Page 8

Introduction

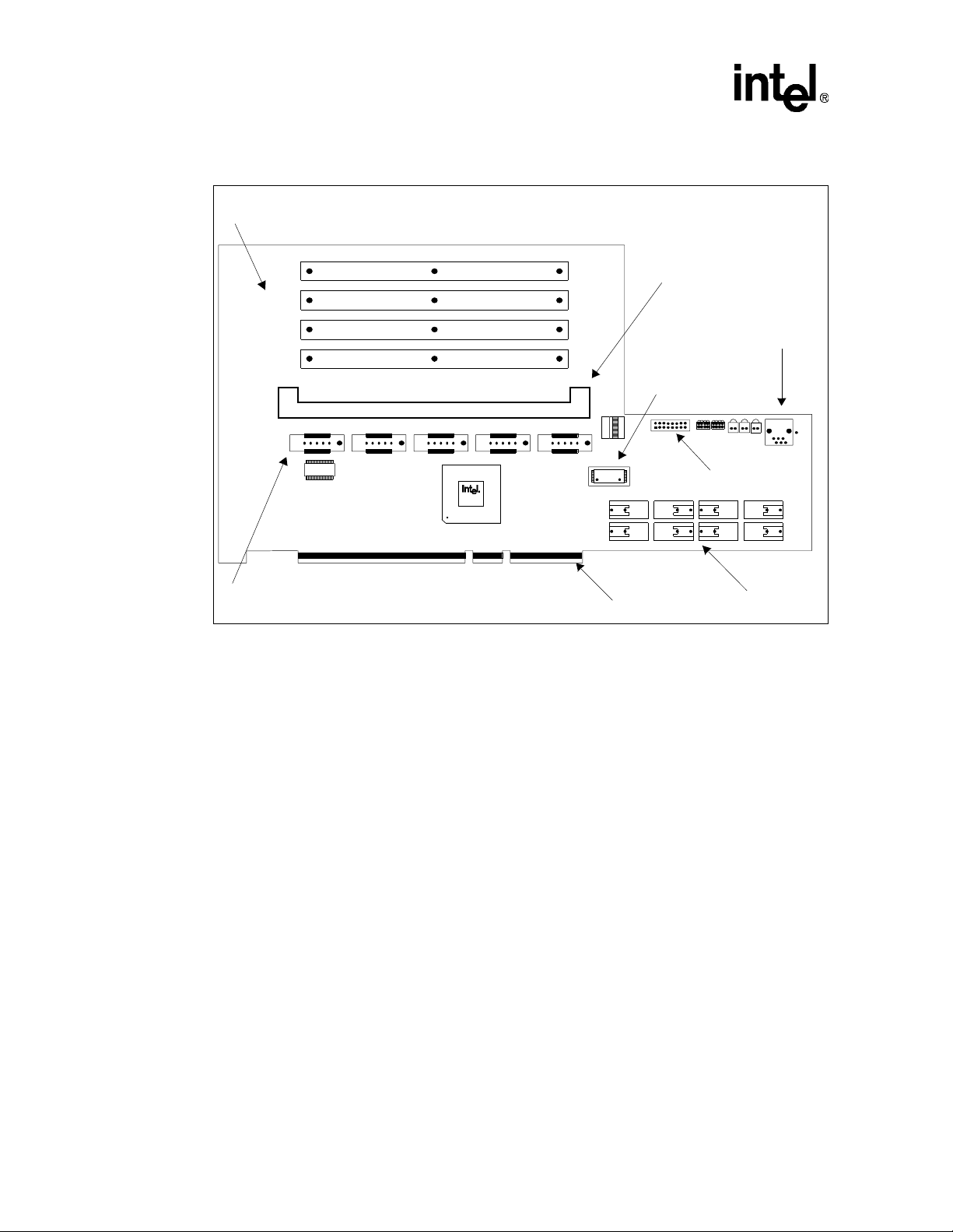

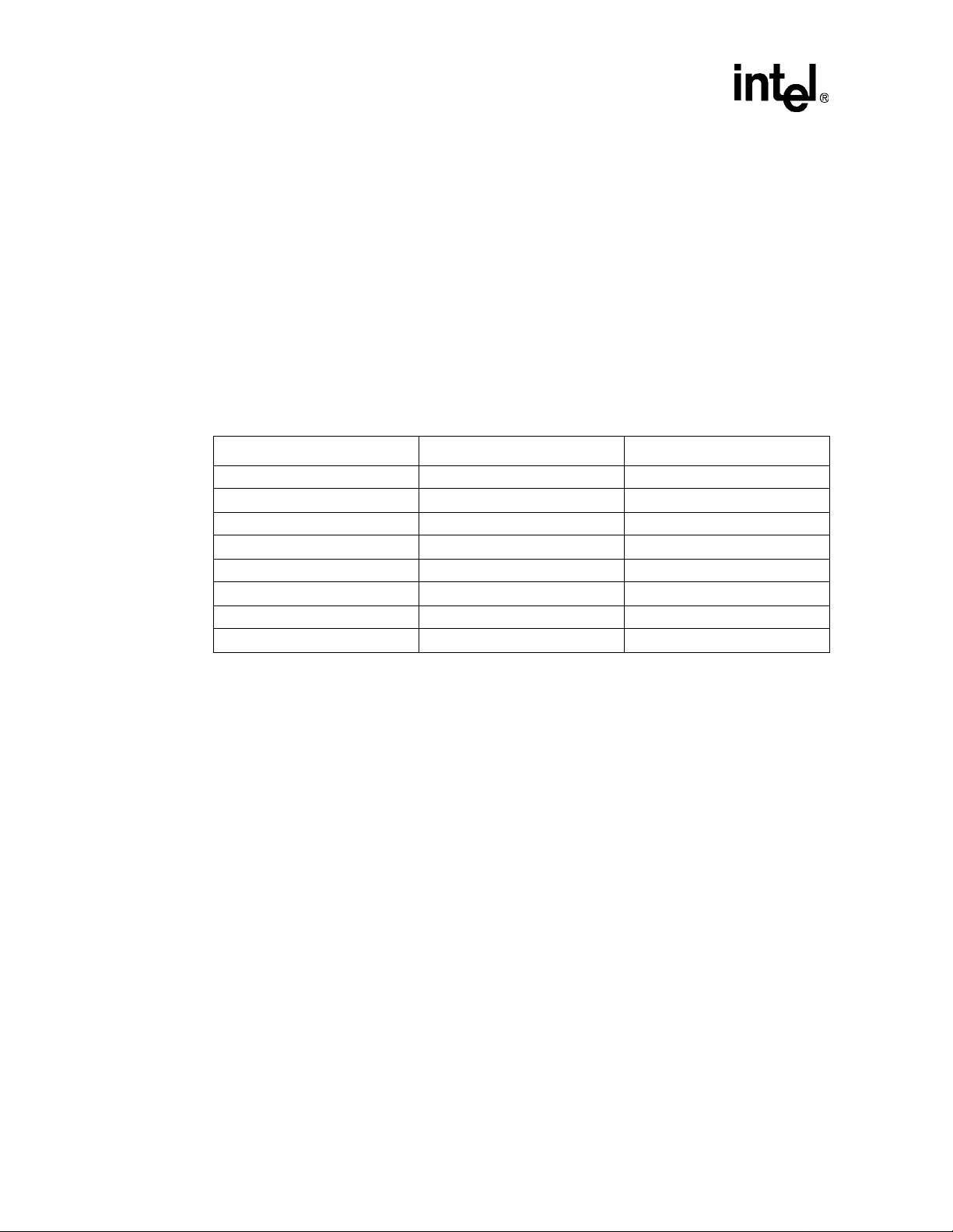

Figure 1-2. IQ80960RN Platform Physical Diagram

64-Bit Secondar y PCI Slots

J4

J3

J2

J1

J5

J8 J9 J10 J11 J12

U9

Logic Analyzer Connectors

i960

U15

168-Pin SDRAM DIMM Socket

RS-232 Serial Port

Flash Memory

SW1

1 2 3 4

OFF

J6

U11

®

64-Bit PCI

CR1 CR2

CR3 CR4 CR5

JTAG Port

NiCd Batteries

J7

1-2 I Q80960RM/RN Evaluation Board Manu al

Page 9

Introduction

1.1 i960® RM/RN I/O Processor and IQ80960RM/RN Features

The i960 RM/RN I/O processor serves as the mai n component of a high performance , PCI-based

intelligent I/O subsystem. The IQ80960RM and IQ80960RN pla tforms allow the developer to

connect PCI devices to the i960 RM/RN I/O processors using the four secondary PCI expansion

connectors. The features of the IQ80960RM and IQ80960RN platforms are enumerated below and

shown in Figure 1-1 and Figu re 1-2.

• i960 RM/RN I/O processor

• Modified PCI long-card form factor

• 64-bit or 32-bit primary PCI bus interface (80960RM 32-bit only)

• 64-bit or 32-bit secondary PCI bus connected to the pri mary P CI interface with a PCI-to-PCI

bridge (80960RM 32-bit only)

• DMA channels on both PCI buses

2

• I

C Serial Bus

• 168-pin, 3.3V DIMM socket supporting 16 to 128 Mbytes of Synchronous DRAM organized

x72 to support Error Correction Code (ECC) and clocked at 66 MHz (ships with 16 M/ECC

installed)

• Serial console port based on 16C550 UART

• Eight user-programmable LEDs

• 3 Indicator LEDs: processor has passed self-test, 3.3 V is supplied to SDRAM, and 3.3 V is

supplied to sec ondary PCI slots

• Flash ROM, 2 Mbytes

• Logic analyzer connectors for SDRAM bus, ROM bus and secondary PCI arbitration signals

• Fan heatsink monitor circuit

• Battery bac kup for SDRAM

• JTAG header

1.2 Software Development Tools

A number of software development tools are availab le for the i960® processor family1. This

man ua l provi d es in f orma ti o n on two so f t w a re developme n t toolsets: Wind Ri ver Sys tem’s

Tornado* for I

through the inf ormation in this chapter and in Chapter 2 to gain a general understanding of how to

use your tools with thi s boa rd.

0* and Intel’s CTOOLS. If you are using other software development tools, read

2

1. To view the electronic tools catalog, access http://developer.intel.com/design/develop.htm/ from the web.

IQ80960RM/RN Evaluation Board Ma nual 1-3

Page 10

Introduction

1.3 Tornado* for I20* Software Development Toolset

T orna do for I

compiler, assembler, linker, and debugger. It also features a real-time operating system.

0 is a complete toolset featuring an integrated development environment including a

2

1.3.1 IxWorks* Real-Time Operating System

The IQ80960RM/RN platforms are equipped with Wind River Systems, Inc.’s IxWorks*. IxWorks

provides for the elements of the I

protocols, and executive modules for configuration and control. IxWorks also allows for the

writing of basic devi ce drivers and provides NOS-to-driver independence. TORNADO for I

provides a visual environment for building, testing and debugging of I

O standard: an event-driven driver framework, host message

2

1.3.2 TORNADO Build Tools

TORNADO for I2O includes a coll ection of supporting tools tha t provide a complete development

tool chain. These include the compiler, assembler, linker and bina ry utilities. Als o provided is a n

O module builder, which crea tes I2O-loadable modules .

I

2

1.3.3 TORNADO Test and Debug Tools

TORNADO for I2O test and deb ug t ools i nclude th e dynamic l oader, the CrossWi nd∗ debugger , the

WindSh* interactive shell, and a system browser.

The dynamic loader allows for interactive loading, testing, and replacement of individu al object

modules that comprise a driver.

O drivers.

2

O

2

CrossWind is an extended version of GDB960. Using it you can debug I

breakpoints on desired I

locals, stack frame, memory and so on.

WindSh allows you to commun icate to the IQ80960RM/RN platform via an RS-232 serial port.

The IQ80960RM/RN pla tform supports port speeds from 300 to 115,200 bps. The shell can be

used to:

• control and monitor I

O components. A variety of windows display source code, registers,

2

O drivers

2

O drivers by setting

2

• format, send and receiv e d river messages

• examine hardware registe rs

• run automated I

The shell also provides essential debugging capabilities; including brea kpoints, single stepping,

stack checking, and disassembly.

O test suites

2

1-4 I Q80960RM/RN Evaluation Board Manu al

Page 11

1.4 CTOOLS Software Development Too ls et

Intel’s i960 processor software development toolset, CTOOLS, features advanced

C/C++ - language compilers for the i960 processor family. CTOOLS development toolset is

available for Windows* 95/NT-based systems and a variety of UNIX workstation hosts. These

products provide execution pr ofiling and instruction scheduling optimizat ions and include an

assembler, a linker, and utilities designed for embedded proc essor software developm ent.

1.4.1 CTOOLS and the MON960 Debug Monitor

In place of IxWorks, the IQ80960RM/RN platform can be equippe d with Intel’s MON960, an

on-board softwa re monitor that allows you to execute and debug programs written for i960

processors in a non-I

step, memory display, and other useful functions for runnin g and de bugging a program.

The IQ80960RM/RN platform works with the source-level debuggers provided with CTOOLS,

including GDB960 (command line version) and GDB960V (GUI version).

1.4.1.1 MON960 Host Communications

MON960 allows you to communicate and download programs developed for the IQ80960RM/RN

platform across a host system’s s erial port or PCI interface. The IQ80960RM/RN platform supports

two methods of communication: terminal emulation and Host Debugger Interface (HDI).

2

O environment. The monitor provides program download, bre akpoint, single

Introduction

1.4.1.2 Terminal Emulation Method

Terminal emulation software on your host system can communicate to MON960 on the

IQ80960RM/RN platform via an RS-232 serial port. The IQ80960RM/RN platform s upports port

speeds from 300 to 115,200 bps. Serial downl oads to MON960 require that the terminal emulation

software support th e XMODEM proto col.

Configure the serial port on the host system for 300-115,200 baud, 8 bits, one stop bit, no parity

with XON/XOFF flow control.

1.4.1.3 Host Debugger Interface (HDI) Method

You may use a source-l evel debugger, such as Intel’s GDB960 a nd GDB960V to establish seria l or

PCI communications with the IQ80960RM/RN platform. The MON960 Host Debugger Interface

(HDI) provides a defined mess aging layer between MON960 and the debugger. For more

information on this interface, see the MON960 Debug Monitor User’s Manual (484290).

HDI connection requests cannot be detected by MON960 if the user has already initiated a

connection using a terminal emula tor. In this case, the IQ80960RM/RN platform must be reset

before the debugger can connect to MON960.

1.5 SPI610 JTAG Emulation System

The SPI610 JTAG Emulation System from Spectrum Digital, Inc. is included in the

IQ80960RM/RN development kit. It fur nishes the default host development environment-toevaluation board communication link based on the i960 RM/R N I/O processor JTAG interface.

IQ80960RM/RN Evaluation Board Ma nual 1-5

Page 12

Introduction

Refer to the SPI610 Referen ce Manual for JTAG emulation system installation and operation for

both the Tornado and CTOOLS environment. Op tionally, evaluation board serial port

communications can be used for thi s com municati on link (s ee Secti on 1.3.3, “TORNADO Test and

Debug Tools” on page 1-4).

1.6 About Thi s M a nu a l

A brief description of the contents of this manual follows.

Chapter 1, “Introduction”

Chapter 2, “Getting Started”

Chapter3, “Hardware

Refere nce”

Chapter 4, “i960® RM/RN

I/O Processor Overview”

Chapter 5, “MON960

Support for IQ80960RM/RN”

AppendixA, “Bill of

Materials”

AppendixB, “Schematics”

AppendixC, “PLD Code”

AppendixD, “Recycling the

Battery”

Introduces the IQ80 960RM

chapter also describes Intel’s CTOOLS* and WindRiver Systems Ix Works*

software development tools, and defines notational-conventions and related

documentation.

Provid es st ep-b y-s te p i ns tru ct ions fo r in st al li ng t he IQ8 09 60R M or I Q80 96 0RN

platform in a host system and downloading and executing an application

program. This chapter also describes Intel’s software development tools, the

MON960 Debug Monitor, IxWORKS, software installation, and hardware

configuration.

Descri bes the locations of connector s, switches and LEDs on the IQ80960RM

and IQ80960RN platforms. Header pinouts and register descriptions are also

provided in this chapter.

Presents an overview of the capabilities of the i960 RM/RN I/O proc essor and

includes the CPU memory map.

Describes a number of features added to MON960 to support application

development on the i960 RM/RN I/O processor.

Shows complete parts list IQ80960RM and IQ80960RN Evaluation Platforms.

Complete set of schematics for the IQ80960RM and IQ80960RN Evaluation

Platforms.

Example PLD code used on IQ80960RM and IQ80960RN evaluation boards

for SDRAM battery backup.

Information on the RBRC program and the locations of participating recycling

centers.

and IQ80960RN Evaluation Board feat ures. This

1-6 I Q80960RM/RN Evaluation Board Manu al

Page 13

1.7 Notational-Conventions

The following notation conventions are consistent with other i960 RM/RN I/O processor

documentation and general indust ry standards.

Introduction

# or overbar

Bold Indicates user entry and/or c ommands.

Italics Indicates a reference to related docum ents; also used to show emphasis.

Courier font I ndicates code examples and file di rectories and names.

Asterisks (*) On non-Intel company and product names, a tra iling asterisk indicates

UPPERCASE In text, signal na mes are shown in uppe rcase. When several sig nals shar e

Designations for

hexadecimal and

binary numbers

In code examples the pound sym bol (#) is appended to a signal name to

indicate that the signal is active. Normal ly inverted clock signals are

indicate d with an overbar above the signal name (e.g., RAS).

PLD signal names are in bold lowercase letters (e.g., h_off, h_on).

the item is a tra d emark or register ed trademark. Such brand s and names

are the property of their respective owners.

a common name, each signal is represented by the signal name followed

by a numbe r; the group is represented by the signal name followed by a

variable (n). In code example s, signal names are shown in the case

required by the software development tool in us e.

In text, instead of using subscripted “base” designators (e.g., FF

leading “0x” (e.g., 0xFF) hexadecimal numbers are represented by a

string of hex digi ts followed by th e letter H. A zero prefix is added to

numbers that begin with A through F. (e.g . , FF is shown as 0FFH.) In

examples of actual code, “0x” is used. Decimal and binary numbers are

represented by their customary notations. (e.g. , 255 is a decimal number

and 1111 1111 is a binary number. In some cases, the letter B is added to

binary numbers for clari ty.)

16

) or

1.8 Technical Support

Up-to-date product and technical information is available electronically from:

• Intel’s World-Wide Web (WWW) Locatio n: http://www.intel.com

• IQ80960RM and IQ80960RN Produc t Information: http://developer.intel.com/d es ign/i960

For technical assistance, electronic m ail (e-mail) pro v id es the fastest route to reach engineers

specializing in IQ80960RM and IQ80960RN issues. Posting messages on the Embedded

Microprocessor Forum at http://support.intle.com/newsgroups / is also a direct rout e for

IQ80960RM and IQ80960RN technical assistance. See Section 1.8.2.

Within the United States and Canada you may contact the Intel Technical Support Hotline. See

Section 1.8.1 for a list of customer support sources for the US and other geographical area s.

IQ80960RM/RN Evaluation Board Ma nual 1-7

Page 14

Introduction

1.8.1 Intel Customer Electronic Mail Supp ort

For direct support from engineer s specia li ng in i960® Microprocessor issues send e-mail in english

to 960tools@intel.com.

Questions and other messages may be posted to the Embedded Microprocessor Forum at

http://support.intel.com/newsgroups/.

1.8.2 Intel Cus to mer Su pp or t Con ta ct s

Contact Intel Corporation for technical assistance for the IQ80960RM/RN evaluation platform.

Country Literature Customer Suppo rt Number

United States 800-548-4725 800-628-8686

Canada 800-468-8118 or 303-297-7763 800-628-8686

Europe Contact local distributor Contact local distri butor

Australia Contact local distributor Contac t local distribu tor

Israel Contact local distributor Contact local distributor

Japan Contact local distributor Contact local distributor

1-8 I Q80960RM/RN Evaluation Board Manu al

Page 15

1.8.3 Related Information

T o orde r printe d manua ls fro m Intel, c ontac t your loc al sales re prese ntati ve or Intel L iteratur e Sal es

(1-800-548-4725 ).

Table 1-1. Document Information

Product Document Name Compan y/ Order #

Introduction

All

80960RM/RN

Developers’ Insight CD-ROM

i

960®

RM/RN I /O Processor Developer’s Manual

80960RM I/O Processor

80960RN I/O Processor

i

960®

RM/RN I/O Processor Design Guide

MON960 Debug Monitor User’s Guide

PCI Local Bus Specification

Writing I2O Device Drivers in IxWorks

IxWorks Reference Manual

VxWorks Programmer’s Guide

Tornado User’s Guide

Tornado for I2O

Tornado for I2O Compact Disk

SP610 Em ulation System Reference Manual

Data Sheet Intel # 273156

Data Sheet Intel # 273157

Revision2.1

Rev. 1.0 #TDK-12380-ZC-00

Intel # 273000

Intel # 273158

Intel # 273139

Intel #484290

PCI Special Interest Group

1-800-433-5177

Wind River Systems, Inc.

#DOC-1173-8D-02

Wind River Systems, Inc.

#DOC-1173-8D-03

Wind River Systems, Inc.

#DOC-11045-ZD-01

Wind River Systems, Inc.

#DOC-1116-8D-01

Wind River Systems, Inc.

#DOC-12381-8D-00

Spectrum Dig ita l Inc.

# 503715

Contact Cyclo ne Microsystems for additional information about their products and literature:

Table 1-2. Cyclone Contacts

Phone: 203-786-5536

Cyclone Microsystems

25 Science Park

New Haven CT 06511

IQ80960RM/RN Evaluation Board Ma nual 1-9

F AX: 203-786-5025

e-mail: info@cyclone.com

WWW: http://www.cyclone.com

Page 16

Page 17

Getting Started

This chapter conta ins in struc tio ns for ins tall ing the IQ80 960RM/ RN platfor m in a host s yste m and,

how to download and execute an application program using Wind River System’s IxWorks∗ or

Intel’s CTOOLS software development toolsets.

2.1 Pre-Installation Considerations

This section pr ovides a general overview of the components required to develop and exec ute a

program on the IQ80960RM/RN platform. IQ80960RM/RN evaluation boards support two

software development toolsets, Wind River System’s IxWorks and Intel’s CTOOLS.

IxWorks is a complete toolset featuri ng an integrated developmen t environment including a

compiler, assembler, linker, and debugger . It al so features a real-time operati ng system. If you are

using the IxWorks operating system with th e T O RNADO* development environment, refer to the

Wind River Systems, Inc. doc umentation referenced in Sectio n 1.8.3.

CTOOLS is a complete C/C++-language software-development toolset for developing embedded

applications to run on i960 processors. It contains a C/C++ compiler, the gcc960 and ic960 compiler

driver programs, an assembler, runtime libraries, a collection of software-development tools and

utilities, and printed and on-line documentation. The MON960 Debug Monitor User’s Guide fully

describes the components of MON960, including MON960 commands, the Host Debugger Interface

Library (HDIL), and the MONDB.EXE utility. If you are using MON960 and the CTOOLS toolset,

refer to section Section 2.2.1, “Installing Software Development Tools” on page 2-1.

2

See Chapter 1 for more information on the IxWorks and CTOOLS features.

The IQ80960RM/RN evaluation boards are supplied with IxWorks intelligent real-time operating

system pre-loaded into the on-board Flash. You also have the option of installing the MON960

debug monitor, which is required if you are using the CTOOLS debugging tools, GDB960,

GDB960V, or MONDB. Sec ti o n 3.3.1 descr ibes the Fla sh ROM pro gramming util it y, which allows

you to load MON960 onto the platform or re-load IxWorks.

2.2 Software Installation

2.2.1 Installing Software Development Tools

If you haven’t done so already, install your development software as described in its manuals. All

references in this manual to CTOOL S or CrossWind assume that the default directories were

selected dur ing installation. If this is not the case, substitute the appropriate path for the defa ult

path wherever fil e loc ations are referenced in this manual.

IQ80960RM/RN Evaluation Board Ma nual 2-1

Page 18

Getting Started

2.3 Hardware Installation

Follow these in st ructions to get your new IQ80960RM/RN platform running. Be sure all items on

the checklist were provided with your IQ80960RM/RN.

Warning: Static charges can severely damage th e IQ80960RM/RN platforms. Be sure you are properly

grounded before re moving the IQ80960RM/RN platform from the anti-sta tic bag.

2.3.1 Battery Bac ku p

Battery backup is provided to save any information in SDRAM during a power failure . Th e

IQ80960RM/RN platform contains four AA NiCd bat teries, a charging circuit and a regul ator

circuit. The batte ries installed in the IQ80960RM/RN platform are rated at 600 mA/Hr.

SDRAM technology provides a simple way of enabling data preservation through the self-refresh

command. When the processor receives an active Primary PCI reset it issues the self-refresh

command and drives the SCKE signals low. Upon seeing this condition, a PAL on the

IQ80960RM/RN platform holds SCKE low before the processor loses power. The batteries

maintain power to the SDRAM and the PAL to ensure self-refresh mode. When the PAL detects

PRST# returning to ina ctive state, the PAL releases the hold on SCKE.

The battery circuit can be disabled by removing the batteries. LED CR4 indicates when the SDRAMs

have sufficient power. If the batteries remain in the evaluation platform when it is depowered and/or

removed from the chassis, the batteries will maintain the SDRAM for approximately 30 hours. Once

power is again applied, the batteries will be fully charged in about 4 hours.

2.3.2 Installing the IQ80960RM/RN Platforms in the Host System

If you are installing the IQ80960RM/RN platform for the first time, visually inspect the board for

any damage that may have oc curred during shipment. If there are visible defects, return the board

for repl acement. Follow the host system manufacturer’s instructions for in stalling a PCI adapter.

The IQ80960RM/RN pl atform is a full-length PCI adapter and requires a PCI slot th at i s free from

obstructions. The IQ80960RM/RN platform is ta ller than specifie d in the PCI Local Bus

Specification Revision 2.1. The extended height of the board will require you to kee p the cover off

of your PC. Refer to Chapt er 3 for physical dimensions of the board.

2.3.3 Verify IQ80960RM/RN Platform is Functional

These instruct ions ass ume that you have alrea dy install ed the I Q80960RM/RN pla tfor m in the host

system as described in Section 2.3.2.

1. To connect the serial port for communicati ng with and downloading to the IQ80960RM/RN

platform, conne ct the RS-232 cable (provided with the IQ80960RM/RN) from a free serial

port on the host syst em to the phone jack-s tyle connector on the IQ80960RM/RN platform.

2. Upon power-up, the red FAIL LED turns off, indicating that the processor has passed its self-test.

3. If you have IxWorks installed in the flash R OM, the user LEDs dis play the bi na ry pattern 99H.

In the IxWorks development environment, raw serial input/output is not used. Instead , the

Wind DeBug (WDB) protocol is run over the serial port, to a llow communication with

Tornado development tools. If t he terminal emu lation package is running at 115,200 baud, the

letters “W DB_READY” display prior to launching in the WDB serial protocol.

2-2 I Q80960RM/RN Evaluation Board Manu al

Page 19

4. If you have MON960 installed in the fl as h ROM, press <ENTER> on a termin al con nec te d to

the IQ80960RM/RN platform to bring up the MON960 prompt. MON960 automatically

adjusts its baud rat e to match that of the te rmi nal at start-u p. At ba ud rates other than 9600, it

may be necessary to press <ENTER> several times.

2.4 Creating and Downloading Executable Files

To download code to the IQ80960RM/RN pla tform running IxWorks, consult Wind River

documentation on the s upplied TORNADO for I

IQ80960RM/RN platform, your compiler produces an ELF-format object file.

To download code to the IQ80960RM/RN platform running CTOOLS, consult the CTOOL S

documentation for information regarding compiling, linking, and downloading applications.

During a download, MON960 check s the link address stored in the ELF file, and stores the file at

that locati on on the IQ80960RM/RN platform. If the executa ble file is linked to an invalid address

on the IQ80960RM/RN platform, MON960 aborts the download.

2.4.1 Sample Download and Executio n Using GDB960

This example shows you how to us e GBD960 to download and exec ute a file named myapp via

the serial port.

O CD-ROM. T o download code to the

2

Getting Started

• Invoke GDB960. From a Windows 95/NT command prompt, issue the command:

gdb960 -r com2 myapp

This command establ ishes communication and downloads the fil e myapp.

• To execute the program, enter the command from the GDB960 comm and prompt:

(gdb960) run

More information on the GDB960 commands mentioned in this section can be found in the

GDB960 User’s Manu al.

IQ80960RM/RN Evaluation Board Ma nual 2-3

Page 20

Page 21

Hardware Reference

3.1 Power Requirements

The IQ80960RM/RN platform draws power from the PCI bus. The power requirements of the

IQ80960RM/RN platforms are shown in Table 3-1 and Table 3-2. The number s do not include the

power required by a PCI card(s) mounted on one or more of the IQ80960RM/RN platforms’ f ou r

expansion slot s.

Table 3-1. IQ80960RN Platform Power Requirements

Voltage Typical Current Maximum Current

+3.3 V 0 V* 0 V*

+5 V 1.45 A 1.96 A

+12 V 286 mA 485 mA

-12 V 1 mA 1 mA

NOTE: Does not include the pow er required by a PCI card(s) mounted on the IQ80960RN platform.

* +3.3V for 80960RN Processor created on board from +5V.

Table 3-2. IQ80960RM Platform Power Requirements

3

NOTE: Does not include the pow er required by a PCI card(s) mounted on the IQ80960RM pla tform.

* +3.3V for 80960RM Processor created on board from +5V.

3.2 SDRAM

The IQ80960RM/RN platform is equipped with a 168-pin DIMM socket formatted to accept +3.3V

synchronous DRAM with or without Error Correction Code (ECC). T he socket will acc ept SDRAM

from 8 Mbytes to 128 Mbytes. 128 Mbyte SDRAMs are available in both x64 and x72 configurations.

Note that 8 Mbyte SDRAMs are only for x64 or non-ECC memory. The SDRAM is accessible from

either of the PCI buses, via the ATUs, and the local bus on the IQ80960RM/RN platform.

Voltage Typical Current Maximum Current

+3.3 V 0 V* 0 V*

+5 V 1.32 A 1.86 A

+12 V 284 mA 485 mA

-12 V 1 mA 1 mA

IQ80960RM/RN Evaluation Board Ma nual 3-1

Page 22

Hardware Reference

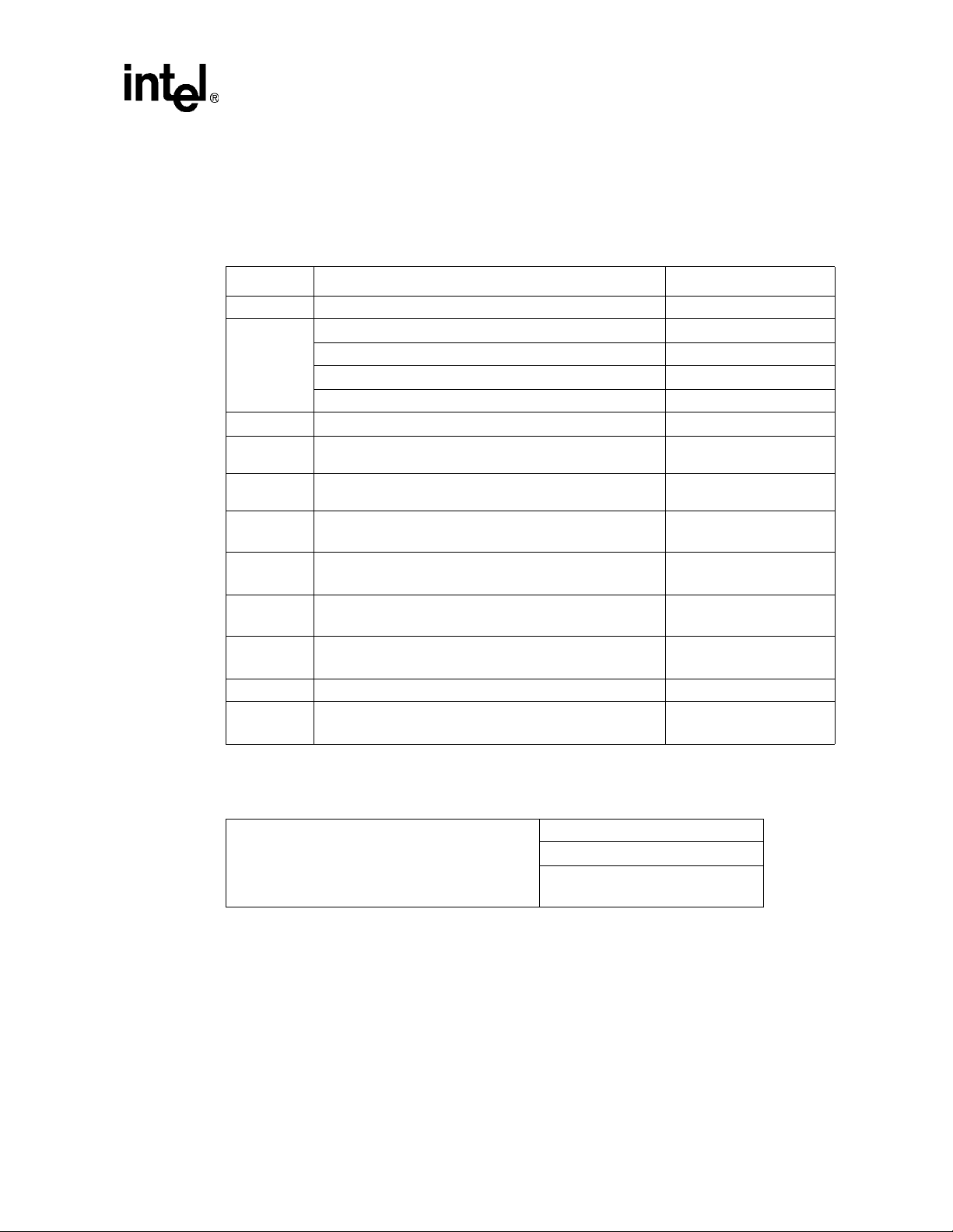

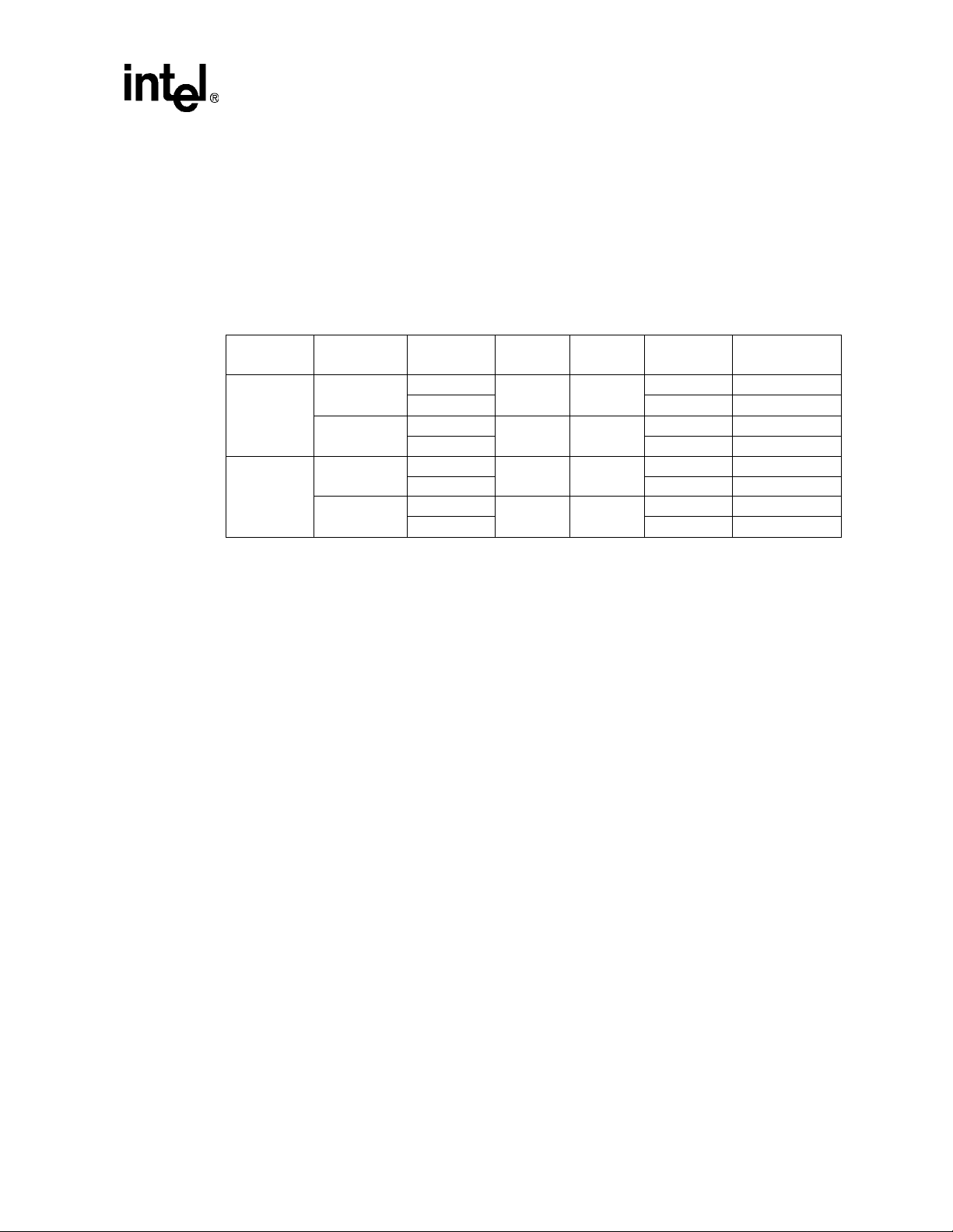

3.2.1 SDRAM Performance

The IQ80960RM/RN pla tform uses 72-bit SDRAM with ECC or 64-bit SDRAM without ECC.

SDRAM allows zero data-to-data wait state operation at 66 MHz. The memory controller unit

(MCU ) of the i 96 0

of four enables sea mless read/write bursting of long data streams, as long as the MCU does not

cross the page boundary. Page boundaries are naturally aligned 2 Kbyte blocks. 72-bit SDRAM

with ECC allows a maximum throughput of 528 Mbytes per second.

Both 16 Mbit and 64 Mbit SDRAM devices are supporte d. The MCU keeps two pages per ba nk

open simulta neous ly for 16 Mbit de vices a nd 4 pages pe r ba nk for 64 Mb it device s. Si multa neous ly

open pages allo w for greate r performanc e for seq uentia l access , dist ribute d acros s multipl e in ternal

bus transactions. Table 3-3 shows read and write examples of a single 8 byte access and for a

multiple 40 byte access.

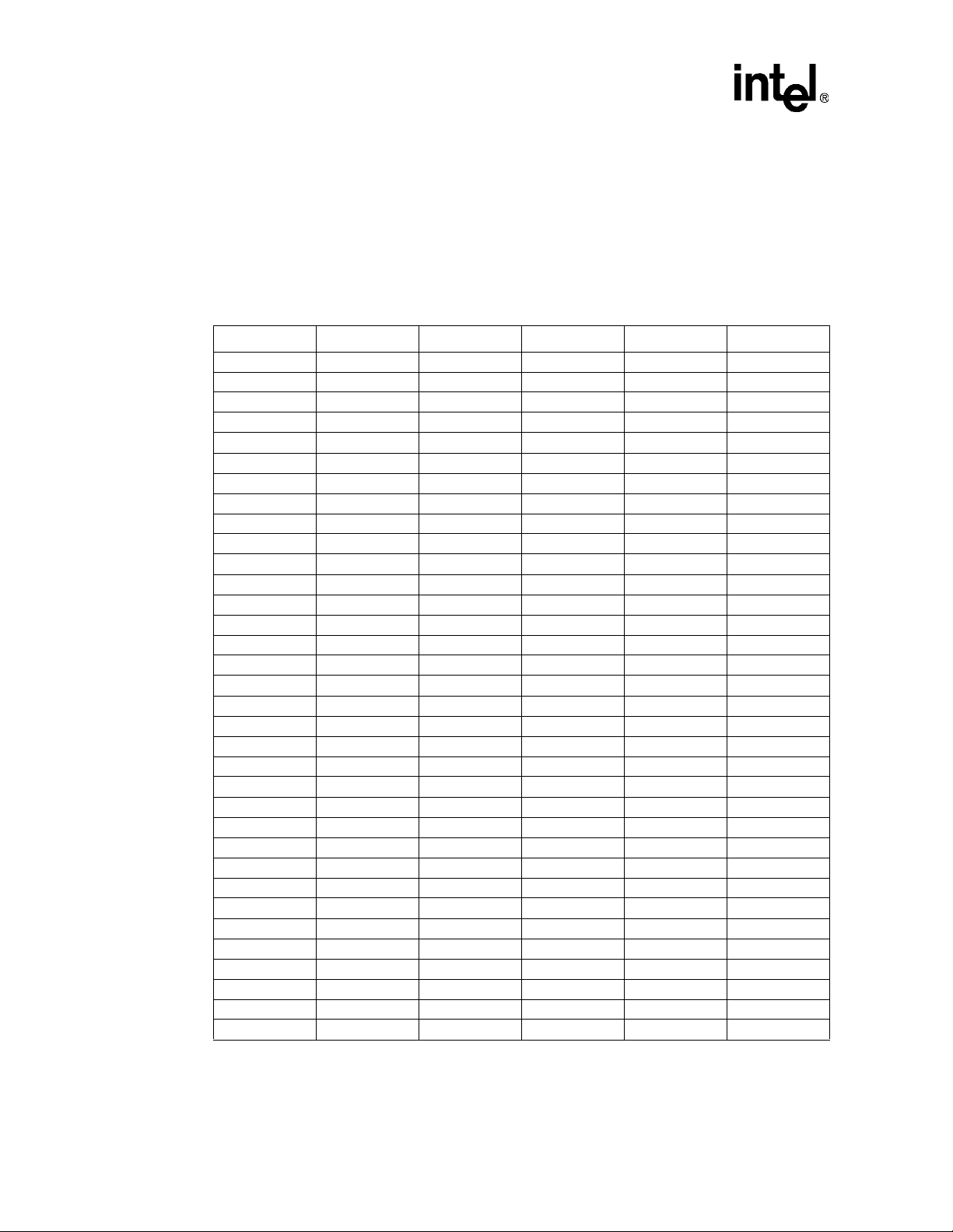

Table 3-3. SDRAM Performance

Read Pag e Hit (8 by te s) 7 76 Mby tes /s ec

Read Page Miss (8 bytes) 12 44 Mbytes/sec

Read Pa ge Hit (40 bytes) 11 240 Mbytes/sec

Read Page Miss (40 bytes) 16 165 Mbytes/sec

Write Page Hit (8 bytes) 4 132 Mbytes/sec

Write Page Miss (8 bytes) 8 66 Mbytes/sec

Write Page Hit (40 bytes) 8 330 Mbytes/sec

Write Page Miss (40 bytes) 12 220 Mbytes/sec

®

RM/RN I/O processor supports SDRAM burst lengt hs of four. A burst length

Cycle Type T able Clocks Performance Bandwidth

Note that if ECC is enabled and you attempt a partial write — less than 64 bits — you will incur a

penalty. Because ECC is enabled, the MCU will translate the write into a read-modify-write

transaction. Therefore, for a single byte write the clock count will be 1 1.

3-2 I Q80960RM/RN Evaluation Board Manu al

Page 23

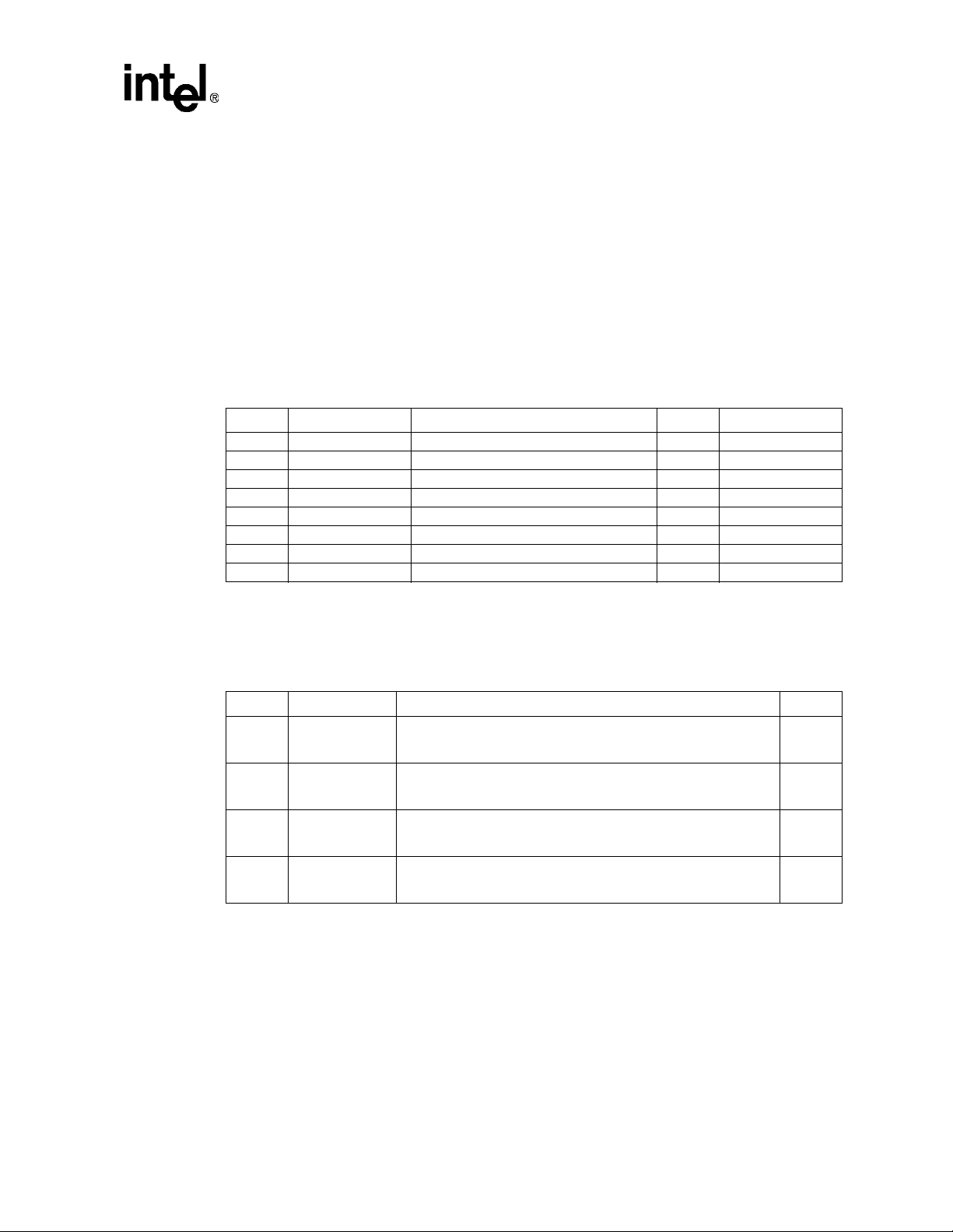

3.2.2 Upgrading SDRAM

The IQ80960RM/RN is equipped with 16 Mbytes of SDRAM with ECC inserted in the 168-pin

DIMM socket. The memory may be expanded by inserting up to a 128 Mbyte module into the

DIMM socket. The various memory c ombinations are shown in Table 3-4. Only 168-pin +3.3V

SDRAM modules with or witho ut ECC rated at 10 ns should be used on the IQ80960R M/RN

platform. The column labeled ECC dete rmines if that parti cular memory configuration c an be used

with ECC.

Table 3-4. SDRAM Configurations

Hardware Reference

SDRAM

Technology

16 Mbit

64 Mbit

SDRAM

Arrangement

2M x 8

1M x 16

8M x 8

4M x 16

# Banks Row Column ECC

1

2 Yes 32 Mb yt es

1

2 No 16 Mbyt es

1

2 Yes 128 Mbytes

1

2 No 64 Mbyt es

3.3 Flash ROM

An E28F016S5 (2 Mbytes) Flash ROM is included on the IQ80960RM/RN platform. This Fl ash

ROM contains IxWorks* and may be used to store user ap plications.

3.3.1 Flash ROM Programming

Two types of Fl ash ROM programming exist on the IQ80960RM/RN platform. The first is normal

application development programming. T his occurs using IxWorks to download new software and

the 80960JT core to writ e the new code to the Flash ROM. During this time the boot sec tors

(containing IxWorks) are write protected.

11 9

11 8

12 9

12 8

Total Memory

SIze

Yes 1 6 Mb yt es

No 8 Mbytes

Yes 6 4 Mb yt es

No 3 2 Mbytes

The second type of Flash ROM progra m mi ng is loading the boot sectors. You will not be required

to load the boot sectors except:

• To load MON960

• To load a new rele ase of IxWorks

• To change between the check build and the fre e build of IxWorks

The following steps are required to program the Flash ROM boot sectors:

1. Set switch S1 #’s 1 and 2 to the on position.

2. Reset the board by cycling power on the workstation.

3. Run the Intel DOS-based flash utility to program the Flash ROM boot sectors.

4. Set switch S1 #’s 1 and 2 to the off position.

5. Reset the board by cycling power on the workstation.

IQ80960RM/RN Evaluation Board Ma nual 3-3

Page 24

Hardware Reference

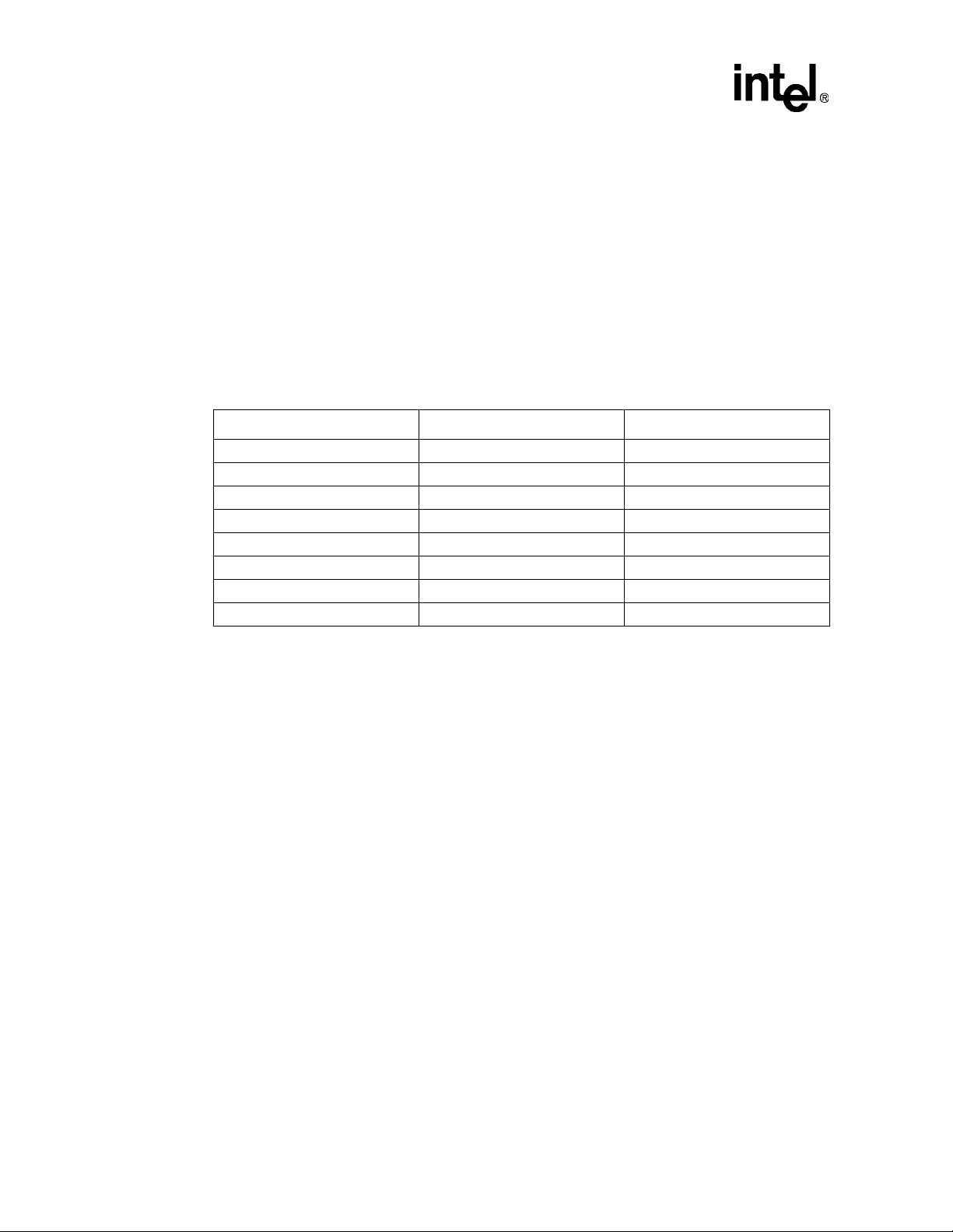

3.4 Console Serial Port

The console seria l port on the IQ80960RM/ RN platform, based on a 16C550 UART, is capable of

operation from 300 to 115,200 bps. The port is connected to a phone jack-style plug on the

IQ80960RM/RN platform. The DB25 to RJ-45 cable included w ith the IQ80960RM/RN can be

used to connect the console port to any standard RS-232 port on the host system.

The UART on the IQ80960RM/RN platform is clock ed with a 1.843 MHz clock, and may be

programmed to use thi s clo ck with its in te rnal baud rate coun ters. Th e UAR T regi ste r address es are

shown in Table 3-5; refer to the 16C550 device data book for a detailed description of the registers

and device operat ion. Note that some UART addresses refer to different registers depending on

whether a read or a write is being per f orm ed.

Tab le 3-5. UART Register Addresses

Address Read Register Write Register

E000 0000H Receive Holding Register Transmit Holding Register

E000 0001H Unused Interrupt Enable Register

E000 0002H Interrupt Status Register FIFO Control Register

E000 0003H Unused Line Control Register

E000 0014H Unused Modem Control Register

E000 0015H Line Status Register Unused

E000 0016H Modem Status Register Unused

E000 0017H Scratchpad Register Scratchpad Register

3.5 Secondary PCI Bus Expansion Connectors

Four PCI Expansion Slots are available on the IQ80960RM/RN platform. The IQ80960 RM

supports 32-b it P CI expansion and the IQ80960RN supports 64-bit PCI expans ion. The slots ar e

designed for +5V PCI signall ing and accommodate PCI cards with +5V or univers al s ignalling

capabilities.

3.5. 1 PCI Slots Power A vailabili ty

Power from the Primary PCI bus, +3.3V, +5V, +12V, and –12V, is routed to the Secondary P CI bus

expansion sl ots. +3.3V is only available at the secondary PCI slots if the host system makes +3.3V

available on the Primary PCI slots. LED CR5 indicates if this power is available.

3-4 I Q80960RM/RN Evaluation Board Manu al

Page 25

3.5.2 Interrupt and IDSEL Routing

Table 3-6. Secondary PCI Bus Interrupt and IDSEL Routing

Connector IDSEL INTA# INTB# INTC# INTD#

J11 SAD16 SINTA# SINTB# SINTC# SINTD#

J12 SAD17 SINTB# SINTC# SINTD# SINTA#

J13 SAD18 SINTC# SINTD# SINTA# SINTB#

J14 SAD19 SINTD# SINTA# SINTB# SINTC#

3.6 Battery Backup

Battery backu p is provided to save any information in SDRAM during a power failure. The

IQ80960RM/RN platform contains four AA NiCd batteries, a charging circuit and a regulator

circuit. The batteries installed in the IQ80960RM/RN pla tform are rated at 600 mA/H r.

SDRAM technology pro vides a simple way of enabling data preservation though the self-refresh

command. When the processor receives an active Primary PCI reset it will issue the sel f-refresh

command and drive the SCKE signals low. Upon seeing this condition a PAL on the

IQ80960RM/RN platfor m will hol d SCKE low before the proce ssor los es power. The batteries will

maintain power to the SDRAM and the PAL to ensure self-refresh mode. When the PAL sees

PRST# r et ur n i n g to in active st at e th e PAL wi ll re lease the h ol d on SC K E .

Hardware Reference

The battery circuit can be disabled by removing the batteries. LED CR4 indicates when the

SDRAMs have suff icient power . If the batteries remain in the evaluation platf orm when it is

depowered and/or removed from the chassis, the batteries will maintain the SDRAM for

approximately 30 hours. Once power is again applied, the batteries will be fully charged in about

four hours.

3.7 Loss of Fan Detect

The i960 RM/RN I/O processor can be cooled by an active he at sink mounted on top. T he fan

provides a square wave output that is monitored by a comparator circuit on the IQ80960RM/RN

platform. The frequency of the fan output is appr oxim ately 9K RPM. If the frequency fall s below

approximately 8K RPM the circuit will provide an interrupt to the processor. This is an evaluation

board feature intended as an example of system hardware monitoring, sin ce the IQ80960RM/RN

platf o r m does no t ship with a heatsin k .

Note: When using a passive heat sink, the proces so r never sees an interrupt from not having a fan.

IQ80960RM/RN Evaluation Board Ma nual 3-5

Page 26

Hardware Reference

3.8 Logic Analyzer Headers

There are five logic analyzer connectors on the IQ80960RM/RN platform. The connectors are

Mictor type, AMP part # 76705 4-1. Hewl ett-Pa ckard a nd Tektronix manufac ture an d sell i nte rfaces

to these connectors. The logic analyzer connectors al low for interfacing to the SDRAM and ROM

buses along with secondary PCI arbitration signals. Table 3-7 shows the connectors and the pin

assignm e nt s fo r each.

Table 3-7. Logic Analyzer Header Definitions

PIN J9 J11 J12 J10 J8

3 SDRAMCLK

4 DQ15 SDQM7 DQ31 RAD15

5 DQ14 SDQM6 DQ30 RAD14

6 DQ13 SDQM5 DQ29 RAD13

7 DQ12 SDQM4 DQ28 RAD12

8 DQ11 SDQM3 DQ27 RAD11

9 DQ10 SDQM2 DQ26 RAD10

10 DQ9 SDQM1 DQ25 RAD9

11 DQ8 SDQM0 DQ24 RAD8

12 DQ7 SCB 7 DQ23 RAD7

13 DQ6 SCB 6 DQ22 RAD6

14 DQ5 SCB 5 DQ21 RAD5

15 DQ4 SCB 4 DQ20 RAD4

16 DQ3 SCB3 DQ19 SCE0# RAD3

17 DQ2 SCB2 DQ18 SCE1# RAD2

18 DQ1 SCB 1 DQ17 SBA1 RAD1

19 DQ0 SCB 0 DQ16 SBA0 RAD0

20 DQ32 SA0 DQ48 SREQ0# RAD16

21 DQ33 SA1 DQ49 SREQ1#

22 DQ34 SA2 DQ50 SREQ2#

23 DQ35 SA3 DQ51 SREQ3# RALE

24 DQ36 SA4 DQ52 SREQ4# RCE0#

25 DQ37 SA5 DQ53 SREQ5# RCE1#

26 DQ38 SA6 DQ54 SGNT0# ROE#

27 DQ39 SA7 DQ55 SGNT1# RWE#

28 DQ40 SA8 DQ56 SGNT2#

29 DQ41 SA9 DQ57 SGNT3# I_RST#

30 DQ42 SA10 DQ58 SGNT4#

31 DQ43 SA11 DQ59 SGNT5#

32 DQ44 DQ60

33 DQ45 SWE# DQ61

34 DQ46 SCAS# DQ62

35 DQ47 SRAS# DQ63

36 P_PCICLK RALE

3-6 I Q80960RM/RN Evaluation Board Manu al

Page 27

3.9 JTAG Header

The JTAG header allows debugging hardware to be quic kly and easily connected to some of the

IQ80960RM/RN proc essor’s logic signals.

The JTAG header is a 16-pin header. A 3M connector (part number 2516-6002UG) is required to

connect to this header. The pinout for the JTAG header is shown in Table 3-8. The header and

connector are keyed using a tab on the connector and a slot on the header to ensure proper installation.

Hardware Reference

Each signal in the JTAG header is pa ired with its own ground connection to avoid the noise problems

associated with long ribbon cables. Signal descriptions are found in the i960

Developer’s Manual, 80960RM I/O Processor Data Sheet and the 80960RN I/O Process or Data Sheet.

Table 3-8. JTAG Header Pinout

Pin Signal Input/Output to 80960RM/RN Pin Signal

1 TRST# IN 2 GND

3 TDI IN 4 GND

5 TDO OUT 6 GND

7TMS IN 8GND

9TCK IN 10GND

11 LCDINIT# IN 12 GND

13 I_RST# OUT 14 GND

15 PWRVLD OUT 16 GND

Table 3-9 describes switch setti ng options and defaults. These switch settings are sampled at

Primary PCI Reset. See Table 5-1 “Initialization Modes” on page 5-3 for processor initialization

configurations .

Table 3-9. Switch S1 Settings

Position Name Description Default

S1-1 RST_MODE#

S1-2 RETRY

S1-3 32BITMEM_EN#

a

S1-4

a. This switch is active for IQ80960RN ONLY.

32BITPCI_EN#

®

RM/RN I/O Pr oces sor

Determines if the processor is to be held in reset.

ON = hold in rest

OFF = allows processor initializati on

Deter m ines if the Primary PCI interface will be disabled.

ON = allows Primary PCI configuration cycles to occur

OFF = retries all Primary PCI configuration cycles

Notifies Memory Controller of the SDRAM width.

ON = Memory Controller utilizes 32-bit SDRAM access protocol

OFF = Memory Contoller utilizes 64-bit SDRAM access protocol

Determines whether Secondary PCI bus is a 32- or 64-bit bus.

ON = indicates Secondary PCI bus is a 32-bit bus

OFF = indicates Secondary P CI bus is a 64-bit bus

OFF

OFF

OFF

OFF

IQ80960RM/RN Evaluation Board Ma nual 3-7

Page 28

Hardware Reference

3.10 User LEDs

The IQ80 960RM /RN plat form has a bank of eight user -prog rammable LEDs, locat ed on the upper e dge of

the adapter board. These LEDs are controlled by a write-only register and used as a debugging aid during

development. Software can control the state of the user LEDs by writing to the LED Register, located at

E004 0000H. Each of the eight bits of this register correspond to one of the user LEDs. Clearing a bit in the

LED Register by writing a “0” to it turns the corresponding LED “on”, while setting a bit by writing a “1”

to it turns the corresponding LED “off”. Resetting the IQ80960RM/RN platform results in clearing the

register and turning all the LEDs “on”. The LED Register bitmap is shown in Figure 3-1.

The user LEDs are numbered in de scending order from left to right, with LED7 being on the left

when looking at the component side of the adapter.

Figure 3-1. LED Register Bitmap

76543210

User LED 7

User LED 6

User LED 5

User LED 4

User LED 3

User LED 2

User LED 1

User LED 0

3.10.1 User LEDs During Initialization

MON960 indicate s the progress of its hardware initialization on the user LEDs. In the event that

initia lization should fail for s ome reason, the number of lit LEDs can be used to determine the

cause of th e failure . Table 3-10 lists the tes ts that correspond to each lit LED.

Tab le 3-10. Start-up LEDs MON960

LEDs Tests

LED 0 SDRAM serial EEPROM checksum validated

LED 1 UART walking ones test passed

LED 2 DRAM walking ones test passed

LED 3 DRAM multiword test passed

LED 4 Hardware initializat ion started

LED 5 Flash ROM initialized

LED 6 PCI-to-PCI Bridge initialized

LED 7 UART int ernal loopback test passed

3-8 I Q80960RM/RN Evaluation Board Manu al

Page 29

Table 3-11 lists the connectors and LEDs.

Ta ble 3-11. IQ80960RM/RN Connectors and LEDs

Item Description

J1-J4 Secondary PCI bus expansion connector

J5 168-pin SDRAM DIMM socket

J6 JT AG connector

J7 Serial port connector

J8 Logic analyzer connector for flash ROM bus

J10 Logic analyzer connector for Secondary PCI bus arbitrat ion signals

J9, J11, J12 Logic analyzer connecto r for access to SDRAM bus

J13 Active heatsink connector for example fan monitor circuit

CR1, CR2 Eight user LEDs

CR3 Self-test fail LED

CR4 Battery backup SDRAM, 3.3 V available

CR5 Indicates host system providing 3.3 V to Secondary PCI bus connectors

S1 DIP switch (Table 3-9)

Hardware Reference

IQ80960RM/RN Evaluation Board Ma nual 3-9

Page 30

Page 31

i960® RM/RN I/O Processor Overview

4

This chapter desc ribes the features and operation of the processor on the IQ80960 RM/RN

platform. For more detail, refer to the i960

Figure 4-1. i960

®

RM/RN I/O Processor Developer’s Manual.

®

RM/RN I/O Processor Block Diagram

Local Memory

(SDRAM, Flash)

80960 Core

Processor

Memory

Controller

Messaging

Unit

Two DMA

Channels

Bus

Interface

Unit

64-bit Internal Bus

Address

Translat ion

Unit

I2C Serial Bus

I2C Bus

Interface

Application

Accelerator

One DMA

Channel

Internal

Arbitration

Address

Translation

Unit

PCI to PCI

64-bit/32-bit Primary PCI Bus

Performance

Monitoring

Unit

IQ80960RM/RN Evaluation Board Ma nual 4-1

Bridge

64-bit/32-bit Secondary PCI Bus

Secondary

PCI

Arbitration

Page 32

i960® RM/RN I/O Processor Overview

4.1 CPU Memory Map

The memory map for the IQ80960RM/RN platform is shown in Figure 4-2. All addresses below

9002 0000H on the IQ80960RM/RN platform are reserved for various functions of the i960

RM/RN I/O processor, a s shown on the memory map. Doc ument ation for t hese areas , as we ll as t he

processor memory m apped registe rs at FF00 0000 H and the IBR , can be f ound i n the i 960

I/O Pro ce ssor Dev eloper’s Manual.

Figure 4-2. IQ80960RM/RN Platform Memory Map

®

RM/RN

F000 0000H

E000 0000H

B000 0000H

A000 0000H

9002 0000H

8000 0000H

0000 2000H

0000 1900H

0000 0800H

0000 0400H

0000 0000H

Flash RO M

and

Processor Registers

On-board Devices

Reserved

DRAM

Reserved

ATU Outbound

Translation Windows

ATU Outbound

Direct Addressing Window

Reserved

Peripheral

Memory Mapped Registers

Reserved

Processor Internal Data RAM

Processor

Memory Mapped

Registers

Flash ROM

Reserved

LED Register

(write only)

UART

FF00 0000H

FEE0 0000H

F000 0000H

E004 0000H

E000 0000H

4-2 I Q80960RM/RN Evaluation Board Manu al

Page 33

4.2 Local Interrupts

The i960 RM/RN I/O processor is built around an 80960JT core, which has seven external interrupt

lines designated XINT0# through XINT5# and NMI#. In the i960 RM/RN I/O processor, these

interrupt lines are not directly connected to external interrupts, but pass through a layer of internal

interrupt routing logic. Figure 4-3 shows the interrupt connections on the i960 RM/RN I/O processor.

XINT0# through XINT3# on the 80960JT core can be us ed to re ce ive PCI interrupt s from the

secondary PCI bus, or thes e interrupts can be passed through to the primary PCI interface,

depending on the setting of the XINT Select bit of the PCI Interrupt Routing Select Register in the

i960 RM/RN I/O processor. On the IQ80960RM/RN platform, XINT0# through XINT3# are

configured to receive interrupts from the secondary PCI bus.

XINT4# and XINT5# on the i960 RM/RN I/O processor may be connected to interrupt sources

external to the proc essor. On the IQ80960RM/RN platfor m, XINT4# is connec ted to th e loss of fan

detect and XINT5# is conne cte d to the 16C550 UART.

XINT6#, XINT7# receive interrupt s from internal sources . NMI# receives interrupts from internal

sources an d from an external source. Since all of these interrupts accept signal s from multiple

sources, a status register is provided for each of them to allow service routine s to identify the

source of the interrupt. Each of the possible interrupt sources is assigned a bit position in the sta tus

register. The interrupt sources for these lines are shown in Figure 4-3. On the IQ80960RM/RN

platform, the NMI# interrupt is not connected to any external interrupt source and receives

interrupts onl y from the internal devices on the i960 RM/RN I/O proc es s or. Note that all error

conditions result in an NMI# interrupt.

i960® RM/RN I/O Processor Overview

IQ80960RM/RN Evaluation Board Ma nual 4-3

Page 34

i960® RM/RN I/O Processor Overview

Figure 4-3. i960® RM/RN I/O Processor Interrupt Controller Connections

P_INTB# Output

P_INTC# Output

P_INTD# Output

P_INTA# Output

i960®RN/RM I/O Processor

S_INTA#/XINT0#

S_INTB#/XINT1#

S_INTC#/XINT2#

S_INTD#/XINT3#

XINT4#

(Loss of Fan)

XINT5# (UART)

NMI# (N/C)

S_INTD# Select bit

S_INTC# Select bit

S_INTB# Select bit

S_INTA# Select bit

m

u

x

m

u

x

m

u

x

m

u

x

DMA Channel 0 Interrupt Pending

DMA Channel 1 Interrupt Pending

DMA Channel 2 Interrupt Pending

Performance Monitor Unit Interrupt Pending

Application Accelerator Interrupt Pending

I2C Bus Interface Unit Interrupt Pending

Messaging Unit Interrupt Pending

Primary ATU/Start BIST Interrupt Pending

Primary PCI Bridge Interface Error

Secondary PCI Bridge Interface Error

Bus Interface Unit Error

Primary ATU Error

Secondary ATU Error

Memory Controller Unit Error

DMA Channel 0 Error

DMA Channel 1 Error

DMA Channel 2 Error

Application Accelerator Unit Error

Messag ing Unit Er ro r

80960 Outbound Doorbell 0

80960 Outbound Doorbell 1

80960 Outbound Doorbell 2

80960 Outbound Doorbell 3

Latch

XINT6 Interrupt

Latch

XINT7 Interrupt

Latch

NMI Interrupt

XINT0#

XINT1#

XINT2#

XINT3#

XINT4#

XINT5#

XINT6#

XINT7#

NMI#

i960 Core

Processor

4-4 I Q80960RM/RN Evaluation Board Manu al

Page 35

4.3 CPU Counter/Timers

The i960 RM/RN I/O processor is equipped with two on-chip counter/timers which are clocked

with the i960 RM/ RN I/O process or clock s ignal. The i 960 RM/RN I/ O proc essor re ceives its c lock

from the primary PCI interface clock, generated by the motherbo ard. Most motherboards generat e

a 33 MHz clock signal, although the PCI specification requires a clock frequency between 0 and

33 MHz. The timers can be prog rammed for single-shot or continuous mode, and can generate

interrupts to the proc es s or when the countdown expires.

4.4 Primary PCI Interface

The primary P CI interface on the IQ80960RM/RN platform provides the i960 RM/RN I/O

processor with a connection to the PCI bus on the host system. Only the PCI-to-PCI bridge unit on

the i960 RM/RN I/O proc essor i s dire ctly c onnect ed to the primary P CI interf ace. Devices i nstall ed

on the expansion sl ots are connected to the PCI bus via the bridge unit on the i960 RM/RN I/O

processor. The PCI-to-PCI bridge accepts Type 1 configuratio n cyc les destined for devices on the

secondary bus, and will forward them as Type 0 or Type 1 con f iguration cycles, or as special

cycles. The IQ80960RN pla tform interfac es to a 64-bit PCI bus and the IQ80960RM platform

interfaces to a 32-bit PCI bus.

i960® RM/RN I/O Processor Overview

4.5 Secondary PCI Interface

The secondary PCI interface provided by the i960 RM/RN I/O processor is used to connect PCI

cards via the expansion slots to the host system’s PCI bus. PCI cards are attached to the

IQ80960RM/RN platform with a standard PCI connector and may contain up to four separate PCI

devices. The i960 RM/RN I/O processor provides PCI-to-PCI bridge functionality to map installed

PCI devices onto the host P CI bus , and supports tr ans action forwarding in both directions across

the bridge. PCI devi ces connected via the expansion slots can therefore act as masters or slaves on

the host sys tem’s PCI bus. Additional PC I-to- PCI bri dge devi ces are suppor ted by t he i960 R M/RN

I/O processor on its second ary PCI interface and can be designed into add-on PCI cards. In

addition, the i960 RM/RN I/O processor supports “private” PCI devices on its secondary bus.

Private device s are hidden from in itialization code on the host system, and are configure d and

accessed dire ctly by the i960 RM/RN I/O processor. These devices are not part of the normal PCI

address space, but they can act as PCI bus mast ers and transfer dat a to and from other PCI devi ce s

in the system.

Unless designated as private devices, PCI devices installed on the se condary PCI interface of the

IQ80960RM/RN platform are mapped into the system-wide PCI address space by configuration

software running on the host system. No logical distinction is made at the system level between

devices on the prim ary PCI bus and devices on secondary buses; all transaction forwarding is

handled transparently by the PCI-to-PCI bridge. Configuration cycles and read and write accesses

from the host are forwarded through the PCI-to-PCI bridge un it of the i960 RM/RN I/O processor.

Master read and write cycles from devices on the secondary PCI bus are also forwarded to the h ost

bus by the PCI-to-PCI bridge unit.

IxWORKS allows secondary PCI devices to be configured as Public or Private. Public devices are

configured by the PCI host. Private devices are configured by the IxWORKS kerne l and the

device-speci fic HDM.

IQ80960RM/RN Evaluation Board Ma nual 4-5

Page 36

i960® RM/RN I/O Processor Overview

4.6 DMA Channels

The i960 RM/RN I/O processor features three independent DMA channels, two of which operate

on the primary PCI interface, whereas the remaining one operates on the secondary PCI interface.

All three of the DMA channel s c onnect to the i960 RM/RN I/O proc es s or’s local bus and can be

used to transfe r data from PCI devices to memory on the IQ80960RM/RN platform. Support for

chaining, and scatter/gather is built into all three channels. The DMA can address the entire 2

bytes of address sp ace on the PCI bus and 2

®

Figure 4-4. i960

RM/RN I/O Processor DMA Controller

Primary PCI Bus

32

bytes of address space on the internal bus.

DMA Channel 0

64

DMA Channel 1

PCI to PCI Bridge

DMA Channel 2

Secondary PCI Bus

4.7 Application Accelerator Unit

The Application Accelerat or provides low-latency , high-throughput data transfer cap ability

between the AA unit and 80960 local memory. It executes data transf ers to and from 80960 local

memory and a lso provides the nec essary programming interface. The Application Ac celerator

performs the following functions:

• Transfers data (read) from memory c ontroller

• Performs an optiona l boolean operati on (XOR) on rea d data

• Tr ansfers data (write) to memory controller

The AA uni t fe at u r es:

• 128-byte, a rranged as 8-byte x 16-deep store queue

• Utilizati on of the 80960RN/RM proces sor memory controll er interface

32

• 2

addressing range on the 80960 local memory interface

80960

Local Bus

• Hardware support for unaligned data transfers for the internal bus

• Full progra mmability from the i960 core processor

• Support for automatic data chaining for gathering and scattering of data blocks

4-6 I Q80960RM/RN Evaluation Board Manu al

Page 37

Figure 4-5 shows a simplif ied connection of the Application Accelerator to the i960 RM/RN I/O

Processor Internal Bus.

Figure 4-5. Application Accelerator Unit

Application Accelerator Unit

Data Queue

Boolea n U ni t

i960® RM/RN I/O Processor Overview

Packing/

Unpacking

Unit

4.8 Performance Monitor Unit

The Performance Monitoring features aid in measuring and monito ring various system parameters

that contribute to the overall performance of the processor. The monitoring facility is generic ally

referred to as PMON – Performance Moni toring. The facility is model specific, not architectural;

its inte n d ed use is to gath er p erformance measurements that can b e u sed to retune/refine code for

better system level performance.

The PMON facility provided on the i960 RM/RN I/O processor co mprises:

• One dedicated global Time Stamp counter, and

• Fourteen (14) Programmab le Event counters

The global time sta mp c ounter is a dedicated, free running 32-bit counter.

The progr a m m ab le event coun t er s are 3 2- b i ts w i de . Ea ch co un t er can be progr am m e d to obs e r v e

an event from a defined set of events. An event consists of a set of parameters which define a start

condition and a stop condit ion. The monitored events are selec ted by programming an event select

register (ESR).

80960

Bus Interface

64-bit

Internal Bus

IQ80960RM/RN Evaluation Board Ma nual 4-7

Page 38

Page 39

MON960 Support for IQ80960RM/RN

5

This chapter discusses a number of additions that have been made to MON960 to support the

IQ80960RM/RN in an optional non-I

MON960, see the MON960 Debug Monitor User’s Guide. The IQ80960RM/RN evaluation

platform ships with IxWorks* from Wind River Systems installed in flash firmware. To use

CTOOLS and MON960 instead of IxWorks, you need to download MON960 into the onboard

Flash. See Chapter 2 for more information on updating the onboard Flash. See Chapter1 for

descriptions of both IxWorks and CTOOLS.

2

O capacity. For complete documentation on the operation of

5.1 Secondary PCI Bus Expansion Connectors

The IQ80960RM/RN pl atform con tains four secon dary PCI bus expan sion c onnect ors to g ive us ers

access to the secondary PCI bus of the i960

perform secondary PCI bus ini tialization including the establishment of a secondary PCI bus

address map. Routines compatible with the PCI Local Bus Specification Revision 2.1 allow the

software on the IQ80960RM/RN platform to search for devices on the secondary PCI bus and read

and write the configuration space of those devices.

®

RM/RN I/O proce ssor. Extensions to MON960

5.2 MON960 Components

The remaining sect ions of this chapter assume that MON960 is installed in the onboard Flash,

replacing IxWorks. The IQ80960RM/RN optional MON960 debug monitor consists of four main

components:

• Initialization firmware • MON960 extensions

• MON 9 60 kernel • Diagnostics/example code

These four components togeth er are refe rred to as MON960.

5.2.1 MON960 Initia lizat ion

At initialization, MON960 puts the IQ80960RM/RN platform into a known, func tional state that

allows the host processor to perform PCI initialization. Once in this state, the MON960 kernel and

the MON960 extensions can load and execute correctl y. Initialization is performed after a RESET

condition. MON960 initialization encompasses all m ajor portions of the i960 RM/RN I/O

processor and IQ8 0960RM/RN pl at form includi ng 80 960JT core ini tial izati on, Memory C ontr oll er

initial ization, SDRAM initialization, Primary PCI Address Translation Unit (ATU) initialization,

and PCI-to-PC I Br idge Unit initialization.

The IQ80960RM/RN pl atform is desig ned to use th e Conf igur ation Mode of the i96 0 RM/RN I/O

processor. Conf igu ration Mode all ows th e 8 0960 JT core to in itia li ze an d cont rol the i nit iali za tion p roc ess

before the PCI host conf igur es t he i 960 RM/ RN I/O proc essor. By u ti lizi ng Confi gura tion Mode , t he user

IQ80960RM/RN Evaluation Board Ma nual 5-1

Page 40

MON960 Support for IQ80960RM/RN

is give n the ability to initialize the P CI configuration re gisters to values other than the default power-up

values. Confi gura tion Mode giv es the use r maximu m flexi bilit y to cu stomiz e the way in which the i960

RM/RN I/O process or and IQ80960 RM/RN plat form appea r to th e PCI host confi gurati on soft ware.

5.2.2 80960JT Core Initialization

The 80960JT core begins the initialization process by reading its Initial Memory Image (IMI) from

a fixed address in the boot ROM (FEFF FF30H in the i960 address space). The IMI include s the

Initialization Boot Record (IBR), the Process Control Block (P RCB), and seve r al system data

structures. The I BR provides initial configuration information for the core and integrated

peripheral s, pointers to the system data structures and the first instruction to be executed after

processor initialization, and checksum words that the processor uses in its self-test routine. In

addition to the IBR and PRCB, the required data str uctures are the:

• System Procedure Table

• Control Table

• Interrupt Table

• Fault Table

• User Stack (application dependent)

• Supervisor Stack

• Interrupt Stack

5.2.3 Memory Controller Initialization

Since the i960 RM/RN I/O processor Memory Cont roller is integral to the design and opera tion of

the IQ80960RM/RN platform, the operat ional parameters for Bank 0 and Bank 1 are established

immediately after processor core initialization. Memory Bank 0 is associated with the ROM on the

IQ80960RM/RN pla tform. Memory Bank 1 is associated with the UART and the LED Control

Register. Parameters such as Bank Base Address, Read Wait States, and Write W ait States must be

established to ensure the prope r operation of the IQ80960RM/RN platform. The Memory