Page 1

Intel® Core

2 Duo P r oc e ssor and

®

TM

Intel

Q35 Express Chipset

Development Kit

User’s Manual

October 2007

Order Number: 3184 76-001US

Page 2

Lega l Li nes and Discl a imers

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR

OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS

OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHAT SOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELA T ING

TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE,

MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for

use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the

present e d subject m att er. The f urnishing o f do cu m ents a nd ot h er mat e ri als a nd i nfo rm ati on do es n ot provide any license, expre ss o r impl ied, by es topp el

or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different

processor families. See http://www.intel.com/products/processor_number for details.

The Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit may contain design defects or errors known as errata which may

cause the product to deviate from published specifications. Current characterized errata are available on request.

Hyper-Threading Technology requires a computer system with an Intel® Pentium® 4 processor supporting HT Technology and a HTTechnology enabled

chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See http://www.intel.com/

products/ht/Hyperthreading_more.htm for additional information.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740,

IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel NetMerge, Inte l

NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel vPro, Intel XScale, IPLink, Itanium, Itanium Inside, MCS, MMX,

Oplus, OverDrive, PDCharm, Pentium, Pentium Inside, skoool , Sou nd Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks or

registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

*Other na m es and bra nds may be claimed as the pro perty of others.

Copyright © 2007, Intel Corporation. All Rights Reserved.

Intel® CoreTM 2 Duo Proc es sor and Intel ® Q35 Express Chipset Development Kit

User’s Manual Octob er 2007

2 Order Number: 318476-001US

Page 3

Contents—Intel Core 2 Duo Processor and Intel Q35 Express Chipset

Contents

1.0 About This Manual .....................................................................................................6

1.1 Content Overview................................................................................................6

1.2 Text Conventions ........................ ........................................................................6

1.3 Glossary of Terms and Acronyms...........................................................................7

1.4 Support Options..................................................................................................8

1.4.1 Electronic Support Systems .......................................................................8

1.4.2 Additional Technical Support......................................................................8

1.5 Product Literature ............................................................................................... 8

2.0 Development Kit Hardware Features .......................................................................10

2.1 Intel® Q35 Express Chipset Development Kit Overview..........................................10

2.2 System Block Diagram.......................................................................................11

2.3 Development Kit Inventory Checklists..................................................................12

2.4 Processor Support.............................................................................................14

2.5 System Memory............... .................................................................................14

2.5.1 Dual Channel (Interleaved) Mode Configurations ........................................15

2.5.2 Single Channel (Asymmetric) Mode Configurations................................. ..... 17

2.6 Back-Panel Connectors.......................................................................................18

2.6.1 Audio-Connectors...................................................................................18

2.6.2 RJ-45 LAN Connector with Integrated LEDs ................................................19

2.6.3 USB Port...............................................................................................19

2.6.4 Coaxial S/PDIF In/Out Connector..............................................................19

2.6.5 eSATA Port................................................................. ...........................19

2.7 Debug Features.................................................................................................20

2.7.1 Extended Debug Probe (XDP)...................................................................20

2.7.2 Power LEDs .......................... .................................................................20

2.7.3 Port 80 POST Code LEDs .........................................................................20

2.7.4 Voltage Referen ce..................................................................................21

2.8 Development Kit Major Connectors and Jumpers....................................................21

2.8.1 Jumper Functions...................................................................................22

2.8.2 U SB 2.0 Front Panel ...............................................................................22

2.8.3 1394a Header........................................................................................22

2.9 SPI Removal / Installation Technique...................................................................23

2.9.1 SPI Device Removal................................................................................24

2.9.2 SPI Device Installation............................................................................24

3.0 Setting Up and Configuring the Development Kit .....................................................26

3.1 Overview .........................................................................................................26

3.2 Installing Board Standoffs ..................................................................................26

3.3 BTX Heatsink Setup with SRM.............................................................................28

3.3.1 SRM Alignment on any BT X Board ............................................................28

3.4 Board Setup and Configuration before Boot...........................................................30

3.5 Post Codes Definitions........................................................................................32

3.5.1 Normal Post Codes.................................................................................32

Figures

1 Board Features........................................................................................................11

2 Intel® Q35 Express Chipset Development Kit block diagram..........................................12

3 Memory Channel and DIMM Configuration ...................................................................15

4 Dual Channel (Interleaved) Mode Configuration with 2x DIMMs ......................................16

5 Dual Channel (Interleaved) Mode Configuration with 3x DIMMs ......................................16

Octobe r 20 07 User’s Manual

Order Nu mber: 318476 - 00 1U S 3

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit

Page 4

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—Contents

6 Dual Channel (Interleaved) Mode Configuration with 4x DIMMs.......................................17

7 Single Channel (Asymmetric) Mode Configuration with 1x DIMM.....................................17

8 Single Channel (Asymmetric) Mode Configuration with 3x DIMMs....................................18

9 Back-panel Connectors..............................................................................................18

10 LAN Connector LED locations......................................................................................19

11 ITP-XDP Connector location (J2BC)...................... .......................................................20

12 Major Jumper and Header Locations ............................................................................21

13 Location for 1394a Header and USB Front Panel ...........................................................23

14 SPI Socket with Retaining Clip....................................................................................24

15 SPI Device Installation..............................................................................................25

16 Intel® Q35 Development Kits ....................................................................................26

17 Mounting Hole Locations............................................................................................27

18 Mounting the Standoff for BTX Heatsink.......................................................................28

19 Casing with “Support and Retention Module”................................................................28

20 BTX board alignment on SRM.....................................................................................29

21 Heatsink Alignment...................................................................................................29

22 Tightening Heatsink on the SRM and Board..................................................................30

23 CPU Fan location ............ ..........................................................................................31

24 2x12 Standard power supply and 2x2 power supply......................................................32

Tables

1 Definition ................................................................................................................. 7

2 Intel Literature Centers.............................................................................................. 9

3 Development Kit Hardware Items ...............................................................................12

4 Development Kit Board Specification...........................................................................13

5 Internal I/O headers.................................................................................................13

6 Supported Intel Technologies.....................................................................................13

7 Additional F eatures...................................................................................................14

8 LAN Connector LED status .........................................................................................19

9 Voltage Reference detail............................................................................................21

10 Intel

11 USB Front Panel.......................................................................................................22

12 1394a Header..........................................................................................................23

®

CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit Board

Jumpers Description .................................................................................................22

®

CoreTM 2 Duo Proc es sor and Intel ® Q35 Express Chipset Development Kit

Intel

User’s Manual Octob er 2007

4 Order Number: 318476-001US

Page 5

Revision History—Intel Core 2 Duo Processor and Intel Q35 Express Chipset

Revision History

Date Revision Description

October 2007 001 Initi al release

Octobe r 20 07 User’s Manual

Order Nu mber: 318476 - 00 1U S 5

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit

Page 6

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—About This Manual

1.0 About This Manual

This user’s manual describes the use of the Intel

Kit. This manual has been written for OEMs, system evaluators, and embedded system

developers. All jumpers, headers, LED functions, and their locations on the board,

along with subsystem features and POST codes, are defined in this document.

For the latest information about the Intel

reference platform, visit:

http://developer.intel.com/design/intarc h/d evkits/

index.htm?iid=embed_body+devkits

For design documents related to this platform, such as schematics and layout, please

contact your Intel Representative.

1.1 Content Overview

Chapter 1.0, “About This Manual”

This chapter contains a description of conventions used in this manual. The last few

sections explain how to obtain literature and contact customer support.

Chapter 2.0, “Development Kit Hardware Features”

This chapter provides information on the development kit features and the board

capability. This includes the information on board component features, jumper settings,

pin-out information for connectors and overall development kit board capability.

Chapter 3.0, “Setting Up and Configuring the Development Kit”

®

Q35 Expr ess Chi ps et Developm en t

®

Q35 Express Chip se t De ve lop m en t Kit

This chapter provides instructions on how to configure the evaluation board and

processor assembly by setting BTX heatsink, jumpers, connecting peripherals,

providing power, and configuring the BIOS.

1.2 Text Conventions

The following notations may be used throughout this manual.

# The pound symbol (#) appended to a signal name indicates that

the signal is active low.

Variables Variables are shown in italics. Variables must be replaced with

Instructions Instruction mnemonics are shown in uppercase. When you are

Numbers Hexadecimal numbers are represented by a string of

®

CoreTM 2 Duo Proc es sor and Intel ® Q35 Express Chipset Development Kit

Intel

User’s Manual Octob er 2007

6 Order Nu mber: 318476 001US

correct values.

progr amming , i ns truc ti ons are no t ca se- sen si tiv e . You may use

either upper-case or lower-case.

hexa de c im al di g it s fo l lo we d b y th e ch aracter H. A zero prefix is

added to n umbers that beg in wit h A through F. (For example, FF

Page 7

About This Manual—Intel Core 2 Duo Processor and Intel Q35 Express Chipset

is shown as 0FFH.) Decimal and binary numbers are

represented by their customary notations (That is, 255 is a

decimal number and 1111 1111 is a binary number). In some

cases, the letter B is add ed for cla rit y.

Units of Measure The following abbreviations are used to represent units of

measure:

GByte gigabytes

KByte kilobytes

MByte megabytes

MHz megahertz

W watts

V volts

Signal Names Signal names are shown in uppercase. When several signals

share a common name, an individual signal is represented by

the signal name followed by a number, while the group is

represented by the signal name followed by a variable (n). For

example, the lower chip-select signals are named CS0#, CS1#,

CS2#, and so on; they are collectively called CSn#. A pound

symbol (#) appended to a signal name identifies an active-low

signal. Port pins are represented by the port abbreviation, a

period, and the pin number (e.g., P1.0).

1.3 Glossary of Terms and Acronyms

This section defines conventions and terminology used throughout this document.

Table 1. Definition (Sheet 1 of 2)

Term Description

nd

Advanced Digita l Disp lay Card – 2

for an Intel Graphics Controller that supports ADD2+ cards. It plugs into a x16 PCI

ADD2 Card

ACPI Advanced Configuration and Power Interface

Core The internal base logic in the (G)MCH

DDR2 A second generation Double Data Rate SDRAM memory technology

DMI (G)MCH-Intel

DVI

FSB Front Side Bus. FSB is synonymous with Host or processor bus

GMA 3100 Intel® Graphic Media Accelerator 3100

Æ

Intel

ICH9

IGD Int er na l Gra phic s Dev ice.

LVDS

Express* connector but uses the multiplexed SDVO interface. The card adds Video In

capabilities to platform. This Advanced Digital Display Card will not work with an Intel

Graphics Controller that supports DVO and ADD cards. It will function as an ADD2 card in

an ADD2 supported system, but video in capabilities will not work.

Æ

ICH9 Direct Media Interface

Digital Video Interface. Specification that defines the connector and interface for digital

displays.

Eighth generation I/O Controller Hub component that contains additional functionality

compared to previous ICHs. The I/O Controller Hub component contains the primary PCI

interface, LPC interface, USB2, ATA-100, and other I/O functions. It communicates with

the (G)MCH over a propri etary interconnect called DMI.

Low Voltage Differential Signaling. A high speed, low power data transmission standard

used for display connections to LCD panels.

Generation. This card provides digital display options

Octobe r 20 07 User’s Manual

Order Nu mber: 318476 001US 7

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit

Page 8

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—About This Manual

Table 1. Definition (Sheet 2 of 2)

Term Description

Advanced Digital Display Card – 2

for an Intel Graphics Controller that supports ADD2+ cards. It plugs into a x16 PCI

ADD2 Card

MCH

MEC Media Expansio n Card, also known as ADD2+ card. Refer to ADD2+ te rm for description.

PCI Express*

Primary PCI

SDVO

SDVO Device

SMI

Rank

Express* connector but uses the multiplexed SDVO interface. The card adds Video In

capabilities to platform. This Advanced Digital Display Card will not work with an Intel

Graphics Controller that supports DVO and ADD cards. It will function as an ADD2 card in

an ADD2 supported system, but video in capabilities will not work.

Memory Controller Hub c o mponen t that contains t he processor interface, DRAM

controller, and x16 PCI Express* port (typically, the external graphics interface). It

communicates with the I/O controller hub (Intel ICH9) and other I/O controller hubs over

the DMI interconnect. In this document MCH refers to the Intel® Q35 MCH component.

Third Generation input/output graphics attach called PCI Express* Graphics. PCI Express*

is a high-speed serial interface whose configuration is software compatible with the

existing PCI specifications. The specific PCI Express* implementation intended for

connecting the (G)MCH to an external Graphics Controller is a x16 link and replaces AGP.

The Primary PCI is the physical PCI bus that is driven directly by the ICH9 component.

Communication between Primary PCI and the (G)MCH occurs over DMI. Note that the

Primary PCI bus is not PCI Bus 0 from a configuration standpoint.

Serial Digital Video Out (SDVO). SDVO is a digital display channel that serially transmits

digital display data to an external SDVO device. The SDVO device accepts this serialized

format and then translates the data into the appropriate display format (i.e., TMDS,

LVDS, TV-Out). This interface is not electrically compatible with the previous digital

display channel - DVO. For the 82Q965 GMCH, it will be multiplexed on a portion of the

x16 graphics PCI Express* interface.

Third party codec that us es SDVO as an input. May have a variety o f output format s,

includi ng DVI, LVDS, HDMI, TV-out, etc.

System Management Interrupt. SMI is used to indicate any of several system conditions

(such as, thermal sensor events, throttling activated, access to System Management

RAM, chassis open, or other system state related activity).

A unit of DRAM corresponding to eight x8 SDRAM devices in parallel or four x16 SDRAM

devices in parallel, ignoring ECC. These devices are usually, but not always, mounted on a

single side of a DIMM.

nd

Generati on. T his c ard provi des d igi tal displ ay op ti ons

1.4 Support Options

1.4.1 Electron ic Su p p or t Sy s t ems

Intel’s site on the World Wide Web (http://www.intel.com/) provides up-to-date

technical information and product support. This information is available 24 hours per

day, 7 days per week, providing technical information whenever you need it.

Product documentation is provided online in a variety of web-friendly formats at:

(http://developer.intel.com/

)

1.4.2 A dditional Technical Support

If you require additional technical support, please contact your field sales

representative or local distributor.

1.5 Product Literature

Product literature can be ordered from the following Intel literature centers:

®

CoreTM 2 Duo Proc es sor and Intel ® Q35 Express Chipset Development Kit

Intel

User’s Manual Octob er 2007

8 Order Nu mber: 318476 001US

Page 9

About This Manual—Intel Core 2 Duo Processor and Intel Q35 Express Chipset

Table 2. Intel Literature Centers

Location Telephone Number

U.S. and Canada 1-800-548-4725

U.S. (from overseas) 708-296-9333

Europe (U.K.) 44(0)1793-431155

Germany 44(0)1793-421333

France 44(0)1793-421777

Japan (fax only) 81(0)120-47-88-32

Octobe r 20 07 User’s Manual

Order Nu mber: 318476 001US 9

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit

Page 10

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—Development Kit Hardware Features

2.0 Development Kit Hardware Features

This chapte r describes the features of the Intel® Q35 Development Kit. These

recommendations would largely apply to other designs incorporating Intel® Q35

chipset. This documentation should be used in conjunction with the datasheets,

specification updates and platform design guides for the Intel® I/O Controller Hub 9

(ICH9) Family and the Intel® Q35 Express Chipset. Contact your Intel representative

for the availability of these documents.

2.1 Intel® Q35 Express Chipset Development Kit Overview

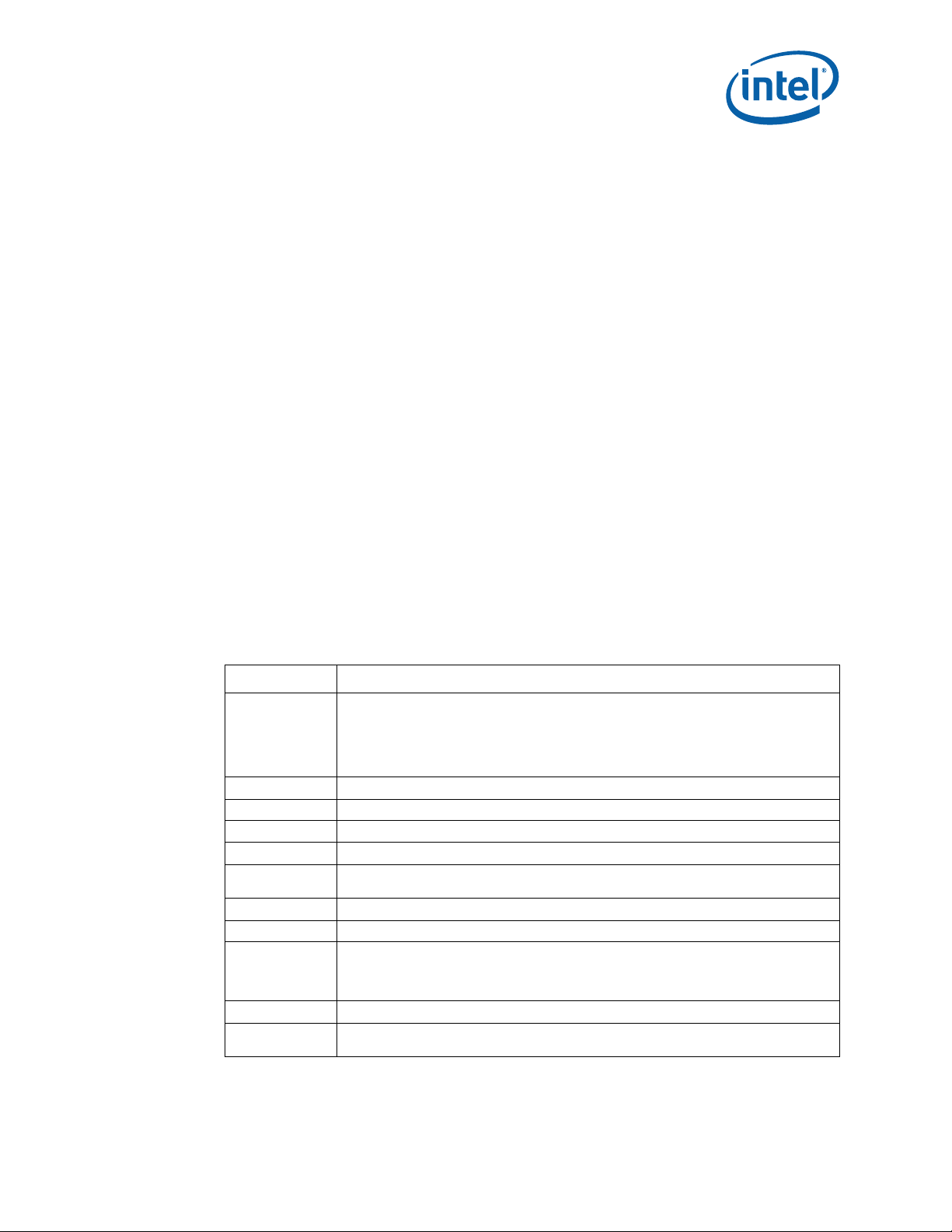

Figure 1 shows overview of the major features present on the development kit board.

Refer to next page for system block diagram of the development kit’s motherboard.

®

CoreTM 2 Duo Proc es sor and Intel ® Q35 Express Chipset Development Kit

Intel

User’s Manual Octob er 2007

10 Order Nu mber: 318476 001US

Page 11

Development Kit Hardware Features—Intel Core 2 Duo Processor and Intel Q35 Express Chipset

Figure 1. Board Features

PCI Slot

PCI Express

x1 Slot

SPI EEPROM

(Secondary)

SPI EEPROM

(Primary)

PCI Express

x16 Graphics

Slot

Intel® I/O

Controll er Hu b

(ICH)

SATA Port

2x12

Standard

Power Supply

Res e t b u tto n

Power Button

Port 80 LED Display

LGA775 Processor

Socket

Intel® Q35 Memory

Controll er Hub (MCH)

2x2 Standard

Power Supply

2-DIMM p er c hanne l DD R2

667/800 (Channel-B)

2-DIMM p er c hanne l DD R2

667/800 (Channel-A)

2.2 System Block Diagram

This section will document the common features that are applicable to the Intel®

TM

Core

shows a simple block diagram of the development kit.

Octobe r 20 07 User’s Manual

Order Nu mber: 318476 001US 11

2 Duo Processor and Intel ® Q35 Expre s s Chip se t De velo pment Kit. Figure 2

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit

Page 12

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—Development Kit Hardware Features

Figure 2. Intel® Q35 Express Chipset Deve lopm e n t Kit blo ck di agram

2.3 Development Kit Inventory Checklists

This section describes major hardware items which should be available on this

development kit.

Table 3. Development Kit Hardware Items

1x 4-Layer Micro-BTX form factor (targeted dimensions: 10.5” x 10.4”) motherboard

1x Intel ® CoreTM 2 Duo E6400 Processors in the LGA775 Socke t

2x 1 GByt es DDR2 800 DIMM

1x BTX Heatsink with fan

1x CD-ROM contain chipset drivers (this include Intel® GMA3100 driver)

8x hex standoffs and 4x screws for bench top usage

®

CoreTM 2 Duo Proc es sor and Intel ® Q35 Express Chipset Development Kit

Intel

User’s Manual Octob er 2007

12 Order Nu mber: 318476 001US

Page 13

Development Kit Hardware Features—Intel Core 2 Duo Processor and Intel Q35 Express Chipset

Table 4. Development Kit Board Specification

1 PCI Express x16, 2 PCIe x1, 1 PCI expansion slots

1394a

• 1 front panel headers for support of 1 port

• 1 back panel port

Universal Serial Bus 2.0

• 2 front panel headers for support of 4 ports

• 1 internal header for support o f 2 ports

• 6 back panel ports

6 SATA 3 Gb/sec ports (1 port used for eSATA)

Table 5. Inte rnal I/O he aders

2x5 Front Panel I/O header

2x7 Front Panel audio header

1x2 Chassis intrusion header

3 four-wire fan headers

2x8 High Definition audio header

Table 6. Supported Intel Technologies (Sheet 1 of 2)

Technology Features/support Reference Documentation

• Enables remote, down-the-wire management

of out-of-band networked systems regardless

of system state, helping improve efficiency,

Intel® Acti ve Management

Te chnology with System

Defense feature (Intel®

ICH8 DO only)

Intel® Graphics Media

Accelerator 3000

asset management and system security and

availability.

• System Defense Feature can help block

incoming software attacks, isolate a device

from the network if infected, and proactively

alert embedded system vendors if critical

software agents are missing.

• Dual independent display expands viewable

workspace for devices such as point-of-sale

terminals wit h two monitors.

• Provides next-generation graphics

performance for advanced embedded

operating systems.

• Delivers richer visual color and picture clarity

without the need for additional discrete

graphics cards.

http://www.intel.com/technology/

platform-technology/intel-amt/

http://www.intel.com/products/chipsets/

gma3000/demo/demo.html

Octobe r 20 07 User’s Manual

Order Nu mber: 318476 001US 13

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit

Page 14

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—Development Kit Hardware Features

Table 6. Suppor ted In te l Techno logies (S h eet 2 of 2)

Technology Features/supp or t Ref ere nce Docum enta tio n

• Helps improve system performa nce by

optimizing use of available memory

bandwidth and reducing latency of memory

Intel® Fast Memory Access

Intel® Matrix Storage

Technology (Intel® ICH8

DO only)

Intel® High Definition Audio

access by monitoring all pending read/write

requests; allows safe and efficient

overlapping of commands on all system bus

interfaces.

• With a second hard drive added, provides

quicker access to digital photo, video and

data files with RAID 0, 5 and 10, and greater

data protection against a hard disk drive

failure with RAID 1, 5 and 10.

• Enables premium digital sound and delivers

advanced features such as multiple audio

streams and jack re-tasking.

• Support for microphone array enables

enhanced voice capture for high-quality input

to voice-driven activities.

Table 7. Additional Features

6 Analog audio connectors and 2 digital audio connectors

Piezo speaker for BIOS POST codes

BIOS configuration jumper

Clear CMOS jumper

Power But to n

Reset Button

XDP connector

http://www.intel.com/products/chipsets/

q965_q963/demo/demo.html

http://www.intel.com/design/chipsets/

matrixstorage_sb.htm

http://www.intel.com/design/chipsets/

hdaudio.htm

2.4 Processor Support

The Intel® Q35 Development Kit supports the following processors in the LGA775

Socket with FSB of 800/1067/1333 MHz.

These processors, with long-life support are also supported by this development kit:

•Intel

•Intel

•Intel

•Intel

®

CoreTM 2 Duo E6400 (Included in the development kit)

®

CoreTM 2 Duo E4 30 0

®

Pen tiu m® Dual-Core Processor E2160

®

Celeron® 440

Refer to this link for other processors which is also supported by Intel® Q35 Express

Chipset.

http://developer.intel.com/products/chipsets/Q35_Q3 3/index.htm

2.5 System Memory

The Intel® Q35 Exp ress Chipse t support s two types of memor y organiz ation. The se are

interleaved mode and asymmetric mode. The Q35 supports:

Listed here are the summary of the system memory supported.

®

CoreTM 2 Duo Proc es sor and Intel ® Q35 Express Chipset Development Kit

Intel

User’s Manual Octob er 2007

14 Order Nu mber: 318476 001US

Page 15

Development Kit Hardware Features—Intel Core 2 Duo Processor and Intel Q35 Express Chipset

• Non-ECC DDR2 (667/800)

• 512M b, 1G b an d 2G b techn o lo g y

• 4 DIMMs, 4GB maximum per channel, 8GB total memory

• Dual chan ne l ( Inte r l eav e d) mod e . This mode offers the highest throughput for real

world applications. Dual channel mode is enabled when the installed memory

capacities of both DIMM channels are equal. Technology and device width can vary

from one channel to the other but the installed memory capacity for each channel

must be equal. If different speed DIMMs is used between channels, the slowest

memory timing will be used.

• Single channel (Asymmetric) mode. This mode is equivalent to single channel

bandwidth operation for real world applications. This mode is used when only a

single DIMM is installed or the memory capacities are unequal. Technology and

device width can vary from one channel to the other. If different speed DIMMs is

used between channels, the slowest memory timing will be used.

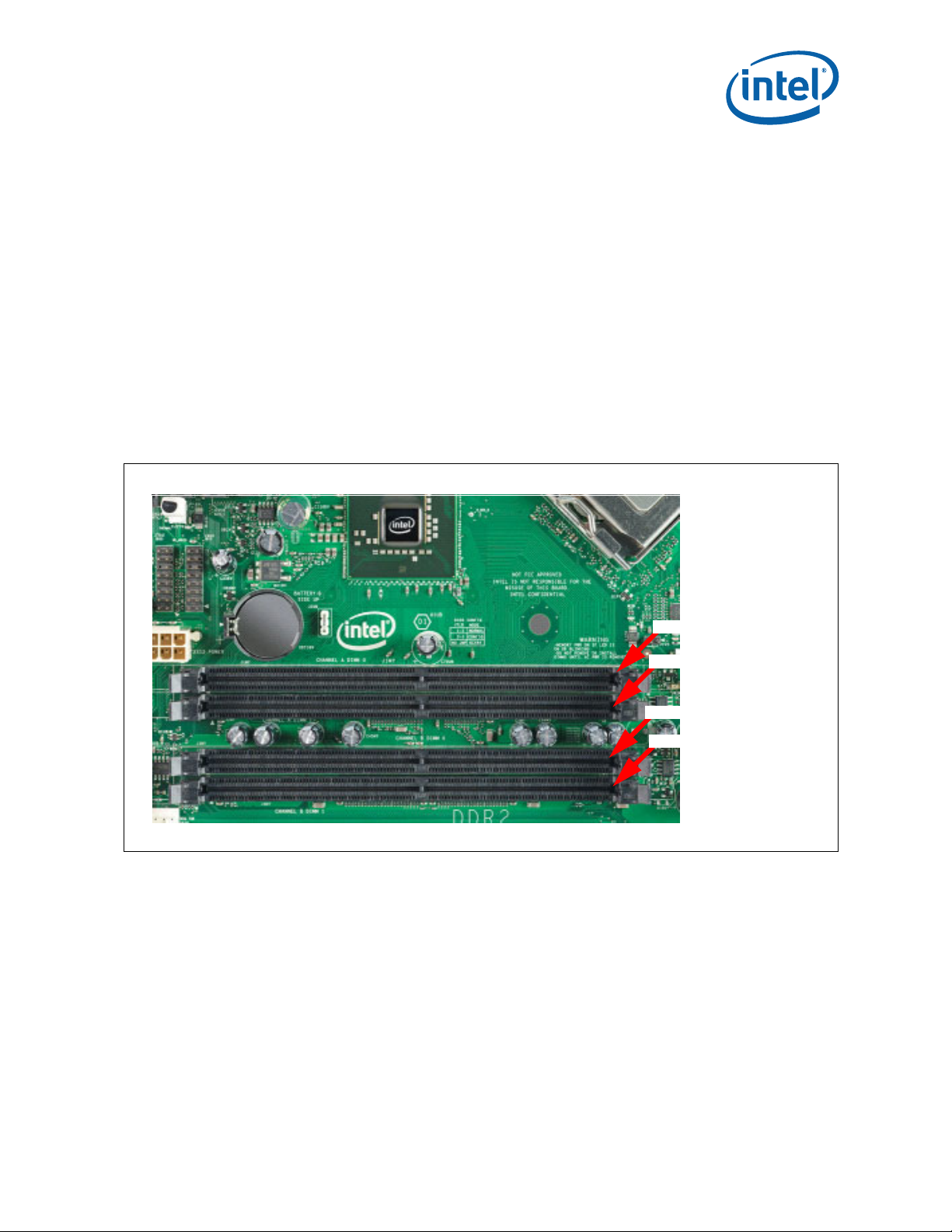

Figure 3 illustrates the memory channel and DIMM configuration.

Figure 3. Memory Channel and DIMM Configuration

Channel A DIMM 0

Channel A DIMM 1

Channel B DIMM 0

Channel B DIMM 1

2.5.1 Dual Channel (Interleaved ) Mo d e C onfigura tions

Figure 4 shows a dual channel configuration using two DIMMs. In this example, the

DIMM 0 sockets of both channels are populated with identical DIMMs.

Octobe r 20 07 User’s Manual

Order Nu mber: 318476 001US 15

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit

Page 16

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—Development Kit Hardware Features

Figure 4. Dual Channel (Interleaved) Mode Configuration with 2x DIMMs

Figure 5 shows a dual channel configuration using 3 DIMMs. In this example, the

combined capacity of the two DIMMs in Channel A equal the capacity of the single

DIMM in the DIMM 0 socket of Channel B.

Figure 5. Dual Channel (Interleaved) Mode Configuration with 3x DIMMs

Figure 6 shows a dual channel configuration using 4 DIMMs. In this example, the

combined capacity of the 2x DIMMs in Channel A equals the combined capacity of the

2x DIMMs in Channel B. Also, the DIMMs are matched between DIMM 0 and DIMM 1 of

both channels.

®

CoreTM 2 Duo Proc es sor and Intel ® Q35 Express Chipset Development Kit

Intel

User’s Manual Octob er 2007

16 Order Nu mber: 318476 001US

Page 17

Development Kit Hardware Features—Intel Core 2 Duo Processor and Intel Q35 Express Chipset

Figure 6. Dual Channel (Interleaved) Mode Configuration with 4x DIMMs

2.5.2 Single Channel (Asymmetric) Mode Configuratio ns

Figure 7 shows a single channel configuration using 1x DIMM. In this example, only the

DIMM 0 socket of Channel A is populated. Channel B is not populated.

Figure 7. Single Channel (Asymmetric) Mode Configuration with 1x DIMM

Figure 8 shows a single channel configuration using 3x DIMMs. In this example, the

combined capacity of the 2x DIMMs in Channel A does not equal the capacity of the

single DI M M in th e DIMM 0 socket of C ha nnel B.

Octobe r 20 07 User’s Manual

Order Nu mber: 318476 001US 17

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit

Page 18

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—Development Kit Hardware Features

Figure 8. Single Channel (Asymmetric) Mode Configuration with 3x DIMMs

2.6 Back-Panel Connectors

Figure 9 shows back-panel connectors for the development kit.

Figure 9. Back-panel Connectors

1394a Port

USB Port

(Total 6

Ports)

eSATA Port

2.6.1 Audio-Connectors

This development kit board supports up to 7.1-channel audio configuration. It is

backward compatible with 5.1, 2.1 and stereo (2-channel) audio configuration as well.

Line In Jack (Light Blue)

This audio jack is used to for line in devices, including some optical devices.

Line Out Jack (Light Green)

RJ-45 LAN Port

VGA Analog

Display

Speaker

Speaker

S/PDIF IN

S/PDIF OUT

Side

Out

Rear

Out

Center/

Sub

Woofer

Speaker

Out Jack

Line-in Jack

Line-out

Mic In Jack

Jack

This audio jack i s used for line out devices. It’s used in 2.1, 5.1 and 7.1 channel- audio

configuration. It can be used for headphone and stereo speaker as well.

Mic In Jack (Pink)

This audio jack is use for microphone input.

®

CoreTM 2 Duo Proc es sor and Intel ® Q35 Express Chipset Development Kit

Intel

User’s Manual Octob er 2007

18 Order Nu mber: 318476 001US

Page 19

Development Kit Hardware Features—Intel Core 2 Duo Processor and Intel Q35 Express Chipset

Center/Subwoofer Speaker Out Jack (Orange)

This audio jack is used to connect to center/subwoofer speakers in a 5.1 and 7.1channel audio configuration.

Rear Speaker Out (Black)

This audio jack is used to connect to rear speakers in a 5.1 and 7.1-channel audio

configuration.

Side Speaker Out (Gray)

This audio jack is used to connect to side speakers for 7.1-channel audio configuration

only.

2.6.2 RJ-45 LAN Connector with Integrated LEDs

Two LEDs are built into the RJ-45 LAN connector (as shown in Figure 10). Table 8

describes the LED states when the board is powered up and the Gigabit LAN subsystem

is operating.

Figure 10. LAN Connector LED locations

Table 8. LAN Conne c to r LE D sta t us

LED Color LED State Condition

Off LAN link is not established

Left Green

N/A Off 10 Mbits/sec data rate is selected

Right

Green On 100 Mbits/sec data rate is selected

Yellow On 1000 Mbits/sec data rate is selected

On LAN link is established

Blinking LAN activity is occurring

2.6.3 USB Port

The USB port supports the USB 1.1/2.0 specification.

2.6.4 Coaxi al S/PDIF In/Out Connec tor

This connector provides digital audio input and output from external audio system that

supports digital coaxial audio. Ensure that the audio system provides a coaxial digitalin/out connector.

2.6.5 eSATA Port

This d ev e l opment kits sup p o r t th e f ir st gene ra t io n eSATA port .

Octobe r 20 07 User’s Manual

Order Nu mber: 318476 001US 19

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit

Page 20

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—Development Kit Hardware Features

2.7 Debug Features

2.7.1 Extended Debug Probe (XDP)

The reference board provides a JTAG-compliant test access port (TAP) for attachment

of an XDP connector. The XDP connector and associated circuitry enable the use of the

ITP for the particular processor to interrupt the boot sequence and view processor

status.

The XDP connector is located on the backside of the board at location J2BC. Refer to

Figure 11 to the XDP connector location. Take notes that ITP-XDP SSA connector is

needed. Refer to diagram below for the ITP-XDP SSA connector.

Figure 11. ITP-XDP Connector location (J2BC)

ITP-XDP

Connector

ITP-XDP SSA Connector is

needed in ord er to

connect to ITP-XDP2/3

tools

2.7.2 Power LEDs

Power LEDs on the board indicate when standby power is being applied to the standby

planes. When li t they indic ate that no DIMM modul es should be inserted or removed. To

install or replace DIMM modules insure that AC power to the power supply is removed

by unplugging the AC power cord from the power supply or placing the switch on the

power supply to the open position.

Caution: Removing DIMM modules when the standby power LEDs is lit could result in damage to

the memory devices on those modules.

2.7.3 Port 80 PO ST Code LEDs

Two LEDs display the POST codes output from Port 80 to indicate the progress of the

boot sequence or display the POST code of the last operation successfully completed

during the boot sequence. Please refer to Section 3.4 for more information on Port 80

code reference.

®

CoreTM 2 Duo Proc es sor and Intel ® Q35 Express Chipset Development Kit

Intel

User’s Manual Octob er 2007

20 Order Nu mber: 318476 001US

Page 21

Development Kit Hardware Features—Intel Core 2 Duo Processor and Intel Q35 Express Chipset

2.7.4 Voltage Reference

See Table 9 for details of the expected voltage levels for each voltage rail on the CRB.

Table 9. Voltage Reference detail

Voltage Rail Expected Voltage Voltage Rail Expected Voltage

VCC 5.0 V_1P25_CORE 1.25

VCC3 3.3 V_1P25_CL_MCH 1.25

+12V 12 V_1P25_PCIEXPRESS 1.25

-12V -12 V_SM 1.8

V_5P0_STBY\G 5.0 V_SM_VTT 0.9

V_3P3_STBY\G 3.3 V_3P3_CL 3.3

V_1P5_ICH 1.5 V_3P3_PCIVAUX 3.3

V_1P05_ICH_CORE 1.05 VDD_CLK 3.3

V_FSB_VTT 1.2 VCC_CLK_IO 0.8

VCCP Varies

2.8 Development Kit Major Connectors and Jumpers

Figure 12 shows major jumpers and headers used on the development kit.

Figure 12. Major Jumper and Header Locations

J4LB/J10LB

J6LB

J115LB

J14LB

J15LB

J16LB

J7LB

Octobe r 20 07 User’s Manual

Order Nu mber: 318476 001US 21

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit

Page 22

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—Development Kit Hardware Features

2.8.1 Jumper F unctions

Table 10 provides a list of the setting definitions for the Intel® CoreTM 2 Duo Processor

and Intel

Table 10. Intel

®

Q35 Express Chipset Development Kit.

®

CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development

Kit Board Jumper s D e scr ip tion

Jumper Description Default Position

J6LB

J115LB

J7LB

J4LB/J10LB

Clear CMOS

(1-2: Normal, 2-3: Clear CMOS)

RTC Reset

(1-2: Normal, 2-3: Clear)

Confi g /Recovery

(1-2: Normal, 2-3: Configure, jumper removed –

recovery)

Manufa cturing mode

(enable if jumper plug-in)

2.8.2 USB 2.0 Fr ont Panel

There are 4 USB 2.0 Front Panel can be found in the development kits board. Front

panel USB header thermistor protection is required. USB front panel is label as U14LB,

U15LB, U16LB and U1FW on the boards. Refer to Figure 12 for header location of

U14LB, U15LB and U16LB. Refer to Figure 13 for U1FW.

1-2

1-2

1-2

Empty

Table 1 1. USB Front Panel

Pin Numbe r Definition

15V

25V

3USB Dx4USB Dy5USB Dx+

6USB Dy+

7GND

8GND

9No pin

10 No co nnect

2.8.3 1394a Header

The development kit board supports a 1394a solution on the PCIe bus with a single

1394a port on the back panel (see Figure 9) and another header supporting a 1394a

port (see Figure 13). Front panel 1394a header thermistor protection is required.

®

CoreTM 2 Duo Proc es sor and Intel ® Q35 Express Chipset Development Kit

Intel

User’s Manual Octob er 2007

22 Order Nu mber: 318476 001US

Page 23

Development Kit Hardware Features—Intel Core 2 Duo Processor and Intel Q35 Express Chipset

Figure 13. Location for 1394a Header and USB Front Panel

U1FW

(USB Front

Panel)

J24LB

1394a

Header

Table 12. 1394 a Hea der

Pin Number Definition

1 NDCD A2NSIN A

3NSOUT A

4NDTR A5GND

6NDSR A7 NRT S A8NCTS A9NRI A10 No Pin

2.9 SPI Removal / Installation Technique

When removing or installing the SPI device, care must be taken to avoid damage to the

SPI socket. The cap is constructed of plastic and can easily be damaged.

Octobe r 20 07 User’s Manual

Order Nu mber: 318476 001US 23

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit

Page 24

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—Development Kit Hardware Features

2.9.1 SPI Device Removal

T o remove the SPI device from the socket, use a tweezer tip to gently pry one leg of the

cap away from the socket. There is a small latch on the bottom of the leg of the cap.

Once the cap latch is dise ngaged , the cap may be remov ed witho ut ca using damage to

the latches on the ends.

With the SPI device exposed, move the small retaining clip to release the SPI device

from the socket (see Figure 14). The SPI device should now spring up to allow removal

from the socket.

Figure 14. SPI Socket with Retaining Clip

1. Fol low t he u nclenc h pro cess

to unclench the cover.

3. Remove the fresh IC from

the socket.

2.9.2 SPI Device Installation

To Install an SPI device in a socket, first place the side opposite from the retaining clip

into the socket at an angle of approximately 15 degrees. Continue to gently insert the

device into the socket until the metal retaining clip latches the device in place, as

shown in Figure 15. Carefully place the cap straight down over the device until both

ends latch into the socket. The installation is now complete.

2. Clamp the fresh IC at

location 1 and location 2 with

tweezers.

®

CoreTM 2 Duo Proc es sor and Intel ® Q35 Express Chipset Development Kit

Intel

User’s Manual Octob er 2007

24 Order Nu mber: 318476 001US

Page 25

Development Kit Hardware Features—Intel Core 2 Duo Processor and Intel Q35 Express Chipset

Figure 15. SPI Device Install a t ion

1. Place the fresh IC into the

socket. Match pin 1. on the IC

to pin 1 on the so cket .

3. Lock the co ver wit h

the hook.

2. Close the cover.

Octobe r 20 07 User’s Manual

Order Nu mber: 318476 001US 25

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit

Page 26

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—Setting Up and Configuring the

Development Kit

3.0 Setting Up and Configuring the Development Kit

This chapter discusses basic board set up and operation. Please refer to Chapter 2.0 for

the board layout, jumper setting location and the component reference designator.

3.1 Overview

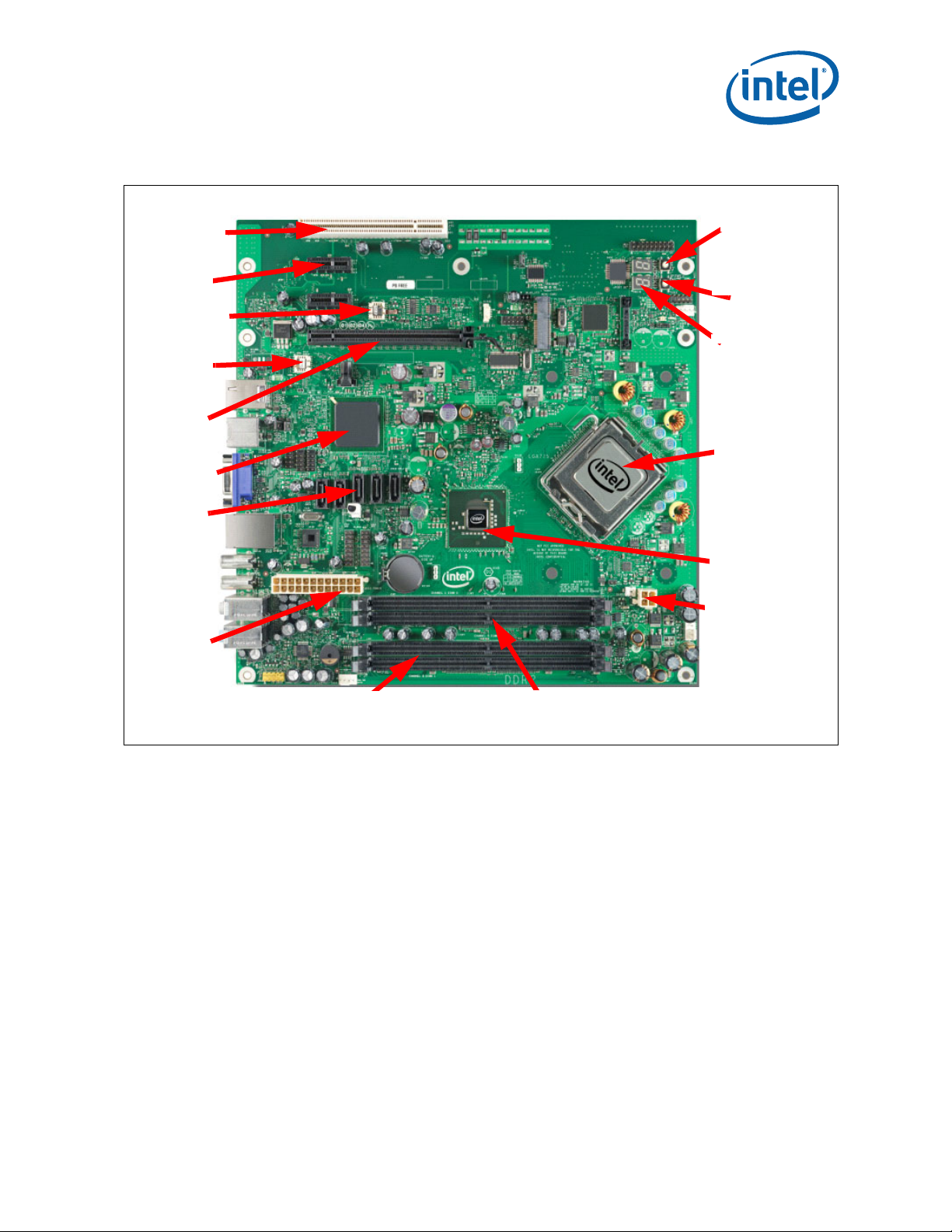

The board consists of a baseboard populated with one Intel® Core™ 2 Duo processor

E6400, the Intel

®

Q35 Express chipset, and other system board components and

peripheral connectors.

Note: This board is shipped as an open system allowing for maximum flexibility in changing

hardware configuration and peripherals. Since the board is not in a protective chassis,

take extra precaution when handling and operating the system.

Figure 16. Intel® Q35 Dev elopm e nt Kits

3.2 Installing Board Standoffs

Caution: The evaluation board in this development kit is shipped as an open system allowing for

maximum flexibility in changing hardware configuration and peripherals in the lab

®

Intel

CoreTM 2 Duo Proc es sor and Intel ® Q35 Express Chipset Development Kit

User’s Manual Octob er 2007

26 Order Nu mber: 318476 001US

Page 27

Setting Up and Configuring the Development Kit—Intel Core 2 Duo Processor and Intel Q35

Express Chipset

environment. Since the board is not in a protective chassis, the user is required to

observe extra precautions when handling and operating the system.

The board is a standard uBTX form factor and provides non-plated mounting holes with

top and bottom ground rings. If the board is not going to be used in a chassis,

standoffs are included for bench top use in the lab environment.

The development kit in clud es eig ht hex standof fs and for screws to atta ch to the board

for bench top use. Four of the standoffs are used to mount the heatsink (refer to

Section 3.3 for heatsink installation). Attach standoffs to the screws to the board at the

following mounting hole locations.

1. Insert screw through top mounting hole for the BTX Heatsink. Refer to Figure 17 for the mounting hole location.

2. Place standoff on backside of board and hand tighten to screw. Refer to Figure 18 for guide.

3. Repeat for additional standoffs on the board until all standoffs are installed. Refer to Figure 17 for recommended mounting hole locations.

Figure 17. Mounting Hole Locations

J24LB

Recommended

Mounting Hole

Locations

Mountin g Hole for

BTX heatsink

Locations

Octobe r 20 07 User’s Manual

Order Nu mber: 318476 001US 27

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit

Page 28

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—Setting Up and Configuring the

Figure 18. Mounting the Standoff for BTX Heatsink

Development Kit

3.3 BTX Heatsink Setup with SRM

This s e cti on d es cri b es B T X ca si ng w hi ch us e s “Sup po r t a nd R e te nti on M od ul e ( SRM )” as

shown in Figure 19.

Note: SRM is not included in this development kits.

Figure 19. Casing with “Support and Retention Module”

3.3.1 SRM Alignment on any BTX Board

Attach th e B TX The rmal Module Asse mbly (TMA) o ve r the p roc esso r to th e Sup port an d

Retention Module (SRM) by following procedures described below.

®

Intel

CoreTM 2 Duo Proc es sor and Intel ® Q35 Express Chipset Development Kit

User’s Manual Octob er 2007

28 Order Nu mber: 318476 001US

Page 29

Setting Up and Configuring the Development Kit—Intel Core 2 Duo Processor and Intel Q35

Express Chipset

1. Place the uBTX b oar d on the Sup por t and R ete nti on Mo dule ( SRM) so tha t the h ol es

A, B, C and D on the PCB line up with the corresponding locations on the SRM (see

Figure 19). The board and SRM assembly should look like Figure 20.

Figure 20. BTX board alignment on SRM

2. Place the heatsi nk on top of the p roc esso r. The he a tsi nk s hou ld al i gn wi th t he hol es on the SRM and board as shown below Figure 21. Clean the surface of the processor with isopropyl alcohol before attaching the heatsink.

Figure 21. Heatsink Alignment

3. Use two 6-32 screws to partially tighten the rear end of the heatsink to the board and the SRM as shown in Figure 22. The screw uses the threaded holes of the SRM for retention.

Octobe r 20 07 User’s Manual

Order Nu mber: 318476 001US 29

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit

Page 30

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—Setting Up and Configuring the

Figure 22. Tightening Heatsink on the SRM and Board

Development Kit

3.4 Board Setup and Configuration before Boot

Follow the steps below to operate the board.

Warning: Before starting, ensure the power supply is not connected to the board.

Ensure a safe and static-free work environment before removing any components from

their anti-static packaging. The Development Platform is susceptible to electrostatic

discharge, which may cause failure or unpredictable operation.

The Development Platform must be operated on a flame retardant surface because a

chassis is not included with the platform.

Caution: Connecting the wrong cable or reversing a cable may damage the board and may

Caution: The power supply cord is the main disconnect device to main power (AC power). The

Note: Ensure that setting up the ATX power supply is the fin al step performed in the proce ss

damage the device being connected. Since the board is not in a protective chassis, use

caution when connecting cables to the board.

socket outlet should be installed near the equipment and should be readily accessible.

To avoid shock, ensure that the power cord is connected to a properly wired and

grounded receptacle. Do not connect/disconnect any cables or perform installation/

maintenance of the boards in this product during an electrical storm. Ensure that any

equipment to which this product will be attached is also connected to properly wired

and grounded receptacles.

of assembly.

1. Physically inspect the motherboard for obvious defects. Note that each reference board has been tested prior to distribution, but a visual check should be performed to ensure no damage has occurred during shipping.

®

Intel

CoreTM 2 Duo Proc es sor and Intel ® Q35 Express Chipset Development Kit

User’s Manual Octob er 2007

30 Order Nu mber: 318476 001US

Page 31

Setting Up and Configuring the Development Kit—Intel Core 2 Duo Processor and Intel Q35

Express Chipset

2. Set jumpers to default positions. Refer to Section 2.8.1 for default positions.

3. Install the processor and ensure the 4-pin CPU fan power connector is installed on header shown in Figure 23.

Figure 23 . CPU Fan location

4-pin CPU Fan Power

4. Install the DDR2 DIMM in the Channel A Slot 0 connector. DIMMs should never be inserted or removed unless the power supply is disconnected from the AC power source . Ref er to Section 2.5 for system memory configuration.

5. Connect a SATA hard drive, USB keyboard, USB mouse, and VGA monitor (video card is optional).

6. Connect a 2x12 standard power supply and 2x2 standard power supply as well. Refer to Figure 24 for the location.

7. Plug the power cable into the back of the power supply, leaving the switch in the OFF positi on.

8. Once the board i s se t up, plug the cord int o the powe r sou rce . S wit c h on t he pow er supply.

9. Press the power button. Refer to Figure 24 or Figure 1 for power-on button location.

Octobe r 20 07 User’s Manual

Order Nu mber: 318476 001US 31

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit

Page 32

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—Setting Up and Configuring the

Figure 24. 2x12 Standard power supply and 2x2 power supply

Development Kit

Power-on button

2x12 Standard

power supply

2x2 Standard

power supply

3.5 Post Codes Definitions

The CRB BIOS writes progress and error codes to Port 80 during POST. These codes are

defined below.

3.5.1 Norma l Po st C od es

Uncompressed INIT code checkpoin ts

Before D1 – Early chipset and SIO initialization. NMI disabled.

D1 Perform keyboard controller BAT test. Save power-on CPUID to

scratch C MO S.

D0 Go to flat mode with 4GB limit. Start checksum verification.

D2 Disable cache and begin sizing full memory array.

D3 Additional chipset initialization, re-enable cache.

D4 Test base 512 MB of memory, adjust policies and cache first 8

D5 Bootblock code cop ied from ROM to l ower system memory. BIOS

D6 Check for recovery mode and verify main BIOS checksum.

If either in recovery mode or main BIOS checksum is bad, go to check point E0

else goto checkpoint D7.

MB.

now executes out of RAM.

®

Intel

CoreTM 2 Duo Proc es sor and Intel ® Q35 Express Chipset Development Kit

User’s Manual Octob er 2007

32 Order Nu mber: 318476 001US

Page 33

Setting Up and Configuring the Development Kit—Intel Core 2 Duo Processor and Intel Q35

Express Chipset

D7 Restore CPUID value to register. Bootblock runtime module

transferred to system memory.

D8 Main BIOS runtime code is to be decompressed.

D9 Copy main BIOS into system memory.

E1-E8 OEM memory detection/configuration error . R ange reserved for

chipse t vendors/OE M s.

EC-EE

Boot Block Recovery Code Checkpoints

E0 Initialize Floppy Controller, DMA controller and interrupt

controller.

E9 Set up floppy controller and data. Attempt to read from floppy.

EA Enable ATAPI hardw ar e. At tempt to r ead fro m ARMD an d ATAPI

CDROM.

EB Disable ATAPI hardware. Jump back to checkpoint E9.

EF Read error occurred on media. Jump back to checkpoint EB.

EF Floppy read error.

F0 Search for pre-defined recovery file in root directory.

F1 Recovery file not found.

F2 Start reading FAT table and analyze FAT to find the clusters

occupied by the recovery file.

F3 Start reading recovery file cluster by cluster.

F5 Disable L1 cache.

FA Check validity of recovery file configuration against

configuration of FLASH part.

FB Enable FLASH write through POEM and chipset specific method.

Detect FLASH type.

F4 Recovery file size does not match FLASH part size.

FC Erase FLASH.

FD Program FLASH.

FF Flash program successful. Disable FLASH write. Restore CPUID

into register.

Runtime POST Code Checkpoints

03 Disable NMI, Parity , EGA video and DMA controllers. Initialize

BIOS, POST and runtime data area.

04 Verify CMOS checksum. Initialize status register A.

05 Initialize interrupt hardware and interrupt vector table.

06 Do R/W to CH-2 count reg. Initialize CH-0 as system timer.

Install POSTINTCH handler.

Enable IRQ0 in PIC for system timer interrupt.

Octobe r 20 07 User’s Manual

Order Nu mber: 318476 001US 33

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit

Page 34

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—Setting Up and Configuring the

Development Kit

08 Initialize CPU. The BAT test performed on KBC. Auto detection

of KB and MS.

C0 Early CPU Init Start. Disable cache and init local APIC.

C1 Set up boot strap processor information.

C2 Set up boot strap processor for POST.

C5 Enumerate and set up application processors.

C6 Re-enable cache for boot strap processor.

C7 Early CPU Init Exit.

0A Initialize 8042 compatible keyboard controller.

0B Detect PS/2 mouse.

0C Detect keyboard in KBC port.

0E Test and ini t ia li za ti on of different in pu t dev i ces. Un compress a l l

language, BIOS logo and Silent logo.

13 Early POST initialization of chipset registers.

11 Going to check pressing of <INS>, <END> key during power-

on.

12 To init CMOS if “Init CMOS in every boot” is set or <END> key

is pressed. Going to disable DMA and Interrupt controllers.

13 Video display is disabled and port-B is initialized. Chipset init

about to begin.

24 Uncompress and initialize platform specific BIOS modules.

30 Initialize System Management Interrupt.

2A Initialize different devices through Device Initialization Manager

(DIM).

2C Detect and initialize video adapter with optional ROM.

2E Initialize all output devices.

31 Allocate memory for ADM module. Uncompress and initialize

ADM module.

33 Initialize silent boot mode. Set window to display text

information.

37 Dis pla y si g n-o n mes sa ge , CPU in f or ma ti on, se tu p me ss age an d

OEM specif ic information.

38 Initialize different devices through DIM.

39 Initialize DMAC-1 and DMAC-2.

3A Initialize RTC date/time.

3B Test and display total memory in system.

3C Mid POST initialization of chipset registers.

40 Detect peripheral devices.

50 Program memory hole or implementation specific adjustments

to system memory.

52 Update CMOS memory size. Allocate memory for extended BIOS

data area.

®

Intel

CoreTM 2 Duo Proc es sor and Intel ® Q35 Express Chipset Development Kit

User’s Manual Octob er 2007

34 Order Nu mber: 318476 001US

Page 35

Setting Up and Configuring the Development Kit—Intel Core 2 Duo Processor and Intel Q35

Express Chipset

60 Initialize NUM-LOCK status and program typematic rate.

75 Initialize INT-13 and prepare for IPL detection.

78 Initialize IPL devices controlled by BIOS and option ROMs.

7A Initialize option RMs.

7C Generate and write contents of ESCD in NVRAM.

84 Log errors encountered during POST.

85 Display errors and prompt for user response.

87 Execute BIOS setup if requested.

8C Late PO ST ch ips et regist e r initial iz at ion .

8D Build ACPI tables if supported.

8E Program peripheral parameters. Enable/Disable NMI as

selected.

90 Late POST initialization of system management interrupt.

A0 Check for boot password.

A1 Clean-up work needed before boot to OS.

A2 Prepare runtime image for different BIOS modules. Initialize MS

IRQ Routing Table.

A4 Initialize runtime language module.

A7 Display system configuration screen. Initialize CPU for boot,

program MTRRs.

A8 Pr epar e CPU for boot inclu ding fin al MTR R value s.

A9 Wait for user input at configuration display if needed.

AA Uninstall POST INT1CH vector and INT09 vector. De-initialize

ADM module.

AB Prepare BBS for INT19 boot.

AC End of POST initialization of chipset registers.

B1 Save system context for ACPI.

00 Pass control to OS loader via INT19.

61-70 OEM POST error. Reserved for chipset vendors and system

manufacturers.

Octobe r 20 07 User’s Manual

Order Nu mber: 318476 001US 35

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit

Page 36

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—Setting Up and Configuring the

Development Kit

®

Intel

CoreTM 2 Duo Proc es sor and Intel ® Q35 Express Chipset Development Kit

User’s Manual Octob er 2007

36 Order Nu mber: 318476 001US

Loading...

Loading...