Page 1

Intel® 945G Express Chipset

Development Kit

User’s Manual

April 2007

Reference #308823-002

Page 2

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

2

Contents

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. EXCEPT AS PROVIDED IN INTEL’S

TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL

DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO SALE AND/OR USE OF INTEL PRODUCTS, INCLUDING

LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF

ANY PATENT, COPYRIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to

the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or

implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel products are not intended for use in medical, life-saving, life-sustaining, critical control or safety systems, or in nuclear-facility

applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves

these for future definition and shall have no responsibility whatsoever for conflicts o r incompatibilities arising fr om future changes to them.

®

The Intel

the product to deviate from published specifications. Current characterized errata are available on request.

This document and the software described in it are furnished under license and may only be used or copied in accordance with the terms of

the license. The information in this document is furnished for informational use only, is subject to change without notice, and should not be

construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that

may appear in this document or any software that may be provided in association with this document. Except as permitted by such license,

no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the e xpres s

written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling

1-800-548-4725, or by visiting Intel's website at http://www.intel.com.

AlertVIEW, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Connect, CT Media, Dialogic, DM3,

EtherExpress, ETO X, FlashFil e, i386, i486, i960, iCOMP, InstantIP, Intel, Intel logo, Intel386, Intel48 6, Intel740, IntelDX 2, IntelDX4,

IntelSX2, Intel Create & Share, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel

NetStructure, Intel Play, Intel Play logo, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Xeon, Intel XSc ale,

IPLink, Itanium, LANDesk, LanRover, MCS, MMX, MMX logo, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, PDCharm,

Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, RemoteExpress, Shiva, SmartDie, Solutions960, Sound

Mark, StorageExpress, The Computer Inside., The Journey Inside, TokenExpress, Trillium, VoiceBrick, Vtune, and Xircom are trademarks

or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

† Hyper-Threading Technology (HT Technology) requires a computer system with an Intel

Technology and an HT Technology-enabled chipset, BIOS, and operating system. Performance will vary depending on the specific

hardware and software you use. See http://www.intel.com/info/hyperthreading/ for more information including which processors support HT

Technology.

*Other names and brands may be claimed as the property of others.

Copyright © Intel Corporation 2007. All rights reserved.

945G Express Chipset Development Kit User’s Manual may contain design defects or errors known as errata which may cause

®

Pentium® 4 processor supporting HT

Reference #308823

Page 3

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

3

Contents

Contents

1 About Th is Ma nua l..........................................................................................................6

1.1 Content Overview..............................................................................................................6

1.2 Text Conventions.............................................................................................................. 6

1.3 Glossary of Terms and Acronyms......................................................................................7

1.4 Support Options ................................................................................................................ 9

1.4.1 Electroni c Support Systems...............................................................................................9

1.4.2 Additional Technical Support............................................................................................. 9

1.5 Product Literature ..............................................................................................................9

1.6 Related Documents.........................................................................................................10

2 Development Kit F eatures.............................................................................................11

2.1 Overview.........................................................................................................................11

2.1.1 Intel® 945G Express Platform Feat ur es and Benef its .......................................................12

2.1.2 Development Kit Features Summary ...............................................................................13

2.2 Development Kit Hardware Lists......................................................................................14

2.3 Software Key Features....................................................................................................14

2.3.1 AMI* BIOS.......................................................................................................................14

2.4 Processor Featur es and Oper ation..................................................................................15

2.4.1 Intel® Pentium® 4 Processor 551......................................................................................15

2.4.2 Intel® Celeron® D Processor 341......................................................................................16

2.5 Intel® 945G Express Chipset Feat ur es and Oper ation......................................................16

2.5.1 Intel® 945G Memory Controller Hub ((G ) M CH) .................................................................17

2.5.2 Intel® I/O Controller Hub 7 (ICH7)....................................................................................19

2.5.3 Power Management ........................................................................................................21

3 Setting Up the Develop ment Kit ...................................................................................23

3.1 Overview.........................................................................................................................23

3.2 Additional Hardware and Software Required ....................................................................23

3.3 Setting up the Evaluation Board.......................................................................................24

3.3.1 Memory Configurations ...................................................................................................25

3.3.2 Audio Subsystem Configurations .....................................................................................28

3.3.3 LAN Subsystem Configurations.......................................................................................29

3.3.4 Intel® Active Management Technology (Optional) ............................................................31

3.3.5 Configu rin g th e BIOS.......................................................................................................32

3.4 Error Messages and Beep Codes....................................................................................32

3.4.1 Speaker ..........................................................................................................................32

3.4.2 BIOS Beep Codes...........................................................................................................32

3.4.3 BIOS Error Messages......................................................................................................33

3.4.4 Port 80h POST Codes.....................................................................................................33

4 Hardware References....................................................................................................38

4.1 Overview.........................................................................................................................38

4.1.1 Board Layout...................................................................................................................39

4.1.2 Back Panel Connectors ...................................................................................................41

4.2 Primary Features.............................................................................................................41

4.2.1 Core Components ...........................................................................................................42

4.2.2 Expansion Slots and Sockets ..........................................................................................42

4.3 Secondary Features........................................................................................................46

4.3.1 Jumper Settings..............................................................................................................47

4.3.2 LEDs...............................................................................................................................47

4.3.3 Front Panel Header ( P ower up and Reset) ......................................................................47

4.4 Headers ..........................................................................................................................48

Reference #308823

Page 4

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

4

Contents

4.4.1 Evaluation Board Headers...............................................................................................48

4.4.2 ATX Power Connectors...................................................................................................49

4.4.3 IDE Connector.................................................................................................................50

4.4.4 SATA Pinout ...................................................................................................................50

4.4.5 Fan Connectors...............................................................................................................51

4.4.6 Front Panel USB Header.................................................................................................51

4.4.7 Front Panel Audio Header ...............................................................................................51

4.4.8 Front Panel Header.........................................................................................................52

4.4.9 Serial Port Header...........................................................................................................52

4.5 Thermal Considerations...................................................................................................53

Figures

Figure 1 Intel® 945G/ICH7 Platform Bloc k Diagram .......................................................................11

Figure 2 Memory Channel and DIMM Configuration ......................................................................27

Figure 3 Dual Channel (Interleaved) Mode Confi gur ation with 2x DIMMs.......................................27

Figure 4 Dual Channel (Interleaved) Mode Confi gur ation with 3x DIMMs.......................................27

Figure 5 Dual Channel (Interleaved) Mode Confi gur ation with 4x DIMMs.......................................28

Figure 6 Single Channel (Asymmetric) Mode Configuration with 1x DIMM.....................................28

Figure 7 Single Channel (Asymmetric) Mode Configuration with 3x DIMMs ...................................28

Figure 8 Back Panel Audio Connect or Options for 8-channel Audio Subsystem............................. 29

Figure 9 LAN Connector LED locati ons .........................................................................................30

Figure 10 Evaluation Board Layout..................................................................................................38

Figure 11 Evaluation Boar d M ajor Com ponents...............................................................................39

Figure 12 Back Panel I/O Connectors..............................................................................................41

Figure 13 Evaluation Board Main Jumpers......................................................................................46

Figure 14 Front Panel Header.........................................................................................................48

Figure 15 Processor Heat Si nk for Om ni- Directional Airflow.............................................................53

Figure 16 Localized High Temperature Zones.................................................................................54

Tables

Table 1 Intel Literature Centers......................................................................................................9

Table 2 Related Documents.........................................................................................................10

Table 3 Key Features and Benef its of the Intel® 945G Express Platform.......................................12

Table 4 Development Kit Features Summary ...............................................................................13

Table 5 Effects of Power Switch Pressing Duration......................................................................22

Table 6 Back Panel Task (Audio) .................................................................................................29

Table 7 LAN Connector LED Status .............................................................................................30

Table 8 Beep Codes ....................................................................................................................32

Table 9 Error Messages ...............................................................................................................33

Table 10 Port 80h POST Code Ranges..........................................................................................33

Table 11 Port 80h POST Codes.....................................................................................................34

Table 12 Typical Port 80h POST Sequence ...................................................................................36

Table 13 Evaluation Boar d Components ........................................................................................39

Reference #308823

Page 5

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

5

Contents

Table 14 Back Panel I/O Connectors..............................................................................................41

Table 15 Core Components ...........................................................................................................42

Table 16 Expansion Slots and Sockets ..........................................................................................42

Table 17 Intel® sDVO to PCI Express* Connector Mapping for MEC Cards ....................................43

Table 18 PCI Express* (x1) Pi nout.................................................................................................45

Table 19 Jumpers........................................................................................................................ ..47

Table 20 Boot Select Opti ons for J 3601 and J 3602........................................................................47

Table 21 LEDs...............................................................................................................................47

Table 22 Front Panel Jumper Setting.............................................................................................48

Table 23 Evaluation Board Headers...............................................................................................48

Table 24 2x12 ATX Power Connector ............................................................................................49

Table 25 2x2 Auxiliary 12V Power Connector.................................................................................49

Table 26 IDE Connector.................................................................................................................50

Table 27 SATA Pinout ...................................................................................................................50

Table 28 Fan Connectors...............................................................................................................51

Table 29 Front Panel USB Header.................................................................................................51

Table 30 Front Panel Audio Header ...............................................................................................51

Table 31 Front Panel Header ( J 7J 2) ..............................................................................................52

Table 32 Serial Port Header ( J 2B 1) ................................................................................................52

Revision History

Date Revision Description

April 2007 002 Updated Section 2.2 to reflect that heat sink fan is pre

August 20 05 001 Initial release

installed.

Updated Section 3.3 to add safety warning.

Reference #308823

Page 6

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

6

About Th is Ma nua l

1 About This Manual

This us er’s manual descr ibes the u se of t he Intel® 945G® Express Chipset Development

Kit. Th is manual ha s been written for OEM s, system evaluators, and embedded system

developers. All jumpers, headers, LED functions, and their locations on the board, along

with subsystem fea tur es and POST codes, are defined in th is document .

®

For the latest information about the Intel

reference platform, visit:

945G® Express Chipset Development Kit

http://developer.intel.com/design/intarch/devkits/index.htm

For design documents related to this platform, such as schematics and bill of materials,

pleas e conta ct your Intel field sa les repr esentative.

1.1 Content Overview

Chapter 1: About This Manu al

Description of conventions used in this manual. The last few sections explain how to obtain

literature and contact customer support.

Chapter 2: D ev elo p m ent Kit Features

Describes de velop men t kit features and board capability. This includes the inform ation on

the pr ocessor featur es, com ponent features an d operati on, and overa ll developm ent kit

board capability.

Chapter 3: Setting Up the Development Kit Board

Complete instructions on how to configure the evaluation board and processor assembly by

setting jumpers, connecting peripherals, providing power, and configuring the BIOS.

Chapter 4: H ardware Reference

Description of jumper settings and functions, board debug capabilities, and pinout

information for connectors.

1.2 Text Conventions

The following notations may be used throughout this manual.

# The pound symbol (#) appended to a signal name indicates that the signal is

active low.

Variables Vari ables ar e shown in ita lics. Var iables mu s t be replaced wi th corr ect valu es.

Instructions Instr uction mnemonics are shown in upper case. When you are progr amming,

instructi on s ar e n ot case sensitive. You may use either upper cas e or lower case.

Numbers Hexadecimal numbers are represented by a string of h ex adecimal digits

followed by the character H. A zero prefix is added to numbers that begin with A

through F (e.g., FF is shown as 0FFH). Decimal and bin ary number s ar e

represented by their customary notations. (That is, 255 is a decimal number and

1111 1111 is a binary number. In some cases, the letter B is added for clarity.)

Reference #308823

Page 7

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

7

About Th is Ma nua l

Units of Measure The foll o wi ng abbrevi ations are us ed t o represen t units of measure:

A amps, amperes

GByte gigabytes

KByte kilobytes

KΩ kilo-o hms

mA milliamps, millia mp eres

MByte megabytes

MHz megahertz

ms milliseconds

mW milliwatts

ns nanoseconds

pF picofarads

W watts

V volts

Signal Names Signal names are shown in uppercase. When several signals share a common

name, an individual signal is represented by the signal name followed by a

number, while the group is represented by the signal name followed by a

variable (n). F or exampl e, the lower chip-sel ect sign als are nam ed CS0 #, CS1#,

CS2#, and so on; they are collectively call ed C S n#. A pound sym bol (#)

appen d ed to a signal nam e identifi es an active-low sign al. Port pin s ar e

repr esented by the port abbreviat ion, a period, and the pin number (e.g., P 1. 0 ).

1.3 Glossar y of Terms and Acronyms

This section defines conventions and terminology used throughout this document.

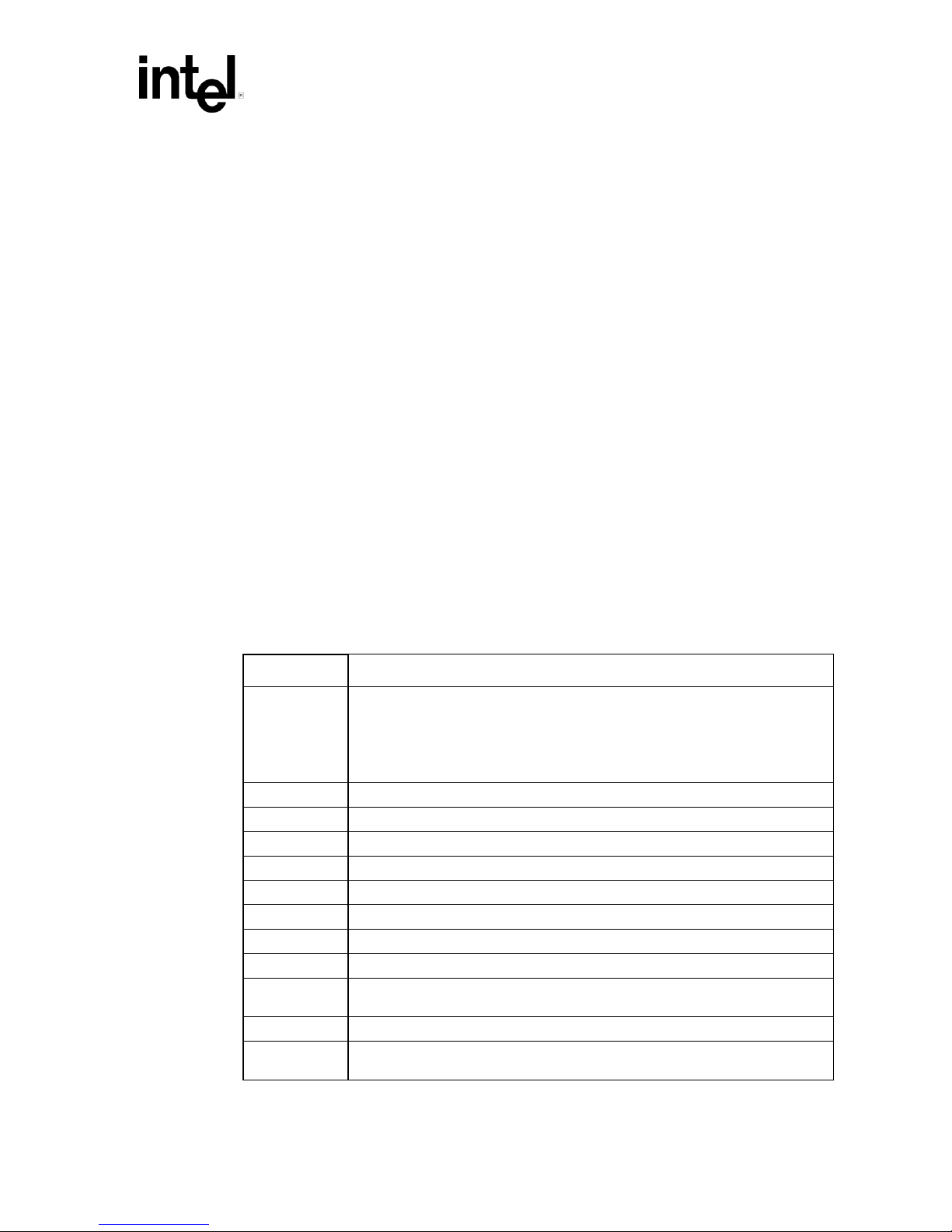

Term Description

ADD2+ Card Advanced Digital Display Card – 2nd Generation. Provides digital display options for

ACPI Advanc ed Configur ation an d Pow er In t erface

BLT Block Level Tran sfer

Core Th e internal base logic in the (G)MCH

CRT Cathode Ray Tube

DBI Dynamic Bus Inversion

DDR Double Data Rate SDRAM memory technology

DDR2 A second generation Double Data Rate SDRAM memory technology

DMI (G)MCH-Intel® ICH7 Direct Media Interface

DVI Digital Video Interface. Specification that defines the connector and interface for

FSB Front Side B us .Synonym ous with h ost or process or bus .

Full Reset Full reset is when PWROK is de-asserted. Warm reset is when both RSTIN# and

an Intel graphics controller that supports ADD2+ cards. It plugs into a x16 PCI

Express* connector but uses the multiplexed SDVO interface. The card adds Video

In capabilities. This card will not wor k with an I nt el graphics c ontr ol ler that supp ort s

DVO and ADD c ards . I t will f u nc ti on as an ADD2 card in an ADD2-su pp orted

system, but Video In capabilities will not work.

digital dis p lays.

PWROK are asserted.

Reference #308823

Page 8

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

8

About Th is Ma nua l

Term Description

GMCH Graphics Memory Controller Hub. Component that contains the processor interface,

Host This term is used synonymously with processor.

Intel® DVO Digital Video Out port. Term used for the first generation of Intel Graphics

Intel® ICH7 Seventh generation I/O Controller Hub component that contains additional

LCD Liquid Crystal Display.

LVDS Low Voltage Differential Signaling. A high speed, low power data transmission

MCH Memory Controller Hub. Component that contains the processor interface, DRAM

MEC Media Expansion Card, also known as ADD2+ card. Refer to ADD2+ term for

PCI Express Third Generation input/output graphics attach called PCI Express Graphics. PCI

Primary PCI The Primary PCI is the physical PCI bus that is driven directly by the ICH7

SDVO Serial Digital Video Out. A digital display channel that serially transmits digital

SDVO Device Third party codec that uses SDVO as an input. May have a variety of output

SMI System Management Interrupt. SMI is used to indicate any of several system

UMA Unified Memory Architecture. Describes an integrated graphics device using system

DRAM controller, x16 PCI Express port (typically, the external graphics interface),

and integrated graphics device (IGD). It communicates with the Intel

Hub 7 (ICH7) and other I/O controller hubs over the DMI interconnect. In this

docu ment G MCH refers to the Intel

Controller’s digital display channels. Digital display data is provided in a parallel

format. This int er face is not electrically compatible with the 2

display channel discussed in this document – SDVO.

functionality compared to previous ICHs. The I/O Controller Hub component

contains th e pr i m ary P CI int erfac e, LPC int erface, USB 2, ATA-1 00, and other I/O

functi ons . It c omm un icates wi th th e (G)MCH ov er a propriet ary interc on n ect c all ed

Direct Media Interface (DMI).

standard used for display connections to LCD panels.

controller, and x16 PCI Express port (typically, the external graphics interface). It

communicates with the I/O controller hub (ICH7) and other I/O controller hubs over

the DMI interconnect. In this document MCH refers to the 82945P MCH component.

description.

Express is a high-speed serial interface whose configuration is software compatible

with the existing PCI specifications. The specific PCI Express implementation

intended for connecting the (G)MCH to an external Graphics Controller is a x16 link

and replaces AGP.

component. Communication between Primary PCI and the (G)MCH occurs over

DMI . Note that the Primary PCI bus is not PCI Bus 0 from a configuration

standpoint.

displ ay d ata t o an ext er n al SD V O device. Th e SDVO device accepts this seriali z ed

format and then translates the data into the appropriate display format (i.e., TMDS,

LVDS, TV-Out). This interface is not electrically compatible with the previous digital

display channel (DVO). For the 82945G GMCH, it will be multiplexed on a portion of

the x16 graphics PCI Express interface.

formats, including DVI, LVDS, HDMI, TV-Out, etc.

conditions (such as, thermal sensor events, throttling activated, access to System

Management RAM, chassis open, or other system state related activity).

memory for its frame buffers.

®

82945G GMCH component.

®

I/O Controller

nd

generati on digit al

Reference #308823

Page 9

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

9

About Th is Ma nua l

1.4 Support Options

1.4.1 Electronic Support Systems

Intel’s site on the World Wi d e Web ( http://www.intel.com/) provides up-to-date technical

information and product support. This information is available 24 hours a day, 7 days a

week, providing technical infor mation whenever you need it.

Product documentation is provided online in a variety of web-friendly formats at:

http://appzone.intel.com/literature/index.asp

1.4.2 Additional Technical Support

If you require additional technical support, please contact your field sales representative or

local distributor.

1.5 Product Literature

Product literature can be ordered from the following Intel literature centers:

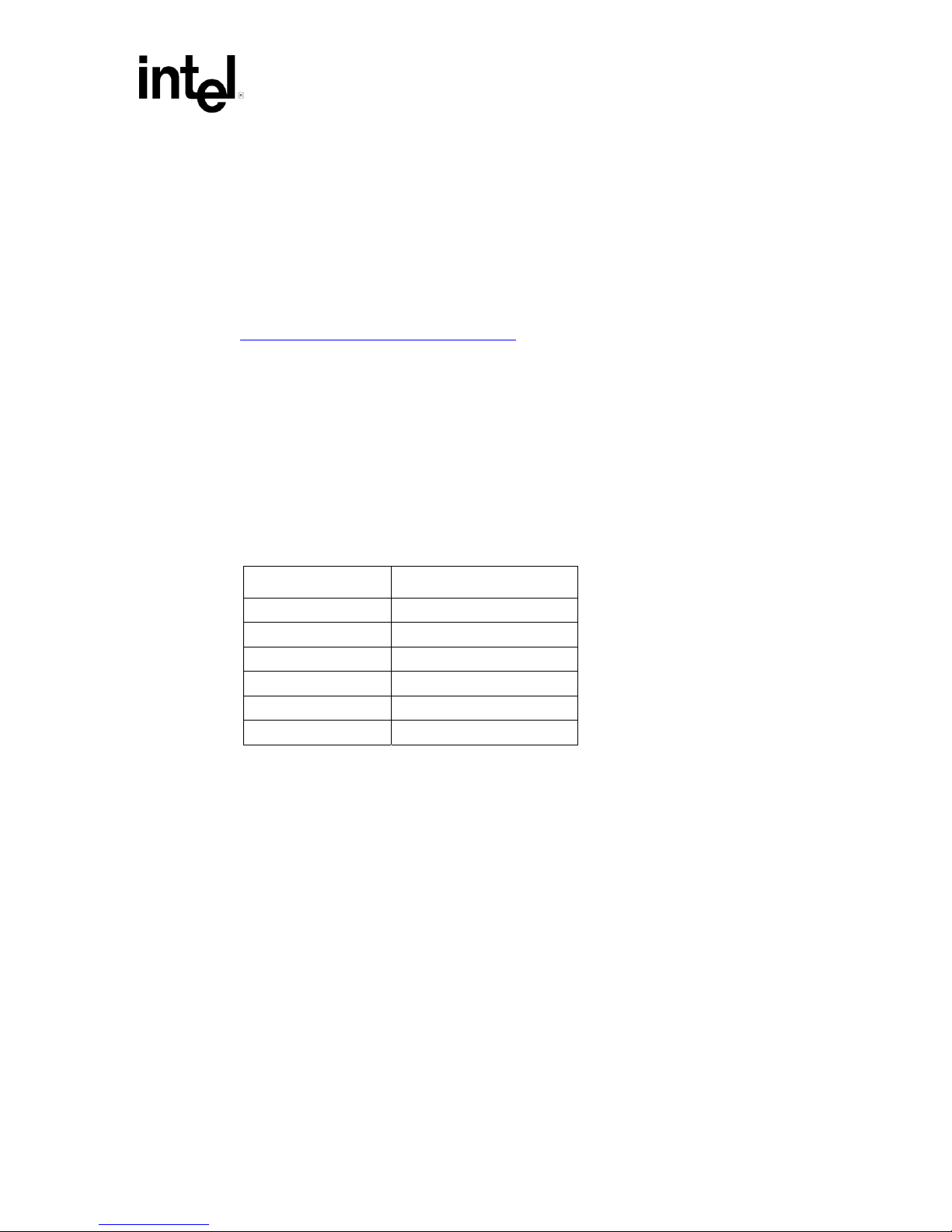

Table 1 Intel Literature Centers

Location Telephone Number

U.S. and Canada 1-800-548-4725

U.S. (from overseas) 708-296-9333

Europe (U.K.) 44(0)1793-431155

Germany 44(0)1793-421333

France 44(0)1793-421777

Japan (fax only) 81(0)120-47-88-32

Reference #308823

Page 10

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

10

About Th is Ma nua l

1.6 Related Documents

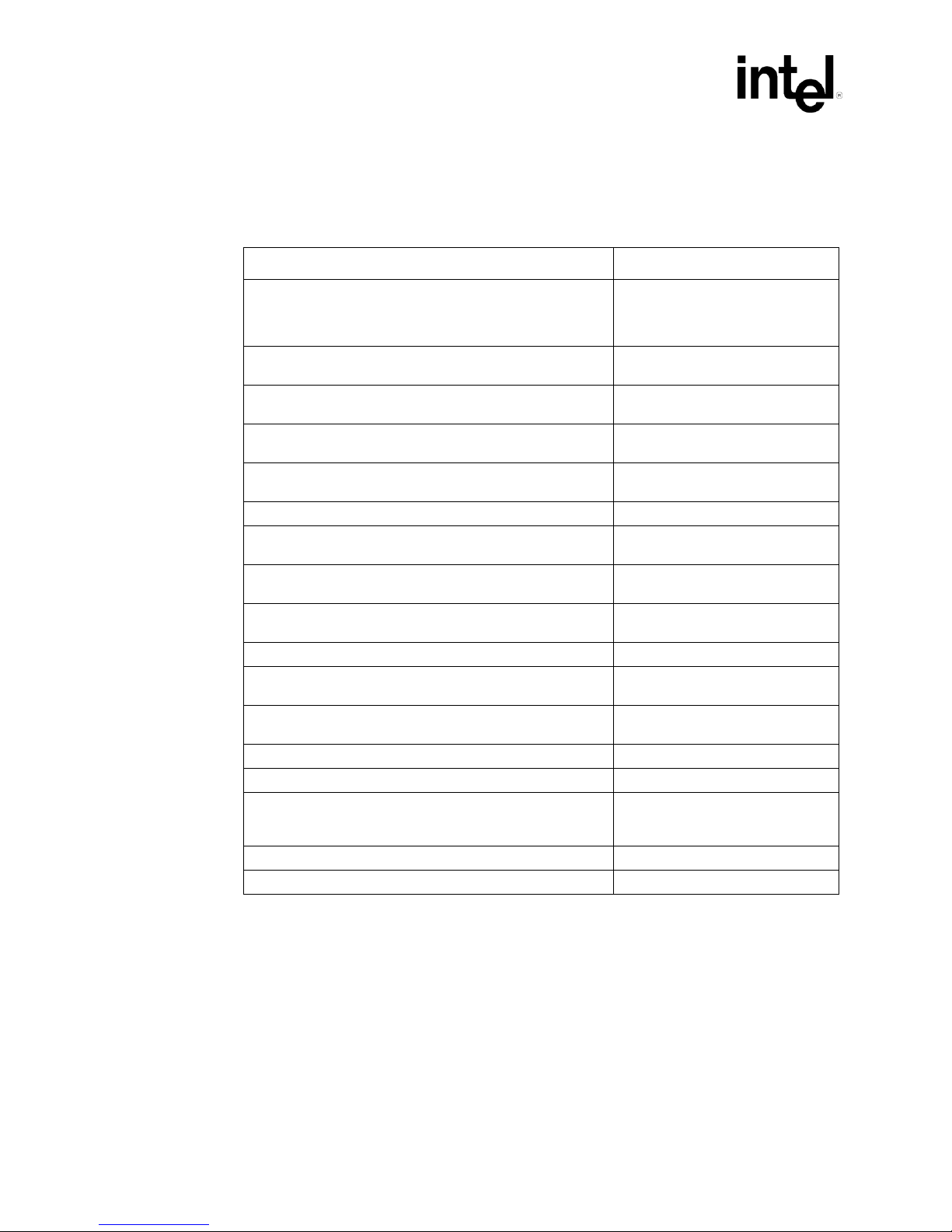

Table 2 Related Documents

Document Title Order Number

Intel® Pentium® 4 Processor 570/571, 560/561, 550/551,

540/541 , 53 0/ 5 31 and 520/521 Su pp or ti n g H yp er- T hreadin g

Technology

and supporting Intel

Intel® Pentium® 4 Proces sor o n 9 0 nm P roces s Specificati o n

Update

Intel® Pentium® 4 Processor on 90 nm Pr oc ess in the 77 5- L an d

LGA Package Thermal and Mechanical Design Guidelines

Intel® Celeron® D Processors 335, 33 0, 3 25, and 320

Datasheet

Intel® Celeron® D Processors 335, 33 0, 3 25, and 320

Specification Update

LGA775 Socket Mechanical Design Guide 302666

Voltage Regulator Down (VRD) 10.1 Design Guide for Desktop

LGA775 Socket

Intel® Pentium 4 Pr oc es sor in the 77 5-L and LGA Pac k ag e f or

Embedded Applications Thermal Design Guide

Intel® Celeron D Processor in the 775-Land LGA Package for

Embedded Applications Thermal Design Guide

Intel® 945G/945P Express Chipset Family Datasheet 307502

Intel® 945G/P Express Chipset Family Memory Controller Hub

Specification Update

Intel® 945G/P Express Chipset Family Thermal and Mechanical

Design Guidelines

Intel® I/O Controller Hub 7 (ICH7) Family Datasheet 307013

Intel® I/O Controller Hub 7 (ICH7) Specification Update 307014

Intel® I/O Controller Hub 7 (ICH7) Thermal Design Guidelines:

For the Intel

Controller Hubs

PCI Lo cal Bus Specification, Rev. 2.3 http://www.pcisig.com/specifications

PCI Express Specification, Rev 1.0a, July 22, 2002 http://www.pcisig.com/specifications

†

Datasheet: On 90nm in 775-land LGA Package

®

Extend ed M em ory 64 Tec hn ol og y

®

82801GB ICH7 and 82801GR ICH7R I/O

302351

302352

302553

302353

302354

302356

302822

302823

307503

307504

307015

Reference #308823

Page 11

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

11

533/800 MHz FSB

Display

Display MEC

Super I/O

Other ASICs

(Optional)

AC '97 / Intel

®

High

SMBus 2.0 / I

2

C*

PCI Express* x1

PCI Express

Flash BIOS

Development Kit F eatures

2 Development Kit Features

2.1 Overview

This chapter provides a platform overview of the Intel® 945G Express Chipset platform.

®

The Int el

551 and Intel

Intel

(ICH7) Family for the I/O subsystem.

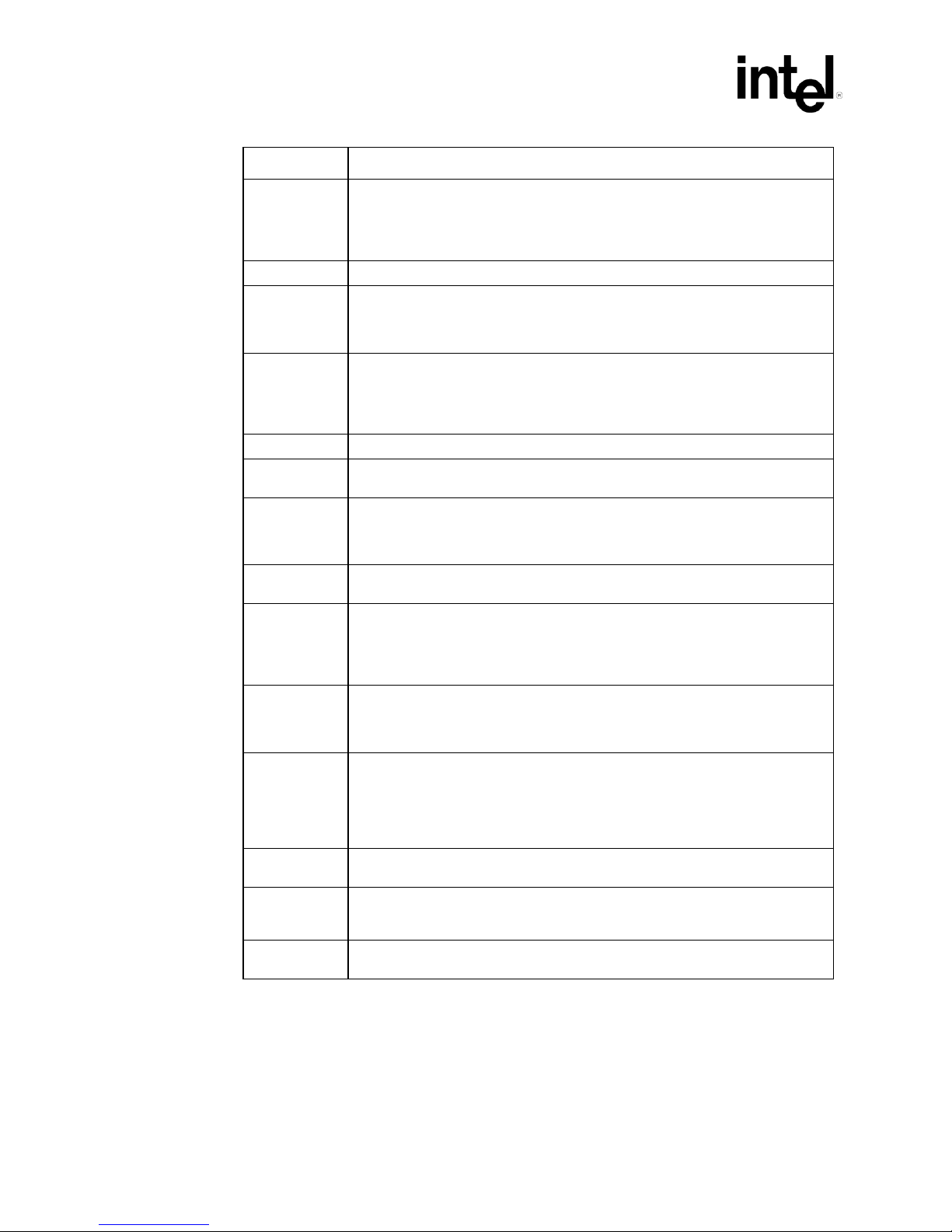

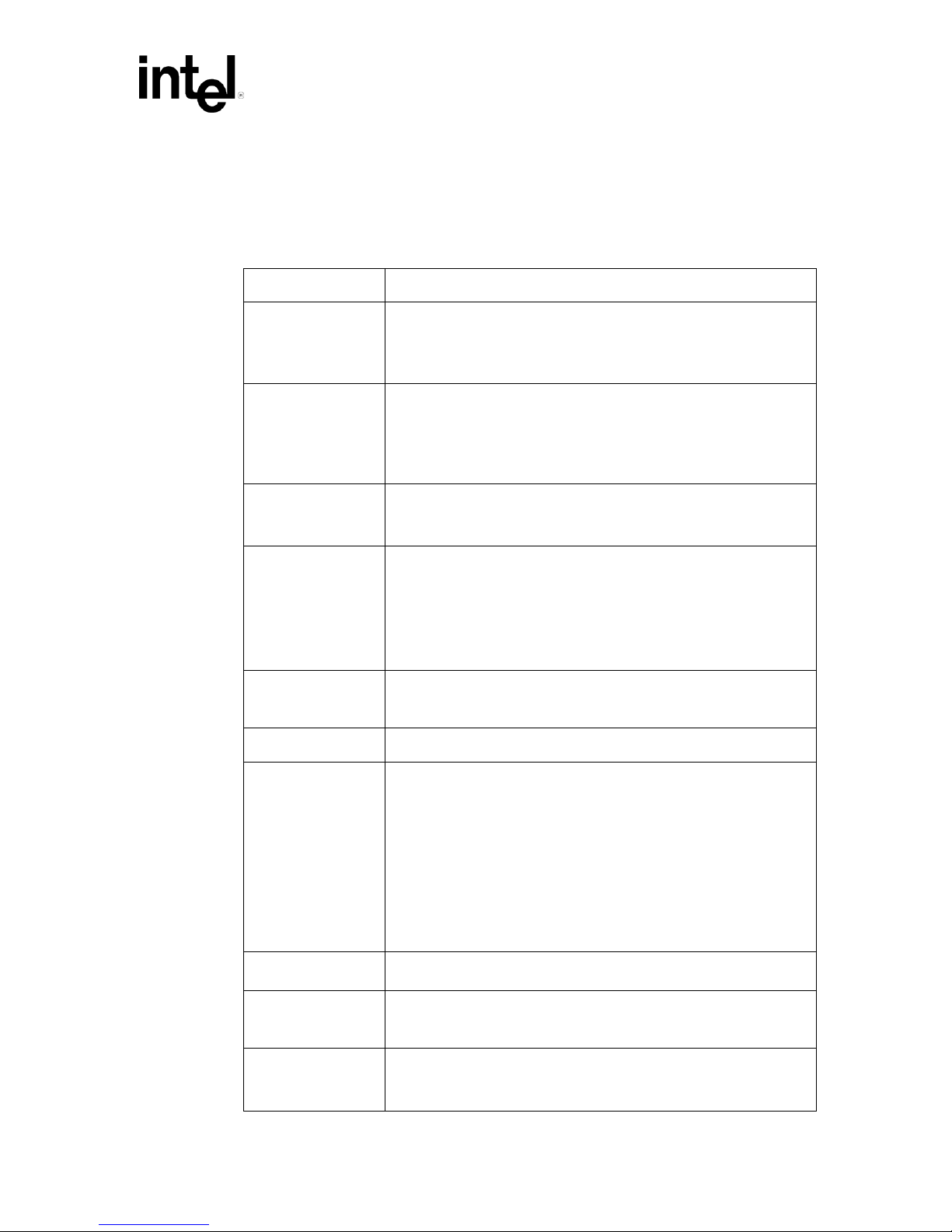

Figur e 1 shows an ex ample system block di agram for the 945G Express Chipset.

Figure 1 Intel

945G Express Chipset is designed for use with the Intel® Pentium® 4 Processor

®

®

82945G GMCH (or MCH) for the host bridge, and Intel® I/O Controller Hub 7

®

945G/ICH7 Platform Block Diagram

Celeron® D Processor 3 4 1. Each chi p s et contains two compon ents: the

Processor

Display

Gigabit Ethernet

VGA

Graphics C ard

USB 2.0

8 ports, 480 Mb/s

IDE

4 SATA Ports

Definition Audio CODECs

GPIO

Analog Disp lay

SDVO

OR

PCI Express

x16 Graphics

(Optional)

TPM

Intel® 82945G GMCH

DMI Interface

Intel® ICH7 Family

LPC Interface

Intel® 945G Express Chipset

Channel A

Channel B

Power Management

Clock Generation

LAN Connect

System Management (TCO)

PCI Bus

System Memory

DDR2

DDR2

SPI BIOS

Reference #308823

Page 12

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

12

Development Kit F eatures

2.1.1 Intel® 945G Express Platform Features and Benefits

The 945G Express platform is designed to support several processor types: Intel® Pentium

4 Process or on 90n m Process in the 775-land LGA Pa ck age and the Intel® Celeron® D

Processor. The only processor included in this development kit will be the Pentium 4

processor.

®

The Intel 945G Express Chipset includes the Intel

ICH7 or Intel

®

82801GR ICH7R (not offered in the development kit).

The foll o wi ng table lists th e major features present on the Intel

Section 2.1.2 will summarize the development kit features.

Table 3 Key Features and Benefits of the Intel

Features Benefits

82945G (G)MCH and Intel® 82801GB

®

945G Express platform.

®

945G Express Platform

®

800/533 MHz FSB Supports the Intel® Pentium® 4 Processor with HT Technology† and

PCI Express Interface The PCI Express x16 graphics interface delivers more than 3.5 times

Intel® Graphics Media

Accelerator (GMA) 950

Intel® High Definition

Audio

Intel® Matrix Storage

Technology

Intel® Active Management

Technology

Serial ATA (SATA-II) -

1.5/3 Gb/s

Dual Channel DDR2,

533/667 MHz

Intel® Flex Memory

Technology

®

the Intel

the LGA775 socket, with scalability for future processor innovations.

the band wi dt h ov er a tr ad it i on al AG P 8 X inter face and su pp ort s th e

latest high-performance graphics cards. The PCI Express x1 I/O ports

offer 3.5 tim es th e b and w idth over tr adition al PC I arc hitectur e,

deliver in g faster access to peri pheral d evices and n et w or ki ng .

Deliver s rich vis u al c olor and pict ure clarit y wi th ou t th e need for

additional discrete graphics cards.

Integrated audio support enables premium home theater sound and

delivers ad van ced f eatur es such as mul ti ple audi o str eams and jack

re-tasking. The Dolby* PC Entertainment Experience is available

exclus i vel y on s ystems with I nt el

Provides quicker fil e access with RAID 0, 5, and 10, and prot ection

against data loss from a hard disk drive failure with RAID 1, 5, and 10.

This feature requires the ICH7R (n ot of fered in the develop me nt k it).

Enables remote , down-the-wire management of out-of-band

networked systems regardless of system state. Helps improve IT

effici ency, ass et man ag em en t an d s yst em s ecur i t y an d av ail ab ility.

High-speed storage interface supports faster transfer rate for

improv ed d at a access.

Delivers up to 10.7 GB/s of bandwidth and 4 GB memory

addressability for faster system responsiveness and support of 64-bit

computing.

Facilit ates easier upgrad es by all ow i ng different m em ory sizes to b e

populated and remain in dual-channel mode.

Celeron® D Processor (not offered in this development kit) in

®

High Definition Audio.

Reference #308823

Page 13

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

13

Development Kit F eatures

2.1.2 Develo pm e nt Ki t Fe at ur e s Summ ary

This sect ion sum marizes the actual developm ent kit featur es .

Table 4 Development Kit Features Summary

Form Factor

Processor

Memory

Chipset

Video

Audio

Legacy I/O Control

microATX (9.60 x 9.60 inches)

®

Pentium® 4 Processor 551 in the 775-lan d LG A p ac k age

Intel

Suppor ts a 533/800 MH z front side bus

†

Hyper-Threading Technology

®

Extended Memory 64 Technology (EM64T)

Intel

(HT Technology)

DDR2 533/667 dual-channel system memory interface (DIMM sockets)

Four 240-pin DDR2 SDRAM DIMM sockets (two per channel)

Support for unbuffered, non-ECC DDR2 SDRAM modules

Supports 128 MB to 4 G B of system memory

256 Mbit, 51 2 M bit , or 1 Gbit tec hn ol ogy

®

945G Express Chipset, consisting of:

Intel

®

82945G Graphics Memory Controller Hub ((G)MCH)

• Intel

®

82801GB I/O Controller Hub 7 (ICH7)

• Intel

Option of eith er us in g int egrated gr ap hic s s yst em or external PC I E xpress

graphics port:

®

GMA950 integrated graphics subsystem

Intel

Supports Intel

®

Media Expansion Card (MEC, also known as ADD2+) for

additi on al dig i t al dis p l ay such as DVI, LV D S , etc . d ep end in g on t h e m edi a

expansion card features.

Support s ext er n al PC I Express (x1 6) graphic s c ard

®

High Definition Audio subsystem:

Intel

8-chann el (7 .1) audio subsystem and tw o S/P D IF di gital aud i o outp uts

using the Realtek* ALC882 audio codec.

Legacy I/O controller for diskette drive, serial, parallel, and PS/2 ports

Peripheral Int erf a ce s

LAN Support

BIOS

Expansion

Capabilities

Reference #308823

Four SATA 1.5/3.0 Gb/s ports

One Pa rallel A TA IDE interface with UDMA 33, ATA-66/100 support

Six Universal Serial Bus (USB) 2.0 ports

PS/2-st yl e k e yb o ard and PS/2 m ouse (6-pin mini-DIN) connectors

One VGA connector provides access to integrated graphics

Six audi o con nectors (Line-in, Li n e- ou t, MIC-in, Sur round L/R, Surround

L/R Rear, Center) driven by Intel High Definition Audio

Two Audio SPDIF connectors

One parallel port

One disk ette drive int er f ac e

®

Gigabit (10/100/1000 Mbits/s) LAN subsystem using the Intel

82573 E

Gigabit Ethernet Controller

Support for Advanced configuration and power interface (ACPI), plug and

play, and S MBIO S

AMI system BIOS

Two conventional PCI bus connectors

One PCI Express x16 bus add-in card connector

One PCI Express x1 bus add-in card connector

Page 14

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

14

Development Kit F eatures

Hardware Monito r

Subsystem

Hardware monitoring and fan control ASIC

Voltage sense to detect out of range power supply voltages

Thermal sense to detect out of range thermal values

Three fan connectors

Three fan sense inputs used to monitor fan activity

Fan speed control

2.2 Development Kit Hardware Lists

The following hardware is included in the development kit:

• 1x Intel® 945G Express Chipset Development Kit reference board.

• 1x Intel

• 1x Pre-installed CPU fan heat sink

• 2x 512 MByte DDR2 533 unbuffered DIMMs

• 1x Pre-progr amme d and installed fir mware hub

• 1x Pre-installed Type 2032, socketed 3V lithium coin cell battery

• 1x Pre-installed (G)MCH heat sink

• 1x Pre-installed ICH7 heat sink

• Jum per ( for boa rd power-on)

• 1x Intel

®

Pentium® 4 Processor 551 with HT Technology (at 3.4 GHz)

®

945G Express Chipset Development Kit Software CD-ROM

2.3 Software Key Features

The software in the kit was chosen to facilitate development of real-time applications based

on th e components u s ed in the evaluation board. The driver CD included in the kit cont ains

all of the software drivers necessary for basic system functionality under the following

operating systems: Microsoft* Windows* 2000/XP/XP Embedded, and Linux*.

Note: While every car e wa s taken to en s ure the lat es t version of drivers were pr ovi d ed on the

enclosed CD at t ime of publi c ation, newer revision s m ay be available . Updated dri ve rs for

Intel components can be found at: http://developer.intel.com/design/intarch/devkits.

For all th ird party components, pl ease conta ct the appropriate vendor for updated drivers.

Note: Software in the kit is provided free by th e ve ndor an d is only lic ensed for evalu ation

purposes.

Refer to the documentation in the evaluation kit for further details on any terms and

conditions that may be applicable to the granted licenses. Customers using the tools that

work with Microsoft products must license those products. Any targets created by those

tools sh ould also have a ppropria te li c enses. Software included in t he kit is su bj e ct to

change. Refer to http://developer.intel.com/design/intarch/devkits for details on addition al

software from oth e r third- pa rt y vendors.

2.3.1 AMI* BIOS

This developmen t kit ships pre-installe d with AMI BI O S pre-boot fir mware from AMI.

AMI BIOS provides an industry-standard BIOS platform to run most standard operating

systems, including Windows 2000/XP/XP Embedded, Linux, and others.

Reference #308823

Page 15

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

15

Development Kit F eatures

2.4 Processor Features and Operation

The foll o wi ng sect ion provid es a detail ed view at processor features and oper ation.

2.4.1 Intel® Pentium® 4 Processor 551

The main differ en t between the Pentium 4 process or 550 and the 551 is th at the 551

supports Intel

®

Extended Memory 64 Technology (EM64T), while the 550 does not. The

rest of the features are th e s ame.

®

The Intel Pentium 4 processor 551 supports Intel

(EM64T ) as an enhan cement to the IA-32 Intel

Extended Memory 64 Technology

®

Architectur e. Th is enhan cement enabl es

the processor to execute operating systems and applications written to take advantage of

EM64T features. With appropriate 64-bit supporting hardware and software, platforms

based on an Intel processor supporting EM64T can use extended virtual and physical

memory.

In addition to supporting all the existing Streaming SIMD Extensions 2 (SSE2), there are

13 new instructions that further extend the capabilities of Intel processor technology. These

new ins tructions, called Str eaming SIM D Extensions 3 (SSE3), enhance the performance

of optimized applications for the digital home such as video, image processing, and media

compression technology.

®

The pr ocessor’ s Intel NetBurst

microar ch itecture front side bus uses a s p lit-tr ansaction,

deferred reply protocol. The Net Bu rst micr oarchitecture F SB u ses s ource-s yn ch ronou s

transfer ( S ST) of a ddress and data to improve p e rformance by transferring data four tim e s

per bus clock. Along with the 4x data bus, the address bus can deliver addresses two times

per bus clock and i s r e ferred to as a “dou ble-clocked ” or 2x address bus. Features of the

processor include:

• Binary compatible with applications running on previous members of the Intel

microp rocessor line

• NetBurst microarchitecture

• System bus frequency at 533/800 MHz

• 775-Land LGA Package

• Supports EM64T Technology

• Rapid Ex ecu tion Eng ine: ari th metic log ic units ( A LUs) run at twi ce the processor

core freq uenc y

• Supports Hyper-Threading Technology (HT Technology)

• Hyper Pipelined Technology

⎯ Advance Dyna mic Execution

⎯ Very deep out- of-order execution

• Enhanced branch predi ction

• 16 KByte Level 1 data cache

• 1 MByte Adva nced Transfer Ca che (on- d ie, full - s p eed Level 2 (L2) cache) with 8-

way associ ati vely and Err or C or rectin g C od e ( ECC)

• 144 Streaming SIMD Extensions 2 (SSE2) and 13 Streaming SIMD Extensions 3

(SSE3) instructions.

• Enhanced floating point and multimedia unit for enhanced video, audio, encryption,

and 3D performance

• Power ma n agement capabilit ies

Reference #308823

Page 16

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

16

Development Kit F eatures

⎯ System Management mode

⎯ Multiple low-power states

• Optimized for 32-bit applications running on advanced 32-bit operating systems

2.4.2 Intel® Celeron® D Processor 341

Note: This processor is not available in this development kits

®

The Int el

with efficient power usage. It is binary compatible with previous Intel Architecture

processors. Featur es of the process or include:

• Binary compatible with applications running on previous members of the Intel

• NetBurst microarchitecture

• Support EM64T Technology

• System bus frequency at 533 MHz

• Rapid Ex ecu tion Engine: Ar ithmeti c Log ic Units (ALUs) run at twice the processor

• Hyper Pipelined Technology

• Enhanced branch predi ction

• 16 KByte Level 1 data cache

• 256 KByte Advanced Transfer Cache (on-die, full-speed Level 2 (L2) cache) with 8-

• 144 Streaming SIMD Extensions 2 (SSE2) and 13 Streaming SIMD Extensions 3

• Power Management capabilities

• Optimized for 32-bit applications running on advanced 32-bit operating systems

Celeron® D Processor provid es ex cep tion al value and balanced performan ce

microp rocessor line

core frequency.

⎯ Advance Dyna mic Execution

⎯ Very deep out- of-order execution

way associ ati vely and Err or C or rectin g C od e ( ECC)

(SSE3) instructions.

⎯ System Management mode

⎯ Multiple low-power states

2.5 Intel® 945G Express Chipset Features and

Operation

The Intel 945G Express Chip s e t platfor m is de s ign e d base d on the 32- bit IA -32 Intel®

Architecture.

The MCH connects t o the processor as sh own in Figure 1. The prim ary role of an M C H in

a system is to manage the flow of information between its interfaces: the processor

inter face (FSB), the system memor y interfa ce ( D RAM controll er), the integrated graphics

interface, the extern al graph ics inter face (PCI Express) , and th e I/ O con troll er th rough the

DMI int erface. Th is inclu des arbitrating bet we en the four inter fa ces when ea ch initia tes

transactions. The ICH7 will provide extensive I/O support. The functions and capabilities

include PCI Express, PCI, Serial ATA, USB, IDE, and much more.

Reference #308823

Page 17

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

17

Development Kit F eatures

2.5.1 Intel® 945G Memory Controller Hub ((G)MCH)

The Int el® 945G Express Chipset (G)MCH provides the processor interface optimized for

Intel Pentium 4 Processors, system memory interface, DMI, and internal/external graphics.

It provides flexibility and scalability in graphics and memory subsystem performance. The

following sections describe the reference board’s implementation of the Intel 945G Express

Chipset (G)MCH features.

• 1202 FCBGA package (34 mm x 34 mm)

• 533/800 MHz processor system bus

• 32-bit host bus addressin g

• 12 deep in -order qu eu e

• Processor support for the Pentium 4 Processor with HT Technology in the 775-Land

LGA Package and th e Celeron D Processor .

• System memory controller (DDR2 implemented)

⎯ Supports Dual Channel or Single Channel operation

⎯ Four DIMM slots (2 DIMM per channel)

⎯ DDR2 533/667 MHz

• Dir ect Media Interface (D M I )

®

• Integrated graphic s based on the Inte l

⎯ Directly supports on-board VGA connector

⎯ Supports resolutions up to 2048 x 1536 @ 75 Hz refresh.

• SDVO interface via Media Expansion Card connector provides maxim um displa y

flexibility

⎯ Operates in Single Chan nel an d Dua l Ch an nel modes.

⎯ Flat panels up to 2048x1536 @ 60 Hz or digital CRT/HDTV at 1920x1080

@ 8 Hz.

⎯ Dual independent display options with digital display.

Graphics Media Accelerator 950

2.5.1.1 System Memory

The customer reference board supports DDR2 533/667 MHz main memory. Four 240-pin

DIMM connectors (two per channel) on the board support unbuffered, non-ECC, single and

double-sided DDR2 400/533 MHz DIMMs. These DIMMs provide the ability to use up to

1 Gbit technology for a maximum of 4 GBytes system memory.

The syst em memory control l er will operate in th ree modes: S ingle Ch an nel, Dual Ch an nel,

and Virtual Single Channel. Best performance is obtained in Dual Channel mode. In order

to run in Dual Channel mode, both channels must contain the same total amount of

memory. It is not necessary to have identical DIMM configurations. For more information

on how to configure the system memory, refer to Section 3.3.1, “Memory Configurations.”

2.5.1.2 Direct Media Interface (DMI)

The Int el 945G Express MCH’s Direct Med ia Interface (DMI) provides a hi gh-speed bi directional chip-to-chip interconnect for communication with the Intel

(not included with the development kit).

2.5.1.3 PCI Express* x16 Graphic Interface

The (G)MCH contains one 16-lane (x16) PCI Express port intended for an external PCI

Expr ess graphi cs card. The P CI Ex press port is compl ian t to the PC I Ex press Base

Reference #308823

®

ICH7 or ICH7R

Page 18

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

18

Development Kit F eatures

Specification, Revision 1.0 a. The x16 port operates at a fr eq uency of 2.5 G bi ts/s on each

lane while employing 8b/10b encoding, and supports a maximum theoretical bandwidth of

4 GBytes/s in each direction. The 82945G (G)MCH multiplexes the PCI Express interface

with two Intel

®

SDVO ports. Features of the (G)MCH include:

• One 16- lane PCI Express p or t in tended for Graphics Attach, compatible t o the PCI

Express Base Specification, Revision 1.0a.

• A base PCI Express frequency of 2.5 Gbits/s only.

• Raw bit-rate on th e data pi ns of 2 .5 Gbi ts/ s , resulting in a real ba ndwidth per pair of

250 MBytes/s given the 8b/10b encoding used to transmit data across this interface.

• Maxim u m theoretical realized bandwidth on the int erface of 4 GB ytes/s in each

direction simultaneously, for an aggregate of 8 Gbits/s when x16 PCI Express

extended configuration space. The first 256 bytes of configuration space is aliased

directly to the PCI compatibility configuration space. The remaining portion of the

fixed 4 KByte block of memory-mapped space above the first 256 bytes (starting at

100h) is known as ext ended con fi g ur ation space.

• PCI Express Enhanced Addressin g Mechani sm. This mechanism acces s es the device

configuration space in a flat memory mapped fashion.

• Automatic discovery, negotiation , and training of link out of reset.

• Supports traditional PCI style traffic (asynchronous snooped, PCI ordering).

• Supports traditional AGP style traffic (asynchronous non-snooped, PCI Express-

relaxed ordering).

• Hierarchical PCI-com plian t configuration mechani s m for downst ream devices (i.e.,

normal PCI 2.3 Configuration space as a PCI-to-PCI bridge).

• Supports “static” lane numbering reversal. This method of lane reversal is controlled

by a hard ware reset s trap, and reverses both th e recei v ers and transmitters for all

lanes (e.g., TX15->TX0, RX15->RX0). This method is transparent to all external

devices and is different than lane reversal as defined in the PCI Express

specification. In particular, link initialization is not affected by static lane reversal.

2.5.1.4 Intel® Graphics Media Accelerator 950 (Intel® GMA950)

The 82945G (G)MCH provides an integrated graphics device (IGD) delivering cost

competitive 3D, 2D, and video capabilities. The (G)MCH contains an extensive set of

instructions supporting:

• 3D oper ations

• Block Le vel Tran sfer (BLT) an d Stretch BLT op er ation s

• Motion compensation, overlay, and display control

The (G)MCH’s video engines support video conferencing and other video applications.

The (G)MCH does n ot support a dedicated local graphics mem ory interface; it may only be

used in a UMA configuration. The (G)MCH also has the capability to support external

graphics accel erat or s via the PCI Express Gra phics ( PE G) port but cannot work

concurrent ly with the integrated graph ics device.

High bandwidth access to data is provided through the system memory port. The (G)MCH

also pr ovi d es 3D har d ware accelerati on for BLTs. The 2D BLTs are cons i dered a special

case of 3D tr ansfer s and use the 3 D acceleration. The BLT engin e provides the abili ty to

copy a source block of data to a destination and perform raster operations (e.g., ROP1,

ROP2, an d ROP3) on th e data us i ng a p attern, and/or another d e s tination. Pe rforming the s e

comm on ta sks in har dware redu c e s proce ssor loa d, an d t hus im proves per forman c e .

Reference #308823

Page 19

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

19

Development Kit F eatures

2.5.1.5 Analog and Serial Digital Video Out (SDVO) Displays

The (G)MCH provides interfaces to a progressive scan analog monitor and two SDVO

ports (multiplexed with PCI Express x16 graphics port signals) capable of driving an MEC

card. The digital disp la y chann el s are ca pable of driving a variety of SDVO devices (e.g.,

TMDS, TV-Out). Note that SDVO onl y works with the int egrated graphics device (IGD).

The MEC card adds Video-In capabilities. The (G)MCH provides two multiplexed SDVO

port s that are ca pa ble of dri ving up to 200 MHz p ixel clock each. Th e ( G ) MCH ca n make

use of th ese digit al displa y ch an nels via a media expansion card.

The (G)MCH SDVO ports can each support a single-channel SDVO device. If both ports

are active in sin g le-channel mode, they can have different di splay ti ming and da ta.

Alternatively, the SDVO ports can be combined to support dual channel devices,

supporting higher reso lutions and ref resh rates . The (G)MCH is complia nt wit h DVI

Specification 1.0. Wh en com bined wi th a D VI-compliant exter nal d evi ce and conn ector,

the (G) M C H has a high-s p eed inter fa ce to a digital displ ay (e.g., fla t panel or d ig ital CRT ).

The (G)MCH supports Hot Plug and Display for the PCI Express x16 graphics port. This is

not supported for MEC card s. Featur es of the (G)MCH SDVO incl ud e:

• SDVO ports support ed in sin gle, sin gle-combined, or dual operation modes

• Analog display support

• 400 MHz integrated 24-bit RAMDAC

• Up to 2048x1536 @ 75 Hz refresh

• Hardware color cursor support

• DDC2B-compliant interface

• Dual independent display options with digital display

• Mult ip lexed dig ital display channels ( s u pp orted with MEC card)

• Two channels multiplexed with PCI Express port

• 200 MHz dot clock on each 12-bit interface

• Can com bine two chan nels to for m one larg er interface

• Supports flat panels up to 2048x1536 @ 60 Hz or digital CRT/HDTV at 1920x1080

@ 85 Hz

• Supports Hot Plug and Display

• Supports TMDS transmitte rs or TV-Out encoders

• MEC card utilizes PCI Express graphics x16 connector

2

• Three d isplay control in terfaces ( I

C/DDC) multiplexed on PCI Express port

2.5.2 Intel® I/O Controller Hub 7 (ICH7)

The ICH7 provides ex tensive I/O s upport. The followi ng su b-sect ion s provi de an overview

of the ICH7 capabilities.

Direct Media Interface

Dir ect Media Interface (D M I ) is the chip- to-chip connecti on between the Memory

Controller Hub / Graphics Memory Controller Hub ((G)MCH) and I/O Controller Hub 7

(ICH7). This high-sp eed interface int egrates a dvanced priority- based servicing, which

allows concurrent traffic and true isochronous transfer capabilities. Base functionality is

completely software-transparent, permitting current and legacy software to operate

normally.

Reference #308823

Page 20

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

20

Development Kit F eatures

PCI Express* Interface

The ICH7 has 4x PCI Express root ports (ports 1-4), supporting the PCI Express Base

Specification, Revision 1.0 a . PCI E xpre s s root ports 1- 4 ca n be st atically con figu red as four

x1 ports or ganged together to form one x4 port. Each root port supports 2.5 Gb/s

bandwidth in each direction (5 Gb/s concurrent).

Serial ATA (SATA) Controller

The ICH7 has an integrated SATA host controller that supports independent DMA

operation on four ports and supports data transfer rates of up to 3.0 Gb/s (300 MB/s). The

SATA controller for this development kit contains the legacy mode using I/O space

operation.

The ICH7 supports the Serial ATA Specification, Revision 1.0a. The ICH7 also supports

optional sections of the Serial ATA II: Extensions to Serial ATA 1.0 Specification,

Revision 1. 0.

IDE Interface (Bus Master Capability and Synchronous DMA Mode)

The fast IDE interface supports up to two IDE devices providing an interface for IDE hard

disks and ATAPI devices. Each IDE device can have independent timings. The IDE

interface supports PIO IDE transfers up to 16 MB/s and Ultra ATA transfers up to 100

MB/s. I t d oes not con s um e any legacy DMA resources. The IDE int er face int egrates

16x32-bit buffers for optimal transfers.

The IC H7’ s I D E system con tains a single, in d ependent IDE sign al channel that can be

electrically isolat ed . There are integr ated ser ies resis tors on th e data and con trol lines.

PCI Interfac e

The IC H7 PCI interface provides a 33 MHz, Revision 2.3 imp lement ation. The ICH7

integrates a PC I arbiter that supp or ts up to si x ex ternal P CI bus masters in addition to the

internal ICH7 requests. This allows for combinations of up to six PCI down devices and

PCI slots.

Low Pin Count (LPC) Interface

The IC H7 implements an LPC In terface as d es cribed in th e LP C 1 . 1 S p ecificat ion. The

LPC bridge function of the ICH7 resides in PCI Device 31:Function 0. In addition to the

LPC bridge interface function, D31:F0 contains other functional units including DMA,

interrupt controllers, timers, power management, system management, GPIO, and RTC.

Serial Peripheral Interface (SPI)

The IC H7 implements an SPI In terface a s an alternat ive interfa ce for th e BI OS fl ash

device. An SPI fla sh device can be used as a r ep lacement for the firmwa re hub.

Uni ver sal Se r ial Bus ( U SB) Con trol ler

The IC H7 contains an Enhanced Host Controller Interface (EHCI) host controller that

supports USB Hi-Speed signaling. Hi-Speed USB 2.0 allows data transfers up to 480 Mb/s,

which is up to 40 times faster than full-speed USB. The ICH7 also contains four Universal

Host Controller Interface (UHCI) controllers that support USB full-speed and low-speed

signali ng.

The ICH7 supports eight USB 2.0 ports. All eight ports are Hi-Speed, full-speed, and lowspeed cap able. I CH7’s port-rout ing logi c d etermin es whether a USB por t is controlled by

one of th e UHCI controller s or b y th e EHCI controll er.

Reference #308823

Page 21

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

21

Development Kit F eatures

GPIO

Various general purpose inputs and outputs are provided for custom system design. The

number of inputs and outputs varies depending on ICH7 configuration.

System Managemen t Bus (S MBus 2.0 )

The IC H7 contains an SMBus host inter face that a llows the processor to commun icate wi th

SMBus slaves. This interface is compatible with most I

are implement ed .

The IC H7’ s SM Bu s host controll er provides a mechani sm for the processor t o in i tiate

communications with SMBus peripherals (slaves). Also, the ICH7 supports slave

functionality, including the Host Notify protocol. Hence, the host controller supports eight

comman d protocols o f t he SMBus interface (see the System Managem ent Bus

Specification, Version 2.0): Quick Command, Send Byte, Receive Byte, Write Byte/Word,

Read Byte/Word, Process Call, Block Read/Write, and Host Notify.

Intel® Active Management Technology

Intel® AMT is the next generation of client manageability via the wired network. Intel®

AMT is a set of advanced manageability features developed as a direct result of IT

customer feedba ck gained throu gh Intel market resea rch.

2.5.3 Power Management

Power management is implemented at several levels, including:

• Software support through Advanced Configuration and Power Interface (ACPI)

• Hardware support:

⎯ Power conn ector

⎯ Fan connect ors

⎯ LAN wake capabilities

⎯ Instantly Available PC technology

⎯ Resume on Ring

⎯ Wake from USB

⎯ Wake from PS /2 Devi c e s

⎯ Power Management Event signal (PME#) wake-up support

2

C devices. Special I2C commands

2.5.3.1 Advanced Configuration and Power Interface (ACPI)

ACPI gives the operating system direct control over the power management and Plug and

Play functions of a comp uter. Th e u s e of A CPI with t his board requ ires an operating

syste m th at provide s full ACPI support . ACPI fe atures includ e :

• Plu g and Play (incl udin g bus and device enum eration )

• Power manag ement c ontrol of indi vidu al devices, ad d-in boards (some ad d-in boards

may require an ACPI-aware driver), video displays, and hard disk drives

• Methods for achieving less than 15-watt system operation in the power-on/standby

sleepi ng stat e

• A soft-o ff feature that en ables th e operating system to po wer-off the compu ter

• Support for multiple wake-up events

• Support for a front panel power and sleep mode switch

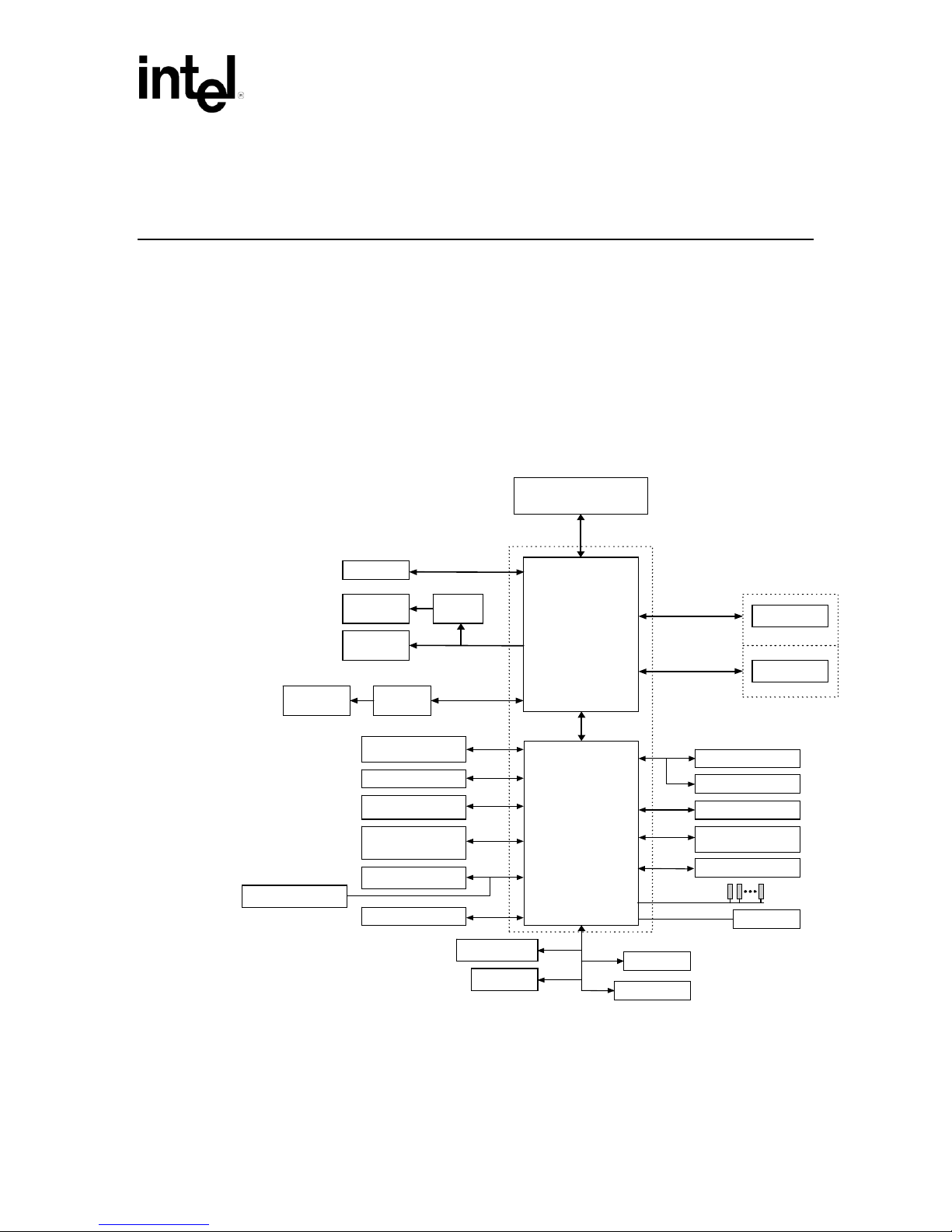

Table 5 lists the system states based on h ow long the power switch is pressed, depending

on how ACPI is config ured with an ACPI-a ware operating system .

Reference #308823

Page 22

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

22

Development Kit F eatures

Table 5 Effects of Power Switch Pressing Duration

If the system is in this state… …and the power switch

Off

(ACPI G2/ G5 – soft off)

On

(ACPI G0 – working state)

On

(ACPI G0 – working state)

Sleep

(ACPI G1 – sleeping state)

Sleep

(ACPI G1 – sleeping state)

is pressed for

Less than 4 seconds Power-on

Less than 4 seconds Soft-off/Standby

More than 4 secon ds Fai l safe power-off

Less than 4 seconds Wake-up

More than 4 seconds Power-off

…the system enters this

(ACPI G0 – working state)

(ACPI G1 – sleeping state)

(ACPI G2/ G5 – soft off)

(ACPI G0 – working state)

(ACPI G2/ G5 – soft off)

state

Reference #308823

Page 23

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

23

Setting Up the Develop ment Kit

3 Setting Up the De velopment Kit

This section identifies the evaluation kit basic board’s set up and operation. Please refer to

Chapter 4 for the board layout, jumper setting location , and the component reference

designator.

3.1 Overview

The e valu a tion boar d c onsists of a bas e boar d populated wit h one Intel® Pentium® 4

Process or 551 with HT Technology

board components and peripheral connectors.

Note: The evaluation board is shipped as an open system allowing for maximum flexibility in

chang ing hardwa re confi g ur ation and p er ipherals. Since the board i s not in a protective

chas sis, tak e ex tr a precaution when h andling and operating the s ystem .

†

, the Intel® 945G Express Chipset, and other system

3.2 Additional Hardware and Software Required

Before you set u p an d c onfigur e your e valu a tion board, you may want to gather some

additional hardware and software.

VGA Mon itor

You can use any standard VGA or multi-resolution monitor. The setup instru ct i on s in this

section assume that you are using a standard VGA monitor.

Keyboard

You will need a PS/2 style or USB keyboard.

Mouse

You will need a PS/2 style or USB mouse.

Hard Drives, Floppy Drives, and Compact Disk Drives

You can connect u p t o four SATA dr ives and t wo IDE devices (mast er and slave) t o the

evaluation board. A floppy drive or compact disk drive may be used to load the OS. No

drives or cables are in clu d ed in the kit; the user mu s t provide them as necessary. All the

storage devices may be attached t o the board si multaneou s ly.

Video Adapter

Integrate d video is pr ovided on the back pan e l of the system board. Alter nat e ly, us e rs ca n

choose to use any standard PCI video adapter or use the included MEC video adapter (not

inclu ded in this development kit). It is th e u s er ’s responsibility to ins t all the ap propria te

drivers and correctl y confi gure any software for video adapters used. Check th e BIO S for

the proper video settings.

Note: The MEC connector is similar to the industry standard PCI Express x16 connector.

Reference #308823

Page 24

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

24

Setting Up the Develop ment Kit

Power Supply

The evaluation board requires the use of a standard desktop ATX power supply with a

minimum of 250 W output. The power supply selected must also provide an auxiliary 2x2

12 V connector.

Other Devices and Adapters

The evaluation board functions much like a standard desktop computer motherboard. Most

PC-compatible peripherals can be attached and configured to work with the board.

3.3 Setting up the Evaluation Board

Once the hardware descri bed in the pr evi ou s s ection is gath ered, follo w the steps bel ow to

set up the evaluation board. This manual assumes you are familiar with the basic concepts

involved in installing and configuring PC hardware.

Note: To locate items discussed in the procedure below, please refer to Chapter 4.

1. Cr eate a safe work environment. Ma k e sure you are in a static-free envi ronmen t

before removin g any compon ents fr om th eir anti - st atic packag ing. Th e eva luati on

board is susceptible to electrostatic discharge damage, and such damage may cause

pr oduct failure or unpre dictable operat ion.

2. In s p ect the contents of your k it. Check for damag e th at may have occurred d ur ing

shipment. Contact your sales representative if any items are missing or damaged.

Caution: Connecting the wrong cable or reversing the cable can damage the evalu ation board and

may dama ge the device b eing connected. Since the board is n ot in a protect ive chas s is, use

caution when connecting cables to this product.

Caution: Do not connect the power supply to the board until all other steps have been completed.

The last step in the installation process must be to plug the AC cord to the power supply.

Standby voltage is constantly applied to the board. Therefore, do not insert or remove any

hardware unless the system is unplugged.

Note: The eval uation board is a microATX for m fa ctor. An AT X chassis may be used if a

prot ected environmen t is desir ed.

3. Ch eck the jumper s etting s (r efer to Section 4.3.1). Jump er J6J3 is used to cl ear the

CMOS memory. Make sure this jumper is set for normal operation.

4. Popul ate har d wa re component to the evaluation board. Make s ure the fol lowing

hardware is populated on your evaluation board. Please refer to Section 3.3.1 for

more detail on the memory configurations.

®

a. 1x 3.4 GHz Intel

Pentium® 4 Processor 551

b. 1x CPU thermal solution

c. At least one 256 MByte DDR2 533 DIMM or 1x 256 MByte DDR2 400 DIMM

5. Inst all CPU fa n heat sink.

6. Install a SATA or IDE hard disk drive.

7. Connect an y ad d itional s torage devices to th e eva luati on board.

8. Connect a floppy dri ve (op tiona l ).

Reference #308823

Page 25

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

25

Setting Up the Develop ment Kit

a. Insert a flopp y cable int o J3 J 1 (be sure to orient pin 1 corr ect ly).

b. Conne ct the ot her end of the ribbon cable to the flop py dri ve .

c. Connect a power cable to the floppy dr ive.

9. Connect the keyboard and mouse.

10. Connect a PS/2-style or USB mouse and keyboard (see Figure 3 on page 29 for

connector locations).

Note: J1A1 (on the baseboard) is a stacked PS/2 connect or. The bottom conn ector is for th e

keyboard and the top is for the mouse.

11. Connect the monitor through the VGA connector.

12. (Optional) Install the MEC card.

13. (Optional) Connect the audio speakers. Please refer to Section 3.3.2 for more detail

on audio setu p.

14. (Optional) Connect an Eth er net cabl e. Please refer to Sect ion 3.3. 3 for more detail

on the LAN s ubsys tem.

15. Connect the power supply.

a. Connect a standard ATX power supply to the evaluation board. Make sure the

power supply is not plugged into electrical outlet turned off).

b. Insert the ATX board connector of the power supply cord into the J2J1 power

supply header on the evaluation board.

c. Insert the +12 V p ower connector of the power supply cord into the J 3 B2 +1 2 V

header on t he evalu ation board.

d. After connecting the power supply board connectors, plug the power supply

cord into the el ectrica l ou tlet.

16. Power up the board. Use jumper on J7J3, pin 6-8 (Section 4.1.2.3) to power up the

boar d. Tur n on the power t o th e monitor and evaluation board . Ensur e th at the fan

sin k on the proce s sor is opera t ing.

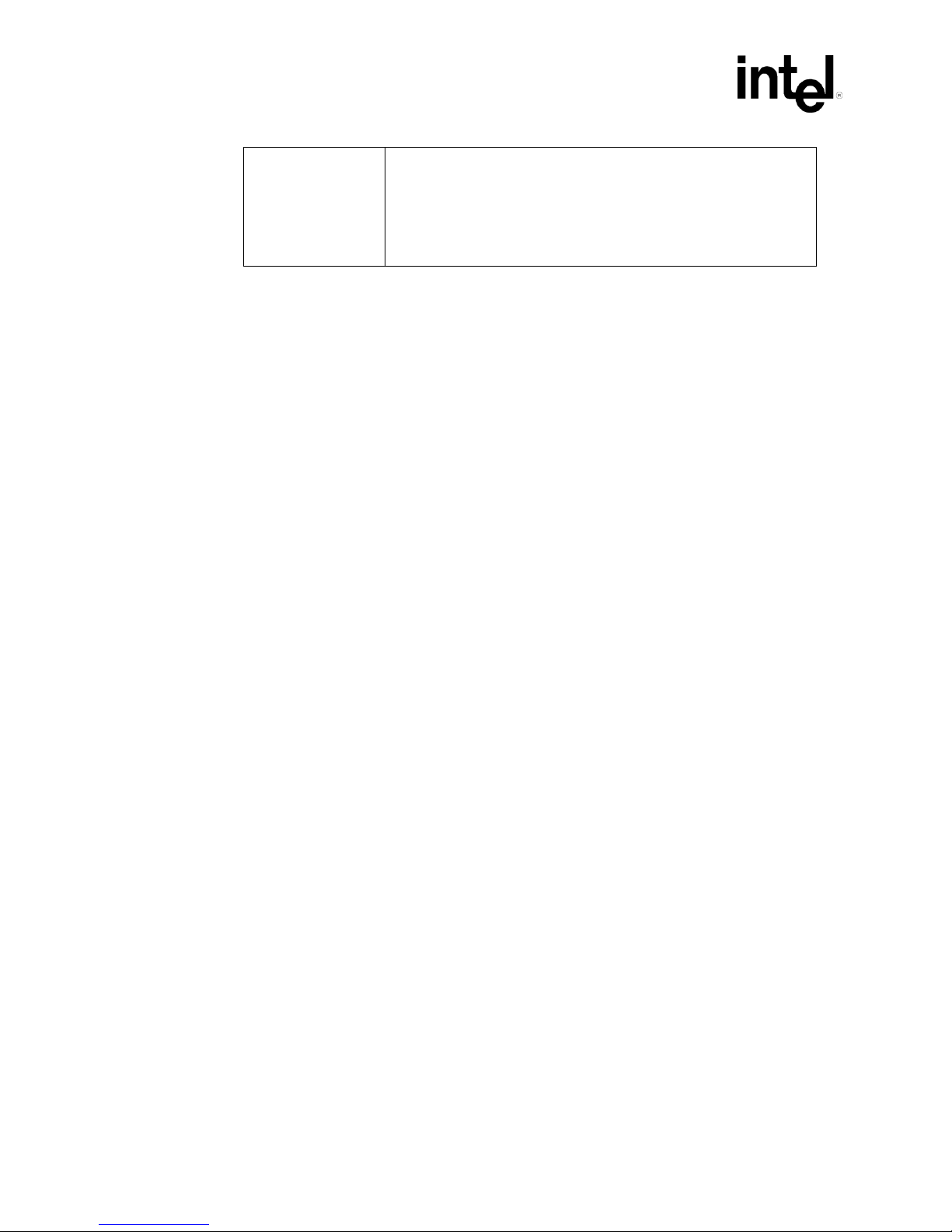

3.3.1 Memory Configurations

The Int el® 945G MCH supports two types of memory organization:

Dual Channel (Interleaved) Mode

This mode offers the highest throughput for real-world applications. Dual channel mode is

enabled when the installed memory capacities of both DIMM channels are equal.

Technology and device width can vary from one ch annel t o th e other but th e installed

memory capacity for each channel must be equal. If different speed DIMMs are used

between channels, the slowest memory timing will be used.

Single Channel (Asymmetric) Mode

This mode is equivalent to single channel bandwidth operation for real-world applications.

This mode is used when only a single DIMM is installed or the memory capacities are

uneq ua l. Techn ol ogy and devi ce wi d th can vary from on e chan nel to the other. I f d ifferen t

speed DIMMs are used between chann el s, the slowest memory timing will be used.

Figure 2 illustrates the memory channel and DIMM configuration.

Reference #308823

Page 26

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

26

Setting Up the Develop ment Kit

Reference #308823

Page 27

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

27

Setting Up the Develop ment Kit

Figure 2 Memory Channel and DIMM Configuration

3.3.1.1 Dual Channel (Interleaved) Mode Configurations

Figur e 3 shows a dua l ch annel con figuration using two DIMMs. In th is exampl e, the

DIMM 0 sockets of both channels are popu lated with identical DIMMs.

Figure 3 Dual Channel (Interleaved) Mode Configu rat ion wi th 2x DIMM s

Figur e 4 shows a dua l ch annel con figuration using 3 DIMMs. In th is example, the

combined capaci t y of the two DIMMs in Chann el A equal the capacity of the single DIMM

in the DI M M 0 socket of Chan nel B.

Figure 4 Dual Channel (Interleaved) Mode Configu rat ion wi th 3x DIMM s

Figur e 5 shows a dua l ch annel con figuration using 4 DIMMs. In th is example, the

combined capacity of th e 2 x DI M M s in Chann el A eq ua ls the combined cap acity of th e 2 x

DIMMs in Channel B. Also, the DIMMs are matched between DIMM 0 and DIMM 1 of

both chan nels.

Reference #308823

Page 28

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

28

Setting Up the Develop ment Kit

Figure 5 Dual Channel (Interleaved) Mode Configu rat ion wi th 4x DIMM s

3.3.1.2 Single Channel (Asymmetric) Mode Configura tions

Figur e 6 shows a single channel configuration using 1x DIMM. In th is exampl e, only the

DIMM 0 socket of Chan nel A is popul ated. Chan nel B is not p op u lated.

Figure 6 Single Channel (Asymmetric) Mode Configuration with 1x DIMM

Figur e 7 shows a sing le channel config ur ation using 3x DIMMs. In this example, th e

combined capacity of th e 2 x DI M M s in Chann el A does not equal the capa city of th e single

DIMM in the DIMM 0 socket o f C h an nel B.

Figure 7 Single Channel (Asymmetric) Mode Configuration with 3x DIMMs

3.3.2 Audio Subsystem Configurations

The board supports the Intel® High De fin ition Audio subsyst em bas e d on the Rea ltek

ALC882 audio codec. The ALC882 series provides 8 channels of DAC (Digital to Analog

Converter) that simultaneously support 7.1 sound playback.

Reference #308823

Page 29

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

29

Setting Up the Develop ment Kit

The board contains audio connectors on th e ba ck panel and two chann els of indep endent

stereo sound output at t he si de of the board. The funct ions of the back panel a udio

connectors are dependent on the 8-channel audio subsystem, as describe in Section 3.3.2.2.

For more information such as specification, schematic, layout and driver on the ALC882

audio codec, please refer to the Realtek web site: www.realtek.com.tw.

3.3.2.1 8-Channel (7.1) Audio Subsystem

Figure 8 shows the back panel audio connector for the 8-Channel (7.1) Audio Subsystem.

The 8- ch annel (7.1) audi o subsystem includes the following :

®

• Intel

• Realtek ALC882 audio codec

Figure 8 Back Panel Audio Conn ect or Options for 8-channel Audio Sub syst em

82801G I/O Controller Hub 7 (ICH7)

Table 6 lists t he back panel (a udi o) tasks.

Table 6 Back Panel T ask (Audio)

Symbols Task

C S/PDIF Out

F S/PDIF In

K Surround Rear L/R

J Surround L/R

M Center / LFE

O Line In

P Front / Line Out

N Mic In

3.3.3 LAN Subsystem Configurations

The LAN subsystem consists of the following:

• Physica l layer in terfa ce d evi ce. The d evelopment kit includes the follo wi ng LAN

device:

⎯ Intel

• RJ-45 LAN connector with in tegrat ed s tatus LED s.

®

82573E for Gigabit (10/100/1000 Mbits/sec) Ethernet LAN

connectivity

Reference #308823

Page 30

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

30

Setting Up the Develop ment Kit

3.3.3.1 Gigabit LAN Subsystem

The Gigabit (10/100/1000 Mbits/sec) LAN subsystem includes the Intel® 82573E Gigabit

Ethernet Con troller an d an RJ-45 LAN connector with int egr ated sta tus LEDs.

The 82573E controller supports the following features:

• PCI Expr e s s link

• 10/100/1000 IEEE 802.3 compliant

• Compliant to IEEE 802.3x flow control support

• TCP, IP, UDP checksum offload

• Transmit TCP segmentation

• Advanced packet filtering

• Full device driver compatibility

• PCI Express Power Management support

• Jumbo frame support

®

• Intel

• Alert Standard Format (ASF) 2.0

Active Management Technology

3.3.3.2 RJ-45 LAN Connector with Integrated LEDs

Two LEDs are bu ilt into the RJ-45 LAN c onne ctor (as shown in Figure 9). Ta ble 7

describe s th e L ED states when the board is power ed up and the Gig abit LAN subsystem is

operating.

Figure 9 LAN Connector LED locations

Table 7 LAN Connector LED Status

LED Color LED State Condition

Left

Right

Green

N/A Off 10 Mbits/sec data rate is selected.

Green On 100 Mbits/sec data rate is selected.

Yellow On 1000 Mbits /sec dat a r ate is s elec ted.

Off LAN link is not established.

On LAN link is established.

Blinking LAN activity is occurring.

Reference #308823

Page 31

Intel® 945G Express Chipset Develop m ent Kit User’s Manual

31

Setting Up the Develop ment Kit

3.3.4 Intel