Intel 925 - Pentium D 925 3.0GHz 800MHz 4MB-Cache Socket 775 CPU, 925X, 925XE, 82925X, 82925XE Datasheet

Page 1

R

Intel® 925X/925XE Express

Chipset

Datasheet

For the Intel® 82925X/82925XE Memory Controller Hub (MCH)

November 2004

Document Number: 301464-003

Page 2

R

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY

ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN

INTEL’S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL

DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR

WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT,

COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining

applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

®

The Intel

specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Ω Look for systems with the Intel® Pentium® 4 Processor with HT Technology logo and also including an Intel® 925, 915, or 910 Express Chipset

(see the product spec sheet or ask your salesperson). Performance and functionality will vary depending on (i) the specific hardware and software

you use and (ii) the feature enabling/system configuration by your system vendor. See www.intel.com/products/ht/hyperthreading_more.htm

information on HT Technology or consult your system vendor for more information.

Φ Intel

drivers and applications enabled for Intel EM64T. Processor will not operate (including 32-bit operation) without an Intel EM64T-enabled BIOS.

Performance will vary depending on your hardware and software configurations. See www.intel.com/info/em64t

details on which processors support EM64T or consult with your system vendor for more information.

Intel and Pentium are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

*Other names and brands may be claimed as the property of others.

Copyright

82925X/82925XE MCH may contain design defects or errors known as errata, which may cause the product to deviate from published

for

®

Extended Memory 64 Technology (Intel® EM64T) requires a computer system with a processor, chipset, BIOS, operating system, device

for more information including

©

2004, Intel Corporation

2 Intel

®

82925X/82925XE MCH Datasheet

Page 3

R

Contents

1

2

Introduction .......................................................................................................................13

1.1

Terminology..........................................................................................................15

1.2

Reference Documents..........................................................................................16

1.3

MCH Overview .....................................................................................................16

1.3.1 Host Interface........................................................................................16

1.3.2 System Memory Interface.....................................................................17

1.3.3 Direct Media Interface (DMI).................................................................18

1.3.4 PCI Express* Graphics Interface..........................................................18

1.3.5 System Interrupts..................................................................................19

1.3.6 MCH Clocking.......................................................................................20

1.3.7 Power Management..............................................................................20

Signal Description.............................................................................................................21

2.1

Host Interface Signals..........................................................................................23

2.2

DDR2 DRAM Channel A Interface.......................................................................26

2.3

DDR2 DRAM Channel B Interface.......................................................................27

2.4

DDR2 DRAM Reference and Compensation.......................................................28

2.5

PCI Express* x16 Graphics Port Signals.............................................................28

2.6

Clocks, Reset, and Miscellaneous.......................................................................29

2.7

Direct Media Interface (DMI)................................................................................29

2.8

Power and Ground...............................................................................................30

2.9

Reset States and Pull-up/Pull-downs...................................................................30

3

4

®

Intel

82925X/82925XE MCH Datasheet 3

Register Description..........................................................................................................35

3.1

Register Terminology...........................................................................................35

3.2

Platform Configuration..........................................................................................37

3.3

General Routing Configuration Accesses............................................................38

3.3.1 Standard PCI Bus Configuration Mechanism.......................................38

3.3.2 Logical PCI Bus 0 Configuration Mechanism.......................................39

3.3.3 Primary PCI and Downstream Configuration Mechanism....................39

3.3.4 PCI Express* Enhanced Configuration Mechanism.............................40

3.3.5 Intel® 82925X/925XE MCH Configuration Cycle Flowchart .................42

3.4

I/O Mapped Registers ..........................................................................................43

3.4.1 CONFIG_ADDRESS—Configuration Address Register ......................43

3.4.2 CONFIG_DATA—Configuration Data Register....................................44

Host Bridge/DRAM Controller Registers (D0:F0) .............................................................45

4.1

Device 0 Function 0 PCI Configuration Register Details .....................................48

4.1.1 VID—Vendor Identification (D0:F0)......................................................48

4.1.2 DID—Device Identification (D0:F0) ......................................................48

4.1.3 PCICMD—PCI Command (D0:F0).......................................................49

4.1.4 PCISTS—PCI Status (D0:F0)...............................................................50

4.1.5 RID—Revision Identification (D0:F0)....................................................51

4.1.6 CC—Class Code (D0:F0).....................................................................51

Page 4

R

4.1.7

MLT—Master Latency Timer (D0:F0)...................................................52

4.1.8 HDR—Header Type (D0:F0) ................................................................52

4.1.9 SVID—Subsystem Vendor Identification (D0:F0).................................52

4.1.10 SID—Subsystem Identification (D0:F0)................................................53

4.1.11 CAPPTR—Capabilities Pointer (D0:F0)...............................................53

4.1.12 EPBAR—Egress Port Base Address (D0:F0) ......................................54

4.1.13 MCHBAR—MCH Memory Mapped Register Range Base Address

(D0:F0)..................................................................................................55

4.1.14 PCIEXBAR—PCI Express* Register Range Base Address (D0:F0) ...56

4.1.15 DMIBAR—Root Complex Register Range Base Address (D0:F0)......57

4.1.16 DEVEN—Device Enable (D0:F0) .........................................................58

4.1.17 DEAP—DRAM Error Address Pointer (D0:F0) (Intel® 82925X Only)...59

4.1.18 DERRSYN—DRAM Error Syndrome (D0:F0) (Intel® 82925X Only)....60

4.1.19 DERRDST—DRAM Error Destination (D0:F0) (Intel® 82925X Only)...61

4.1.20 PAM0—Programmable Attribute Map 0 (D0:F0)..................................62

4.1.21 PAM1—Programmable Attribute Map 1 (D0:F0)..................................63

4.1.22 PAM2—Programmable Attribute Map 2 (D0:F0)..................................64

4.1.23 PAM3—Programmable Attribute Map 3 (D0:F0)..................................65

4.1.24 PAM4—Programmable Attribute Map 4 (D0:F0)..................................66

4.1.25 PAM5—Programmable Attribute Map 5 (D0:F0)..................................67

4.1.26 PAM6—Programmable Attribute Map 6 (D0:F0)..................................68

4.1.27 LAC—Legacy Access Control (D0:F0).................................................69

4.1.28 TOLUD—Top of Low Usable DRAM (D0:F0).......................................70

4.1.29 SMRAM—System Management RAM Control (D0:F0)........................71

4.1.30 ESMRAMC—Extended System Management RAM Control (D0:F0)..72

4.1.31 ERRSTS—Error Status (D0:F0)...........................................................72

4.1.32 ERRCMD—Error Command (D0:F0) ...................................................74

4.1.33 SMICMD—SMI Command (D0:F0) ......................................................75

4.1.34 SCICMD—SCI Command (D0:F0).......................................................76

4.1.35 SKPD—Scratchpad Data (D0:F0) ........................................................76

4.1.36 CAPID0—Capability Identifier (D0:F0).................................................77

5

4 Intel

MCHBAR Registers ..........................................................................................................79

5.1

MCHBAR Register Details ...................................................................................80

5.1.1 C0DRB0—Channel A DRAM Rank Boundary Address 0....................80

5.1.2 C0DRB1—Channel A DRAM Rank Boundary Address 1....................82

5.1.3 C0DRB2—Channel A DRAM Rank Boundary Address 2....................82

5.1.4 C0DRB3—Channel A DRAM Rank Boundary Address 3....................82

5.1.5 C0DRA0—Channel A DRAM Rank 0,1 Attribute .................................83

5.1.6 C0DRA2—Channel A DRAM Rank 2,3 Attribute .................................83

5.1.7 C0DCLKDIS—Channel A DRAM Clock Disable ..................................84

5.1.8 C0BNKARC—Channel A DRAM Bank Architecture ............................85

5.1.9 C0DRT1—Channel A DRAM Timing Register .....................................86

5.1.10 C0DRC0—Channel A DRAM Controller Mode 0 .................................88

5.1.11 C1DRB0—Channel B DRAM Rank Boundary Address 0....................90

5.1.12 C1DRB1—Channel B DRAM Rank Boundary Address 1....................90

5.1.13 C1DRB2—Channel B DRAM Rank Boundary Address 2....................90

5.1.14 C1DRB3—Channel B DRAM Rank Boundary Address 3....................90

5.1.15 C1DRA0—Channel B DRAM Rank 0,1 Attribute .................................90

5.1.16 C1DRA2—Channel B DRAM Rank 2,3 Attribute .................................91

5.1.17 C1DCLKDIS—Channel B DRAM Clock Disable ..................................91

5.1.18 C1BNKARC—Channel B Bank Architecture........................................91

5.1.19 C1DRT1—Channel B DRAM Timing Register 1 ..................................91

®

82925X/82925XE MCH Datasheet

Page 5

R

5.1.20

C1DRC0—Channel B DRAM Controller Mode 0 .................................91

5.1.21 PMCFG—Power Management Configuration ......................................92

5.1.22 PMSTS—Power Management Status ..................................................92

6

7

EPBAR Registers—Egress Port Register Summary........................................................93

6.1

EP RCRB Configuration Register Details ............................................................93

6.1.1 EPESD—EP Element Self Description.................................................94

6.1.2 EPLE1D—EP Link Entry 1 Description ................................................95

6.1.3 EPLE1A—EP Link Entry 1 Address......................................................95

6.1.4 EPLE2D—EP Link Entry 2 Description ................................................96

6.1.5 EPLE2A—EP Link Entry 2 Address......................................................97

DMIBAR Registers—Direct Media Interface (DMI) RCRB ...............................................99

7.1

Direct Media Interface (DMI) RCRB Register Details........................................100

7.1.1 DMIVCECH—DMI Virtual Channel Enhanced Capability Header .....100

7.1.2 DMIPVCCAP1—DMI Port VC Capability Register 1..........................100

7.1.3 DMIPVCCAP2—DMI Port VC Capability Register 2..........................101

7.1.4 DMIPVCCTL—DMI Port VC Control ..................................................101

7.1.5 DMIVC0RCAP—DMI VC0 Resource Capability ................................102

7.1.6 DMIVC0RCTL0—DMI VC0 Resource Control ...................................103

7.1.7 DMIVC0RSTS—DMI VC0 Resource Status.......................................104

7.1.8 DMIVC1RCAP—DMI VC1 Resource Capability ................................104

7.1.9 DMIVC1RCTL1—DMI VC1 Resource Control ...................................105

7.1.10 DMIVC1RSTS—DMI VC1 Resource Status.......................................106

7.1.11 DMILCAP—DMI Link Capabilities ......................................................106

7.1.12 DMILCTL—DMI Link Control..............................................................107

7.1.13 DMILSTS—DMI Link Status...............................................................107

8

Host-PCI Express* Graphics Bridge Registers (D1:F0) .................................................109

8.1

Device 1 Configuration Register Details ............................................................112

8.1.1 VID1—Vendor Identification (D1:F0)..................................................112

8.1.2 DID1—Device Identification (D1:F0) ..................................................112

8.1.3 PCICMD1—PCI Command (D1:F0)...................................................113

8.1.4 PCISTS1—PCI Status (D1:F0)...........................................................114

8.1.5 RID1—Revision Identification (D1:F0)................................................116

8.1.6 CC1—Class Code (D1:F0).................................................................116

8.1.7 CL1—Cache Line Size (D1:F0)..........................................................117

8.1.8 HDR1—Header Type (D1:F0) ............................................................117

8.1.9 PBUSN1—Primary Bus Number (D1:F0)...........................................117

8.1.10 SBUSN1—Secondary Bus Number (D1:F0)......................................118

8.1.11 SUBUSN1—Subordinate Bus Number (D1:F0) .................................118

8.1.12 IOBASE1—I/O Base Address (D1:F0) ...............................................119

8.1.13 IOLIMIT1—I/O Limit Address (D1:F0) ................................................119

8.1.14 SSTS1—Secondary Status (D1:F0)...................................................120

8.1.15 MBASE1—Memory Base Address (D1:F0)........................................121

8.1.16 MLIMIT1—Memory Limit Address (D1:F0).........................................122

8.1.17 PMBASE1—Prefetchable Memory Base Address (D1:F0)................123

8.1.18 PMLIMIT1—Prefetchable Memory Limit Address (D1:F0).................124

8.1.19 CAPPTR1—Capabilities Pointer (D1:F0)...........................................124

8.1.20 INTRLINE1—Interrupt Line (D1:F0) ...................................................125

8.1.21 INTRPIN1—Interrupt Pin (D1:F0).......................................................125

8.1.22 BCTRL1—Bridge Control (D1:F0)......................................................126

8.1.23 PM_CAPID1—Power Management Capabilities (D1:F0) ..................128

®

Intel

82925X/82925XE MCH Datasheet 5

Page 6

R

8.1.24

PM_CS1—Power Management Control/Status (D1:F0)....................129

8.1.25 SS_CAPID—Subsystem ID and Vendor ID Capabilities (D1:F0) ......130

8.1.26 SS—Subsystem ID and Subsystem Vendor ID (D1:F0) ....................130

8.1.27 MSI_CAPID—Message Signaled Interrupts Capability ID (D1:F0)....131

8.1.28 MC—Message Control (D1:F0)..........................................................132

8.1.29 MA—Message Address (D1:F0).........................................................133

8.1.30 MD—Message Data (D1:F0)..............................................................133

8.1.31 PEG_CAPL—PCI Express* Capability List (D1:F0)...........................134

8.1.32 PEG_CAP—PCI Express*-G Capabilities (D1:F0).............................134

8.1.33 DCAP—Device Capabilities (D1:F0)..................................................135

8.1.34 DCTL—Device Control (D1:F0)..........................................................136

8.1.35 DSTS—Device Status (D1:F0)...........................................................137

8.1.36 LCAP—Link Capabilities (D1:F0) .......................................................138

8.1.37 LCTL—Link Control (D1:F0)...............................................................139

8.1.38 LSTS—Link Status (D1:F0)................................................................140

8.1.39 SLOTCAP—Slot Capabilities (D1:F0)................................................141

8.1.40 SLOTCTL—Slot Control (D1:F0)........................................................142

8.1.41 SLOTSTS—Slot Status (D1:F0).........................................................143

8.1.42 RCTL—Root Control (D1:F0) .............................................................144

8.1.43 RSTS—Root Status (D1:F0)...............................................................145

8.1.44 PEGLC—PCI Express*-G Legacy Control.........................................146

8.1.45 VCECH—Virtual Channel Enhanced Capability Header (D1:F0) ......147

8.1.46 PVCCAP1—Port VC Capability Register 1 (D1:F0)...........................147

8.1.47 PVCCAP2—Port VC Capability Register 2 (D1:F0)...........................148

8.1.48 PVCCTL—Port VC Control (D1:F0) ...................................................148

8.1.49 VC0RCAP—VC0 Resource Capability (D1:F0) .................................149

8.1.50 VC0RCTL—VC0 Resource Control (D1:F0) ......................................149

8.1.51 VC0RSTS—VC0 Resource Status (D1:F0)........................................150

8.1.52 VC1RCAP—VC1 Resource Capability (D1:F0) .................................150

8.1.53 VC1RCTL—VC1 Resource Control (D1:F0) ......................................151

8.1.54 VC1RSTS—VC1 Resource Status (D1:F0)........................................152

8.1.55 RCLDECH—Root Complex Link Declaration Enhanced Capability

Header (D1:F0)...................................................................................152

8.1.56 ESD—Element Self Description (D1:F0)............................................153

8.1.57 LE1D—Link Entry 1 Description (D1:F0)............................................154

8.1.58 LE1A—Link Entry 1 Address (D1:F0).................................................155

8.1.59 PEGSSTS—PCI Express*-G Sequence Status (D1:F0)....................155

9

6 Intel

System Address Map......................................................................................................157

9.1

Legacy Address Range......................................................................................158

9.1.1 DOS Range (0h – 9_FFFFh)..............................................................159

9.1.2 Legacy Video Area (A_0000h–B_FFFFh)..........................................159

9.1.3 Expansion Area (C_0000h–D_FFFFh)...............................................160

9.1.4 Extended System BIOS Area (E_0000h–E_FFFFh)..........................161

9.1.5 System BIOS Area (F_0000h–F_FFFFh)...........................................161

9.1.6 Programmable Attribute Map (PAM) Memory Area Details................161

9.2

Main Memory Address Range (1 MB to TOLUD) ..............................................162

9.2.1 ISA Hole (15 MB–16 MB) ...................................................................162

9.2.2 TSEG ..................................................................................................163

9.2.3 Pre-allocated Memory.........................................................................163

9.3

PCI Memory Address Range (TOLUD – 4 GB) .................................................163

9.3.1 APIC Configuration Space (FEC0_0000h–FECF_FFFFh).................164

9.3.2 HSEG (FEDA_0000h–FEDB_FFFFh)................................................165

®

82925X/82925XE MCH Datasheet

Page 7

R

9.3.3

10

FSB Interrupt Memory Space (FEE0_0000h–FEEF_FFFFh) ............165

9.3.4 High BIOS Area ..................................................................................165

9.3.5 PCI Express* Configuration Address Space ......................................165

9.3.6 PCI Express* Graphics Attach............................................................166

9.3.7 AGP DRAM Graphics Aperture ..........................................................166

9.4

System Management Mode (SMM) ...................................................................167

9.4.1 SMM Space Definition ........................................................................167

9.4.2 SMM Space Restrictions ....................................................................168

9.4.3 SMM Space Combinations.................................................................168

9.4.4 SMM Control Combinations................................................................169

9.4.5 SMM Space Decode and Transaction Handling ................................169

9.4.6 Processor WB Transaction to an Enabled SMM Address Space ......169

9.4.7 SMM Access through GTT TLB..........................................................170

9.4.8 Memory Shadowing............................................................................170

9.4.9 I/O Address Space..............................................................................170

9.4.10 PCI Express* I/O Address Mapping ...................................................171

9.4.11 MCH Decode Rules and Cross-Bridge Address Mapping .................171

9.4.12 Legacy VGA and I/O Range Decode Rules .......................................171

Functional Description ....................................................................................................173

10.1 Host Interface.....................................................................................................173

10.1.1 FSB GTL+ Termination.......................................................................173

10.1.2 FSB Dynamic Bus Inversion...............................................................173

10.1.3 APIC Cluster Mode Support ...............................................................174

10.2 System Memory Controller.................................................................................174

10.2.1 Memory Organization Modes..............................................................174

10.3 System Memory Configuration Register Overview ............................................176

10.3.1 DRAM Technologies and Organization..............................................177

10.3.1.1 Rules for Populating DIMM Slots ......................................177

10.3.1.2 System Memory Supported Configurations ......................178

10.3.1.3 Main Memory DRAM Address Translation and Decoding 178

10.3.2 DRAM Clock Generation ....................................................................181

10.3.3 Suspend to RAM and Resume...........................................................181

10.3.4 DDR2 On-Die Termination..................................................................181

10.3.5 DDR2 Off-Chip Driver Impedance Calibration....................................181

10.4 PCI Express*......................................................................................................182

10.4.1 Transaction Layer...............................................................................182

10.4.2 Data Link Layer...................................................................................182

10.4.3 Physical Layer.....................................................................................182

10.5 Power Management...........................................................................................183

10.6 Clocking..............................................................................................................183

11

12

®

Intel

82925X/82925XE MCH Datasheet 7

Electrical Characteristics.................................................................................................185

11.1 Absolute Maximum Ratings................................................................................185

11.2 Power Characteristics ........................................................................................186

11.3 Signal Groups.....................................................................................................187

11.4 General DC Characteristics ...............................................................................189

Ballout and Package Information....................................................................................193

12.1 Ballout.................................................................................................................193

12.2 Package Information ..........................................................................................219

Page 8

13

R

Testability........................................................................................................................221

13.1 Complimentary Pins ...........................................................................................221

13.2 XOR Test Mode Initialization..............................................................................222

13.3 XOR Chain Definition .........................................................................................222

13.4 XOR Chains........................................................................................................222

13.5 Pads Excluded from XOR Mode(s)....................................................................242

8 Intel

®

82925X/82925XE MCH Datasheet

Page 9

R

Figures

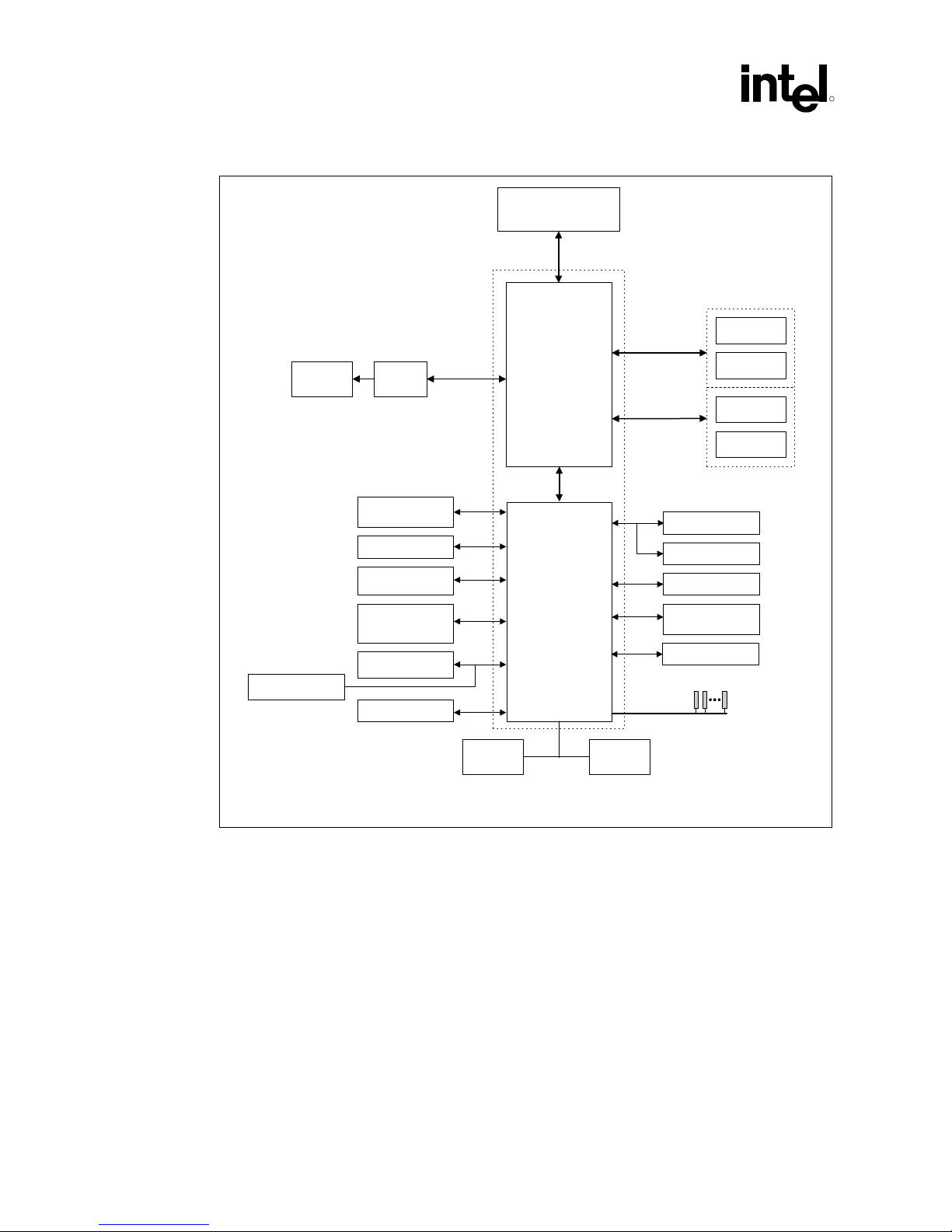

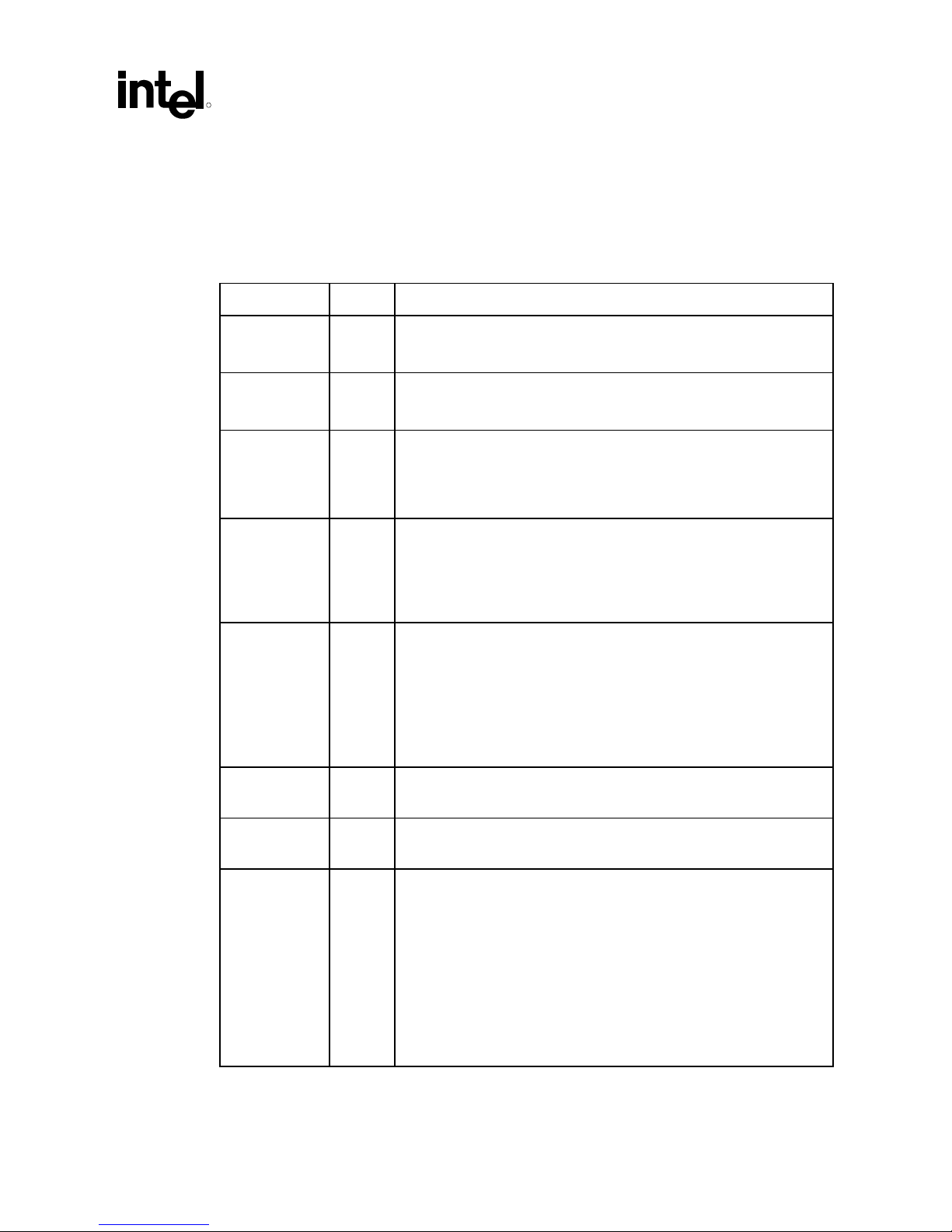

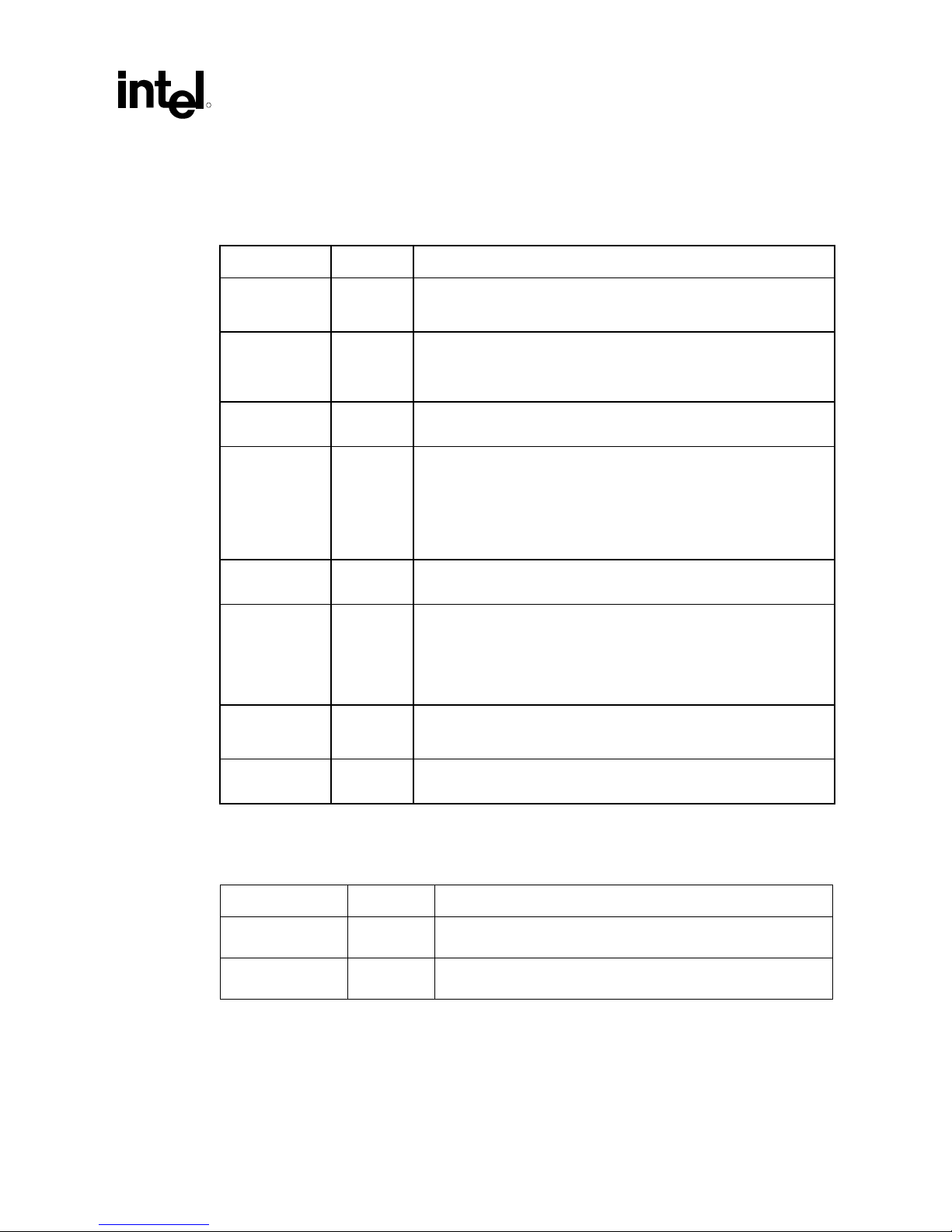

Figure 1-1. Intel® 925X/925XE Express Chipset System Block Diagram Example..........14

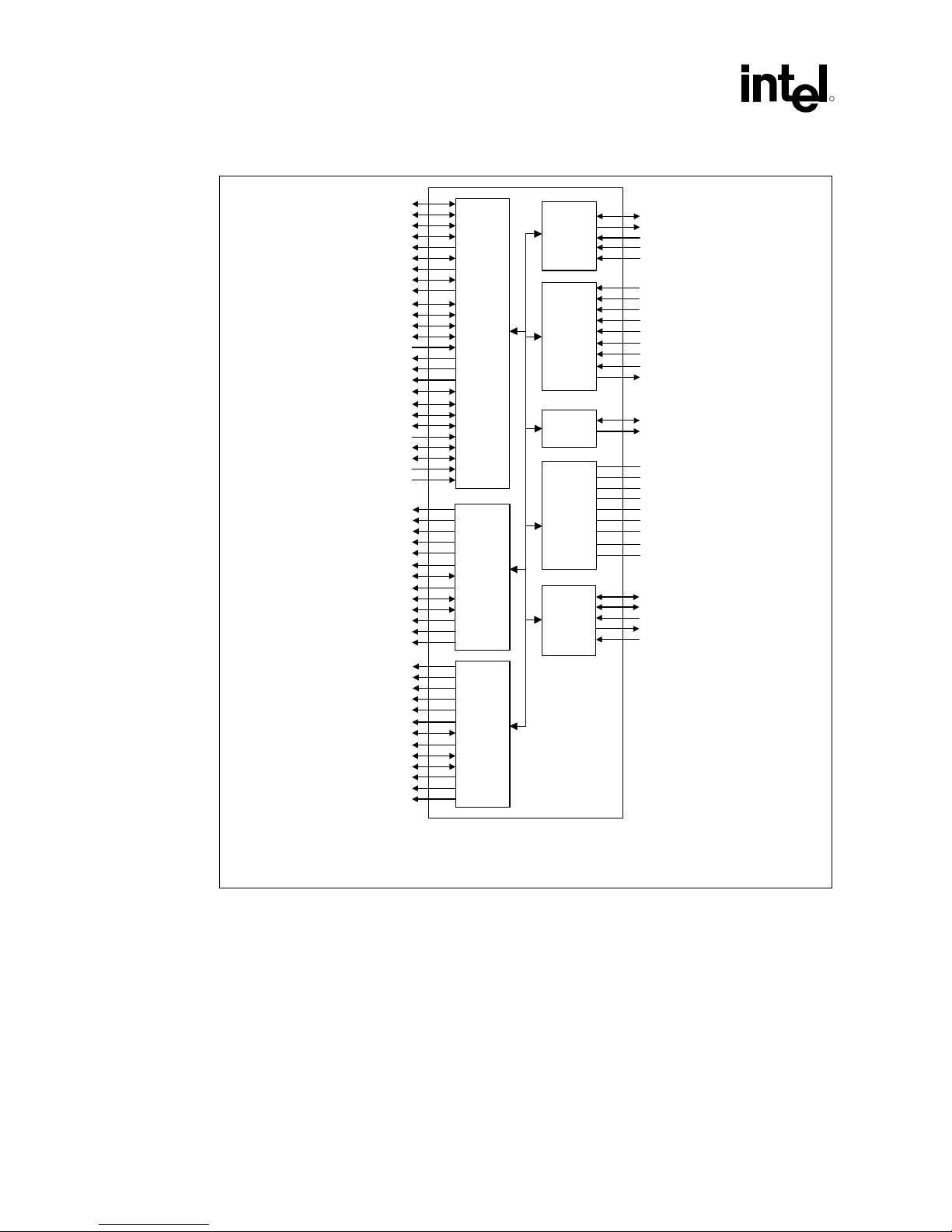

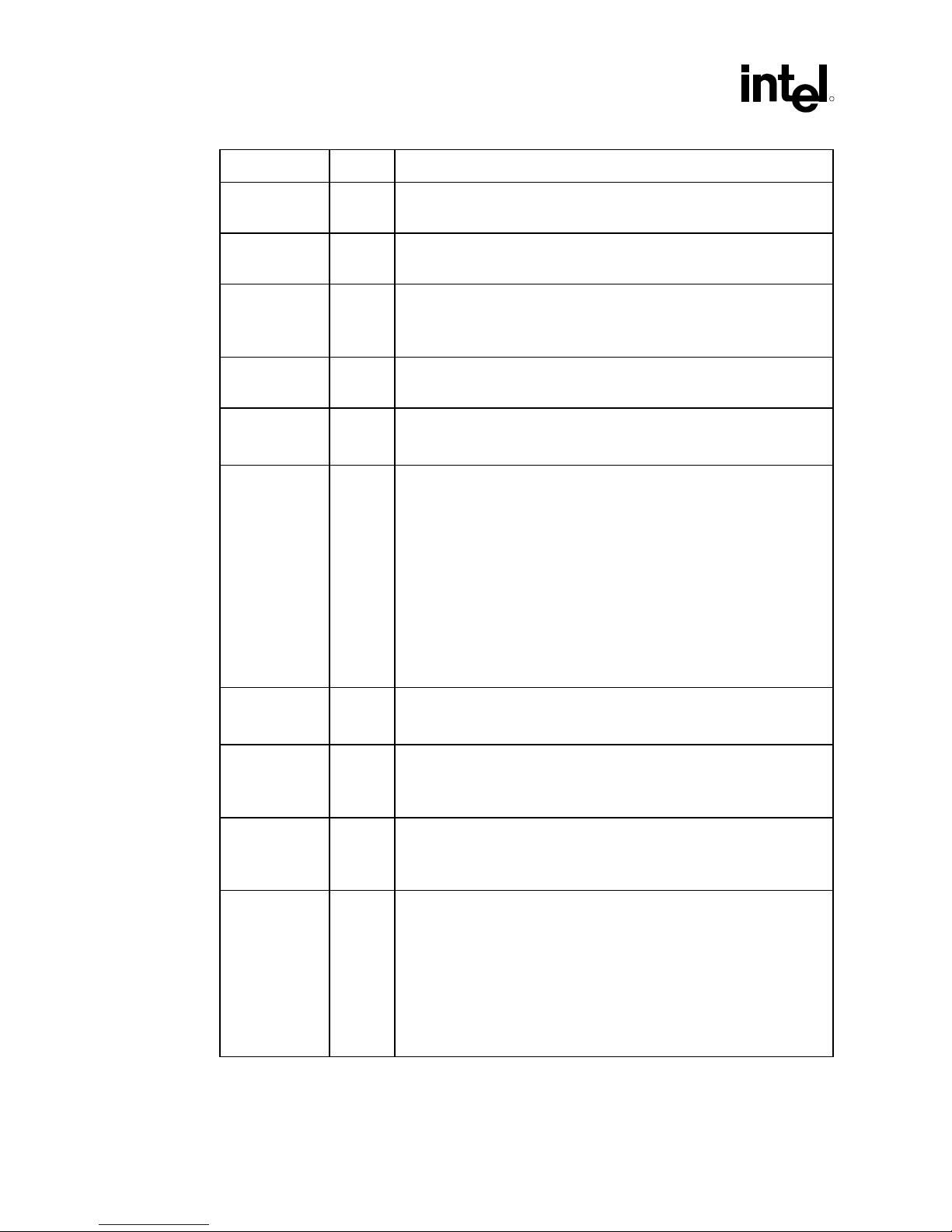

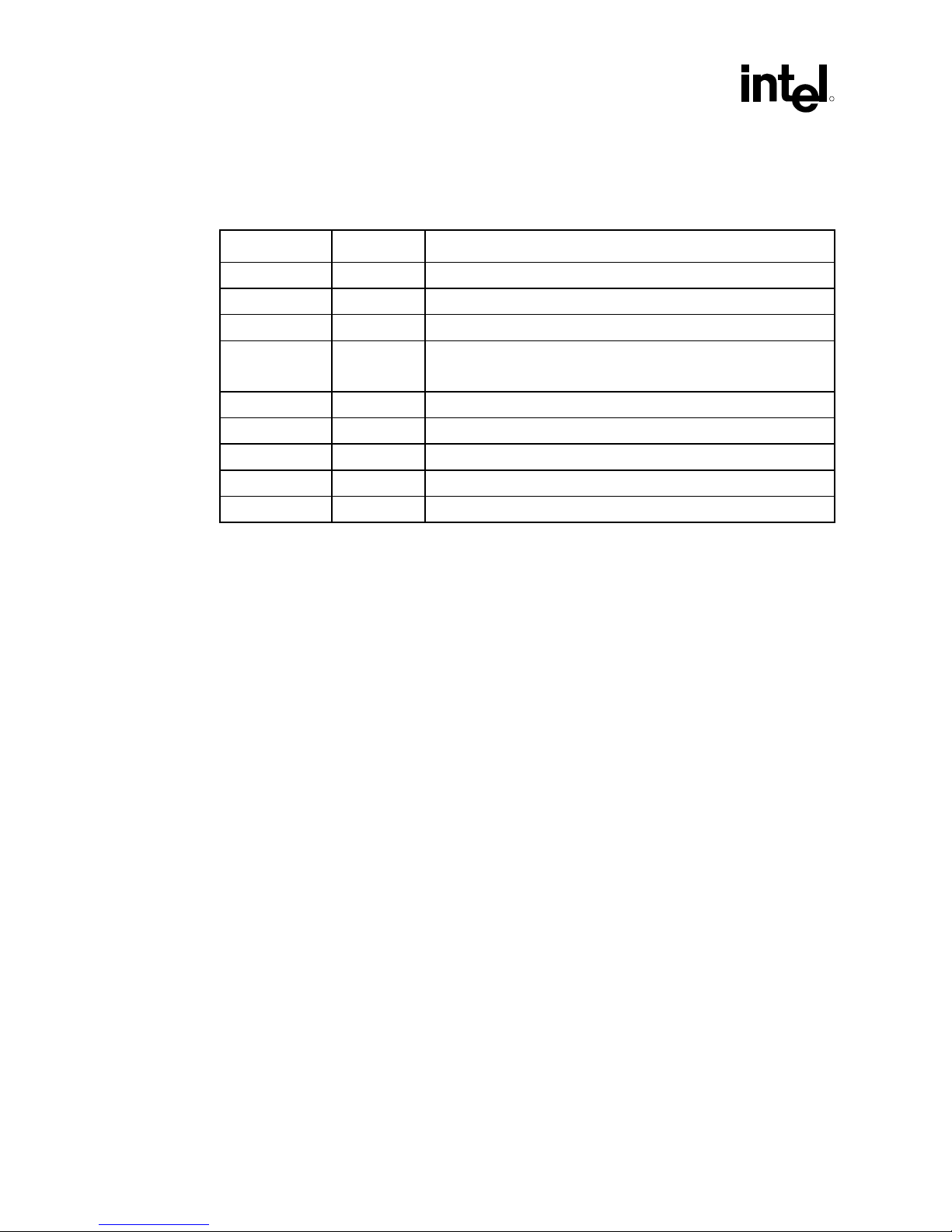

Figure 2-1. Intel® 82925X/82925XE MCH Signal Interface Diagram................................22

Figure 3-1. Conceptual Intel® 925X/925XE Express Chipset Platform PCI

Configuration Diagram...............................................................................................37

Figure 3-2. DMI Type 0 Configuration Address Translation.............................................39

Figure 3-3. DMI Type 1 Configuration Address Translation.............................................40

Figure 3-4. Memory Map to PCI Express* Device Configuration Space..........................41

Figure 3-5. Intel® 82925X/82925XE MCH Configuration Cycle Flowchart.......................42

Figure 6-1. Link Declaration Topology..............................................................................93

Figure 9-1. System Address Ranges..............................................................................158

Figure 9-2. Microsoft MS-DOS* Legacy Address Range ...............................................159

Figure 9-3. Main Memory Address Range......................................................................162

Figure 9-4. PCI Memory Address Range........................................................................164

Figure 10-1. System Memory Styles...............................................................................175

Figure 10-2. System Clocking Example..........................................................................184

Figure 12-1. Intel® 82925X/82925XE MCH Ballout (Top View: Left Side)......................194

Figure 12-2. Intel® 82925X/82925XE MCH Ballout (Top View: Right Side)...................195

Figure 12-3. MCH Package Dimensions ........................................................................220

®

Intel

82925X/82925XE MCH Datasheet 9

Page 10

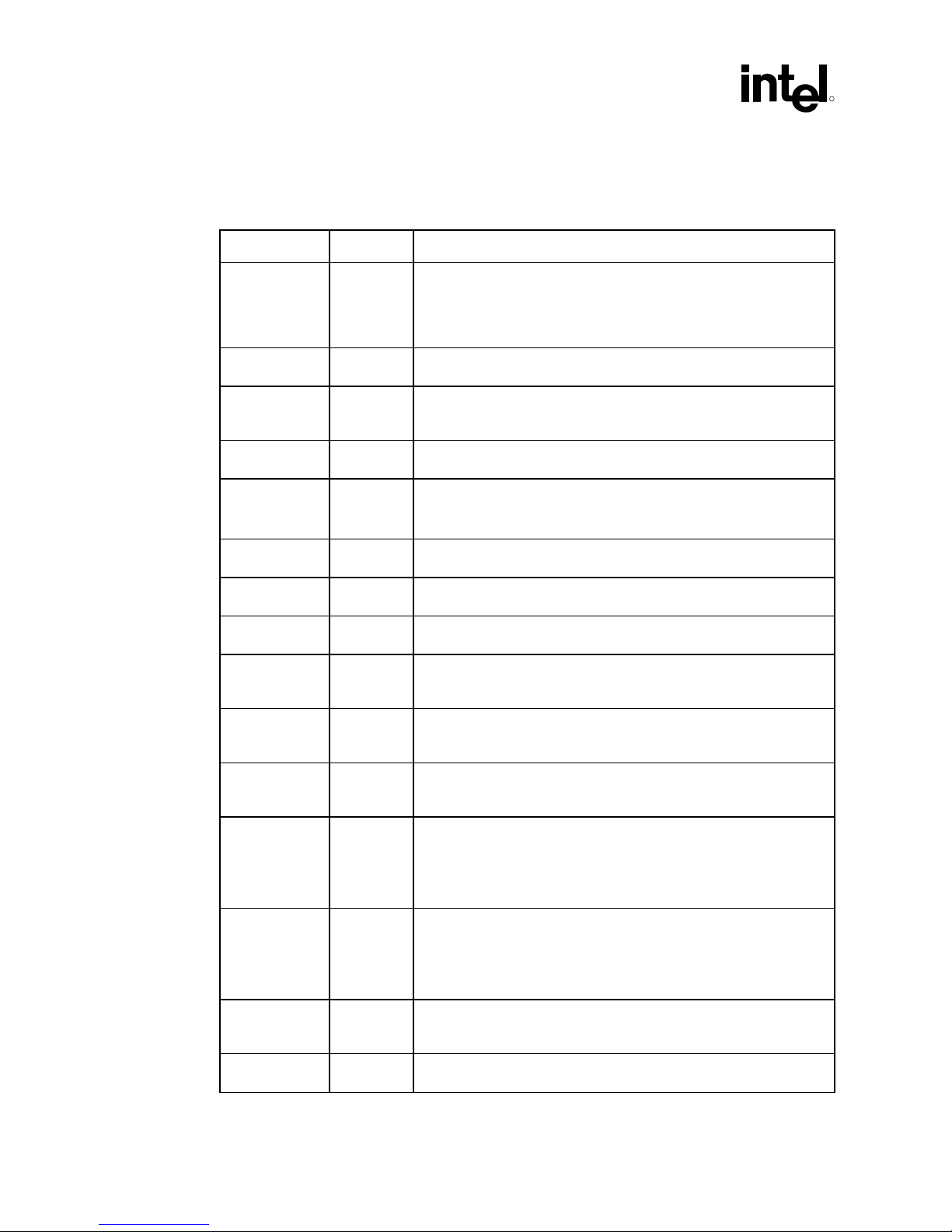

Tables

Table 2-1. Host Interface Reset and S3 States................................................................31

Table 2-2. System Memory Reset and S3 States.............................................................32

Table 2-3. PCI Express* Graphics x16 Port Reset and S3 States...................................33

Table 2-4. DMI Reset and S3 States................................................................................33

Table 2-5. Clocking Reset and S3 States.........................................................................34

Table 2-6. Miscellaneous Reset and S3 States................................................................34

Table 3-1. Device Number Assignment for Internal MCH Devices ..................................38

Table 4-1. Device 0 Function 0 Register Address Map Summary....................................45

Table 6-1. Egress Port Register Address Map.................................................................93

Table 7-1. DMI Register Address Map Summary.............................................................99

Table 8-1. Host-PCI Express* Graphics Bridge Register Address Map (D1:F0) ...........109

Table 9-1. Expansion Area Memory Segments..............................................................160

Table 9-2. Extended System BIOS Area Memory Segments.........................................161

Table 9-3. System BIOS Area Memory Segments.........................................................161

Table 9-4. Pre-Allocated Memory Example for 64-MB DRAM and 1-MB TSEG............163

Table 9-5. SMM Space Table.........................................................................................168

Table 9-6. SMM Control Table........................................................................................169

Table 10-1. Sample System Memory Organization with Interleaved Channels.............175

Table 10-2. Sample System Memory Organization with Asymmetric Channels............175

Table 10-3. DDR2 DIMM Supported Configurations ......................................................178

Table 10-4. DRAM Address Translation (Single Channel/Dual Asymmetric Mode) ......179

Table 10-5. DRAM Address Translation (Dual Channel Symmetric Mode) ...................180

Table 11-1. Absolute Maximum Ratings.........................................................................185

Table 11-2. Non-Memory Power Characteristics............................................................186

Table 11-3. DDR2 Power Characteristics.......................................................................186

Table 11-4. Signal Groups..............................................................................................187

Table 11-5. DC Characteristics.......................................................................................189

Table 12-1. MCH Ballout Sorted By Signal Name..........................................................196

Table 12-2. MCH Ballout Sorted By Ball Number...........................................................207

Table 13-1. Complimentary Pins to Drive.......................................................................221

Table 13-2. XOR Chain Outputs.....................................................................................222

Table 13-3. XOR Chain #0..............................................................................................223

Table 13-4. XOR Chain #1..............................................................................................225

Table 13-5. XOR Chain #2..............................................................................................227

Table 13-6. XOR Chain #3..............................................................................................229

Table 13-7. XOR Chain #4..............................................................................................231

Table 13-8. XOR Chain #5..............................................................................................233

Table 13-9. XOR Chain #6..............................................................................................235

Table 13-10. XOR Chain #7............................................................................................237

Table 13-11. XOR Chain #8............................................................................................239

Table 13-12. XOR Chain #9............................................................................................241

Table 13-13. XOR Pad Exclusion List.............................................................................242

R

10 Intel

®

82925X/82925XE MCH Datasheet

Page 11

R

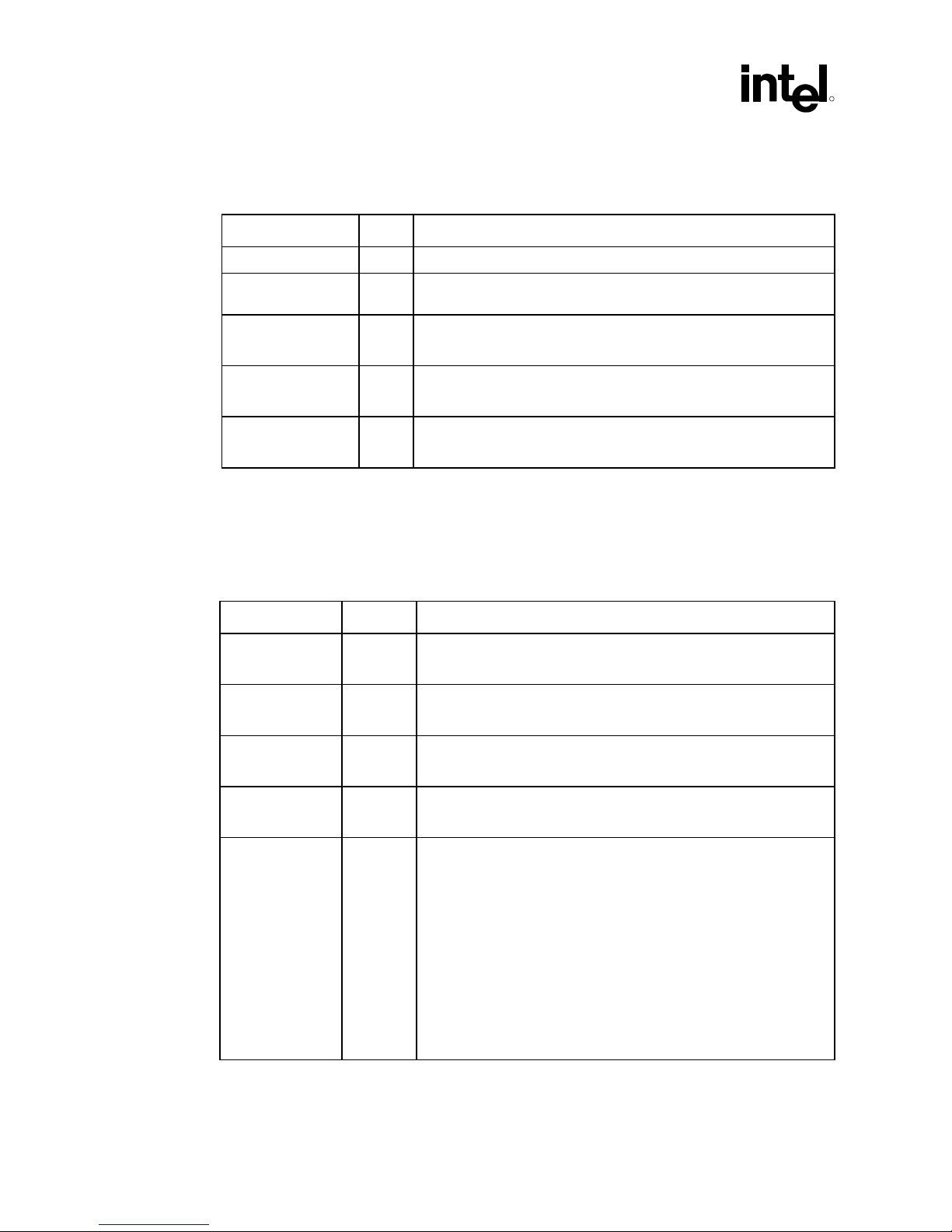

Revision History

Revision Description Date

-001 • Initial Release June 2004

-002 • Added Intel® Extended Memory 64 Technology (Intel® EM64T)

Support Information

-003 • Added 82925XE MCH Product Information November 2004

August 2004

§

®

Intel

82925X/82925XE MCH Datasheet 11

Page 12

Intel® 82925X/82925XE MCH Features

Processor Interface

⎯ One Intel

®

Pentium® 4 processor (supports

775-land package)

⎯ Supports Pentium 4 processor FSB interrupt

delivery

⎯ 800 MT/s (200 MHz) FSB

⎯ 1066 MT/s (266 MHz) FSB (82925XE

MCH Only)

⎯ Supports Hyper-Threading Technology

(HT Technology)

Ω

⎯ FSB Dynamic Bus Inversion (DBI)

⎯ 32-bit host bus addressing for access to

4 GB of memory space

⎯ 12-deep In-Order Queue

⎯ 1-deep Defer Queue

⎯ GTL+ bus driver with integrated GTL

termination resistors

⎯ Supports a Cache Line Size of 64 bytes

⎯ Supports Intel Pentium

DMI Interface

Intel

®

EM64T Φ

®

4 processors with

⎯ A chip-to-chip connection interface to Intel

ICH6

⎯ 2 GB/s point-to-point DMI to ICH6 (1 GB/s

each direction)

⎯ 100 MHz reference clock (shared with PCI

Express Graphics Attach).

⎯ 32-bit downstream addressing

⎯ Messaging and Error Handling

System Memory

⎯ One or two 64-bit wide DDR2 SDRAM

data channels

⎯ Bandwidth up to 8.5 GB/s (DDR2 533) in

dual-channel Interleaved mode

⎯ ECC (82925X MCH Only) and Non-ECC

memory

⎯ 256-Mb, 512-Mb and 1-Gb DDR2

technologies

⎯ Only x8, x16, DDR2 devices with four

banks and also supports eight bank, 1-Gbit

DDR2 devices.

⎯ Opportunistic refresh

⎯ Up to 64 simultaneously open pages (four

ranks of eight bank devices* 2 channels)

⎯ SPD (Serial Presence Detect) scheme for

DIMM detection support

⎯ Suspend-to-RAM support using CKE

⎯ Supports configurations defined in the

JEDEC DDR2 DIMM specification only

PCI Express Graphics Interface

®

⎯ One x16 PCI Express port

⎯ Compatible with the PCI Express Base

Specification Revision 1.0a

Package

⎯ 37.5 mm × 37.5 mm., 1210 balls, variable

ball pitch

R

12 Intel

®

82925X/82925XE MCH Datasheet

Page 13

Introduction

R

1 Introduction

The Intel® 925X Express chipset and Intel® 925XE Express chipset are designed for use with the

®

Pentium® 4 processor in entry-level, uniprocessor, workstation platforms. The chipsets

Intel

contain two components: 82925X or 82925XE Memory Controller Hub (MCH) for the host

bridge and I/O Controller Hub 6 (ICH6) for the I/O subsystem. The MCH provides the interface

to the processor, main memory, PCI Express, and the ICH6. The ICH6 is the sixth generation I/O

Controller Hub and provides a multitude of I/O related functions. Figure 1-1 shows an example

system block diagram for the 925X/925XE Express chipset.

®

For great workstation application flexibility, the Intel

specifically designed to support Intel

®

Extended Memory 64 Technology Φ (Intel® EM64T)

enabling 64-bit memory addressability. Select versions of the Pentium 4 processor support

Intel EM64T) as an enhancement to Intel's IA-32 architecture on workstation platforms. This

enhancement enables the processor to execute operating systems and applications written to take

advantage of Intel EM64T. Further details on the 64-bit extension architecture and programming

model can be found in the Intel

®

Extended Memory 64 Technology Software Developer Guide at

http://developer.intel.com/technology/64bitextensions/.

925X/925XE Express chipset is

®

This document is the datasheet for the Intel

82925X MCH and Intel® 82925XE MCH. Topics

covered include; signal description, system memory map, register descriptions, a description of

the MCH interfaces and major functional units, electrical characteristics, ballout definitions, and

package characteristics.

Φ

Note:

Intel® Extended Memory 64 Technology (Intel® EM64T) requires a computer system with a

processor, chipset, BIOS, operating system, device drivers and applications enabled for Intel

EM64T. Processor will not operate (including 32-bit operation) without an Intel EM64T-enabled

BIOS. Performance will vary depending on your hardware and software configu r ations. See

www.intel.com/info/em64t

for more information including details on which processors support

EM64T or consult with your system vendor for more information.

Note: Unless otherwise specified, the information in this document applies to both the 82925X MCH

and 82925XE MCH.

Note: Unless otherwise specified, ICH6 refers to the Intel

®

82801FB ICH6 and 82801FR ICHR I/O

Controller Hub components.

®

Intel

82925X/82925XE MCH Datasheet 13

Page 14

Introduction

R

Figure 1-1. Intel

®

925X/925XE Express Chipset System Block Diagram Example

®

Intel

Pentium® 4

Processor

200/266 MHz FSB

Display

Intel® PCI Express

Gigabit Ethernet

Graphics

Card

USB 2.0

8 ports, 480 Mb/s

IDE

4 SATA Ports

150 MB/s

AC '97/Intel® High

Defini tion Audio

CODECs

PCI Express* x1

GPIO

PCI Express

x16 Graphics

(800/1066 MT/s)

Intel® 82925X MCH/

Intel® 82925XE MCH

DMI Interface

Intel® ICH6 Family

Intel® 925X/925XE Express Chipset

Channel A

Channel B

Power Management

Clock Gener a tion

LAN Connect/ASF

System

Management ( TCO)

SMBus 2.0/I2C

Seven PCI Masters

PCI Bus

System Memory

DDR2

DDR2

DDR2

DDR2

Note: 266 MHz ( 10 66 MT/s) FSB is for 82925XE MCH only

14 Intel

Flash

BIOS

LPC

Interface

SIO

Sys_Blk_P

®

82925X/82925XE MCH Datasheet

Page 15

Introduction

R

1.1 Terminology

Term Description

Core

DBI

DDR2

DMI

FSB

Full Reset

Host

INTx

Intel® ICH6

MCH

MSI

PCI Express*

Primary PCI

SCI

Core refers to the internal base logic in the MCH.

Dynamic Bus Inversion.

A second generation Double Data Rate SDRAM memory technology.

®

The Direct Media Interface is the connection between the MCH and the Intel

Front Side Bus. The FSB is synonymous with Host or processor bus

Full reset is when PWROK is de-asserted. Warm reset is when both RSTIN# and

PWROK are asserted.

This term is used synonymously with processor.

An interrupt request signal where X stands for interrupts A,B,C and D.

Sixth generation I/O Controller Hub component that contains additional functionality

compared to previous ICH6s. The Intel

primary PCI interface, LPC interface, USB2, ATA-100, and other I/O functions. It

communicates with the MCH over a proprietary interconnect called DMI.

The Memory Controller Hub (MCH) component contains the processor interface and

DRAM controller. It may also contain an x16 PCI Express port (typically the external

graphics interface). It communicates with the I/O controller hub (ICH6*) and other I/O

controller hubs over the DMI interconnect.

Message Signaled Interrupt. A transaction initiated outside the host, conveying interrupt

information to the receiving agent through the same path that normally carries read and

write commands.

Third Generation Input Output (PCI Express) Graphics Attach called PCI Express

Graphics. A high-speed serial interface whose configuration is software compatible with

the existing PCI specifications. The specific PCI Express implementation intended for

connecting the MCH to an external graphics controller is a x16 link and replaces AGP.

The physical PCI bus that is driven directly by the ICH6 component. Communication

between Primary PCI and the MCH occurs over DMI. Note that the Primary PCI bus is

not PCI Bus 0 from a configuration standpoint.

System Control Interrupt. SCI is used in ACPI protocol.

®

I/O Controller Hub component contains the

ICH6.

SERR

SMI

Rank

TOLM

VCO

®

Intel

82925X/82925XE MCH Datasheet 15

An indication that an unrecoverable error has occurred on an I/O bus.

System Management Interrupt. SMI is used to indicate any of several system conditions

(such as thermal sensor events, throttling activated, access to System Management

RAM, chassis open, or other system state related activity).

A unit of DRAM corresponding to eight x8 SDRAM devices in parallel or four x16

SDRAM devices in parallel, ignoring ECC. These devices are usually, but not always,

mounted on a single side of a DIMM.

Top Of Low Memory. The highest address below 4 GB for which a processor-initiated

memory read or write transaction will create a corresponding cycle to DRAM on the

memory interface.

Voltage Controlled Oscillator.

Page 16

Introduction

1.2 Reference Documents

Document Title Document Number/Location

Intel® 925X/925XE Express Chipset Thermal Design Guide http://intel.com/design/chipsets/

Intel® I/O Controller Hub 6 (ICH6) Family Datasheet http://intel.com/design/chipsets/

Advanced Configuration and Power Interface Specification, Version 2.0 http://www.acpi.info/

Advanced Configuration and Power Interface Specification, Version

1.0b

The PCI Local Bus Specification, Version 2.3 http://www.pcisig.com/specificat

PCI Express* Specification, Version 1.0a http://www.pcisig.com/specificat

R

designex/301466.htm

datashts/301473.htm

http://www.acpi.info/

ions

ions

1.3 MCH Overview

The MCH connects to the processor as shown in Figure 1-1. A major role of the MCH in a system

is to manage the flow of information between its interfaces: the processor interface (FSB), the

System Memory interface (DRAM controller), the external graphics interface via PCI Express,

and the I/O Controller Hub through the DMI interface. This includes arbitrating between the

interfaces when each initiates transactions. The processor interface supports the Pentium 4

processor subset of the Extended Mode of the Scalable Bus Protocol.

The MCH supports one or two channels of DDR2 SDRAM. The MCH also supports the new PCI

Express based external graphics attach. Thus, the 925X/925XE Express chipset is not compatible

with AGP (1X, 2X, 4X, or 8X).

To increase system performance, the MCH incorporates several queues and a write cache. The

MCH also contains advanced desktop power management logic.

1.3.1 Host Interface

The MCH is optimized for the Pentium 4 processors in the LGA775 socket. The 82925X MCH

supports a FSB frequency of 200 MHz (800 MT/s) using a scalable FSB. The 82925XE MCH

supports a FSB frequency of 266 MHz (1066 MT/s).

The MCH supports the Pentium 4 processor subset of the Extended Mode Scaleable Bus Protocol.

The primary enhancements over the Compatible Mode P6 bus protocol are: Source synchronous

double-pumped (2) Address and Source synchronous quad-pumped (4x) Data.

The MCH supports 32-bit host addressing, decoding up to 4 GB of the processor’s memory

address space. Host-initiated I/O cycles are decoded to PCI Express, DMI, or the MCH

configuration space. Host-initiated memory cycles are decoded to PCI Express, DMI, or system

memory. PCI Express device accesses to non-cacheable system memory are not snooped on the

host bus. Memory accesses initiated from PCI Express using PCI semantics and from DMI to

system memory will be snooped on the host bus.

16 Intel

®

82925X/82925XE MCH Datasheet

Page 17

Introduction

R

1.3.2 System Memory Interface

The MCH integrates a system memory DDR2 controller with two, 64-bit wide interfaces. Only

Double Data Rate (DDR2) memory is supported; consequently, the buffers support only

SSTL_1.8 V signal interfaces. The memory controller interface is fully configurable through a set

of control registers. Features of the MCH memory controller include:

• The MCH System Memory Controller directly supports one or two channels of memory

(each channel consisting of 64 data lines).

• Supports two memory addressing organization options:

⎯ The memory channels are asymmetric: "Stacked" channels are assigned addresses

serially. Channel B addresses are assigned after all Channel A addresses.

⎯ The memory channels are interleaved: Addresses are ping-ponged between the channels

after each cache line (64-B boundary).

• Available bandwidth up to:

⎯ 3.2 GB/s (DDR2 400) for single-channel mode

⎯ 6.4 GB/s in dual-channel interleaved mode assuming DDR2 400 MHz.

⎯ 8.5 GB/s in dual-channel interleaved mode assuming DDR2 533 MHz.

• Supports DDR2 memory DIMM frequencies of 400 MHz and 533 MHz. The speed used in

all channels is the speed of the slowest DIMM in the system.

• I/O Voltage of 1.8 V for DDR2.

• I/O Voltage of 1.9 V for DDR2 533 MHz CL3-3-3.

• Supports non-ECC and ECC (925X only) memory.

• Supports 256-Mb, 512-Mb and 1-Gb DDR2 technologies

• Supports only x8, x16, DDR2 devices with four banks and also supports eight bank,

1-Gbit DDR2 devices.

• Supports opportunistic refresh

• In dual channel mode the MCH supports 64 simultaneously open pages (four ranks of eight

bank devices* 2 channels)

• Supports Partial Writes to memory using Data Mask (DM) signals.

• Supports page sizes of 4 KB, 8 KB, and 16 KB.

• Supports a burst length of 8 for single-channel and dual-channel interleaved and asymmetric

operating modes.

• Supports unbuffered DIMMs.

• SPD (Serial Presence Detect) scheme for DIMM detection support

• Suspend-to-RAM support using CKE

• Supports configurations defined in the JEDEC DDR2 DIMM specification only

The MCH supports a memory thermal management scheme to selectively manage reads and/or

writes. Memory thermal management can be triggered either by on-die thermal sensor, or by

preset limits. Management limits are determined by weighted sum of various commands that are

scheduled on the memory interface.

®

Intel

82925X/82925XE MCH Datasheet 17

Page 18

Introduction

1.3.3 Direct Media Interface (DMI)

Direct Media Interface (DMI) is the chip-to-chip connection between the MCH and ICH6. This

high-speed interface integrates advanced priority-based servicing allowing for concurrent traffic

and true isochronous transfer capabilities. Base functionality is completely software transparent

permitting current and legacy software to operate normally.

To provide for true isochronous transfers and configurable Quality of Service (QoS) transactions,

the ICH6 supports two virtual channels on DMI: VC0 and VC1. These two channels provide a

fixed arbitration scheme where VC1 is always the highest priority. VC0 is the default conduit of

traffic for DMI and is always enabled. VC1 must be specifically enabled and configured at both

ends of the DMI link (i.e., the ICH6 and MCH). Features of the DMI include:

• A chip-to-chip connection interface to ICH6

• 2 GB/s point-to-point DMI to ICH6 (1 GB/s each direction)

• 100 MHz reference clock (shared with PCI Express Graphics Attach).

• 32-bit downstream addressing

• APIC and MSI interrupt messaging support. Will send Intel-defined “End Of Interrupt”

broadcast message when initiated by the processor.

• Message Signaled Interrupt (MSI) messages

• SMI, SCI and SERR error indication

• Legacy support for ISA regime protocol (PHOLD/PHOLDA) required for parallel port

DMA, floppy drive, and LPC bus masters

R

1.3.4 PCI Express* Graphics Interface

The MCH contains a 16-lane (x16) PCI Express* port intended for an external PCI Express

.

graphics card

Revision 1.0a. The x16 port operates at a frequency of 2.5 Gb/s on each lane while employing

8b/10b encoding, and supports a maximum theoretical bandwidth of 4 Gb/s each direction.

The PCI Express port is compatible with the PCI Express Base Specification

18 Intel

®

82925X/82925XE MCH Datasheet

Page 19

Introduction

R

Features of the PCI Express Interface include:

• One x16 PCI Express port intended for graphics attach, compatible with the PCI Express

Base Specification revision 1.0a.

• Theoretical PCI Express transfer rate of 2.5 Gb/s.

• Raw bit-rate on the data pins of 2.5 Gb/s, resulting in a real bandwidth per pair of 250 MB/s

given the 8b/10b encoding used to transmit data across this interface

• Maximum theoretical realized bandwidth on the interface of 4 GB/s in each direction

simultaneously, for an aggregate of 8 GB/s when (1)x16.

• PCI Express Graphics Extended Configuration Space. The first 256 bytes of configuration

space alias directly to the PCI Compatibility configuration space. The remaining portion of

the fixed 4-KB block of memory-mapped space above that (starting at 100h) is known as

extended configuration space.

• PCI Express Enhanced Addressing Mechanism. Accessing the device configuration space in

a flat memory mapped fashion.

• Automatic discovery, negotiation, and training of link out of reset

• Supports traditional PCI style traffic (asynchronous snooped, PCI ordering)

• Supports traditional AGP style traffic (asynchronous non-snooped, PCI Express-relaxed

ordering)

• Hierarchical PCI-compliant configuration mechanism for downstream devices (i.e., normal

PCI 2.3 Configuration space as a PCI-to-PCI bridge)

• Supports “static” lane numbering reversal. This method of lane reversal is controlled by a

Hardware Reset strap, and reverses both the receivers and transmitters for all lanes (e.g.,

TX15->TX0, RX15->RX0). This method is transparent to all external devices and is different

than lane reversal as defined in the PCI Express Specification. In particular, link initialization

is not affected by static lane reversal.

1.3.5 System Interrupts

The MCH interrupt support includes:

• Supports both 8259 and Pentium 4 processor FSB interrupt delivery mechanisms.

• Supports interrupts signaled as upstream Memory Writes from PCI Express and DMI

⎯ MSIs routed directly to FSB

⎯ From I/OxAPICs

®

Intel

82925X/82925XE MCH Datasheet 19

Page 20

Introduction

1.3.6 MCH Clocking

The differential FSB clock (HCLKP/HCLKN) is set to 200 MHz on the 82925X MCH and

266 MHz on the 82925XE MCH. This supports FSB transfer rates of 800 MT/s for the 82925X

MCH and FSB transfer rates of 1066 MT/s for the 82925XE MCH. The Host PLL generates 2X,

4X, and 8X versions of the host clock for internal optimizations. The MCH core clock is

synchronized to the host clock.

The internal and external memory clocks of 133 MHz, 200 MHz, and 266 MHz are generated

from one of two MCH PLLs that use the host clock as a reference. This includes 2X and 4X for

internal optimizations.

The PCI Express core clock of 250 MHz is generated from a separate PCI Express PLL. This

clock uses the fixed 100 MHz Serial Reference Clock (GCLKP/GCLKN) for reference.

All of the above mentioned clocks are capable of tolerating Spread Spectrum clocking as defined

in the Clock Generator specification. Host, Memory, and PCI Express* x16 Graphics PLLs, and

all associated internal clocks are disabled until PWROK is asserted.

R

1.3.7 Power Management

MCH Power Management support includes:

• PC99 suspend to DRAM support (“STR”, mapped to ACPI state S3)

• SMRAM space remapping to A0000h (128 KB)

• Supports extended SMRAM space above 256 MB, additional 1-MB TSEG from the Base of

graphics stolen memory (BSM) when enabled, and cacheable (cacheability controlled by

processor)

• ACPI Rev 1.0 compatible power management

• Supports processor states: C0, C1, C2, C3, and C4

• Supports System states: S0, S1, S3, S4, and S5

• Supports processor Thermal Management 2 (TM2)

• Microsoft Windows NT* Hardware Design Guide v1.0 compliant

§

20 Intel

®

82925X/82925XE MCH Datasheet

Page 21

Signal Description

R

2 Signal Description

This chapter provides a detailed description of MCH signals. The signals are arranged in

functional groups according to their associated interface. The states of all of the signals during

reset are provided in the Section 2.9.

The following notations are used to describe the signal type:

I Input pin

O Output pin

I/O Bi-directional input/output pin

GTL+ Open Drain GTL+ interface signal. Refer to the GTL+ I/O Specification for

complete details. The MCH integrates GTL+ termination resistors, and supports

of from 0.83 V to 1.65 V (including guardbanding).

VTT

PCIE PCI-Express interface signals. These signals are compatible with PCI Express

1.0 Signaling Environment AC Specifications and are AC coupled. The buffers

are not 3.3 V tolerant. Differential voltage specification

= (|D+ - D-|) * 2 = 1.2 V maximum Single-ended maximum = 1.5 V.

Single-ended minimum = 0 V.

DMI Direct Media Interface signals. These signals are compatible with PCI Express

1.0 Signaling Environment AC Specifications, but are DC coupled. The buffers

are not 3.3 V tolerant. Differential voltage specification

= (|D+ - D-|) * 2 = 1.2 V maximum. Single-ended maximum = 1.5 V.

Single-ended minimum = 0 V.

CMOS CMOS buffers. 1.5 V tolerant.

COD CMOS Open Drain buffers. 2.5 V tolerant.

HVCMOS High Voltage CMOS buffers. 2.5 V tolerant.

HVIN High Voltage CMOS input-only buffers. 3.3 V tolerant.

SSTL-1.8 Stub Series Termination Logic. These are 1.8 V output capable buffers; 1.8 V

tolerant. An I/O voltage of 1.9 V is needed for D DR2 533 MHz CL3-3-3.

A Analog reference or output. May be used as a threshold voltage or for buffer

compensation.

®

Intel

82925X/82925XE MCH Datasheet 21

Page 22

Signal Description

R

Figure 2-1. Intel

®

82925X/82925XE MCH Signal Interface Diagram

HA[31:3]#

HD[63:0]

HADS#

HBNR#

HBPRI#

HDBSY#

HDEFER#

HDRDY#

HEDRDY#

HHIT#

HHITM#

HLOCK#

HREQ[4:0]#

HPCREQ#

HTRDY#

HRS[2:0]#

HCPURST#

HBREQ0#

HDINV[3:0]#

HDSTBP[3:0]#, HDSTBN[3:0]#

SDQS_A[8:0], SDQS_A[8:0]#

SCLK_A[5:0], SCLK_A[5:0]#

SDQS_B[8:0], SDQS_B[8:0]#

SCLK_B[5:0], SCLK_B[5:0]#

HADSTB[1:0]#

BSEL[2:0]

HRCOMP

HSCOMP

HSWING

HVREF

SCS_A[3:0]#

SMA_A[13:0]

SBS_A[2:0]

SRAS_A#

SCAS_A#

SWE_A#

SDQ_A[63:0]

SDM_A[7:0]

SCB_A[7:0]

SCKE_A[3:0]

SODT_A[3:0]

SCS_B[3:0]#

SMA_B[13:0]

SBS_B_B[2:0]

SRAS_B#

SCAS_B#

SWE_B#

SDQ_B[63:0]

SDM_B[7:0]

SCB_B[7:0]

SCKE_B[3:0]

SODT_B[3:0]

Processor

System

Bus

Interface

System

Memory

DDR2

Channel

A

System

Memory

DDR2

Channel

B

PCI

Express

x16

Graphics

Port

Clocks,

Reset, and

Misc.

Direct

Media

Interface

Voltage

Reference,

and Powe r

System

Memory

DDR2 Ref./

Comp.

EXP_RXN[15:0], EXP_RXP[15:0]

EXP_TXN[15:0], EXP_TXP[15:0]

EXP_COMPO

EXP_COMPI

EXP_SLR

HCLKP, HCLKN

GCLKP, GCLKN

DREFCLKN, DREFCLKP

RSTIN#

PWROK

EXTTS#

BSEL[2:0]

MTYPE

ICH_SYNC#

DMI_RXP[3:0 ], DM I_ RXN[3:0]

DMI_TXP[3:0], DMI_TXN[3:0]

VCC

VTT

VCC_EXP

VCCSM

VCC2

VCCA_EXPPLL

VCCA_HPLL

VCCA_SMPLL

VSS

SRCOMP[1:0]

SOCOMP[1:0]

SM_SLEWIN[1:0]

SM_SLEWOUT[1:0]

SMVREF[1:0]

Note:

1. SCB_A[7:0] an d SCB_B[7:0] are on the Intel

2. SDQS_A8/SDQS_A8# and SDQS_B8/SDQS_B8# are on the Intel® 8 2925X only.

22 Intel

®

82925X only.

Signal_Info

®

82925X/82925XE MCH Datasheet

Page 23

Signal Description

R

2.1 Host Interface Signals

Note: Unless otherwise noted, the voltage level for all signals in this interface is tied to the termination

voltage of the Host Bus (V

Signal Name Type Description

).

TT

HADS# I/O

GTL+

HBNR# I/O

GTL+

HBPRI# O

GTL+

HBREQ0# I/O

GTL+

HCPURST# O

GTL+

HDBSY# I/O

GTL+

HDEFER# O

GTL+

HDINV[3:0]# I/O

GTL+

Address Strobe: The processor bus owner asserts HADS# to indicate the

first of two cycles of a request phase. The MCH can assert this signal for

snoop cycles and interrupt messages.

Block Next Request: This signal is used to block the current request bus

owner from issuing new requests. This signal is used to dynamically control

the processor bus pipeline depth.

Priority Agent Bus Request: The MCH is the only Priority Agent on the

processor bus. It asserts this signal to obtain the ownership of the address

bus. This signal has priority over symmetric bus requests and will cause the

current symmetric owner to stop issuing new transactions unless the

HLOCK# signal was asserted.

Bus Request 0: The MCH pulls the processor’s bus HBREQ0# signal low

during HCPURST#. The processor samples this signal on the active-toinactive transition of HCPURST#. The minimum setup time for this signal is

4 HCLKs. The minimum hold time is 2 clocks and the maximum hold time is

20 HCLKs. HBREQ0# should be tri-stated after the hold time requirement

has been satisfied.

CPU Reset: The HCPURST# pin is an output from the MCH. The MCH

asserts HCPURST# while RSTIN# is asserted and for approximately 1 ms

after RSTIN# is de-asserted. The HCPURST# allows the processors to

begin execution in a known state.

Note that the Intel

up and hold times around HCPURST#. This requires strict synchronization

between MCH HCPURST# de-assertion and the Intel® ICH6 driving the

straps.

Data Bus Busy: This signal is used by the data bus owner to hold the data

bus for transfers requiring more than one cycle.

Defer: Signals that the MCH will terminate the transaction currently being

snooped with either a deferred response or with a retry response.

Dynamic Bus Inversion: Driven along with the HD[63:0] signals. Indicates

if the associated signals are inverted or not. HDINV[3:0]# are asserted such

that the number of data bits driven electrically low (low voltage) within the

corresponding 16 bit group never exceeds 8.

HDINVx# Data Bits

HDINV3# HD[63:48]

HDINV2# HD[47:32]

HDINV1# HD[31:16]

HDINV0# HD[15:0]

®

ICH6 must provide processor frequency select strap set-

®

Intel

82925X/82925XE MCH Datasheet 23

Page 24

Signal Description

R

Signal Name Type Description

HDRDY# I/O

GTL+

HEDRDY# O

GTL+

HA[31:3]# I/O

GTL+

HADSTB[1:0]# I/O

GTL+

HD[63:0] I/O

GTL+

HDSTBP[3:0]#

HDSTBN[3:0]#

HHIT# I/O

HHITM# I/O

HLOCK# I/O

HPCREQ# I

I/O

GTL+

GTL+

GTL+

GTL+

GTL+

2x

Data Ready: This signal is asserted for each cycle that data is transferred.

Early Data Ready: This signal indicates that the data phase of a read

transaction will start on the bus exactly one common clock after assertion.

Host Address Bus: HA[31:3]# connect to the processor address bus.

During processor cycles, the HA[31:3]# are inputs. The MCH drives

HA[31:3]# during snoop cycles on behalf of DMI and PCI Express Graphics

initiators. HA[31:3]# are transferred at 2x rate.

Host Address Strobe: The source synchronous strobes used to transfer

HA[31:3]# and HREQ[4:0] at the 2x transfer rate.

Host Data: These signals are connected to the processor data bus. Data on

HD[63:0] is transferred at 4x rate. Note that the data signals may be

inverted on the processor bus, depending on the HDINV[3:0]# signals.

Differential Host Data Strobes: The differential source synchronous

strobes are used to transfer HD[63:0]# and HDINV[3:0]# at 4x transfer rate.

These signals are named this way because they are not level sensitive.

Data is captured on the falling edge of both strobes. Hence, they are

pseudo-differential, and not true differential.

Strobes Data Bits

HDSTBP3#, HDSTBN3# HD[63:48] HDINV3#

HDSTBP2#, HDSTBN2# HD[47:32] HDINV2#

HDSTBP1#, HDSTBN1# HD[31:16] HDINV1#

HDSTBP0#, HDSTBN0# HD[15:0] HDINV0#

Hit: This signal indicates that a caching agent holds an unmodified version

of the requested line. Also, driven in conjunction with HHITM# by the target

to extend the snoop window.

Hit Modified: This signal indicates that a caching agent holds a modified

version of the requested line and that this agent assumes responsibility for

providing the line. This signal is also driven in conjunction with HHIT# to

extend the snoop window.

Host Lock: All processor bus cycles sampled with the assertion of HLOCK#

and HADS#, until the negation of HLOCK# must be atomic (i.e., no DMI or

PCI Express Graphics accesses to DRAM are allowed when HLOCK# is

asserted by the processor).

Precharge Request: The processor provides a “hint” to the MCH that it is

OK to close the DRAM page of the memory read request with which the hint

is associated. The MCH uses this information to schedule the read request

to memory using the special “AutoPrecharge” attribute. This causes the

DRAM to immediately close (Precharge) the page after the read data has

been returned. This allows subsequent processor requests to more quickly

access information on other DRAM pages, since it will no longer be

necessary to close an open page prior to opening the proper page.

Asserted by the requesting agent during both halves of Request Phase. The

same information is provided in both halves of the request phase.

24 Intel

®

82925X/82925XE MCH Datasheet

Page 25

Signal Description

R

Signal Name Type Description

HREQ[4:0]# I/O

GTL+

2x

HTRDY# O

GTL+

HRS[2:0]# O

GTL+

BSEL[2:0] I

CMOS

HRCOMP I/O

CMOS

HSCOMP I/O

CMOS

HSWING I

HVREF I

Host Request Command: These signals define the attributes of the

request. HREQ[4:0]# are transferred at 2x rate. They are asserted by the

requesting agent during both halves of Request Phase. In the first half the

signals define the transaction type to a level of detail that is sufficient to

begin a snoop request. In the second half the signals carry additional

information to define the complete transaction type.

The transactions supported by the MCH Host Bridge are defined in the Host

Interface section of this document.

Host Target Ready: This signal indicates that the target of the processor

transaction is able to enter the data transfer phase.

Response Signals: These signals indicate the type of response as shown

below:

000 = Response type

001 = Idle state

010 = Retry response

011 = Deferred response

100 = Reserved (not driven by MCH)

101 = Hard Failure (not driven by MCH)

110 = No data response

111 = Implicit Writeback

111 = Normal data response

Bus Speed Select: At the de-assertion of RSTIN#, the value sampled on

these pins determines the expected frequency of the bus.

Host RCOMP: Used to calibrate the Host GTL+ I/O buffers.

This signal is powered by the Host Interface termination rail (VTT).

Slew Rate Compensation: Compensation for the Host Interface.

Host Voltage Swing: This signal provides the reference voltage used by

FSB RCOMP circuits. HSWING is used for the signals handled by

A

HRCOMP.

Host Reference Voltage Reference: Voltage input for the data, address,

and common clock signals of the Host GTL interface.

A

®

Intel

82925X/82925XE MCH Datasheet 25

Page 26

Signal Description

2.2 DDR2 DRAM Channel A Interface

Signal Name Type Description

R

SCLK_A[5:0] O

SSTL-1.8

SCLK_A[5:0]# O

SSTL-1.8

SCS_A[3:0]# O

SSTL-1.8

SMA_A[13:0] O

SSTL-1.8

SBS_A[2:0] O

SSTL-1.8

SRAS_A# O

SSTL-1.8

SCAS_A# O

SSTL-1.8

SWE_A# O

SSTL-1.8

SDQ_A[63:0] I/O

SSTL-1.8

2x

SDM_A[7:0] O

SSTL-1.8

2X

SCB_A[7:0]

®

(Intel

82925X

Only)

SDQS_A[8:0]

(82925X MCH)

SDQS_A[7:0]

(82925XE

MCH)

SDQS_A[8:0]#

(82925X MCH)

SDQS_A[7:0]#

(82925XE

MCH)

SCKE_A[3:0] O

SODT_A[3:0] O

I/O

SSTL-1.8

2X

I/O

SSTL-1.8

2x

I/O

SSTL-1.8

2x

SSTL-1.8

SSTL-1.8

SDRAM Differential Clock: (3 per DIMM). SCLK_Ax and its

complement SCLK_Ax# signal make a differential clock pair output. The

crossing of the positive edge of SCLK_Ax and the negative edge of its

complement SCLK_Ax# are used to sample the command and control

signals on the SDRAM.

SDRAM Complementary Differential Clock: (3 per DIMM) These are

the complementary differential DDR2 Clock signals.

Chip Select: (1 per Rank) These signals select particular SDRAM

components during the active state. There is one chip select for each

SDRAM rank.

Memory Address: These signals are used to provide the multiplexed

row and column address to the SDRAM

Bank Select: These signals define which banks are selected within each

SDRAM rank

DDR2: 1-Gb technology is 8 banks.

Row Address Strobe: This signal is used with SCAS_A# and SWE_A#

(along with SCS_A#) to define the SDRAM commands.

Column Address Strobe: This signal is used with SRAS_A# and

SWE_A# (along with SCS_A#) to define the SDRAM commands.

Write Enable: This signal is used with SCAS_A# and SRAS_A# (along

with SCS_A#) to define the SDRAM commands.

Data Lines: SDQ_A signals interface to the SDRAM data bus.

Data Mask: When activated during writes, the corresponding data

groups in the SDRAM are masked. There is one SDM_Ax signal for

every data byte lane.

ECC Check Byte: These signals require a 6-layer board to be routed.

Data Strobes: For DDR2, SDQS_Ax and its complement SDQS_Ax#

signal make up a differential strobe pair. The data is captured at the

crossing point of SDQS_Ax and its complement SDQS_Ax# during read

and write transactions.

Data Strobe Complements: These signals are the complementary

DDR2 strobe signals.

Clock Enable: (1 per Rank) SACKE is used to initialize the SDRAMs

during power-up, to power-down SDRAM ranks, and to place all SDRAM

ranks into and out of self-refresh during Suspend-to-RAM.

On Die Termination: Active On-die Termination Control signals for

DDR2 devices.

26 Intel

®

82925X/82925XE MCH Datasheet

Page 27

Signal Description

R

2.3 DDR2 DRAM Channel B Interface

Signal Name Type Description

SCLK_B[5:0] O

SSTL-1.8

SCLK_B[5:0]# O

SSTL-1.8

SCS_B[3:0]# O

SSTL-1.8

SMA_B[13:0] O

SSTL-1.8

SBS_B[2:0] O

SSTL-1.8

SRAS_B# O

SSTL-1.8

SCAS_B# O

SSTL-1.8

SWE_B# O

SSTL-1.8

SDQ_B[63:0] I/O

SSTL-1.8

2x

SDM_B[7:0] O

SSTL-1.8

2x

SCB_B[7:0]

®

(Intel

82925X

Only)

SDQS_B[8:0]

(82925X MCH)

SDQS_B[7:0]

(82925XE MCH)

SDQS_B[8:0]#

(82925X MCH)

SDQS_B[7:0]#

(82925XE MCH)

SCKE_B[3:0] O

SODT_B[3:0] O

I/O

SSTL-1.8

2X

I/O

SSTL-1.8

2x

I/O

SSTL-1.8

2x

SSTL-1.8

SSTL-1.8

SDRAM Differential Clock: (3 per DIMM) SCLK_Bx and its complement

SCLK_Bx# signal make a differential clock pair output. The crossing of

the positive edge of SCLK_Bx and the negative edge of its complement

SCLK_Bx# are used to sample the command and control signals on the

SDRAM.

SDRAM Complementary Differential Clock: (3 per DIMM) These are

the complementary differential DDR2 clock signals.

Chip Select: (1 per Rank) These signals select particular SDRAM

components during the active state. There is one chip select for each

SDRAM rank

Memory Address: These signals are used to provide the multiplexed

row and column address to the SDRAM

Bank Select: These signals define which banks are selected within

each SDRAM rank

DDR2: 1-Gb technology is 8 banks.

Row Address Strobe: This signal is used with SCAS_B# and SWE_B#

(along with SCS_B#) to define the SDRAM commands

Column Address Strobe: This signal is used with SRAS_B# and

SWE_B# (along with SCS_B#) to define the SDRAM commands.

Write Enable: This signal is used with SCAS_B# and SRAS_B# (along

with SCS_B#) to define the SDRAM commands.

Data Lines: SDQ_Bx signals interface to the SDRAM data bus

Data Mask: When activated during writes, the corresponding data

groups in the SDRAM are masked. There is one SDM_Bx signal for

every data byte lane.

ECC Check Byte: These signals require a 6-layer board to be routed.

Data Strobes: For DDR2, SDQS_Bx and its complement SDQS_Bx#

make up a differential strobe pair. The data is captured at the crossing

point of SDQS_Bx and its complement SDQS_Bx# during read and write

transactions.

Data Strobe Complements: These signals are the complementary

DDR2 strobe signals.

Clock Enable: (1 per Rank) SCKE_B is used to initialize the SDRAMs

during power-up, to power-down SDRAM ranks, and to place all SDRAM

ranks into and out of self-refresh during Suspend-to-RAM.

On Die Termination: Active On-die Termination Control signals for

DDR2 devices.

®

Intel

82925X/82925XE MCH Datasheet 27

Page 28

Signal Description

2.4 DDR2 DRAM Reference and Compensation

Signal Name Type Description

SRCOMP[1:0] I/O System Memory RCOMP

SOCOMP[1:0] I/O

SM_SLEWIN[1:0] I A Buffer Slew Rate Input: Slew Rate Characterization buffer input for X

SM_SLEWOUT[1:0] O A Buffer Slew Rate Output: Slew Rate Characterization buffer output for

DDR2 On-Die DRAM Over Current Detection (OCD) driver

A

compensation

and Y orientation.

X and Y orientation

R

SMVREF[1:0] I

SDRAM Reference Voltage: Reference voltage inputs for each DQ,

DM, DQS, and DQS# input signals.

A

2.5 PCI Express* x16 Graphics Port Signals

Unless otherwise specified, PCI Express Graphics signals are AC coupled, so the only voltage

specified is a maximum 1.2 V differential swing.

Signal Name Type Description

EXP_RXN[15:0]

EXP_RXP[15:0]

EXP_TXN[15:0]

EXP_TXP[15:0]

EXP_COMPO I A PCI Express Graphics Output Current Compensation

EXP_COMPI I A PCI Express Graphics Input Current Compensation

EXP_SLR I

I/O

PCIE

O

PCIE

CMOS

PCI Express Graphics Receive Differential Pair

PCI Express Graphics Transmit Differential Pair

Note: EXP_COMP0 is used for DMI current compensation.

Note: EXP_COMPI is used for DMI current compensation.

PCI Express* Static Lane Reversal: The MCH’s PCI Express lane

numbers are reversed. For example, the MCH PCI Express interface

signals can be configured as follows:

Normal Lane

Ball Operation Reversed

C10 EXP_TXP0 EXP_TXP15

A9 EXP_TXP1 EXP_TXP14

… … …

N3 EXP_TXP14… EXP_TXP1…

P1 EXP_TXP15 EXP_TXP0

0 = MCH’s PCI Express lane numbers are reversed

1 = Normal operation

28 Intel

®

82925X/82925XE MCH Datasheet

Page 29

Signal Description

R

2.6 Clocks, Reset, and Miscellaneous

Signal Name Type Description

HCLKP

HCLKN

GCLKP

GCLKN

DREFCLKN

DREFCLKP

RSTIN# I

PWROK I

EXTTS# I

MTYPE I

ICH_SYNC# O

I

CMOS

I

CMOS

I

CMOS

HVIN

HVIN

HVCMOS

CMOS

HVCMOS

Differential Host Clock In: These pins receive a differential host clock

from the external clock synthesizer. This clock is used by all of the MCH

logic that is in the Host clock domain.

Differential PCI Express Graphics Clock In: These pins receive a

differential 100 MHz serial reference clock from the external clock

synthesizer. This clock is used to generate the clocks necessary for the

support of PCI Express.

Display PLL Differential Clock In

Reset In: When asserted, this signal will asynchronously reset the MCH

logic. This signal is connected to the PLTRST# output of the Intel

All PCI Express Graphics Attach output signals will also tri-state

compatible with PCI Express* Specification Rev 1.0a.

This input should have a Schmitt trigger to avoid spurious resets.

This signal is required to be 3.3 V tolerant.

Power OK: When asserted, PWROK is an indication to the MCH that

core power has been stable for at least 10 us.