Page 1

R

Intel® 855PM Chipset Platform

Design Guide

For use with Intel® Pentium® M and Intel® Celeron® M Processors

May 2004

Revision Number 003

Document Number: 252614-003

Page 2

R

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended

for use in medical, life saving, or life sustaining applications.

Actual system-level properties, such as skin temperature, are a function of various factors, including component placement, component power

characteristics, system power and thermal management techniques, software application usage and general system design. Intel is not responsible for its

customers’ system designs, nor is Intel responsible for ensuring that its customers’ products comply with all applicable laws and regulations. Intel

provides this and other thermal design information for informational purposes only. System design is the sole responsibility of Intel’s customers, and

Intel’s customers should not rely on any Intel-provided information as either an endorsement or recommendation of any particular system design

characteristics.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future

definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® Pentium® M processor, Intel® Pentium® M processor on 90nm process with 2-MB L2 Cache, Intel® Celeron® M Processor and Intel® 855PM

Chipset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current

characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Alert on LAN is a result of the Intel-IBM Advanced Manageability Alliance and a trademark of IBM.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

www.intel.com

or call 1-800-548-4725

Intel, the Intel logo, Pentium, Celeron, Intel SpeedStep, and Intel Centrino are trademarks or registered trademarks of Intel Corporation and its

subsidiaries in the United States and other countries.

*Other brands and names are the property of their respective owners.

2 Intel

®

855PM Chipset Platform Design Guide

Page 3

R

Contents

1.

2.

3.

4.

Introduction .................................................................................................................................19

1.1. Terminology ...................................................................................................................19

1.2. Referenced Documents .................................................................................................21

System Overview........................................................................................................................23

2.1. Intel® CentrinoTM Mobile Technology Features..............................................................23

2.2. Intel® Pentium® M Processor/Intel® Celeron® M Processor ............................................25

2.2.1. Architectural Features ....................................................................................25

2.2.1.1. Packaging/Power ............................................................................25

2.3. Intel 855PM Memory Controller Hub (MCH)..................................................................25

2.3.1. Front Side Bus Support..................................................................................25

2.3.2. Integrated System Memory DRAM Controller................................................26

2.3.3. Accelerated Graphics Port (AGP) Interface...................................................26

2.3.4. Packaging/Power ...........................................................................................26

2.4. Intel 82801DBM I/O Controller Hub (ICH4-M) ...............................................................27

2.4.1. Packaging/Power ...........................................................................................27

2.5. Intel PRO/Wireless Network Connection.......................................................................27

2.5.1. Packaging and Power ....................................................................................28

2.6. Firmware Hub (FWH).....................................................................................................28

2.6.1. Packaging/Power ...........................................................................................28

General Design Considerations .................................................................................................29

3.1. Nominal Board Stack-Up ...............................................................................................29

FSB Design Guidelines ..............................................................................................................33

4.1. FSB Design Recommendations.....................................................................................33

4.1.1. Recommended Stack-up Routing and Spacing Assumptions .......................33

4.1.1.1. Trace Space to Trace – Reference Plane Separation Ratio ..........33

4.1.1.2. Trace Space to Trace Width Ratio..................................................34

4.1.1.3. Recommended Stack-up Calculated Coupling Model ....................34

4.1.1.4. Signal Propagation Time to Distance Relationship

and Assumptions.............................................................................35

4.1.2. Common Clock Signals..................................................................................36

4.1.3. Source Synchronous Signals.........................................................................41

4.1.3.1. Source Synchronous General Routing Guidelines .........................41

4.1.3.2. Source Synchronous – Data ...........................................................43

4.1.3.3. Source Synchronous – Address .....................................................44

4.1.3.4. Source Synchronous Signals Recommended Layout Example .....45

4.1.3.5. Trace Length Equalization Procedures...........................................50

4.1.4. Asynchronous Signals....................................................................................51

4.1.4.1. Topologies.......................................................................................51

4.1.4.1.1. Topology 1A: Open Drain (OD) Signal Driven by the

Processor – IERR# .......................................................52

4.1.4.1.2. Topology 1B: Open Drain (OD) Signals Driven by the

Processor – FERR# and THERMTRIP#.......................53

4.1.4.1.3. Topology 1C: Open Drain (OD) Signals Driven by the

Processor – PROCHOT#..............................................54

4.1.4.1.4. Topology 2A: Open Drain (OD) Signal Driven by Intel

82801DBM ICH4-M – PWRGOOD ...............................55

4.1.4.1.5. Topology 2B: CMOS Signals Driven by Intel 82801DBM

ICH4-M – DPSLP#........................................................56

®

Intel

855PM Chipset Platform Design Guide 3

Page 4

5.

R

4.1.4.1.6.

4.1.4.1.7. Topology 3: CMOS Signals Driven by Intel 82801DBM

4.1.4.2. Voltage Translation Logic ............................................................... 60

4.1.5. Processor RESET# Signal ............................................................................ 60

4.1.5.1. Processor RESET# Routing Example............................................ 62

4.1.6. Processor and Intel 855PM MCH Host Clock Signals .................................. 63

4.1.7. GTLREF Layout and Routing Recommendations ......................................... 65

4.1.8. AGTL+ I/O Buffer Compensation .................................................................. 69

4.1.8.1. Processor AGTL+ I/O Buffer Compensation ..................................69

4.1.8.2. Intel 855PM MCH AGTL+ I/O Buffer Compensation...................... 71

4.1.9. Processor FSB Strapping .............................................................................. 73

4.1.10. Processor V

4.2. Intel System Validation Debug Support ........................................................................ 76

4.2.1. In Target Probe (ITP) Support ....................................................................... 76

4.2.1.1. Background and Justification ......................................................... 76

4.2.1.2. Implementation ............................................................................... 76

4.2.2. Processor Logic Analyzer Support (FSB LAI) ............................................... 76

4.2.2.1. Background and Justification ......................................................... 76

4.2.2.2. Implementation ............................................................................... 77

4.2.3. Intel Pentium M Processor and Intel Celeron M Processor On-Die Logic

Analyzer Trigger Support (ODLAT) ............................................................... 77

4.3. Onboard Debug Port Routing Guidelines ..................................................................... 77

4.3.1. Recommended Onboard ITP700FLEX Implementation................................ 78

4.3.1.1. ITP Signal Routing Guidelines........................................................ 78

4.3.1.2. ITP Signal Routing Example........................................................... 82

4.3.1.3. ITP_CLK Routing to ITP700FLEX Connector ................................ 83

4.3.1.4. ITP700FLEX Design Guidelines for Production Systems .............. 85

4.3.2. Recommended ITP Interposer Debug Port Implementation ......................... 86

4.3.2.1. ITP_CLK Routing to ITP Interposer................................................ 86

4.3.2.2. ITP Interposer Design Guidelines for Production Systems ............ 87

4.3.3. Logic Analyzer Interface (LAI) ....................................................................... 87

4.3.3.1. Mechanical Considerations ............................................................88

4.3.3.2. Electrical Considerations ................................................................88

4.4. Intel Pentium M Processor / Intel Celeron M Processor and Intel 855PM MCH FSB

Signal Package Lengths ...............................................................................................88

Platform Power Requirements ................................................................................................... 91

5.1. General Description....................................................................................................... 91

5.2. Intel 855PM MCH Phase Lock Loop Power Delivery Design Guidelines ..................... 91

5.2.1. Intel 855PM MCH PLL Power Delivery.......................................................... 91

5.2.2. Intel 855PM MCH PLL Voltage Supply Power Sequencing .......................... 92

5.3. Processor Phase Lock Loop Power Delivery Design Guidelines ................................. 92

5.3.1. Processor PLL Power Delivery...................................................................... 92

5.3.2. Processor PLL Voltage Supply Power Sequencing ......................................94

5.3.2.1. Voltage Identification for Intel Pentium M/

Intel Celeron M Processor .............................................................. 94

5.3.2.2. V

5.4. V

5.5. V

5.6. Thermal Power Dissipation ........................................................................................... 98

Output Requirements............................................................................................ 97

CCP

Output Requirements .......................................................................................98

CC-MCH

Topology 2C: CMOS Signals Driven by Intel 82801DBM

ICH4-M – LINT0/INTR, LINT1/NMI, A20M#, IGNNE#,

SLP#, SMI#, and STPCLK# .........................................58

ICH4-M to Processor and FWH – INIT#....................... 59

CCSENSE/VSSSENSE

CC-CORE

Power Sequencing ........................................................... 97

Design Recommendations.............................. 75

4 Intel

®

855PM Chipset Platform Design Guide

Page 5

R

6.

5.7.

Voltage Regulator Topology ........................................................................................100

5.8. Voltage Regulator Design Recommendations ............................................................100

5.8.1. High Current Path, Top MOSFET Turned ON .............................................101

5.8.2. High Current Paths During Abrupt Load Current Changes .........................101

5.8.3. High Current Paths During Switching Dead Time........................................102

5.8.4. High Current Path with Bottom MOSFET(s) Turned ON .............................102

5.8.5. General Layout Recommendations .............................................................103

5.9. Processor Decoupling Recommendations ..................................................................104

5.9.1. Transient Response .....................................................................................104

5.9.2. High Frequency, Mid Frequency, and Bulk Decoupling...............................105

5.9.3. Processor Core Voltage Plane and Decoupling ..........................................106

5.9.4. Intel Pentium M Processor / Intel Celeron M Processor

and Intel 855PM MCH V

5.9.4.1. Processor V

5.9.4.2. Intel 855PM MCH V

5.9.5. Intel 855PM MCH Core Voltage Plane and Decoupling ..............................119

System Memory Design Guidelines (DDR-SDRAM)................................................................125

6.1. DDR 200/266/333 MHz System Memory Topology and Layout Design Guidelines ...126

6.1.1. Data Signals – SDQ[71:0], SDQS[8:0].........................................................126

6.1.1.1. Data to Strobe Length Matching Requirements............................129

6.1.1.2. Strobe to Clock Length Matching Requirements ..........................131

6.1.1.3. Data Routing Example ..................................................................133

6.1.1.4. Support for Small Form Factor Design DDR Data Bus Routing...134

6.1.2. Control Signals – SCKE[3:0], SCS#[3:0] .....................................................134

6.1.2.1. Control to Clock Length Matching Requirements .........................136

6.1.2.2. Control Routing Example ..............................................................138

6.1.3. Command Signals – SMA[12:0], SBS[1:0], SRAS#, SCAS#, SWE#...........139

6.1.3.1. Command Topology 1 Solution.....................................................139

6.1.3.1.1. Routing Description for Command Topology 1...........139

6.1.3.1.2. Command Topology 1 to Clock Length Matching

6.1.3.1.3. Command Topology 1 Routing Example ....................143

6.1.3.2. Command Topology 2 Solution.....................................................144

6.1.3.2.1. Routing Description for Command Topology 2...........144

6.1.3.2.2. Command Topology 2 to Clock Length Matching

6.1.3.2.3. Command Topology 2 Routing Example ....................148

6.1.4. Clock Signals – SCK[5:0], SCK#[5:0] ..........................................................149

6.1.4.1. Clock Signal Length Matching Requirements...............................151

6.1.4.1.1. Clock Routing Example...............................................154

6.1.4.2. Intel 855PM Chipset High Density Memory Support ....................155

6.1.5. Feedback – RCVENOUT#, RCVENIN#.......................................................155

6.1.5.1. RCVEN# Routing Example ...........................................................156

6.1.6. Support for “DDP Stacked” SO-DIMM Modules ..........................................157

6.1.7. Recommended Design Option to Support PC2700 DDR SDRAM

with Existing PC1600 and PC2100 Intel 855PM Platforms .........................158

6.1.7.1. Shortened Data Signal Group Trace Length ................................158

6.1.7.1.1. Supporting PC2700 Based on an Existing PC Platform

6.1.7.1.2. Additional Design Considerations for Adapting Intel

6.2. Intel 855PM MCH DDR Signal Package Lengths .......................................................160

Voltage Plane and Decoupling........................114

CCP

Voltage Plane and Decoupling............................114

CCP

Voltage Plane and Decoupling................118

CCP

Requirements..............................................................141

Requirements..............................................................146

Layout .........................................................................158

855PM DDR 200/266 MHz Platforms To Support

PC2700 .......................................................................159

®

Intel

855PM Chipset Platform Design Guide 5

Page 6

7.

8.

9.

R

6.3.

DDR System Memory Interface Strapping .................................................................. 161

6.4. ECC Disable Guidelines.............................................................................................. 161

6.4.1. Intel 855PM MCH ECC Functionality Disable ............................................. 161

6.4.2. DDR Memory ECC Functionality Disable.................................................... 162

6.5. System Memory Compensation .................................................................................. 162

6.6. SMVREF Generation................................................................................................... 162

6.7. DDR Power Delivery ................................................................................................... 162

6.8. External Thermal Sensor Based Throttling (ETS#)..................................................... 163

6.8.1. ETS# Usage Model...................................................................................... 163

6.8.2. ETS# Design Guidelines ............................................................................. 164

6.8.3. Thermal Sensor Placement Guidelines....................................................... 164

AGP Port Design Guidelines.................................................................................................... 167

7.1. AGP Interface.............................................................................................................. 167

7.2. AGP 2.0 Spec.............................................................................................................. 168

7.2.1. AGP Interface Signal Groups ...................................................................... 168

7.3. AGP Routing Guidelines ............................................................................................. 169

7.3.1. 1x Timing Domain Routing Guidelines ........................................................ 169

7.3.1.1. Trace Length Requirements for AGP 1X...................................... 169

7.3.1.2. Trace Spacing Requirements....................................................... 170

7.3.1.3. Trace Length Mismatch ................................................................ 170

7.3.2. 2X/4X Timing Domain Routing Guidelines .................................................. 170

7.3.2.1. Trace Length Requirements for AGP 2X/4X ................................ 170

7.3.2.2. Trace Spacing Requirements....................................................... 171

7.3.2.3. Trace Length Mismatch Requirements ........................................ 172

7.3.3. AGP Clock Skew ......................................................................................... 173

7.3.4. AGP Signal Noise Decoupling Guidelines................................................... 173

7.3.5. AGP Routing Ground Reference ................................................................. 174

7.3.6. Pull-ups........................................................................................................ 174

7.3.7. AGP VDDQ and VREF ................................................................................ 176

7.3.8. VREF Generation for AGP 2.0 (2X and 4X) ................................................ 176

7.3.8.1. 1.5-V AGP Interface (2X/4X) ........................................................ 176

7.3.9. AGP Compensation ..................................................................................... 176

Hub Interface............................................................................................................................ 177

8.1. Hub Interface Compensation ...................................................................................... 177

8.2. Hub Interface Data HI[7:0] and Strobe Signals........................................................... 177

8.2.1. Internal Layer Routing ................................................................................. 178

8.2.2. External Layer Routing ................................................................................ 178

8.3. Hub Interface Data HI[10:8] Signals............................................................................ 179

8.3.1. Internal Layer Routing ................................................................................. 179

8.3.2. External Layer Routing ................................................................................ 179

8.3.3. Terminating HI[11] ....................................................................................... 179

8.4. HIREF/HI_VSWING Generation/Distribution ..............................................................179

8.5. Hub Interface Decoupling Guidelines.......................................................................... 181

I/O Subsystem.......................................................................................................................... 183

9.1. IDE Interface................................................................................................................ 183

9.1.1. Cabling......................................................................................................... 183

9.1.2. Primary IDE Connector Requirements ........................................................ 184

9.1.3. Secondary IDE Connector Requirements ................................................... 185

9.1.4. Mobile IDE Swap Bay Support ....................................................................186

9.1.4.1. Intel 82801DBM ICH4-M IDE Interface Tri-State Feature............ 186

9.1.4.2. S5/G3 to S0 Boot Up Procedures for IDE Swap Bay................... 187

6 Intel

®

855PM Chipset Platform Design Guide

Page 7

R

9.1.4.3.

9.1.4.4. Power Up Procedures After Device “Hot” Swap Completed ........187

9.2. PCI ...............................................................................................................................188

9.3. AC’97 ...........................................................................................................................188

9.3.1. AC’97 Routing ..............................................................................................192

9.3.2. Motherboard Implementation .......................................................................193

9.3.2.1. Valid Codec Configurations ..........................................................193

9.3.3. SPKR Pin Configuration...............................................................................193

9.4. USB 2.0 Guidelines and Recommendations ...............................................................194

9.4.1. Layout Guidelines ........................................................................................194

9.4.1.1. General Routing and Placement...................................................194

9.4.1.2. USB 2.0 Trace Separation ............................................................195

9.4.1.3. USBRBIAS Connection.................................................................195

9.4.1.4. USB 2.0 Termination.....................................................................196

9.4.1.5. USB 2.0 Trace Length Pair Matching ...........................................196

9.4.1.6. USB 2.0 Trace Length Guidelines ................................................196

9.4.2. Plane Splits, Voids, and Cut-Outs (Anti-Etch)..............................................196

9.4.2.1. VCC Plane Splits, Voids, and Cut-Outs (Anti-Etch)......................197

9.4.2.2. GND Plane Splits, Voids, and Cut-Outs (Anti-Etch) .....................197

9.4.3. USB Power Line Layout Topology ...............................................................197

9.4.4. EMI Considerations......................................................................................198

9.4.4.1. Common Mode Chokes ................................................................198

9.4.5. ESD ..............................................................................................................199

9.5. I/O APIC (I/O Advanced Programmable Interrupt Controller) .....................................199

9.6. SMBus 2.0/SMLink Interface .......................................................................................200

9.6.1. SMBus Architecture and Design Considerations.........................................201

9.6.1.1. SMBus Design Considerations .....................................................201

9.6.1.2. General Design Issues/Notes .......................................................202

9.6.1.3. High Power/Low Power Mixed Architecture..................................202

9.6.1.4. Calculating the Physical Segment Pull-Up Resistor .....................202

9.7. FWH .............................................................................................................................204

9.7.1. FWH Decoupling ..........................................................................................204

9.7.2. In Circuit FWH Programming .......................................................................204

9.7.3. FWH INIT# Voltage Compatibility ................................................................204

9.7.4. FWH VPP Design Guidelines ........................................................................205

9.7.5. FWH INIT# Assertion/Deassertion Timings .................................................205

9.8. RTC..............................................................................................................................206

9.8.1. RTC Crystal..................................................................................................207

9.8.2. External Capacitors......................................................................................208

9.8.3. RTC Layout Considerations .........................................................................209

9.8.4. RTC External Battery Connections ..............................................................209

9.8.5. RTC External RTCRST# Circuit...................................................................210

9.8.6. V

9.8.7. SUSCLK .......................................................................................................211

9.8.8. RTC-Well Input Strap Requirements ...........................................................211

9.9. Internal LAN Layout Guidelines ...................................................................................212

9.9.1. Footprint Compatibility .................................................................................212

9.9.2. Intel 82801DBM ICH4-M – LAN Connect Interface Guidelines ...................213

9.9.2.1. Bus Topologies .............................................................................213

9.9.2.2. Signal Routing and Layout............................................................214

Power Down Procedures for Mobile Swap Bay ............................187

DC Voltage and Noise Measurements................................................211

BIAS

9.9.2.1.1. LOM (LAN On Motherboard) Point-To-Point

Interconnect ................................................................214

®

Intel

855PM Chipset Platform Design Guide 7

Page 8

10.

11.

R

9.9.2.3.

9.9.2.4. Impedances .................................................................................. 215

9.9.2.5. Line Termination........................................................................... 215

9.9.2.6. Terminating Unused LAN Connect Interface Signals................... 215

9.9.3. Intel 82562ET / Intel 82562 EM Guidelines................................................. 215

9.9.3.1. Guidelines for Intel 82562ET / Intel 82562EM Component

9.9.3.2. Crystals and Oscillators................................................................ 216

9.9.3.3. Intel 82562ET / Intel 82562EM Termination Resistors................. 216

9.9.3.4. Critical Dimensions....................................................................... 217

9.9.3.5. Reducing Circuit Inductance ........................................................ 218

9.9.4. Intel 82562ET/EM Disable Guidelines......................................................... 220

9.9.5. Design and Layout Consideration for Intel 82540EP / 82551QM ............... 221

9.9.6. General Intel 82562ET / 82562EM / 82551QM / 82540EP Differential Pair

9.9.6.2. Common Physical Layout Issues ................................................. 224

9.10. Power Management Interface ..................................................................................... 225

9.10.1. SYS_RESET# Usage Model ....................................................................... 225

9.10.2. PWRBTN# Usage Model............................................................................. 225

9.10.3. Power Well Isolation Control Strap Requirements ...................................... 225

9.11. CPU I/O Signals Considerations .................................................................................226

Platform Clock Routing Guidelines .......................................................................................... 229

10.1. Clock Routing Guidelines ............................................................................................ 229

10.2. Clock Group Topology and Layout Routing Guidelines.............................................. 232

10.2.1. HOST_CLK Clock Group............................................................................. 232

10.2.1.1. BCLK Length Matching Requirements .........................................234

10.2.1.2. BCLK General Routing Guidelines............................................... 235

10.2.1.3. EMI constraints ............................................................................. 235

10.2.2. CLK66 Clock Group..................................................................................... 236

10.2.3. AGPCLK Clock Group ................................................................................. 237

10.2.4. CLK33 Clock Group..................................................................................... 238

10.2.5. PCICLK Clock Group................................................................................... 239

10.2.6. USBCLK Clock Group ................................................................................. 242

10.2.7. CLK14 Clock Group..................................................................................... 243

10.2.8. CK-408 Clock Chip Decoupling ................................................................... 243

10.3. CK-408 Updates for Systems based on Intel Pentium M Processor / Intel Celeron M

Processor and Intel 855PM Chipset ...........................................................................244

10.4. CK-408 PWRDWN# Signal Connections.................................................................... 244

Platform Power Delivery Guidelines ........................................................................................ 245

11.1. Definitions.................................................................................................................... 245

11.2. Platform Power Requirements ....................................................................................246

11.2.1. Platform Power Delivery Architectural Block Diagram ................................ 247

11.3. Voltage Supply ............................................................................................................248

Crosstalk Consideration ............................................................... 215

Placement..................................................................................... 216

9.9.3.4.1. Distance from Magnetics Module to RJ-45 (Distance A)218

9.9.3.4.2. Distance from Intel 82562ET / 82562ET to Magnetics

Module (Distance B)................................................... 218

9.9.3.5.1. Terminating Unused Connections.............................. 219

9.9.3.5.2. Termination Plane Capacitance ................................. 219

Trace Routing Considerations ..................................................................... 221

9.9.6.1.1. Trace Geometry and Length ...................................... 222

9.9.6.1.2. Signal Isolation ........................................................... 222

9.9.6.1.3. Magnetics Module General Power and Ground Plane

Considerations............................................................ 223

8 Intel

®

855PM Chipset Platform Design Guide

Page 9

R

12.

13.

14.

11.3.1.

11.4. Intel 855PM MCH / 82801DBM ICH4-M Platform Power-Up Sequence.....................248

11.4.1. Intel 82801DBM ICH4-M Power Sequencing Requirements.......................251

11.4.2. Intel 855PM MCH Power Sequencing Requirements..................................253

11.4.3. DDR Power Sequencing Requirements ......................................................253

11.5. DDR Power Delivery Design Guidelines .....................................................................254

11.5.1. DDR Interface Decoupling Guidelines .........................................................255

11.5.2. 2.5-V Power Delivery Guidelines .................................................................255

11.5.3. DDR Reference Voltage...............................................................................256

11.5.4. DDR SMRCOMP Resistive Compensation .................................................262

11.5.5. DDR VTT Termination..................................................................................262

11.5.6. DDR SMRCOMP, SMVREF, VTT 1.25-V Supply Disable in S3/Suspend ..262

11.6. Clock Driver Power Delivery Guidelines......................................................................263

11.7. Decoupling Recommendations....................................................................................265

11.7.1. Processor Decoupling Guidelines................................................................265

11.7.2. Intel 855PM MCH Decoupling Guidelines....................................................265

11.7.3. Intel 82801DBM ICH4-M Decoupling Guidelines.........................................265

11.7.4. DDR VTT High Frequency and Bulk Decoupling.........................................267

11.7.5. AGP Decoupling...........................................................................................267

11.7.6. Hub Interface Decoupling.............................................................................267

11.7.7. FWH Decoupling ..........................................................................................267

11.7.8. General LAN Decoupling .............................................................................267

11.7.9. CK-408 Clock Driver Decoupling .................................................................268

11.8. Intel 855PM MCH Power Consumption Numbers .......................................................268

11.9. Intel 82801DBM ICH4-M Power Consumption Numbers ............................................269

11.10. Thermal Design Power ................................................................................................270

Intel® PRO/Wireless 2100 and Bluetooth Design Requirements .............................................271

12.1. PCB Interface Requirements .......................................................................................271

12.2. DC Power Requirements for Bluetooth .......................................................................271

12.3. Selective Suspend Support .........................................................................................272

12.4. Wake on Bluetooth Requirements...............................................................................272

12.5. RF Disable Support Requirements for Intel PRO/Wireless 2100

Reserved, NC, and Test Signals ..............................................................................................273

13.1. Intel Pentium M Processor and Intel Celeron M RSVD Signals ..................................273

13.2. Intel 855PM MCH RSVD Signals.................................................................................274

Platform Design Checklist ........................................................................................................275

14.1. General Information .....................................................................................................275

14.2. Customer Implementation............................................................................................276

14.3. Design Checklist Implementation ................................................................................276

14.4. Intel Pentium M Processor and Intel Celeron M Processor..........................................277

Power Management States..........................................................................248

11.4.1.1. 3.3/1.5 V and 3.3/1.8 V Power Sequencing..................................251

11.4.1.2. V

11.4.1.3. V

11.5.1.1. Intel 855PM MCH VCCSM Decoupling Guidelines ......................255

11.5.1.2. DDR SO-DIMM System Memory Decoupling Guidelines.............255

11.5.3.1. SMVREF Design Recommendations............................................259

11.5.3.2. DDR VREF Requirements ............................................................261

11.5.6.1. VTT Rail Power Down Sequencing During Suspend ...................262

11.5.6.2. VTT Rail Power Up Sequencing During Resume.........................263

and Bluetooth Devices.................................................................................................272

3.3 V Sequencing................................................................251

5REF/

5REF_SUS

Design Guidelines .........................................................251

®

Intel

855PM Chipset Platform Design Guide 9

Page 10

15.

R

14.4.1.

14.4.2. In Target Probe (ITP)................................................................................... 284

14.4.3. Thermal Sensor ........................................................................................... 288

14.4.4. Decoupling Recommendations.................................................................... 288

14.5. CK-408 Clock Checklist............................................................................................... 290

14.5.1. Resistor Recommendations ........................................................................ 290

14.5.2. CK-408 Decoupling Recommendation ........................................................ 292

14.6. Intel 855PM MCH Checklist ........................................................................................293

14.6.1. System Memory........................................................................................... 293

14.6.2. Miscellaneous Signals ................................................................................. 298

14.6.3. Resistive Compensation.............................................................................. 300

14.6.4. Decoupling Recommendations (MCH)........................................................ 301

14.6.5. Memory Decoupling Recommendation ....................................................... 301

14.6.6. MCH Reference Voltage.............................................................................. 302

14.7. AGP Interface.............................................................................................................. 303

14.7.1. Resistor Recommendations ........................................................................ 303

14.8. ICH4-M Checklist ........................................................................................................ 306

14.8.1. ICH4-M Resistor Recommendations........................................................... 306

14.8.2. GPIO ............................................................................................................ 308

14.8.3. AGP Busy/Stop Design Requirements........................................................ 309

14.8.4. System Management Bus (SMBus) Interface ............................................. 310

14.8.5. AC ’97 Interface ........................................................................................... 311

14.8.6. ICH4-M Power Management Interface........................................................ 312

14.8.7. FWH/LPC Interface...................................................................................... 314

14.8.8. USB Interface .............................................................................................. 314

14.8.9. Hub Interface ............................................................................................... 315

14.8.10. RTC Circuitry ............................................................................................... 317

14.8.11. LAN Interface............................................................................................... 319

14.8.12. Primary IDE Interface .................................................................................. 320

14.8.13. IDE Interface (Secondary IDE Connector) ..................................................321

14.8.14. Miscellaneous Signals ................................................................................. 322

14.8.15. ICH4-M Power Signals & Decoupling Recommendations .......................... 323

14.9. USB Checklist ............................................................................................................. 324

14.9.1. Resistor Recommendations ........................................................................ 324

14.9.2. Decoupling Recommendations.................................................................... 325

14.10. FWH Checklist............................................................................................................. 325

14.10.1. Resistor Recommendations ........................................................................ 325

14.10.2. Decoupling Recommendations.................................................................... 325

14.11. LAN / HomePNA Checklist.......................................................................................... 326

14.11.1. LAN Interface (82562ET / 82562EM) .......................................................... 326

Intel Customer Reference Board Schematics.......................................................................... 329

Resistor Recommendations ........................................................................ 277

14.4.2.1. ITP700FLEX Connector

14.4.2.2. ITP Interposer

14.4.2.3. Required Strapping when ITP Debug Port Disable

14.6.1.1. MCH System Memory Interface ................................................... 293

14.6.1.2. DDR SO-DIMM Interface.............................................................. 296

14.7.1.1. AGP Connector ............................................................................ 304

14.7.1.2. AGP Decoupling Recommendations............................................ 304

14.7.1.3. AGP VREF Reference Voltage Dividers ...................................... 304

14.8.9.1. Hub Interface Resistor Recommendations .................................. 315

14.8.9.2. Reference Voltage Dividers.......................................................... 315

14.11.1.1. Resistor Recommendations .........................................................326

14.11.1.2. Decoupling Recommendations .................................................... 327

1, 2

.......................................................................... 287

1, 2

.......................................................... 284

1, 2

................. 288

10 Intel

®

855PM Chipset Platform Design Guide

Page 11

R

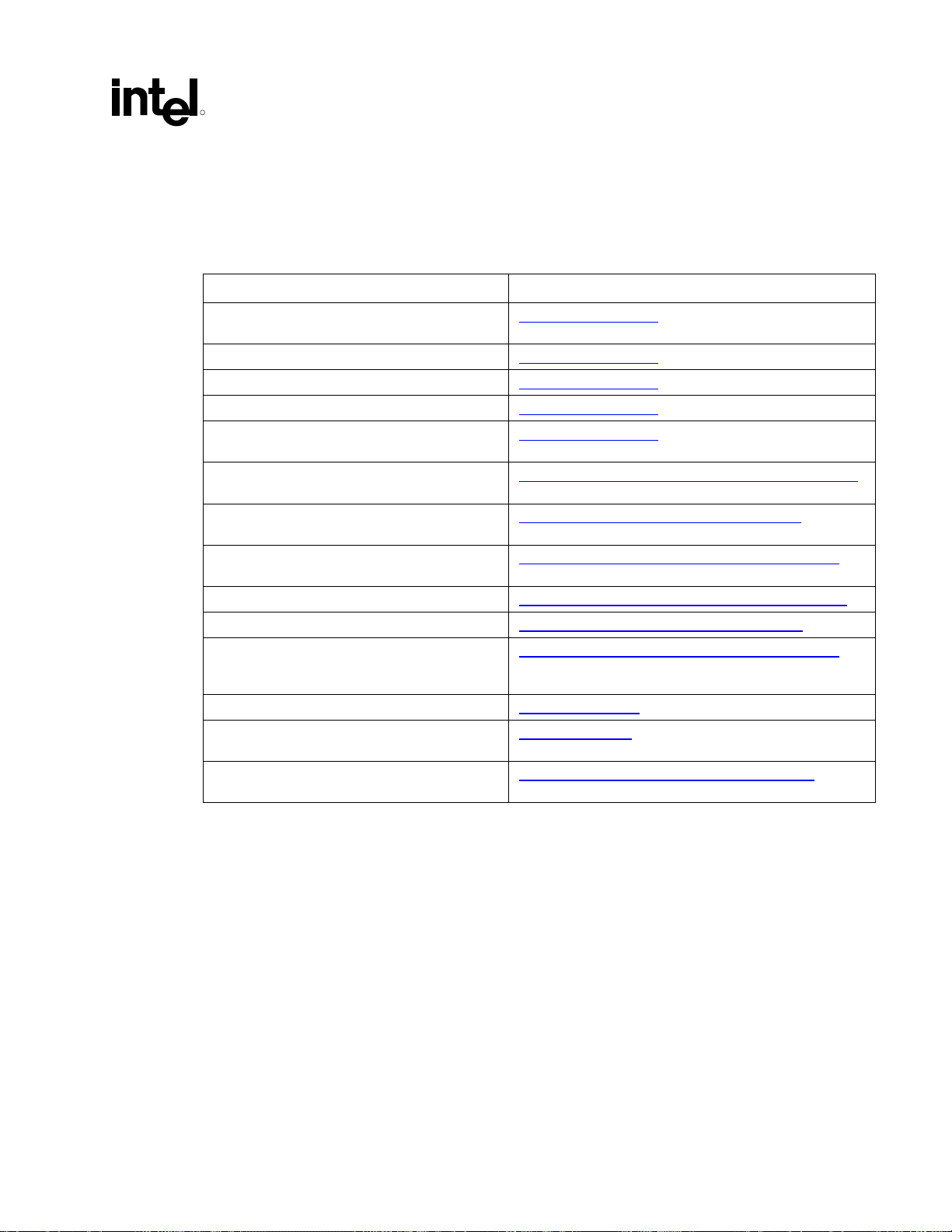

Figures

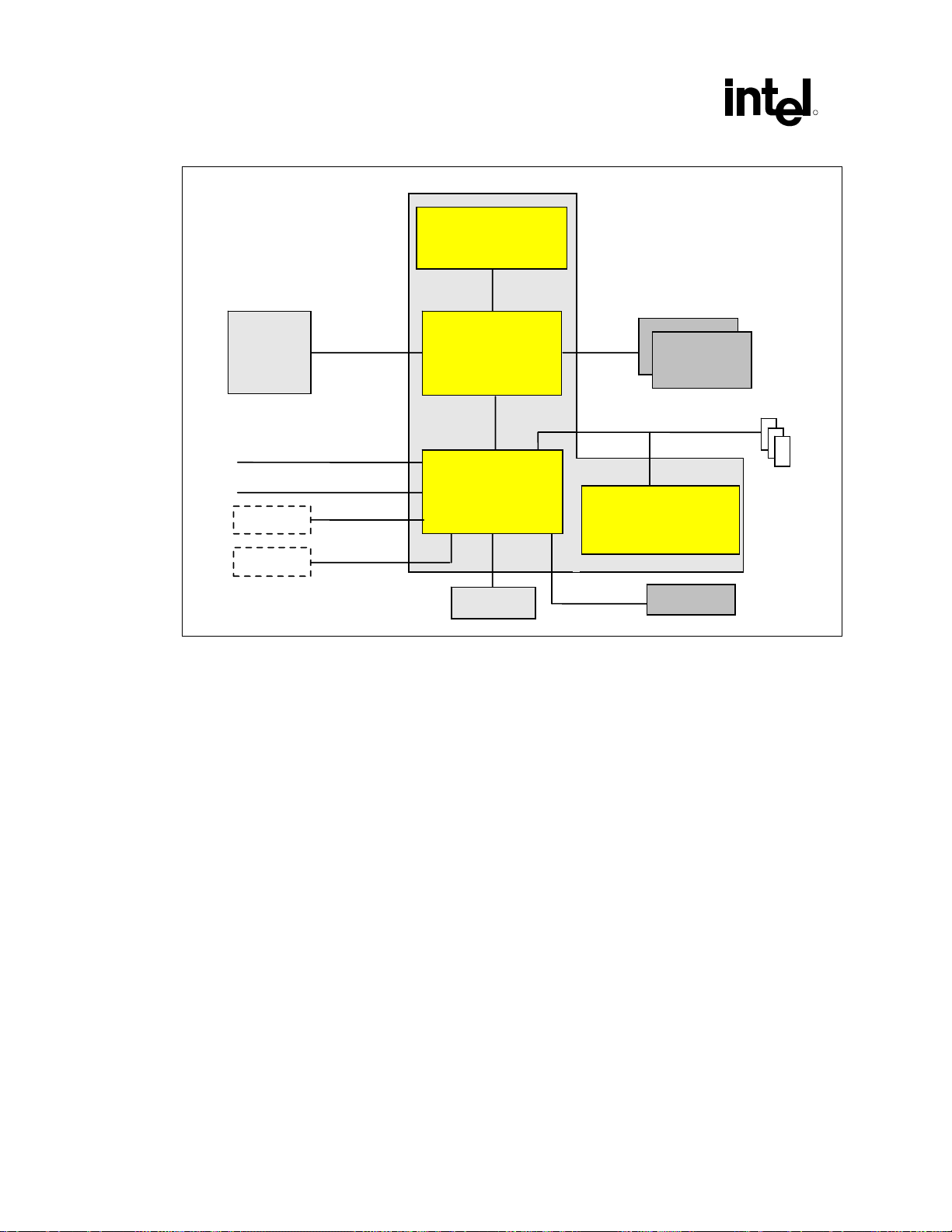

Figure 1. Basic System Block Diagram ................................................................................... 24

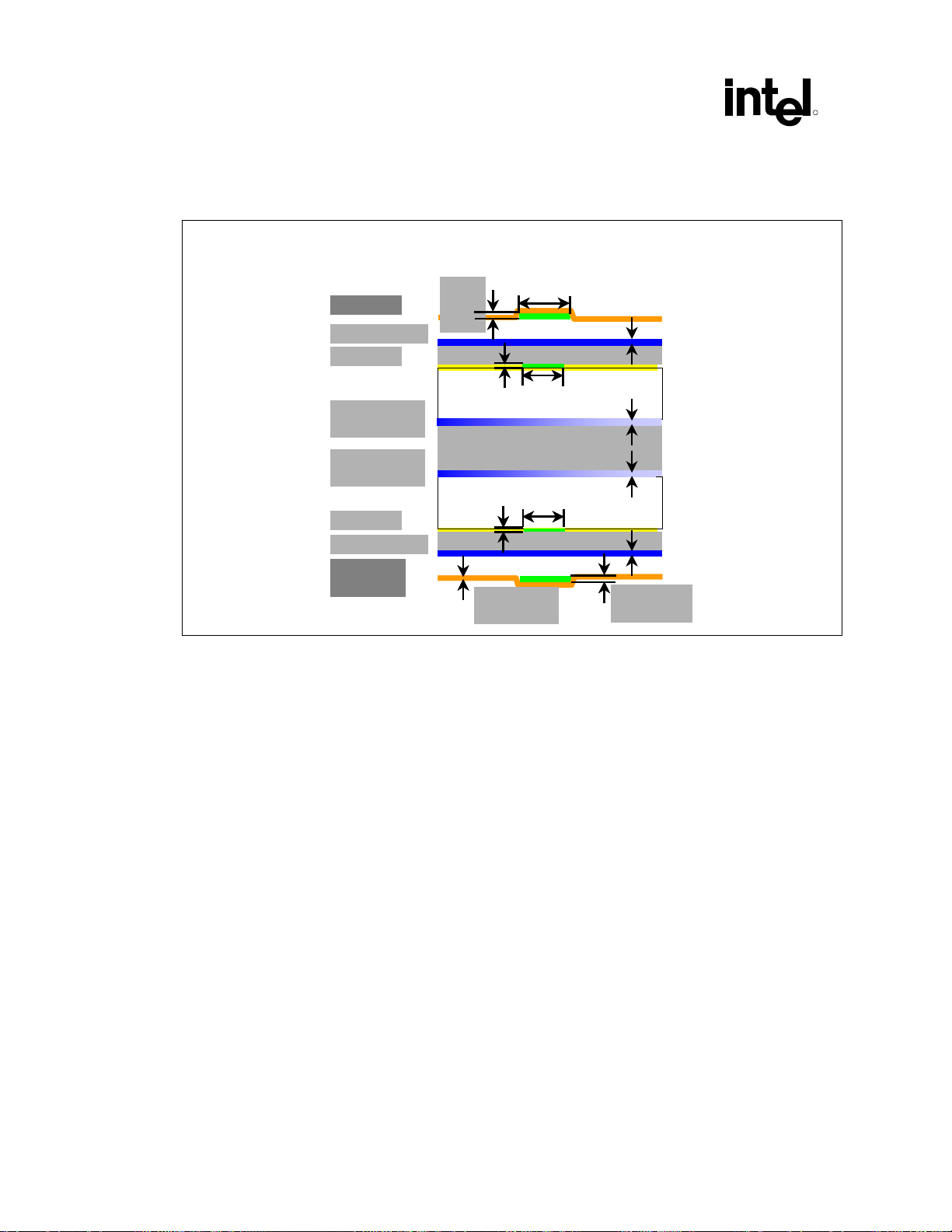

Figure 2. Recommended Board Stack-Up Dimensions .......................................................... 30

Figure 3. Trace Spacing vs. Trace to Reference Plane Example ........................................... 34

Figure 4. Trace Spacing vs. Trace Width Example................................................................. 34

Figure 5. Recommended Stack-up Capacitive Coupling Model ............................................. 35

Figure 6. Common Clock Signals Example – Intel 855PM MCH Escape Routing ................. 39

Figure 7. Common Clock Signals Example – Processor Escape Routing.............................. 39

Figure 8. Common Clock Signals Example – Processor to Intel 855PM MCH

Layer 6 Routing........................................................................................................ 40

Figure 9. Layer 6 FSB Source Synchronous Signals GND Referencing

to Layer 5 and Layer 7 Ground Planes.................................................................... 42

Figure 10. Layer 3 FSB Source Synchronous Signals GND Referencing

to Layer 2 and Layer 4 Ground Planes.................................................................... 42

Figure 11. Intel 855PM MCH Source Synchronous Signals Recommended Escape Routing

Example ................................................................................................................... 47

Figure 12. Processor Source Synchronous Signals Recommended Escape Routing

Example ................................................................................................................... 48

Figure 13. Processor to Intel 855PM MCH Source Synchronous Signals Routing Example .49

Figure 14. Reference Trace Length Selection ........................................................................ 50

Figure 15. Trace Length Equalization Procedures with Allegro*............................................. 51

Figure 16. Routing Illustration for Topology 1A....................................................................... 52

Figure 17. Routing Illustration for Topology 1B....................................................................... 53

Figure 18. Routing Illustration for Topology 1C....................................................................... 54

Figure 19. Routing Illustration for Topology 2A....................................................................... 55

Figure 20. Routing Illustration for Topology 2B....................................................................... 56

Figure 21. DPSLP# Layout Routing Example ......................................................................... 57

Figure 22. Routing Illustration for Topology 2C....................................................................... 58

Figure 23. Routing Illustration for Topology 3 ......................................................................... 59

Figure 24. Voltage Translation Circuit ..................................................................................... 60

Figure 25. Processor RESET# Signal Routing Topology with NO ITP700FLEX Connector .. 61

Figure 26. Processor RESET# Signal Routing Topology With ITP700FLEX Connector........ 61

Figure 27. Processor RESET# Signal Routing Example with ITP700FLEX Debug Port........ 62

Figure 28. Processor and Intel 855PM MCH Host Clock Layout Routing Example ............... 64

Figure 29. Processor GTLREF Voltage Divider Network ........................................................ 65

Figure 30. Processor GTLREF Motherboard Layout .............................................................. 66

Figure 31. Intel 855PM MCH HVREF[4:0] Reference Voltage Generation Circuit ................. 67

Figure 32. Intel 855PM MCH HVREF[4:0] Motherboard Layout ............................................. 68

Figure 33. Processor COMP[3:0] Resistor Layout .................................................................. 70

Figure 34. Processor COMP[1:0] Resistor Alternative Primary Side Layout .......................... 70

Figure 35. Processor COMP[2] and COMP[0] 18-Mil Wide Dog Bones and Traces .............. 71

Figure 36. Intel 855PM MCH HRCOMP[1:0] Resistor Layout................................................. 72

Figure 37. Intel 855PM MCH HSWNG[1:0] Reference Voltage Generation Circuit................ 72

Figure 38. Intel 855PM MCH HSWNG[1:0] Layout ................................................................. 73

Figure 39. Processor Strapping Resistor Layout .................................................................... 74

Figure 40. V

Figure 41. ITP700FLEX Debug Port Signals........................................................................... 79

Figure 42. ITP_CLK to ITP700FLEX Connector Layout Example .......................................... 84

Figure 43. ITP700FLEX Signals Layout Example ................................................................... 85

Figure 44. ITP_CLK to CPU ITP Interposer Layout Example ................................................. 87

Figure 45. Intel 855PM MCH 1.8 V V

Figure 46. Processor 1.8 V VCCA[3:0] Recommended Power Delivery and Decoupling ...... 94

CCSENSE/VSSSENSE

Routing Example....................................................................... 75

CCGA

and V

Recommended Power Delivery ........... 92

CCHA

®

Intel

855PM Chipset Platform Design Guide 11

Page 12

Figure 47. Intel® Pentium® M Processor / Intel® Celeron® M Processor VID[5:0] Escape

Routing Layout Example ..........................................................................................95

Figure 48. Power On Sequencing Timing Diagram .................................................................97

Figure 49. V

Figure 50. V

Figure 51. Voltage Regulator Multi-Phase Topology Example.............................................. 100

Figure 52. Buck Voltage Regulator Example......................................................................... 101

Figure 53. High Current Path With Top MOSFET Turned ON ..............................................101

Figure 54. High Current Path During Abrupt Load Current Changes.................................... 102

Figure 55. High Current Path with Top and Bottom MOSFETs Turned Off (Dead Time) .....102

Figure 56. High Current Path With Bottom MOSFET(s) Turned ON .....................................103

Figure 57. Estimated Processor Current Consumption Change During STPCLK Exit .........105

Figure 58. Intel Pentium M Processor and Intel Celeron M ProcessorSocket Core Power

Figure 59. Processor Core Power Delivery and Decoupling Concept................................... 108

Figure 60. V

Figure 61. Processor Core Power Delivery “North Corridor” Zoom In View.......................... 112

Figure 62. V

Figure 63. Recommended SP Cap Via Connection Layout (Secondary Side Layer) ...........113

Figure 64. Processor V

Figure 65. Processor V

Figure 66. Intel 855PM MCH V

Figure 67. Intel 855PM MCH V

Figure 68. Intel 855PM MCH V

Figure 69. V

Figure 70. V

Figure 71. V

Figure 72. Data Signal Routing Topology.............................................................................. 127

Figure 73. DQ/CB to DQS Trace Length Matching Requirements ........................................ 130

Figure 74. SDQS to SCK/SCK# Trace Length Matching Requirements ...............................132

Figure 75. Data Signals Group Routing Example.................................................................. 133

Figure 76. Control Signal Routing Topology.......................................................................... 135

Figure 77. Control Signal to SCK/SCK# Trace Length Matching Requirements................... 137

Figure 78. Control Signals Group Routing Example.............................................................. 138

Figure 79. Command Signal Routing for Topology 1............................................................. 139

Figure 80. Command Signal to SCK/SCK# Trace Length Matching Requirements.............. 142

Figure 81. Command Signals Topology 1 Routing Example................................................. 143

Figure 82. Command Signal Routing for Topology 2............................................................. 144

Figure 83. Command Signal to SCK/SCK# Trace Length Matching Requirements.............. 147

Figure 84. Command Signals Topology 2 Routing Example................................................. 148

Figure 85. DDR Clock Routing Topology (SCK/SCK#[5:0]) .................................................. 149

Figure 86. SCK/SCK# Trace Length Matching Requirements ..............................................152

Figure 87. Clock Pair Trace Length Matching Requirements1...............................................153

Figure 88. Clock Signal Routing Example .............................................................................154

Figure 89. DDR Feedback (RCVEN#) Routing Topology...................................................... 155

Figure 90. RCVEN# Signal Routing Example........................................................................ 157

Figure 91. Data Signal Group (SDQ[71:0], SDQS[8:0]) Routing Topology –

Figure 92. DDR Memory Thermal Sensor Placement ...........................................................165

Figure 93. AGP Layout Guidelines ........................................................................................171

Figure 94. Hub Interface Routing Example............................................................................ 177

Figure 95. Hub Interface with Single Reference Voltage Divider Circuit ...............................180

Block Diagram ................................................................................................98

CCP

Block Diagram............................................................................................ 98

CC-MCH

Delivery Corridor..................................................................................................... 107

CC-CORE

(Primary and Secondary Side Layers) ................................................................... 112

CC-CORE

Example.................................................................................................................. 118

CC-MCH

CC-MCH

CC-MCH

PC2700, PC2100 and PC1600 Compliant .............................................................158

Power Delivery and Decoupling Example –

Power Delivery and Decoupling Example (Layers 3, 5, and 6) .............113

Power Delivery and Decoupling Concept ...................................116

CCP

Power Plane and Decoupling Example ......................................117

CCP

Power Plane and Decoupling Concept........................... 118

CCP

Power Plane and Decoupling Recommended Layout

CCP

Power Delivery Recommended Layout (Zoom In View). 119

CCP

Power Delivery and Decoupling Concept ................................................ 121

Power Planes and Decoupling Example .................................................122

Secondary Layer Decoupling Capacitor Placement (Zoom in View) ......123

R

12 Intel

®

855PM Chipset Platform Design Guide

Page 13

R

Figure 96. Hub Interface with Locally Generated Reference Voltage Divider Circuit ........... 180

Figure 97. Connection Requirements for Primary IDE Connector ........................................ 184

Figure 98. Connection Requirements for Secondary IDE Connector ................................... 185

Figure 99. PCI Bus Layout Example ..................................................................................... 188

Figure 100. Intel 82801DBM ICH4-M AC’97 – Codec Connection ....................................... 189

Figure 101. Intel 82801DBM ICH4-M AC’97 – AC_BIT_CLK Topology ............................... 190

Figure 102. Intel 82801DBM ICH4-M AC’97 – AC_SDOUT/AC_SYNC Topology ............... 190

Figure 103. Intel 82801DBM ICH4-M AC’97 – AC_SDIN Topology ..................................... 191

Figure 104. Example Speaker Circuit.................................................................................... 194

Figure 105. Recommended USB Trace Spacing .................................................................. 195

Figure 106. USBRBIAS Connection...................................................................................... 196

Figure 107. Good Downstream Power Connection............................................................... 198

Figure 108. Common Mode Choke Schematic ..................................................................... 198

Figure 109. SMBUS 2.0/SMLink Protocol ............................................................................. 201

Figure 110. High Power/Low Power Mixed VCC_

Figure 111. FWH VPP Isolation Circuitry .............................................................................. 205

Figure 112. RTCX1 and SUSCLK Relationship in Intel 82801DBM ICH4-M........................ 206

Figure 113. External Circuitry for Intel 82801DBM ICH4-M Where the Internal RTC

is Not Used............................................................................................................. 206

Figure 114. External Circuitry for the Intel 82801DBM ICH4-M RTC.................................... 207

Figure 115. Diode Circuit to Connect RTC External Battery ................................................. 210

Figure 116. RTCRST# External Circuit for the ICH4-M RTC ................................................ 210

Figure 117. Intel 82801DBM ICH4-M/Platform LAN Connect Section.................................. 213

Figure 118. Single Solution Interconnect .............................................................................. 214

Figure 119. LAN_CLK Routing Example............................................................................... 215

Figure 120. Intel 82562ET / Intel 82562EM Termination ...................................................... 217

Figure 121. Critical Dimensions for Component Placement ................................................. 217

Figure 122. Termination Plane .............................................................................................. 219

Figure 123. Example Intel 82562ET/EM Disable and Power Down Circuitry ....................... 220

Figure 124. Trace Routing..................................................................................................... 222

Figure 125. Ground Plane Separation................................................................................... 223

Figure 126. RTC Power Well Isolation Control ..................................................................... 226

Figure 127. Intel 82801DBM ICH4-M CPU CMOS Signals with CPU and FWH .................. 227

Figure 128. Platform Clock Topology Diagram ..................................................................... 231

Figure 129. Source Shunt Termination Topology ................................................................. 232

Figure 130. Clock Skew as Measured from Agent-to-Agent................................................. 235

Figure 131. CLK66 Group Topology ..................................................................................... 236

Figure 132. AGPCLK to AGP Connector Topology .............................................................. 237

Figure 133. AGPCLK to AGP Device Down Topology.......................................................... 237

Figure 134. CLK33 Group Topology ..................................................................................... 239

Figure 135. PCICLK Group to PCI Device Down Topology .................................................. 240

Figure 136. PCICLK Group to PCI Slot Topology ................................................................. 241

Figure 137. USBCLK Group Topology .................................................................................. 242

Figure 138. CLK14 Group Topology ..................................................................................... 243

Figure 139. Platform Power Delivery Map............................................................................. 247

Figure 140. Intel® 855PM/82801DBM Platform Power-Up Sequence................................... 249

Figure 141. Example V

Figure 142. V5REF_SUS With 5V_ALWAYS Connection Option ........................................ 252

Figure 143. V5REF_SUS With 3.3V_ALWAYS and VCC5 or

VCC5_SUS Connection Option ............................................................................. 252

Figure 144. DDR Power Delivery Block Diagram.................................................................. 254

Figure 145. Decoupling Capacitors Placement and Connectivity ......................................... 264

Figure 146. Minimized Loop Inductance Example ................................................................ 266

Figure 147. Recommended Topology for Coexistence Traces............................................. 271

/ 3.3 V Sequencing Circuitry ...................................................... 251

5REF

SUSPEND/VCC_CORE

Architecture ................... 202

®

Intel

855PM Chipset Platform Design Guide 13

Page 14

Figure 148. Processor GTLREF Voltage Divider Network ....................................................282

Figure 149. Routing Illustration for INIT# ............................................................................... 282

Figure 150. Voltage Translation Circuit..................................................................................283

Figure 151. Routing Illustration for PROCHOT#.................................................................... 283

Figure 152. Clock Power Down Implementation.................................................................... 292

Figure 153. Reference Voltage Level for SMVREF[1:0] ........................................................ 295

Figure 154. Intel 855PM MCH HSWNG[1:0] Reference Voltage Generation Circuit ...........299

Figure 155. Intel 855PM MCH HVREF[4:0] Generation Circuit............................................. 299

Figure 156. AGPREF Implementation (On Intel CRB)........................................................... 305

Figure 157. Hub Interface with Signal Reference Voltage Divider Circuit .............................316

Figure 158. Hub Interface with Locally Generated Reference Voltage Divider Circuit.......... 316

Figure 159 External Circuitry for the RTC.............................................................................. 318

Figure 160. USBPWR_CONN[E:A] Design Recommendation.............................................. 324

Figure 161. LAN_RST# Design Recommendation (On Intel CRB) .......................................327

R

14 Intel

®

855PM Chipset Platform Design Guide

Page 15

R

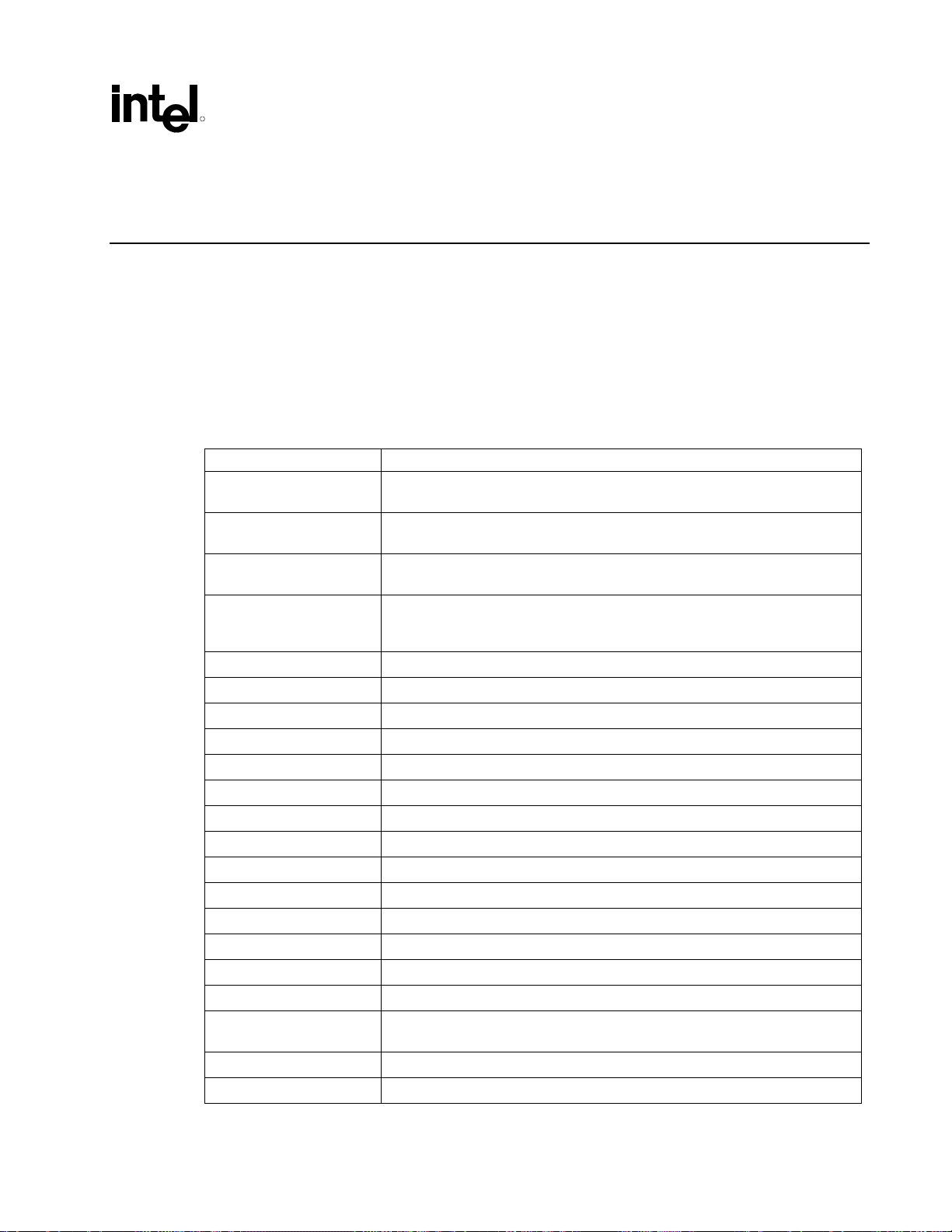

Tables

Table 1. FSB Common Clock Signal Internal Layer Routing Guidelines ................................ 37

Table 2. FSB Common Clock Signal External Layer Routing Guidelines.............................. 38

Table 3. FSB Data Source Synchronous Signal Trace Length Mismatch Mapping ............... 43

Table 4. FSB Source Synchronous Data Signal Routing Guidelines Topology 1................... 44

Table 5. FSB Source Synchronous Data Signal Routing Guidelines Topology 2................... 44

Table 6. FSB Address Source Synchronous Signal Trace Length Mismatch Mapping......... 45

Table 7. FSB Source Synchronous Address Signal Routing Guidelines ................................ 45

Table 8. Layout Recommendations for Topology 1A .............................................................. 52

Table 9. Layout Recommendations for Topology 1B .............................................................. 53

Table 10. Layout Recommendations for Topology 1C............................................................ 54

Table 11. Layout Recommendations for Topology 2A ............................................................ 55

Table 12. Layout Recommendations for Topology 2B ............................................................ 56

Table 13. Layout Recommendations for Topology 2C............................................................ 58

Table 14. Layout Recommendations for Topology 3 .............................................................. 59

Table 15. Processor RESET# Signal Routing Guidelines with ITP700FLEX Connector........ 62

Table 16. ITP Signal Default Strapping When ITP Debug Port Not Used .............................. 74

Table 17. Recommended ITP700FLEX Signal Terminations ................................................. 82

Table 18. Processor and MCH FSB Signal Package Trace Lengths...................................... 89

Table 19. VID vs. V

Table 20. V

Table 21. V

Table 22. V

Table 23. Intel 855PM Chipset DDR Signal Groups ............................................................. 125

Table 24. Data Signal Group Routing Guidelines ................................................................. 127

Table 25. SDQ[71:0] to SDQS[8:0] Length Mismatch Mapping ............................................ 129

Table 26. Control Signal to SO-DIMM Mapping .................................................................... 134

Table 27. Control Signal Routing Guidelines ........................................................................ 135

Table 28. Command Topology 1 Routing Guidelines ........................................................... 140

Table 29. Command Topology 2 Routing Guidelines ........................................................... 145

Table 30. Clock Signal Mapping1........................................................................................... 149

Table 31. Clock Signal Group Routing Guidelines................................................................ 150

Table 32. Feedback Signal Routing Guidelines .................................................................... 156

Table 33. Data Signal Group (SDQ[71:0], SDQS[8:0]) Routing Guidelines –

Table 34. Existing PC2100/PC1600 DDR SDRAM Design Guidelines Required

Table 35. Intel 855PM Chipset DDR Signal Package Lengths ............................................. 160

Table 36. AGP 2.0 Signal Groups ......................................................................................... 168

Table 37. AGP 2.0 Data/Strobe Associations ....................................................................... 169

Table 38. Layout Routing Guidelines for AGP 1X Signals .................................................... 170

Table 39. Layout Routing Guidelines for AGP 2X/4X Signals............................................... 172

Table 40. AGP 2.0 Data Lengths Relative to Strobe Length................................................. 172

Table 41. AGP 2.0 Routing Guideline Summary................................................................... 173

Table 42. AGP Pull-Up/Pull-Down Requirements and Straps .............................................. 175

Table 43. AGP 2.0 Pull-up Resistor Values .......................................................................... 175

Table 44. Hub Interface RCOMP Resistor Values ................................................................ 177

Table 45. Hub Interface Signals Internal Layer Routing Summary....................................... 178

Table 46. Hub Interface Signals External Layer Routing Summary...................................... 179

Table 47. Hub Interface HIREF/HI_VSWING Generation Circuit Specifications .................. 180

Table 48. AC’97 AC_BIT_CLK Routing Summary ................................................................ 190

CC-CORE

CCP

CC-MCH

PC2700, PC2100 and PC1600 Compliant ............................................................ 158

for PC2700 Support ............................................................................................... 159

CC-CORE

Decoupling Guidelines1........................................................................... 109

Decoupling Guidelines .................................................................................. 114

Decoupling Guidelines.............................................................................. 120

Voltage ......................................................................................... 96

®

Intel

855PM Chipset Platform Design Guide 15

Page 16

Table 49. AC’97 AC_SDOUT/AC_SYNC Routing Summary ................................................ 191

Table 50. AC’97 AC_SDIN Routing Summary....................................................................... 191

Table 51. Supported Codec Configurations........................................................................... 193

Table 52. USBRBIAS/USBRBIAS# Routing Summary.......................................................... 196

Table 53. USB 2.0 Trace Length Guidelines (With Common-mode Choke) .........................196

Table 54. Bus Capacitance Reference Chart ........................................................................203

Table 55. Bus Capacitance/Pull-Up Resistor Relationship.................................................... 203

Table 56. RTC Routing Summary.......................................................................................... 207

Table 57. LAN Component Connections/Features ................................................................ 212

Table 58. LAN Design Guide Section Reference ..................................................................213

Table 59. LAN LOM Routing Summary .................................................................................214

Table 60. Intel 82562ET/EM Control Signals......................................................................... 220

Table 61. Intel 855PM Chipset Clock Groups........................................................................ 229

Table 62. Platform System Clock Cross-reference................................................................ 230

Table 63. BCLK/BCLK#[1:0] Routing Guidelines................................................................... 233

Table 64. CLK66 Group Routing Guidelines .........................................................................236

Table 65. AGPCLK Routing Guidelines ................................................................................. 238

Table 66. CLK33 Group Routing Guidelines .........................................................................239

Table 67. PCICLK Group Routing Guidelines .......................................................................240

Table 68. PCICLK Group Routing Guidelines .......................................................................241

Table 69. USBCLK Routing Guidelines .................................................................................242

Table 70. CLK14 Group Routing Guidelines .........................................................................243

Table 71. Power Management States.................................................................................... 248

Table 72. Timing Sequence Parameters for Figure 140........................................................ 250

Table 73. DDR Power-Up Initialization Sequence ................................................................. 253

Table 74. Absolute vs. Relative Voltage Specification........................................................... 256

Table 75. DDR SDRAM Memory Supply Voltage and Current Specification ........................257

Table 76. MCH System Memory Supply Voltage and Current Specification......................... 258

Table 77. Termination Voltage and Current Specifications ................................................... 259

Table 78. Intel 855PM MCH System Memory I/O.................................................................. 260

Table 79. Effects of Varying Resistor Values in the Divider Circuit .......................................260

Table 80. DDR VREF Calculation.......................................................................................... 261

Table 81. Reference Distortion Due to Load Current ............................................................261

Table 82. Decoupling Requirements for the Intel 855PM MCH............................................. 265

Table 83. Decoupling Requirements for the Intel 82801DBM ICH4-M.................................. 266

Table 84. Intel 855PM MCH Power Consumption Estimates ................................................268

Table 85. Intel 82801DBM ICH4-M Power Consumption Estimates ..................................... 269

Table 86. Intel 855PM MCH Component Thermal Design Power .........................................270

Table 87. Intel 82801DBM ICH4-M Component Thermal Design Power ..............................270

Table 88. Processor RSVD and TEST Signal Pin-Map Locations ........................................273

Table 89. MCH RSVD and NC Signal Pin-Map Locations ....................................................274

R

16 Intel

®

855PM Chipset Platform Design Guide

Page 17

R

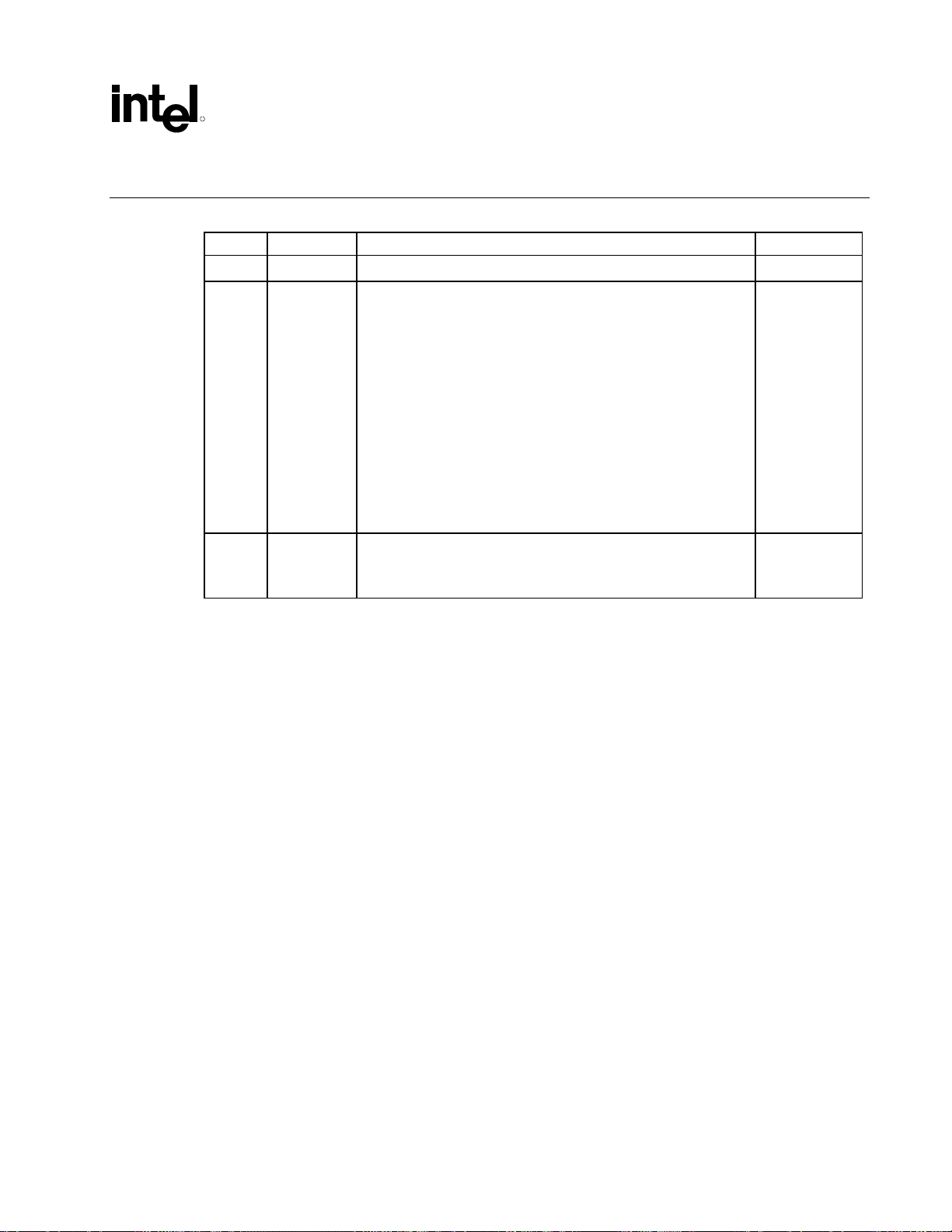

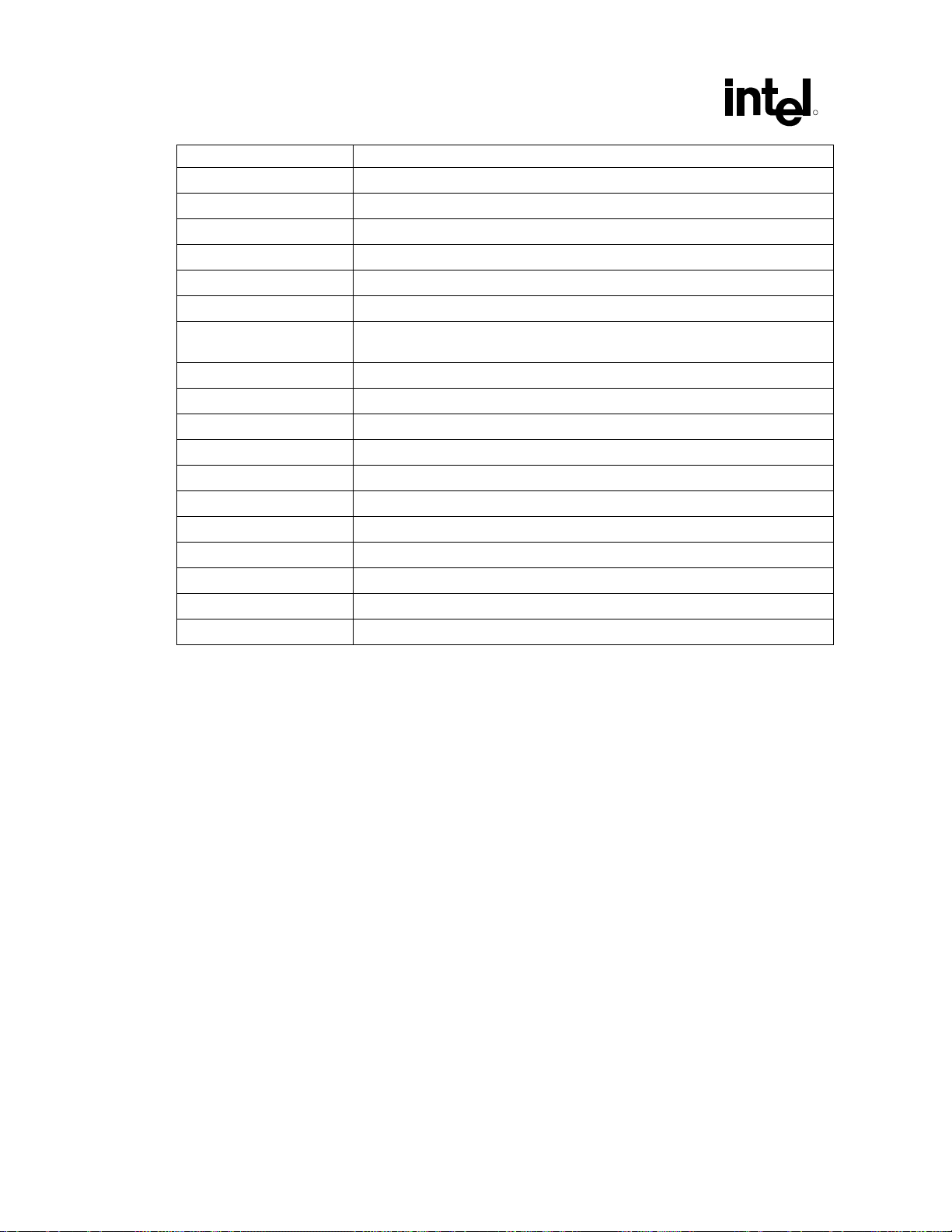

Revision History

Rev. Order No. Description Date

001

002

003

252614 Initial Release

252614

252614

Updates include:

Added Support for the Intel

Incorporated information from Design Guide Update 253479-002

Updated design guidelines for supporting PC2700 (333 MHz) DDR

SDRAM

Transition from Intel 855PM DDR 266/200 MHz Chipset to Intel

855PM DDR 200/266/333 MHz Chipset Design Guidelines