Page 1

Intel® 855GME Chipset and Intel® 6300ESB ICH Embedded Platform

For use with the Intel® Pentium® M Processor, Intel® Pentium® M

Processor on 90 nm process with 2 MB L2 cache, and the Intel®

Celeron® M Processor

Design Guide

October 2005

300669-006

Page 2

®

855GME Chipset and Intel® 6300ESB ICH Embedded Platform Design Guide

Intel

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY

ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN

INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS

ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES

RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER

INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

®

The Intel

product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

AlertVIEW, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Connect, CT Media, Dialogic, DM3, EtherExpress,

ETOX, FlashFile, i386, i486, i960, iCOMP, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share,

Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play logo, Intel

SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Xeon, Intel XScale, IPLink, Itanium, LANDesk, LanRover, MCS, MMX, MMX

logo, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, PDCharm, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your

Command, RemoteExpress, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside., The Journey Inside,

TokenExpress, Trillium, VoiceBrick, Vtune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United

States and other countries.

*Other names and brands may be claimed as the property of others.

Copyright © Intel Corporation, 2007. All rights reserved.

855GME Chipset and Intel® 6300ESB ICH Embedded Platform may contain design defects or errors known as errata which may cause the

2

Page 3

Intel® 855GME Chipset and Intel® 6300ESB ICH Embedded Platform Design Guide

Contents

1 Introduction..................................................................................................................................21

1.1 Reference Documents.......................... ............... .............. .............. .............. ....... ..............23

2 System Overview.........................................................................................................................25

2.1 Terminology........................................................................................................................25

2.2 System Feature s................ ............... .............. ....... .............. .............. .............. ............... .... 25

2.3 Component Features ..........................................................................................................27

2.3.1 Intel

2.3.2 Intel

2.3.3 Intel

2.3.4 Intel

2.3.5 ULV Intel

2.3.6 Intel

2.3.7 Intel

2.3.8 Firmware Hub (FWH).............................................................................................31

®

Penti u m® M Processor ................................................................................ 27

2.3.1.1 Architect u ra l Features..... ........ .............. .............. .............. .............. .......27

2.3.1.2 Packaging/Power...................................................................................27

®

Penti u m® M Processor on 90 nm Process with 2 MB L2 Cache.................27

®

Celeron® M Processor.................................................................................28

®

Celeron® M Processor on 90 nm process...................................................28

®

Celeron® M Processor at 600 MHz......................................................28

®

855GME Chipset Graphics Memory Controller Hub (82855GME) ..............29

2.3.6.1 Intel

®

Pentium® M Processor/Intel® Celeron® M Processor Support....29

2.3.6.2 Integrated System Memory DRAM Controller........................................29

2.3.6.3 I nte rnal Graphics Controller ...................................................................29

2.3.6.4 Packaging/Power...................................................................................31

®

6300ESB System Features........ ....... .............. ............... .............. .............. ..31

2.3.8.1 Packaging/Power...................................................................................32

3 General Design Considerations .................................................................................................33

3.1 Nominal Board Stack-Up....................................................................................................33

3.2 Alternate Stack-Ups............................................................................................................35

4Intel

®

Pentium® M/Celeron® M Processor FSB Design and Power Delivery Gu idel ines......37

®

4.1 Intel

Penti u m® M/Celeron® M Processor FSB Design Recommendations....................... 37

4.1.1 Recommended Stack-Up Routing and Spac ing Assumpt ions...............................37

4.1.1.1 Trace Space to Trace – Reference Plane Separation Ratio..................37

4.1.1.2 Trace Space to Trac e Width Ratio........................... .............. .............. ..38

4.1.1.3 R ecom m ended S ta ck-up Calculate d Coupling Model ...........................38

4.1.1.4 S igna l Propagation Time-t o-Distan ce Relationship and Assumpt ions...39

4.1.2 Common Clock Signals ................................................. ............ ....... ....... ....... .......40

4.1.2.1 Intel

®

Pentium® M/Celeron® M Processor Common Clock Signal

Package Length Compensation............................................................. 41

4.1.3 Source Synchronous Signals General Routing Guidelin es....................................42

4.1.3.1 Source Synchronous – Data Group.......................................................47

4.1.3.2 Source Synchronous – Address Group .................................................48

4.1.3.3 Intel

®

Pentium® M/Celeron® M Processor and Intel® 855GME Chipset

GMCH (82855GME) FSB Signal Packa ge Lengths...............................49

4.1.4 Length Matching Constraints.................................................................................55

4.1.4.1 P ac kage Lengt h Com pensat ion............................................................. 56

4.1.4.2 Trace Length Equalization Procedures..................................................56

4.1.5 Asynchronous Signals............................ ....... .............. .............. .............. ..............58

4.1.5.1 Topology 1A: Open Drain (OD) Signals Driven by the Intel

Pentium M/Celer o n M Proce sso r – IE RR#................................. ...........59

3

Page 4

Intel® 855GME Chipset and Intel® 6300ESB ICH Embedded Platform Design Guide

4.1.5.2 Top ology 1B : Open Drain (OD) Signals Driven by the Intel

Pentium M/Celeron M Processor – FERR# and THERMTRIP# ............59

4.1.5.3 Topology 1C: Open Drain (OD) Signals Driven by the Intel

Pentium M/Celeron M Processor – PROCHOT#...................................60

4.1.5.4 Top ology 2A : Open Drain (OD) Signals Driven by AND Gate–

PWRGOOD............................................................................................61

4.1.5.5 Topology 2B: CMOS Signals Driven by 6300ESB-LINT0/INTR,

LINT1/NMI, A20M#, IGNNE#, SLP#, SMI#, and STPCLK#...................62

4.1.5.6 Topology 3: CMOS Signals Driven by 6300ESB

to CPU and FWH – INIT# ......................................................................62

4.1.5.7 V oltage Trans lation Logic ......................................................................63

4.1.6 Pentium

®

M/Cele r on® M Processor RESET# Signal.............................................64

4.1.6.1 Processor RESET# Rout ing Exa mp l e......... ........ .............. ....................65

4.1.7 Pentium

®

M/Cele r on® M Processor and Intel 855GME

Chipset GMCH (82855GME) Host Clock Signals..................................................66

®

4.1.8 Pentium

M/Cele r on® M Processor GTLREF Layout and

Routing Recommendations...................................................................................67

4.1.9 AGTL+ I/O Buffer Compensation................................................................ ....... ....69

4.1.9.1 Pentium

4.1.10 Pentium

4.1.11 Pentium

®

M/Cele r on® M Processor System Bus Strapping. .................................72

®

M/Cele r on® M Processor VCCSENSE/VSSSENSE

Design Recommendations.....................................................................................74

4.1.12 PLL Voltage Design for Low Voltage Intel

®

M/Cele ro n® M Processor AGTL+ I/O Buffer Compensation..69

®

Pentium® M

Processors on 90 nm proces s with 2 MB L2 Cache..............................................74

4.2 Intel System Validation Debug S upport..............................................................................75

4.2.1 ITP Support............................................................................................................75

4.2.1.1 Background/Justification........................................................................75

4.2.1.2 Implementation......................................................................................75

4.2.2 Pentium

®

M/Cele r on® M Processor Logic Analyzer Support (FSB LAI)................76

4.2.2.1 Background/Justification........................................................................76

4.2.2.2 Implementation......................................................................................76

®

4.2.3 Intel

Pentium® M/Cele r on® M Processor On-Die Logic

Analyzer Trigger (ODLAT) Support .......................................................................76

4.3 Onboard Debug Port Routing Guidelines....................................................................... ....77

4.3.1 Recommended Onboard I TP700F LE X Implementation........................................77

4.3.1.1 ITP Signal Routing Guidelin e s....... .............. ............... .............. ....... ......77

4.3.1.2 ITP Signal Routing Example............. .............. .............. .............. ....... ....81

4.3.1.3 ITP_CLK Routing to ITP700FLEX Connector........................................82

4.3.1.4 ITP700FLEX Design Guidelines for Production Systems......................83

4.3.2 Recommended ITP Interposer Debug Port Implementa tion..................................84

4.3.2.1 ITP_CLK Routing to ITP Interposer........... .............. .............. ............... .84

4.3.2.2 ITP Interposer Design Guidelines for Production Systems....................85

4.3.3 L ogic Analyzer Interface (LAI)...............................................................................85

4.3.3.1 Mechanical Considerations.................................................................... 86

4.3.3.2 Electri ca l Cons ide r a tions ....................................... .............. .............. ....86

4.3.4 Processor Phase Lock Loop (PLL) Design Guidelines..........................................86

4.3.4.1 Processor PLL Power Delivery..............................................................86

4.3.4.2 Processor PLL Voltage Supply Power Sequencing...............................88

4.3.4.3 Processor PLL Decoup ling Requiremen ts.................. .............. .............88

4.3.5 Intel

4.3.6 Thermal Power Dissipation....................................................................................89

4.4 Intel

®

Pentium® M/Cele r on® M Processor Decoupling Recommendations ........................90

®

Pentium® M/Cele r on® M Processor Power Status Indicator (PSI#) Signal.89

4

Page 5

Intel® 855GME Chipset and Intel® 6300ESB ICH Embedded Platform Design Guide

4.4.1 Transient Response............................................................................................... 90

4.4.2 High-Frequency/Mid-Frequency and Bulk Dec oupling Capac itors ........................91

4.4.3 Processor Core Voltage Plane and Decoupling..................................................... 91

4.4.4 Processor and GMCH VCCP Voltage Plane and Decoupling .............................100

4.4.5 GMCH Core Voltage Pla ne and Dec oupling......... .............. ..................... ............101

4.5 Power and Sleep State Def initions............................. .............. .............. .............. ............101

4.6 Power Delivery Ma p.... .............. ............... .............. .............. .............. .............. ............... ..103

4.7 Intel 855GME Chipset Platform Power-Up Sequen ce. .....................................................105

4.7.1 GMCH Power Sequencing Requirements ...........................................................105

4.7.2 6300ESB Power Sequencing Requirements .................................................. .....105

4.7.2.1 V5REF/3.3V Sequencing.....................................................................105

4.7.2.2 3. 3V/1 .5V Power Seque ncing ..............................................................106

4.7.3 PCI-X Power Sequencing .................................. ..... .. .......... .. ..... .. ..... ....... ..... .. .....106

4.7.4 DDR Memory Power Sequencing Requirements.................................................106

4.8 Intel 855GME Chipset Platform Power Delivery Guidelines.............................................107

4.8.1 Intel 855GME Chipset and Decoupling Guidelines..............................................1 08

4.8.1.1 G MCH VCCS M Decoupl ing.................................................................108

4.8.1.2 DDR SDRAM VDD Decoupling............................................................109

4.8.1.3 DDR VTT Decoupling Placement and Layout Guidelines....................109

4.8.2 DDR Memory Power Delivery Design Guidelines................................................ 1 09

4.8.2.1 2.5 V Power Delivery Guidelines .........................................................110

4.8.2.2 G MCH and DDR SMVRE F Design Recomm endations ....................... 111

4.8.2.3 DDR SMRCOMP Resistive Compensation. .........................................111

4.8.2.4 DDR VTT Termination .........................................................................112

4.8.2.5 DDR S MRC OM P and VTT 1.25 V Supply Disable in S3/Suspend......1 12

4.8.3 Other GMCH Reference Voltage and Analog Power Delivery............................. 1 13

4.8.3.1 GMCH GTLVREF ................................................................................ 1 13

4.8.3.2 GMCH AGTL+ I/O Buffer Compensation............................................. 1 15

4.8.3.3 GMCH AGTL+ Reference Voltage ....................................................... 1 15

4.8.3.4 GMCH Analog Power...........................................................................1 16

®

4.8.4 Intel

6300ESB Power Delive ry.. .............. .............. .............. .............. ........ .........118

4.8.5 Power Supply PS_ON Considerat ion....... ....... .............. .............. ............... ....... ..119

4.8.6 Intel

4.8.7 Intel

®

6300ESB Analog Power Del iver y............... .............. .............. .............. .....120

®

6300ESB Standby Power Distribution ....................................................... 120

4.8.8 Intel® 6300ESB Power Consumptio n......... ....... ............... .............. ....... ..............120

4.8.9 Intel

®

6300ESB Decouplin g Recommendations.. ................................................120

4.8.10 6300ESB Power Signal Decoupling ................. ....... .......... ....... .. ....... .......... .......121

4.8.11 Hub Interface Decoupling....................................................................................1 21

4.8.12 F WH Decoupl ing............................. ............... .............. .............. .............. ............121

4.9 Thermal Design Power.....................................................................................................121

5 System Memory Design Guidelines (DDR-SDRAM)............................................................... 1 23

5.1 Introduction.......................................................................................................................123

5.2 Length Matching and Length Formulas ............................................................................124

5.3 Package Length Compensation................................................................................... .....124

5.4 Topologi es and Routing Guideline s................ .............. .............. .............. ............... .........125

5.4.1 Clock Signals – SCK[5:0], SCK[5: 0 ]#....... .............. .............. .............. ............... ..125

5.4.2 Clock Topology Diagram ...................................................... ....... ....... .......... .......125

5.4.3 DDR Clock Routing Guidelines............................................................................126

5.4.3.1 C lo ck Length Ma tching Requirem ent s. ................................................1 27

5.4.3.2 C lo ck Reference Lengt hs..................................................................... 1 28

5

Page 6

Intel® 855GME Chipset and Intel® 6300ESB ICH Embedded Platform Design Guide

5.4.3.3 Clock Length Package Table...............................................................130

5.4.4 Data Signals – SDQ[71:0], SDM[8:0], SDQS[8:0] ...............................................130

5.4.4.1 Data Bus Topology........ .............. .............. .............. .............. ........ ......131

5.4.4.2 SDQS to Clock Length Matching Requirements..................................133

5.4.4.3 D ata to Strobe Length Matchin g Requirement s. . .................................134

5.4.4.4 SDQ to SDQS Mapping....................................................................... 135

5.4.4.5 SDQ/SDQS Signal Packa g e Le ngt h s.......... ...................... .............. ....136

5.4.5 Control Sig nals – SCKE[3:0], SCS[3 :0 ]#............................. ....... .............. ...........138

5.4.5.1 C ontrol Signal Routing To pology .........................................................139

5.4.5.2 C ontrol Signal Routing Gu idelines.......................................................140

5.4.5.3 C ontrol to Clock Length Matching Requ irem ents ................................140

5.4.5.4 C ontrol Group P acka ge Length Table .................................................142

5.4.6 Command Signals – SMA[12:6,3,0], SBA[1:0],

SRAS#, SCAS#, SWE#..................... ........ .............. .............. .............. .............. ..142

5.4.6.1 Command Signal Routing Topology....................................................142

5.4.6.2 Command Topology Routing Guidelines .............................................143

5.4.6.3 Command Topology Length Matching Requirements..........................144

5.4.6.4 Command Group Package Length Table ............................................146

5.4.7 CPC Signals – SMA[5,4,2,1], SMAB [5,4,2, 1] ......................................................146

5.4.7.1 CPC Signal Routing Topology.............................................................147

5.4.7.2 CPC Signal Routing Guidelines ...........................................................148

5.4.7.3 CPC to Clock Length Matching Requirements ....................................148

5.4.7.4 CPC Group Package Length Table ................................ ................... ..150

5.4.8 Feedback – RCVENOUT#, RCVENIN#...............................................................150

5.5 ECC Guidelines................................................................................................................150

5.5.1 GMCH ECC Functionality....................... .............. ............... .............. ..................150

5.5.2 D RAM Clock Flexibility........................................................................................151

6 Integrated Graphics Display Port.............................................................................................153

6.1 Analog RGB/CRT Guidelines........................................................................................... 153

6.1.1 R AMDAC/Display Interface.................................................................................153

6.1.2 Reference Resistor (RSET)................................ .............. .............. ............... ......153

6.1.3 RAMDAC Board Design Guide li n e s................. ..................... .............. .............. ..154

6.1.4 D AC Routing Guidelines......................................................................................155

6.1.5 DAC Power Requirements...................................................................................157

6.1.6 HSYNC and VSYNC Design Considerations.......................................................158

2

6.1.7 DDC and I

C Design Considerations................................................................... 158

6.2 LVDS Transmitter Interface.............................................................................................. 158

6.2.1 Length Matching Constraints........................................................ ......... ............ ..159

6.2.1.1 Package Length Compensation...........................................................159

6.2.2 L VDS Routing Guidelines .................................................................................... 160

6.3 Digital Video Out Port.......................................................................................................161

6.3.1 DVO Interface Signal Groups .................................................. ....... ....... ............ ..162

6.3.1.1 DVO/I2C to AGP Pin Mapping.............................................................162

6.3.2 D VOB and DVOC Port Interface Routing Guidelines.......................................... 163

6.3.2.1 Lengt h Mi smatc h Requirement s ..........................................................163

6.3.2.2 Package Length Compensation...........................................................164

6.3.2.3 DVOB and DVOC Routing Guidel i n e s................... .............. .............. ..165

6.3.2.4 DVOB and DVOC Port Termina tion.............................. ....... .............. ..166

6.3.3 D VOB and DVOC Assumptions, Definitions, and Specifications.........................167

6.3.4 D VOB and DVOC Simulation Method................................................................. 167

6.4 DVOB and DVOC Port Flexible (Modular) Design............................................................168

6

Page 7

Intel® 855GME Chipset and Intel® 6300ESB ICH Embedded Platform Design Guide

6.4.1 DVOB and DVOC Module Design ............................ .......... ....... ....... ....... ....... .....168

6.4.1.1 Generic Connector Model....................................................................169

6.5 DVO GMBUS and DDC Interface Considerations............................................................170

6.5.1 Leaving the GMCH DVOB or DVOC Port Unconnected......................................1 71

6.6 Miscellaneous Input Signals and Voltage Reference .................................... ............ .......171

7 AGP Port Design Guid elin es ....................................................................................................173

7.1 AGP Interfa ce...... .............. ....... ............... .............. .............. .............. .............. .................173

7.1.1 AGP 2.0 ................ ............... .............. .............. .............. .............. ............... ....... ..173

7.1.2 AGP Interface Signal Groups ............................................. ......... ................... .....174

7.2 AGP Routing Guidelines.......................... .............. .............. .............. .............. ............... ..175

7.2.1 1x Timing Domain Routing Guidelines.................................................................175

7.2.1.1 Trace Length Requirements for AGP 1X.............................................175

7.2.1.2 Trace Spacing Requi r e men ts................. .............. .............. ............... ..175

7.2.1.3 Trace Length Mismatch ................... .............. .............. ............... .........175

7.2.2 2x/4x Timing Domain Routing Guid elines...................... .............. ............... .........175

7.2.2.1 Trace Length Requirements for AGP 2X/4X........................................175

7.2.2.2 Trace Spacing Requi r e men ts................. .............. .............. ............... ..176

7.2.2.3 Trace Length Mismatch Requirements ................................................ 177

7.2.3 AGP Clock Skew .. ............... .............. .............. .............. .............. ............... .........177

7.2.4 AGP Signal Noise Decoupling Guidelines. ..........................................................1 78

7.2.5 AGP Interface Package Lengths .........................................................................178

7.2.6 AGP Routing Ground Reference .........................................................................179

7.2.7 Pull-Ups ............................................................................................................... 1 80

7.2.8 AGP VDDQ and VCC .......... .............. .............. .............. .............. ............... .........181

7.2.9 VREF Generation for AGP 2.0 (2X and 4X) . ....................................................... 181

7.2.9.1 1.5 V AGP Interface (2X/4X)................................................................181

7.2.10 AG P Comp ensa tion..... ........ .............. .............. .............. .............. ............... .........181

7.2.11 PM_SUS_CLK/AGP_PIPE# Design Consideration.............................................181

8Hub Interface..............................................................................................................................183

8.1 8-Bit Hub Interface Routing Guidelines. ...........................................................................1 83

8.1.1 8-Bit Hub Interface Data Signals ......................................................................... 1 83

8.1.2 8-Bit Hub Interface Signal Referencing . ..............................................................1 84

8.1.3 8-Bit Hub Interface Strobe Signals ......................................................................184

8.1.4 8-bit Hub Interface HIREF and HI_VSWING Generation/Dist r i b ut ion...... ....... .....184

8.1.4.1 G MCH Singl e Generated Vo ltage Reference Divider Circuit............... 187

8.1.4.2 S eparate GM CH Voltag e Divider Circuits for HLVREF and PSWING .188

8.1.5 Hub Interface Compensation...............................................................................189

8.1.6 8-Bit Hub Interface Decoupling Guidelines.......................................................... 189

8.1.7 Terminating HI_11 If Not Used ............................................................................189

9Intel

®

6300ESB Design Guidelines ..........................................................................................191

9.1 Serial ATA Interface..........................................................................................................1 91

9.1.1 Layout Guidelines........... ....... .............. .............. ............... .............. ....... ..............191

9.1.1.1 General Routing and Placement... .......................................................191

9.1.1.2 S erial ATA Trace Separat ion ...............................................................191

9.1.1.3 S erial ATA Trace Length Pa ir Matching...............................................192

9.1.1.4 S erial ATA Trace Length Guid eline s....................................................192

9.1.1.5 SATA BIAS Connections ................... ............ ....... ............ ............ .......192

9.1.1.6 SATALED# Implementation.................................................................1 93

7

Page 8

Intel® 855GME Chipset and Intel® 6300ESB ICH Embedded Platform Design Guide

9.2 IDE Interface.... .............. ....... ............... .............. .............. .............. .............. ............... ...... 194

9.2.1 C abling.................................................................................................................194

9.3 Cable Detection for Ultra ATA/66 and Ult ra ATA/10 0.... ....... .............. .............. .............. ..195

9.3.1 Combination Host-Side/Device-Side Cable Detection.........................................195

9.3.2 Device-Side Cable Detection......................... ...................... .............. .............. ....196

9.3.3 Primary IDE Connector Requirements .............................................................. ..198

9.3.4 Secondary IDE Connector Requirements............................................................199

9.4 AC’97................................................................................................................................200

9.4.1 AC’97 Routing........................... ..................... .............. ............... .............. ...........203

9.4.2 Motherboard Implementat ion.............................. .............. .............. ............... ......204

9.4.2.1 V alid Codec Configuration s .................................................................205

9.4.3 SPKR Pin Consideration. ............... .............. .............. .............. ....... ............... ......205

9.4.4 AC_SDOUT Pin Consideration............................................................................ 206

9.4.5 SIU0_DTR# Pin Consideration................................ .............. ..................... .........206

9.5 Communication Net wo r k Riser.............. .............. .............. ...................... .............. ...........206

9.5.1 AC’97 Audio Codec Detect Circuit and Configuration Options............................207

9.5.1.1 CNR 1.2 AC’97 Disable and Demotion Rules for the Motherboard .....207

9.5.2 CNR Routing Summary................... .............. .............. ............... ..................... ....209

9.6 USB 2.0............................................................................................................................210

9.6.1 L ayout Guidelines................................................................................................210

9.6.1.1 General Routing and Placement..........................................................210

9.6.1.2 USB 2.0 Trace Separation.................... ....... ............... .............. ...........211

9.6.1.3 U S B BIAS Connec tions .......................................................................211

9.6.1.4 USB 2.0 Termination............................................................................212

9.6.1.5 USB 2.0 Trace Length Pair Matching ..................................................212

9.6.1.6 USB 2.0 Trace Length Guidelines ............... ............ .............. ..............212

9.6.2 Plane Splits, Voids and Cut-Outs (An ti-Etch)............................... .............. .........213

9.6.2.1 VCC Plane Splits, Voids, and Cut-Outs (Anti-Etch).............................213

9.6.2.2 GND P lane Splits, Voids, and Cut-Outs (Anti-Etch).............................214

9.6.3 USB Power Line Layout Topology....................................................................... 214

9.6.4 EMI Considerations.............................................................................................214

9.6.4.1 Common-Mode Chokes........................ ............... .............. .............. ....215

9.6.5 ESD ..................................................................................................................... 215

9.6.6 Front Panel Solutions ............................................................................ ............ ..216

9.6.6.1 Interna l USB Cabl e s............... .............. ............... .............. .............. ....216

9.6.6.2 Motherboard/PCB Mating Connector...................................................217

9.6.6.3 Front Pan el Connector Card................................................................218

9.7 Low Pin Count (LPC) Inter fa c e ....................... ............... .............. .............. .............. .........219

9.7.1 General Routing and Placement..........................................................................220

9.7.2 L PC Trace Length Matching ................................................................................220

9.7.3 L PC Interface Routing Guidelines.......................................................................220

9.8 SMBus 2.0/SMLink Interface........................ .............. .............. ............... .............. ....... ....221

9.8.1 SMBus Architecture & Design Conside r a ti o n s............... .............. ..................... ..222

9.8.1.1 SMBus Design Considerations............................................................ 222

9.8.1.2 General Design Issues / Notes............................................................222

9.8.1.3 High Power/Low Power Mixed Architecture.........................................223

9.8.1.4 Calculating the Physical Segment Pull-Up Resistor............................223

9.9 PCI....................................................................................................................................224

9.9.1 PCI Routing Summary................ ............... .............. .............. .............. .............. ..224

9.9.2 PIRQ Routing Example........................................................................................227

9.10 PCI-X Design Guideli n e s....................... .............. .............. ............... .............. ..................228

8

Page 9

Intel® 855GME Chipset and Intel® 6300ESB ICH Embedded Platform Design Guide

9.10.1 66 MHz Topologies and Trac e Le ngt h...... ....... .............. .............. ............... .........229

9.10.1.1 PCI-X Clock Length Matching Guidelines............................................231

9.10.2 IDSEL Series Resistor.........................................................................................231

9.10.3 PCI-X Secondary Bus Reset .................... .............. ..................... ............... .........232

9.10.3.1 Secondary Bus Reset Not Utilized.................................................. .....232

9.10.4 PME# Signal Sharing ...........................................................................................232

9.10.4.1 Issues with Sharing PME#...................................................................232

9.11 RTC ..................................................................................................................................233

9.11.1 RTC Crystal .........................................................................................................2 34

9.11.2 External Capacitors ........................... .............. .............. .............. ............... .........235

9.11.3 RTC Layout Considerations.................................................................................236

9.11.4 RTC External Battery Connection........................................................................236

9.11.5 RTC External RTCRST# Circuit...........................................................................2 38

9.11.6 VBIAS DC Voltage and Noise Measurements.....................................................238

9.11.7 SUSCLK ..............................................................................................................2 39

9.11.8 RTC-Well Input Strap Requirements................................................................... 2 39

9.12 Serial I/O ...........................................................................................................................239

9.12.1 Ser ial I/ O I nter f ac e N ot Ut iliz e d ........ .... . .. .... . .... ... .. .. ... .. ... .. .... . .. .... . .... ............... .. .239

9.13 FWH..................................................................................................................................240

9.13.1 FWH Vendors ................................. ................... ....... ................... ................... .....240

9.13.2 FWH Decoupling......................... .............. .............. .............. .............. ............... ..240

9.13.3 In-circuit FWH Programming................................................................................240

9.13.4 FWH INIT# Voltage Compatibility........................................................................240

9.13.5 FWH VPP Design Guidelines................. .............. .............. .............. .............. .....241

9.14 GPIO Summary................................................................................................................242

9.15 Power Management....................... .............. ............... .............. .............. .............. ............244

9.15.1 SYS_RESET# Usage Model ...............................................................................244

9.15.2 PWRBTN# Usage Model.....................................................................................244

9.15.3 Power-Well Isolation Control Strap Requirements...............................................244

10 Miscellaneous Logic ................................................................................................................. 2 47

10.1 Glue Chip 4* ........................... .............. ............... .............. .............. .............. ...................2 47

10.2 Discrete Logic...................................................................................................................248

11 Platform Clock Routing Guidelines .........................................................................................249

11.1 System Clock Grou ps........ ....... ............... .............. .............. ....... .............. ............... .........249

11.2 Clock Group Topologies and Routing Constraints............................................................251

11.2.1 Host Clock Group ................................................................................................251

11.2.1.1 Host Clock Group General Routing Guidelines .............................. .....253

11.2.1.2 Clock-to-Clock Length Matching and Compensation...........................253

11.2.1.3 EMI Constraints ...................................................................................253

11.2.2 CLK66 Clock Group .............................................................................................254

11.2.3 CLK33 Clock Group .............................................................................................255

11.2.4 PCI Clock Group.................................................................................................. 2 56

11.2.5 CLK14 Clock Group .............................................................................................257

11.2.6 DOTCLK Clock Group ............................ .............. .............. ..................... ............258

11.2.7 SSCCLK Clock Group .........................................................................................2 59

11.2.8 USBCLK Clock Group .........................................................................................260

11.2.9 SRC Clock Group ....................... .............. .............. .............. ...................... .........261

11.2.9.1 SRC Clock Topology............................................................................261

11.2.9.2 SRC General Routing Guidelines ........................................................263

9

Page 10

Intel® 855GME Chipset and Intel® 6300ESB ICH Embedded Platform Design Guide

12 Schematic Checklist Summary................................................................................................265

12.1 Intel

®

Pentium® M/Cele r on® M Processor Checklist........................................................265

12.1.1 Connection Recommen dations ............................................................................265

12.1.2 In Target Probe (ITP)...........................................................................................268

12.1.3 Decoupling Recommendations......................................... ....... ....... ....... .......... ....269

12.1.3.1 VCCP (I/O)...........................................................................................269

12.1.3.2 VCCA (PLL).........................................................................................269

12.1.3.3 VCC (CORE)......................... .............. .............. .............. ............... ......269

12.2 CK409 Clock Checklis t..................... .............. ...................... .............. .............. .............. ..270

12.2.1 Connection Recommen dations ............................................................................270

®

12.3 Intel

855GME Chipset GMCH (82855GME) Checklist ...................................................272

12.3.1 System Memory...................................................................................................272

12.3.1.1 GMCH System Memory Interface Checklist ........................................ 272

12.3.1.2 DDR DIMM Interface Checklist............................................................274

12.3.1.3 DIMM Decoupling Recommendation Checklist....................................275

12.3.2 Frontside Bus (FSB) Checklist.............................................................................275

12.3.3 Hub Interfa ce Checklist...................... ............... .............. .............. .............. .........277

12.3.4 Graphics Interfaces Checklist..............................................................................278

12.3.4.1 Low Voltage Digital Signalling (LVDS) Checklist................................. 278

12.3.4.2 Digital Video Out (DVO) Checklist.......................................................278

12.3.4.3 Digital-to-Analog Converter (DAC) Checklist.......................................280

12.3.5 Miscellaneous Signal Checklist ...........................................................................281

12.3.5.1 Intel

12.3.6 GMCH Decoupling Recommendations Checklist .................................. .......... .. ..281

12.4 Intel

®

6300ESB Checklist............ ............... .............. .............. .............. .............. ..............283

®

Penti u m® M/Celeron® M Processor GST[2:0] Configurations ...281

12.4.1 PCI-X Interface Checklist... ....... .............. .............. ............... .............. .............. ....283

12.4.2 PCI Interface Checklist.................. .............. .............. .............. .............. ..............285

12.4.3 Hub Interfa ce Checklist...................... ............... .............. .............. .............. .........288

12.4.4 FWH/LPC Interf a ce Checkl ist...................... .............. .............. .............. ..............288

12.4.5 GPIO Checklist........ ....... ............... .............. .............. .............. .............. ..............289

12.4.6 U SB Checklist......................................................................................................290

12.4.7 Power Management Checklist.............................................................................290

12.4.8 CPU Signals Checklist. ........................................................................................291

12.4.9 System Management C heck list. ..........................................................................292

12.4.10 RTC Checklist......................................................................................................292

12.4.11 UART Checklist............................... .............. .............. ............... .............. ...........293

12.4.12 AC’97 Checklist........................ .............. .............. ............... .............. .............. ....294

12.4.13 Miscellaneous Signals.........................................................................................294

12.4.14 Serial ATA Checklis t................... ............... .............. .............. .............. .............. ..295

12.4.15 IDE Checklist....................... ....... ............... .............. .............. .............. .............. ..295

12.4.16 Power Checklist...................................................................................................297

13 Layout Checklist........................................................................................................................299

13.1 Processor Check li st................. ....... .............. .............. .............. ............... .............. ...........299

13.2 Intel

13.3 Intel

®

855GME Chipset GMCH (82855GME) Layout Checklist .......................................307

®

6300ESB Layout Check li st............ ............... .............. .............. .............. .............. ..312

13.3.1 8 -Bit Hub Interface Layout Checklist................................................................... 312

13.3.2 Serial ATA Interface Layout Checklist.................................................................313

13.3.3 IDE Interface Layout Checklist............................................................................314

13.3.4 U SB 2.0 Layout Checklist....................................................................................314

10

Page 11

Intel® 855GME Chipset and Intel® 6300ESB ICH Embedded Platform Design Guide

13.3.5 AC’97 Layout Checklist........................................................................................3 15

13.3.5.1 RTC Layout Checkli st............. .............. .............. .............. .............. .....315

13.3.6 PCI-X Layout Checklist...................... ..................... .............. .............. .................316

13.3.7 PCI Layout Checklist...........................................................................................3 16

13.3.8 FWH Decoupling Layout Checklist......................................................................316

13.3.9 Power Delivery Checklist........................ .............. .............. .............. ...................317

11

Page 12

Intel® 855GME Chipset and Intel® 6300ESB ICH Embedded Platform Design Guide

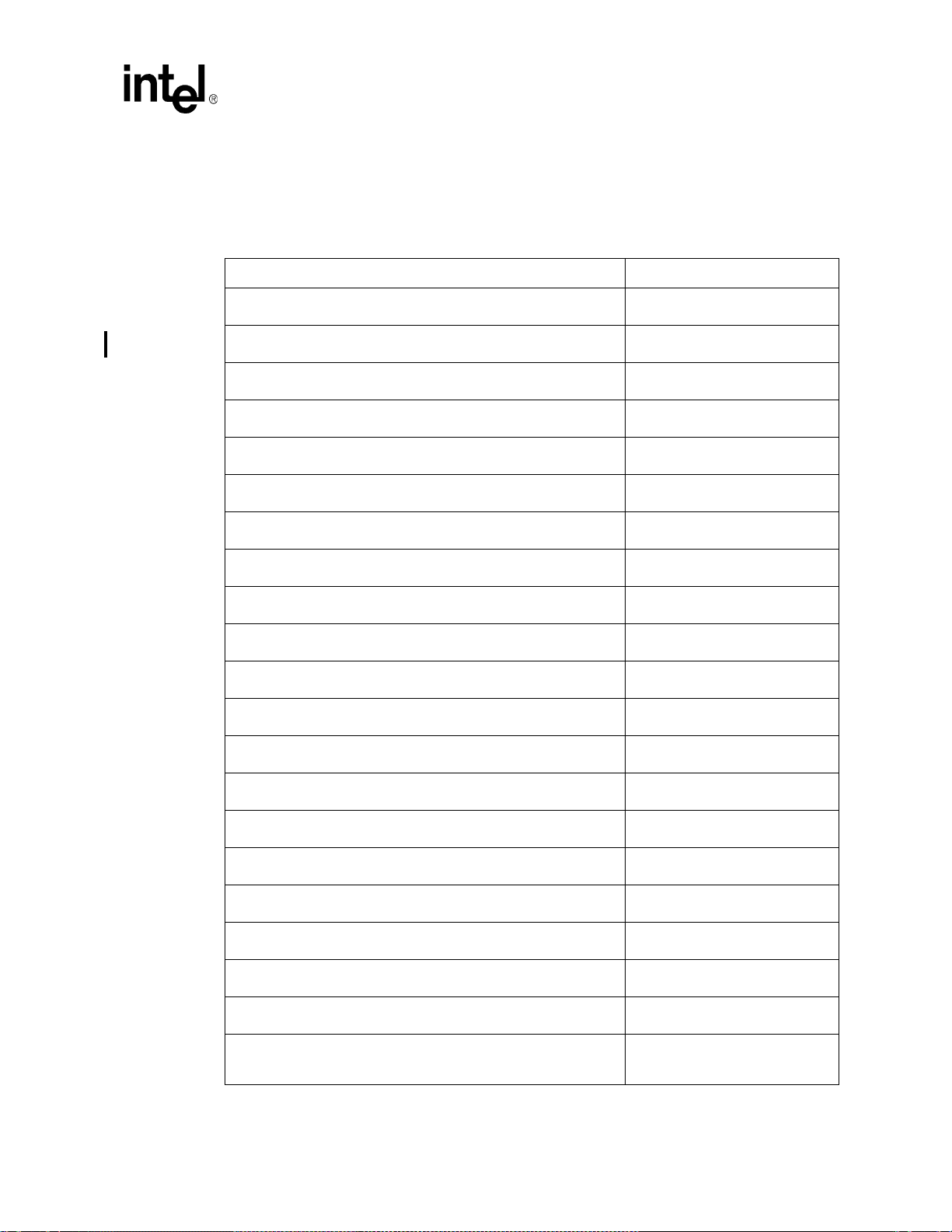

Figures

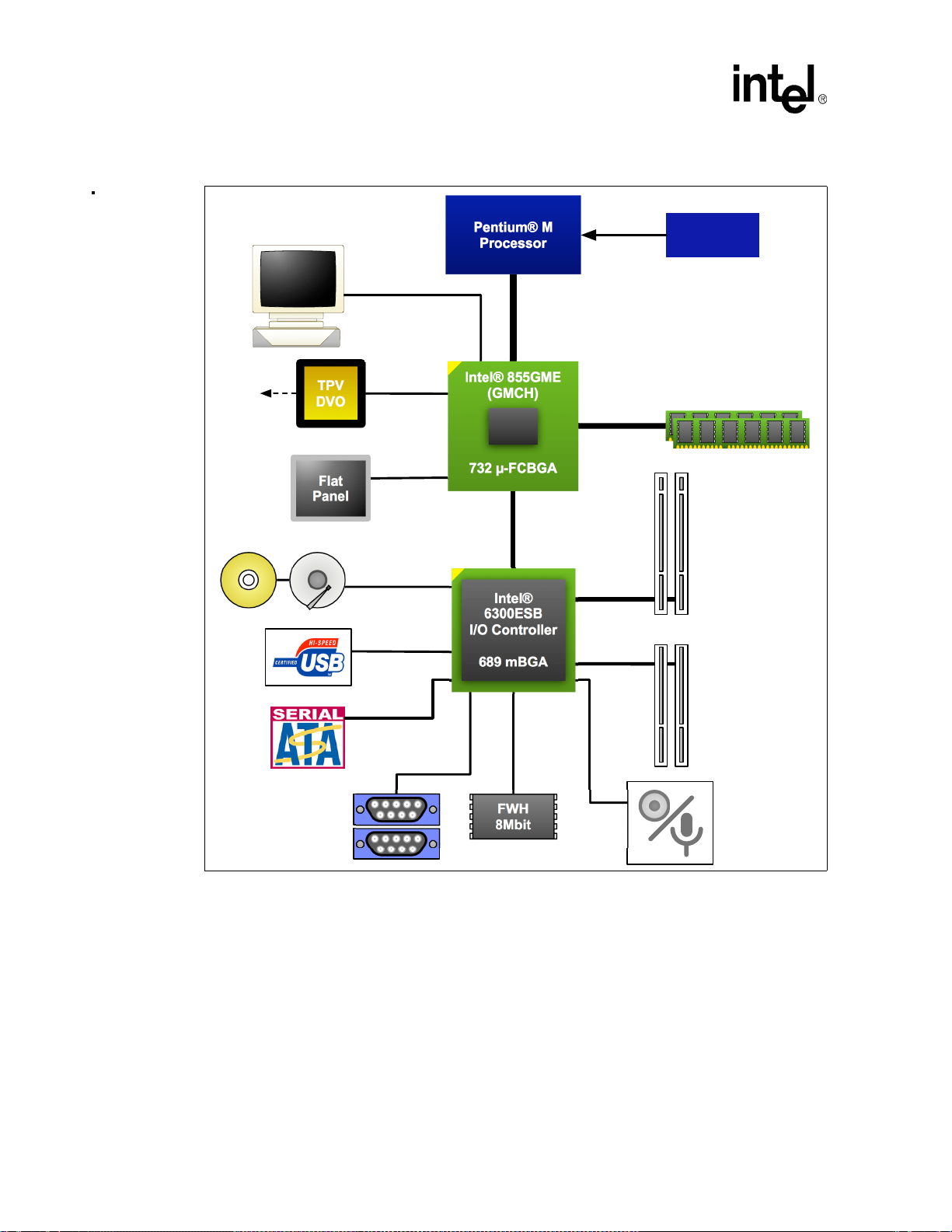

1 Embedded Intel® 855GME Chipset System Block Diagram...................................................... 26

2 Recommended Board Stack-up Dimensions................................................ ....... ....... ............ ....34

3 Tra ce Spaci n g versus Trace to Referenc e Pla n e Example.......... ..................... .............. ...........38

4 Two- to -One Trace Spacing-to-Trace Width Example.............. .............. .............. ............... ........38

5 Thr e e- to - O ne Trac e Sp a cing-to-Trace Wid th Exa mple...... .............. ............... .............. .............38

6 Recommended Stack-up Capacitive Coupling Model ................................................................39

7 Common Clock Topology............................ .............. .............. .............. .............. ............... ........42

8 Layer 6 Intel

Signals GND Referencing to Layer 5 and Layer 7 Ground Planes ............................................ 43

9 Layer 6 Intel

Data Signals...................... .............. .............. .............. .............. ............... .............. ....................44

10 Layer 6 Intel

Source Synchronous Address Signals ............................................. .......... ......... ....... .......... ......45

11 Layer 3 Intel

Signals GND Referencing to Layer 2 and Layer 4 Ground Planes ............................................46

12 Layer 3 Intel

Data Signals...................... .............. .............. .............. .............. ............... .............. ....................46

13 Layer 3 Intel

Address Sign als......... ........ .............. .............. .............. .............. ............... .............. ....................47

14 Reference Trace Length Selection........................................................................... ............ ......57

15 Trace Length Equalization Procedures with Allegro* . ................................................................57

16 Routing Illustration for Topology 1A .......................................... ....... .......... ....... .. ....... .......... ......59

17 Routing Illustration for Topology 1B .......................................... ....... .......... ....... .. ....... .......... ......60

18 Routing Illustration for Topology 1C .......................................... ..... ....... ....... ....... ....... .......... .. ....61

19 Routing Illustration for Topology 2A .......................................... ....... .......... ....... .. ....... .......... ......61

20 Routing Illustration for Topology 2B .......................................... ....... .......... ....... .. ....... .......... ......62

21 Routing Illustration for Topology 3..................................................................... ....... .. .......... .. ....63

22 Voltage Translation Circuit .........................................................................................................64

23 Processor RESET# Signal Routing Topology With NO ITP700FLEX Connector ...................... 64

24 Processor RESET# Signal Routing Topology With ITP700FLEX Connector............................. 65

25 Processor RESET# Signal Routing Example with ITP700FLEX Debug Port.............................65

26 Intel

27 Intel

28 Intel

29 Intel

30 Intel

®

(82855GME) Host Clock Layout Routing Example ....................................................................67

®

®

®

Resistive Compe nsation....................................... .............. .............. ...................... .............. ......70

®

Resistive Compe nsation....................................... .............. .............. ...................... .............. ......70

31 Intel

32 Intel

®

®

Primary Side Layout...................................................................................................................71

33 COMP2 and COMP0 18 -mi l Wid e Dog Bo nes an d Tr ac es.......... ....... ..................... .............. ....72

34 Intel

®

35 VCCSENSE/VSSSENSE Routing Example...............................................................................74

36 ITP700FLEX Debug Port Signals...............................................................................................78

37 ITP_CLK to ITP700FLEX Connector Layout Example. .............................................................. 82

38 ITP700FLEX Signals Layout Example .......................................................................................83

®

Pentium® M/Celeron® M Processor FSB Source Synchronous

®

Pentium® M/Celeron® M Processor FSB Source Synchronous

®

Pentium® M/Celeron® M Processor System Bus

®

Pentium® M/Celeron® M Processor FSB Source Synchronous

®

Pentium® M/Celeron® M Processor FSB Source Synchronous

®

Pentium® M/Celeron® M Processor FSB Source Synchronous

Penti u m® M/Cele r on® M Processor and Intel® 855GME Chipset GMCH

Penti u m® M/Cele r on® M Processor GTLREF Voltage Divider Network...........................68

Penti u m® M/Cele r on® M Processor GTLREF Motherboard Layout.................................69

Penti u m® M/Cele r on® M Processor COMP[2] and COMP[0]

Penti u m® M/Cele r on® M ProcessorCOMP[3] and COMP[1]

Penti u m® M/Cele r on® M Processor COMP[3:0] Resistor Layout.....................................71

Penti u m® M/Cele r on® M Processor COMP[1:0] Resistor Alternative

Penti u m® M/Cele r on® M Processor Strapping Resistor Layout.......................................73

12

Page 13

Intel® 855GME Chipset and Intel® 6300ESB ICH Embedded Platform Design Guide

39 ITP_CLK to CPU ITP Interposer Layout Example......................................................................85

40 Intel

41 Intel

42 Intel

43 Intel

®

Pentium® M/Celeron® M Processor 1.8-V VCCA[3:0] Recommended

Power Delivery and Decoupling.................................................................................................. 87

®

Pentium® M/Celeron® M Processor 1.8 V Intel® Customer Reference Board

Routing Example......... .............. ............... .............. .............. .............. .............. ............... ........... 88

®

Pentium® M/Celeron® M Processor Socket Core Power Delivery Corridor......................92

®

Pentium® M/Celeron® M Processor Core Power Delivery

and Decoupling Concept Exa mp le (Option #4) ....................................... .............. .............. .......93

44 VCC-CORE Power Delivery and Decoupling Example –

Option 4 (Primary and Secondary Side Layers) .........................................................................98

®

45 Intel

Pentium® M/Celeron® M Processor Core Power Delivery

‘North Corridor’ Zoom-in View ....................................................................................................99

46 VCC-CORE Power Delivery and Decoupling Example – Option 4 (Layers 3, 5, and 6).............99

47 Recommended SP Cap Via Connection Layout (Secondary Side Layer)................................100

48 Platform Power Deli v er y Map........... ........ .............. .............. .............. .............. ............... .........104

49 GMCH Power-up Sequence..................................................................................................... 1 05

50 Example V5REF/3 .3 V Sequencing Circuitry............................................................................106

51 Example for Minimizing Loop Inductance.................................................................................107

52 DDR Power Delivery Block Diagram ........................................................................................110

53 GMCH SMRCOMP Resistive Compensati on ...........................................................................111

54 GMCH System Memory Reference Voltage Generation Circuit...............................................1 12

55 GMCH HDVREF[2:0] Reference Voltage Generation Circuit...................................................113

56 GMCH HAVREF Reference Voltage Generation Circuit . ..... .. ..... .. ..... ..... ....... .. ..... .. ..... ..... .. .....113

57 GMCH HCCVREF Reference Voltage Generation Circuit........................................................114

58 Pr imary Side of the Moth erboard Layout...... ............................................................................114

59 Secondary Side of the Motherboard Layout............................................................................. 1 15

60 GMCH HXRCOMP and HYRCOMP Resist ive Comp ensation........................................ .........115

61 GMCH HXSWING and HYSWING Reference Voltage Generation Circuit. ..............................116

62 Example Analog Supply Filter...................................................................................................116

63 Intel

®

6300ESB Power Delivery Example ................................................................................118

64 DDR Clock Routing Topology (SCK[5:0]/SCK[5:0]#)................................................................1 26

65 DDR Clock Trace Length Matching Diagram............................................................................ 1 29

66 Data Signal Routing Topology..................................................................................................131

67 SDQS to Clock Trace Length Matching Diagram.. ...................................................................134

68 SDQ/SDM to SDQS Trace Length Matching Diagram .............................................................136

69 Control Signal Routing Topology.................................................................................. ....... .....139

70 Control Signal to Clock Trace Length Matching Diagram.........................................................141

71 Command Routing for Topology...............................................................................................143

72 Topology Command Signal to Clock Trace Length Matching Diagram....................................145

73 CPC Control Signal Routing Topology .....................................................................................1 47

74 CPC Signals to Clock Length Matching Diagram.....................................................................1 49

75 GM CH DAC Routing Gui d el i n e s...............................................................................................155

76 Rse t Placement ................................................................................................ ........................156

77 DAC R, G, B Routing and Resistor Layout Example................................................................157

78 DVOB and DVOC Simulations Model . ......................................................................................167

79 Driver-Receiver Waveforms Relationship Specification...........................................................168

80 DVO Enabled Simulation Model ..................................................................... ......... ............ .....169

81 Generic Module Connector Parasitic Model...................................................................... .......169

82 GV REF Refe r e n ce Volta g e. ..................................................................................................... .171

83 AGP Layout Guidelines ............................................................................................................176

13

Page 14

Intel® 855GME Chipset and Intel® 6300ESB ICH Embedded Platform Design Guide

84 DPMS Circuit............................................................................................................................182

85 8-Bit Hub Interface Routing Example .......................................................................................183

86 8-Bit Hub Interface Single HIREF/HI_VSWING Generation Circuit Option A...........................185

87 8-Bit Hub Interface Local HIREF/HI_VSWING Generation Circuit Option B............................186

88 8-Bit Hub Interface Single HIREF/HI_VSWING Generation Circuit Option C ..........................186

89 8-Bit Hub Interface Local HIREF/HI_VSWING Generation Circuit Option D............................187

90 GMCH Locally Generated Reference Voltage Divider Circuit ..................................................187

91 Individual HLVREF and PSWING Voltage Reference Divider Circuits for GMCH ..... .......... ....188

92 Serial ATA Trace Spacing Recommendation............................................................. ............ ..192

93 SATA BIAS Connections ..................................................................................... ....... ............ ..193

94 SATALED# Circuitry Exa mple ..................................................................................................193

95 Combination Host-Si de/Device-Side IDE Cable Detecti on.......................................................196

96 Device Side IDE Cable Detection.............................................................................................197

97 Connection Requirements for Primary IDE Connector.. ........................................................... 198

98 Connection Requirements for Secondary IDE Connector........................................................199

99 6300ESB AC'97 - Codec C onnection.......................................................................................200

100 6300ESB AC'97 – AC_BIT_CLK Topology ..............................................................................201

101 6300ESB AC'97 – AC_SDOUT/AC_SYNC Topology ..............................................................202

102 6300ESB AC'97 – AC_SDIN Topology....................................................................................202

103 Example Sp e ak er Circuit..........................................................................................................205

104 CNR Interface...........................................................................................................................207

105 Motherboard AC’97 CNR Implementation with a Single Codec Down On Board.....................208

106 Motherboard AC’97 CNR Implementation without Codec Down On Board..............................209

107 Trace Routing...........................................................................................................................211

108 Recommended Genera l USB Trace Spacing (55 Ω ± 10%).....................................................211

109 USB BIAS Connections............................................................................................................ 212

110 Good Downs tre a m Po wer Con nection .....................................................................................214

111 A Common-Mode Choke.................................................................. .......... ....... .. ....... .......... ....215

112 Front Panel Header Schematic . ...............................................................................................218

113 Motherboard Front Panel USB Support........................................................................... ....... ..219

114 LPC Interface Diagram.............................................................................................................220

115 LPC Interface Topology......... ....................................................................... ............................220

116 SMBUS 2.0/SMLink Interf a c e............ .......................................................................................222

117 High Power/Low Power M ixed VCC_SUSPEND/VCC_CORE Architecture ............................223

118 PCI Bus Layout Example..........................................................................................................225

119 PCI Bus Layout Example with IDSEL.......................................................................................225

120 PCI 33MHz Clock Layout Example ..........................................................................................226

121 Example PIRQ Routi n g............ ................................................................................................227

122 66 MHz PCI-X, Two Slots, Two Down Devices Configuration.................................................. 229

123 66 MHz PCI-X, One Down Device Configuration.....................................................................229

124 66 MHz PCI-X, Three Slot Configuration..................................................................................230

125 66 MHz Clock Signal Configuration..........................................................................................231

126 Usage Model for SBR Functionality..........................................................................................232

127 RTCX1 and SUSCLK Relationship in 6300ESB.......................................................................233

128 External Circuitry in the 6300ESB Without Use of Int e r n al RTC..................... .........................234

129 External Circuitry for the 6300ESB RTC ..................................................................................234

130 Diode Circuit to Connect RTC External Battery........................................................................237

131 RTCRST# External Circuit for the 6300ESB RTC.................................................... .. ..... ....... ..238

132 FWH/CPU UP Signal Topology Solution.................................................... ....... ....... ....... ....... ..241

133 FWH Level Tran slation Circuitry...... ........................................................................................ .241

14

Page 15

Intel® 855GME Chipset and Intel® 6300ESB ICH Embedded Platform Design Guide

134 FWH VPP Isol a tion Circuitry.....................................................................................................242

135 SYS_RESET# and PWRBTN# Connection......................................................................... .....244

136 RTC Power Well Iso l a tion Control.............. ..............................................................................245

137 Clock Distribution Diagram.......................................................................................................250

138 Source Shunt Termination Topology ........................................................................................2 51

139 CLK66 Clock Group Topology..................................................................................................254

140 CLK33 Group Topology............................................................................................................255

141 PCI Clock Group Topology........................................................................................... ....... .....256

142 CLK14 Clock Group Topology..................................................................................................257

143 DOTCLK Clock Topology .........................................................................................................2 58

144 SSCCLK Clock Topology..........................................................................................................259

145 USBCLK Clock Topology..........................................................................................................260

146 Source Shunt Termination........................................................................................................261

147 Tr ac e Spa cing for SRC Clocks......... ........................................................................................262

148 Routing Illustration for INIT# (for Intel

149 Voltage Translation Circuit for PROCHOT# (for Intel

150 Reference Voltage Level for SMVREF.....................................................................................2 74

151 Intel

®

855GME Chipset HXSWING and HYSWING Referen ce

®

Pentium® M/Celeron® M Processor)..........................267

®

Pentium® M/Celeron® M Processor)...268

Voltage Generation Circuit........................................................................................................277

15

Page 16

Intel® 855GME Chipset and Intel® 6300ESB ICH Embedded Platform Design Guide

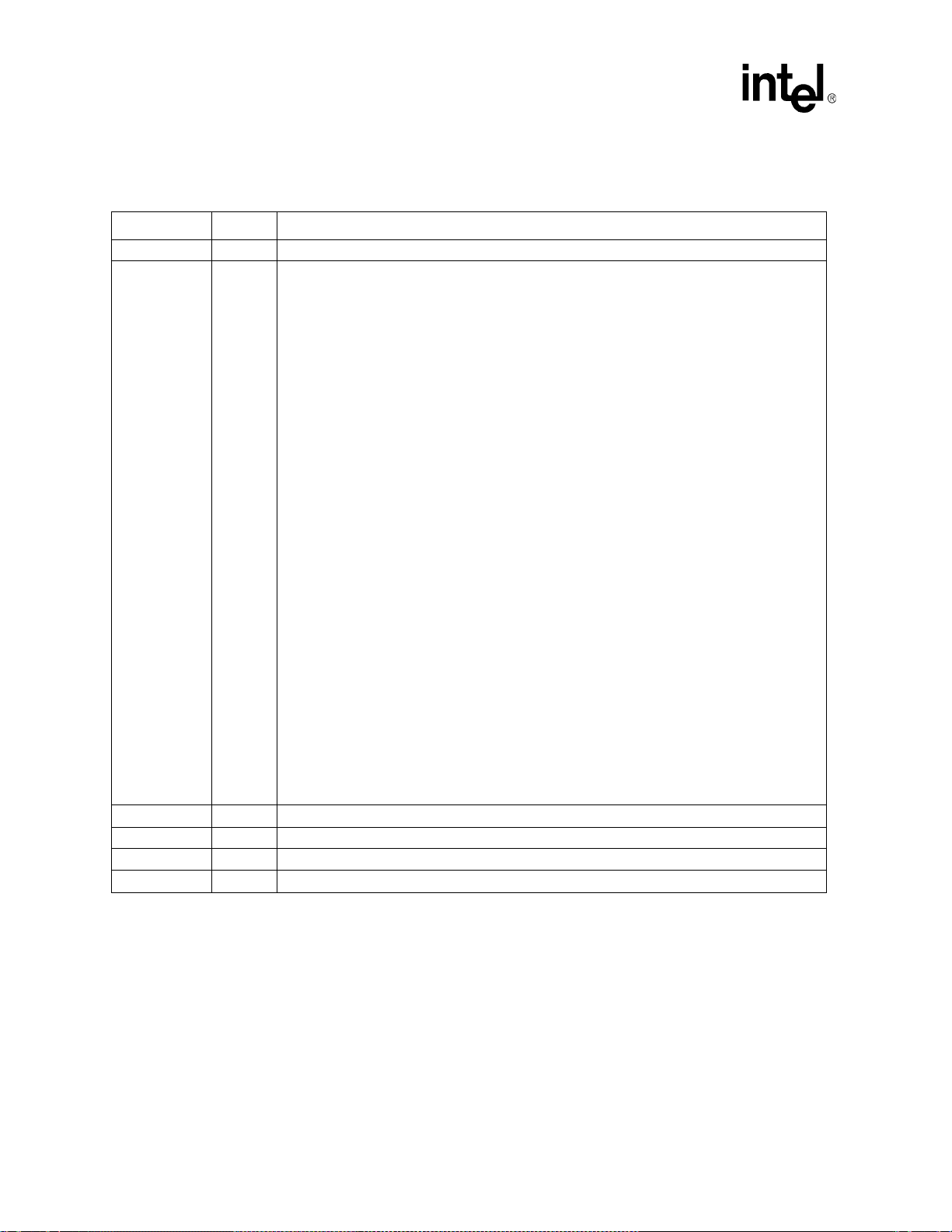

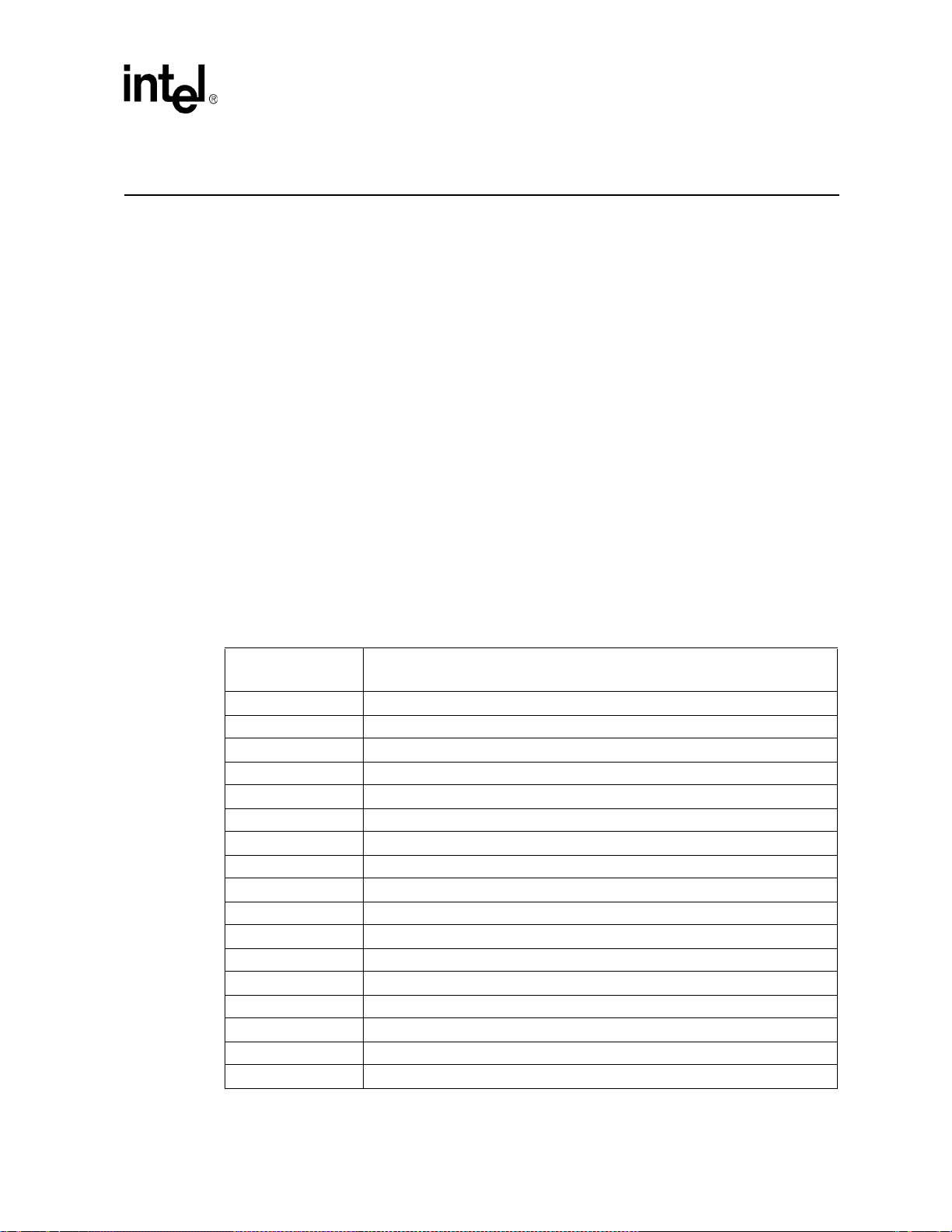

Tables

1 Conventions and Terminology....................................................................................................21

2 Refer e n ce Documents................................................................................................................23

3Intel

4Intel

5Intel

6Intel

7Intel

8Intel

9Intel

10 Asyn ch r o nous AG TL+ Nets........................................................................................................58

11 Layout Recommendations for Topology 1A ............................ ....... ....... ....... ....... ....... .......... ......59

12 Layout Recommendations for Topology 1B ............................ ....... ....... ....... ....... ....... .......... ......60

13 Layout Recommendations for Topology 1C ...............................................................................61

14 Layout Recommendations for Topology 2A ............................ ....... ....... ....... ....... ....... .......... ......62

15 Layout Recommendations for Topology 2B ............................ ....... ....... ....... ....... ....... .......... ......62

16 Layout Recommendations for Topology 3.................................................... ....... ....... .......... ......63

17 Processor RESET# Signal Routing Guidelines with ITP700FLEX Connector ...........................65

18 ITP Signal Default Strapping When ITP Debug Port Not Used..................................................73

19 Recommended ITP700FLEX Signal Termin ations.....................................................................80

20 VCCA[3 :0 ] De co u pling Guidelines..............................................................................................88

21 Intel

22 Intel

23 DDR Power-Up Initializat ion Sequence.............. ......................................................................107

24 GMCH Decoupling Recommendations.....................................................................................108

25 Analog Supply Filter Requirements..........................................................................................117

26 Power Signal Decoupling ............. ....... .......... .. ....... ..... ....... ..... ....... .. .......... .. ....... ..... ....... ..... ....121

27 Intel

28 Length Matching Formulas.......................................................................................................124

29 Clock Signal Mapping....................................................... ........................................................125

30 DDR Clock Signal Group Routing Guidelines ..........................................................................126

31 DDR Clock Package Lengths.. .................................................................................................130

32 Data Signal Group Routing Guidelines. . ...................................................................................132

33 SDQ/SDM to SDQS Mapping ...................................................................................................135

34 DDR SDQ/SDM/SDQS Package Lengths................................................................................137

35 Control Signal to DIMM Mapping..............................................................................................138

36 Control Signal Routing Guidelines.. .......................................................................................... 140

37 Control Group Package Lengths ..............................................................................................142

38 Command Topology Routing Guidelines..................................................................................143

39 Command Group Package Lengths .........................................................................................146

40 Control Signal to DIMM Mapping..............................................................................................146

41 CPC Contro l Signal Routing Guid elines...................................................................................148

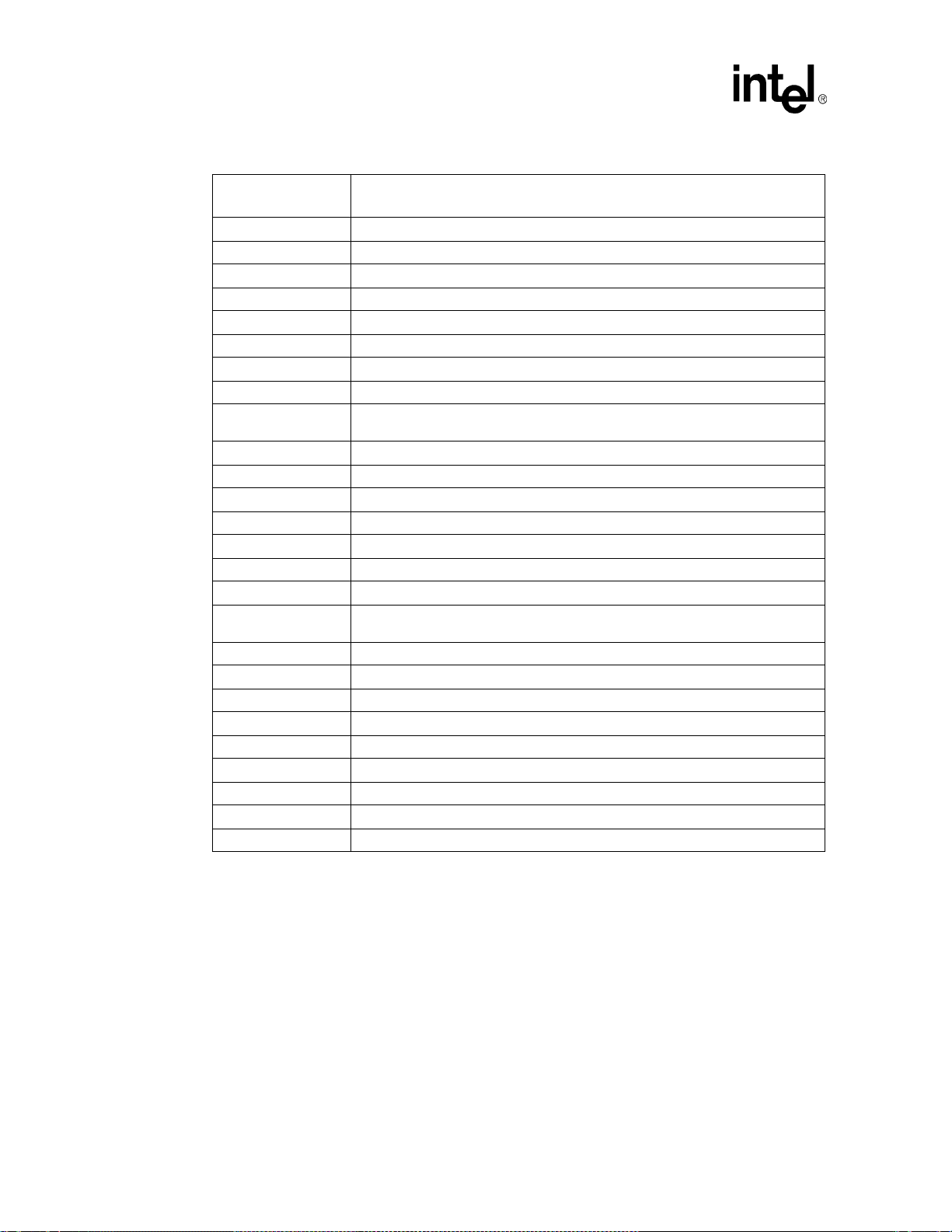

®

Penti u m® M/Cele r on® M Processor System Bus

Common Clock Signal Internal Layer Routing Guidelines..........................................................40

®

Penti u m® M/Cele r on® M Processor and Intel® GMCH FSB Common Clock

Signal Package Lengths and Minimum Board Trace Lengt hs....................................................42

®

Penti u m® M/Cele r on® M Processor FSB Data Source Synchronous Signal

Trace Length Mismatch Mapping ...............................................................................................48

®

Penti u m® M/Cele r on® M Processor System Bus Source Synchronous

Data Signal Routing Guidelines..................................................................................................48

®

Penti u m® M/Cele r on® M Processor FSB Address Source Synchronous

Signal Trace Length Mismatch Mapping....................................................................................49

®

Penti u m® M/Cele r on® M Processor FSB Source Synchronous

Address Sign al Routing Guidelin e s........ ....................................................................................49

®

Penti u m® M/Cele r on® M Processor and GMCH Source Synchronous

FSB Signal Pack a ge Leng ths.......... ............................ ...............................................................50

®

Penti u m® M/Cele r on® M Processor VCC-CORE Decoupling Guidelines ........................95

®

Penti u m® M/Cele r on® M Processor VCCP Decoupling Guidelines................................ 101

®

855GME Chipset DDR Signal Groups............................................................................123

16

Page 17

Intel® 855GME Chipset and Intel® 6300ESB ICH Embedded Platform Design Guide

42 CPC Group Package Lengths ..................................................................................................1 50

43 Recommended GMCH DAC Components ...............................................................................1 56

44 Signal Group and Signal Pair Names.......................................................................................158

45 LVDS Signal Trace Length Matching Requirements ................................................................159