Page 1

R

Intel® 852GM Chipset Platform

Design Guide

For Use with the Mobile Intel® Pentium® 4 Processor-M, Mobile Intel®

Celeron® Processor on .13 Micron Process in the 478-Pin Package, and

Intel® Celeron® M Processor

January 2005

Document Number: 252338-003

Page 2

R

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended

for use in medical, life saving, or life sustaining applications.

Actual system-level properties, such as skin temperature, are a function of various factors, including component placement, component power

characteristics, system power and thermal management techniques, software application usage and general system design. Intel is not responsible for its

customers’ system designs, nor is Intel responsible for ensuring that its customers’ products comply with all applicable laws and regulations. Intel

provides this and other thermal design information for informational purposes only. System design is the sole responsibility of Intel’s customers, and

Intel’s customers should not rely on any Intel-provided information as either an endorsement or recommendation of any particular system design

characteristics.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future

definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Mobile Intel® Pentium® 4 Processor-M , Intel® Celeron® Processor, Intel ® Celeron M® Processor and Intel 852GM Chipset may contain design

defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on

request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

2

I

C is a 2-wire communications bus/protocol developed by Philips*. SMBus is a subset of the I2C bus/protocol and was developed by Intel.

Implementations of the I

Corporation.

Alert on LAN is a result of the Intel-IBM Advanced Manageability Alliance and a trademark of IBM*.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

www.intel.com

or call 1-800-548-4725

Intel, Intel logo, Pentium, Intel SpeedStep, and Intel NetBurst are registered trademarks or trademarks of Intel Corporation and its subsidiaries in the

United States and other countries.

*Other brands and names are the property of their respective owners.

Copyright © Intel Corporation 2003-2005

2

C bus/protocol may require licenses from various entities, including Philips* Electronics N.V. and North American Philips

2 Intel

®

852GM Chipset Platform Design Guide

Page 3

R

Contents

1. Introduction .................................................................................................................................19

1.1. Terminology ...................................................................................................................19

1.2. Referenced Documents .................................................................................................20

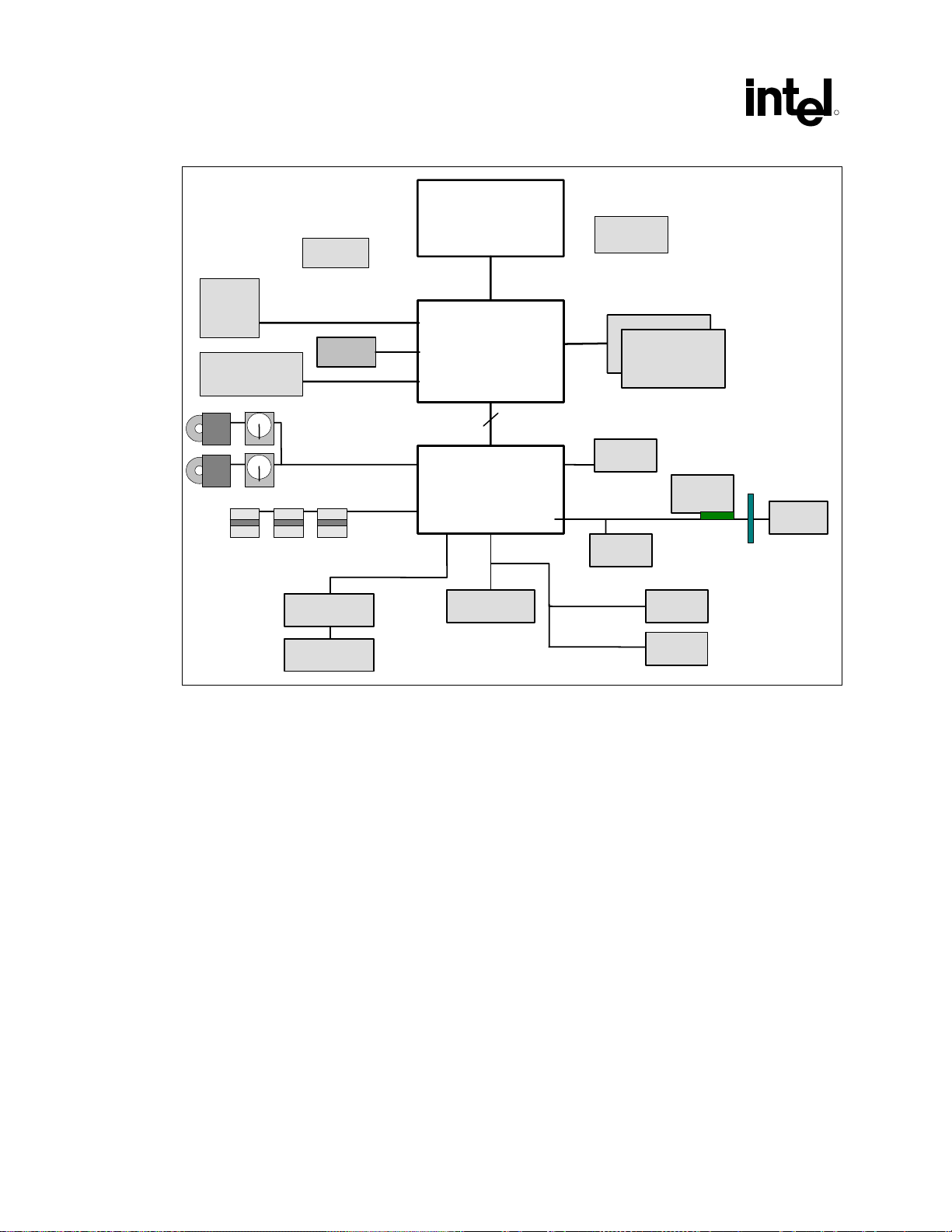

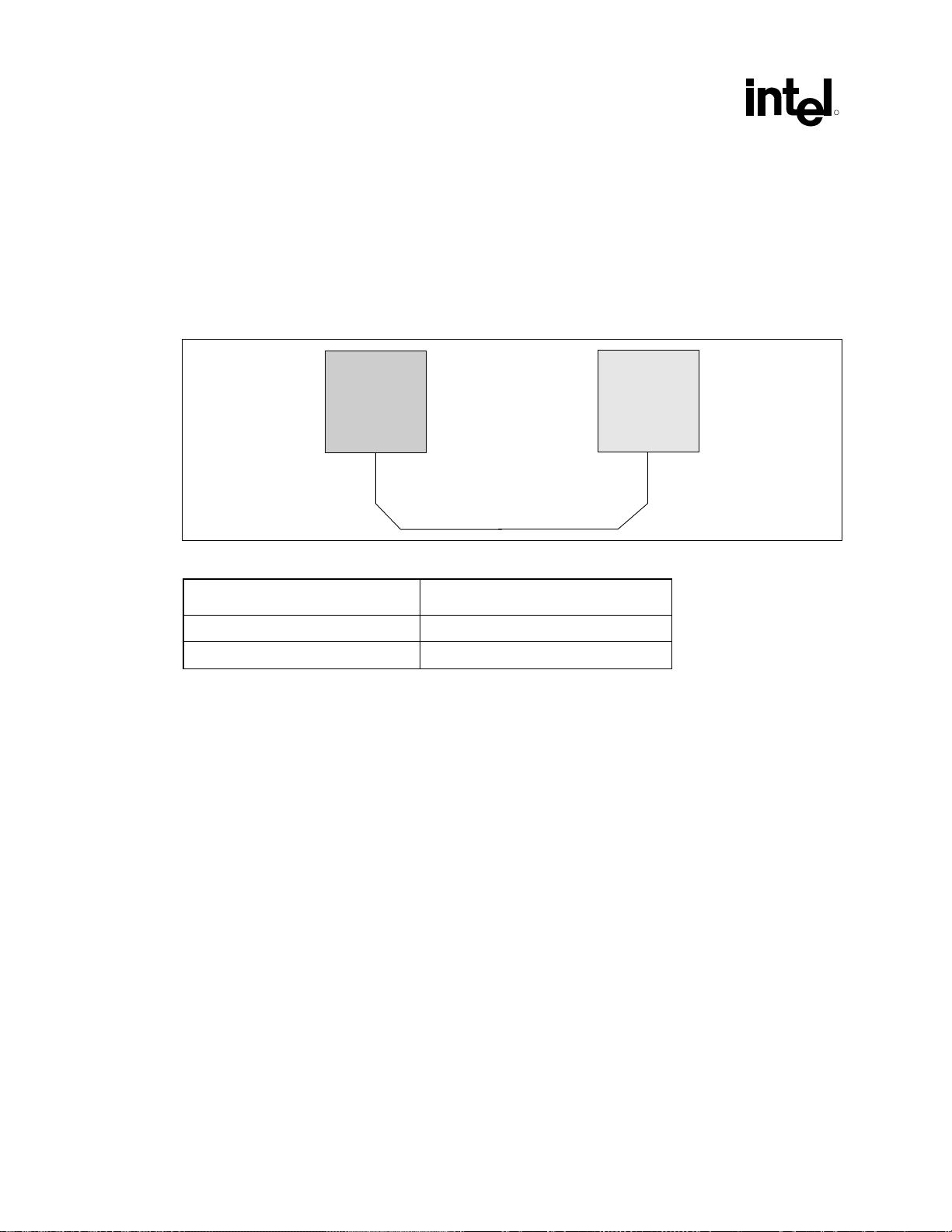

2. System Overview........................................................................................................................21

2.1. Intel® 852GM Chipset Platform System Features .........................................................21

2.2. Processor Interface........................................................................................................22

2.2.1. Mobile Intel Celeron Processor......................................................................22

2.2.2. Mobile Intel Pentium 4 Processor-M ..............................................................23

2.2.3. Intel Celeron M Processor..............................................................................23

2.3. Intel 852GM Graphics Memory Controller Hub .............................................................24

2.3.1. Processor Front Side Bus Support ................................................................24

2.3.1.1. Integrated System Memory DRAM Controller ................................24

2.3.2. Integrated Graphics Controller.......................................................................24

2.3.2.1. Packaging/Power ............................................................................25

2.3.3. I/O Controller Hub (ICH4-M) ..........................................................................25

2.3.3.1. Packaging/Power ............................................................................26

3. General Design Considerations .................................................................................................27

3.1. Nominal Board Stack-Up ...............................................................................................27

3.2. Alternate Stack Ups .......................................................................................................29

4. Mobile Intel Pentium 4 Processor–M and Mobile Intel Celeron Processor FSB Design

Guidelines...................................................................................................................................31

4.1. Processor Front Side Bus (FSB) Routing Guidelines....................................................31

4.1.1. Return Path Evaluation ..................................................................................33

4.2. Processor Configuration ................................................................................................33

4.3. General Topology and Layout Design Guidelines.........................................................33

4.3.1. Source Synchronous (SS) Signal Group .......................................................34

4.3.1.1. Source Synchronous Data Group...................................................34

4.3.1.2. Source Synchronous Address Group .............................................35

4.3.2. FSB Data and Address Routing Example......................................................36

4.3.3. Common Clock (CC) AGTL+ Signal Group ...................................................39

4.3.4. Asynchronous AGTL+ Signals.......................................................................39

4.3.4.1. Topology 1A: Open Drain (OD) Signals Driven by the Processor –

IERR# and FERR#..........................................................................39

4.3.4.2. Topology 1B: Open Drain (OD) Signals Driven by the Processor –

THERMTRIP# .................................................................................40

4.3.4.3. Topology 1C: Open Drain (OD) Signals Driven by the Processor –

PROCHOT# ....................................................................................41

4.3.4.4. Topology 2A: Open Drain (OD) Signals Driven by ICH4-M –

PWRGOOD.....................................................................................42

4.3.4.5. Topology 2B: CMOS Signals Driven by ICH4-M – DPSLP# ..........43

4.3.4.6. Topology 2C: CMOS Signals Driven by ICH4-M – A20M#, IGNNE#,

LINT0/INTR, LINT1/NMI, SLP#, SMI#, and STPCLK# ...................44

4.3.4.7. Topology 3: CMOS Signals Driven by ICH4-M to CPU and FWH –

INIT#................................................................................................44

4.4. ITP Debug Port ..............................................................................................................45

4.4.1. Logic Analyzer Interface (LAI)........................................................................46

4.4.1.1. Mechanical Considerations.............................................................46

4.4.1.2. Electrical Considerations ................................................................46

®

Intel

852GM Chipset Platform Design Guide 3

Page 4

4.5.

Mobile Intel Pentium 4 Processor–M and Intel 852GM Chipset FSB Signal Package

Lengths .........................................................................................................................46

4.5.1. Mobile Intel Pentium 4 Processor-M GTLREF Layout and Routing

Recommendations......................................................................................... 50

4.5.2. AGTL+ I/O Buffer Compensation .................................................................. 50

4.5.2.1. Mobile Intel Pentium 4 Processor–M AGTL+ I/O Buffer

Compensation ................................................................................ 51

5. Intel Celeron M Processor Front Side Bus Design Guidelines .................................................. 52

5.1. Intel Celeron M Processor Front Side Bus Design Recommendations ........................ 52

5.2. Recommended Stack-up Routing and Spacing Assumptions ...................................... 52

5.2.1. Trace Space to Trace – Reference Plane Separation Ratio......................... 52

5.2.2. Trace Space to Trace Width Ratio ................................................................ 53

5.3. Common Clock Signals ................................................................................................. 53

5.3.1. Processor Common Clock Signal Package Length Compensation.............. 54

5.4. Source Synchronous Signals General Routing Guidelines .......................................... 56

5.4.1. Source Synchronous Signal Length Matching Constraints........................... 58

5.4.2. Package Length Compensation .................................................................... 58

5.4.3. Source Synchronous – Data Group .............................................................. 59

5.4.4. Source Synchronous – Address Group......................................................... 60

5.4.5. Intel Celeron M Processor and Intel 852GM Chipset GMCH FSB Signal

Package Lengths ........................................................................................... 61

5.5. Asynchronous Signals................................................................................................... 64

5.5.1. Topology 1A: Open Drain (OD) Signals Driven by the Processor – IERR#.. 65

5.5.2. Topology 1B: Open Drain (OD) Signals Driven by the Processor – FERR#

and THERMTRIP#......................................................................................... 65

5.5.3. Topology 1C: Open Drain (OD) Signals Driven by the Processor –

PROCHOT#................................................................................................... 66

5.5.4. Topology 2A: Open Drain (OD) Signals Driven by ICH4-M – PWRGOOD... 67

5.5.5. Topology 2B: CMOS Signals Driven by ICH4-M – DPSLP# ......................... 68

5.5.6. Topology 2C: CMOS Signals Driven by ICH4-M – LINT0/INTR, LINT1/NMI,

A20M#, IGNNE#, SLP#, SMI#, and STPCLK# ............................................. 68

5.5.7. Topology 3: CMOS Signals Driven by ICH4-M to CPU and FWH – INIT# ... 69

5.5.8. Voltage Translation Logic .............................................................................. 70

5.6. Processor RESET# Signal ............................................................................................ 71

5.6.1. Processor RESET# Routing Example........................................................... 72

5.7. Processor and GMCH Host Clock Signals.................................................................... 73

5.8. Processor GTLREF Layout and Routing Recommendations ....................................... 74

5.9. AGTL+ I/O Buffer Compensation .................................................................................. 76

5.9.1. Processor AGTL+ I/O Buffer Compensation ................................................. 76

5.10. Intel Celeron M Processor Front Side Bus Strapping and Debug Port......................... 79

5.11. Processor V

CCSENSE/VSSSENSE

Design Recommendations ............................................. 80

6. Processor Power Delivery Requirements .................................................................................. 81

7. System Memory Design Guidelines (DDR-SDRAM) ................................................................. 83

7.1. Length Matching and Length Formulas......................................................................... 84

7.2. Package Length Compensation .................................................................................... 84

7.3. Topologies and Routing Guidelines .............................................................................. 85

7.3.1. Clock Signals – SCK[4,3,1,0], SCK#[4,3,1,0]................................................ 85

7.3.2. Clock Topology Diagram ............................................................................... 85

7.3.3. DDR Clock Routing Guidelines ..................................................................... 86

7.3.3.1. Clock Length Matching Requirements ........................................... 87

7.3.3.2. Clock Reference Lengths............................................................... 87

R

4 Intel

®

852GM Chipset Platform Design Guide

Page 5

R

7.3.3.3.

Clock Package Length Table..........................................................89

7.3.3.4. Clock Routing Example...................................................................89

7.3.3.4.1. Clock Routing Updates for “DDP Stacked” Memory

Device Support .............................................................90

7.3.4. Data Signals – SDQ[64:0], SDM[7:0], SDQS[7:0]..........................................90

7.3.4.1. Data Bus Topology..........................................................................92

7.3.4.2. SDQS to Clock Length Matching Requirements.............................94

7.3.4.3. Data to Strobe Length Matching Requirements..............................95

7.3.4.4. SDQ to SDQS Mapping ..................................................................96

7.3.4.5. SDQ/SDQS Signal Package Lengths.............................................98

7.3.4.6. DDR Data Routing Example .........................................................100

7.3.5. Control Signals – SCKE[3:0], SCS#[3:0] .....................................................100

7.3.5.1. Control Signal Topology................................................................101

7.3.5.2. Control Signal Routing Guidelines................................................102

7.3.5.3. Control to Clock Length Matching Requirements.........................103

7.3.5.4. DDR Control Routing Example .....................................................105

7.3.5.5. Control Group Package Length Table ..........................................106

7.3.6. Command Signals – SMA[12:6,3,0], SBA[1:0], SRAS#, SCAS#, SWE#.....106

7.3.6.1. Command Topology 1...................................................................106

7.3.6.2. Command Topology 1 Routing Guidelines...................................108

7.3.6.3. Command Topology 1 Length Matching Requirements ...............109

7.3.6.4. Command Topology 2...................................................................111

7.3.6.5. Command Topology 2 Routing Guidelines...................................112

7.3.6.6. Command Topology 2 Length Matching Requirements ...............113

7.3.6.7. Command Topology 2 Routing Example......................................115

7.3.6.8. Command Topology 3...................................................................116

7.3.6.9. Command Topology 3 Routing Guidelines...................................117

7.3.6.10. Command Topology 3 Length Matching Requirements ...............118

7.3.6.11. Command Group Package Length Table .....................................120

7.3.7. CPC Signals – SMA[5,4,2,1], SMAB[5,4,2,1]...............................................121

7.3.7.1. CPC Signal Topology....................................................................122

7.3.7.2. CPC Signal Routing Guidelines....................................................122

7.3.7.3. CPC to Clock Length Matching Requirements .............................123

7.3.7.4. CPC Group Package Length Table ..............................................125

7.3.8. Feedback – RCVENOUT#, RCVENIN#.......................................................125

7.4. System Memory Compensation...................................................................................125

7.5. SMVREF Generation ...................................................................................................125

7.6. DDR Power Delivery....................................................................................................125

7.7. External Thermal Sensor Based Throttling (ETS#) .....................................................126

7.7.1. ETS# Usage Model......................................................................................126

7.7.2. ETS# Design Guidelines..............................................................................126

7.7.3. Thermal Sensor Placement Guidelines .......................................................127

8. Integrated Graphics Display Port .............................................................................................129

8.1. Analog RGB/CRT Guidelines ......................................................................................129

8.1.1. RAMDAC/Display Interface..........................................................................129

8.1.2. Reference Resistor (REFSET).....................................................................129

8.1.3. RAMDAC Board Design Guidelines.............................................................130

8.1.4. RAMDAC Routing Guidelines ......................................................................131

8.1.5. DAC Power Requirements...........................................................................133

8.1.6. HSYNC and VSYNC Design Considerations...............................................134

8.1.7. DDC and I2C Design Considerations ..........................................................134

8.2. LVDS Transmitter Interface .........................................................................................134

8.2.1. Length Matching Constraints .......................................................................135

®

Intel

852GM Chipset Platform Design Guide 5

Page 6

8.2.1.1.

Package Length Compensation ................................................... 136

8.2.2. LVDS Routing Guidelines............................................................................ 136

8.3. Digital Video Out Port.................................................................................................. 138

8.3.1. DVO Interface Signal Groups...................................................................... 138

8.3.1.1. DVOC Interface Signals ............................................................... 138

8.3.2. DVO Port Interface Routing Guidelines....................................................... 139

8.3.2.1. Length Mismatch Requirements................................................... 139

8.3.2.2. Package Length Compensation ................................................... 139

8.3.2.3. DVO Routing Guidelines .............................................................. 140

8.3.2.4. DVO Port Termination ..................................................................141

8.4. DVO GMBUS and DDC Interface Considerations ...................................................... 141

8.4.1. Leaving the DVO Port Unconnected ........................................................... 142

8.5. Miscellaneous Input Signals and Voltage Reference.................................................. 142

9. Hub Interface............................................................................................................................ 145

9.1. Hub Interface Compensation ...................................................................................... 145

9.2. Hub Interface Data HL[10:0] and Strobe Signals........................................................ 146

9.2.1. HL[10:0] and Strobe Signals Internal Layer Routing................................... 146

9.2.2. Terminating HL[11] ......................................................................................148

9.3. Hub VREF/VSWING Generation/Distribution ............................................................. 148

9.3.1. Single Generation Voltage Reference Divider Circuit ................................. 148

9.3.2. Locally Generated Voltage Reference Divider Circuit................................. 149

9.3.2.1. ICH4-M Single Generated Voltage Reference Divider Circuit ..... 149

9.3.2.2. GMCH Single Generated Voltage Reference Divider Circuit....... 150

9.3.3. Separate GMCH and ICH4-M Voltage Divider Circuits for VREF and

VSWING ......................................................................................................150

9.3.3.1. Separate ICH4-M Voltage Divider Circuits for HIVREF and

HI_VSWING.................................................................................. 150

9.3.3.2. Separate GMCH Voltage Divider Circuits for HLVREF and

PSWING ....................................................................................... 151

9.4. Hub Interface Decoupling Guidelines.......................................................................... 152

10. I/O Subsystem.......................................................................................................................... 153

10.1. IDE Interface................................................................................................................ 153

10.1.1. Cabling......................................................................................................... 153

10.1.2. Primary IDE Connector Requirements ........................................................ 154

10.1.3. Secondary IDE Connector Requirements ................................................... 155

10.1.4. Mobile IDE Swap Bay Support .................................................................... 155

10.1.4.1. ICH4-M IDE Interface Tri-State Feature....................................... 156

10.1.4.2. S5/G3 to S0 Power-Up Procedures for IDE Swap Bay................ 157

10.1.4.3. Power Down Procedures for Mobile Swap Bay ........................... 157

10.1.4.4. Power-Up Procedures After Device “Hot” Swap Completed........ 157

10.2. PCI............................................................................................................................... 158

10.3. AC’97........................................................................................................................... 158

10.3.1. AC’97 Routing.............................................................................................. 162

10.3.2. Motherboard Implementation....................................................................... 163

10.3.2.1. Valid Codec Configurations .......................................................... 163

10.3.3. SPKR Pin Configuration .............................................................................. 163

10.4. USB 2.0 Guidelines and Recommendations............................................................... 164

10.4.1. Layout Guidelines........................................................................................ 164

10.4.1.1. General Routing and Placement .................................................. 164

10.4.1.2. USB 2.0 Trace Separation............................................................ 165

10.4.1.3. USBRBIAS Connection ................................................................ 165

10.4.1.4. USB 2.0 Termination .................................................................... 166

R

6 Intel

®

852GM Chipset Platform Design Guide

Page 7

R

10.4.1.5.

USB 2.0 Trace Length Pair Matching ...........................................166

10.4.1.6. USB 2.0 Trace Length Guidelines ................................................166

10.4.2. Plane Splits, Voids, and Cut-Outs (Anti-Etch)..............................................166

10.4.2.1. VCC Plane Splits, Voids, and Cut-Outs (Anti-Etch)......................167

10.4.2.2. GND Plane Splits, Voids, and Cut-Outs (Anti-Etch) .....................167

10.4.3. USB Power Line Layout Topology...............................................................167

10.4.4. EMI Considerations......................................................................................168

10.4.4.1. Common Mode Chokes ................................................................168

10.4.5. ESD ..............................................................................................................169

10.5. IOAPIC (I/O Advanced Programmable Interrupt Controller) .......................................169

10.5.1. IOAPIC Disabling Options............................................................................170

10.5.1.1. Recommended Implementation ....................................................170

10.6. SMBus 2.0/SMLink Interface .......................................................................................170

10.6.1. SMBus Architecture and Design Considerations.........................................171

10.6.1.1. SMBus Design Considerations .....................................................171

10.6.1.2. General Design Issues and Notes ................................................172

10.6.1.3. High Power and Low Power Mixed Architecture...........................172

10.6.1.4. Calculating the Physical Segment Pull-Up Resistor .....................172

10.7. FWH.............................................................................................................................173

10.7.1. FWH Decoupling..........................................................................................173

10.7.2. In Circuit FWH Programming .......................................................................174

10.7.3. FWH INIT# Voltage Compatibility ................................................................174

10.7.4. FWH VPP Design Guidelines ........................................................................175

10.8. RTC..............................................................................................................................175

10.8.1. RTC Crystal..................................................................................................176

10.8.2. External Capacitors......................................................................................177

10.8.3. RTC Layout Considerations.........................................................................178

10.8.4. RTC External Battery Connections ..............................................................178

10.8.5. RTC External RTCRST# Circuit...................................................................179

10.8.6. V

DC Voltage and Noise Measurements................................................180

BIAS

10.8.7. SUSCLK.......................................................................................................180

10.8.8. RTC-Well Input Strap Requirements ...........................................................180

10.9. Internal LAN Layout Guidelines ...................................................................................181

10.9.1. ICH4-M – LAN Connect Interface Guidelines ..............................................182

10.9.1.1. Bus Topologies .............................................................................182

10.9.1.1.1. LOM (LAN On Motherboard) Point-To-Point

Interconnect ................................................................182

10.9.1.2. Signal Routing and Layout............................................................183

10.9.1.3. Crosstalk Consideration................................................................183

10.9.1.4. Impedances...................................................................................183

10.9.1.5. Line Termination ...........................................................................184

10.9.1.6. Terminating Unused LAN Connect Interface Signals ...................184

10.9.2. Intel 82562ET / Intel 82562 EM Guidelines .................................................184

10.9.2.1. Guidelines for Intel 82562ET / Intel 82562EM Component

Placement .....................................................................................184

10.9.2.2. Crystals and Oscillators ................................................................184

10.9.2.3. Intel 82562ET / Intel 82562EM Termination Resistors .................185

10.9.2.4. Critical Dimensions .......................................................................185

10.9.2.4.1. Distance from Magnetics Module to RJ-45

(Distance A) ................................................................186

10.9.2.4.2. Distance from Intel 82562ET to Magnetics Module

(Distance B) ................................................................186

10.9.2.5. Reducing Circuit Inductance .........................................................186

®

Intel

852GM Chipset Platform Design Guide 7

Page 8

10.9.2.5.1.

Terminating Unused Connections.............................. 187

10.9.2.5.2. Termination Plane Capacitance ................................. 187

10.9.3. Intel 82562ET/EM Disable Guidelines......................................................... 187

10.9.4. General Intel 82562ET/82562EM Differential Pair Trace Routing

Considerations............................................................................................. 188

10.9.4.1.1. Trace Geometry and Length ......................................189

10.9.4.1.2. Signal Isolation ........................................................... 190

10.9.4.1.3. Magnetics Module General Power and Ground Plane

Considerations............................................................ 190

10.9.4.2. Common Physical Layout Issues ................................................. 192

10.10. Power Management Interface ..................................................................................... 193

10.10.1. SYS_RESET# Usage Model ....................................................................... 193

10.10.2. PWRBTN# Usage Model............................................................................. 193

10.10.3. Power Well Isolation Control Strap Requirements ...................................... 193

10.11. CPU CMOS Considerations........................................................................................ 194

11. Platform Clock Routing Guidelines .......................................................................................... 197

11.1. System Clock Groups.................................................................................................. 197

11.2. Clock Group Topologies and Routing Constraints...................................................... 198

11.2.1. Host Clock Group ........................................................................................ 199

11.2.1.1. Host Clock Group General Routing Guidelines............................ 201

11.2.1.2. Clock to Clock Length Matching and Compensation ................... 201

11.2.1.3. EMI Constraints ............................................................................ 201

11.2.2. CLK66 Clock Group..................................................................................... 202

11.2.3. CLK33 Clock Group..................................................................................... 203

11.2.4. PCI Clock Group.......................................................................................... 204

11.2.5. CLK14 Clock Group..................................................................................... 205

11.2.6. DOTCLK Clock Group ................................................................................. 206

11.2.7. SSCCLK Clock Group ................................................................................. 207

11.2.8. USBCLK Clock Group ................................................................................. 208

11.3. CK-408 Clock Updates for Intel Celeron M Processor Platforms ............................... 209

11.4. CK-408 PWRDWN# Signal Connections.................................................................... 209

12. Intel 852GM Platform Power Delivery Guidelines.................................................................... 211

12.1. Definitions.................................................................................................................... 211

12.2. Platform Power Requirements ....................................................................................211

12.2.1. Platform Power Delivery Architectural Block Diagram ................................ 212

12.3. Voltage Supply ............................................................................................................214

12.3.1. Power Management States ......................................................................... 214

12.3.2. Power Supply Rail Descriptions .................................................................. 214

12.4. Intel 852GM Platform Power-Up Sequence................................................................ 215

12.4.1. Processor Power Sequence Requirement ..................................................215

12.4.2. GMCH Power Sequencing Requirements................................................... 215

12.4.3. ICH4-M Power Sequencing Requirements .................................................216

12.4.3.1. 3.3 V/1.5 V Power Sequencing..................................................... 218

12.4.3.2. V

12.4.3.3. V

Sequencing .........................................................................218

5REF

Design Guidelines .......................................................... 219

5REFSUS

12.4.4. DDR Memory Power Sequencing Requirements........................................ 220

12.5. Intel 852GM Platform Power Delivery Guidelines....................................................... 221

12.5.1. Processor Decoupling / Power Delivery Guidelines.................................... 221

12.5.2. Intel 852GM Decoupling Guidelines............................................................ 221

12.5.2.1. GMCH VCCSM Decoupling.......................................................... 222

12.5.2.2. DDR SDRAM VDD Decoupling .................................................... 223

12.5.2.3. DDR VTT Decoupling Placement and Layout Guidelines............ 223

R

8 Intel

®

852GM Chipset Platform Design Guide

Page 9

R

12.5.3.

DDR Memory Power Delivery Design Guidelines........................................223

12.5.3.1. 2.5-V Power Delivery Guidelines ..................................................224

12.5.3.2. GMCH and DDR SMVREF Design Recommendations................224

12.5.3.3. DDR SMRCOMP Resistive Compensation ..................................225

12.5.3.4. DDR VTT Termination ..................................................................226

12.5.3.5. DDR SMRCOMP, SMVREF, and VTT 1.25-V Supply Disable in

S3/Suspend...................................................................................226

12.5.4. Other GMCH Reference Voltage and Analog Power Delivery ....................226

12.5.4.1. GMCH GTLVREF..........................................................................226

12.5.4.2. GMCH AGTL+ I/O Buffer Compensation......................................229

12.5.4.3. GMCH AGTL+ Reference Voltage................................................229

12.5.4.4. GMCH Analog Power....................................................................229

12.5.5. ICH4-M Decoupling / Power Delivery Guidelines ........................................231

12.5.5.1. ICH4-M Decoupling.......................................................................231

12.5.6. Hub Interface Decoupling.............................................................................231

12.5.7. FWH Decoupling..........................................................................................231

12.5.8. General LAN Decoupling .............................................................................232

13. Reserved, NC, and Test Signals ..............................................................................................233

13.1. Intel 852GM GMCH RSVD Signals .............................................................................234

14. Platform Design Checklist ........................................................................................................237

14.1. General Information .....................................................................................................237

14.2. Customer Implementation of Voltage Rails .................................................................237

14.3. Design Checklist Implementation ................................................................................238

14.4. Mobile Intel Pentium 4 Processor-M and Mobile Intel Celeron Processor ..................239

14.4.1. Resistor Recommendations.........................................................................239

14.4.2. In Target Probe (ITP) ...................................................................................242

14.4.3. Decoupling Recommendations....................................................................242

14.4.4. Power-up Sequence.....................................................................................243

14.5. Intel Celeron M Processor ...........................................................................................244

14.5.1. Resistor Recommendations.........................................................................244

14.6. CK-408 Clock Checklist ...............................................................................................247

14.6.1. Resistor Recommendations.........................................................................247

14.7. Intel 852GM GMCH Checklist......................................................................................249

14.7.1. System Memory ...........................................................................................249

14.7.1.1. GMCH System Memory Interface .................................................249

14.7.1.2. DDR SO-DIMM Interface ..............................................................250

14.7.1.3. SODIMM Decoupling Recommendation.......................................251

14.7.2. FSB ..............................................................................................................251

14.7.3. Hub Interface................................................................................................252

14.7.4. Graphics Interfaces......................................................................................252

14.7.4.1. LVDS.............................................................................................252

14.7.4.2. DVO...............................................................................................252

14.7.4.3. DAC...............................................................................................254

14.7.5. Miscellaneous ..............................................................................................254

14.7.6. GMCH Decoupling Recommendations........................................................255

14.7.7. GMCH Power-up Sequence ........................................................................256

14.8. ICH4-M Checklist .........................................................................................................257

14.8.1. PCI Interface and Interrupts.........................................................................257

14.8.2. GPIO ............................................................................................................258

14.8.3. AGP_BUSY# Design Requirement..............................................................259

14.8.4. (SMBus) System Management Interface.....................................................259

14.8.5. AC ’97 Interface ...........................................................................................260

®

Intel

852GM Chipset Platform Design Guide 9

Page 10

14.8.6.

ICH4-M Power Management Interface........................................................ 261

14.8.7. FWH/LPC Interface...................................................................................... 261

14.8.8. USB Interface ..............................................................................................262

14.8.9. Hub Interface ............................................................................................... 262

14.8.10. RTC Circuitry ............................................................................................... 263

14.8.11. LAN Interface............................................................................................... 264

14.8.12. Primary IDE Interface ..................................................................................265

14.8.13. Secondary IDE Interface ............................................................................. 265

14.8.14. Miscellaneous Signals ................................................................................. 265

14.8.15. ICH4-M Decoupling Recommendations...................................................... 266

14.9. USB Power Checklist .................................................................................................. 267

14.9.1. Downstream Power Connection.................................................................. 267

14.10. FWH Checklist............................................................................................................. 268

14.10.1. Resistor Recommendations ........................................................................268

14.11. LAN / HomePNA Checklist.......................................................................................... 269

14.11.1. Resistor Recommendations (for 82562ET / 82562EM) .............................. 269

14.11.2. Decoupling Recommendations.................................................................... 269

15. Schematics............................................................................................................................... 271

R

10 Intel

®

852GM Chipset Platform Design Guide

Page 11

R

Figures

Figure 1. Intel 852GM Chipset System Block Diagram........................................................... 22

Figure 2. Recommended Board Stack-Up Dimensions .......................................................... 28

Figure 3. Cross-Sectional View of 2:1 Ratio............................................................................ 32

Figure 4. Processor Topology ................................................................................................. 34

Figure 5. SS Topology for Address and Data.......................................................................... 36

Figure 6. FSB Host Data Routing Example Layer 3................................................................ 36

Figure 7. FSB Host Address Routing Example Layer 3 .......................................................... 37

Figure 8. FSB Host Data Routing Example Layer 6................................................................ 37

Figure 9. FSB Host Address Routing Example Layer 6 .......................................................... 38

Figure 10. Routing Illustration for Topology 1A....................................................................... 40

Figure 11. Routing Illustration for Topology 1B....................................................................... 41

Figure 12. Routing Illustration for Topology 1C....................................................................... 42

Figure 13. Routing Illustration for Topology 2A....................................................................... 43

Figure 14. Routing Illustration for Topology 2B....................................................................... 43

Figure 15. Routing Illustration for Topology 2C....................................................................... 44

Figure 16. Routing Illustration for Topology 3 ......................................................................... 45

Figure 17. Voltage Translation Circuit for 3.3-V Receivers ..................................................... 45

Figure 18. GTLREF Routing.................................................................................................... 50

Figure 19. Mobile Intel Pentium 4 Processor-M COMP[1:0] Resistive Compensation ........... 51

Figure 20. Common Clock Topology....................................................................................... 55

Figure 21. Layer 6 FSB Source Synchronous Signals GND Referencing to Layer 5 ............. 57

Figure 22. Layer 3 FSB Source Synchronous Signals............................................................ 58

Figure 23. Routing Illustration for Topology 1A....................................................................... 65

Figure 24. Routing Illustration for Topology 1B....................................................................... 66

Figure 25. Routing Illustration for Topology 1C....................................................................... 67

Figure 26. Routing Illustration for Topology 2A....................................................................... 67

Figure 27. Routing Illustration for Topology 2B....................................................................... 68

Figure 28. Routing Illustration for Topology 2C....................................................................... 69

Figure 29. Routing Illustration for Topology 3 ......................................................................... 70

Figure 30. Voltage Translation Circuit ..................................................................................... 71

Figure 31. Processor RESET# Signal Routing Topology with NO ITP700FLEX Connector .. 71

Figure 32. Processor RESET# Signal Routing Topology with ITP700FLEX Connector......... 72

Figure 33. Processor RESET# Signal Routing Example with ITP700FLEX Debug Port........ 73

Figure 34. Processor and GMCH Host Clock Layout Routing Example ................................. 74

Figure 35. Processor GTLREF Voltage Divider Network ........................................................ 75

Figure 36. Processor GTLREF Motherboard Layout .............................................................. 76

Figure 37. Processor COMP[2] & COMP[0] Resistive Compensation.................................... 77

Figure 38. Processor COMP[3] & COMP[1] Resistive Compensation.................................... 77

Figure 39. Processor COMP[3:0] Resistor Layout .................................................................. 78

Figure 40. Processor COMP[1:0] Resistor Alternative Primary Side Layout .......................... 78

Figure 41. COMP2 & COMP0 27.4-Ω Traces ......................................................................... 79

Figure 42. V

CCSENSE/VSSSENSE

Figure 43. DDR Clock Routing Topology SCK/SCK#[5:0] ...................................................... 85

Figure 44. DDR Clock Trace Length Matching Diagram......................................................... 88

Figure 45. Clock Signal Routing Example............................................................................... 90

Figure 46. Data Signal Routing Topology ............................................................................... 92

Figure 47. SDQS to Clock Trace Length Matching Diagram .................................................. 95

Figure 48. SDQ/SDM to SDQS Trace Length Matching Diagram .......................................... 97

Routing Example....................................................................... 80

®

Intel

852GM Chipset Platform Design Guide 11

Page 12

Figure 49. Data Signals Group Routing Example.................................................................. 100

Figure 50. Control Signal Routing Topology.......................................................................... 101

Figure 51. Control Signal to Clock Trace Length Matching Diagram ....................................104

Figure 52. Control Signals Group Routing Example..............................................................105

Figure 53. Command Routing for Topology 1........................................................................ 107

Figure 54. Topology 1 Command Signal to Clock Trace Length Matching Diagram ............110

Figure 55. Command Routing Topology 2............................................................................. 111

Figure 56. Topology 2 Command Signal to Clock Trace Length Matching Diagram ............114

Figure 57. Example of Command Signal Group ....................................................................115

Figure 58. Command Routing Topology 3............................................................................. 116

Figure 59. Topology 3 Command Signal to Clock Trace Length Matching Diagram ............119

Figure 60. Command per Clock Signal Routing Topology ....................................................122

Figure 61. CPC Signals to Clock Length Matching Diagram................................................. 124

Figure 62. DDR Memory Thermal Sensor Placement ...........................................................127

Figure 63. GMCH RAMDAC Routing Guidelines with Docking Connector ........................... 131

Figure 64. RAMDAC Routing w/ Resistor and Analog Switch Layout Example for Docking

Connector ...............................................................................................................132

Figure 65. Rset Resistor Placement ......................................................................................133

Figure 66. GVREF Reference Voltage................................................................................... 143

Figure 67. Hub Interface Routing Example............................................................................ 145

Figure 68. Single VREF/VSWING Voltage Generation Circuit for Hub Interface ..................149

Figure 69. ICH4-M Locally Generated Reference Voltage Divider Circuit ............................150

Figure 70. GMCH Locally Generated Reference Voltage Divider Circuit.............................. 150

Figure 71. Individual HIVREF and HI_VSWING Voltage Reference Divider Circuits for

ICH4-M ...................................................................................................................151

Figure 72. Individual HLVREF and PSWING Voltage Reference Divider Circuits for

GMCH..................................................................................................................... 151

Figure 73. Connection Requirements for Primary IDE Connector......................................... 154

Figure 74. Connection Requirements for Secondary IDE Connector.................................... 155

Figure 75. PCI Bus Layout Example...................................................................................... 158

Figure 76. ICH4-M AC’97 – Codec Connection..................................................................... 159

Figure 77. ICH4-M AC’97 – AC_BIT_CLK Topology ............................................................. 160

Figure 78. ICH4-M AC’97 – AC_SDOUT/AC_SYNC Topology............................................. 160

Figure 79. ICH4-M AC’97 – AC_SDIN Topology ...................................................................161

Figure 80. Example Speaker Circuit ......................................................................................164

Figure 81. Recommended USB Trace Spacing..................................................................... 165

Figure 82. USBRBIAS Connection ........................................................................................166

Figure 83. Good Downstream Power Connection .................................................................168

Figure 84. Common Mode Choke Schematic........................................................................ 168

Figure 85. Minimum IOAPIC Disable Topology .....................................................................170

Figure 86. SMBUS 2.0/SMLink Protocol................................................................................ 171

Figure 87. High Power/Low Power Mixed VCC_

SUSPEND/VCC_CORE

Architecture...................... 172

Figure 88. Voltage Translation Circuit for 3.3-V Receivers ...................................................174

Figure 89. FWH VPP Isolation Circuitry.................................................................................175

Figure 90. RTCX1 and SUSCLK Relationship in ICH4-M .....................................................175

Figure 91. External Circuitry for the ICH4-M Where the Internal RTC Is Not Used ..............176

Figure 92. External Circuitry for the ICH4-M RTC ................................................................. 176

Figure 93. Diode Circuit to Connect RTC External Battery ................................................... 179

Figure 94. RTCRST# External Circuit for the ICH4-M RTC ..................................................179

Figure 95. ICH4-M/Platform LAN Connect Section ...............................................................181

Figure 96. Single Solution Interconnect................................................................................. 182

Figure 97. LAN_CLK Routing Example .................................................................................183

Figure 98. Intel 82562ET / Intel 82562EM Termination ......................................................... 185

Figure 99. Critical Dimensions for Component Placement.................................................... 185

R

12 Intel

®

852GM Chipset Platform Design Guide

Page 13

R

Figure 100. Termination Plane .............................................................................................. 187

Figure 101. Intel 82562ET/EM Disable Circuitry ................................................................... 188

Figure 102. Trace Routing..................................................................................................... 189

Figure 103. Ground Plane Separation................................................................................... 191

Figure 104. RTC Power Well Isolation Control ..................................................................... 194

Figure 105. ICH4-M CPU CMOS Signals with CPU and FWH ............................................. 195

Figure 106. Clock Distribution Diagram................................................................................. 198

Figure 107. Source Shunt Termination Topology ................................................................. 199

Figure 108. CLK66 Clock Group Topology ........................................................................... 202

Figure 109. CLK33 Group Topology ..................................................................................... 203

Figure 110. PCI Clock Group Topology ................................................................................ 204

Figure 111. CLK14 Clock Group Topology ........................................................................... 205

Figure 112. DOTCLK Clock Topology................................................................................... 206

Figure 113. SSCCLK Clock Topology ................................................................................... 207

Figure 114. USBCLK Clock Topology ................................................................................... 208

Figure 115. Platform Power Delivery Map............................................................................. 212

Figure 116. Platform Power Delivery Map for Intel Celeron M Processor ............................ 213

Figure 117. GMCH Power-Up Sequence .............................................................................. 216

Figure 118. ICH4-M Power-Up Sequence............................................................................. 217

Figure 119. Example V

5REF

/ V

Sequencing Circuitry.................................................. 219

5REFSUS

Figure 120. V5REFSUS With +V5ALWAYS Connection Option .......................................... 219

Figure 121. V5REFSUS With +V3ALWAYS and +V5S or +V5 Connection Option.............. 220

Figure 122. Example for Minimizing Loop Inductance .......................................................... 221

Figure 123. DDR Power Delivery Block Diagram.................................................................. 224

Figure 124. GMCH SMRCOMP Resistive Compensation .................................................... 225

Figure 125. GMCH System Memory Reference Voltage Generation Circuit........................ 225

Figure 126. GMCH HDVREF[2:0] Reference Voltage Generation Circuit ............................ 227

Figure 127. GMCH HAVREF Reference Voltage Generation Circuit ................................... 227

Figure 128. GMCH HCCVREF Reference Voltage Generation Circuit................................. 227

Figure 129. Primary Side of the Motherboard Layout .......................................................... 228

Figure 130. Secondary Side of the Motherboard Layout ...................................................... 228

Figure 131. GMCH HXRCOMP and HYRCOMP Resistive Compensation .......................... 229

Figure 132. GMCH HXSWING and HYSWING Reference Voltage Generation Circuit ....... 229

Figure 133. Example Analog Supply Filter ............................................................................ 230

Figure 134. Routing Illustration for INIT# .............................................................................. 241

Figure 135. Voltage Translation Circuit for PROCHOT#....................................................... 241

Figure 136. VCCIOPLL, VCCA and VSSA Power Distribution ............................................. 241

Figure 137. Mobile Intel Pentium 4 Processor-M Power Up Sequence................................ 244

Figure 138. Routing Illustration for INIT# (for Intel Celeron M Processor)............................ 246

Figure 139. Voltage Translation Circuit for PROCHOT# (for Intel Celeron M Processor).... 246

Figure 140. Clock Power-down Implementation ................................................................... 248

Figure 141. Reference Voltage Level for SMVREF .............................................................. 250

Figure 142. Intel 852GM GMCH HXSWING and HYSWING Reference Voltage Generation

Circuit ..................................................................................................................... 251

Figure 143. DPMS Clock Implementation ............................................................................. 253

Figure 144. Intel 852GM GMCH Power-up Sequence.......................................................... 256

Figure 145. Single or Locally Generated GMCH & ICH4-M HIVREF/HI_VSWING Circuit... 262

Figure 146. Single Generated GMCH & ICH4-M VSWING/VREF Reference Voltage/ Local

Voltage Divider Circuit for VSWING/VREF............................................................ 263

Figure 147. External Circuitry for the RTC ............................................................................ 264

Figure 148. Good Downstream Power Connection............................................................... 267

Figure 149. LAN_RST# Design Recommendation ............................................................... 269

®

Intel

852GM Chipset Platform Design Guide 13

Page 14

Tables

Table 1. Front Side Bus Routing Summary for the Processor................................................. 31

Table 2. Processor Front Side Bus Data Signal Routing Guidelines....................................... 35

Table 3. Processor Front Side Bus Address Signal Routing Guidelines................................. 35

Table 4. Processor Front Side Bus Control Signal Routing Guidelines .................................. 39

Table 5. Layout Recommendations for Topology 1A............................................................... 40

Table 6. Layout Recommendations for Topology 1B............................................................... 41

Table 7. Layout Recommendations for Topology 1C ..............................................................42

Table 8. Layout Recommendations for Topology 2A............................................................... 43

Table 9. Layout Recommendations for Topology 2B............................................................... 43

Table 10. Layout Recommendations for Topology 2C ............................................................44

Table 11. Layout Recommendations for Topology 3 ............................................................... 45

Table 12. Mobile Intel Pentium 4 Processor-M and Intel 852GM Chipset Package Lengths.. 46

Table 13. FSB Common Clock Signal Internal Layer Routing Guidelines .............................. 54

Table 14. Processor and GMCH FSB Common Clock Signal Package Lengths and Minimum

Board Trace Lengths................................................................................................ 55

Table 15. Processor FSB Data Source Synchronous Signal Trace Length Mismatch

Mapping.................................................................................................................... 59

Table 16. FSB Source Synchronous Data Signal Routing Guidelines ....................................60

Table 17. Processor FSB Address Source Synchronous Signal Trace Length Mismatch

Mapping.................................................................................................................... 60

Table 18. Processor FSB Source Synchronous Address Signal Routing Guidelines .............61

Table 19. Intel Celeron M Processor and GMCH Source Synchronous FSB Signal Package

Lengths..................................................................................................................... 62

Table 20. Asynchronous AGTL+ Nets ..................................................................................... 64

Table 21. Layout Recommendations for Topology 1A............................................................. 65

Table 22. Layout Recommendations for Topology 1B............................................................. 66

Table 23. Layout Recommendations for Topology 1C ............................................................67

Table 24. Layout Recommendations for Topology 2A............................................................. 68

Table 25. Layout Recommendations for Topology 2B............................................................. 68

Table 26. Layout Recommendations for Topology 2C ............................................................69

Table 27. Layout Recommendations for Topology 3 ............................................................... 70

Table 28. Processor RESET# Signal Routing Guidelines with ITP700FLEX Connector ........72

Table 29. ITP Signal Default Strapping When ITP Debug Port Not Used ............................... 80

Table 30. Intel 852GM GMCH Chipset DDR Signal Groups ...................................................83

Table 31. Length Matching Formulas ......................................................................................84

Table 32. Clock Signal Mapping .............................................................................................. 85

Table 33. Clock Signal Group Routing Guidelines ..................................................................86

Table 34. DDR Clock Package Lengths .................................................................................. 89

Table 35. Data Signal Group Routing Guidelines.................................................................... 93

Table 36. SDQ/SDM to SDQS Mapping .................................................................................. 96

Table 37. DDR SDQ/SDM/SDQS Package Lengths ...............................................................98

Table 38. Control Signal to SO-DIMM Mapping ....................................................................101

Table 39. Control Signal Routing Guidelines......................................................................... 102

Table 40. Control Group Package Lengths ...........................................................................106

Table 41. Command Topology 1 Routing Guidelines ............................................................ 108

Table 42. Command Topology 2 Routing Guidelines ............................................................ 112

Table 43. Command Topology 3 Routing Guidelines ............................................................ 117

Table 44. Command Group Package Lengths ......................................................................120

Table 45. CPC Signal to SO-DIMM Mapping ........................................................................121

Table 46. CPC Signal Routing Guidelines............................................................................. 122

R

14 Intel

®

852GM Chipset Platform Design Guide

Page 15

R

Table 47. CPC Group Package Lengths ............................................................................... 125

Table 48. Recommended GMCH RAMDAC Components.................................................... 133

Table 49. Signal Group and Signal Pair Names ................................................................... 135

Table 50. LVDS Signal Trace Length Matching Requirements ............................................ 135

Table 51. LVDS Signal Group Routing Guidelines ............................................................... 136

Table 52. LVDS Package Lengths ........................................................................................ 137

Table 53. DVO Interface Trace Length Mismatch Requirements ......................................... 139

Table 54. DVOC Routing Guideline Summary...................................................................... 140

Table 55. DVOC Interface Package Lengths ........................................................................ 141

Table 56. GMBUS Pair Mapping and Options....................................................................... 142

Table 57. Hub Interface RCOMP Resistor Values ................................................................ 145

Table 58. Hub Interface Signals Internal Layer Routing Summary....................................... 146

Table 59. Hub Interface Package Lengths for ICH4-M ......................................................... 147

Table 60. Hub Interface Package Lengths for GMCH........................................................... 147

Table 61. Hub Interface VREF/VSWING Reference Voltage Specifications ........................ 148

Table 62. Recommended Resistor Values for Single VREF/VSWING Divider Circuit ......... 149

Table 63. Recommended Resistor Values for HIVREF and HI_VSWING Divider Circuits for

ICH4-M................................................................................................................... 151

Table 64. Recommended Resistor Values for HLVREF and PSWING Divider Circuits for

GMCH .................................................................................................................... 152

Table 65. AC’97 AC_BIT_CLK Routing Summary ................................................................ 160

Table 66. AC’97 AC_SDOUT/AC_SYNC Routing Summary ................................................ 161

Table 67. AC’97 AC_SDIN Routing Summary ...................................................................... 161

Table 68. Supported Codec Configurations .......................................................................... 163

Table 69. USBRBIAS/USBRBIAS# Routing Summary ......................................................... 166

Table 70. USB 2.0 Trace Length Preliminary Guidelines (with Common Mode Choke) ...... 166

Table 71. Bus Capacitance Reference Chart........................................................................ 173

Table 72. Bus Capacitance/Pull-Up Resistor Relationship ................................................... 173

Table 73. RTC Routing Summary ......................................................................................... 177

Table 74. LAN Component Connections/Features ............................................................... 181

Table 75. LAN Design Guide Section Reference.................................................................. 181

Table 76. LAN LOM Routing Summary................................................................................. 183

Table 77. Intel 82562ET/EM Control Signals ........................................................................ 188

Table 78. Individual Clock Breakdown .................................................................................. 197

Table 79. Host Clock Group Routing Constraints ................................................................. 200

Table 80. Clock Package Length .......................................................................................... 201

Table 81. CLK66 Clock Group Routing Constraints.............................................................. 202

Table 82. CLK33 Clock Group Routing Constraints.............................................................. 203

Table 83. PCICLK Clock Group Routing Constraints............................................................ 204

Table 84. CLK14 Clock Group Routing Constraints.............................................................. 205

Table 85. DOTCLK Clock Routing Constraints ..................................................................... 206

Table 86. SSCCLK Clock Routing Constraints ..................................................................... 207

Table 87. USBCLK Clock Routing Constraints ..................................................................... 208

Table 88. Power Delivery Definitions .................................................................................... 211

Table 89. Power Management States on Intel Reference Board.......................................... 214

Table 90. Power Supply Rail Descriptions on Intel Reference Board................................... 214

Table 91. Timing Sequence Parameters for Figure 118 ....................................................... 218

Table 92. DDR Power-Up Initialization Sequence ................................................................ 220

Table 93. GMCH Decoupling Recommendations ................................................................. 222

Table 94. Analog Supply Filter Requirements....................................................................... 230

Table 95. ICH4-M Decoupling Requirements ....................................................................... 231

Table 96. Processor “Intel Reserved” Signal Pin-Map Locations ......................................... 233

Table 97. Intel 852GM RSVD and NC Signal Pin-Map Locations ........................................ 234

Table 98. Mobile Intel Pentium 4 Processor-M Power-up Timing Specifications ................. 243

®

Intel

852GM Chipset Platform Design Guide 15

Page 16

Table 99. GST[1:0] Configurations ........................................................................................255

Table 100. Intel 852GM GMCH Power-up Timing Specifications.......................................... 256

Equations

Equation 1. Calculation to Determine Package Delta Addition to Motherboard Length for UP

Systems .................................................................................................................... 34

R

16 Intel

®

852GM Chipset Platform Design Guide

Page 17

R

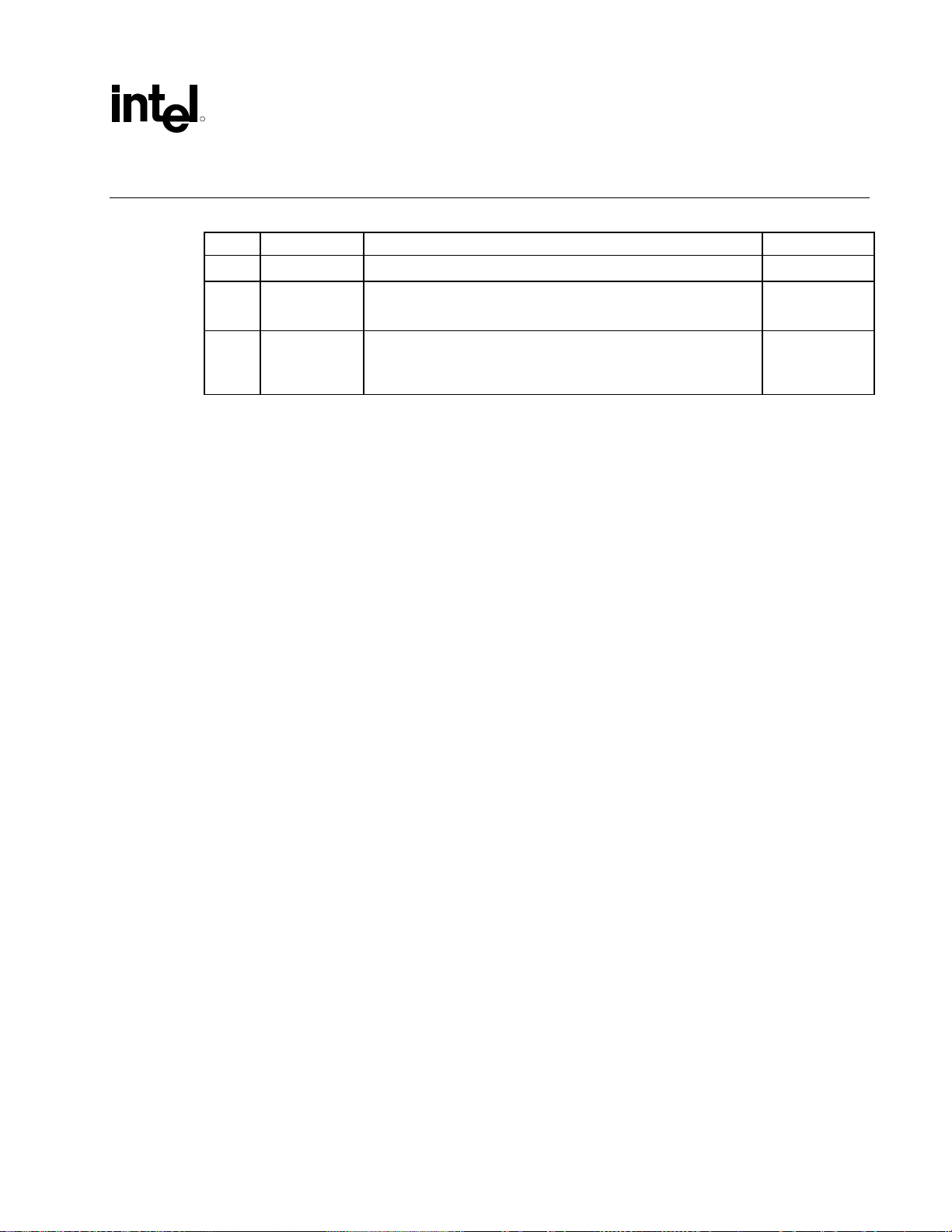

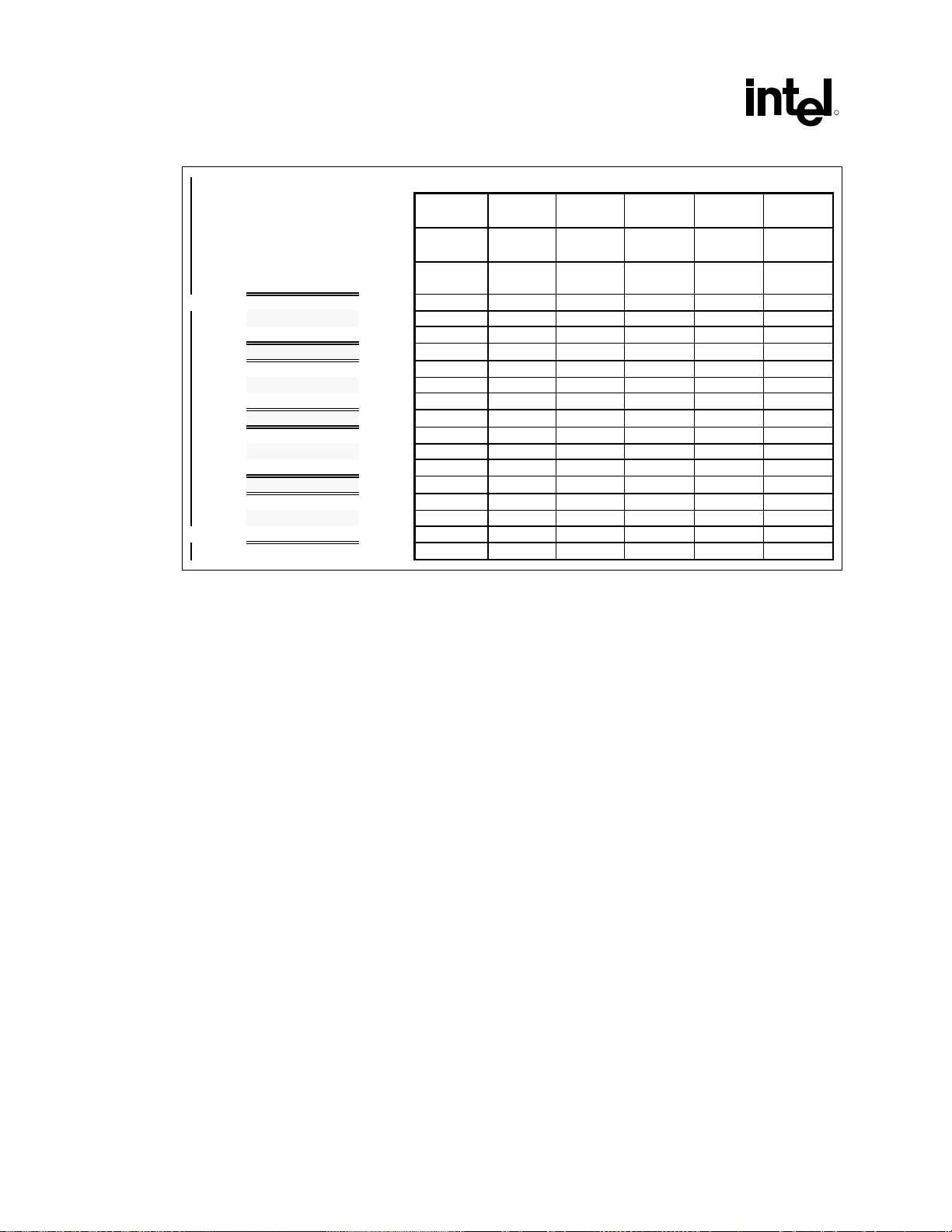

Revision History

Rev Order No. Description Date

001 252338

002 252338

003 252338

Initial Release

Revisions include:

• Added support for the Intel Celeron M Processor

Revisions include:

• Updated sheets 40 and 41 of the Intel Celeron M / 852GM CRB

schematics

January 2003

January 2004

January 2005

®

Intel

852GM Chipset Platform Design Guide 17

Page 18

This page intentionally left blank.

R

18 Intel

®

852GM Chipset Platform Design Guide

Page 19

R

1. Introduction

This design guide organizes and provides Intel’s design recommendations for the Intel® 852GM chipset

based systems. These design guidelines have been developed to ensure maximum flexibility for board

designers while reducing the risk of board related issues.

Introduction

The following processors can be combined with the Intel 852GM GMCH chipset:

• Mobile Intel

• Mobile Intel

• Intel

®

®

Pentium® 4 Processor-M

®

Celeron® processor

Celeron® M processor

1.1. Terminology

Term Definition

AC Audio Codec

AMC Audio/Modem Codec

Anti-Etch Any plane-split, void or cutout in a VCC or GND plane is referred to as an anti-etch

ASF Alert Standards Format

BER Bit Error Rate

CMC Common Mode Choke

EMI Electro Magnetic Interference

ESD Electrostatic Discharge

FS Full Speed – Refers to USB 1.1 Full Speed.

FWH Firmware Hub – A non-volatile memory device used to store the system BIOS.

HS High Speed – Refers to USB 2.0 High Speed.

ICH4-M I/O Controller Hub Fourth Generation – Mobile

LCI LAN Connect Interface

LOM LAN on Motherboard

LPC Low Pin Count

LS Low Speed – Refers to USB 1.0 Low Speed.

MC Modem Codec

GMCH Graphics Memory Controller Hub

PCM Pulse Code Modulation

PLC Platform LAN Connect

FSB Front Side Bus – Processor to GMCH

RTC Real Time Clock

SMBus System Management Bus – A two-wire interface through which various system

components can communicate

®

Intel

852GM Chipset Platform Design Guide 19

Page 20

Introduction

Term Definition

SPD Serial Presence Detect

STD Suspend-To-Disk

STR Suspend-To-Ram

TCO Total Cost of Ownership

TDR Time Domain Reflectometry

UBGA Micro Ball Grid Array

USB Universal Serial Bus

VRM Voltage Regulator Module

1.2. Referenced Documents