Page 1

Intel 8255x 10/100 Mbps Ethernet Controller Family

Open Source Software Developer Manual

January 2003

Revi sion 1.0

Page 2

Information in this document is provided in connection with Intel® products. This specification, the Intel 8255x 10/100 Mbps Ethernet Controller Family

Open Source Software Developer Manual, is provided “as is” with no warranties whatsoever, including any warranty of merchantability,

noninfringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification or sample. Intel products are

not intended for use in medical, life saving, life sustaining applications. Intel may make changes to specifications and product descriptions at any time,

without notice.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

®

The Intel

from published specifications. Current characterized errata are available on request.

The information in this document is furnished for informational use only, is subject to change without notice, and should not be construed as a

commitment by Intel Corporation. It is intended to enable the maintenance of the open source Intel

adapters. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that

may be provided in association with this document. Except as permitted by such license, no part of this document may be reproduced, stored in a

retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © 2003, Intel Corporation.

* Other product and corporate names may be trademarks of other companies and are used only for explanation and to the owners’ ben efit, without

intent to infringe.

82557, 82558, 82559, 82550, and 82551 may contain design defects or errors known as errata which may cause the product to deviate

®

PRO/100 drivers for the Intel® PRO/100 family of

ii

Intel 8255x 10/ 100 M bps Ethern et Co ntroller Family O pen Sourc e Sof tware Devel ope r Manua l

Page 3

Contents

Contents

1 Introduction....................................................................................................................................1

1.1 Scope....................................................................................................................................1

1.2 Document Conve nt ions ..... ........................ ............................... ............................... .............2

1.2.1 Device References .................................................................................................. 2

1.2.2 Numbering...............................................................................................................2

1.2.3 Signal Name Representation.................................... ............ ....... ....... .......... ....... ....2

1.2.4 Memory Alignment Terminology..............................................................................2

2 Adapter and Controller Overview ................................................................................................5

2.1 Adapter Block Diagram.......................................................... .......... ....... .. ....... .......... .. ....... ..5

2.2 Intel Fast Ethernet MAC Features ........................................................................................6

2.2.1 82557 Features............................................................................................... .........6

2.2.2 82558 Features............................................................................................... .........6

2.2.3 82559 , 82550, 82551, and 82562 Fe atures.. ...........................................................7

2.3 Working with the Physical Layer...........................................................................................7

3 Power Management Interface.......................................................................................................9

3.1 Low Power Mode Requirements...........................................................................................9

3.2 Device Power States............................................................................................................9

3.3 Power Management Registers ................................... .............................. ............................9

3.4 Link Operation ....................................................................................................................10

4 PCI Interface.................................................................................................................................11

4.1 PCI Configuration Space ....................................................................................................11

4.1.1 Vendor ID (Offset 0)...............................................................................................12

4.1.2 Device ID (Offset 2) ...............................................................................................12

4.1.3 Command Register (Offset 4) ................................................................................12

4.1.4 Status Register (Offset 6)......................................................................................12

4.1.5 Revision (Offset 8).................................................................................................13

4.1.6 Class Code (Offset 9) ............................................................................................14

4.1.7 Cache Line Size (Offset C).................................................................................... 14

4.1.8 Latency Timer (O ffset D) .............. ........................ .............................. ...................14

4.1.9 Header Type (Offset E).. ........................................................................................14

4.1.10 Built in Self Test ( Of fset F)............ ........................ .............................. ...................15

4.1.11 Subsystem ID (Offse t 2 C ).................................. ............................... .....................16

4.1.12 Subsystem Vendor ID ( Of fse t 2E) .......... .............................. ........................ .........16

4.1.13 Expansion ROM Base Address Register (Offset 30).............................................16

4.1.14 The Capabilit ies Pointer (Offse t 34)............................. ............................... ...........17

4.1.15 Interrup t Lin e (Offset 3C)................................... ............................... .....................17

4.1.16 Interrup t Pin (Offset 3D)............................................ ............................... ..............17

4.1.17 Max_Lat / Min_Gnt ( O ffset 3E)............................. .............................. ...................18

4.1.18 Power Management PCI Configuration Registers.................................................18

4.2 PCI Command Usage.........................................................................................................21

4.2.1 Memory Write and Invalidate.................................................................................22

4.2.2 Read Align .............................................................................................................23

4.2.3 Odd Byte Alignmen t Support .................................................................................23

Intel 8255x 10/100 Mbps Eth ernet Controller Family Open Source Software Developer Manual

iii

Page 4

Contents

5 EEPROM Interface .......................................................................................................................25

6 Host Software Interface ..............................................................................................................27

6.1 The Shared Memory Architecture....................................................................................... 27

6.2 Initializing the LAN Controller.............................................................................................29

6.2.1 LAN Controller Addressing Format........................................................................29

6.3 Controlling the Device.........................................................................................................31

6.3.1 Control / Status Registers (CSR).......... ....................... ............................... ...........31

6.3.2 System Control Block (SCB)..................................................................................33

6.3.3 PORT Interface......................................................................................................42

6.3.4 EEPROM Control Register....................................................................................45

6.3.5 Management Data Interface Control Register.......................................................49

6.3.6 Receive Byte Count Register................................... ....................... .......................51

6.3.7 Early Receive Interrupt..........................................................................................52

6.3.8 Flow Control Register............................................................................................ 53

6.3.9 Powe r Manage men t Driver Register......................................................................54

6.3.10 General Control Register....................................................... .. ....... ....... .......... ......55

6.3.11 General Status Register ........................................................................ ............ ....56

6.4 Shared Memory Structures............... ............................... ............................... ....................57

6.4.1 Action Commands and Operating Modes......... ................ ............................... ......57

6.4.2 Spe cific Action Comm ands....................................................................................59

6.4.3 Receive Operati o n.......... ................. ........................ .............................. ................97

6.5 Command Unit and Receive Unit Operation.....................................................................103

6.5.1 Starting and Comp leting Control Commands......................................................103

6.5.2 Generating and acknowledging interrupts...........................................................103

6.5.3 Command Unit Control......................... ............................... ....................... .........104

6.5.4 Receive Unit Contro l............... ....................... ............................... .......................106

6.5.5 U pdat ing SCB Status...........................................................................................108

6.6 Flow Control......................................................................................................................108

6.6.1 PHY Based Flow Control ..................................................................................... 109

6.6.2 Frame Based Flow Contr o l................... ............................... .............................. ..109

6.6.3 Priority Aware Frame Based Flow Control...........................................................113

6.6.4 Half Duplex Flow Control.....................................................................................114

6.7 Collision Bac k o f f M od if ic a ti on in Sw i tc he d Environm e nts.......... . .. ... .. .. .. . .... .. . .. .... . .. ..........114

7 Physical Layer Interface ...........................................................................................................115

7.1 Management Data Interface (MDI)...................................................................................115

7.2 MDI Register Set.............. ....................... ............................... ........................ ..................116

7.2.1 Control Registe r : Register 0 ............ ............................... ....................... ..............117

7.2.2 Status Register: Register 1......... ........................ ........................ ....................... ..118

7.2.3 Identificat ion Registers: Registers 2 and 3..........................................................118

7.2.4 Auto-Negotia tion Advertisement Register: Regist e r 4........... ................ ..............119

7.2.5 Auto-Negotia tion Link Partner Abi li ty Register: Regist e r 5..................................120

7.2.6 Auto-Negotiation Expansion Register: Register 6 ...................................... ....... ..120

7.3 Intel 82555 Specific Registers.................................................. ................... ................... ..122

7.3.1 Status and Control Register: Register 16......................... ........................ ...........122

7.3.2 Special Control Register: Register 17..................................................................123

7.3.3 C lock Synthes is Test and Control Register: Register 18 . ....................................124

7.3.4 100B ASE- TX Receive False Carrier Counter: Register 19 .................................124

7.3.5 100Base-TX Receive Disconnect Counter: Register 20......................................124

iv

Intel 8255x 10/ 100 M bps Ethern et Co ntroller Family O pen Sourc e Sof tware Devel ope r Manua l

Page 5

Contents

7.3.6 100BASE-TX Receive Error Frame Counter: Register 21...................................1 25

7.3.7 Receive Symbol Err o r Coun ter: Register 22..................................... ...................125

7.3.8 100BASE-TX Receive EOF Error Counter: Register 23......................................125

7.3.9 10BASE-T Receiv e EOF Erro r Counte r : Register 24......... ........................ .........125

7.3.10 10BA SE-T Transmit Jabber Detect Count er: Register 25 ...................................125

7.3.11 Equali zer Control and Status Register: Register 26 ............................................1 26

7.3.12 Special Control Register: Register 27.................................................................. 1 27

7.4 Auto-Negotiation Functionality..........................................................................................128

7.4.1 Description...........................................................................................................128

7.4.2 Paralle l Dete cti o n..... ............................... .............................. ...............................129

7.5 Vendor-Specific PHY Programming ............................................................................ .....130

7.5.1 Intel 82555 TX PHY.......... ............................... ............................... .....................130

7.5.2 82558 and 82559 Embedded PHY Unit. ..............................................................130

8 Programming Recommendatio ns............................................................................................ 1 33

8.1 Adapter Initialization .........................................................................................................133

8.1.1 8255x Initialization ............................................................................................... 1 33

8.1.2 PHY Detection and Initialization .......................................................................... 1 33

8.1.3 NOS Specific Initialization ....................................................................................1 34

8.2 Transmit Pro ce ssing... ............................... ............................... ............................... .........134

8.3 Frame Reception..............................................................................................................134

8.4 Interrup t Pr o ce ssing......... ........................ ...................................... .............................. ..... 1 35

Appendices

A Wake-up Functiona lit y ..............................................................................................................1 37

B 82550 and 82551 Specific Information.....................................................................................153

Figures

1 8 2 557 Network Interface Car d Blo ck Dia gr a m....................... ........................ ........................ ......5

2 Command Register... ..................................................................................................................12

3 Command Register... ..................................................................................................................13

4 Cache Line Size..........................................................................................................................14

5 Base Address Register for Memory Mapping.............................................................................15

6 Base Address Register for I/O Mapping..................................................................................... 15

7 Expansion ROM Base Address Register............................................ ....... ..... ....... .. .......... .. .......17

8 8 2 55x Memo ry Ar ch itecture......................................... .............................. .................................28

9 SCB Sta tus Word.............. ............................... .............................. ............................... ..............34

10 SCB Command Word........................................ .. ..... ..... ....... .. ..... .. ..... ..... ....... .. ..... .. ..... ....... ... ....36

11 Self-Te s t Res ults Format......... ........................ .............................. ........................ .............. .......43

12 EEPROM Control Register.................... ............................... ........................ ..............................45

13 EEPROM Read Timing Diag ra m................................... ........................ ....................... ..............48

14 General Action Command Format.............................................................................................. 58

15 NOP Command Format..............................................................................................................59

16 Individual Address Setup Command Format..............................................................................60

17 Configure Command Format ......................................................... ..... ....... ....... ..... ....... ..... ....... ..61

18 Multicast Setup Command Format .............................................................................................80

19 Transmit Command Format........................................................................................................81

Intel 8255x 10/100 Mbps Eth ernet Controller Family Open Source Software Developer Manual

v

Page 6

Contents

20 Transmit Buffer Descriptor............ ........................ ........................ ....................... .......................83

21 Load Microcode Comman d Forma t............................................................................................88

22 Dump Command Format............................................. ..... ....... .. ..... .. .......... .. ..... .. ..... ....... ..... .. ....89

23 Diagnose Command Format ............................................................................. ....... ....... ....... ....95

24 Simplified Memory Structure ......................................................................................................98

25 Receive Frame Descriptor Format .............................................................................................98

26 Management Frame Structure...................................................................... ....... ............ ....... ..116

27 Command Block Structu r e... ................ ............................... ............................... .......................144

Tables

1 PCI Configuration Space............................................................................................................11

2 Device and Revision ID..............................................................................................................13

3 Base Ad d re ss Regi ste r Su mmary.......... ........................ ....................... ........................ .............16

4 Power Management Capabilities................................................................................................18

5 Power Man ageme n t Control/Sta tu s Register...................................... ............................... ........20

6 Power Consumption / Dissipation Reporting.................................. ....... ....... ..... ....... .. .......... .. ....21

7 Generated PCI Commands ................................................ ....... ..... ....... ....... ....... ....... .......... ......22

8 Reset Commands..................................................................................................... ....... ...........29

9 Device Addressing Formats.......................................................................................................30

10 Alignment Requirements for 8255x Data Structures ........................ .......... ....... .. ....... ............ ....31

11 Control / Status Register ............................................................................................................ 32

12 System Control Blo ck.................................... ........................ .............................. ............... ........34

13 SCB Status Word Bits Descriptions............................................................................................35

14 SCB Command Word Bits Descriptions ..................................................................................... 37

15 SCB General Pointer for the CU Command............................................................................... 39

16 Statistical Counters. .................................................................................................................... 40

17 Port Register Location................................................................................................................42

18 Port Selection Function ..............................................................................................................43

19 Dump Wake-up Data Struc tu re......... ........................ ....................... ........................ ..................44

20 EEPROM Control Register Locations.........................................................................................45

21 EEPROM Control Register Bits Definitions................................................................................45

22 EEPROM Opcode Summary (64-register EEPROM).................................................................46

23 MDI Control Registe r L o c a ti o n .......... ........................ ....................... ........................ ..................49

24 Management Data Pins...................................................... ....... ....... ..... ....... ....... ....... ................49

25 MDI Control Registe r Bi ts...... ........................ ............................... .............................. ......... .......50

26 Receive Byte Count Register Location.......................................................................................51

27 Early Receive Inte rrupt Register Location..... ........................ .............................. .......................52

28 Flow Control Registers Location.................................................................................................53

29 Flow Control Threshold Values ..................................................................................................54

30 Power Management Driver Register Location ............................................................................54

31 Power Management Driver Register ..........................................................................................55

32 General Contr o l Register Location.... ................. ................ ........................ ........................ ........55

33 General Contr o l Register....... ........................ ........................ ....................... ..............................56

34 General Status Re g ister Location........................... ............................... ........................ .............56

35 General Status Re g ister........ ................. ............................... .............................. .......................56

36 Operation Codes.......................... ............................... ............................... ................................57

37 82557 Configuration Byte Map ............................................................................................. ......62

38 82558 Configuration Byte Map ............................................................................................. ......63

39 82559 Configuration Byte Map ............................................................................................. ......64

vi

Intel 8255x 10/ 100 M bps Ethern et Co ntroller Family O pen Sourc e Sof tware Devel ope r Manua l

Page 7

Contents

40 82557 Dual-Po r t FIFO Settings................ .............................. ............................... .....................65

41 82558 and 82559 Dual-Port FIFO Settings ................................... ............ ....... ....... ............ .......66

42 Extended Statistics Functionality................................................................................................70

43 Pre-amble Length .......................................................................................................................73

44 82558 B-step Configuration Block ARP Frame IP Address.......................... ..............................74

45 82558 B-step ARP Fra me IP Ad d ress Mapping............................... ............................... ...........75

46 Full Duplex Functionality.............................................................................................................77

47 Dump Data Bytes (0-79).............................................................................................................90

48 Dump Data Dwords (20-148)...................................................................................................... 93

49 RFD Status Bit Descriptions.... ........................ ....................... ........................ ............................99

50 Actual Count i n Header RFD.................................. ....................... ........................ ...................100

51 CU Control Commands: Actions at Acceptance Time..............................................................105

52 CU Activities Performed at the End of Execution .....................................................................1 05

53 RU Control Commands: Actions at Acceptance Time..............................................................106

54 Flow Control Frame For m at.......... ....................... ............................... ............................... .......110

55 Flow Control Configuration Bits................................................................................................1 13

56 MDI Register Set...................................................................................................................... 1 16

57 82555 MDI Regist er Set .................................. ....................... ........................ ..........................116

58 24-bit OUI Identification Number ..............................................................................................119

59 MDI Identification Registers 2 and 3: PHY ID Encoding...........................................................119

60 LED Switch Control...................................................................................................................1 28

61 Technology Ability Field Bit Assignments................................................................................. 129

62 Technology Priority...................................................................................................................129

63 Fixed Wake-up Configuration Bits............................................................................................141

64 82559 Port Commands........................................................... ..... ....... ....... ..... ....... .. .......... .. .....148

65 Dump Data Structure................................................................................................................149

66 IPCB Structure..........................................................................................................................153

67 IP Activation Bits (Byte 13)........................... ........................ ............................... ............... ......1 53

68 IP Activation Bits (Byte 12)........................... ........................ ............................... ............... ......1 53

69 IPCB Fields...............................................................................................................................154

70 IPCB Structure Checksum Offload........................................................................................... 1 56

71 IPCB Structu re Lar g e Se nd...................... .............................. ............................... ................... 1 60

Intel 8255x 10/100 Mbps Eth ernet Controller Family Open Source Software Developer Manual

vii

Page 8

Contents

Revision History

Date Revision Description

January 2003 1.0 Initial rele ase.

viii

Intel 8255x 10/ 100 M bps Ethern et Co ntroller Family O pen Sourc e Sof tware Devel ope r Manua l

Page 9

Introduction

This document is intended for use as a software tec hnic al reference manual for the Intel® 10/100

Mbps Fast Ethe rnet controll er family, which includes the 825 57, 82558, 82559, 82550, and 82551,

as well as the 82562 Platform LAN Connect device. It also contains inform ation for several PCI

LAN adapters based on these devices: Intel

PRO/100B Wake on LAN (WOL), Intel

PRO/10+.

1.1 Scope

®

EtherExpress™ PRO/100+, Intel® EtherExpress™

®

EtherExpress™ PRO/100B, and Intel® EtherExpress™

1

This manual is intended to be used as a technical reference for software and test engine ers

developing device dr ivers or related softwa re for adapters or systems using the Intel

82558, 82559, 82550, or 82551 Fast Ethernet controllers or the Intel

Connect (PLC) device. It contains reference information about the controllers as well as other

information th at may be required by software developers (such as PHY information, EEPROM

contents, PCI scanning, etc.). Since this document uses many examples and contains sample code

fragments, it is assum ed that the reader has a fundamental und ers tanding of device driver

programming and a working knowledge of both C programming language and x86 assembler

programming language. Familiarity with at least one industry sta ndard network operating system

(NOS) device driver interface (for example, Net work Drive r Interface Specification [NDIS] or

ODI) is also helpful.

®

The Intel

successive order.

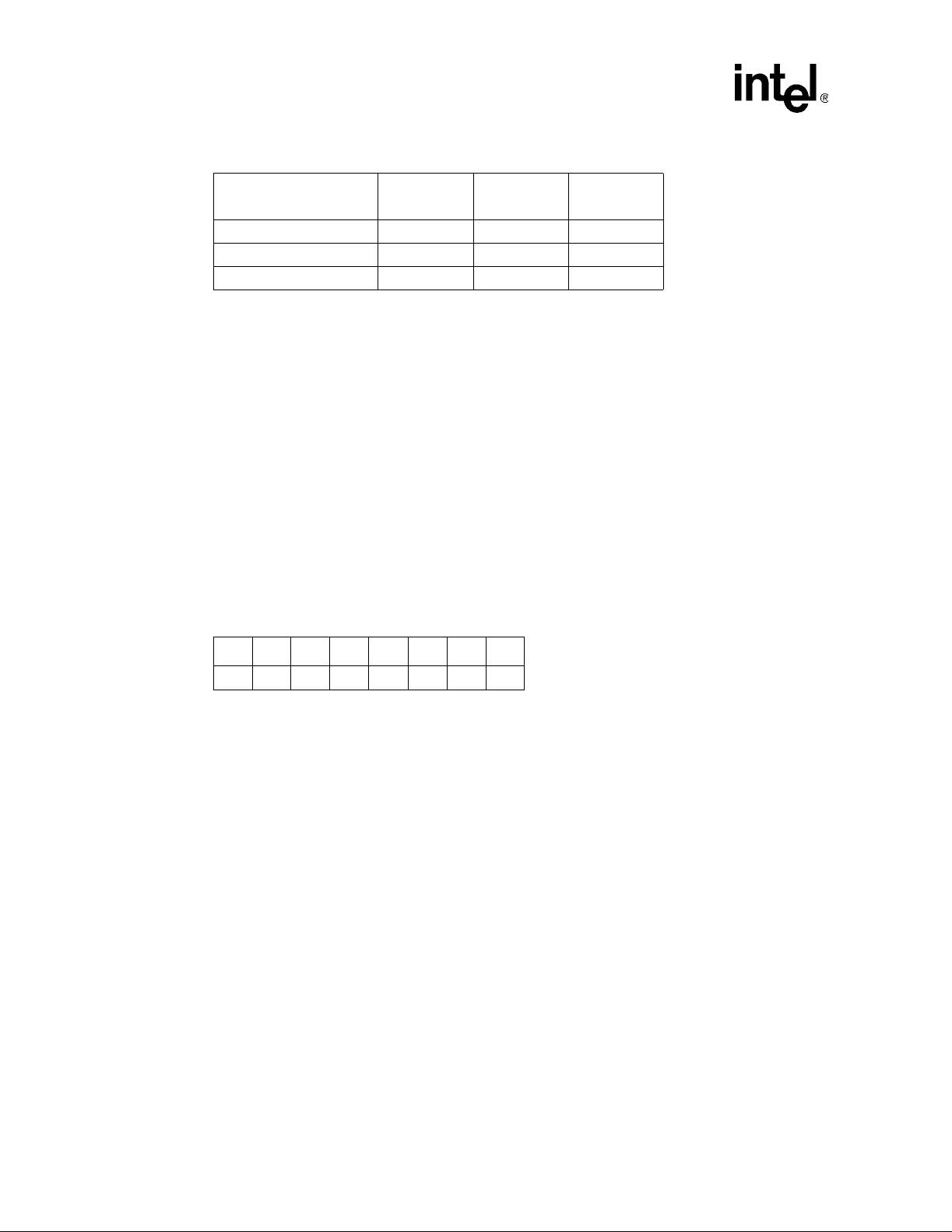

Device Notes

82557 First generation Intel® 10/100 Mbps Fast Ethernet Controller (includes MAC unit only)

82558

82559 Third generation Intel® 10/100 Mbps Fast Ethernet Control ler (inc ludes both a MAC and PHY unit)

82550 Intel® 10/100 Mbps Fast Ethernet Controller (includes both MAC and PHY)

82551 Intel® 10/100 Mbps Fast Ethernet Controller (includes both MAC and PHY)

In general, the Intel family of Fast Ethernet controllers are similar. All family members share the

same core hardware and software interface . The later generation components have a higher

integration and include suppor t for mi scellaneous fea tures (for example, manageability). Since the

differe nt generations of Fast Et hernet controllers are highly simila r, this manu al doc uments the

functionali ty of all de vic es and deta il s the dif f erenc es betwee n the devi ces. It is int ended t o be used

as a tool to maintain and develop software for all devi ces in the Intel family of Fast Ethe rnet

controllers.

10/100 Mbps Fast Ethern et Controller Family includes the following devices in

Second generation Intel® 10/100 Mbps Fast Ether net Controller (include s MAC and an integrated

PHY unit)

®

82562 Platform LAN

®

82557,

Intel 8255x 10/100 Mbps Eth ernet Controller Family Open Source Software Developer Manual

1

Page 10

Introduction

1.2 Document Conventions

1.2.1 Device Refer ences

This do cu m e n t en comp ass e s in f o r mat ion for al l m e m b er s o f th e Intel Fast Eth er n et co ntroll er s:

82551, 82550, 82559, 82558, 82557 and the 82562.

The document convent ion, “8255x,” will be used to refe r to all devices. In addition, there are

specific references to the 82557 throughout this manual that pertains to all 8255x devic es . Devicespecific differences and exceptions will be documented.

1.2.2 Numbering

Decimal, binary, and hexadecimal numbers are used through the manual. They will be de signated

as follows:

• Decimal numbers: Decimal numbers will not be followed by a suffix.

• Binary numbers: Binary numbers (base 2) will be followed by a “b” (for example, 01b).

• Hexadecimal numbers: Hexadecimal numbers (base 16) will be followed with the suffix “h”

(for example, 1Ch). Hexadecimal numbers may also be noted with a pre f ix of “0x” (for

example, 0x1c).

1.2.3 Signal Name Representation

Signals that are active in a low logic state when asserted are followed by the pound sign (#). For

example, FRAME# is asserted low by the master during a transaction. It is asserted low at the start

and duration of a trans action and de-asserted during the final data phase.

Signals that are not followed by a pound sign are ac tive in a high logic state when as serted. For

example, the IDSEL signal is asserted high when the 82559 during PCI read and write transactions.

1.2.4 Memory A lignment Terminology

The 8255x data structures have special memory alignment requirements. T his implies that the

starting phy si cal address of a data structure must be aligned as specified. The following terms are

used for this purpos e:

• Byte alignment: Byte alignment implies that the physical addresses can be odd or even.

Examples: 0FECBD9A1h or 02345ADC6h

• Word ali gnm ent : Word alignment implies that phys ical addresses must be aligned on even

boundaries . In other words, the last nibble of the address may only end in 0h, 2h, 4h, 6h, 8h,

Ah, Ch, or Eh.

Example: 0FECBD9A2h

• Dword alignment: Dword alignment im plies that the physical addres ses may only be aligned

on 4-byte boundarie s. In othe r words, the last nibbl e of the addres s may only end in 0h, 4h, 8h,

or Ch.

Example: 0FECBD9A8h

2

Intel 8255x 10/ 100 M bps Ethern et Co ntroller Family O pen Sourc e Sof tware Devel ope r Manua l

Page 11

Introduction

• Paragraph alignment: Paragraph align me nt implies that the phys ical addresses may only be

aligned on 16-byte boundaries. In other words, the last nibble must be a 0.

Example: 02345ADC0h

Intel 8255x 10/100 Mbps Eth ernet Controller Family Open Source Software Developer Manual

3

Page 12

Introduction

4

Intel 8255x 10/ 100 M bps Ethern et Co ntroller Family O pen Sourc e Sof tware Devel ope r Manua l

Page 13

Adapter and Controller Overview

Adapters based on an Inte l® 8255x device support the ANSI/IEEE 802.3u standard for 100BASETX (100 Mbps operation) and 10BASE-T (10 Mbps operation).

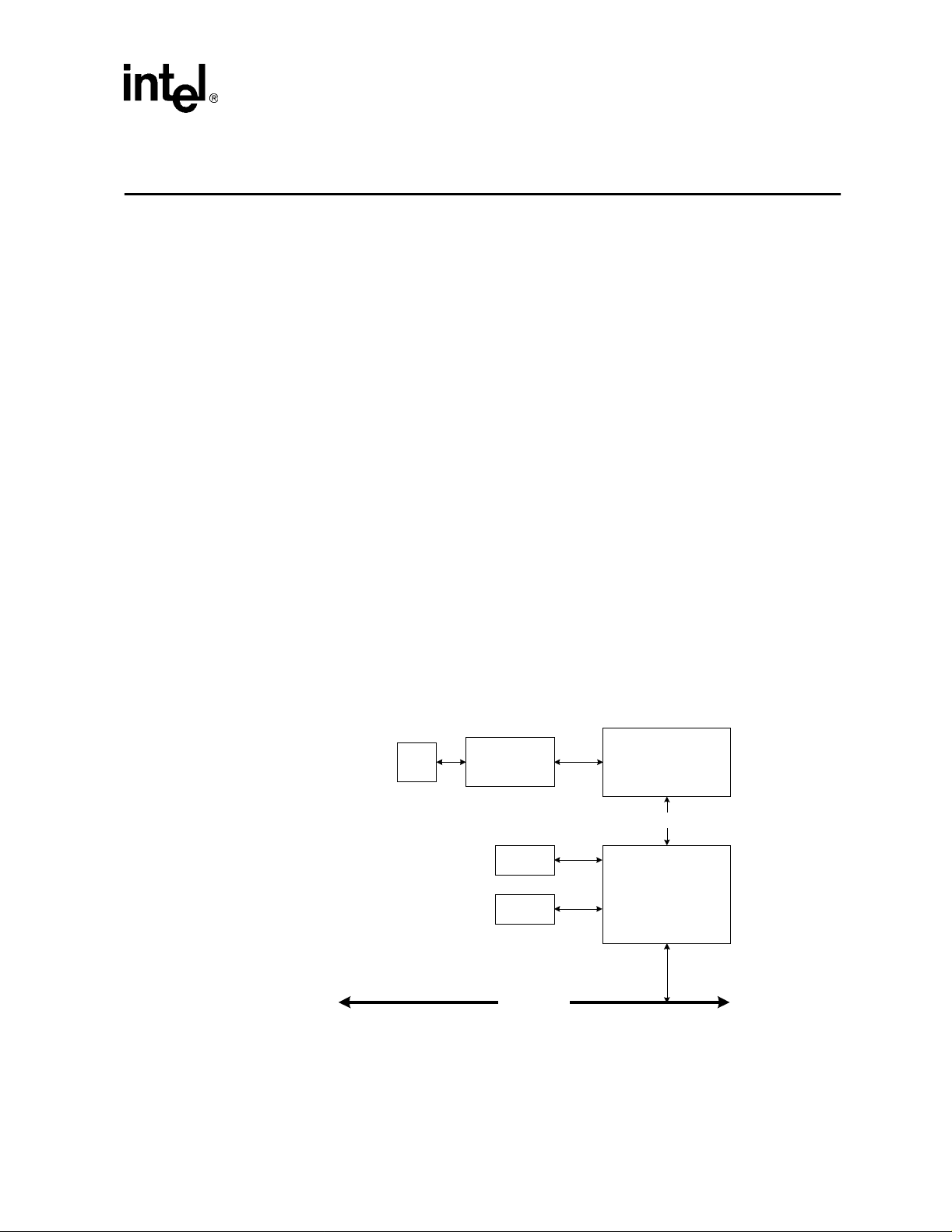

2.1 Adapter Block Diagram

The main components of I ntel Fast Ethernet adapters are:

• A Fast Ethernet Media Acces s Controller (MAC), such as the 8255x, is the core component.

The MAC supports the Fast Ethernet ANSI/IEEE 802.3u standard.

• A Physical Layer (PHY) inte rfac e device is also required. The 82558, 82559, 82550, and

82551 components ha ve an i ntegrated PHY that supports 100BAS E-TX and 10BASE-T.

Adapters based on the 82557 must include an appropriate PHY component for their design.

• A serial EE PROM is required to hold the adapter’s individual E thernet node address and othe r

configuration information including fixed PCI configuration parameters.

The adapters are based on 100BASE-T X spe cifications. 100BAS E-TX is a specific scheme

designed for use over 2 pairs of Category 5 unshiel ded twisted-pair cable . 100BASE-TX defines a

signaling sche m e for 100 Mbps and provides compatibi lity with the existing 10 Mbps IEEE 802.3

10BASE-T signaling standard. Since only 2-wire pairs are used, TX technology allows full duplex

operation at 100 Mbps. The Intel 82555 is one possible TX solution.

2

®

The block diagra m belo w illus trate s an Intel

MAC with a TX or T4 PH Y.

Figure 1. 82557 Network Interface Card Block Diagram

RJ-45

PRO/100B adapter confi gurat ion bas ed on t he 82557

Filter

Module

Optional

Flash

EEPROM

PCI Local Bus

100BASE-T4 or

100BASE-TX PHY

MII

Intel® 82557

Intel 8255x 10/100 Mbps Eth ernet Controller Family Open Source Software Developer Manual

5

Page 14

Adapter and Controller Overview

2.2 Intel Fast Ethernet MAC Features

2.2.1 82557 Features

• Glueless 32-bit, zero wait state PCI bus master interface compliant with PCI Specification,

Revision 2.1.

• 10 and 100 Mbps support in compliance with IEEE 802.3 10BASE-T and 802.3u 100BASE-

TX.

• Fast back-to-back transmit interf rame spacing (IFS) of 960 ns in 100 Mbps networks and 9. 6

µs in 10 Mbps networks.

• On-chip Control/Status Register (CSR) incorporating the System Control Block (SCB).

• Simple and flexible packet support with Dynamic transmit chaining.

• Packed Transmit Buf f er Descriptors (TBDs).

• Early transmit complete indication.

• Simple receive pack et support al lows ear ly receive in terrupt support for concurre nt processing

(in simplified mode).

• IEEE Media Independent Interfac e (MII) compliant PHY interface other MII compliant PHYs.

• Full and half duplex transmit and receive capability.

• Separate on-c hip receive and transmit FI F Os.

• On-chip network management counters.

• EEPROM support.

• Optional Flash ROM support (256 Kbytes or 1 Mbyte).

2.2.2 82558 Features

For the most part, the 82558 is a superset of the 82557. In addi tion to incorporat ing the features of

the 82557, it al so i ncludes the following :

• Backward compatibl e to 82557 software.

• Integrated 100BASE-TX PHY.

• IEEE 802.3u auto-ne gotiation support in 10BASE-T, 100BASE-TX, full dupl ex a nd f ull

duplex flow control configurations.

• Auto-polarity correction for 10BASE-T.

• Optimized PCI interface with support for the memory write and invalida te PCI command.

• Automatic read of EEPROM (programmable I D).

• IEEE 802.3x flow control capable.

• PHY based flow control supp ort when the internal 100BASE-TX PHY is used.

• Advanced Configuration and Power Interface (ACPI) Specification and PCI Power

Management Specification compliant.

• Remote power up support (for Magic Packet*).

6

Intel 8255x 10/ 100 M bps Ethern et Co ntroller Family O pen Sourc e Sof tware Devel ope r Manua l

Page 15

Adapter and Controller Overview

• Optional Flash support up to 64 Kbytes. (The 82557 is cap able of larger Flash size support.)

2.2.3 82559, 82550, 82551, and 82562 Fea tures

The 82559, 82550, and 82551 devices are supersets of the 82557 and 82558. However , the 82559

does not support PHY based flow control as the 82558 did. The new 82559 features are:

• Backward compatible to the 82557 and 82558 software.

• Low power 3.3 V device:

• Clockrun protocol support.

• System Management Bus (SMB) s upport.

• Wired for Management support (WfM).

• Expanded Wake on LAN capabiliti es .

• 128 Kbytes Flash size support. (The 82558 only supp orted a 64 Kbyte Flash.)

• Thin ball grid array (BGA) 15 x 15 mm package.

2.2.3.1 82559ER Features

The 82559ER is a member of the 82559 Fast Eth ernet controllers. It is a subset of the 82559.

However, the 82559ER does not support:

• SMB.

• Wake on Magic Packet*.

2.3 Working with the Physical Layer

The 82557 contains an IEEE MII compl iant interface to a MII complian t P HY, allowing

connections to 10/100 Mbps networks. Software communicates to a MII compl iant device thro ugh

the 82557 by using the its Management Data Interface (MDI) port.

The 82558, 82559, 82550 and 82551 contain an embedded PHY module. Although the PHY is

internal for these devices, software still communicates to the PHY unit through the MDI port.

For 10/100 Mbps connections, t he 82557 can be used in conjunction with the Intel

Mbps only connections, the 82557 can be interfaced to the Intel

maintaining software compatibil ity to 100 Mbps solutions. The 82558 and later devices do not

have a 10 Mbps only interface as the 82557. However , it is possible to interface these devices with

a 10 Mbps only MII device.

®

®

82503 serial interface, while

82555. For 10

Intel 8255x 10/100 Mbps Eth ernet Controller Family Open Source Software Developer Manual

7

Page 16

Adapter and Controller Overview

8

Intel 8255x 10/ 100 M bps Ethern et Co ntroller Family O pen Sourc e Sof tware Devel ope r Manua l

Page 17

Power Management Interface

The 82557 has no power management support. The 82558 added support for th e Advanced

Configuration and Power Interface (ACPI) Specification and limited support for Wake on LAN

(WOL). The 82558 B-s tep upgraded and expanded the WOL capability, while the 82559 expanded

and simplified the WOL functionality even more.

3.1 Low Power Mode Requirements

The 82558, 82559, 825 50, a nd 82551 adhere to the emerging power management sta ndards as

defined in:

• PCI Bus Power Management Interfa ce Specificatio n, Revision 1.0.

• Advanced Configura tion and Power Interface Specification (ACPI), Rev 1.0; Dec ember 22,

1996.

• Device Class Power Managem ent Reference Specification - Network Device Class, Revision

1.0.

These three specifications define how a PCI network device can be controlled in an OS Directed

Power Management (OSPM) environment. These devices all adhere to these specific ations.

Additionally, they support bus isolation within the chip and Wake on LAN (WOL) capabilities.

3

3.2 Device Power States

Currently, operating systems only support the D0 and D3 power states. However, starting with the

82558, the Intel Fast Ethernet controller fami ly supports all four power states as defined in the PCI

Power Management Specification. These power states are named D0, D1, D2 and D3. D0 is the

maximum powered state, and D3, the minimum powered state.

3.3 Power Management Re gis ters

The 82558, 82559, 82550, and 82551 support power manage ment registers:

• Power Management Capability Pointer (Cap_Ptr)

• Power Management Capabilities (PMC)

• Power Management Control/Status Register (PMCSR)

• Power Management Driver Register (PMDR)

The first three registers are located in PCI configuration space and are defined in the PCI Power

Management Spec ification. It is part of the device CSR, which is mapped into sys tem memory and

I/O space.

Intel 8255x 10/100 Mbps Eth ernet Controller Family Open Source Software Developer Manual

9

Page 18

Power Management Interface

3.4 Link Operation

In the D0 state, the device maintains an active link. The 82558 B-step (refer to Table 2, “Device

and Revisi on ID” on page 13) and later devices also maintain an active link in the D3 state if PME

is enabled and the device has power. This implies:

• 10BASE-T Mode: The device expects a normal clock input on the X1 a nd X2 pins. It expects

to receive norma l reception on the Rece iv e Differ ential Pos itive and Receive Differential

Negative signals (RDP/RDN pair). The device will not transmit on the Transmit Dif f erential

Positive and Tra n smit Diffe r ential Negative signal s (TDP/TDN pair).

• 100BASE-TX Mod e: The device expects a normal cloc k input on the X1 and X2 pins and to

receive normal reception on the RDP/RDN pair. It transmits a continuous idle st ream on the

TDP/TDN pair, as required by the 100BASE -TX s tandard. The 82558 does not transmit

frames on the link.

• Auto-Negotiation: If the link f ails whil e th e device is in the D1 state, it performs the nor mal

auto-negoti ation p roto col in or der t o re-est abl ish t he link. F or the 8 2558 B -step , if the link fa il s

in the D3 state and PME is enabl ed and t he devi ce has power , th e devic e will attempt to use the

normal auto-negotiation protocol in order to re-establish the link. If the link fails on the 82559

in the D3 state and PME is enabled and the device has power, the 82559 will go into a deep

power down state, rather than trying to re-establish the link with the auto-ne gotiation prot ocol.

During the D3 power state, the 82558 A-step does not mainta in an active link. The 82558 B-st ep

and later generation devices do not maintain a link in D3 if PME is disabled or if the device does

not have power.

10

Intel 8255x 10/ 100 M bps Ethern et Co ntroller Family O pen Sourc e Sof tware Devel ope r Manua l

Page 19

PCI Interface

4.1 PCI Configuration Space

One of the most important functions for enabling superior configurability and ease of use is the

ability to r elocate PCI devices in the address spaces. By def ault PCI devices support “Plug and

Play.” When the system is powered on, dev ice independent software (usually the system BIOS)

determines present devices, builds an address map, and assigns non-conflicting resources to those

devices. The device independent software accomplishes this configuration task by writing to the

PCI configuration s pace of each individual PCI dev ice.

The 8255x supports 16 Dwords of Type 0 Configuration Space Header, as defined in the PCI

Specification, Revision 2.1. The 82259 and 82558 also support a small section in the device

specific configuration space. The configuration space is depicted below. The registers that are not

identi cal betw ee n the de vi ce s ar e s h ad e d.

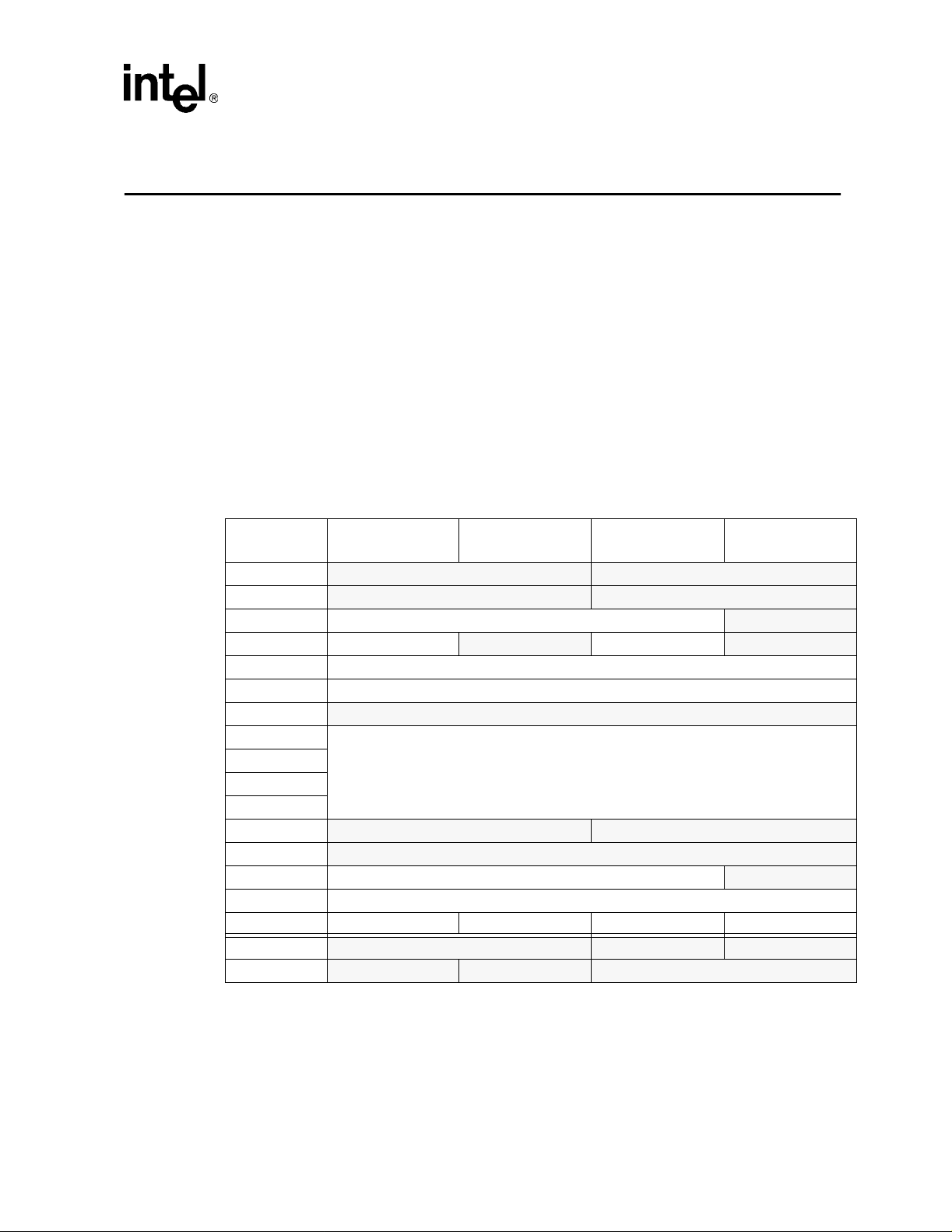

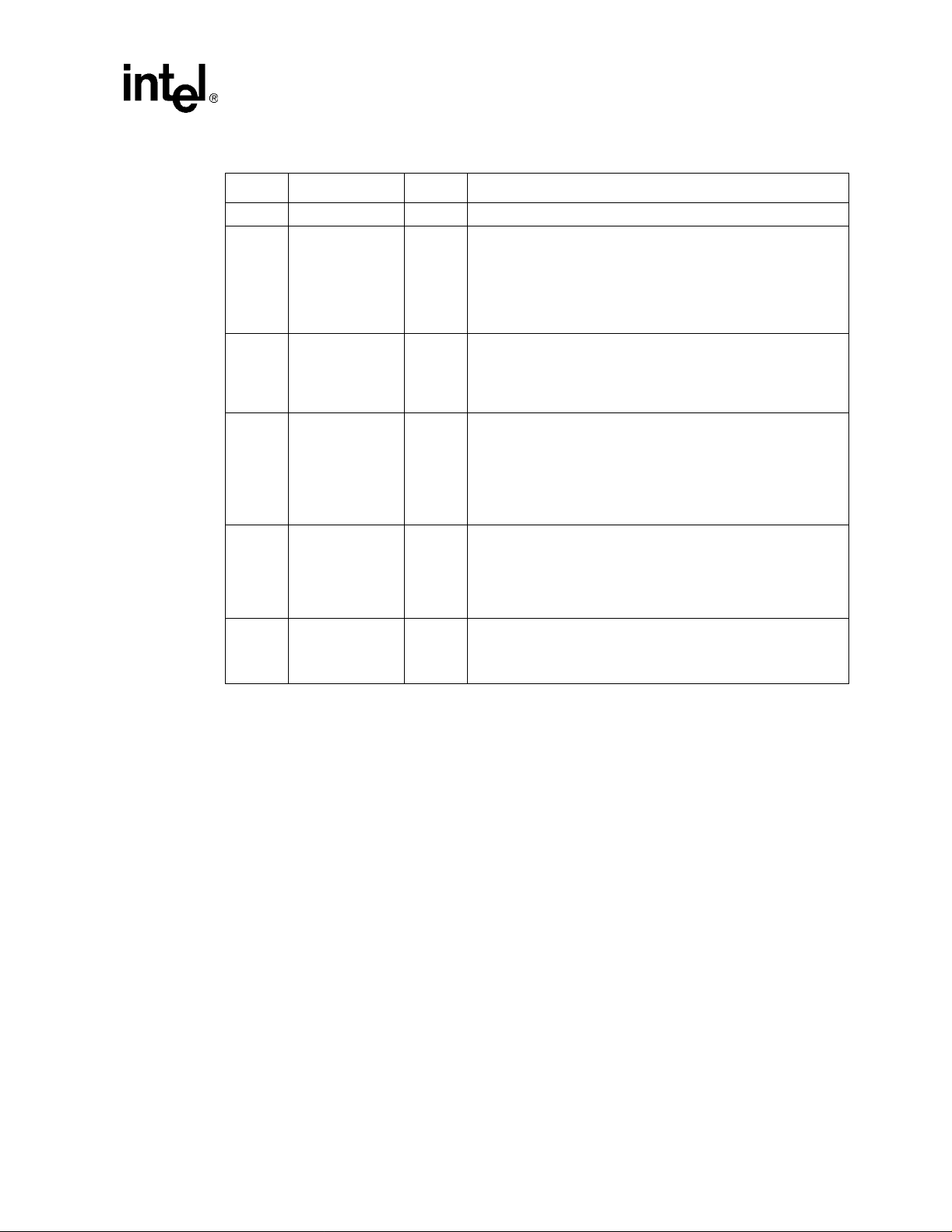

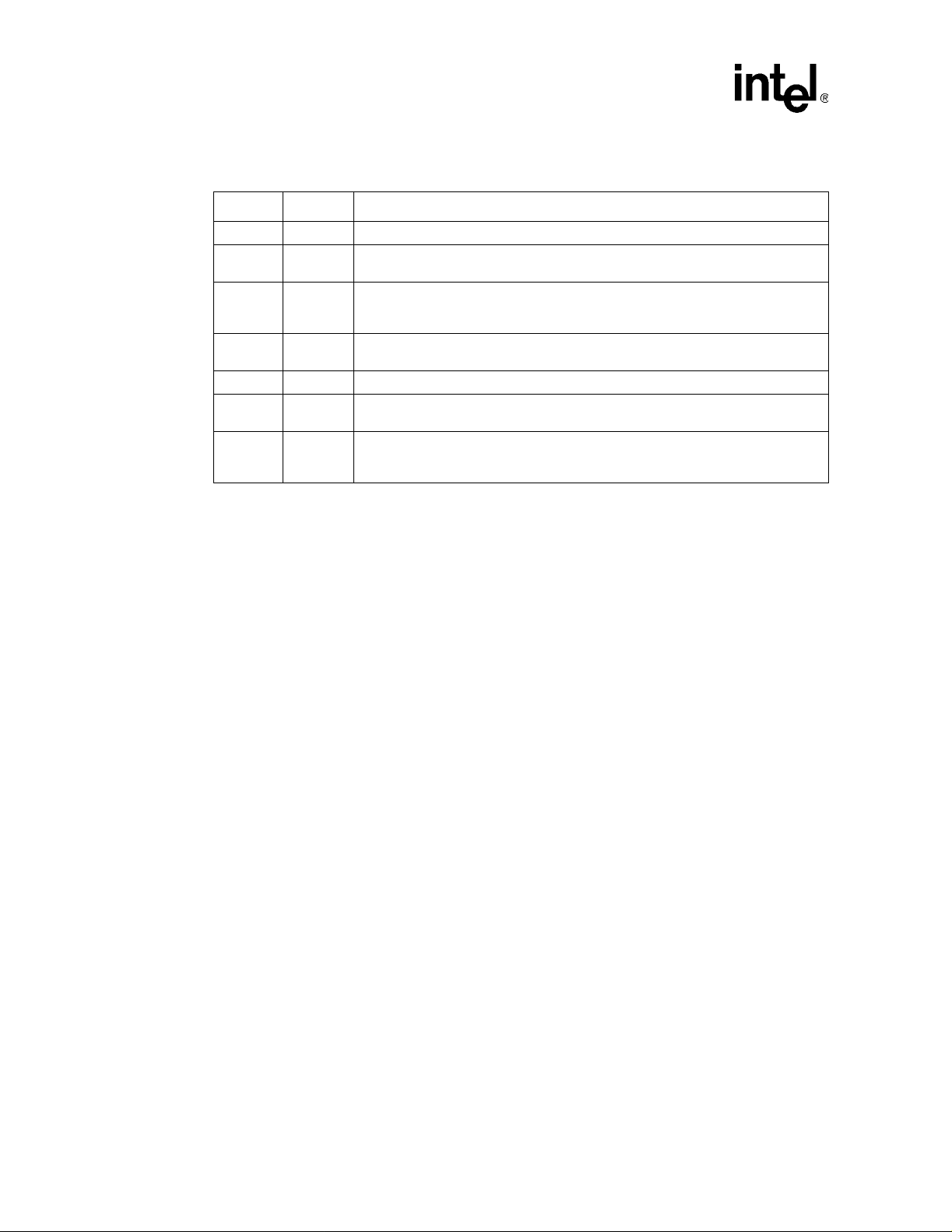

Table 1. PCI Configuration Space

4

Byte Offset

(hexadecimal)

0

4

8 Class Code (200000h)

CBIST

10 CSR Memory Mapped Base Address Register

14 CSR I/O Mapped Base Address Regist er

18

1C

20

24

28

2C

30

34 Reserved

38 Reserved

3C Max_Lat ency (FFh) Min_Grant (FF h) Interrupt Pin (01h) Interr upt Line

DC

E0

Byte 3 Byte 2 Byte 1 Byte 0

Device ID Vendor ID

Status Register Command Register

Header Ty pe Latenc y Timer C a che Line Siz e

Flash Memory Mapped Base Address Regis ter

Reserved

Subsystem ID Subsystem Vendor ID

Expansion ROM Base Address Register

Power Management Capabilities Next Item Pointer Capability ID

Reserved Data Power Management CSR

Revision ID

Cap_Ptr

Intel 8255x 10/100 Mbps Eth ernet Controller Family Open Source Software Developer Manual

11

Page 20

PCI In terfac e

4.1.1 Vendor ID (Offset 0)

This field ide ntifies the device manufacturer. For the 82557 B-ste p this field equals 8086h. For the

82557 C-Ste p, 82558, and 82559, this fie ld i s automa tical ly loade d from the EEPROM at power on

or upon the asserti on of PCI reset. If the EEPROM is not present or inva lid, this value defaults to

8086h.

4.1.2 Device ID (Offset 2)

This field uniquely identifies the devi ce . For the 82557 B-step this field i s 1229h. For the 82557 CStep, 82558, and 82559, this field is automatically loaded from the EEPROM at power on or upon

the asse rtion of PCI reset. If the EEPROM is not present or invalid, this value defaults to 12 29h for

the 82558 and 82559. The 82559ER does not load the Device ID from the EEPROM and will

always equal 1209h.

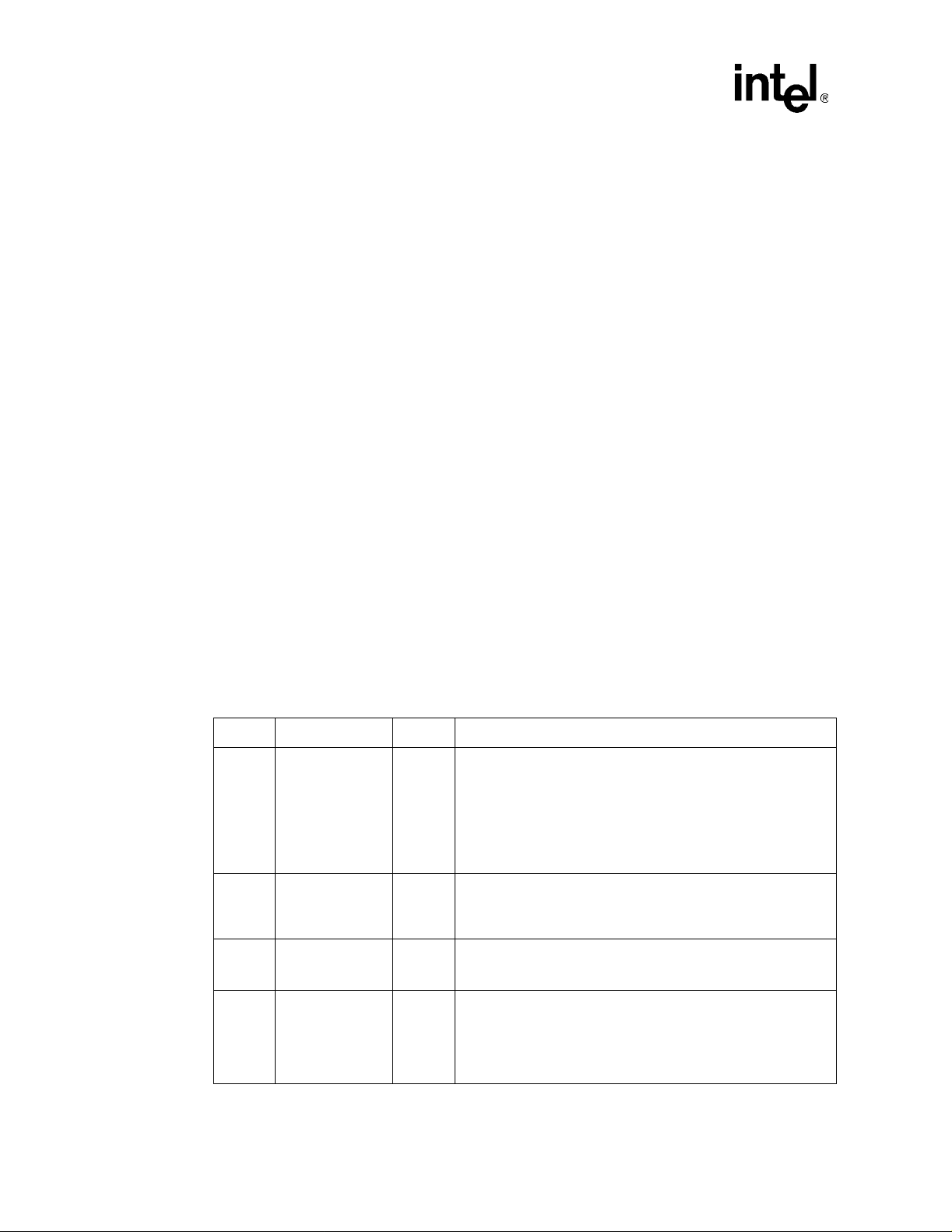

4.1.3 Command Register (Offset 4)

The Command Register provides control over the device’s ability to generate and respond to CPU

cycles. Its layout is shown below. The shaded bits are not used and are hard-wired to 0.

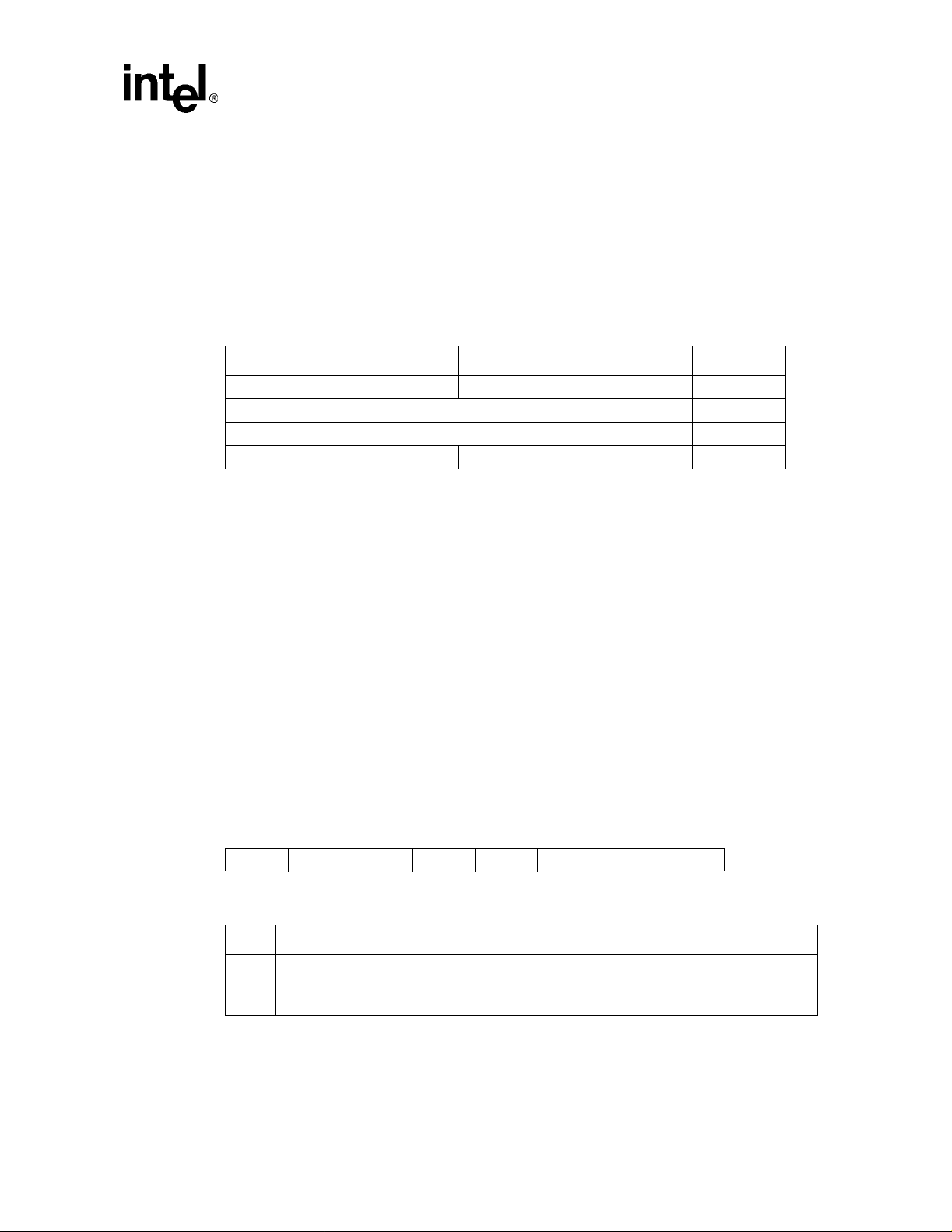

Figure 2. Comm a n d R egi s te r

15 10 9 0

Reserved Command Bits

Bits

15:10 0 Reserved.

9 0 Fast back-to-back enable.

8 x SERR# enable.

7 0 Wait cycle enable.

6 x Parity error response

5 0 Palette snoop enable.

4x

3 0 Special cycle monitoring.

2 x Ma stering enable.

1 x Memory access enable.

0 x I/O acce s s en ab le .

Initial

Value

Memory write and invalidate (MWI) enable.

NOTE: More information regarding the MWI command is loca ted in Section 4.2.1,

Description

“Memory Writ e and Invalidate”.

4.1.4 Status Register (Offset 6)

The Status Register is used to record status information for PCI bus related events. Its layout is

shown below. The shaded bits are not used and are hard-wired to 0.

12

Intel 8255x 10/ 100 M bps Ethern et Co ntroller Family O pen Sourc e Sof tware Devel ope r Manua l

Page 21

Figure 3. Command Registe r

15 43 0

Status Bits Reserved

PCI Interface

Bits

15 x Detected parity error.

14 x Signaled system error.

13 x Received master abort.

12 x Recei ved targ et abort.

11 0 Signaled target abort.

10:9 01 DEVSEL timing (indicates minimum timing).

8 x Data parity reported.

7 1 Fast ba ck-to-back capabl e.

6 0 UDF supported.

5 0 66 MHz capable.

4

3:0 0 Reserved.

Initial

Value

1 (82559

and

82558)

0

(82557)

Capabilities list. This bit indicates whether the device implements a list of new capabilities

such as PCI Power Management. If it is set, the Cap_Ptr register in the PCI Configuration

Space points to the location of the first item in the Capabilities List.

NOTE: This bi t is set to 1 f or the 82559 an d 82558 if it i s not disabled by the EE PROM. I t

is always equal to 0 for the 82557.

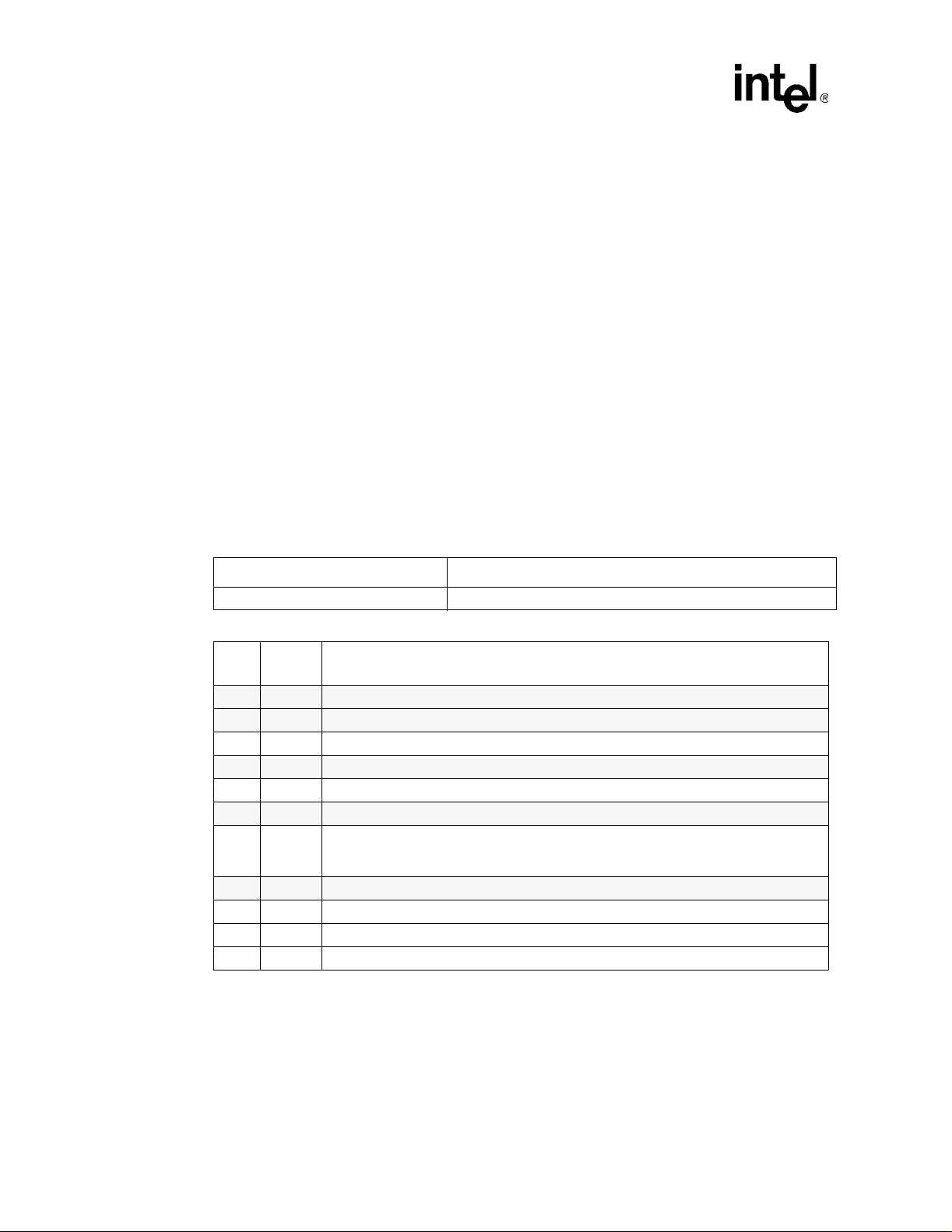

4.1.5 Revision (Offset 8)

This register specifies a device specific revision identifier. For the 82557 C-Step, 82558, and

82559, this f ield m ay be a utoma tical ly loa ded f rom the EEPROM at power on or u pon th e asserti on

of a PCI reset. The default revision register values for the various devices are:

Description

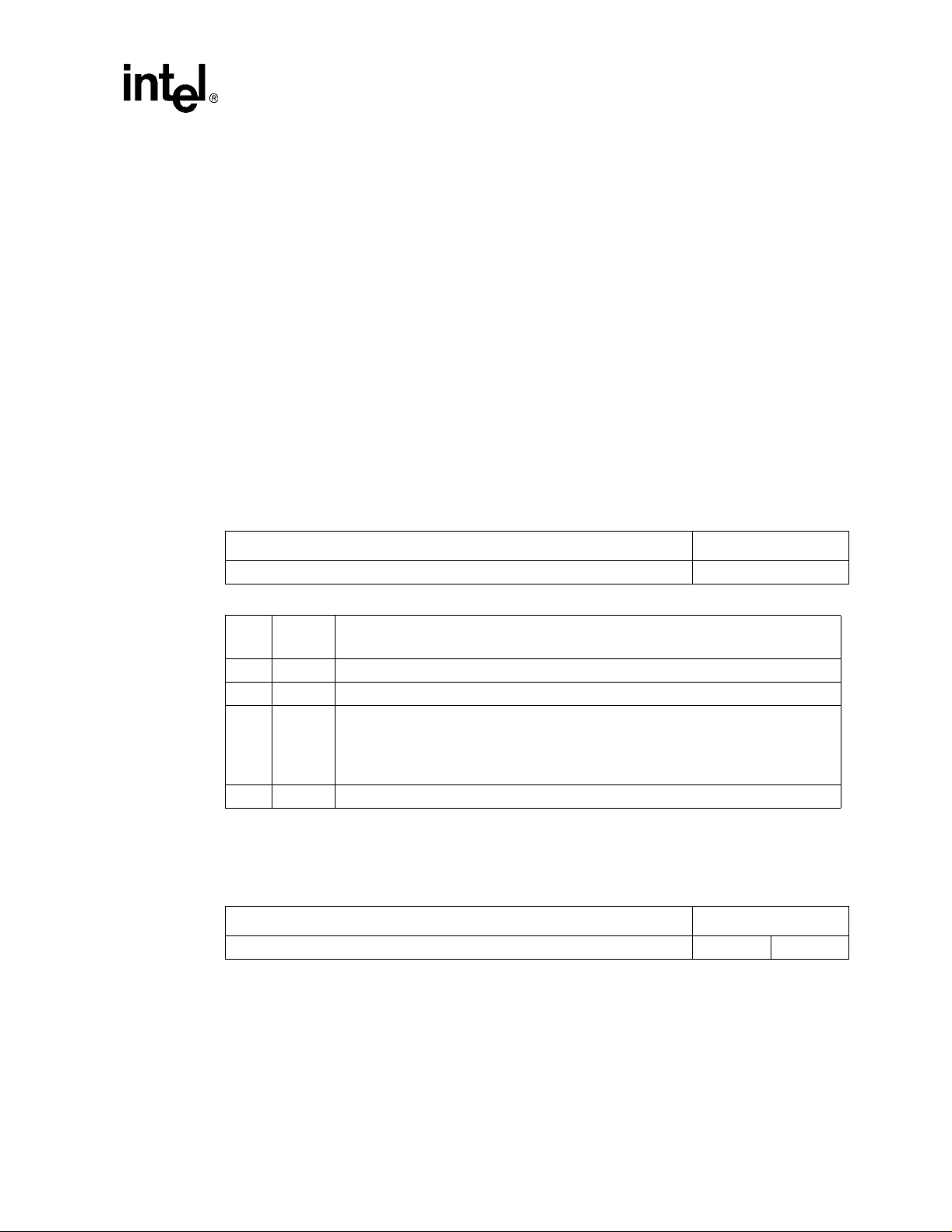

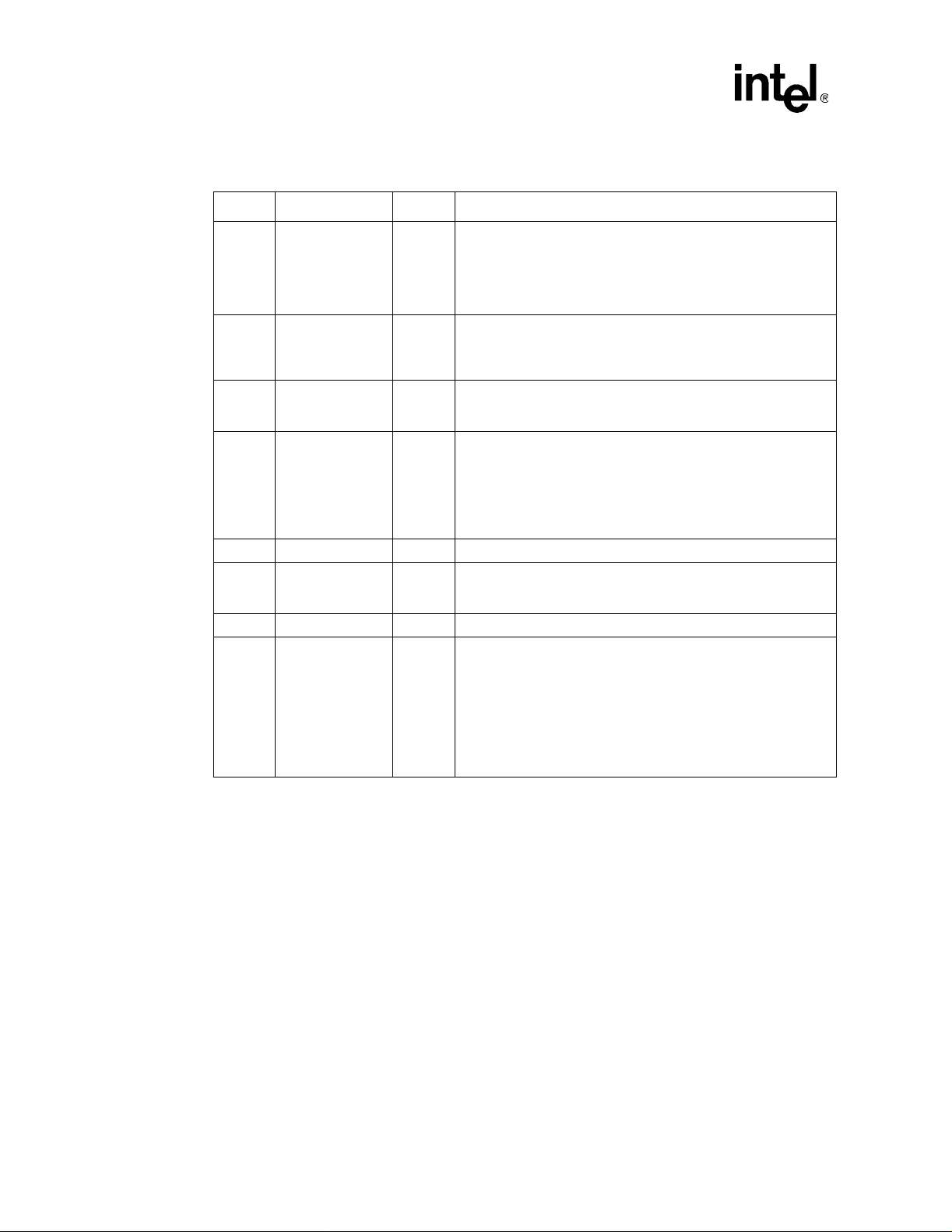

Table 2. Device and Revision ID

Device Revision ID

82557 A-Step 01h 2.0 Yes

82557 B-Step 02h 2.0 Yes

82557 C-Step 03h 2.1 No

82558 A-Step 04h 2.1 Yes

82558 B-Step 05h 2.1 Yes

82559 A-Step 06h 2.1 No

82559 B-Step 07h 2.1 No

82559 C-Step 08h 2.2 Yes

PCI Revision

Supported

Intel 8255x 10/100 Mbps Eth ernet Controller Family Open Source Software Developer Manual

Intel Driver

Supported

13

Page 22

PCI In terfac e

Table 2. Device and Revision ID

Device Revision ID

82559ER A-Step 09h 2.2 Yes

82550 0Ch, 0Dh, 0Eh 2.2 Yes

82551 0Fh, 10h 2.2 Yes

4.1.6 Class Code (Offset 9)

The class code, 020000h, identifies the device as an Ethernet adapter.

4.1.7 Cache Line Size (Offset C)

This regis ter specifie s the system cache line size in units of 32-bit words and ca n be read or written

to. The system BIOS or OS should initialize this register at power on or after a PCI reset .

The 82557 does no t suppor t Me mory W rit e and In valida te (MWI) and the refore re turns 0 when thi s

register is re ad. The 82258 and 82559 support the MW I command and must support this register.

The 82558 and 82559 can only support cache line sizes of 8 and 16 Dwords. Any value other than

8 or 16 written to the register is ignored, and the dev ice does not use the MWI command. If a value

other than 8 or 16 is written into the Cache Line Size (CLS) register, the device returns all zero es

when th e CL S re gi ster is rea d.

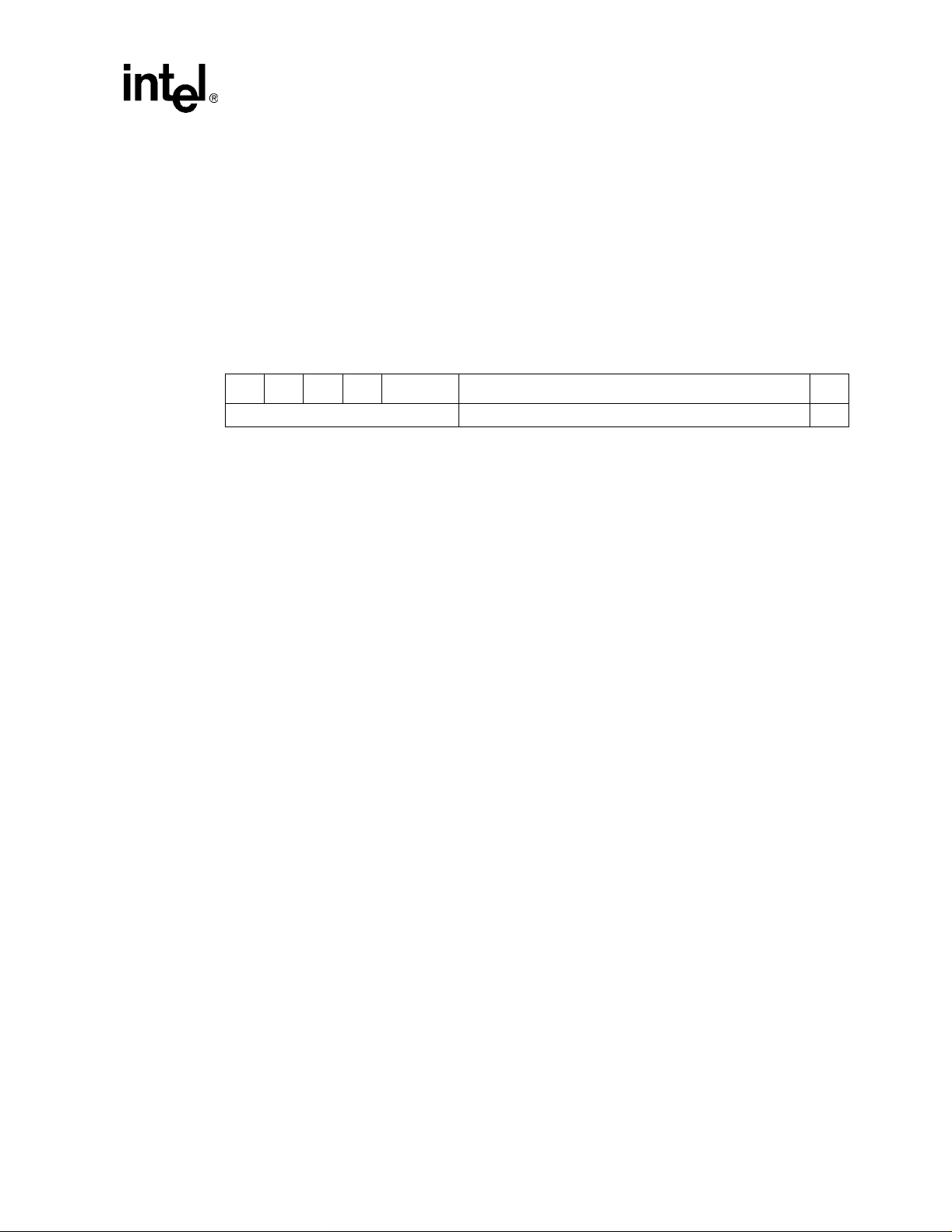

Figure 4. Cache Line Size

PCI Revision

Supported

Intel Driver

Supported

76543210

0 0 0 RWRW0 0 0

Bit 3 is set to 1 only if t he value 00001000b (8) is written to this register. Bit 4 is set to 1 only if the

value 00010000b (16) is written to this register. All other bits are read only and will return 0 on

read.

4.1.8 Latency Timer (Offset D)

This register sp ecifies, in units of PCI bus clocks, the minimum time that a bus master can retain

ownership of the bus. This value is set by the PCI bus arbitrator based on the values in the

maximum latenc y ( Max_Lat) and Maximum Grant (Max_Gnt) regis ters.

4.1.9 Header Type (Offset E)

This byte fi el d ident if i es the lay o ut of the seco n d part of the p red efi n ed con figu r at ion spa c e head er

and if the device is a multi-function compone nt. The 82557 and 82558 are both single function

devices and have this register hard-coded to 00h. For the 82559, the value of this register is

determined by a bit in the EEPROM. This register should read 00h for a standard Ethernet adapter,

00h.

14

Intel 8255x 10/ 100 M bps Ethern et Co ntroller Family O pen Sourc e Sof tware Devel ope r Manua l

Page 23

4.1.10 Built in Self Test (Offset F)

This optional register is used for control and status of Built in Self Test (BIST). This register is

hard-wired to 0 indicating that the dev ices do not support BIST.

Three base address registers are supported by the 8255x:

• CSR Memory Mapped Base Address Register (BAR 0 at offset 10)

• CSR I/O Mapped Base Address Register (BAR 1 at offset 14)

• Flash Memory Mapped Base Address Register (BAR 2 at offset 18)

Two request memory mapped resources, and the third, I/O mapping. Each register is 32 bits wide.

The least significant bit in each base add ress register determines w hether it represen ts an I/O or

memory space. The figures below illustrate layouts for I/O and memory mapped base address

registers. After determining which resources wil l be used, the power-up software maps the I/O and

memory controller s into available locations and continues wit h the power up. To perform the

mapping in a device independent manner, the base registers are placed in the pr edefined header

portion of confi guration space. Device drivers access th is configuration space to determine the

mapping of a particul ar device.

Figure 5. Base Address Register for Memory Mapp ing

PCI Interface

32 43 0

Base Address Configuration Bits

Bits

31:4 x Base Address.

3 x Pre-fetchable.

2:1 x

0 0 Memory space indicator.

NOTE: Bit 0 in all base registers is read-only and used to determine whether the register maps into memory or

Initial

Value

00 = Locate address anywher e in 32-bi t address s pace.

01 = Locate address below 1 MByte.

10 = Locate address anywher e in 64-bi t address s pace.

11 = Reserved.

I/O sp ace. Base registers mapping to memory space must return a 0 in bit 0, and base registers

mappin g to I/O space, a 1.

Figure 6. Base Address Register for I/O Mapping

32 21 0

Base Address Reserved 1

NOTE: Base registers that map into I/O space are always 32 bits with bit 0 hard wired to a 1, bit 1 is reserved

and must return 0 on reads, and the other bits are used to map the device into I /O space.

Description

The number of upper bits that a device actually implements depends on how much of the address

space the device responds to. A device that wants a 1 Mbyte memory address space would set the

most significant 12 bits of the base address register to be configu r able, setting the other bits to 0.

Intel 8255x 10/100 Mbps Eth ernet Controller Family Open Source Software Developer Manual

15

Page 24

PCI In terfac e

The 8255x requires one BAR for I/O mapping and one BAR for memory mapping of these

registers anywhere within the 32-bi t memory address space. The driver determines which BAR (I/

O or Memory) is used to access the Control/Sta tus Registers. However, both are always requested

by the device.

One BAR is also require d to map the ac ces ses to a n option al Fl ash mem ory. The 82557 implements

this registe r regardless of the presence or absence of a Flash chip on the adapte r. The 82558 and

82559 only imple me nt this register if a bit is set in the EEPROM. The size of the spa ce requested

by this register is 1Mbyte, and it is always ma pped anywhere in the 32-bit memory address space.

Note: Although the 82558 only supports up to 64 Kbytes of Flash memo ry and the 82559 only supports

128 Kbytes of Flash memory, 1 Mbyte of address space is still requested. Software should not

access Flash addresses above 64 Kbytes for the 82558 or 128 Kbyt es for the 82559 because Flash

accesse s abo v e the limit s ar e al iased to lo w e r add r es s es. Table 3 describes the implementation of

the base address register s.

Table 3. Base Address Register Summary

Register

Location

10h

14h I/O space for the device Control/Status Registers. The size of this space is 32 bytes.

18h

1Ch - 27h Reserved.

Description

Memory space for the device Control/Status Registers. The size of this space is 4 Kbytes

and it is mapped anyw here in the 32-bi t memory add ress space. It is marked as prefetchable. Software should not assume that this memo ry will be granted below 1 Mby te.

Memory space for FLASH buffer accesses. The size of this space is 1Mbyte. It is mapped

anywhere in the 32-bit address space and is not pre-f etchable.

4.1.11 Subsystem ID (Offset 2C)

This register uniquely identifies the add-in adapter or subs ys tem where the PCI device resides. It

provides a mechanism to distinguis h different adapters that use the same PCI controller. For the

82557 B-step thi s field equals 0000h. For the 825 57 C-Step and later devices, this field is lo aded

from the EEPROM at power on or upo n the ass ertio n of PCI re set . If the EE PROM is not prese nt or

invalid, this value defaults to 0000h.

4.1.12 Subsystem Vendor ID (Offset 2E)

This register uniquely identifies the add-in adapter or subs ys tem where the PCI device resides. It

provides a mechanism to distinguis h the vendor of a adapter from the vend or of the PCI controller

used on the adapter. For th e 82557 B-step this field is 0000h. For the 82557 C-Step and later

devices, this field is automatically loaded from the EEPROM at power on or upon the as sertion of

PCI reset. If the EEPROM is not present or invalid, this value defaults to 0000h.

4.1.13 Expansion ROM Base Address Register (Offset 30)

The 8255x provides an interface to a local Flash device (or EEPROM) which may be used as an

expansion ROM. A 32-bit E xpansion ROM Base Address Regi st er at offset 30h in the PCI

Configuration Space is defined to handle the address and size information for boot-time access to

16

Intel 8255x 10/ 100 M bps Ethern et Co ntroller Family O pen Sourc e Sof tware Devel ope r Manua l

Page 25

the Flash. The 82557 implements this register regardless of the prese nce or abs ence of a Flash

component on the adapter. For the 82558 and later Fast Etherne t controllers, this register is only

implemen te d if a bit is set in the EEP R O M .

The register func tions exactly lik e a 32-bi t bas e address register exc ept that the encoding ( and

usage) of the bottom bits is different. The upper 21 bits correspon d to the upper 21 bits of the

expansion ROM base address. The 8255x only allow an expansion ROM to be mapped on a 1

Mbyte boundary. Therefore, only the most significant 12 bits are configurable to indicate the 1

Mbyte size requ irement ( as with the Fla sh Memory Ma pped BAR, the 825 58 an d 82559 request a 1

Mbyte mapping even though the maximum Flash size allowed with those devices is 65 Kb ytes).

The format of the register is sh own in the figure below .

Figure 7. Expansion ROM Base Address Register

32 20 19 1 0

Read / Write Reserved (all bits set to 0) En

Bit 0 in the register is used to control whether or not the device accepts accesses to its expansion

ROM. When this bit is reset, the devices expansion ROM address space is disabled. This bit is

programmed at initialization time by the system BIOS. The Memory Space bit in the Command

register has precedence over the Expansion ROM Base Address Enable bit. A device responds to

accesses to its expansion ROM only if both the Memory Space bit and the Expansion ROM Base

Address Enable bit are set to 1 (it is reset to 0 upon PCI reset).

PCI Interface

4.1.14 The Capabilities Pointer (Offset 34)

This an 8-bit field that provides an offse t in the device PCI Configuration S pace for the loca tion of

the first item in the Capabilities Linked List. The Power Management Interface documentation

specifies this linked list to provide access to all appropriate device information in the

implementation of the ACPI.

For the 82257, this register is hard-wire d to 0 si nce it does not support power management.

For the 82558 this r egis ter is set to DCh if powe r mana gement is ena bled in the EEPROM. If power

management is dis abled, then this register is set to 0.

For the 82559 and later Intel Fast Ethernet controllers, this regist er is hard-wired to DCh.

4.1.15 Interrupt Line (Offset 3C)

The Interrupt Line register is an 8-bit register used to communicate interrupt line routing

information. This register is configurable by the system BIOS or OS. POST software writes the

routing information into this register as it initializes and configures the system. The value in this

register specifies which system inte rrupt controller input the device interrupt pin is connected to.

Device drivers and operating systems use this information to determine priority and vector

information.

4.1.16 Interrupt Pin (Offset 3D)

The Interrupt Pin register specifies which interrupt pin the device (or device function) uses. This

register is always set to a 1, indicating that INTA# is used.

Intel 8255x 10/100 Mbps Eth ernet Controller Family Open Source Software Developer Manual

17

Page 26

PCI In terfac e

4.1.17 Max_Lat / Min_Gnt (Offset 3E)

These registe rs specify the device settings for Latency Timer va lues. For both registers , the value

specifies a period of time in units of ¼ microsec ond. Min_Gnt is used to specify the burst length

period the devi ce needs assuming a clock rate of 33 MHz. Max_Lat is used to specify how often

the device needs to gain access to the PCI bus. The value s of these registers are 8h (2 µS) for

Min_Gnt and 18h (6 µS) for Max_Lat.

4.1.18 Pow er Management PCI Configuratio n Registers

4.1.18.1 Capability Identifier (Offset DC)

The Capability Identif ier signals this item in the capability linked list as the PCI Power

Management regis ters. The PCI Power Management registers ha ve be en a ssigned the ID of 01h.

Since power manage ment is not implemented in the 82557, this register is hard-coded to 0 for that

device. For the 82558 and later devices, this rea d only register returns 01h.

4.1.18.2 Next Item Pointer (Offset DD)

The Next Item Pointer register describes the location of the next item in the capability lis t. Since

power managem ent is the last it em in the list, this register is se t to 0.

4.1.18.3 Power Management Capabilities (Offset DE)

The Power Management Capabilities (PMC) register is a 16-bit re ad-only register, which provides

informatio n on the capabilities of the device related to power manage me nt. Since power

management is not imp lemented in the 82557, this register is hard-coded to 0 for that device. For

the 82558 and later devices, this regist er returns values according to the chart below.

T able 4. Power Management Capabilities

Bit Default Value R / W Description

82558A: 00011

82558B, 82559:

31:27

26 1 RO

25 1 RO

24

no auxi liary power

- 01111

with auxiliary

power - 11111

82558A: 1

82558B: 0

82559: 0

RO

RO

PME_Support. This five bit field indicates the power states in

which the device may assert PME#. A value of 0b for any bit

indicates that the function is not capable of asserting the PME#

signa l while in that po w er sta t e.

The 82558 A-step supports wake-up from D0 and D1. The 82558

B-step an d 8255 9 s up po rt w ake- u p fr om D0, D1, D2 a nd D3

auxili ary power is prese nt and from all power state s if auxiliary

power exists.

D2_Support. If this bit is set, this function supports the D2 Power

Managem en t State. All devi ce s mus t sup po rt t he D0 an d D3 s t ates .

The 8255 9 an d later devi ces suppo r t the D 2 P ower Mana ge me nt

State.

D1_Support. If this bit is set, this function supports the D1 Power

Management State. The 82558 and later devices supports the D1

Power Management State.

FullClk. If this bit is set, this function requires a full speed clock at

all times when it is in the D0 state in order to perform its function. If

this bit is cleared, the function only requires a full speed PCI clock

while actually transferring data so dynamic clock control may be

used. The 82558 A-step requires a fu ll speed clock at all times

when it is in the D0 state in order to pe rform its functi on.

hot

if no

18

Intel 8255x 10/ 100 M bps Ethern et Co ntroller Family O pen Sourc e Sof tware Devel ope r Manua l

Page 27

T able 4. Power Management Capabilities

Bit Default Value R / W Description

23 0 RO Reserved. This field is not used by the 8255x.

82558: 0

82559:

22

21 1 RO

20

19 0 RO

81:16 001 RO

no auxiliary power

- 0

with auxiliary

power - 1

82558A: 0

82558B, 82559:

no auxiliary power

- 0

with auxiliary

power - 1

RO

RO

PCI Interface

AUX_Current. If the device is connected to an auxiliary power

supply, the 82559 reports a “1” to indicate that it consume less than

250 mA from the 3.3 Vaux pin while in the D3

reflection of bit 31.

DSI. The Device Specific Initialization bit indicates whether special

initialization of this function is required (beyond the standard PCI

configuration header) before the generic class device driver is able

to use it. Device specific initialization is required for the 82558 and

82559 af ter a D3 to D0 transition.

Auxiliary Power Source

This bit is only meaningful if PM CSR bit 31 (D3

PME) equ als 1 . When t hi s b it al so eq ual s 1, i t indi ca te s th at su ppor t

for PME# in D3

B-step and 82559 require auxiliary power for wake up from the

D3

state. Therefore this bit is set to 1 if auxiliary power is

cold

present.

PME Clock. When this bit is 1, it indicates that the PME#

generat io n l ogi c r equ ir e s it s ho st P CI bu s t o mai n t ain a f ree - run ni ng

PCI clock. When this bit is 0, it indicates that no host bus clock is

required for the functi on to gener ate PME# . The 82558 and later

generation devices do not require a clock to ge nerate PME# and

return 0.

Version. This field specifies to software how to interpret the PMC

and PMCSR registers. A value of 001b indicates that the device

complies with the Revision 1.0 of the PCI Power Management

Interface Specification.

requires an auxiliary pow er supply. The 82558

cold

state. This bit is a

cold

supporting

cold

4.1.18.4 Power Management Control/Status (Offset E0)

The Power Management Control/Status Register (PMCSR) is u sed to determine and change the

current power state of the device . It also all ows for the control of the power management inte rrupts

in a standard way. Since power management is not implemented in the 82557, this register is hardcoded to 0 for that device. For the 82558 and later devices this register acts according to the chart

below.

Intel 8255x 10/100 Mbps Eth ernet Controller Family Open Source Software Developer Manual

19

Page 28

PCI In terfac e

Table 5. Power Management Control/Status Register

Bit Value at Reset R / W Description

82558A: 0

82558B, 82559:

15

14:13

12:9 0000 R/W

8

7:5 000 Reserved.

40 RO

3:2 00 RO Reserved.

01:00 00 R/W

no auxi liary power

- 0

Sticky bit

82558: 00

82559: 10 or 00

82558A = 0

82558B & 82559

= 0

Unknown

(0 if no auxiliary

power available)

Read

Clear

RO

Read

Clear

PME Status. This bit is set upon a wake-up event from the link. It is

independent of the sta te of the PM E_Enable bit. Wh en software

writes 1 to this bit it is cleared and the device stops asserting PME#

(if enabled).

Data Scale. The Data Scale is not supported on the 82558 and

always returns 0. For the 82559, it is a 2-bit read-only field

indicati ng the da ta regi s ter sca lin g fac to r. For the 82559, it eq ua ls

10b for registers 0 through 8 and 00b for registers 9 through 15.

Data Select. This 4-bit field selects which data is reported through

the Data Register and Data Scale field. This register is only

supported on the 82559 and later generation devices.

PME Enable. This bit enables the device to assert PME#.

Dynamic Data. The 8255 8 do es not im pl em ent this reg is te r and

returns 0. The 82559 does not support the ability to monitor power

consumption dynamically.

Power State. This 2-bit field is used both to dete rmine the current

power state of the 82258 or 82559 and to set the 82558 or 82559

into a n ew power st ate. Th e definition of the field values is given

below.

00b - D0

01b - D1

10b - D2

11 b - D3

20

While wake-up events are not allowed in the D0 power state, hardware does not automatically

preclude this functionality. To ensure that wake-up events are not gen era ted when in D0, software

must clear the PME Enable bit when putting the device into that state. To ensure that no spurious

wake-up events are generated by the function, the PME Status bit (in the PMDR regi ster or the

PMCSR) must be specifically cleared (by writing a 1) when the PME Enable bit is set.

T o support Wake on LAN mode (pre-boot wake), the PME Enable and PME Sta tus bits are set wit h

known values after power-up reset. The ALTRST# pin should be connec ted to the device auxiliary

power good signal on the motherboard so that it will be active low on system power up. Assertion

of ALTRST# clears the PME Status bit and se ts the PME Enable bi t if the clock is active on the

CLK pin. Thus, if the Wake on LAN (WOL) bit in the EEPROM is se t, the device will wake up the

system upon receiving of Magic Packet*.

Intel 8255x 10/ 100 M bps Ethern et Co ntroller Family O pen Sourc e Sof tware Devel ope r Manua l

Page 29

4.1.18.5 Ethernet Power Consumption Registers (Offset E2h)

The Data Register is an 8-bit read-only registe r providing a mechanism for the device to report

state depende nt maximum power consumption and hea t dissipation. The value reported in this

register depends on the value written to the Data Select field in the PMCSR register .

The power measurements defined in the register have a dynamic range of 0 to 2.55 W wit h 0.01 W

resolution according to the data scale.

Note: The required accurac y should be in the range of +20% and -10%. The 82557 and 82558 do not

implement this register. The 82559 and later Intel Fast Ethe rnet controllers do. The val ue reported

in this register is hard-coded in the 82559 silicon. The structure of the data register is presented

below:

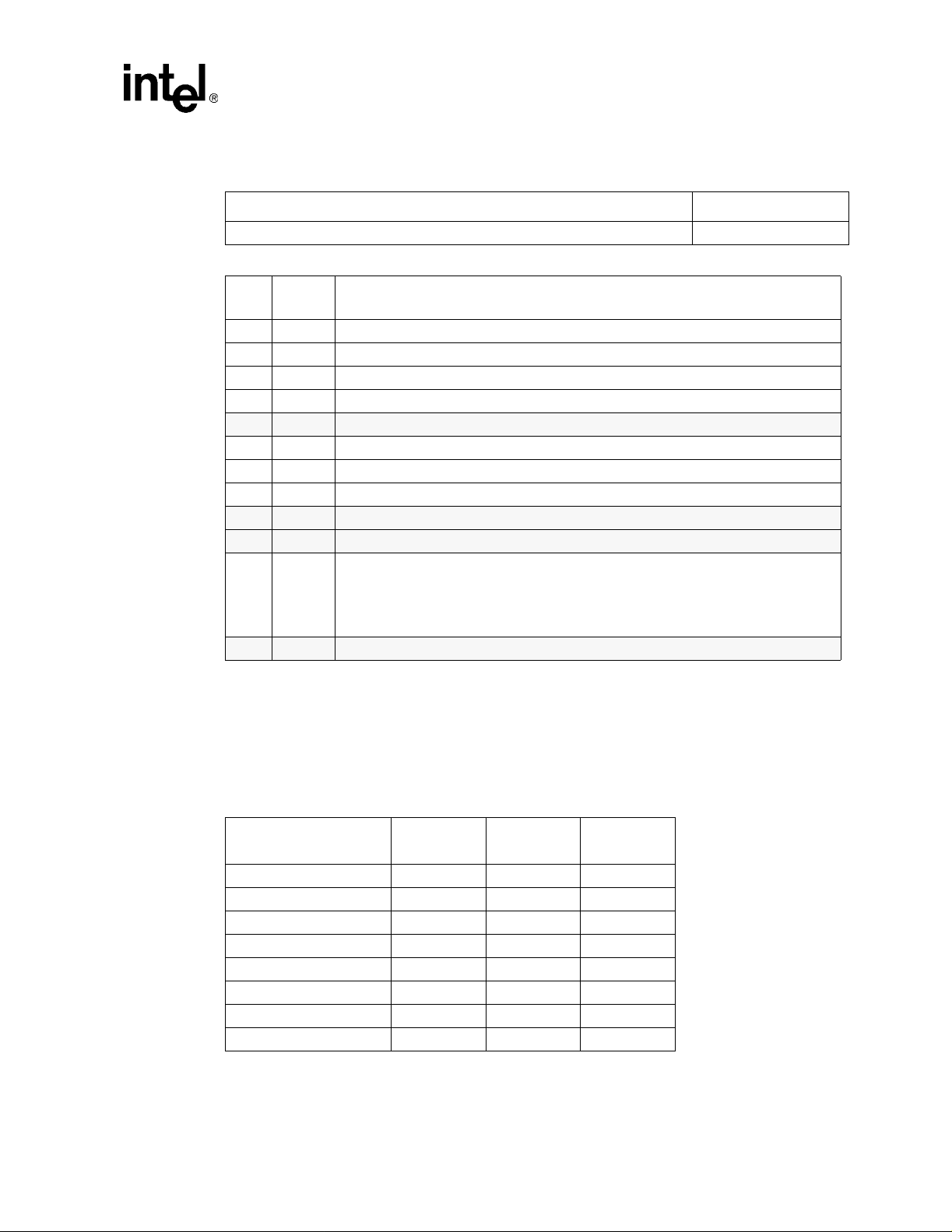

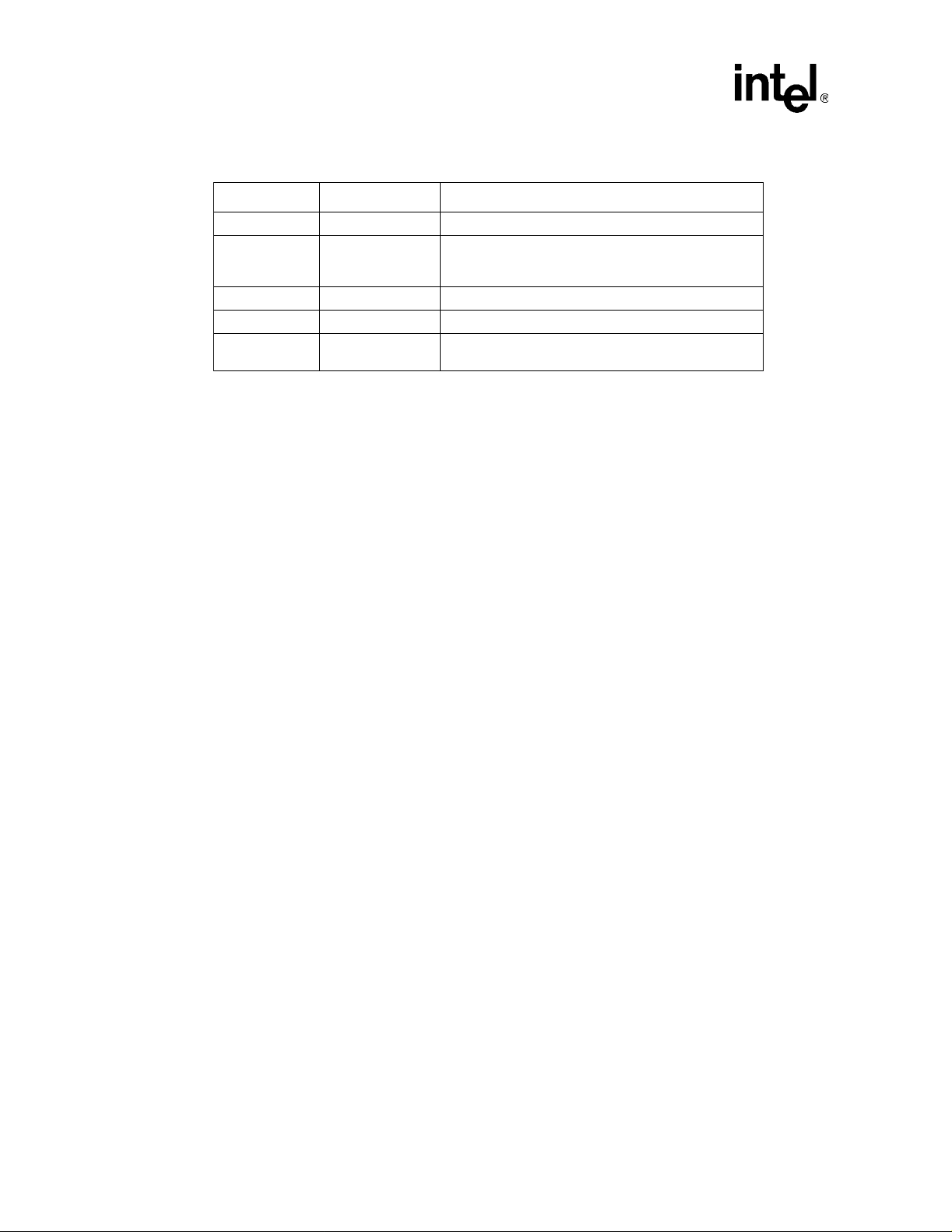

T able 6. Power Consumption / Dissipation Reporting

Data Select Data Scale Data Reported

0 2 D0 Power Consumption = 58 (580 mW)

1 2 D1 Power Consumption = 40 (400 mW)

2 2 D2 Power Consumption = 40 (400 mW)

3 2 D3 Power Consumption = 40 (400 mW)

4 2 D0 Power Dissipated = 58 (580 mW)

5 2 D1 Power Dissipated = 40 (400 mW)

6 2 D2 Power Dissipated = 40 (400 mW)

7 2 D3 Power Dissipated = 40 (400 mW)

8 2 Common Function Power Dissipated = 00

9-15 0 Reserved 00 h

PCI Interface

NOTE: The D1 and D2 power states are not currently s upporte d by operating systems.

4.2 PCI Command Usage

The table below lists the PCI commands that the various Intel Fast Ethernet controllers can use.

Intel 8255x 10/100 Mbps Eth ernet Controller Family Open Source Software Developer Manual

21

Page 30

PCI In terfac e

Table 7. Gener ated PCI Commands

PCI Command Name Circumstance Used

0x6 MR TxCB “S” bit read.

0x7 MW

0xC MRM Re ading transmit data buffers.

0xE MRL CB, TBD, and RFD.

0xF

MWI (82558 &

82559)

CB and RFD. Writing sta tistics co unters or dump data

buffer to memory. Writing received packet data into

receive buffers.

Writing received packet data into receive buffers.

The controllers do not generate I/O commands, Interrupt Acknowledge cycle s, or Configuration

cycles. The controllers also do not support Dual Address Cycle (DAC). Targets (typically the

system bridge ) must respond to all of the commands that the Ethernet controller generates.

4.2.1 Memory Write and Invalidate

The 82558, 82559 , 825 50, and 82551 hav e 4 int ernal DMA channe ls. Of thes e 4, t he Rec eive DMA

channel is used to deposit packet data received from the link into sy stem memory. The Receive

DMA channel uses both the Memory Write (MW) and the Memory Write and Invalidate (MWI)

commands. In order to use MWI the device m us t guarantee:

• A minimum transfer of one cac he line.

• All byte- en a bl e bits are ac ti v e dur i n g ea ch M W I acc es s.

• The device may cros s a cache line boundary only if it intends to transfer the e ntire next cache

line too.

In order to ensure the abo ve conditions, the device may use the MWI command only if the

following c onditions hold:

1. The cache line size written in the CLS register during PCI configuration is 8 or 16 Dwords.

2. The accessed address is cache line aligned.

3. The 82558 or 82559 has at le as t a c ache line size of data byte in its Receive FIFO.

4. Ther e is a t le ast a cache li n e s iz e o f sp ac e left in the sy s t em m e m o r y buff er. In addit i on , the

device will use two configuration bits to enable and disable the us e of MWI: