Page 1

82555 10/100 Mbps LAN Physical Layer

Interface

Networking Silicon

Datasheet

Product Features

■

Optimal integration for lower cost solutions

—Integrated 10/100 Mbps single chip

physical layer interface solution

—Complete 10/100 Mbps MII compliance

with MDI support

—Full duplex operation in 10 Mbps and

100 Mbps modes

—IEEE 802.3u Auto-Negotiation support

for 10BASE-T half and full duplex,

100BASE-TX half and full duplex, and

100BASE-T4 configurations

—Parallel detection algorithm for legacy

support of non-Auto-Negot ia ti on

enabled link partner

—Integrated 10BASE-T transcei v er with

built in transmit and receive filters

—Glueless interface to T4-PHY for

combination TX/T4 designs with single

magnetics

—Glueless support for 4 LEDs: activity,

link, speed, and duplex

—LED function mapping support via MDI

—Low external component count

—Single 25 MHz clock support for 10

Mbps and 100 Mbps (crystal or

oscillator)

—Single magnetics for 10 Mbps and 100

Mbps operation

—QFP 100-pin package

■

Performance enhancements

—Flow control support for IEEE 802.3x

Auto-Negotiation and Bay Technologies

PHY Base* scheme

—Adaptive Channel Equalizer for greater

functionality over varying cable lengths

—High tolerance to extreme noise

conditions

—Very lo w emissions

—Jabber control circuitry to prevent data

loss in 10 Mbps operation

—Auto-polarity correction for 10BASE-T

—Software compatible with 82557 drivers

■

Repeater functionality

—Repeater mode operation

—Support for forced speed of 10 Mbps

and 100 Mbps

—Automatic carrier disconnect for IEEE

802.3u compliance

—Auto-Negotiation enable/disable

capability

—Receive port enable function

—Support for 32 configurable addresses

—Narrow analog side (14 mm) for tight

packing in repeater and switch designs

Notice:

Notice:

Document Number: 666252-004

Revision 2.0

March 1998

Page 2

82555 — Networking Silicon

■

Low power consumption

—Typical total solution power including

all resistors and magnetics:

- 275 mA 100BASE-TX

- 230 mA 10BASE-T

- 250 mA Auto-Negotiation

—300 mA maximum total solution power

in DTE (adapter) mode

—Power-down of 10BASE-T/100BASE-

■

Added modes for design, testing, and

manufacturability

—Test Access Port (TAP)

- NAND Tree

- Board Level Functional Test (BIST)

—Programmable bypass for 4B/5B

encoding/decoding and scrambler/

descrambler

—Diagnostic loopback mode

TX sections when not in use

Revision Hist ory

Revision

Date

Jan. 1997 1.0 First external release of the preliminary datasheet

Apr. 1997 1.1 First release edition

Mar. 1998 2.0 General editing

Revision Description

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any f e atures or instructions marked "reserved" or "undefined." Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 82555 10/100 Mbps LAN Physical Layer Interface may contain design defects or errors known as errata which may cause the product to deviate

from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

P.O. Box 7641

Mt. Prospect IL 60056-7641

or call 1-800-879-4683.

Copyright © Intel Corporation, 1997

*Third-party brands and names are the property of their respective owners.

ii Datasheet

Page 3

Networking Silicon — 82555

Contents

1.0 INTRODUCTION..........................................................................................................................1

1.1 Functional Overview........................................................................................................1

1.2 Compliance to Industry Standards..................................................................................1

2.0 ARCHITECTURAL OVERVIEW...................................................................................................3

2.1 100 Mbps Mode...............................................................................................................3

2.2 10 Mbps Mode.... ...... ....... ...... ....... ...... ....... ...... ................................................................4

2.3 Media Independent Interface (MII)..................................................................................5

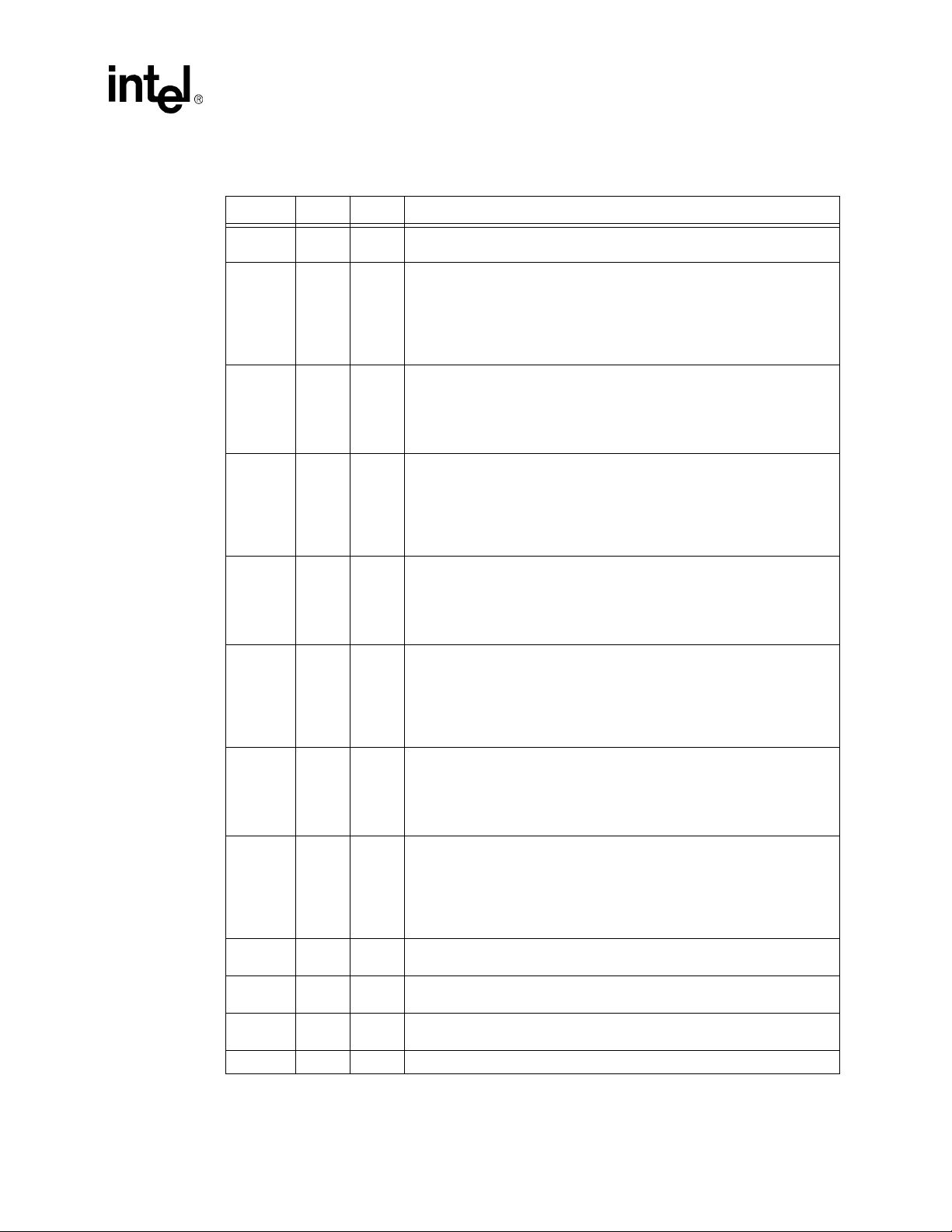

3.0 PIN DEFINITIONS........................................................................................................................7

3.1 Pin Types .......................................................................................................................8

3.2 Clock Pins ......................................................................................................................8

3.3 Twisted Pair Ethernet (TPE) Pins ...................................................................................8

3.4 Media Independent Interface (MII) Pins .........................................................................8

3.5 Media Access Control/Repeater Interface Control Pins .................................................9

3.6 LED Pins ......................................................................................................................10

3.7 External Bias Pins ........................................................................................................10

3.8 Miscellaneous Control Pins .................................. ....... ...... ....... ....................................11

3.9 Power and Ground Pins ...............................................................................................12

4.0 100BASE-TX ADAPTER MODE OPERATION..........................................................................13

4.1 100BASE-TX Transmit Clock Generation .....................................................................13

4.2 100BASE-TX Transmit Blocks ......................................................................................13

4.2.1 100BASE-TX 4B/5B Encoder ....................................................................13

4.2.2 100BASE-TX Scrambler and MLT-3 Encoder ...........................................14

4.2.3 100BASE-TX Transmit Framing ................................................................15

4.2.4 Transmit Driver ..........................................................................................16

4.3 100BASE-TX Receive Blocks .......................................................................................16

4.3.1 Adaptive Equalizer.....................................................................................17

4.3.2 Receive Clock and Data Recovery............................................................17

4.3.3 MLT-3 Decoder, Descrambler, and Receive Digital Section......................17

4.3.4 100BASE-TX Receive Framing .................................................................17

4.3.5 100BASE-TX Receive Error Detection and Repo rt ing. ..............................17

4.4 100BASE-TX Collision Detection..................................................................................17

4.5 100BASE-TX Link Integrity and Auto-Negotiation Solution...........................................18

4.5.1 Link Integrity...............................................................................................18

4.5.2 Auto-Negotiation ........................................................................................18

4.5.3 Combination Tx/T4 Auto-Negotiation Solution...........................................18

4.6 Auto 10/100 Mbps Speed Selection..............................................................................19

4.7 Adapter Mode Addresses.......................... ...... ..............................................................19

5.0 10BASE-T FUNCTIONALITY IN ADAPTER MODE ..................................................................21

5.1 10BASE-T Transmit Clock Generation..........................................................................21

5.2 10BASE-T Transmit Blocks...........................................................................................21

5.2.1 10BASE-T Manchester Encoder................................................................21

5.2.2 10BASE-T Driver and Filter .......................................................................21

5.3 10BASE-T Receive Blocks............................................................................................21

5.3.1 10BASE-T Manchester Decoder................................................................21

5.3.2 10BASE-T Twisted Pair Ethernet (TPE) Receive Buffer and Filter............21

Datasheet iii

Page 4

82555 — Networking Silicon

Contents

5.3.3 10BASE-T Error Detection and Reporting .................................................22

5.4 10BASE-T Collision Detection.......................................................................................22

5.5 10BASE-T Link Integrity................................................................................................22

5.6 10BASE-T Jabber Control Function..............................................................................22

5.7 10BASE-T Full Duplex ..................................................................................................23

6.0 REPEATER MODE....................................................................................................................25

6.1 Special Repeater Features............................................................................................25

6.2 Connectivity...................................................................................................................25

7.0 MANAGEMENT DATA INTERFACE..........................................................................................27

7.1 MDI Frame Structure.....................................................................................................27

7.2 MDI Registers................................................................................................................28

7.2.1 MDI Registers 0 - 7....................................................................................28

7.2.2 MDI Registers 8 - 15..................................................................................31

7.2.3 MDI Registers 16 - 31................................................................................31

8.0 AUTO-NEGOTIATION FUNCTIONALITY..................................................................................35

8.1 Description ....................................................................................................................35

8.2 Parallel Detect and Auto-Negotiation............................................................................36

9.0 LED DESCRIPTIONS ................................................................................................................39

10.0 RESET AND MISCELLANEOUS TEST MODES.......................................................................41

10.1 Reset.............................................................................................................................41

10.2 Loopback.......................................................................................................................41

10.3 Scrambler Bypass .........................................................................................................41

10.4 Test Port........................................................................................................................41

11.0 ELECTRICAL SPECIFICATIONS AND TIMING PARAMETERS..............................................43

11.1 Absolute Maximum Ratings ..........................................................................................43

11.2 General Operating Conditions ........................... ...... ....... ...... ....... ...... ....... ...... ....... .......43

11.3 DC Characteristics ............................................. ...... ....... ...... ....... ...... ....... ...... ....... ...... .43

11.3.1 MII DC Characteristics ..............................................................................43

11.3.2 10BASE-T Voltage/Current DC Characteristics ........................................43

11.3.3 100BASE-TX Voltage/Current DC Characteristics .................................. .44

11.4 AC Characteristics.........................................................................................................45

11.4.1 MII Clock Specifications.............................................................................45

11.4.2 MII Timing Parameters ..............................................................................46

11.4.3 Repeater Mode Timing Parameters ..........................................................47

11.4.4 Transmit Packet Timing Parameters .........................................................48

11.4.5 Squelch Test Timing Parameters ..............................................................48

11.4.6 Jabber Timing Parameters ........................................................................49

11.4.7 Receive Packet Timing Parameters ..........................................................49

11.4.8 10BASE-T Normal Link Pulse (NLP) Timing Parameters .........................50

11.4.9 Auto-Negotiation Fast Link Pulse (FLP) Timing Parameters ....................50

11.4.10 Reset Timing Parameters .........................................................................51

11.4.11 X1 Clock Specifications ............................................................................51

11.4.12 100BASE-TX Transmitter AC Specification ..............................................52

12.0 82555 PACKAGE INFORMATION.............................................................................................53

iv

Datasheet

Page 5

1.0 Introduction

g

The 82555 is a highly integrated, physical layer interface solution designed for 10 and 100 Mbps

Ethernet systems based on the IEEE 10BASE-T and 100BASE-TX specifications . 100B ASE-TX is

an IEEE 802.3 physical layer s peci fication for use o v er t wo pairs of Category 5 unshielded twist ed

pair or Type 1 shielded twisted pair cable. 100BASE-TX defines a signaling scheme not only for

100 Mbps, but also provides CSMA/CD compatibility with the 10 Mbps IEEE 802.3 10BASE-T

signaling stand ard.

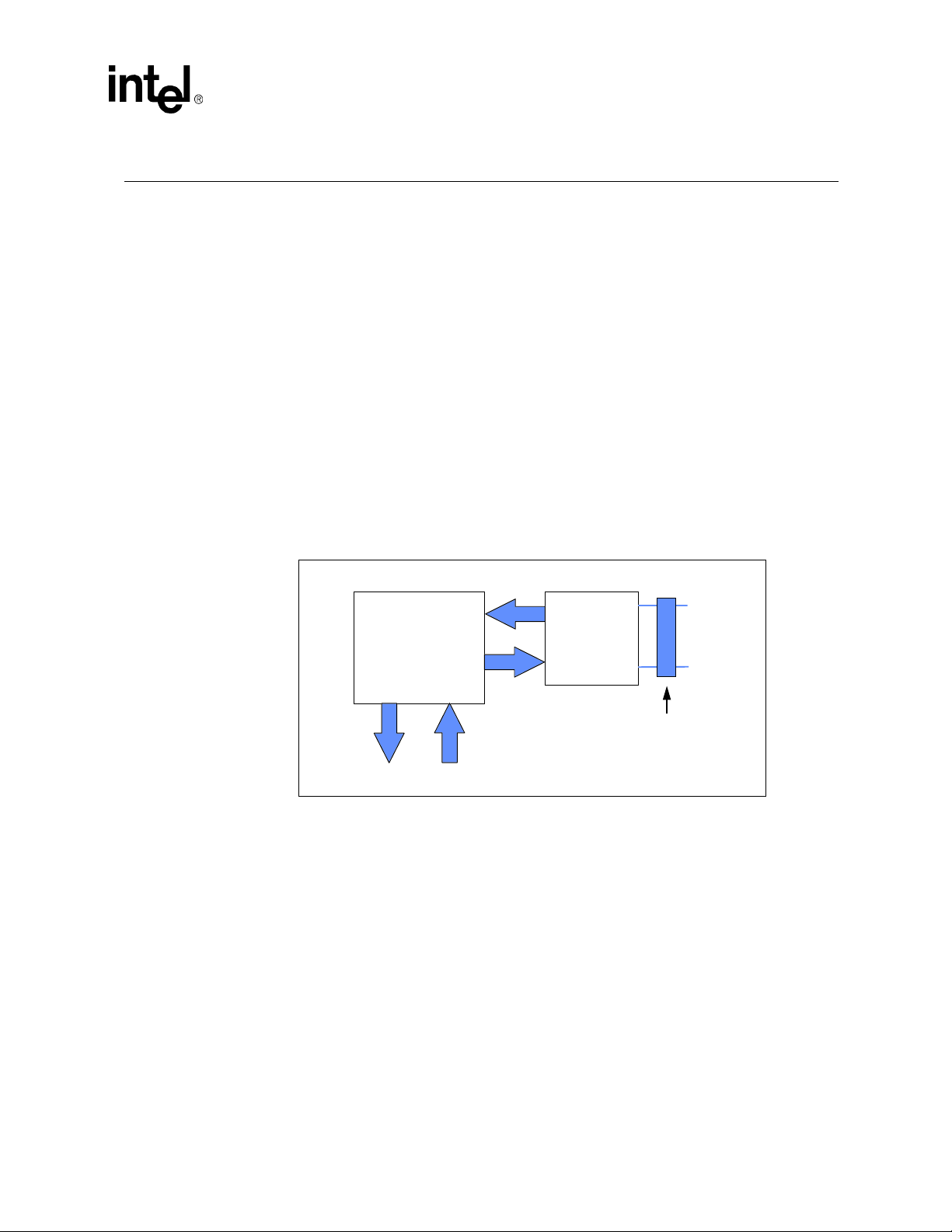

1.1 Functional Overview

The 82555 is designed to work in two modes: Data Terminal Equipment (DTE) for adapters and

repeater for hubs and switches. When configured to DTE (adapter) mode, the 82555 incorporates

all active circuitry required to interface 10/100 Mbps Ethernet controllers and CSMA/CD MAC

components to 10 Mbps and 100 Mbps networks. In this and other documents the 82555 may be

referred to as the DTE, Physical Medium Device (PMD), or Physical Layer Medium (PLM). It

supports a direct glueless interface to Intel components such as the 82557 Fast Ethernet controller.

The 82555 also supports the Media Independent Interface (MII) signals as specified in the IEEE

802.3u standard. The figure below shows how the 82555 fits into a 10/100 Mbps Ethernet adapter

design.

Networking Silicon — 82555

Controller/MAC

System Bus Interface

Intel 82555

Figure 1. 82555 10/100 Mbps Ethernet Solution

When configured to repeater mo de, the 82555 incorporates sev eral f eatures that allo w it to f unction

as a Class I or MII level repeater. Section 6.0, “Repeater Mode” on page 25 describes the 82555 in

a repeater type of application.

1.2 Compliance to Industry Standards

When operating in 100 Mbps mode, the 82555 complies with IEEE 802.3u 100BASE-TX

specification. The PMD section with the related changes established in 802.3u 100BASE-TX

complies with ANSI X3.263:1995 TP-PMD, Revision 2.2.

When operating in the 10 Mbps mode, the 82555 complies with the IEEE 802.3 10BASE-T

specification.

Ma

Pair 1

Pair 2

netics

Datasheet 1

Page 6

82555 — Networking Silicon

The 82555 also complies with the IEEE 802.3u Auto-Negotiation and the IEEE 802.3x Full Duplex

Flow Control sections. The MAC interface on the 82555 is a superset of the IEEE 802.3u Media

Independent Interface (MII) standard.

2

Datasheet

Page 7

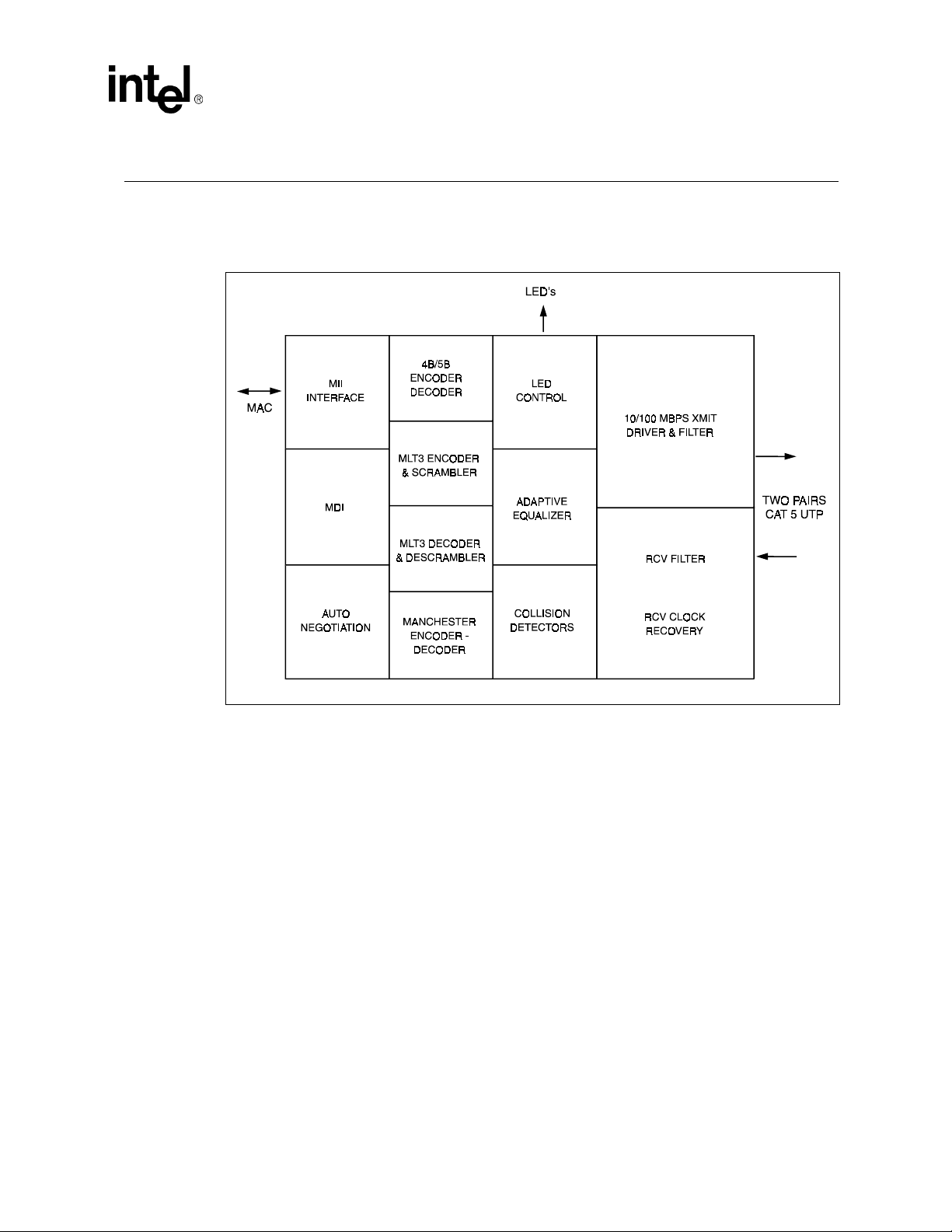

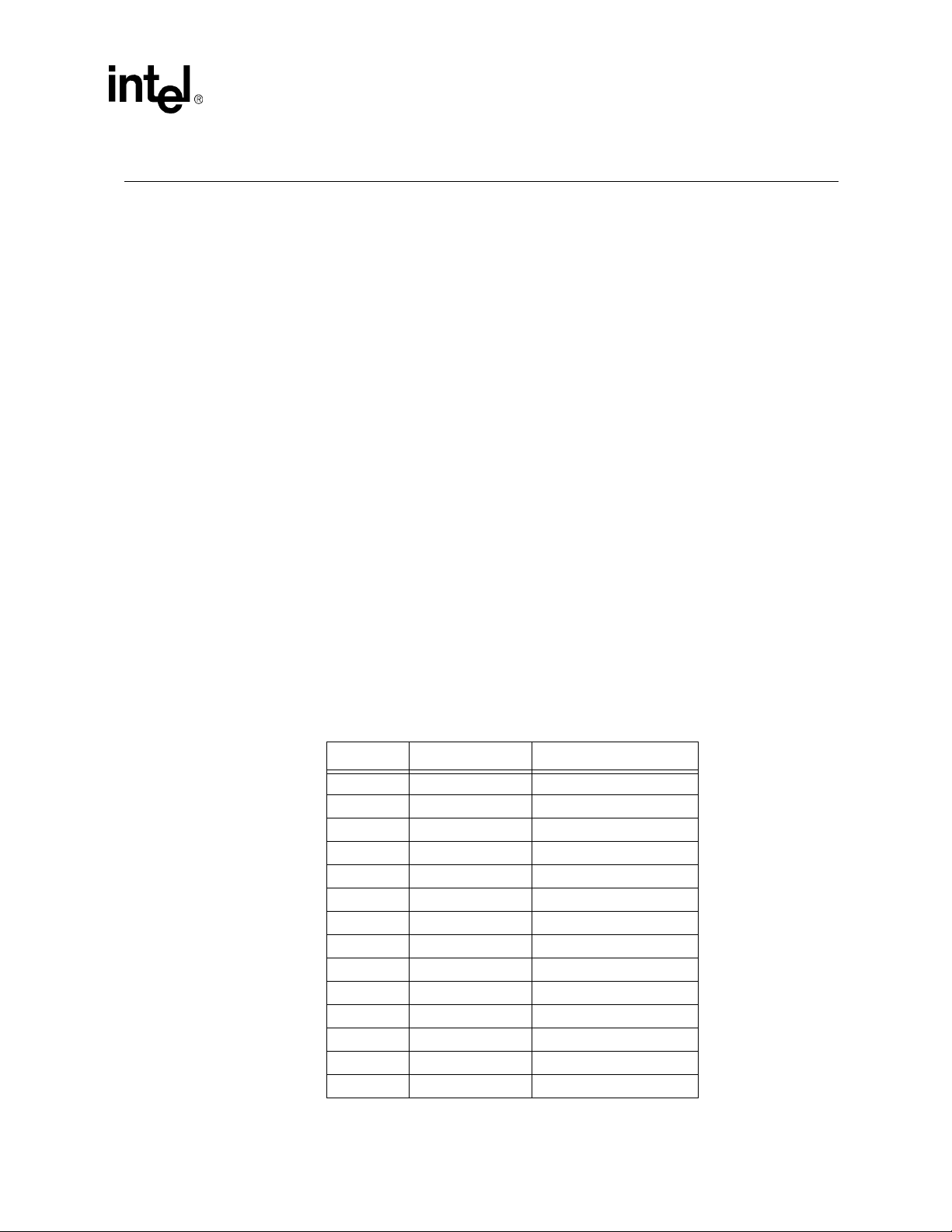

2.0 Architectural Overview

The 82555 is an advanced combin ation of both digital and an alog logic which combine to pro vide a

functional stack between the Media Independent Interface (MII) and the wire through the

magnetics. Figure 2 shows a general block diagram of the 82555 component.

Networking Silicon — 82555

Figure 2. 82555 Simplified Block Diagram

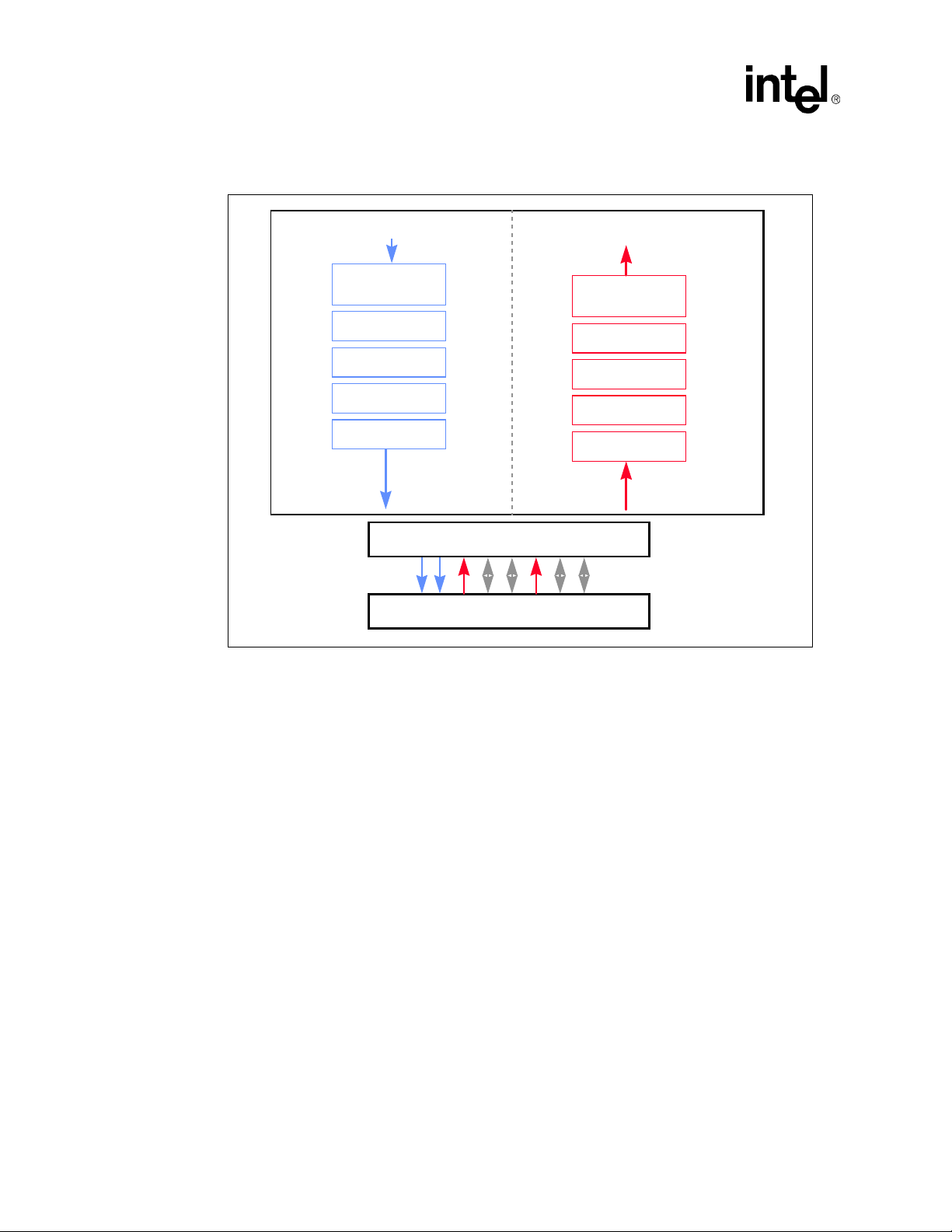

2.1 100 Mbps Mode

In 100BASE-TX mode the 82555 digital subsection performs all signal processing of digital data

obtained from the analog reception and the data to be driven into the analog transmit subsection.

This includes 4B/5B encoding/deco ding, scrambling/descrambling, carrier sense, collision

detection, link detection, Auto-Negotiation, data validation, and providing MII to the Media

Access Controller (MAC). The 82555 supports the IEEE defined MII as its MAC interface and

expects the controller to drive the Management Data Input/Output and Management Data Clock

signals to perform the management functions.

In 100BASE-TX mode, the analog subsection of the 82555 performs two functions:

Transmit: The 82555 converts a digital 125 Mbps stream into MLT-3 format and drives it

•

through the transmit differential pair onto the physical medium.

Datasheet 3

Page 8

82555 — Networking Silicon

Receive: The 82555 takes receive analog MLT-3 data from the receive differential pair and

•

converts it into a digital 125 Mbps stream, recovering both clock and data signals.

MII TX Interface

4b/5b

Encoding

Scrambler

Serialization

NRZ to NRZI

NRZI to MLT3

Magnetics Module

12345678

MII RX Interface

4b/5b

Decoding

De-scrambler

Serial to 5B

NRZI to NRZ

MLT3 to NRZI

RJ-45 Connector

Figure 3. 82555 Analog Logic

2.2 10 Mbps Mode

The 82555 operation in 1 0BASE-T mode is similar to the 82555 operation in 100BASE-TX mode.

Manchester encoding and decoding is used instead of 4B/5B encoding/decoding and scrambling/

descrambling. In addition, the Transmit Clock and Receive Clock (MII clock signals) provide 2.5

MHz instead of 25 MHz.

4

Datasheet

Page 9

Networking Silicon — 82555

(

)

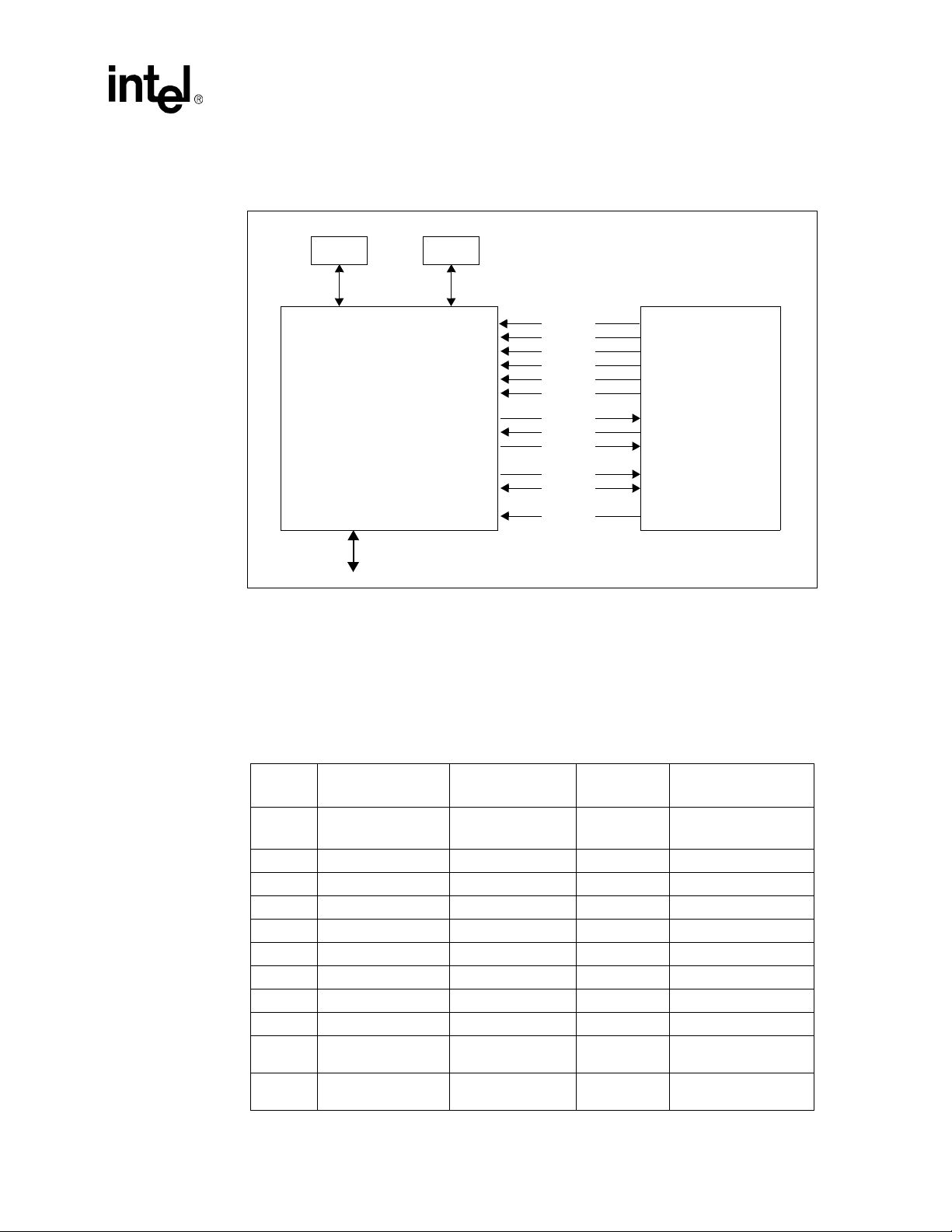

The 82555 provides a glueless interface to Intel components such as the 82557 Fast Ethernet

Controller, as well as any MII compatible device. Figure 4 shows a schematic-level diagram of the

82557 Fast Ethernet controller implementation connected to the 82555 using the MII interface.

Flash

(optional)

82557

EEPROM

optional

RXD[3:0]

RXERR

RXDV

TXD[3:0]

TXEN

MDIO

RESET

PCI Bus Signals

Figure 4. Intel 82557/82555 Solution

2.3 Media Independent Interface (MII)

RXC

CRS

COL

TXC

MDC

82555

The 82555 supports the Media Independent Interface (MII) as its primary interface to the MAC.

The MII Interface is summarized in Table 1.

Table 1. 82555 MII

Signal

Name

TXC Transmit Cloc k

TXD[3:0] Transmit Data From MAC TXC Yes

TXEN Transmit Enable From MAC TXC Yes

COL Collision Detect From 82555 Asynchronous Yes

CRS Carrier Sense From 82555 Asynchronous Yes

RXC Receive Clock From 82555 -- Yes

RXD[3:0] Receive Data From 82555 RXC Yes

RXDV Receive Data Valid From 82555 RXC Yes

RXERR Receive Error From 82555 RXC Yes

MDC

MDIO

Description Direction

From 82555

(adapter mode only)

Management Data

Clock

Management Data

Input/Output

From manager -- Yes

From manager MDC Yes

Clock

Reference

-- Yes

MII Signal Supported

by the 82555?

Datasheet 5

Page 10

82555 — Networking Silicon

Table 1. 82555 MII

Signal

Name

TXERR

Description Direction

Transmit Err or

(repeater mode only)

From RIC TXC Yes

Clock

Reference

MII Signal Supported

by the 82555?

6

Datasheet

Page 11

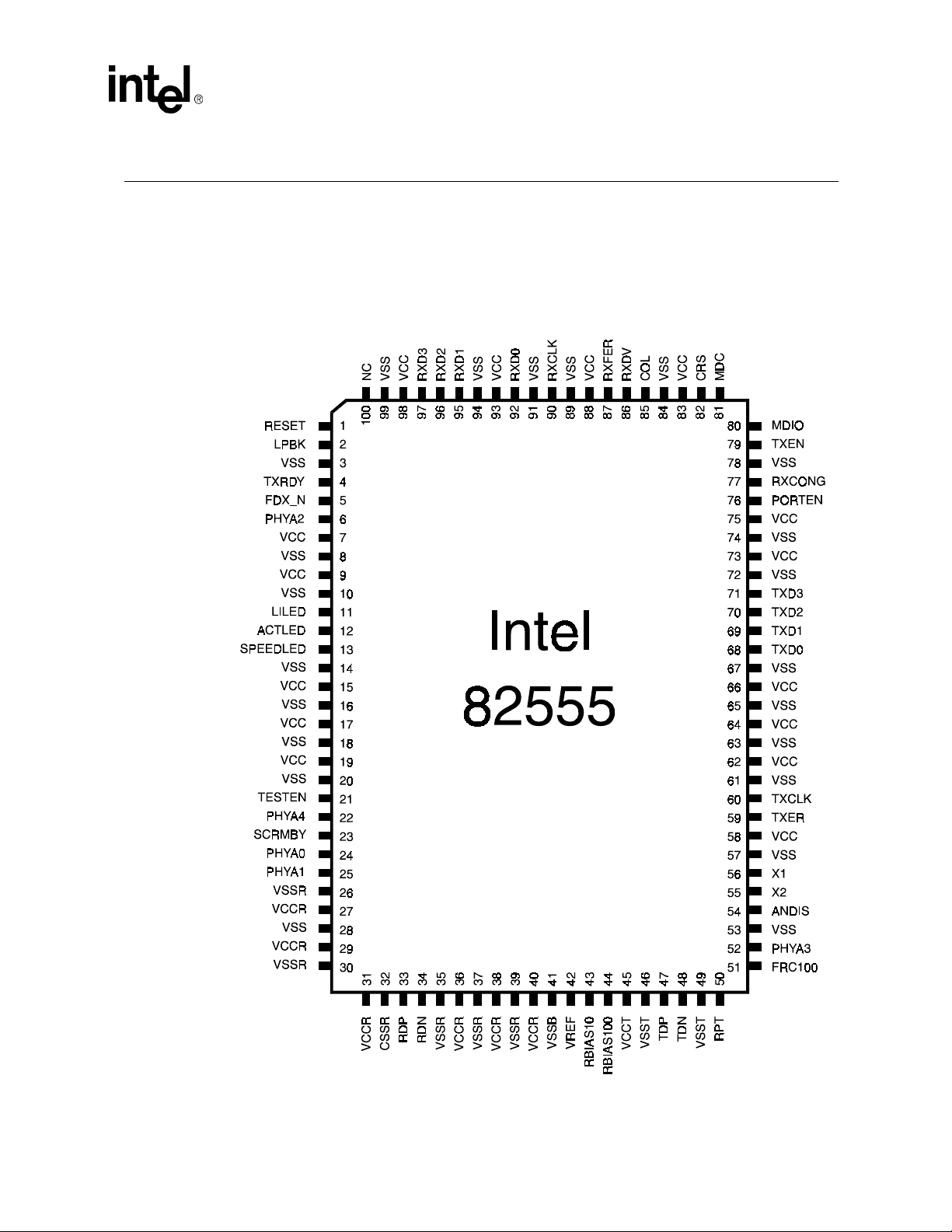

3.0 Pin Definitions

All active digital pins are defined to have transistor-to-transistor logic voltage levels except the X1

and X2 crystal signals. The transmit differential and recei ve d iffer ential pins are specifi ed as analog

outputs and inputs, respectively.

The figure below show the pin locations on the 82555 component. The following subsections

describe the pin functions .

Networking Silicon — 82555

Figure 5. 82555 Pin Numbers and Labels

Datasheet 7

Page 12

82555 — Networking Silicon

Pin allocation is based on a 100-lead quad flat package. All pin locations are based on printed

circuit board layout and other design constraints.

3.1 Pin Types

Pin Type Description

I This type of pin is an input pin to the 82555.

O This type of pin is an output pin from the 82555.

I/O This type of pin is both an input and output pin for the 82555.

B This pin is used as a bias pin. The bias pin is either pulled up or do wn with a resistor. The bias pin

may also be used as an external voltage reference.

3.2 Clock Pins

Symbol Pin Type Name and Function

X1 56 I

X2 55 O

Crystal Input One.

Otherwise, X1 may be driven by an external MOS level 25 MHz oscillator

when X2 is left floating. (The crystal should have a tolerance of 50 PPM or

better.)

Crystal Output Two.

crystal. Otherwise, X1 may be driven by an external MOS level 25 MHz

oscillator when this pin is left floating.

X1 and X2 can be driven by an external 25 MHz crystal.

X1 and X2 can be driven by an external 25 MHz

3.3 Twisted Pair Ethernet (TPE) Pins

Symbol Pin Type Name and Function

TDP

TDN

RDP

RDN

47

48

33

34

O

I

Transmit Differential Pair.

transmission on an unshielded twisted pair (UTP) cable. The current-driven

differential driver can be two-level (10BASE-T or Manchester) or three-level

(100BASE-TX or MLT-3) signals depending on the operating mode. These

signals interface directly with an isolation transformer.

Receive Differential Pair.

isolation transformer. The bitstream can be two-level (10BASE-T or

manchester) or three-level (100BASE-TX or MLT-3) signals depending on the

operating mode.

These pins send the serial bitstream for

These pins receive the serial bitstream from the

3.4 Media Independent Interface (MII) Pins

Symbol Pin Type Name and Function

RXD3

RXD2

RXD1

RXD0

97

96

95

92

O

Receive Data.

these four lines one nibble at a time.

In 100 Mbps and 10 Mbps mode, data is transferred across

8

Datasheet

Page 13

Networking Silicon — 82555

Symbol Pin Type Name and Function

RXC 90 O

RXDV 86 O

RXERR 87 O

TXD3

TXD2

TXD1

TXD0

TXC 60 I/O

TXEN 79 I

TXERR 59 I

CRS 82 O

COL 85 O

MDIO 80 I/O

MDC 81 II

71

70

69

68

I

Receive Clock.

depending on the 82555’s operating speed (25 MHz for 100 Mbps and 2.5

MHz for 10 Mbps). The Receive Clock is recovered directly from incoming

data and is continuous into the Media Access Controller (MAC). Thus, it must

be resynchronized in 10 Mbps mode at the start of each incoming packet.

Receive Data Valid.

RSC[3:0] pins are valid.

Receive Error.

occurred during frame reception.

T ransmit Data.

these four lines one nibble at a time.

T ransmit Clock.

depending on the 82555’s operating speed (25 MHz for 100 Mbps and 2.5

MHz for 10 Mbps). The Transmit Clock outputs a continuous clock into the

MAC that is generated directly from the external clock source in DTE

(adapter) mode. In repeater mode, the TXC is an input signal operating at

either 25 MHz or 2.5 MHz depending on the operating speed, which is

typically clocked by a receiver interface de vice .

T ransmit Enabl e.

valid data is present on the TXD[3:0] pins.

T ransmit Error.

occurred during transmissions of a frame.

Carrier Sense.

present on the link. CRS is an asynchronous output signal.

Collision Detect.

and indicates to the 82555 that a collision has occurred on the link. COL i s an

asynchronous output signal to the controller.

Management Data Input/Output.

for the Management Data Interface (MDI).

Management Data Clock.

the MDIO signal. MDC should operate at a maximum frequency of 2.5 MHz

The Receive Clock may be either 25 MHz or 2.5 MHz

This signal indicates that the incoming data on the

The RXERR signal indicates to the 82555 that an error has

In 100 Mbps and 10 Mbps mode, data is transferred across

The Transmit Clock may be either 25 MHz or 2.5 MHz

The Transmit Enable signal indicates to the 82555 that

The TXERR signal indicates to the 82555 that an error has

The Carrier Sense signal indicates to the 82555 that traffic is

The Collision Detect signal operates in half duplex mode

The MDIO signal is a bidirectional data pin

The MDC signal functions as a clock reference for

3.5 Media Access Control/Repeater Interface Control Pins

Symbol Pin Type Name and Function

RXCONG 77 I

PORTEN 76 I

Receive Congestion.

active high and indicates an overrun on the controller receive side:

• Full duplex PHY Base (Bay Technologies) flow control DTE (adapter)

mode

• Full duplex signal (FDX_N) is high

• Full duplex technology is active through Auto-Negotiation

Port Enable.

signals will be tri-stated: RXD[3:0], RXC, RXDV, and RXERR.

In repeater mode when the PORTEN signal is low, the follo wing

Datasheet 9

If the following conditions exist, the RXCONG is an

Page 14

82555 — Networking Silicon

Symbol Pin Type Name and Function

TXRDY

(TOUT)

FDX_N 5 I/O

4 O This pin is multiplexed and can be used for one of the following:

3.6 LED Pins

Symbol Pin Type Name and Function

ACTLED 12 O

LILED 11 O

SPEEDLED

13 O Speed LED

T ransmit Ready.

modes are enabled, the TXRDY signal enables transmission while it is

asserted.

When the Test Enable signal is activated, this signal functions as the

TOUT .

Test Output port.

Full Duplex.

result of the duplex configuration to the MAC. This pin can also operate as

the LED driver and will be an active low for all technologies.

In repeater mode, this signal is used for Auto-Negotiation advertisement to

the 82555’s link partner and activates the PHY Base (Bay Technologies) flow

control if 100BASE-TX full duplex is the highest common technology between

the 82555 and its link partner.

Activity LED.

activity is present, the ACTLED is on. When no activity is present, the

ACTLED is off.

Link Integrity LED.

present in either 10 Mbps or 100 Mbps, the LILED is on; and if an invalid link

is preset, LILED is off.

For a combination design board, the LILED should be connected to the TX

technology LED.

This signal is used to indicate the speed of operation. For 100 Mbps, the

SPEEDLED will be on; and for 10 Mbps, the SPEEDLED will be off.

If full duplex and PHY Base (Bay T echnologies) flow control

In DTE (adapter) mode, this active lo w output signal reports the

This signal indicates either transmit or receive activity. When

This signal indicates the link integrity. If a valid link is

3.7 External Bias Pins

Symbol Pin Type Name and Function

RBIAS100 44 B

RBIAS10 43 B

PD1 42 I

PD2 100 I

Note: The resistor values described for the external bias pins are only recommended values and may

require to be fine tuned for various designs.

10

Bias Reference Resistor 100.

this pin to ground.

Bias Reference Resistor 10.

this pin to ground.

Pull Down One.

ground.

Pull Down One.

ground.

A 10 KΩ resistor should be connected from this pin to

A 1 KΩ resistor should be connected from this pin to

Datasheet

A 634 Ω resistor should be connected from

A 768 Ω resistor should be connected from

Page 15

3.8 Miscellaneous Control Pins

Symbol Pin Type Name and Function

RESET 1 I

FRC100

(MACTYP)

PHYA4

(TIN)

PHYA3

(SLVTRI)

PHYA2

(LISTAT)

PHYA1

(TEXEC)

PHYA0

(TCK)

ANDIS

(T4ADV)

SCRMBY 23 I

LPBK 2 I

RPT 50 I

TESTEN 21 I

51 I This pin is multiplexed and can be used for one of the following:

22 I This pin is multiplexed and can be used for one of the following:

52 I/O This pin is multiplexed and can be used for one of the following:

6 I This pin is multiplexed and can be used for one of the following:

25 I This pin is multiplexed and can be used for one of the following:

24 I This pin is multiplexed and can be used for one of the following:

54 I This pin is multiplexed and can be used for one of the following:

The Reset signal is active high and resets the 82555. A reset pulse

Reset.

width of at least 1 µs should be used.

Force 100/10 Mbps.

either 100 Mbps (active high) or to 10 Mbps (active low).

MAC Type.

82555 drives 82557 mode. If this input signal is low, the 82555 drives a

generic MII MAC mode.

PHY Address 4.

address port configuration.

TIN.

data.

PHY Address 3.

address port configuration.

Slave T ri - state.

with the T4 Advanced signal. When both are active, the slave PHY is inactive

and tri-states all its outputs.

PHY Address 2.

address port configuration.

Link Status.

signal is active low and the slave PHY link is valid.

PHY Address 1.

address port configuration.

Test Execute.

execution command indicating that the pin 22 is being used as the Test Input

pin.

PHY Address 0.

address port configuration.

Test Clock.

signal.

Auto-Negotiation Disable.

for management reasons. If this input signal is high, the Auto-Negotiation

operation will be disabled.

T4ADV.

allows the LISTAT and SLVTRI pins to be used as interface to the slave PHY.

Scrambler/Descrambler Bypass.

descrambler of TP-PMD will be bypassed.

Loopback.

diagnostic loopback function.

Repeater.

mode. When this signal is low, the 82555 runs in DTE (adapter) mode.

Test.

In DTE (adapter) full duplex mode, if this input signal is high, the

If the Test Enable signal is active, this signal is used as the Test Input

In DTE (adapter) mode, this output operates in conjunction

In DTE (adapter) mode, if T4 Advance is active, the LISTAT _N

If Test Enable is asserted, this signal acts as the test

If Test Enable is asserted, this signal acts as the Test Clock

In DTE (adapter) mode, this pin enables the combo mode. This

When the LPBK signal is high, the 82555 will perform a

When the RPT signal is high, the 82555 functions in repeater

If the TESTEN signal is high, the 82555 enables the test ports.

Networking Silicon — 82555

In repeater mode, this pin configures the repeater to

In repeater mode, this signal represents the fifth bit for

In repeater mode, this signal represents the fourth bit for

In repeater mode, this signal represents the third bit for

In repeater mode, this signal represents the second bit for

In repeater mode, this signal represents the first bit for

In repeater mode, the Auto-Negotiation operates

If SCRMBY is high, the scrambler/

Datasheet 11

Page 16

82555 — Networking Silicon

3.9 Power and Gr ound Pins

Symbol Pin Type Name and Function

VCC 7, 9, 15, 17, 19, 27, 29, 31, 36, 38, 40, 45, 58, 62,

64, 66, 73, 75, 83, 88, 93, 98

VSS 3, 8, 10, 14, 16, 18, 20, 26, 28, 30, 32, 35, 37, 39,

41, 46, 49, 53, 57, 61, 63, 65, 67, 72, 74, 78, 84, 89,

91, 94, 99

I Power: +5 V ± 5%

I Ground: 0 V

12

Datasheet

Page 17

Networking Silicon — 82555

4.0 100BASE-TX Adapter Mode Operation

4.1 100BASE-TX Transmit Clock Generation

A 25 MHz crystal or a 25 MHz oscillator is used to drive the 82555’s X1 and X2 pins. The 82555

derives its internal transmit digital clocks from this crystal or oscillator input. The Transmit Clock

signal is a derivativ e of the 25 MHz internal clock. The accuracy of the external crystal or oscillator

must be ± 0.0005% (50 PPM).

4.2 100BASE-TX Transmit Blocks

The transmit subsection of the 82555 accepts nibble-wide data on the TXD[3:0] lines when TXEN

is asserted (high). The transmit subsection passes data unconditionally to the 4B/5B encoder as

long as TXEN is active.

The 4B/5B encoder accepts nibble-wide data (4 bits) from the MA C and compiles it into 5-bit-wide

parallel symbols. These symbols are scrambled and serialized into a 125 Mbps bit stream,

converted by the analog transmit driver into a MLT-3 waveform format, and transmitted onto the

Unshielded Twisted Pair (UTP) or Shielded Twisted Pair (STP) wire.

4.2.1 100BASE-TX 4B/5B Encoder

The 4B/5B encoder complies with the IEEE 802.3u 100BASE-TX standard . Fo ur bits are encoded

according to the transmit 4B/5B lookup table. The lookup table matches a 5-bit code to each 4-bit

code.

The table below illustrates the 4B/5B encoding scheme associated with the given symbol.

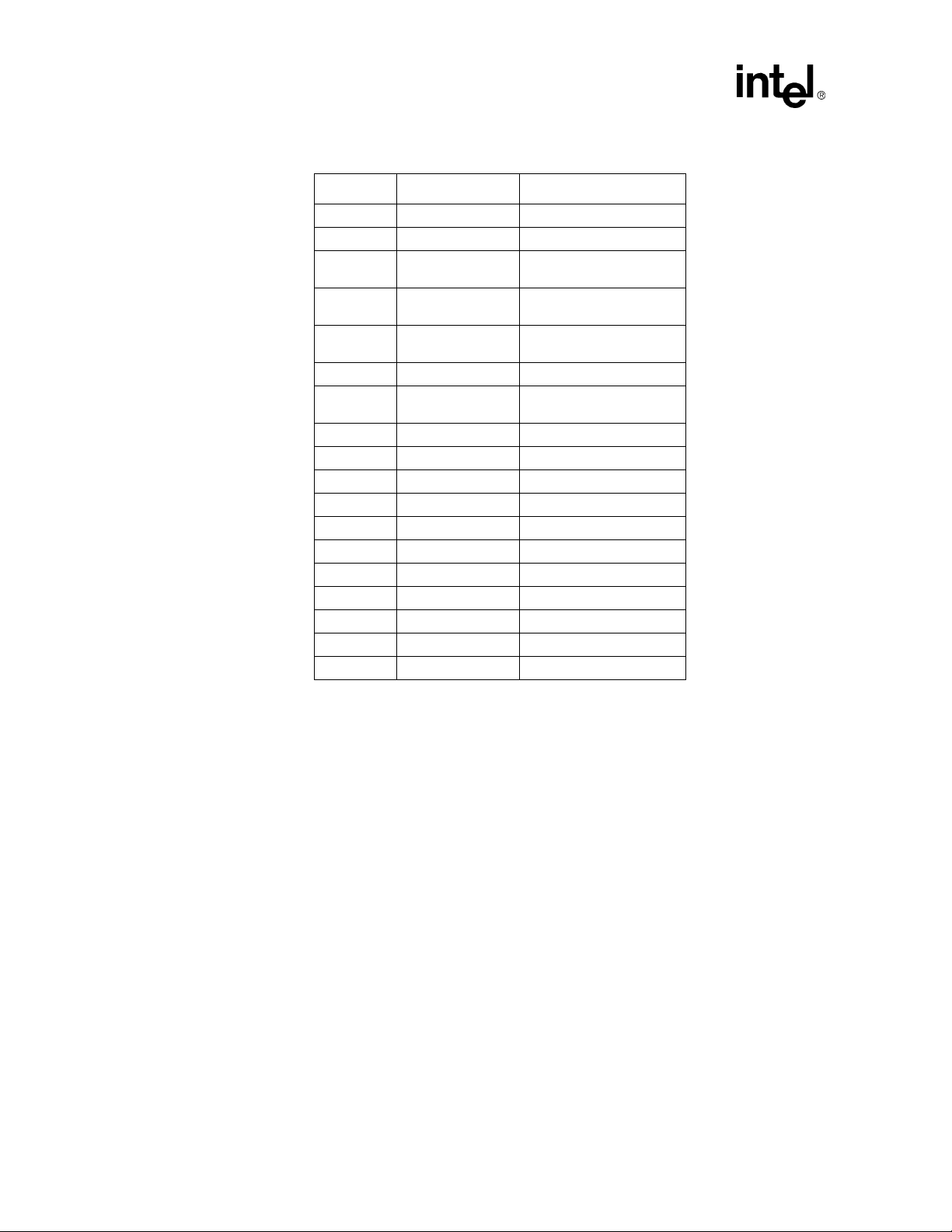

Symbol 5B Symbol Code 4B Nibble Code

0 11110 0000

1 01001 0001

2 10100 0010

3 10101 0011

4 01010 0100

5 01011 0101

6 01110 0110

7 01111 0111

8 10010 1000

9 10011 1001

A 10110 1010

B 10111 1011

C 11010 1100

D 11011 1101

Table 2. 4B/5B Encoder

Datasheet 13

Page 18

82555 — Networking Silicon

Table 2. 4B/5B Encoder

Symbol 5B Symbol Code 4B Nibble Code

E 11100 1110

F 11101 1111

I 11111

J 11000

K 10001

T 01101 1st End of Packet Symbol

R 00111

V 00000 INVALID

V 00001 INVALID

V 00010 INVALID

V 00011 INVALID

H 00100 INVALID

V 00101 INVALID

V 00110 INVALID

V 01000 INVALID

V 01100 INVALID

V 10000 Flow Control S

V 11001 INVALID

Inter Pack et Idle Symbol

(No 4B)

1st Start of Packet Symbol

0101

2nd Start of Packet Symbol

0101

2nd End of Packet Symbol

and Flow Control

4.2.2 100BASE-TX Scrambler and MLT-3 Encoder

Data is scrambled in 100BASE-TX in order to reduce electromagnetic emissions during long

transmissions of high-frequency data codes. The scrambler logic accepts 5 bits from the 4B/5B

encoder block and presents the scrambled data to the MLT-3 encoder. The 82555 implements the

11-bit stream cipher scrambler as adopted by the ANSI XT3T9.5 committee for UTP operation.

The cipher equation used is:

X[n] = X[n-11] + X[n-9] (mod 2)

The MLT-3 encoder receives the scrambled Non-Return to Zero (NRZ) data stream from the

scrambler and encodes the stream into MLT-3 for presentation to the driver. MLT-3 is similar to

NRZI coding, but three levels are output instead of two. There are three output levels: positive,

negative and zero. When an NRZ “0” arrives at the input of the encoder, the last output level is

14

Datasheet

Page 19

Networking Silicon — 82555

maintained (either positive, n eg ativ e o r zero). When an NR Z “1” arri v es at th e input of the encoder,

the output steps to the next level. The order of steps is negative-zero-positive-zero which continues

periodically. The figure below illustrates this process.

Clock

NRZ

NRZ1

MLT-3

1100 0110

1100 0110

1100 0110

Figure 6. NRZ to MLT-3 Encoding Diagram

4.2.3 100BASE-TX T ransmit Framing

The 82555 does not differentiate between the fields of the MAC frame containing preamble, start

of frame delimiter, data and Cyclic Redund anc y Check (CRC). When TXE N is asserted, the 82555

accepts data on the MII TXD[3:0] lines, encodes it, and sends it out onto the wire. The 82555

encodes the first byte of the preamble as the “JK” symbol, encodes all other pieces of data

according to the 4B/5B lookup table, and adds the “TR” code after the end of the packet (deassertion of TXEN). The 82555 scrambles and serializes the data into a 125 Mbps stream, encodes

it as ML T-3, and drives it onto the wire. If TXERR is asserted dur ing trans mission of v alid data, th e

82555 transmits an invalid “H” symbol.

Datasheet 15

Page 20

82555 — Networking Silicon

(V

TDP-VTDN

)

+1V

0V

-1V

40mA

I

TDP

20mA

0

40mA

20mA

0

I

TDN

t

t

t

4.2.4 Transmit Driver

The transmit differential lines are implemented with a digital slope controlled current driver that

meets the TP-PMD specifications. Current is sunk from the isolation transformer by the transmit

differential pins. The conceptual transmit differential waveform for 100 Mbps is illustrated in the

following figure.

Figure 7. Conceptual Transmit Differential Waveform

The magnetics module that is external to the 82555 converts I

by the TP-PMD specification. The same magnetics used for 100BASE-TX mod e should also work

in 10BASE-T mode. The following is a list of current magnetics modules available from several

vendors:

Vendor Model/Type 100BASE-TX 10BASE-T

Delta LF8200A Yes Yes

Pulse Engineering PE-68515 Yes Yes

Pulse Engineering H1012 Yes Yes

4.3 100BASE-TX Receive Blocks

The receive subsection of the 82555 accepts 100BASE-TX MLT-3 data on the receive differential

pair. Due to the advanced digital signal processing design techniques employed, the 82555 will

accurately receive valid data from Category 5 (C AT5) UTP and Type 1 STP cable of length well in

excess of 100 meters.

16

TDP

and I

to 2.0 Vpp, as required

TDN

Table 3. Magnetics Modules

Datasheet

Page 21

Networking Silicon — 82555

4.3.1 Adaptive Equalizer

The distorted MLT-3 signal at the end of the wire is restored by the equalizer. The equalizer

performs adaptation based on the shape of the received signal, equalizing the signal to meet

superior Data Dependent Jitter performance.

4.3.2 Receive Clock and Data Recovery

The clock recovery circuit uses advanced digital signal processing technology to compensate for

various signal jitter causes. The circuit recovers the 125 MHz clock and data and presents the data

to the MLT-3 decoder.

4.3.3 MLT-3 Decoder, Descrambler, and Receive Digital Section

The 82555 first decodes the MLT-3 data; afterwards, the descrambler reproduces the 5B symbols

originated in the transmitter. The descrambling is based on synchronization to the transmit 11-bit

Linear Feedback Shift Register (LFSR) during idle. The data is decoded at the 4B/5B decoder.

Once the 4B symbols are obtained, the 82555 outputs the receive data to the CSMA unit.

4.3.4 100BASE-TX Receive Framing

The 82555 does not differentiate between the fields of the MAC frame containing preamble, start

of frame delimiter, data and CRC. During 100 Mbps reception, the 82555 differentiates between

the idle condition ("L" symbols on the wire) and the preamble or start of frame delimiter. When

two non-consecutive bits are 0b within 10 bits (125 Mbps 5B data coding) the 82555 immediately

asserts the CRS signal. When the “JK” symbols (“11000, 10001”) are fully recognized, the 82555

asserts the RXDV signal and provides the data recei v ed on the MII RXD[3:0] to the Receiv e Clock.

If the “JK” symbol is not recognized (“false carrier sense”), the CRS signal is immediately deasserted and RXERR is asserted. Otherwise, the valid data is passed through th e MII until the

82555 finds the “TR” (“01101, 00111”) and idle symbols in order to de-assert TXDV and CRS.

4.3.5 100BASE-TX Receive Error Detect ion and Reporting

In 100BASE-TX mod e, the 825 55 can detect errors in recei v e d ata in a nu mber of ways. An y o f the

following conditions is considered an error:

Link integrity fails in the middle of frame reception.

•

The start of stream delimiter “JK” symbol is not fully detected after idle.

•

An invalid symbol is detected at the 4B/5B decoder.

•

Idle is detected in the middle of a frame (before “TR” is detected).

•

When any of the above error conditions occurs, the 82555 immediately asserts the Receive Error

signal to the MAC. The R XERR signal is asserted as lon g as the receive error condition persists on

the receive pair.

4.4 100BASE-TX Collision Detection

100BASE-TX collisions in half duplex mode only are detected similarly to 10BASE-T collision

detection, via simultaneous transmission and reception.

Datasheet 17

Page 22

82555 — Networking Silicon

4.5 100BASE-TX Link Integrity and Auto-Negotiation Solution

The 82555’s Auto-Negotiation function automatically configures the device to the technology,

media, and speed to operate with its link partner. Auto-Negotiation is widely described in IEEE

specification 802.3u, Clause 28. The 82555 supports 10BASE-T half duplex, 10BASE-T full

duplex, 100BASE-TX half duplex, and 100BASE-TX full duplex.

The 82555 has two Physical Medium Attachment (PMA) technologies with its link integrity

function, 10BASE-T and 100BASE-TX. The 82555 also has a special interface defined between

itself and a PHY-T4 in order to implement an Auto-Negotiation combination card.

4.5.1 Link Integrity

In 100BASE-TX, the link integrity function is determined by a stable signal status coming from the

TP-PMD block. Signal status is asserted when the PMD detects breaking squelch energy and the

right bit error rate according to the ANSI specification.

4.5.2 Auto-Negotiation

The 82555 fully supports IEEE 802.3u, Clause 28. In DTE (adapter) mode, the technology,

10BASE-T or 100BASE-TX, is determined by the Auto-Negotiation result . In repeat er mod e onl y,

this function can be disabled by pin configuration. If the T4ADV pin is active, the AutoNegotiation function will advertise and negotiate T4 technology.

Speed and duplex auto-select are functions of Auto-Negotiation. However, these parameters may

be manually configured via the MII management interface (MDI registers).

4.5.3 Combination Tx/T4 Auto-Negotiation Solution

The Auto-Negotiation function is available in both the 82555 and a PHY-T4. For these PHYs to

operate together, some arbitration at the PMA level is required and the Auto-Negotiation function

of one of the PHYs must be disabled. For this purpose, the 82555 is defined as the master; and the

PHY-T4, the slave. In combination mode, only the 82555’s Auto-Negotiation function is enabled

(the PHY-T4’s Auto-Negotiation is disabled).

In a combination boar d, a PHY-T4 is used on ly to supp ort 1 00BASE-T4 operation and the 82555 is

sued to support 100BASE-TX full or half duplex and 10BASE-T full or half duplex as determined

by the Auto-Negotiation or Parallel Detection function.

Combination mode is available only in DTE (adapter) mode with the following pin interface:

T4ADV (pin 54): Enables T4 technology in a PHY-TX Auto-Negotiation system.

•

SLVTRI (pin 52): Disables the PHY -T4.The PHY-T4 is enabled only if the T4 technology has

•

been detected by Auto-Negotiation or Parallel Detection.

LISTAT (pin 6): Indicates valid link on the PHY-T4. When SLVTRI is de-asserted, the PHY-

•

T4 should be active.

18

Datasheet

Page 23

Networking Silicon — 82555

3669

The figure below illustrates an 82557/82555/PHY-T4 s olution in a block diagram.

T4

adv

82555

PCI BUS

82557

fdx_n

MII

PHY-T4

Figure 8. Combination Card Example

4.6 Auto 10/100 Mbps Speed Selection

The MAC may either allow the 82555 to automatically select its operating speed or force the 82555

into 10 Mbps or 100 Mbps mode. The Management Data Interface (MDI) can control the 82555

speed mode.

The 82555 autoselect function determines the operation speed of the media based on the link

integrity pulses it receives. If no Fast Link Pulses (FLPs) are detected and Normal Link Pulses

(NLPs) are detected, the 82555 defaults to 10 Mbps operation. If the 8255 5 detects a speed chang e,

it dynamically changes its transmit clock and receive clock frequencies to the appropriate value.

This change takes a maximum of five milliseconds.

listat_n

slave_tri

Common

Magnetics

4.7 Adapter Mode Addresses

In DTE (adapter) mode, the 82555 supports addresses 0, 1, 2, and 3 through the pins PHYA1 and

PHYA0. Four addresses are sufficient in the case of a combination adapter having three PHYs. For

switch applications, the T4ADV signal should be de-asserted to allow all 32 addresses to be

available in repeater mode.

Datasheet 19

Page 24

82555 — Networking Silicon

20

Datasheet

Page 25

Networking Silicon — 82555

5.0 10BASE-T Functionality in Adapter Mode

5.1 10BASE-T Transmit Clock Generation

The 20 MHz and 10 MHz clocks needed for 10B A SE-T are synthesized fr om th e external 25 MHz

crystal or oscillator. The 82555 provides the transmit clock and receive clock to the MAC at 2.5

MHz.

5.2 10BASE-T Transmit Blocks

5.2.1 10BASE-T Manchester Encoder

After the 2.5 MHz clocked data is serialized in a 10 Mbps serial stream, the 20 MHz clock

performs the Manchester encoding. The Manchester code always has a mid-bi t trans ition. If the

value is 1b then the transition is from low to high. If the value is 0b then the transition is from high

to low. The boundary transition occurs only when the data changes from bit to bit. For example, if

the value is 10b, then the change is from high to low; if 01b, then the change is from low to high.

5.2.2 10BASE-T Driver and Filter

Since 10BASE-T and 100BASE-TX have different filtration needs, both filters are implemented

inside the chip. This allows the two technologies to share the same magnetics. The 82555 suppo rts

both technologies through one pair of transmit differential pins and by externally sharing the same

magnetics.

In 10 Mbps mode, the 82555 begins transmitting the serial Manchester bit stream within 3 bit times

(300 nanoseconds) after the MAC asserts TXEN. In 10 Mbps mode the line drivers use a predistortion algorithm to improve jitter tolerance. The line drivers reduce their drive level during the

second half of “wide” (100 ns) Manchester pulses and maintain a full drive level during all narrow

(50 ns) pulses and the first half of the wide pulses. This reduces line overcharging during wide

pulses, a major source of jitter.

5.3 10BASE-T Receive Blocks

5.3.1 10BASE-T Manchester Decoder

The 82555 performs Manchester decoding and timing recovery when in 10 Mbps mode. The

Manchester encoded data stream is decoded from the receive differential pair to separate Receive

Clock and Receive Data lines from the differential signal. This data is transferred to the controller

at 2.5 MHz/nibble through the MII. The hig h-performance circuitry of the 82555 e xceeds the I EEE

802.3 jitter requirements.

5.3.2 10BASE-T Twisted Pair Ethernet (TPE) Receive Buffer and Filter

In 10 Mbps mode, data is expected to be received on the receive differential pair after passing

through isolation transformers. The filter is implemented inside the 82555 for supporting single

magnetics that are shared with the 100BASE-TX side. The input differential voltage range for the

Datasheet 21

Page 26

82555 — Networking Silicon

Twisted Pair Ethernet (TPE) receiver is greater than 585 mV and less than 3.1 V. The TPE receive

buffer distinguishes valid receive data, link test pulses, and the idle condition, according to the

requirements of the 10BASE-T standard.

The following line activity is determined to be inactive and is rejected:

Differential pulses of peak magnitude less than 300 mV.

•

Continuous sinusoids with a differential amplitude less than 6.2 Vpp and frequency less than 2

•

MHz.

Sine waves of a single cycle duration starting with 0° or 180° phase that have a differential

•

amplitude less than 6.2 V

These single-cycle sine waves are discarded only if they are preceded by 4 bit times (400

nanoseconds) of silence.

All other activity is determined to be either data, link test pulses, Auto-Negotiation fast link pulses,

or the idle condition. When activity is detected, the carrier sense signal is asserted to the MAC.

and a frequency of at least 2 MHz and not more than 16 MHz.

pp

5.3.3 10BASE-T Error Detection and Reporting

In 10 Mbps mode, the 82555 can detect errors in the receive data. The following condition is

considered an error:

The receive pair’s voltage level drops to the idle state during reception bef ore the end-of-f rame

bit is detected (250 nanoseconds without mid-bit transitions).

5.4 10BASE-T Collision Detection

Collision detection in 10 Mbps mode is indicated by simultaneous transmission and reception. If

the 82555 detects this condition, it asserts a collision indication to the controller.

5.5 10BASE-T Link Integrity

The link integrity in 10 Mbps works with link pulses. The 82555 senses and differentiates those

link pulses from fast link pulses and from 100BASE-TX idles. In the first and last case, the 82555

activates parallel detection of the respecti ve technology; and in the second case, Auto-Negotiation.

The 10 Mbps link pulses or normal link pulses are driven in the transmit differential pair line but

are 100 ns wide and ha ve l e v els fr om 0 V to 5 V. The link beat pulse i s also used t o det ermine if the

receive pair polarity is reversed. If it is, the polarity is corrected internally.

5.6 10BASE-T Jabber Control Function

The 82555 contains a jabber control function that inhibits transmission after a specified time

window when enabled. In 10 Mbps mod e, the jabber timer is set to a v alue between 26 .2 ms and 39

ms. If the 82555 detects continuous transmissi on that is greater than this time period, it prevents

further transmissions from onto the wire until it detects that the MAC transmit enable signal has

been inactive for at least 314 ms.

22

Datasheet

Page 27

5.7 10BASE-T Full Duplex

The 82555 supports 10 Mbps full duplex by disabling the collision function, the squelch test, and

the carrier sense transmit function. This allows the 82555 to transmit and receive simultaneously,

achieving up to 20 Mbps of network bandwidth. The configuration can be achieved through AutoNegotiation. Full duplex should only be used in point-to-point connections (no shared media).

Flow control is always disabled.

Networking Silicon — 82555

Datasheet 23

Page 28

82555 — Networking Silicon

24

Datasheet

Page 29

6.0 Repeater Mode

The 82555 has a compete set of repeater features making it the ideal PHY for Class 1 (MII)

repeater designs. The 82555 works in repeater mode when the RPT signal (pin 50) is high. The

FRC100 signal (pin 51) determines which type of repeater is supported, either 100BASE-TX or

10BASE-T.

6.1 Special Repeater Features

Special features of the 82555 repeater mode operation include:

Fully IEEE compliant with automatic carrier disconnect.

•

The 82555 will disconnect when it receives false carrier detects. Either a long series of valid

idle symbols or a valid “JK” pair will cause it to reconnect.

Narrow 14 mm analog side that enables tight packing of multiple PHYs, which is ideal for 8,

•

12, 18, 24, or even 32 port repeater designs.

Very low emissions and high noise immunity.

•

32 configurable addresses through five address lines.

•

Auto-Negotiation di sab l e functi on.

•

In repeater mode, the Auto-Negotiation fu ncti on is n ot us ed f or configuration purposes. When

Auto-Negotiation is enabled in repeater mode, the MII management will be able to obtain data

from the MDI Auto-Negotiation register about the remote partner. This is a feature for hub

management allowing a 10/100 Mbps r epeater d esign to autom atically detect wheth er o r n ot it

can operate at 100 Mbps. If the ANDIS signal is de-asserted, the Auto-Negotiation feature will

be disabled.

Networking Silicon — 82555

Forced 10 Mbps or 100 Mbps operation (allows for a 10/100 repeater design).

•

Receive port enable function.

•

The PORTEN signal is a glueless interface to the Repeater Interface Controller (RIC). When

the PORTEN signal is low, all receive signals are tri-stated, except CRS and COL.

26-bit PHY budget for round trip.

•

The total PHY bit budget is 8 bits from the MII to the wire and 18 bits from the wire to the

MII.

Static 2.5 MHz (10BASE-T) or 25 MHz (100BA SE-TX) clock input for repeater designs

•

(issued by RIC).

The 82555 clock source is fixed between Resets. There is one input, either 2.5 MHz or 25

MHz, as indicated by the level at the FRC100 pin. All clocks have a common source

generation so the that PPM is 0 between them (X1, 2.5 MHz and 25 MHz).

DTE (adapter) features not available in repeater mode: full duplex, flow control, and the

•

combination Auto-Negotiation interface for T4.

6.2 Connectivity

A 25 MHz buffered oscillator can provide the clock to all of the 82555 devices. A 2.5 MHz (10

Mbps) or a 25 MHz (100 Mbps) signal is required to clock the RIC and the TXC signal in the

PHYs. TXD[3:0], TXERR, RXC, RXD[3: 0], RXD V, and RXERR are single -bus (s hortened) fo r all

Datasheet 25

Page 30

82555 — Networking Silicon

PHYs connected to the RIC. Signals TXEN, CRS, and PORTEN are connected from each of the

82555 devices to the specified RIC pin. The figure below illustrates an example of multiple 82555s

connected to a 25 MHz (or 2.5 MHz) oscillator.

2.5/25 MHz (10/100)

RIC

CLK

2.5/25 MHz (10/100)

TXCLK

PHY1

X1

TXCLK TXCLK

PHY2

X1 X1

PHY3

PC-3691

Figure 9. Clock Signal Example

26

Datasheet

Page 31

7.0 Management Data Interface

The 82555 provides status and accepts management information through the Management Data

Interface (MDI). This is accomplished through read and write operations to various registers in

accordance with the IEEE 802.3u MII specification.

7.1 MDI Frame Structure

Data read from or written to a particular register is called a management frame and is sent serially

over the MDIO pin synchronously to the MDC signal. Read and write cycles are viewed from the

perspective of the controller. Thus, the controller always drives the start, opcode, PHY address, and

register address onto the MDIO pin. For read cycles, the controller drives the transition bits and

data onto the MDIO pin; for write cycles, to the 82555. The controller dri v es addresses and data on

the falling edge of the MDC signal, and the 82555 latches the data on the rising edge of the MDC

signal. The following list defines protocol terms:

Networking Silicon — 82555

PREAMBLE

ST

OP

PHYAD

REGAD

TA

DATA

At the beginning of each transaction, the controller send a sequence of 32

contiguous logic one bits on the MDIO pi n with corres pon di ng cycles on the MDC

pin for synchronization by the 82555.

This field contains the value of 01b indicating the start of a frame.

This is a 2-bit field containing one of the follo wing two operation codes: 10 b (read)

or 01b (write).

This field is a 5-bit address of th e 8 2555 device that provides su ppo rt for 32 unique

PHY addresses. The controller drives the value written into the PHYAD portion of

the MDI register in this field.

This field is a 5-bit address of a specific register within the 82555. This provides

support for 32 unique registers. The desired register address is specified by the

value written to the MDI register.

This field contains a 2-bit value specifying the period during a read cycle that no

device may actively drive the MDIO signal. During a read transaction, the 82555

should not drive the MDIO signal in the first bit time; however, it will drive a 0b in

the second bit time. During a write transaction, the controller drives the pattern of

10b to fill this time.

This field contains 16 bits of data driven by the 82555 on a read transaction or by

the controller on a write transactions. This data is either control or status parameters

passed between the controller and the 82555.

IDLE

During the idle state, the MDIO signal is in a high impedance state. The MDIO

driver is disabled, and the 82555 will pull the MDIO signal high to a logic 1.

Datasheet 27

Page 32

82555 — Networking Silicon

The 82555 address can be configu red t o fou r 0 th rough 3 in DTE (adapter) mode and 0 through 31

in repeater mode. A special functions for switches allows 32 addresses to exist in repeater mode.

The management frame structure is as follows:

T ransition ST OP PHYAD REGAD TA D ATA

READ <01> <10> <AAAAA> <RRRRR> <

WRITE <01> <01> <AAAAA> <RRRRR> <10> 16 bits

7.2 MDI Registers

MDI registers are described in the following subsections and the acronyms me ntioned in the

registers are defined as follows:

SC - Self Cleared.

RO -Read Only.

P- External pin affects 82555 register content.

LL - Latch Low.

LH - Latch High.

X

0> 16 bits

7.2.1 MDI Regis t ers 0 - 7

7.2.1.1 Register 0: Control Register Bit De finitions

Bit(s) Name Description Default R/W

15 Reset This bit sets the status and control register of the 82555

14 Loopback This bit enables loopback of transmit data nibbles from

13 Speed Selection This bit controls speed when Auto-Negotiation is disabled

12 Auto-Negotiation

Enable

to their default states and is self-clearing. The PHY

returns a value of 1b until the reset process has

completed and accepts a read or write transaction.

1 = PHY Reset

0 = Normal operation

the TXD[3:0] signals to the receive data path. The

82555’s receive circuitry is isolated from the network.

Note that this may cause the descrambler to lose

synchronization and produce 560 nanoseconds of “dead

time.”

Note also that the loopback configuration bit takes priority

over the Loopback MDI bit.

1 = Loopback enabled

0 = Loopback disabled (normal operation)

and is valid on read when Auto-Negotiation is disabled.

1 = 100 Mbps

0 = 10 Mbps

This bit enables Auto-Negotiation. Bits 13 and 8, Speed

Selection and Duplex Mode, respectively, are ignored

when Auto-Negotiation is enabled.

1 = Auto-Negotiation enabled

0 = Auto-Negotiation disabled

0RW

SC

0RW

P

1RW

P

1RW

28

Datasheet

Page 33

Networking Silicon — 82555

Bit(s) Name Description Default R/W

11 Power-Down This bit sets the 82555 into a low power mode.

1 = Power-down enabled

0 = Power-down disabled (normal operation)

10 Isolate This bit allows the 82555 to electrically isolate the Media

9 Restart Auto-

Negotiation

8 Duplex Mode This bit controls the duplex mode when Auto-Negotiation

7 Collision Test This bit will force a collision in response to the assertion

6:0 Reserved T hese bits are reser ved and should be set to 0000000b. 0 RW

Independent Interface. When the MII is isolated, the

82555 does not respond to TXD[3:0], TXEN, and TXERR

input signals. Also, the 82555 presents high impedance

on its TXC, RXC, RXDV, RXERR, RXD[3:0], COL, and

CRS output signals. In the TX mode, the 82555 responds

to management transactions.

1 = Electrically isolate MII

0 = Normal operation

This bit restarts the Auto-Negotiation process and is selfclearing.

1 = Restart Auto-Negotiation process

0 = Normal operation

is disabled. If the 82555 reports that it is only able to

operate in one duplex mode, the value of this bit shall

correspond to the mode which the 82555 can operate.

When the 82555 is placed in Loopback mode, the

behavior of the PHY shall not be affected by the status of

this bit, bit 8.

1 = Full Duplex

0 = Half Duplex

of the transmit enable signal.

1 = Force COL

0 = Do not force COL

0RW

0RW

0RW

SC

0RW

0RW

7.2.1.2 Register 1: Status Register Bit Definitions

Bit(s) Name Description Default R/W

15 100BASE-T4 1 = 82555 able to perf orm 100BASE-T4

0 = 82555 not able to perform 100BASE-T4

14 100BASE-TX Full

Duplex

13 100 Mbps Half

Duplex

12 10 Mbps Full

Duplex

11 10 Mbps Half

Duplex

10:7 Reserved These bits are reserved and should be set to 0000b. 0 RO

1 = 82555 able to perform full duplex 100BASE-TX

0 = 82555 not able to perform full duplex in repeater

mode

1 = 82555 able to perform half duplex 100BASE-TX

0 = 82555 not able to perform 100BASE-TX

1 = 82555 able to operate at 10 Mbps in full duplex

mode

0 = 82555 not able to operate in full duplex mode in

10BASE-T

1 = 82555 able to operate at 10 Mbps in half duplex

mode

0 = 82555 not able to operate in 10BASE-T

Datasheet 29

-- RO

P

-- RO

P

-- RO

P

-- RO

P

-- RO

P

Page 34

82555 — Networking Silicon

Bit(s) Name Description Default R/W

6 Management

Frames Preamble

Suppression

5 Auto-Negotiation

Complete

4 Remote Fault 1 = Remote fault condition detected

3 Auto-Negotiation

Ability

2 Link Status 1 = Valid link has been established

1 Jabber Detect 1 = Jabber condition detected

0 Extended

Capability

1 = 82555 will accept management frames with

preamble suppressed

0 = 82555 will not accept management frames with

preamble suppressed

1 = Auto-Negotiation process completed

0 = Auto-Negotiation process has not completed

0 = No remote fault condition detected

1 = 82555 is able to perform Auto-Negotiation

0 = 82555 is in repeater mode and Auto-Negotiation

Disable pin is high

0 = Invalid link detected

0 = No jabber condition detected

1 = Extended register capabilities enabled

0 = No extended register capabilities

-- RO

0RO

0RO

P

1RO

0RO

LL

SC

0RO

LH

SC

1RO

7.2.1.3 Register 2: 82555 Identifier Register Bit Definitions

Bit(s) Name Description Default R/W

15:0 82555 ID (high

byte)

Value: 02A8H -- RO

7.2.1.4 Register 3: 82555 Identifier Register Bit Definitions

Bit(s) Name Description Default R/W

15:0 82555 ID (low

byte)

Value: 0150H -- RO

7.2.1.5 Register 4: Auto-Negotiation Advertisement Register Bit Definitions

Bit(s) Name Description Default R/W

15 Next Page Constant 0 = Transmitting primary capability data

14 Reserved This bit is reserved and should be set to 0b. 0 RO

13 Remote Fault 1 = Indicate link partner’s remote fault

12:5 Technolog y Ability

Field

4:0 Selector Field The Selector Field is a 5-bit field identifying the type of

page

0 = No remote fault

Technology Ability Field is an 8-bit field containing

information indicating supported technologies specific

to the selector field value.

message to be sent via Auto-Negotiation. This field is

read only in the 82555 and contains a value of

00001b, IEEE Standard 802.3.

-- RO

0RW

-- RW

00001 RO

30

Datasheet

Page 35

Networking Silicon — 82555

7.2.1.6 Register 5: Auto-Negotiation Link Part ner Ability Register Bit Definitions

Bit(s) Name Description Default R/W

15 Next Page This bit reflects the 82555’s link partner’s Auto-

14 Acknowledge This bit is used to indicate that the 82555 has

13 Remote Fault This bit reflects the 82555’s link partner’s Auto-

12:5 T echnology Ability

Field

4:0 S elector Field This bit reflects the 82555’s link partner’s Auto-

Negotiation ability.

successfully received its link partner’s AutoNegotiation advertising ability.

Negotiation ability.

This bit reflects the 82555’s link partner’s Auto-

Negotiation ability.

Negotiation ability.

-- RO

-- RO

-- RO

-- RO

-- RO

7.2.1.7 Register 6: Auto-Negotiation Expansion Register Bit Definitions

Bit(s) Name Description Default R/W

15:5 Reserved These bits are reserved and should be set to a

4 Parallel Detection

Fault

3 Link Partner Next

page Able

2 Next Page Able 1 = Local drive is Next Page able

1 Page Received 1 = New Page received

0 Link Partner Auto-

Negotiation Able

constant 0.

1 = Fault detected via parallel detection (multiple link

fault occurred)

0 = No fault detected via parallel detection

This bit will self-clear on read

1 = Link Partner is Next Page able

0 = Link Partner is not Next Page able

0 = Local drive is not Next Page able

0 = New Page not received

This bit will self-clear on read.

1 = Link Partner is Auto-Negotiation able

0 = Link Partner is not Auto-Negotiation able

0RO

0RO

SC

LH

0RO

0RO

0RO

SC

LH

0RO

7.2.2 MDI Registers 8 - 15

Registers eight through fifteen are reserved for IEEE.

7.2.3 MDI Registers 16 - 31

Register numbers 16, 17, 20, 21, 22, 23, 24, 25, and 27 are described in the following subsections.

Datasheet 31

Page 36

82555 — Networking Silicon

7.2.3.1 Register 16: 82555 Status and Control Register Bit Definitions

Bit(s) Name Description Default R/W

15 Flow Control This bit enables PHY Base (Bay Technologies) flow

14 Reserved These bits are reserved and should be set to 0b 0 RW

13 Carrier Sense

Disconnect

Control

12 Transmit Flow

Control Disable

11 Receive De-

Serializer In-Sync

Indication

10 100BASE-TX

Power-Down

9 10BASE-T

Power-Down

8 Polarity This bit indicates 10BASE-T polarity.

7:3 Reserved These bits are reserved and should be set to a

2 T4 This bit indicates the Auto-Negotiation result.

1 Speed This bit indicates the Auto-Negotiation result.

0 Duplex Mode This bit indicates the Auto-Negotiation result.

control.

1 = Enable PHY Base flow control

0 = Disable PHY Base flow control

This bit enables the disconnect function.

1 = Disconnect function enabled (default in DTE)

0 = Disconnect function disabled (default in repeater)

This bit enables Transmit Flow Control

1 = Transmit Flow Control enabled

0 = Transmit Flow Control disabled

This bit indicates status of the 100BASE-TX Receive

De-Serializer In-Sync.

This bit indicates the power state of 100BASE-TX

82555.

1 = Power-down

0 = Normal operation

This bit indicates the power state of 10BASE-TX

82555.

1 = Power-Down

0 = Normal operation

1 = Reverse polarity

0 = Normal polarity

constant 0.

1 = 100BASE-T4

0 = No 100BASE-T4

1 = 100 Mbps

0 = 10 Mbps

1 = Full Duplex

0 = Half Duplex

0RW

0 (DTE

1 (Rptr)

00000 RO

RW

0RW

-- RO

-- RO

-- RO

-- RO

-- RO

-- RO

-- RO

7.2.3.2 Register 17: 82555 Special Control Bit Defini tions

Bit(s) Name Description Default R/W

15 Scrambler By-

pass

14 By-pass 4B/5B 1 = 4 bit to 5 bit by-pass

32

1 = By-pass Scrambler

0 = Normal operations

0 = Normal operation

Datasheet

0RW

0RW

Page 37

Networking Silicon — 82555

Bit(s) Name Description Default R/W

13 Force Transmit H-

Pattern

12 Force 34 Transmit

Pattern

11 Good Link 1 = 100BASE-TX link good

10 Reserved T his bit is reserved and should be set to 0b. 0 RW

9 Transmit Carrier

Sense Disable

8 Disable Dynamic

Power-Down

7 Auto-Negotiation

Loopback

6 MDI Tri-State 1 = MDI Tri-state (transmit driver tri-states)

5 Filter By-pass 1 = By-pass filter

4 Auto Polarity

Disable

3 Squelch Disable 1 = 10BASE-T squelch test disable

2 Extended

Squelch

1 Link Integrity

Disable

0 Jabber Function

Disable

1 = Force transmit H-pattern

0 = Normal operation

1 = Force 34 transmit pattern

0 = Normal operation

0 = Normal operation

1 = Transmit Carrier Sense disabled

0 = Transmit Carrier Sense enabled

1 = Dynamic Power-Down disabled

0 = Dynamic Power-Down enabled (normal)

1 = Auto-Negotiation loopback

0 = Auto-Negotiation normal mode

0 = Normal operation

0 = Normal filter operation

1 = Auto Polarity disabled

0 = Normal polarity operation

0 = Normal squelch operation

1 = 10BASE-T Extended Squelch control enabled

0 = 10BASE-T Extended Squelch control disabled

1 = Link disabled

0 = Normal Link Integrity operation

1 = Jabber disabled

0 = Normal Jabber operation

0RW

0RW

0RW

0RW

0RW

0RW

0RW

0RW

0RW

0RW

-- RW

0RW

0RW

7.2.3.3 Register 20: 100BASE-TX Receive Disconnect Counter Bit Definitions

Bit(s) Name Description Default R/W

15:0 Disconnect Event This field contains a 16-bit counter that increments for

each disconnect event. The counter stops when full

(and does not roll over) and self-clears on read

In repeater mode, a frame that starts without “JK” is a

disconnect event.

-- RO

SC

7.2.3.4 Register 21: 100BASE-TX Receive Error Frame Counter Bit Definitions

Bit(s) Name Description Default R/W

15:0 Receive Error

Frame

Datasheet 33

This field contains a 16-bit counter that increments

once per frame for any receive error condition (such

as a symbol error or premature end of frame) in that

frame. The counter stops when full (and does not roll

over) and self-clears on read.

-- RO

SC

Page 38

82555 — Networking Silicon

7.2.3.5 Register 22: Receive Symbol Error Counter Bit Definitions

Bit(s) Name Description Default R/W

15:0 Symbol Error

Counter

This field contains a 16-bit counter that increments f or

each symbol error. The counter stops when full (and

does not roll over) and self-clears on read.

In a frame with a bad symbol, each sequential six bad

symbols count as one.

-- RO

SC

7.2.3.6 Register 23: 100BASE-TX Receive Premature End of Frame Error Counter Bit Definitions

Bit(s) Name Description Default R/W

15:0 Premature End of

Frame

This field contains a 16-bit counter that increments f or

each premature end of frame event. The counter

stops when full (and does not roll over) and self -clears

on read.

A frame without a “TR” at the end is considered a

premature end of frame event.

-- RO

SC

7.2.3.7 Register 24: 10BASE-T Receive End of Frame Error Counter Bit Definitions

Bit(s) Name Description Default R/W

15:0 End of Frame

Counter

This is a 16-bit counter that increments for each end

of frame error event. The counter stops when full (and

does not roll over) and self-clears on read.

-- RO

7.2.3.8 Register 25: 10BASE-T Transmit Jabber Detect Counter Bit Definitions

Bit(s) Name Description Default R/W

15:0 Jabber Detect

Counter

This is a 16-bit counter that increments for each

jabber detection event. The counter stops when full

(and does not roll over) and self-clears on read.

-- RO

7.2.3.9 Register 27: 82555 Special Control Bit Defini tions

Bit(s) Name Description Default R/W

15:3 Reserved These bits are reserved and should be set to 0b. 0 RW

2:0 LED Switch

Control

Value

000

001

010

011

100

101

110

111

ACTLED

Activity

Speed

Speed

Activity

Off

Off

On

On

LILED

Link

Collision

Link

Collision

Off

On

Off

On

000 RW

SC

SC

34

Datasheet

Page 39

8.0 Auto-Negotiation Functionality

The 82555 supports Auto-Negotiation. Auto-Negotiation is a scheme of auto-configuration

designed to manage interoperability in multifu nctional LAN environments. It allows two stations

with “N” different modes of communication to establish a common mode of operation. At powerup, Auto-Negotiation automatically establishes a link that takes advantage of an Auto-Negotiation

capable device. An Auto-Negotiation capable device can detect and automatically configure its

port to take maximum adv antage of comm on mod es of operati on with out user inter v entio n or prior

knowledge by either station. The possible common modes of operation are: 100BASE-TX,

100BASE-TX Full Duplex, 100BASE-T4, 10BASE-T, and 10BASE-T Full Duplex.

8.1 Description

Auto-Negotiation selects the fastest operating mode (in other words, the highest common

denominator) available to hardware at both ends of the cable. A PHY’s capability is encoded by

bursts of link pulses called Fast Link Pulses (FLPs). Connection is established by FLP exchange