Page 1

Page 2

THE 2920 ANALOG

SIGNAL

PROCESSOR

DESIGN

HANDBOOK

AUGUST 1980

Page 3

Intel Corporation makes no warranty

for

the use of its products and assumes no responsibility for any errors which

may appear in this document nor does it make a commitment

to

update the information contained herein.

Intel software products are copyrighted

by

and shall remain the property

of

Intel Corporation. Use, duplication or

disclosure is subject

to

restrictions stated in Intel's software license, or

as

defined

in

ASPR

7-104.9

(a)

(9).

Intel Cor-

poration assumes no responsibility for the use

of

any circuitry other than circuitry embodied in

an

Intel product. No

other circuit patent licenses are implied.

No part

of

this

document may be copied

or

reproduced in any form or by any means

without

the prior written consent

of

Intel Corporation.

The following are trademarks

of

Intel Corporation and may only be used to identify Intel products:

BXP

Intelevision

CREDIT Intellec

i iSBC

ICE iSBX

ICS

Library Manager

im

MCS

Insite

Megachassis

Intel Micromap

MULTIBUS·

MULTIMODULE

PROMPT

Promware

RMX

UPI

,",Scope

and the combinations

of

ICE, iCS, iSBC, MCS or

RMX

and a numerical suffix.

MDS is

an

ordering code only and is not used as a product name or trademark.

MDS®

is a registered trademark of

Mohawk Data Sciences Corporation.

"MULTIBUS is a patented Intel bus.

Additional copies

of

this manual or other Intel literature may

be

obtained from:

Literature Department

Intel Corporation

3065 Bowers Avenue

Santa Clara, CA

95051

© INTELCORPORATION,1980 AFN-01300A-1

Page 4

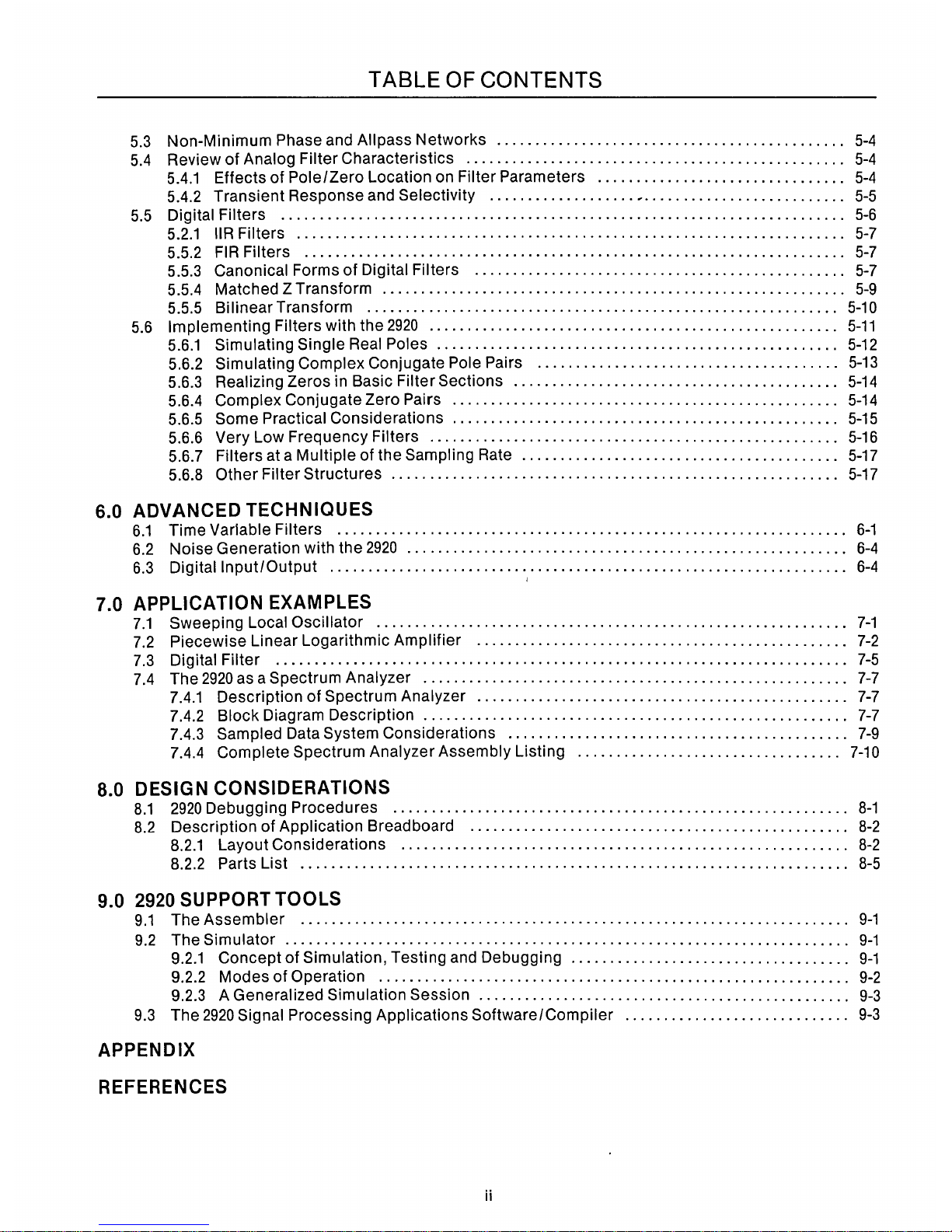

TABLE OF

CONTENTS

1.0 INTRODUCTION AND TERMINOLOGY

1.1

The

2920

Signal Processor

.............................................................

1-1

1.2

Typical

2920

Design Sequence

.........................................................

1-2

1.3

Benefits

of

the

2920

Signal Processor Approach

.........................................

1-4

1.3.1

2920

Device Benefits

............................................................

1-4

1.3.2 Deveiopment-Support-Tool Benefits

.............................................

1-4

2.0 SAM PLED DATA SYSTEMS

2.1

Elements of a Digital Sampled Data System

.............................................

2-1

2.2

Effects of Sampling

...................................................................

2-2

2.2.1

Aliasing Noise

..................................................................

2-3

2.2.2

Signal Reconstruction Distortion

.................................................

2-4

2.2.3

Jitter

Noise

.....................................................................

2-5

2.2.4

Quantization Noise

..............................................................

2-6

3.0 THE 2920 SIGNAL PROCESSOR

3.1

Device Operation

.................

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

..

3-1

3.1.1

Overview of the

2920

.............................................................

3-1

3.1.2

Analog Operations

..............................................................

3-2

3.1.3

DigitalOperations

...............................................................

3-2

3.2

A Closer Look at the Functional Elements

...............................................

3-2

3.2.1

EPROM

Section

.................................................................

3-2

3.2.2

Arithmetic Unit and Memory

.....................................................

3-3

3.2.3

The Analog Section

.............................................................

3-7

3.3

Basic

2920

Performance Parameters and Limits

........................................

3-10

4.0 BUILDING BLOCK

FUNCTIONS-FOUNDATION

OF

DESIGN

4.1

Arithmetic Building Blocks

.............................................................

4-1

4.1.1

Elementary Arithmetic

...........................................................

4-1

4.1.2

Multiplication by a Constant

......................................................

4-1

4.1.3

Multiplication by a Variable

......................................................

4-3

4.1.4

Division by a Variable

............................................................

4-5

4.2

Realizing Relaxation Oscillators

........................................................

4-6

4.2.1

Reset Technique for Relaxation Oscillator

........................................

4-6

4.2.2

Overflow Technique for Relaxation Oscillator

.....................................

4-7

4.3

Voltage Controlled Oscillators (VCO's)

.................................................

4-7

4.4

Oscillators Based on Unstable Second-Order Section

...................................

4-8

4.5

Gain Controlled Oscillator

.............................................................

4-8

4.6

Realization of Non-Linear Functions

....................................................

4-9

4.6.1

Simulation of Rectifiers

..........................................................

4-9

4.6.2

Simulation of Limiters

...........................................................

4-9

5.0 SUMMARY

OF

FILTER CHARACTERISTICS

5.1

Characteristics of

"Ideal"

Filters

.......................................................

5-1

5.1.1

The Rectangular Filter

...........................................................

5-1

5.2

Minimum Phase Filters

................................................................

5-2

5.2.1

Butterworth Filters

..............................................................

5-2

5.2.2

Chebyshev Filters

...............................................................

5-2

5.2.3

Elliptic Function Filters

..........................................................

5-2

5.2.4

Bessel and Gaussian Filters

.....................................................

5-3

5.2.5

Transitional Gaussianl Butterworth Filters

........................................

5-3

5.2.6

Other Minimum Phase Filters

....................................................

5-3

5.2.7

Comparison of Minimum Phase Filters

...............................•............

5-3

Page 5

TABLE OF CONTENTS

5.3

Non-Minimum Phase and Allpass Networks

.............................................

5-4

5.4

Review

of

Analog Filter Characteristics

.................................................

5-4

5.4.1

Effects

of

Pole/Zero

Location on Filter Parameters

................................

5-4

5.4.2 Transient Response and Selectivity

...................

,

..........................

5-5

5.5

Digital Filters

.........................................................................

5-6

5.2.1

IIR

Filters

.......................................................................

5-7

5.5.2

FIR

Filters

......................................................................

5-7

5.5.3 Canonical Forms

of

Digital Filters

................................................

5-7

5.5.4 Matched Z Transform

............................................................

5-9

5.5.5

Bi

linear Transform

.............................................................

5-10

5.6

Implementing Filters with the

2920

.....................................................

5-11

5.6.1

Simulating Single Real Poles

....................................................

5-12

5.6.2 Simulating Complex Conjugate Pole Pairs

.......................................

5-13

5.6.3 Realizing Zeros in Basic Filter Sections

..........................................

5-14

5.6.4 Complex Conjugate Zero Pairs

..................................................

5-14

5.6.5 Some Practical Considerations

..................................................

5-15

5.6.6 Very Low Frequency Filters

.....................................................

5-16

5.6.7 Filters at a Multiple of the Sampling Rate

.........................................

5-17

5.6.8 Other Filter Structures

..........................................................

5-17

6.0 ADVANCED

TECHNIQUES

6.1

Time VarIable Filters

..................................................................

6-1

6.2

Noise Generation with the

2920

.........................................................

6-4

6.3

Digitallnput/Output

..........................

,.........................................

6-4

7.0 APPLICATION EXAMPLES

7.1

Sweeping Local Oscillator

.............................................................

7-1

7.2

Piecewise Linear Logarithmic Amplifier

................................................

7-2

7.3

Digital Filter

..........................................................................

7-5

7.4

The

2920

as a Spectrum Analyzer

.......................................................

7-7

7.4.1

Description

of

Spectrum Analyzer

................................................

7-7

7.4.2 Block Diagram Description

.......................................................

7-7

7.4.3 Sampled Data System Considerations

............................................

7-9

7.4.4 Complete Spectrum Analyzer Assembly Listing

..................................

7-10

8.0 DESIGN

CONSIDERATIONS

8.1

2920

Debugging Procedures

...........................................................

8-1

8.2

Description of Application Breadboard

.................................................

8-2

8.2.1

Layout Considerations

..........................................................

8-2

8.2.2 Parts List

.......................................................................

8-5

9.0 2920 SUPPORT TOOLS

9.1

The Assembler

.......................................................................

9-1

9.2

The Simulator

.........................................................................

9-1

9.2.1

Concept

of

Simulation, Testing and Debugging

....................................

9-1

9.2.2 Modes

of

Operation

.............................................................

9-2

9.2.3 A Generalized Simulation Session

................................................

9-3

9.3

The

2920

Signal Processing Applications Software/Compiler

.............................

9-3

APPENDIX

REFERENCES

ii

Page 6

Introduction

and Terminology 1

Page 7

Page 8

CHAPTER 1

INTRODUCTION

AND

TERMINOLOGY

1.0

INTRODUCTION

AND

TERMINOLOGY

This

handbook

provides the

background

review

and

design examples

that

will help the reader

to

understand

analog signal processing applications using

INTEL's

digital signal processing system, the 2920.

The

2920 uses

digital sampled

data

techniques

to

implement con-

tinuous analog functions. In

another

words, analog

signal processing can now be

performed

with digital

signal processing techniques using the 2920.

Before looking

at

digital signal processing, it

is

useful to

clarify the distinctions between signal processing

and

digital processing. Signal processing deals with continuous

analog

waveforms, whereas digital processing

operates

on

data

that

are represented in a digital form.

Digital signill processing would then be the

operation

on

digital representation

of

continuous signals.

Digital signal processing, in the

most

general sense,

means creating, altering,

or

detecting continuous

signals, using digital

rather

than

analog

or

electro-

mechanical implementations.

Furthermore,

signal pro-

cessing can be distinguished from

data

processing in

that the former implies

that

real-time processing

is

needed.

Data

processing, however, implies the

manipulation

of

data

(which

mayor

may

not

represent

an

action occurring presently) in a batch

or

off-line

manner, where the need for the result

is

not

a function

of

real-time.

Most digital microprocessors are designed for

data

processing, not for high-speed complex signal processing.

The industry-standard 8080/8085 microprocessor system can

operate

as a signal processor

at

frequencies

to

only a few

hundred

hertz,

and

will require mUltiple

chips with a

separate

analog/digital

conversion system

and

I/O

circuitry.

By

contrast, general signal processing frequencies are in

the kilohertz range (thousands

of

cycles per second).

Many signals, such as speech, heartbeat,

and

seismic

waveforms are complex,

and

in

many

cases, multiple

signals must be processed in parallel. Because

of

different requirements for signal processing, a general purpose microprocessor

is

not well suited for signal processing applications. A different processor architecture

is

required to implement signal processing algorithms.

1-1

1.1

The 2920 Signal Processor

The 2920 Signal Processor

is

a single chip microcom-

puter designed especially

to

process real-time analog

signals.

The

2920 has

on-board

program

memory,

scratchpad memory,

D/

A circuitry,

A/D

circuitry,

digital processor,

and

I/O

circuitry. It

is

more

than

a

single device,

but

is

a complete digital sampled

data

system.

The

architecture and instruction set was

developed to

perform

precise, high speed signal process-

ing.

The

processor executes its

programs

at

typically

13,000 times a second when used with a

10

MHz

clock

and full

program

memory. Each execution

(1

pass

of

the

2920

program

memory) can process up to four

input

signals

and

up

to eight analog

output

signals. The processing speed allows signals with bandwidths to 5

kilohertz to be processed; shorter programs permit

higher

bandwidth.

Its capabilities in signal processing

are diverse

and

powerful, and include

an

extremely

broad

range

of

applications.

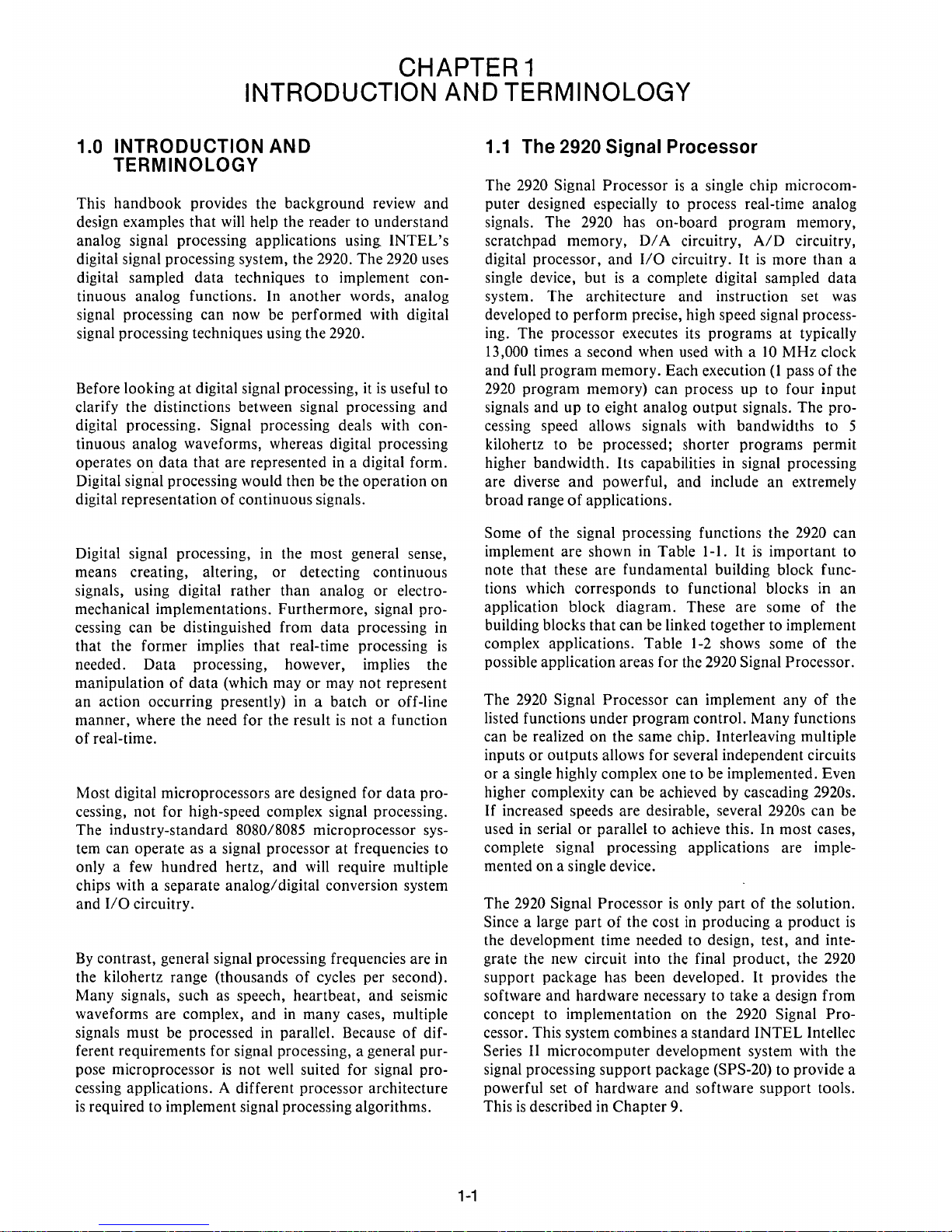

Some

of

the signal processing functions the 2920 can

implement

are

shown in Table 1-1. It

is

important

to

note

that

these are fundamental building block func-

tions which corresponds

to

functional blocks in

an

application block

diagram.

These are some

of

the

building blocks

that

can

be linked together to implement

complex applications. Table 1-2 shows some

of

the

possible application areas for the 2920 Signal Processor.

The

2920 Signal

Processor

can implement any

of

the

listed functions under

program

control.

Many

functions

can be realized

on

the same chip. Interleaving multiple

inputs

or

outputs

allows for several independent circuits

or

a single highly complex one

to

be implemented. Even

higher complexity

can

be achieved by cascading 2920s.

If

increased speeds are desirable, several 2920s can be

used in serial

or

parallel to achieve this. In most cases,

complete signal processing applications are implemented

on

a single device.

The

2920 Signal Processor

is

only

part

of

the solution.

Since a large

part

of

the cost

in

producing a

product

is

the development time needed to design, test,

and

inte-

grate the new circuit into the final

product,

the 2920

support

package has been developed. It provides the

software and

hardware

necessary to take a design

from

concept to implementation on the 2920 Signal

Pro-

cessor. This system combines a

standard

INTEL

Intellec

Series II

microcomputer

development system with the

signal processing

support

package (SPS-20) to provide a

powerful set

of

hardware

and software

support

tools.

This

is

described in

Chapter

9.

Page 9

INTRODUCTION AND TERMINOLOGY

Table 1-1. Signal Processing Functions

FILTERING

Complex poles

and

zeros

Arbitrary

digital filter configurations

Multiple parallel

or

cascaded filter combinations

High accuracy

and

stability

WAVEFORM

GENERATION

Arbitrary

waveforms, e.g., sine, square, triangle, etc.

Broad

frequency range with high resolution

9-bit

amplitude

accuracy

NONLINEAR

FUNCTIONS

Full wave rectifiers

Limiters

Comparators

~

ANXN

Multiply/Divide

EX

PROCESSING

Controllable

with external signals (analog

or

digital inputs)

Phase

locked loops

Adaptive filters

MODULATION/DEMODULATION

Amplitude,

frequency

and

phase

modulation

Continuous

or

digital, e.g., FM

and/or

FSK

Analog

or

digital inputs

and

outputs

Pipeline processing using multiple 2920s

Table 1-2. Broadly Based 2920 Signal Processor Applications Base

TELECOMMUNICATIONS

DTMF

/MF

receivers

Modems

Tone/cadence

generators

FSK/PSK

mod/demod

Adaptive equalizers.

PROCESS

CONTROL

Transducer

linearization

Remote feedback control

Remote

data

link

Signal conditioning

SIGNAL

PROCESSING

Waveform

generators

Correia

tors

Digital filters

Adaptive filters

Speech processing

Seismic processing

Sonar

processing

Transducer

linearization

1.2 Typical 2920 Design Sequence

Designing with the 2920 Signal Processor

is

best thought

of

in terms

of

the building block functions it can imple-

ment

and

the application models already available as

2920 routines (see

Chapter

7). The designer should

COnsider short 2920 assembly language routines as tools

which can be combined to achieve the desired system

function.

1-2

GUIDANCE

AND

CONTROL

Missile guidance

Torpedo

guidance

Motor

control

SPEECH

PROCESSING

Vocoders

Speech analysis

Pitch extraction

Speech synthesis

Speech recognition

TEST

AND

INSTRUMENTATION

Phase

locked loops

Frequency locked loops

Scanning spectrum analyzer

Digital filters

INDUSTRIAL

AUTOMATION

Position

and

rate

control

Communication

links

Servo links

The

first operation for the designer

is

to develop a

detailed system block diagram similar to one for a continuous analog design. Each block

is

then realized in

2920 code

and

arranged in a suitable sequence. The 2920

Signal Processing Applications Software/Compiler

(SP AS-20) can be used interactively to facilitate

developing the precise code to meet design constraints.

The

code

can

then be assembled as individual functional

blocks

or

as an entire system. Once the functions

or

system has been assembled, it can be debugged via use

of

the simulator.

Page 10

INTRODUCTION AND

TERMINOLOGY

The

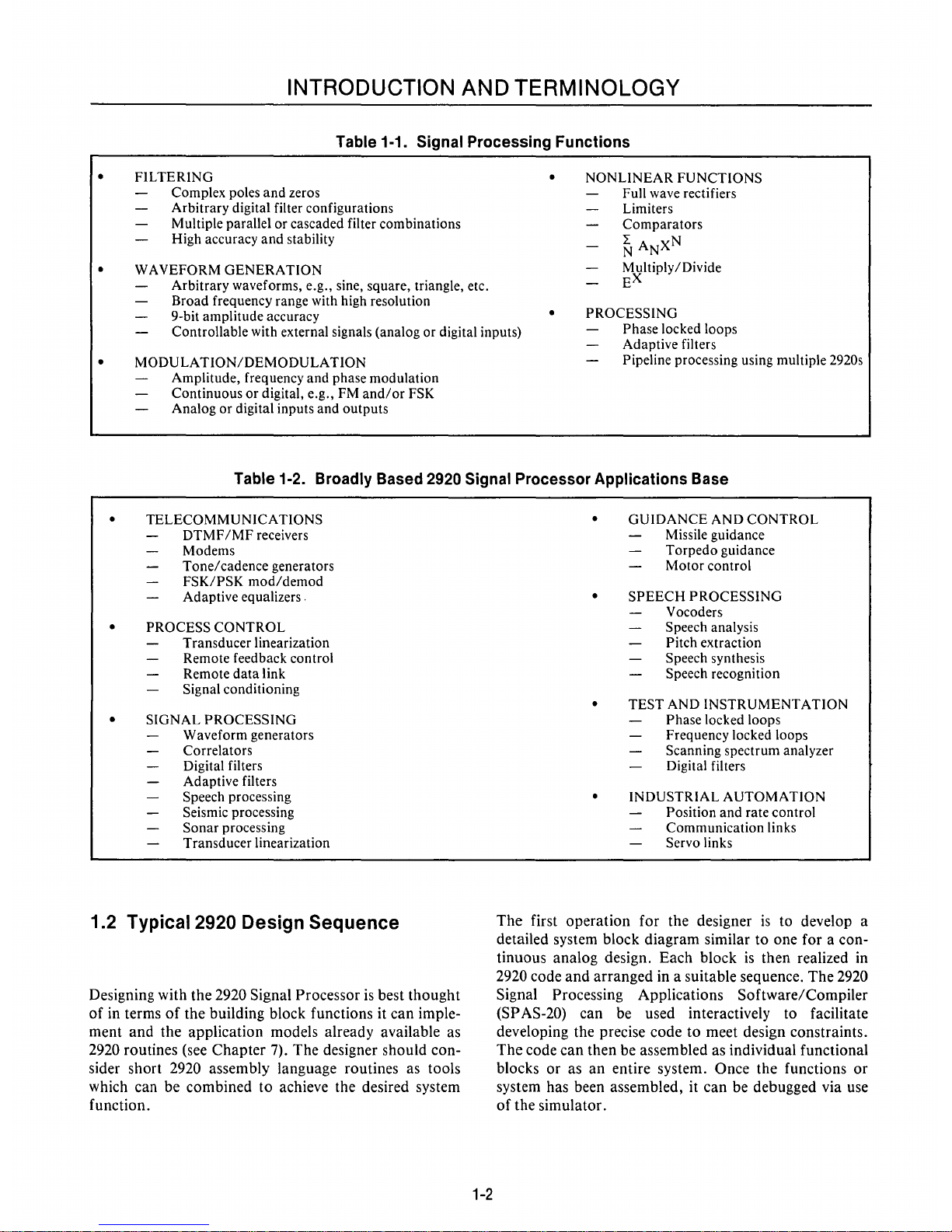

AS2920 Assembler tests the logical sequence, syn-

tax,

and

editing

of

the

program,

and

issues

error

or

warning messages.

When

assembly

is

successful, the

code used to

program

the

EPROM

is created. This code

is

also used as

the

program

input

to the SM2920

Simulator.

The

Simulator

can

be used

to

test the actual

operation

of

the 2920 prograrp.

For

example, the first step

of

such

a test might be

to

specify

an

input

waveform; such as a

sweeping sinusoid

for

a filter application, which will test

the

performance

of

the

filter

over

different

frequencies.

• Establish Objectives

• DeSign

Block

Diagram

• Translate Functional

Blocks

Into

Program

Blocks

• 2920 Assembler

(Intellec®Senes

II)

• Signal Processor

Appllcallons

Soltware/Compller

If

a

problem

occurs, i.e., unexpected

or

erroneous

out-

put,

the

debugging tools

of

the

Simulator

can

be called

into

action

to test variables

at

different

points

of

the

2920

program.

If

a

program

change

is

needed, it

can

be implemented

immediately within the Simulator, by directly changing

the

contents

of

the

program

through

the Intellec system

keyboard.

The

revised

program

is

then tested anew.

Every

parameter

of

the 2920's

operations

can

be tested,

changed, traced,

or

stored on diskette files for later

analysis

or

documentation

.

• SimUlator

•

Test Program

• System Debug

• Evaluate

System

Performance

• Program EPROM

(Intellec®)

•

UPP 103

• 2920

Personality

Card

• DeSign

Venllcallon

Figure 1-1. 2920 Design Sequence

Table 1-3. Development System Provides Computer Aided DeSign Contrast

Between Discrete Component

and

2920 DeSign Methodologies

Task

Discrete Component

2920 Approach

2920 Benefits

1.

Specify

Product

Develop Block Diagram Develop Block Diagram

Same starting point

2.

Develop

Prototype

A. Design Circuits

A. Translate block Reduce

2-3

weeks to

2-3

B.

Design Breadboard

diagram into program

days

C. Build Breadboard

B.

Use Signal Processing

-Locate

parts

Applications

Software/Compiler

-Put

together

C.

Assemble program

3. Troubleshoot prototype A.

Input

signal Via Simulator

Use classic troubleshooting

B.

Observe

output

with scope

A. Specify input signal techniques

on

interactive

and DVM

or

Spectrum

B.

Observe

output

and

terminal

Analyzer RAM contents

4. Correct Errors

A. Replace

Component

A. Edit and assemble Reduce 3 degrees

of

error to

B. Redesign layout

program

1;

save time

C. Redesign circuit B. Go back to 3

D.

Go

back to 3

5. Documentation

Write down observation

data,

Data

recorded

on

develop-

Accuracy increases;

and

write report ment system in an easy to Time savings

follow report

1-3

Page 11

INTRODUCTION AND TERMINOLOGY

When the simulation indicates the program

is

operating

to

specifications, it can be stored on a diskette. The

latest version

can

then be loaded into the 2920 device for

testing in the

hardware

prototype.

Figure

1-1

outlines the development sequence for a 2920

design. There

are

several

important

points to note that

makes the 2920 much more efficient for a system design:

1)

With the 2920, hardwired analog functions are now

implemented with flexible software,

2)

Instead

of

designing circuits for each

of

the building

blocks

of

the block diagram, a sequence

of

2920

instructions are used to implement each

of

the

blocks,

3)

Instead

of

building hardware prototypes early in the

design phase

of

the

product

development, the 2920

uses a computer-aided design and debug package to

facilitate design

and

development,

and

4)

There

is

no need for a hardware prototype until

such a time

that

the system has been simulated

and

found to be completely functional

and

meets design

specifications.

Table

1-3

shows the contrast in design methodologies

for a 2920 design

and

one using analog components.

Numerous benefits derive from using the 2920 development system for signal processing design

and

implementation. The digital methodology, with its unique tools

(see Chapters 3

and

9) to aid designing

and

debugging,

helps to:

a) standardize the design process, and

b)

allow for immediate changes. Thus it can

c)

reduce drastically the time needed for creating new

products

or

for modifying prior work to fix errors

or

to

add

new features.

1.3 Benefits of the 2920 Signal

Processor Approach

The 2920

is

a solution for many signal processing needs.

It

is

a complete system in a single 28-pin package. Along

with 2920 are all the design

and

development tools

required to move a

product

idea into finished product.

The 2920 uses a digital sampled data system

approach

for signal processing applications. The digital sampled

data

approach brings many attributes to signal process-

ing. Table

1-4

summarizes some

of

these benefits.

1.3.1

2920 Device Benefits

Lower manufacturing cost for

2920-based products

results from a lower

part

count,

improved reliability,

1-4

and

the elimination

of

costly preCiSion components.

Also eliminated

is

the

production

re-tuning

or

'tweak-

ing' so

often

required in analog systems integration.

The flexibility for rapid design changes in prototypes

is

a direct result

of

the 2920's programmability. Alternative designs are readily compared by reprogramming

the 2920's

EPROM.

The re-use

of

standard

debugged

program blocks facilitates the creation

of

alternatives in

both

existing

and

future products.

The digital approach provides inherently stable, predictable,

and

reproducible results.

The

NMOS integrated

circuitry means increased reliability. Conceptual errors

or inefficient implementation choices are easily found

during debugging

and

performance evaluation using the

2920 Simulator.

The

performance you design for

is

the

realized performance.

Savings in long-term

product

maintenance, support,

and enhancement result from the relative ease with

which engineering changes are implemented in software.

Field maintenance

is

reduced by digital stability

and

LSI

reliability.

1.3.2 Deveiopment-Support-Tool Benefits

Long term savings in large

part

are derived from the

2920 support package. The 2920 Signal Processing

Applications

Software/Compiler

(SPAS-20) contains

very powerful code generation

and

macro capabilities,

plus graphics

and

analysis capabilities permitting inter-

active specification

and

adjustment

of

design param-

eters. Creating usable libraries

of

macros

and

signal

processing routines means ever increasing productivity

due to building

on

the successes

of

the past.

The

2920 Assembler creates the actual machine bit patterns to be programmed into the 2920. Its careful error

analysis detects problem areas,

and

the debugging

information it provides greatly facilitates design evaluation during simulation.

The 2920 Simulator permits execution

of

any

part

of a

2920 program, plus collection

of

trace

data

on variables.

This tool bears a strong family resemblance to Intel's

In-Circuit-Emulators (ICE).

The

analysis and evaluation capabilities inherent in the 2920 Simulator make

possible rapid problem isolation in the field

or

in the

factory.

It

can also be used to generate revised object

code for a quick check

on

proposed fixes

or

enhance-

ments. This revised code

can

be saved

and

used to pro-

gram the 2920.

Page 12

J.

2.

3.

4.

5.

6.

7.

8.

INTRODUCTION

AND

TERMINOLOGY

Table 1-4. 2920 Benefits

Discrete

Analog Components

Board full

of

components

Component

matching: select, test, combine,

match,

tune, test

Production-lot

variation

in circuit

performance

Performance

degradation

over time, signal

degradation,

due to circuit

interaction

or

noise

Discrete

component

tolerances

prohibit

exact matching

of

multi-pole frequency

Time-consuming fixes

to

problems with hardwired

design

Costly

components

for

accuracy

Custom

designs

are

costly, risky,

and

require

or

create

heavy

commitments

1-5

Intel 2920 Signal Processor Methodology

Single chip

System tweaking eliminated because

performance

from

device to device

is

identical: digital processing

is

stable,

predictable,

and

repeatable

Digital accuracy

is

repeatable

Eliminated-the

2920 restricts

degradation

of

signal

quality to the instants

at

which signal

samples

are

digitized

and

converted back to

analog

Restriction eliminated because digital realizations

are

not

subject to such tolerances

Quick

program

changes

Not

needed because their functions

can

be

created

in

software

Programming

permits vastly

greater

flexibility for

modifications, improvements, and

extra

features;

Much wider range

of

options

at

reduced

costs, size,

weight

and

maintenance.

Page 13

Page 14

Sampled Data Systems 2

Page 15

Page 16

CHAPTER 2

SAMPLED

DATA

SYSTEMS

2:0 SAMPLED DATA SYSTEMS

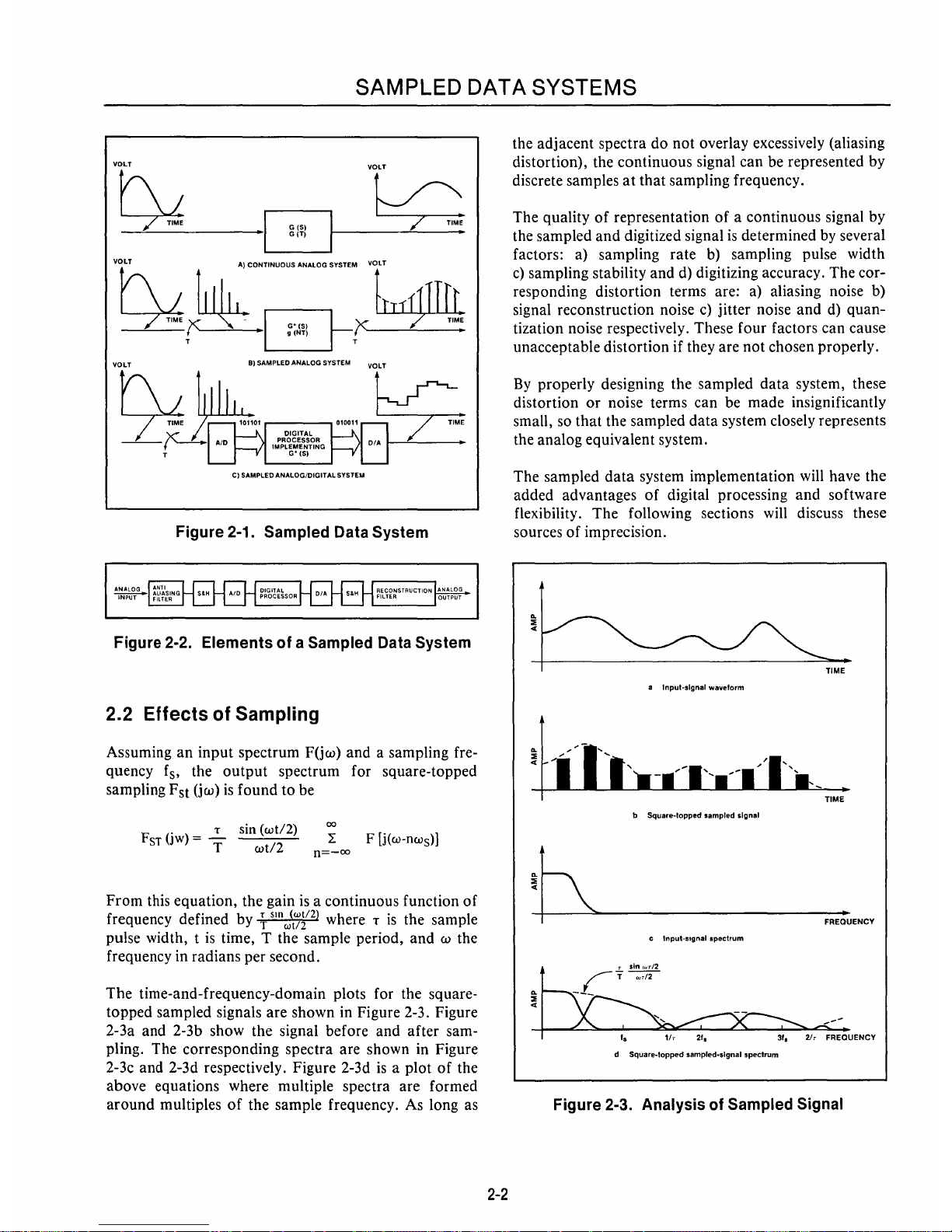

Sampled

data

systems can be implemented using either

analog

or

digital processing techniques,

or

both.

Figure

2-1

shows two different types

of

sampled

data

systems:

sampled analog system

and

sampled analog/digital

system. Examples

of

sampled analog systems include

transversal filters using

CCD

or

bucket brigade shift

registers analog weighted-taps

and

switched capacitor

techniques to implement a filter characteristic. The

identical systems can also be implemented using digital

instead

of

analog processing. Such systems are referred

to as digital sampled

data

systems. This type

of

system

can be implemented with the 2920 Signal Processor.

This chapter will discuss the various elements

that

com-

prise a digital sampled

data

system

and

also look

at

the

design considerations in representing a continuous

analog signal with digital sampled

data

techniques.

2.1

Elements of a Digital Sampled Data

System

The block diagram shown in Figure 2-2 illustrates the

basic blocks

of

a general purpose sampled

data

system

using a digital signal processor. In this configuration it

is

assumed

that

both

the

input

and

output

signals are

analog. This

is

not

a necessary condition since digital

signals

can

be considered a special type

of

analog signals

and

processed accordingly. Elements

of

the block

diagram are discussed below.

The system in Figure 2-2 operates

on

the input analog

signal using the indicated components in sequence:

• Anti-Aliasing

Filter-This

filter

is

used to bandlimit

the incoming analog signal prior to sampling; thus a

continuous analog filter

is

used. This minimizes

possible distortion terms (aliasing noise) which

could arise from signal frequencies

that

are

too

high

relative to the sample rate (Section 2-2).

•

Input

Sample

and

Hold

(S&H)-

The filtered input

signal

is

then sampled at a fixed rate determined by

the digital processor. Each resulting sampled

amplitude

is

held long enough for subsequent pro-

cessing (such as analog-to-digital conversion).

2-1

Analog-to-Digital Converter

(A/D)-The

held

analog voltage

is

converted to a digital word. This

digital word then represents the sampled input

signal voltage. (Since the processor must operate on

individual digital words, it

is

necessary to

characterize the continuous analog

input

signal by

discrete digital words which retain the information

of

the original signal.)

• Digital

Processor-Each

digitized sample

is

now

processed by the digital processor, which has been

programmed to

perform

a predetermined algorithm. Typically, a general microprocessor can be

programmed to

perform

any funciton,

but

the

resulting execution time

is

too

limiting for most

analog applications.

The

2920 eliminates this pro-

blem because its architecture

is

configured to take

advantage

of

serial repetitive signal processing,

while

at

the same time preserving many

of

the

advantages

of

the general purpose microprocessor.

Digital-to-Analog Converter

(D/

A)-The

processed digital words are converted back to analog

using the

D/

A. Again, the analog signal

is

approx-

imated by discrete amplitude levels (as in the

A/D).

In addition, the

D/

A sampled

output

weights the

signal

output

in the frequency

domain

by sin(x)/x,

thereby causing some signal distortion (Section

2-2).

•

Output

Sample-and-Hold

(S&H)-One

method

of

reducing the

output

frequency distortion

is

to widen

the sin(x)/x rolloff by resampling the

output

signal

using a very narrow sample width. The S&H takes

the

D/

A held

output

and

res

am pies it with narrow

pulses.

Another

use

of

an

output

S&H

is

to store

values when several outputs are multiplexed during

a single sample period.

• Reconstruction

Filter-Since

the desired

output

signal

is

a continuous representation

of

the pro-

cessed input signal, it

is

necessary to remove high

frequency components resulting from the

D/ A or

sample-and-hold outputs. This, in effect, smooths

the analog

output

from sample to sample. A

lowpass filter

is

used to perform the signal

"reconstruction".

This filter

can

also be used to

compensate for the sin(x)/x frequency rolloff

of

the

D/ A or

S&H (Section 2-2).

Page 17

SAMPLED

DATA

SYSTEMS

C) SAMPLED

ANALOG/DIGITAL

SYSTEM

Figure 2·1. Sampled Data System

Figure 2·2. Elements of a Sampled Data System

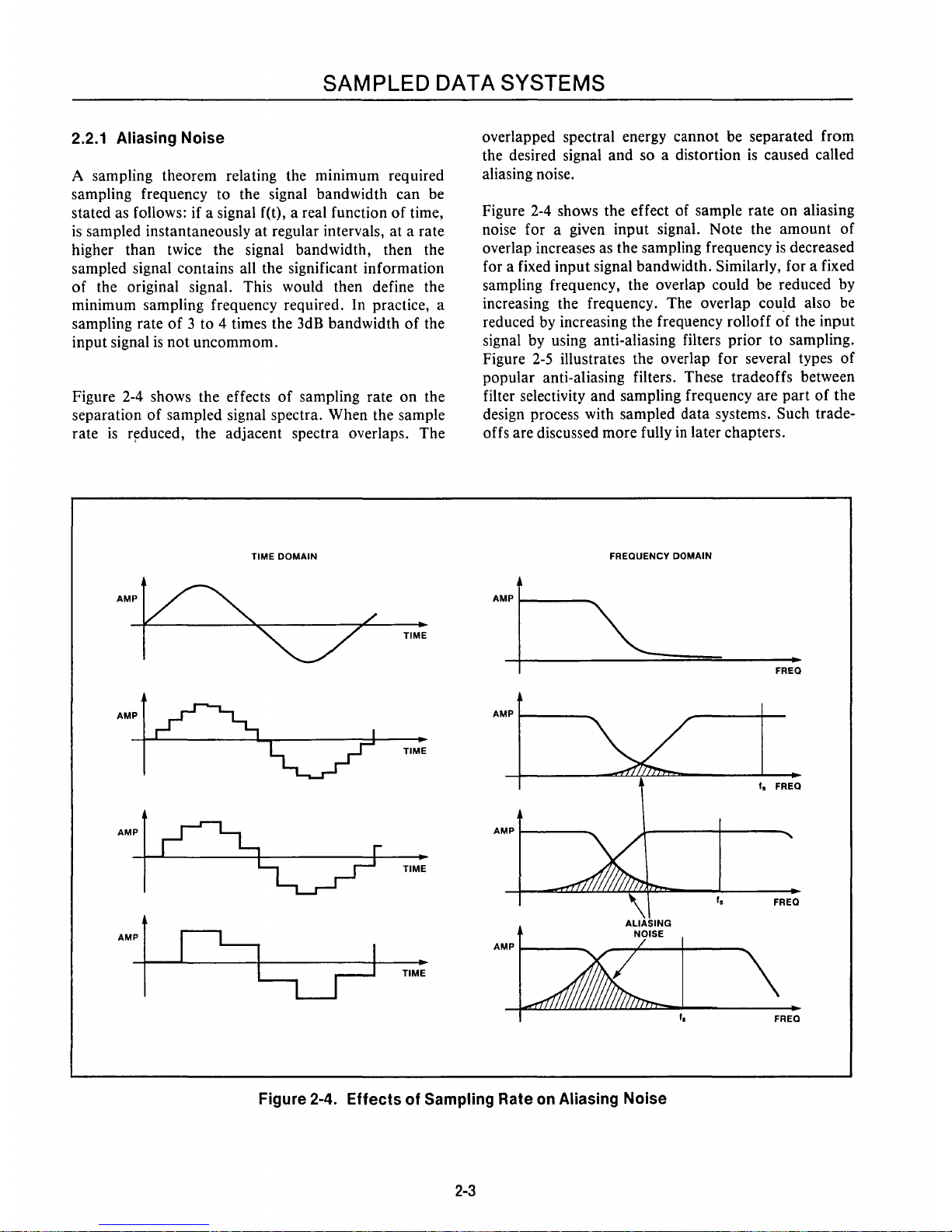

2.2 Effects of Sampling

Assuming

an

input

spectrum F(jw) and a sampling fre-

quency fs, the

output

spectrum for square-topped

sampling

Fst

(jw)

is

found

to

be

FST (jw)

=.2....

sin

(wtl2)

T

wtl2

L F [j(w-nws)]

n=-oo

From

this

equation,

the gain is a continuous function

of

frequency defined by

~

SIn

Jt~y2)

where T

is

the sample

pulse width, t

is

time, T the sample period,

and

w the

frequency in radians per second.

The

time-and-frequency-domain plots for the square-

topped

sampled signals are shown in Figure 2-3. Figure

2-3a and 2-3b show the signal before and

after

sampling. The corresponding spectra are shown in Figure

2-3c and 2-3d respectively. Figure 2-3d

is

a plot

of

the

above equations where multiple spectra are formed

around

mUltiples

of

the sample frequency. As long as

2-2

the

adjacent

spectra

do

not

overlay excessively (aliasing

distortion), the

continuous

signal can be represented by

discrete samples

at

that

sampling frequency.

The quality

of

representation

of

a continuous signal by

the sampled

and

digitized signal

is

determined by several

factors: a) sampling rate b) sampling pulse width

c)

sampling stability

and

d) digitizing accuracy.

The

corresponding distortion terms are: a) aliasing noise b)

signal reconstruction noise

c)

jitter noise

and

d)

quan-

tization noise respectively. These

four

factors can cause

unacceptable distortion if they are

not

chosen properly.

By

properly designing the sampled

data

system, these

distortion

or

noise terms can be

made

insignificantly

small, so

that

the sampled

data

system closely represents

the analog equivalent system.

The

sampled

data

system implementation will have

the

added advantages

of

digital processing

and

software

flexibility.

The

following sections will discuss these

sources

of

imprecision.

a

lnput~slgnal

waveform

b Square-topped sampled signal

FREQUENCY

c Input-signal spectrum

{T--;;;;t2

D..

-

__

~

::E

..:

~....

--

....

--

t'""""t

•

d Square-topped sampled-signal spectrum

Figure 2·3. Analysis of Sampled Signal

Page 18

SAMPLED DATA SYSTEMS

2.2.1 Aliasing Noise

A sampling theorem relating the minimum required

sampling frequency

to

the signal bandwidth can be

stated as follows: if a signal f(t), a real function

of

time,

is

sampled instantaneously

at

regular intervals, at a rate

higher than twice the signal bandwidth, then the

sampled signal contains all the significant information

of

the original signal. This would then define the

minimum sampling frequency required. In practice, a

sampling rate

of

3 to 4 times the 3dB bandwidth

of

the

input signal

is

not

uncommom.

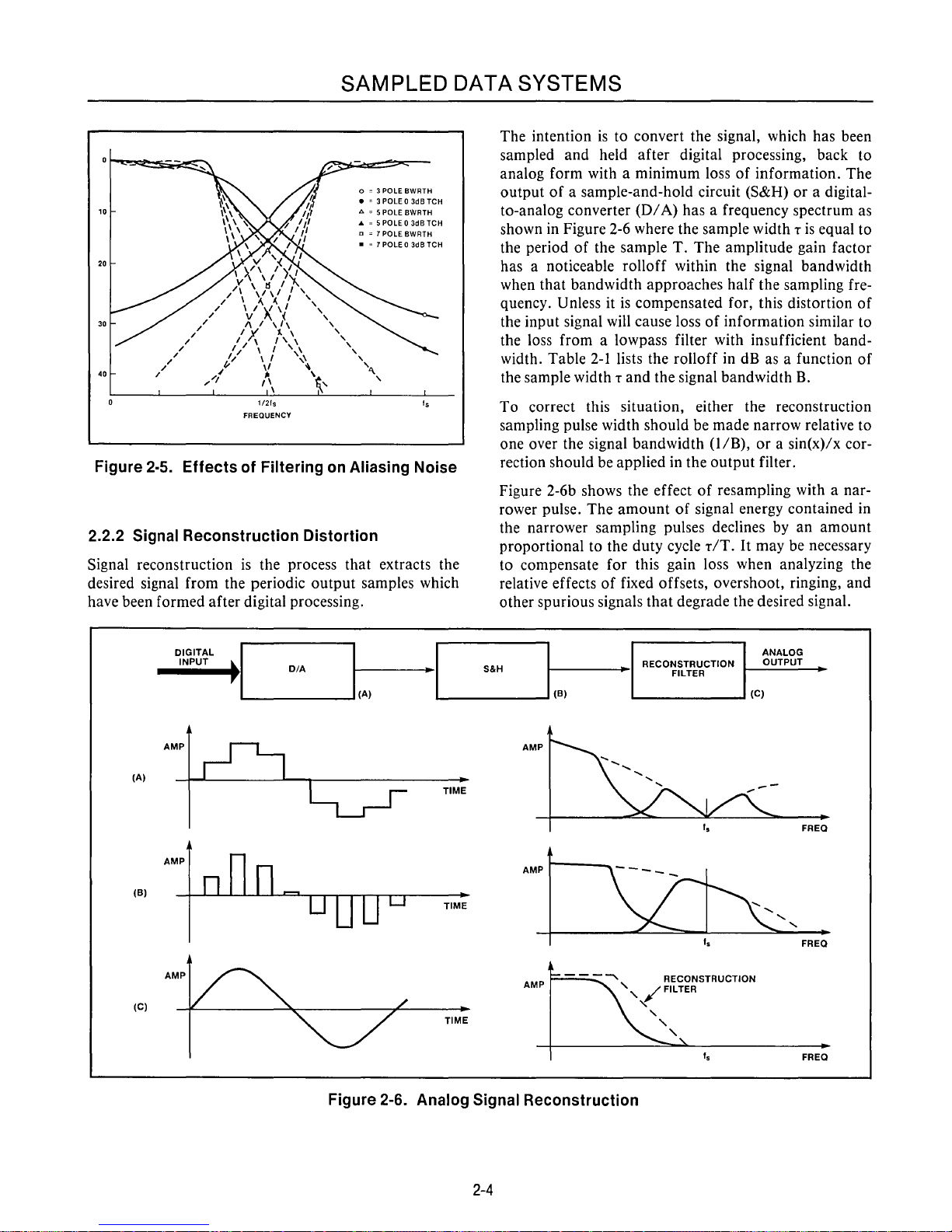

Figure 2-4 shows the effects

of

sampling rate

on

the

separation

of

sampled signal spectra. When the sample

rate

is

r~duced,

the adjacent spectra overlaps. The

TIME DOMAIN

AM'~'C7L

TIME

A·'I~LLL:/

TIME

A·'I~

TIME

A.')

~

TIME

overlapped spectral energy cannot be separated from

the desired signal

and

so a distortion

is

caused called

aliasing noise.

Figure 2-4 shows the effect of sample rate

on

aliasing

noise for a given input signal. Note the

amount

of

overlap increases as the sampling frequency

is

decreased

for a fixed input signal bandwidth. Similarly, for a fixed

sampling frequency, the overlap could be reduced by

increasing the frequency. The overlap

couJd also be

reduced by increasing the frequency rolloff

of

the input

signal by using anti-aliasing filters prior to sampling.

Figure

2-5

illustrates the overlap for several types

of

popular anti-aliasing filters. These tradeoffs between

filter selectivity and sampling frequency are

part

of

the

design process with sampled data systems.

Such trade-

offs are discussed more fully

in

later chapters.

FREQUENCY DOMAIN

A.'

I

~

FREQ

A.'

I

f.

FREQ

AMP

f.

FREQ

A·'IZ!.

\

•

FREQ

Figure 2-4. Effects of Sampling Rate

on

Aliasing Noise

2-3

Page 19

SAM PLED DATA SYSTEMS

10

20

30

40

1/21s

FREQUENCY

o 0 3

POLE

BWRTH

.0

3POLEO

3dBTCH

A 0 5

POLE

BWRTH

..

0

5POLEO

3dBTCH

c 0 7

POLE

BWRTH

• 0

7POLEO

3dBTCH

Is

Figure 2·5.

Effects

of

Filtering on Aliasing Noise

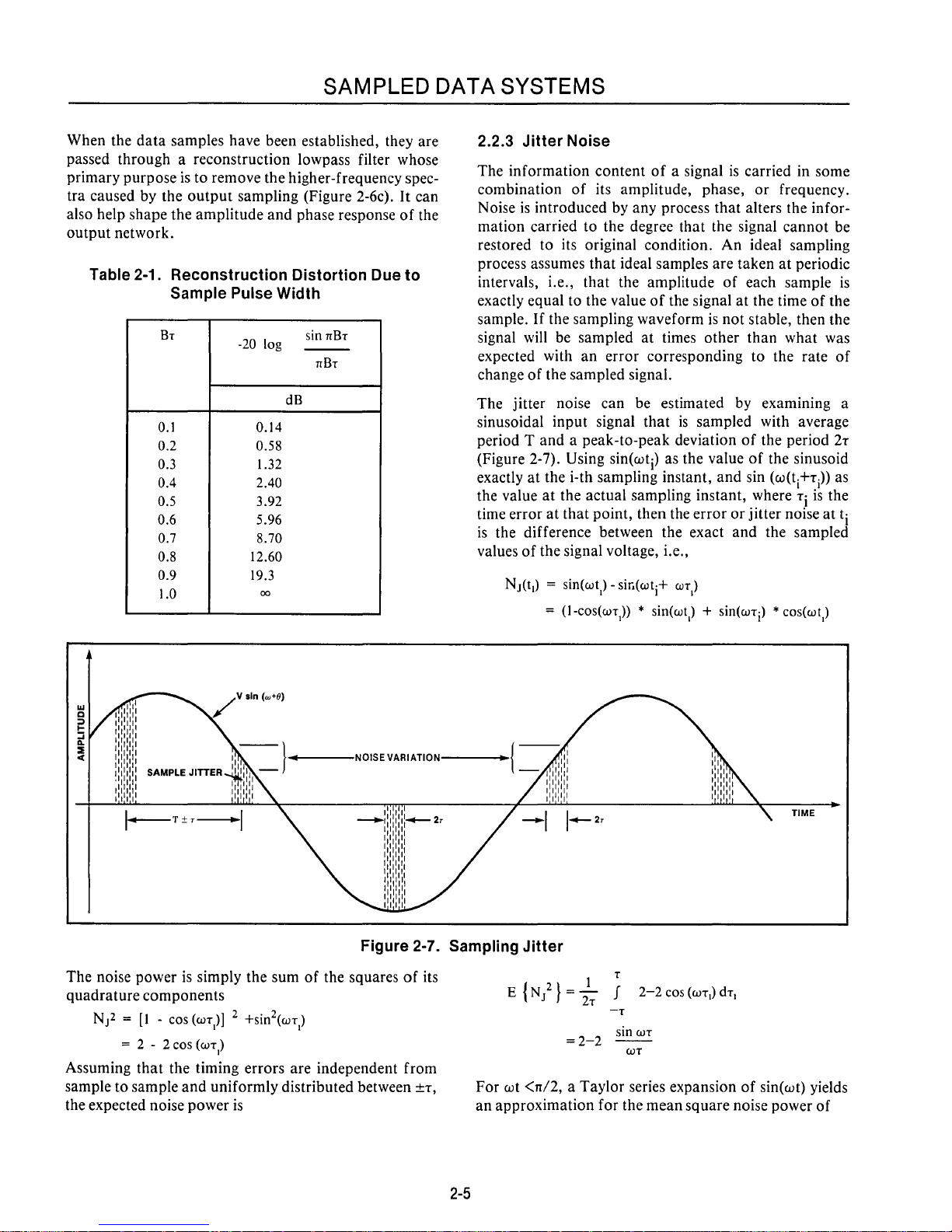

2.2.2

Signal Reconstruction Distortion

Signal reconstruction

is

the process

that

extracts the

desired signal from the periodic

output

samples which

have been formed

after

digital processing.

DIGITAL

INPUT

D/A

The intention

is

to

convert the signal, which has been

sampled

and

held

after

digital processing, back

to

analog form with a

minimum

loss

of

information.

The

output

of

a sample-and-hold circuit (S&H)

or

a digital-

to-analog converter (DI A) has a frequency spectrum as

shown in Figure 2-6 where the sample width

T

is

equal to

the period

of

the sample

T.

The

amplitude

gain factor

has a noticeable

rolloff

within the signal bandwidth

when

that

bandwidth

approaches

half

the sampling fre-

quency. Unless it

is

compensated for, this distortion

of

the input signal will cause loss

of

information

similar to

the loss

from

a lowpass filter with insufficient band-

width. Table

2-1

lists the

rolloff

in dB as a function

of

the sample width T

and

the signal

bandwidth

B.

To

correct this situation, either the reconstruction

sampling pulse width should be

made

narrow

relative

to

one over the signal

bandwidth

(1/B),

or

a sin(x)/x cor-

rection should be applied in the

output

filter.

Figure 2-6b shows the effect

of

resampling with a nar-

rower pulse.

The

amount

of

signal energy contained in

the narrower sampling pulses declines by

an

amount

proportional

to the

duty

cycle TIT.

It

may

be necessary

to

compensate for this gain loss when analyzing the

relative effects

of

fixed offsets, overshoot, ringing, and

other spurious signals

that

degrade the desired signal.

ANALOG

OUTPUT

·1

L

S&H

~

___

----I,",~I

RECO~~L~~~CTION

'-

_____

-"

(8)

""--

_____

....

(C)

.;

(A)

AM'I~

LLJ

..

TIME

AMP

I.

FREO

AM'I

n

n

Dr-.

(8)

DODD

TIME

AM'

t

~"

I.

FREO

AM'p~//

(C)

-------

RECONSTRUCTION

AMP

,

,/FILTER

,

"

"

I.

FREO

..

TIME

Figure 2-6. Analog Signal Reconstruction

2-4

Page 20

SAMPLED DATA SYSTEMS

When the

data

samples have been established, they are

passed through a reconstruction lowpass filter whose

primary

purpose

is

to remove

the

higher-frequency spec-

tra caused by the

output

sampling (Figure 2-6c).

It

can

also help shape the

amplitude

and

phase response

of

the

output

network.

Table 2-1. Reconstruction Distortion Due to

Sample Pulse Width

BT

-20

log

sin

nBT

---

nBT

dB

0.1

0.14

0.2 0.58

0.3

1.32

0.4

2.40

0.5

3.92

0.6 5.96

0.7 8.70

0.8 12.60

0.9

19.3

1.0

00

2.2.3 Jitter Noise

The

information

content

of

a signal

is

carried in some

combination

of

its amplitude, phase,

or

frequency.

Noise

is

introduced by any process

that

alters the infor-

mation

carried to the degree that the signal

cannot

be

restored to its original condition.

An

ideal sampling

process assumes

that

ideal samples are

taken

at

periodic

intervals, i.e.,

that

the amplitude

of

each sample

is

exactly equal to the value

of

the signal

at

the time

of

the

sample.

If

the sampling waveform

is

not

stable, then the

signal will be sampled

at

times

other

than

what

was

expected with

an

error

corresponding

to

the rate

of

change

of

the sampled signal.

The

jitter noise can be estimated by examining a

sinusoidal

input

signal

that

is

sampled with average

period T

and

a peak-to-peak deviation

of

the period

2T

(Figure 2-7). Using sin(wti) as the value

of

the sinusoid

exactly

at

the i-th sampling instant,

and

sin

(W(tj+T

j

» as

the value

at

the actual sampling instant, where

Ti

is

the

time

error

at

that

point, then the

error

or

jitter noise

at

ti

is

the difference between the exact

and

the sampled

values

of

the signal voltage, i.e.,

NJ(t.) = sin(wt

l

) -

sir,(wti+

WT

I

)

=

(l-COS(WT)

* sin(wt) + sin(wTi) * cos(wt)

11--

}

....

I-----NOISE

VARIATION---

__

SAMPLE

JITTER~::II

-

11111111

11111111

I-T±T_/

/_2T

TIME

Figure 2-7. Sampling Jitter

The noise power

is

simply the sum

of

the squares

of

its

quadrature

components

NJ2 =

[1

- cos

(WT)]

2 +sin2(WT)

= 2 -

2COS(WT

I

)

Assuming

that

the timing

errors

are independent from

sample

to

sample

and

uniformly distributed between

±T,

the expected noise power

is

2-5

T

E {N/ } =

;T

f

2-2

cos

(WT

I

)

dTI

=2-2

sin

WT

WT

For

wt

<TI12,

a

Taylor

series expansion

of

sin(wt) yields

an

approximation

for the

mean

square

noise power

of

Page 21

SAM PLED DATA SYSTEMS

The

signal-to-noise ratio (SNR)

of

a sampled sinusoid

sin(wT) due

to

jitter uniformly distributed over

-T~TO~T

seconds

is

Mean

Square

Signal

Mean

Square

Noise = (SNR)

jitter

3

(WT)

2

2

Expressed

another

way,

(SNR) .. = 0.038

(~)2

JItter T

where T

is

the

period

of

the sampled signal. The jitter

SNR

is

plotted in Figure 2-8 as a function

of

the jitter-

tolerance

ratio

T/T.

rg

-'UI

<tUl

z-

,,0

iii

Z

WUl

a:

a::

<t<

::J:l

0°

cn

Ul

ZZ

<t<

wUl

::;:i:

a:

z

III

I

r

LOG SCALE

IlJ..U..l.LL..J

"-

10 5 2 1

100

~

~

80

60

40

20

o

10-6

~

~

""

~

10-

5

10-

3

JITTER TOLERANCE, T

MINIMUM SIGNAL PERIOD, T

Figure

2-8.

Jitter

SNR

""

Since each pass

of

the 2920

program

uses the same

number

of

clock cycles, overall sampling jitter will be

entirely a function

of

the clock stability.

When

the

2920

clock

is

crystal controlled,

clock/sampling

jitter will be

insignificant.

2-6

2.2.4 Quantization Noise

Digital signal processing

of

a signal implies

that

at

specific times the signal

is

sampled

and

a digital word

is

formed

that

represents

the

amplitude

of

the signal

at

that

time.

The

sections above described the effect

of

this

sampling process,

and

showed

that

a minimum loss

of

information

is

possible with the

proper

selection

of

the

input filter

and

sampling frequency.

The conversion

from

a continuous signal

to

a digital

signal requires

that

signal voltage be divided into a finite

number

of

levels which can be defined using a digital

word n bits long.

An

n-bit word can describe 2n different voltage steps. Signal variations between these

steps will go undetected.

It

is

therefore necessary

to

determine the range

of

signal levels from maximum

to

minimum

that

the system must

operate

with, to deter-

mine the

number

of

bits needed in

an

A/D

conversion.

Figure 2-9 illustrates how

the

error

voltage (called

quan-

tization noise)

is

generated. The corresponding ratio

of

peak signal to

quantization

noise, expressed in dB,

is

a

function

of

the digital

word

length.

OUTPUT

VOLTAGE

Ja

=

2N-1

N = It BITS

Ja

' 6N OB I

MAX

I

ERROR I

1

:

VOLTAGE"

"

t\

" 1\

t\

I

'J 'J

\I

\I

\I

'\

INPUT

VOLTAGE

INPUT

VOLTAGE

2 3 4 5 6 7 8

91011

SINO

DB

"6

18 24 30 36 42 48 54 60 66

Figure 2-9. Quantization Noise

The

quantizing

error

can be expressed in terms

of

the

total

mean

squared

error

voltage between the exact

and

the quantized samples

of

the signal. In Figure 2-10,

any

signal voltage v(t) falls between the i-th

and

the (i+ 1

)th

levels which define the i-th quantizing interval.

The

error signal

ei

is

expressed

as

ei=V(t)-Vi

Page 22

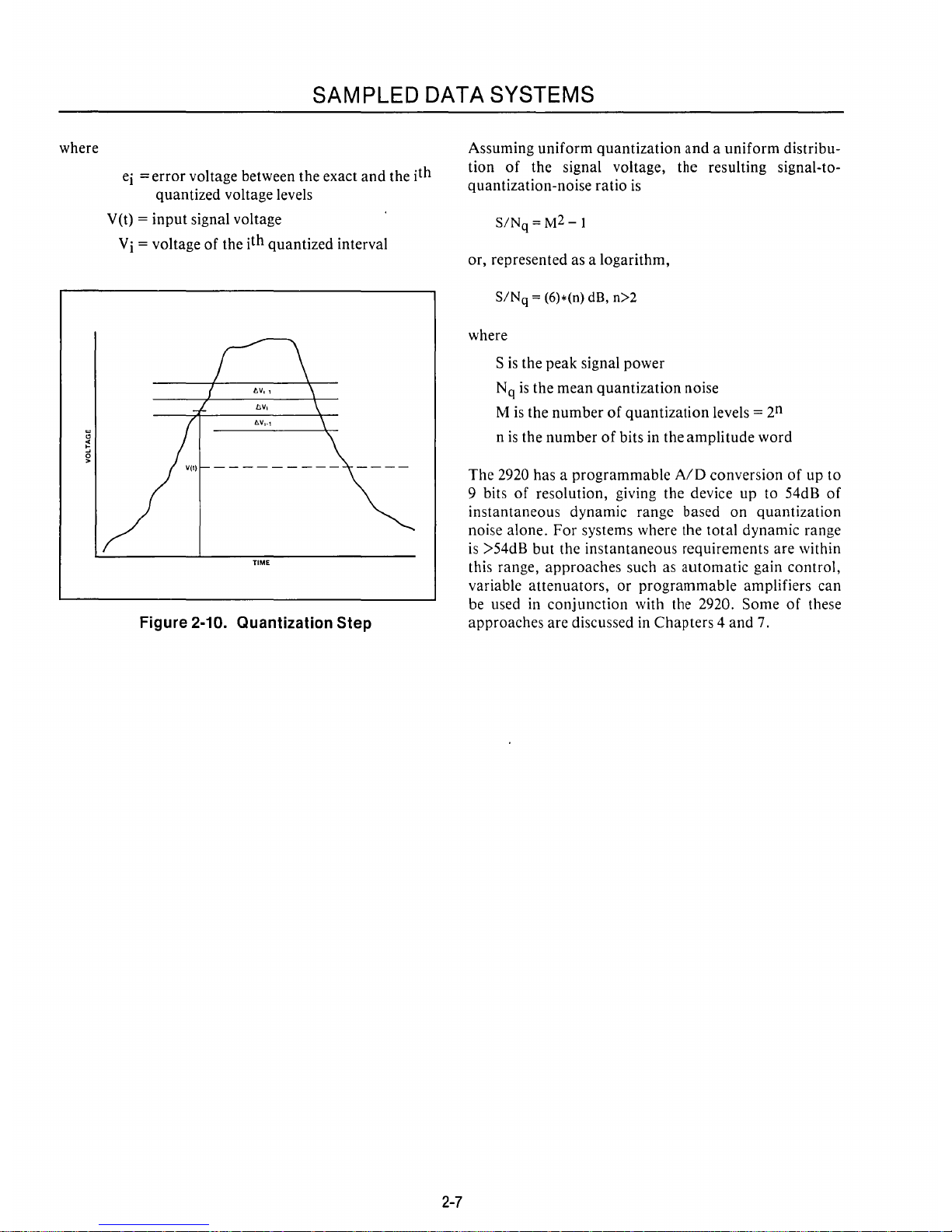

where

SAMPLED

DATA

SYSTEMS

ei =

error

voltage between

the

exact

and

the i

th

quantized

voltage levels

V(t)

=

input

signal voltage

Vi

= voltage

of

the i

th

quantized

interval

Figure 2-10. Quantization Step

2-7

Assuming

uniform

quantization

and a uniform

distribu-

tion

of

the

signal voltage, the resulting signal-to-

quantization-noise

ratio

is

S/N

q

=

M2-1

or,

represented

as a logarithm,

S/N

q

= (6)*(n) dB,

n>2

where

S

is

the

peak

signal

power

Nq is

the

mean

quantization

noise

M

is

the

number

of

quantization

levels = 2

n

n

is

the

number

of

bits in the

amplitude

word

The

2920

has a programmable

AID

conversion

of

up

to

9 bits

of

resolution,

giving the device

up

to

54dB

of

instantaneous

dynamic

range

based

on

quantization

noise

alone.

For

systems where the

total

dynamic

range

is >54dB

but

the

instantaneous

requirements

are

within

this range,

approaches

such as

automatic

gain

control,

variable

attenuators,

or

programmable

amplifiers

can

be used in

conjunction

with the 2920.

Some

of

these

approaches

are

discussed in

Chapters 4 and

7.

Page 23

Page 24

The 2920

Signal

Processor

3

Page 25

Page 26

CHAPTER 3

THE

2920

SIGNAL PROCESSOR

3.0 THE 2920 SIG NAL PROCESSOR

This chapter will discuss the 2920 device operation functional elements

and

operating conventions.

3.1

Device Operation

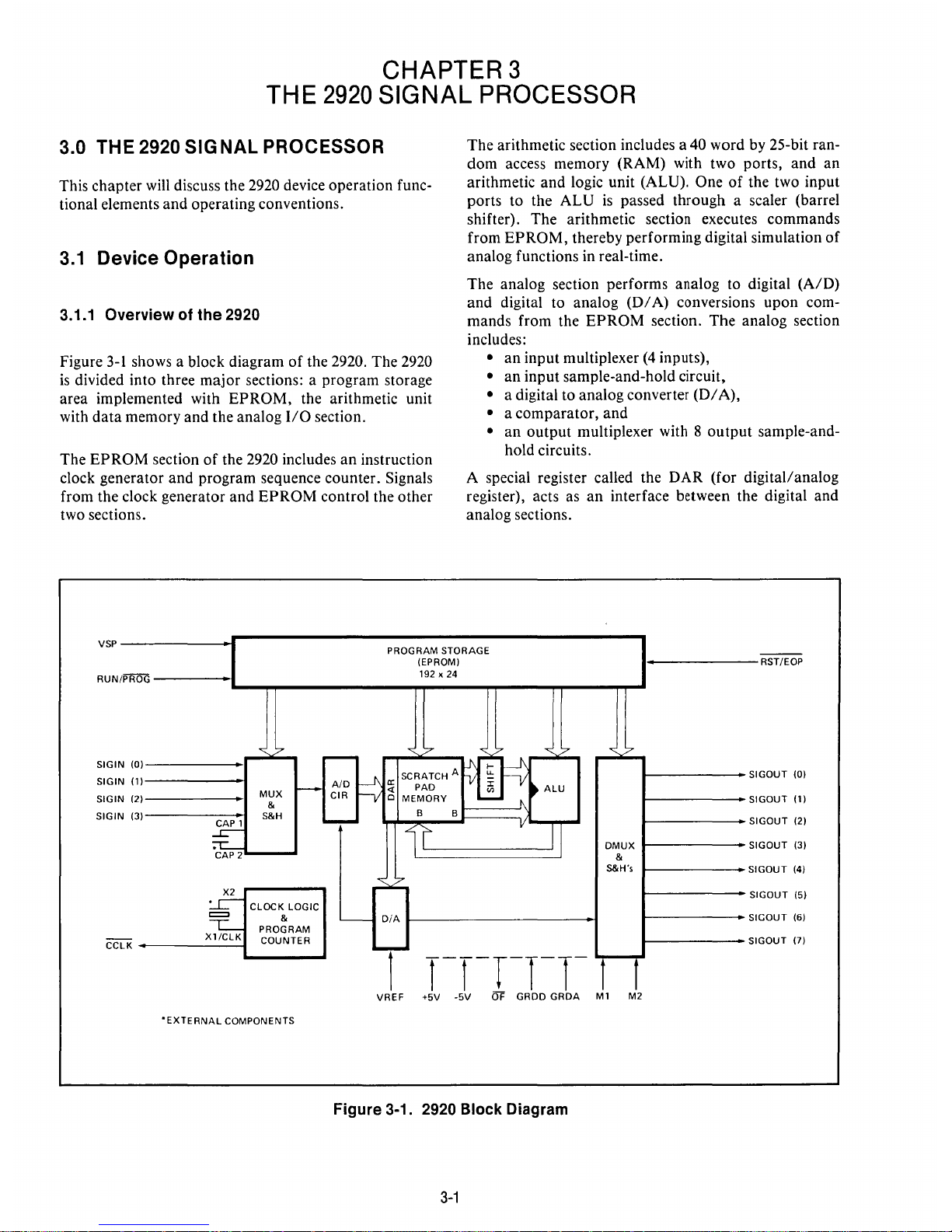

3.1.1 Overview of the 2920

Figure

3-1

shows a block diagram

of

the 2920. The 2920

is

divided into three

major

sections: a program storage

area implemented with

EPROM,

the arithmetic unit

with

data

memory

and

the analog 110 section.

The

EPROM

section

of

the 2920 includes

an

instruction

clock generator

and

program sequence counter. Signals

from the clock generator

and

EPROM

control the other

two sections.

The

arithmetic section includes a 40 word by 25-bit ran-

dom

access memory (RAM) with two ports,

and

an

arithmetic

and

logic unit (ALU). One

of

the two input

ports to the

AL U is

passed through a scaler (barrel

shifter).

The

arithmetic section executes commands

from

EPROM,

thereby performing digital simulation

of

analog functions in real-time.

The

analog section performs analog to digital

(AID)

and

digital to analog

(01

A) conversions

upon

com-

mands from the

EPROM

section.

The

analog section

includes:

•

an

input multiplexer

(4

inputs),

•

an

input sample-and-hold circuit,

• a digital to analog converter

(01

A),

• a

comparator,

and

•

an

output

mUltiplexer with 8

output

sample-and-

hold circuits.

A special register called the DAR (for digital/analog

register), acts as

an

interface between the digital and

analog sections.

VSP------------~--------------------------------------------,

PROGRAM STORAGE

(EPROM)

1----------

RST/EOP

RUN/PROG--------·L

__

~~--------------~'9:2~X~24~--~----~~----~~

SIGIN

(0)----------,

SIGIN

(1)-------1

SIGIN

(2)-------,

SIGIN

(3)------1

X2

CCLK

_----X-'_/C_LK-I

CLOCK LOGIC

&

PROGRAM

COUNTER

'EXTERNAL

COMPONENTS

1

VREF

Figure 3-1. 2920 Block Diagram

3-1

1------

SIGOUT

(0)

1--------

SIGOUT

(,)

1-------

SIGOUT

(2)

DMUX

1--------

SIGOUT

(3)

&

s&H's

1--------_

SIGOUT

(4)

1------

SIGOUT

(5)

1--------

SIGOUT (6)

I------SIGOUT

(7)

M2

Page 27

THE

2920

SIGNAL PROCESSOR

3.1.2 Analog Operations

The basic operation

of

the 2920 can be seen by assuming

that an input signal

is

to be processed, for example by a

digital filter,

and

outputted

as

an

analog signal. Under

program control, one

input

would be selected from the

four possible inputs,

and

the signal sampled

and

held.

This signal would then be converted to a digital word

with up

to

9 bits

of

linear conversion (sign bit

and

8

amplitude bits).

The bits are formed by a successive approximation

AID

conversion

and

stored in the DAR. This DAR register

is

the interface between the analog

and

digital sections

of

the 2920. During

AID

conversion, the DAR accum-

ulates each bit

of

the digital word until conversion

is

complete.

This word may then be loaded into a scratch pad RAM

location for further processing. When outputting a

value, the 9 most significant bits

of

a RAM location are

loaded into the DAR. Under program control, the DAR

drives the

01

A converter, whose

output

can be routed

to any

of

8 analog outputs by the

output

demultiplexer

and

S&Hs.

3.1.3 Digital Operations

The digital

part

of

the 2920 will be operating

simultaneously with the above analog operations.

For

example, during a 9-bit

AID

conversion, a 3-pole

lowpass filter could be realized using the digital cir-

cuitry. The digital loop includes the 2-port addressable

40-word RAM, a binary shifter,

and

the ALU. Under

program control, two 25-bit locations in RAM are

simultaneously addressed, with the

data

from the A

address passing through the binary shifter. This shifter

allows scaling from 22 (a 2-bit left shift) to

2-

13

(a 13-bit

right shift). The scaled A value

and

the unscaled B value

are then propagated to the

ALU

as operands.

The

ALU operates

on

these values with digital instruc-

tions specified by the

program.

The

25-bit result

of

that

operation

is

loaded into the B address location

of

the

RAM.

What

makes the 2920 fast enough for real-time

processing

is

that

the entire set

of

actions (analog opera-

tion, dual memory fetch, binary shift,

ALU

execution,

and

write back to RAM can take place in as little as 400

nanoseconds (depending

on

the clock rate).

3-2

3.2 A Closer Look at the Functional

Elements

3.2.1 EPROM Section

The

EPROM

section contains 4608 bits

of

user pro-

grammable

and

erasable read-only memory. In normal

operation

of

the 2920, i.e., in the RUN mode, it

is

arranged as

192

words

of

24

bits each. Each word corresponds to one 2920 instruction. During programming,

each 24-bit word

is

treated as six 4-bit nibbles; i.e., in

PROGRAM

mode the

EPROM

appears as 1152 words

of

four bits each. Figure 3-2 shows the 2920 pin connec-

tions for the RUN and

PROG

mode.

Run

Mode-During

the RUN

mode

the

EPROM

section acts as the system controller. Each 24-bit control

word contains bit patterns that determine the operations

to be performed by the analog

and

arithmetic sections.

The control word

is

composed

of

five fields,

of

which

one controls the analog section

and

the remaining four

control the arithmetic section.

The

four arithmetic sec-

tion control fields include the two 6-bit fields which

identifies RAM locations, a 4-bit scaler control field

and

a 3-bit ALU control field.

In the RUN mode,

EPROM

word addresses

are

numbered from 0 to 191. In

normal

operation

allioca-

tions are accessed in sequence

and

no program jumps

are allowed.

The

EPROM

program

counter returns to

location

0

upon

completion

of

execution

of

the com-

mand in word 191,

or

when

an

EOP

instruction

is

encountered in the analog control instruction field.

The

EOP

feature allows the

program

to be terminated at the

end

of

a user's program shorter

than

192

words. Place-

ment

of

the

EOP

is

explained below.

The

EPROM

may

be

thought

of

as a crystal-

or

clock-

controlled cycle generator as

program

length determines

the sampling frequency

of

the analog signals.

If

an

input

is

sampled once per

program

pass, the sampling fre-

quency

is

liNT

where N

is

the number

of

words

(instructions) in the program

and T is

the time required

to execute one instruction.

The

EPROM

fetchlexecute cycle

is

pipelined four deep,

meaning

that

the next four instructions are being

fetched while the previously fetched instructions are

being executed. Although otherwise invisible to the

user, this technique requires

that

the

EOP

instruction be

inserted in a word with an address divisible by four,

Page 28

THE

2920

SIGNAL

PROCESSOR

e.g., program location

0,4,

....

,188.

The

EOP

does

not

take effect until the three following instructions are

executed.

An

open

drain active low logic pin RST may be used to

display the presence

of

an

EOP

signal

or

to apply an

external active-low reset signal (which forces a

jump

to

EPROM

location zero). This

output

can sink 2.5mA,

which allows connecting

a 2.2K pull-up resistor,

or

one

TTL

load

with a 6.2K pull-up.

If

the internal

EOP

instruction

is

not

used, the pin may be tied to VCC

or

driven by a

TTL

or

CMOS gate.

An

OR-tied connection

may also be used. In normal operation, the 2920 does

not use a reset signal,

but

one may be useful in

applications requiring synchronization

of

the 2920

and

other equipment.

Proper

operation

of

the

EOP

instruc-

tion requires-

an

external pull-up resistor

on

the RST

pin.

Since RST

and

EOP

are internally equivalent functions,

an externally generated RST must

conform

to the same

rules as the

program

placement

of

EOP.

CCLK pro-

vides this cycle indication

and

should be used to strobe

an externally supplied RST signal.

Two pins associated with the

PROGRAM/RUN

mode

selection are

VSP

and

RUN/PROG.

Both pins should

be tied to

GRDD

(digital ground) for RUN mode.

EPROM

Program

Mode-During

programming,

each 24-bit

EPROM

word

is

treated as six 4-bit nibbles,

with the result

that

the

EPROM

is

programmed as if it

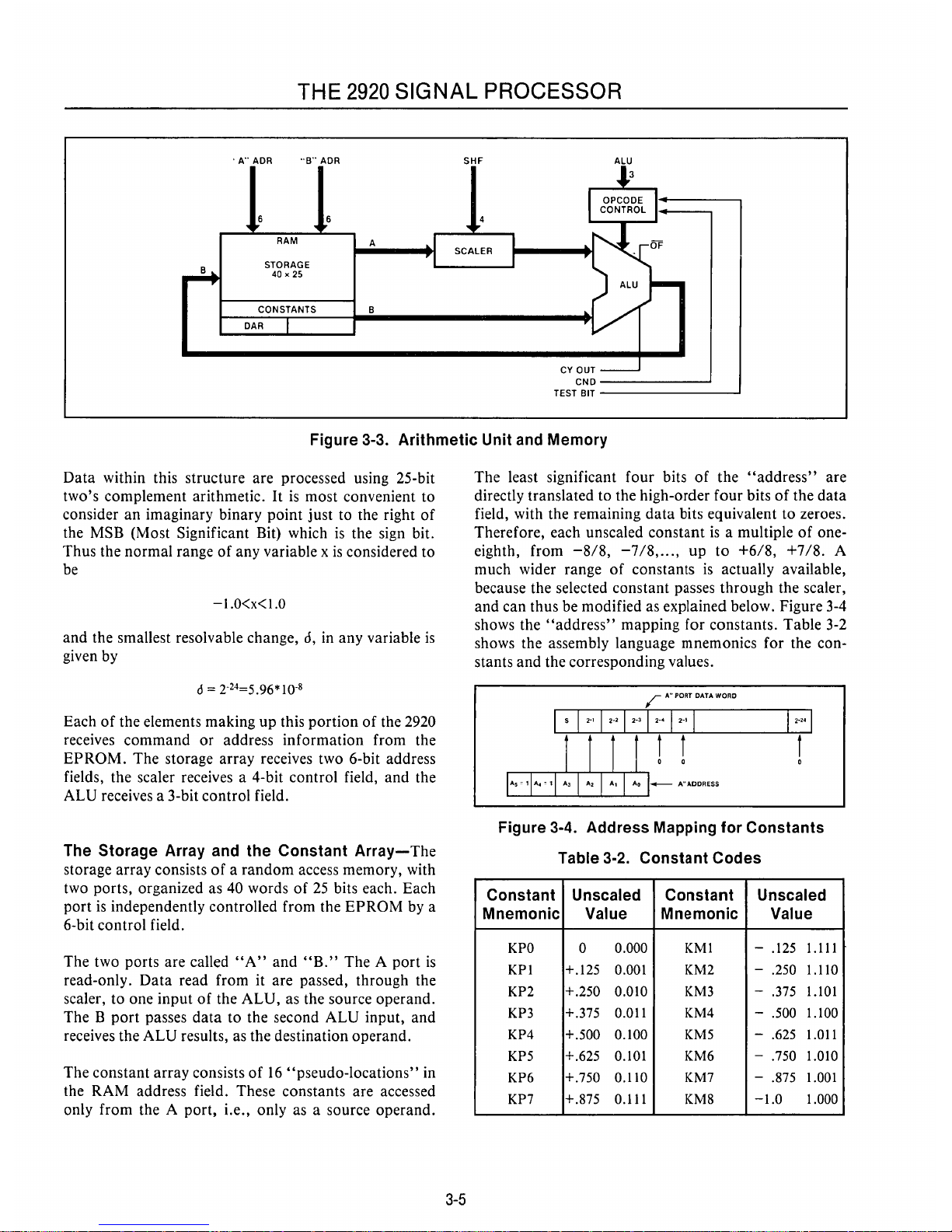

were organized as 1152 x 4. Table

3-1

shows the rela-

tionship between the control fields

and

the bit positions

in each nibble. (See the sections below

on

the arithmetic

and

analog sections for details

on

the significance

of

each control bit.)

Many

of

the pins

of

the 2920

perform

different func-

tions in the

PROG

mode

than

they

do

in the RUN

mode. These differences are noted in Figure 3-2.

Note

that

for the 2920 pin outs as shown in Figure 3-2,

the power supply conventions are different for RUN

and

PROG

mode. These conventions allow the pro-

grammer designer to use

popular

TTL

family products

as a basis for design.

With

the exception

of

the power

connections, VSP

is

the only pin

that

requires other

than

5 volt logic levels.

3-3

In the

PROG

mode, the four pins labelled

DO

through

D3

are used for

both

data

input

and

output.

Their direc-

tion

is

controlled by the

PROG/VER

pin. A high level

on

this pin switches to

input

mode, a low to

output.

This

feature allows the programmed

data

to be verified

before proceeding to the next address. The

input

data

must be presented in true form (logical 1 =high, logical

O=low)

but

is

read back complemented (logical 1 =low,

10gicaI0=high).

The

internal counters are incremented during the falling

edge

of

INCR. 1152

INCR

transitions will complete the

full

program

cycle.

To

initialize at nibble address 0,

RST must be pulsed active (low)

and

an

INCR

must be

issued.

For

programming the

RUN/PROG

pin

must

be tied to

VBB, the VCC pin to +5 volts,

and

VSP (the high

voltage programming pin) should be pulsed from

5.0 ±

.5

volts to +25 ± 1 V @ 15mA max.

The

data

pins

DO

through

D3

have open drains

in

the

output

direction;

thus pull up resistors are required.

Table

3-1.

2920

Control

Bit

Assignments/Programming

Nibble

Bit

Assignment

Nibble

Number

MSB LSB

(3) (2)

(1

) (0)

0

ADFO

ADK2

ADKI

ADKO

1

A2

Bl

Al

ADFI

2

A4

B3

A3

B2

3

AO

B5

A5

B4

4

S2

Sl

SO

BO

5

L2

Ll

LO

S3

3.2.2

Arithmetic

Unit

and

Memory

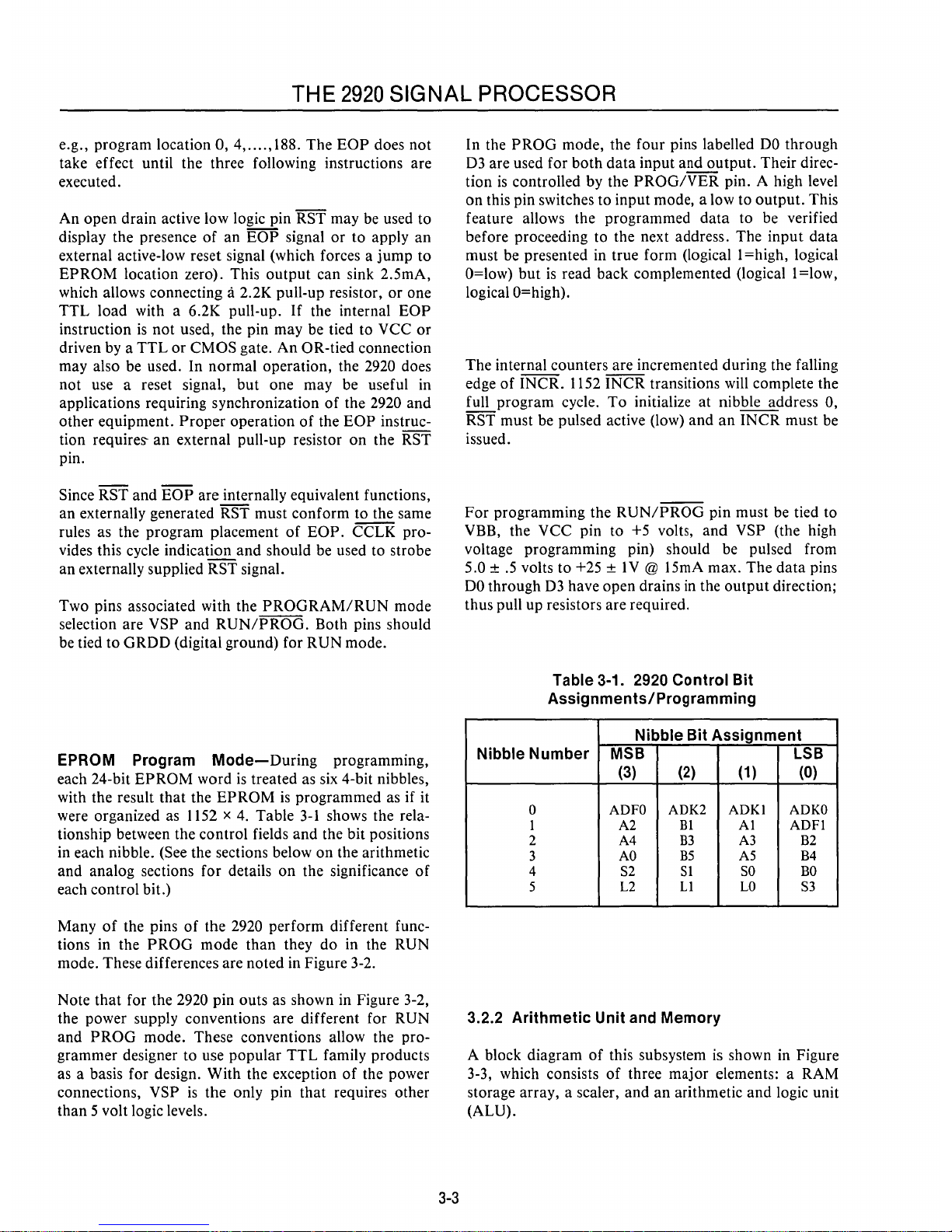

A block diagram

of

this subsystem is shown in Figure

3-3, which consists

of

three

major

elements: a RAM

storage array, a scaler,

and

an

arithmetic

and

logic unit

(ALU).

Page 29

TH E

2920

SIGNAL

PROCESSOR

PIN

DESCRIPTIONS

(RUN

MODE)

Symbol

Function

SIGOUT

8

PinS

corresponding

to the 8

demultl-

plexed analog

outputs

(0-7)

GROA

Analog signal

ground

held at

or

near

GROO tYPically

CAP,

& CAP2

External

capacitor

connections

for

the

Input

signal sample and

hold

CirCUit

VREF

Input

Reference Voltage

SIGIN

4 pins

corresponding

to the 4

multi-

plexed analog Inputs (0-3)

VBB

Most

negative

power

Pin set at -5 volts

dUring run mode

(different

voltage

In

program

mode)

X1/CLK

Clock

Input

when uSing external

clock

signals,

OSCillator

Input

for

external

crystal when uSing Internal

clock

X2

OSCillator

Input

for

external crystal when

uSing Internal

clock

GROO Digital

ground

Vee

5 volts In run mode

CCLK

Internal

fetch

cycle clock

output

The

failing

edge

designates

the

START

of

a

new

PROM

fetch

cycle.

CCLK

IS

1/16

of

X1/CLK rate.

RUN/PROG

Mode

control

tied

to

GROO In run mode

(different

voltage

In

program

mode)

RST/EOP

Low

RST

input

initializes

program

fetch

counter

to

first

location.

As an

output

It

Signifies

EOP

instruction

present (open

drain,

active

low).

PIN

DESCRIPTIONS

(PROGRAM

MODE)

Symbol

00,01,02,03

Function

4

pins

carrying EPROM program

data

for

both

input

and

output

(open drain, active

low

output;

active

high

Input)

VB"

VB2

VB3

Digital

ground

In

PROGRAM mode

(dif-

ferent voltage for RUN mode)

VS"

VS2,

VS3

+5 volts In

PROGRAM

mode

(function

changes

for

RUN

mode)

RUN/PROG

Mode

control

pin tied to

VBB

for

PROGRAM

mode (voltage

changes

for

RUN

mode)

INCR

Input

pulse Increments the

nibble

(4-blts)

counter

In PROG

mode

(func-

tion

changes

In

RUN

mode)

VSP

PROGIVER

EPROM po\',er pin

+5

volts

for

VERIFY

mode and +25 volts

for

PROGRAM

mode