Integrated Device Technology Inc IDT54FCT162511ATPV, IDT54FCT162511ATPVB, IDT54FCT162511CTE, IDT54FCT162511CTEB, IDT54FCT162511CTPAB Datasheet

...

Integrated Device Technology, Inc.

FAST CMOS 16-BIT

REGISTERED/LATCHED

TRANSCEIVER WITH PARITY

IDT54/74FCT162511AT/CT

FEATURES:

• 0.5 MICRON CMOS Technology

• Typical tsk(o) (Output Skew) < 250ps, clocked mode

• Low input and output leakage ≤1µA (max)

• ESD > 2000V per MIL-STD-883, Method 3015;

> 200V using machine model (C = 200pF, R = 0)

• Packages include 25 mil pitch SSOP, 19.6 mil pitch TSSOP,

15.7 mil pitch TVSOP and 25 mil pitch Cerpack

• Extended commercial range of –40°C to +85°C

•VCC = 5V ±10%

• Balanced Output Drivers: ±24mA (commercial)

±16mA (military)

• Series current limiting resistors

• Generate/Check, Check/Check modes

• Open drain parity error allows wire-OR

DESCRIPTION:

The FCT162511AT/CT 16-bit registered/latched transceiver

with parity is built using advanced dual metal CMOS technology. This high-speed, low-power transceiver combines D-

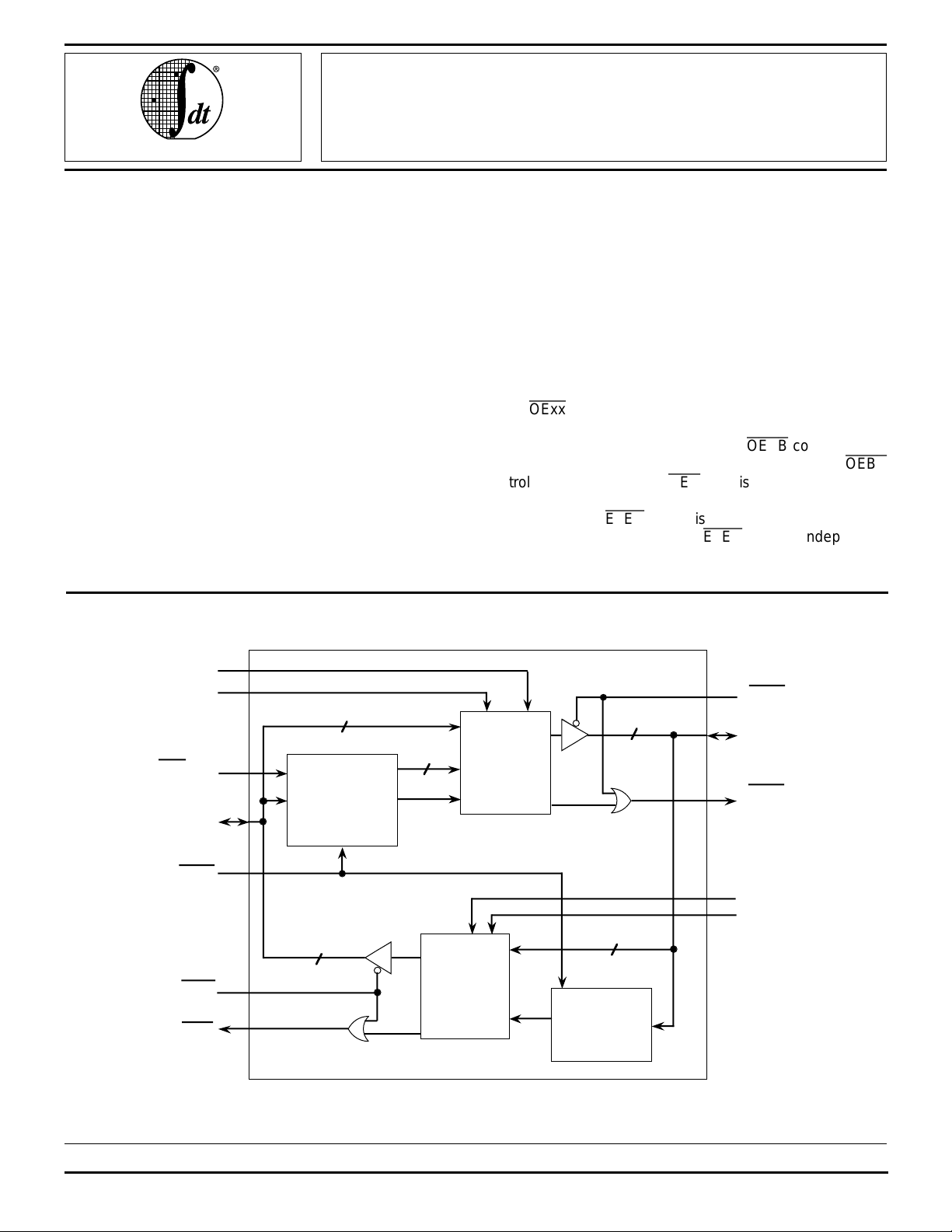

SIMPLIFIED FUNCTIONAL BLOCK DIAGRAM:

type latches and D-type flip-flops to allow data flow in transparent, latched or clocked modes. The device has a parity

generator/cheker in the A-to-B direction and a parity checker

in the B-to-A direction. Error checking is done at the byte level

with separate parity bits for each byte. Separate error flags

exits for each direction with a single error flag indicating an

error for either byte in the A-to-B direction and a second error

flag indicating an error for either byte in the B-to-A direction.

The parity error flags are open drain outputs which can be tied

together and/or tied with flags from other devices to form a

single error flag or interrupt. The parity error flags are enabled

by the

OExx

control pins allowing the designer to disable the

error flag during combinational transitions.

The control pins LEAB, CLKAB and

tion in the A-to-B direction while LEBA, CLKBA and

control the B-to-A direction.

GEN

/CHK is only for the selection

OEAB

control opera-

OEBA

of A-to-B operation, the B-to-A direction is always in checking

mode. The ODD/

directions. Except for the ODD/

EVEN

select is common between the two

EVEN

control, independent

operation can be achieved between the two directions by

using the corresponding control lines.

LEAB

CLKAB

GEN/CHK

A0-15

PA1,2

ODD/EVEN

OEBA

PERA

(Open Drain)

Data

Byte

Parity

Generator/

Checker

Parity, data

18

16

Parity

2

Latch/

Register

Latch/

Register

Parity, data

Parity, Data

18

Byte

Parity

Checking

18

OEAB

B0-15

PB1,2

PERB

(Open Drain)

LEBA

CLKBA

2916 drw 01

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES AUGUST 1996

1996 Integrated Device Technology, Inc. 5.11 DSC–2916/5

1

IDT54/74FCT162511AT/CT

FAST CMOS 16-BIT REGISTERED/LATCHED TRANSCEIVER WITH PARITY MILITARY AND COMMERCIAL TEMPERATURE RANGES

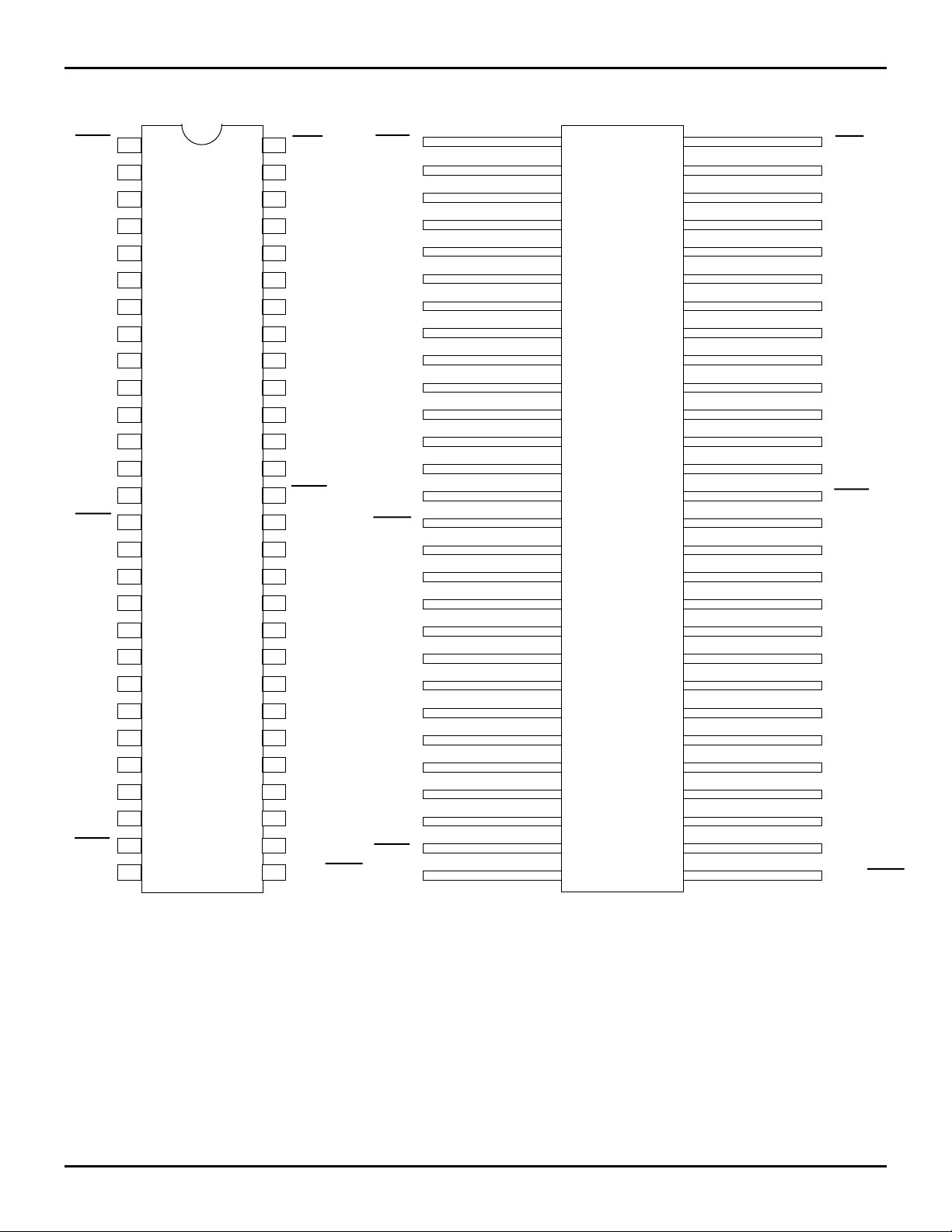

FUNCTIONAL BLOCK DIAGRAM

ODD/EVEN

OEAB

LEBA

CLKBA

CLKAB

LEAB

A0 - A

OEBA

PA

A8 - A

C

7

D

C

D

C

D

B0 - B

7

C

D

P

1

O

C

D

I

C

D

C

PB

1

D

P

C

D

C

15

D

C

D

C

D

B8 - B

15

C

D

PA

2

GEN/CHK

PERA

(Open Drain)

P

O

C

D

I

C

D

PB

2

C

D

C

D

C

D

5.11 2

C

D

C

D

PERB

(Open Drain)

C

D

P

2916 drw 02

IDT54/74FCT162511AT/CT

FAST CMOS 16-BIT REGISTERED/LATCHED TRANSCEIVER WITH PARITY MILITARY AND COMMERCIAL TEMPERATURE RANGES

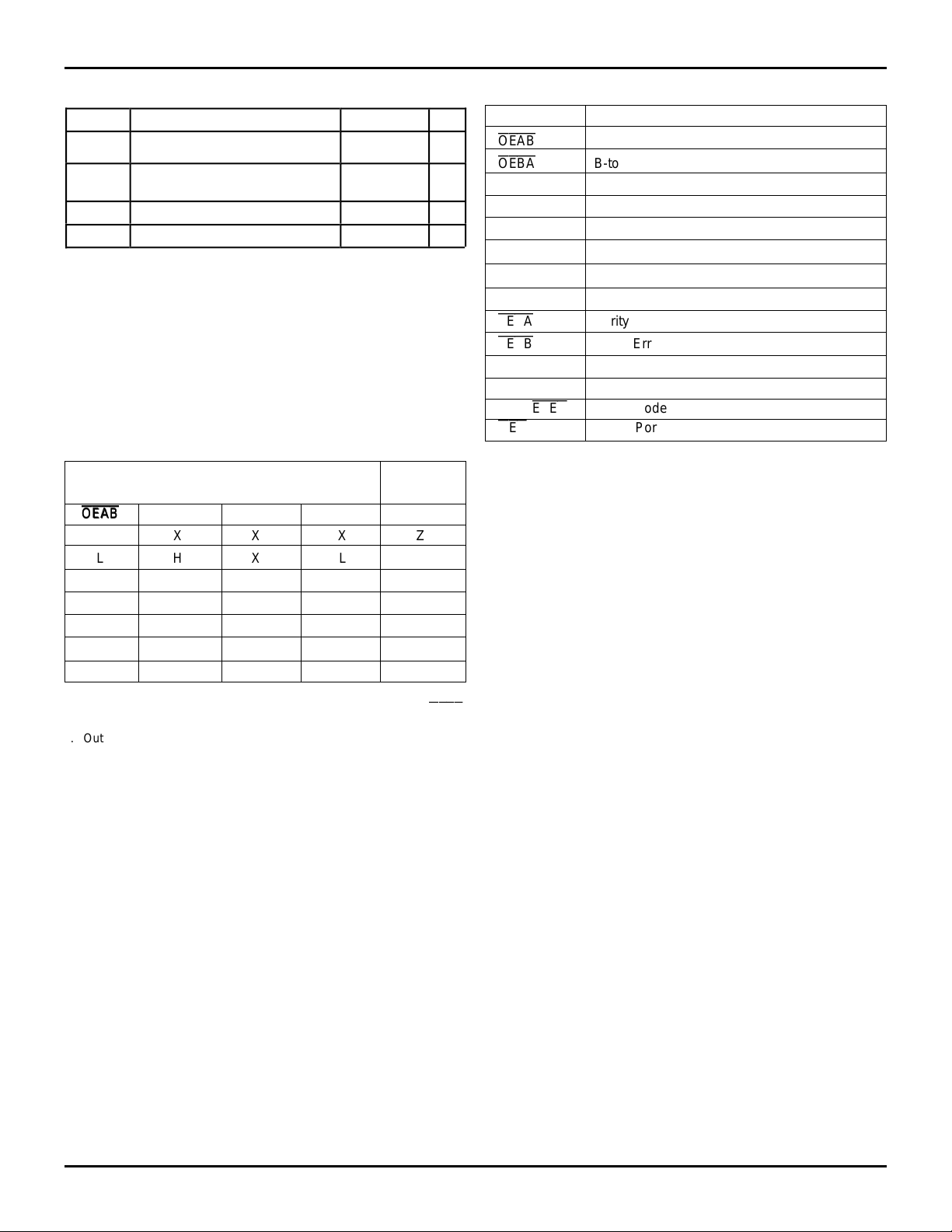

PIN CONFIGURATIONS

OEAB

LEAB

PA

GND

A

A

V

CC

A

A

A

A

A

A

GND

PERA

A

A

A

A

A

A

V

CC

A

A

GND

PA

OEBA

LEBA

1

2

1

3

4

0

1

5

6

7

2

3

4

5

6

7

8

9

10

11

12

13

8

9

10

11

12

13

14

15

16

17

18

19

20

21

SO56-1

SO56-2

SO56-3

22

14

15

2

23

24

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

3225

31

30

29

GEN/CHK

CLKAB

PB

1

GND

0

B

B

1

V

CC

2

B

B

3

B

4

B

5

B

6

B

7

PERB

GND

B

8

B

9

B

10

B

11

B

12

B

13

V

CC

14

B

B

15

GND

2

PB

CLKBA

ODD/EVEN

OEAB

LEAB

PA

GND

A

A1

VCC

A2

A3

A4

A5

A6

A7

GND

PERA

A

A9

A

A11

A12

A

VCC

A14

A

GND

PA2

OEBA

LEBA

1

0

8

10

13

15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

26

27

28

E56-1

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

3225

31

30

29

GEN/CHK

CLKAB

PB1

GND

B

0

B1

VCC

2

B

B3

B4

B5

B6

B7

PERB

GND

8

B

B9

B10

B11

B12

B13

VCC

B

14

B15

GND

PB

2

CLKBA

ODD/EVEN

SSOP/

TSSOP/TVSOP

TOP VIEW

2916 drw 03

CERPACK

TOP VIEW

2916 drw 04

5.11 3

IDT54/74FCT162511AT/CT

FAST CMOS 16-BIT REGISTERED/LATCHED TRANSCEIVER WITH PARITY MILITARY AND COMMERCIAL TEMPERATURE RANGES

ABSOLUTE MAXIMUM RATINGS

(1)

Symbol Description Max. Unit

(2)

VTERM

VTERM

Terminal Voltage with Respect to

GND

(3)

Terminal Voltage with Respect to

GND

–0.5 to +7.0 V

–0.5 to

CC +0.5

V

V

TSTG Storage Temperature –65 to +150 °C

IOUT DC Output Current –60 to +120 mA

NOTES:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating

only and functional operation of the device at these or any other conditions

above those indicated in the operational sections of this specification is

not implied. Exposure to absolute maximum rating conditions for

extended periods may affect reliability.

2. Open drain and all device terminals except FCT162XXXT Output and I/O

terminals.

3. Output and I/O terminals for FCT162XXXT.

FUNCTION TABLE

(1,4)

2916 lnk 01

Inputs Outputs

OEAB

OEAB

LEAB CLKAB Ax Bx

HXX XZ

LHX LL

LHX HH

LL↑ LL

LL↑ HH

LLL XB

LLH XB

NOTES: 2916 tbl 02

1. A-to-B data flow is shown. B-to-A data flow is similar but uses

LEBA, and CLKBA.

2. Output level before the indicated steady-state input conditions were

established.

3. Output level before the indicated steady-state input conditions were

established, provided that CLKAB was HIGH before LEAB went LOW.

4. H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

Z = High Impedance

↑ = LOW-to-HIGH Transition

(2)

(3)

OEBA

PIN DESCRIPTION

Pin Names Description

OEAB

OEBA

LEAB A-to-B Latch Enable Input

LEBA B-to-A Latch Enable Input

CLKAB A-to-B Clock Input

CLKBA B-to-A Clock Input

Ax A-to-B Data Inputs or B-to-A 3-State Outputs

Bx B-to-A Data Inputs or A-to-B 3-State Outputs

PERA

PERB

(1)

PAx

PBx B-to-A Parity Input, A-to-B Parity Output

ODD/

EVEN

GEN

/CHK A to B Port Generate or Check Mode Input

NOTES:

1. The PAx pin input is internally disabled during parity generation. This

means that when generating parity in the A to B direction there is no need

to add a pull up resistor to guarantee state. The pin will still function

properly as the parity output for the B to A direction.

,

A-to-B Output Enable Input (Active LOW)

B-to-A Output Enable Input (Active LOW)

Parity Error (Open Drain) on A Outputs

Parity Error (Open Drain) on B Outputs

A-to-B Parity Input, B-to-A Parity Output

Parity Mode Selection Input

2916 tbl 03

5.11 4

Loading...

Loading...