Page 1

VHF TRANSCEIVER

S-14406XZ-C1

Sep. 2007

Page 2

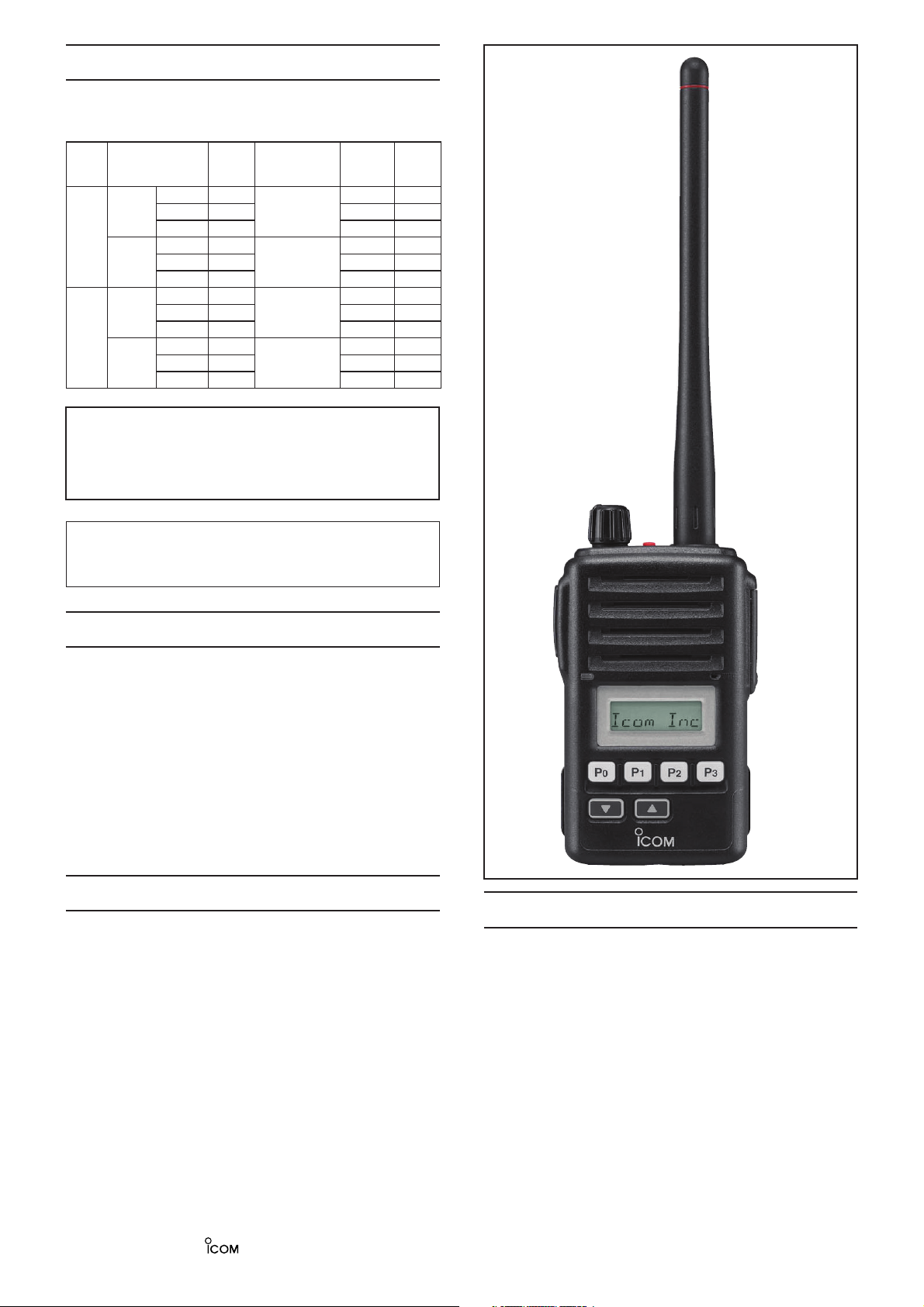

INTRODUCTION

This service manual describes the latest service information

for the IC-F50V/F51V VHF TRANSCEIVER at the time of

publication.

Model Version Symbol

USA [A]

USA

USA-01 [B] Yes N/A

F50V

Export

Europe

F51V

USA-02 [C] Yes Yes

EXP [D]

EXP-01 [E] Yes N/A

EXP-02 [F] Yes Yes

EUR [G]

EUR-01 [H] Yes N/A

EUR-02 [I] Yes Yes

CHN [J]

China

CHN-01 [K] Yes N/A

CHN-02 [L] Yes Yes

UNIT ABBREVIATIONS:

F=FRONT UNIT

M=MAIN UNIT

V=VR UNIT

CO=CONNECT UNIT

Channel

spacing

(kHz)

15.0/30.0

12.5/25.0

12.5/20.0/25.0

12.5/25.0

Vibration

Voice

storage

N/A N/A

N/A N/A

N/A N/A

N/A N/A

To upgrade quality, any electrical or mechanical parts and

internal circuits are subject to change without notice or

obligation.

CAUTION

NEVER connect the transceiver to an AC outlet or to a DC

power supply that uses more than specified. This will ruin

the transceiver.

DO NOT reverse the polarities of the power supply when

connecting the transceiver.

DO NOT apply an RF signal of more than 20 dBm (100 mW) to

the antenna connector. This could damage the transceiver’s

front-end.

ORDERING PARTS

Be sure to include the following four points when ordering

replacement parts:

1. 10-digit Icom parts numbers

2. Component name

3. Equipment model name and unit name

4. Quantity required

<ORDER EXAMPLE>

1110003491 S.IC TA31136FNG IC-F50V MAIN UNIT 5 pieces

8820001210 Screw 2438 screw IC-F51V Top cover 10 pieces

Addresses are provided on the inside back cover for your

convenience.

REPAIR NOTES

1. Make sure the problem is internal before disassembling

the transceiver.

2. DO NOT open the transceiver until the transceiver is

disconnected from its power source.

3. DO NOT force any of the variable components. Turn

them slowly and smoothly.

4. DO NOT short any circuits or electronic parts. An

insulated tuning tool MUST be used for all adjustments.

5. DO NOT keep power ON for a long time when the

transceiver is defective.

6. DO NOT transmit power into a Standard Signal

Generator or a Sweep Generator.

7. ALWAYS connect a 50 dB to 60 dB attenuator between

the transceiver and a Deviation Meter or Spectrum

Analyzer when using such test equipment.

8. READ the instructions of test equipment throughly

before connecting a test equipment to the transceiver.

Icom, Icom Inc. and

logo are registered trademarks of Icom Incorporated (Japan) in the United States, the United

Kingdom, Germany, France, Spain, Russia and/or other countries.

Page 3

CONTENTS

SECTION 1 SPECIFICATIONS

SECTION 2 INSIDE VIEWS

SECTION 3 DISASSEMBLY INSTRUCTIONS

SECTION 4 CIRCUIT DESCRIPITON

4-1 RECEIVER CIRCUITS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4-2 TRANSMITTER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4-3 FREQUENCY SYNTHESIZER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

4-4 OTHER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

4-5 VOLTAGE BLOCK DIAGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

4-6 CPU (F: IC401) PORT ALLOCATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

SECTION 5 ADJUSTMENT PROCEDURES

5-1 PREPARATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5-2 FREQUENCY ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

5-3 TRANSMIT ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

5-4 RECEIVE ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

SECTION 6 PARTS LIST

SECTION 7 MECHANICAL PARTS

SECTION 8 BOARD LAYOUTS

SECTION 9 BLOCK DIAGRAM

SECTION 10 VOLTAGE DIAGRAM

FRONT UNIT (Incl. CONNECT and VR UNITS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-1

MAIN UNIT (Left side) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-2

MAIN UNIT (Right side) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-3

Page 4

SECTION 1 SPECIFICATIONS

M GENERAL

• Frequency coverage : TX/RX 136–174 MHz

• Number of conventional channels : 128 ch / 8 banks

• Type of emission : Wide 16K0F3E (25.0 kHz)

• Antenna impedance : 50 Ω (Nominal)

• Operating temperature range : –30˚C to +60˚C; –22˚F to +140˚F [USA], [EXP], [CHN]

• Power supply requirement (nominal) : Specified Icom's battery packs only (7.2 V DC; negative ground)

• Current drain (Approx.) : Receiving 85 mA (stand-by)

• Dimensions (Projections not included) : 56.0 (W)×97.0 (H)×36.4 (D) mm; 2

• Weight (Incl. BP-227) : Approx. 280 g; 9

M TRANSMITTER

• Output power : 5 W (High)/2 W (Low2)/1 W (Low1)

• Modulation : Variable reactance frequency modulation

• Maximum frequency deviation : ±5.0 kHz (Wide)

• Frequency stability : ±2.5 ppm

• Spurious emissions : 70 dB typ. [USA], [EXP], [CHN]

• Adjacent channel power : 70 dB min. (Wide, Middle)

• Audio harmonic distortion : 3% (at AF 1 kHz 40% deviation)

• FM Hum and noise (without CCITT filter)

[USA], [EXP], [CHN] only

• Residual modulation (with CCITT filter)

[EUR] only

• Limitting charact of modulator : 60–100% of max. deviation

• Microphone impedance : 2.2 k

Middle 14K0F3E (20.0 kHz) [EUR] only

Narrow 11K0F3E (12.5 kHz)

–25˚C to +55˚C [EUR]

500 mA (max. audio with internal speaker)

350 mA (max. audio with external speaker)

Transmitting 1.8 A (at 5.0 W)

0.7 A (at 1.0 W)

7

/8 oz.

±4.0 kHz (Middle) [EUR] only

±2.5 kHz (Narrow)

0.25 μW (≤1 GHz), 1.0 μW (>1 GHz) [EUR]

60 dB min. (Narrow)

: 40 dB min., 46 dB typ. (Wide)

34 dB min., 40 dB typ. (Narrow)

: 50 dB min., 55 dB typ. (Wide)

43 dB min., 53 dB typ. (Middle)

40 dB min., 50 dB typ. (Narrow)

Ω

7

/32 (W)×3 13⁄16 (H)×1 7⁄16 (D) in.

M RECEIVER

• Receive system : Double-conversion superheterodyne system

• Intermediate frequencies : 1st IF: 46.35 MHz, 2nd IF: 450 kHz

• Sensitivity : 0.25 μV typ. at 12 dB SINAD [USA], [EXP], [CHN]

–4 dBµ V (EMF) typ. at 20 dB SINAD [EUR]

• Squelch sensitivity (at threshold) : 0.25 μV typ. [USA], [EXP], [CHN]

–4 dBµ V (EMF) typ. [EUR]

• Adjacent channel selectivity : 70 dB min., 75 dB typ. (Wide, Middle)

• Spurious response : 70 dB

• Intermodulation rejection ratio : 70 dB min., 74 dB typ. [USA], [EXP], [CHN]

• Hum and noise (without CCITT filter)

[USA], [EXP], [CHN] only

• Hum and noise (with CCITT filter)

[EUR] only

• Audio output power

(at 5% distortion with an 8 Ω load)

• Audio output impedance : 8

Specifications are measured in accordance with TIA/EIA 603 ([USA], [EXP], [CHN]) or EN 300 086 ([EUR]).

All stated specifications are subject to change without notice or obligation.

60 dB min., 65 dB typ. (Narrow)

65 dB min., 67 dB typ. [EUR]

: 40 dB min., 45 dB typ. (Wide)

34 dB min., 40 dB typ. (Narrow)

: 45 dB min., 55 dB typ. (Wide)

43 dB min., 53 dB typ. (Middle)

40 dB min., 50 dB typ. (Narrow)

: 0.7 W typ. (max. audio with internal speaker)

0.5 W typ. (max. audio with external speaker)

Ω

1 - 1

Page 5

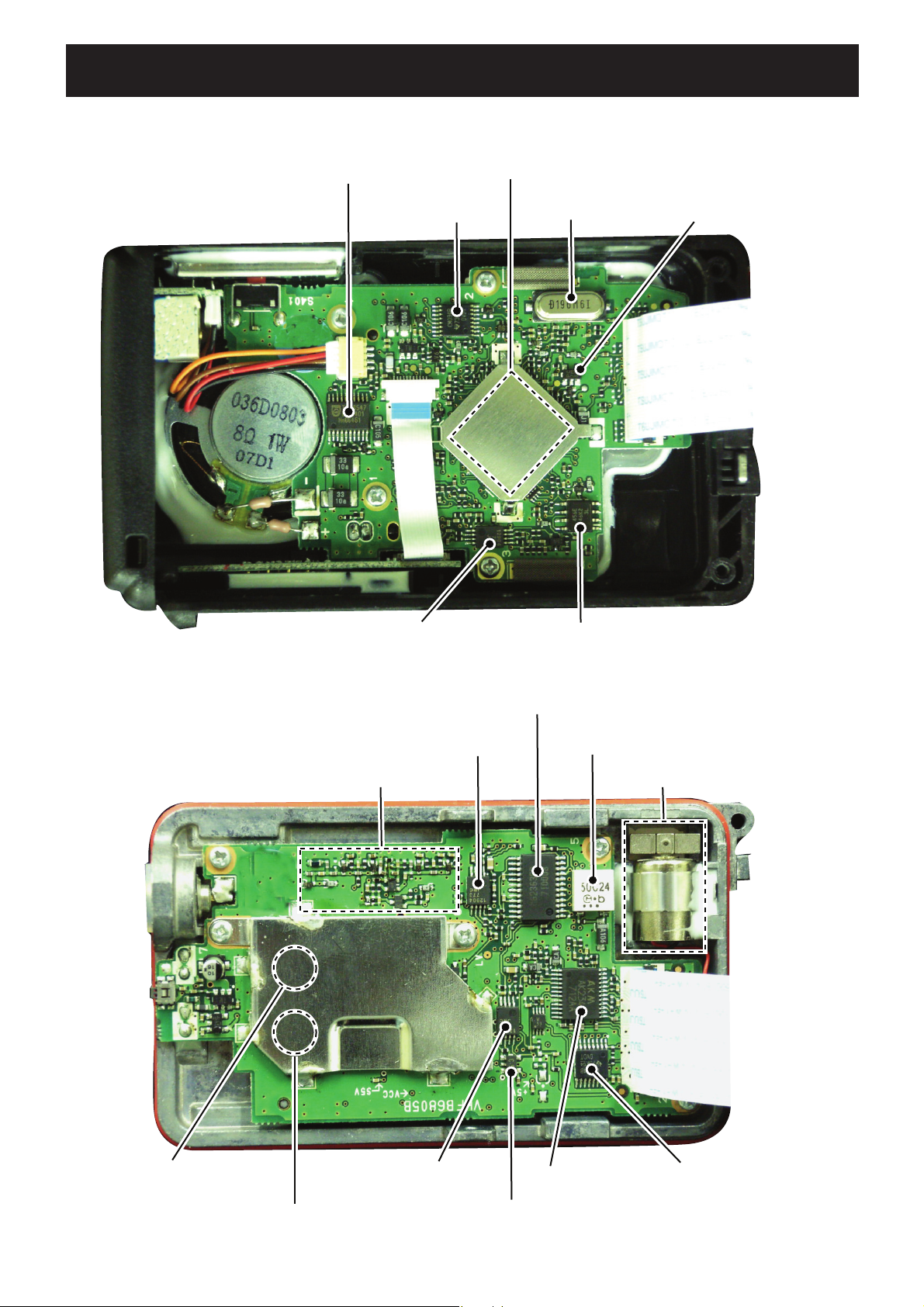

SECTION 2 INSIDE VIEWS

• FRONT UNIT

AF POWER AMP

(IC405: TDA8547TS)

EXPANDER

(IC410: CD4094BPWR)

CPU

(IC401: HD64F2268TFV)

CPU CLOCK

(X401: CR-764)

RESET IC

(IC408: BD5242G)

• MAIN UNIT

MIC AMP

(IC407: NJM12904V)

AF BUFFER, AF MIXER

(IC5: NJM12904V)

RF CIRCUITS

EEPROM

(IC409: HN58X24256FPIE)

DAC

(IC6: M62363FP-650C)

DISCRIMINATOR

(X1: CDBKB450KCAY24)

VIBRATION MOTOR

(MF1: QX10A(R5.5X3))

TX POWER AMP

(Q7: RD07MVS2-T112)

DRIVE AMP

(Q8: RD01MUS1-T113)

AF BUFFER

(IC6: NJM12904V)

LOCK VOLTAGE SWITCH

(IC17: TC4S66F)

2 - 1

BASE BAND IC

(IC10: AK2346)

EXPANDER

(IC12: CD4094BPWR)

Page 6

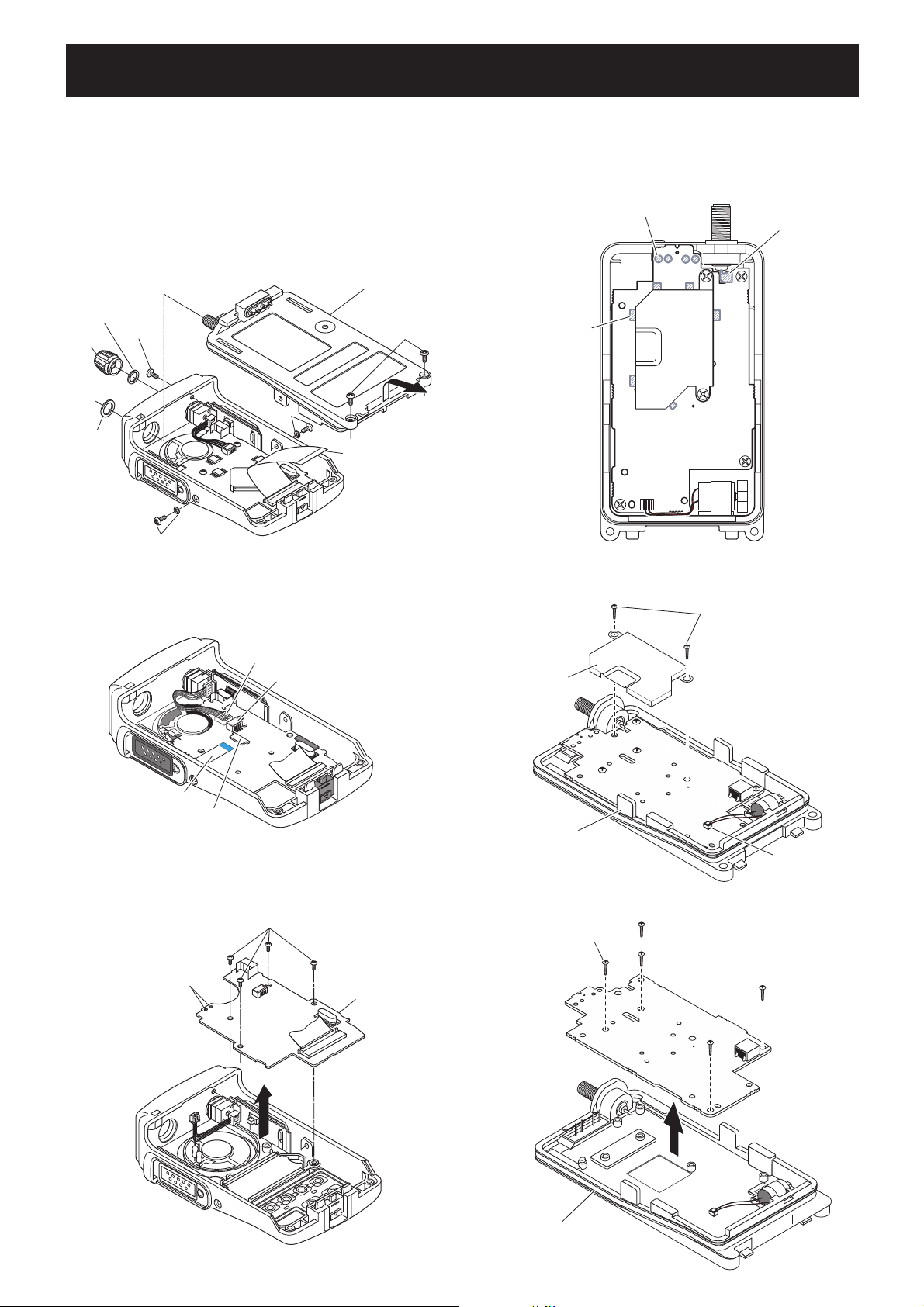

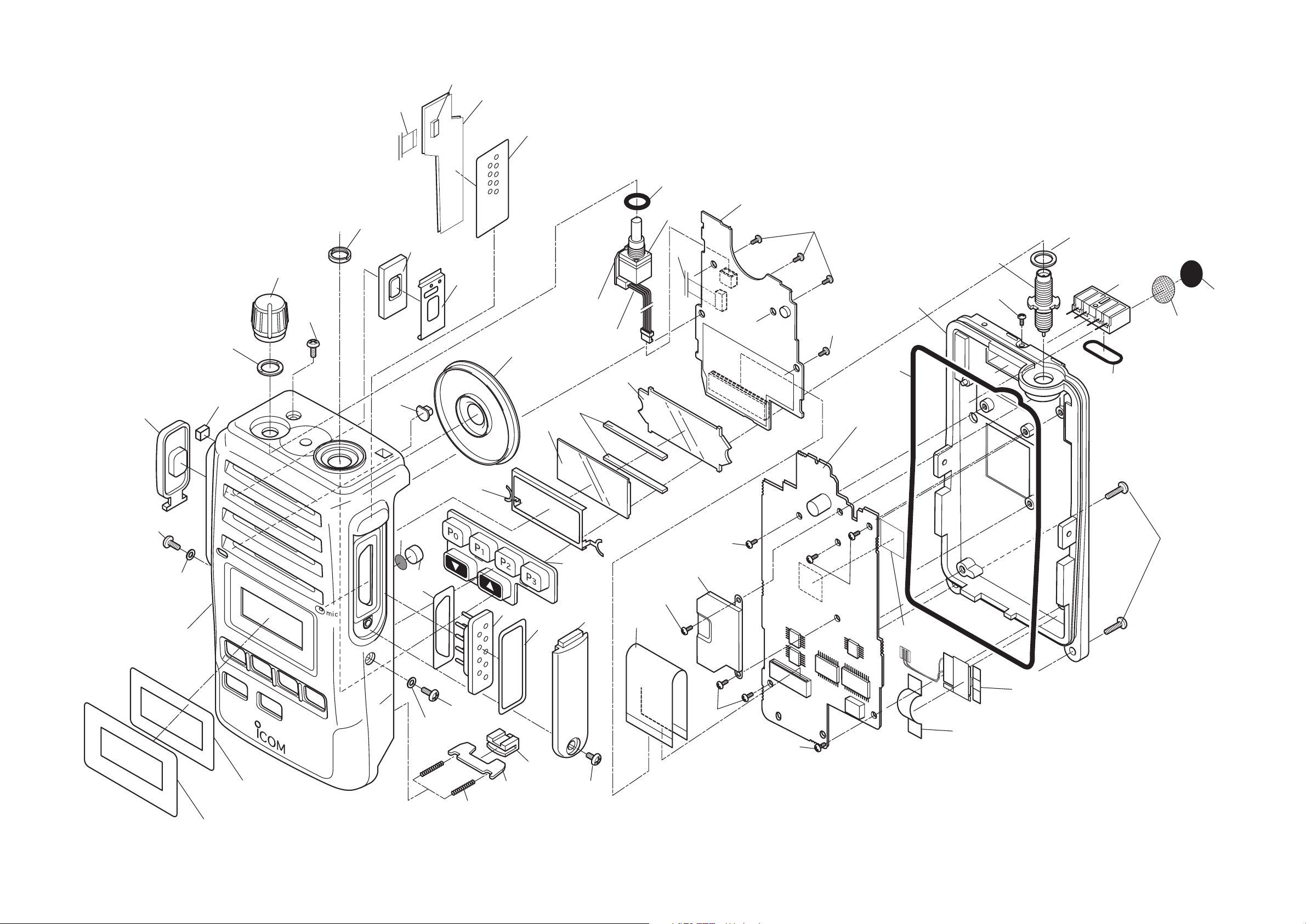

SECTION 3 DISASSEMBLY INSTRUCTION

1. REMOVING THE CHASSIS UNIT

q Unscrew the ANT nut, and remove the VR knob.

w Remove the VR washer, and unscrew the top screw.

e Unscrew side screws and washers.

r Unscrew bottom screws.

t Take off the CHASSIS UNIT in the direction of the

arrow.

y Disconnect the flat cable from the CHASSIS UNIT

(MAIN UNIT).

CHASSIS

VR washer

VR knob

ANT nut

Side screw & Washer

Top screw

Side screw & washer

Bottom screws

Flat cable

2. REMOVING THE FRONT UNIT

q Disconnect the VR cable from J402.

w Disconnect the flat cable from J403.

3. REMOVING THE MAIN UNIT

q Unsolder 6 points from the shield cover.

w Unsolder 4 points from the contact spring.

e Unsolder 1 point from the antenna connector.

Unsolder ×4

(contact spring)

Unsolder ×6

(shield cover)

MAIN UNIT

Unsolder ×1

(antenna connector)

r Unscrew 2 screws, and remove the shield cover.

t

Disconnect the motor connector* from the MAIN UNIT.

Unscrew ×2

VR cable

J402

Flat cable

J403

e Unscrew 4 screws.

r Unsolder 2 points (at the speaker leads).

t Take off the FRONT UNIT in the direction of the

arrow.

Unscrew ×4

Unsolder ×2

(Speaker leads)

FRONT UNIT

Shield cover

CHASSIS

*: Except [A], [D], [G], [J]

MAIN UNIT

Disconnect

(motor connector)

y Unscrew 5 screws, and take off the MAIN UNIT.

Unscrew ×5

MAIN UNIT

*

3 - 1

CHASSIS

Page 7

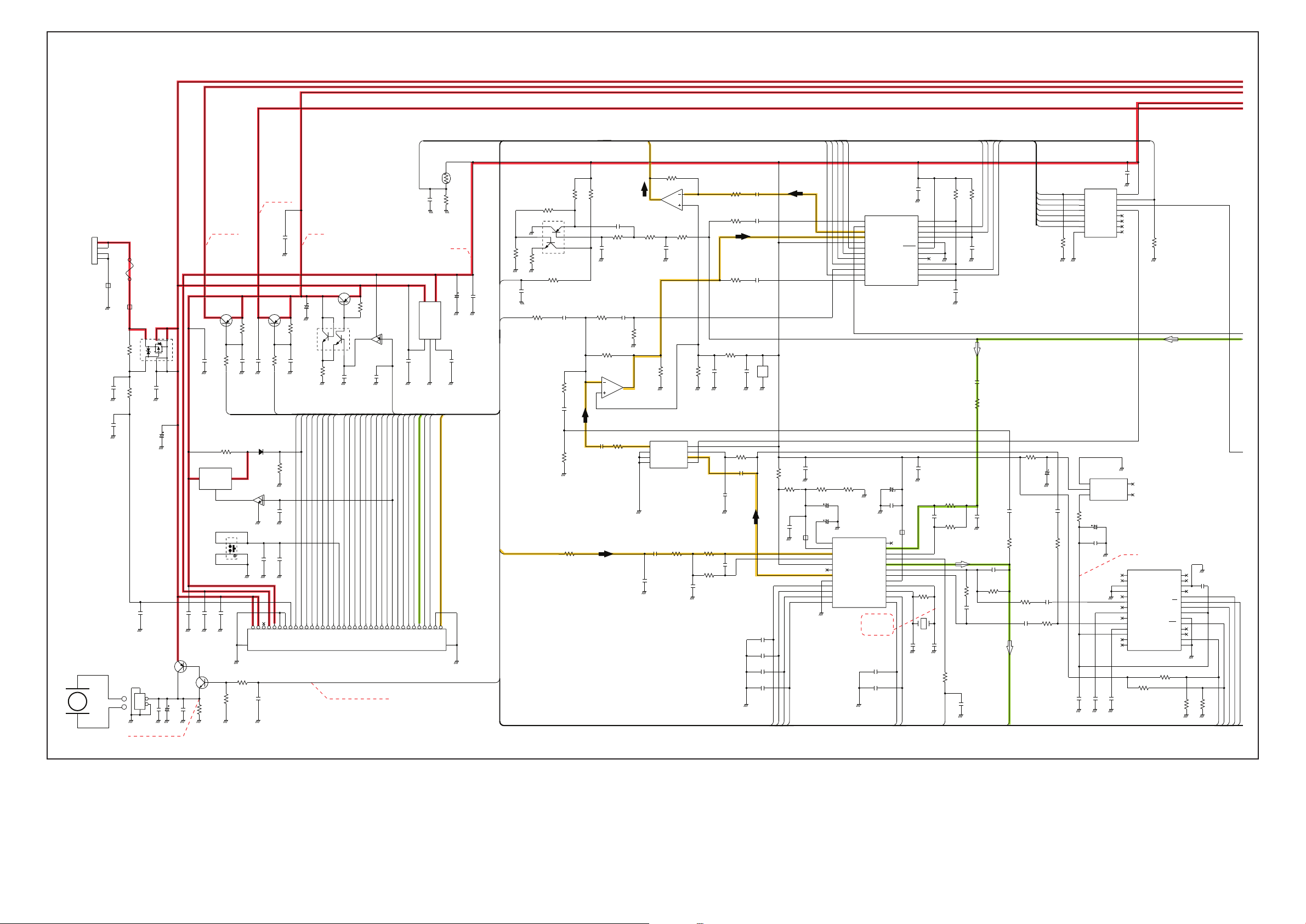

SECTION 4 CIRCUIT DESCRIPTION

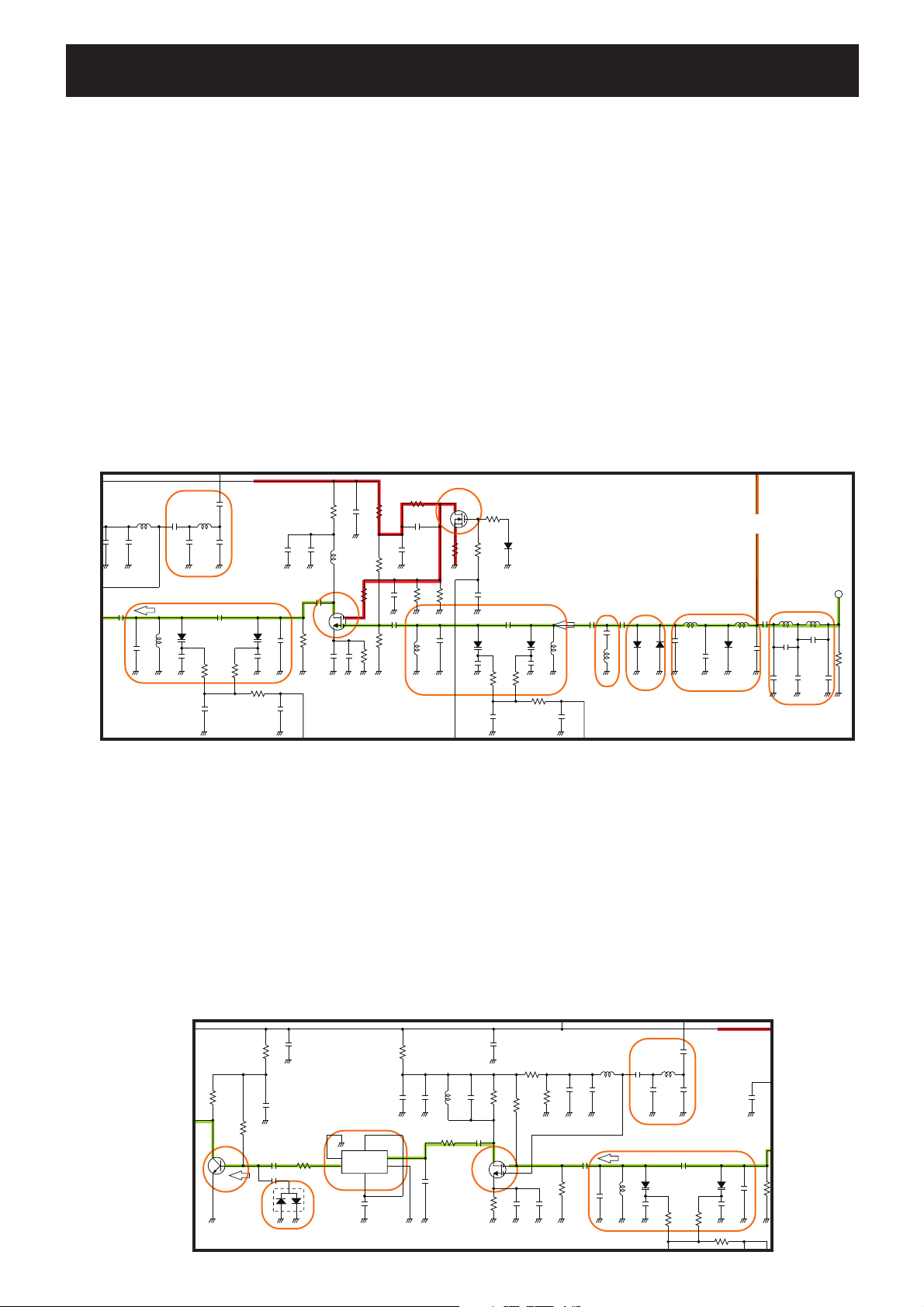

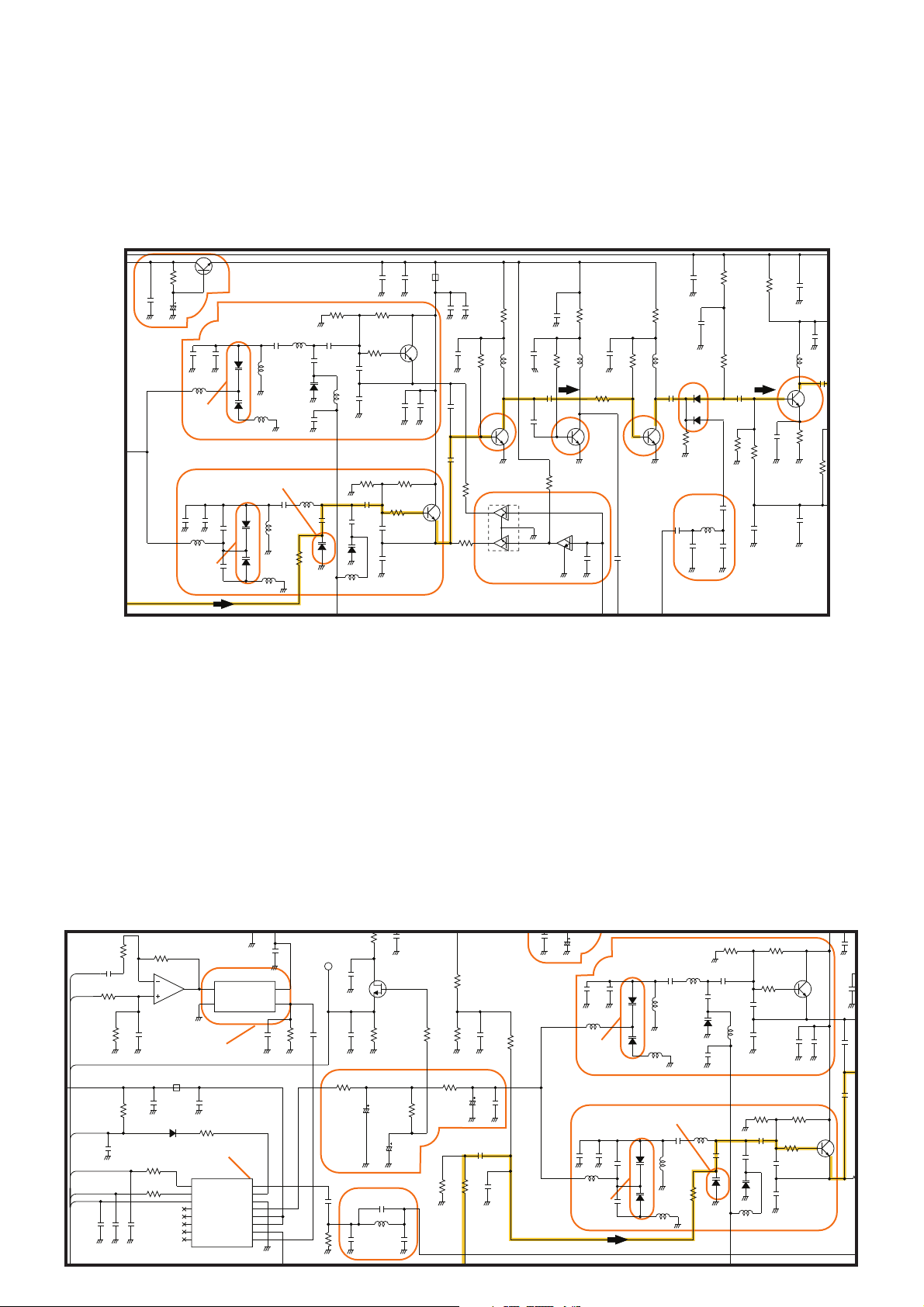

4-1 RECEIVER CIRCUITS

RF CIRCUITS

RF circuits consist of RF fi lters, antenna switch (ANT SW),

RF amplifi er (RF AMP), etc., and extracts and amplifi es the

signals of frequency which desired to receive.

The received signals (RX signals) from the antenna are passed

through the LPF, ANT SW (as an LPF in RX), limitter , BEF

(Band Eliminate Filter) and the two-staged tuned BPF. The

fi ltered RX signals are amplifi ed by the RF AMP, and passed

through another two-staged tuned BPF. The fi ltered RX signals

are then applied to the 1st IF circuits.

The ANT SW toggles RX line and TX line. While receiving,

the TX line and the antenna is disconnected to prevent RX

signals entering. The RX line is disconnected from the GND

simultaneously, and an LPF which guides received signals

to the RX circuits is composed.

While transmitting, serial-connected PIN diodes are ON,

thus the TX line is connected to the antenna, and the RX

line is connected to the GND simultaneously to prevent TX

signal entering.

The limitter protects RX line from over-level RF inputs, and

the BEF (=trap) damps unwanted signals to GND.

The tuned-BPF is adjusted so that it responds to receiving

frequency and rejects all others, by the variable capacitor

whose capacitance is varied by added voltage "T1" and "T2."

The RF AMP amplifi es RX signals to a level suited to the 1st

mixer.

• RF CIRCUITS

R5V

L1

2

C322

1stLO

C41

C44

Two-staged

TUNED BPF

LPF

C183

L14

C49

C324

C323

C40

D10

L11

C45

R23

C43

D9

C39

R21

R22

C42

R17

C35

C36

L9

RF

AMP

C37

Q2

C38

C32

R20

C33

R16

T2

C184

R172

R18

C186

C31

R19

C30

R12

R213

C29

R15

L8

1ST IF CIRCUITS

The 1st IF circuits consist of 1st mixer, 1st IF fi lter and 1st IF

amplifi er (IF AMP). And it converts the RX signals into the

1st IF signal, then filters to remove unwanted signals and

amplifi es.

R171

C28

AGC LINE

Q1

DRIVER

R173

RSSI

R174

D23

R175

Two-staged

C23

TUNED BPF

C22

D4

C26

R13

C27

LIMITTER

C19

C25

6P

D8

L7

C20

R11

R14

BEF

C24

T1

D6

C18

L31

C17

D7

To TX AMP

L6

L5

D5

C16

LPF (ANT SW)

C14

C5

The converted 1st IF signal is passed through the 1st IF fi lter

to be removed unwanted signals. The fi ltered 1st IF signal is

applied to the 1st IF AMP via the limitter. The amplifi ed 1st

IF signal is then applied to the 2nd IF circuits.

L2

C4

C3

LPF

To ANT

L1C6

C2

R51

C1

The filtered RX signals are applied to the 1st mixer to be

converted into the 1st IF signal, by being mixed with the 1st

Local Oscillator (LO) signals “1stLO” from the RX VCO via

the LPF.

• 1ST IF CIRCUITS

R5V R5V

56

FL-335

R31

C53

C54

FI1

1

IN

C55

R48

1stIF

Q4

R34

1st IF

AMP

C329

C59

R35

C60

C58

R33

D26

LIMITTER

1st IF

FILETR

4

GND

2

OU T3GND

C56

L13

R32

1st

MIXER

4 - 1

C51

R5V

C57

R27

C322

C321

C52

R30

1

Q3

R29

R26

R28

C50

1stLO

C41

R25

C48

LPF

C183

L1

2

C44

L14

C49

C324

C323

C40

D10

L11

C45

R21

R23

C35

C36

D9

C38

R20

C39

Two-staged

Page 8

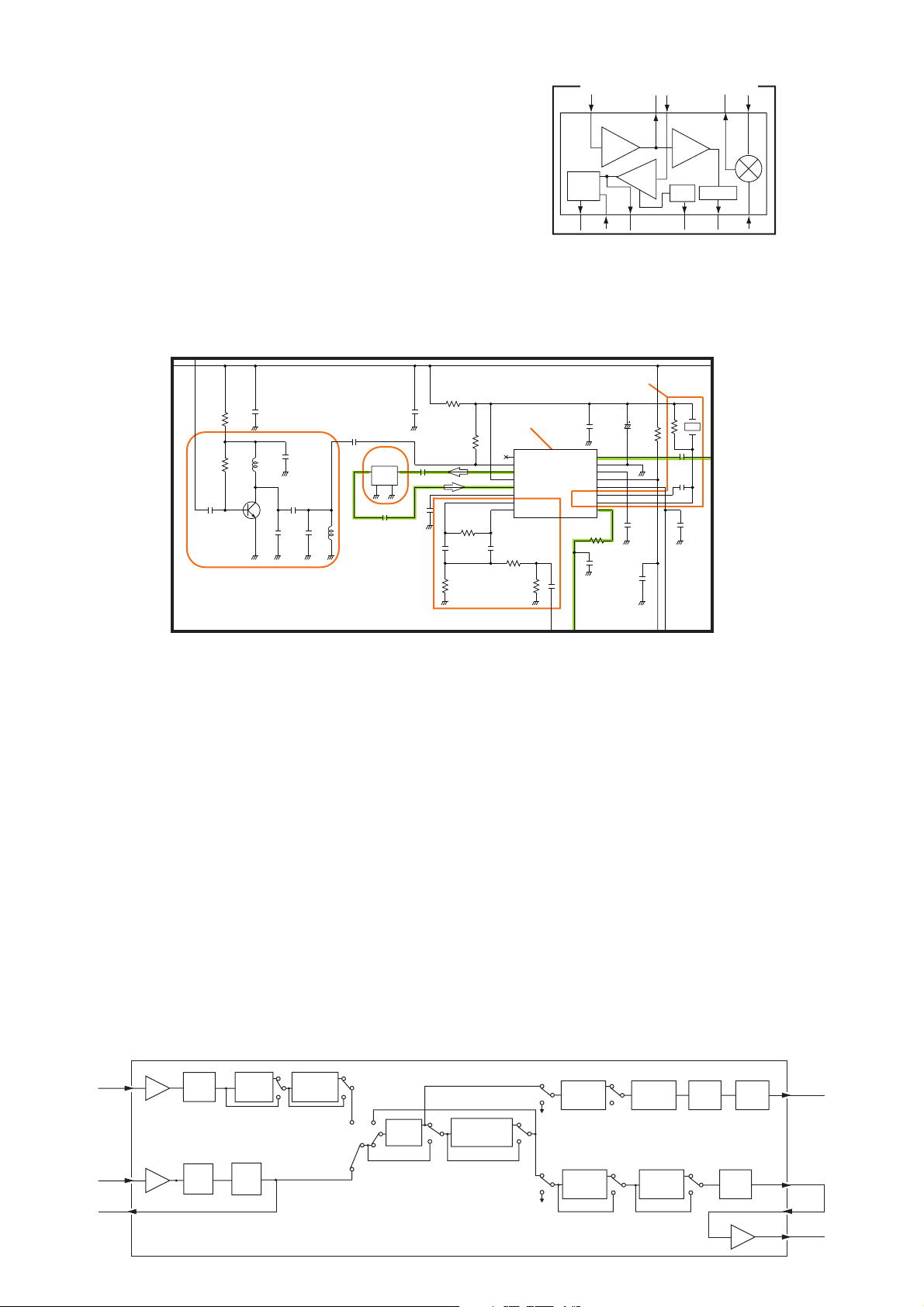

2ND IF AND FM DEMODULATOR CIRCUITS

The 2nd IF circuits consist of 2nd mixer, 2nd IF filter, 2nd

IF amplifier. And it converts the 1st IF signal into the 2nd

IF signal, then filters to remove unwanted signals and

amplifi es. IF IC "TA31136FNG" contains whole of the 2nd IF

circuits and FM demodulator circuit too.

The 1st IF signal is applied to the IF IC, and converted into

the 2nd IF signal, by being mixed with the 2nd LO signal

(from the X2 via the PLL IC (IC4, pins 1, 2) and tripler), at

internal 2nd mixer. The converted 2nd IF signal is filtered by

external 2nd IF filter (ceramic filter), and saturation-amplified

by internal 2nd IF AMP. The amplified 2nd IF signal is

F

M-demodulated by the quadrature detector.

The demodulated AF signals "SQLI" are applied to the RX

AF circuits.

• 2ND IF AND FM DEMODULATOR CIRCUITS

R115

R116

C185

C166

C165

L35

Q19

C162

C163

C164

L33

2nd IF

FILTER

FI2

C169

C167

IO

C168

C71

Ref.Freq.

C161

TRIPLER

(×3)

R46

R39

R44

C69

R40

C70

NOISE

FILTER

IF IC

IC1

1

OSCIN

2

OSCOUT

3

M IXOUT

4

VCC

5

IFIN

6

DEC

7

FILOUT

8

FILIN

TA31136FNG

R45

C68

R42

SQLO

IF IC (TA31136FNG) BLOCK DIAGRAM

FM

Detector

9

8

73

5

Noise

Filter

2nd IF

AMP

1110

Noise

AMP

RSSI

Noise Det.

12

QUADRATURE

DETECTOR

MIXIN

N-REC

N-DET

IFOUT

AFOUT

SQLI

RSSI

QUAD

C67

16

15

GND

14

13

12

11

10

9

R43

C188

C66

C75

1stIF

C63

R36

X1

R38

C61

C62

C65

NOIS

RSSI

2

2nd

Mixer

14

16

RX AF CIRCUITS

The RX AF circuits consist of AF filters, AF amplifier (AF

AMP), AF power amplifier, etc., and amplify, filter the AF

signals FM-demodulated by the FM IF IC.

This transceiver employs the base band IC for audio signal

processing for both transmit and receive. The base band

IC is an audio processor and composed of RF AMPlifier,

compressor, expander, scrambler, etc. in its package.

The demodulated AF signals from the IF IC are applied to

the base band IC (IC10, pin 23). The applied AF signals are

amplified at the amplifier section and level adjusted at the

volume controller section, then suppressed unwanted 3 kHz

and higher audio signals at LPF. The filtered AF signals are

applied (bypassed) the TX/RX HPF, scrambler, de-emphasis

sections in sequence.

• BASE BAND IC BLOCK DIAGRAM

Com-

pressor

TXA1

VR1

(HPF)

3 TXIN

Pre-

emphasis

TX/RX

HPF

The TX/RX HPF filters out 250 Hz and lower audio signals,

and the de-emphasis circuit obtains –6 dB/oct of audio

characteristics. The expander expands the compressed

audio signals and also noise reduction function is provided.

The AF signals are then level adjusted at the volume

controller section and amplified at the amplifier section, then

output from pin 20 (IC10).

The processed AF signals from the base band IC (IC10) are

applied to the FRONT UNIT via J1 (MAIN) and J401

(FRONT).

The AF signals from the MAIN UNIT

"SIGNAL" are passed

through the AF mute SW, LPF and variable register (VR

UNIT) for audio level adjustment, then applied to the AF

power AMP. The amplified AF signals

"AFO" are applied to

the internal speaker, or external speaker via the [SP MIC]

jack (MP701; CHASSIS).

BASE BAND IC (IC10)

SMF

7 MOD

Scrambler/

De-scrambler

Limiter Splatter VR2

23 RXIN

21 SDEC

RXA1

VR3

(HPF)

RX

LPF

4 - 2

De-

emphasis

Expander

VR4

RXA2

18

19

20

SIGNAL

Page 9

SQUELCH CIRCUITS

• NOISE SQUELCH

The noise squelch cuts off the AF output signals when

no RF signals are received. Extracting noise components

(approx. 30 kHz signals) in the demodulated AF signals,

the squelch circuit turns the AF power amplifier and AF

switches ON and OFF.

A portion of FM-demodulated AF signal from the IF IC is

adjusted its level (=squelch threshold level) by DAC (D/A

converter; IC6, pins 1, 2), then passed through the noise

filter (M: IC1, pins 7, 8 and R42, 44–46, C68–70) to extract

the noise components (approx. 30 kHz signals) only. The

noise components are rectified to be

pulse-type signal

by noise detector to produce DC voltage

corresponding to the noise level "NOIS". Then the DC

voltage is applied to the CPU (IC401, pin 41) and compared

with the reference level preset in the CPU.

If the CPU interpretes that the noise level is higher than

preset one, the CPU sets the "AFON" signal to "High" to

turn the AF power AMP controller OFF, and the AF mute

SW is turned OFF simultaneously. Thus closing the squelch

is accomplished.

To RX AF circuits

From IF IC (Pin16)

NOISE SQUELCH DIAGRAM

1 2

DAC

Fc=30 kHz

Noise

AMP

Active filter

converted into the

Rectify

“NOIS”

Noise detector

• TONE SQUELCH

The tone squelch connects the RX AF line and activates

the AF power amplifier to emit the AF signals only when

receiving a signal which contains the tone frequency

matched with preset in the CPU. Detecting signal in the

demodulated AF signals, the tone squelch circuit turns the

AF power amplifier and AF switches ON and OFF.

<CTCSS/DTCS>

A portion of FM-demodulated AF signals from the FM IF

IC are passed through the tone filter (M: Q6, pins 5, 6) to

remove unwanted voice siganls. The filtered tone signals

are applied to the CPU (IC401, pin 44).

<2/5 TONE, DTMF>

A portion of FM-demodulated AF signals are output from

the baseband IC (M: IC10, pin 21), and passed through

the tone filter (M: R136, C220) to remove unwanted voice

siganls. The filtered tone signals are applied to the CPU

(IC401, pin 43).

The CPU compars the tone frequency/code preset in the

CPU, and if the applied tone frequency/code is matched to

preset one, the CPU controls the AF power AMP and AF

mute SW as same as "NOISE SQUELCH."

4-2 TRANSMITTER CIRCUITS

TX AF CIRCUITS

The TX AF circuits consist of microphone amplifier (MIC

AMP) and AF fi lters. The AF fi lter cuts off the signals except

voice signals (300 Hz or lower and 3 kHz or higher).

The audio signals from the internal microphone (MIC

signals) are passed through MIC mute SW and amplifi ed by

two MIC AMPs (#1 and #2).

• TX AF CIRCUITS

AFO

R401

C404

AUDIO

VR UNIT

SP401

W601

4

3

2

1

LEVEL

ADJUST

J402

56

1

2

3

4

W401

Q413

R445

W402

BPMAX

R446

PWON

C502

C503

C426

C496

C435

MC401

R434

R517

R518

C437

R519

R520

R402

R521

R522

R541

C423

C401

R430

C425

R432

13

14

12

IC403

LPF

C513

R537

The MIC signals from the external microphone "EXMIC” are

applied to the FRONT UNIT via [SP MIC] jack, and amplifi ed

by MIC AMP (#2).

The amplified MIC signals "MIC” are applied to the MAIN

UNIT via J401(FRONT UNIT) and J1 (MAIN UNIT).

The MIC signals from the FRONT UNIT are applied to the

baseband IC (IC10, pin 3) and processed.

5

8

7

6

IC406

MUTE SW

1

2

3

4

C497

R433

C482

C512

Q415

R538

AF POWER AMP

IC405

20

19

18

17

16

15

14

13

12

11

VCC1

NC

OUT1IN1IN1+

IN2+

IN2OUT2NC

VCC2

R523

R539

GND1

OUT1 +

MODE

SVRR

SELECT

OUT2 +

GND2

NC

NC

NC

MIC/AF

MIC AMP

R513

R408

C481

R535

1

2

3

4

5

6

7

8

9

10

C510

#1

2

3

C498

R511

R429

R524

IC407

Q406

1

R426

R428

R525

EXMIC

R406

R405

R512

Q401, Q402

MIC AMP

C407

R407

6

5

C406

C405

C421

AF POWER AMP

CONTROLLER

#2

IC407

AFON

7

DUSE

BEEP

MIC

SIGNAL

AFON

VCC

SPON

4 - 3

Page 10

VCC

The applied MIC signals are amplified at the amplifier

(TXA1), and level adjusted at the volume controller (VR1).

The level adjusted MIC signals are applied (bypassed) the

compressor section, pre-emphasis section, TX/RX HPF,

de-scrambler, limiter, splatter, in sequence, then applied to

another volume controller.

The compressor compresses the MIC signals to provide

high S/N ratio for receive side, and the pre-emphasis obtains

+6 dB/oct audio characteristics. The TX/RX HPF fi lters out

250 Hz and lower audio signals, the limiter limits its level and

the splatter fi lters out 3 kHz and higher audio signals. The

filtered MIC signals are level adjusted at another volume

controller (VR2), and then output from pin 7 via smoothing

fi lter (SMF).

The output MIC signals are passed through the FM/PM

SW (IC11, pins 6, 1) and LPF (IC5, pins 2, 1) then applied

to the DAC (D/A Converter; IC6, pin 4) and level-adjusted

(deviation adjustment). The level-adjusted MIC siganls are

output from pin 3, then applied to the modulation circuit as

the modulation signals

"MOD” via buffer (IC5, pins 6, 7).

<CTCSS/DTCS>

CTCSS/DTCS signals ("CEN0"–"CEN2") are generated by

the CPU (F: IC401, pins 79–81) and converted its wave

form by R461–R463 (F), then passed through the LPF (F:

IC403, pins 3, 1). The fi ltered CTCSS/DTCS signals are

then level-adjusted by DAC (M: IC6, pins 9, 10) and applied

to the AF mixer (M: IC5, pin 2) to be mixed with MIC signals,

then applied to the TX VCO as the modulation signals. The

CTCSS/DTCS signals are also applied to the reference

signal oscillator (M; X2) too, via the buffer (M: IC16, pins 2, 1).

<2/5 TONE, DTMF>

2/5 tone and DTMF signals are ("SEN0"–"SEN3") are

generated by the CPU (F: IC401, pins 72–75) and converted

its wave form by R471–R474 (F), then passed through

the two-staged LPF (F: IC403, pins 5, 7 and pins 10, 8).

The filtered 2/5 tone and DTMF signals are applied to the

AF mixer (M: IC5, pin 2) to be mixed with MIC signals.

The mixed signals are then applied to the TX VCO as the

modulation signals). The CTCSS/DTCS signals are also

applied to the reference signal oscillator (M: X2, pin 1) too,

via the buffer (M: IC16, pins 2, 1).

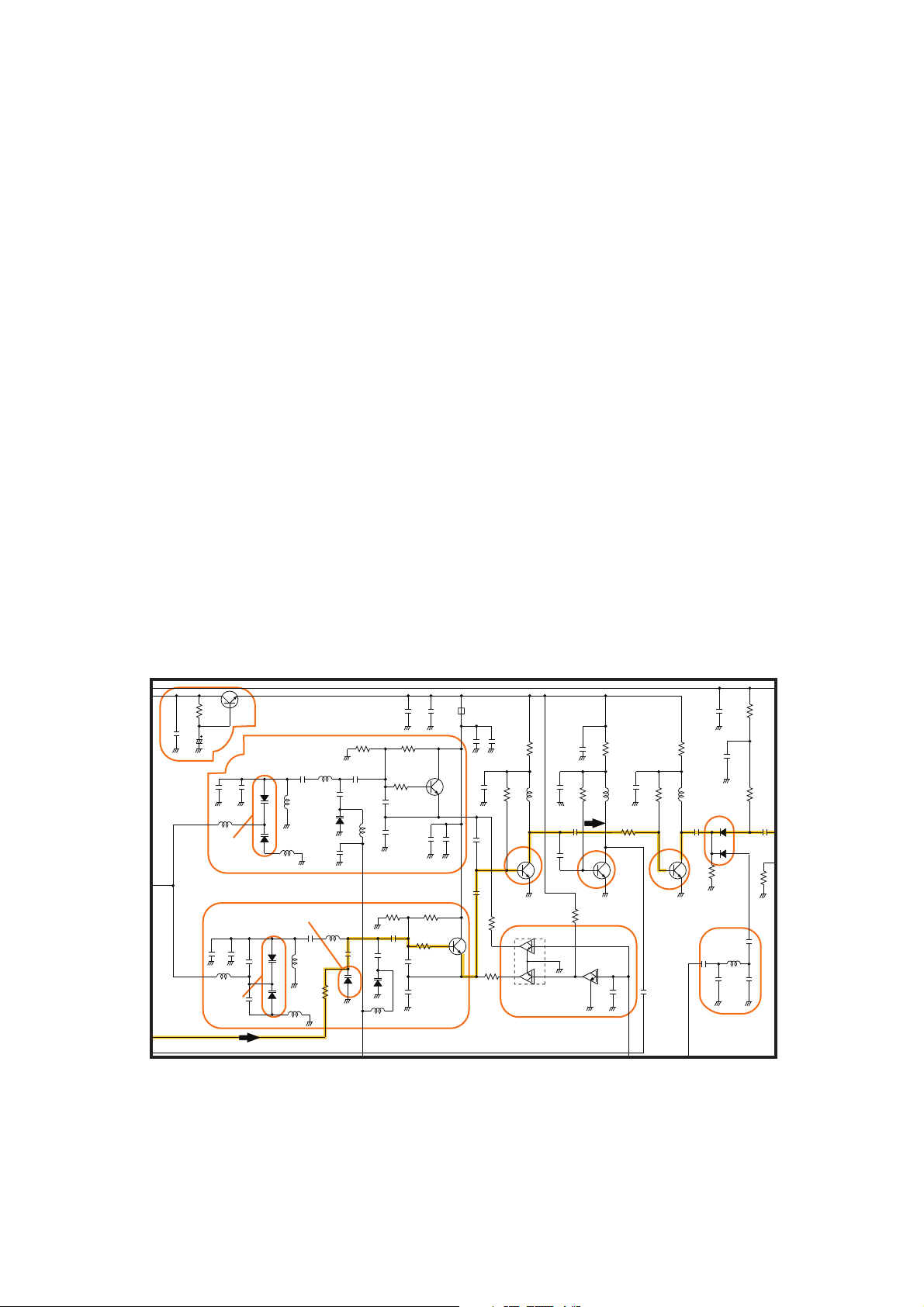

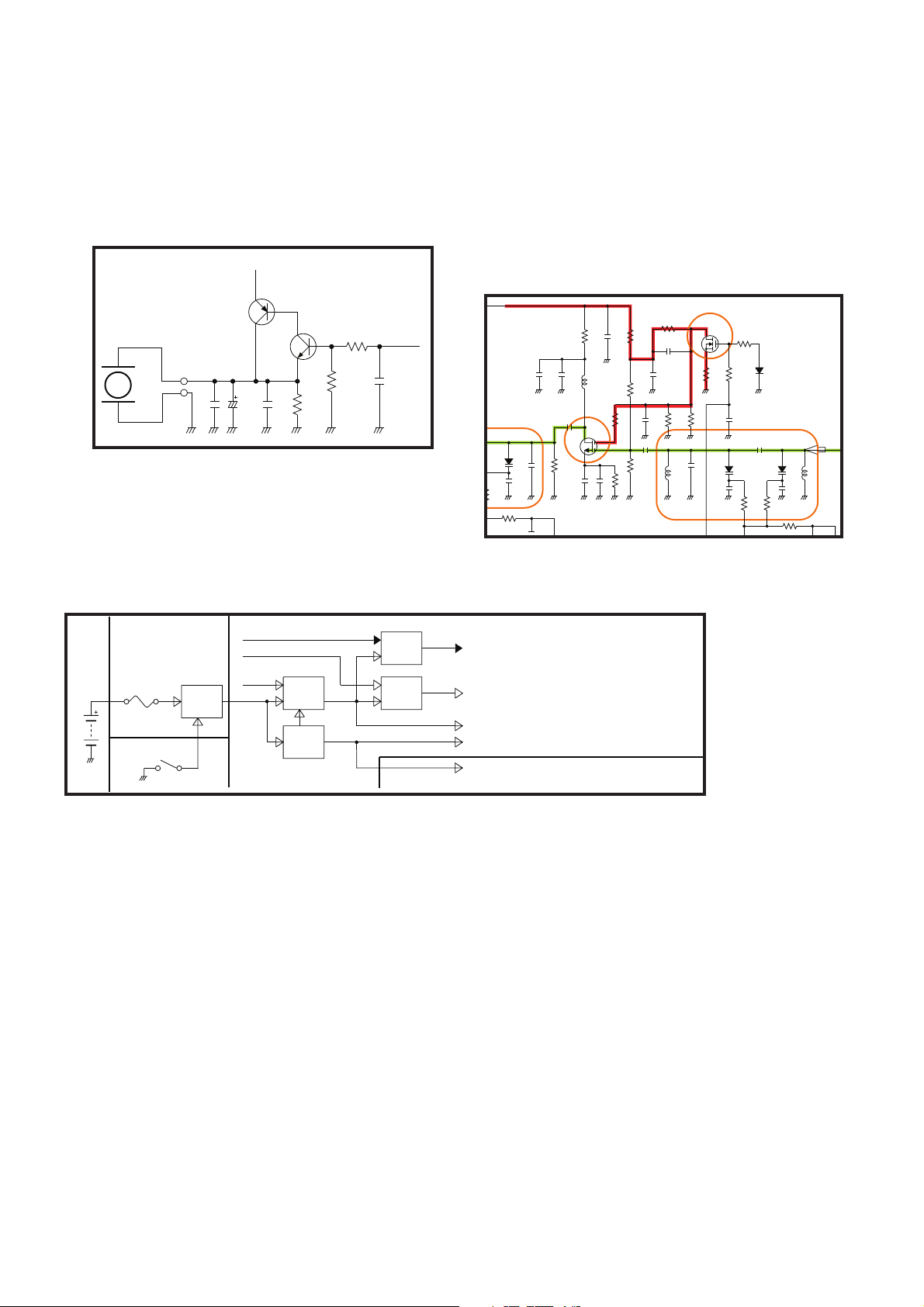

MODULATION CIRCUIT

The modulation circuit FM-modulates the VCO oscillating

signal with the modulation signals from the TX AF circuits.

• VOICE SIGNAL

The buffer-amplified AF signals are applied to the variable

capacitor (VD) to change its reactance for FM modulation.

• TONE SIGNALS

Tone signals are generated in the CPU and applied to the

both of the VCO and reference frequency oscillator to be

modulated.

• MODULATION CIRCUIT AND TX/RX VCOs

RIPPLE

C148

C190

C191

L28

Freq.

adjust

TX VCO

C195

L27

Freq.

adjust

Q17

FILTER

RX VCO

D1 9

C194

C192

C193

C127

D2 0

L37

L39

Modulation

C124

D17

L24

D1 6

L38

L26

C139

R79

R85

C126

C134

D22

L42

C203

L25

C129

D18

R86

L43

LVA

Q14

R81

C114

C115

C119

R84

R83

C123

R82

C133

C121

D21

C122

R98

C137

LV

MOD

The modulated VCO output is buffer-amplifi ed by two buffers

(Q12, Q10), and applied to the pre-driver via TX/RX SW.

T5V

C110

Q13

from VCO

C120

EP1

C116

C104

C118

R88

C117

C113

Q12

BUFFER

R87

Q15

5

R78

R77

VCO

SW

C109

R76

R75

C105

C102

C103

1

2

34

L41

R72

Q11

R80

Q16

C111

R5V

C107

R71

BUFFERBUFFER

C205

To PLL

R70

L21

C100

Q10

1stLO

C108

C99

TX/RX

SW

D14

D15

R69

LPF

L14

C49

C323

0.01

0.001

TX

R68

R67

C93

C183

C324

R65

C95

4 - 4

Page 11

TRANSMIT AMPLIFIERS

0

The transmit amplifiers consist several RF amplifiers (predriver, driver, power), and amplify the TX VCO output to the

transmit output level.

The TX VCO output is applied to the pre-drive amplifi er

via

the TX/RX switch. The amplified TX signal is amplified by

drive amplifier, then power-amplified by the power amplifier

to obtain 5 W (max.) of TX output power.

The power-amplified TX signal is passed through the LPFs

(as a harmonic filter), ANT SW (TX), and another LPF, then

applied to the antenna.

• TRANSMIT AMPLIFIERS AND APC CIRCUIT

L20

R68

C108

TX/RX

SW

0

R69

LPF

C49

C323

0.01

C99

0.001

R67

D14

C93

TX

D15

R65

C183

L14

C95

C324

R61

Pre-

DRIVE

R63

C106

C96

C97

DRIVE

L19

AMP

C92

Q9

C90

R62

R59

C91

C94

C292

R58

EP2

C81

C85

L18

Q8

C87

R57

C89

C88

C98

C82

C86

Q7

R53

R54

R55

C77

C76

R9

R10

C73

APC CIRCUIT

APC CIRCUIT

The APC (Automatic Power Control) circuit stabilizes

transmit output power to prevent transmit output power level

change which is caused by load mismatching or heat effect,

etc. The APC circuit also selects transmit output power from

high, middle and low power.

A portion of the TX signal is rectifi ed by the power detector

to be converted into DC voltage which is in proportion to the

transmit output power level. The detected voltage is applied

to the comparator. The transmit power setting voltage is applied to another input terminal as the reference voltage.

The comparator compares the detected voltage and reference voltage, and the difference of voltage is output. The

output voltage controls the bias of the TX amplifiers to reduce/increase the gain of these amplifi ers for stable transmit

output power.

The change of transmit power is carried out by changing

reference voltage.

R52

C291

PWR

L17

2681

C84

0.1

AMP

L16

MP 1

C83

R3

4

LPF

L4

C302

C12

C13

C79

R8

IC2

5

3

1

2

LPF

R1

C11

C308

C15

D25

L3

C9

TX POWER

DETECTOR

R2

C10

D1

COMPARATOR

R5

R7

R6

C80

C74

T2

R4

C101

C8

C78

C72

L15

C7

ANT SW

(TX)

TMUT

D2

C6

C5

LPF

L2

C4

To ANT

L1

C2

C1

C3

R51

4 - 5

Page 12

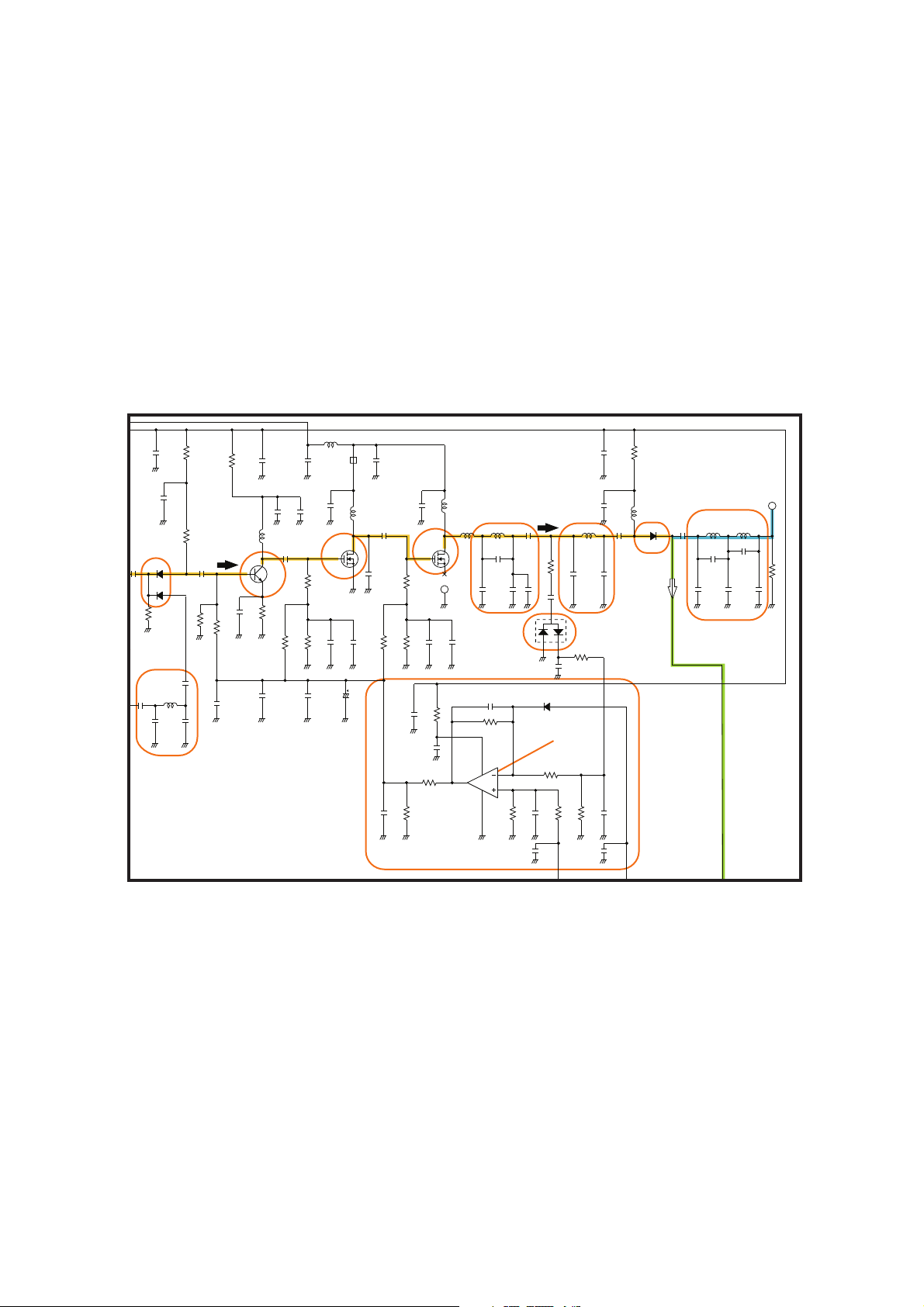

4-3 FREQUENCY SYNTHESIZER CIRCUITS

3

1

5

VCOs

A VCO is an oscillator which its oscillation frequency is

determined by the applied voltage. This transceiver has

two VCOs; RX VCO and TX VCO. The RX VCO generates

the 1st LO signals for the 1st IF produce, and TX VCO

generates TX signal. The VCO SW toggles these VCOs.

• RX VCO

The RX VCO oscillates 89.65 to 127.65 MHz LO signals.

The generated 1st LO signals are applied to the 1st mixer

(Q3) via two buffers (Q12 and Q10) and LPF.

RIPPLE

C148

C190

C191

L28

Freq.

adjust

TX VCO

C195

L27

Freq.

adjust

Q17

FILTER

RX VCO

D1 9

C194

C192

C193

C127

D2 0

L37

L39

Modulation

C124

D17

L24

D1 6

L38

L26

C110

C139

R79

R85

C126

C134

D22

L42

C203

L25

C129

D18

R86

L43

LVA

Q14

R81

C114

C115

R84

C123

C133

D21

C121

C122

R82

C119

R83

C120

Q13

R98

C137

LV

MOD

• TX VCO

The TX VCO oscillates 136 to 174 MHz TX signal. The

generated TX signal is applied to the pre-driver (one of TX

AMPs) via the TX/RX SW.

A portion of the VCO output is applied to the PLL IC via the

buffer (Q11).

• VCOs AND BUFFERS

T5V

R68

EP1

C116

C104

C118

C117

C113

Q12

BUFFER

R87

Q15

5

R88

R78

R77

VCO

SW

C109

R76

R75

C105

C102

Q11

C103

R80

1

2

Q16

34

C107

L41

R71

R72

Q10

BUFFERBUFFER

C205

C111

To PLL

R5V

C108

0.01

R70

C99

0.001

TX/RX

L21

SW

D14

C100

TX

D15

R69

LPF

L14

C49

C323

1stLO

R67

C183

C324

C93

R61

Pre-

DRIVE

R65

R63

C95

C106

C96

L19

C92

Q9

C90

R62

R59

C94

PLL (Phase Locked Loop) CIRCUIT

The PLL circuit provides stable oscillation for both of the

transmit and 1st LO frequencies (for receive). By comparing

the feed backed VCO output and the reference frequency

signal, the oscillating frequency is stabilized.

The PLL output frequency is controlled by the serial data

including divide ratio from the CPU.

A portion of VCO output from the buffer (Q11) is applied

to the PLL IC via LPF. The applied VCO output is divided

according to the serial data including divide ratio from

the CPU, at the prescaler and programmable divider. In

the same way, the reference frequency signal from the

reference frequency signal oscillator is applied to the PLL

IC and divide so that these are the same frequency.

• PLL CIRCUITS

R103

47K

C211

BAL

REF

LVIN

S5V

UNLK

SCK

SO

PLST

R104

C154

R105

C151

C153

2

3

Ref. Freq.

C213

OSCILLATOR

ACZ1005Y

C155

R94

D24

R117

R118

C152

IC16

1

EP6

9

10

11

12

13

14

15

16

X2

1

VCON

2

GND3OUT

CR-783

C140

R93

PLL IC

MB15A02PFV1

CLOCK

DATA

LE

FC

NC

FOUT

P

B

FIN

GND

VCC

OSCOUT

OSCIN

IC4

PLL

LD

DO

VP

E

C1

R108

CP1

C141

C156

R97

C158

4

VCC

C157

LOOP

FILTER

8

7

6

5

4

3

2

1

C209

R109

C143

C208

0.001

LPF

R10

R100

L32

C149

C207

C1

Q18

R89

R96

C147

3.3 MSVA

R187

C206

R95

The frequency-matched signals are applied to the phase

comparator and phase-compared. The resulted phase

difference is detected as a phase-type signal, and leveladjusted at the charge pump then output. The output pulse

type signal is passed through the loop filter to be converted

into the DC voltage (=Lock Voltage).

Applying the lock voltage to the variable capacitors

(VD) which composes a part of the resonator of VCO,

the capasitance of VDs changes corresponding to the

applied lock voltage. This causes the change of resonation

frequency that determines the VCO oscillating frequency to

keep the VCO frequency constant.

When the oscillation frequency drifts, its phase changes

from that of the reference frequency, causing a lock voltage

change to compensate for the drift in the VCO oscillating

frequency.

C137

C148

RX VCO

L26

R92

R91

C132

R90

C190

L28

Freq.

C191

C127

D2 0

L37

D1 9

L39

adjust

LV

C146

R110

C150

C145

C138

TX VCO

C195

L27

Freq.

adjust

MOD

C194

Modulation

D17

C192

C193

D1 6

L38

L24

C124

C126

C134

D22

L42

C203

L25

C129

D18

R86

R85

LVA

R79

R81

C114

C115

R84

C123

C133

D21

L43

4 - 6

Q14

C121

C122

C117

C116

C104

C120

C119

R83

R82

Q13

from VCO

C113

C118

R87

R

Page 13

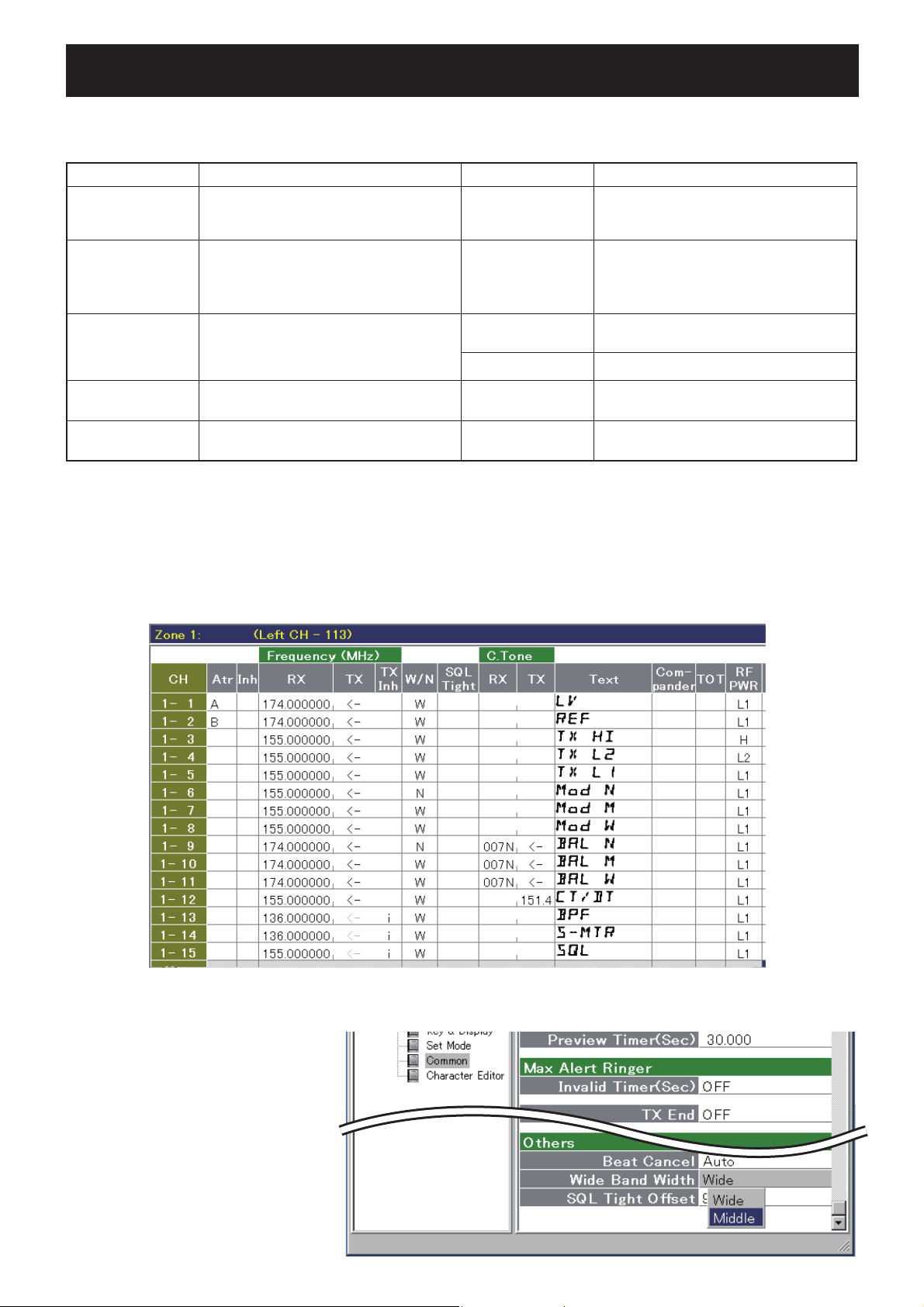

4-4 OTHER CIRCUITS

VIBERATION MOTOR CIRCUIT

(except [A], [D], [G], [J])

MF1 is a vibration motor. When the matched RX code signal

is received, MF1 rotates to produce viberation.

In vibration mode, and when the transceiver is called, "VIB"

signal from the expander (IC12, pin 6) turns to "High(=VCC

level)" and motor driver (Q30, Q31) is activated to rotate the

vibration motor (MF1).

• MOTOR DRIVER

VCC

Q31

M

MF1

C317

C316

Q30

C315

R201

R202

R203

VIB

C318

AGC (Automatic Gain Controller) CIRCUIT

The AGC circuit effectively reduces the RX signal level if

the signal is strong, and raises it when it is weaker. The

AGC circuit detects the overall strength of the signal and

automatically adjusting the gain of the RF AMP to maintain

an approximately constant average level of the received

signals.

RSSI signal which is in proportion to the RX signal level is

applied to the gate terminal of AGC line driver. The driver

controls the voltage which supplied to the RF AMP to

control the gain of RF AMP.

• AGC CIRCUIT

R22

R5V

C184

R172

R18

C186

C31

R19

C30

R12

R213

C29

R15

L8

R17

C35

C36

L9

RF

AMP

C37

Q2

D9

C38

C32

R20

C39

42

C33

R16

R171

C28

Q1

R173

AGC LINE

DRIVER

R174

D23

R175

Two-staged

C23

TUNED BPF

C22

D4

C26

R13

C25

6P

D8

L7

C20

R11

R14

4

4-5 VOLTAGE BLOCK DIAGRAM

Voltage from the battery pack is routed to whole of the transceiver via switches and regulators.

Q21

T5

REG

Q22

R5

REG

FRONT UNIT

T5V

Pre-drive AMP (Q9), APC AMP (IC2), etc.

R5V

IF IC (IC1), 1st IF AMP (Q4), 1st mixer (Q3), RF AMP (Q2), etc.

S5V

PLL IC (IC4), VCOs, etc.

+5V

Base-band IC (IC10), DAC (IC6), etc.

CPU5

CPU (IC401), EEPROM (IC409), expander (IC410)

2

FRONT UNIT

BATTERY PACK

T5C

R5C

Q25

Q24

Q23

S5C

VCC

MAIN UNITVR UNIT

S5

REG

+5

REG

IC9

1

PWR

R601

Q26

POWER

SW

F1

4 - 7

Page 14

4-6 CPU (F: IC401) PORT ALLOCATION

Pin

No.

1–

11

15–

25

26 SO

27 SCK

28 MDIO Data I/O for baseband IC (M: IC10). I/O

29 MSCK Clock to the baseband IC (M: IC10). O

30 SS

31 PLST Strobe signal to the PLL IC (M: IC4). O

32 SDA

33 SCL

34 INT

35 EXSF Strobe to the expander (F: IC410). O

36 EXSM Strobe to the expander (M: IC12) O

37 EXOE

38 BEEP Beep sounds. O

39 MTDT

40 MTCK

41 NOISE Noise level from FM IF IC (M: IC1). I

43 SDEC Tone signals (DTMF, 2/5tone). I

44 CDEC CTCSS/DTCS signals. I

45 VOXV

46 KR1

47 KR0

48 BATV Battery volatge for monitoring. I

49 LVIN Lock voltage for monitoring. I

50 RSSI

51 TEMP

52 OPTV

55 UNLK

59 RES

68 BPMAX

69 RAC

*; [C], [F], [I], [L] only

Line

name

SEG23–13

SEG11–1

Description I/O

LCD segment ports. O 13 SEG12

Serial data to DAC (M: IC6) and

audio strage IC (M: IC18).

Serial clock to DAC (M: IC6) and

audio strage IC (M: IC18).

Chip select signal to the Voice

strage IC* (M: IC18).

Serial data to DAC and voice strage

IC* (M: IC18).

Serial clock to DAC (M: IC6) and

voice strage IC* (M: IC18).

Interupt signal to voice strage IC* (M:

IC18).

Output enable signal to the

expander ICs (F: IC410 and M:

IC12).

Data (MSK TX data) to the

baseband IC (M: IC10).

Clock (for MSK TX data) to

baseband IC (M: IC10).

VOX detect.

"High"=start to transmit.

Key input for [UP], [P0] and [P3]

keys.

(Pulled up)

Key input for [DOWN], [P1] and [P2]

keys. (Pulled up)

RSSI voltage from FM IF IC (M:

IC1).

Voltage divided by thermal register

(M: R190) and R191. (temperature

monitor)

Optional unit detect.

"High"=An optional unit is connected.

PLL unlock signal from IC4.

"Low"=PLL is unlocked.

Reset signal from the reset IC (F:

IC408).

Beep sound level control signal to

BEEP SW (F: Q415).

"Low"=Maximum beep sound level.

Row address clock to the Voice

strage IC* (M: IC18).

Pin

No.

70 PTT

71 MDIR

72–75SENC3–

O

O

O

O

O

O

O

O

O

I

I

I

I

I

I

I

I

O

O

78 MRDF

79–81CENC0–

82 DAST Strobe signal to the DAC (M: IC6). O

88–91COM4–

92–

100

4 - 8

Line

name

[PTT] key (F: S401).

(Pulled up)

Serial data I/O control signal to the

baseband IC (M: IC10).

SENC6

CENC2

COM1

SEG32–24 LCD segment ports. O

2/5 tone, DTMF signals. O

MSK data RX flag/flame detect

signal to the baseband IC (M: IC6).

CTCSS/DTCS signals. O

LCD common terminals. –

Description I/O

I

O

O

Page 15

SECTION 5 ADJUSTMENT PROCEDURE

5-1 PREPARATION

¤ REQUIRED EQUIPMENTS

EQUIPMENT GRADE AND RANGE EQUIPMENT GRADE AND RANGE

Cloning software

RF power meter

(terminated type)

Frequency counter

Modulation

Analyzer

Audio generator

CS-F50V

(Revision 1.0 or later)

Measuring range : 0.1–10 W

Frequency range : 100–300 MHz

Impedance : 50

SWR : Less than 1.2 : 1

Frequency range : 0.1–300 MHz

Frequency accuracy : ±1 ppm or better

Input level : Less than 1 mW

Frequency range : 30–300 MHz

Measuring range : 0 to ±10 kHz

Frequency range : 300–3000 Hz

Output level : 1–500 mV

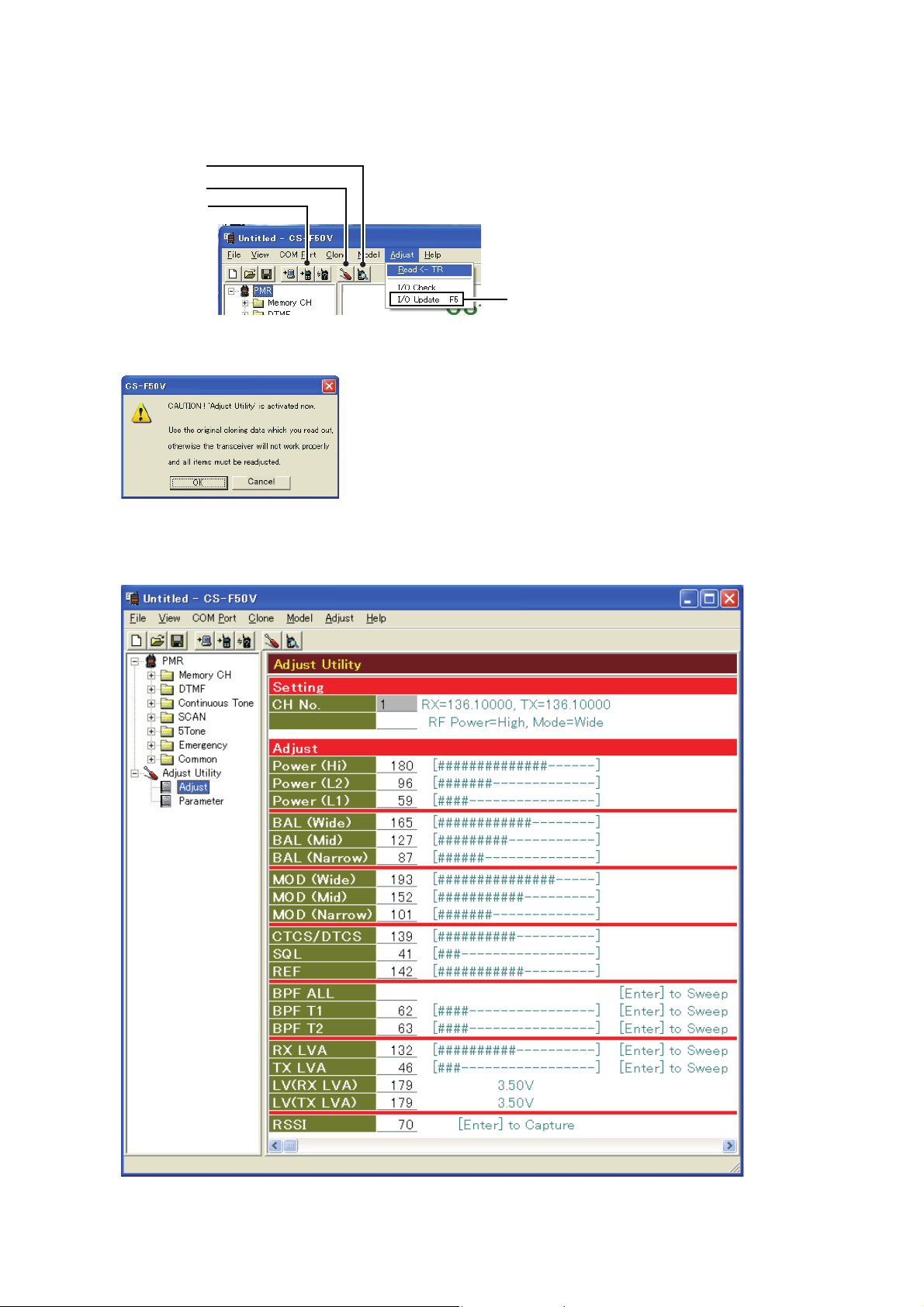

CLONING SOFTWARE

Ω

¤ CLONING ADJUSTMENT CHANNELS

Before starting adjustment, clone adjustment frequencies and other conditions into the transceiver using CS-F50V

CLONING SOFTWARE as below.

CAUTION!: BACK UP the originally programmed memory data in the transceiver before programming the adjustment frequen-

cies. When program the adjustment frequencies into the transceiver, the transceiver’s memory data will be overwritten and lose original memory data at the same time.

JIG cable

(Modifi ed OPC966C/UC)

Standard signal

generator (SSG)

Oscilloscope

AC millivoltmeter Measuring range : 10 mV to 10 V

External speaker

Attenuator

(See the page 5-3)

Frequency range : 0.1–300 MHz

Output level : 0.1 mV to 32 mV

(–127 to –17 dBm)

Frequency range : DC–20 MHz

Measuring range : 0.01–20 V

Input impedance : 8

Capacity : More than 1 W

Power attenuation : 30 dB

Capacity : More than 10 W

Ω

• ADJUSTMENT CHANNELS

NOTE: FOR [EUR], [EUR-01] AND [EUR-02], when adjust “Devation” and “Modulation Balance” in the middle band, change the

bandwidth to “Middle” as below.

5 - 1

Page 16

STARTING SOFTWARE ADJUSTMENT

¤

Connect the transceiver and PC with OPC-966/U. (see the page 5-3)

q

Turn the transceiver power ON.

w

Boot up Windows, and click the program group ‘CS-F50V’

e

CS-F50V’s window appears. (Or click the shortcut

Click [Adjust Read] button.

r

[I/O Check]

[Adjust Read]

[Clone Write]

The 'CAUTION' dialog appears. Click [OK].

t

‘CS-F50V’

in the ‘Programs’ folder of the [Start] menu, then

on the desktop.)

[I/O Update F5]

The adjustment window shows transceiver’s condition and adjustment items as below.

y

Set or modify adjustment data as specifi ed in the guidances (pages 5-4 to 5-12).

u

* This screen is an example only. Each transceiver has its own specific values for each setting.

When the adjustment is completed, click [Clone Write] button.

i

5 - 2

Page 17

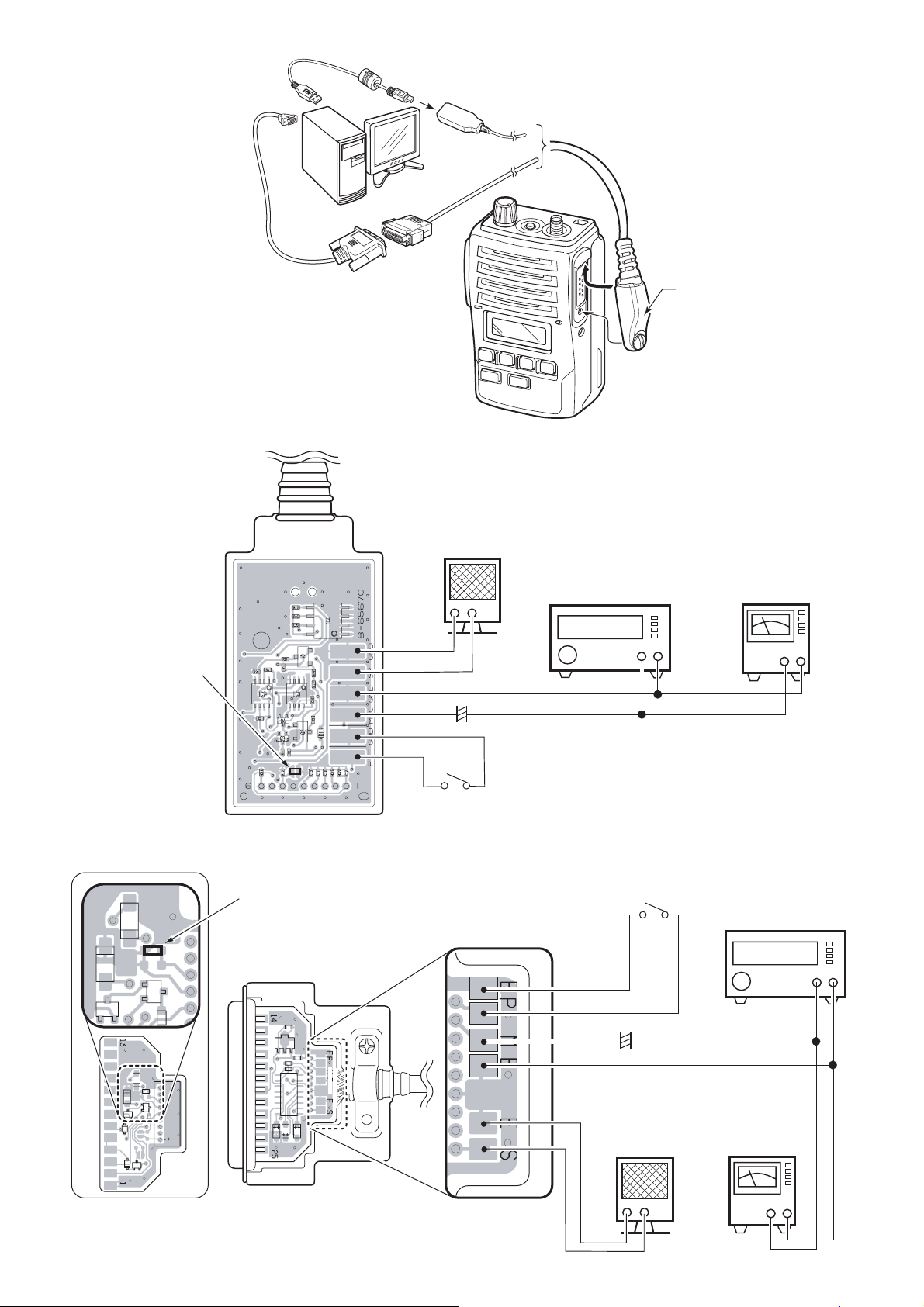

▄

PC CONNECTIONS

to an RS-232C port

RS-232C cable

(straight)

▄

JIG CABLES

OPC-966U

(USB type Cloning cable)

PC

JIG CABLE

OPC-966U (USB type)

JIG CABLE

C type)

OPC-966

(RS-232

EXT. SPEAKER

(1 W/8 Ω)

CAUTION: Attach the [SP

MIC] jack snugly, but do

not overtighten.

An overtightened jack will

damage the connector

pins in the transceiver.

Add a jumper wire here

GND

SP

GND

MIC

GND

PTT

Add a jumper wire here

OPC-966

(RS-232C type Cloning cable)

+−

+

4.7 µF

PTT SWITCH

AUDIO GENERATOR

(300–3000 Hz/1–500 mV)

+−

<SETTING>

Frequency

: 1 kHz

Level : 150 mV rms

PTT SWITCH

PTTE

PTT

MIC

MICE

(300–3000 Hz/1–500 mV)

+

4.7 µF

AC MILLIVOLTMETER

(10 mV to 10 V)

+−

SETTING;

Freq.

: 1 kHz

Level : 150 mV rms

AUDIO GENERATOR

+−

5 - 3

EXT. SPEAKER

(1 W/8 Ω)

+−

GND

SP

AC

MILLIVOLT-

METER

(10 mV to 10 V)

+−

Page 18

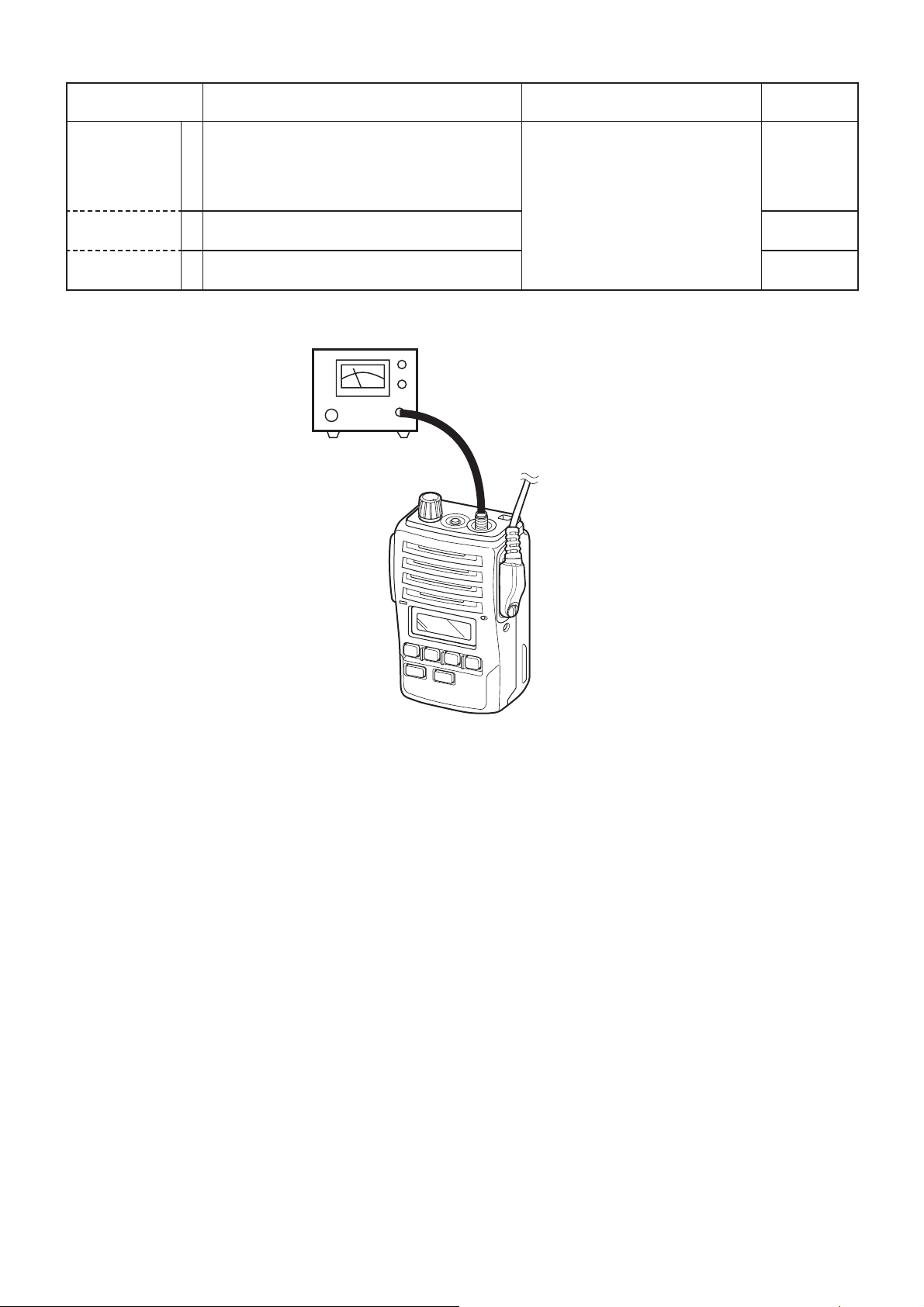

5-2 FREQUENCY ADJUSTMENT

Select an adjustment item using [↑] / [↓] keys, then set to the specifi ed value using [←] / [→] keys on the connected PC’s keyboard.

ADJUSTMENT

[ADJUST ITEM]

PLL LOCK

VOLTAGE

[RX LVA]

[TX LVA] 2 •

1• • Channel : 1-1

CONVENIENT:

1: Set the Lock voltage preset ([RX LVA] and [TX LVA]) to “179.”

2: Push the [ENTER] key on the connected PC’s keyboard.

PLL LOCK

VOLTAGE

(verify)

1• • Channel : 1-13

2• • Channel : 1-13

•

•

ADJUSTMENT CONDITION OPERATION VALUE

Click [I/O Update (F5)] in the [Adjust]

Receiving

Channel : 1-1

Connect an RF Power Meter to the

antenna connector.

Transmitting

The “

PLL LOCK VOLTAGE”

Receiving

Transmitting

RF POWER METER

(10 W/50 Ω)

menu (see the page 5-2), then check

the “LVIN” item on the I/O check window as below.

can be adjusted automatically.

Click [I/O Update (F5)] in the [Adjust]

menu (see the page 5-2), then check

the “LVIN” item on the I/O check window as below.

3.5 V

3.5 V

0.9–1.5 V

(Verify)

0.9–1.5 V

(Verify)

• I/O CHECK WINDOW

Lock Voltage

Check

* This screen is an example only. Each transceiver has its own specific values for each setting.

5 - 4

Page 19

5-2 FREQUENCY ADJUSTMENT (continued)

Select an adjustment item using [↑] / [↓] keys, then set to the specifi ed value using [←] / [→] keys on the connected PC’s keyboard.

ADJUSTMENT

[ADJUST ITEM]

REFERENCE

FREQUENCY

[REF]

1 • Channel : 1-2

•

•

ADJUSTMENT CONDITION OPERATION VALUE

Loosely couple a Frequency Counter to

Connect an RF Power Meter to the

the antenna connector.

antenna connector.

Transmitting

FREQUENCY COUNTER

(0.1–300 MHz)

RF POWER METER

(10 W/50 Ω)

174.000 MHz

(Loose Coupling)

5 - 5

Page 20

5-3 TRANSMIT ADJUSTMENT

Select an adjustment item using [↑] / [↓] keys, then set to the specifi ed value using [←] / [→] keys on the connected PC’s keyboard.

ADJUSTMENT

[ADJUST ITEM]

TRANSMIT

OUTPUT

POWER

(Hight)

[Hi]

(Low2)

[L2]

(Low1)

[L1]

1 • Channel : 1-3

•

Transmitting

•

2

Channel : 1-4

•

Transmitting

•

3

Channel : 1-5

•

Transmitting

ADJUSTMENT CONDITION OPERATION VALUE

Connect an RF power meter to the

antenna connector.

RF POWER METER

(10 W/50 Ω)

5.0 W

2.0 W

1.0 W

5 - 6

Page 21

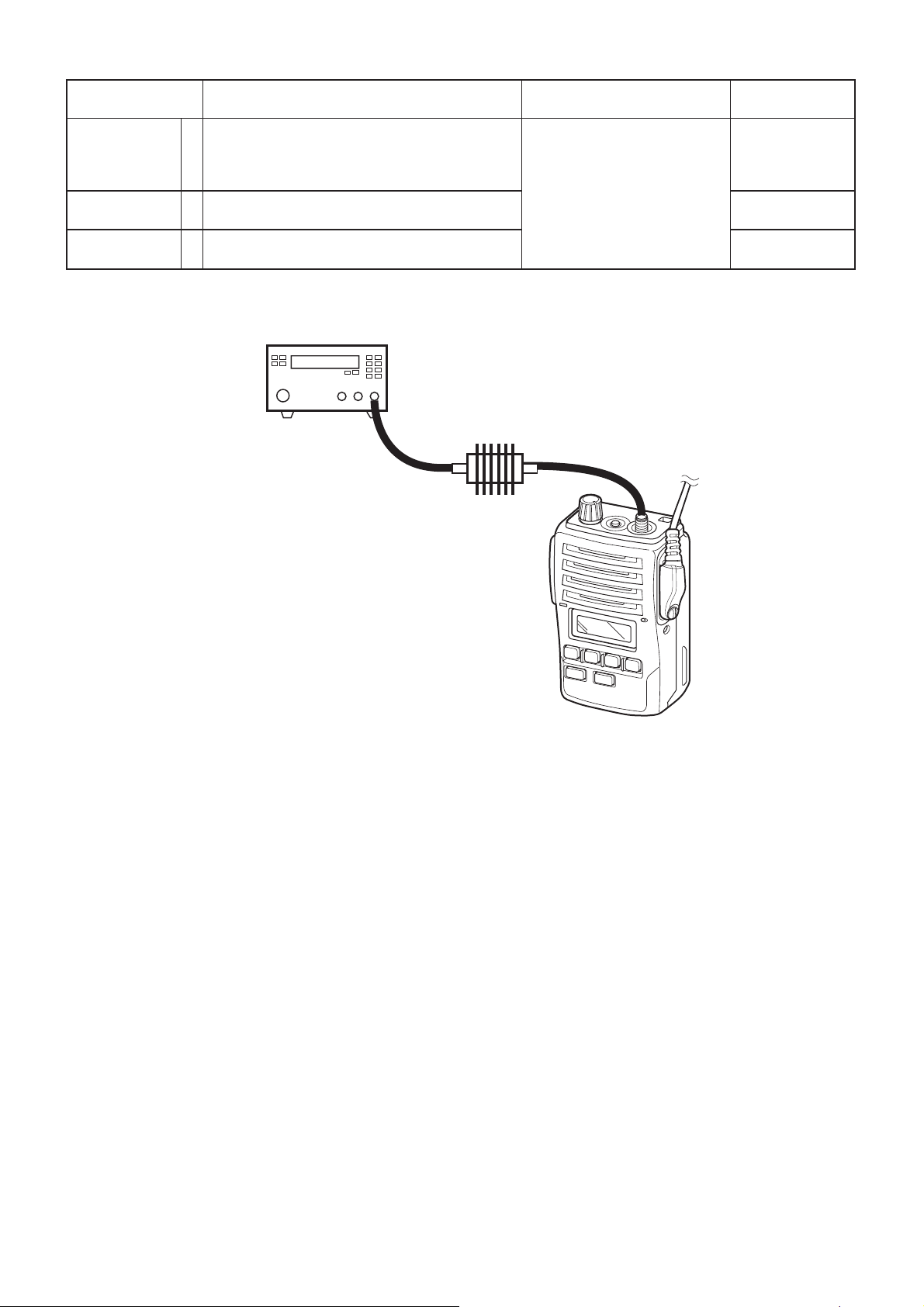

5-3 TRANSMIT ADJUSTMENT (continued)

Select an adjustment item using [↑] / [↓] keys, then set to the specifi ed value using [←] / [→] keys on the connected PC’s keyboard.

ADJUSTMENT

[ADJUST ITEM]

FM DEVIATION

(Narrow)

[MOD(Narrow])

(Middle)*

[MOD(Mid])

(Wide)

[MOD(Wide])

1 • Channel : 1-6

Connect an Audio Generator and an AC Millivolt-

•

meter to the JIG cable (see the page 5-3).

Transmitting

•

2• • Channel : 1-7

Transmitting

3••Channel : 1-8

Transmitting

*; [EUR], [EUR-01], [EUR-02] only

SETTING;

HPF : OFF

LPF : 20 kHz

De-emphasis : OFF

Detector : (P-P)/2

ADJUSTMENT CONDITION OPERATION VALUE

Connect an Modulation Ana-

±2.05 to 2.15 kHz

lyzer to the antenna connector

through an Attenuator.

±3.15 to 3.25 kHz

±4.05 to 4.15 kHz

MODULATION ANALYZER

(0.1–300 MHz)

ATTENUATOR

(30 dB/10 W)

5 - 7

Page 22

5-3 TRANSMIT ADJUSTMENT (continued)

Select an adjustment item using [↑] / [↓] keys, then set to the specifi ed value using [←] / [→] keys on the connected PC’s keyboard.

ADJUSTMENT

[ADJUST ITEM]

MODULATION

BALANCE

(Narrow)

1•

Channel : 1-9

•

No audio signals are applied to the JIG cable.

•

Transmitting

[BAL(Narrow])

(Middle)*

[BAL(Mid])

(Wide)

[BAL(Wide])

2• • Channel : 1-10

Transmitting

3••Channel : 1-11

Transmitting

*; [EUR], [EUR-01], [EUR-02] only

ADJUSTMENT CONDITION OPERATION VALUE

Connect an Oscilloscope to the

detect output terminal of the

Set to the square

wave form

Modulation Analyzer.

OSCILLOSCOPE

(DC to 10 kHz)

MODULATION ANALYZER

(0.1–300 MHz)

SETTING;

HPF : OFF

LPF : 20 kHz

De-emphasis : OFF

Detector : (P-P)/2

ATTENUATOR

(30 dB/10 W)

(Detect output)

5 - 8

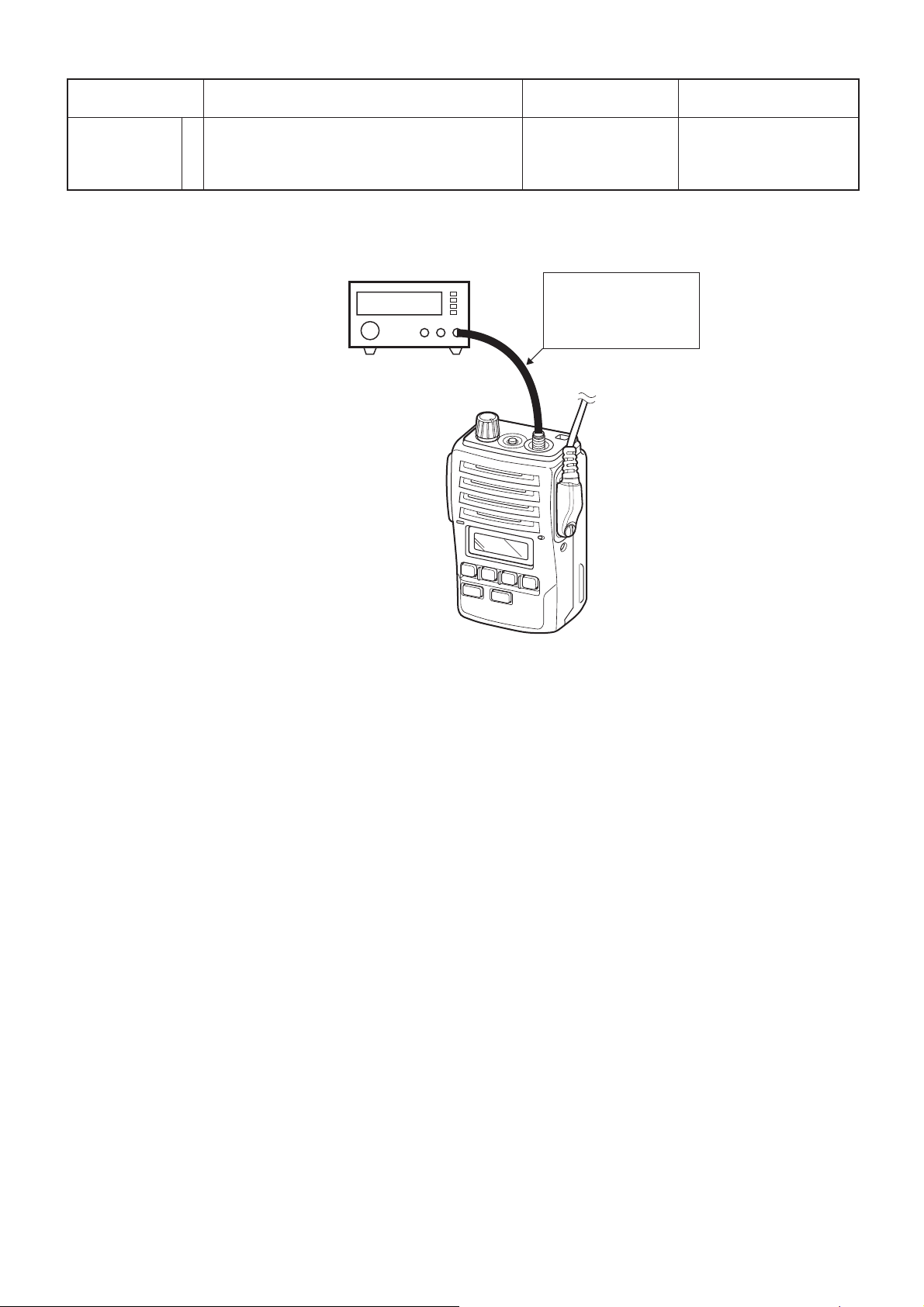

Page 23

5-3 TRANSMIT ADJUSTMENT (continued)

Select an adjustment item using [↑] / [↓] keys, then set to the specifi ed value using [←] / [→] keys on the connected PC’s keyboard.

ADJUSTMENT

[ADJUST ITEM]

CTCSS/DTCS

DEVIATION

[CTCSS/DTCS]

SETTING;

HPF : OFF

LPF : 20 kHz

De-emphasis : OFF

Detector : (P-P)/2

1 • Channel : 1-12

•

No audio signals are applied to the JIG cable.

•

Transmitting

ADJUSTMENT CONDITION OPERATION VALUE

Connect a Modulation Analyzer

±0.66 to 0.70 kHz

to the antenna connector through

an Attenuator.

MODULATION ANALYZER

(0.1–300 MHz)

ATTENUATOR

(30 dB/10 W)

5 - 9

Page 24

5-4 RECEIVE ADJUSTMENT

Select an adjustment item using [↑] / [↓] keys, then set to the specifi ed value using [←] / [→] keys on the connected PC’s keyboard.

ADJUSTMENT

[ADJUST ITEM]

RECEIVE

SENSITIVITY

[BPF T1]

1•

Channel : 1-13

•

Connect a Standard Signal Generator to the

antenna connector.

•

Receiving

[BPF T2] 2 Put the cursor on the [BPF T2],

CONVENIENT:

RECEIVE SENSITIVITY can be adjusted totally. Put the cursor on the [BPF ALL], and push the return key.

ADJUSTMENT CONDITION OPERATION VALUE

Put the cursor on the [BPF T1],

and push the return key.

(Automatic

adjustment)

and push the return key.

STANDARD SIGNAL GENERATOR

SETTING;

Modulation : 1 kHz

Deviation : 3.5 kHz

Level : +20 dBµ

(1–300 MHz)

CAUTION:

DO NOT transmit while

an SSG is connected to

the antenna connector.

5 - 10

Page 25

5-4 RECEIVE ADJUSTMENT (continued)

Select an adjustment item using [↑] / [↓] keys, then set to the specifi ed value using [←] / [→] keys on the connected PC’s keyboard.

ADJUSTMENT

[ADJUST ITEM]

S-METER

[S-METER]

(S6 LEVEL)

[S-METER]

(S1 LEVEL)

NOTE:

be adjusted properly.

1•

Channel : 1-14

•

Connect a Standard Signal Generator to the

antenna connector.

•

Set the SSG output level to “+13 dBµ (–94 dBm).”

•

Receiving

2•

Set the SSG output level to “–12 dBµ (–119 dBm).”

•

Receiving

ADJUSTMENT CONDITION OPERATION VALUE

“RECEIVE SENSITIVITY” must be adjusted before “S-METER.” Otherwise, “S-METER” will not

Push the return key to set the S6

level.

(Automatic

adjustment)

Push the return key to set the S1

level.

STANDARD SIGNAL GENERATOR

SETTING;

Modulation : 1 kHz

Deviation : 3.5 kHz

Level : +13 dBµ (S6 level)

−12 dBµ (S1 level)

(1–300 MHz)

CAUTION:

DO NOT transmit while

an SSG is connected to

the antenna connector.

5 - 11

Page 26

5-4 RECEIVE ADJUSTMENT (continued)

Select an adjustment item using [↑] / [↓] keys, then set to the specifi ed value using [←] / [→] keys on the connected PC’s keyboard.

ADJUSTMENT

[ADJUST ITEM]

SQUELCH

[SQL]

1 • Channel : 1-15

•

Connect a Standard Signal Generator to the

antenna connector.

ADJUSTMENT CONDITION OPERATION VALUE

Set the [SQL] value to close

–

squelch. Then set [SQL]

value at the point where the

audio signals just appear.

STANDARD SIGNAL GENERATOR

SETTING;

Modulation : 1 kHz

Deviation : 3.5 kHz

Level : −15 dBµ

(1–300 MHz)

CAUTION:

DO NOT transmit while

an SSG is connected to

the antenna connector.

5 - 12

Page 27

SECTION 6 PARTS LIST

[FRONT UNIT]

REF ORDER

NO. NO.

IC401 1140010191 S.IC HD64F2268TF20V T 22.9/28

IC403 1110005340 S.IC NJM12902V-TE1 T 16.9/42.9

IC405 1110006770 S.IC TDA8547TS/N T 25.8/53.2

IC406 1130011741 S.IC TC7W66FK (TE85L,F) T 8.1/42.4

IC407 1110005330 S.IC NJM12904V-TE1 T 7.1/31.6

IC408 1110006260 S.IC BD5242G-TR T 32/18.5

IC409 1130012690 S.IC HN58X24256FPIE (SOP8) T 10.1/17.8

IC410 1130011760 S.IC CD4094BPWR T 40.6/36.3

IC411 1130013240 S.IC TC75S51FU (TE85L,F) T 6.2/21.3

Q401 1550000090 S.FET RSQ035P03TR T 36.3/43.7

Q402 1590003800 S.TR KTC811U-GR-RTK/P T 35/39.6

Q406 1590003790 S.TR KRC404E RTK/P T 20.9/50.7

Q407 1590003780 S.TR KRA304E-RTK/P T 42/31.3

Q408 1590003790 S.TR KRC404E RTK/P T 26/39.2

Q409 1590002370 S.TR XP4111 (TX) T 39.2/29

Q411 1590003790 S.TR KRC404E RTK/P T 29.3/18.8

Q412 1590003780 S.TR KRA304E-RTK/P T 14.3/17.6

Q413 1560001330 S.FET RSR025N03 B 32.3/53

Q414 1590003790 S.TR KRC404E RTK/P T 40.8/41.8

Q415 1530003091 S.TR 2SC4213-B (TE85R,F) B 23.9/51.1

D401 1790001250 S.DIO MA2S111-(TX) T 35.4/23.1

D402 1790001250 S.DIO MA2S111-(TX) T 35.1/18.1

D403 1790001250 S.DIO MA2S111-(TX) T 15/16

D404 1790001260 S.DIO MA2S077-(TX) T 37/24

D406 1790001250 S.DIO MA2S111-(TX) T 36.5/36

D407 1790001250 S.DIO MA2S111-(TX) T 9/23.1

X401 6050011720 S.XTL CR-764 (19.6608 MHz) T 42.6/18.8

R401 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) T 9.9/44.3

R402 7030005060 S.RES ERJ2GEJ 333 X (33 k) T 10.7/52.2

R403 7030005120 S.RES ERJ2GEJ 102 X (1 k) T 34.3/22.3

R404 7030005120 S.RES ERJ2GEJ 102 X (1 k) T 35.8/20.2

R405 7030007340 S.RES ERJ2GEJ 153 X (15 k) T 9.6/35.1

R406 7030005210 S.RES ERJ2GEJ 822 X (8.2 k) T 10.5/36.4

R407 7030005230 S.RES ERJ2GEJ 334 X (330 k) T 7.4/27.3

R408 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 6.8/36.3

R409 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 36.3/21.4

R410 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 9.8/39.6

R411 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 13.8/20.4

R412 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 29.2/13.9

R413 7030005600 S.RES ERJ2GEJ 273 X (27 k) T 27.3/13.7

R414 7030005600 S.RES ERJ2GEJ 273 X (27 k) T 36.9/13.6

R415 7030005100 S.RES ERJ2GEJ 154 X (150 k) T 39/23.4

R416 7030005100 S.RES ERJ2GEJ 154 X (150 k) T 33.4/20.9

R417 7030005170 S.RES ERJ2GEJ 474 X (470 k) T 17.5/19

R418 7030005170 S.RES ERJ2GEJ 474 X (470 k) T 5.3/16.3

R420 7030005600 S.RES ERJ2GEJ 273 X (27 k) T 28.7/37.2

R421 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 29.9/36.5

R422 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 30.2/35.6

R423 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 31.5/36.5

R426 7030005160 S.RES ERJ2GEJ 105 X (1 M) T 12.3/35.3

R427 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 14.5/37.8

R428 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 13.8/36.9

R429 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) T 12.3/36.2

R430 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 12.9/40.2

R432 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 14.5/39.6

R433 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 12.2/42.1

R434 7030005000 S.RES ERJ2GEJ 471 X (470) B 35/55.4

R437 7030005120 S.RES ERJ2GEJ 102 X (1 k) T 32.9/38.4

R438 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 34.7/37.7

R439 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) T 36.8/40.2

R440 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 36.1/33.4

R441 7030005070 S.RES ERJ2GEJ 683 X (68 k) T 37.3/33.7

R445 7030004980 S.RES ERJ2GEJ 101 X (100) B 32.3/55.2

R446 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 30.1/52.1

R455 7030005000 S.RES ERJ2GEJ 471 X (470) T 43.2/27.8

R456 7030004980 S.RES ERJ2GEJ 101 X (100) T 43.2/28.7

R457 7030005000 S.RES ERJ2GEJ 471 X (470) B 45.2/48.4

R458 7030005120 S.RES ERJ2GEJ 102 X (1 k) B 43.9/49.9

R461 7030008300 S.RES ERJ2GEJ 184 X (180 k) T 33.2/32.4

R462 7030005720 S.RES ERJ2GEJ 563 X (56 k) T 32/33.2

R463 7030005220 S.RES ERJ2GEJ 223 X (22 k) T 31.1/33.6

R464 7030005220 S.RES ERJ2GEJ 223 X (22 k) T 31.5/34.8

R465 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 33.2/34.7

R466 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 23.9/41.3

R467 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 23/41.3

R468 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 21.2/41.3

R469 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) T 18.5/39

R470 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 19.7/38.6

R471 7030005110 S.RES ERJ2GEJ 224 X (220 k) T 34.5/24.7

R472 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 33.6/24.7

R473 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 32.7/24.7

R474 7030005220 S.RES ERJ2GEJ 223 X (22 k) T 31.8/24.3

R475 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 35.7/24.8

R476 7030005070 S.RES ERJ2GEJ 683 X (68 k) T 23.3/46.1

R477 7030005070 S.RES ERJ2GEJ 683 X (68 k) T 21.7/46.1

R478 7030005070 S.RES ERJ2GEJ 683 X (68 k) T 21.2/44.6

R479 7030005070 S.RES ERJ2GEJ 683 X (68 k) T 18.3/46.2

R480 7030005070 S.RES ERJ2GEJ 683 X (68 k) T 12.5/45

R482 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 36.5/32

R483 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 15.8/21.8

DESCRIPTION

M.

H/V

LOCATION

[FRONT UNIT]

REF ORDER

NO. NO.

R484 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 15.6/20.9

R485 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 14.2/21.7

R486 7410001130 S.ARY EXB28V102JX T 13.6/24.7

R487 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 33.9/23.5

R488 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 31.9/31.3

R489 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 32.9/31.2

R490 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 33.8/31.2

R491 7030005530 S.RES ERJ2GEJ 100 X (10) T 38.5/18.4

R492 7030005160 S.RES ERJ2GEJ 105 X (1 M) T 38.5/20.1

R493 7030008010 S.RES ERJ2GEJ 123 X (12 k) T 37.6/19.3

R494 7030008010 S.RES ERJ2GEJ 123 X (12 k) T 38.4/25.8

R495 7030008010 S.RES ERJ2GEJ 123 X (12 k) T 37.2/20.5

R496 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 11.3/22.8

R497 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 11.9/21.9

R500 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 29/21.1

R501 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 28.1/20.3

R502 7030010080 S.RES ERJ2RHD 104 X (100 k) T 38.4/14.3

R503 7030010080 S.RES ERJ2RHD 104 X (100 k) T 39.3/14.3

R506 7030007300 S.RES ERJ2GEJ 332 X (3.3 k) T 7.6/23.9

R507 7030005600 S.RES ERJ2GEJ 273 X (27 k) T 7.6/24.8

R508 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) T 5/25.7

R509 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 26.2/18.9

R511 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 9.6/33.2

R512 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 6.2/26.9

R513 7030009290 S.RES ERJ2GEJ 562 X (5.6 k) T 7.7/36.3

R515 7520000270 S.POS PRG21BC4R7MM1RA T 34.2/46.7

R516 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) T 37/38.7

R517 7030008010 S.RES ERJ2GEJ 123 X (12 k) T 31.1/50.8

R518 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 30.7/48.7

R519 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 30.4/53.8

R520 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 30.4/52.2

R521 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 30.5/55.1

R522 7030005100 S.RES ERJ2GEJ 154 X (150 k) T 30.2/49.6

R523 7030005120 S.RES ERJ2GEJ 102 X (1 k) T 21.1/52.3

R524 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 21.1/53.7

R525 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 21.5/54.9

R526 7030007340 S.RES ERJ2GEJ 153 X (15 k) T 5/24.8

R527 7030005230 S.RES ERJ2GEJ 334 X (330 k) T 5/23.9

R528 7030009140 S.RES ERJ2GEJ 272 X (2.7 k) T 5/19.6

R529 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 6.6/19.6

R530 7030005160 S.RES ERJ2GEJ 105 X (1 M) T 10.4/24.2

R532 7030005700 S.RES ERJ2GEJ 274 X (270 k) T 36.7/41.5

R533 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 35.1/41.5

R534 7030005170 S.RES ERJ2GEJ 474 X (470 k) T 36.9/34.9

R535 7030005070 S.RES ERJ2GEJ 683 X (68 k) T 11.9/33.5

R537 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 22/50.7

R538 7030005060 S.RES ERJ2GEJ 333 X (33 k) B 22/52.3

R539 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) B 25.5/52.8

R541 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 10.3/53.4

C401 4030017460 S.CER ECJ0EB1E102K T 10.7/51.3

C402 4030017460 S.CER ECJ0EB1E102K T 15/20

C403 4030017460 S.CER ECJ0EB1E102K T 31/22.6

C404 4030017460 S.CER ECJ0EB1E102K T 10.3/43.1

C405 4030017760 S.CER ECJ0EB1H222K T 10.5/34.8

C406 4030018110 S.CER ECJ0EB1H272K T 9.6/36.7

C407 4030017430 S.CER ECJ0EC1H101J T 7.4/26.4

C408 4030016930 S.CER ECJ0EB1A104K T 29.6/37.7

C409 4030016930 S.CER ECJ0EB1A104K T 27.8/37.6

C410 4030016930 S.CER ECJ0EB1A104K T 30.5/37.7

C411 4030016930 S.CER ECJ0EB1A104K T 31.7/37.4

C412 4030016930 S.CER ECJ0EB1A104K T 36.7/19.3

C413 4030016930 S.CER ECJ0EB1A104K T 38.1/24.6

C414 4030017640 S.CER ECJ0EC1H150J T 38.1/21.4

C415 4030016790 S.CER ECJ0EB1C103K T 34.6/20.2

C416 4030017630 S.CER ECJ0EC1H120J T 39.4/19.2

C417 4030017580 S.CER ECJ0EC1H060C T 39.4/20.8

C418 4030016930 S.CER ECJ0EB1A104K T 39/24.6

C419 4550006050 S.TAN TEESVA 0J 106M8R T 24.6/16.9

C420 4030016930 S.CER ECJ0EB1A104K T 24.9/18.5

C421 4030016930 S.CER ECJ0EB1A104K T 13.5/35.7

C423 4030018890 S.CER ECJ0EB0J224K T 12.9/39.2

C425 4030017440 S.CER ECJ0EC1H221J T 14.5/38.7

C426 4030017460 S.CER ECJ0EB1E102K B 35.6/54.2

C427 4550007080 S.TAN TEESVA 1C 106M8R T 40.6/44.3

C428 4030016930 S.CER ECJ0EB1A104K T 37.6/47

C429 4030017460 S.CER ECJ0EB1E102K T 36.7/47

C430 4030017460 S.CER ECJ0EB1E102K T 34.7/36.8

C431 4030016790 S.CER ECJ0EB1C103K T 32.9/39.3

C432 4030017460 S.CER ECJ0EB1E102K T 38.9/42.7

C435 4550006760 S.TAN TEESVB21A336M8R T 18.5/54.3

C437 4030018860 S.CER ECJ0EB0J105K B 34.1/55.4

C441 4030016780 S.CER ECJ0EB1C153K T 23.4/42.9

C442 4030016930 S.CER ECJ0EB1A104K T 22.1/41.3

C443 4030017740 S.CER ECJ0EB1E821K T 22.2/42.5

C444 4030016930 S.CER ECJ0EB1A104K T 19.7/39.5

C445 4030017460 S.CER ECJ0EB1E102K T 33.2/33.8

C446 4030017460 S.CER ECJ0EB1E102K T 22.5/45.2

C447 4030017760 S.CER ECJ0EB1H222K T 20.1/45.7

C448 4030017690 S.CER ECJ0EC1H121J T 22.5/44.3

C449 4030017770 S.CER ECJ0EB1E332K T 13.7/45.7

C450 4030017420 S.CER ECJ0EC1H470J T 12.2/43.7

C461 4030017420 S.CER ECJ0EC1H470J T 39/22.5

C462 4030017420 S.CER ECJ0EC1H470J T 32/21

C463 4030017420 S.CER ECJ0EC1H470J T 17.5/19.9

C464 4030017420 S.CER ECJ0EC1H470J T 4.4/16.3

C465 4030017420 S.CER ECJ0EC1H470J T 26.4/13.7

DESCRIPTION

M.=Mounted side (T: Mounted on the Top side, B: Mounted on the Bottom side)

6 - 1

M.

S.=Surface mount

H/V

LOCATION

Page 28

[FRONT UNIT]

REF ORDER

NO. NO.

C466 4030017420 S.CER ECJ0EC1H470J T 36.9/14.5

C467 4030017420 S.CER ECJ0EC1H470J T 30.5/13.1

C468 4030017420 S.CER ECJ0EC1H470J T 40.4/11.5

C473 4030016790 S.CER ECJ0EB1C103K T 38.1/15.9

C474 4030018860 S.CER ECJ0EB0J105K T 5/26.6

C475 4030017460 S.CER ECJ0EB1E102K T 33/45.4

C476 4030017460 S.CER ECJ0EB1E102K T 29.9/21.9

C477 4030017420 S.CER ECJ0EC1H470J T 33.3/44.1

C478 4030017420 S.CER ECJ0EC1H470J T 33.5/41.9

C479 4030017460 S.CER ECJ0EB1E102K T 27.8/17.7

C481 4030017460 S.CER ECJ0EB1E102K T 6.4/38.1

C482 4030017460 S.CER ECJ0EB1E102K T 11.8/41.2

C483 4030017460 S.CER ECJ0EB1E102K T 38.8/41.8

C485 4030017460 S.CER ECJ0EB1E102K T 33.7/48

C486 4030017460 S.CER ECJ0EB1E102K T 32.1/47.5

C487 4030017460 S.CER ECJ0EB1E102K T 34.4/35.9

C488 4030017460 S.CER ECJ0EB1E102K T 22.1/43.4

C489 4030017460 S.CER ECJ0EB1E102K T 9.9/30.9

C490 4030017460 S.CER ECJ0EB1E102K T 40.3/27

C491 4030017460 S.CER ECJ0EB1E102K T 37.3/37.3

C492 4030017460 S.CER ECJ0EB1E102K T 6.8/18.2

C493 4030016930 S.CER ECJ0EB1A104K T 17.4/34.7

C494 4030017460 S.CER ECJ0EB1E102K T 39.6/67.3

C495 4030017460 S.CER ECJ0EB1E102K T 10/40.5

C496 4550006760 S.TAN TEESVB21A336M8R T 13.2/54.7

C497 4030018390 S.CER ECJ0EB1A563K T 8.1/37.9

C498 4030017430 S.CER ECJ0EC1H101J T 10.5/33.2

C499 4030017420 S.CER ECJ0EC1H470J T 15.4/36.9

C500 4030016930 S.CER ECJ0EB1A104K T 9.3/37.9

C501 4030017730 S.CER ECJ0EB1E471K T 35.1/13.2

C502 4030016930 S.CER ECJ0EB1A104K T 31.9/49.6

C503 4030018860 S.CER ECJ0EB0J105K T 32.3/48.7

C504 4550007080 S.TAN TEESVA 1C 106M8R T 40.6/46.4

C505 4030016960 S.CER ECJ0EB1C183K T 6.3/25.3

C506 4030016960 S.CER ECJ0EB1C183K T 6.3/23.4

C507 4030017730 S.CER ECJ0EB1E471K T 5/23

C508 4030017730 S.CER ECJ0EB1E471K T 11.3/24.2

C510 4550000460 S.TAN TEESVA 1C 105M8R T 23.5/48.6

C512 4030018860 S.CER ECJ0EB0J105K B 22.3/49.5

C513 4030018860 S.CER ECJ0EB0J105K B 25.9/51.5

DESCRIPTION

M.

H/V

LOCATION

[VR UNIT]

REF ORDER

NO. NO.

R601 7210003130 VAR TP76N97N-13F-10KA-2497

W601 8900012340 CBL OPC-1260

DESCRIPTION

M.

H/V

LOCATION

[CONNECT UNIT]

REF ORDER

NO. NO.

D701 1790001810 S.VSR AVR-M1005C080MTABB T 9.5/31.8

D702 1790001810 S.VSR AVR-M1005C080MTABB T 9.2/32.8

D703 1790001810 S.VSR AVR-M1005C080MTABB T 4.7/32.3

D704 1790001810 S.VSR AVR-M1005C080MTABB T 3.4/32

D705 1790001810 S.VSR AVR-M1005C080MTABB T 4.8/20.7

R701 7410001130 S.ARY EXB28V102JX T 6.5/32.5

C701 4030017460 S.CER ECJ0EB1E102K T 4.6/9.9

C702 4030017460 S.CER ECJ0EB1E102K T 4.4/14.2

C704 4030017460 S.CER ECJ0EB1E102K T 3.9/17.1

J1 6510026140 S.CNR 11FH-SM1-TB (LF) (SN) T 3.6/37.1

EP701 6910016330 S.BEA MMZ1005S 601CT-S T 6.4/9.9

EP702 6910016330 S.BEA MMZ1005S 601CT-S T 4.8/12.9

EP703 6910016330 S.BEA MMZ1005S 601CT-S T 4.9/16.5

EP704 6910016330 S.BEA MMZ1005S 601CT-S T 4.4/18.4

EP705 6910016330 S.BEA MMZ1005S 601CT-S T 4.8/19.4

DESCRIPTION

M.=Mounted side (T: Mounted on the Top side, B: Mounted on the Bottom side)

S.=Surface mount

M.

H/V

LOCATION

J401 6510026130 S.CNR IMSA-9681S-36Y900 T 30.9/6.2

J402 6510023831 S.CNR (G) SM04B-SRSS-TB(LF)(SN) T 34.9/52.5

J403 6510026140 S.CNR 11FH-SM1-TB (LF) (SN) T 29/43.5

DS401 5030002730 LCD L3-0048TAY-5

DS402 5040002420 S.LED SML-310MT T86 B 13.5/16.1

DS403 5040002420 S.LED SML-310MT T86 B 32.7/15.3

DS404 5040002961 S.LED SML-A12MT T86J B 6.2/38

DS405 5040002961 S.LED SML-A12MT T86J B 42.8/38

DS406 5040002670 S.LED CL-165HR/YG B 45.3/50.2

MC401 7700002760 MIC EM6027P-46C33-G-01 <HOR>

S401 2260002840 SW SKHLLFA010

SP401 2510001330 SP 036D0803 <FG>

W401 8900016840 CBL OPC-1753 (P0.5,N36,L70) <TJM>

W402 7120000470 JMP ERDS2T0

W403 7120000470 JMP ERDS2T0

W404 8900017120 CBL OPC-1754 (P0.5,N11,L35) <TJM>

EP402 8930061530 LCT SRCN-2681-SP-N-W

6 - 2

Page 29

[MAIN UNIT]

REF ORDER

NO. NO.

IC1 1110003201 S.IC TA31136FNG (EL) B 19.1/9.1

IC2 1110002751 S.IC TA75S01F (TE85R,F) T 52.3/18.1

IC4 1140005991 S.IC MB15A02PFV1-G-BND-ERE1 B 28.7/24.1

IC5 1110005330 S.IC NJM12904V-TE1 T 34.3/9.3

IC6 1190000350 S.IC M62363FP-650C T 25.2/8.9

IC7 1190001860 S.IC EW-460-FT B 50.7/39.9

IC9 1110005350 S.IC NJM2870F05-TE1-#FZZB T 73.8/28.6

IC10 1110006221 S.IC AK2346P-E2/P T 18.9/25.1

IC11 1130009981 S.IC TC7W53FK (TE85L,F) T 25.2/29.2

IC12 1130011760 S.IC CD4094BPWR T 17.2/35.8

IC16 1110005330 S.IC NJM12904V-TE1 T 30/29.1

IC17 1130004201 S.IC TC4S66F (TE85R,F) T 29.5/35.7

IC18 1190002660 S.IC ISD4004-08MEYI

[C], [I], [F], [L] only B 13.1/36.5

IC19 1180002391 S.REG S-812C33AMC-C2N-G

[C], [I], [F], [L] only B 24.5/41

Q1 1560000841 S.FET 2SK1829 (TE85R,F) T 46.4/10.8

Q2 1580000731 S.FET 3SK293 (TE85L,F) T 47.3/8.2

Q3 1580000800 S.FET 3SK324UG-TL-E B 41.2/9.1

Q4 1530002601 S.TR 2SC4215-O (TE85R,F) B 23.9/4.1

Q6 1590001650 S.TR XP4601 (TX) B 5.9/26.7

Q7 1560001232 S.FET RD07MVS2-T112 T 59.8/21.9

Q8 1560001241 S.FET RD01MUS1-T113 T 60.2/28

Q9 1530003421 S.TR 2SC5110-O (TE85R,F) B 52.4/29

Q10 1530003311 S.TR 2SC5107-O (TE85R,F) B 47.9/21.9

Q11 1530003311 S.TR 2SC5107-O (TE85R,F) T 43.7/32.1

Q12 1530003311 S.TR 2SC5107-O (TE85R,F) B 47.6/29.5

Q13 1530002920 S.TR 2SC4226-T1 R25 B 45/22.4

Q14 1530002920 S.TR 2SC4226-T1 R25 B 43.9/29.9

Q15 1590001400 S.TR XP1214 (TX) T 45.8/26.2

Q16 1590003790 S.TR KRC404E RTK/P T 43.4/27

Q17 1530003900 S.TR KTC4075 BL-RTK/P B 47.4/37.1

Q18 1560000541 S.FET 2SK880-Y (T5RICOM,F) T 46.4/17.3

Q19 1530003900 S.TR KTC4075 BL-RTK/P B 26/15.9

Q21 1510001090 S.TR KTA2015Y-RTK/P B 52.8/36.5

Q22 1510001090 S.TR KTA2015Y-RTK/P B 31.9/37.9

Q23 1520000840 S.TR KTA1664Y-RTF/P B 72.1/25.4

Q24 1590003800 S.TR KTC811U-GR-RTK/P B 72.1/29.2

Q25 1590003780 S.TR KRA304E-RTK/P B 68.8/31.6

Q26 1550000090 S.FET RSQ035P03TR T 72.9/25.1

Q29 1590003790 S.TR KRC404E RTK/P B 54.6/39.7

Q30 1530003900 S.TR KTC4075 BL-RTK/P

[C], [I], [F], [L] only B 36.7/40.4

Q31 1520000840 S.TR KTA1664Y-RTF/P

D1 1790001670 S.DIO RB706F-40T106 B 55.5/12.3

D2 1750000581 S.DIO 1SV307 (TPH3,F) B 59.8/8.3

D4 1750000721 S.VCP HVC375BTRF-E T 50.2/5.6

D5 1750000581 S.DIO 1SV307 (TPH3,F) B 57/3.5

D6 1790001260 S.DIO MA2S077-(TX) T 59.9/7.9

D7 1790001240 S.DIO MA2S728-(TX) T 56.6/7.9

D8 1750000721 S.VCP HVC375BTRF-E T 54.6/5.6

D9 1750000711 S.VCP HVC350BTRF-E T 43.2/5.6

D10 1750000711 S.VCP HVC350BTRF-E T 38.8/5.6

D12 1790001250 S.DIO MA2S111-(TX) B 47.6/40.1

D14 1790001260 S.DIO MA2S077-(TX) B 51.8/23.7

D15 1790001260 S.DIO MA2S077-(TX) B 51.8/18

D16 1750000771 S.VCP HVC376BTRF-E B 40.6/20.5

D17 1750000771 S.VCP HVC376BTRF-E B 42.8/21.8

D18 1720000471 S.VCP 1SV239 (TPH3,F) T 37.9/21.5

D19 1750000771 S.VCP HVC376BTRF-E B 40.8/27.4

D20 1750000771 S.VCP HVC376BTRF-E B 40.8/28.8

D21 1750000721 S.VCP HVC375BTRF-E B 37.2/22.7

D22 1750000721 S.VCP HVC375BTRF-E B 37.2/29.4

D23 1790001250 S.DIO MA2S111-(TX) T 42.1/8.7

D24 1790001250 S.DIO MA2S111-(TX) B 32.5/29.2

D25 1790001250 S.DIO MA2S111-(TX) T 53.3/15

D26 1790000980 S.DIO MA742 (TX) B 28/1.8

FI1 2030000150 S.MLH FL-335 (46.350 MHz) B 32.4/5.8

FI2 2020002160 S.CER CFWKA450KFFA-R0 B 19.7/21

X1 6070000191 S.DCR CDBKB450KCAY24-R0 T 16.9/9.6

X2 6050011940 S.XTL CR-783 (15.3 MHz) B 28.4/33.4

X4 6050011730 S.XTL CR-765 (3.6864 MHz) B 16.6/29.6

L1 6200012780 S.COL 0.30-1.4-6TL 27.2N B 67.8/7

L2 6200012770 S.COL 0.26-1.1-7TR 24N B 63.4/5.5

L3 6200012470 S.COL 0.30-1.7-7TL 45.3N B 62/11.4

L4 6200012390 S.COL 0.30-0.92-3TR 5.8N B 67.4/13.4

L5 6200012470 S.COL 0.30-1.7-7TL 45.3N B 57.3/5.8

L6 6200005711 S.COL ELJRE 27NGFA B 56.5/7.9

L7 6200008090 S.COL LQW2BHN68NJ03L B 53.6/4.5

L8 6200008090 S.COL LQW2BHN68NJ03L B 50.9/4.5

L9 6200007750 S.COL LQW2BHN56NJ03L B 47.3/7.7

L11 6200007750 S.COL LQW2BHN56NJ03L B 41.3/5.2

L12 6200008090 S.COL LQW2BHN68NJ03L B 44.1/11.3

L13 6200007850 S.COL ELJNC R82K-F B 38.1/11.7

L14 6200005681 S.COL ELJRE 15NGFA B 47.8/12.1

L15 6200002861 S.COL NLV25T-4R7J B 57.2/9.8

L16 6200012400 S.COL 0.30-0.91-4TL 8.6N B 68.6/18.3

L17 6200013100 S.COL 0.45-1.5-5TL 18.3N B 67.3/21.4

L18 6200005701 S.COL ELJRE 22NGFA T 65.5/26.5

L19 6200005741 S.COL ELJRE 47NGFA B 54.4/29

L20 6200003590 S.COL EXCCL3225U1 B 71.9/21.4

L21 6200009181 S.COL ELJRE R10JFA T 47.8/21.4

L22 6200009181 S.COL ELJRE R10JFA B 47.7/27.6

DESCRIPTION

[B], [H], [E], [K], [C], [I], [F], [L] only

H/V

M.

LOCATION

B 41.1/39.7

[MAIN UNIT]

REF ORDER

NO. NO.

L24 6200003640 S.COL MLF1608E 100K-T B 41.4/24.4

L25 6200007760 S.COL LQW2BHN82NJ03L B 38.8/24.9

L26 6200008090 S.COL LQW2BHN68NJ03L B 37.8/31.6

L27 6200007170 S.COL MLF1608A 3R3K-T T 41/21.9

L28 6200007170 S.COL MLF1608A 3R3K-T T 40.4/25.1

L31 6200009181 S.COL ELJRE R10JFA T 58.8/4.8

L32 6200005721 S.COL ELJRE 33NGFA T 37.1/32.1

L33 6200004480 S.COL MLF1608D R82K-T B 27.3/12.7

L35 6200003540 S.COL MLF1608D R22K-T B 27.8/18.1

L37 6200003640 S.COL MLF1608E 100K-T B 40.8/30.1

L38 6200008090 S.COL LQW2BHN68NJ03L B 37.7/21

L39 6200007720 S.COL LQW2BHN33NJ03L B 37.9/27.7

L41 6200009181 S.COL ELJRE R10JFA T 41.3/30.9

L42 6200007170 S.COL MLF1608A 3R3K-T T 36.6/28.5

L43 6200007170 S.COL MLF1608A 3R3K-T T 36.6/25.1

R1 7030003490 S.RES ERJ3GEYJ 272 V (2.7 k) B 59.1/11.7

R2 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) T 55.5/15.2

R3 7030005530 S.RES ERJ2GEJ 100 X (10) T 52.6/20.3

R4 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 56.5/17

R5 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 54.5/15.2