WINGTECH

97511_1_12_20130417_1200.sch-1 - Fri May 24 15:20:33 2013

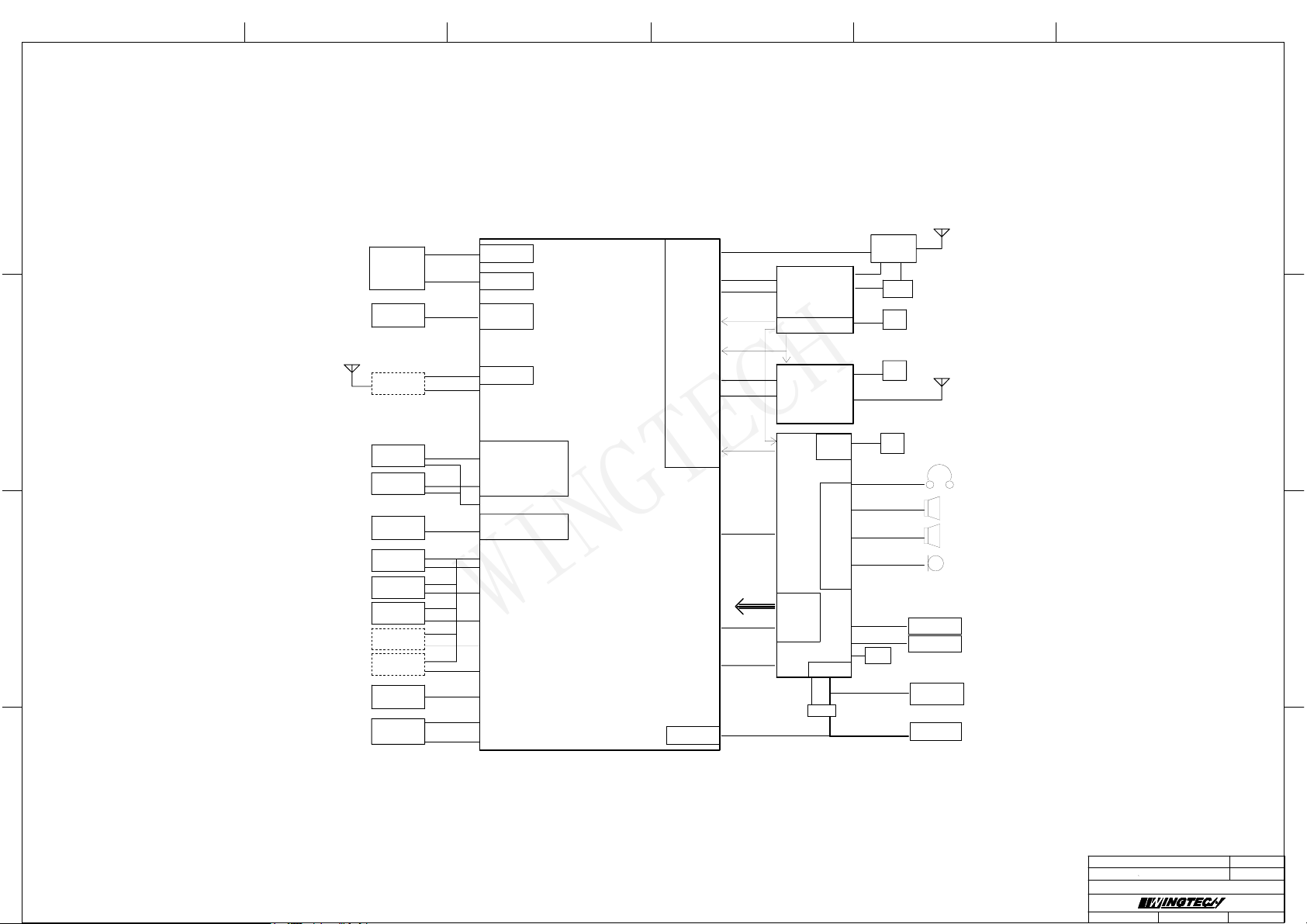

Project : MT6572

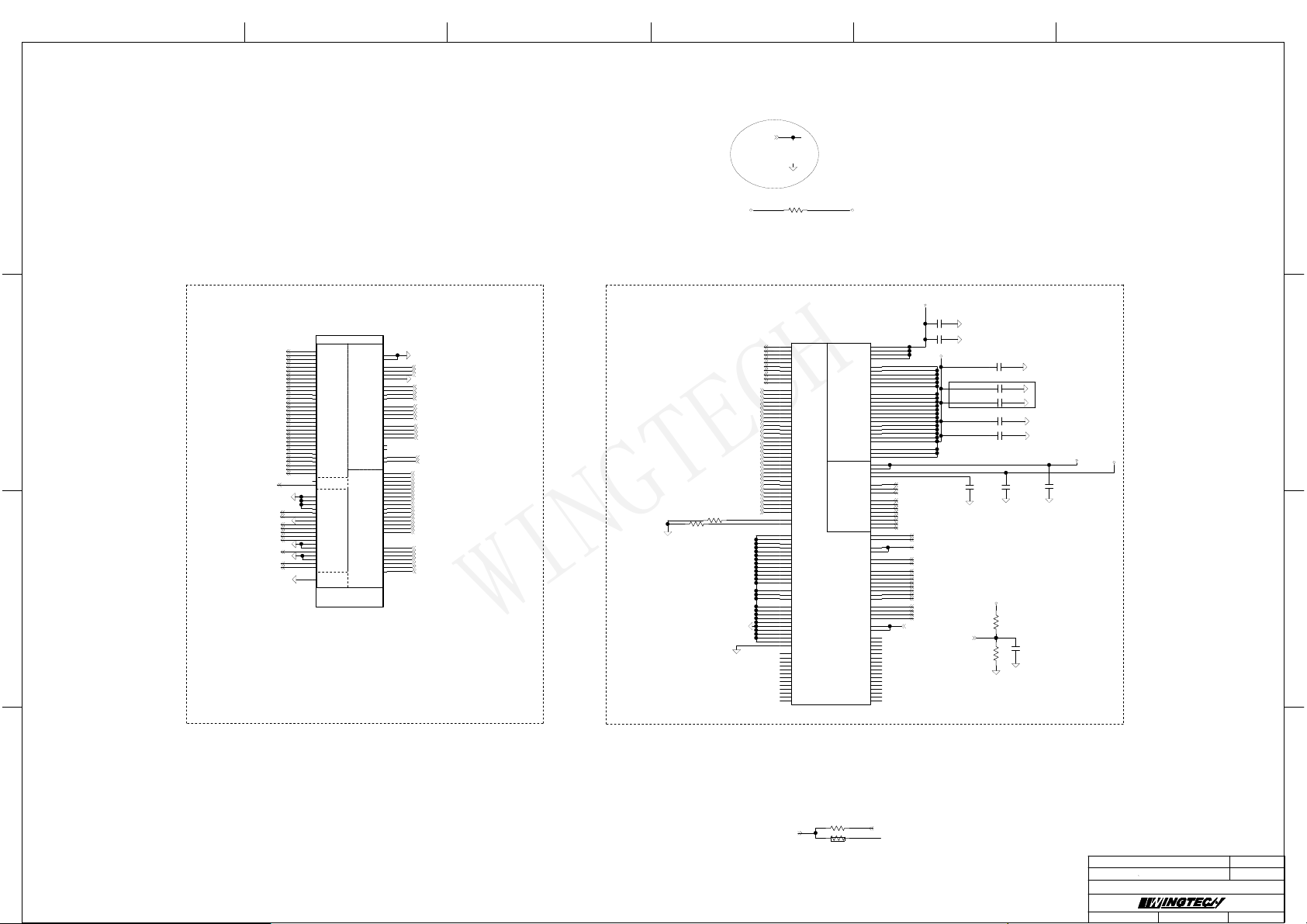

REF_SCH TOP LEVEL

Memory

MCP

micro SD

+ hot-plug

CMMB

Camera

Module

2nd Camera

Module

LCD

module

CTP

controller

Motion

Sensor

ALS + PXS

Magnetic

sensor

Gyro

sensor

Keypad

Debug

port

EMI x32

NFI

MSDC 4-bit

EINT

Camera IF

Camera IF

LCD IF

I2C

EINT

I2C

EINT

I2C

EINT

I2C

EINT

I2C

EINT

JTAG

UART

I2C

EMI

NFI

MSDC1

SPI

CAM

(MIPI / Parallel)

i2C_0

LCD

(MIPI / Parallel)

i2C_1

MT6572

ABB

USB

BPI, APC

RF IQ

BSI ctrl

26M_BB

26M_CN

CONN IQ

CONN ctrl

32K_BB

AUD I/F

SPI

BC1.1

USB 2.0

26M_AUD

POWER

MT6166

DCXO ctrl

26M_CN

MT6627

MT6323

Power

Management

Charger

Audio

Speech

Charger

BJT

RTC

FEM

TX

RX

balun

26M

TCXO

32K

Headset

(HPL, HPR, AU_VIN1)

Class D/AB

Receiver

AU_VIN0

SIM2

SIM1

VIB

Celullar ANT

RX

Connectivity ANT

SIM2

SIM1

Battery

micro USB

TITLE:

DOCUMENT NO.:

DEPARTMENT:

COMPANY:

DESIGNER:

<DESIGNER>

<TITLE>

BLOCK_DIAGRAM

Hardware DEPT.

Last Saved Date:

2013-5-10

<REV>

REV:

SIZED:

A1

OF

SHEET:

1

17

WINGTECH

97511_1_12_20130417_1200.sch-2 - Fri May 24 15:20:33 2013

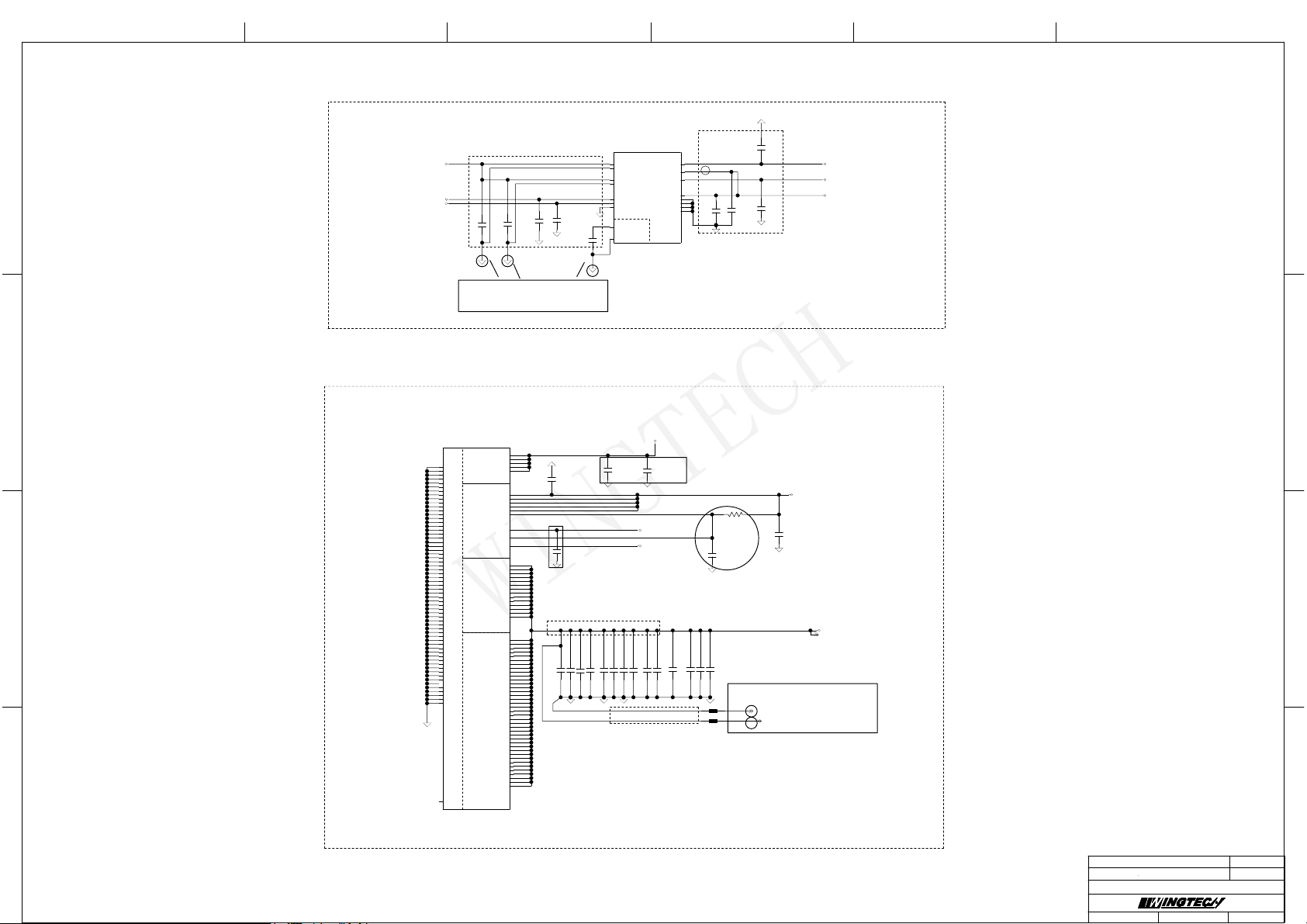

VIO18_PMU

VIO18_PMU

VUSB_PMU

cap Close to BB IC

C101

100nF

C107

100nF

dedicate VSS ball, must return to cap then to main GND:

1. REFN(G6) => C109

2. DVSS18_MIPIRX(U25) => C107

3. DVSS18_MIPITX(P25) => C101

VIO18_PMU

VIO18_PMU

VUSB_PMU

1uF

C113

C104

100nF

T25

U25

R25

P25

H23

G24

G23

REFP

1uF

C109

DVDD18_MIPIRX

DVSS18_MIPIRX

DVDD18_MIPITX

DVSS18_MIPITX

AVDD18_USB

AVDD33_USB

AVSS33_USB

BG

F6

REFP

G6

REFN

BGA428-10.7X10.7-0.4E0.25B(MT6572)

U101-H

AVDD28_DAC

AVDD18_AP

DVDD18_PLLGP

AVDD18_MD

AVSS18_MD

AVSS18_MD

AVSS18_MD

AVSS18_MD

cap Close to BB IC

VTCXO_PMU

F1

E5

VIO18_PMU

U9

D3

A1

A4

C3

E2

C108

100nF

100nF

C128

0.1uF

C112

100nF

C122

VTCXO_PMU

VIO18_PMU

VIO18_PMU

U101-B

VCCIO_EMI

VCC

VCCIO_EMI

Memory

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VSS

VSS

VSS

VSS

VSS

VSS

DUMMY

DVDD

Peripheral

VCC

CPU

VCC

Core

VCCIO_EMI

VCCIO_EMI

VCCIO_EMI

DVDD18_MC0

DVDD18_CAM

DVDD18_VIO_1

DVDD18_VIO_2

DVDD18_VIO_3

DVDD18_LCD

DVDD3_MC1

DVDD3_LCD

DVDD28_BPI

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

AC21

AD11

AF13

AB11

AC8

AB5

AB14

W26

T15

W23

T14

AF26

G3

K21

L11

L12

L14

L15

L16

M5

M11

M12

M13

M14

M15

M16

N10

N8

N9

N11

N12

N13

N14

N15

N16

P10

N22

P11

P12

P13

P14

P15

P16

R10

R11

R12

R13

R14

R15

R16

T10

T11

T12

T13

AF1

U10

U11

V13

W11

Y21

A26

BGA428-10.7X10.7-0.4E0.25B(MT6572)

C405

100nF

1uF

1uF

1uF

C135

C134

C120

4mil - defferential - GND shielding

1uF

C119

VIO_EMI

C406

VMC_PMU

VIO28_PMU

2.2uF

C136

If double-sided SMT, put C405 & C406 below BB.

100nF

If single-sided SMT, put C405 & C406 around memory.

C121

1uF_NF

120mil

10uF

10uF

10uF

C111

2.2uF

C137

C103

C106

C102

4.7uF

HT1

GND

HT2

0

R119

Based on your system level

design , if better FM performance

is needed on your system ,

please refer to FM desense

performance enhance proposal

Vproc remote sense :

differential 4mil with good shielding, from the BB to PMIC

VIO18_PMU

1uF

C126

VPROC_PMU

[3]

[4]GND_VPROC_FB

[4]VPROC_FB

[3]

[2,4]VPROC_PMU

[3]

<REV>

2013-5-10

REV:

SIZED:

A1

OF

2

17

TITLE:

DOCUMENT NO.:

DEPARTMENT:

COMPANY:

DESIGNER:

<TITLE>

01_MT6572_POWER

Hardware DEPT.

Last Saved Date:

<DESIGNER> SHEET:

1.8V IO for DDR1

W9

W12

1.2V IO for DDR2

W14

W16

W19

C124

AA1

K20

L3

J19

H13

AB24

K24

W24

C10

P6

T7

P7

P8

P9

R6

R7

R8

R9

T6

U6

T9

T8

U7

J9

VCCK

J15

VCCK

M9

VCCK

K6

VCCK

K7

VCCK

K8

VCCK

K9

VCCK

K11

VCCK

K14

VCCK

K15

VCCK

M10

VCCK

K16

VCCK

K17

VCCK

U17

VCCK

M17

VCCK

L7

VCCK

L8

VCCK

L9

VCCK

L17

VCCK

M6

VCCK

M7

VCCK

M8

VCCK

J17

VCCK

J16

VCCK

R17

VCCK

T16

VCCK

L6

VCCK

K12

VCCK

T17

VCCK

J10

VCCK

J11

VCCK

U12

VCCK

U13

VCCK

U14

VCCK

U15

VCCK

U16

VCCK

J8

VCCK

J14

VCCK

100nF

VIO18_PMU

VIO18_PMU

VIO18_PMU

VIO18_PMU

VIO18_PMU

DVDD18_LCD

VMC_PMU

DVDD18_LCD

VIO28_PMU

1uF

C117

Close to BB IC, recommand < 150mil

100nF

100nF

100nF

C114

C118

C115

100nF

C116

WINGTECH

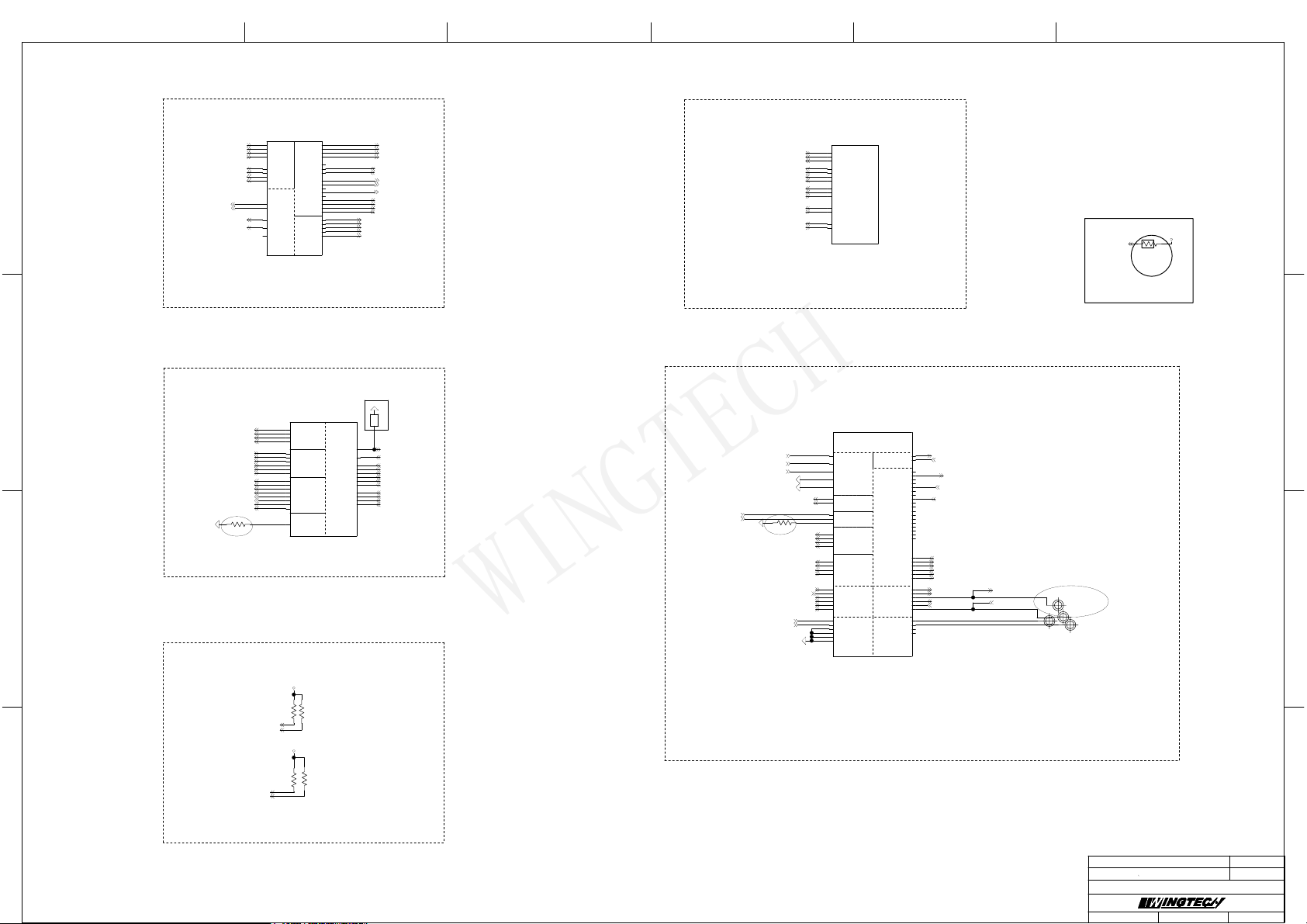

97511_1_12_20130417_1200.sch-3 - Fri May 24 15:20:34 2013

[13]

[13]

[13]

[13]

100-ohm differential

100-ohm differential

close to BB

U101-A

D2

[6]

[7]RX_I_P

DL_I_P

C2

[6]

[7]RX_I_N

DL_I_N

B1

[6]

[7]RX_Q_P

DL_Q_P

C1

[6]

[7]RX_Q_N

DL_Q_N

A2

[6]

[7]TX_I_P

UL_I_P

B2

[6]

[7]TX_I_N

UL_I_N

B4

[6]

[7]TX_Q_P

UL_Q_P

B3

[6]

[7]TX_Q_N

UL_Q_N

A8

VM1

[7]TXBPI

[8]VAPC1

MIPI_TDN2

MIPI_TDP2

R202

1.5k

A7

D5

F2

F3

[11]GPIO_CMPDN2

[11]GPIO_CMRST2

[11]GPIO_CMPDN

[11]GPIO_CMRST

[11]MIPI_RDN0

[11]MIPI_RDP0

[11]MIPI_RDN1

[11]MIPI_RDP1

[11]MIPI_RCN

[11]MIPI_RCP

[10]MIPI_TDN0

[10]MIPI_TDP0

[10]MIPI_TDN1

[10]MIPI_TDP1

[10]MIPI_TCN

[10]MIPI_TCP

MIPI_VRT

VM0

VM1

TXBPI

APC

VBIAS

BGA428-10.7X10.7-0.4E0.25B(MT6572)

[8] VM0

[8]

[6]

[6]

[13]

[13]

[13]

[13]

[13]

[13]

[12]

[12]

[12]

[12]

[12]

[12]

BPI_BUS0

BPI_BUS1

BPI_BUS2

BPI_BUS3

BPI_BUS4

BPI_BUS5

BPI_BUS6

BPI_BUS7

BPI_BUS8

BPI_BUS9

BPI_BUS10

BPI_BUS11

BPI_BUS12

BPI_BUS13

BPI_BUS14

BPI_BUS15

BSI_DATA2

BSI_DATA1

BSI_DATA0

BSI_EN

BSI_CLK

U101-G

L25

CMPDN2

K25

CMRST2

H22

CMPDN

J22

CMRST

R24

RDN0

MIPI_CAM

R23

RDP0

R22

RDN1

R21

RDP1

R26

RCN

T26

RCP

P19

TDN0

MIPI_LCD

P20

TDP0

N25

TDN1

N26

TDP1

P23

TDN2

P24

TDP2

N20

TCN

N19

TCP

P26

VRT

BGA428-10.7X10.7-0.4E0.25B(MT6572)

B12

B11

C12

A11

D11

C11

A13

A10

B10

D10

E9

E8

B9

B8

E7

D7

D6

C7

F9

F11

G11

Based on your system level design , if better

desense performance is needed on your

system , please refer to desense

performance enhance proposal

MIPI_2nd_CAM

Parallel 8-bit

CMMCLK

CMPCLK

RCN_A

RCP_A

RDN1_A

RDP1_A

RDN0_A

RDP0_A

CMDAT3

CMDAT2

CMDAT1

CMDAT0

[6]

[7,8]BPI_0

[6]

[7,8]BPI_1

[6]

[7,8]BPI_2

[6]

[7,8]BPI_3

[6]EINT_HP

[5]

[8]

W_PA_B1_EN

[8]

W_PA_B2_EN

[8]W_PA_B8_EN

[80]

[16]EINT_MAG

[16]EINT_ALPXS

[16]EINT_ACC

[16]EINT8_ACC1

[6]

[7]BSI-A_DAT2

[6]

[7]BSI-A_DAT1

[6]

[7]BSI-A_DAT0

[6]

[7]BSI-A_EN

[6]

[7]BSI-A_CK

Y22

[11]CMMCLK

Y23

[11]CMPCLK

V25

W25

V24

[11]CMDAT7

V23

[11]CMDAT6

U22

[11]CMDAT5

U21

[11]CMDAT4

Y26

[11]CMDAT3

Y25

[11]CMDAT2

AA25

[11]CMDAT1

AB25

[11]CMDAT0

[3]

[4]AUD_MISO

[3]

[4]AUD_CLK

[3]

[4]AUD_MOSI

[3]

90-ohm differential

[9]USB_DM

[9]USB_DP

close to BB

[3,4]

[3,6]

[6]

[3]

[3]

[3]

[3]

[3]

[3]

[3]

[3]

[3]

[3]

[4] BAT_ID_ADC

[4,7]SRCLKENA

[4]EINT_PMIC

[3,4]SIM1_SCLK

[4]SIM1_SIO

[4]SIM2_SCLK

[4]SIM2_SIO

[7]CLK1_BB

[4]CLK32K_BB

[4]RESETB

[3]

[3]

R203

5.1K

[13]

[13]

[12,21]

[12,21]

SPI_MISO

[80]

SPI_MOSI

[80]

SPI_SCK

[80]

SPI_CSB

[80]

[18]

[18]

[18]

[18]

[18]

[18]

[12]GPIO_GPS_LNA_EN

[21]

[21]

[13]

[13]

[13]

[11]CMVSYNC

[13]

[11]CMHSYNC

[13]

[13]

[13]

[13]

[13]

[13]

[13]

[13]

[14]

[14]

[4,5]PMIC_SPI_CS

[4,5]WATCHDOG

[10]LCD_ID_ADC

[4]PMIC_SPI_MOSI

[4]PMIC_SPI_MISO

[4]PMIC_SPI_SCK

[4]CHD_DP

[4]CHD_DM

USB_VRT

[3,11]SCL_0

[3,11]SDA_0

[3,10,16]SCL_1

[3,10,16]SDA_1

[14]MC1CMD

[14]MC1CK

[14]MC1DAT0

[14]MC1DAT1

[14]MC1DAT2

[14]MC1DAT3

U101-D

J1

AUD_DAT_MISO

K5

AUD_CLK_MOSI

K1

AUD_DAT_MOSI

L2

PMIC_SPI_MOSI

L5

PMIC_SPI_MISO

L4

PMIC_SPI_SCK

K2

PMIC_SPI_CSN

G2

WATCHDOG

H4

SRCLKENA

J2

EINTX

H5

SIM1_SCLK

M3

SIM1_SIO

J5

SIM2_SCLK

M1

SIM2_SIO

BGA428-10.7X10.7-0.4E0.25B(MT6572)

U101-E

E1

CLK26M

H2

CLK32K_IN

M2

SYSRSTB

G4

TESTMODE

AC24

FSOURCE

J26

CHD_DP

J25

CHD_DM

G26

USB_DM

G25

USB_DP

H25

USB_VRT

C25

SCL_0

C26

SDA_0

B24

SCL_1

B23

SDA_1

F24

SPI_MISO

F25

SPI_MOSI

F23

SPI_SCK

E23

SPI_CS

K23

MC1_CMD

L21

MC1_CK

K22

MC1_DAT0

M22

MC1_DAT1

M25

MC1_DAT2

L26

MC1_DAT3

B7

AUX_IN0

B6

AUX_IN1

C5

AUX_IN2_XP

B5

AUX_IN3_YP

C4

AUX_IN4_XM

A5

AUX_IN5_YM

SYSTEM

BC 1.1

USB 2.0

i2C

SPI

T-flash

ADC

reserve for JTAG debug

VIO18_PMU

R210

[3,4]SIM1_SCLK

20K_NF

Normal : NC

JTAG : 20K

Reserve R footprint

for JTAG debugging

D12

PWM_A

PWM

E12

PWM_B

LCD

N1

LPD17

Parallel

N2

LPD16

N3

LPD15

P2

LPD14

N4

LPD13

R2

LPD12

N5

LPD11

R1

LPD10

P5

LPD9

T1

LPD8

R5

LPD7

T2

LPD6

T5

LPD5

U2

LPD4

T3

LPD3

U5

LPD2

T4

LPD1

V2

LPD0

AD25

LPCE0B

AB26

LPTE

AC26

LRSTB

AA22

LPRDB

AB23

LPA0

AC25

LPWRB

B25

KROW0

KP

A24

KROW1

B26

KROW2

C24

KCOL0

D24

KCOL1

A25

KCOL2

E25

UTXD1

UART

D25

URXD1

E26

UTXD2

F26

URXD2

EINT_CMMB

GPIO_TV_RST

KROW1

[15]KCOL1

[11]GPIO_FLASH_EN

[80]

[12]

[10]EINT_CTP

[10]LCD_BL_CTL

[80]

[14]MC1_INS

[18]

[80]

[16]EINT_GY

[12]

[10]LPTE

[12]

[10]GPIO_LRSTB

[11]GPIO_FLASH_SEL

[80]

[80]

[10]GPIO_CTP_RSTB

[12]

[20]

[15]KROW0

[20]

[20]

[9,15]KCOL0

MT6572 support JTAG from below :

1. KP (recommand)

KROW2

2. MC1

KCOL2

3. CAM

for JTAG pin out from MC1/CAM, refer

to HW design notice

UTXD1

URXD1

KROW2

TP205

KCOL2

TP206

TP201

TP202

VCAMD_IO_PMU

2.2K

2.2K

R204

[12,21]

[12,21]

[13]

[13]

R205

Power by CAM_IO

[3,11]SCL_0

[3,11]SDA_0

VIO18_PMU

2.2K

2.2K

R207

R206

[3,10,16]SCL_1

[3,10,16]SDA_1

Power by CTP, MEMS sensor

BGA428-10.7X10.7-0.4E0.25B(MT6572)

TITLE:

DOCUMENT NO.:

DEPARTMENT:

COMPANY:

DESIGNER:

<TITLE>

02_MT6572_BASEBAND

Hardware DEPT.

Last Saved Date:

<DESIGNER> SHEET:

2013-5-10

<REV>

REV:

SIZED:

A1

OF

3

17

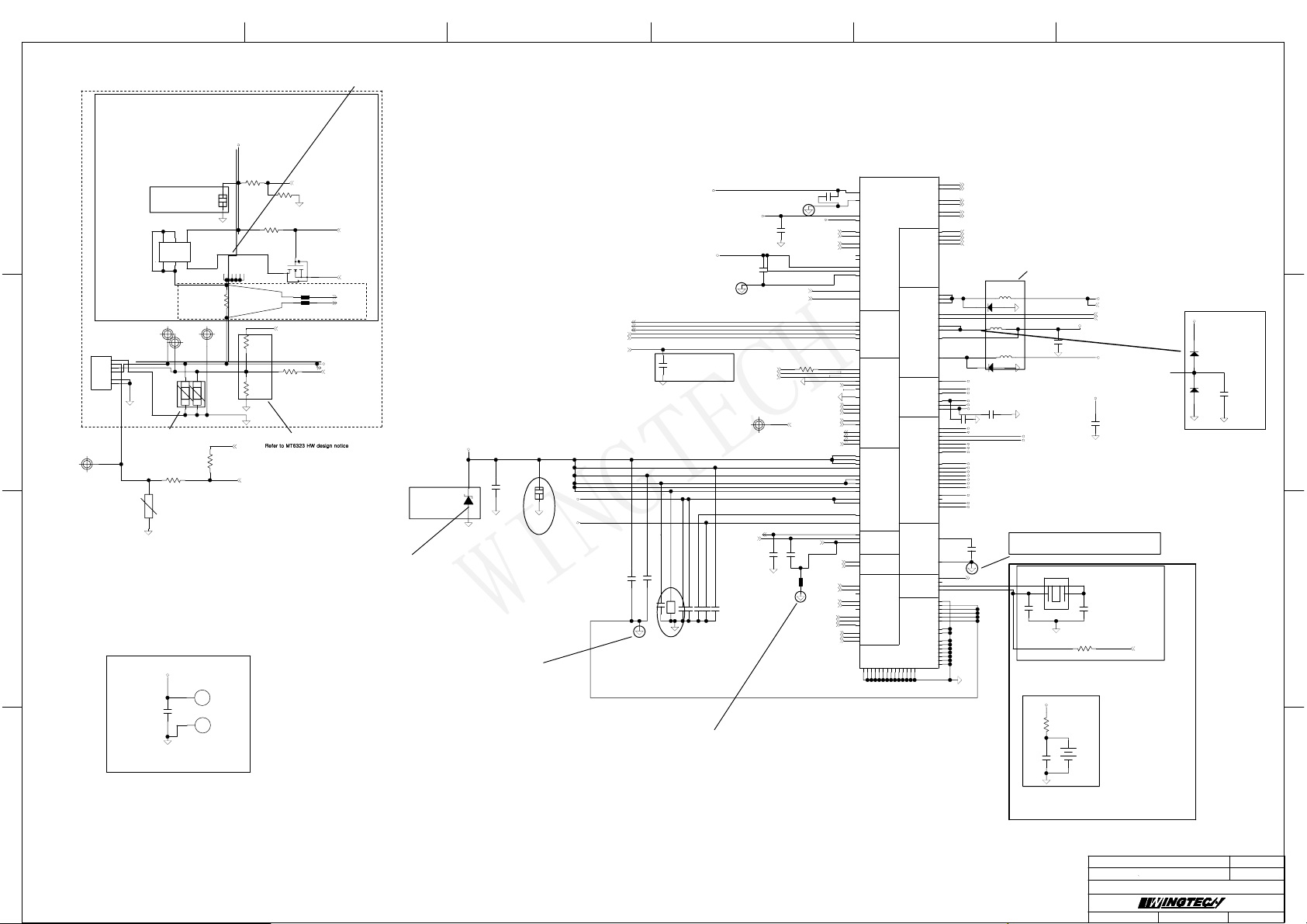

WINGTECH

97511_1_12_20130417_1200.sch-4 - Fri May 24 15:20:36 2013

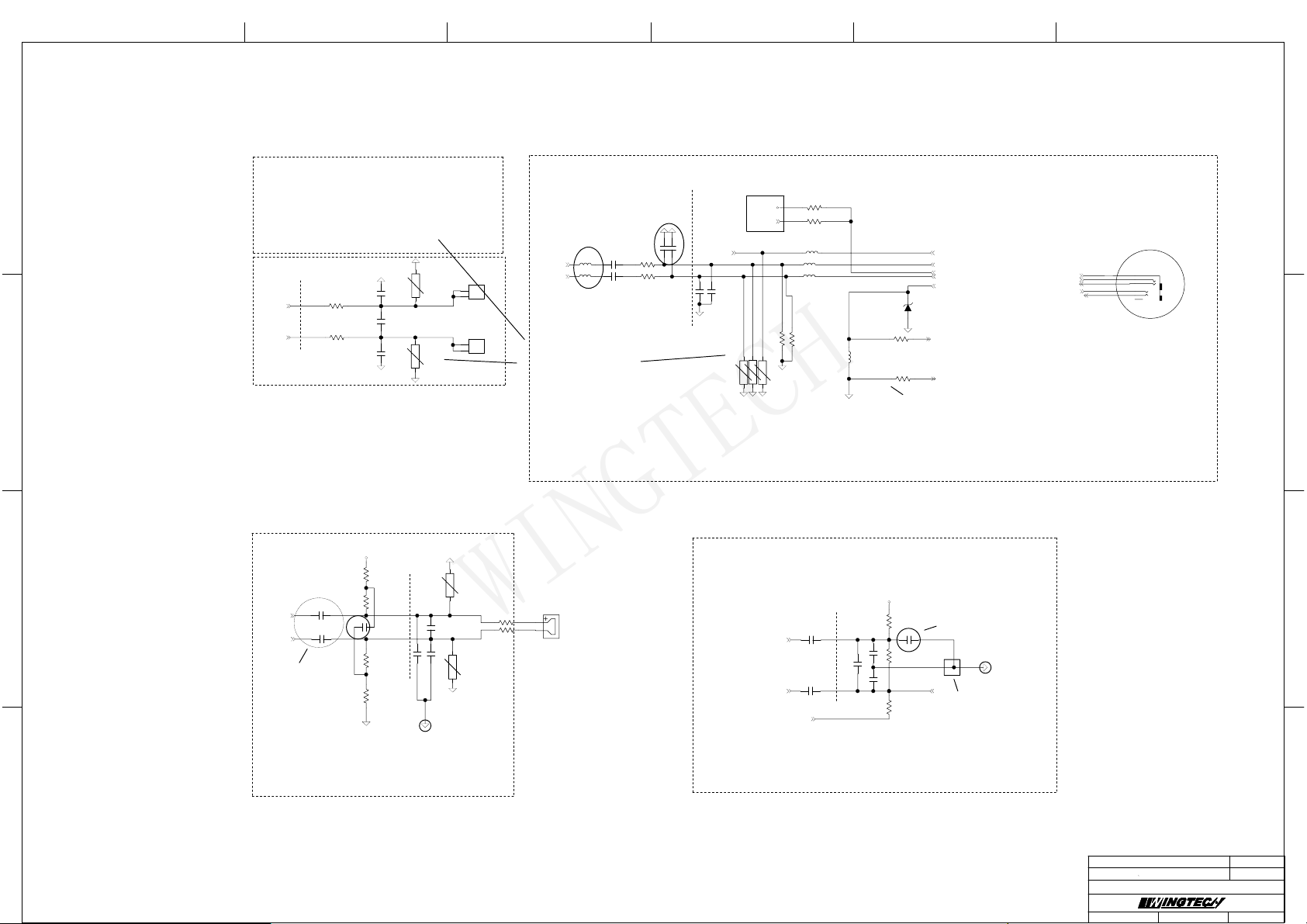

Before you select BJT , please take power dissipation into consideration.

Refer to MT6323 design notice

Charger

VBUS

1. Close to Battery Connector.

(Rsense (R328) <10mm)

2. Main path should be 40mil.

(VBUS -> U303's E, -> U303's C -> R328 -> VBAT)

3. Star connection from R328 to BAT Connector

BATTERY

CON301

CONNECTOR

BBATTCON-BAC3290400

TP9

1

TP-1.0MM

cap rating depends on

Phone OVP spec.

C

C

16

TP-1.0MM

TP310

1

2

3

4

5

6

Based on your system level design , if

better ESD performance is needed on

your system, please refer to ESD

performance enhance proposal

VR310

VIBR_PMU

Vibra

1uF

52

E

C

U303

40mils

BC

34

Rsense

TP-1.0MM

TP312

TP-1.0MM

TP311

1

1

40mils 40mils

VR301

VR302

R360

1K

1

AUDIO-CON_SPK(MIC-RE-MOT)

C311

1

AUDIO-CON_SPK(MIC-RE-MOT)

R329

330K

1uF

C329

40mils

40mils

4mil

40mils

0.2

R328

SR0805

4mil

40mils

AUXADC_REF

1

R334

16.9K

R335

27K

[2,3,4,5,7,10,14,16]

VIO18_PMU

R361

20K

BAT_ID_ADC

[4]VCDT

VCDT rating: 1.268V

VCDT rating: 1.268V

R324

39K

R331

3.3K

1

G

U305

3

D

2

[4]VDRV

S

FET-N-2SK3541T2L

HT303

Differential

HT304

[6]

[4,7]AUXADC_REF

R317

1K

R334,R335 must to be close to

PMIC AUXADC_REF pin

if battery NTC is 10kohm, R334=16.9K, R335=27K

if battery NTC is 47kohm, R334=61.9K, R335=100K

Refer to MT6323 HW design notic

[3]

[4]ISENSE

[4]BATSNS

VBAT

[6]

[4,7,8,10,11,15]VBAT

[4]BAT_ON

e

[4]CHR_LDO

[6]

Add Zenar Diode

Place on the path

from VBAT to IC

(Battery connector

or test point or IO

connector)

VF : 4.85V~5.36V

Between IC and IO port

Refer to MT6323 design

notice for Zener selection

CON3

CON4

VBAT

80mil

500mW

10uF

C310

D302

21

Refer to MT6323 design notice

for Buck GND layout rule

C330

Based on your system level design , if

better EOS performance is needed on your

system, please refer to EOS performance

enhance proposal

10uF_NF

VSYS_PMU

VIO18_PMU

ISENSE/BSTSNS 4mil

[6]

[4]BATSNS

differential to Rsense

[4]ISENSE

[4]BAT_ON

[4]VCDT

[4]VDRV

[4]CHR_LDO

1uF

C316

Close to PMIC

40mil

4mil (VPA no use)

15mil

20mil

20mil

20mil

20mil

10uF

C301

VBAT

VBAT

VBAT

VBAT

VBAT

10uF

C303

1uF

10uF

10uF

C304

C306

C309

refer to system analog LDO

performance improve proposal

Refer to GPS co-clock layout rule

VBAT

VA_PMU

C322 must to be close

to PMIC AUXADC_TSX pin

1uF

1uF

C350

4.7uF

Connect TSX/XTAL GND

to AUXADC_GND first

C307

C308

than connect to main GND

CHARGER

VBAT INPUT

SIM LVS

AUDIO

AUXADC

H10

U301

K1

[9]AU_SPKP

SPK_P

SPK_N

AU_HSP

AU_HSN

AU_HPL

AU_HPR

ISINK0

DRIVER

ISINK1

ISINK2

ISINK3

BUCK OUTPUT

VPROC

VPROC

VPROC

VPROC_FB

GND_VPROC_FB

VPA

VPA

VPA_FB

VSYS

ALDO OUTPUT

VA

VCN28

VTCXO

VCAMA

VCN33

AVDD33_RTC

DLDO OUTPUT

VM

VRF18

VIO18

VIO28

VCN18

VCAMD

VCAM_IO

VEMC_3V3

VMC

VMCH

VUSB

VSIM1

VSIM2

VGP1

VIBR

VGP2

VGP3

VCAM_AF

VREF

GND_VREF

RTC_32K1V8

RTC

RTC_32K2V8

XIN

XOUT

GND_ISINK

GND_VSYS

GND_VPA

GND_VPROC

GND_VPROC

GND_VPROC

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDOG8GND_LDOG9GND_LDOH6GND_LDOH7GND_LDOJ9GND_LDOJ8GND_LDOJ7GND_LDOJ6GND_LDO

GND_LDOH9GND_LDO

GND_LDO

GND_LDO

H8

H5

G7

[5]

L1

[9]AU_SPKN

[5]

H1

[6]AU_HSP

[5]

G1

[6]AU_HSN

[5]

H4

[6]AU_HPL

[5]

J4

[6]AU_HPR

[5]

E9

ISINK0

[12]

C9

ISINK1

[12]

E10

ISINK2

[12]

C10

[15]ISINK3

[12]

Please use inductor recommand by MTK

Refer to MT6323 design notice

C14

D14

E14

B12

C12

A14

B14

D12

H14

M3

N3

L4

P3

M6

C3

J13

H11

L12

M4

J12

K14

L13

P7

L6

P4

N6

P9

N9

L8

M7

N8

L14

N7

P14

N14

D5

C4

A3

A4

B10

G11

E13

E11

F11

F10

K6

K8

F5

F6

F7

F8

F9

G5

G6

VPA_PMU

C355

VSYS_SW

VREF

32K_IN

32K_OUT

VA_PMU

VCN_2V8_PMU

VTCXO_PMU

VCAMA_PMU

VCN_3V3_PMU

VRTC

1uF

VM_PMU

VRF18_PMU

VCN_1V8_PMU

VCAMD_PMU

VCAMD_IO_PMU

VEMC_3V3_PMU

VMC_PMU

VMCH_PMU

VUSB_PMU

VSIM1_PMU

VSIM2_PMU

VGP1_PMU

VIBR_PMU

VGP3_PMU

VCAM_AF_PMU

C320

L301

0.68UH

2

1

A

C

NF

D301

L305

2.2UH

L303

0.68UH

2

1

A

C

NF

D303

C331

100nF

VIO18_PMU

VIO28_PMU

dedicate VSS ball, must return to cap then to main GND:

100nF

1. GND_VREF(N14) => C320

[3]CLK32K_BB

[2]

X301

RTC 32K : X301+C324+C319=> mount, R333=> NC

32K-less: X301+C324=> remove, C319+R333=> 0R

12

18PF

XTAL-32.768K-KYOCERA

C324

Close to chip

VRTC

1K

C325

2.2uF

C337

12

R312

22uF

VPROC_PMU

[1]

[2,4]

VPROC_PMU

[2]VPROC_FB

[1]

[1]

VPA_PMU

C354

GND_VPROC_FB

[2]

VSYS_PMU

VEMC_3V3_PMU

0.1uF

VPA_SW

2

1

2

1

靠近L305

VBAT

D306

D305

SOD-323

0.1uF

C345

SOD-323

RTC

18PF

C319

R333

0_NF

12

GB301

3V_NF

[7]DCXO_32K

[6]

BGA145-5.8X5.8-0.4E0.25B(MT6323)

C313

P1

AUXADC_REF

AUXADC_TSX

[7]GND_AUXADC

[2]

[2]

[19]

[19]

[19]

[19]

[19]

[19]

2.2uF

BATSNS

ISENSE

BAT_ON

VCDT

VDRV

CHR_LDO

[3]AUD_CLK

[3]

[3,5]PMIC_SPI_CS

[3]PMIC_SPI_MOSI

[3]PMIC_SPI_MISO

GND_AUXADC

[3]SIM1_SCLK

[3]SIM1_SIO

[3]SIM2_SCLK

[3]SIM2_SIO

VBAT_SPK

L2

GND_SPK

F2

AU_MICBIAS0

G2

AU_MICBIAS1

E4

[6]AU_VIN0_P

AU_VIN0_P

F4

[6]AU_VIN0_N

AU_VIN0_N

G3

[6]AU_VIN1_P

AU_VIN1_P

G4

[6]AU_VIN1_N

AU_VIN1_N

D2

AU_VIN2_P

D1

AU_VIN2_N

J2

AVDD28_ABB

D3

AVDD28_AUXADC

H2

GND_ABB

E2

ACCDET

E1

CLK26M

P13

BATSNS

P12

ISENSE

K3

BATON

A12

VCDT

M13

VDRV

N13

CHRLDO

CONTROL SIGNAL

M2

PWRKEY

A1

SYSRSTB

K4

RESETB

A9

FSOURCE

A7

[3]EINT_PMIC

INT

N12

EXT_PMIC_EN

N2

PMU_TESTMODE

E7

[3]AUD_MOSI

AUD_MOSI

E8

AUD_CLK

B6

[3]AUD_MISO

AUD_MISO

A2

[3,7]SRCLKENA

SRCLKEN

M1

[4]FCHR_ENB

FCHR_ENB

D9

SPI_CLK

B7

SPI_CSN

D8

SPI_MOSI

B8

SPI_MISO

F13

VBAT_VPROC

F14

VBAT_VPROC

G13

VBAT_VPROC

A13

VBAT_VPA

H13

VBAT_VSYS

P8

VBAT_LDOS3

P6

VBAT_LDOS3

P5

VBAT_LDOS2

P2

VBAT_LDOS1

J14

AVDD22_BUCK

M14

AVDD22_BUCK

A8

DVDD18_DIG

A5

DVDD18_IO

C2

AUXADC_VREF18

B1

AUXADC_AUXIN_GPS

B2

AVSS28_AUXADC

BC 1.1

A10

[3]CHD_DM

CHG_DM

A11

[3]CHD_DP

CHG_DP

B5

SIM1_AP_SCLK

M11

SIMLS1_AP_SIO

E6

SIM1_AP_SRST

C5

SIM2_AP_SCLK

K11

SIMLS2_AP_SIO

D6

SIM2_AP_SRST

M9

[13]SCLK

SIMLS1_SCLK

N11

[13]SIO

SIMLS1_SIO

M10

[13]SRST

SIMLS1_SRST

K9

[13]SCLK2

SIMLS2_SCLK

L11

[13]SIO2

SIMLS2_SIO

K10

[13]SRST2

SIMLS2_SRST

GND_LDO

J10

VBAT

MICBIAS0

[20]

[2]

[2]

[3]RESETB

TP301

[4,7]AUXADC_REF

[6]

[7]AUXADC_TSX

[6]

1uF

C314

[15]PWRKEY

100nF

[3,5]WATCHDOG

C323

VA_PMU

1uF

C312

[5]

[6]

R316

DVDD18_DIG_PMIC

VIO18_PMU

[6]

1uF

[2,4]

HT301

[2]

[2]

[2]

C322

MICBIAS1

[5]

[5]

[5]

[5]

[6]ACCDET

[7]CLK4_AUDIO

[2]

[2]

[2]

[2]

[2,6]

[4]FCHR_ENB

PMIC_SPI_SCK

[2]

[2]

[2]

[2]

1K

==> for longer RTC time sustain after battery remove,

please refer to RTC design notice

TITLE:

DOCUMENT NO.:

DEPARTMENT:

COMPANY:

<DESIGNER> SHEET:

DESIGNER:

<TITLE>

03_MT6323

Hardware DEPT.

Last Saved Date:

2013-5-10

<REV>

REV:

SIZED:

A1

OF

4

17

WINGTECH

97511_1_12_20130417_1200.sch-5 - Fri May 24 15:20:37 2013

U101-F

DRAM

DRAM

Data

Ctrl

ED31

ED30

ED29

ED28

ED27

ED26

ED25

ED24

ED23

ED22

ED21

ED20

ED19

ED18

ED17

ED16

ED15

ED14

ED13

ED12

ED11

ED10

ED9

ED8

ED7

ED6

ED5

ED4

ED3

ED2

ED1

ED0

NAND I/F

VREF1

VREF0

DRAM

Address

EA18

EA17

EA16

EA15

EA14

EA13

EA12

EA11

EA10

EA9

EA8

EA7

EA6

EA5

EA4

EA3

EA2

EA1

EA0

ERESET

BGA428-10.7X10.7-0.4E0.25B(MT6572)

ECS0_B

ECS1_B

ERAS_B

ECAS_B

EDQS0_B

EDQS1_B

EDQS2_B

EDQS3_B

EDCLK0_B

EDCLK0

EDCLK1_B

EDCLK1

EWR_B

EDQM0

EDQM1

EDQM2

EDQM3

EDQS0

EDQS1

EDQS2

EDQS3

GPIO47

AF22

AF19

AF21

[5]EA3

AD21

[5]EA7

AB20

[5]EA5

AD24

ECKE

AB13

AD12

EDQM0

AD8

AE12

AA14

Y13

Y8

AA9

Y14

AA13

AA8

EDQS3_B

Y9

Y18

AA18

AA19

EDCLK_B

Y19

AA2

ND0

NLD1

Y2

NLD8

ND1

W1

NLD3

ND2

W3

ND3

NLD13

AB1

ND4

ND5

ND6

ND7

ND8

ND9

ND10

ND11

ND12

ND13

ND14

ND15

NCEB

NWRB

NREB

NCLE

NALE

NRNB

[5]NLD10

AD2

[5]

NLD5

W4

NLD12

AE1

[5]NLD14

W2

NLD9

Y3

NLD6

AC2

[5]

NLD4

AC1

[5]NREB

Y4

NLD0

V5

NLD2

AE2

[5]NLD7

V1

NLD15

W5

NCEB

Y5

NWRB

AB2

GPIO46

AC3

AD3

AE3

AB3

[5] EVREF

[5] ECS1_B

BA[1:0] =

[5] ECS0_B

EA[15:14]

(LPDDR1)

[5]

[5] ED8

[5] ED10

[5] ED14

[5] ED9

[5] ED13

[5] ED15

[5] ED11

[5] ED26

[5] ED25

[5] ED28

[5] ED30

[5] ED29

[5] ED27

[5] ED31

[5] ED24

[5] ED7

[5] ED0

[5] ED1

[5] ED6

[5] ED2

[5] ED3

[5] ED5

[5] ED4

[5] ED17

[5] ED22

[5] ED18

[5] ED21

[5] ED16

[5] ED19

[5] ED20

[5] ED23

[5] ECKE

[5] EA4

[5] EA6

[5] EA8

[5] EA2

[5] EA9

[5] EA0

[5] EA1

AF6

ED12

AE6

AF8

AE7

AE8

AC9

AC7

AB9

AF5

AE5

AD5

AC5

AE4

AF3

AF2

AB6

AE11

AD15

AE10

AE9

AF12

AF11

AF9

AC13

AE16

AE13

AE15

AE14

AF15

AF16

AC15

AB16

AB17

AC11

AB18

AE18

AE17

AE21

AB19

AE22

AC23

AD22

AD18

AE25

AE23

AF25

AE24

AF24

AE26

AC18

AE19

AE20

AF18

AC22

Please make sure the ball map is

match to the MCP type you selected

[2,3]

[3,4] PMIC_SPI_CS

HW trapping PIN

20K: VM=1.8V

NC : VM=1.2V

VM_PMU VIO_EMI

[5]EDQM2

[5]

[5]EDQM3

[5]EDQM1

[5]EDQS2

[5]EDQS0

[5]EDQS3

[5]EDQS1

[5]EDQS2_B

[5]EDQS0_B

[5]

[5]EDQS1_B

[5]

[5]EDCLK

R454

2

1

R455

2

1

240

240

[5]

[5]NCLE

[5]NALE

[5]NRNB

[5]NLD11

0

R401

U3

[5]EA0

CA0

T3

[5]EA1

CA1

R3

[5]EA2

CA2

R2

[5]EA3

CA3

R1

[5]EA4

CA4

K2

[5]EA5

CA5

J2

[5]EA6

CA6

J3

[5]EA7

CA7

H3

[5]EA8

CA8

H2

[5]EA9

CA9

[5]ED0

T8

DQ0

[5]ED1

R8

DQ1

[5]ED2

R7

DQ2

[5]ED3

R9

DQ3

[5]ED4

R6

[5]ED5

P7

[5]ED6

P8

[5]ED7

P9

[5]ED8

K9

[5]ED9

K8

[5]ED10

K7

[5]ED11

J6

[5]ED12

J9

[5]ED13

J7

[5]ED14

J8

[5]ED15

H8

[5]ED16

W7

[5]ED17

U6

[5]ED18

W8

[5]ED19

T5

[5]ED20

U7

[5]ED21

W9

[5]ED22

V8

[5]ED23

T6

[5]ED24

H6

[5]ED25

F8

[5]ED26

E9

[5]ED27

G7

[5]ED28

H5

[5]ED29

E8

[5]ED30

G6

[5]ED31

E7

G3

F3

F6

F9

G10

H10

J5

K10

M5

P10

R5

T10

U10

V6

V9

T1

M1

H1

B9

E1

F2

F5

G1

L2

M8

U1

V2

V5

C3

A1

A2

A9

A10

B1

B10

E10

W1

W10

Y1

Y2

Y9

Y10

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

ZQ0

ZQ1/NC

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSCA

VSSCA

VSSCA

VSSM

VSSM

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSQM

DNU

DNU

DNU

DNU

DNU

DNU

DNU

DNU

DNU

DNU

DNU

DNU

DNU

LP-DDR2

eMMC

Power

CS1#/NC

CKE1/NC

VREFCA

VREFDQ

Memory MCP

VIO18_PMU

C421

12

4.7uF

C422

EMMC_VDDI

12

100nF

VIO_EMI

Put C402 & C403 between BB & memory.

[5]NREB

[5]NLD10

[5]NRNB

[5]NALE

[5]NCLE

[5]NLD4

[5]NLD5

[5]NLD7

[5]NLD14

[5]NLD11

[5]NWPB

[5]ECS0_B

[5]ECS1_B

[5]ECKE

[5]EDCLK

[5]EDCLK_B

[5]EDQS0

[5]EDQS0_B

[5]EDQS1

[5]EDQS1_B

[5]EDQS2

[5]EDQS2_B

[5]EDQS3

[5]EDQS3_B

[5]EDQM0

[5]EDQM1

[5]EDQM2

[5]EDQM3

[5]EVREF

U402

E6

VDD1

F1

VDD1

V1

VDD1

W6

VDD1

E5

VDD2

G2

VDD2

K1

VDD2

M7

VDD2

U2

VDD2

W5

VDD2

F7

VDDQ

F10

VDDQ

G5

VDDQ

H9

VDDQ

J10

VDDQ

L6

VDDQ

M6

VDDQ

N6

VDDQ

R10

VDDQ

T9

VDDQ

U5

VDDQ

V7

VDDQ

V10

VDDQ

J1

VDDCA

L1

VDDCA

T2

VDDCA

A8

VCC

B2

VCC

B8

VCCQ

A5

VDDI

B5

CLKM

C1

RST

C5

CMD

B4

DAT7

A4

DAT6

A6

DAT5

B6

DAT4

A7

DAT3

B7

DAT2

B3

DAT1

A3

DAT0

P1

CS0#

P2

N1

CKE0

N2

M3

CLK

L3

CLK#

P6

DQS0

P5

DQS0#

K6

DQS1

K5

DQS1#

U8

DQS2

U9

DQS2#

G8

DQS3

G9

DQS3#

N5

DM0

L5

DM1

T7

DM2

H7

DM3

K3

M9

C2

NC

C4

NC

C6

NC

D1

NC

D2

NC

D3

NC

D4

NC

D5

NC

D6

NC

E2

NC

E3

NC

M2

NC

N3

NC

P3

NC

V3

NC

W2

NC

W3

NC

Hynix H9TP32A4GDMCPR;H9TP32A8JDMCPR-KGM;Micron MT29PZZZ4D4TKETF-25

100nF

12

[5]EVREF

C410

4.7uF

12

C401

100nF

C402

12

100nF

C403

1uF

12

C129

12

4.7uF

C110

1uF

12

VIO_EMI

1

10K

R452

2

1

10K

R453

2

12

C404

C453

12

VEMC_3V3_PMU

VIO18_PMU

4.7uF

C412

12

100nF

0_NF

R412

2

1

[5]NWPB

2

1

R413

0

[3,4]WATCHDOG

GPIO46

<REV>

2013-5-10

REV:

SIZED:

A1

OF

5

17

TITLE:

DOCUMENT NO.:

DEPARTMENT:

COMPANY:

DESIGNER:

<TITLE>

04_MEMORY_EMMC_LPDDR2

Hardware DEPT.

Last Saved Date:

<DESIGNER> SHEET:

WINGTECH

97511_1_12_20130417_1200.sch-6 - Fri May 24 15:20:38 2013

Based on your system level design , if better

desense performance is needed on your

system , please refer to desense

performance enhance proposal

Receiver

close to connectorclose to IC

[4]

AU_HSP

[3]

[3]

[4]

AU_HSN

R520

0

R521

0

Handset Microphone 1

C511

[4] AU_VIN0_P

[4] AU_VIN0_N

if you use digital MIC,

please change cap

(C511,C512) to 1.0uF

0.1uF

0.1uF

C512

together then single via to main GND

MICBIAS0

R514

R515

C513

4.7uF

R516

1K

Earphone Audio

Reserve bead+C footprint for FM

performance tuning

1800ohm

BEAD503

C519

[4]AU_HPL

[3]

1800ohm

BEAD504

C520

[4]AU_HPR

J502

VR502

C506

33PF

C505

100PF

C504

33PF

VR503

1

2

REC-NOG-93045-WQM2000000

J503

1

2

REC-NOG-93045-WQM2000000

[3]

Based on your system level design , if better ESD

performance is needed on your system, please

refer to ESD performance enhance proposal

10uF

close to IC

close to connector

NF

NF

C530

10uF

C529

HP_MP3L

33

R507

33

R508

HP_MP3R

33PF

C521

same power domain

[6]

HP_MIC

33PF

C522

VR505

VR504

VIO28_PMU

[3]

VR506

EINT_HP

R505

470K

47K

R506

1800ohm

BEAD501

1800ohm

BEAD502

1800ohm

BEAD505

12

VR501

470

470

R509

R510

100NH

R501

1

0

L502

R502

1

0

[6]HP_MIC-1

[6]HP_MP3L-1

[6]

EAR_DET

[6]HP_MP3R-1

[6]FM_ANT-1

2

2

[10]

[12]FM_ANT

[10]

[12]FM_RX_N_6572

[6] HP_MIC-1

[6]

FM_ANT-1

[6] HP_MP3R-1

HP_MP3L-1

[6]

[6] EAR_DET

J501

1

2

3

4

5

6

AUDIO-EAR-PH8-5B05F35A

Single via to GND plane

1K

Close to

Close to

BB

1.5K

1.5K

R517

VR508

MIC

Analog MIC

C508

100PF

33PF

33PF

C509

C510

VR509

R522

R523

0

0

AUDIO-MIC-OB-F15PD44-26-C10C33EP

CON502

1

2

Earphone MICPHONE

Close to BB Close to MIC

100nF

C523

[4] AU_VIN1_N

100nF

C524

[4] AU_VIN1_P

[4] ACCDET

AU_VIN1_N1

MICBIAS1

1K

GND of C(4.7uF) and headset

should tie together and single

R511

4.7uF

via to GND plane

C531

Close to EarJack

1K

GND

[6]HP_MIC

together then single

via to main GND

R512

C526

33PF

1.5K

100PF

C527

C525

33PF

R513

TITLE:

DOCUMENT NO.:

DEPARTMENT:

COMPANY:

DESIGNER:

<TITLE>

05_AUDIO

Hardware DEPT.

Last Saved Date:

<DESIGNER> SHEET:

2013-5-10

<REV>

REV:

SIZED:

A1

OF

6

17

Loading...

Loading...