WWW.AliSaler.Com

1

WWW.AliSaler.Com

2

3

4

5

6

7

8

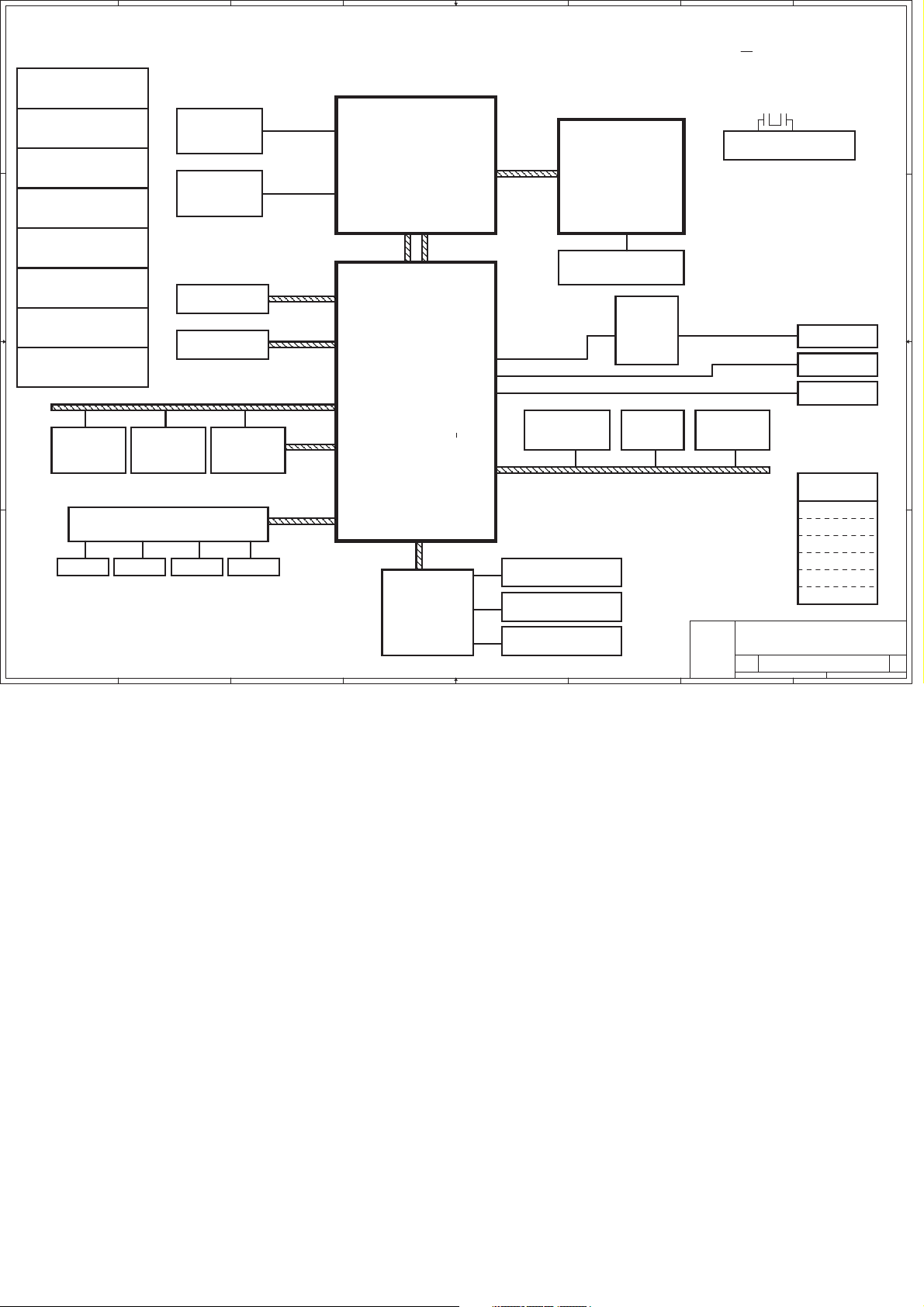

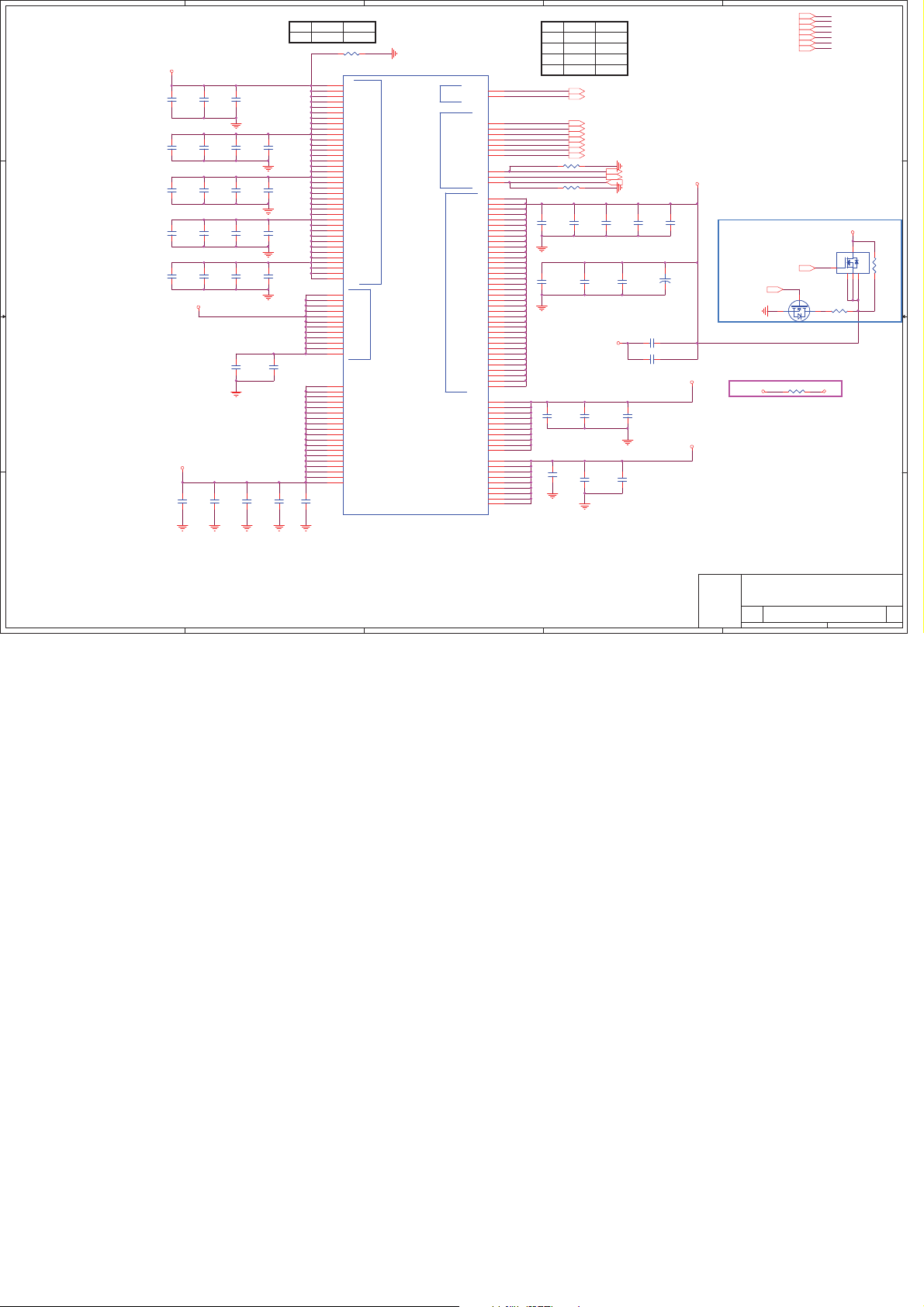

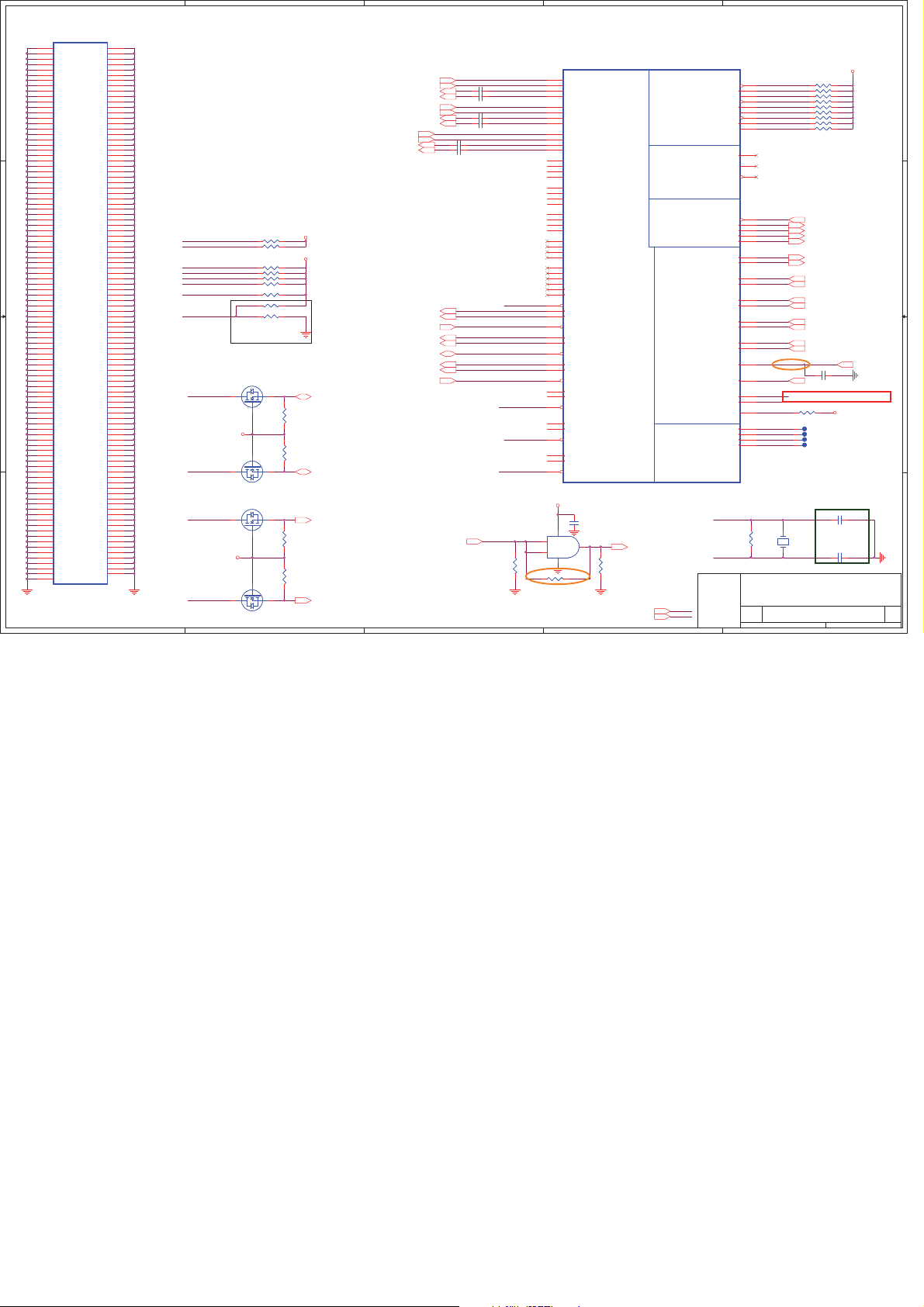

R18D INTEL UMA/DISCRETE SYSTEM DIAGRAM

+3V/+5V

A A

+1.05VTT

CPU Core

VGAC

+1.

B B

Charger

Discharger

UMA V

C C

D D

PG.34

PG.35

PG.36

ore/+1.1V

PG.37

5VSUS

PG.38

PG.39

P

G.40

GACORE

PG.41

d reader

Car

RTS

5219-GR

10/100

KB TP

1

/+1.8V

LAN3

PG.27

En

SOD

Max. 4GB

SOD

Max. 4GB

HDD

D

OD

3&,([

LAN

RTS

8165EH

PG.30 P

10/100

KBC

E KB3930QF D2

ROM FAN

2

IMM1

G.15

P

IMM2

PG.16

PG.26

PG.26

LAN1LAN2

WLAN

BT COMB

PG.32

DDR3

Channel A

DDR3

Channel B

SATA

SATA

O

G.33

LPC

USB 2.0

3

INTEL

Arrandale

34mm X 28mm

1288pin BGA

5W

TDP 3

PG.3~9

FDI

DMI

PCI-E x8

Nvidia

N12P-GV

PP;PP

7'3

PG.17~21

DDR3

900M

CLOCK GE

Hz

14.318MHz

N

PG.2

VRAM

64Mx16x4,64bit

0

1

INTEL PCH

Ibex Peak-m

DP Po

CRT

rt B

LVDS

27mm X 25mm

1071pin F

TDP 5W

CBGA

USB2.

X2

USB 2.

0

0 Ports

G.29

PORT0,1

PG.21

HDMI

Leve

l

Shifter

PG.24

Webcam

PG.23P

PORT4PORT10

S

oftbre

BT

e

G.29

P

PORT13

ze

HDMI

CRT

LVDS

PG.24

PG.25

G.23

P

Stackup

PG.10~14

TOP

GND

Azalia

AUDI

CODEC

T92H

ID

4

O

D80B1

PG.28

Speaker

IC

HP/M

Anal

og MIC

5

PG.28

PG.29

PG.28

352-(&75'

352-(&75'

352-(&75'

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

hursday, January 13, 2011

Date: Sheet

hursday, January 13, 2011

Date: Sheet

hursday, January 13, 2011

6

Date: Sheet

7

IN1

IN2

VCC

BOT

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

1A

1A

1A

of

of

of

142T

142T

142T

8

WWW.AliSaler.Com

1

WWW.AliSaler.Com

2

3

4

5

6

7

8

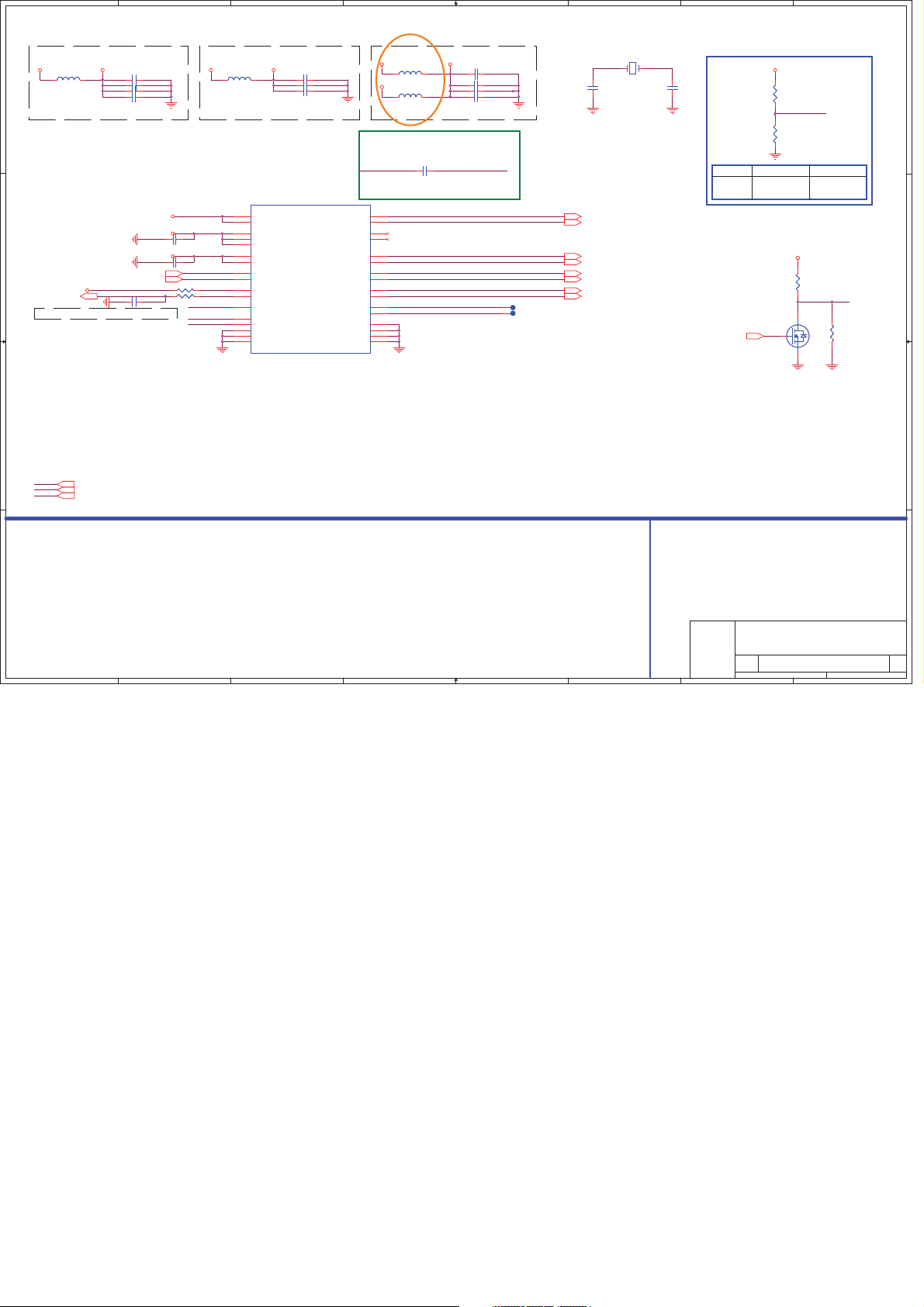

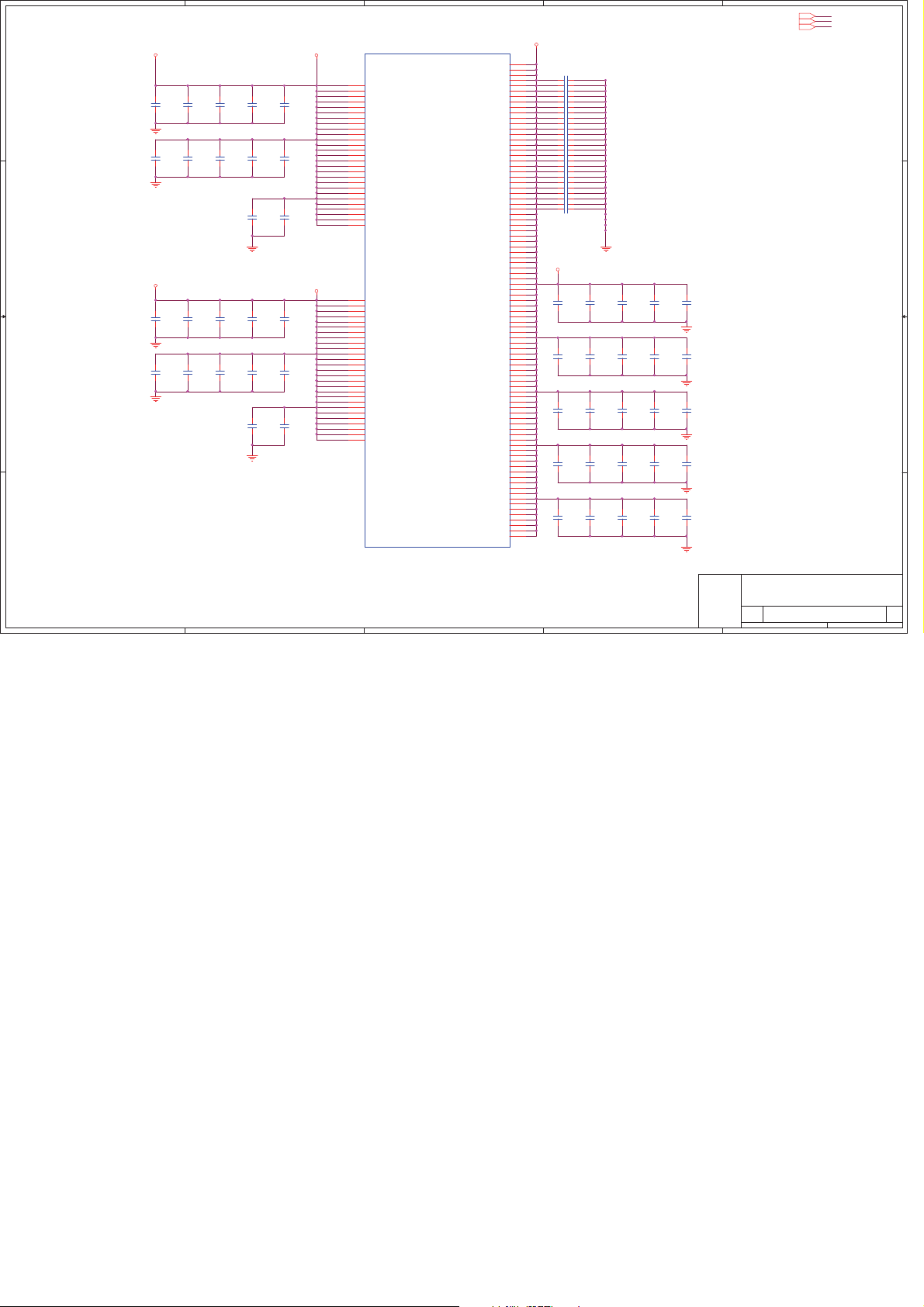

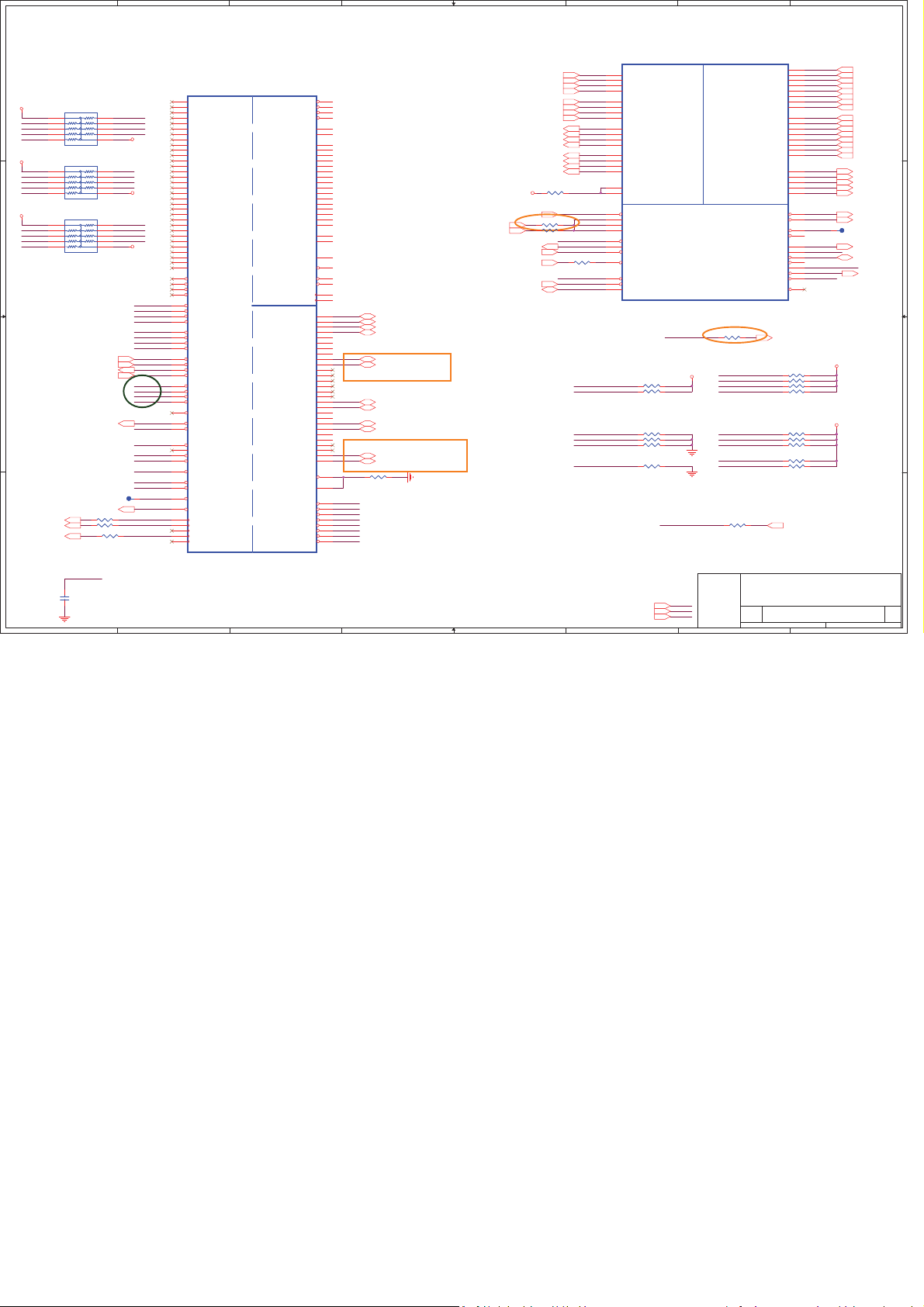

02

25mA 150mA

+1.0

A A

Place each 0.1uF cap close to pin

B B

C C

+VDDIO

-181T15/1.5A_6

-181T15/1.5A_6

+3V

_CLK

C742 0.

C742 0.

C723 0.1U/10V_4C723 0.1U/10V_4

C747 10U

C747 10U

C746

C746

+VDDCO

CLK_IC

H_14M

C708 *

C708 *

1U/10V_4

1U/10V_4

/6.3VS_6

/6.3VS_6

*10U/6.3V_8

*10U/6.3V_8

+VDDS

+VDDIO_CLK

CGDAT_SMB<11,15,16>

CGCLK

10P/50V_4

10P/50V_4

E_CLK

RE_CLK

C722 *

C722 *

C737 *

C737 *

_SMB<11,15,16>

R494 10K_4R494 10K_4

R478 33_4R478 33_4

5V

L56

L56

1 2

HCB1608KF

HCB1608KF

CLK_

ICH_14M<11>

Place R8044 within 0.5" of C/G

1 2

HCB1608KF

HCB1608KF

L57

L57

-181T15/1.5A_6

-181T15/1.5A_6

+VDDS

E_CLK

C704 4.

C704 4.

C731 0.1U/10V_4C731 0.1U/10V_4

C705 0.

C705 0.

7U/6.3V_6

7U/6.3V_6

1U/10V_4

1U/10V_4

+3V

Place each 0.1uF cap close to pin Place each 0.1uF cap close to pin

U29

U29

5

VDD_L

CD

29

VDD_REF

1

VDD_US

12

0.047U/10V_4

0.047U/10V_4

12

0.047U/10V_4

0.047U/10V_4

CK_PW

XTAL_OUT

XTAL_I

CPU_

SEL

RGD_R

N

Vender

ICS

RealtekRTM

Sil

B

17

VDD_S

RC

24

VDD_CPU

18

U_IO

VDD_CP

15

VDD_S

RC_IO

31

SDATA

890N-632

890N-632

RTM

RTM

32

SCLK

16

CPU_STOP#

30

/CPU_SEL

REF_0

25

CK_PWR

GD/PD#_3.3

27

XOUT

28

XIN

QFN32

9

2

8

ego

QFN32

VSS_SATA

VSS_USB

VSS_LCD

RT

RT

M890N-632

M890N-632

AL000890000

AL000890000

IC OTHER(32P) RTM890N-632-GRT(QFN)

IC OTHER(32P) RTM890N-632-GRT(QFN)

Part Part Number

ICS

9LVS3197 AL003197001

890N-632 AL000890000

SLG8LV

595VTR AL000595000

DOT

DOT9

27MHz

CPU-0

CPU-0#

CPU-1

CPU-1

96T_LPR

6C_LPR

SRC-1

SRC-1

SATA

SATA#

_nonSS

27MHz_SS

VSS_REF

VSS_CPU

VSS_SRC

+3V

1 2

*HCB1608KF-181T15/1.5A_6

*HCB1608KF-181T15/1.5A_6

V

+1.5

1 2

HCB1608KF

HCB1608KF

_BCLK_P

CLK_BUF

23

22

20

19

#

3

4

13

14

#

10

11

6

7

33

GND

26

21

12

Part Description

IC OTHER(3

IC OTHER(32P) RTM890N-632-GRT(QFN)

IC O

150mA

+VDDCO

-181T15/1.5A_6

-181T15/1.5A_6

C714 * 3.3P/50 V_4C71 4 *3.3P/ 50V_4

CLK_BUF

_BCLK_P

CLK_BUF

_BCLK_N

_PCIE_3GPLL

_PCIE_3GPLL#

_DREFSSCLK

_DREFSSCLK#

A_27M_NOSS

A_27M_SS

CLK_VG

RE_CLK

C733 4.

C733 4.

C729 0.1U/10V_4C729 0.1U/10V_4

C711 0.

C711 0.

C716 0.

C716 0.

_BCLK_N

CLK_BUF

L53

L53

L54

L54

0510 add for WiMAX

close to U13

CLK_BUF_DREFCLK

BUF_DREFCLK#

CLK_

CLK_BUF

CLK_BUF

CLK_BUF

CLK_BUF

CLK_VG

2P) ICS9LVS3197AKLFT(MLF)

THER(32P)SLG8LV595VTR(QFN)

7U/6.3V_6

7U/6.3V_6

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

Y6

Y6

_IN

XTAL

12

C702

C702

33P/

33P/

50V_4

50V_4

1 2

14.318MH

14.318MH

_OUT

XTAL

12

Z

Z

C703

C703

33

33

P/50V_4

P/50V_4

+3V

R474

R474

*10K_4

*10K_4

_SEL

CPU

R476

R476

10K_4

10K_4

01

CPU_SEL

CPU0/1=133MHz

(de

CLK_BUF

_BCLK_P <11>

_BCLK_N <11>

CLK_BUF

CLK_BUF_DREFCLK <11>

BUF_DREFCLK# <11>

CLK_

CLK_BUF_PCIE_3GPLL < 11>

CLK_BUF

_PCIE_3GPLL# <11>

CLK_BUF

_DREFSSCLK <11>

_DREFSSCLK# <11>

T47T47

T46T46

CLK_BUF

VR_P

WRGD_CLKEN#<35>

fault)

CPU0/1=100MHz

+3V

R493

R493

1K_4

1K_4

RGD_R

CK_PW

3

Q39

Q39

2N7002E

2N7002E

R495

2

R495

100K_4

100K_4

1

<10,11,12,14,41>

+1.05V

+1.5V

<6,32>

3,10,11,12,13,14,15,16,17,19,22,23,24,25,26,27,29,30,31,32,35,36,38>

+3V <

D D

352-(&75'

352-(&75'

352-(&75'

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

Size Docume n t Number Rev

Size Docume n t Number Rev

Size Document Number Rev

Custom

Custom

Custom

Clock G

Clock G

Clock G

en(9LRS3197)

en(9LRS3197)

en(9LRS3197)

uesday, February 15, 2011

Date: Sheet

uesday, February 15, 2011

Date: Sheet

uesday, February 15, 2011

1

2

3

4

5

6

Date: Sheet

7

1A

1A

1A

of

of

of

242T

242T

242T

8

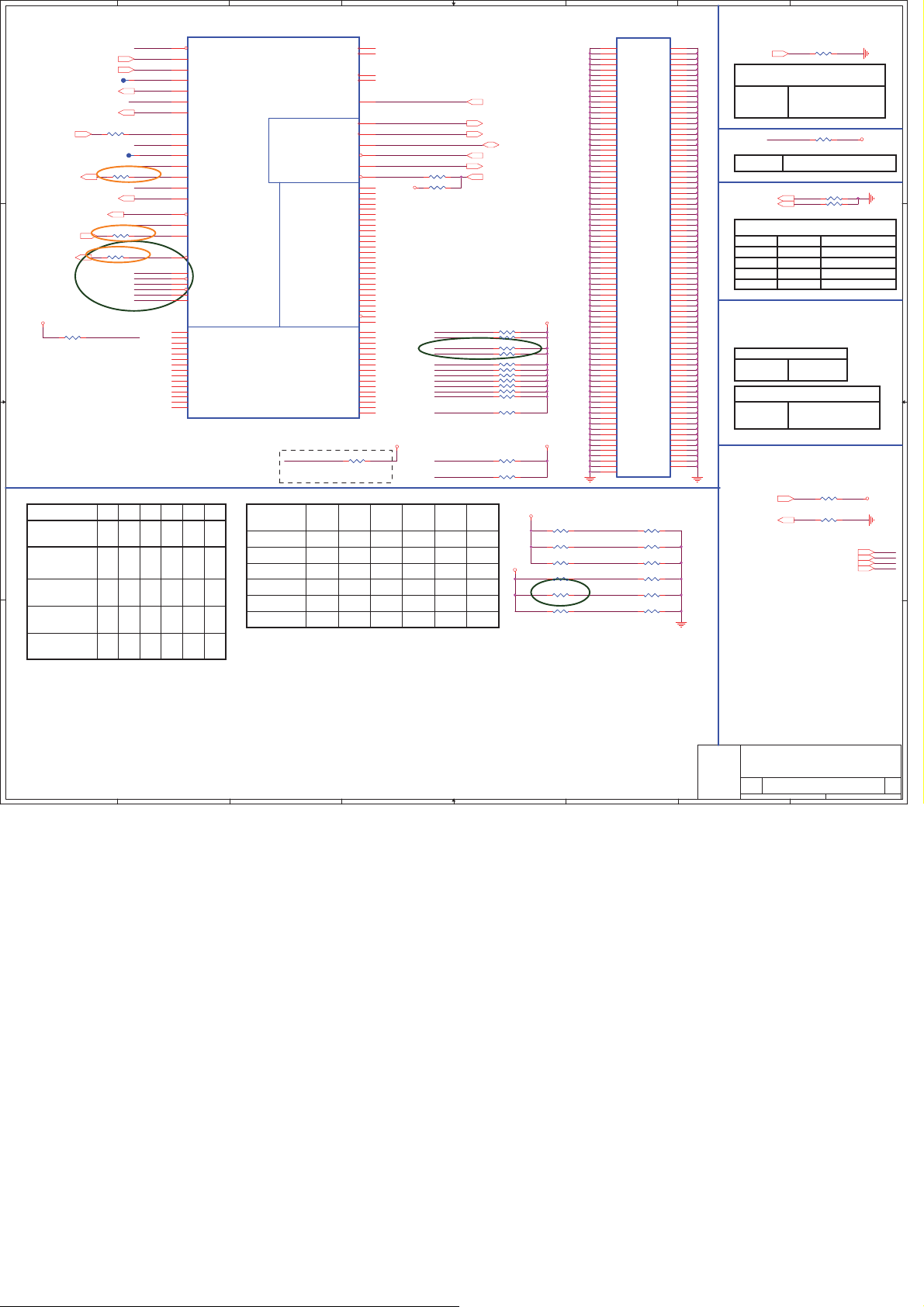

WWW.AliSaler.Com

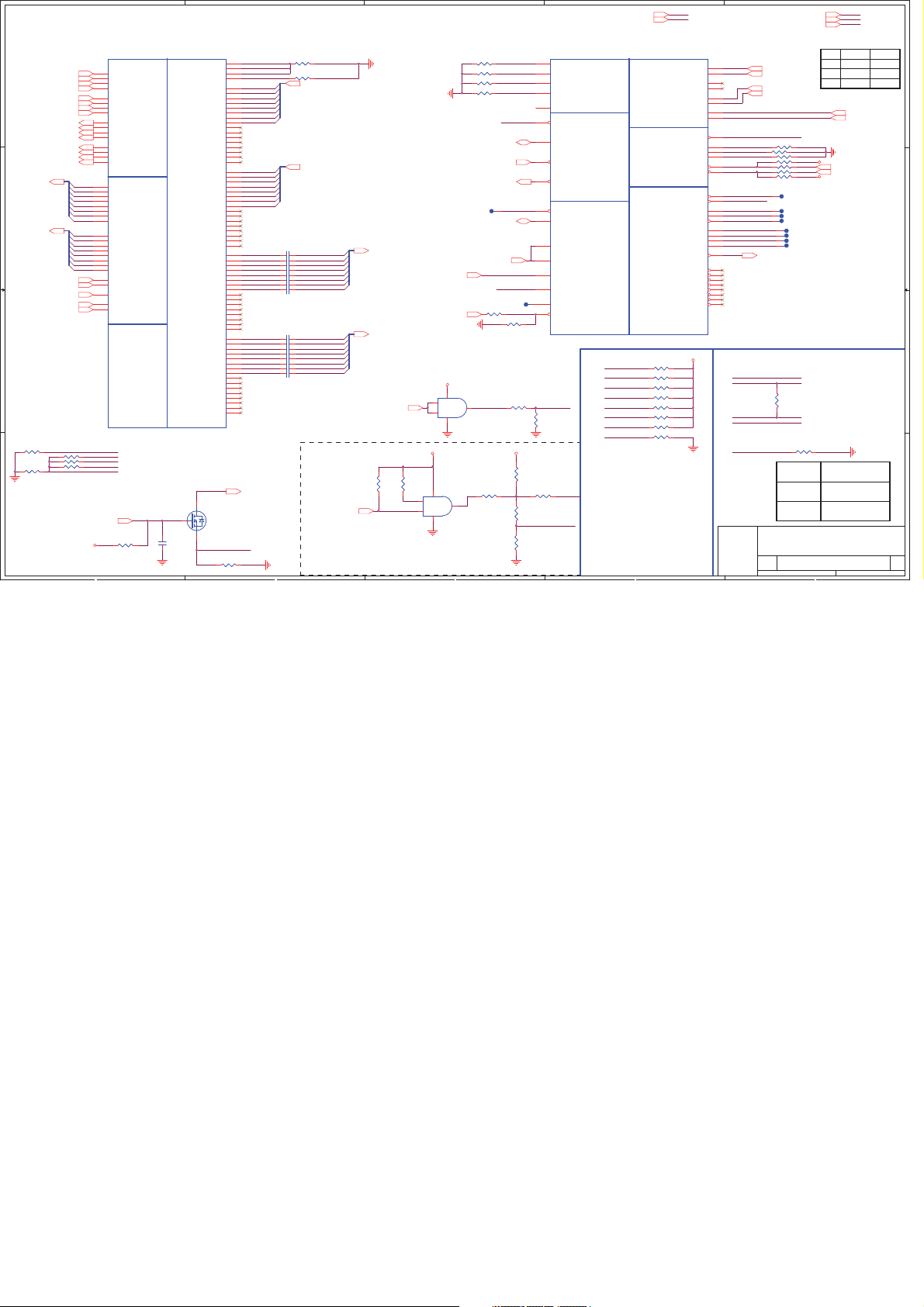

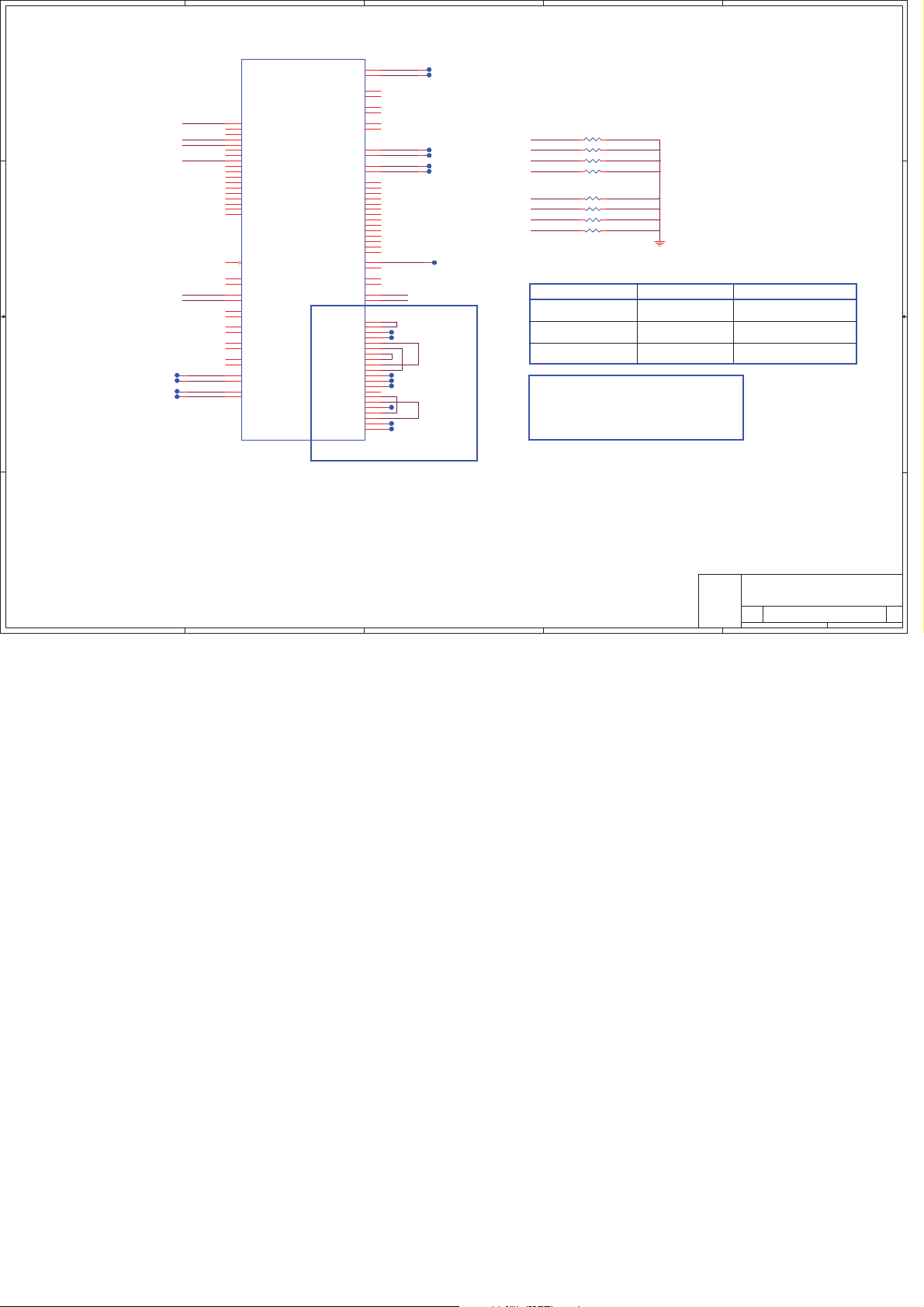

5

WWW.AliSaler.Com

U3018A

U3018A

F7

DMI_

TXN0<12>

DMI_RX#[

0]

D D

2.7GT/s data rate

FDI

_TXN[7:0]<12>

C C

TXP[7:0]<12>

FDI_

FDI_

FDI_

FDI

FDI

B B

Discrete O

R3361 *1K/F_4R3361 *1K/F_4

R3355 *

R3355 *

R3350 *

R3350 *

R3356 *

R3356 *

1K/F_4

1K/F_4

R3351 *

R3351 *

FDI_FSYNC can

gang all these

4 signals

A A

together and

tie them with

only one 1K

resistor to GND

( Check list

1.0 ).

J8

TXN1<12>

DMI_

DMI_

DMI_

_TXP0<12>

DMI

_TXP1<12>

DMI

DMI

_TXP2<12>

DMI

_TXP3<12>

DMI_

DMI_

DMI_

DMI_

DMI_

DMI_

DMI_

DMI_

FSYNC0<12>

FSYNC1<12>

FDI_

_LSYNC0<12>

_LSYNC1<12>

nly

DMI_RX#[

1]

K8

TXN2<12>

TXN3<12>

RXN0<12>

RXN1<12>

RXN2<12>

RXN3<12>

RXP0<12>

RXP1<12>

RXP2<12>

RXP3<12>

FDI_

FDI_

FDI_

FDI_

FDI_

FDI_

FDI_

FDI_

FDI_

FDI_

FDI_

FDI_TXP3

FDI_

FDI_

FDI_

FDI_

INT<12>

0_4

0_4

0_4

0_4

0_4

0_4

2]

DMI_RX#[

J4

3]

DMI_RX#[

F9

DMI_RX[

0]

J6

DMI_RX[

K9

DMI_RX[

J2

DMI_RX[

H17

DMI_TX#[0]

K15

DMI_TX

J13

DMI_TX

F10

DMI_TX

G17

DMI_TX

M15

DMI_TX

G13

DMI_TX

J11

DMI_TX[3]

TXN0

L2

FDI_T

TXN1

N7

FDI_T

TXN2

M4

FDI_T

TXN3

P1

FDI_T

TXN4

N10

FDI_T

TXN5

R7

FDI_T

TXN6

U7

FDI_T

TXN7

W8

FDI_T

TXP0

K1

FDI_

TXP1

N5

FDI_

TXP2

N2

FDI_TX[2]

R2

FDI_

TXP4

N9

FDI_

TXP5

R8

FDI_

TXP6

U6

FDI_TX[6]

TXP7

W10

FDI_

AC7

FDI_

AC9

FDI_FSYNC[1]

5

AB

FDI_INT

AA1

FDI_LSYNC[0]

AB2

FDI_LS

IC

IC

,ARD_BGA,R1P0

,ARD_BGA,R1P0

FDI_INT

FDI_

FSYNC0

FDI_

FSYNC1

LSYNC0

FDI_

LSYNC1

FDI_

#[1]

#[2]

#[3]

[0]

[1]

[2]

X#[0]

X#[1]

X#[2]

X#[3]

X#[4]

X#[5]

X#[6]

X#[7]

TX[0]

TX[1]

TX[3]

TX[4]

TX[5]

TX[7]

FSYNC[0]

YNC[1]

1]

2]

3]

DMI Intel(R) FDI

DMI Intel(R) FDI

For S3 leakage issue

PCI

PCI

E_CLK_REQ7#<13>

+3VS5

E_CLK_REQ7#

R346910K/

R346910K/

F_4

F_4

1 2

5

COMPI

PEG_I

COMPO

PEG_I

PEG_R

COMPO

PEG_R

BIAS

X#[0]

PEG_R

PEG_R

X#[1]

PEG_R

X#[2]

X#[3]

PEG_R

X#[4]

PEG_R

PEG_R

X#[5]

PEG_R

X#[6]

PEG_RX#[7]

X#[8]

PEG_R

PEG_R

X#[9]

PEG

_RX#[10]

PEG_RX#[11]

_RX#[12]

PEG

_RX#[13]

PEG

PEG

_RX#[14]

PEG_RX#[15]

_RX[0]

PEG

PEG

_RX[1]

PEG_RX[2]

_RX[3]

PEG

_RX[4]

PEG

PEG

_RX[5]

PEG

_RX[6]

_RX[7]

PEG

_RX[8]

PEG

PEG

_RX[9]

PEG

_RX[10]

_RX[11]

PEG

_RX[12]

PEG

PEG

_RX[13]

PEG

_RX[14]

PEG_RX[15]

PEG_T

X#[0]

PEG_T

X#[1]

PEG_TX#[2]

X#[3]

PEG_T

PEG_T

X#[4]

PEG_T

X#[5]

PEG_TX#[6]

X#[7]

PEG_T

X#[8]

PEG_T

PEG_T

X#[9]

PEG_TX#[10]

X#[11]

PEG_T

X#[12]

PEG_T

PEG_T

X#[13]

PEG_T

X#[14]

X#[15]

PEG_T

PEG

_TX[0]

PEG

_TX[1]

_TX[2]

PEG

_TX[3]

PEG

PEG

_TX[4]

PEG

_TX[5]

PEG_TX[6]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

_TX[7]

PEG

PEG

_TX[8]

PEG

_TX[9]

PEG_TX[10]

X[11]

PEG_T

PEG_T

X[12]

PEG_T

X[13]

PEG_TX[14]

X[15]

PEG_T

3

Q3006

Q3006

DMN60

DMN60

1K-7

1K-7

2

1

7

7

C303

C303

DDR3_DRAMRST#_C

0.047U 10V_4

0.047U 10V_4

R304

R304

7 100K/F_4

7 100K/F_4

B12

A13

D12

B11

G40

G38

H34

P34

G28

H25

H24

D29

B26

D26

B23

D22

A20

D19

A17

B14

F40

J38

G34

M34

J28

G25

K24

B28

A27

B25

A24

B21

B19

B18

B16

D15

N40

L38

M32

D40

A38

G32

B33

B35

L30

A31

B32

L28

N26

M24

G21

J20

L40

N38

N32

B39

B37

H32

A34

D36

J30

B30

D33

N28

M25

N24

F21

L20

PEG_C

PEG_R

PEG_R

PEG_RX#1

PEG_R

PEG_R

PEG_R

PEG_R

PEG_R

PEG_R

PEG_R

PEG_R

PEG_R

PEG_R

PEG_R

PEG_R

PEG_R

PEG_R

C_PEG

C_PEG

C_PEG

C_PEG

C_PEG_TX#4

C_PEG

C_PEG

C_PEG

C_PEG

C_PEG

C_PEG

C_PEG

C_PEG

C_PEG

C_PEG

C_PEG_TX7

DDR3_DRA

OMP

BIAS

X#0

X#2

X#3

X#4

X#5

X#6

X#7

X0

X1

X2

X3

X4

X5

X6

X7

_TX#0

C3751 0.

C3751 0.

C3744 0.

C3744 0.

_TX#1

C3740 0.

C3740 0.

_TX#2

C3733 0.1U/10V_4C3733 0.1U/10V_4

_TX#3

C3728 0.1U/10V_4C3728 0.1U/10V_4

C3724 0.

C3724 0.

_TX#5

C3722 0.

C3722 0.

_TX#6

_TX#7

C3717 0.

C3717 0.

C3747 0.

C3747 0.

_TX0

C3741 0.1U/10V_4C3741 0.1U/10V_4

_TX1

_TX2

C3735 0.

C3735 0.

C3729 0.

C3729 0.

_TX3

C3725 0.

C3725 0.

_TX4

_TX5

C3723 0.

C3723 0.

C3718 0.

C3718 0.

_TX6

C3715 0.1U/10V_4C3715 0.1U/10V_4

MRST# <15,16>

4

R3062 49.9/F_4R3062 49.9/F_4

F_4

F_4

R3060 750/

R3060 750/

PEG_R

X#[0..7] <17>

PEG_RX[0..7] <17>

PEG_T

PEG_T

20,31,33,34,37,40,41>

X#[0..7] <17>

X[0..7] <17>

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

1U/10V_4

PEG_T

PEG_T

PEG_T

PEG_T

PEG_TX#4

PEG_T

PEG_T

PEG_T

PEG_T

PEG_T

PEG_T

PEG_T

PEG_T

PEG_T

PEG_T

PEG_TX7

X#0

X#1

X#2

X#3

X#5

X#6

X#7

X0

X1

X2

X3

X4

X5

X6

For S3 leakage issue

R320

R320

*10K/F_4

*10K/F_4

1.1<34>

STAT_

Use a voltage divider with VDDQ (1.5 V) rail

ON in S3) and resistor combination of 1.5K ±1%

(to VDDQ)/750±1% (to GND) to convert to

processor VTT level.

4

3

R3152 20/F_4R3152 20/F_4

H_COM

R3151 20/

R3151 20/

F_4

F_4

H_COMP2

9/F_4

9/F_4

H_COM

R3150 49.

R3150 49.

H_COMP0

R3149 49.9/F_4R3149 49.9/F_4

H_CAT

I<13>

H_PEC

H_PRO

CHOT#<31,35>

PM_

THRMTRIP#<13,31>

T3055T3055

H_CPURS

PM_SY

NC<12>

H_P

WRGOOD<13>

PLTR

3 5

ST#<11,17,26,29,31,32>

U3010

U3010

MC

MC

4

3

R3212 *

R3212 *

PM_DRAM_PWRGD

R3140 1.5K/F_4R3140 1.5K/F_4

R3144 750/F

R3144 750/F

74VHC1G08DFT2G

74VHC1G08DFT2G

HWPG

_1

4

H_V

0_4

0_4

TTPWRGD

T3057T305

CPU_P

R318

R318

2K/F_4

2K/F_4

+1.5

VSUS

PM_DRAM_PWRGD<12>

+3V

2

HWPG<

1

+3VS5

6

6

5

R3215

R321

.25K/F_4

*8.25K/F_4

*8

2

1

3 5

U3012

U3012

*MC74VHC1G08DFT2G

*MC74VHC1G08DFT2G

P3

AD71

AC70

P1

AD69

AE66

M71

ERR#

N61

N19

N67

N17

T#

N70

M17

AM7

Y67

AM5

H15

7

Y70

LTRST#

G3

_4

_4

7

7

H_VT

H_VT

TPWRGDH_VTTPWRGD

TPWRGDH_VTTPWRGD

R3180

R3180

F_4

F_4

1K/

1K/

8

R3178

R317

4

*0_4

*0_

R3213 *

R3213 *

R3211

R3211

/F_4

/F_4

1.5K

1.5K

PM_DRAM_PWRGD

R314

R314

7

7

750/F_4

750/F_4

11,12,13,14,17,28,33,34,36,38,40>

U3018B

U3018B

3

COMP

COMP

2

1

COMP

COMP

0

_DETECT

PROC

CATERR#

PECI

PROCHOT#

THERMTRIP#

OBS#

RESET_

PM_SYN

C

VCCPWRGOOD_1

VCC

PWRGOOD_0

SM_DRA

MPWROK

PWRGOOD

VTT

TAPPWRGOOD

N#

RSTI

IC

IC

,ARD_BGA,R1P0

,ARD_BGA,R1P0

_1

0_4/S

0_4/S

HWPG

2

+3VS5<10,

+1.5V_CPU<5,6>

Misc

Misc

Thermal Power Management

Thermal Power Management

DDR3

DDR3

R3155 51/J

R3155 51/J

XDP_T

DO_R

ERR#

H_CAT

R3142 49.9/

R3142 49.9/

H_PRO

R3138 68_4R3138 68_4

CHOT#

LTRST#

CPU_P

R3135 *68/

R3135 *68/

R3146 *51/

R3146 *51/

XDP_T

MS

R3162 *51/

R3162 *51/

DI_R

XDP_T

XDP_PR

R3153 *51/

R3153 *51/

EQ#

CLK

XDP_T

R3145 *51/

R3145 *51/

2

BCLK#

BCLK_

BCLK_

PEG_C

_CLK#

PEG

DPLL_R

EF_SSCLK

DPLL

_REF_SSCLK#

Clocks

Clocks

SM_D

RAMRST#

SM_RCO

SM_RCO

SM_RCO

XT_TS#[0]

PM_E

XT_TS#[1]

PM_E

Misc

Misc

PRDY#

PREQ#

TRST#

TDI_

TDO_M

DBR#

BPM

BPM

BPM

BPM#[3]

BPM

BPM

BPM

BPM#[7]

JTAG & MBP

JTAG & MBP

+1.05V_VTT

_4

_4

F_4

F_4

J_4

J_4

J_4

J_4

J_4

J_4

J_4

J_4

J_4

J_4

1

+1.05

V_VTT<5,6,13,14,31,34,35,36,40>

+1.5VSUS<6,15,16,36,37,38>

+3V<2,10,11,12,13,14,15,16,17,19,22,23,24,25,26,27,29,30,31,32,35,36,38>

03

A

DIS UM

NA

Rc

F_4

F_4

F_4

F_4

/F_4

/F_4

0_4/S

0_4/S

/F_4

/F_4

T3052T3052

T3028T3028

7

T3027T302

T3030T3030

T3031T3031

11/6

T3029T3029

must

T3054T3054

T3056T3056

test point.

G MAPPING

6

6

R317

R317

*0_4/S

*0_4/S

R3161 51/J_4R3161 51/J_4

Scan Chain

(Default)

Ra

Rb

Rc 0 oh

+1.05

+1.05

add

7

AK

BCLK

AK

8

K71

ITP

J70

ITP#

L21

LK

J21

Y2

W4

BJ12

SM_RCOMP_0

BV33

MP[0]

SM_RCOMP_1

BP39

MP[1]

SM_

BV40

MP[2]

PM_EXT

AV66

PM_EXT

AV64

U7

1

U6

9

T67

TCK

N65

TMS

P6

9

T69

TDI

T71

TDO

P71

M

T70

W71

J69

#[0]

J67

#[1]

J62

#[2]

K65

K62

#[4]

J64

#[5]

K69

#[6]

M69

DREFS

DREFS

RCOMP_2

_TS#0

_TS#1

XDP_PR

XDP_PR

XDP_T

XDP_T

XDP_T

XDP_T

XDP_T

XDP_T

XDP_T

XDP_T

XDP_T

XDP_T

XDP_T

XDP_TRST#

CPU_BCLK <13>

CLK_

CLK_CPU_BCLK# <13>

CLK_

PCIE_3GPLL <11>

CLK_PCIE_3GPLL# <11>

SCLK

SCLK#

Rb

MRST#_C

DDR3_DRA

R3393 100/

R3393 100/

R3401 24.9/F_4R3401 24.9/F_4

R3403 130/

R3403 130/

R3181 10K

R3181 10K

R3177 *

R3177 *

R3175 *0_4/SR3175 *0_4/S

R3188 10K

R3188 10K

DY#

EQ#

CLK

MS

RST#

DI_R

DO_R

DI_M

DO_M

XDP_DBRESET# <12>

JTA

DI_R

DO_M

DI_M

DO_R

Ra

Ra

Rb

Rc

Rd

Re

CPU Only

GMCH Only

352-(&75'

352-(&75'

352-(&75'

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

e Document Number Rev

Siz

Size D ocument N umber R ev

Size D ocument N umber R ev

Custo

Custo

Custo

m

m

m

ESSER 1/7(HOST&PEX)

ESSER 1/7(HOST&PEX)

ESSER 1/7(HOST&PEX)

PROC

PROC

PROC

Date: Sheet

Date: Sheet

Date: Sheet

1

0 ohm

m NA

DREF

SSCLK <11>

SSCLK# <11>

DREF

V_VTT

PM_EXTTS#0 <15,16>

TS#1 <16>

PM_EXT

V_VTT

STUFF -> Ra, Rc, Re

NO STUFF -> Rb, Rd

STUFF -> Ra, Rb

NO ST

UFF -> Rc, Rd, Re

STUFF -> Rd, Re

NO ST

UFF -> Ra, Rb, Rc

3

3

3

of

of

of

0 ohm

NA

42Tuesday, Febru a ry 15, 2011

42Tuesday, Febru a ry 15, 2011

42Tuesday, Febru a ry 15, 2011

1A

1A

1A

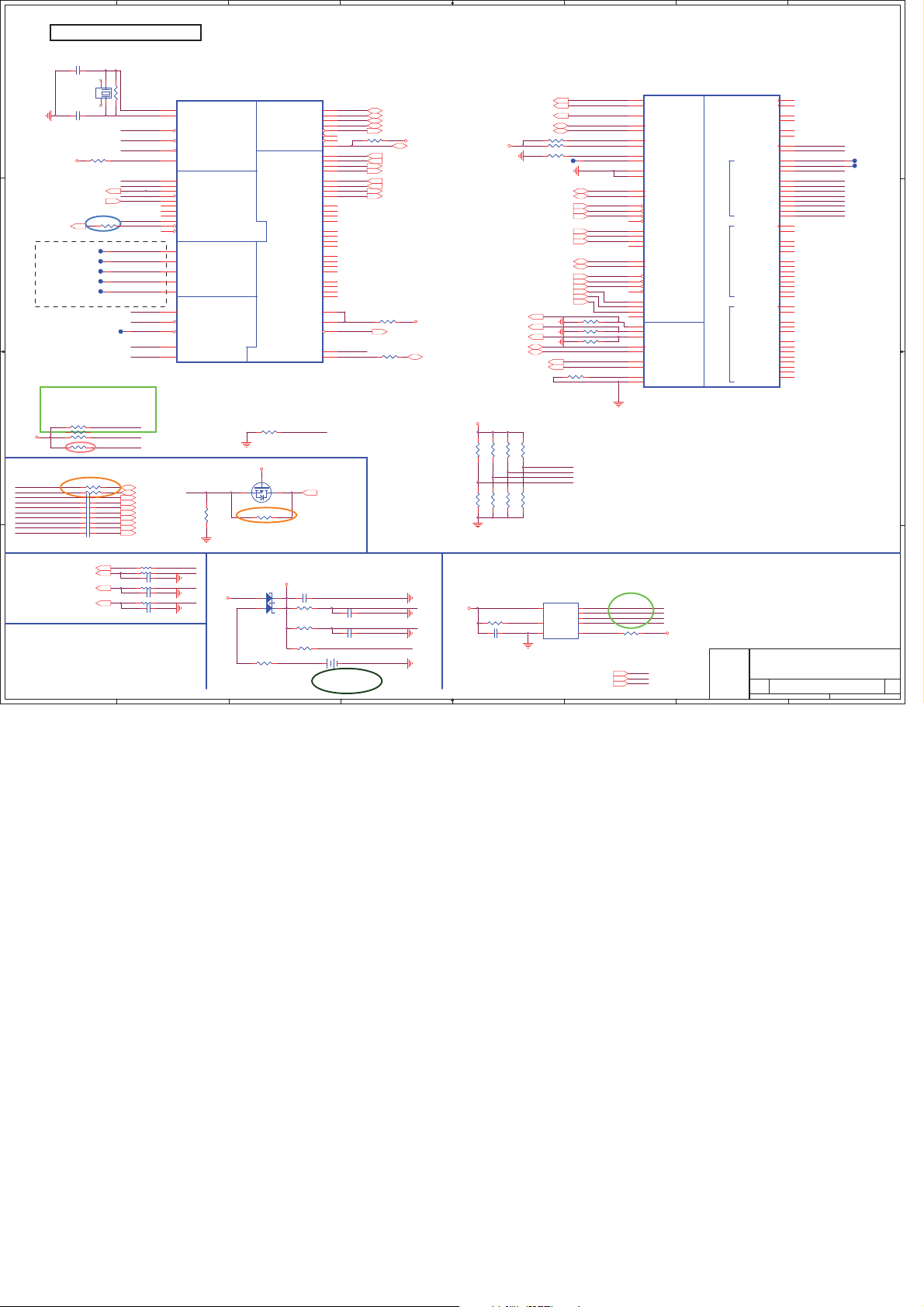

WWW.AliSaler.Com

5

WWW.AliSaler.Com

4

3

2

1

ARRANDALE/CLARKSFIELD PROCESSOR (DDR3)

U3018D

U3018C

U3018C

34

BM

SA_CK[0]

D D

C C

B B

M_A_DQ[63:0]<15>

M_A_DQ0

AT8

SA_DQ[

BM43

BM53

BF11

BE11

BH13

BN11

BG17

BK15

BG15

BH17

BK17

BN20

BN17

BK25

BH25

BJ20

BH21

BG24

BG25

BJ40

BF47

BF48

BN40

BH43

BN44

BN47

BN48

BN51

BH53

BJ55

BH48

BJ48

BN55

BF55

BN57

BN65

BJ61

BF57

BJ57

BK64

BK61

BJ63

BF64

BB64

BB66

BJ66

BF65

AY64

BC70

BT38

BH38

BF21

BK43

BL38

BF38

0]

AT6

SA_DQ[

1]

BB5

2]

SA_DQ[

BB9

SA_DQ[3]

AV7

SA_DQ[4]

AV6

SA_DQ[

5]

BE6

SA_DQ[

6]

BE8

7]

SA_DQ[

8]

SA_DQ[

SA_DQ[9]

BK5

SA_DQ[

10]

SA_DQ[

11]

BF9

SA_DQ[

12]

BF6

13]

SA_DQ[

BK7

SA_DQ[14]

BN8

SA_DQ[

15]

16]

SA_DQ[

BN9

SA_DQ[

17]

18]

SA_DQ[

SA_DQ[19]

BK9

SA_DQ[

20]

21]

SA_DQ[

SA_DQ[

22]

23]

SA_DQ[

24]

SA_DQ[

25]

SA_DQ[

26]

SA_DQ[

SA_DQ[

27]

28]

SA_DQ[

SA_DQ[

29]

30]

SA_DQ[

31]

SA_DQ[

SA_DQ[

32]

SA_DQ[33]

SA_DQ[

34]

35]

SA_DQ[

36]

SA_DQ[

37]

SA_DQ[

SA_DQ[38]

SA_DQ[

39]

40]

SA_DQ[

SA_DQ[

41]

42]

SA_DQ[

SA_DQ[43]

SA_DQ[

44]

45]

SA_DQ[

SA_DQ[

46]

47]

SA_DQ[

SA_DQ[48]

SA_DQ[

49]

SA_DQ[

50]

DDR SYSTEM MEMORY A

SA_DQ[

SA_DQ[

SA_DQ[53]

SA_DQ[54]

SA_DQ[

SA_DQ[

SA_DQ[

SA_DQ[

SA_DQ[

SA_DQ[

SA_DQ[

SA_DQ[

SA_DQ[

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

DDR SYSTEM MEMORY A

51]

52]

55]

56]

57]

58]

59]

60]

61]

62]

63]

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_BS#0<15>

M_A_BS#1<15>

M_A_BS#2<15>

M_A_CAS#< 15>

M_A_RAS#< 15>

M_A_WE#<15>

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[

SA_DM[

SA_DM[

SA_DM[

SA_DM[

SA_DM[

SA_DM[

SA_DM[

SA_DM[

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[

SA_DQS[

SA_DQS[2]

SA_DQS[

SA_DQS[

SA_DQS[

SA_DQS[

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

BP35

BF

20

BK36

BH36

BK24

BH40

BJ

47

BF43

BL47

1]

M_A_DM0

BB10

0]

M_A_DM1

BJ10

1]

M_A_DM2

BM15

2]

M_A_DM3

BN24

3]

M_A_DM4

BG44

4]

M_A_DM5

BG53

5]

M_A_DM6

BN62

6]

M_A_DM7

BH59

7]

M_A_DQS#0

AY5

M_A_DQS#1

7

BJ

M_A_DQS#2

13

BN

M_A_DQS#3

BL21

M_A_DQS#4

BH44

M_A_DQS#5

BK51

M_A_DQS#6

BP58

M_A_DQS#7

BE62

M_A_DQS0

AY7

0]

M_A_DQS1

BJ5

1]

M_A_DQS2

BL13

M_A_DQS3

BN21

3]

M_A_DQS4

BK44

4]

M_A_DQS5

BH51

5]

M_A_DQS6

BM60

6]

M_A_DQS7

BE64

M_A_A0

36

BT

M_A_A1

BP33

M_A_A2

BV36

M_A_A3

BG34

M_A_A4

BG32

M_A_A5

32

BN

M_A_A6

BK32

M_A_A7

BJ

30

M_A_A8

30

BN

M_A_A9

BF

28

M_A_A10

BH

34

M_A_A11

30

BH

M_A_A12

BJ

28

M_A_A13

40

BF

M_A_A14

BN28

M_A_A15

BN

25

M_A_CLK0 <15>

M_A_CLK0# <15>

M_A_CKE0 <15>

M_A_CLK1 <15>

M_A_CLK1# <15>

M_A_CKE1 <15>

M_A_CS#0 <15>

M_A_CS#1 <15>

M_A_ODT0 <15>

M_A_ODT1 <15>

M_A_DM[7:0] <15>

M_A_DQS#[7:0] <15>

M_A_DQS[7:0] <15>

M_A_A[15:0] <15>

M_B_DQ[63:0]<16>

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_BS#0<16>

M_B_BS#1<16>

M_B_BS#2<16>

M_B_CAS#<16>

M_B_RAS#<16>

M_B_WE#<16>

U3018D

33

BU

SB_CK[0]

BV34

SB_CK#[0]

BA2

SB_DQ[0]

AW

2

SB_DQ[1]

BD

1

SB_DQ[2]

BE4

SB_DQ[3]

AY1

SB_DQ[4]

BC2

SB_DQ[5]

BF

2

SB_DQ[6]

BH

2

SB_DQ[7]

BG4

SB_DQ[8]

BG1

SB_DQ[9]

BR6

SB_DQ[10]

BR

8

SB_DQ[11]

BJ

4

SB_DQ[12]

BK2

SB_DQ[13]

9

BU

SB_DQ[14]

BV10

SB_DQ[15]

BR

10

SB_DQ[16]

12

BT

SB_DQ[17]

BT

15

SB_DQ[18]

BV15

SB_DQ[19]

BV12

SB_DQ[20]

BP12

SB_DQ[21]

BV17

SB_DQ[22]

BU

16

SB_DQ[23]

BP15

SB_DQ[24]

19

BU

SB_DQ[25]

BV22

SB_DQ[26]

22

BT

SB_DQ[27]

BP19

SB_DQ[28]

BV19

SB_DQ[29]

BV20

SB_DQ[30]

20

BT

SB_DQ[31]

48

BT

SB_DQ[32]

BV48

SB_DQ[33]

BV50

SB_DQ[34]

BP49

SB_DQ[35]

47

BT

SB_DQ[36]

BV52

SB_DQ[37]

BV54

SB_DQ[38]

BT54

SB_DQ[39]

BP53

SB_DQ[40]

53

BU

SB_DQ[41]

BT

59

SB_DQ[42]

57

BT

SB_DQ[43]

BP56

SB_DQ[44]

BT

55

SB_DQ[45]

60

BU

SB_DQ[46]

BV59

SB_DQ[47]

BV61

SB_DQ[48]

BP60

SB_DQ[49]

BR

66

SB_DQ[50]

BR

64

SB_DQ[51]

BR

62

SB_DQ[52]

61

BT

SB_DQ[53]

BN68

SB_DQ[54]

BL69

SB_DQ[55]

BJ

71

SB_DQ[56]

BF

70

SB_DQ[57]

BG71

SB_DQ[58]

67

BC

SB_DQ[59]

BK70

SB_DQ[60]

BK67

SB_DQ[61]

BD

71

SB_DQ[62]

BD

69

SB_DQ[63]

BV43

SB_BS[0]

BV41

SB_BS[1]

BV24

SB_BS[2]

BU46

SB_CAS#

BT40

SB_RAS#

BT41

SB_WE#

DDR SYSTEM MEMORY - B

DDR SYSTEM MEMORY - B

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[

SB_DM[

SB_DM[

SB_DM[

SB_DM[

SB_DM[

SB_DM[

SB_DM[

SB_DM[

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

BT

26

BV38

BU39

BT24

BP46

BT

43

BV45

BU49

1]

M_B_DM0

BB4

0]

M_B_DM1

BL4

1]

M_B_DM2

BT13

2]

M_B_DM3

BP22

3]

M_B_DM4

BV47

4]

M_B_DM5

BV57

5]

M_B_DM6

BU65

6]

M_B_DM7

BF67

7]

M_B_DQS#0

BE2

M_B_DQS#1

BM

3

M_B_DQS#2

12

BU

M_B_DQS#3

19

BT

M_B_DQS#4

52

BT

M_B_DQS#5

BV55

M_B_DQS#6

BU

63

M_B_DQS#7

BG69

M_B_DQS0

4

BD

M_B_DQS1

BN4

M_B_DQS2

BV13

M_B_DQS3

BT

17

M_B_DQS4

BT

50

M_B_DQS5

56

BU

M_B_DQS6

BV62

M_B_DQS7

BJ69

M_B_A0

BT

34

M_B_A1

BP30

M_B_A2

BV29

M_B_A3

BU

30

M_B_A4

BV31

M_B_A5

BT

33

M_B_A6

BT

31

M_B_A7

BP26

M_B_A8

BV27

M_B_A9

27

BT

M_B_A10

BU42

M_B_A11

BU

26

M_B_A12

29

BT

M_B_A13

45

BT

M_B_A14

BV26

M_B_A15

BU23

M_B_CLK0 <16>

M_B_CLK0# <16>

M_B_CKE0 <16>

M_B_CLK1 <16>

M_B_CLK1# <16>

M_B_CKE1 <16>

M_B_CS#0 <16>

M_B_CS#1 <16>

M_B_ODT0 <16>

M_B_ODT1 <16>

M_B_DM[7:0] <16>

DM signals are not present on Clarkfield

processor. All DM signal can br left as

NC on Clarkfield and connect directly to

GND on So-DIMM side for Clarkfield

design only

M_B_DQS#[7:0] <16>

M_B_DQS[7:0] <16>

M_B_A[15:0] <16>

04

IC,ARD_BGA,R1P0

A A

5

IC,ARD_BGA,R1P0

IC,ARD_BGA,R1P0

IC,ARD_BGA,R1P0

4

3

2

352-(&75'

352-(&75'

352-(&75'

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

PROCESSER 2/7(DDR3)

PROCESSER 2/7(DDR3)

PROCESSER 2/7(DDR3)

Date: Sheet

Date: Sheet

Date: Sheet

4

4

4

of

of

of

42Tuesday, February 15, 2011

42Tuesday, February 15, 2011

1

42Tuesday, February 15, 2011

1A

1A

1A

WWW.AliSaler.Com

5

WWW.AliSaler.Com

4

3

2

+1.5V_CPU<6>

+1.05V_VTT<3,6,13,14,31,34,35,36,40>

+VCORE<7,35>

1

+1.8V<14,34>

05

VTT0_11

VTT0_12

VTT0_13

VTT0_14

VTT0_15

VTT0_16

VTT0_17

VTT0_18

VTT0_19

VTT0_20

VTT0_21

VTT0_22

VTT0_23

VTT0_24

VTT0_25

VTT0_26

VTT0_27

VTT0_28

VTT0_29

VTT0_30

VTT0_31

VTT0_32

VTT0_33

VTT0_34

VTT0_35

VTT0_36

VTT0_37

VTT0_38

VTT0_39

VTT0_40

VTT0_41

VTT0_42

VTT0_1

VTT0_2

VTT0_3

VTT0_4

VTT0_5

VTT0_6

VTT0_7

VTT0_8

VTT0_9

VTT0_10

VTT0_43

VTT0_44

VTT0_45

VTT0_46

VTT0_47

VTT0_48

VTT0_49

VTT0_50

VTT0_51

VTT0_52

VTT0_53

VTT0_54

VTT0_55

VTT0_56

VTT0_57

VTT0_58

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT0_63

VTT0_64

VTT0_65

VTT0_66

VTT0_67

VTT0_68

VTT0_69

VTT0_70

VTT0_71

VTT0_72

VTT0_73

AW

AW

AU60

AU59

AU

AR

AR

AR

AN60

AN

AN

AN

AN

AN15

AN

AN

AM

AL60

AL59

AL17

AL15

AL14

AL12

AK35

AK33

AF

AF

AF

AF

AF

AF

AD

BF60

BF

BD

BD

BB60

BB59

AY60

AW

AW

AW

AD37

AD

AD

AD

AD

W35

W3

W3

W3

W2

W26

W24

W2

U3

U3

U3

U3

U2

U2

U2

U2

R3

R3

R3

R3

R2

R2

R2

R2

AY10

AN

14

12

12

60

59

12

59

35

33

17

14

12

10

39

37

35

33

32

30

39

59

60

59

60

35

33

35

33

32

30

3

2

0

8

3

5

3

2

0

8

6

4

3

5

3

2

0

8

6

4

3

9

+1.05V_VTT

$

3ODFHXQGHU&38

C3239

C3239

C3228

C3228

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

C3238

C3129

C3129

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

C3135

C3135

C3223

C3223

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

C3198

C3198

C3171

C3171

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

C3202

C3202

C3218

C3218

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

C3240

C3240

1U/6.3V_4

1U/6.3V_4

C3136

C3136

1U/6.3V_4

1U/6.3V_4

C3162

C3162

1U/6.3V_4

1U/6.3V_4

C3185

C3185

1U/6.3V_4

1U/6.3V_4

C3242

C3242

1U/6.3V_4

1U/6.3V_4

C3217

C3217

1U/6.3V_4

1U/6.3V_4

C3227

C3227

1U/6.3V_4

1U/6.3V_4

C3149

C3149

1U/6.3V_4

1U/6.3V_4

C3208

C3208

1U/6.3V_4

1U/6.3V_4

C3216

C3216

1U/6.3V_4

1U/6.3V_4

D D

C C

B B

+1.05V_VTT

HFM_VID : Max 1.4V

LFM_VID : Min 0.65V

H_PSI#

R3449*1K/F_4 R3449*1K/F_4

R34461K/F_4 R34461K/F_4

CPU_VID0

R34311K/F_4 R34311K/F_4

R3422*1K/F_4 R3422*1K/F_4

CPU_VID1

R34301K/F_4 R34301K/F_4

R3421*1K/F_4 R3421*1K/F_4

CPU_VID2

R34361K/F_4 R34361K/F_4

R3438*1K/F_4 R3438*1K/F_4

CPU_VID3

R3437*1K/F_4 R3437*1K/F_4

R34391K/F_4 R34391K/F_4

CPU_VID4

R3440*1K/F_4 R3440*1K/F_4 C3238

R34421K/F_4 R34421K/F_4

CPU_VID5

R34481K/F_4 R34481K/F_4

R3445*1K/F_4 R3445*1K/F_4

CPU_VID6

R3441*1K/F_4 R3441*1K/F_4

R34431K/F_4 R34431K/F_4

DPRSLPVR

R34521K/F_4 R34521K/F_4

R3450*1K/F_4 R3450*1K/F_4

VCCSENSE<35>

VSSSENSE<35>

+VCORE

R3129

R3129

100/F_4

100/F_4

R3134

R3134

100/F_4

100/F_4

CPU_VID0<35>

CPU_VID1<35>

CPU_VID2<35>

CPU_VID3<35>

CPU_VID4<35>

CPU_VID5<35>

CPU_VID6<35>

H_VTTVID1<34>

DPRSLPVR<35>

Zo=27.4/Space=50mil

Zo=27.4/Space=50mil

VTT_SENSE<34>

VSS_SENSE_VTT<34>

H_PSI#< 35>

I_MON<35>

H_VTTVID1

VTT_SENSE

VSS_SENSE_VTT

$

+1.8V

U3018F

U3018F

F68

PSI#

A61

0]

VID[

D61

1]

VID[

D62

VID[2]

A62

VID[

3]

B63

VID[

4]

D64

VID[

5]

D66

6]

VID[

AN1

VTT_

SELECT[1]

F66

PROC_D

PRSLPVR

A41

ISENSE

F64

VCC_SEN

F63

VSS_SENSE

N13

VTT_SENSE

2

R1

VSS_SENSE_VTT

W39

VCCPL

C336810U/6.3V_6 C336810U/6.3V_6

C33694.7U/6.3V_6 C33694.7U/6.3V_6

C33662.2U/6.3V_6 C33662.2U/6.3V_6

C32711U/6.3V_4 C32711U/6.3V_4

C32571U/6.3V_4 C32571U/6.3V_4

L1

W37

VCCPL

L2

U37

L3

VCCPL

R39

VCCPLL4

R37

VCCPLL5

SENSE LINESCPU VIDS

SENSE LINESCPU VIDS

SE

1.8V

1.8V

1.1V RAIL POWER

1.1V RAIL POWER

POWER

POWER

$

MPZ2012S221A_8

MPZ2012S221A_8

L3017

+1.5V_CPU

L3017

C3122

C3122

1U/6.3V_4

1U/6.3V_4

BB14

VDDQ

_CK[1]

BB12

_CK[2]

VDDQ

IC,ARD_BGA,R1P0

IC,ARD_BGA,R1P0

A A

352-(&75'

352-(&75'

352-(&75'

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

PROCESSER 3/7(POWER1)

PROCESSER 3/7(POWER1)

PROCESSER 3/7(POWER1)

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

1

1A

1A

1A

5

5

5

of

of

of

42Tuesday, February 15, 2011

42Tuesday, February 15, 2011

42Tuesday, February 15, 2011

WWW.AliSaler.Com

5

WWW.AliSaler.Com

ues are

Max 22A

D D

C C

B B

A A

VTT Rail Val

Auburndal VTT=1.05V

Clarksfield VTT=1.1V

+VGACORE_IGPU

Please note that +VCC_GFX_CORE

should be 1.05V in Arrandale

C3191

C3191

C3190

C3190

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

C3169

C3169

C3157

C3157

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

C3215

C3215

C3201

C3201

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

C3123

C3123

C3131

C3131

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

C3163

C3163

C3124

C3124

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

+1.05V_VTT

+VCCTTG

C3422

C3422

1U/6.3V_4

1U/6.3V_4

9&$3

9&$3

9&$3

C3424

C3424

1U/6.3V_4

1U/6.3V_4

C3151

C3151

10U/6.3V_6

10U/6.3V_6

C3200

C3200

1U/6.3V_4

1U/6.3V_4

C3138

C3138

1U/6.3V_4

1U/6.3V_4

C3199

C3199

1U/6.3V_4

1U/6.3V_4

C3168

C3168

1U/6.3V_4

1U/6.3V_4

C3130

C3130

1U/6.3V_4

1U/6.3V_4

C3421

C3421

1U/6.3V_4

1U/6.3V_4

4

C3056

C3056

1U/6.3V_4

1U/6.3V_4

C3213

C3213

1U/6.3V_4

1U/6.3V_4

C3049

C3049

1U/6.3V_4

1U/6.3V_4

C3137

C3137

1U/6.3V_4

1U/6.3V_4

C3154

C3154

1U/6.3V_4

1U/6.3V_4

C3420

C3420

1U/6.3V_4

1U/6.3V_4

DI

SNAUMA

Ra 0 ohm

AN32

AN30

AN28

AN26

AN24

AN23

AN21

AN19

AL32

AL30

AL28

AL26

AL24

AL23

AL21

AL19

AK14

AK12

AJ10

AH14

AH12

AF28

AF26

AF24

AF23

AF21

AF19

AF17

AF15

AF14

AD28

AD26

AD24

AD23

AD21

AD19

AD17

W2

W19

U2

U1

U1

U1

U14

U1

R2

R1

R1

R15

AK62

AK60

AK59

AH60

AH59

AF60

AF59

AD60

AD59

AB60

AB59

AA60

AA59

W60

W59

U60

U59

R60

R59

C3423

C3423

1U/6.3V_4

1U/6.3V_4

Ra

U3018G

U3018G

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

VAXG37

1

VTT1_1

VTT1_2

1

VTT1_3

9

VTT1_4

7

VTT1_5

5

VTT1_6

VTT1_7

2

VTT1_8

1

VTT1_9

9

VTT1_10

7

VTT1_11

VTT1_21

VCAP2_1

VCAP2_2

VCAP2_3

VCAP2_4

VCAP2_5

VCAP2_6

VCAP2_7

VCAP2_8

VCAP2_9

VCAP2_10

VCAP2_11

VCAP2_12

VCAP2_13

VCAP2_14

VCAP2_15

VCAP2_16

VCAP2_17

VCAP2_18

VCAP2_19

R3032*0_8 R3032*0_8

IC,ARD_BGA,R1P0

IC,ARD_BGA,R1P0

GRAPHICS

GRAPHICS

PEG & DMI

PEG & DMI

POWER

POWER

3

AF12

VAXG_SENSE

AF10

VSSAXG_SENSE

SENSE

LINES

SENSE

LINES

GRAPHICS VIDs

GRAPHICS VIDs

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

GFX_VR_EN

GFX_DPR

VTT0_

VTT0_

VTT0_

VTT0_

VTT0_

VTT0_

VTT0_

VTT0_

VTT0_

GFX_VID

GFX_VID

GFX_VID

GFX_VID

GFX_VID[4]

GFX_VID

GFX_VID

SLPVR

GFX_IM

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ1

VDDQ1

VDDQ1

VDDQ1

VDDQ1

VDDQ15

VDDQ1

VDDQ1

VDDQ1

VDDQ1

VDDQ20

VDDQ2

VDDQ2

VDDQ2

VDDQ2

VDDQ25

VDDQ2

VDDQ2

VDDQ2

VDDQ2

VDDQ30

VDDQ3

VDDQ3

VDDQ3

VDDQ3

VDDQ35

VDDQ36

VTT0_

DDR[1]

DDR[2]

DDR[3]

DDR[4]

DDR[5]

DDR[6]

DDR[7]

DDR[8]

DDR[9]

VTT1_12

VTT1_13

VTT1_14

VTT1_15

VTT1_16

VTT1_17

VTT1_18

VTT1_19

VTT1_20

AF71

[0]

AG67

[1]

AG70

[2]

AH71

[3]

AN71

AM67

[5]

AM70

[6]

AH69

AL71

AL69

ON

BU40

BU

BU

BN

BM

BL30

BJ

BH

BH

BG43

0

BF16

1

BF15

2

BD35

3

BD33

4

BD32

BD30

6

BD28

7

BD26

8

BD24

9

BD23

BD21

1

BD19

2

BD17

3

BD15

4

BB35

BB33

6

BB32

7

BB30

8

BB28

9

BB26

BB24

1

BB23

2

BB21

3

BB19

4

BB17

BB15

AW32

DDR

AW30

AW28

AW26

AW24

AW23

AW21

AW19

AW17

AW15

AD

AD

AD

AB12

AA12

W1

W1

W1

W1

35

28

38

38

32

28

15

14

12

25

7

5

4

2

GFX_VR_EN

Rd

Rf

Rc

Rd

Re

R3182 *1K/J_4R3182 *1K/J_4

Rf

C3153

C3153

1U/6.3V_4

1U/6.3V_4

C3345

C3345

*10U/6.3V_6

*10U/6.3V_6

$

DISNAUMA

NA

NA

NA

R3451 4.7K_4R3451 4.7K_4

$

C3127

C3127

1U/6.3V_4

1U/6.3V_4

C3206

C3206

1U/6.3V_4

1U/6.3V_4

C3121

C3121

10U/6.3V_6

10U/6.3V_6

2

4.7KNARc

0 ohm

0 ohmRe

VCC_AXG_SENSE <40>

VSS_AXG_SENSE <40>

GFXVR_VID_0 <40>

GFXVR_VID_1 <40>

GFXVR_VID_2 <40>

GFXVR_VID_3 <40>

GFXVR_VID_4 <40>

GFXVR_VID_5 <40>

GFXVR_VID_6 <40>

GFXVR_EN <40>

GFXVR_DPRSLPVR <40>

GFXVR_IMON <40>

C3119

C3119

1U/6.3V_4

1U/6.3V_4

C3186

C3186

C3344

C3344

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

C3116 0.1U/10V_4C3116 0.1U/10V_4

+1.5VSUS

C3113 0.1U/10V_4C3113 0.1U/10V_4

C3181

C3181

C3212

C3212

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

C3141

C3141

C3214

C3214

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

C3139

C3139

1U/6.3V_4

1U/6.3V_4

C3172

C3172

1U/6.3V_4

1U/6.3V_4

12

C3211

C3211

+

+

*330U/2.5V_3528

*330U/2.5V_3528

+1.05V_VTT

+1.05V_VTT

+1.5V_CPU

1

+VCORE<5,7,35>

+1.05V_VTT<3,5,13,14,31,34,35,36,40>

+1.5VSUS<3,15,16,36,37,38>

+1.8V<5,14,34>

+VGACORE_IGPU<40>

+1.5V_CPU<5>

+VCC TTG

for S3 power reduction

Q3010

Q3010

AON6718L

AON6718L

MAIND<38>

MAINON_G<15,38>

+1.5V_CPU +1.5V

2

1

Q3011 2N7002EQ3011 2N7002E

+1.5V_CPU

R394 *0_8/SR394 *0_8/S

3

R3127 220/F_4R3127 220/F_4

06

+1.5VSUS

5

R3097

R3097

D

D

G

G

4

S

S

*0/F_2512

*0/F_2512

213

ile routing

40m

352-(&75'

352-(&75'

352-(&75'

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

PROCESSER 4/7(POWER2)

PROCESSER 4/7(POWER2)

PROCESSER 4/7(POWER2)

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

1

1A

1A

1A

6

6

6

of

of

of

42Tuesday, February 15, 2011

42Tuesday, February 15, 2011

42Tuesday, February 15, 2011

WWW.AliSaler.Com

5

WWW.AliSaler.Com

+VCC0

+VCC2

XI

C3339

C3339

1U/6.3V_4

1U/6.3V_4

C3286

C3286

1U/6.3V_4

1U/6.3V_4

C3314

C3314

1U/6.3V_4

1U/6.3V_4

C3313

C3313

1U/6.3V_4

1U/6.3V_4

C3312

C3312

1U/6.3V_4

1U/6.3V_4

C3341

C3341

1U/6.3V_4

1U/6.3V_4

D D

C C

XI

C3273

C3273

C3283

C3283

C3236

C3236

1U/6.3V_4

1U/6.3V_4

C3235

C3235

1U/6.3V_4

1U/6.3V_4

B B

A A

1U/6.3V_4

1U/6.3V_4

C3262

C3262

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

C3284

C3284

1U/6.3V_4

1U/6.3V_4

C3338

C3338

1U/6.3V_4

1U/6.3V_4

C3342

C3342

1U/6.3V_4

1U/6.3V_4

C3310

C3310

1U/6.3V_4

1U/6.3V_4

C3261

C3261

1U/6.3V_4

1U/6.3V_4

C3246

C3246

1U/6.3V_4

1U/6.3V_4

C3237

C3237

1U/6.3V_4

1U/6.3V_4

4

C3290

C3290

1U/6.3V_4

1U/6.3V_4

C3315

C3315

1U/6.3V_4

1U/6.3V_4

C3340

C3340

1U/6.3V_4

1U/6.3V_4

C3263

C3263

1U/6.3V_4

1U/6.3V_4

C3247

C3247

1U/6.3V_4

1U/6.3V_4

C3274

C3274

1U/6.3V_4

1U/6.3V_4

+VCC0

+VCC2

BD55

BD51

BD48

AW57

AW53

AW50

AU55

AU51

AU48

AR55

AR51

AR48

AN57

AN53

AN50

BD44

BD41

BD37

AW46

AW42

AW39

AU44

AU41

AU37

AR44

AR41

AR37

AN46

AN42

AN39

BB55

BB51

BB48

AY57

AY53

AY50

AL57

AL53

AL50

AK57

AK53

AK50

BB44

BB41

BB37

AY46

AY42

AY39

AL46

AL42

AL39

AK46

AK42

AK39

U3018H

U3018H

VCAP0_1

VCAP0_2

VCAP0_3

VCAP0_4

VCAP0_5

VCAP0_6

VCAP0_7

VCAP0_8

VCAP0_9

VCAP0_10

VCAP0_11

VCAP0_12

VCAP0_13

VCAP0_14

VCAP0_15

VCAP0_16

VCAP0_17

VCAP0_18

VCAP0_19

VCAP0_20

VCAP0_21

VCAP0_22

VCAP0_23

VCAP0_24

VCAP0_25

VCAP0_26

VCAP0_27

VCAP1_1

VCAP1_2

VCAP1_3

VCAP1_4

VCAP1_5

VCAP1_6

VCAP1_7

VCAP1_8

VCAP1_9

VCAP1_10

VCAP1_11

VCAP1_12

VCAP1_13

VCAP1_14

VCAP1_15

VCAP1_16

VCAP1_17

VCAP1_18

VCAP1_19

VCAP1_20

VCAP1_21

VCAP1_22

VCAP1_23

VCAP1_24

VCAP1_25

VCAP1_26

VCAP1_27

IC,ARD_BGA,R1P0

IC,ARD_BGA,R1P0

3

POWER

POWER

CPU CORE SUPPLY

CPU CORE SUPPLY

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_1

VCC_1

VCC_1

VCC_1

VCC_16

VCC_1

VCC_1

VCC_1

VCC_2

VCC_21

VCC_2

VCC_2

VCC_2

VCC_2

VCC_26

VCC_2

VCC_2

VCC_2

VCC_3

VCC_3

VCC_3

VCC_3

VCC_3

VCC_3

VCC_3

VCC_3

VCC_3

VCC_3

VCC_40

VCC_4

VCC_4

VCC_4

VCC_4

VCC_45

VCC_4

VCC_4

VCC_4

VCC_4

VCC_50

VCC_5

VCC_5

VCC_5

VCC_5

VCC_55

VCC_5

VCC_5

VCC_5

VCC_5

VCC_60

VCC_61

VCC_6

VCC_6

VCC_6

VCC_6

VCC_6

VCC_6

VCC_6

VCC_6

VCC_7

VCC_7

VCC_7

VCC_7

VCC_7

VCC_7

VCC_7

VCC_7

VCC_7

VCC_79

VCC_8

VCC_8

VCC_8

VCC_8

VCC_84

VCC_8

VCC_8

VCC_8

VCC_8

VCC_89

2

+VCORE

AF

57

55

AF

AF

53

C3267 10U/6.3V_6C3267 10U/6.3V_6

51

AF

C3297 10U/6.3V_6C3297 10U/6.3V_6

AF50

C3330 10U/6.3V_6C3330 10U/6.3V_6

AF

48

C3296 10U/6.3V_6C3296 10U/6.3V_6

AF

46

C3266 10U/6.3V_6C3266 10U/6.3V_6

AF

44

C3331 10U/6.3V_6C3331 10U/6.3V_6

42

AF

C3268 10U/6.3V_6C3268 10U/6.3V_6

AF41

C3298 10U/6.3V_6C3298 10U/6.3V_6

AD55

C3332 10U/6.3V_6C3332 10U/6.3V_6

AD51

2

C3333 10U/6.3V_6C3333 10U/6.3V_6

AD48

3

C3099 10U/6.3V_6C3099 10U/6.3V_6

AD44

4

C3106 10U/6.3V_6C3106 10U/6.3V_6

AD41

5

C3336 10U/6.3V_6C3336 10U/6.3V_6

AB55

C3048 10U/6.3V_6C3048 10U/6.3V_6

AB51

7

C3094 10U/6.3V_6C3094 10U/6.3V_6

AB48

8

C3104 10U/6.3V_6C3104 10U/6.3V_6

AB44

9

C3044 10U/6.3V_6C3044 10U/6.3V_6

AB41

0

C3351 10U/6.3V_6C3351 10U/6.3V_6

AA55

C3334 10U/6.3V_6C3334 10U/6.3V_6

AA51

2

C3335 10U/6.3V_6C3335 10U/6.3V_6

AA48

3

C3299 10U/6.3V_6C3299 10U/6.3V_6

AA44

4

C3301 10U/6.3V_6C3301 10U/6.3V_6

AA41

5

C3300 10U/6.3V_6C3300 10U/6.3V_6

W55

C3111 0.1U/10V_4C3111 0.1U/10V_4

W51

7

C3108 0.1U/10V_4C3108 0.1U/10V_4

W48

8

W44

9

W41

0

U55

1

U51

2

U48

3

U44

4

U41

5

R55

6

R51

7

R48

8

+VCORE

R44

9

R41

P60

1

N55

2

N51

3

N48

4

N44

N42

6

M60

7

M51

8

M44

9

L55

K60

1

K51

2

K44

3

J55

4

H60

H51

6

H44

7

G60

8

G55

9

G51

G44

F55

2

E60

3

E57

4

E53

5

E50

6

E46

7

E42

8

D59

9

D57

0

D55

1

D54

2

D52

3

D50

4

D48

5

D47

6

D45

7

D43

8

B60

B56

0

B53

1

B49

2

B46

3

B42

A57

5

A54

6

A50

7

A47

8

A43

C3065

C3065

1U/6.3V_4

1U/6.3V_4

C3061

C3061

1U/6.3V_4

1U/6.3V_4

C3270

C3270

1U/6.3V_4

1U/6.3V_4

C3039

C3039

1U/6.3V_4

1U/6.3V_4

C3071

C3071

1U/6.3V_4

1U/6.3V_4

C3068

C3068

1U/6.3V_4

1U/6.3V_4

C3060

C3060

1U/6.3V_4

1U/6.3V_4

C3772

C3772

1U/6.3V_4

1U/6.3V_4

C3035

C3035

1U/6.3V_4

1U/6.3V_4

C3776

C3776

1U/6.3V_4

1U/6.3V_4

C3067

C3067

1U/6.3V_4

1U/6.3V_4

C3064

C3064

1U/6.3V_4

1U/6.3V_4

C3063

C3063

1U/6.3V_4

1U/6.3V_4

C3059

C3059

1U/6.3V_4

1U/6.3V_4

C3780

C3780

1U/6.3V_4

1U/6.3V_4

C3774

C3774

1U/6.3V_4

1U/6.3V_4

C3075

C3075

1U/6.3V_4

1U/6.3V_4

C3081

C3081

1U/6.3V_4

1U/6.3V_4

C3078

C3078

1U/6.3V_4

1U/6.3V_4

C3087

C3087

1U/6.3V_4

1U/6.3V_4

C3771

C3771

1U/6.3V_4

1U/6.3V_4

C3036

C3036

1U/6.3V_4

1U/6.3V_4

C3092

C3092

1U/6.3V_4

1U/6.3V_4

C3066

C3066

1U/6.3V_4

1U/6.3V_4

C3750

C3750

1U/6.3V_4

1U/6.3V_4

1

+VCORE<5,35>

+VCC2

+VCC0

07

352-(&75'

352-(&75'

352-(&75'

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

PROCESSER 5/7(POWER3)

PROCESSER 5/7(POWER3)

PROCESSER 5/7(POWER3)

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

1

1A

1A

1A

7

7

7

of

of

of

42Tuesday, February 15, 2011

42Tuesday, February 15, 2011

42Tuesday, February 15, 2011

WWW.AliSaler.Com

5

WWW.AliSaler.Com

4

3

2

1

U3018E

U3018E

D D

CFG0

AL4

CFG[0

]

AM2

CFG[1

]

AK1

]

AK2

AK4

AJ2

AT2

AG7

AF4

AG2

AH1

AC2

AC4

AE2

AD1

AF8

AF6

AB7

AU1

T4

T2

U1

V2

AV71

AW

70

AY69

BB69

D8

B7

A10

B9

C5

A6

E3

F1

CFG[2

]

CFG[3

CFG[4]

CFG[5

]

CFG[6

]

CFG[7

]

]

CFG[8

CFG[9]

CFG[

10]

11]

CFG[

CFG[

12]

13]

CFG[

CFG[14]

CFG[

15]

16]

CFG[

CFG[

17]

P[0]

RSVD_T

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD26

RSVD27

CTF[7]

RSVD_N

RSVD_NCTF[8]

RSVD_N

CTF[6]

RSVD_N

CTF[5]

IC,ARD_BGA,R1P0

IC,ARD_BGA,R1P0

RSVD

RSVD

RSVD

RSVD_NCTF[1]

RESERVED

RESERVED

DC_T

DC_TEST_BV69

DC_T

DC_T

DC_T

DC_T

DC_TEST_BT71

DC_TES

DC_TES

DC_TES

DC_TES

DC_TEST_BR1

DC_TEST_E71

DC_T

DC_T

DC_TES

DC_TES

DC_TES

CFG3

CFG4

CFG7

C C

TP_RSVD17_R

TP_RSVD18_R

VSS_NCTF7

T3002T3002

VSS_NCTF8

T3003T3003

VSS_NCTF6

T3004T3004

VSS_NCTF5

B B

T3036T3036

VCAP0 Voltage Sense Rails

CPU_RSVD32

6

W6

RSVD32

CPU_RSVD33

W6

4

RSVD33

AC

69

RSVD34

AC

71

RSVD35

AA71

RSVD36

AA69

RSVD37

R6

6

RSVD38

R6

4

RSVD39

VSS_NCTF3

BT5

RSVD_T

RSVD_T

EST_BV71

EST_BV68

DC_TES

DC_TES

DC_TES

_NCTF[3]

_NCTF[4]

_NCTF[2]

EST_BV5

EST_BV3

EST_BV1

EST_C71

EST_C69

VSS_NCTF4

BR5

VSS_NCTF2

BV6

VSS_NCTF1

BV8

AV69

RSVD45

AK71

RSVD46

69

AN

RSVD47

AP66

RSVD48

AH

66

RSVD49

AK66

RSVD50

AR

71

RSVD51

66

AM

RSVD52

AK69

RSVD53

71

AU

RSVD54

70

AT

RSVD55

AR

69

RSVD56

69

AU

RSVD57

AT

67

RSVD58

RSVD_TP2

AP2

P[2]

AN7

P[1]

AV4

RSVD62

2

AU

RSVD63

RSVD64_R

BE69

RSVD64

RSVD65_R

BE71

RSVD65

BV71

BV69

BV68

T3047T3047

BV5

T3042T3042

BV3

BV1

BT71

BT69

T_BT69

BT3

T_BT3

BT1

T_BT1

BR71

T_BR71

T_E1

T_C3

T_A71

T_A69

T_A68

T_A5

Add for Daisy Chain function support

T3051T3051

BR1

T3039T3039

E71

T3053T3053

E1

C71

C69

C3

T3001T3001

A71

A69

A68

T3025T3025

A5

T3005T3005

T3049T3049

T3050T3050

T3041T3041

T3040T3040

T3043T3043

T3044T3044

T3038T303 8

CFG0

R3349 3.01K/F_4R3349 3.01K/F_4

CFG3

CFG4

CFG7

RSVD64_R

RSVD65_R

TP_RSVD17_R

TP_RSVD18_R

R3354 *3.01K/F_4R3354 *3.01K/F_4

R3346 *3.01K/F_4R3346 *3.01K/F_4

R3347 *3.01K/F_4R3347 *3.01K/F_4

R3160 *0_4R3160 *0_4

R3159 *0_4R3159 *0_4

R3358 *0_4R3358 *0_4

R3357 *0_4R3357 *0_4

CFG[ 1:0 ] - PC

* 11= 1 x 16 PEG

* 10= 2 x 8 PEG

10

4

CFG

(Display Port Presence)

0

CFG

(PCI-Epress Configuration Select)

CFG3

(PCI-Epress Static Lane Reversal)

The Clarkfield processor's PCI Express interface may

not meet PCI Express 2.0 jitter specifications. Intel

recommends placing a 3.01K +/- 5% pull down resisto

VSS on CFG[7] pin for both rPGA and BGA components.

This pull down resistor should be removed when this

issue is fixed.

Disabled; No Physical Display Port

attached to Embedded Diplay Port

PEG

Single

al Operation

Norm

I_Epress Configuration Select

Enabled; An external Display port device is

connected to the Embedded Display port

urcati on enabled

Bif

Lane Num

15 -> 0 , 14 -> 1

r to

bers Reversed

08

A A

352-(&75'

352-(&75'

352-(&75'

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

PROCESSER 6/7(CFG)

PROCESSER 6/7(CFG)

PROCESSER 6/7(CFG)

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

1

1A

1A

1A

8

8

8

of

of

of

42Friday, January 14, 2011

42Friday, January 14, 2011

42Friday, January 14, 2011

WWW.AliSaler.Com

5

WWW.AliSaler.Com

ARRANDALE PROCESSOR (GND)

D D

C C

B B

A A

5

BM70

BM51

BM44

BM32

BM24

BM17

BK63

BK60

BK53

BK34

BK10

BH70

BH57

BH55

BH47

BH24

BH20

BH15

BG51

BG36

BE70

BE65

BD57

BD53

BD50

BD46

BD42

BD39

BD14

BB71

BB62

BB57

BB53

BB50

BB46

BB42

BB39

BA70

AY71

AY66

AY62

AY59

AY55

AY51

AY48

AR42

AR39

AR35

AR33

AR32

AR30

AR28

AR26

AR24

AR23

AR21

AR19

AR17

AR15

AR14

AP70

AP64

AN62

AN55

AY44

AY41

AY37

AY35

AY33

AY32

AY30

AY28

AY26

BU62

BU58

BU55

BU51

BU48

BU44

BU37

BU32

BU25

BU21

BU18

BU14

BU11

BP42

BN64

BL57

BL55

BL48

BL40

BL28

BL20

BJ64

BJ21

BF62

BF30

BF13

BU7

BN6

BJ9

BJ1

BF8

BE9

BE1

BB7

BB1

AR4

AR1

4

U3018I

U3018I

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

IC,ARD_BGA,R1P0

IC,ARD_BGA,R1P0

4

VSS

VSS

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

AY24

AY23

AY21

AY19

AY17

AY15

AY14

AY12

AY8

AY4

AW67

AW62

AW59

AW55

AW51

AW48

AW44

AW41

AW37

AV9

AV1

AU70

AU62

AU57

AU53

AU50

AU46

AU42

AU39

AU35

AU33

AU32

AU30

AU28

AU26

AU24

AU23

AU21

AU19

AU17

AU15

AU14

AU4

AT64

AT10

AR62

AR57

AR53

AR50

AR46

AN51

AN48

AN44

AN41

AN37

AN5

AN4

AM64

AM8

AL62

AL55

AL51

AL48

AL44

AL41

AL37

AL35

AL33

AL1

AK70

AK64

AK55

AK51

AK48

AK44

AK41

AK37

AK32

AK30

AK28

AK26

AK24

AK23

AK21

AK19

AK17

AK15

AJ70

AH62

AH57

AH55

BV66

BV64

BT68

BR69

BR68

BR3

BN71

BN1

BL71

BL1

R14

H71

F71

E69

E68

A66

A64

E5

C68

3

3

AH53

AH51

AH50

AH48

AH46

AH44

AH42

AH41

AH39

AH37

AH35

AH33

AH32

AH30

AH28

AH26

AH24

AH23

AH21

AH19

AH17

AH15

AH4

AG64

AG9

AG6

AF69

AF62

AF1

AE70

AE64

AD62

AD57

AD53

AD50

AD46

AD42

AD4

AC67

AC64

AC10

AC5

AC1

AB70

AB62

AB57

AB53

AB50

AB46

AB42

AB39

AB37

AB35

AB33

AB32

AB30

AB28

AB26

AB24

AB23

AB21

AB19

AB17

AB15

AB14

AB9

AA66

AA64

AA62

AA57

AA53

AA50

AA46

AA42

AA39

AA37

AA35

AA33

AA32

AA30

AA28

AA26

AA24

AA23

AA21

AA19

F20

F4

E37

E33

E30

E16

E12

D41

D38

D34

D31

D27

D24

D20

D17

D13

D10

D6

B65

B40

U3018J

U3018J

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

VSS286

VSS287

VSS374

VSS375

VSS376

VSS377

VSS378

VSS379

VSS380

VSS381

VSS382

VSS383

VSS384

VSS385

VSS386

VSS387

VSS388

VSS389

VSS390

VSS391

VSS392

VSS415

IC,ARD_BGA,R1P0

IC,ARD_BGA,R1P0

VSS

VSS

VSS404

VSS405

VSS406

VSS407

VSS408

VSS409

VSS410

VSS411

VSS412

VSS413

VSS393

VSS394

VSS395

VSS396

VSS397

VSS398

VSS399

VSS400

VSS401

VSS402

VSS403

VSS288

VSS289

VSS290

VSS291

VSS292

VSS293

VSS294

VSS295

VSS296

VSS297

VSS298

VSS299

VSS300

VSS301

VSS302

VSS303

VSS304

VSS305

VSS306

VSS307

VSS308

VSS309

VSS310

VSS311

VSS312

VSS313

VSS314

VSS315

VSS316

VSS317

VSS318

VSS319

VSS320

VSS321

VSS322

VSS323

VSS324

VSS325

VSS326

VSS327

VSS328

VSS329

VSS330

VSS331

VSS332

VSS333

VSS334

VSS335

VSS336

VSS337

VSS338

VSS339

VSS340

VSS341

VSS342

VSS343

VSS344

VSS345

VSS346

VSS347

VSS348

VSS349

VSS350

VSS351

VSS352

VSS353

VSS354

VSS355

VSS356

VSS357

VSS358

VSS359

VSS360

VSS361

VSS362

VSS363

VSS364

VSS365

VSS366

VSS367

VSS368

VSS369

VSS370

VSS371

VSS372

VSS373

2

A40

A36

A33

A29

A26

A22

A19

A15

A12

A8

B62

B58

B55

B51

B48

B44

A59

A55

A52

A48

A45

AA17

AA15

AA14

AA4

W69

W62

W57

W53

W50

W46

W42

W6

W1

V70

U64

U62

U57

U53

U50

U46

U42

U39

U9

U4

T1

R70

R62

R57

R53

R50

R46

R42

R5

P4

N63

N57

N53

N50

N46

N30

N21

N15

M53

M42

M36

M1

L70