Page 1

A

1 1

2 2

B

C

D

E

Compal confidential

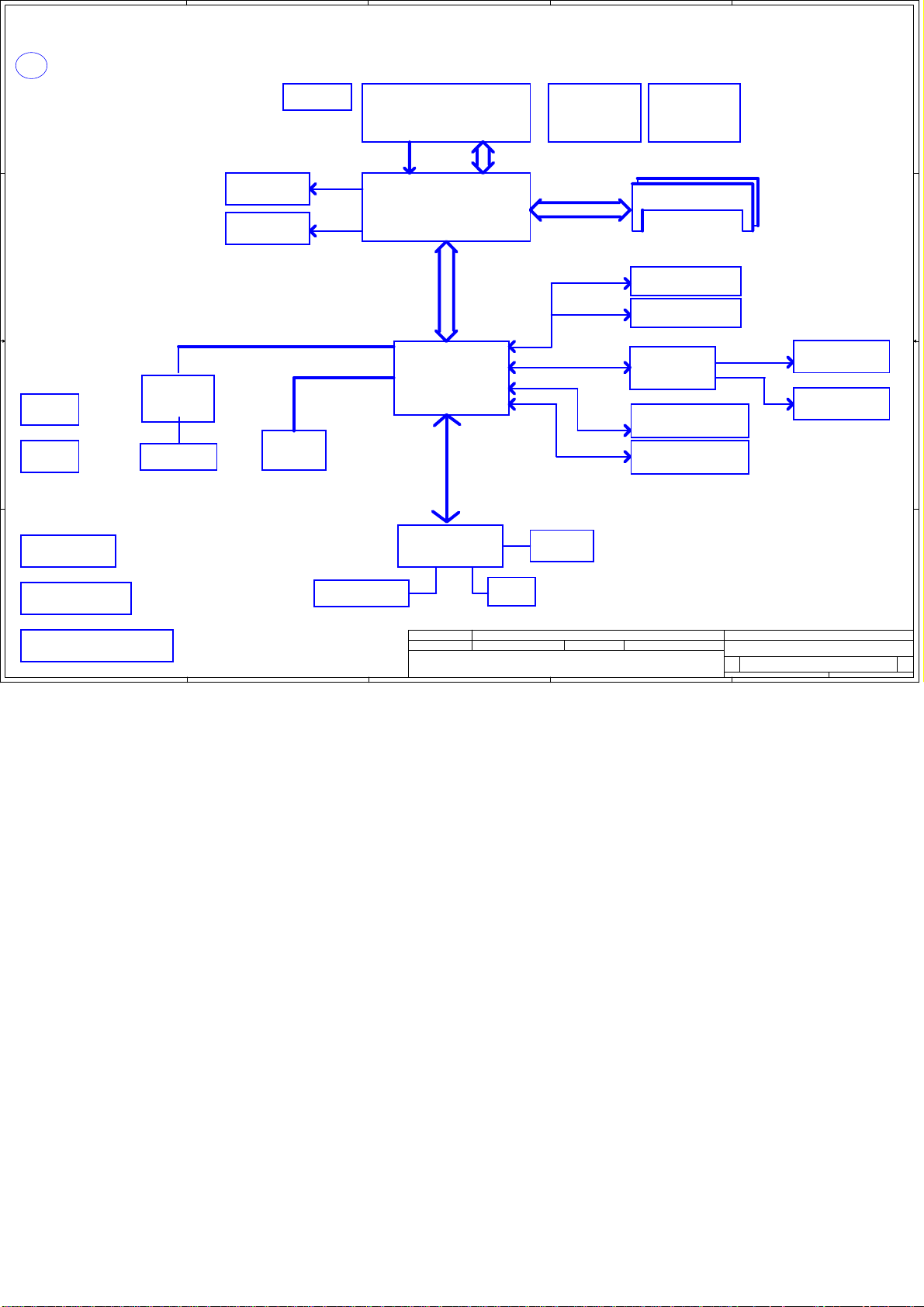

Schematics Document

Mobile Merom uFCPGA with Satna Rosa Platform

3 3

2007-07-30

REV:0.2

4 4

Security Classification

Issued Date

THIS SHEET OF ENG INEE RIN G DR AWIN G IS T HE PRO PRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECR ET INFO RMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRON ICS, INC. NE ITHER THIS SHE ET NOR THE INFO RMATION IT C ONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2007/03/26 2006/07/26

C

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Title

Size Document Number Rev

Custom

LA-4031P

D

Date: Sheet of

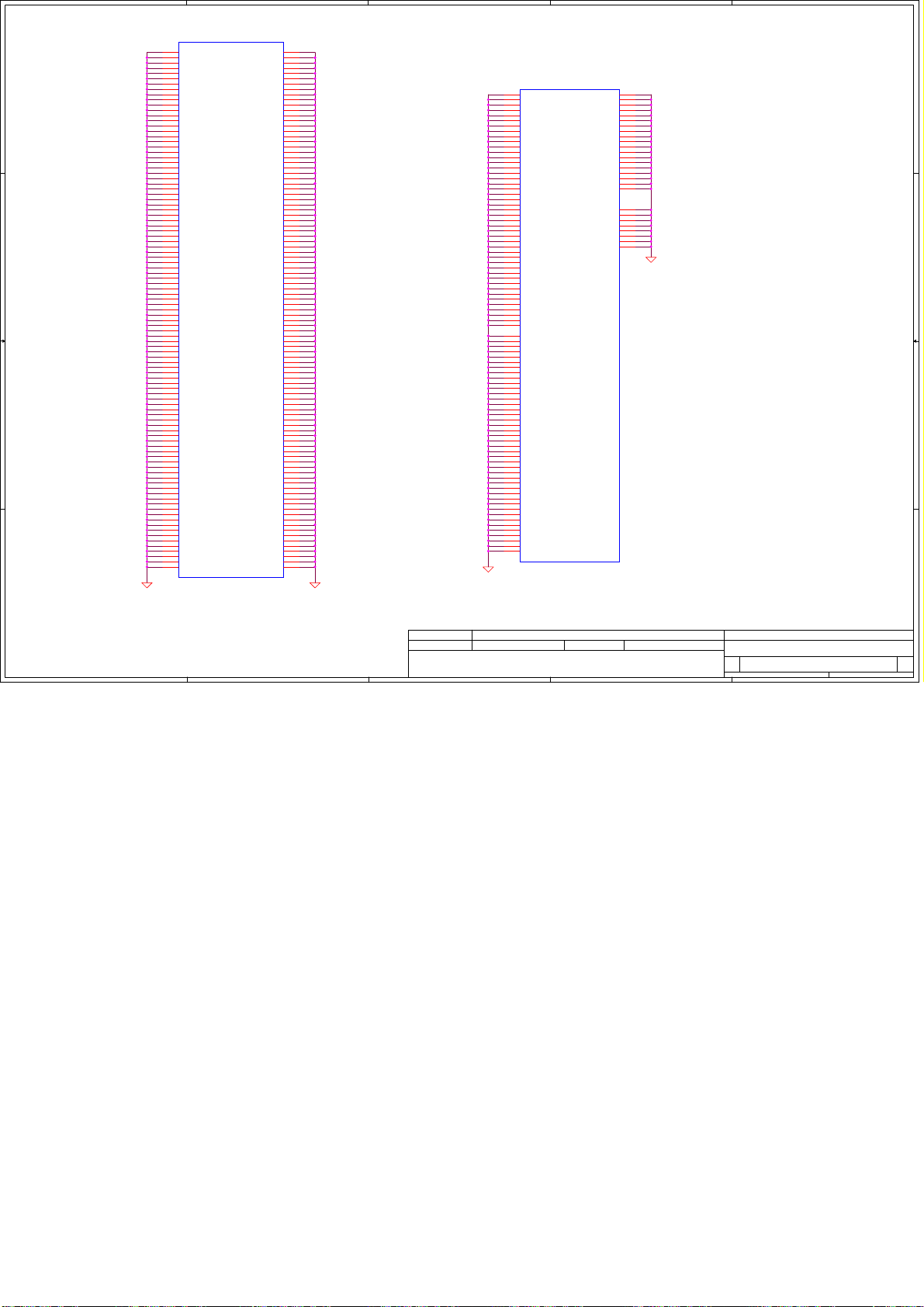

Cover Sheet

E

142Wednesday, October 24, 2007

1.0

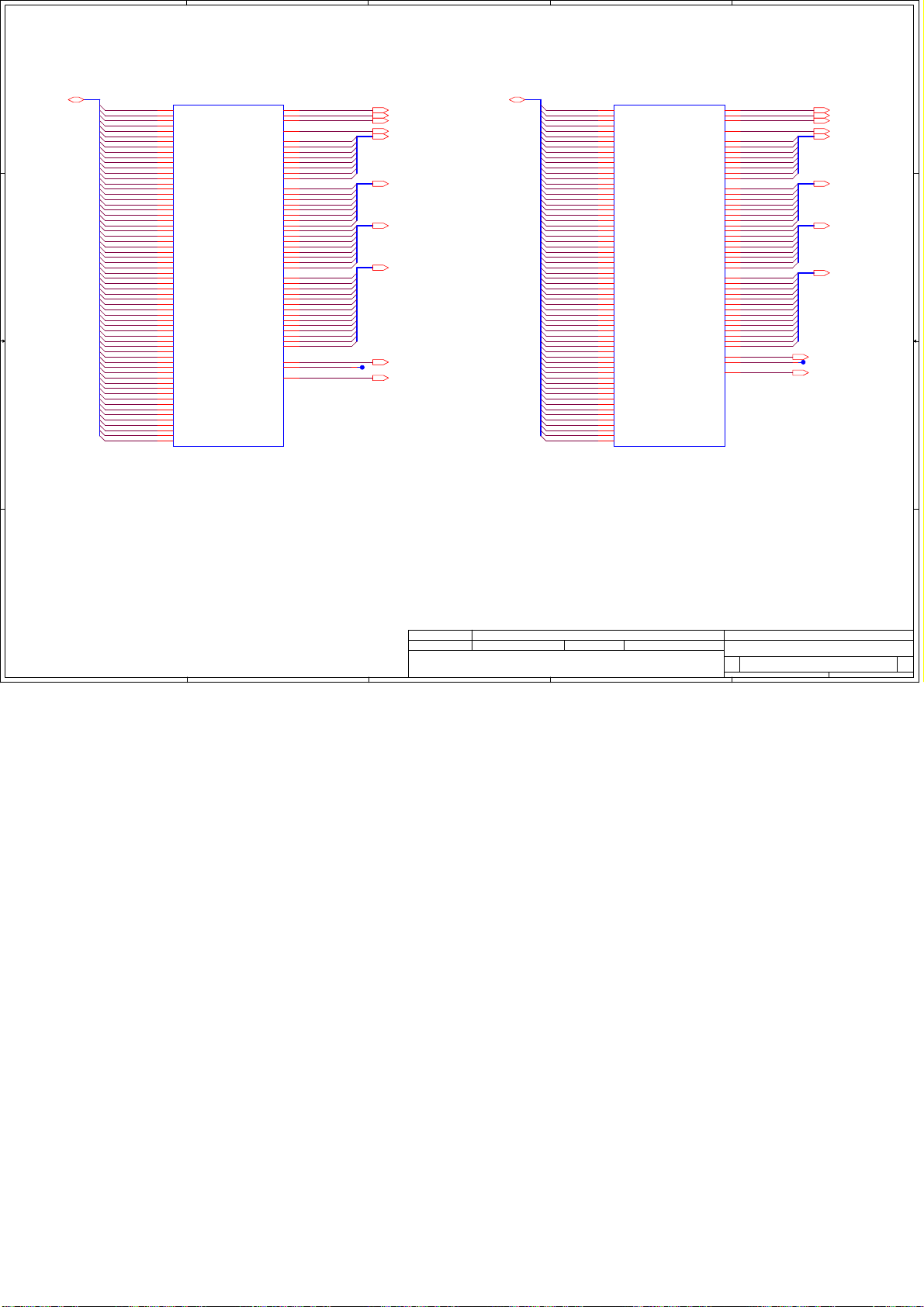

Page 2

A

B

C

D

E

Compal confidential

File Name : LA-4031P

ZZZ1

PCB

1 1

2 2

LED

page 28

3 3

RTC CKT.

page 19

Spartan 1.1 (Merom +Crestline+ICH8)

Mobile Yonah/Merom

uFCPGA-478 CPU

H_A#(3..31)

NB Crestline

Socket P

FSB

533/667/800MHz

page 7,8,9,10,11,12

DMI

SB ICH8

page 18,19,20,21

LPC BUS

H_D#(0..63)

DDR2 -400/533/667

USB2.0

AC-LINK/Azalia

Thermal Sensor

ADM1032AR

Dual Channel

SATA

PATA Master

Clock Generator

ICS9LPRS355

page 4page 4,5,6

DDR2-SO-DIMM X2

BANK 0, 1, 2, 3

USB Card Reader

USB Conn

Audio Conexant

CX20561-12Z

SATA HDD Connector

IDE ODD Connector

page 15

page 13,14

page 27

page 27

page 24

page 22

page 22

Realtek

RTL8100CL

page 23

RJ45/11 CONN

page 23

CRT/TV-OUT

page 16

LVDS Conn

page 17

Mini-Card

WLAN

Fan Control

page 4

PCI BUS

PCI-E BUS

page 22

MODEM AMOM

CX20548

page 25

AMP & Audio Jack

ENE P3017

page 26

SPI

SPI ROM

Power On/Off CKT.

4 4

DC/DC Interface CKT.

Power Circuit DC/DC

page 28

page 31

Page 32,33,34,35,36,37,38

A

Touch Pad CONN.

B

ENE KB926

page 30

Int.KBD

Security Classification

Issued Date

THIS SHEET OF ENG INEE RIN G DR AWIN G IS T HE PRO PRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECR ET INFO RMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRON ICS, INC. NE ITHER THIS SHE ET NOR THE INFO RMATION IT C ONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2007/03/26 2006/07/26

C

25LF080A

page 29

page 30page 28

Compal Secret Data

Deciphered Date

D

Compal Electronics, Inc.

Title

Size Document Number Rev

Custom

LA-4031P

Date: Sheet of

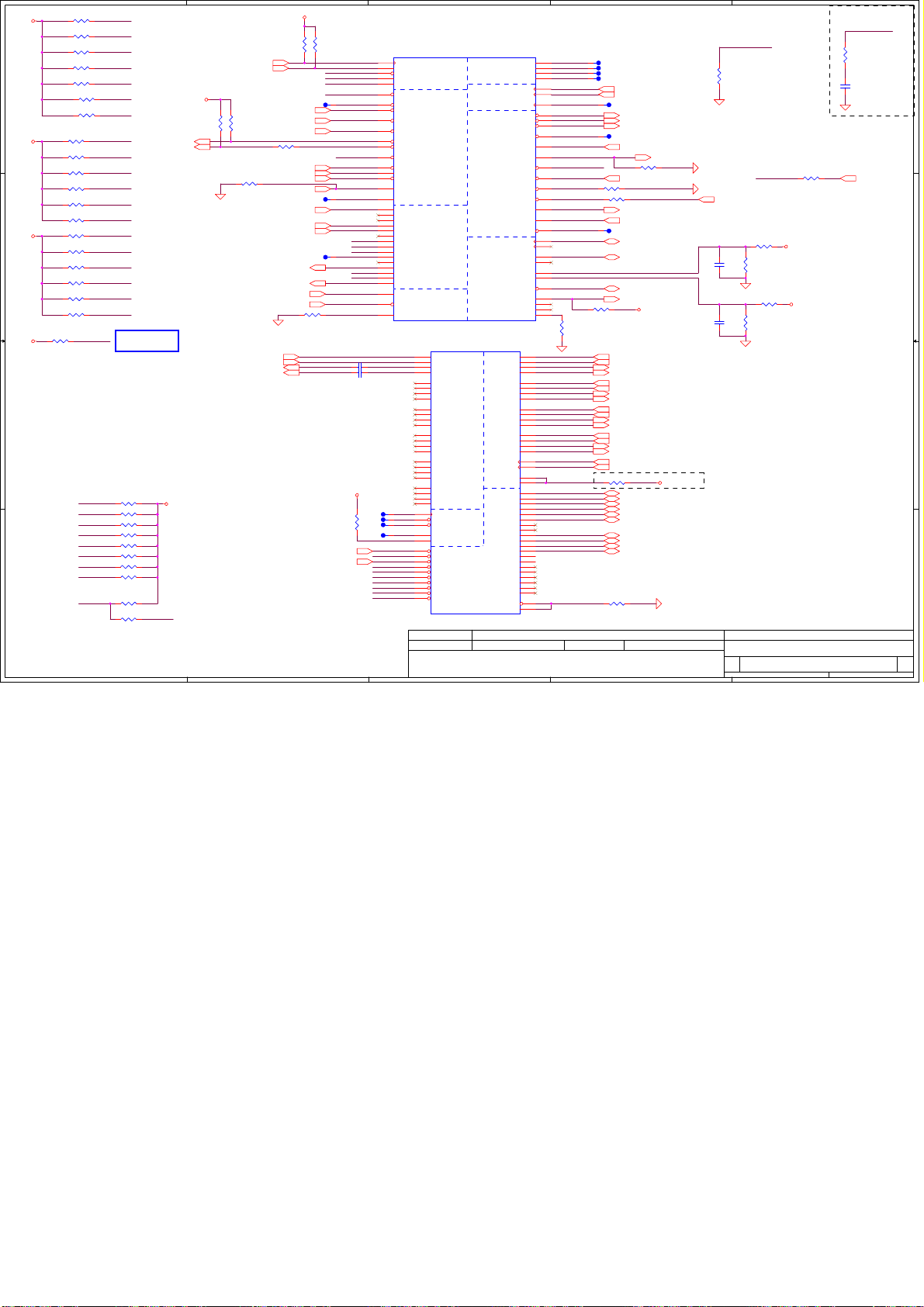

Block Diagram

E

242Wednesday, October 24, 2007

1.0

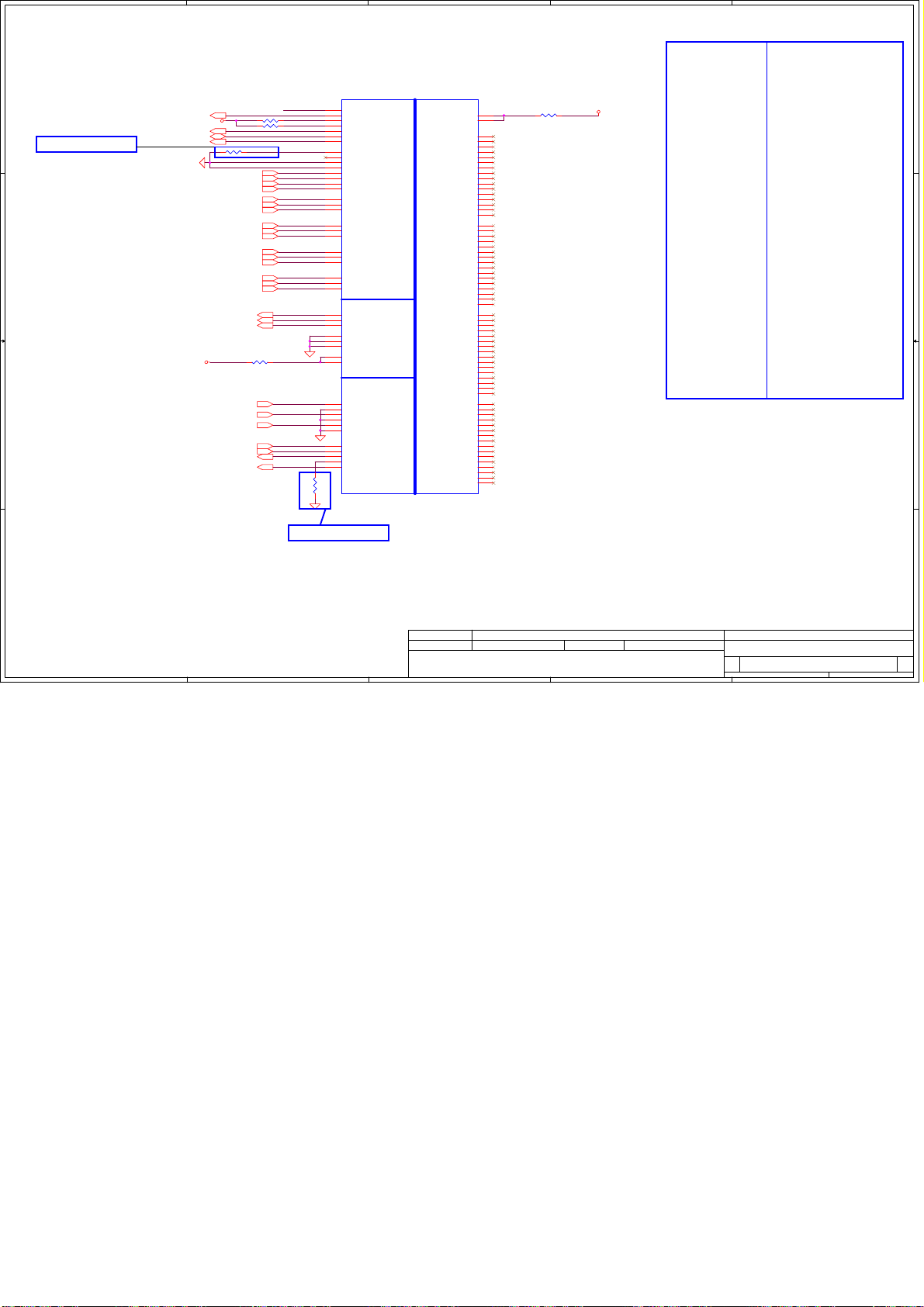

Page 3

5

4

3

2

1

Voltage Rails

+5VS

power

plane

D D

State

S0

S1

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

C C

+5VALW

+B

+3VALW

O

O

O

O

O

X

O

O

O

O

X

XX X

+1.8V

O

XX

X

+3VS

+1.5VS

+1.25VS

+0.9V

+VCCP

+CPU_CORE

OO

OO

X

X

Symbol Note :

: means Digital Ground

: means Analog Ground

@ : means just reserve , no build

DEBUG@ : means just reserve for debug.

External PCI Devices

LAN AD17 0 A

IDSEL # PIRQREQ/GNT #DEVICE

B B

I2C / SMBUS ADDRESSING

DEVICE

DDR SO-DIMM 0

DDR SO-DIMM 1

CLOCK GENERATOR (EXT.)

A A

BOM: 43152432L03(965GM) & 43152432L04(960GML) with card reader

HEX

A0

D2

ADDRESS

1 0 1 0 0 0 0 0

1 0 1 0 0 1 0 0A4

1 1 0 1 0 0 1 0

SMBUS Control Table

SOURCE

SMB_EC_CK1

SMB_EC_DA1

SMB_EC_CK2

SMB_EC_DA2

SMB_CK_CLK1

SMB_CK_DAT1 ICH8

LCD_CLK

LCD_DAT

KB925

KB925

Crestline

INVERTER BATT EEPROM

X

X

X

XX

SERIAL SENSOR

VV

XX

X

X

XX

THERMAL

(CPU)

SODIMM CLK CHIP

ADM1032

XX

X

V

X

VVV

XX

X

X

MINI CARD

LCD

XX

X

X

X

X

V

BOM: 43152432L01(965GM) & 43152432L02(960GML) without card reader

Jump-Short: PJP?

5

Security Classification

Issued Date

THIS SHEET OF EN GINE ERI NG D RAW ING IS THE PR OPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRE T INFO RMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRON ICS, INC. NE ITHER THIS SHE ET NOR THE INFO RMATION IT C ONTAINS

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2007/03/26 2006/07/26

3

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Title

Size Document Number Rev

2

Date: Sheet of

LA-4031P

Notes List

1

342Wednesday, October 24, 2007

1.0

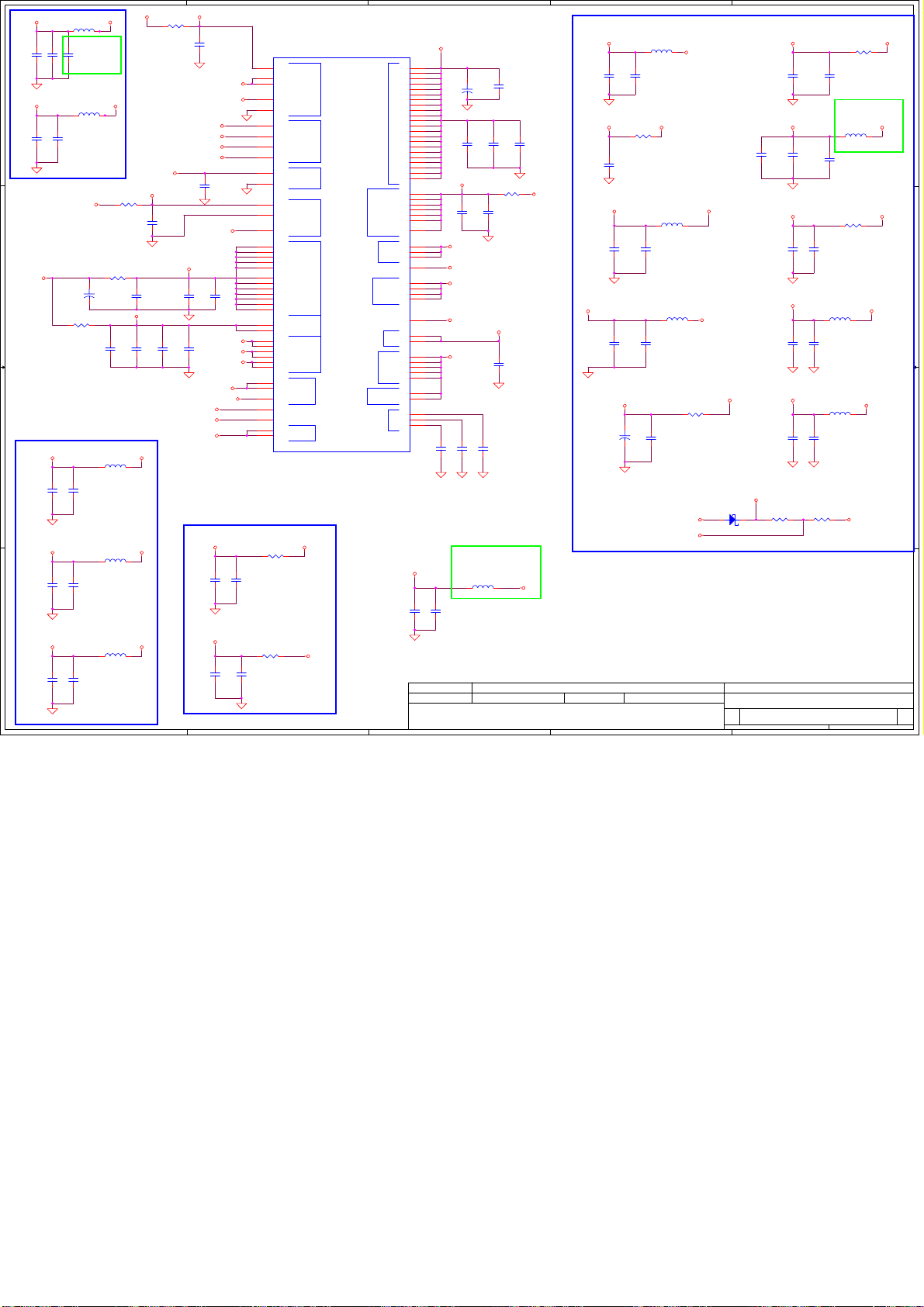

Page 4

5

D D

4

3

2

1

H_A#[3..16]7

H_ADSTB#07

H_REQ#07

H_REQ#17

H_REQ#27

H_REQ#37

H_REQ#47

H_A#[17..35]7

C C

H_ADSTB#17

H_A20M#19

H_FERR#19

H_IGNNE#19

H_STPCLK#19

H_INTR19

H_NMI19

H_SMI#19

B B

+VCCP

12

B

2

H_PROCHOT# OCP#

A A

E

3 1

Q2

@

MMBT3904_SOT23

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_ADSTB#0

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADSTB#1

H_A20M#

H_FERR#

H_IGNNE#

H_STPCLK#

H_INTR

H_NMI

H_SMI#

R17

56_0402_5%@

C

OCP# 20

JP2A

J4

ADDR GROUP 0 ADDR GROUP 1

A[3]#

L5

A[4]#

L4

A[5]#

K5

A[6]#

M3

A[7]#

N2

A[8]#

J1

A[9]#

N3

A[10]#

P5

A[11]#

P2

A[12]#

L2

A[13]#

P4

A[14]#

P1

A[15]#

R1

A[16]#

M1

ADSTB[0]#

K3

REQ[0]#

H2

REQ[1]#

K2

REQ[2]#

J3

REQ[3]#

L1

REQ[4]#

Y2

A[17]#

U5

A[18]#

R3

A[19]#

W6

A[20]#

U4

A[21]#

Y5

A[22]#

U1

A[23]#

R4

A[24]#

T5

A[25]#

T3

A[26]#

W2

A[27]#

W5

A[28]#

Y4

A[29]#

U2

A[30]#

V4

A[31]#

W3

A[32]#

AA4

A[33]#

AB2

A[34]#

AA3

A[35]#

V1

ADSTB[1]#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

M4

RSVD[01]

N5

RSVD[02]

T2

RSVD[03]

V3

RSVD[04]

B2

RSVD[05]

C3

RSVD[06]

D2

RSVD[07]

D22

RSVD[08]

D3

RSVD[09]

F6

RSVD[10]

Merom Ball-out Rev 1a

CONN@

SP07000FP00 S SOCKET TYCO 2-1871873-2 478P H3 CPU

SP07000FD00 S SOCKET FOXCONN PZ4782A-274M-41 478P H3

XDP/ITP SIGNALS

THERMAL

PROCHOT#

THERMDA

THERMDC

ICH

THERMTRIP#

H CLK

RESERVED

H1

ADS#

E2

BNR#

G5

BPRI#

H5

DEFER#

F21

DRDY#

E1

DBSY#

F1

BR0#

D20

IERR#

B3

INIT#

H4

LOCK#

CONTROL

C1

RESET#

F3

RS[0]#

F4

RS[1]#

G3

RS[2]#

G2

TRDY#

G6

HIT#

E4

HITM#

AD4

BPM[0]#

AD3

BPM[1]#

AD1

BPM[2]#

AC4

BPM[3]#

AC2

PRDY#

AC1

PREQ#

AC5

TCK

AA6

TDI

AB3

TDO

AB5

TMS

AB6

TRST#

C20

DBR#

D21

A24

B25

C7

A22

BCLK[0]

A21

BCLK[1]

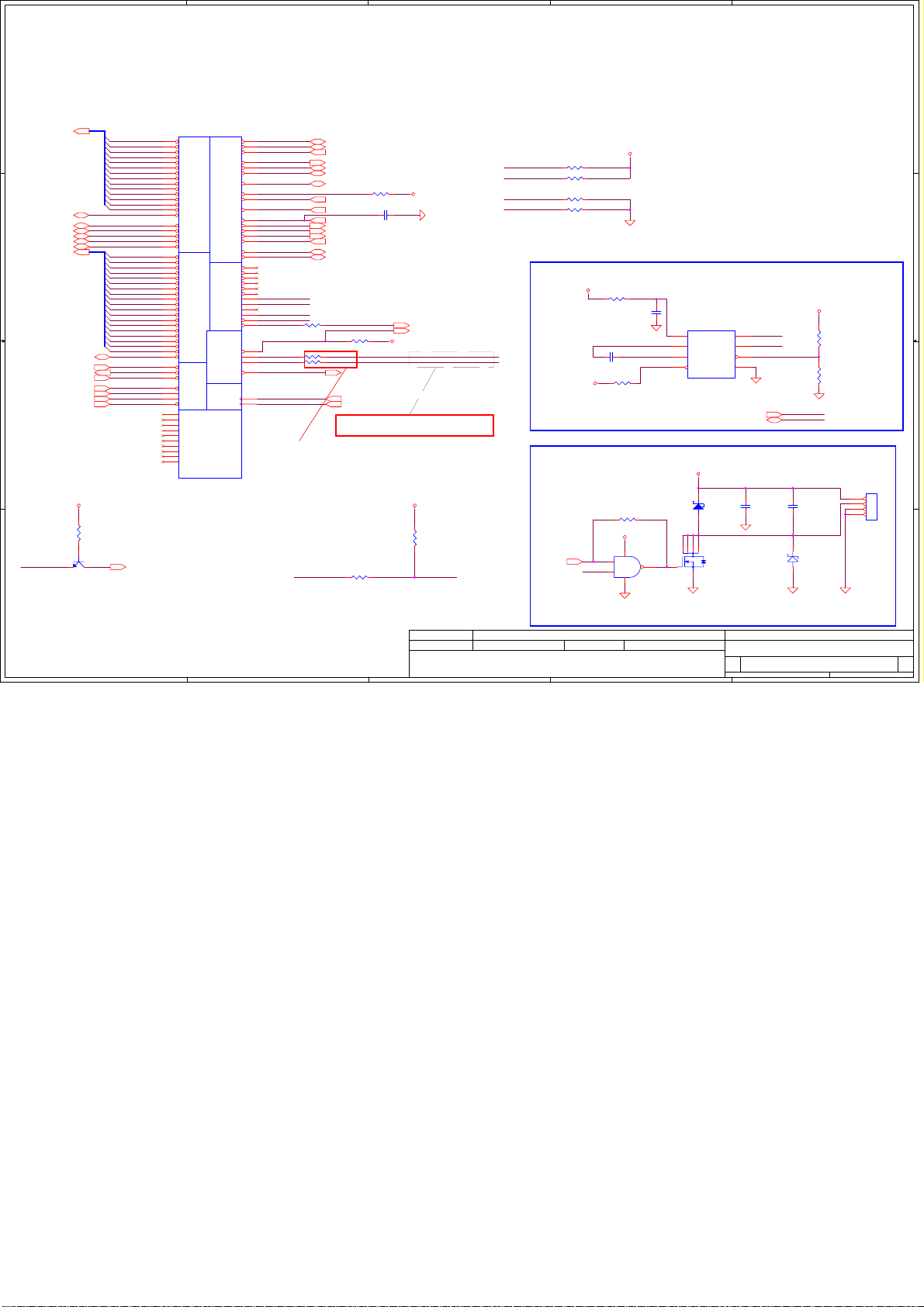

For Merom, R14 and R15 are 0ohm

For Penryn, R14 and R15 are 100ohm.

H_ADS#H_A#3

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

H_BR0#

H_IERR#

H_INIT#

H_LOCK#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#H_REQ#3

H_HIT#

H_HITM#

XDP_TCK

XDP_TDI

XDP_TMS

XDP_TRST#

DBRESET#

H_PROCHOT#

H_THERMDA_R

H_THERMDC_R

H_THERMTRIP#

CLK_CPU_BCLK

CLK_CPU_BCLK#

H_ADS# 7

H_BNR# 7

H_BPRI# 7

H_DEFER# 7

H_DRDY# 7

H_DBSY# 7

H_BR0# 7

H_INIT# 19

H_LOCK# 7

H_RESET# 7

H_RS#0 7

H_RS#1 7

H_RS#2 7

H_TRDY# 7

H_HIT# 7

H_HITM# 7

R413

@

1 2

0_0402_5%

R14 0_0402_5%

1 2

R15 0_0402_5%

1 2

R10

56_0402_5%

C2 0.1U_0402_16V4Z

1 2

XDP_DBRESET#

R13

12

68_0402_5%

H_THERMDA

H_THERMDC

H_THERMTRIP# 7,19

CLK_CPU_BCLK 15

CLK_CPU_BCLK# 15

H_THERMDA, H_THERMDC routing together,

Trace width / Spacing = 10 / 10 mil

R415 0_0402_5%@

1 2

12

+VCCP

+VCCP

XDP_DBRESET# 20

H_PROCHOT# 37

+3VS

12

R416

@

10K_0402_5%

THERM#L_THERM#

+VCCP

XDP_TDI

R2 15_0402_5%

XDP_TMS

XDP_TRST#

XDP_TCK

1 2

R3 39_0402_1%

1 2

R7 560_0402_5%

1 2

R8 27_0402_5%

1 2

Thermal Sensor ADM1032ARMZ

+3VS

2200P_0402_50V7K

+3VS

R414

1 2

0_0402_5%

0.1U_0402_16V4Z

C4

1 2

R16

1 2

10K_0402_5%

PWM Fan Control circuit

R405 0_0402_5%

1 2

+3VS

@

5

1

THERM#

INB

2

INA

P

O

G

TC7SH00FU_SSOP5

3

FAN_PWM30

C3

H_THERMDA

H_THERMDC

L_THERM#

U2

4

2

1

U1

1

VDD

2

D+

3

DTHERM#4GND

ADM1032ARMZ-2REEL_MSOP8

Address:100_1100

+5VS

2

1

G

3

4 5

SCLK

SDATA

ALERT#

SMB_EC_DA230

SMB_EC_CK230

D1

RB751V_SOD323

2 1

6

D

Q1

S

SI3456BDV-T1-E3_TSOP6

+3VS

SMB_EC_CK2

8

SMB_EC_DA2

7

6

5

SMB_EC_DA2

SMB_EC_CK2

SP02000D000 S W-CONN ACES 85204-02001 2P P1.25

ACES_85204-02001_2P

C5

4.7U_0805_10V4Z

FAN

1

C6

0.1U_0402_16V4Z

2

12

D26

@

RLZ5.1B_LL34

1

2

12

12

R426

10K_0402_5%

@

R427

10K_0402_5%

@

JP3

1

1

2

2

3

G1

4

G2

ACES_85204-02001

CONN@

Security Classification

Issued Date

THIS SHEET OF EN GINE ERI NG D RAW ING IS THE PR OPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRE T INFO RMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRON ICS, INC. NE ITHER THIS SHE ET NOR THE INFO RMATION IT C ONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2007/03/26 2006/03/10

3

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Title

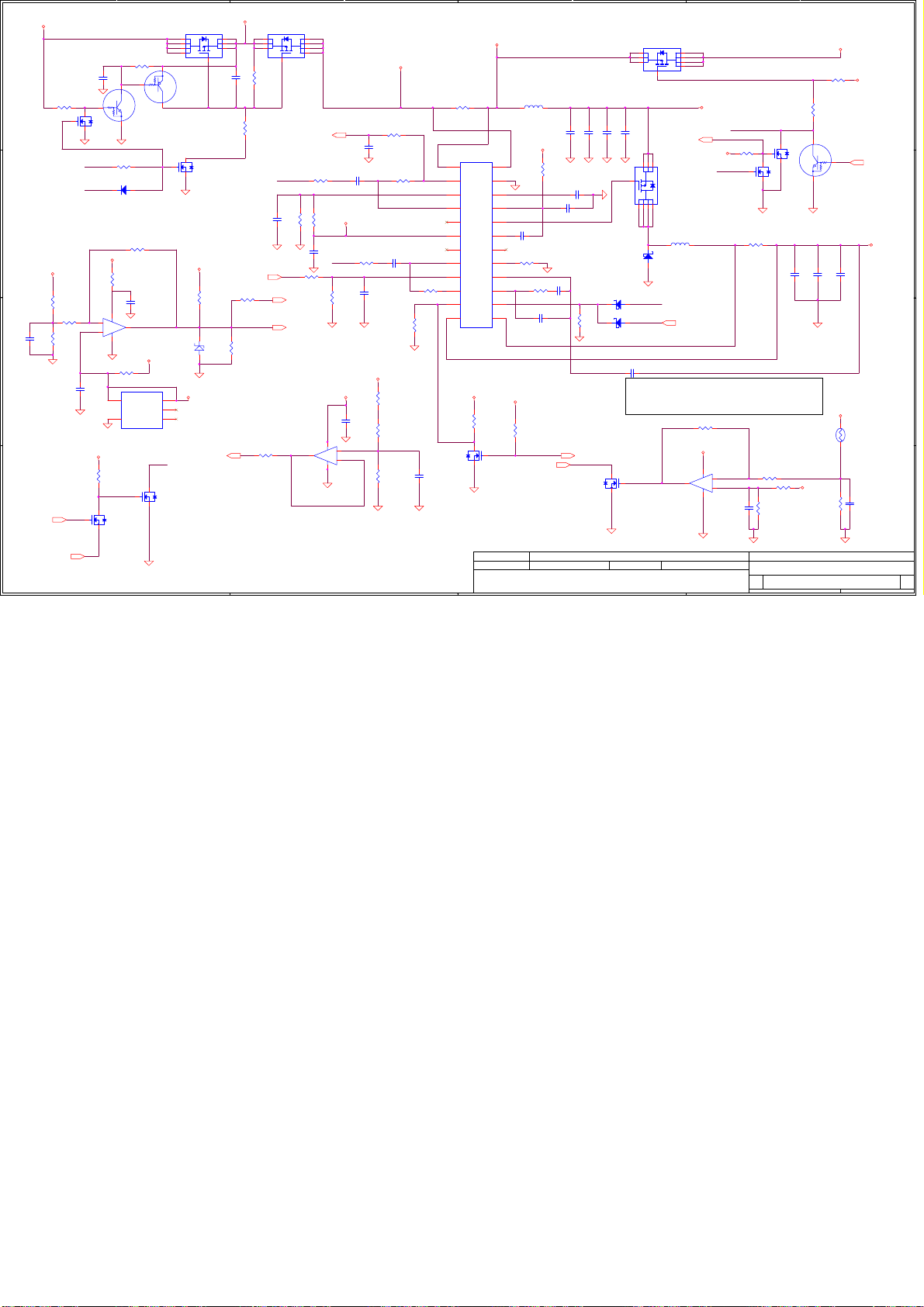

Merom(1/3)-AGTL+/XDP

Size Document Number Rev

Custom

LA-4031P

2

Date: Sheet of

442Wednesday, October 24, 2007

1

1.0

Page 5

5

4

3

2

1

H_D#[0..15]7

D D

H_DSTBN#07

H_DSTBP#07

H_DINV#07

H_D#[16..31]7

C C

H_DSTBN#17

H_DSTBP#17

H_DINV#17

R20 1K_0402_5%@

1 2

R21 1K_0402_5%@

1 2

C8 0.1U_0402_16V4Z@

1 2

CPU_BSEL015

CPU_BSEL115

CPU_BSEL215

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DSTBN#0

H_DSTBP#0

H_DINV#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DSTBN#1

H_DSTBP#1

H_DINV#1 H_DINV#3

V_CPU_GTLREF

TEST1

TEST2

TEST3

T1

TEST4

TEST5

T2

TEST6

T3

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

JP2B

E22

D[0]#

F24

D[1]#

E26

D[2]#

G22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

D[9]#

J24

D[10]#

J23

D[11]#

H22

D[12]#

F26

D[13]#

K22

D[14]#

H23

D[15]#

J26

DSTBN[0]#

H26

DSTBP[0]#

H25

DINV[0]#

N22

D[16]#

K25

D[17]#

P26

D[18]#

R23

D[19]#

L23

D[20]#

M24

D[21]#

L22

D[22]#

M23

D[23]#

P25

D[24]#

P23

D[25]#

P22

D[26]#

T24

D[27]#

R24

D[28]#

L25

D[29]#

T25

D[30]#

N25

D[31]#

L26

DSTBN[1]#

M26

DSTBP[1]#

N24

DINV[1]#

AD26

GTLREF

C23

TEST1

D25

TEST2

C24

TEST3

AF26

TEST4

AF1

TEST5

A26

TEST6

B22

BSEL[0]

B23

BSEL[1]

C21

BSEL[2]

Merom Ball-out Rev 1a

CONN@

DATA GRP 1

MISC

D[32]#

D[33]#

D[34]#

DATA GRP 0

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

DATA GRP 2DATA GRP 3

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

H_D#33

AB24

H_D#34

V24

H_D#35

V26

H_D#36

V23

H_D#37

T22

H_D#38

U25

H_D#39

U23

H_D#40

Y25

H_D#41

W22

H_D#42

Y23

H_D#43

W24

H_D#44

W25

H_D#45

AA23

H_D#46

AA24

H_D#47

AB25

H_DSTBN#2

Y26

H_DSTBP#2

AA26

H_DINV#2

U22

H_D#48

AE24

H_D#49

AD24

H_D#50

AA21

H_D#51

AB22

H_D#52

AB21

H_D#53

AC26

H_D#54

AD20

H_D#55

AE22

H_D#56

AF23

H_D#57

AC25

H_D#58

AE21

H_D#59

AD21

H_D#60

AC22

H_D#61

AD23

H_D#62

AF22

H_D#63

AC23

H_DSTBN#3

AE25

H_DSTBP#3

AF24

AC20

COMP0

R26

COMP1

U26

COMP2

AA1

COMP3

Y1

H_DPRSTP#

E5

H_DPSLP#

B5

H_DPWR#

D24

H_PWRGOOD

D6

H_CPUSLP#

D7

SLP#

H_PSI#

AE6

PSI#

H_D#32

Y22

layout note: Route TEST3 & TEST5 traces on ground referenced layer to the TPs

CPU_BSEL CPU_BSEL2 CPU_BSEL1

166

B B

200

V_CPU_GTLREF

01

0

+VCCP

12

R27

1K_0402_1%

12

R29

2K_0402_1%

CPU_BSEL0

1

1

0

H_D#[32..47] 7

H_DSTBN#2 7

H_DSTBP#2 7

H_DINV#2 7

H_D#[48..63] 7

H_DSTBN#3 7

H_DSTBP#3 7

H_DINV#3 7

H_DPRSTP# 7,19,37

H_DPSLP# 19

H_DPWR# 7

H_PWRGOOD 19

H_CPUSLP# 7

H_PSI# 37

12

12

12

R25

R23

R24

R22

54.9_0402_1%

Resistor placed within

0.5" of CPU pin.Trace

should be at least 25

mils away from any other

toggling signal.

COMP[0,2] trace width is

18 mils. COMP[1,3] trace

width is 4 mils.

27.4_0402_1%

54.9_0402_1%

+VCC_CORE +VCC_CORE

12

27.4_0402_1%

JP2C

A7

VCC[001]

A9

VCC[002]

A10

VCC[003]

A12

VCC[004]

A13

VCC[005]

A15

VCC[006]

A17

VCC[007]

A18

VCC[008]

A20

VCC[009]

B7

VCC[010]

B9

VCC[011]

B10

VCC[012]

B12

VCC[013]

B14

VCC[014]

B15

VCC[015]

B17

VCC[016]

B18

VCC[017]

B20

VCC[018]

C9

VCC[019]

C10

VCC[020]

C12

VCC[021]

C13

VCC[022]

C15

VCC[023]

C17

VCC[024]

C18

VCC[025]

D9

VCC[026]

D10

VCC[027]

D12

VCC[028]

D14

VCC[029]

D15

VCC[030]

D17

VCC[031]

D18

VCC[032]

E7

VCC[033]

E9

VCC[034]

E10

VCC[035]

E12

VCC[036]

E13

VCC[037]

E15

VCC[038]

E17

VCC[039]

E18

VCC[040]

E20

VCC[041]

F7

VCC[042]

F9

VCC[043]

F10

VCC[044]

F12

VCC[045]

F14

VCC[046]

F15

VCC[047]

F17

VCC[048]

F18

VCC[049]

F20

VCC[050]

AA7

VCC[051]

AA9

VCC[052]

AA10

VCC[053]

AA12

VCC[054]

AA13

VCC[055]

AA15

VCC[056]

AA17

VCC[057]

AA18

VCC[058]

AA20

VCC[059]

AB9

VCC[060]

AC10

VCC[061]

AB10

VCC[062]

AB12

VCC[063]

AB14

VCC[064]

AB15

VCC[065]

AB17

VCC[066]

AB18

VCC[067]

Merom Ball-out Rev 1a

CONN@

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA[01]

VCCA[02]

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

R18 0_0402_5%

G21

12

V6

12

R19 0_0402_5%

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

VCCSENSE

AF7

VSSSENSE

AE7

.

Length match within 25 mils.

The trace width/space/other is

20/7/25.

+VCC_CORE

R28

100_0402_1%

1 2

R30

100_0402_1%

1 2

+VCCP

1

+

2

CPU_VID0 37

CPU_VID1 37

CPU_VID2 37

CPU_VID3 37

CPU_VID4 37

CPU_VID5 37

CPU_VID6 37

VCCSENSE 37

VSSSENSE 37

VCCSENSE

VSSSENSE

C7

220U_6.3V_M

C9

1

C10

2

10U_0805_6.3V6M

+1.5VS

1

2

0.01U_0402_16V7K

Near pin B26

Close to CPU pin AD26

within 500mils.

A A

Security Classification

Issued Date

THIS SHEET OF EN GINE ERI NG D RAW ING IS THE PR OPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRE T INFO RMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRON ICS, INC. NE ITHER THIS SHE ET NOR THE INFO RMATION IT C ONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2007/03/26 2006/03/10

3

Compal Secret Data

Deciphered Date

2

Close to CPU pin

within 500mils.

Compal Electronics, Inc.

Title

Merom(2/3)-AGTL+/PWR

Size Document Number Rev

Custom

LA-4031P

Date: Sheet of

542Wednesday, October 24, 2007

1

1.0

Page 6

5

D D

C C

B B

A A

JP2D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

AF2

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

VSS[081]P3VSS[162]

Merom Ball-out Rev 1a

CONN@

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[163]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

.

+VCCP

4

Place these capacitors on L8

(North side,Secondary Layer)

Place these capacitors on L8

(North side,Secondary Layer)

Place these capacitors on L8

(Sorth side,Secondary Layer)

Place these capacitors on L8

(Sorth side,Secondary Layer)

220U_D2_2V_Y_LESR9M

1

C50

0.1U_0402_16V4Z

2

1

2

+VCC_CORE

1

C11

10U_0805_6.3V6M

2

+VCC_CORE

1

C19

10U_0805_6.3V6M

2

+VCC_CORE

1

C27

10U_0805_6.3V6M

2

+VCC_CORE

1

C35

10U_0805_6.3V6M

2

Near CPU CORE regulator

+VCC_CORE

1

+

C45

2

C51

0.1U_0402_16V4Z

1

C52

0.1U_0402_16V4Z

2

1

C12

10U_0805_6.3V6M

2

1

C20

10U_0805_6.3V6M

2

1

C28

10U_0805_6.3V6M

2

1

C36

10U_0805_6.3V6M

2

220U_D2_2V_Y_LESR9M

1

+

C47

C46

2

220U_D2_2V_Y_LESR9M

1

C13

10U_0805_6.3V6M

2

1

C21

10U_0805_6.3V6M

2

1

C29

10U_0805_6.3V6M

2

1

C37

10U_0805_6.3V6M

2

1

+

C48

2

220U_D2_2V_Y_LESR9M

1

C53

0.1U_0402_16V4Z

2

3

1

C14

10U_0805_6.3V6M

2

1

C22

10U_0805_6.3V6M

2

1

C30

10U_0805_6.3V6M

2

1

C38

10U_0805_6.3V6M

2

ESR <= 1.5m ohm

Capacitor > 1980uF

1000U 2.5V M H80 LESR8M

1

1

+

+

C49

2

2

@

1

C54

0.1U_0402_16V4Z

2

1

C15

10U_0805_6.3V6M

2

1

C23

10U_0805_6.3V6M

2

1

C31

10U_0805_6.3V6M

2

1

C39

10U_0805_6.3V6M

2

Place these inside

socket cavity on L8

(North side

Secondary)

1

C55

0.1U_0402_16V4Z

2

1

C16

10U_0805_6.3V6M

2

1

C24

10U_0805_6.3V6M

2

1

C32

10U_0805_6.3V6M

2

1

C40

10U_0805_6.3V6M

2

2

1

C17

10U_0805_6.3V6M

2

1

C25

10U_0805_6.3V6M

2

1

C33

10U_0805_6.3V6M

2

1

C41

10U_0805_6.3V6M

2

1

C18

10U_0805_6.3V6M

2

1

C26

10U_0805_6.3V6M

2

1

C34

10U_0805_6.3V6M

2

1

C42

10U_0805_6.3V6M

2

1

Mid Frequence Decoupling

Security Classification

Issued Date

THIS SHEET OF EN GINE ERI NG D RAW ING IS THE PR OPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRE T INFO RMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRON ICS, INC. NE ITHER THIS SHE ET NOR THE INFO RMATION IT C ONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2007/03/26 2006/03/10

3

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Title

Merom(3/3)-GND&Bypass

Size Document Number Rev

Custom

LA-4031P

2

Date: Sheet of

642Wednesday, October 24, 2007

1

1.0

Page 7

5

H_D#[0..63]5

D D

C C

+VCCP

12

12

R40

R39

54.9_0402_1%

54.9_0402_1%

H_SWNG

H_RCOMP

H_SCOMP

H_SCOMP#

H_RESET#4

H_CPUSLP#5

B B

layout note:

Route H_SCOMP and H_SCOMP# with trace width, spacing and

impedance (55 ohm) same as FSB data traces

Layout Note:

H_RCOMP / H_VREF / H_SWNG

trace width and spacing is 10/20

+VCCP

12

R44

1K_0402_1%

0.1U_0402_16V4Z

A A

12

C62

R49

2K_0402_1%

H_RESET#

H_CPUSLP#

H_VREF

1

2

12

R50

24.9_0402_1%

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_RCOMP

E2

G2

G7

M6

H7

H3

G4

F3

N8

H2

M10

N12

N9

H5

P13

K9

M2

W10

Y8

V4

M3

J1

N5

N3

W6

W9

N2

Y7

Y9

P4

W3

N1

AD12

AE3

AD9

AC9

AC7

AC14

AD11

AC11

AB2

AD7

AB1

Y3

AC6

AE2

AC5

AG3

AJ9

AH8

AJ14

AE9

AE11

AH12

AJ5

AH5

AJ6

AE7

AJ7

AJ2

AE5

AJ3

AH2

AH13

B3

C2

W1

W2

B6

E5

B9

A9

U3A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_SWING

H_RCOMP

H_SCOMP

H_SCOMP#

H_CPURST#

H_CPUSLP#

H_AVREF

H_DVREF

CRESTLINE_1p0

+VCCP

R45

R51

12

12

221_0603_1%

100_0402_1%

HOST

H_SWNGH_VREF

1

2

0.1U_0402_16V4Z

C63

Near B3 pinwithin 100 mils from NB

5

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

4

J13

B11

C11

M11

C15

F16

L13

G17

C14

K16

B13

L16

J17

B14

K19

P15

R17

B16

H20

L19

D17

M17

N16

J19

B18

E19

B17

B15

E17

C18

A19

B19

N19

G12

H17

G20

C8

E8

F12

D6

C10

AM5

AM7

H8

K7

E4

C6

G10

B7

K5

L2

AD13

AE13

M7

K3

AD2

AH11

L7

K2

AC2

AJ10

M14

E13

A11

H13

B12

E12

D7

D8

V_DDR_MCH_REF13,14,35

4

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADS#

H_ADSTB#0

H_ADSTB#1

H_BNR#

H_BPRI#

H_BR0#

H_DEFER#

H_DBSY#

CLK_MCH_BCLK

CLK_MCH_BCLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0H_D#58

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

H_A#[3..35] 4

H_ADS# 4

H_ADSTB#0 4

H_ADSTB#1 4

H_BNR# 4

H_BPRI# 4

H_BR0# 4

H_DEFER# 4

H_DBSY# 4

CLK_MCH_BCLK 15

CLK_MCH_BCLK# 15

H_DPWR# 5

H_DRDY# 4

H_HIT# 4

H_HITM# 4

H_LOCK# 4

H_TRDY# 4

H_DINV#0 5

H_DINV#1 5

H_DINV#2 5

H_DINV#3 5

H_DSTBN#0 5

H_DSTBN#1 5

H_DSTBN#2 5

H_DSTBN#3 5

H_DSTBP#0 5

H_DSTBP#1 5

H_DSTBP#2 5

H_DSTBP#3 5

H_REQ#0 4

H_REQ#1 4

H_REQ#2 4

H_REQ#3 4

H_REQ#4 4

H_RS#0 4

H_RS#1 4

H_RS#2 4

Layout Note:

V_DDR_MCH_REF

trace width and

spacing is 20/20.

V_DDR_MCH_REF

1

C61

2

0.1U_0402_16V4Z

3

+1.8V

2

2

12

R31

C56

C57

1

1

1K_0402_1%

2.2U_0805_16V4Z

2.2U_0805_16V4Z

MCH_CLKSEL015

MCH_CLKSEL115

MCH_CLKSEL215

PM_BMBUSY#20

H_THERMTRIP#4,19

1

C58

2

R36

10K_0402_5%

R37

10K_0402_5%

R38

<>

10K_0402_5%

H_DPRSTP#5,19,37

PM_EXTTS#013

PM_EXTTS#114

PM_PWROK20,30

PLT_RST#18,22

DPRSLPVR20,37

0.01U_0402_16V7K

12

R32

3.01K_0402_1%

NA lead free

12

R33

1

1K_0402_1%

2

C59

0.01U_0402_16V7K

DDR_A_MA1413

DDR_B_MA1414

+3VS

12

12

12

MCH_CLKSEL0

MCH_CLKSEL1

MCH_CLKSEL2

CFG5

T4

CFG6

T5

CFG7

T6

CFG8

T7

CFG9

T8

CFG10

T9

CFG11

T10

CFG12

T11

CFG13

T12

CFG16

T13

CFG18

T44

CFG19

T14

CFG20

T15

PM_BMBUSY#

H_DPRSTP#

PM_EXTTS#0

PM_EXTTS#1

PM_PWROK

PLT_RST#

H_THERMTRIP#

DPRSLPVR

SMRCOMP_VOH

SMRCOMP_VOL

PM_EXTTS#0

PM_EXTTS#1

CLKREQ#_B DMI_TXN0

+1.8V

12

R43

1K_0402_1%

12

R46

1K_0402_1%

AR12

AR13

AM12

AN13

AR37

AM36

AM37

BK22

BF19

BH20

BK18

BF23

BG23

BC23

BD24

BE24

BH39

AW20

BK20

AW49

AV20

BK51

BK50

P36

P37

R35

N35

J12

AL36

D20

H10

B51

BJ20

BJ18

BJ29

C48

D47

B44

C44

A35

B37

B36

B34

C34

P27

N27

N24

C21

C23

F23

N23

G23

J20

C20

R24

L23

J23

E23

E20

K23

M20

M24

L32

N33

L35

G41

L39

L36

J36

N20

G36

BJ51

BL50

BL49

BL3

BL2

BK1

BJ1

E1

A5

C51

B50

A50

A49

BK2

U3B

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

PM_BM_BUSY#

PM_DPRSTP#

PM_EXT_TS#_0

PM_EXT_TS#_1

PWROK

RSTIN#

THERMTRIP#

DPRSLPVR

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

NC_10

NC_11

NC_12

NC_13

NC_14

NC_15

NC_16

CRESTLINE_1p0

2

DDR MUXINGCLK

CFGRSVD

DMI

PM

GRAPHICS VID

ME

NC

MISC

SM_CK_0

SM_CK_1

SM_CK_3

SM_CK_4

SM_CK#_0

SM_CK#_1

SM_CK#_3

SM_CK#_4

SM_CKE_0

SM_CKE_1

SM_CKE_3

SM_CKE_4

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF_0

SM_VREF_1

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VR_EN

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

SDVO_CTRL_CLK

SDVO_CTRL_DATA

CLK_REQ#

ICH_SYNC#

0925_Stuff R43 and R46.

Security Classification

Issued Date

THIS SHEET OF ENG INEE RIN G DR AWIN G IS T HE PRO PRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECR ET INFO RMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRON ICS, INC. NE ITHER THIS SHE ET NOR THE INFO RMATION IT C ONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2007/03/26 2006/03/10

3

Compal Secret Data

Deciphered Date

2

For Crestline: 20ohm

M_CLK_DDR0

AV29

M_CLK_DDR1

BB23

M_CLK_DDR2

BA25

M_CLK_DDR3

AV23

M_CLK_DDR#0

AW30

M_CLK_DDR#1

BA23

M_CLK_DDR#2

AW25

M_CLK_DDR#3

AW23

DDR_CKE0_DIMMA

BE29

DDR_CKE1_DIMMA

AY32

DDR_CKE2_DIMMB

BD39

DDR_CKE3_DIMMB

BG37

DDR_CS0_DIMMA#

BG20

DDR_CS1_DIMMA#

BK16

DDR_CS2_DIMMB#

BG16

DDR_CS3_DIMMB#

BE13

M_ODT0

BH18

M_ODT1

BJ15

M_ODT2

BJ14

M_ODT3

BE16

SMRCOMP

BL15

SMRCOMP#

BK14

SMRCOMP_VOH

BK31

SMRCOMP_VOL

BL31

AR49

V_DDR_MCH_REF

AW4

CLK_MCH_DREFCLK

B42

CLK_MCH_DREFCLK#

C42

MCH_SSCDREFCLK

H48

MCH_SSCDREFCLK#

H47

CLK_MCH_3GPLL

K44

CLK_MCH_3GPLL#

K45

AN47

DMI_TXN1

AJ38

DMI_TXN2

AN42

DMI_TXN3

AN46

DMI_TXP0

AM47

DMI_TXP1

AJ39

DMI_TXP2

AN41

DMI_TXP3

AN45

DMI_RXN0

AJ46

DMI_RXN1

AJ41

DMI_RXN2

AM40

DMI_RXN3

AM44

DMI_RXP0

AJ47

DMI_RXP1

AJ42

DMI_RXP2

AM39

DMI_RXP3

AM43

E35

A39

C38

B39

E36

CL_CLK0

AM49

CL_DATA0

AK50

M_PWROK

AT43

CL_RST#

AN49

CL_VREF CL_VREF

AM50

H35

K36

CLKREQ#_B

G39

MCH_ICH_SYNC#

G40

A37

TEST_1

R32

TEST_2

12

R47

20K_0402_5%

Title

Size Document Number Rev

Custom

Date: Sheet of

For Calero: 80.6ohm

M_CLK_DDR0 13

M_CLK_DDR1 13

M_CLK_DDR2 14

M_CLK_DDR3 14

M_CLK_DDR#0 13

M_CLK_DDR#1 13

M_CLK_DDR#2 14

M_CLK_DDR#3 14

DDR_CKE0_DIMMA 13

DDR_CKE1_DIMMA 13

DDR_CKE2_DIMMB 14

DDR_CKE3_DIMMB 14

DDR_CS0_DIMMA# 13

DDR_CS1_DIMMA# 13

DDR_CS2_DIMMB# 14

DDR_CS3_DIMMB# 14

M_ODT0 13

M_ODT1 13

M_ODT2 14

M_ODT3 14

R34

R35 30_0402_1%

0927_Change from 20 ohm to 30 ohm.

CLK_MCH_DREFCLK 15

CLK_MCH_DREFCLK# 15

MCH_SSCDREFCLK 15

MCH_SSCDREFCLK# 15

CLK_MCH_3GPLL 15

CLK_MCH_3GPLL# 15

DMI_TXN0 20

DMI_TXN1 20

DMI_TXN2 20

DMI_TXN3 20

DMI_TXP0 20

DMI_TXP1 20

DMI_TXP2 20

DMI_TXP3 20

DMI_RXN0 20

DMI_RXN1 20

DMI_RXN2 20

DMI_RXN3 20

DMI_RXP0 20

DMI_RXP1 20

DMI_RXP2 20

DMI_RXP3 20

T16

T17

T18

T19

T20

CL_CLK0 20

CL_DATA0 20

M_PWROK 20,30

CL_RST# 20

0.1U_0402_16V4Z

C60

CLKREQ#_B 15

MCH_ICH_SYNC# 20

12

R48

0_0402_5%

Compal Electronics, Inc.

CRESTLINE(1/6)-AGTL+/DMI/DDR2

LA-4031P

1

+1.8V

30_0402_1%

12

12

+1.25VM_AXD

12

R41

1K_0402_1%

12

1

R42

392_0402_1%

2

742Wednesday, October 24, 2007

1

1.0

Page 8

5

D D

DDR_A_D[0..63]13

C C

B B

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

AW44

AW47

BG47

BG50

AW43

BG42

BG40

AW40

AW36

AW41

AW11

BG10

AR43

BA45

AY46

AR41

AR45

AT42

BB45

BF48

BJ45

BB47

BH49

BE45

BE44

BE40

BF44

BH45

BF40

AR40

AT39

AY41

AV38

AT38

AV13

AT13

AV11

AU15

AT11

BA13

BA11

BE10

BD10

BD8

AY9

AW9

BD7

BB9

BB5

AY7

AT5

AT7

AY6

BB7

AR5

AR8

AR9

AN3

AM8

AN10

AT9

AN9

AM9

AN11

U3D

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

CRESTLINE_1p0

4

BB19

SA_BS_0

BK19

SA_BS_1

BF29

SA_BS_2

BL17

SA_CAS#

AT45

SA_DM_0

BD44

SA_DM_1

BD42

SA_DM_2

AW38

SA_DM_3

AW13

SA_DM_4

BG8

SA_DM_5

AY5

SA_DM_6

AN6

SA_DM_7

AT46

SA_DQS_0

BE48

SA_DQS_1

BB43

SA_DQS_2

BC37

SA_DQS_3

BB16

SA_DQS_4

BH6

SA_DQS_5

BB2

SA_DQS_6

AP3

SA_DQS_7

AT47

SA_DQS#_0

BD47

SA_DQS#_1

BC41

SA_DQS#_2

BA37

SA_DQS#_3

BA16

SA_DQS#_4

BH7

SA_DQS#_5

BC1

SA_DQS#_6

AP2

SA_DQS#_7

BJ19

SA_MA_0

BD20

SA_MA_1

BK27

SA_MA_2

BH28

SA_MA_3

BL24

SA_MA_4

BK28

SA_MA_5

BJ27

SA_MA_6

BJ25

SA_MA_7

BL28

SA_MA_8

BA28

SA_MA_9

BC19

SA_MA_10

BE28

SA_MA_11

BG30

SA_MA_12

BJ16

SA_MA_13

BE18

SA_RAS#

AY20

SA_RCVEN#

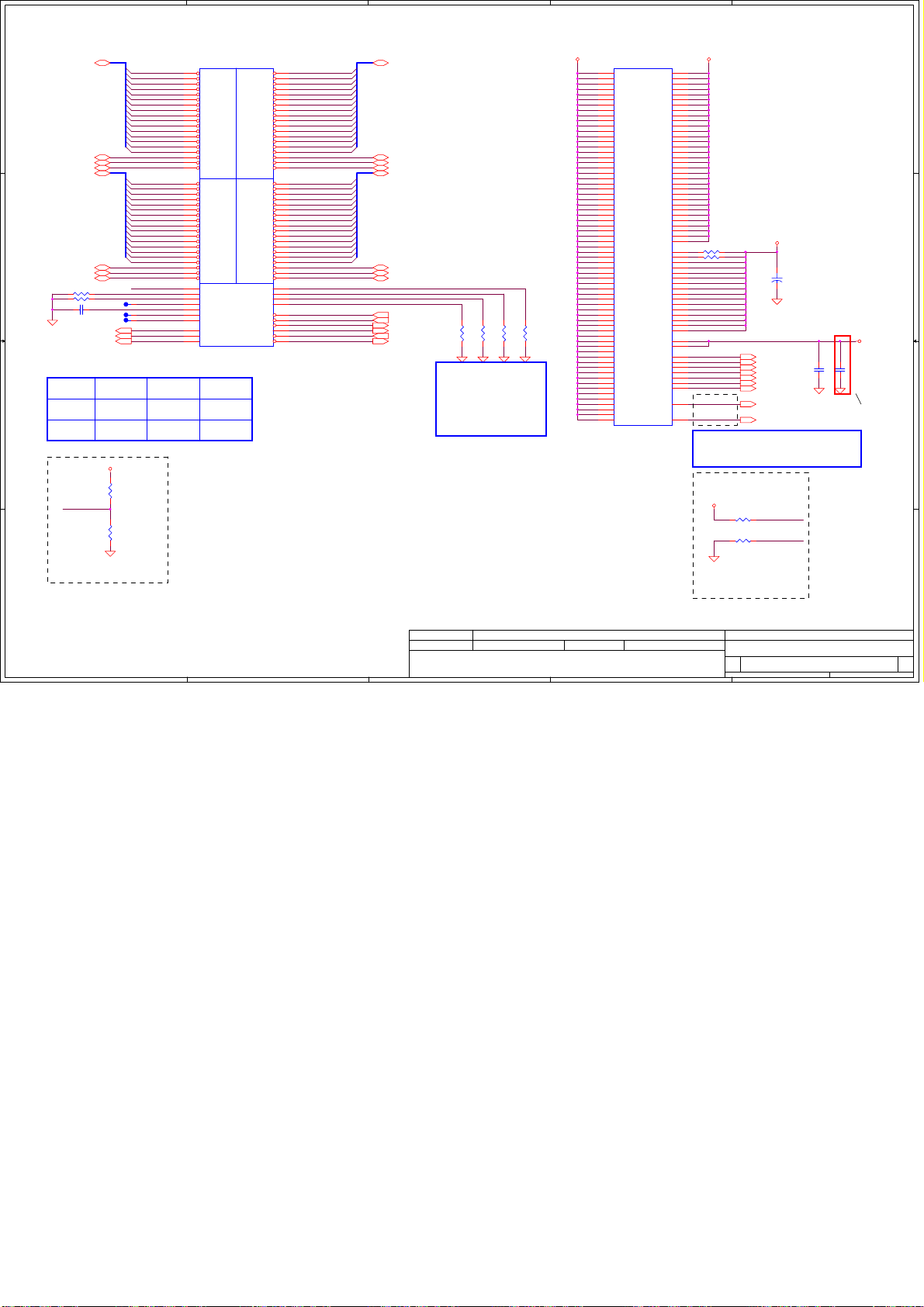

DDR SYSTEM MEMORY A

SA_WE#

BA19

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_A_CAS#

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_RAS#

SA_RCVEN#

DDR_A_WE#

3

DDR_A_BS0 13

DDR_A_BS1 13

DDR_A_BS2 13

DDR_A_CAS# 13 DDR_B_CAS# 14

DDR_A_DM[0..7] 13

DDR_A_DQS[0..7] 13

DDR_A_DQS#[0..7] 13

DDR_A_MA[0..13] 13

DDR_A_RAS# 13

T22

DDR_A_WE# 13

DDR_B_D[0..63]14

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18DDR_A_DQS3

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

AW50

AW51

BG12

AP49

AR51

AN51

AN50

AV50

AV49

BA50

BB50

BA49

BE50

BA51

AY49

BF50

BF49

BJ50

BJ44

BJ43

BL43

BK47

BK49

BK43

BK42

BJ41

BL41

BJ37

BJ36

BK41

BJ40

BL35

BK37

BK13

BE11

BK11

BC11

BC13

BE12

BC12

BJ10

BL9

BK5

BL5

BK9

BK10

BJ8

BJ6

BF4

BH5

BG1

BC2

BK3

BE4

BD3

BJ2

BA3

BB3

AR1

AT3

AY2

AY3

AU2

AT2

U3E

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

CRESTLINE_1p0

2

DDR_B_BS0

AY17

SB_BS_0

SB_BS_1

SB_BS_2

SB_CAS#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_RAS#

SB_RCVEN#

SB_WE#

DDR SYSTEM MEMORY B

BG18

BG36

BE17

AR50

BD49

BK45

BL39

BH12

BJ7

BF3

AW2

AT50

BD50

BK46

BK39

BJ12

BL7

BE2

AV2

AU50

BC50

BL45

BK38

BK12

BK7

BF2

AV3

BC18

BG28

BG25

AW17

BF25

BE25

BA29

BC28

AY28

BD37

BG17

BE37

BA39

BG13

AV16

AY18

BC17

DDR_B_BS1

DDR_B_BS2

DDR_B_CAS#

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10DDR_B_D42

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_RAS#

SB_RCVEN#

DDR_B_WE#

T21

1

DDR_B_BS0 14

DDR_B_BS1 14

DDR_B_BS2 14

DDR_B_DM[0..7] 14

DDR_B_DQS[0..7] 14

DDR_B_DQS#[0..7] 14

DDR_B_MA[0..13] 14

DDR_B_RAS# 14

DDR_B_WE# 14

A A

Security Classification

Issued Date

THIS SHEET OF ENG INEE RIN G DR AWIN G IS T HE PRO PRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECR ET INFO RMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRON ICS, INC. NE ITHER THIS SHE ET NOR THE INFO RMATION IT C ONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2007/03/26 2006/03/10

3

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Title

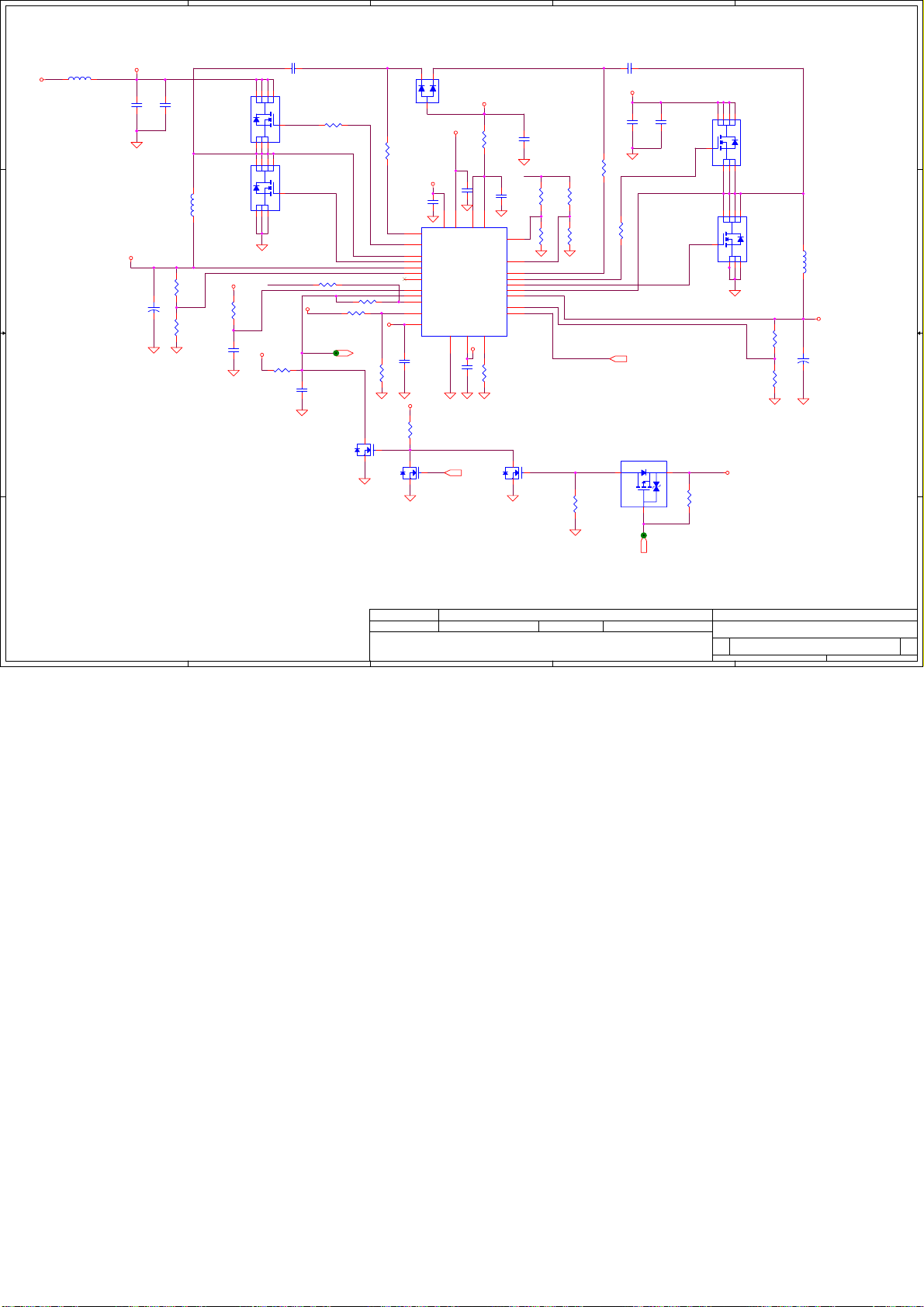

CRESTLINE((2/6)-DDR2 A/B CH

Size Document Number Rev

Custom

LA-4031P

2

Date: Sheet of

842Wednesday, October 24, 2007

1

1.0

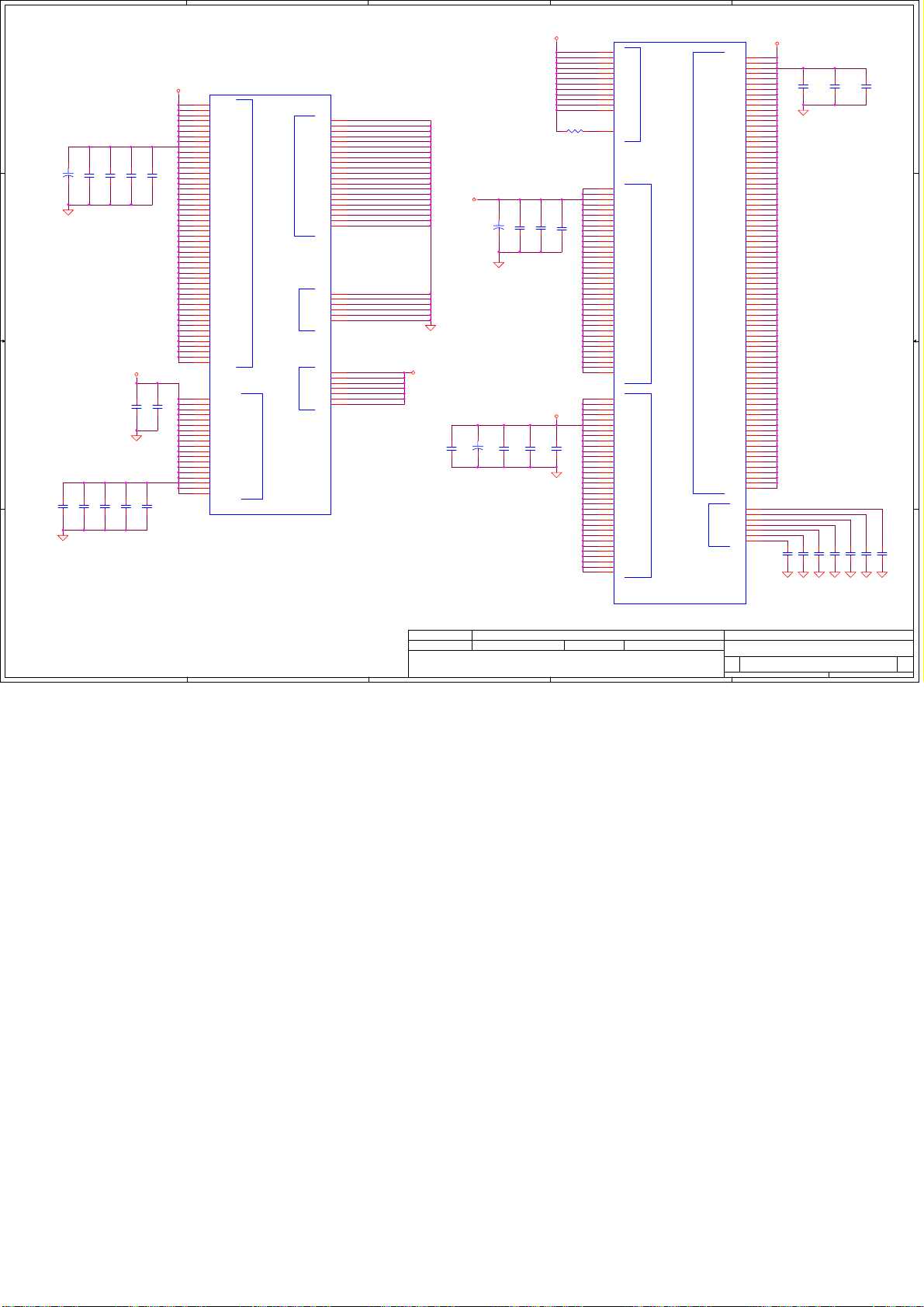

Page 9

5

4

3

2

1

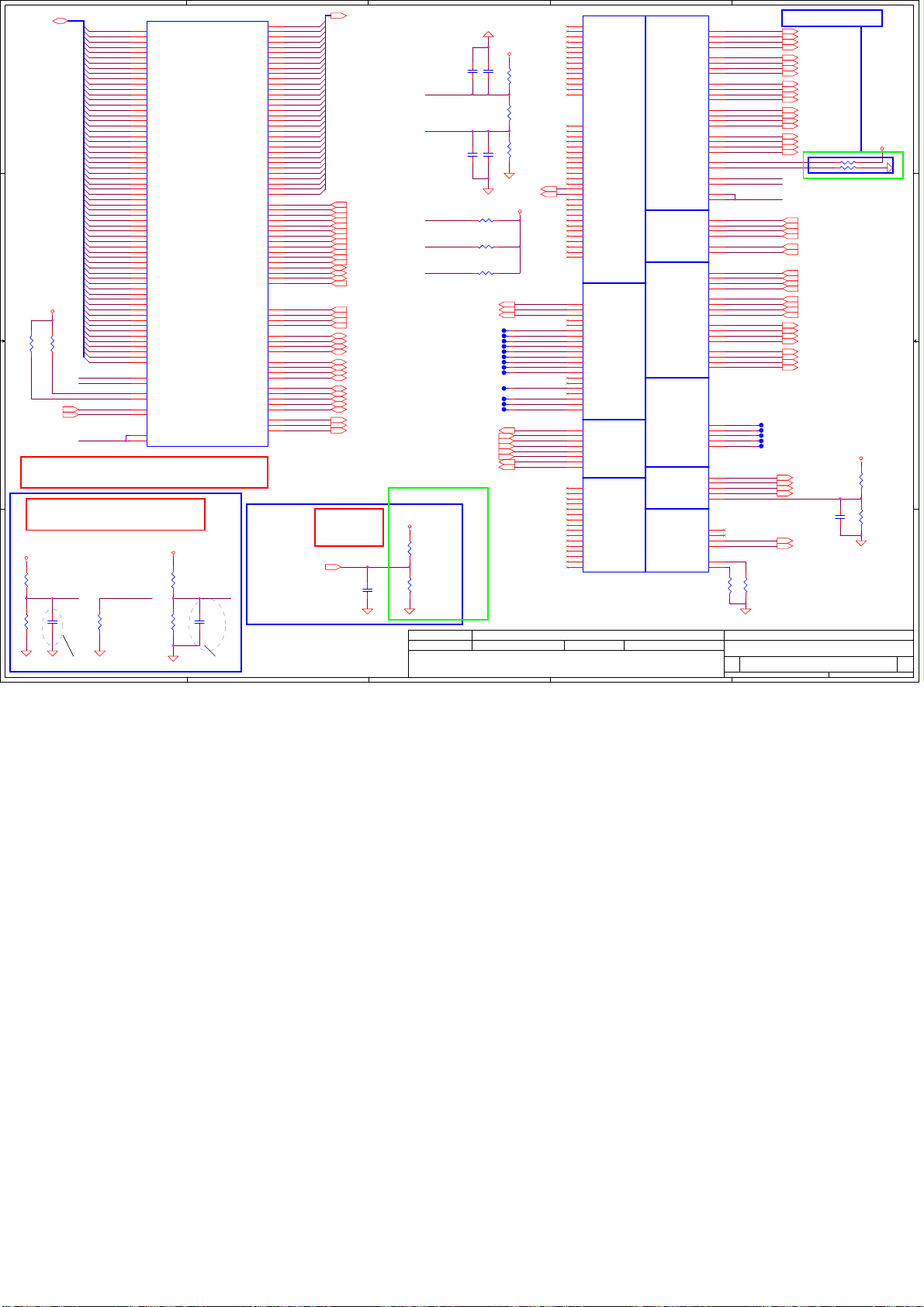

Strap Pin Table

CFG[2:0] FSB Freq select

D D

ENABLT

ENABLT17

+3VS

LCD_CLK17

For Crestline:2.4kohm

For Calero: 1.5Kohm

C C

B B

LCD_DATA17

LCD_CLK

LCD_DATA

ENAVDD

ENAVDD17

R55 2. 4K_0402_1%

LVDSBC-17

LVDSBC+17

TV_COMPS16

TV_LUMA16

TV_CRMA16

R56

+3VS

3VDDCCL16

3VDDCDA16

CRT_HSYNC16

CRT_VSYNC16

BKLT_CTRL

R53 10K_0402_5%

1 2

R54 10K_0402_5%

1 2

12

LVDSAC-

LVDSAC-17

LVDSAC+

LVDSAC+17

LVDSBCLVDSBC+

LVDSA0-

LVDSA0-17

LVDSA1-

LVDSA1-17

LVDSA2-

LVDSA2-17

LVDSA0+

LVDSA0+17

LVDSA1+

LVDSA1+17

LVDSA2+

LVDSA2+17

LVDSB0-

LVDSB0-17

LVDSB1-

LVDSB1-17

LVDSB2-

LVDSB2-17

LVDSB0+

LVDSB0+17

LVDSB1+

LVDSB1+17

LVDSB2+

LVDSB2+17

TV_COMPS

TV_LUMA

TV_CRMA

2.2K_0402_5%

1 2

CRT_B

CRT_B16

CRT_G

CRT_G16

CRT_R

CRT_R16

3VDDCCL

3VDDCDA

CRT_HSYNC

CRT_VSYNC

1.3K_0402_1%

U3C

J40

L_BKLT_CTRL

H39

L_BKLT_EN

E39

L_CTRL_CLK

E40

L_CTRL_DATA

C37

L_DDC_CLK

D35

L_DDC_DATA

K40

L_VDD_EN

L41

LVDS_IBG

L43

LVDS_VBG

N41

LVDS_VREFH

N40

LVDS_VREFL

D46

LVDSA_CLK#

C45

LVDSA_CLK

D44

LVDSB_CLK#

E42

LVDSB_CLK

G51

LVDSA_DATA#_0

E51

LVDSA_DATA#_1

F49

LVDSA_DATA#_2

G50

LVDSA_DATA_0

E50

LVDSA_DATA_1

F48

LVDSA_DATA_2

G44

LVDSB_DATA#_0

B47

LVDSB_DATA#_1

B45

LVDSB_DATA#_2

E44

LVDSB_DATA_0

A47

LVDSB_DATA_1

A45

LVDSB_DATA_2

E27

TVA_DAC

G27

TVB_DAC

K27

TVC_DAC

F27

TVA_RTN

J27

TVB_RTN

L27

TVC_RTN

M35

TV_DCONSEL_0

P33

TV_DCONSEL_1

H32

CRT_BLUE

G32

CRT_BLUE#

K29

CRT_GREEN

J29

CRT_GREEN#

F29

CRT_RED

E29

CRT_RED#

K33

CRT_DDC_CLK

G35

CRT_DDC_DATA

F33

CRT_HSYNC

C32

CRT_TVO_IREF

E33

CRT_VSYNC

12

R57

CRESTLINE_1p0

LVDS

TV VGA

PCI-EXPRESS GRAPHICS

PEG_COMPI

PEG_COMPO

PEG_RX#_0

PEG_RX#_1

PEG_RX#_2

PEG_RX#_3

PEG_RX#_4

PEG_RX#_5

PEG_RX#_6

PEG_RX#_7

PEG_RX#_8

PEG_RX#_9

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

PEG_RX_0

PEG_RX_1

PEG_RX_2

PEG_RX_3

PEG_RX_4

PEG_RX_5

PEG_RX_6

PEG_RX_7

PEG_RX_8

PEG_RX_9

PEG_RX_10

PEG_RX_11

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

PEG_TX#_0

PEG_TX#_1

PEG_TX#_2

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX#_10

PEG_TX#_11

PEG_TX#_12

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

N43

M43

J51

L51

N47

T45

T50

U40

Y44

Y40

AB51

W49

AD44

AD40

AG46

AH49

AG45

AG41

J50

L50

M47

U44

T49

T41

W45

W41

AB50

Y48

AC45

AC41

AH47

AG49

AH45

AG42

N45

U39

U47

N51

R50

T42

Y43

W46

W38

AD39

AC46

AC49

AC42

AH39

AE49

AH44

M45

T38

T46

N50

R51

U43

W42

Y47

Y39

AC38

AD47

AC50

AD43

AG39

AE50

AH43

R52

24.9_0402_1%

PEGCOMP

1 2

PEGCOMP trace w idth

and spacing is 20/25 mils.

+VCCP

CFG5 (DMI select)

CFG6

CFG7 (CPU Strap)

CFG8 (Low power PCIE)

CFG9

(PCIE Graphics Lane Reversal)

CFG[11:10]

CFG[13:12] (XOR/ALLZ)

CFG16 (FSB Dynamic ODT)

SDVO_CTRLDATA

CFG19 (DMI Lane Reversal)

CFG20 (PCIE/SDVO concurrent)

CFG[17:3] have internal pull up

CFG[19:18] have internal pull down

010 = FSB 800MHz

011 = FSB 667MHz

Others = Reserved

0 = DMI x 2

1 = DMI x 4

Reserved

0 = Reserved

1 = Mobile CPU

0 = Normal mode

1 = Low Power mode

0 = Reverse Lane

1 = Normal Operation

*

*

*

*

Reserved

00 = Reserved

01 = XOR Mode Enabled

10 = All Z Mode Enabled

11 = Normal Operation

ReservedCFG[15:14]

0 = Disabled

1 = Enabled

ReservedCFG[18:17]

0 = No SDVO Device Present

1 = SDVO Device Present

0 = Normal Operation

(Lane number in Order)

1 = Reverse Lane

0 = Only PC I E or SDVO is operational.

1 = PCIE/SDVO a re operating simu.

(Default)

*

*

*

*

*

For Crestline:1.3kohm

For Calero: 255ohm

A A

Security Classification

Issued Date

THIS SHEET OF ENG INEE RIN G DR AWIN G IS T HE PRO PRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECR ET INFO RMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRON ICS, INC. NE ITHER THIS SHE ET NOR THE INFO RMATION IT C ONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2007/03/26 2006/03/10

3

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Title

CRESTLINE((3/6)-VGA/LVDS/TV

Size Document Number Rev

Custom

LA-4031P

2

Date: Sheet of

942Wednesday, October 24, 2007

1

1.0

Page 10

BLM18PG181SN1D_0603

R59

0.1U_0402_16V4Z

1

1

C439

4.7U_0603_6.3V6K

2

2

BLM18PG181SN1D_0603

R62

0.1U_0402_16V4Z

1

2

+3VS

1

+

C90

220U_6.3V_M

10U_0805_10V4Z

2

+1.25VM_A_SM_CK

R71

12

0_0603_5%

BLM18PG181SN1D_0603

0.1U_0402_16V4Z

1

1

C112

2

2

BLM18PG181SN1D_0603

0.1U_0402_16V4Z

1

1

C116

2

2

BLM18PG181SN1D_0603

0.1U_0402_16V4Z

1

1

C122

2

2

5

+3VS

12

+3VS

12

0.1U_0402_16V4Z

R68

1 2

0_0805_5%

C99

1

2

5

R66

0_0603_5%

1U_0603_10V4Z

C100

R74

R78

R80

+3VS_PEG_BG

+3VS

12

+3VS

12

+3VS

12

+3VS_DAC_BG

0.022U_0402_16V7K

1

C65

C66

2

0925_Change C439 from 0.47uF to 4.7uF.

D D

+3VS_DAC_CRT

0.022U_0402_16V7K

1

C74

C73

2

+1.25VS

C C

+3VS_TVDACC

B B

0.022U_0402_16V7K

C111

+3VS_TVDACA

0.022U_0402_16V7K

C115

A A

+3VS_TVDACB

0.022U_0402_16V7K

C121

+3VS

+1.8V_TXLVDS

12

1

C85

2

1

C91

4.7U_0805_10V4Z

2

100mA

10U_0805_10V4Z

C101

1

2

R58

0_0603_5%

10mA

5mA

+1.25VM_A_SM

C92

1U_0603_10V4Z

1

2

+1.25VS_PEGPLL

VCCSYNC

12

C64

+1.25VS_DPLLA

+1.25VS_DPLLB

+1.25VM_HPLL

+1.25VM_MPLL

1000P_0402_50V7K

C82

+1.25VS_PEGPLL

1

2

0.1U_0402_16V4Z

C102

1

2

+1.5VS_TVDAC

+1.25VM_HPLL

+1.8V_LVDS

10mA

0.1U_0402_16V4Z

1

2

+3VS_DAC_CRT

+3VS_DAC_BG

80mA

80mA

50mA

150mA

1

2

950mA

1

C93

2

1U_0603_10V4Z

40mA

+3VS_TVDACA

40mA

+3VS_TVDACB

40mA

+3VS_TVDACC

+1.5VS_QDAC

250mA

100mA

150mA

+1.5VS_QDAC

0.022U_0402_16V7K

1

C113

2

+1.8V_LVDS

10U_0805_10V4Z

C119

1

2

80mA

5mA

20 mils

75mA

C114

1U_0603_10V4Z

4

U3H

J32

VCCSYNC

A33

VCCA_CRT_DAC_1

B33

VCCA_CRT_DAC_2

A30

VCCA_DAC_BG

B32

VSSA_DAC_BG

B49

VCCA_DPLLA

H49

VCCA_DPLLB

AL2

VCCA_HPLL

AM2

VCCA_MPLL

A41

VCCA_LVDS

B41

VSSA_LVDS

K50

VCCA_PEG_BG

K49

VSSA_PEG_BG

U51

VCCA_PEG_PLL

AW18

VCCA_SM_1

AV19

VCCA_SM_2

AU19

VCCA_SM_3

AU18

VCCA_SM_4

AU17

VCCA_SM_5

AT22

VCCA_SM_7

AT21

VCCA_SM_8

AT19

VCCA_SM_9

AT18

VCCA_SM_10

AT17

VCCA_SM_11

AR17

VCCA_SM_NCTF_1

AR16

VCCA_SM_NCTF_2

BC29

VCCA_SM_CK_1

BB29

VCCA_SM_CK_2

C25

VCCA_TVA_DAC_1

B25

VCCA_TVA_DAC_2

C27

VCCA_TVB_DAC_1

B27

VCCA_TVB_DAC_2

B28

VCCA_TVC_DAC_1

A28

VCCA_TVC_DAC_2

50mA

M32

VCCD_CRT

25mA

L29

VCCD_TVDAC

5mA

N28

VCCD_QDAC

AN2

VCCD_HPLL

U48

VCCD_PEG_PLL

J41

VCCD_LVDS_1

H42

VCCD_LVDS_2

CRESTLINE_1p0

R77

100_0603_1%

0.1U_0402_16V4Z

1

2

C120

R81

12

0_0603_5%

1

2

4

CRTPLLA PEGA SMTV

POWER

A CK A LVDS

D TV/CRTLVDS

+1.5VS

12

+1.8V

VTT_1

VTT_2

VTT_3

VTT_4

VTT_5

VTT_6

VTT_7

VTT_8

VTT_9

VTT_10

VTT_11

VTT_12

VTT_13

VTT

VTT_14

VTT_15

VTT_16

VTT_17

VTT_18

VTT_19

VTT_20

VTT_21

VTT_22

VCC_AXD_1

VCC_AXD_2

VCC_AXD_3

VCC_AXD_4

VCC_AXD_5

AXD

VCC_AXD_6

VCC_AXD_NCTF

VCC_AXF_1

VCC_AXF_2

VCC_AXF_3

AXF

VCC_DMI

VCC_SM_CK_1

VCC_SM_CK_2

VCC_SM_CK_3

VCC_SM_CK_4

SM CK

VCC_TX_LVDS

VCC_HV_1

VCC_HV_2

HV

VCC_PEG_1

VCC_PEG_2

VCC_PEG_3

VCC_PEG_4

PEG

VCC_PEG_5

VCC_RXR_DMI_1

VCC_RXR_DMI_2

DMI

VTTLF1

VTTLF2

VTTLF3

VTTLF

1000P_0402_50V7K

+1.8V_TXLVDS

C118

Security Classification

THIS SHEET OF ENG INEE RIN G DR AWIN G IS T HE PRO PRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECR ET INFO RMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRON ICS, INC. NE ITHER THIS SHE ET NOR THE INFO RMATION IT C ONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

850mA

U13

U12

U11

U9

U8

U7

U5

U3

U2

U1

T13

T11

T10

T9

T7

T6

T5

T3

T2

R3

R2

R1

AT23

AU28

AU24

AT29

AT25

AT30

AR29

B23

B21

A21

AJ50

BK24

BK23

BJ24

BJ23

A43

C40

B40

AD51

W50

W51

V49

V50

AH50

AH51

A7

F2

AH1

1

2

+VCCP

350mA

100mA

120mA

100mA

1200mA

250mA

0.47U_0603_10V7K

C108

1

2

Issued Date

3

1

+

2

0.47U_0603_10V7K

1

C75

2

+1.25VM_AXD

200mA

1U_0603_10V4Z

C83

1

2

+V1.25VS_AXF

+1.25VS_DMI

+1.8V_SM_CK

+1.8V_TXLVDS

100mA

1450mA

+VCC_PEG

20mils

0.47U_0603_10V7K

0.47U_0603_10V7K

C110

C109

1

1

2

2

1U_WIM32251R0KZF_10%

C117

10U_0805_10V4Z

3

+1.25VS_DPLLB

0.1U_0402_16V4Z

4.7U_0805_10V4Z

1

C71

C72

220U_6.3V_M

2

4.7U_0805_10V4Z

2.2U_0805_16V4Z

1

1

C76

C77

2

2

R65

1 2

+1.25VS

0_0805_5%

10U_0805_10V4Z

C84

1

2

+3VS_HV

0.1U_0402_16V4Z

C103

1

2

1

2

R79

12

2007/03/26 2006/03/10

1022_Change R64, R79 from 0 ohm to 1uH/400mA inductor.

+1.8V

Compal Secret Data

+1.25VS_DMI

+1.25VS_PEGPLL

+1.25VS_DPLLA

Deciphered Date

C67

1

2

C81

1

2

0.1U_0402_16V4Z

1

2

1

2

0.1U_0402_16V4Z

+VCC_PEG

220U_6.3V_M

C104

2

R60

1 2

10U_0805_10V4Z

10U_FLC-453232-100K_0.25A_10%

C68

1

2

+1.25VS

1 2

0.1U_0402_16V4Z

R63

0_0603_5%

BLM18PG121SN1D_0603

10U_0805_10V4Z

C87

C86

1

2

10U_0805_10V4Z

C96

C95

1

2

10U_0805_10V4Z

1

C105

1

+

2

2

2

+1.25VS

+1.25VS

L1

12

R69

1 2

+1.25VS

10U_FLC-453232-100K_0.25A_10%

+VCCP

R72

12

0_0805_5%

D2

2 1

+VCCP

CH751H-40PT_SOD323-2

+3VS

Custom

Date: Sheet of

1

C70

1 2

C80

1 2

0_0805_5%

12

1 2

0_0603_5%

R64

R67

12

+1.25VS

12

+3VS_HV

10 42Wednesday, October 24, 2007

+1.25VS

R61

+1.8V

+1.5VS

+1.25VS

+V1.25VS_AXF

1U_0603_10V4Z

10U_0805_10V4Z

C69

1

1

2

2

+1.8V_SM_CK

10U_0805_10V4Z

10U_0805_10V4Z

C78

1

2

+1.5VS_TVDAC

+1.25VM_HPLL

0.1U_0402_16V4Z

+1.25VM_MPLL

0.1U_0402_16V4Z

+VCCP_D

R75

10_0402_5%

Compal Electronics, Inc.

Title

CRESTLINE(4/6)-PWR

Size Document Number Rev

LA-4031P

0.1U_0402_16V4Z

1U_WIM32251R0KZF_10%

C79

1

1

2

C97

C106

2

0.1U_0402_16V4Z

0.022U_0402_16V7K

1

1

C89

C88

2

2

R70

MBK2012121YZF_0805

1

1

C98

10U_0805_10V4Z

2

2

R73

MBK2012121YZF_0805

1

1

C107

10U_0805_10V4Z

2

2

R76

12

0_0402_5%

1

1.0

Page 11

5

4

3

2

1

+VCCP

VCC=1260mA

D D

0.22U_0603_10V7K

220U_6.3V_M

C C

B B

A A

0.22U_0402_10V4Z

10U_0805_10V4Z

1

C126

+

2

0.22U_0402_10V4Z

1

2

C128

C127

1

1

2

2

0.22U_0402_10V4Z

0.1U_0402_16V4Z

C142

C143

C144

1

1

2

2

VCC=1260mA

0.1U_0402_16V4Z

C129

1

2

+VCCP

VCC_AXM=970mA

10U_0805_10V4Z

10U_0805_10V4Z

C135

1

2

0.1U_0402_16V4Z

C145

1

1

2

2

+VCCP

U3F

AB33

VCC_NCTF_1

AB36

VCC_NCTF_2

AB37

VCC_NCTF_3

AC33

VCC_NCTF_4

AC35

VCC_NCTF_5

AC36

VCC_NCTF_6

AD35

VCC_NCTF_7

AD36

VCC_NCTF_8

AF33

VCC_NCTF_9

AF36

VCC_NCTF_10

AH33

VCC_NCTF_11

AH35

VCC_NCTF_12

AH36

C130

1

2

C136

1

2

0.1U_0402_16V4Z

C146

AH37

AJ33

AJ35

AK33

AK35

AK36

AK37

AD33

AJ36

AM35

AL33

AL35

AA33

AA35

AA36

AP35

AP36

AR35

AR36

Y32

Y33

Y35

Y36

Y37

T30

T34

T35

U29

U31

U32

U33

U35

U36

V32

V33

V36

V37

AL24

AL26

AL28

AM26

AM28

AM29

AM31

AM32

AM33

AP29

AP31

AP32

AP33

AL29

AL31

AL32

AR31

AR32

AR33

VCC_NCTF_13

VCC_NCTF_14

VCC_NCTF_15

VCC_NCTF_16

VCC_NCTF_17

VCC_NCTF_18

VCC_NCTF_19

VCC_NCTF_20

VCC_NCTF_21

VCC_NCTF_22

VCC_NCTF_23

VCC_NCTF_24

VCC_NCTF_25

VCC_NCTF_26

VCC_NCTF_27

VCC_NCTF_28

VCC_NCTF_29

VCC_NCTF_30

VCC_NCTF_31

VCC_NCTF_32

VCC_NCTF_33

VCC_NCTF_34

VCC_NCTF_35

VCC_NCTF_36

VCC_NCTF_37

VCC_NCTF_38

VCC_NCTF_39

VCC_NCTF_40

VCC_NCTF_41

VCC_NCTF_42

VCC_NCTF_43

VCC_NCTF_44

VCC_NCTF_45

VCC_NCTF_46

VCC_NCTF_47

VCC_NCTF_48

VCC_NCTF_49

VCC_NCTF_50

VCC_AXM_NCTF_1

VCC_AXM_NCTF_2

VCC_AXM_NCTF_3

VCC_AXM_NCTF_4

VCC_AXM_NCTF_5

VCC_AXM_NCTF_6

VCC_AXM_NCTF_7

VCC_AXM_NCTF_8

VCC_AXM_NCTF_9

VCC_AXM_NCTF_10

VCC_AXM_NCTF_11

VCC_AXM_NCTF_12

VCC_AXM_NCTF_13

VCC_AXM_NCTF_14

VCC_AXM_NCTF_15

VCC_AXM_NCTF_16

VCC_AXM_NCTF_17

VCC_AXM_NCTF_18

VCC_AXM_NCTF_19

CRESTLINE_1p0

VCC NCTF

POWER

VCC AXM NCTF

VSS_NCTF_1

VSS_NCTF_2

VSS_NCTF_3

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_8

VSS_NCTF_9

VSS_NCTF_10

VSS_NCTF_11

VSS_NCTF_12

VSS_NCTF_13

VSS_NCTF_14

VSS_NCTF_15

VSS NCTF

VSS_NCTF_16

VSS_NCTF_17

VSS_NCTF_18

VSS_NCTF_19

VSS_NCTF_20

VSS_NCTF_21

VSS SCBVCC AXM

VCC_AXM_1

VCC_AXM_2

VCC_AXM_3

VCC_AXM_4

VCC_AXM_5

VCC_AXM_6

VCC_AXM_7

VSS_SCB1

VSS_SCB2

VSS_SCB3

VSS_SCB4

VSS_SCB5

VSS_SCB6

T27

T37