Page 1

A

hexainf@hotmail.com

1 1

2 2

B

C

D

E

Compal confidential

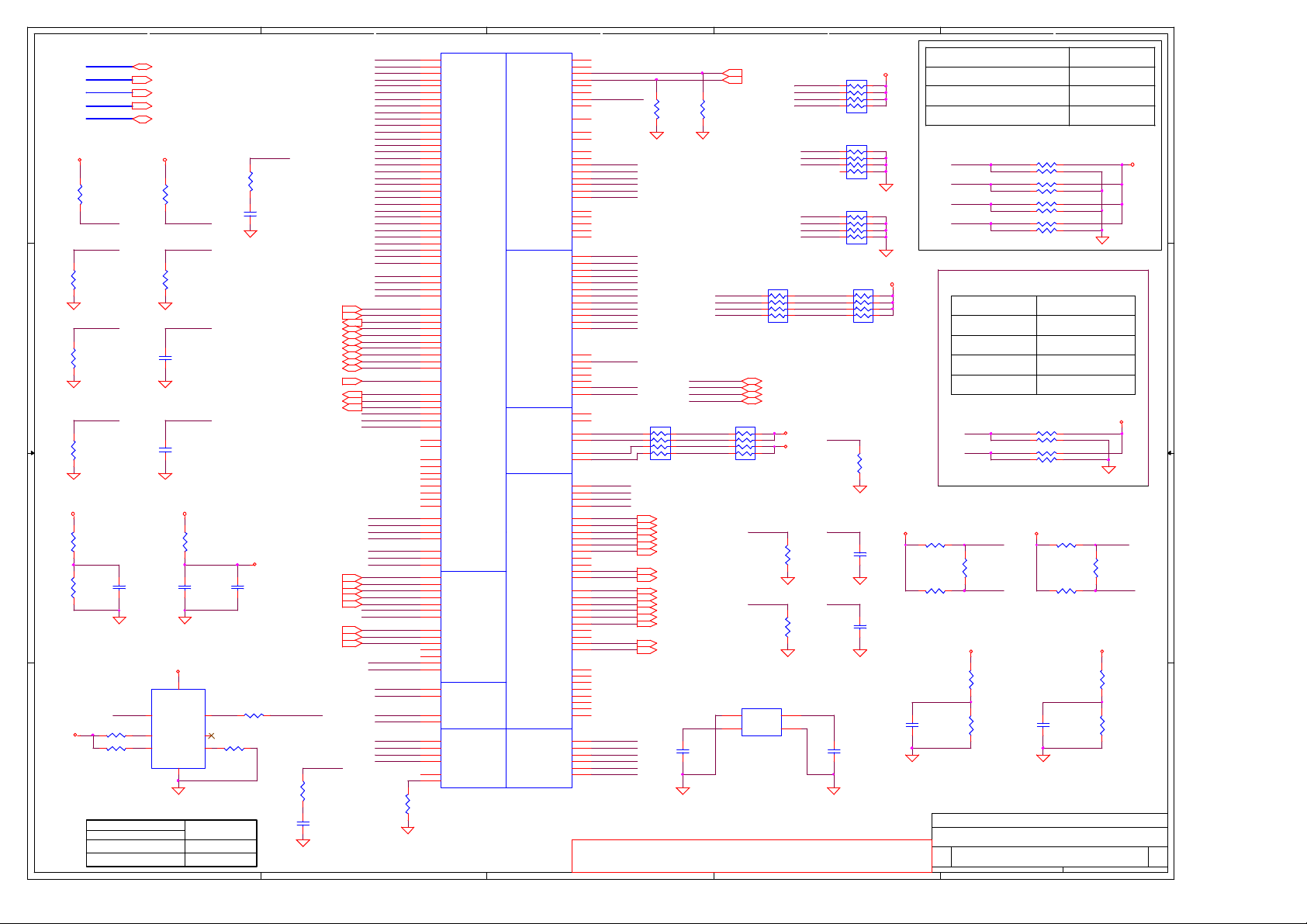

Schematics Document

ClawHammer AMD K8 with

3 3

4 4

A

nVIDIA Chrush K8

2003-10-15

REV:0.5

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Title

Size Document Number Rev

D

Date: Sheet of

Compal Electronics, Inc.

LA-1851

Cover Sheet

E

1 50Thursday, October 16, 2003

0.5

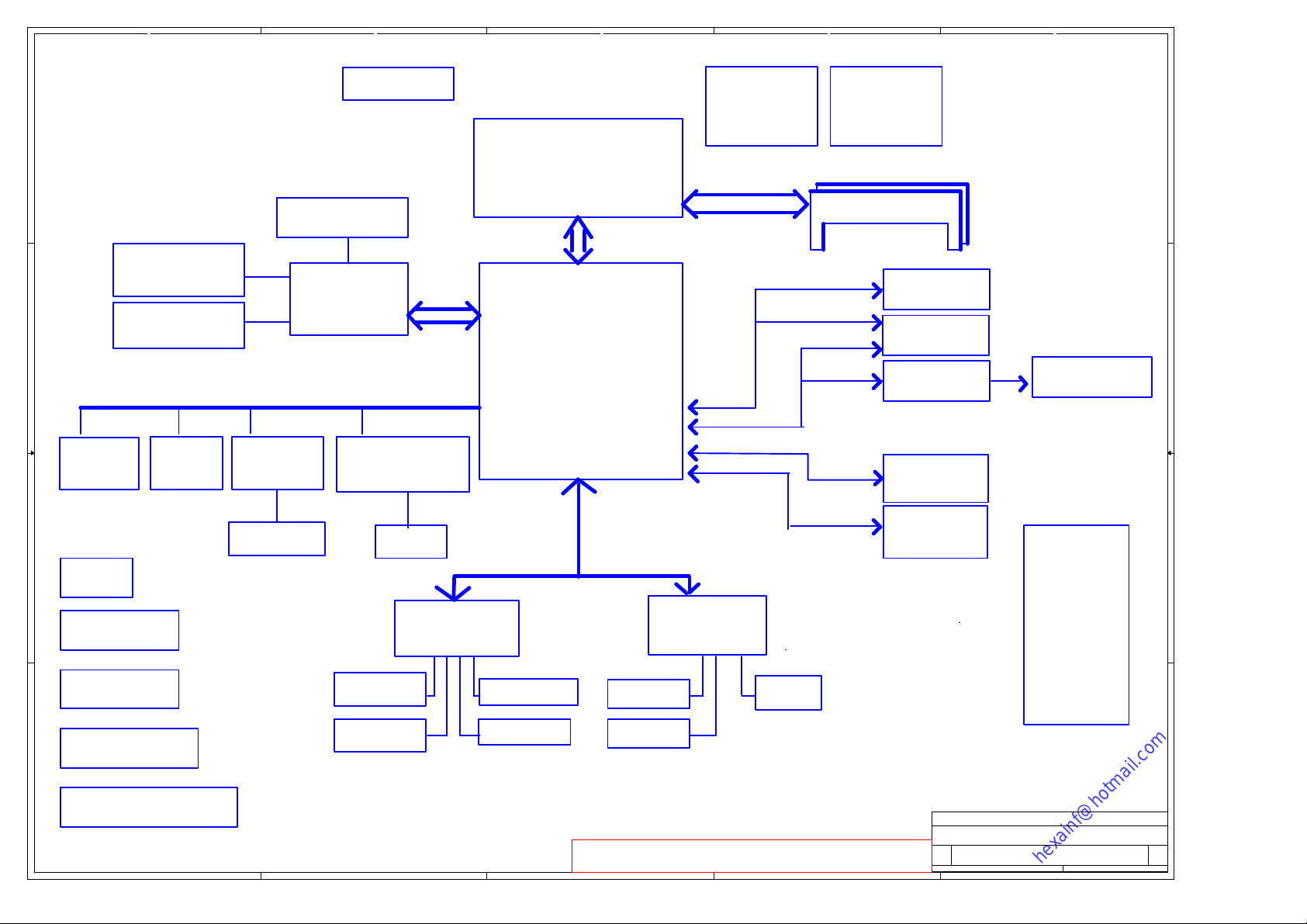

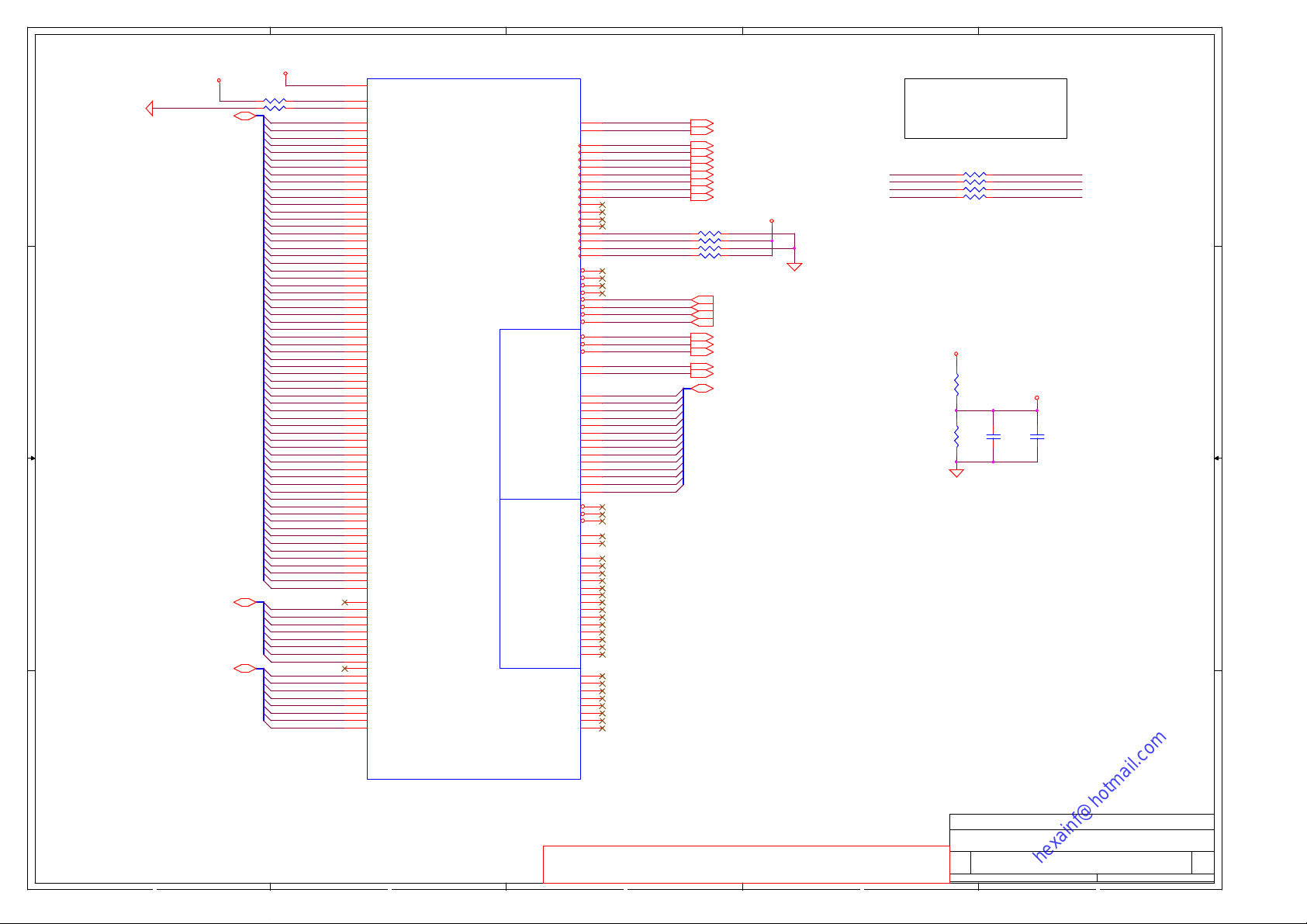

Page 2

A

hexainf@hotmail.com

B

C

D

E

Compal confidential

File Name : LA-1811

1 1

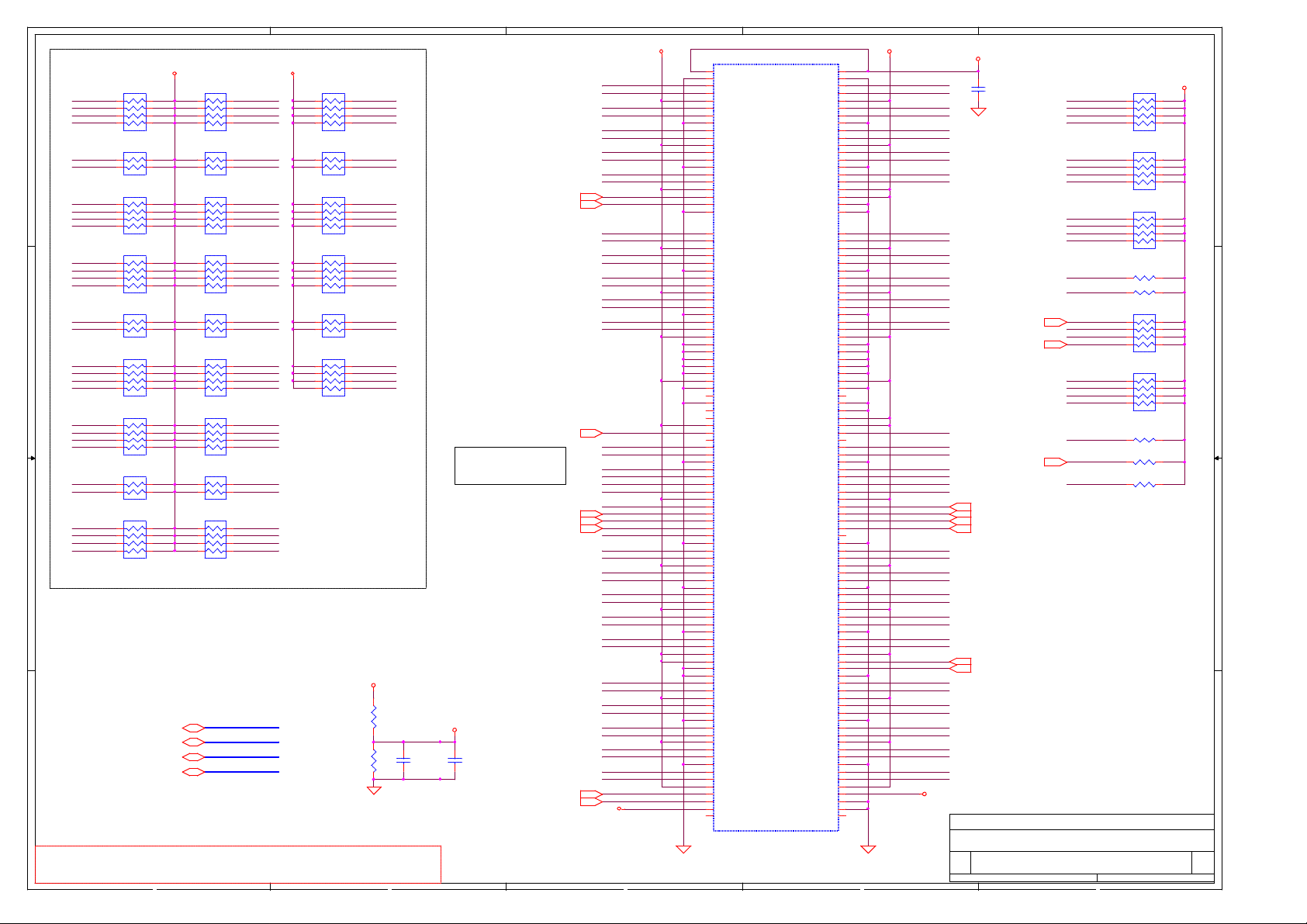

CRT Connector

TFT/HPA Panel

Interface

page 17

TV OUT

2 2

IDSEL:AD18

(PIRQC#,GNT#3,REQ#3)

IDSEL:AD16

(PIRQA#,GNT#0,REQ#0)

IEEE 1394

TSB43AB21A

page 21 page 22

3 3

Connector

page 18

Mini PCI

socket

page 28

3.3V 33 MHz

IDSEL:AD17

(PIRQB#,GNT#1,REQ#1)

LAN

RTL 8101L

page 20

RJ45/11 CONN

page 20

RTC CKT.

Power OK CKT.

page 36

Power On/Off CKT.

page 33

DC/DC Interface CKT.

4 4

page 37

Fan Control

page 18

page 4

nVIDIA

MAP17

page 14, 15, 16

PCI BUS

IDSEL:AD20

(PIRQA#/B#,GNT#2,REQ#2)

CardBus Controller

TI PCI1620

Slot 0/1

page 23

EC ENE

KB3910

Touch Pad

page 33

EC I/O Buffer

page 31

AMD K8

Claw Hammer Processor

nVIDIA

Crush K8

708 BGA

page 11, 12, 13

page 30

Int.KBD

page 33

BIOS

page 31

Thermal Sensor

MAX6649

Memory BUS(DDR)

page 4, 5, 6, 7

HT 16x16 800 MHZ

2.5V DDR- 200/266

AC-LINK

ATA-100

Primary IDE

Secondary IDE

ATA-100

LPC BUS

VIA 1211

Super I/O

page 29

PARALLEL FIR

FDD

page 32

page 4

USB2.0

page 33page 32

DDR-SO-DIMM X2

BANK 0, 1, 2, 3

page 8, 9,10

USB conn

MDC & BT Conn

Audio CKT

AD1981B

HDD

Connector

CDROM

Connector

page 27

page 27

page 25

page 19

page 19

AMP & Audio Jack

page 26

SPR CONN.

page 34

*RJ45 CONN

*PS2 x2 CONN

*CRT CONN

*LINE IN JACK

*LINE OUT JACK

*1394 CONN

*SPDIF CONN

*DVI CONN

*DC JACK

*TVOUT CONN

*PRINTER PORT

*COM PORT

*USB CONN x2

Power Circuit DC/DC

page 38, 39, 40, 41, 42, 43, 44

A

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Size Document Number Rev

Date: Sheet of

Compal Electronics, Inc.

LA-1851

Block Diagram

E

2 50Thursday, October 16, 2003

0.5

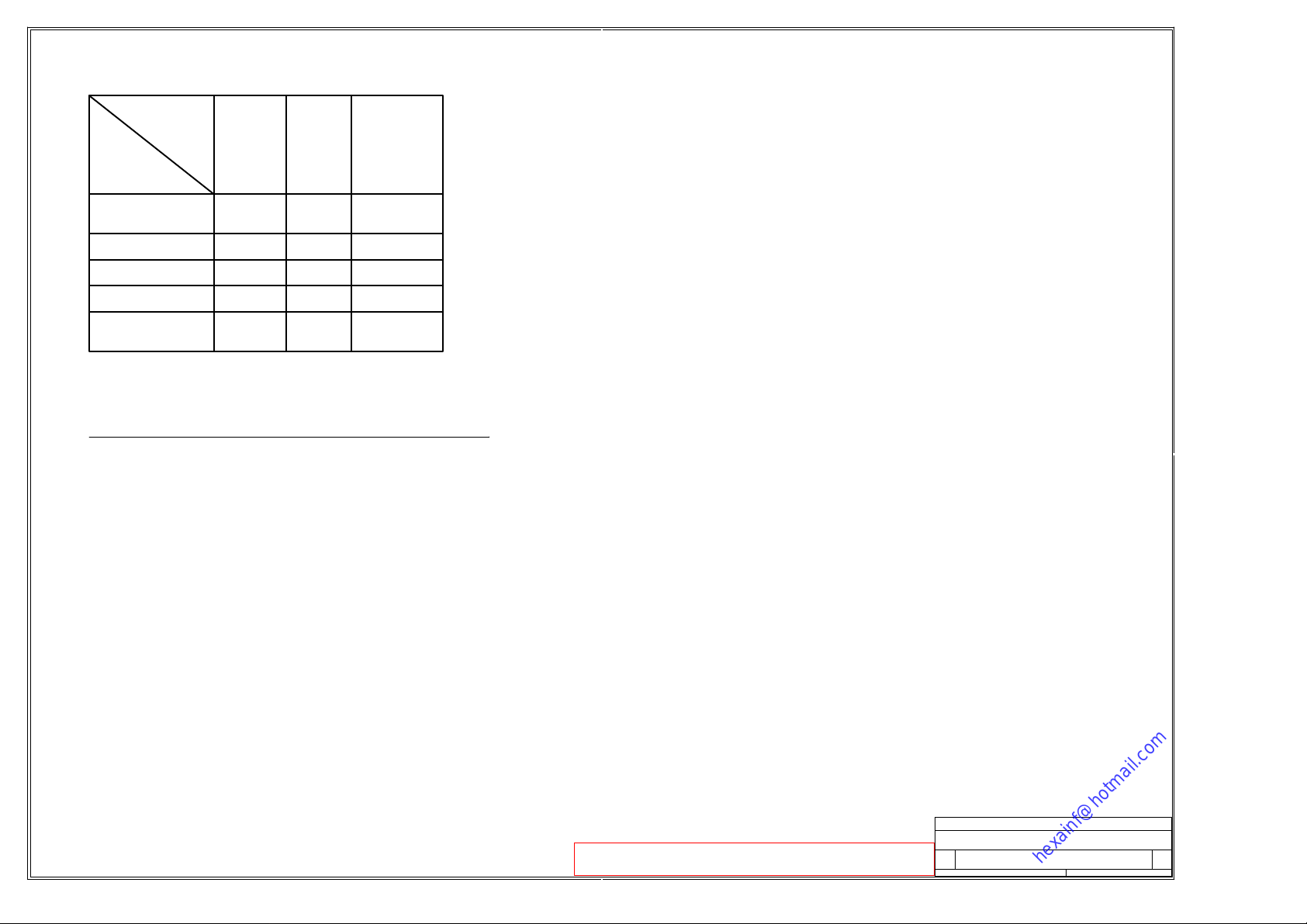

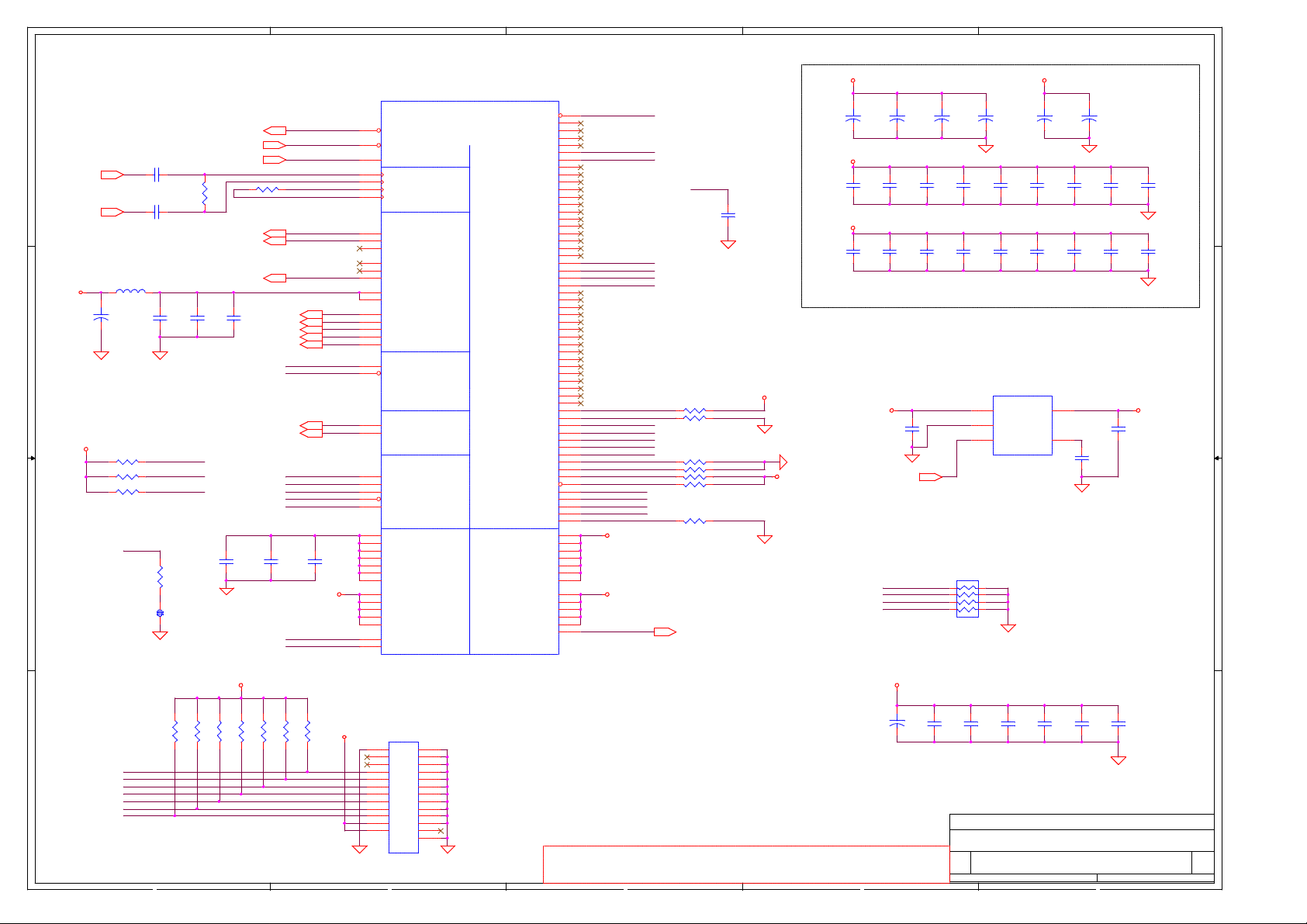

Page 3

Voltage Rails

hexainf@hotmail.com

A

power

plane

State

S0

S1

S3

S5 S4/AC

S5 S4/AC don't exist

O MEANS ON

X MEANS OFF

+1.2VALW

+3VALW

+5VALW

12VALW

O

O

O

O

X

+1.25V

+2.5V

+3V

+5V

O O

O O

O

X X

+1.2V_HT

+1.2VS

+1.5VS

+2.5VS

+3VS

+5VS

X

XX

PCI Devices

1 1

PCI Device ID

INTERNAL

USB 2.0

AC97 MODEM AD17 N/A

AC97

ATA 100

ETHERNET

LPC I/F AD12 N/A

SMBUS N/A

2

6

6

8

5 K

1

1

EXTERNAL

VGA AD16 E0 N/A

1394

LAN

CARD BUS

Wireless LAN

Mini-PCI (no use)

0

1

4

2

3

IDSEL # PIRQREQ/GNT #DEVICE

AD13

AD17

AD20

AD16

AD12

AD16

AD17

AD20

AD18

AD19

N/A

N/A

N/A

N/A

G

M

L

F

0

1

2

3

4

A

B

A, B

C

D

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

Size Document Number Rev

Date: Sheet of

Compal Electronics, Inc.

LA-1851

Notes List

0.5

3 50Thursday, October 16, 2003

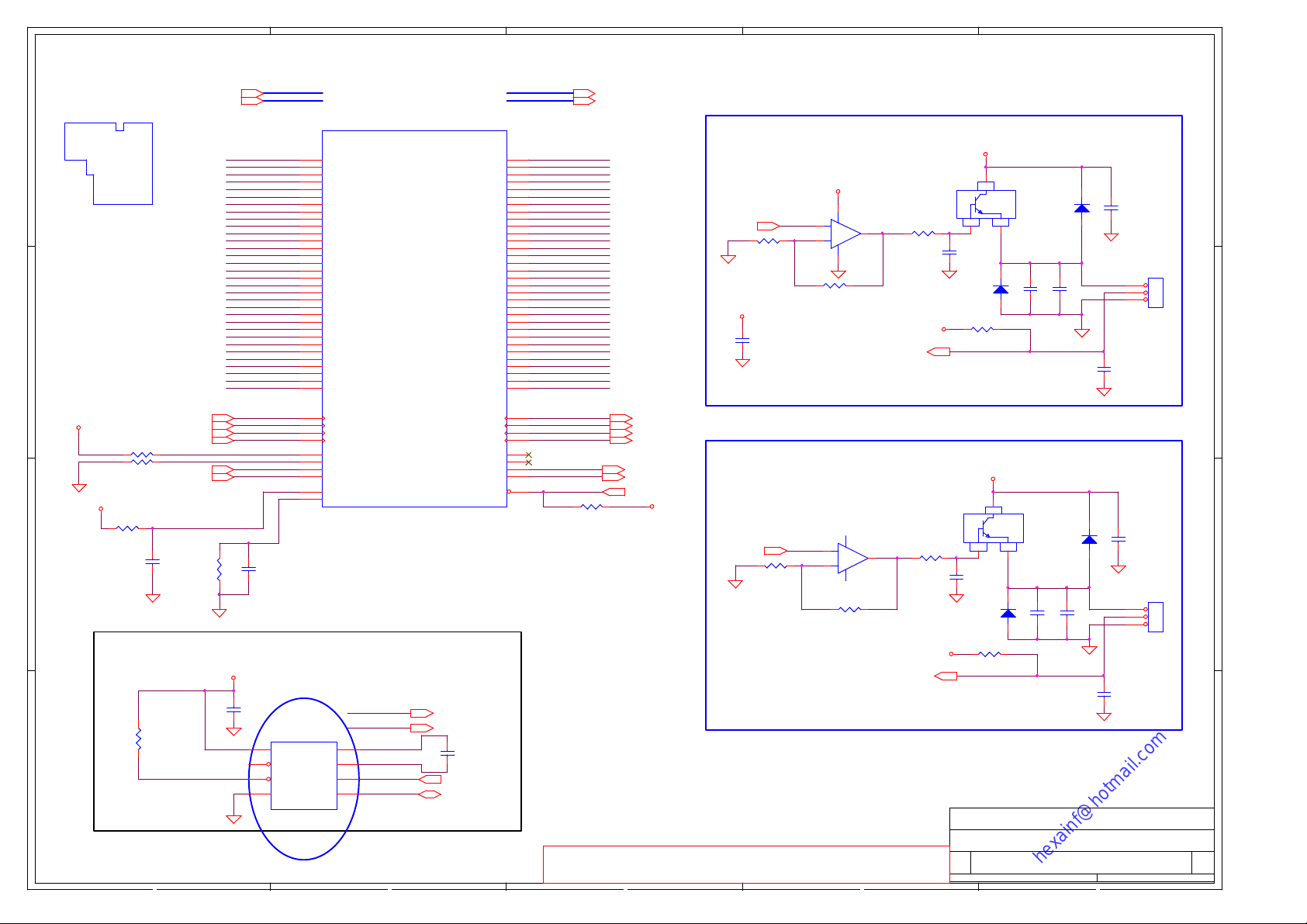

Page 4

A

hexainf@hotmail.com

B

C

D

E

H_CADIP15

H_CADIN15

H_CADIP14

H_CADIN14

H_CADIP13

H_CADIN13

H_CADIP12

H_CADIN12

H_CADIP11

H_CADIN11

H_CADIP10

H_CADIN10

H_CADIP9

H_CADIN9

H_CADIP8

H_CADIN8

H_CADIP7

H_CADIN7

H_CADIP6

H_CADIN6

H_CADIP5

H_CADIN5

H_CADIP4

H_CADIN4

H_CADIP3

H_CADIN3

H_CADIP2

H_CADIN2

H_CADIP1

H_CADIN1

H_CADIP0

H_CADIN0

H_CLKIP1

H_CLKIN1

H_CLKIP0

H_CLKIN0

H_CTLIP1

H_CTLIN1

H_CTLIP0

H_CTLIN0

LVREF0

1

C6

1000P_0402_50V7K

2

2

C610

0.1U_0402_16V4Z

1

1

6

4

5

H_CADIP[0..15]

H_CADIN[0..15]

T25

R25

U27

U26

V25

U25

W27

W26

AA27

AA26

AB25

AA25

AC27

AC26

AD25

AC25

T27

T28

V29

U29

V27

V28

Y29

W29

AB29

AA29

AB27

AB28

AD29

AC29

AD27

AD28

Y25

W25

Y27

Y28

R27

R26

T29

R29

AF27

AE26

U3

VDD1

ALERT#

THERM#

GND

SDATA

ADM1032AR_SOP8

U1A

Claw Hammer-DTR

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_REF1

L0_REF0

FOX_PZ75403-2941-42

Thermal Sensor

ADM1032

THERMDA_CPU

THERMDC_CPU

THERMDA_CPU

2

D+

THERMDC_CPU

3

D-

8

SCLK

7

B

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

HTT Interface

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

LDTSTOP_L

THERMDA_CPU <6>

THERMDC_CPU <6>

1

C611

2200P_0402_25V7K

2

EC_SMC_2 <30>

EC_SMD_2 <30>

H_CADIP[0..15]<11>

LA-1851

4 4

3 3

2 2

1 1

BDW00

LA-1452 REV 0

12

1

C5

2

12

R454

@10K_0402_5%

A

H_CLKIP1<11>

H_CLKIN1<11>

H_CLKIP0<11>

H_CLKIN0<11>

H_CTLIP0<11>

H_CTLIN0<11>

44.2_0603_1%

W=15mil

LVREF1

12

R10

+3VS

+1.2V_HT

R5 49.9_0402_1%

1 2

R6 49.9_0402_1%

1 2

+1.2V_HT +2.5VS

R8 44.2_0603_1%

1000P_0402_50V7K

H_CADOP[0..15]

H_CADON[0..15]

H_CADOP[0..15] <11>

H_CADON[0..15] <11>H_CADIN[0..15]<11>

Fan Control Circuit 1

H_CADOP15

N26

H_CADON15

N27

H_CADOP14

L25

H_CADON14

M25

H_CADOP13

L26

H_CADON13

L27

H_CADOP12

J25

H_CADON12

K25

H_CADOP11

G25

H_CADON11

H25

H_CADOP10

G26

H_CADON10

G27

H_CADOP9

E25

H_CADON9

F25

H_CADOP8

E26

H_CADON8

E27

H_CADOP7

N29

H_CADON7

P29

H_CADOP6

M28

H_CADON6

M27

H_CADOP5

L29

H_CADON5

M29

H_CADOP4

K28

H_CADON4

K27

H_CADOP3

H28

H_CADON3

H27

H_CADOP2

G29

H_CADON2

H29

H_CADOP1

F28

H_CADON1

F27

H_CADOP0

E29

H_CADON0

F29

H_CLKOP1

J26

H_CLKON1

J27

H_CLKOP0

J29

H_CLKON0

K29

N25

P25

H_CTLOP0

P28

H_CTLON0

P27

LDTSTOP#

AJ27

1 2

R7 1K_0402_5%

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

H_CLKOP1 <11>

H_CLKON1 <11>

H_CLKOP0 <11>

H_CLKON0 <11>

H_CTLOP0 <11>

H_CTLON0 <11>

LDTSTOP# <11>

C

EN_FAN1<30>

EN_FAN2<30>

EN_FAN1

R2

10K_0402_5%

+12VALW

C775

0.1U_0402_25V4K

Fan Control Circuit 2

R11

10K_0402_5%

12

EN_FAN2

12

+12VALW

3

+IN

2

-IN

1 2

R3

5

6

1 2

R12

+IN

-IN

8

P

OUT

U2A

G

LM358A_SO8

4

8.2K_0402_5%

U2B

OUT

LM358A_SO8

8.2K_0402_5%

D

FAN1_ON

1

FAN_SPEED1<30>

FAN2_ON

7

FAN_SPEED2<30>

FMMT619_SOT23

R1

1 2

100_0402_5%

+3VS

FMMT619_SOT23

R9

1 2

100_0402_5%

+3VS

+5VS

1

Q1

1N4148_SOT23

B

2

2

C2

0.1U_0402_16V4Z

1

D2

R4

1 2

10K_0402_5%

+5VS

Q2

B

2

2

C7

0.1U_0402_16V4Z

1

1N4148_SOT23

R13

1 2

10K_0402_5%

C

3

12

1

C

D4

@1SS355_SOD323

E

FAN1

1

C3

2

0.1U_0402_16V4Z

E

@1SS355_SOD323

3

FAN2

12

1

C8

2

10U_1206_10V4Z

12

D1

1

C612

100P_0402_50V8K

2

12

D3

1

C614

0.1U_0402_16V4Z

2

1

C1

10U_1206_10V4Z

2

ACES_85205-0300

1

C613

1000P_0402_50V7K

2

1

C4

10U_1206_10V4Z

2

ACES_85205-0300

1

C615

1000P_0402_50V7K

2

JP1

1

2

3

JP2

1

2

3

Compal Electronics, Inc.

Title

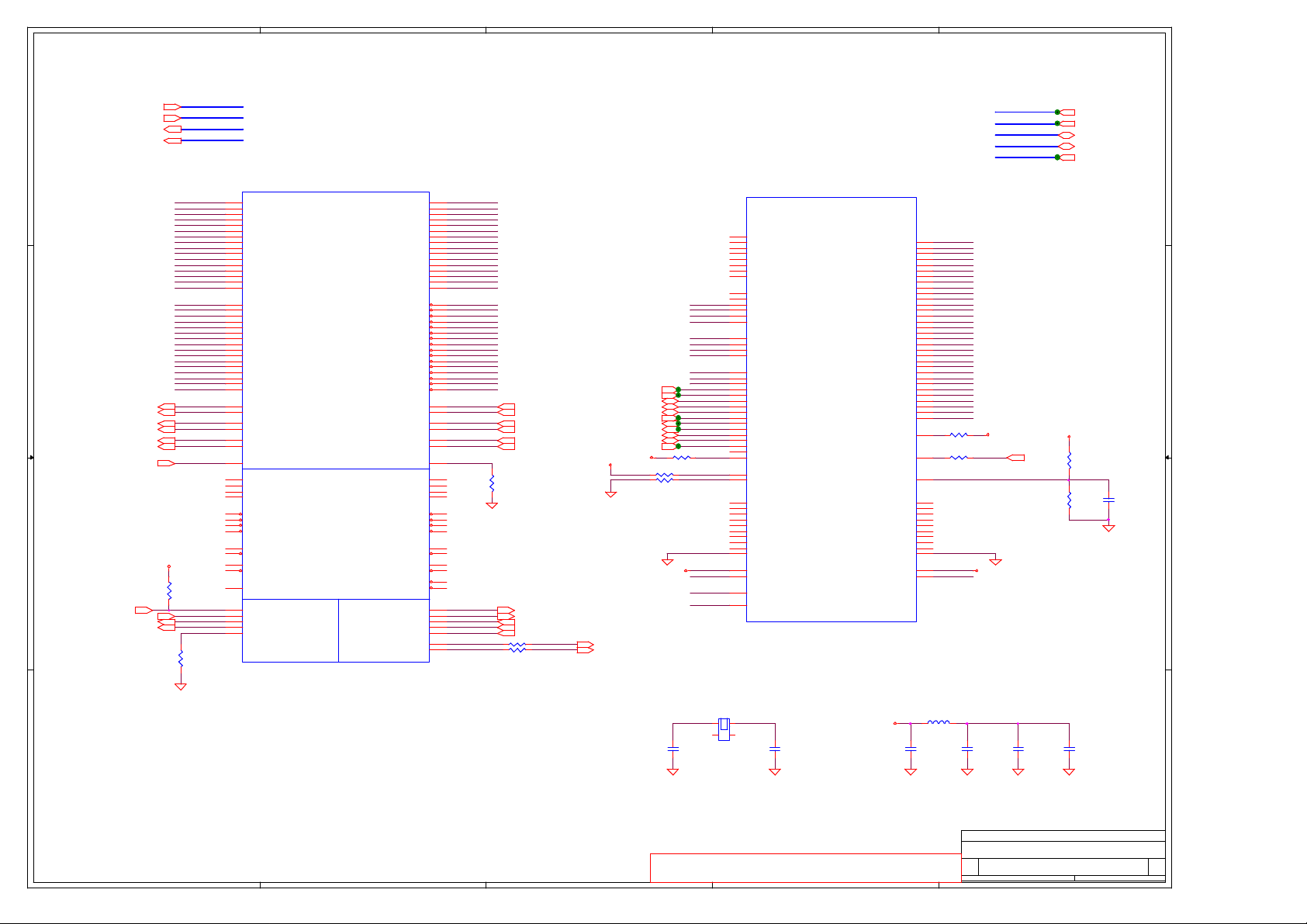

Claw Harmmer CPU (Host Bus)

Size Document Number Rev

Custom

LA-1851

Date: Sheet of

4 50Thursday, October 16, 2003

E

0.5

Page 5

A

hexainf@hotmail.com

B

C

D

E

+2.5V

DDR_SDQ[0..63]<8>

1 1

2 2

3 3

DDR_SDM[0..7]<8>

DDR_SDQS[0..7]<8>

+1.25VREF_CPU

50 mil width

12

12

DDR_SDQ63

DDR_SDQ62

DDR_SDQ61

DDR_SDQ60

DDR_SDQ59

DDR_SDQ58

DDR_SDQ57

DDR_SDQ56

DDR_SDQ55

DDR_SDQ54

DDR_SDQ53

DDR_SDQ52

DDR_SDQ51

DDR_SDQ50

DDR_SDQ49

DDR_SDQ48

DDR_SDQ47

DDR_SDQ46

DDR_SDQ45

DDR_SDQ44

DDR_SDQ43

DDR_SDQ42

DDR_SDQ41

DDR_SDQ40

DDR_SDQ39

DDR_SDQ38

DDR_SDQ37

DDR_SDQ36

DDR_SDQ35

DDR_SDQ34

DDR_SDQ33

DDR_SDQ32

DDR_SDQ31

DDR_SDQ30

DDR_SDQ29

DDR_SDQ28

DDR_SDQ27

DDR_SDQ26

DDR_SDQ25

DDR_SDQ24

DDR_SDQ23

DDR_SDQ22

DDR_SDQ21

DDR_SDQ20

DDR_SDQ19

DDR_SDQ18

DDR_SDQ17

DDR_SDQ16

DDR_SDQ15

DDR_SDQ14

DDR_SDQ13

DDR_SDQ12

DDR_SDQ11

DDR_SDQ10

DDR_SDQ9

DDR_SDQ8

DDR_SDQ7

DDR_SDQ6

DDR_SDQ5

DDR_SDQ4

DDR_SDQ3

DDR_SDQ2

DDR_SDQ1

DDR_SDQ0

DDR_SDM7

DDR_SDM6

DDR_SDM5

DDR_SDM4

DDR_SDM3

DDR_SDM2

DDR_SDM1

DDR_SDM0

DDR_SDQS7

DDR_SDQS6

DDR_SDQS5

DDR_SDQS4

DDR_SDQS3

DDR_SDQS2

DDR_SDQS1

DDR_SDQS0

U1B

AG12

AC1

AC3

AC2

AD1

AG3

AH3

AH9

AG5

AH5

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

AG1

AH7

AH13

AJ13

D14

C14

A16

B15

A12

B11

A17

A15

C13

A11

A10

C11

AE1

AE3

AJ4

AE2

AF1

AJ3

AJ5

AJ6

AJ7

AJ9

A13

AA1

A14

AB1

AJ2

AJ8

B9

C7

A6

A9

A5

B5

C5

A4

E2

E1

A3

B3

E3

F1

G2

G1

L3

L1

G3

J2

L2

M1

W1

W3

W2

Y1

R1

A7

C2

H1

T1

A8

D1

J1

MEMVREF1

MEMZN

MEMZP

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDQS17

MEMDQS16

MEMDQS15

MEMDQS14

MEMDQS13

MEMDQS12

MEMDQS11

MEMDQS10

MEMDQS9

MEMDQS8

MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0

Claw Hammer-DTR

DDR Memory

A CHANGEL ADDRESSB CHANGEL ADDRESS

MEMADDB_B13

MEMADDB_B12

MEMADDB_B11

MEMADDB_B10

MEMCKEA

MEMCKEB

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

MEMADDB_B9

MEMADDB_B8

MEMADDB_B7

MEMADDB_B6

MEMADDB_B5

MEMADDB_B4

MEMADDB_B3

MEMADDB_B2

MEMADDB_B1

MEMADDB_B0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

DDR_CKE0

DDR_CKE1

DDR_CLK7

DDR_CLK7#

DDR_CLK6

DDR_CLK6#

DDR_CLK5

DDR_CLK5#

DDR_CLK4

DDR_CLK4#

DDR_CLK1

DDR_CLK1#

DDR_CLK0

DDR_CLK0#

DDR_SCS#3

DDR_SCS#2

DDR_SCS#1

DDR_SCS#0

DDR_SMAA13

DDR_SMAA12

DDR_SMAA11

DDR_SMAA10

DDR_SMAA9

DDR_SMAA8

DDR_SMAA7

DDR_SMAA6

DDR_SMAA5

DDR_SMAA4

DDR_SMAA3

DDR_SMAA2

DDR_SMAA1

DDR_SMAA0

DDR_CKE0 <8>

DDR_CKE1 <8>

DDR_CLK7 <8>

DDR_CLK7# <8>

DDR_CLK6 <9>

DDR_CLK6# <9>

DDR_CLK5 <8>

DDR_CLK5# <8>

DDR_CLK4 <9>

DDR_CLK4# <9>

R22 10K_0402_5%

1 2

R23 10K_0402_5%

R24 10K_0402_5%

R25 10K_0402_5%

1 2

1 2

1 2

DDR_SCS#3 <9>

DDR_SCS#2 <9>

DDR_SCS#1 <8,9>

DDR_SCS#0 <8,9>

DDR_SRASA# <8,9>

DDR_SCASA# <8,9>

DDR_SWEA# <8,9>

DDR_SBSA1 <8,9>

DDR_SBSA0 <8,9>

DDR_SMAA[0..13] <8,9>

+2.5V

MEMZN

R1634.8_0603_1%

MEMZP

R1734.8_0603_1%

DDR_CLK5/5# & DDR_CLK7/7#

route to nearest DIMM

DDR_CLK4/4# & DDR_CLK6/6#

route to farthest DIMM

R18 120_0402_5%

DDR_CLK6

DDR_CLK5

DDR_CLK4

1 2

R19 120_0402_5%

1 2

R20 120_0402_5%

1 2

R21 120_0402_5%

1 2

within 1.00"

+2.5V

12

R26

100_0402_1%

12

R27

100_0402_1%

1

2

0.1U_0402_10V6K

+1.25VREF_CPU

C11

DDR_CLK7#DDR_CLK7

DDR_CLK6#

DDR_CLK5#

DDR_CLK4#

1

C12

1000P_0402_50V7K

2

4 4

A

FOX_PZ75403-2941-42

B

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Compal Electronics, Inc.

Title

Claw Harmmer (MEMORY BUS)

Size Document Number Rev

Custom

LA-1851

Date: Sheet of

5 50Thursday, October 16, 2003

E

0.5

Page 6

A

B

C

D

E

+1.25V

U1C

1 1

CPU_CLK<11>

CPU_CLK#<11>

Place 169 Ohm within 0.5" from CPU

Route as DIF 5/5/5/20

+2.5VDDA

2 2

+2.5VS

3 3

4 4

C20

3900P_0402_50V7K

169_0402_1%

C30 3900P_0402_50V7K

L1

LQG21F4R7N00_0805

1 2

1

+

C40

100U_D2_10VM

2

4.7U_0805_6.3V6K

H_THERMTRIP#

12

R37 1K_0402_5%

R38 330_0402_5%

R39 330_0402_5%

@100_0402_5%

R563

JOPEN

H_RST#

DBREQ#

DBRDY

TCK

TMS

TDI

TRST#

TDO

H_RST#

12

H_PWRGD

12

J3

R40

@560_0402_5%

A

H_THERMTRIP#<11>

12

12

R28

12

Route as DIFF pair 10/5/10

VDDIO_SENSE

3300P_0402_50V7K

1

1

C41

C42

2

2

0.22U_0603_10V7K

0.22U_0603_10V7K

1 2

@560_0402_5%

R41

12

12

@

@

R42

@560_0402_5%

@

H_RST#<11>

H_PWRGD<11>

R29 80.6_0402_1%

Place within 0.5" from CPU

Route as 80 Ohm DIFF impedence 8/5/20

COREFB<44>

COREFB#<44>

+VDDA

1

C43

2

THERMDA_CPU<4>

THERMDC_CPU<4>

1

C63

2

0.22U_0603_10V7K

+2.5VS

@560_0402_5%

12

12

R43

@560_0402_5%

@

H_THERMTRIP#

H_RST#

H_PWRGD

CLKIN

CLKIN#

FBCLKOUT

12

FBCLKOUT#

COREFB

COREFB#

VDDIO_SENSE

50 mils width

VID4<44>

VID3<44>

VID2<44>

VID1<44>

VID0<44>

DBRDY

DBREQ#

TDO

TMS

TCK

TRST# SCANCLK2

TDI

4.7U_0805_6.3V6K

1

1

C64

2

2

+1.25V +1.25V

TP_K8_A28

TP_K8_AJ28

R44

12

12

@

@

R45

@560_0402_5%

R46

12

@560_0402_5%

VID4

VID3

VID2

VID1

VID0

C68

+2.5VS

@

A20

AF20

AE18

AJ21

AH21

AH19

AJ19

A23

A24

B23

AE12

AF12

AE11

AH25

AJ25

AG13

AF14

AG14

AF15

AE15

AH17

AE19

A26

A27

A22

E20

E17

B21

A21

D29

D27

D25

C28

C26

B29

B27

D17

A18

B17

C17

C16

A28

AJ28

@SAMTEC_ASP-68200-07

Claw Hammer-DTR

THERMTRIP_L

RESET_L

PWROK

CLKIN_H

CLKIN_L

FBCLKOUT_H

FBCLKOUT_L

COREFB_H

COREFB_L

CORE_SENSE

VDDIOFB_H

VDDIOFB_L

VDDIO_SENSE

VDDA1

VDDA2

VID4

VID3

VID2

VID1

VID0

DBRDY

DBREQ_L

THERMDA

THERMDC

TDO

TMS

TCK

TRST_L

TDI

VLDT0_A

VLDT0_A

VLDT0_A

VLDT0_A

VLDT0_A

VLDT0_A

VLDT0_A

VTT_A

VTT_A

VTT_A

VTT_A

VTT_A

KEY1

KEY0

FOX_PZ75403-2941-42

Clock

Debug

JTAG

JP3

2

1

4

3

6

5

8

7

10

9

12

11

14

13

16

15

18

17

20

19

22

21

2423

26

@

B

Miscellaneous

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

VLDT0_B

VTT_B

VTT_B

VTT_B

VTT_B

VTT_B

VTT_SENSE

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

TP_M_RESET#

AG10

E14

D12

E13

C12

TP_K8_D22

D22

TP_K8_C22

C22

B13

B7

C3

K1

R2

AA3

F3

C23

AG7

AE22

C24

A25

C9

CLAW_ANALOG3

AE23

CLAW_ANALOG2

AF23

CLAW_ANALOG1

AF22

CLAW_ANALOG0

AF21

C1

J3

R3

AA2

D3

AG2

B18

AH1

AE21

C20

AG4

C6

AG6

AE9

AG9

AF18

BPSCLK

AJ23

BPSCLK#

AH23

TP_K8_AE24

AE24

TP_K8_AF24

AF24

TP_K8_C15

C15

TP_CPU_BP3

AG18

TP_CPU_BP2

AH18

BP1

AG17

BP0

AJ18

SINCHN

C18

BRN#

A19

SCANCLK1

D20

C21

SCANEN

D18

SCANSHENB

C19

SCANSHENA

B19

AH29

AH27

AG28

AG26

AF29

AE28

AF25

AG15

AF16

AG16

AH16

AJ17

AE13

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

+1.2V_HT

VTT_SENSE

C

H_PWRGD

1

C793

470P_0402_50V7K

R30 820_0402_5%

1 2

R31 820_0402_5%

1 2

R32 680_0402_5%

1 2

R33 680_0402_5%

1 2

R34 680_0402_5%

1 2

R35 680_0402_5%

1 2

R36 680_0402_5%

1 2

VTT_SENSE

2

+2.5V

+2.5VS

470U_D2_2.5VM

1

1

+

+

C13

C14

2

470U_D2_2.5VM

+1.25V

4.7U_0805_6.3V6K

+1.25V

0.22U_0603_10V7K

2

4.7U_0805_6.3V6K

1

1

C22

C21

2

2

1

C31

2

1U_0603_10V6K

D

4.7U_0805_6.3V6K

0.22U_0603_10V7K

1

C32

2

0.22U_0603_10V7K

+3VS +2.5VDDA

1

C734

2

VR_ON<11,44>

SCANCLK2

SCANCLK1

SCANEN

SCANSHENB

+1.2V_HT

0.22U_0603_10V7K

250 mil

1

+

C59

2

100U_D2_10VM

@220U_D2_2.5VM

1

1

+

+

C15

2

4.7U_0805_6.3V6K

1

C24

2

0.22U_0603_10V7K

1

C34

2

2

4.7U_0805_6.3V6K

0.22U_0603_10V7K

330U_D_2VM_R15

1

C23

2

1

C33

2

1

2

3

RP1

4 5

3 6

2 7

1 8

680_1206_8P4R_5%

1

1

C61

C60

2

2

0.22U_0603_10V7K

Compal Electronics, Inc.

Title

ClawHarmmer ( MISC )

Size Document Number Rev

Custom

LA-1851

Date: Sheet of

+1.25V

C16

100U_D2_10VM

4.7U_0805_6.3V6K

1

C25

2

0.22U_0603_10V7K

1

C35

2

U39

VIN

VOUT

GND

SD#

SI9183_SOT23-5

0.22U_0603_10V7K

1

C62

2

0.22U_0603_10V7K

1

+

C17

2

1

C26

2

4.7U_0805_6.3V6K

1

C36

2

0.22U_0603_10V7K

5

4

BP

1

C65

2

Near SocketNear Power Supply

100U_D2_10VM

1

+

C18

2

4.7U_0805_6.3V6K

1

C27

2

0.22U_0603_10V7K

1

C37

2

1

C736

0.01U_0402_16V7K

2

0.22U_0603_10V7K

1

C66

2

0.22U_0603_10V7K

E

1

C28

2

4.7U_0805_6.3V6K

1

C38

2

0.22U_0603_10V7K

1

C735

1U_0603_10V6K

2

1

C67

2

6 50Thursday, October 16, 2003

1

C29

2

1

C39

2

0.5

Page 7

A

AH20

AB21

+CPU_CORE +2.5V

U1D

L7

VDD

AC15

VDD

H18

VDD

B20

VDD

E21

1 1

2 2

3 3

4 4

VDD

H22

VDD

J23

VDD

H24

VDD

F26

VDD

N7

VDD

L9

VDD

V10

VDD

G13

VDD

K14

VDD

Y14

VDD

AB14

VDD

G15

VDD

J15

VDD

AA15

VDD

H16

VDD

K16

VDD

Y16

VDD

AB16

VDD

G17

VDD

J17

VDD

AA17

VDD

AC17

VDD

AE17

VDD

F18

VDD

K18

VDD

Y18

VDD

AB18

VDD

AD18

VDD

AG19

VDD

E19

VDD

G19

VDD

AC19

VDD

AA19

VDD

J19

VDD

F20

VDD

H20

VDD

K20

VDD

M20

VDD

P20

VDD

T20

VDD

V20

VDD

Y20

VDD

AB20

VDD

AD20

VDD

G21

VDD

J21

VDD

L21

VDD

N21

VDD

R21

VDD

U21

VDD

W21

VDD

AA21

VDD

AC21

VDD

F22

VDD

K22

VDD

M22

VDD

P22

VDD

T22

VDD

V22

VDD

Y22

VDD

AB22

VDD

AD22

VDD

E23

VDD

G23

VDD

L23

VDD

N23

VDD

R23

VDD

U23

VDD

W23

VDD

AA23

VDD

AC23

VDD

B24

VDD

D24

VDD

F24

VDD

K24

VDD

M24

VDD

P24

VDD

T24

VDD

V24

VDD

Y24

VDD

AB24

VDD

AD24

VDD

AH24

VDD

AE25

VDD

K26

VDD

P26

VDD

V26

VDD

FOX_PZ75403-2941-42

POWER

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

N28

U28

AA28

AE27

R7

U7

W7

K8

M8

P8

T8

V8

Y8

J9

N9

R9

U9

W9

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

+CPU_CORE

W22

M23

AG25

AG27

AF2

AA8

AB9

AA10

Y15

AE16

G20

R20

U20

W20

AA20

AC20

AE20

AG20

AJ20

D21

H21

M21

Y21

AD21

AG21

G22

N22

R22

U22

AG29

AA22

AC22

AG22

AH22

AJ22

D23

H23

Y23

AB23

AD23

AG23

G24

N24

R24

U24

W24

AA24

AC24

AG24

AJ24

C25

D26

H26

M26

Y26

AD26

AF26

AH26

C27

D28

G28

H15

AB17

AD17

G18

AA18

AC18

D19

H19

Y19

AB19

AD19

AF19

N20

A

U1E

B2

VSS

VSS

VSS

VSS

VSS

L24

VSS

VSS

VSS

D2

VSS

VSS

W6

VSS

Y7

VSS

VSS

VSS

VSS

J12

VSS

B14

VSS

VSS

VSS

J18

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F21

VSS

VSS

K21

VSS

VSS

P21

VSS

T21

VSS

V21

VSS

VSS

VSS

VSS

B22

VSS

E22

VSS

VSS

J22

VSS

L22

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F23

VSS

VSS

K23

VSS

P23

VSS

T23

VSS

V23

VSS

VSS

VSS

VSS

VSS

E24

VSS

VSS

J24

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B25

VSS

VSS

B26

VSS

VSS

VSS

VSS

T26

VSS

VSS

VSS

VSS

VSS

VSS

B28

VSS

VSS

VSS

F15

VSS

VSS

VSS

VSS

B16

VSS

VSS

VSS

VSS

VSS

F19

VSS

VSS

K19

VSS

VSS

VSS

VSS

VSS

J20

VSS

L20

VSS

VSS

FOX_PZ75403-2941-42

B

L28

VSS

R28

VSS

W28

VSS

AC28

VSS

AF28

VSS

AH28

VSS

C29

VSS

F2

VSS

H2

VSS

K2

VSS

M2

VSS

P2

VSS

T2

VSS

V2

VSS

Y2

VSS

AB2

VSS

AD2

VSS

AH2

VSS

B4

VSS

AH4

VSS

B6

VSS

G6

VSS

J6

VSS

L6

VSS

N6

VSS

R6

VSS

U6

VSS

AA6

VSS

AC6

VSS

AH6

VSS

F7

VSS

H7

VSS

K7

VSS

M7

VSS

P7

VSS

T7

VSS

V7

VSS

AB7

VSS

AD7

VSS

B8

VSS

G8

VSS

J8

VSS

L8

VSS

N8

VSS

R8

VSS

U8

VSS

W8

VSS

AC8

VSS

AH8

VSS

F9

VSS

H9

VSS

K9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

M9

P9

T9

V9

Y9

AD9

B10

G10

J10

L10

N10

R10

U10

W10

AC10

AH10

F11

H11

K11

Y11

AB11

AD11

B12

G12

AA12

AC12

AH12

F13

H13

K13

Y13

AB13

AD13

AF17

G14

J14

AA14

AC14

AE14

D16

E15

K15

AB15

AD15

AH14

E16

G16

J16

AA16

AC16

AE29

AJ26

E18

F17

H17

K17

Y17

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

POWER

B

C

+CPU_CORE

330U_D_2VM_R15

1

1

+

+

C69

2

330U_D_2VM_R15

+CPU_CORE

1

+

2

@330U_D_2VM_R15

+CPU_CORE

1

C89

2

10U_1206_6.3V7K

4 in Socket Cavity,

2 on backside under Socket

+CPU_CORE

1

C97

2

4.7U_0805_6.3V6K

2

@330U_D_2VM_R15

1

+

C79

2

10U_1206_6.3V7K

1

C90

2

4.7U_0805_6.3V6K

1

C98

2

C70

330U_D_2VM_R15

C80

330U_D_2VM_R15

1

C91

2

10U_1206_6.3V7K

1

C99

2

4.7U_0805_6.3V6K

CPU Decouping Capacitor

4.7U_0805_6.3V6K

C

330U_D_2VM_R15

1

+

C71

2

@330U_D_2VM_R15

1

+

C81

2

10U_1206_6.3V7K

1

C92

2

4.7U_0805_6.3V6K

1

C100

2

4.7U_0805_6.3V6K

1

C111

2

1

+

C72

2

330U_D_2VM_R15

1

+

C82

2

@330U_D_2VM_R15

1

C93

2

10U_1206_6.3V7K

1

C101

2

4.7U_0805_6.3V6K

1

C112

2

D

330U_D_2VM_R15

1

+

C73

2

@330U_D_2VM_R15

1

+

C83

2

10U_1206_6.3V7K

1

C94

2

4.7U_0805_6.3V6K

1

C102

2

4.7U_0805_6.3V6K

D

1

+

C74

2

@330U_D_2VM_R15

1

+

C84

2

@330U_D_2VM_R15

+CPU_CORE

1

C103

2

+2.5V+2.5V

0.22U_0603_10V7K

1

C113

2

0.22U_0603_10V7K

Near Socket

E

330U_D_2VM_R15

1

+

C76

2

@330U_D_2VM_R15

1

+

C85

2

+CPU_CORE

1

C95

1000P_0402_50V7K

2

0.22U_0603_10V7K

1

C104

2

0.22U_0603_10V7K

Loop Bandwidth

KHz

* 300 3300

1

C114

2

0.22U_0603_10V7K

Title

Size Document Number Rev

Custom

Date: Sheet of

1

1

2

1

2

In Socket CavityClose to Socket

20

50

+

C77

@330U_D_2VM_R15

+

C86

@330U_D_2VM_R15

1

C105

2

0.22U_0603_10V7K

+

C78

2

1

+

C87

2

1

C110

0.1U_0402_10V6K

2

0.22U_0603_10V7K

1

1

C106

C107

2

2

Bulk Cappacitance

uF

23000

9000

0.22U_0603_10V7K

1

C108

2

0.22U_0603_10V7K

1

C109

2

Total

ESR

2.5m ohm

(AMD)

0.9m ohm

1.5m ohm

1

C115

2

0.22U_0603_10V7K

1

C116

2

0.22U_0603_10V7K

1

C117

2

0.22U_0603_10V7K

1

C118

2

Compal Electronics, Inc.

Claw Harmmer (Power & Ground)

LA-1851

7 50Thursday, October 16, 2003

E

0.5

Page 8

A

A

RP2

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP4

1 4

2 3

10_0404_4P2R_5%

RP6

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP8

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP10

1 4

2 3

10_0404_4P2R_5%

RP12

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP14

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP16

1 4

2 3

10_0404_4P2R_5%

RP18

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP20

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP22

1 4

2 3

10_0404_4P2R_5%

RP24

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

DDR_SDQS[0..7]

DDR_SDQ[0..63]

DDR_SDM[0..7]

DDR_SMAA[0..13]

DDR_DQ1

DDR_DQ5

DDR_DQ4

DDR_DQ0

DDR_DQS0

DDR_DQ6

DDR_DQ3

DDR_DQ2

DDR_DQ13

DDR_DQ9

DDR_DQ8

DDR_DQ12

DDR_DQS1

DDR_DM1

DDR_DQ15

DDR_DQ11

DDR_DQ10

DDR_DQ19

DDR_DQ20

DDR_DQ21

DDR_DQ17

DDR_DQS2

DDR_DM2

DDR_DQ22

DDR_DQ16

DDR_DQ23

DDR_DQ28

DDR_DQ24

DDR_DQ25

DDR_DQ29

DDR_DQS3

DDR_DM3

DDR_DQ30

DDR_DQ31

DDR_DQ27

DDR_SDQ1

DDR_SDQ5

DDR_SDQ4

DDR_SDQ0

DDR_SDQS0

1 1

2 2

3 3

4 4

DDR_SDM0 DDR_DM0

DDR_SDQ6

DDR_SDQ3

DDR_SDQ7 DDR_DQ7

DDR_SDQ2

DDR_SDQ13

DDR_SDQ9

DDR_SDQ8

DDR_SDQ12

DDR_SDQS1

DDR_SDM1

DDR_SDQ15

DDR_SDQ14 DDR_DQ14

DDR_SDQ11

DDR_SDQ10

DDR_SDQ19

DDR_SDQ20

DDR_SDQ21

DDR_SDQ17

DDR_SDQS2

DDR_SDM2

DDR_SDQ22

DDR_SDQ18 DDR_DQ18

DDR_SDQ16

DDR_SDQ23

DDR_SDQ28

DDR_SDQ24

DDR_SDQ25

DDR_SDQ29

DDR_SDQS3

DDR_SDM3

DDR_SDQ30

DDR_SDQ26 DDR_DQ26

DDR_SDQ31

DDR_SDQ27

DDR_SDQS[0..7]<5>

DDR_SDQ[0..63]<5>

DDR_SDM[0..7]<5>

DDR_SMAA[0..13]<5,9>

B

DDR_SDQ37

DDR_SDQ32

DDR_SDQ36

DDR_SDQ33

DDR_SDQS4

DDR_SDM4

DDR_SDQ38

DDR_SDQ34 DDR_DQ34

DDR_SDQ35

DDR_SDQ39

DDR_SDQ44

DDR_SDQ40

DDR_SDQ41

DDR_SDQ45

DDR_SDQS5

DDR_SDM5

DDR_SDQ46

DDR_SDQ42 DDR_DQ42

DDR_SDQ47

DDR_SDQ43

DDR_SDQ49

DDR_SDQ48

DDR_SDQ53

DDR_SDQ52

DDR_SDQS6

DDR_SDM6

DDR_SDQ55

DDR_SDQ54 DDR_DQ54

DDR_SDQ50

DDR_SDQ51

DDR_SDQ56

DDR_SDQ60

DDR_SDQ57

DDR_SDQ61

DDR_SDQS7

DDR_SDM7

DDR_SDQ58

DDR_SDQ63 DDR_DQ63

DDR_SDQ59

DDR_SDQ62

DDR_CKE0<5>

DDR_CKE1<5> DDR_CKE1_SR <9>

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

RP3

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP5

1 4

2 3

10_0404_4P2R_5%

RP7

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP9

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP11

1 4

2 3

10_0404_4P2R_5%

RP13

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP15

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP17

1 4

2 3

10_0404_4P2R_5%

RP19

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP21

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

RP23

1 4

2 3

10_0404_4P2R_5%

RP25

1 8

2 7

3 6

4 5

10_0804_8P4R_5%

C

DDR_DQ37

DDR_DQ32

DDR_DQ36

DDR_DQ33

DDR_DQS4

DDR_DM4

DDR_DQ38

DDR_DQ35

DDR_DQ39

DDR_DQ44

DDR_DQ40

DDR_DQ41

DDR_DQ45

DDR_DQS5

DDR_DM5

DDR_DQ46

DDR_DQ47

DDR_DQ43

DDR_DQ49

DDR_DQ48

DDR_DQ53

DDR_DQ52

DDR_DQS6

DDR_DM6

DDR_DQ55

DDR_DQ50

DDR_DQ51

DDR_DQ56

DDR_DQ60

DDR_DQ57

DDR_DQ61

DDR_DQS7

DDR_DM7

DDR_DQ58

DDR_DQ59

DDR_DQ62

1 2

R47 10_0402_5%

1 2

R48 10_0402_5%

DDR_CKE0_SR

DDR_CKE1_SR

C

D

Note:

DDR_SMAA13 Recommend for AMD

Layout note

Place these resistors

close to DIMM0,

all trace length<500 mil

DDR_CKE0_SR <9>

D

E

+2.5V

JP4

1

VREF

3

DDR_DQ5

DDR_DQ1

DDR_DQS0

DDR_DQ2

DDR_DQ6

DDR_DQ8

DDR_DQ9

DDR_DQS1

DDR_DQ14

DDR_DQ15

DDR_CLK5<5>

DDR_CLK5#<5>

DDR_DQ20

DDR_DQ16

DDR_DQS2

DDR_DQ18

DDR_DQ22

DDR_DQ24

DDR_DQ28

DDR_DQS3

DDR_DQ26

DDR_DQ30

DDR_CKE0_SR

DDR_SMAA12

DDR_SMAA9

DDR_SMAA7

DDR_SMAA5

DDR_SMAA3

DDR_SMAA1

DDR_SMAA10

DDR_SBSA0<5,9>

DDR_SWEA#<5,9>

DDR_SCS#0<5,9>

DDR_SBSA0

DDR_SWEA#

DDR_SCS#0

DDR_SMAA13

DDR_DQ33

DDR_DQ36

DDR_DQS4

DDR_DQ34

DDR_DQ38

DDR_DQ40

DDR_DQ44

DDR_DQS5

DDR_DQ42

DDR_DQ46

DDR_DQ48

DDR_DQ49

DDR_DQS6

DDR_DQ54

DDR_DQ55

DDR_DQ60

DDR_DQ56

DDR_DQS7

DDR_DQ63

DDR_DQ58

DIMM_SMDATA<9,12>

DIMM_SMCLK<9,12>

+3VS

E

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

AMP_1565918-1

VSS

DQ0

DQ1

VDD

DQS0

DQ2

VSS

DQ3

DQ8

VDD

DQ9

DQS1

VSS

DQ10

DQ11

VDD

CK0

CK0#

VSS

DQ16

DQ17

VDD

DQS2

DQ18

VSS

DQ19

DQ24

VDD

DQ25

DQS3

VSS

DQ26

DQ27

VDD

CB0

CB1

VSS

DQS8

CB2

VDD

CB3

DU

VSS

CK2

CK2#

VDD

CKE1

DU/A13

A12

A9

VSS

A7

A5

A3

A1

VDD

A10/AP

BA0

WE#

S0#

DU

VSS

DQ32

DQ33

VDD

DQS4

DQ34

VSS

DQ35

DQ40

VDD

DQ41

DQS5

VSS

DQ42

DQ43

VDD

VDD

VSS

VSS

DQ48

DQ49

VDD

DQS6

DQ50

VSS

DQ51

DQ56

VDD

DQ57

DQS7

VSS

DQ58

DQ59

VDD

SDA

SCL

VDD_SPD

VDD_ID

F

DU/RESET#

SO-DIMM0

REVERSE

F

VREF

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

DQ12

VDD

DQ13

DM1

VSS

DQ14

DQ15

VDD

VDD

VSS

VSS

DQ20

DQ21

VDD

DM2

DQ22

VSS

DQ23

DQ28

VDD

DQ29

DM3

VSS

DQ30

DQ31

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

VSS

VSS

VDD

VDD

CKE0

DU/BA2

VSS

VDD

BA1

RAS#

CAS#

VSS

DQ36

DQ37

VDD

DM4

DQ38

VSS

DQ39

DQ44

VDD

DQ45

DM5

VSS

DQ46

DQ47

VDD

CK1#

CK1

VSS

DQ52

DQ53

VDD

DM6

DQ54

VSS

DQ55

DQ60

VDD

DQ61

DM7

VSS

DQ62

DQ63

VDD

SA0

SA1

SA2

G

+2.5V

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

A11

102

A8

104

106

A6

108

A4

110

A2

112

A0

114

116

118

120

122

S1#

124

DU

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DU

20mil

DDR_DQ0

DDR_DQ4

DDR_DM0

DDR_DQ7

DDR_DQ3

DDR_DQ12

DDR_DQ13

DDR_DM1

DDR_DQ10

DDR_DQ11

DDR_DQ17

DDR_DQ21

DDR_DM2

DDR_DQ19

DDR_DQ23

DDR_DQ29

DDR_DQ25

DDR_DM3

DDR_DQ27

DDR_DQ31

DDR_CKE0_SR

DDR_SMAA11

DDR_SMAA8

DDR_SMAA6

DDR_SMAA4

DDR_SMAA2

DDR_SMAA0

DDR_SBSA1

DDR_SRASA#

DDR_SCASA#

DDR_SCS#1

DDR_DQ32

DDR_DQ37

DDR_DM4

DDR_DQ39

DDR_DQ35

DDR_DQ45

DDR_DQ41

DDR_DM5

DDR_DQ43

DDR_DQ47

DDR_DQ52

DDR_DQ53

DDR_DM6

DDR_DQ51

DDR_DQ50

DDR_DQ61

DDR_DQ57

DDR_DM7

DDR_DQ62

DDR_DQ59

Compal Electronics, Inc.

Title

DDR-SODIMM SLOT0

Size Document Number Rev

Custom

LA-1851

Date: Sheet of

G

+1.25VREF_MEM

1

C119

0.1U_0402_10V6K

2

DDR_DQ[0..63]

DDR_DQS[0..7]

DDR_DM[0..7]

DDR_SBSA1 <5,9>

DDR_SRASA# <5,9>

DDR_SCASA# <5,9>

DDR_SCS#1 <5,9>

DDR_CLK7# <5>

DDR_CLK7 <5>

H

DDR_DQ[0..63] <9>

DDR_DQS[0..7] <9>

DDR_DM[0..7] <9>

8 50Thursday, October 16, 2003

H

0.5

Page 9

A

+1.25V +1.25V

DDR_DQ0

DDR_DQ5

DDR_DQ4

DDR_DQ1

1 1

DDR_DM0

DDR_DQS0

DDR_DQ7

DDR_DQ2

DDR_DQ3

DDR_DQ6

DDR_DQ12

DDR_DQ13

DDR_DQ8

DDR_DQ9

DDR_DM1

DDR_DQS1

2 2

DDR_DQ10

DDR_DQ11

DDR_DQ14

DDR_DQ15

DDR_DQ17

DDR_DQ20 DDR_DQ40

DDR_DQ21

DDR_DQ16

DDR_DQS2

DDR_DM2

DDR_DQ19

DDR_DQ18

DDR_DQ22

DDR_DQ23

3 3

4 4

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

RP27

68_0804_8P4R_5%

RP31

68_0402_4P2R_5%

RP35

68_0804_8P4R_5%

RP39

68_0804_8P4R_5%

RP43

68_0402_4P2R_5%

RP47

68_0804_8P4R_5%

RP51

68_0804_8P4R_5%

RP54

68_0402_4P2R_5%

RP57

68_0804_8P4R_5%

DDR_DQS[0..7]<8>

DDR_DQ[0..63]<8>

DDR_DM[0..7]<8>

DDR_SMAA[0..13]<5,8>

18

27

36

45

14

23

18

27

36

45

18

27

36

45

14

23

18

27

36

45

18

27

36

45

14

23

18

27

36

45

A

RP28

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP32

1 4

2 3

68_0402_4P2R_5%

RP36

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP40

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP44

1 4

2 3

68_0402_4P2R_5%

RP48

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP52

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP55

1 4

2 3

68_0402_4P2R_5%

RP58

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

DDR_DQS[0..7]

DDR_DQ[0..63]

DDR_DM[0..7]

DDR_SMAA[0..13]

DDR_DQ29

DDR_DQ24

DDR_DQ25

DDR_DQ28

DDR_DM3

DDR_DQS3

DDR_DQ27

DDR_DQ31

DDR_DQ26

DDR_DQ30

DDR_DQ32

DDR_DQ33

DDR_DQ36

DDR_DQ37

DDR_DQS4

DDR_DM4

DDR_DQ34

DDR_DQ38

DDR_DQ35

DDR_DQ45

DDR_DQ41

DDR_DQ44

DDR_DQS5

DDR_DM5

DDR_DQ43

DDR_DQ47

DDR_DQ42

DDR_DQ46

RP29

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP33

1 4

2 3

68_0402_4P2R_5%

RP37

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP41

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

RP45

1 4

2 3

68_0402_4P2R_5%

RP49

1 8

2 7

3 6

4 5

68_0804_8P4R_5%

Layout note

Place these resistor

closely DIMM1,

all trace

length<=800mil

100_0402_1%

100_0402_1%

DDR_DQ52

DDR_DQ48

DDR_DQ53

DDR_DQ49

DDR_DM6

DDR_DQS6

DDR_DQ51

DDR_DQ54

DDR_DQ50

DDR_DQ55

DDR_DQ61

DDR_DQ57

DDR_DQ60

DDR_DQ56

DDR_DQS7

DDR_DM7

DDR_DQ63

DDR_DQ58DDR_DQ39

DDR_DQ62

DDR_DQ59

R49

R50

+2.5V

12

12

B

+1.25VREF_MEM

1

C121

2

0.1U_0402_10V6K

B

DDR_CKE1_SR<8>

Note:

DDR_SMAA13 Recommend

for AMD.

DDR_SBSA0<5,8>

DDR_SWEA#<5,8>

1

C122

1000P_0402_50V7K

2

DIMM_SMDATA<8,12>

C

+2.5V

DDR_DQ0

DDR_DQ4

DDR_DQS0

DDR_DQ7

DDR_DQ3

DDR_DQ12

DDR_DQ13

DDR_DQS1

DDR_DQ11

DDR_CLK4<5>

DDR_CLK4#<5>

DDR_DQ17

DDR_DQ21

DDR_DQS2

DDR_DQ23

DDR_DQ29

DDR_DQ25

DDR_DQS3

DDR_DQ27

DDR_DQ31

DDR_CKE1_SR DDR_CKE1_SR

DDR_SMAA12

DDR_SMAA9

DDR_SMAA7

DDR_SMAA5

DDR_SMAA3

DDR_SMAA1

DDR_SMAA10

DDR_SBSA0

DDR_SWEA#

DDR_SCS#2<5>

DIMM_SMCLK<8,12>

DDR_SCS#2 DDR_SCS#3

DDR_SMAA13

DDR_DQ32

DDR_DQ37

DDR_DQS4

DDR_DQ39

DDR_DQ35

DDR_DQ45

DDR_DQ41

DDR_DQS5

DDR_DQ47

DDR_DQ52

DDR_DQ53

DDR_DQS6

DDR_DQ51

DDR_DQ50

DDR_DQ61

DDR_DQ57

DDR_DQS7

DDR_DQ62

DDR_DQ59

+3VS

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

JP5

VREF

VSS

DQ0

DQ1

VDD

DQS0

DQ2

VSS

DQ3

DQ8

VDD

DQ9

DQS1

VSS

DQ10

DQ11

VDD

CK0

CK0#

VSS

DQ16

DQ17

VDD

DQS2

DQ18

VSS

DQ19

DQ24

VDD

DQ25

DQS3

VSS

DQ26

DQ27

VDD

CB0

CB1

VSS

DQS8

CB2

VDD

CB3

DU

VSS

CK2

CK2#

VDD

CKE1

DU/A13

A12

A9

VSS

A7

A5

A3

A1

VDD

A10/AP

BA0

WE#

S0#

DU

VSS

DQ32

DQ33

VDD

DQS4

DQ34

VSS

DQ35

DQ40

VDD

DQ41

DQS5

VSS

DQ42

DQ43

VDD

VDD

VSS

VSS

DQ48

DQ49

VDD

DQS6

DQ50

VSS

DQ51

DQ56

VDD

DQ57

DQS7

VSS

DQ58

DQ59

VDD

SDA

SCL

VDD_SPD

VDD_ID

AMP_1565917-1

DIMM1

DU/RESET#

DU/BA2

STANDARD

C

VREF

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

DQ12

VDD

DQ13

DM1

VSS

DQ14

DQ15

VDD

VDD

VSS

VSS

DQ20

DQ21

VDD

DM2

DQ22

VSS

DQ23

DQ28

VDD

DQ29

DM3

VSS

DQ30

DQ31

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

VSS

VSS

VDD

VDD

CKE0

A11

VSS

VDD

BA1

RAS#

CAS#

S1#

VSS

DQ36

DQ37

VDD

DM4

DQ38

VSS

DQ39

DQ44

VDD

DQ45

DM5

VSS

DQ46

DQ47

VDD

CK1#

CK1

VSS

DQ52

DQ53

VDD

DM6

DQ54

VSS

DQ55

DQ60

VDD

DQ61

DM7

VSS

DQ62

DQ63

VDD

SA0

SA1

SA2

D

+2.5V

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

A8

104

106

A6

108

A4

110

A2

112

A0

114

116

118

120

122

124

DU

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DU

50 mil width

DDR_DQ5

DDR_DQ1

DDR_DM0

DDR_DQ2

DDR_DQ6

DDR_DQ8

DDR_DQ9

DDR_DM1

DDR_DQ14DDR_DQ10

DDR_DQ15

DDR_DQ20

DDR_DQ16

DDR_DM2

DDR_DQ18DDR_DQ19

DDR_DQ22

DDR_DQ24

DDR_DQ28

DDR_DM3

DDR_DQ26

DDR_DQ30

DDR_SMAA11

DDR_SMAA8

DDR_SMAA6

DDR_SMAA4

DDR_SMAA2

DDR_SMAA0

DDR_SBSA1

DDR_SRASA#

DDR_SCASA#

DDR_DQ33

DDR_DQ36

DDR_DM4

DDR_DQ34

DDR_DQ38

DDR_DQ40

DDR_DQ44

DDR_DM5

DDR_DQ42DDR_DQ43

DDR_DQ46

DDR_DQ48

DDR_DQ49

DDR_DM6

DDR_DQ54

DDR_DQ55

DDR_DQ60

DDR_DQ56

DDR_DM7

DDR_DQ63

DDR_DQ58

D

+1.25VREF_MEM

1

C120

0.1U_0402_10V6K

2

DDR_SCS#1<5,8>

DDR_SCS#0<5,8>

DDR_CKE0_SR<8>

DDR_SBSA1 <5,8>

DDR_SRASA# <5,8>

DDR_SCASA# <5,8>

DDR_SCS#3 <5>

DDR_CLK6# <5>

DDR_CLK6 <5>

+3VS

Compal Electronics, Inc.

Title

DDR-SODIMM SLOT1

Size Document Number Rev

Custom

LA-1851

Date: Sheet of

E

DDR_SMAA7

DDR_SMAA9

DDR_SMAA12

DDR_SMAA11

DDR_SMAA4

DDR_SMAA6

DDR_SMAA5

DDR_SMAA8

DDR_SMAA0

DDR_SMAA2

DDR_SMAA1

DDR_SMAA3

DDR_SMAA13

DDR_SMAA10

DDR_SCS#1

DDR_SCS#3

DDR_SCASA#

DDR_SCS#0

DDR_SCS#2

DDR_SWEA#

DDR_SBSA0

DDR_SRASA#

DDR_SBSA1

DDR_CKE0_SR

DDR_CKE1_SR

RP26

47_0804_8P4R_5%

RP30

47_0804_8P4R_5%

RP34

47_0804_8P4R_5%

1 2

R479 47_0402_5%

1 2

R480 47_0402_5%

RP42

47_0804_8P4R_5%

RP46

47_0804_8P4R_5%

1 2

R481 47_0402_5%

1 2

R482 68_0402_5%

1 2

R483 68_0402_5%

Layout note

Place these resistor

close by DIMM1,

all trace length

Max=0.8"

9 50Thursday, October 16, 2003

E

+1.25V

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

0.5

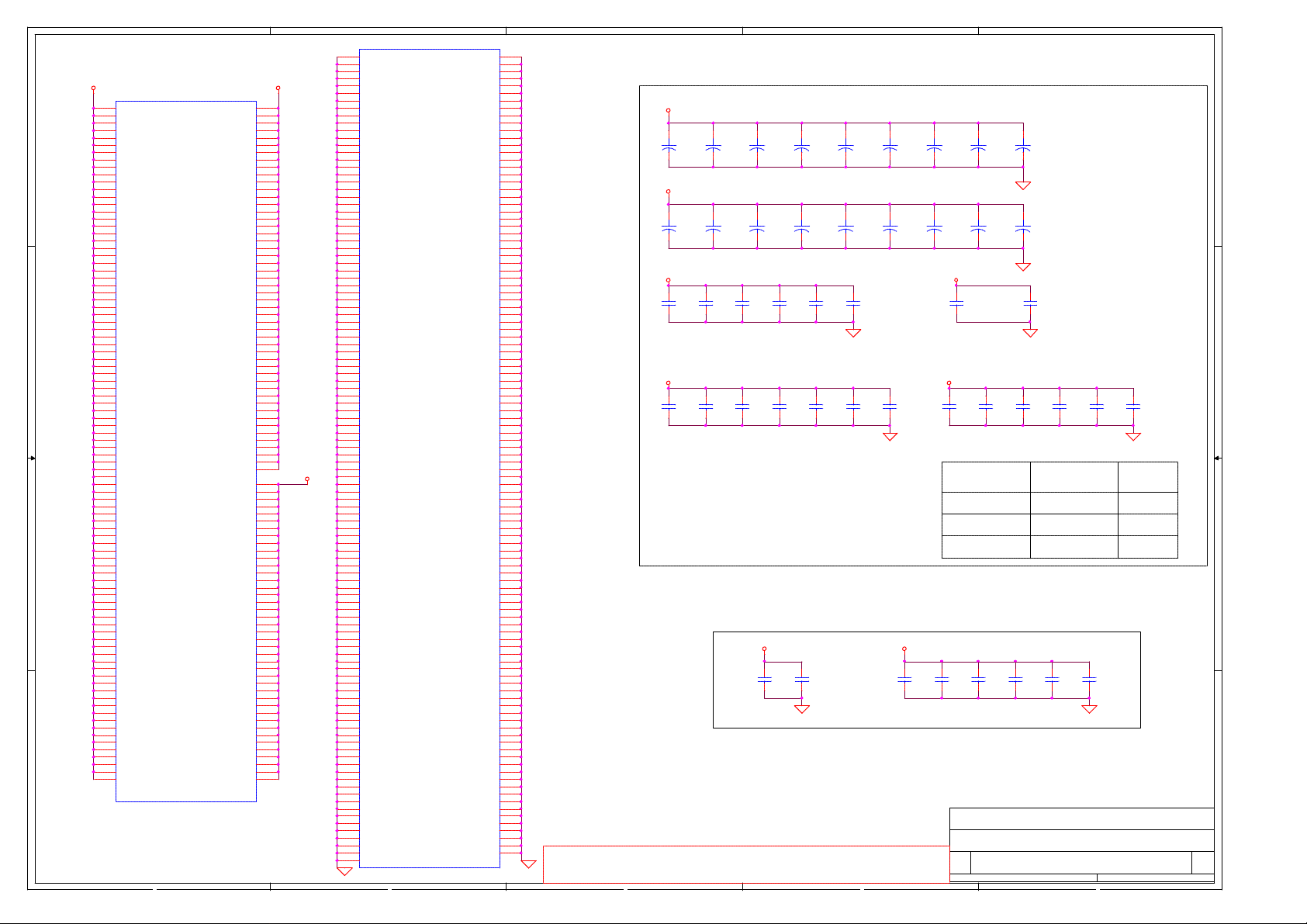

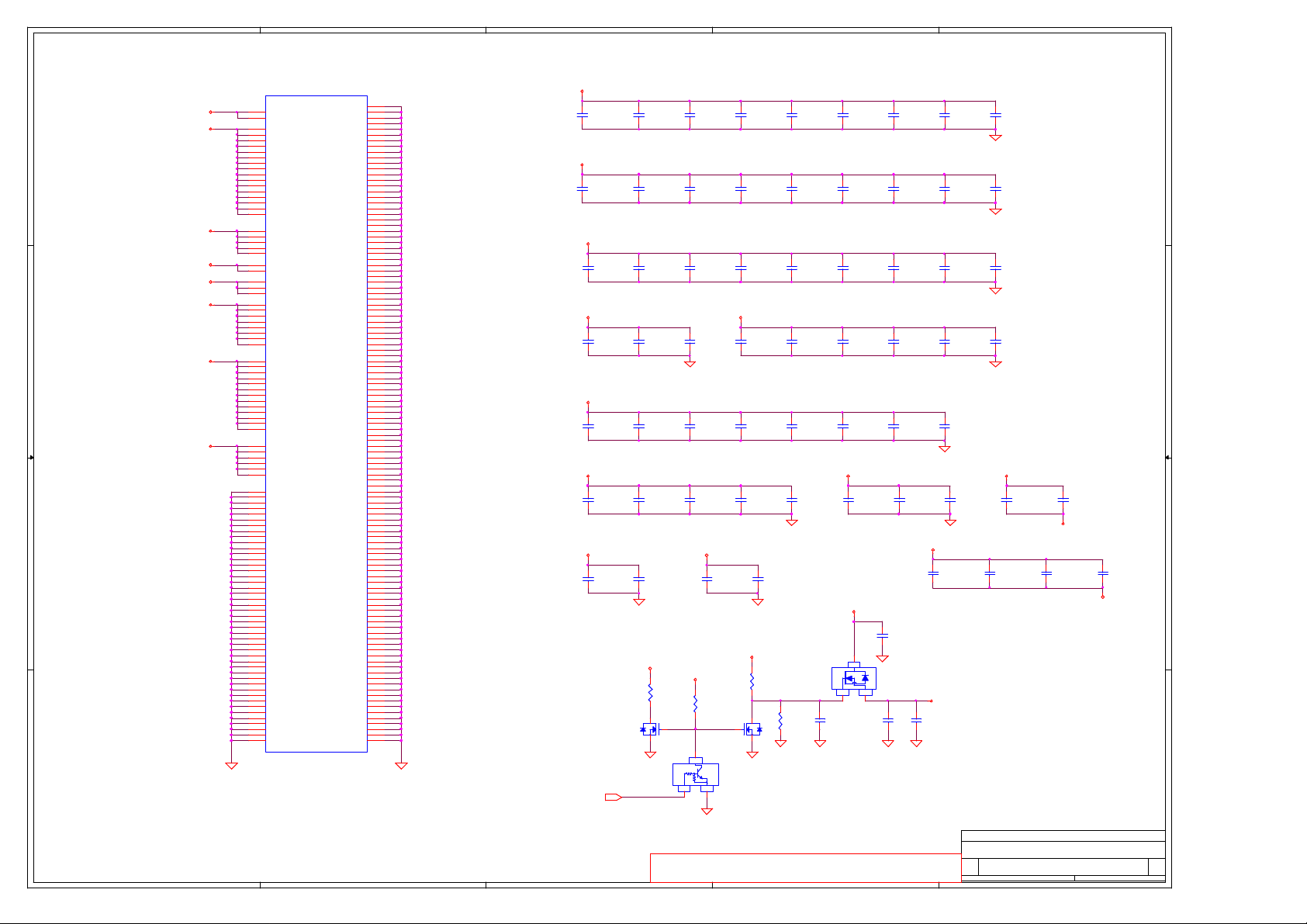

Page 10

A

B

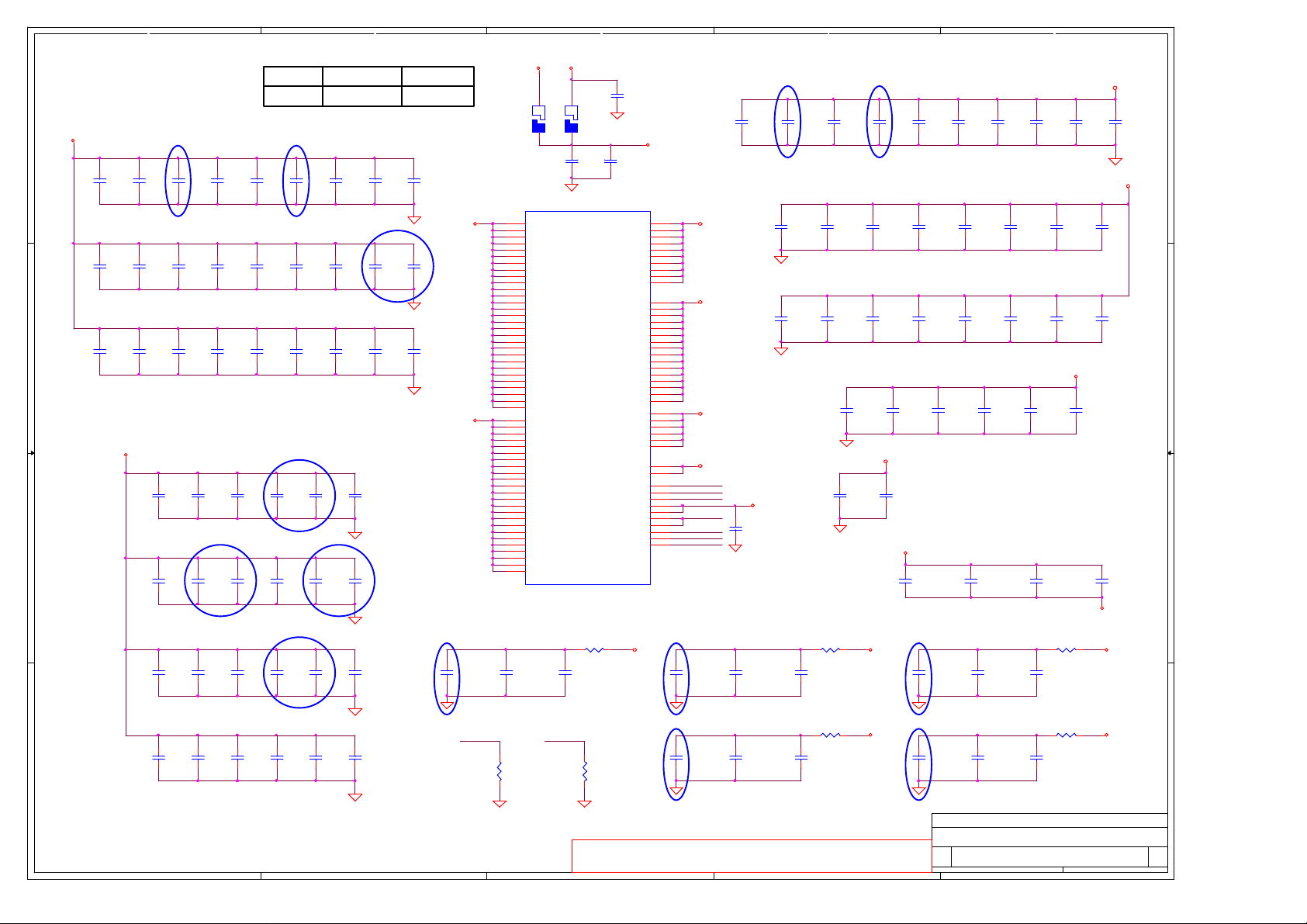

C

D

E

+2.5V

470U_D_4VM

1

1 1

1

2

470U_D_4VM

+

+

C123

C124

2

1

+

2

470U_D_4VM

@220U_D2_4VM

C125

1

+

2

C126

4.7U_0805_6.3V6K

1

C127

2

4.7U_0805_6.3V6K

1

C128

2

Near DIMMs

Layout note :

Place one cap close to every 2 pull up resistors termination to

+1.25VS

+1.25V

0.1U_0402_10V6K

1

C131

2

2 2

0.1U_0402_10V6K

+1.25V

1

C143

2

0.1U_0402_10V6K

+1.25V

1

C155

2

0.1U_0402_10V6K

+1.25V

3 3

1

C167

2

0.1U_0402_10V6K

+1.25V

1

C179

2

0.1U_0402_10V6K

+1.25V

1

4 4

C191

2

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

A

1

C132

2

0.1U_0402_10V6K

1

C144

2

0.1U_0402_10V6K

1

C156

2

0.1U_0402_10V6K

1

C168

2

0.1U_0402_10V6K

1

C180

2

0.1U_0402_10V6K

1

C192

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C133

2

1

C145

2

1

C157

2

1

C169

2

1

C181

2

1

C193

2

1

C134

2

0.1U_0402_10V6K

1

C146

2

0.1U_0402_10V6K

1

C158

2

0.1U_0402_10V6K

1

C170

2

0.1U_0402_10V6K

1

C182

2

0.1U_0402_10V6K

1

C194

2

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C135

2

1

C147

2

1

C159

2

1

C171

2

1

C183

2

1

C195

2

B

1

C136

2

0.1U_0402_10V6K

1

C148

2

0.1U_0402_10V6K

1

C160

2

0.1U_0402_10V6K

1

C172

2

0.1U_0402_10V6K

1

C184

2

0.1U_0402_10V6K

1

C196

2

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C137

2

1

C149

2

1

C161

2

1

C173

2

1

C185

2

1

C197

2

1

C138

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C150

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C162

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C174

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C186

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C198

2

0.1U_0402_10V6K

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

0.1U_0402_10V6K

1

C139

2

1

C151

2

1

C163

2

1

C175

2

1

C187

2

1

C199

2

1

C140

2

0.1U_0402_10V6K

1

C152

2

0.1U_0402_10V6K

1

C164

2

0.1U_0402_10V6K

1

C176

2

0.1U_0402_10V6K

1

C188

2

0.1U_0402_10V6K

1

C200

2

+2.5V

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C141

2

1

C153

2

1

C177

2

1

C189

2

1

C142

2

0.1U_0402_10V6K

1

C154

2

0.1U_0402_10V6K

1

C178

2

+2.5V

0.1U_0402_10V6K

1

C190

2

+2.5V

D

+1.25V

10U_1206_6.3V7K

1

2

10U_1206_6.3V7K

Title

Size Document Number Rev

Custom

Date: Sheet of

1

C165

C166

2

Compal Electronics, Inc.

DDR SODIMM Decoupling

LA-1851

E

10 50Thursday, October 16, 2003

0.5

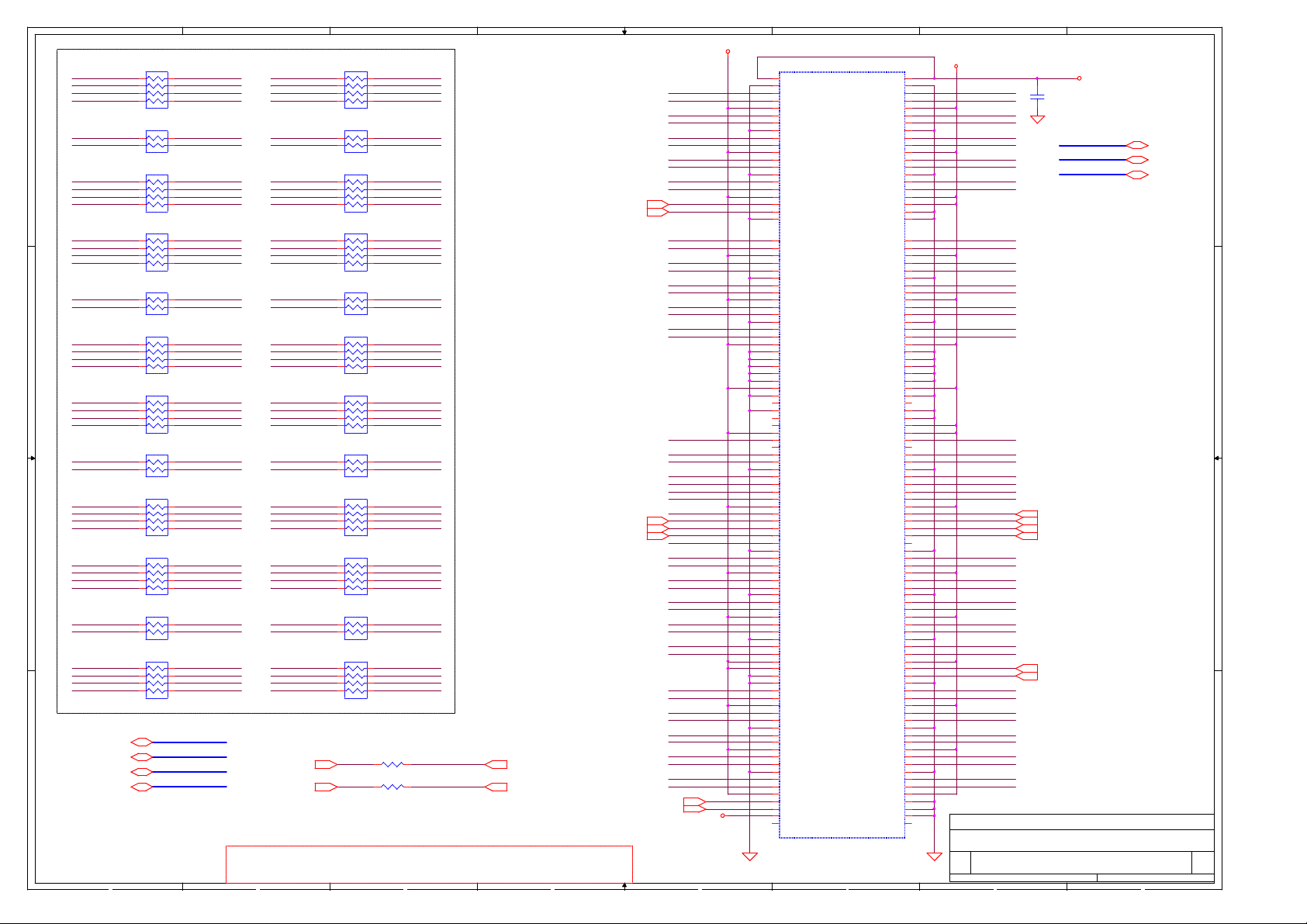

Page 11

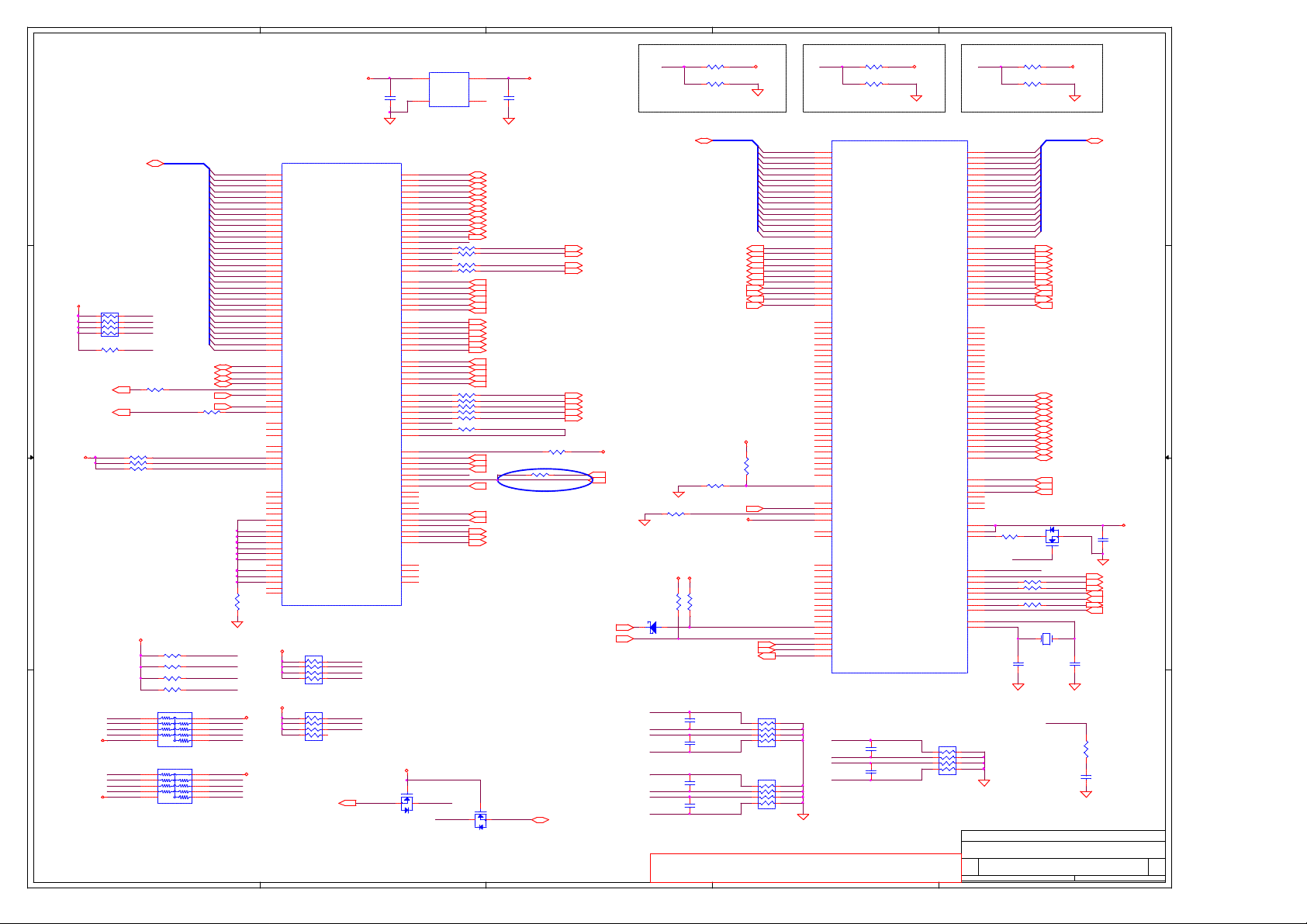

5

4

3

2

1

+3VS

12

R68

10K_0402_5%

12

R71

549_0402_1%

H_CADOP[0..15]

H_CADON[0..15]

H_CADIP[0..15]

H_CADIN[0..15]

H_CADIP0

H_CADIP1

H_CADIP2

H_CADIP3

H_CADIP4

H_CADIP5

H_CADIP6

H_CADIP7

H_CADIP8

H_CADIP9

H_CADIP10

H_CADIP11

H_CADIP12

H_CADIP13

H_CADIP14

H_CADIP15

H_CADIN0

H_CADIN1

H_CADIN2

H_CADIN3

H_CADIN4

H_CADIN5

H_CADIN6

H_CADIN7

H_CADIN8

H_CADIN9

H_CADIN10

H_CADIN11

H_CADIN12

H_CADIN13

H_CADIN14

H_CADIN15

H_CLKIP0

H_CLKIN0

H_CLKIP1

H_CLKIN1

H_CTLIP0

H_CTLIN0

LDTSTOP#

GATEA20

H_THERMTRIP#

H_RST#

H_PWRGD

CPU_COMP

U4A

AP18

HT1_TXD0

AP17

HT1_TXD1

AN16

HT1_TXD2

AP15

HT1_TXD3

AN13

HT1_TXD4

AP12

HT1_TXD5

AP11

HT1_TXD6

AN10

HT1_TXD7

AL18

HT1_TXD8

AJ16

HT1_TXD9

AJ15

HT1_TXD10

AL15

HT1_TXD11

AJ13

HT1_TXD12

AL12

HT1_TXD13

AJ12

HT1_TXD14

AJ10

HT1_TXD15

AN18

HT1_TXD0#

AN17

HT1_TXD1#

AM16

HT1_TXD2#

AN15

HT1_TXD3#

AM13

HT1_TXD4#

AN12

HT1_TXD5#

AN11

HT1_TXD6#

AM10

HT1_TXD7#

AM18

HT1_TXD8#

AK16

HT1_TXD9#

AK15

HT1_TXD10#

AM15

HT1_TXD11#

AK13

HT1_TXD12#

AM12

HT1_TXD13#

AK12

HT1_TXD14#

AJ11

HT1_TXD15#

AP14

HT1_TXCLK0

AN14

HT1_TXCLK0#

AJ14

HT1_TXCLK1

AK14

HT1_TXCLK1#

AP9

HT1_TXCTL

AN9

HT1_TXCTL#

AK17

HT1_STOP#

AN29

HT2_TXD0/NC

AM28

HT2_TXD1/NC

AN27

HT2_TXD2/NC

AN26

HT2_TXD3/NC

AP29

HT2_TXD0#/NC

AN28

HT2_TXD1#/NC

AP27

HT2_TXD2#/NC

AP26

HT2_TXD3#/NC

AM25

HT2_TXCLK0/NC

AN25

HT2_TXCLK0#/NC

AP30

HT2_TXCTL/NC

AN30

HT2_TXCTL#/NC

AM29

HT2_RSET/NC

F9

A20GATE/GPIO50

AJ19

THERMTRIP#/GPIO59

AL20

CPU_RST#

AK19

CPU_PWROK

AP20

CPU_COMP

CRUSHK8G A01_PBGA708

CrushK8M/G/GM

HT1_RXD10

HT1_RXD11

HT1_RXD12

HT1_RXD13

HT1_RXD14

HT1_RXD15

HT1_RXD0#

HT1_RXD1#

HyperTransport Interface

ONLY FOR CrushK8GM

,CrushK8M/G is "NC"

pin

HT1_RXD2#

HT1_RXD3#

HT1_RXD4#

HT1_RXD5#

HT1_RXD6#

HT1_RXD7#

HT1_RXD8#

HT1_RXD9#

HT1_RXD10#

HT1_RXD11#

HT1_RXD12#

HT1_RXD13#

HT1_RXD14#

HT1_RXD15#

HT1_RXCLK0

HT1_RXCLK0#

HT1_RXCLK1

HT1_RXCLK1#

HT1_RXCTL

HT1_RXCTL#

HT2_RXD0/NC

HT2_RXD1/NC

HT2_RXD2/NC

HT2_RXD3/NC

HT2_RXD0#/NC

HT2_RXD1#/NC

HT2_RXD2#/NC

HT2_RXD3#/NC

HT2_RXCLK0/NC

HT2_RXCLK0#/NC

HT2_RXCTL/NC

HT2_RXCTL#/NC

HT2_STOP#/NC

HT2_REQ#/NC

CPUVDD_EN

HT1VDD_EN

HT1_RXD0

HT1_RXD1

HT1_RXD2

HT1_RXD3

HT1_RXD4

HT1_RXD5

HT1_RXD6

HT1_RXD7

HT1_RXD8

HT1_RXD9

HT1_RSET

HT1_VLD#

MEM_VLD#

CPU_VLD#

CPU_CLK

CPU_CLK#

AL1

AM1

AN1

AN2

AN4

AN5

AN6

AM7

AM4

AL5

AJ5

AL6

AJ7

AJ8

AK10

AM9

AL2

AM2

AP1

AP2

AP4

AP5

AP6

AN7

AM3

AL4

AK5

AK6

AK7

AK8

AK9

AL9

AN3

AP3

AM6

AM5

AN8

AP8

AL3

AK28

AK27

AL30

AK26

AJ28

AJ27

AL29

AJ26

AL26

AL27

AK29

AJ29

AK25

AJ25

A2

C2

B1

B4

B2

AN19

AM19

H_CADOP0

H_CADOP1

H_CADOP2

H_CADOP3

H_CADOP4

H_CADOP5

H_CADOP6

H_CADOP7

H_CADOP8

H_CADOP9

H_CADOP10

H_CADOP11

H_CADOP12

H_CADOP13

H_CADOP14

H_CADOP15

H_CADON0

H_CADON1

H_CADON2

H_CADON3

H_CADON4

H_CADON5

H_CADON6

H_CADON7

H_CADON8

H_CADON9

H_CADON10

H_CADON11

H_CADON12

H_CADON13

H_CADON14

H_CADON15

H_CLKOP0

H_CLKON0

H_CLKOP1

H_CLKON1

H_CTLOP0

H_CTLON0

H_RSET

VR_ON

HT1VDD_EN

HT1_VLD#

MEM_VLD#

CPU_VLD#

CPU_CLK_R

CPU_CLK_R#

H_CLKOP0 <4>H_CLKIP0<4>

H_CLKON0 <4>

H_CLKOP1 <4>

H_CLKON1 <4>

H_CTLOP0 <4>

H_CTLON0 <4>

12

R63

51.1_0402_1%

VR_ON <6,44>

HT1VDD_EN <13>

HT1_VLD# <36>

MEM_VLD# <36>

CPU_VLD# <36>

1 2

R69 0_0402_5%

1 2

R70 0_0402_5%

+1.5VS

CPU_CLK <6>

CPU_CLK# <6>

U4B

CrushK8M/G/GM

M33

AGP_SBA0#

P32

AGP_SBA1#

P33

AGP_SBA2#

N33

AGP_SBA3#

T33

AGP_SBA4#

T32

AGP_SBA5#

U32

AGP_SBA6#

U33

AGP_SBA7#

R33

AGP_SBSTBF

R34

AGP_ADSTBF0

AGP_ADSTBS0

AGP_ADSTBF1

AGP_ADSTBS1

AGP_C/BE#0

AGP_C/BE#1

AGP_C/BE#2

AGP_C/BE#3

AGP_ST0

AGP_ST1

AGP_ST2

AGP_RBF#<14>

AGP_WBF#<14>

AGP_FRAME#<14>

AGP_IRDY#<14>

AGP_TRDY#<14>

AGP_REQ#<14>

AGP_GNT#<14>

AGP_STOP#<14>

AGP_DEVSEL#<14>

AGP_PAR<14>

AGP_PIPE#<14>

+3VS

R62 51.1_0402_1%

R64 51.1_0402_1%

AGP_RBF#

AGP_WBF#

AGP_FRAME#

AGP_IRDY#

AGP_TRDY#

AGP_REQ#

AGP_GNT#

AGP_STOP#

AGP_DEVESL#

AGP_PAR

1 2

R60 10K_0402_5%

1 2

1 2

+3VS +3VS

VDD_PLL

RTC_XTALIN

RTC_XTALOUT

AGP_SBSTBS

AD32

AGP_ADSTBF0

AC33

AGP_ADSTBS0

AB30

AGP_ADSTBF1

AC30

AGP_ADSTBS1

V33

AGP_CBE0

AG33

AGP_CBE1

AG29