6-40

2 – 50 GHz Distributed Amplifier

Technical Data

Features

• Frequency Range: 2 – 50 GHz

• Small Signal Gain: 8.5 dB

•P

-1dB

@ 40 GHz: 12 dBm

• Noise Figure:

< 6 dB @ 2 – 35 GHz

< 10 dB @ 35 – 50 GHz

• Return Loss: In/Out: < -10 dB

Description

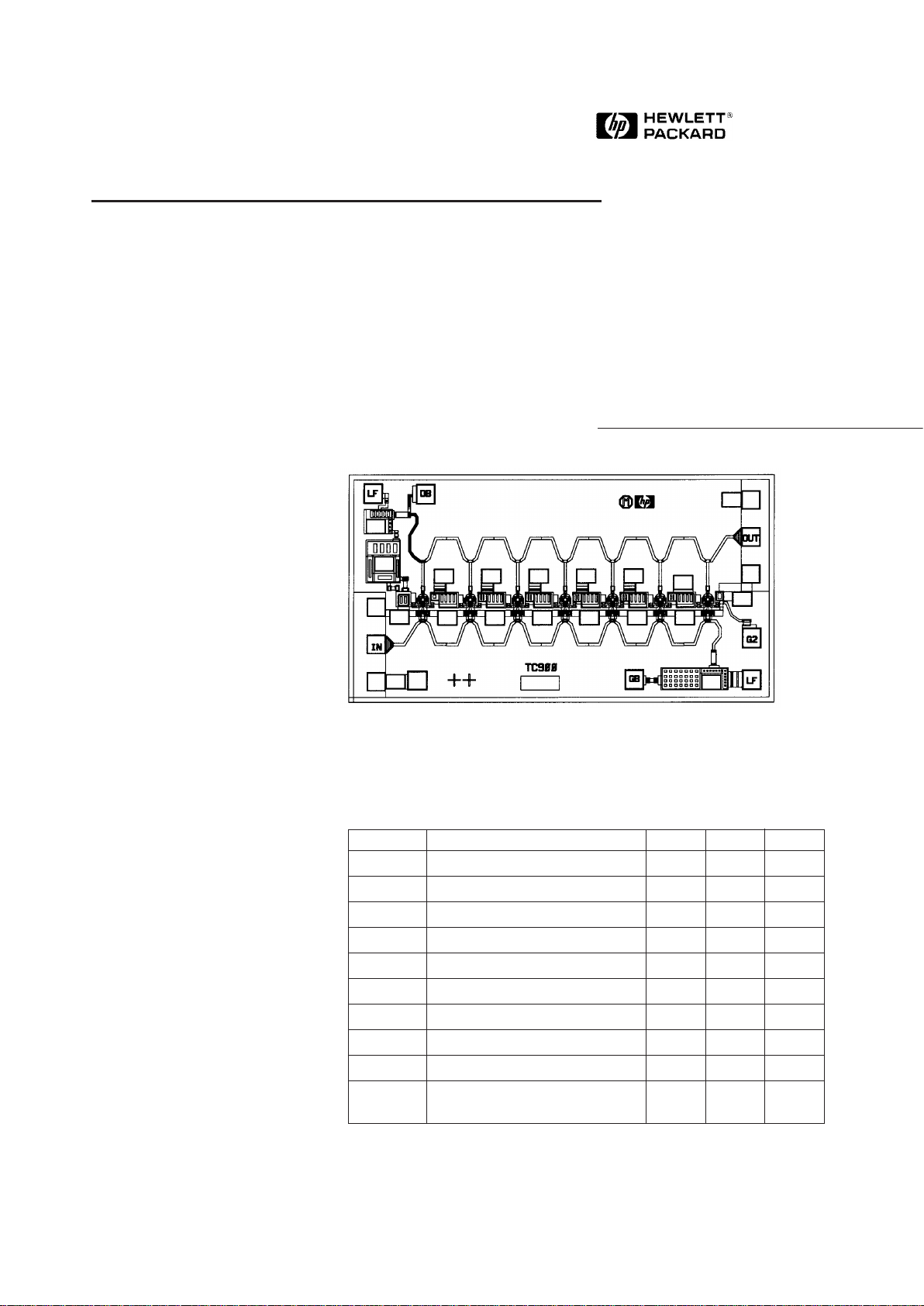

The HMMC-5025 was designed as

a generic wide band distributed

amplifier, covering the frequency

span 2 – 50 GHz. It consists of

seven stages. Each stage is made

up of two cascoded FETs with

gate peripheries of 48 mm per

FET. Both input and output ports

were designed to provide 50 ohm

terminations. Bonding pads are

provided in the layout to allow

amplifier operation at frequencies

lower than 2 GHz by means of

external circuit components.

The HMMC-5025 is typically

biased at VDD = 5 volts and

IDD␣ =␣ 75 mA. The second gate is

internally biased by means of a

voltage divider network and an

a.c. ground.

Chip Size: 1720 x 920 µm (67.7 x 36.2 mils)

Chip Size Tolerance: ± 10 µm (± 0.4 mils)

Chip Thickness: 127 ± 15 µm (5.0 ± 0.6 mils)

Pad Dimensions: 80 x 80 µm (3.2 x 3.2 mils)

HMMC-5025

Absolute Maximum Ratings

[1]

Symbol Parameters/Conditions Units Min. Max.

V

DD

Positive Drain Voltage V 7.0

I

DD

Total Drain Current mA 170

V

G1

First Gate Voltage V -3.5 0

V

G2

Second Gate Voltage mA -3.0 +3.0

P

DC

DC Power Dissipation watts 1.2

P

in

CW Input Power dBm 20

T

ch

Operating Channel Temp. °C +150

T

case

Operating Case Temp. °C -55

T

STG

Storage Temperature °C -6 5 +165

T

max

Maximum Assembly Temp.

°C +300

(for 60 seconds maximum)

Note:

1. Operation in excess of any one of these conditions may result in permanent

damage to this device. T

A

= 25° C except for T

ch

, T

STG

, and T

max

.

5965-5446E

6-41

HMMC-5025 DC Specifications/Physical Properties

[1]

Symbol Parameters and Test Conditions Units Min. Typ. Max.

I

DSS

Saturated Drain Current mA 130 150 170

(VDD = 5.0 V, VG1 = 0.0 V, VG2 = open circuit)

V

p

First Gate Pinch-off Voltage V -1.7 -0.5

(VDD = 5.0 V, IDD = 15 mA, VG2 = open circuit)

V

G2

Second Gate Self-Bias Voltage V 2

(VDD = 5.0 V, IDD = 75 mA)

I

DSOFF(VG1

) First Gate Pinch-off Current mA 6 10

(VDD = 5.0 V, VG1 = -3.5 V, VG2 = open circuit)

I

DSOFF(VG2

) Second Gate Pinch-off Current mA 10

(VDD = 5.0 V, IDD = 75 mA, VG2 = -3.5 V)

θ

ch-bs

Thermal Resistance (T

backside

= 25° C) °C/W 63

Note:

1. Measured in wafer form with T

chuck

= 25°C. (Except θ

ch-bs

.)

HMMC-5025 RF Specifications

[1]

, V

DD

= 5.0 V, IDD(Q) = 75 mA, Zin = Z

o

= 50 Ω

Symbol Parameters and Test Conditions Units Min. Typ. Max.

BW Guaranteed Bandwidth

[2]

GHz 2 50

S

21

Small Signal Gain dB 7.0 8.5

∆ S

21

Small Signal Gain Flatness dB ±0.75 ± 1.5

RL

in

Input Return Loss dB 10 15

RL

out

Output Return Loss dB 10 15

S

12

Reverse Isolation dB 20 30

P

-1dB

Output Power @ 1dB Gain Compression @ 40 GHz dBm 12

P

sat

Saturated Output Power @ 40 GHz dBm 16

H

2

Second Harmonic Power Level (2 < ƒo < 26) dBc -35

Po(ƒo) = 10 dBm

H

3

Third Harmonic Power Level (2 < ƒo < 20) dBc -25

Po(ƒo) = 10 dBm

NF Noise Figure (2 – 35 GHz) dB 5.0

Noise Figure (35 – 50 GHz) 7.0

Notes:

1. Small-signal data measured in wafer form with T

chuck

= 25°C. Harmonic data measured on individual devices mounted

in a microcircuit package at T

A

= 25° C.

2. Performance may be extended to lower frequencies through the use of appropriate off-chip circuitry.

6-42

HMMC-5025 Applications

The HMMC-5025 traveling wave

amplifier is designed for use as a

general purpose wideband power

stage in communication systems

and microwave instrumentation.

It is ideally suited for broadband

applications requiring a flat gain

response and excellent port

matches over a 2 to 50 GHz

frequency range. Dynamic gain

control and low-frequency

extension capabilities are

designed into these devices.

Biasing and Operation

These amplifiers are biased with

a single positive drain supply

(VDD) and a single negative gate

supply (VG1). The recommended

bias conditions for best performance for the HMMC-5025 are

VDD = 5.0 V, IDD = 75 mA. To

achieve these drain current

levels, VG1 is typically biased

between -0.2V and -0.6 V. No other

bias supplies or connections to

the device are required for 2 to

50␣ GHz operation. The gate

voltage (VG1) should be applied

prior to the drain voltage (VDD)

during power up and removed

after the drain voltage during

power down.

The auxiliary gate and drain

contacts are used only for lowfrequency performance extension

below ≈ 1.0 GHz. When used,

these contacts must be AC

coupled only. (Do not attempt to

apply bias to these pads.)

The second gate (VG2) can be

used to obtain 30 dB (typical)

dynamic gain control. For normal

operation, no external bias is

required on this contact.

Assembly Techniques

Solder die-attach using a fluxless

AuSu solder preform is the

recommended assembly method.

Gold thermosonic wedge bonding

with 0.7 mil diameter Au wire is

recommended for all bonds. Tool

force should be 22 ± 1 gram, stage

temperature should be 150 ± ␣2°C,

and ultrasonic power and dura-

tion should be 64 ± 1 dB and

76␣ ± ␣ 8 msec, respectively. The

bonding pad and chip backside

metallization is gold.

For more detailed information

see HP application note #999

“GaAs MMIC Assembly and

Handling Guidelines.”

GaAs MMICs are ESD sensitive.

Proper precautions should be used

when handling these devices.

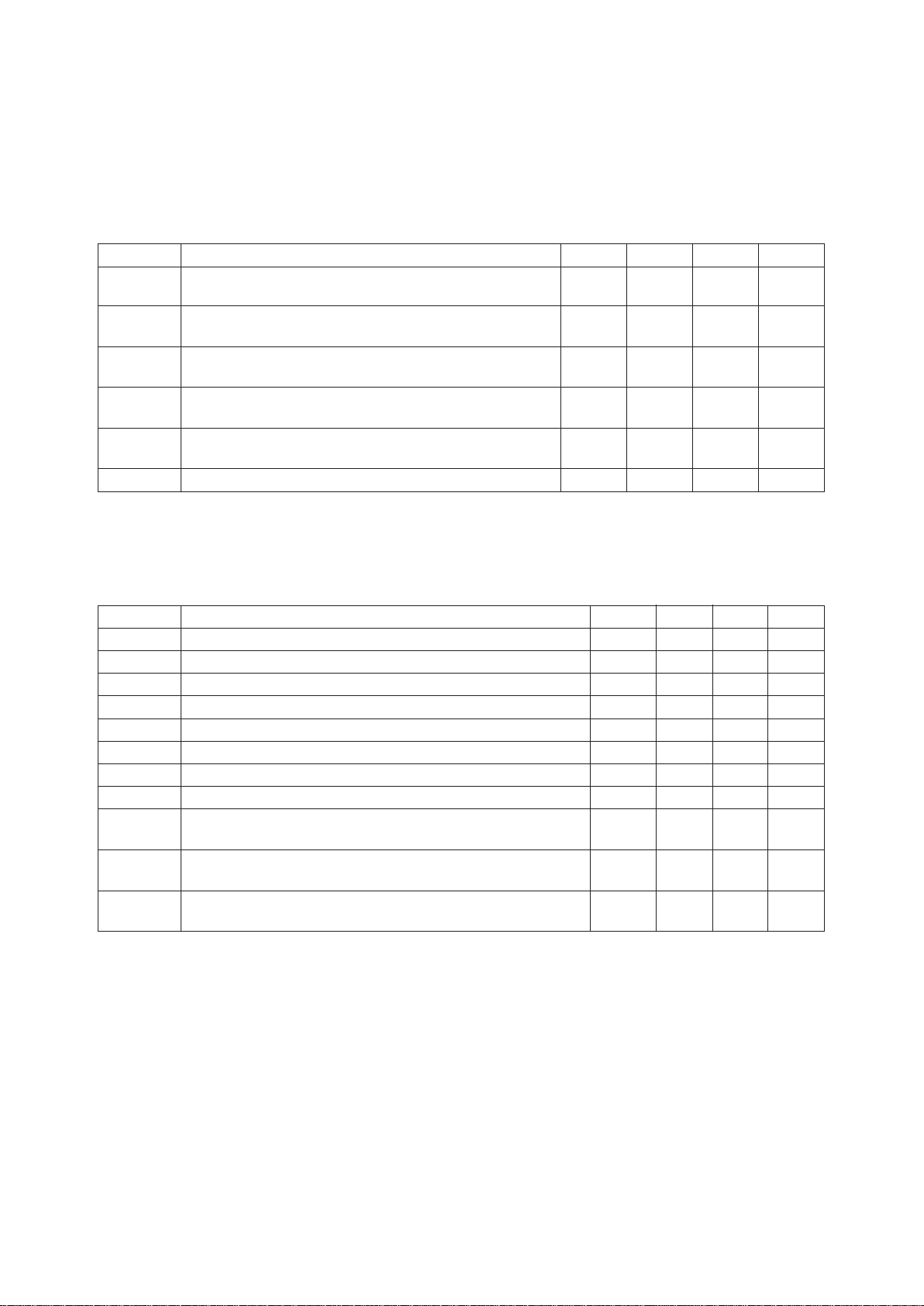

Figure 1. HMMC-5025 Schematic.

Gate

Bias

Low Frequency

Extension

Second Gate

Bias

RF OUTPUT

Low Frequency

Extension

15

15 1.5

4708.5

RF INPUT

GND

340

50

350

9.2

50

8.5

6

Drain

Bias

Seven Identical Stages

Loading...

Loading...